Synaptic transistor based on two-dimensional and three-dimensional perovskite composite structure and preparation method of synaptic transistor

A composite structure and transistor technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as limiting device performance, gate voltage failure, and difficulty in obtaining high-performance three-terminal synaptic transistors, etc., to achieve Avoid ion shielding effect, rapid migration effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

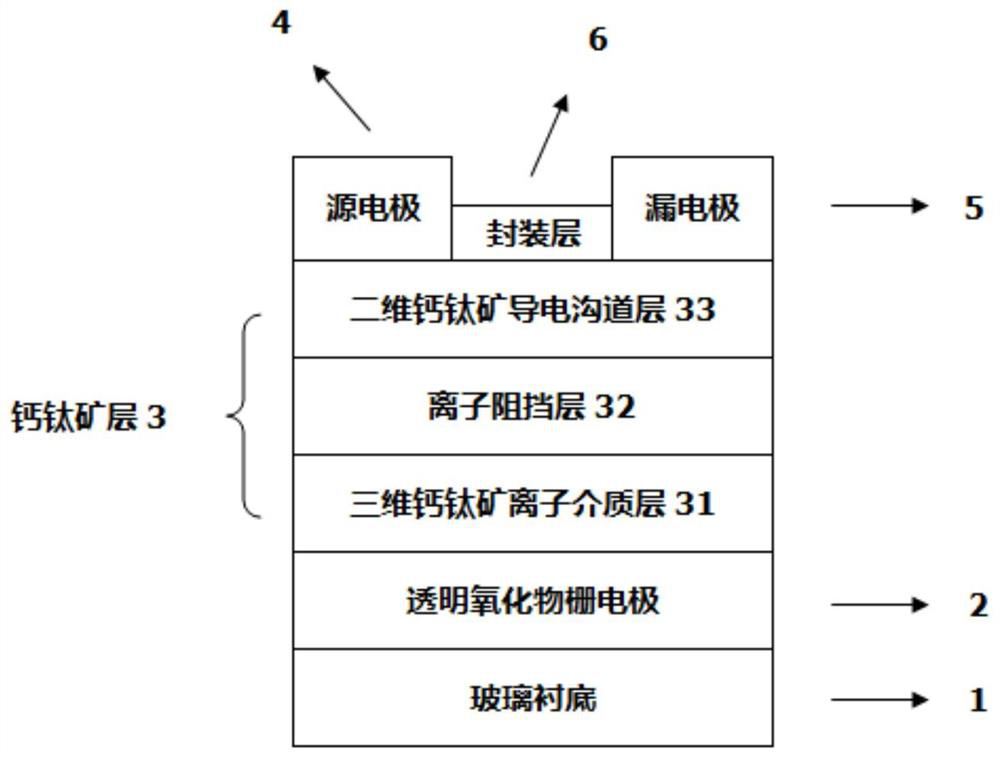

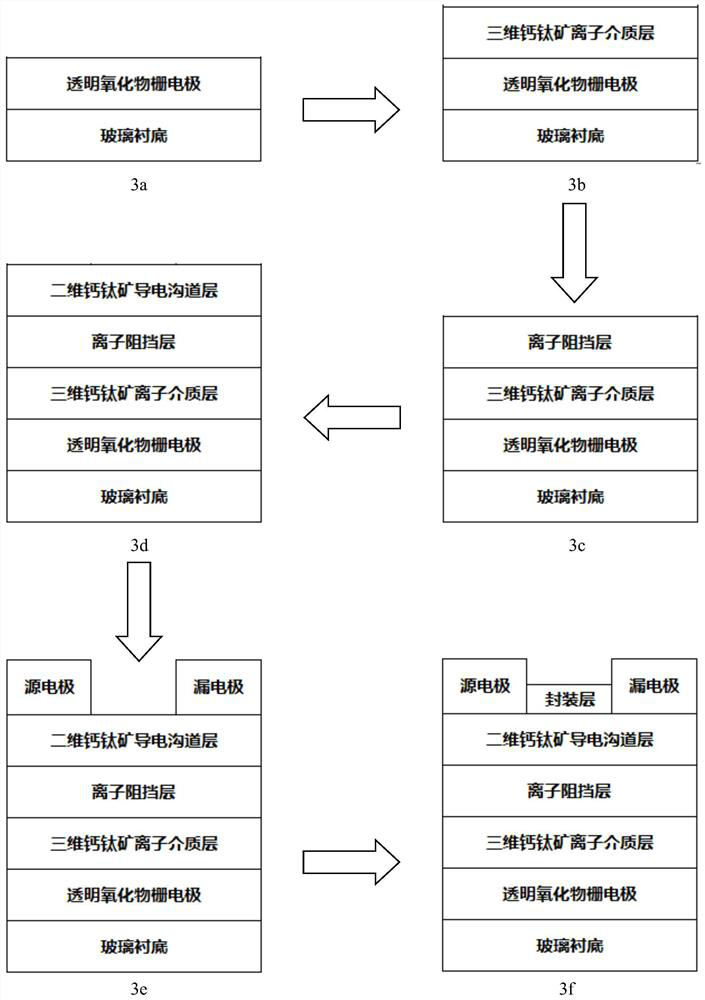

[0044] Embodiment 1: making FTO oxide gate electrode and Al 2 o 3 Purely inorganic three-dimensional perovskite synaptic transistors with an ion barrier.

[0045] Step 1: Treat the conductive substrate.

[0046] Such as image 3 As shown in a, the conductive substrate is composed of a substrate including a glass substrate and an FTO transparent oxide gate electrode. The conductive substrate is first cleaned with acetone, ethanol, and deionized water for 15 minutes ultrasonically, and then cleaned with a high-purity Drying with nitrogen gas; and then UV-ozone ultraviolet ozone treatment on the surface of the cleaned conductive substrate for 20 minutes to obtain the gate electrode of the synaptic transistor.

[0047] Step 2: Growing the perovskite region.

[0048] 2.1) If image 3 As shown in b, on the surface of the conductive substrate after ultraviolet ozone treatment, first spin-coat PbBr at a concentration of 1mol / L and a rotation speed of 2000r / min. 2 DMF solution fo...

Embodiment 2

[0055] Embodiment 2: making ITO oxide gate electrode and MoO 3 Organic-inorganic hybrid three-dimensional perovskite synaptic transistors with ion-blocking layers.

[0056] Step 1: Treat the conductive substrate.

[0057] Such as image 3 As shown in a, the conductive substrate is composed of a substrate including a glass substrate and an ITO transparent oxide gate electrode. The conductive substrate is first ultrasonically cleaned with acetone, ethanol, and deionized water for 15 minutes, and then cleaned with a high-purity Drying with nitrogen gas; and then UV-ozone ultraviolet ozone treatment on the surface of the cleaned conductive substrate for 20 minutes to obtain the gate electrode of the synaptic transistor.

[0058] Step 2: growing the perovskite region.

[0059] 2a) if image 3 As shown in b, on the surface of the conductive substrate after ultraviolet ozone treatment, spin-coat PbI at a concentration of 1.4mol / L and a rotation speed of 3000r / min. 2 DMF solution...

Embodiment 3

[0066] Embodiment 3: making FTO oxide gate electrode and Al 2 o 3 Organic-inorganic hybrid three-dimensional perovskite synaptic transistors with ion-blocking layers.

[0067] Step A: Treating the conductive substrate.

[0068] The specific implementation of this step is the same as step 1 of Embodiment 1.

[0069] Step B: Growing Perovskite Regions.

[0070] B1) If image 3 As shown in b, on the surface of the conductive substrate after ultraviolet ozone treatment, spin-coat PbI at a concentration of 1.4mol / L and a rotation speed of 3000r / min. 2 DMF solution for 45s to obtain PbI 2 layer; then in PbI 2 The layer was spin-coated with CH at a concentration of 100mg / mL and a rotation speed of 3000r / min. 3 NH 3I isopropanol solution for 45 s, and thermal annealing for 10 min under a nitrogen atmosphere at a temperature of 100 °C to obtain a three-dimensional CH with a thickness of 500 nm 3 NH 3 PB 3 ionic medium layer;

[0071] B2) If image 3 As shown in c, Al is gr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More