Lead frame for packaging, semiconductor packaging structure and packaging method

A lead frame and packaging method technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of delamination of lead frame units and packaging resin, affecting the reliability of the packaging body, and increasing production costs and other problems, to achieve the effect of improving the effective utilization rate, not easy to decompose, and prolonging the service life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

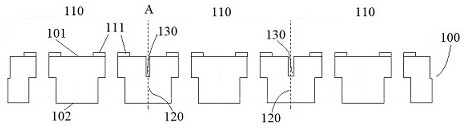

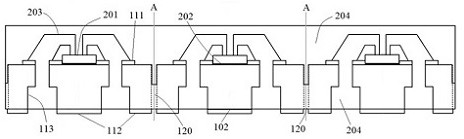

[0049] like figure 2 As shown, the lead frame 100 of this embodiment has an upper surface 101 (front side) and a lower surface 102 (back side), and includes a plurality of lead frame units 110 with a first electroplating layer 111 on the upper surface. The first electroplating layer 111 in this embodiment is a nickel-palladium-gold electroplating layer, and other metal materials with good solderability and conductivity can also be selected for replacement as required. There is a concave groove 130 between adjacent lead frame units, wherein the concave groove 130 is formed after half-etching the upper surface of the substrate, so the opening direction of the concave groove 130 is vertically upward, and the position below the substrate is The remainder of the surface remains to form the metal connection. In the figure, a virtual cutting line A represents a cutting line when cutting and separating the lead frame unit 110 .

[0050] The thickness of the frame body in this embod...

Embodiment 2

[0052] This embodiment provides a method for preparing the lead frame in Embodiment 1, including the following steps:

[0053] Prepare the degreased, cleaned and dried copper substrate as the frame body, paste the dry film on the upper surface 101 and the lower surface 102 of the substrate, and remove the dry film on the local area of the upper surface of the substrate through mask alignment, exposure and development , electroplating nickel-palladium-gold on the substrate to form a first electroplating layer 111 on a local area of the upper surface; the electroplating process is a prior art, and will not be repeated here;

[0054] After electroplating, the substrate is stripped, cleaned, dried, and then laminated again. An etching hole is formed in the middle of the substrate through a conventional etching process to form a patterned lead frame, exposing the side wall 113 inside the lead frame unit 110. Each lead frame unit 110 have the same line pattern on the upper surfa...

Embodiment 3

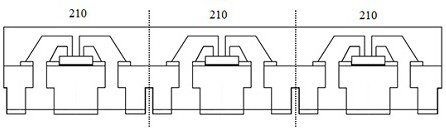

[0058] This embodiment provides a semiconductor package structure 200, including: a plurality of lead frame units 110, adjacent lead frame units are connected through the plastic sealing part 204, wherein the upper surface of the lead frame unit 110 has a first coating on the plastic sealing part 204 An electroplating layer 111, the lower surface of the lead frame machine unit 110 has an exposed second electroplating layer 112; the upper surface 101 of the lead frame unit is also equipped with a semiconductor chip 201, and the semiconductor chip 201 is connected to the corresponding lead frame unit 110 through a gold wire 203 The first electroplating layer 111 of the present embodiment is a nickel-palladium-gold electroplating layer; the plastic sealing part 204 covers the semiconductor chip 201, the lead wire 203 and the lead frame unit 110, wherein the plastic sealing part is made of epoxy resin (EMC) material .

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More