Semiconductor device

a technology of semiconductor devices and dielectric devices, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of less reliable devices, dispersed resistance, and inability to connect materials, so as to minimize the increase and prevent dishing and erosion, and effectively minimize the effect of dispersion of interconnect resistan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

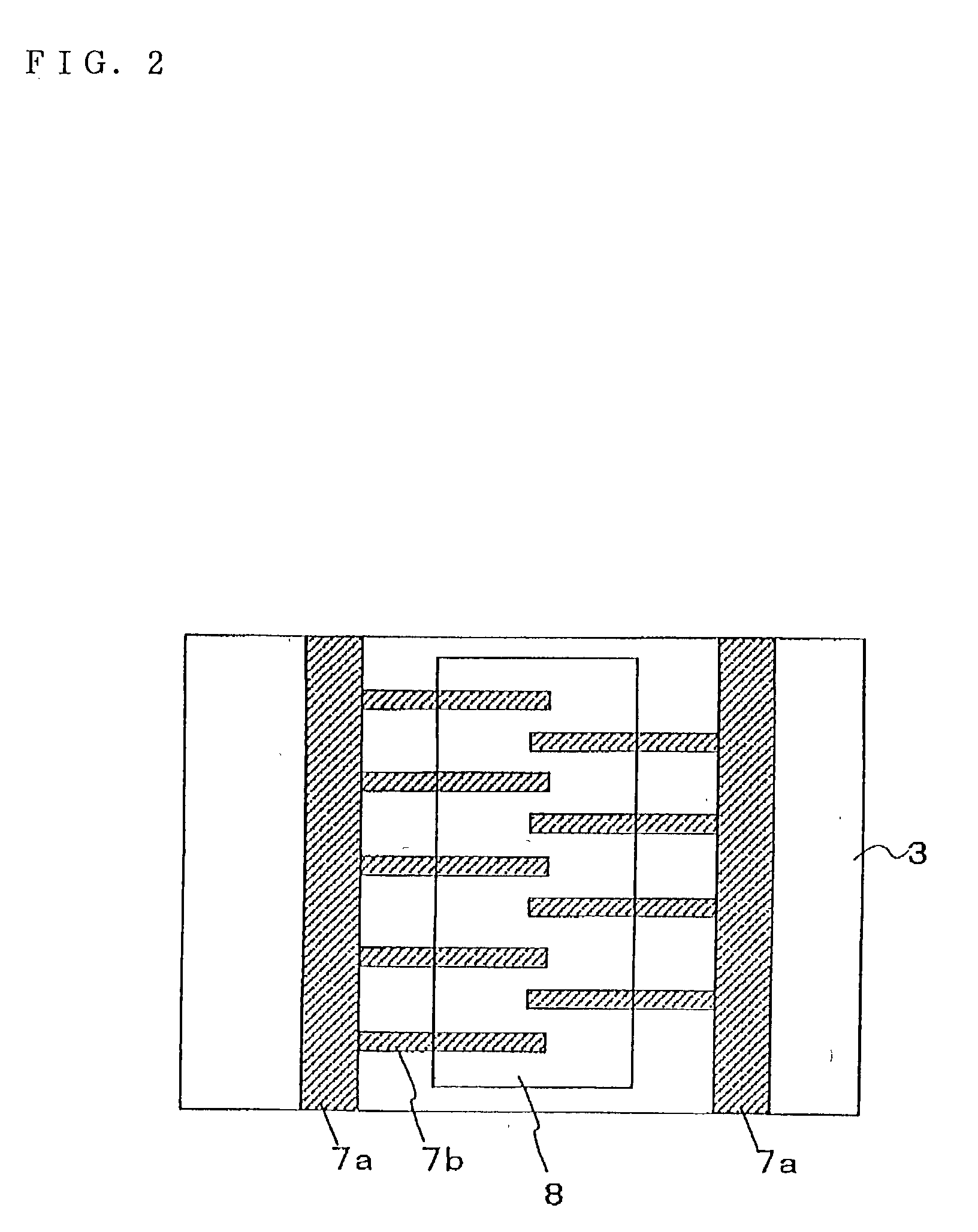

[0071] In this example, various patterns of copper interconnects extending in two or more directions (FIG. 8) were prepared and each pattern was evaluated for a reduction rate of a copper interconnect thickness in chips from its wafer center and periphery. FIG. 8 is a plan view illustrating the evaluated patterns, where the black areas are interconnects and numeric values are interconnect occupancies.

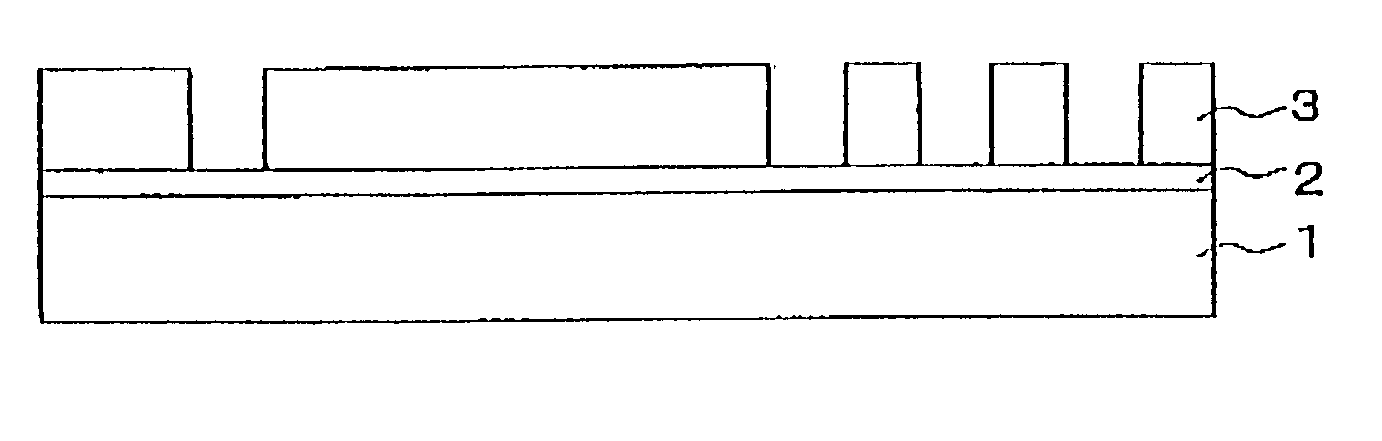

[0072] Copper interconnects were formed as illustrated in FIG. 6. As illustrated in FIG. 6(a), on a silicon substrate 1 are sequentially formed a silicon nitride film 2 with a thickness of 100 nm and a silicon oxide film 3 with a thickness of 1000 nm, and then a plurality of concaves reaching the silicon nitride film 2 were formed by dry etching in the silicon oxide film 3.

[0073] Subsequently, as illustrated in FIG. 6(b), on the whole surface was deposited a barrier metal film 4 consisting of Ta and TaN with a thickness of 15 nm by spattering. On the surface was then deposited by spatte...

example 2

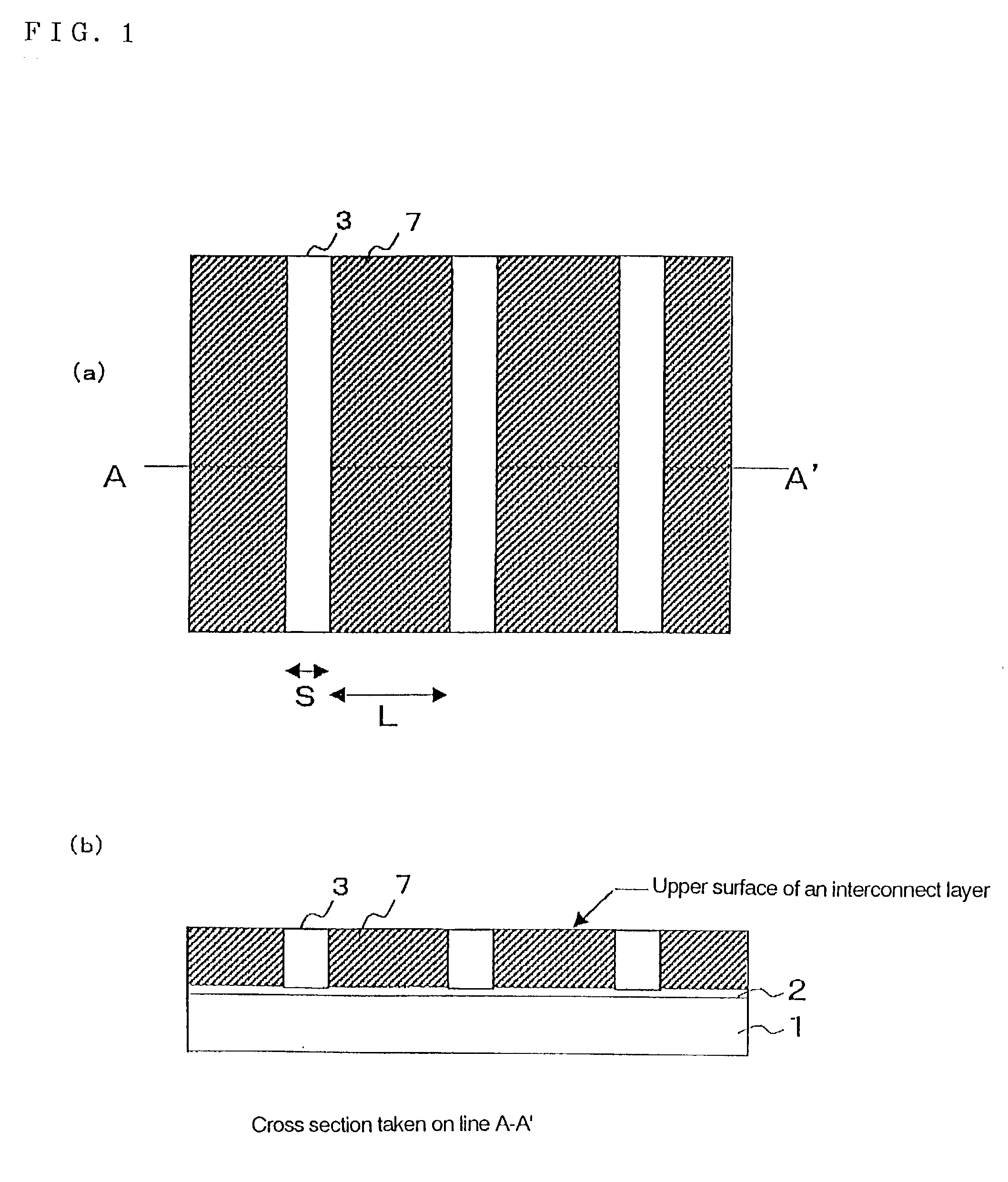

[0078] In this example, various patterns of copper interconnects comprising, as a main area, an area where copper interconnects extended over 100 .mu.m or more in one direction were prepared and each pattern was evaluated for a reduction rate of a copper interconnect thickness in chips from its wafer center and periphery. Each pattern has a unique L / S value where L is an interconnect width and S is a distance between adjacent interconnects.

[0079] The copper interconnects were prepared as described in Example 1, except changing an interconnect pattern. As with Example 1, the thickness of the copper interconnects was 300 nm.

[0080] After preparing the copper interconnects, a sheet resistance was determined for each pattern. A line / space ratio is shown in each figure. For example, "4 / 0.84" in FIG. 10 indicates that an interconnect width (line) is 4.mu.m and a distance between adjacent interconnects (space) is 0.84 .mu.m.

[0081] A sheet resistance was determined by a two-probe or four-pro...

example 3

[0086] On a semiconductor device was formed an MOSFET, on which were then deposited five interconnect layers, to prepare a logic IC. Table 2 shows a profile for each interconnect layer.

2 TABLE 2 Thickness L / S of copper (line / space interconnects ratio) Interconnect occupancy for the (nm) in area (a) whole interconnect layer (%) Lowest layer 30 10 / 3 (3.3) 55 2nd layer 30 10 / 3 (3.3) 55 3rd layer 30 10 / 3 (3.3) 55 4th layer 30 10 / 3 (3.3) 55 5th layer 60 20 / 7 (2.9) 75

[0087] The prepared IC exhibited excellent high-speed operability. In particular, the copper interconnects were made with a designed thickness; matching properties in operation with a high frequency circuit were satisfactory; and an yield was improved.

[0088] As described above, in this invention, an interconnect occupancy and a line / space ratio are adjusted to appropriate ranges. It can, therefore, effectively prevent dishing and erosion, as well as increase and dispersion in an interconnect resistance.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More