Abrasive free formulations for chemical mechanical polishing of copper and associated materials and method of using same

a technology of chemical mechanical polishing and formulation, which is applied in the direction of basic electric elements, electrical equipment, water dispersions, etc., can solve the problems of incomplete etching, unsatisfactory surface polishing, and inability to achieve complete etching, etc., and achieves no surface defects, no dishing or oxide erosion, and good planarization efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

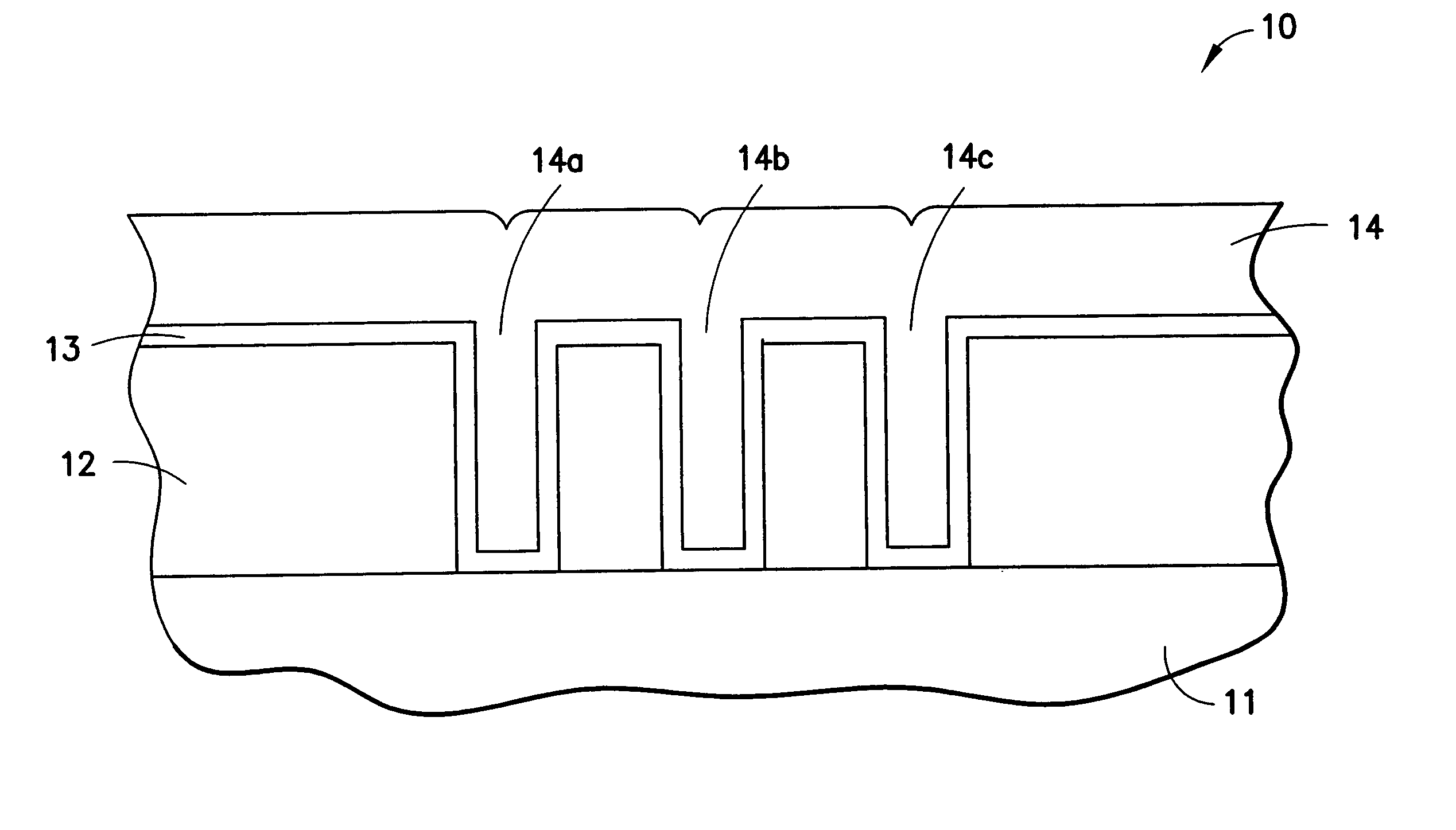

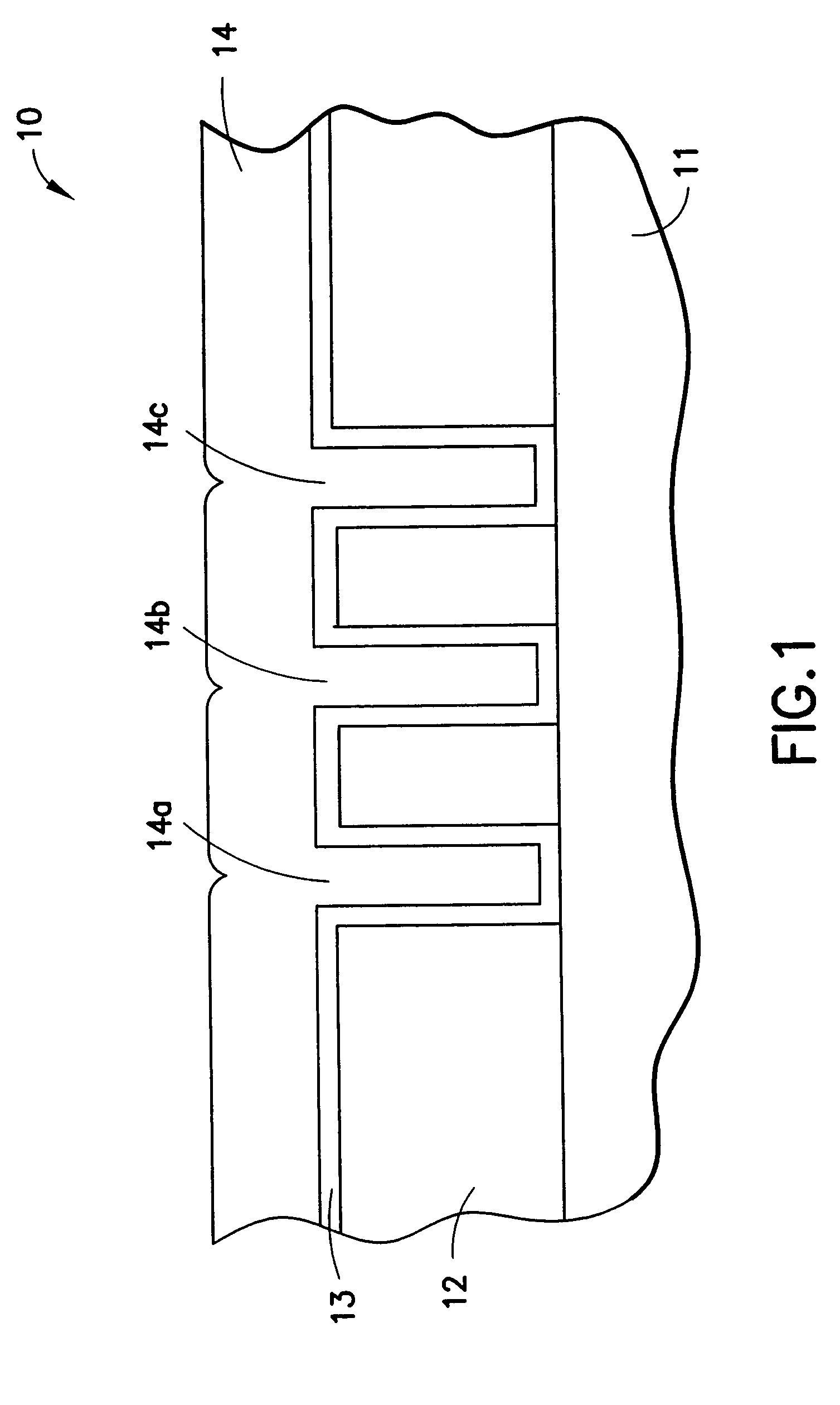

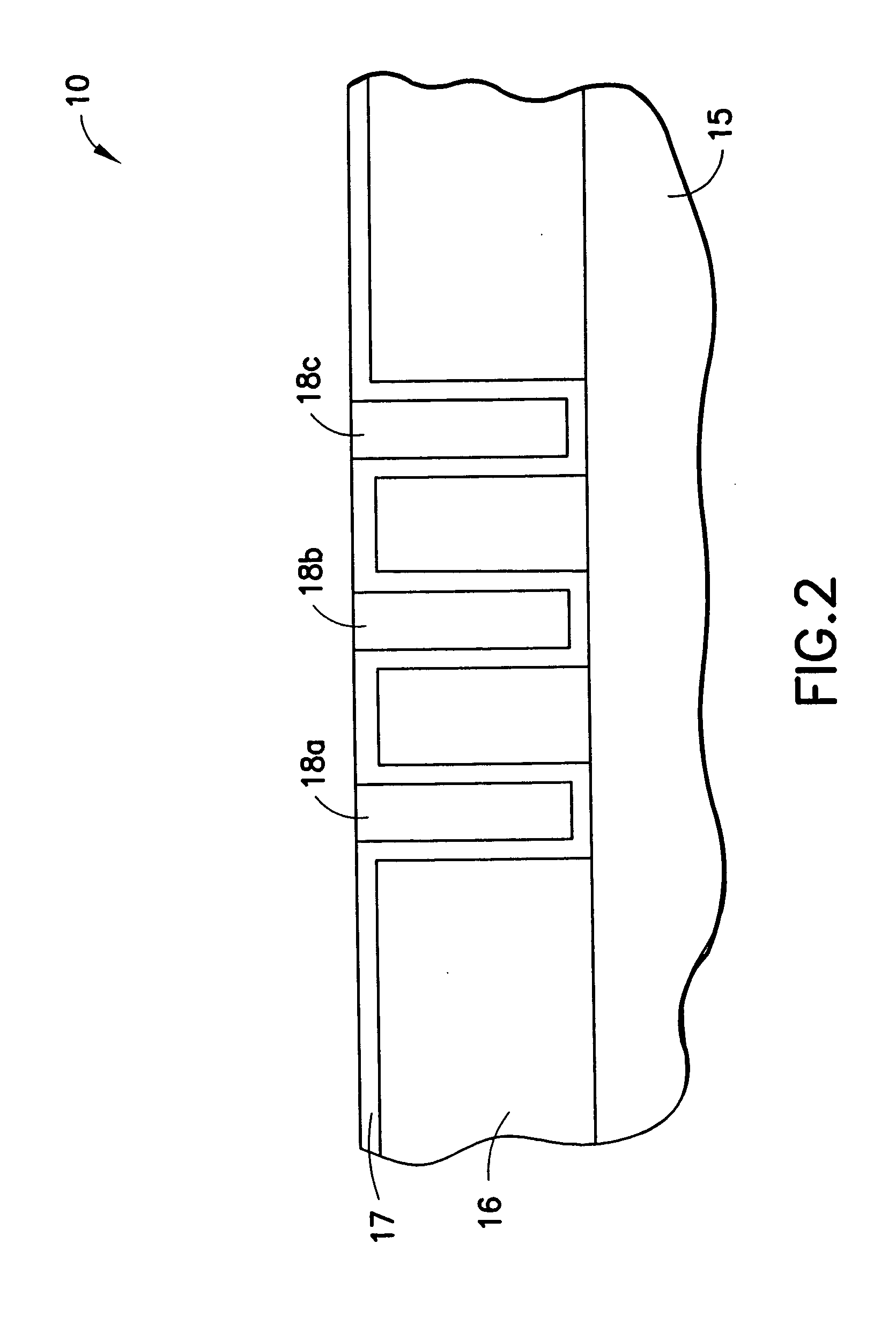

Image

Examples

example 1

Polishing Performance Comparison of Abrasive Free Slurry Formulations (AFS) 1 and 2.

[0082] Table 2 provides a summary of the composition of two abrasive free slurries for polish performance comparison and Table 3 provides actual experimental results for the abrasive free polishing formulation as used on 8″ blanket films wafers of the following composition and thickness: copper wafer (5,000 Å thermal oxide, 300 Å tantalum, 1,500 Å PVD copper seed layer and 15,000 Å electroplated copper), tantalum nitride wafer (5,000 Å thermal oxide and 3,000 Å tantalum nitride), tantalum wafer (5,000 Å thermal oxide and 3,000 Å tantalum), and plasma enhanced tetraethyl orthosilicate (9,000 Å PETEOS).

TABLE 2Abrasive Free Slurry (AFS) Formulations AFS 1 and AFS 2AFS 1Final Weight AFS 2Final WeightComponentPercentComponentPercentHIO34.00HIO34.00IDA0.20IDA0.20H3PO40.75Citric Acid0.20KOH1.73KOH1.37H2OBalanceH2Obalance

[0083]

TABLE 3Polishing Performance Comparison AFS 1 vs. AFS 2AFS 1**AFS 2Room Temp.45...

example 2

Planarization Performance and Step Height Reduction

[0084] One object of CMP processing is to produce a uniform surface on the semiconductor wafer. The uniformity of the planarized surface is a function of several factors. FIGS. 5 and 7 are plots showing the step height remaining verses different copper / dielectric pattern densities on a Sematech 854 CMP AZ mask test wafer after underpolishing with an abrasive free polishing formulation for a bulk copper-polishing step according to one embodiment of the present invention. The initial step height before polishing was approximately 6000 Å. The data plotted in FIG. 5 is based on room temperature experimental conditions and the data plotted in FIG. 7, 45° C. The substantial step height reduction on the patterned wafers while underpolishing evidences the commercial viability of the present invention.

example 3

Planarization Performance and Array Recess

[0085]FIGS. 6 and 8 are plots showing the array recess verses different copper / dielectric pattern densities based on using the same abrasive free polishing formulation and substrate as in the previous step height reduction experimental. The data plotted in FIG. 6 is based on room temperature experimental conditions and the data plotted in FIG. 8, 45° C. The low levels of array recess are further evidence of the commercial viability of the abrasive free polishing formulation.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More