Trench gate type semiconductor device and method of producing the same

a semiconductor device and clamp gate technology, applied in semiconductor devices, diodes, electrical devices, etc., can solve the problems of difficult protection of side walls, and achieve the effect of preventing excessive electric fields and good ohmic conta

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

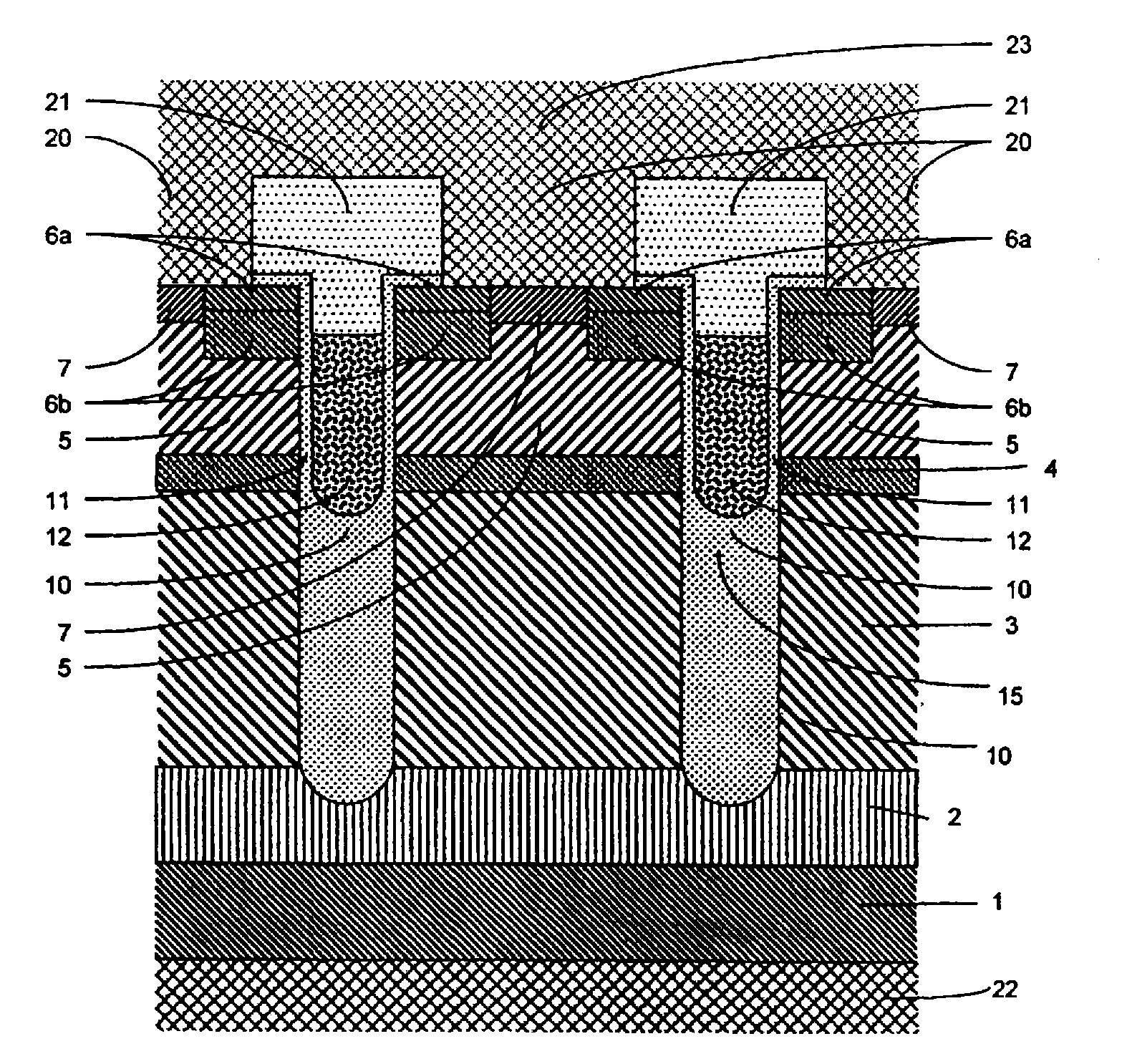

embodiment 1

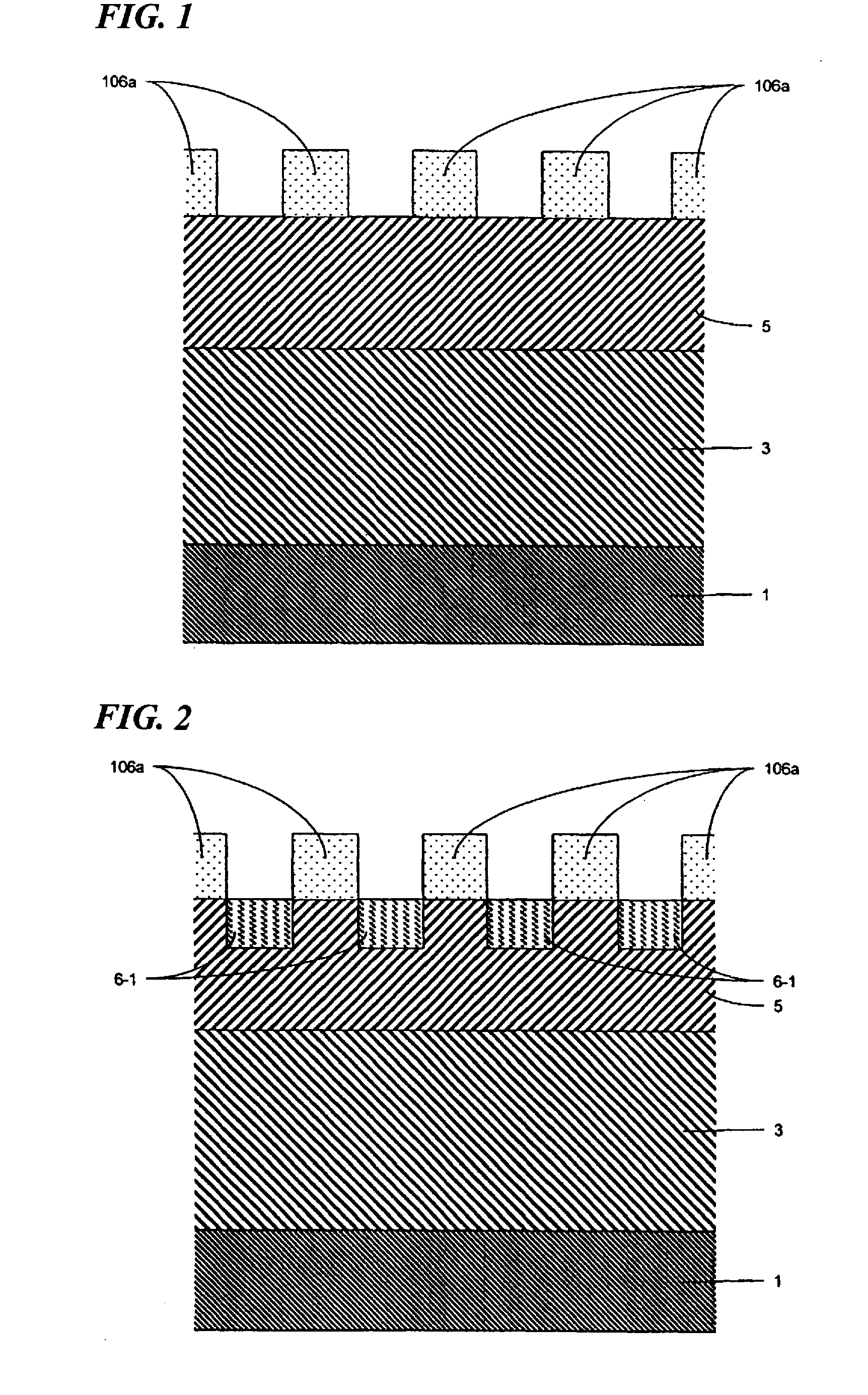

[0139]As shown in FIG. 1, a voltage withstanding layer 3 having a predetermined doping concentration of an n type and a predetermined thickness and a body layer having a predetermined doping concentration of a p type and a predetermined thickness are formed successively by epitaxial growth on the whole area of one principal surface (referred to as front surface) of an n-type SiC substrate 1. A predetermined first mask layer, for example, made of an SiO2 film is formed on a front surface of the body layer. The mask layer is patterned to form a first mask 106a having a predetermined first opening portion by photolithography. Although a SiO2 film is preferred as the first mask, another material may be used. In principle, the term “body region” means a region formed selectively on the wafer surface and the term “body layer” means a layer formed fully on the wafer surface. However, strict discrimination between layer and region may not be made in the following description because it may ...

embodiment 2

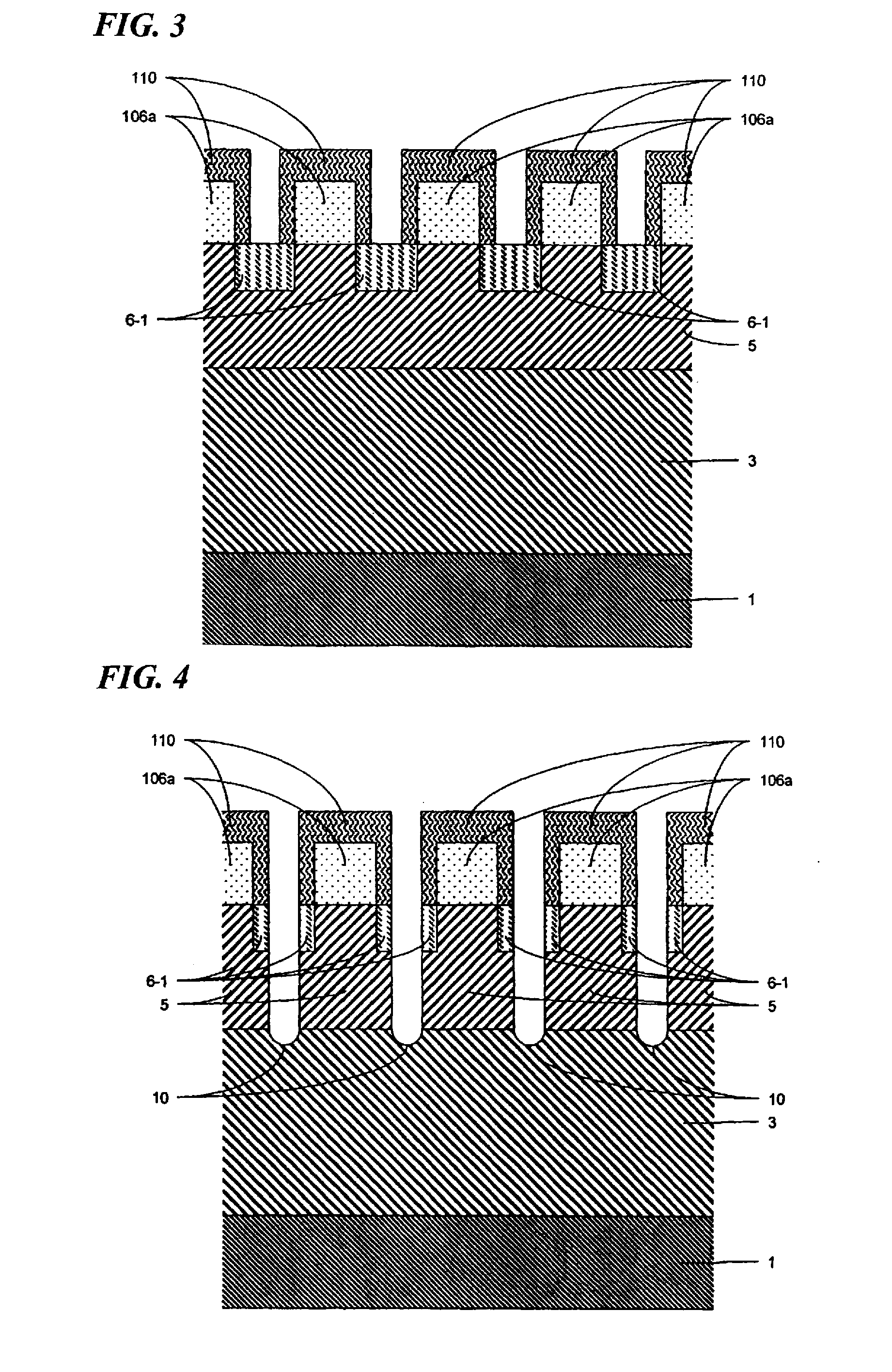

[0144]When nonselective, i.e. full epitaxial growth is an essential or effective method for forming body contact regions 7, a body contact layer 7-1 is first formed on the whole front surface of a body region 5 as shown in FIG. 5. As for the body contact layer 7-1, doping may be performed simultaneously with epitaxial growth to provide a predetermined doping concentration in order to obtain good ohmic contact, or the composition of alloys may be controlled in a growth direction to form a predetermined quantum well structure. Alternatively, the two characteristics may be used in combination. Description will be made topically on the fact that source regions 6, body contact regions 7 and trenches 10 can be formed by self-alignment from the state shown in FIG. 5.

[0145]First, as shown in FIG. 6, a first mask 106a having predetermined first opening portions is formed. Then, anisotropic etching is performed with use of the first mask 106a as a mask to partially remove the body contact lay...

embodiment 3

[0148]Because the producing method according to Embodiment 1 and the producing method according to Embodiment 2 make it possible to form each trench 10 narrower than the resolution limit of the used stepper or the like, the production margin at etching back can be enlarged when a gate electrode or the like to be embedded in each trench 10 is formed by etching back. However, when such a semiconductor material that the temperature for impurity doping due to a thermal diffusion method cannot be said to be practical in an ordinary production process is used, there may occur a second problem that the production margin at etching back is still short because the depth of each source region 6 is limited by the ion implantation device. The producing method according to Embodiment 3 is provided as a modification adapted for such a case.

[0149]First, a body contact layer 7-1 is formed on each body region 5 in accordance with necessity. Although this film-forming is not an essential process, des...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More