CMOS Compatible Material Platform for Photonic Integrated Circuits

a photonic integrated circuit and material platform technology, applied in the direction of instruments, optical elements, optical waveguide light guides, etc., can solve the problems of low energy efficiency, difficult to generate needed light sources, and low optical loss, and achieve the effect of low optical loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

lass="d_n">[0023]The following numerous specific detail descriptions are set forth to provide a thorough understanding of various embodiments of the present disclosure. It will be apparent to one skilled in the art, however, these specific details need not be employed to practice various embodiments of the present disclosure. In other instances, well known components or methods have not been described.

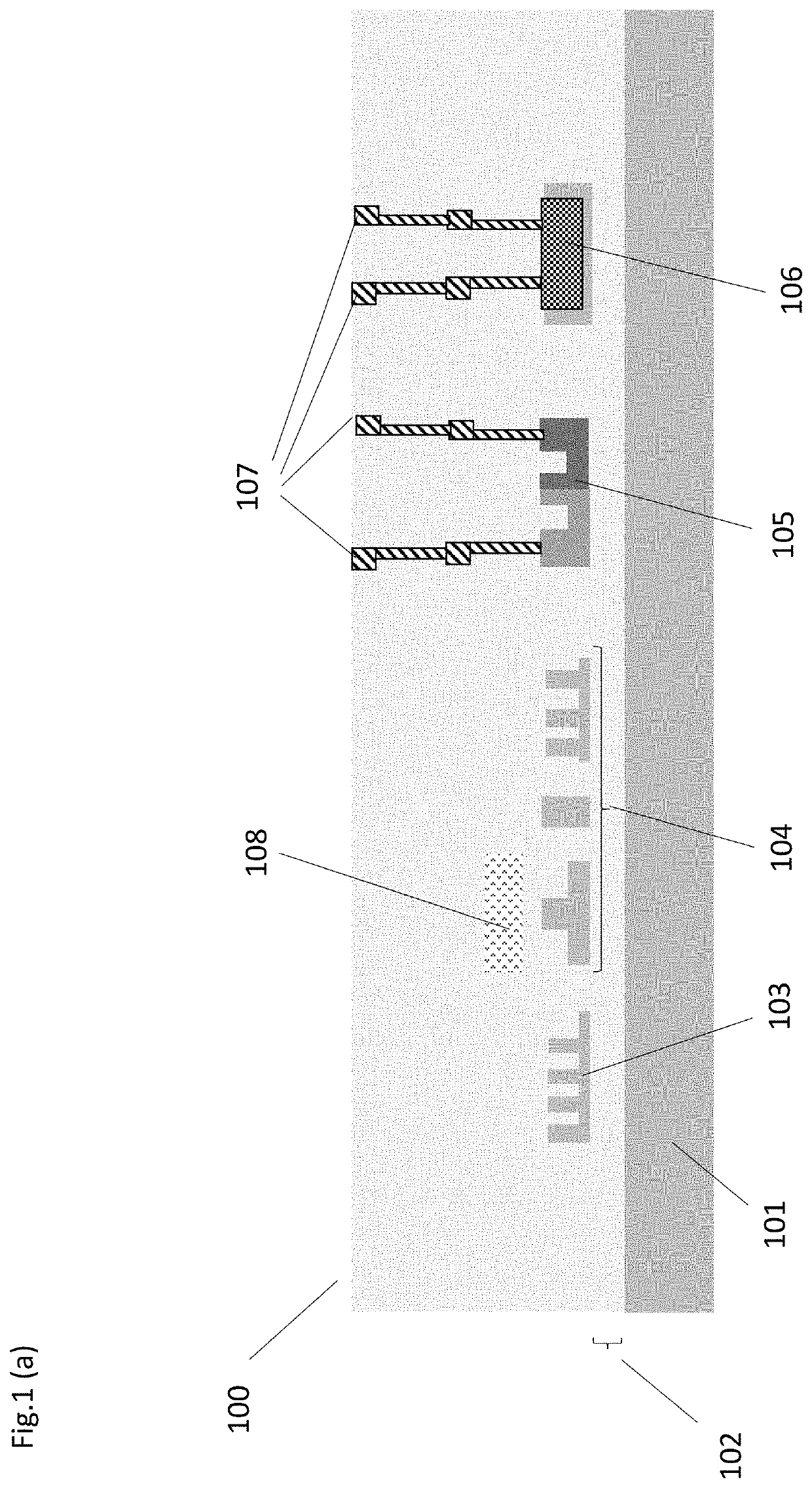

[0024]FIG. 1(a) shows an embodiment of the existing silicon on insulator (SOI) platform 100 with SiN integrated on top of the patterned SOI layer. In details, the incoming SOI wafer has Si substrate 101 with buried oxide (BOX) layer 102. In the SOI layer, various photonic building blocks (devices), such as grating 103, different waveguide structures for the light routing, electrical to optical modulator 105, and Ge photodiode (Ge PD) 106. The active devices such as modulator 105 and Ge PD 106 is connected to vertical electrical connection paths 107. On top of the SOI layer, there is a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

| wavelengths | aaaaa | aaaaa |

| refractive index | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More