Patents

Literature

31results about How to "Convenient and cost-effective for manufacturing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

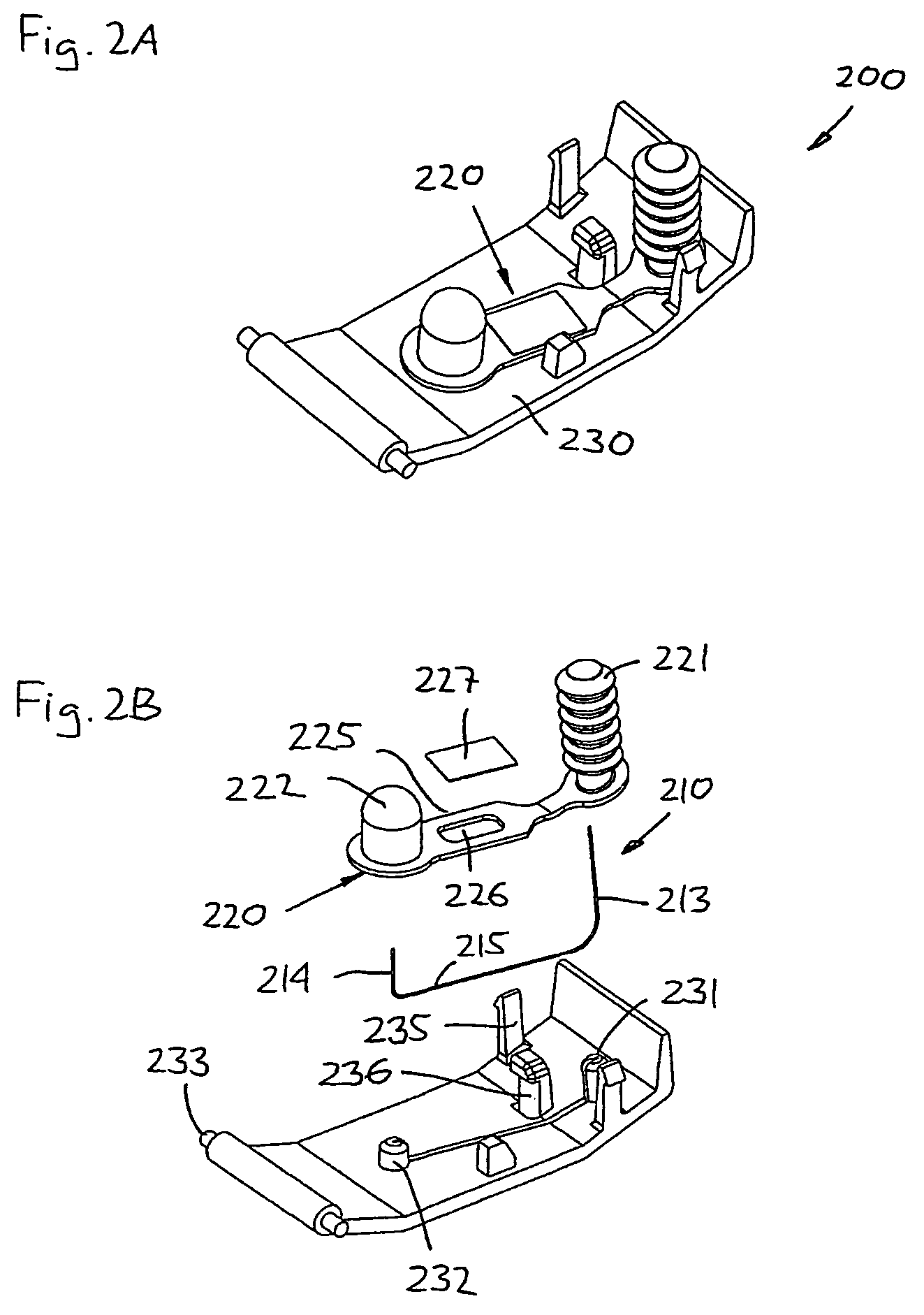

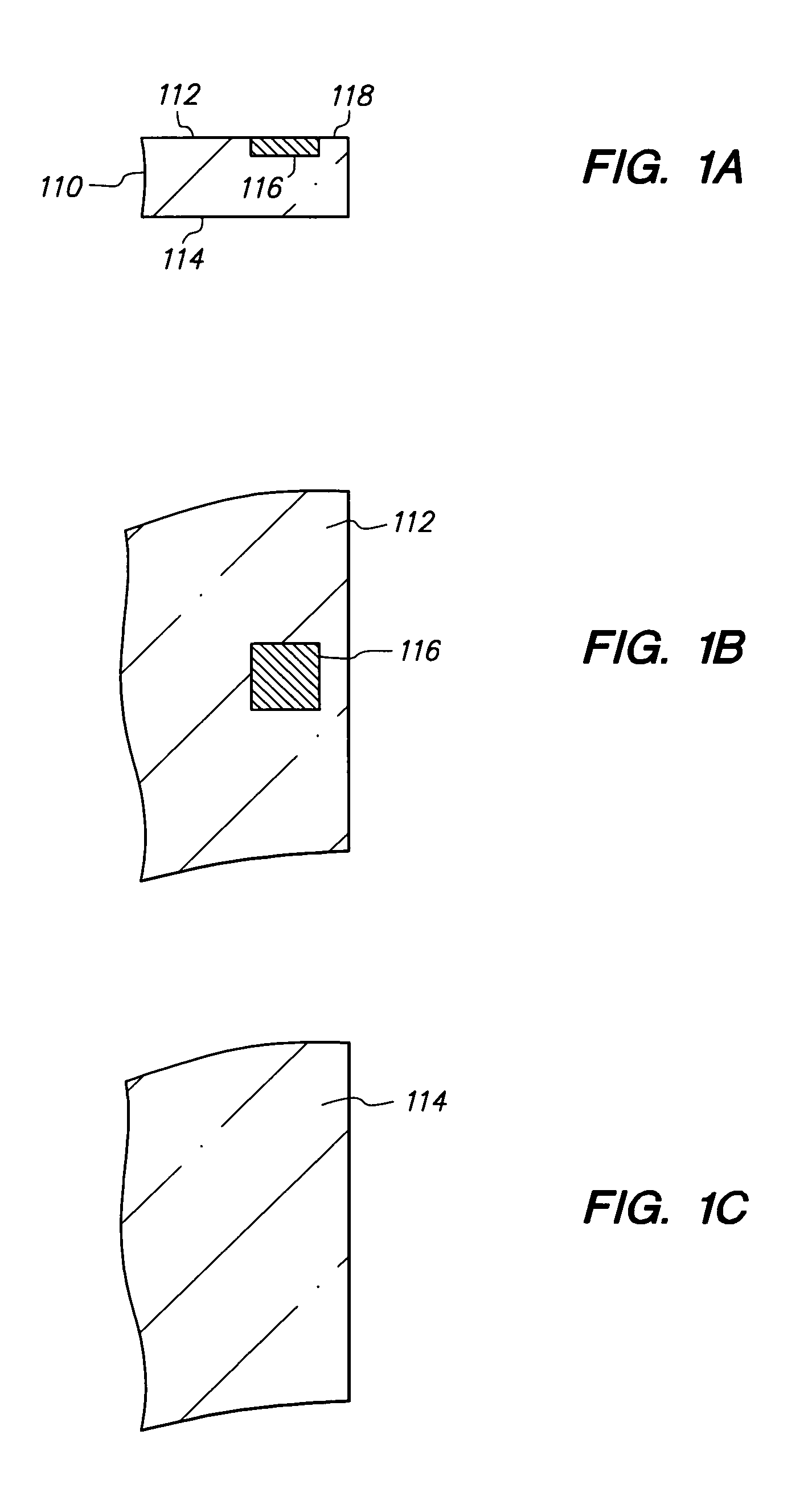

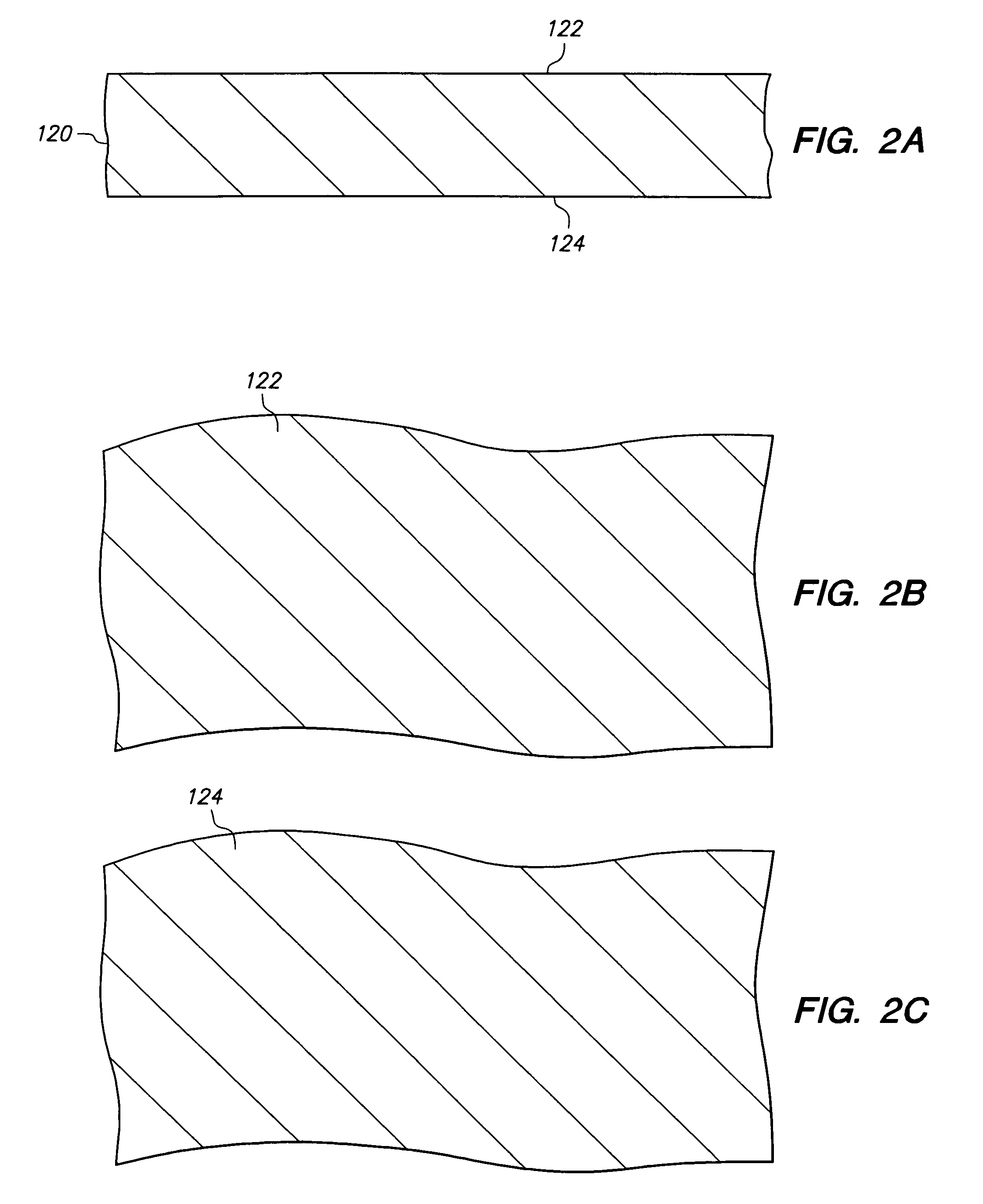

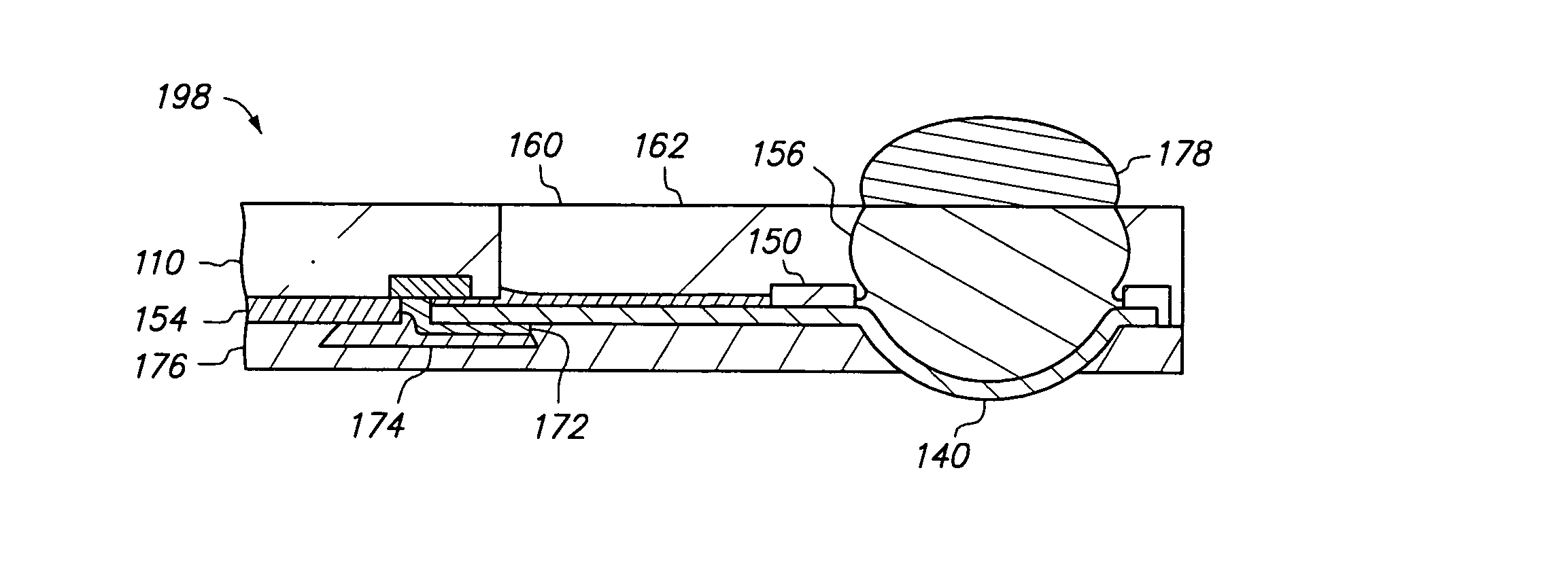

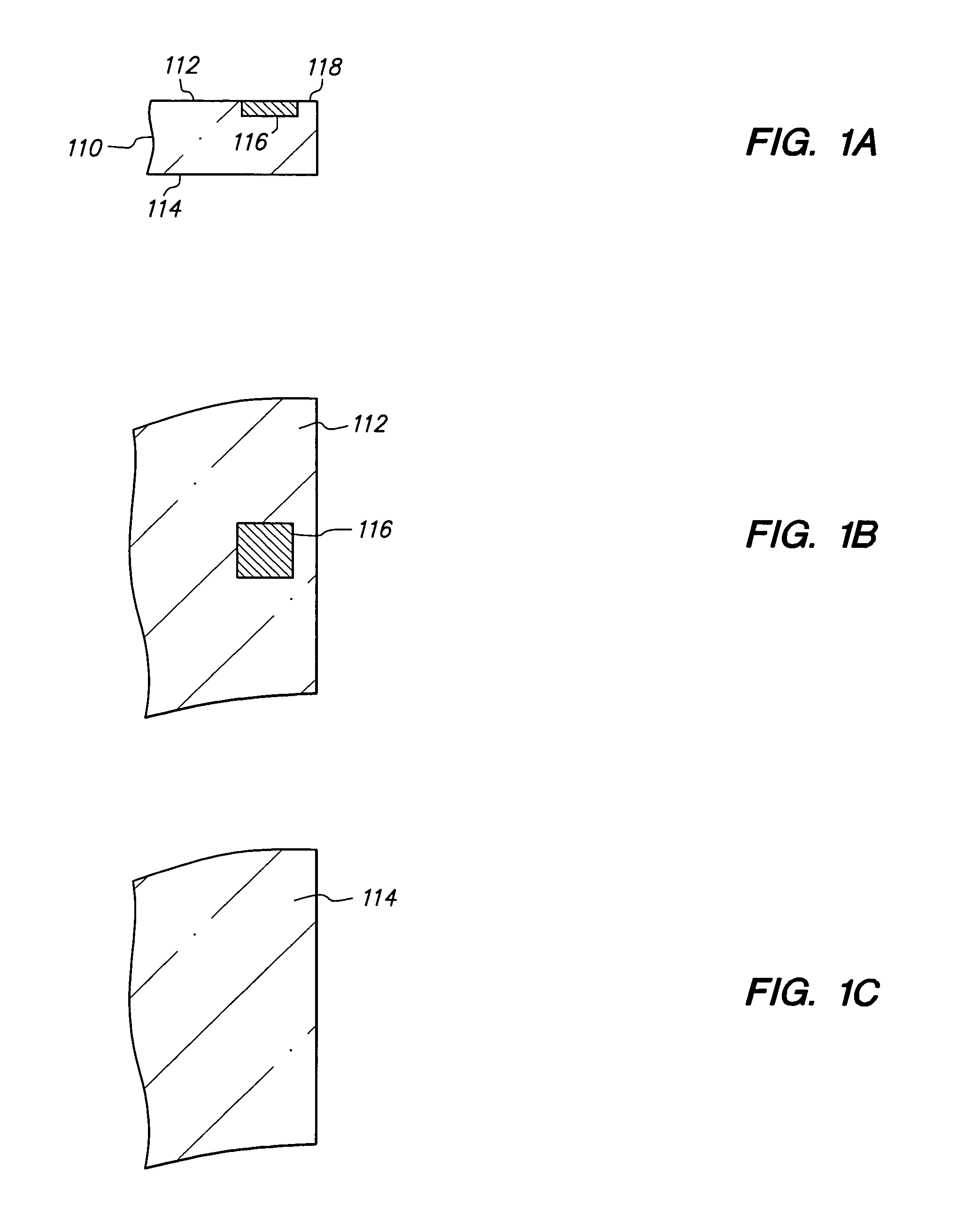

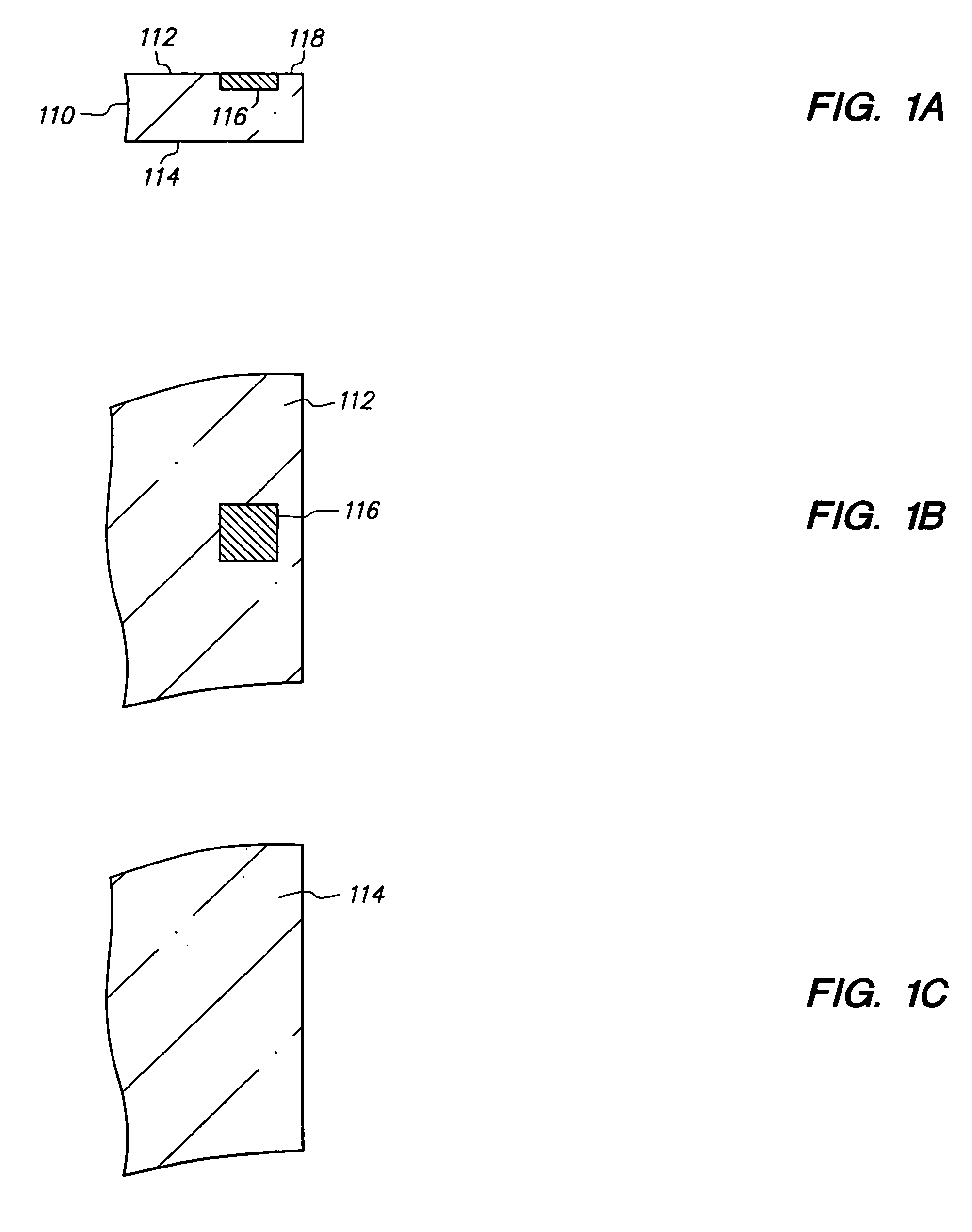

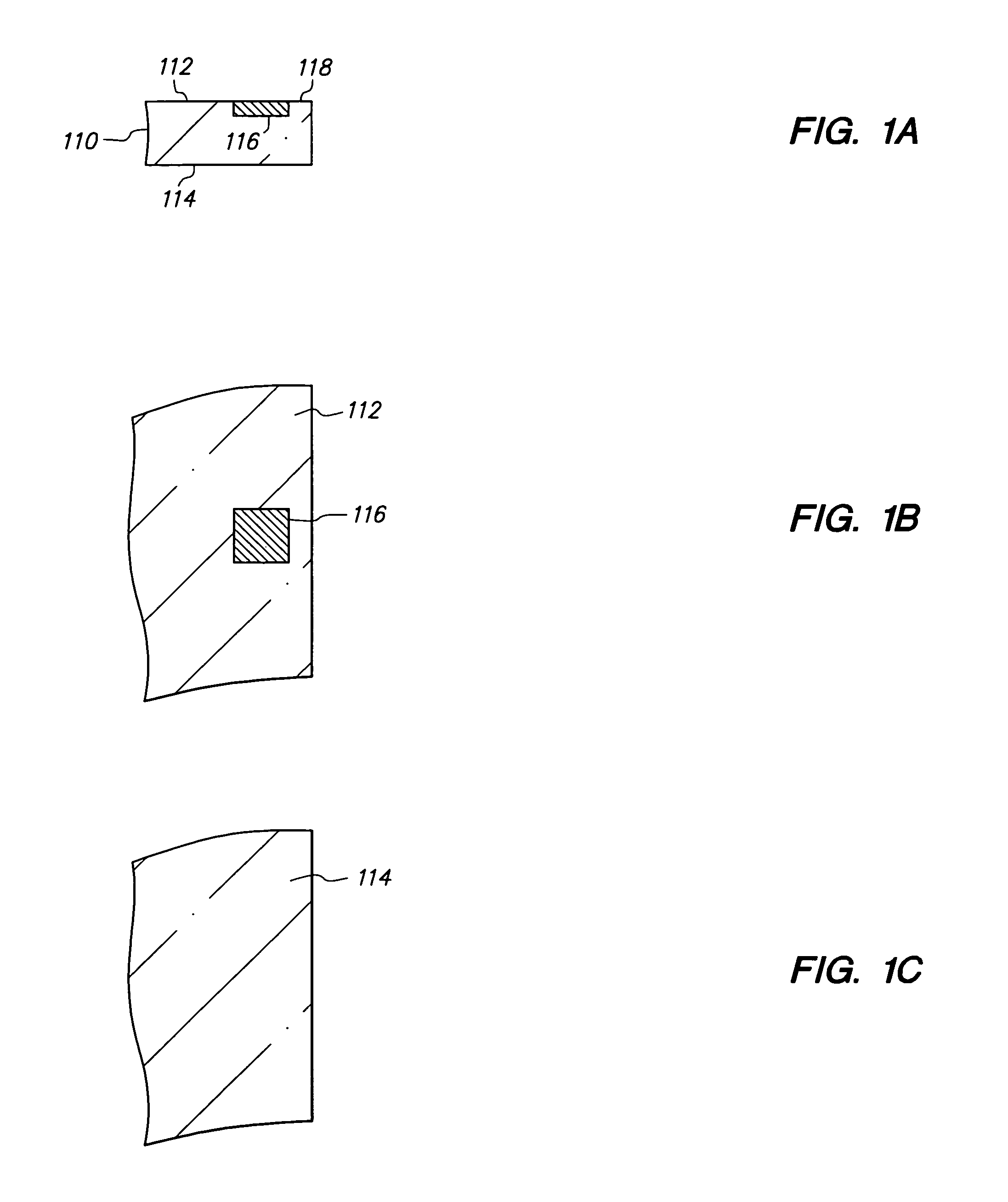

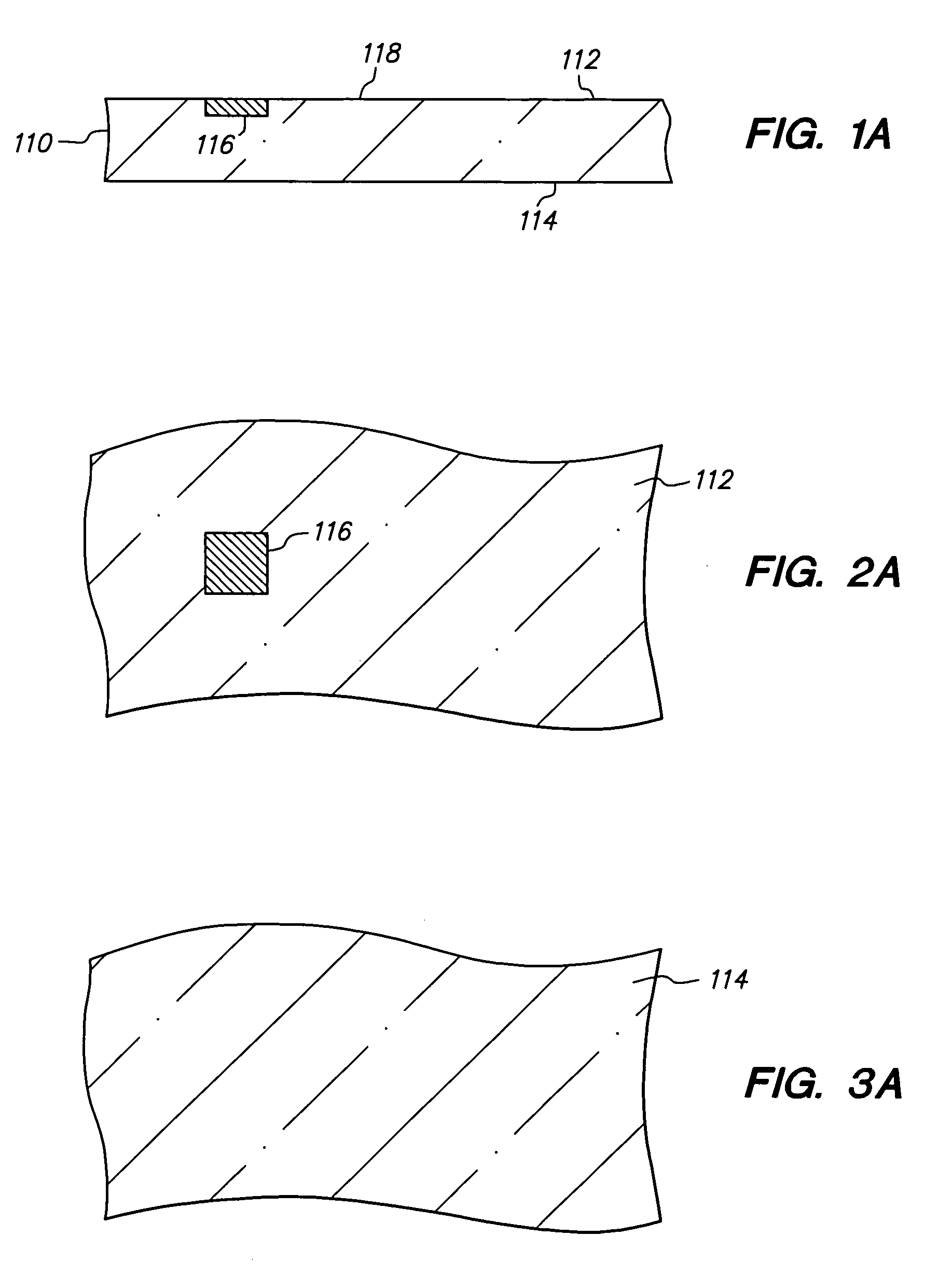

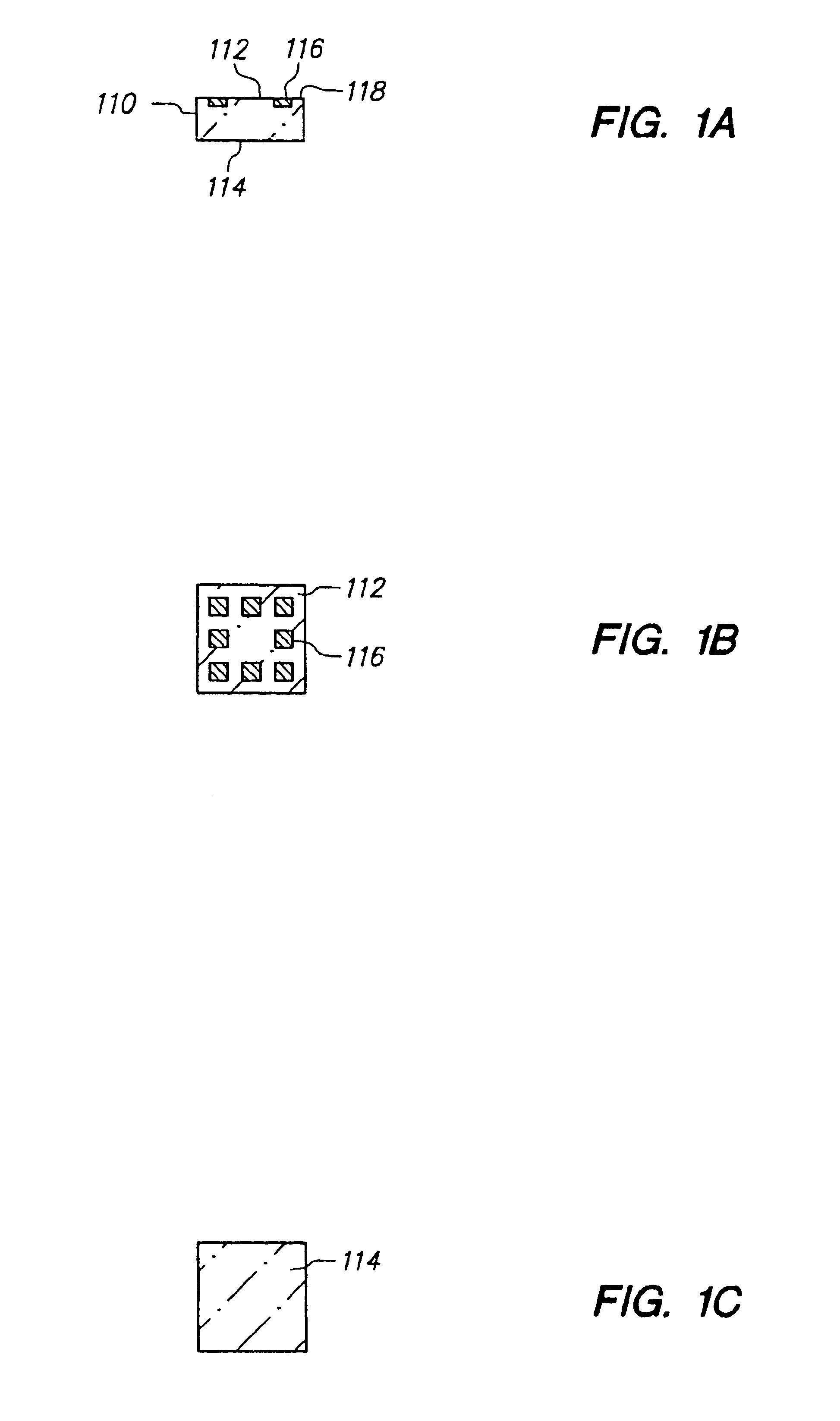

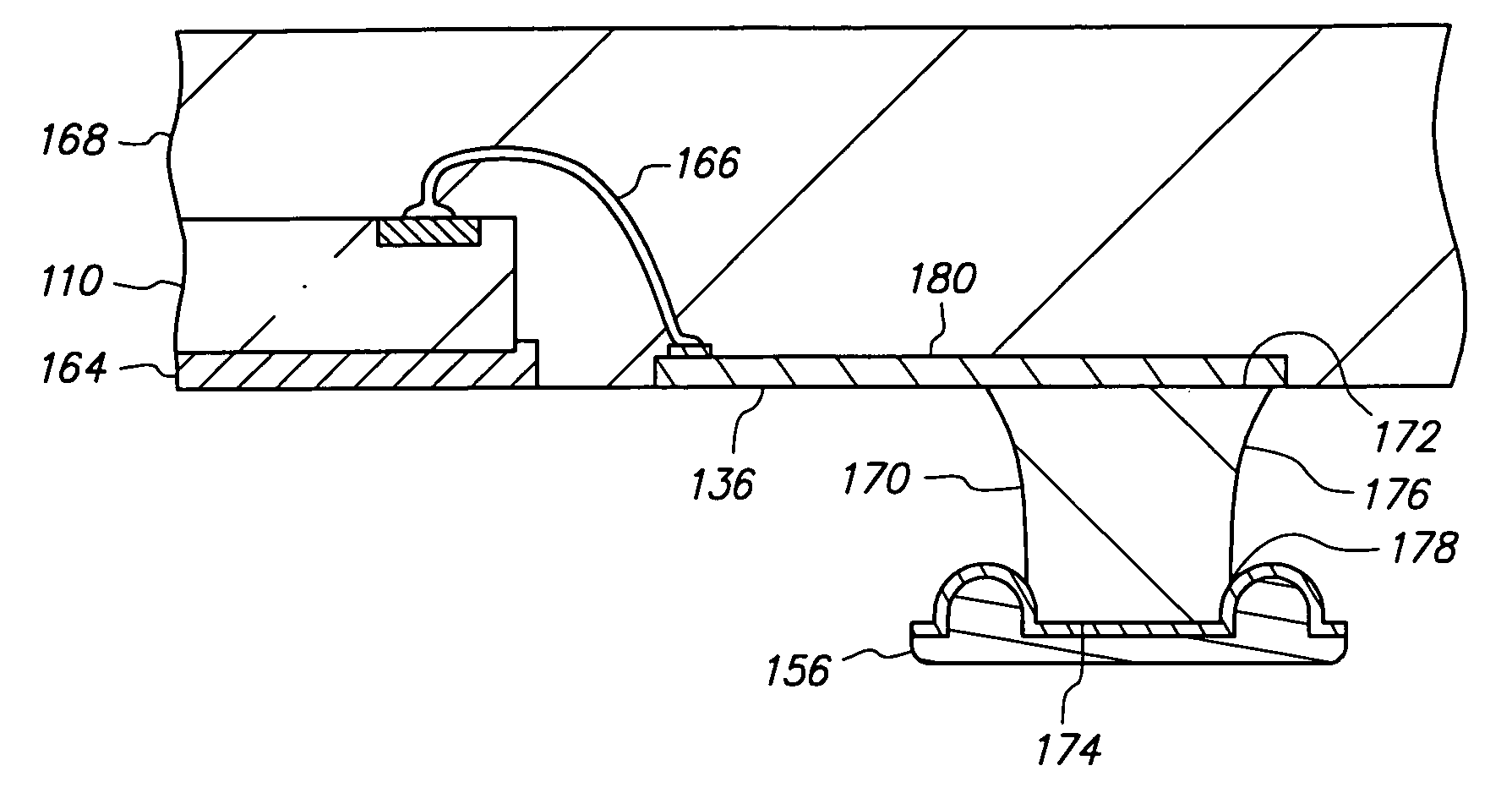

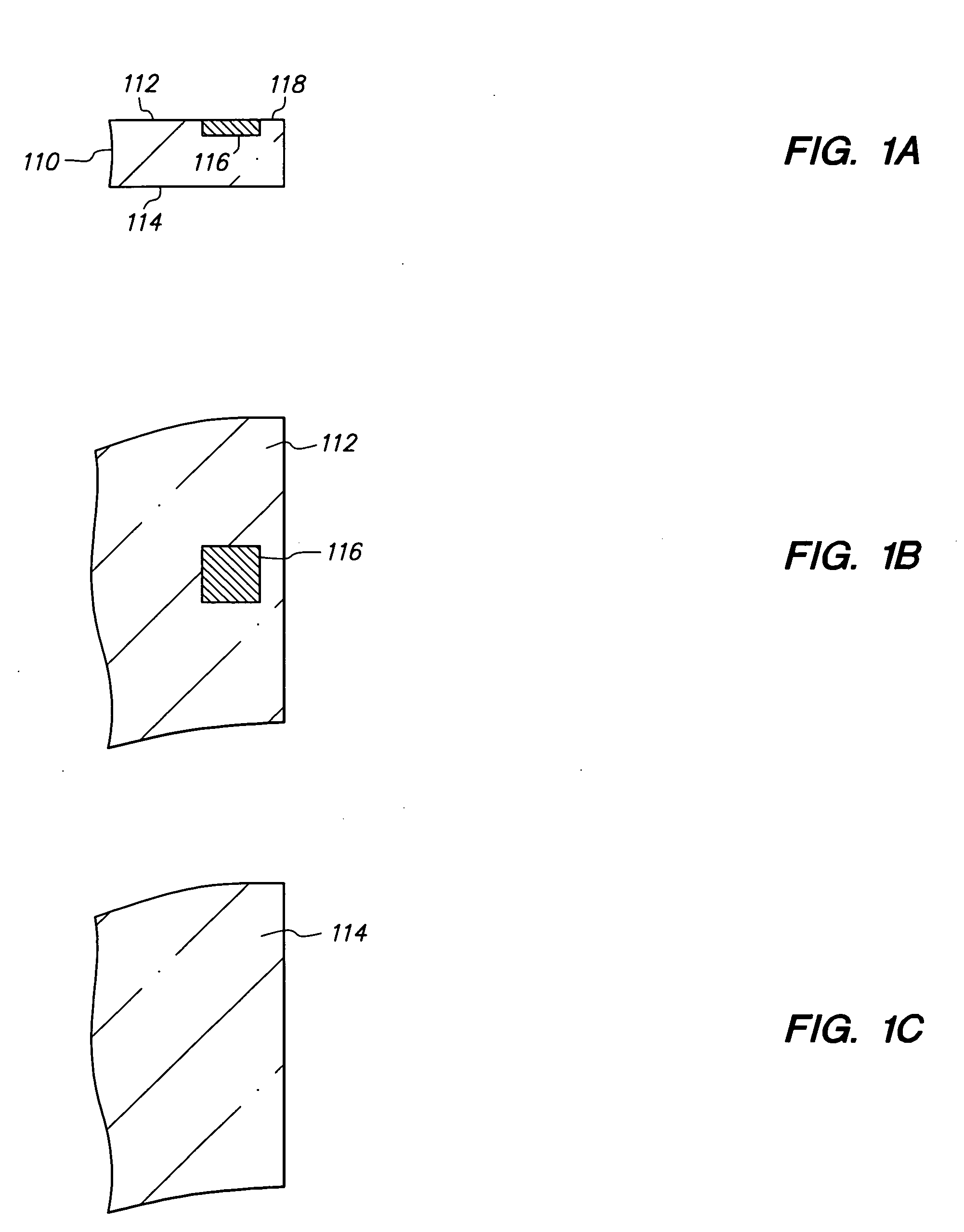

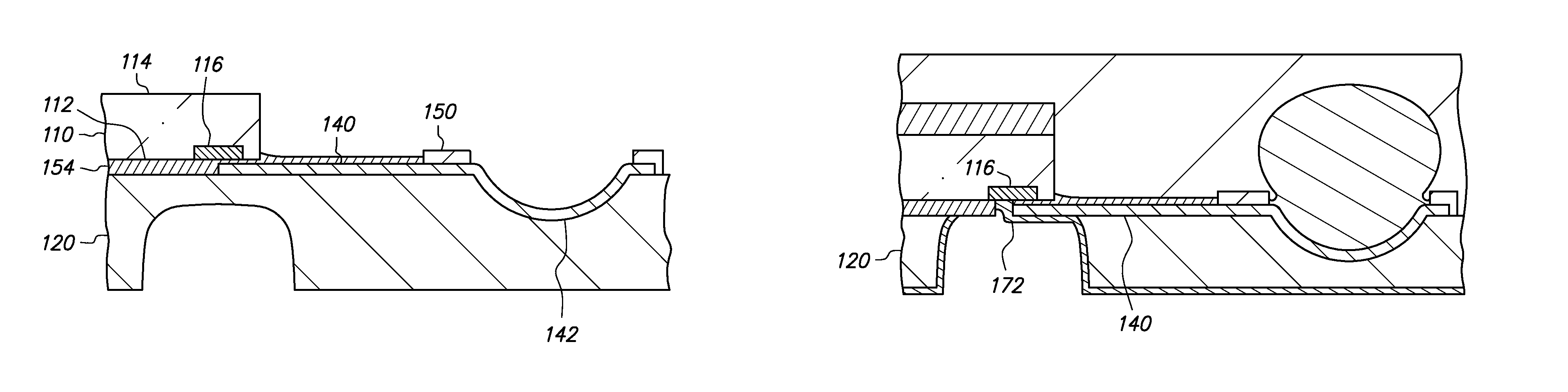

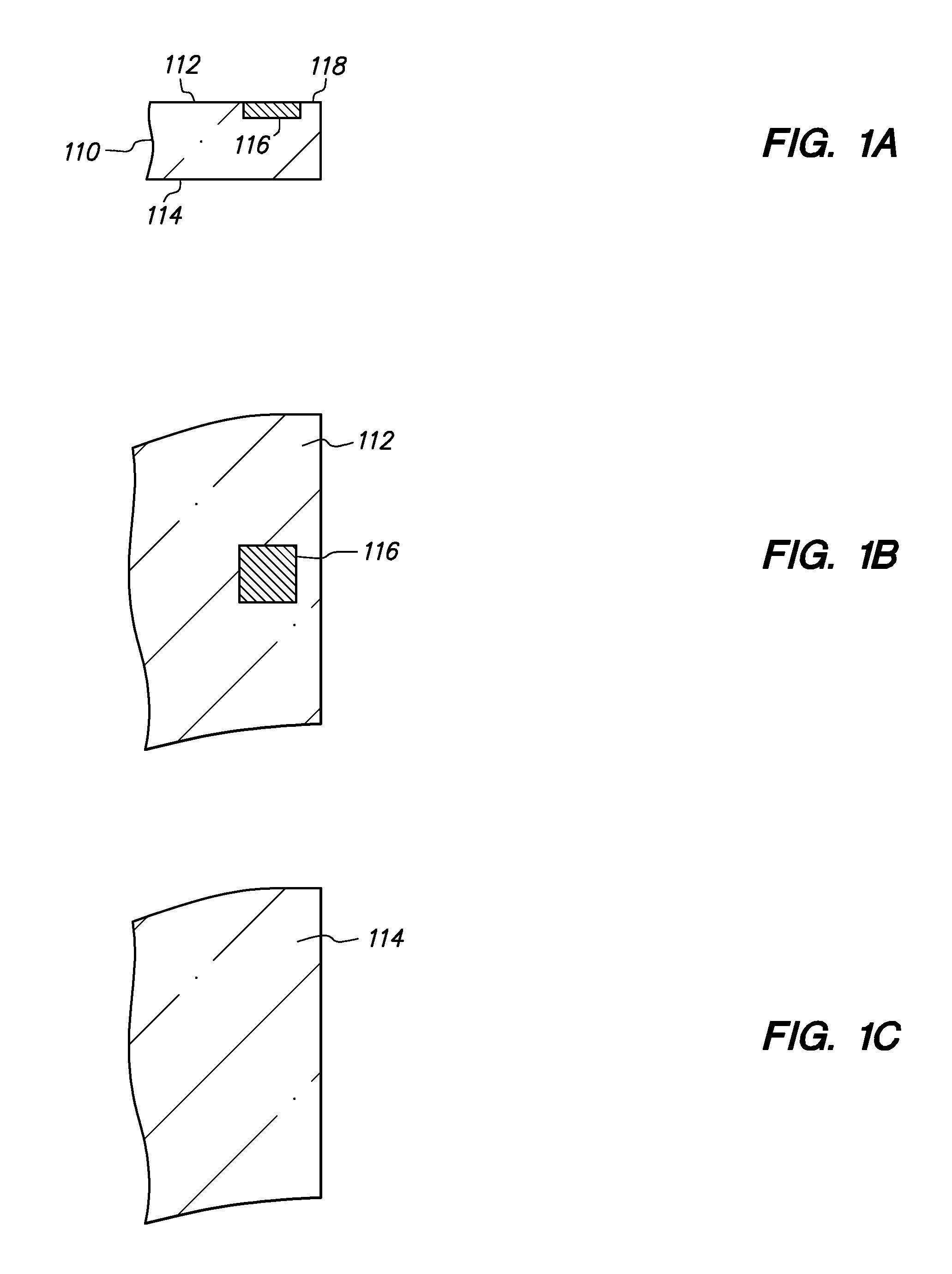

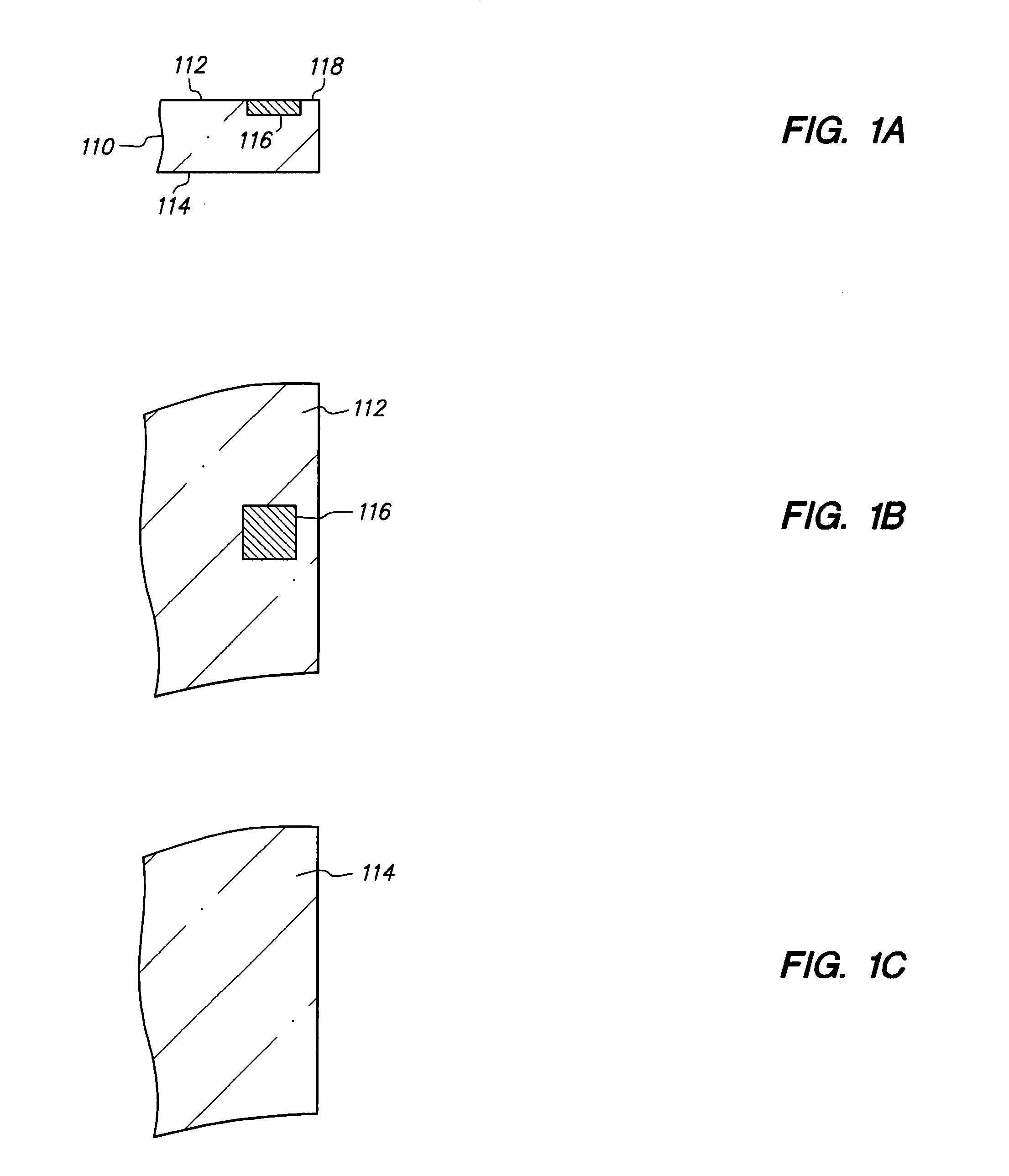

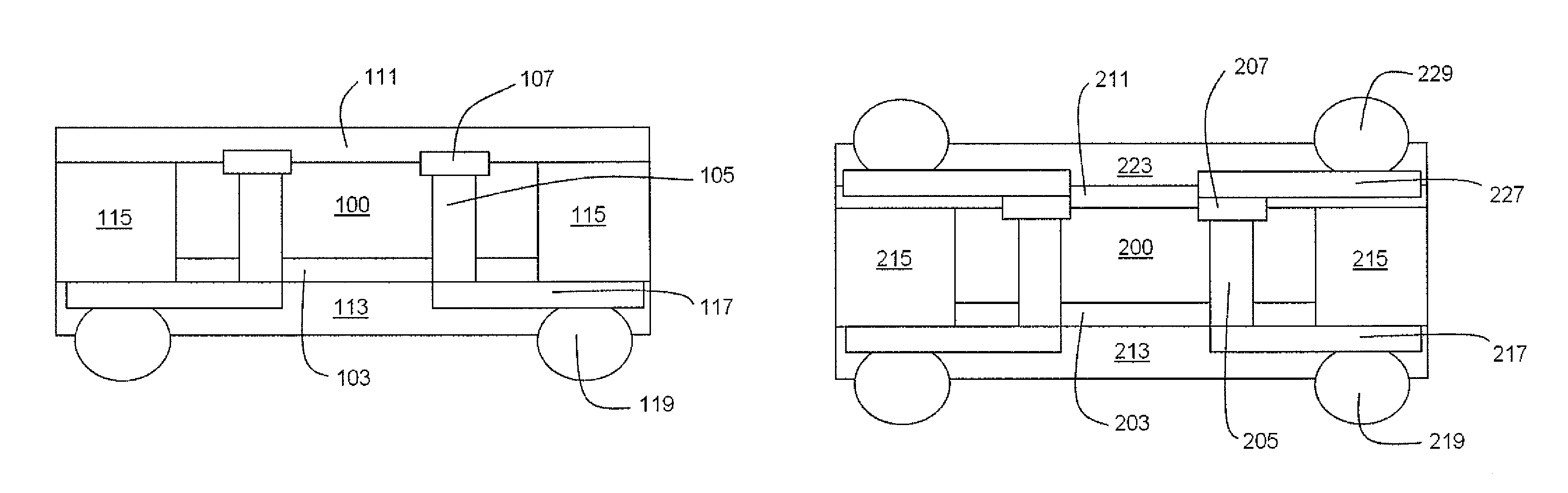

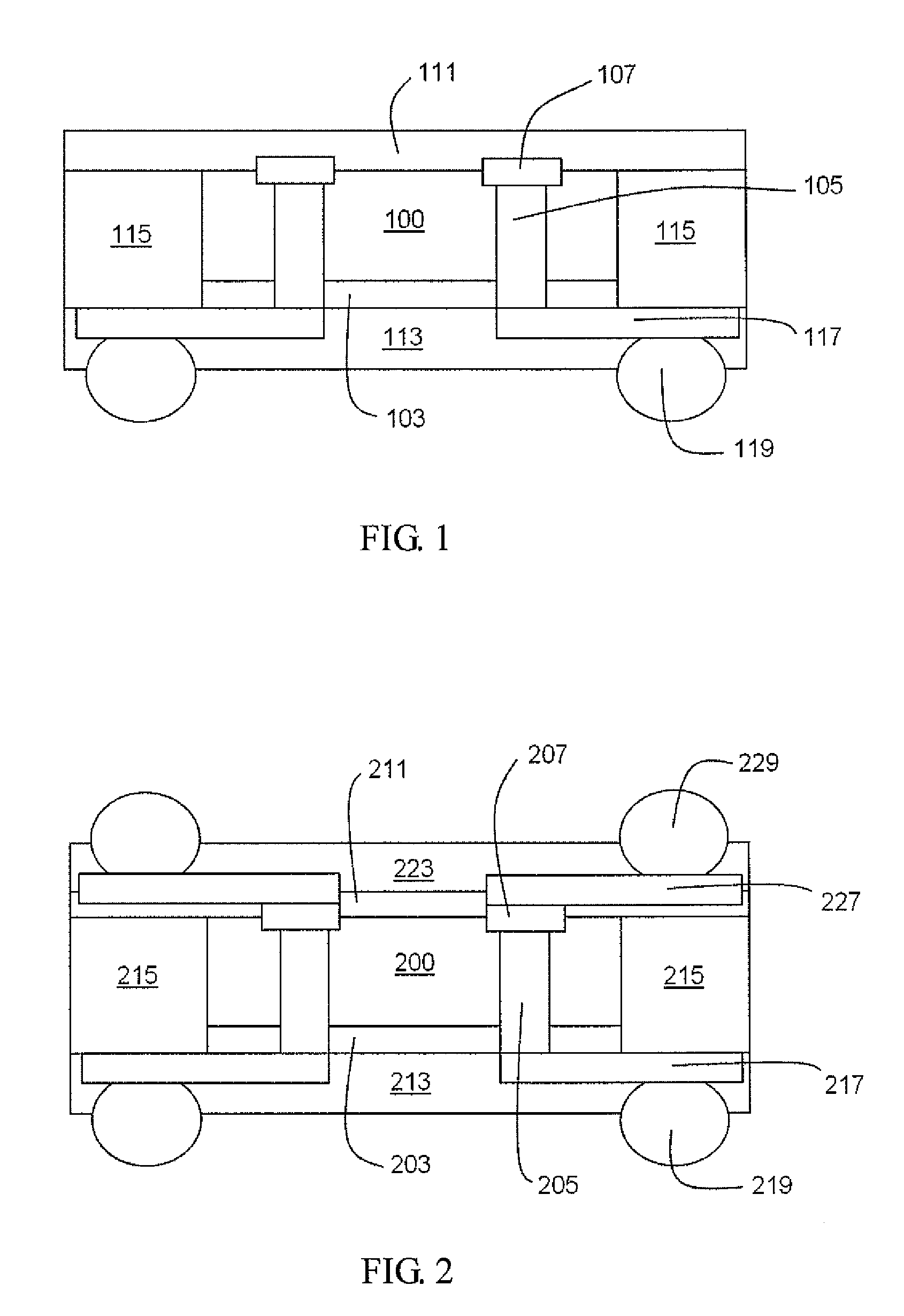

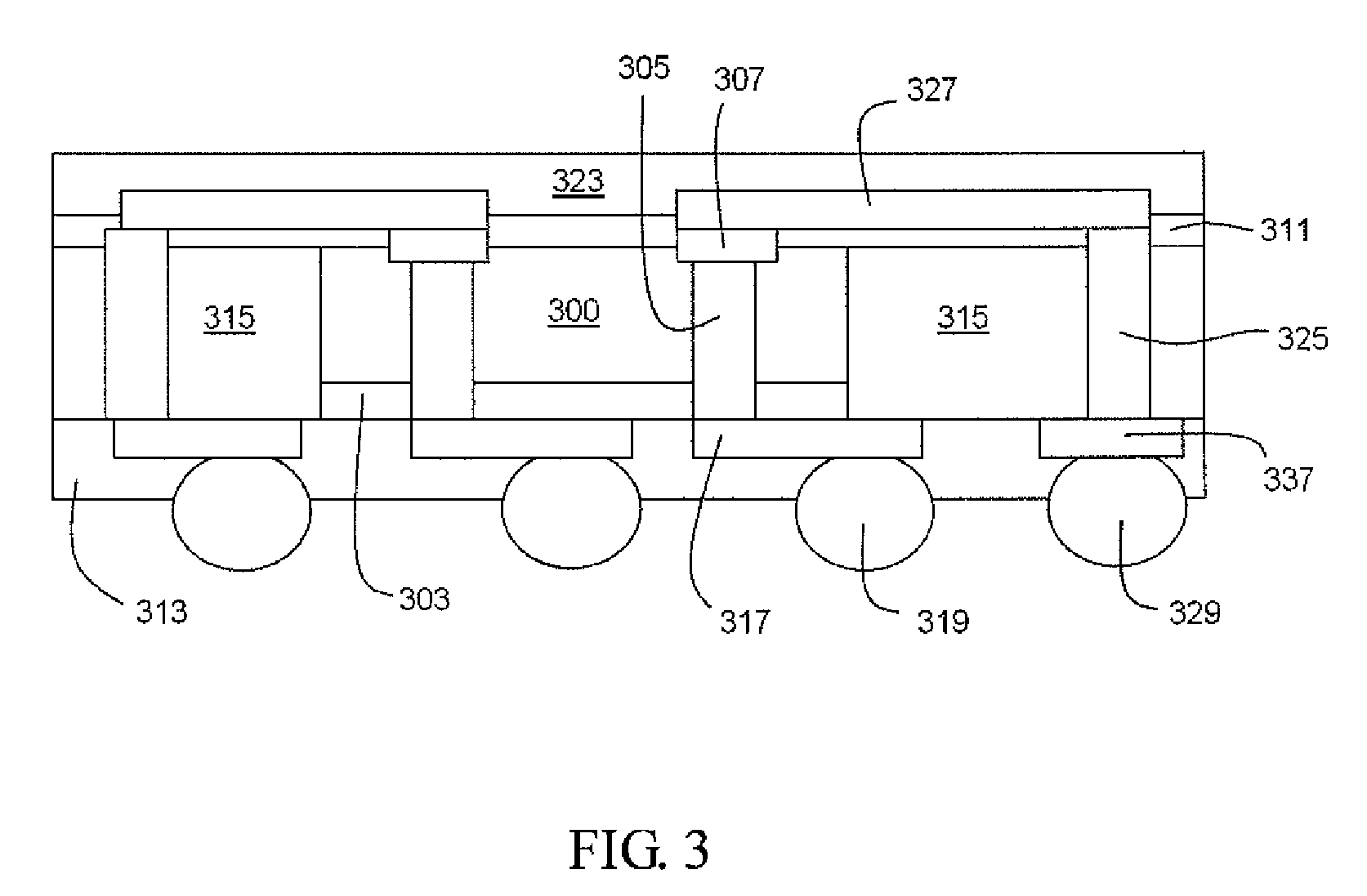

Portable drug delivery device having an encapsulated needle

ActiveUS20060200073A1Easy and swift needle operationEasy to useMedical devicesPressure infusionSkin surfaceMedicine

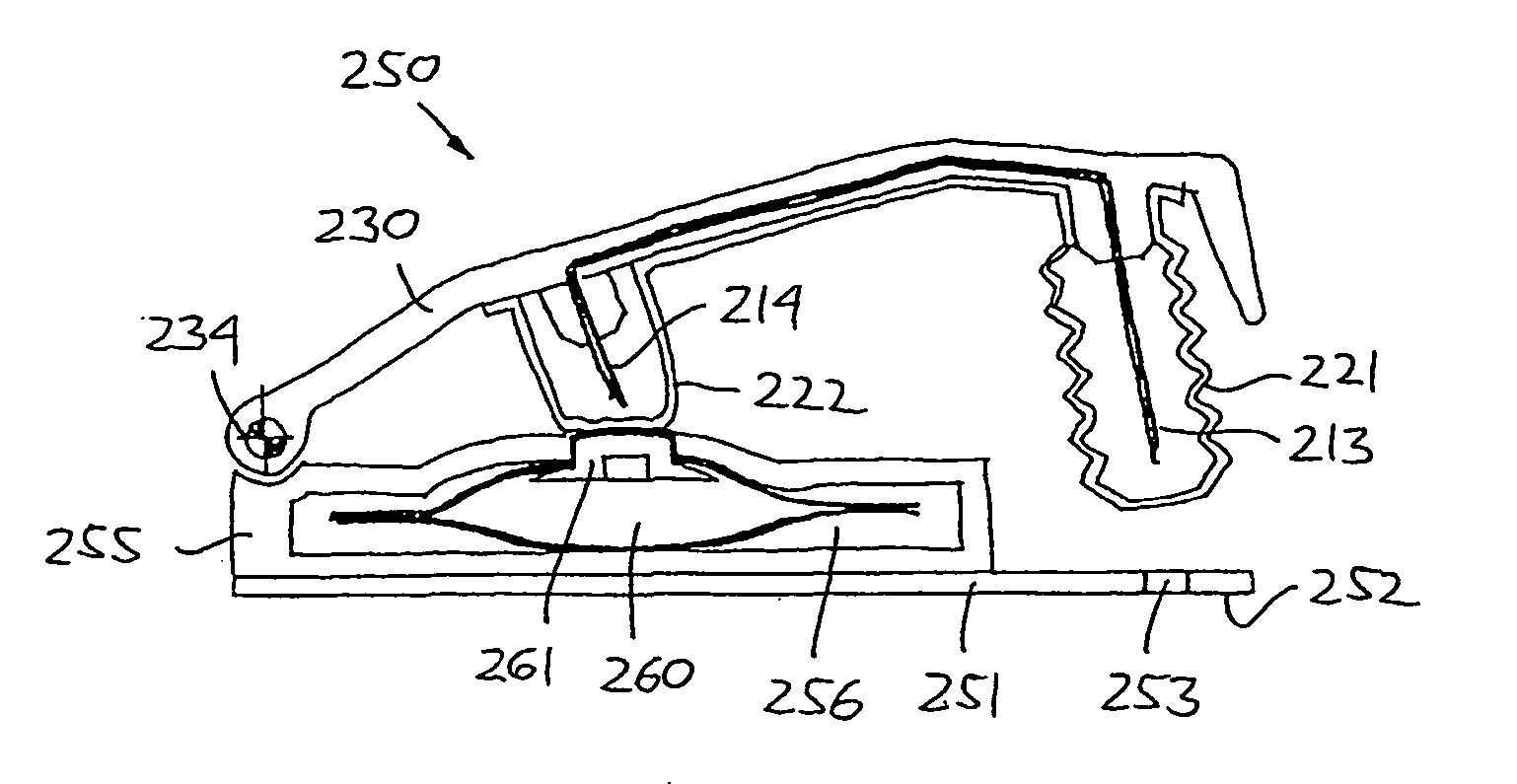

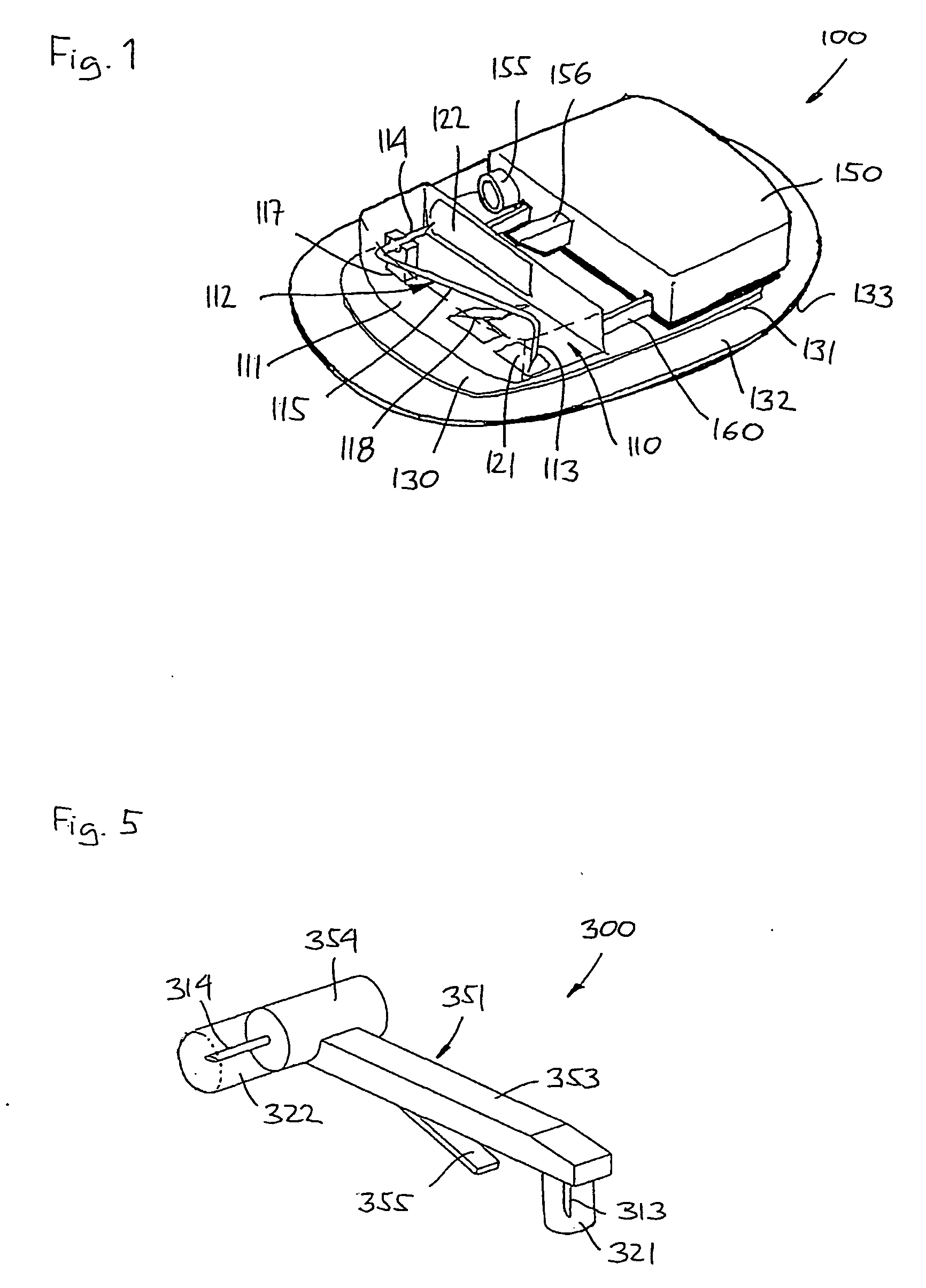

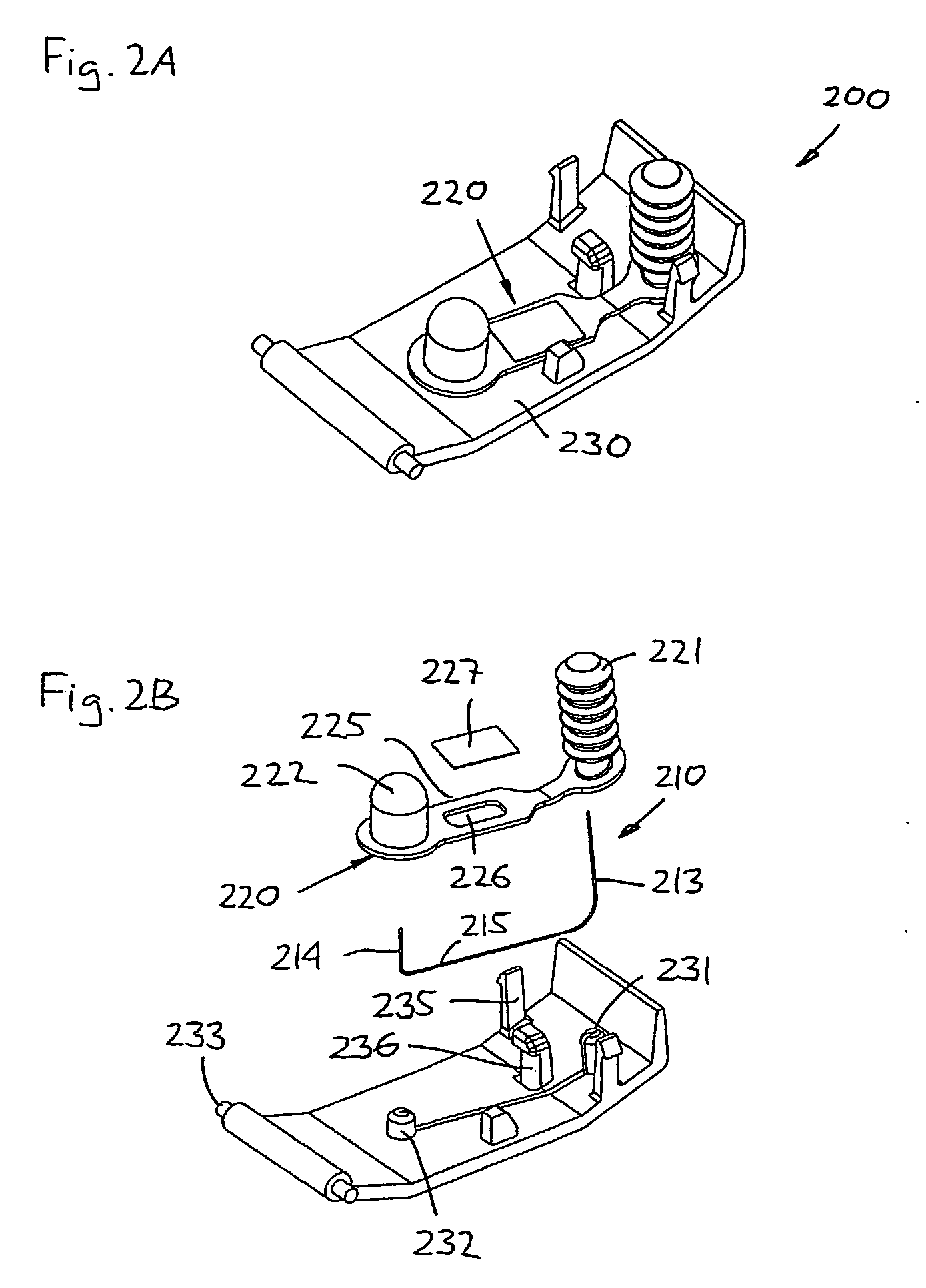

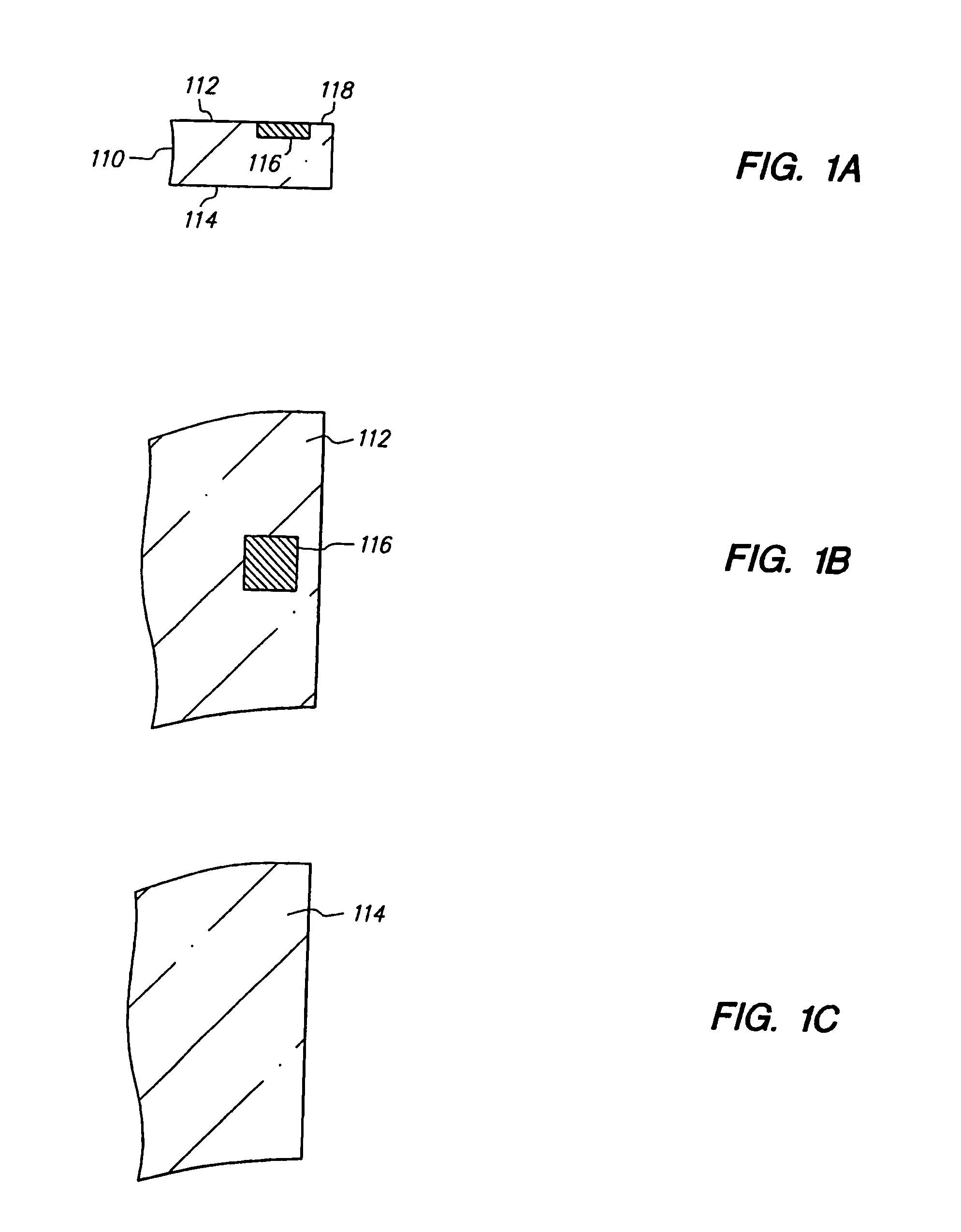

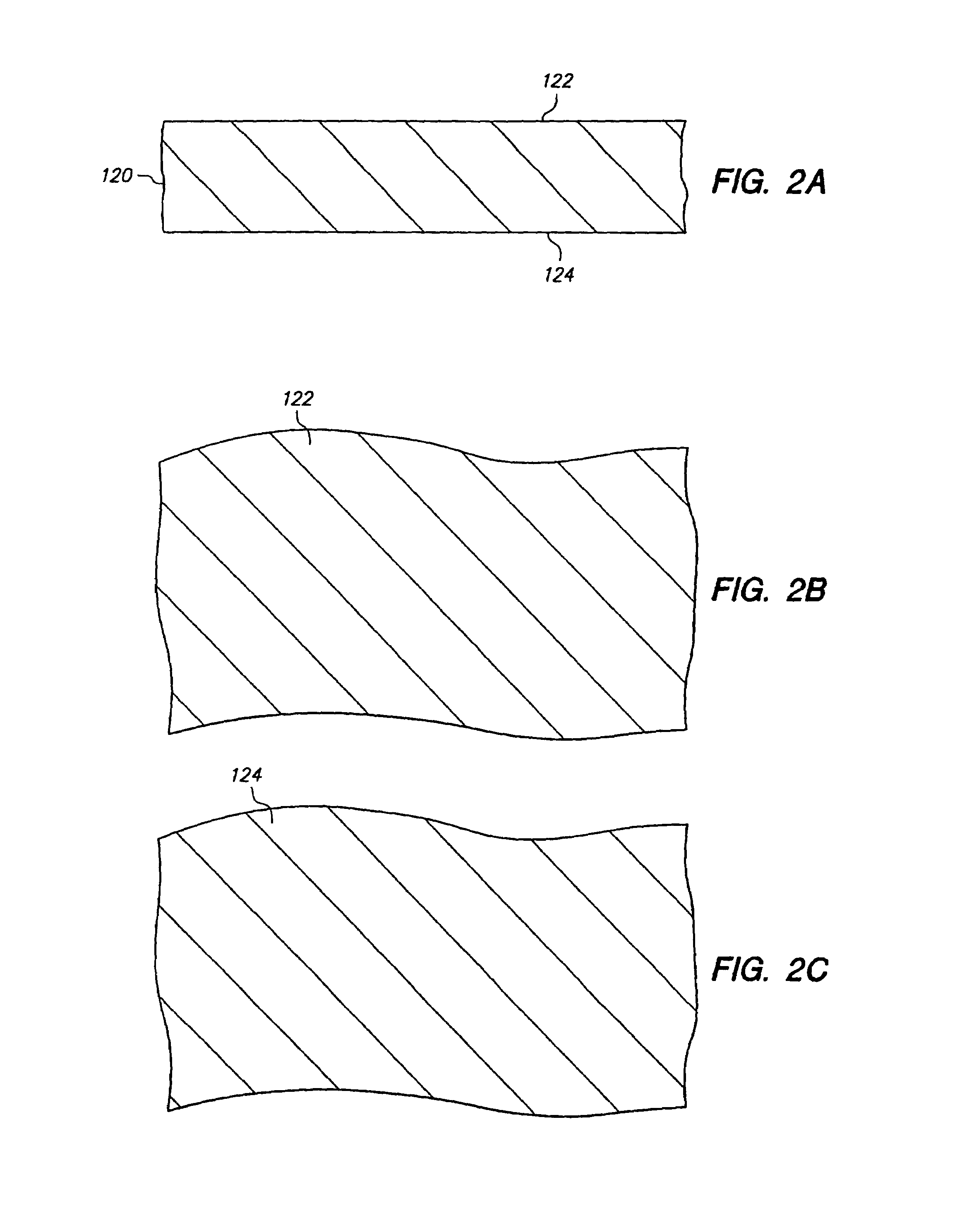

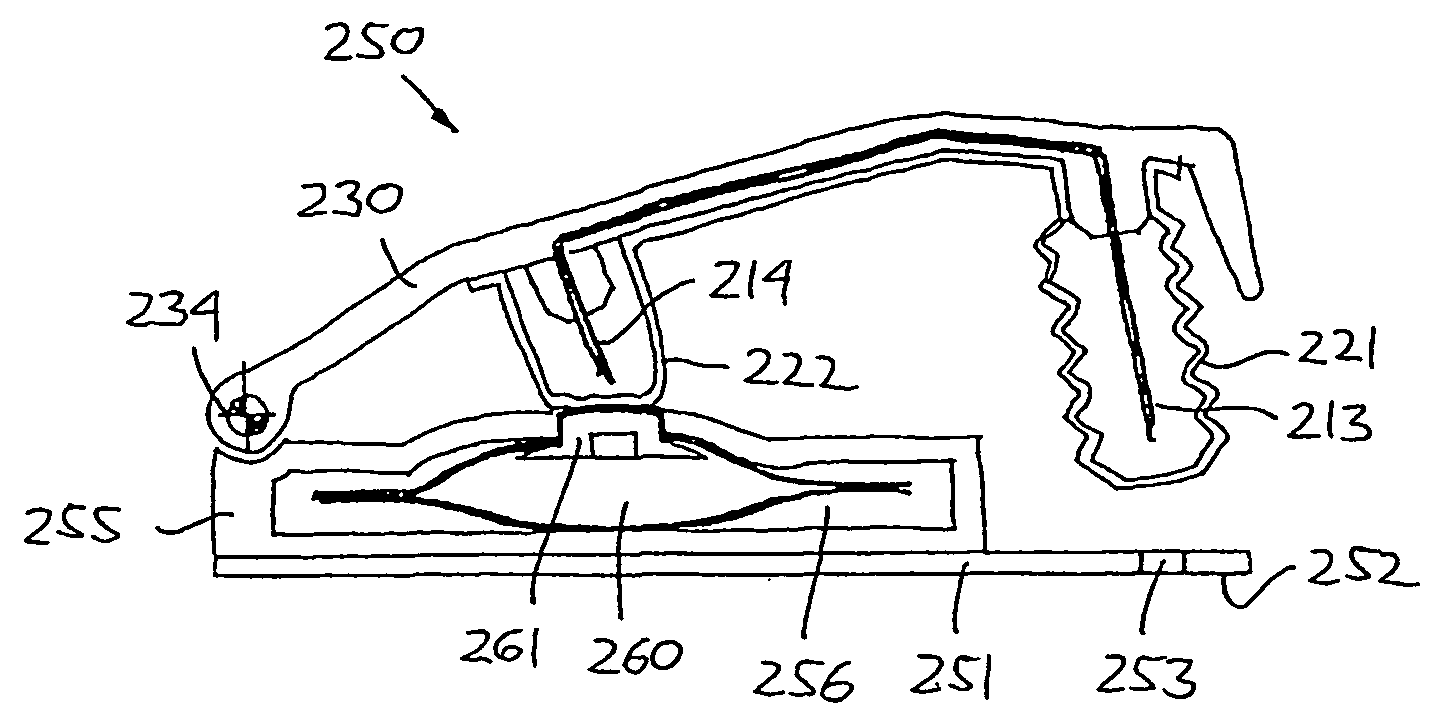

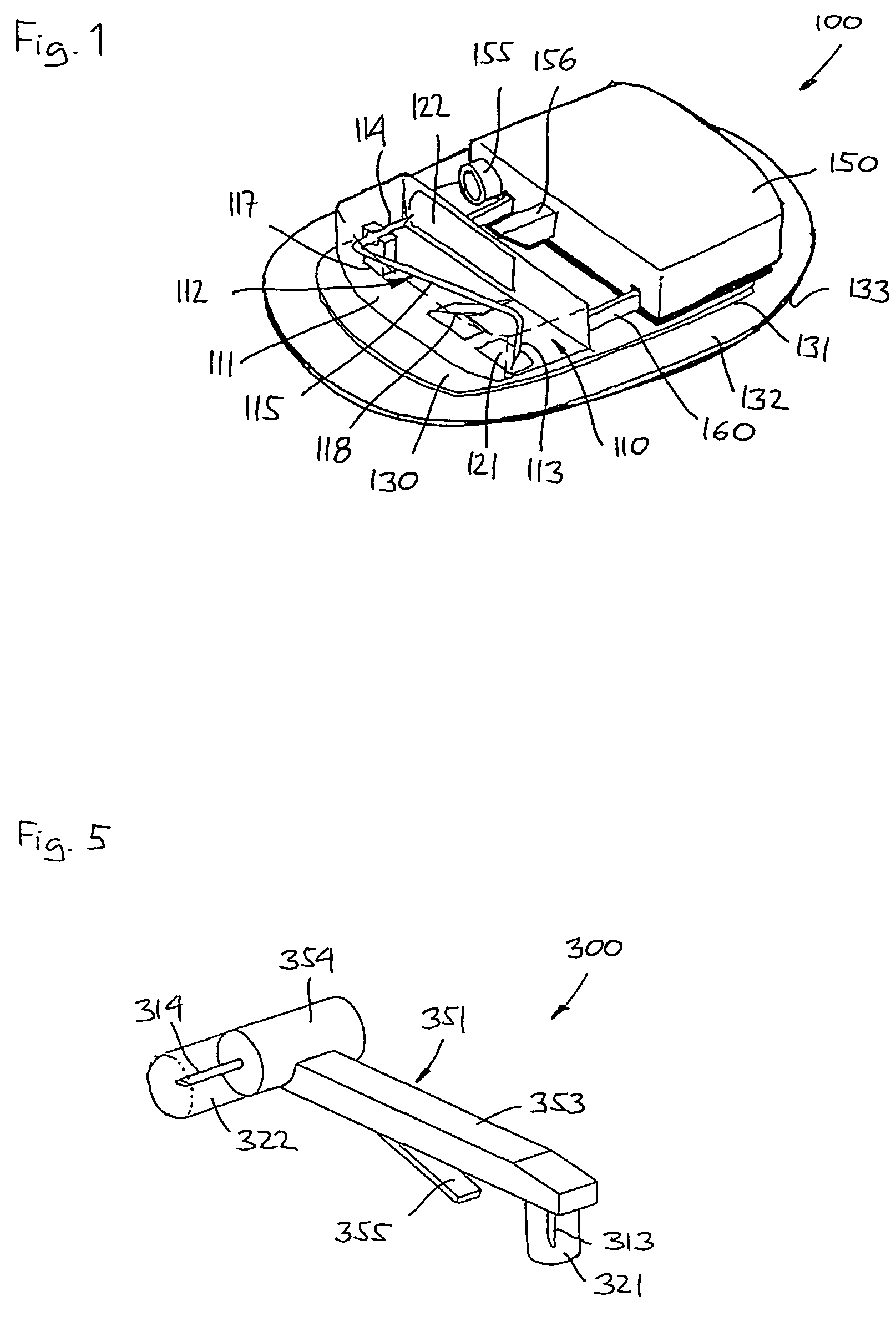

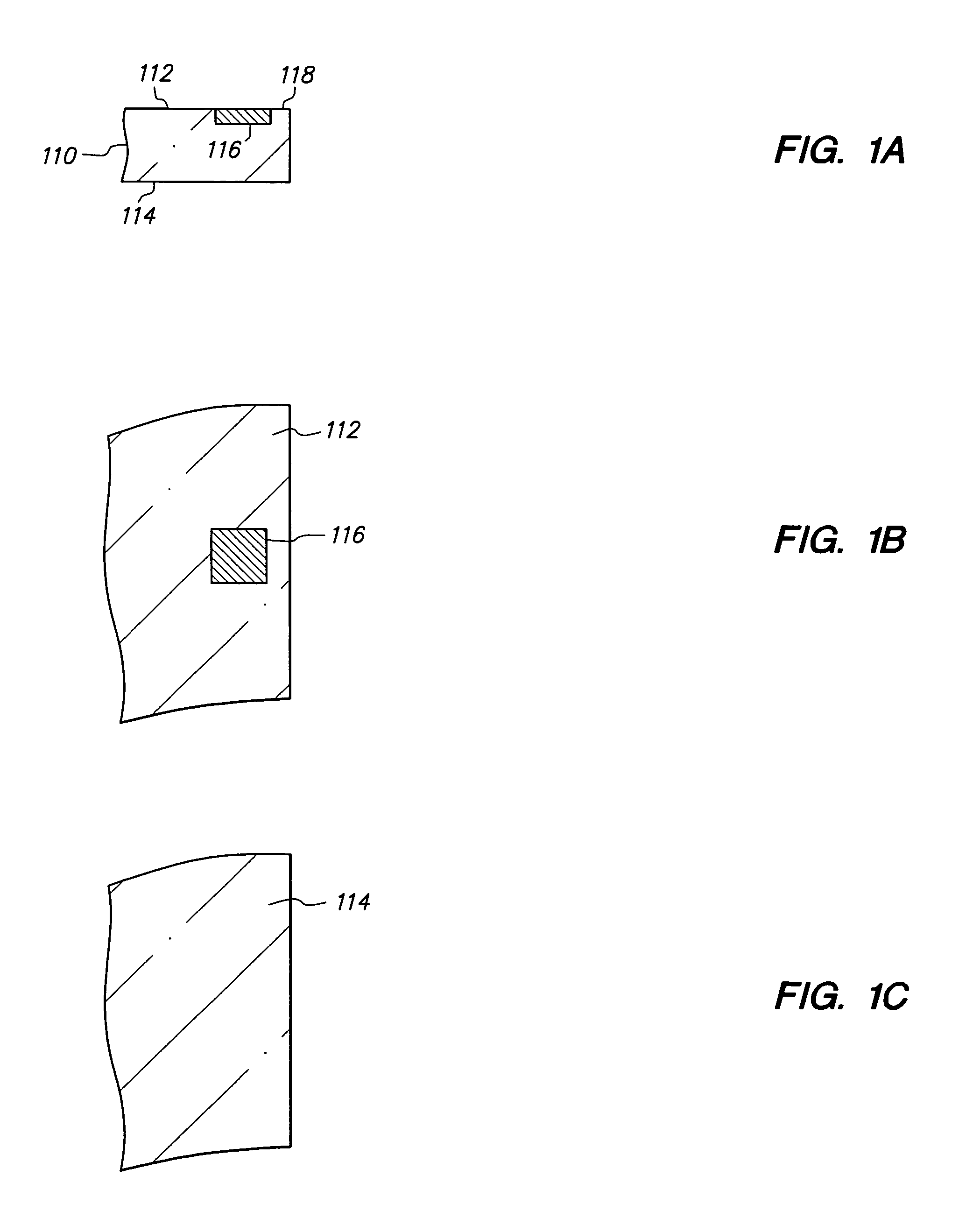

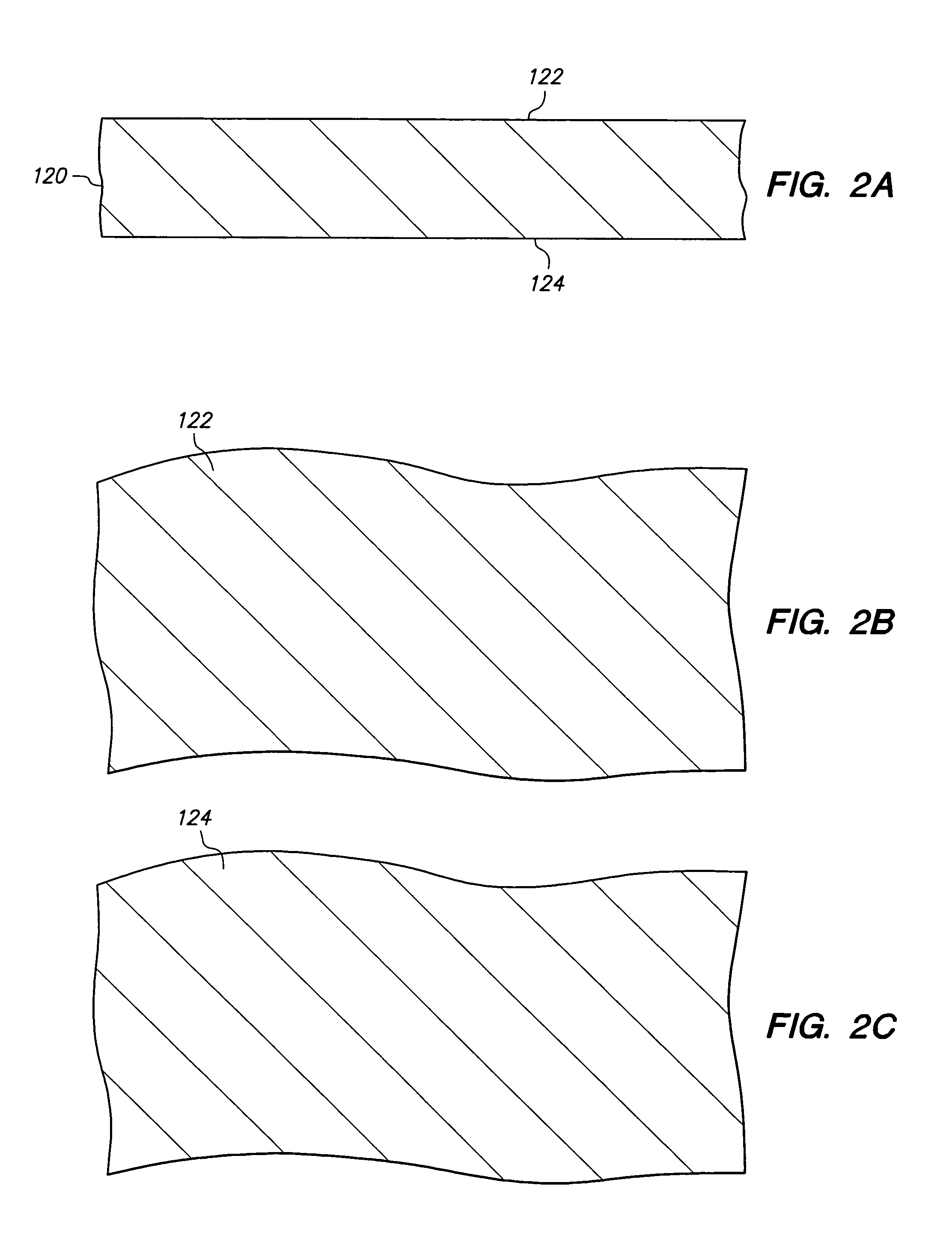

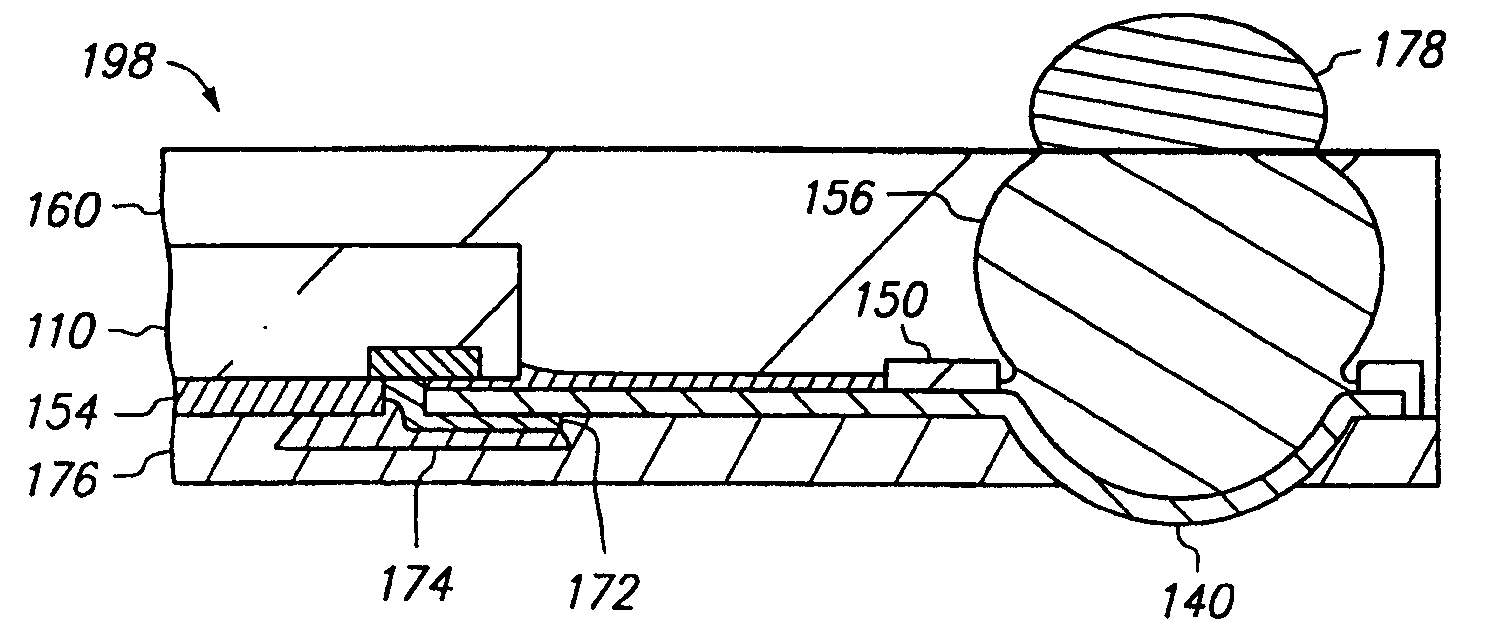

The present invention relates to medical devices which are adapted for application to a skin surface of a user and comprise a transcutaneous device which is supplied in a sterile condition. Thus, a medical device is provided, comprising a mounting surface adapted for application to the skin of a subject, a first portion having a first end adapted to penetrate the skin of the subject, and a second portion in fluid communication with the first portion and having a second end. The device further comprises enclosure means being transformable from an initial configuration encapsulating the first and second portions in an initial aseptic state, to a second configuration in which the ends of the first and second portions are allowed to communicate with the exterior through the enclosure means, wherein the enclosure means does not enclose the mounting surface.

Owner:NOVO NORDISK AS

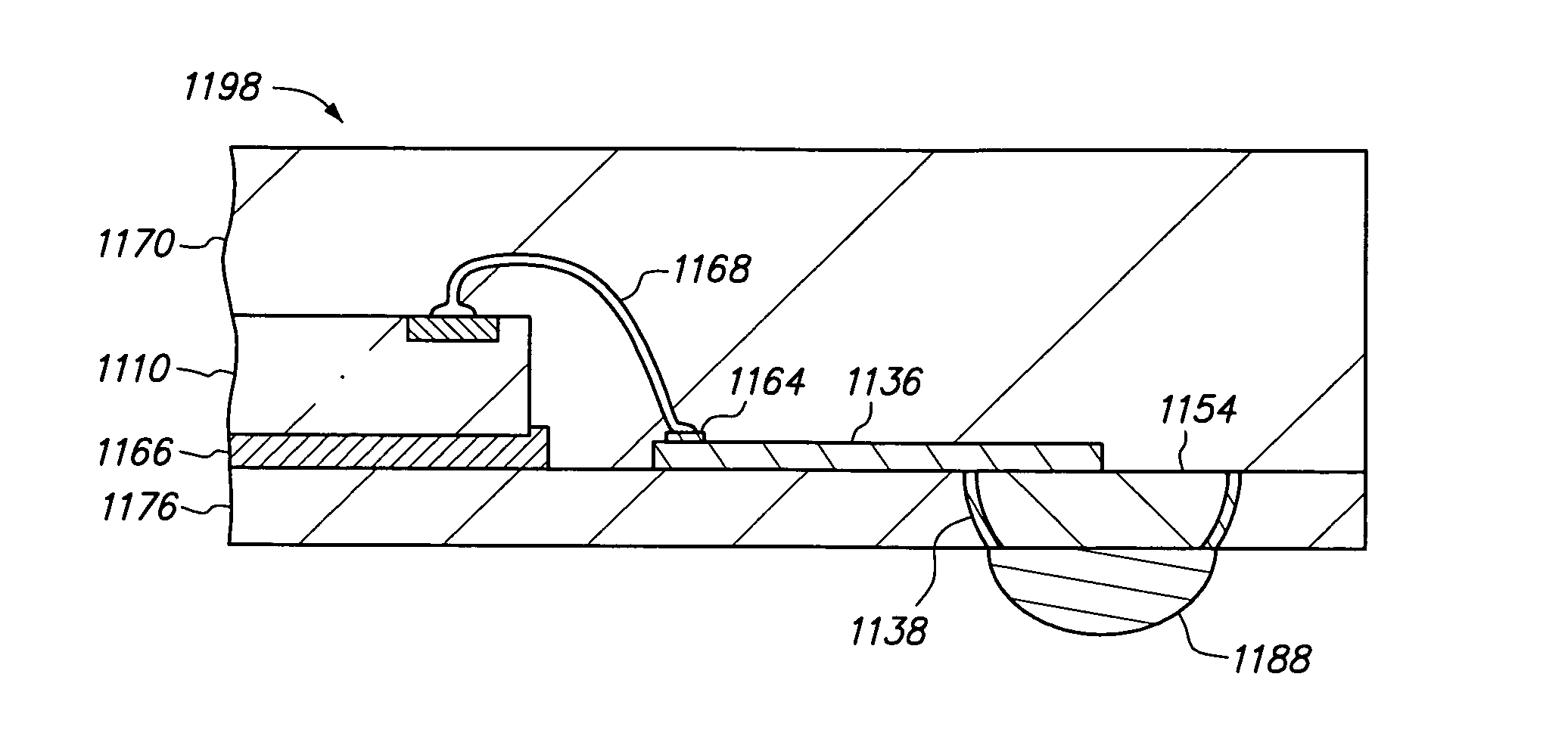

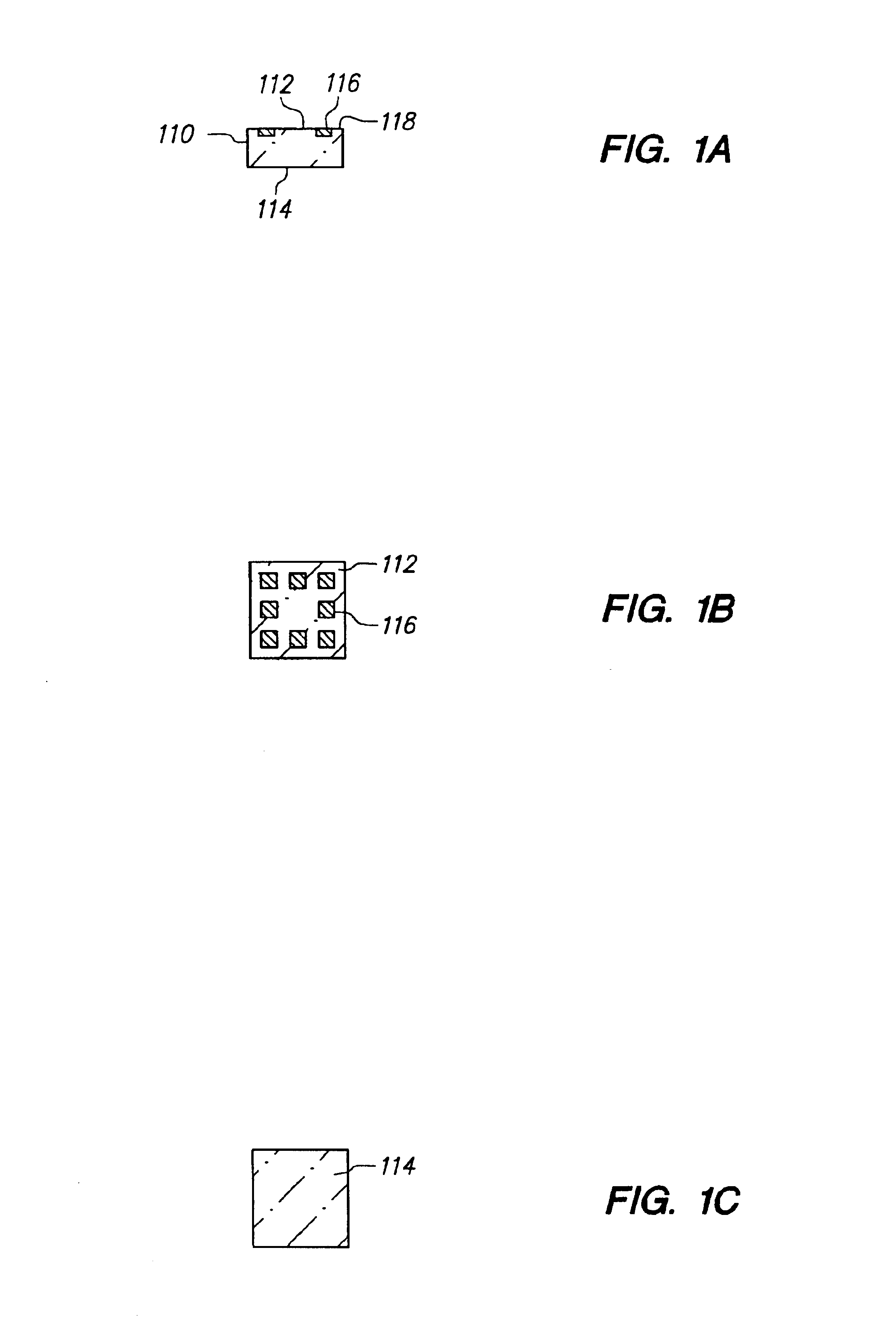

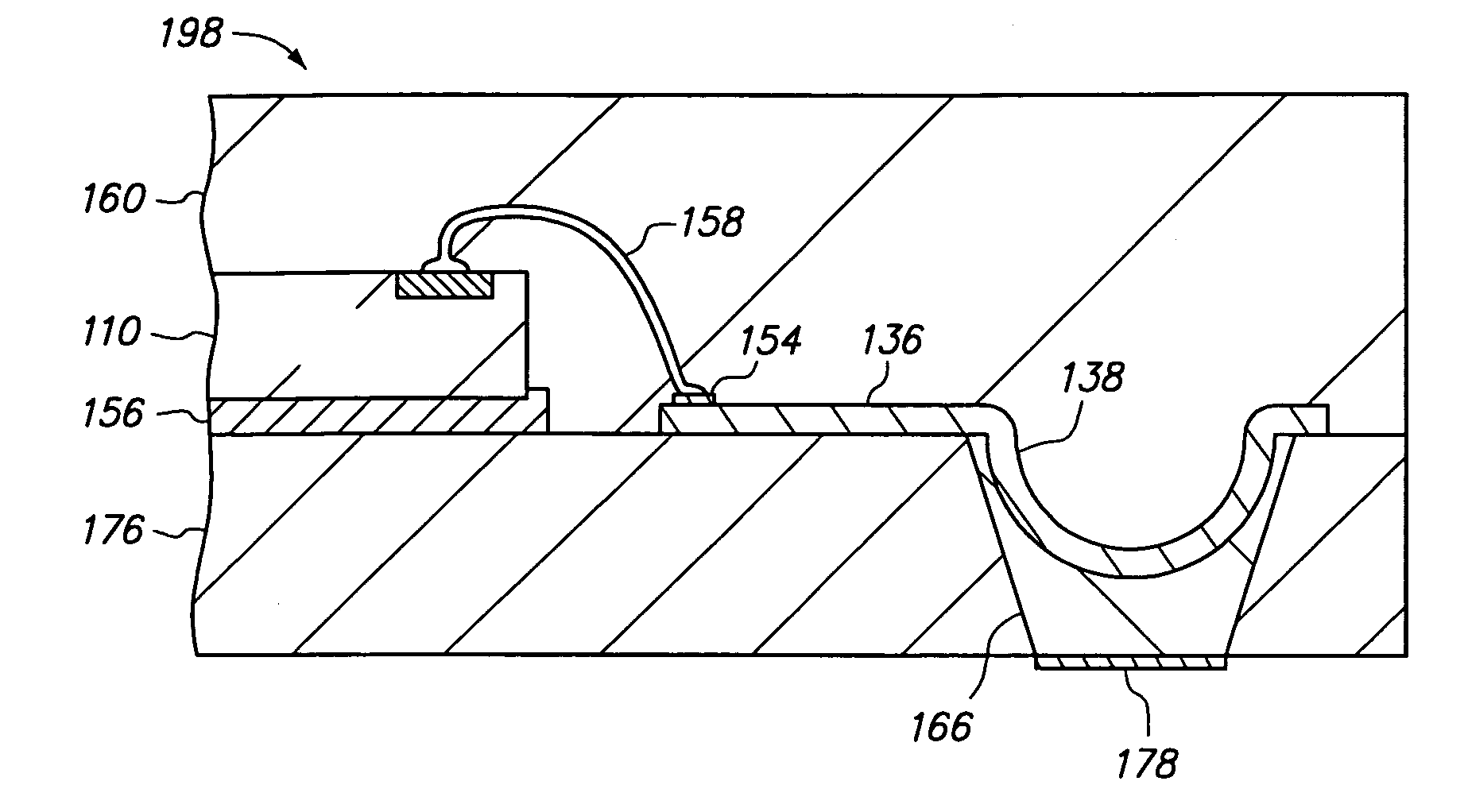

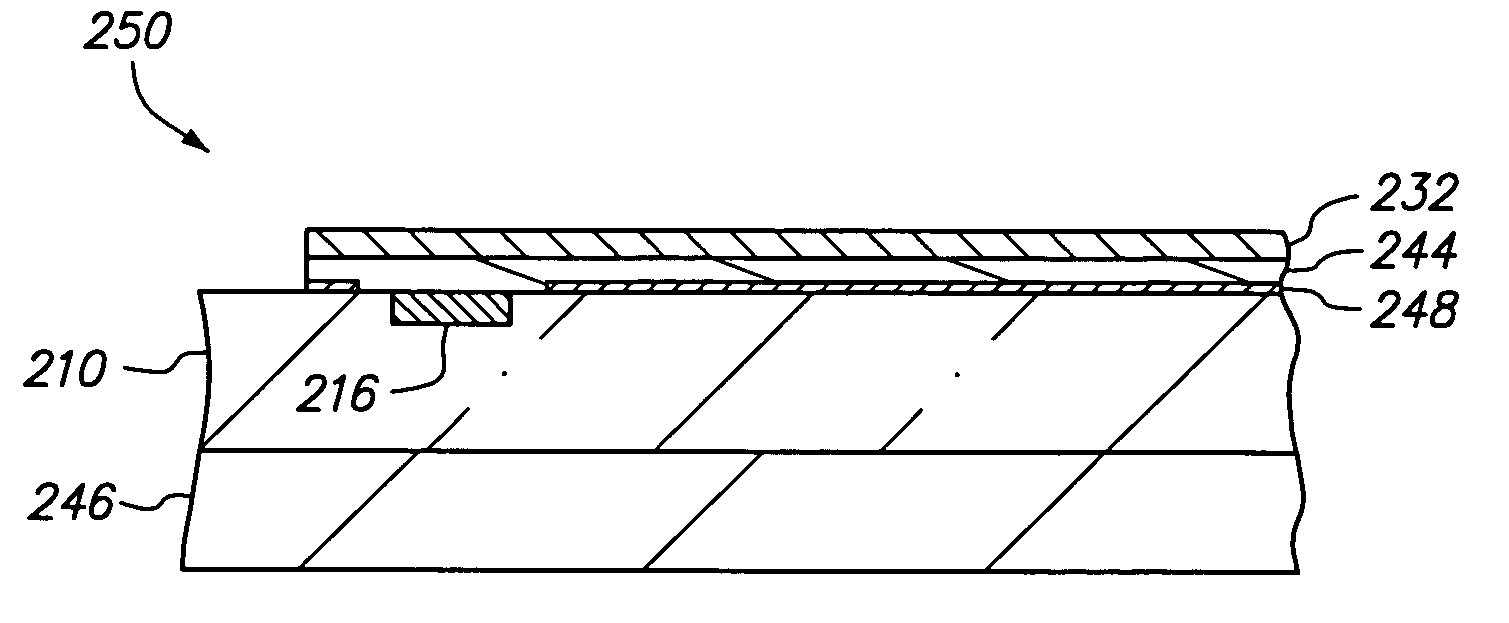

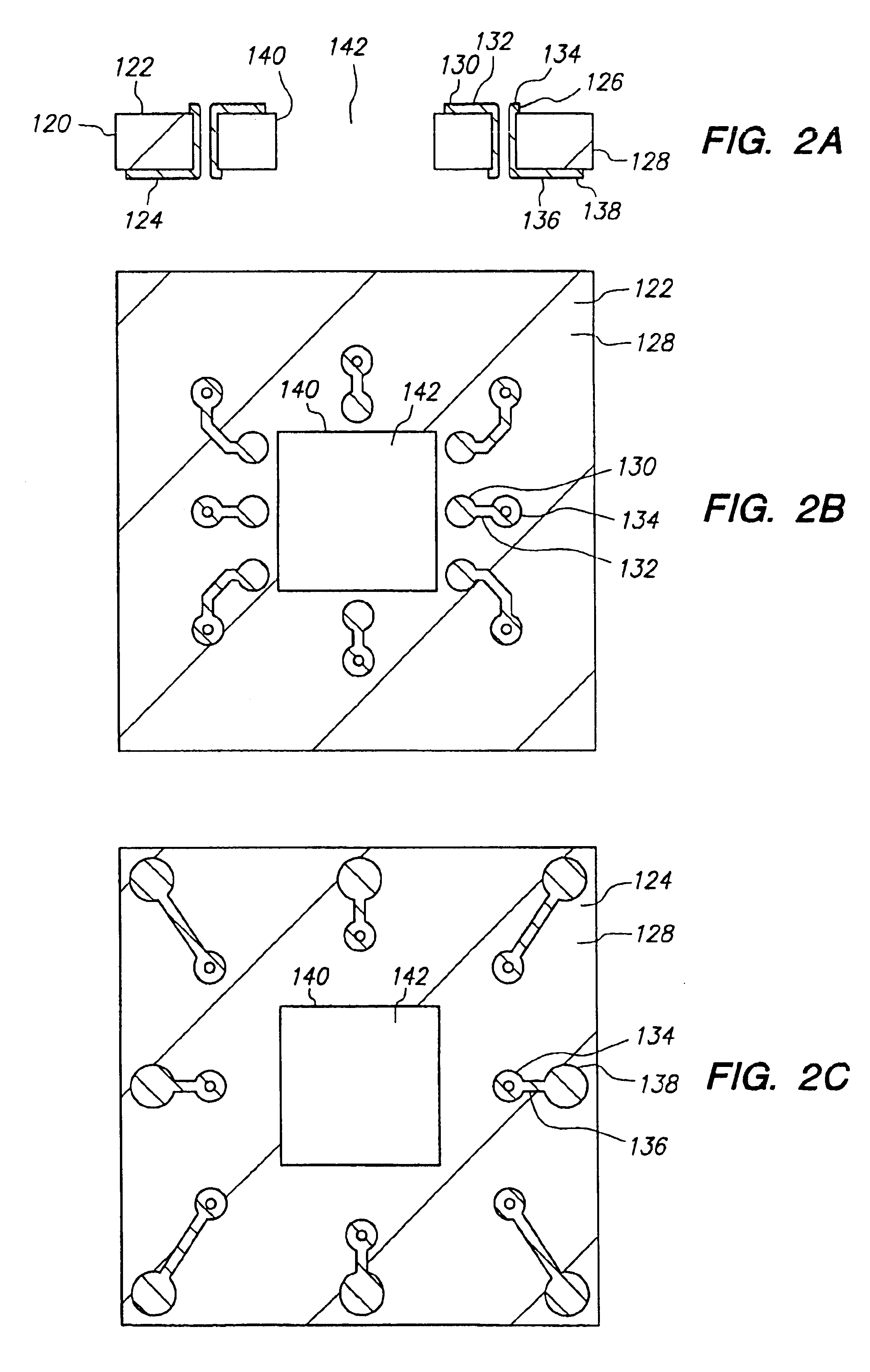

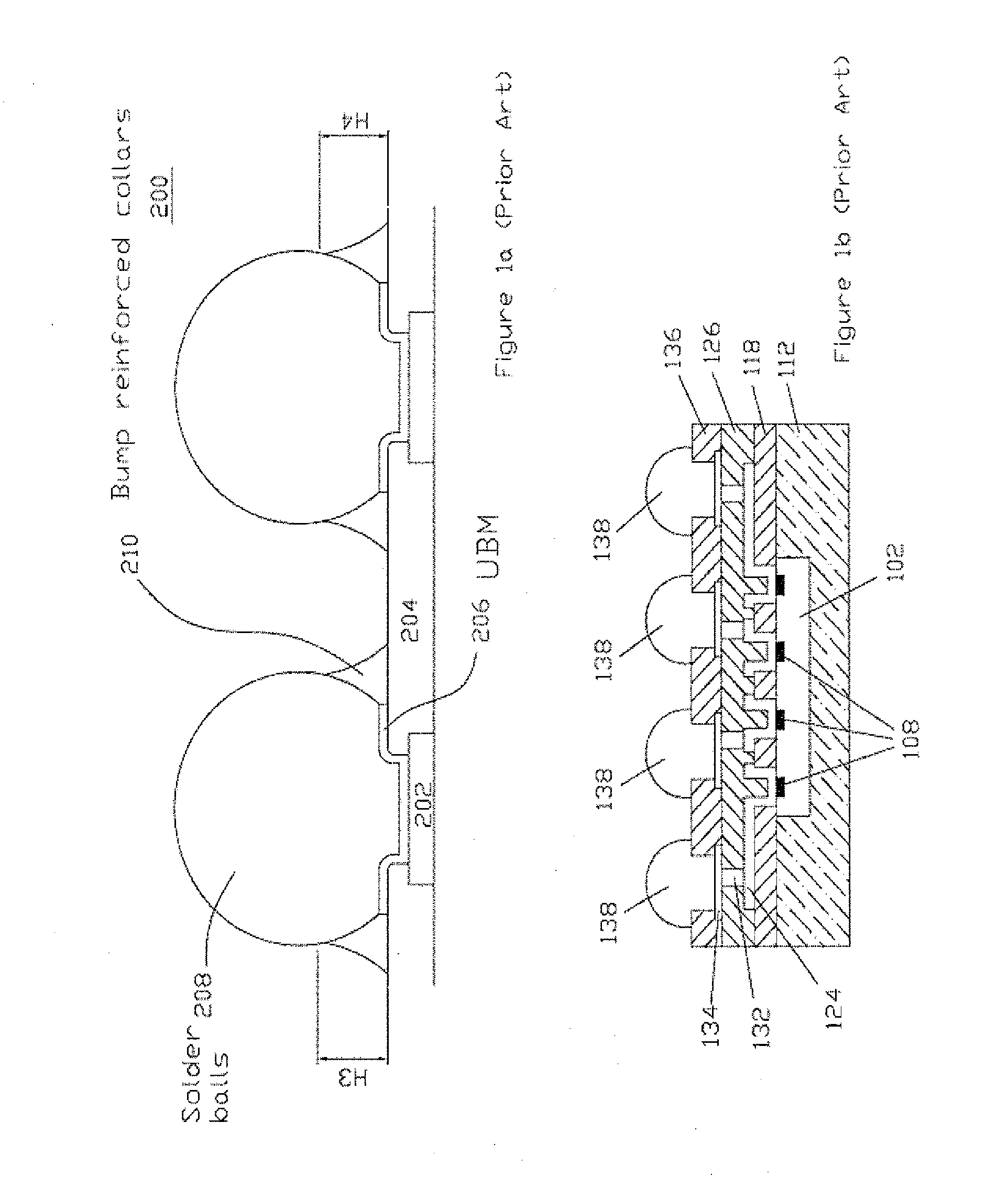

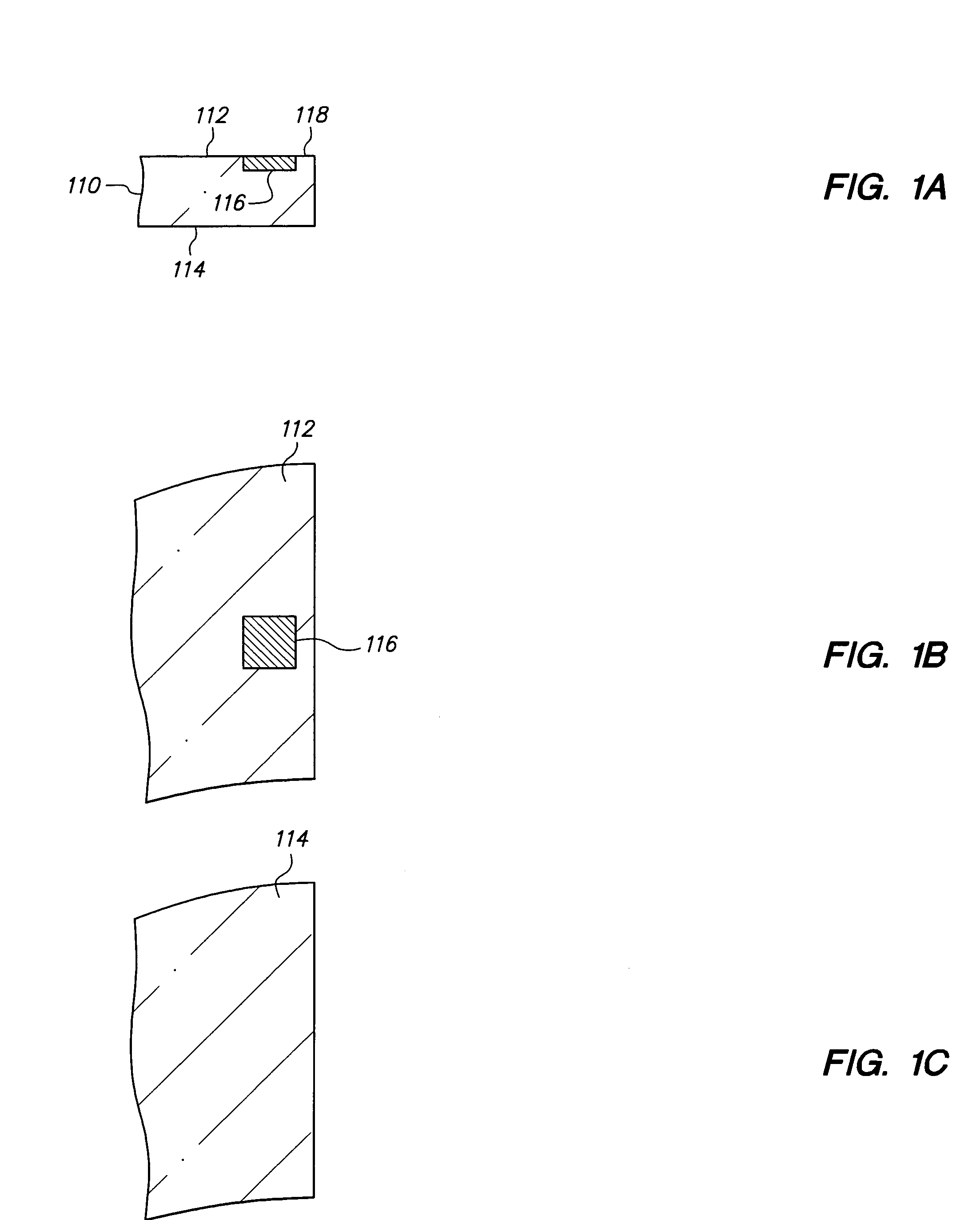

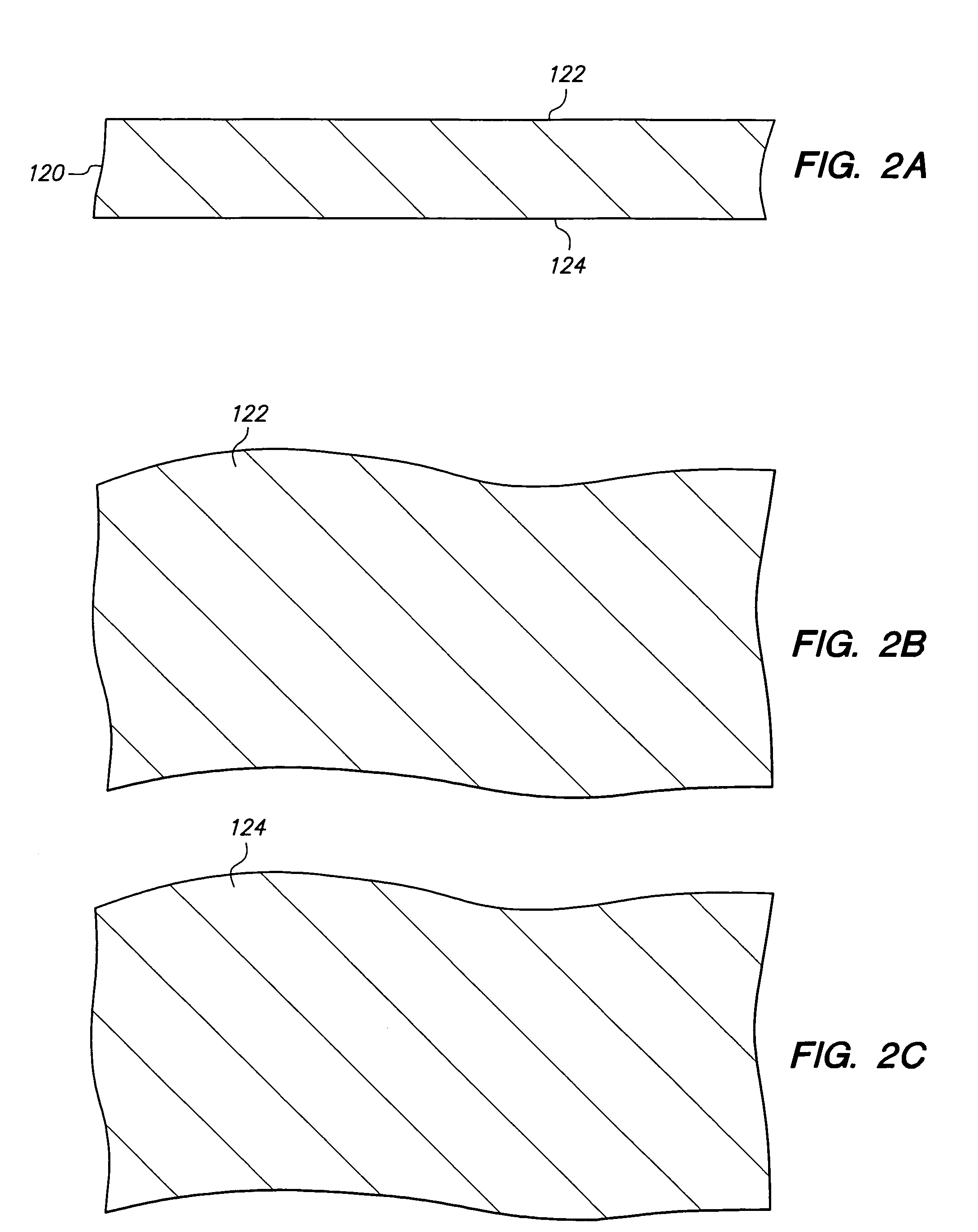

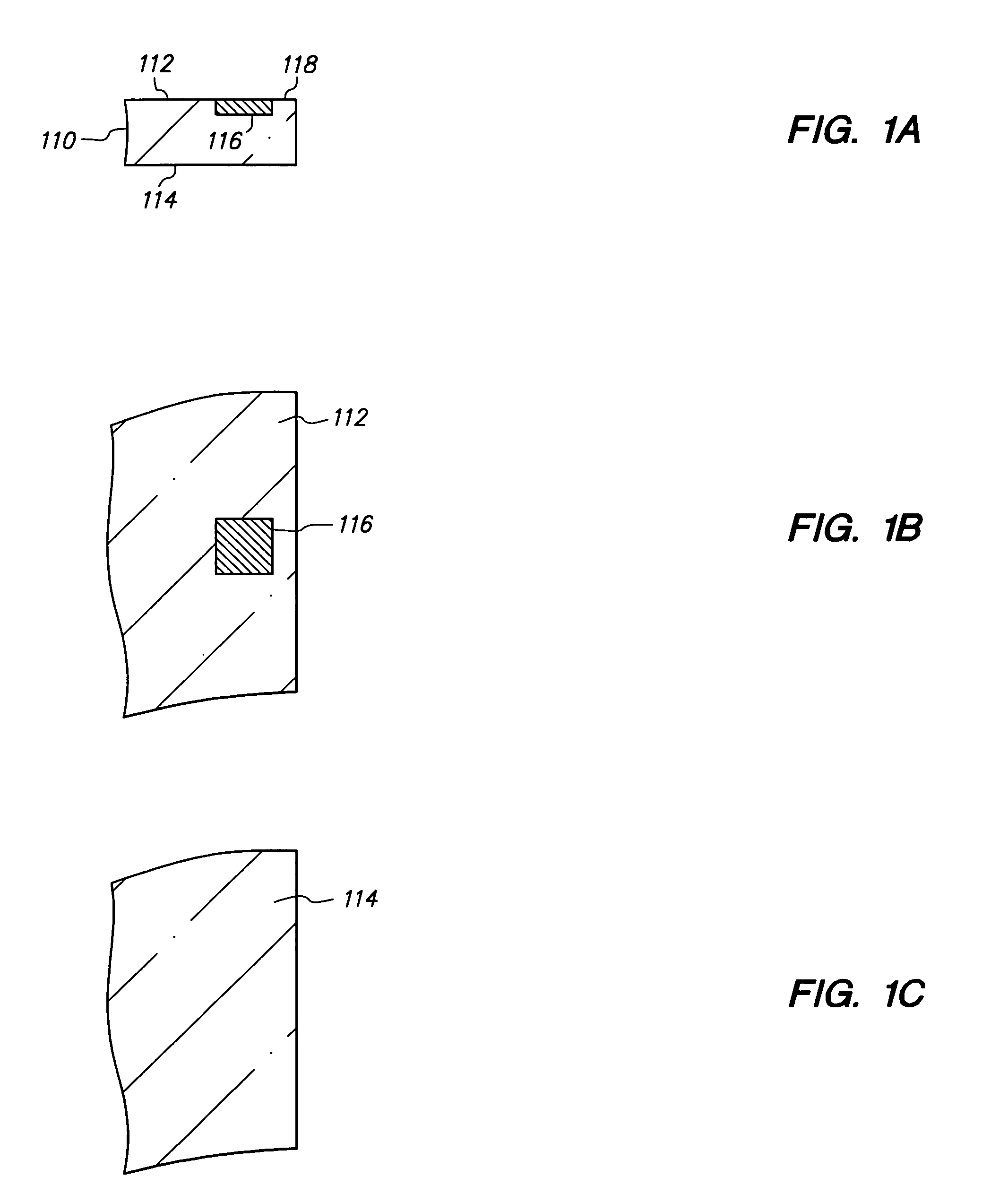

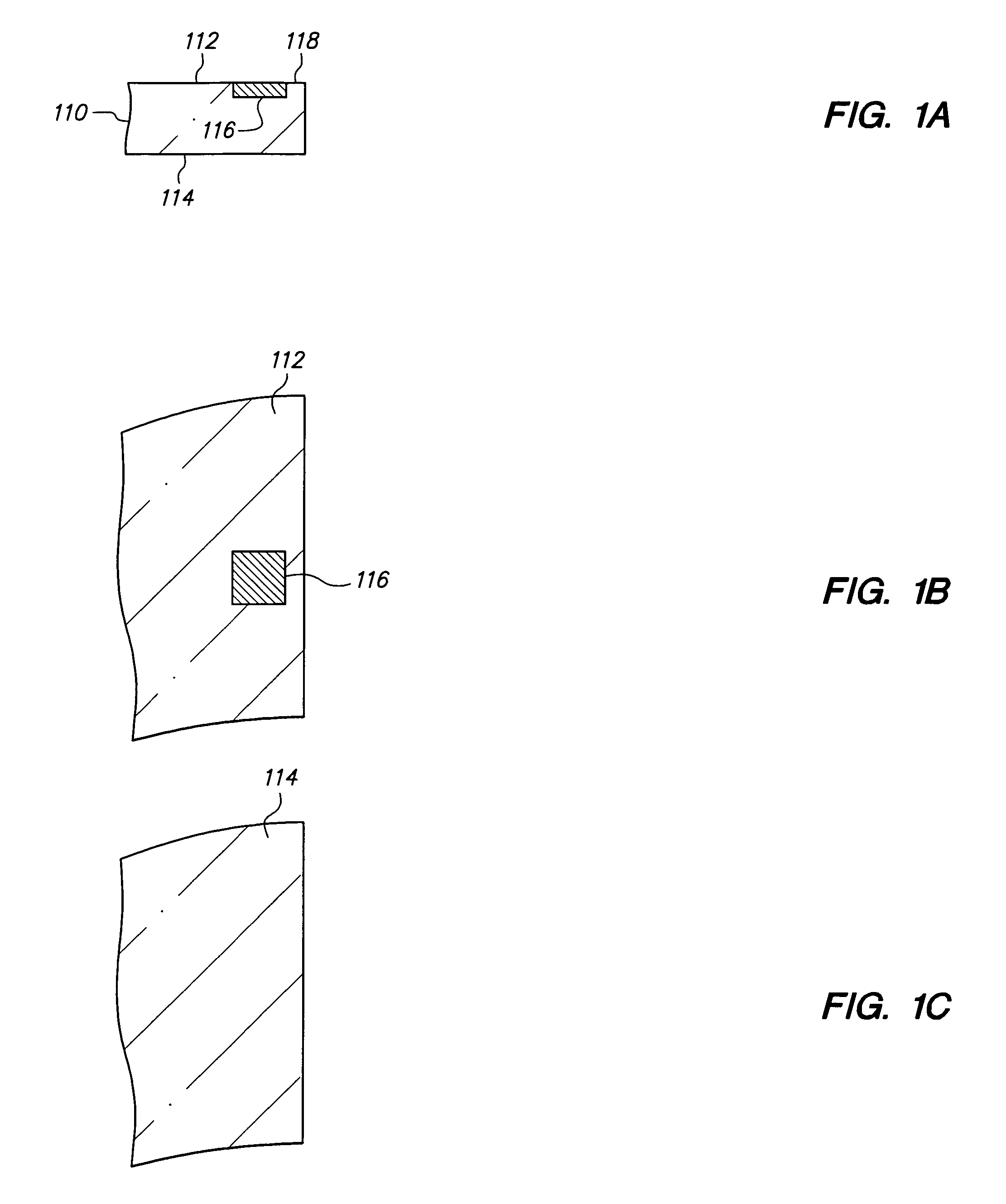

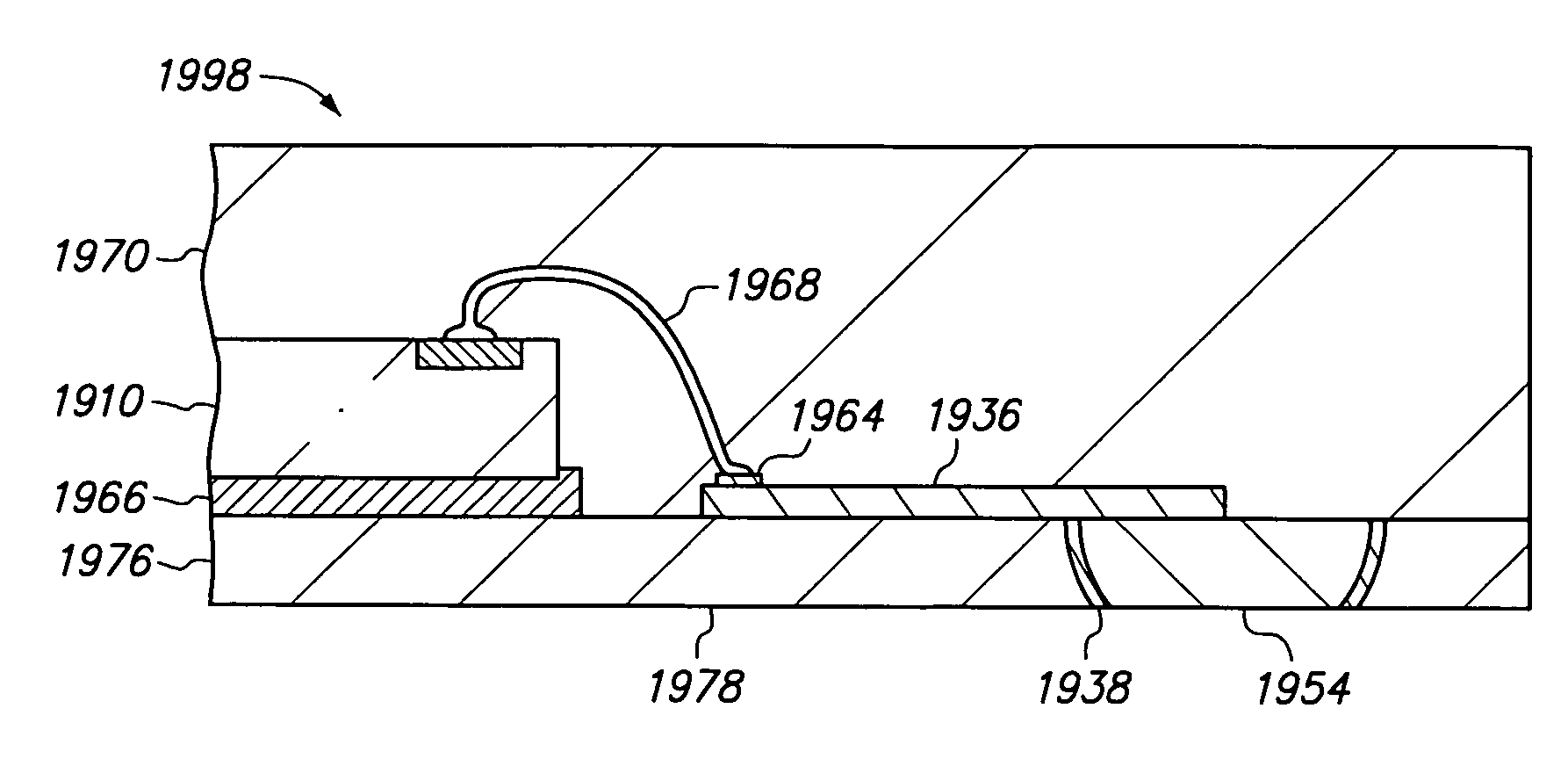

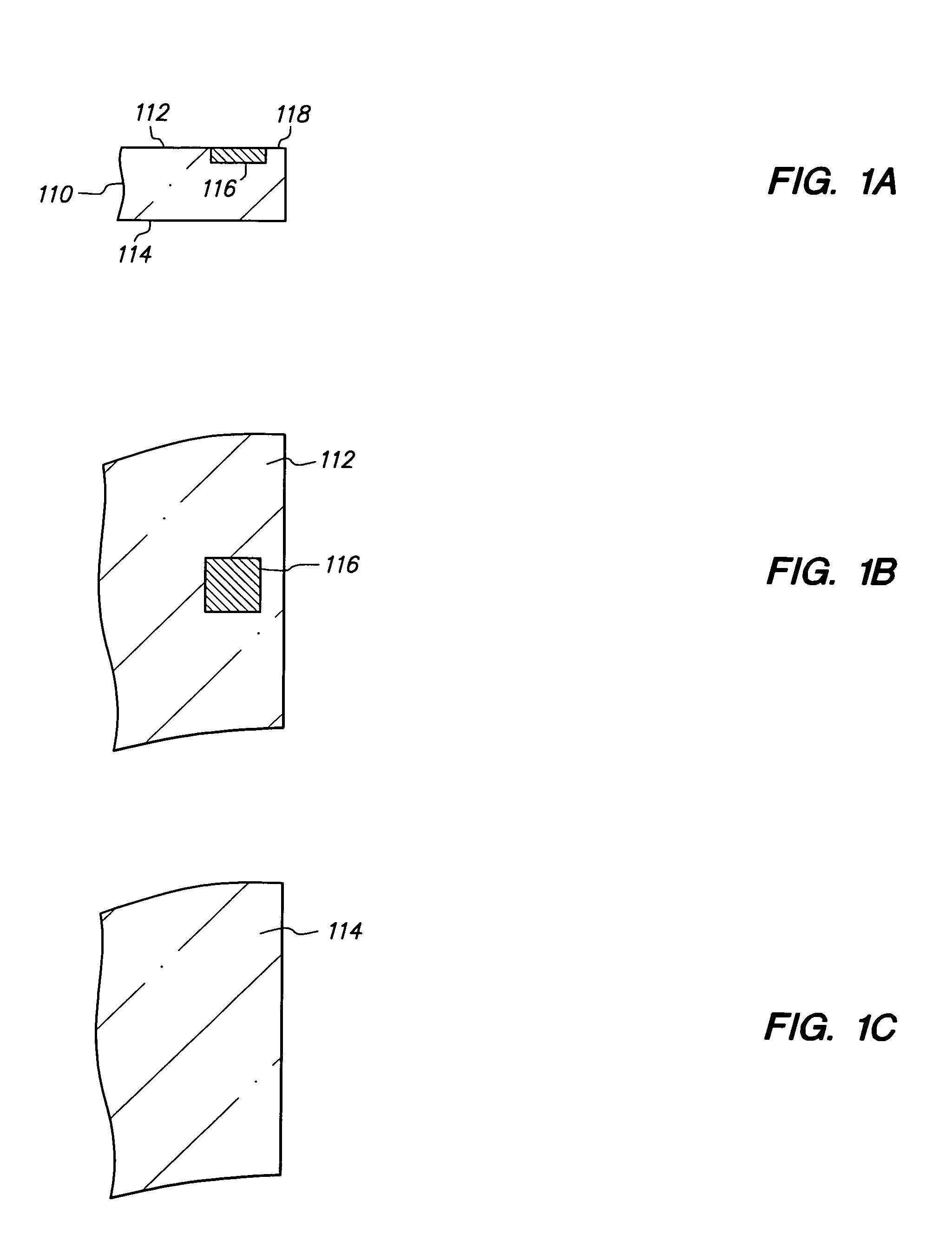

Semiconductor chip assembly with embedded metal particle

InactiveUS7009297B1Enhancing mechanical supportImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal particle

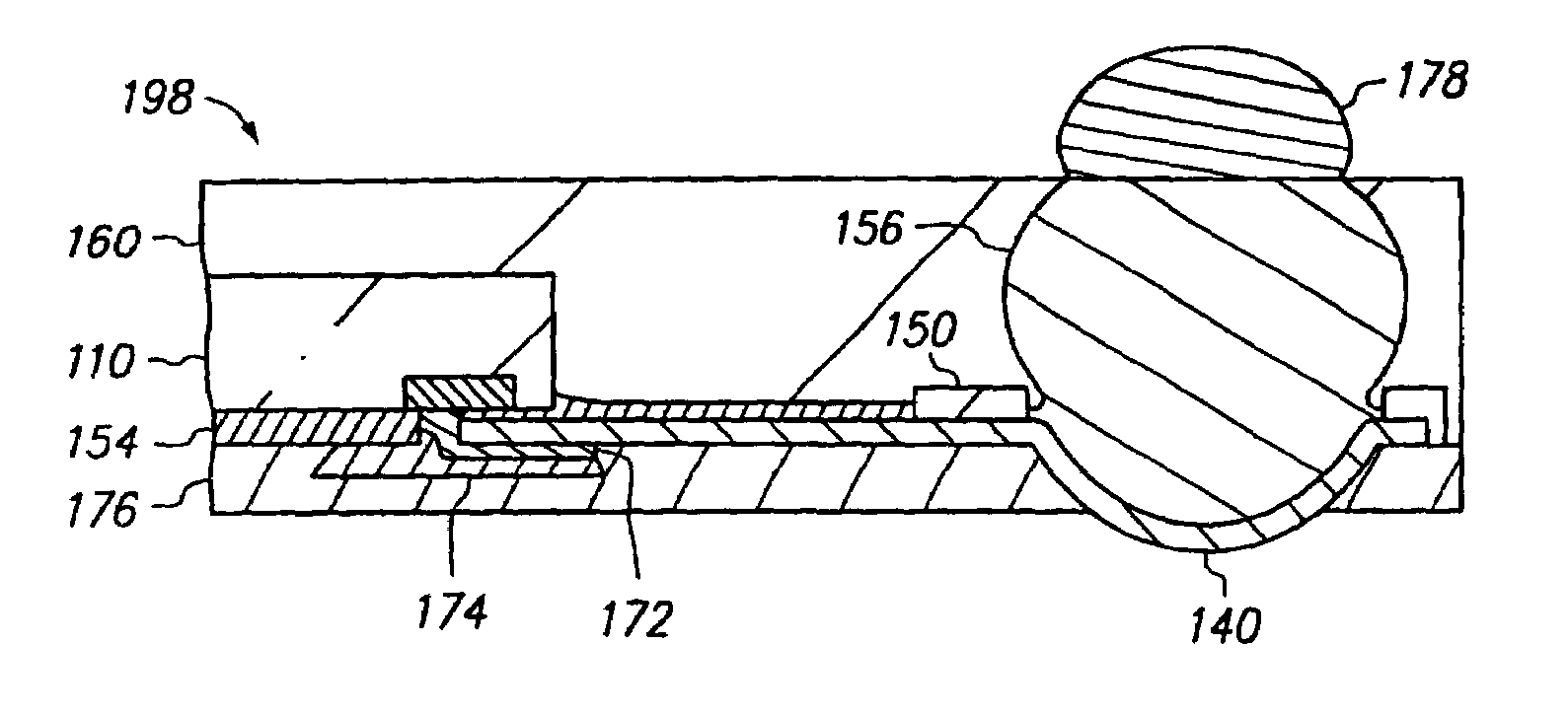

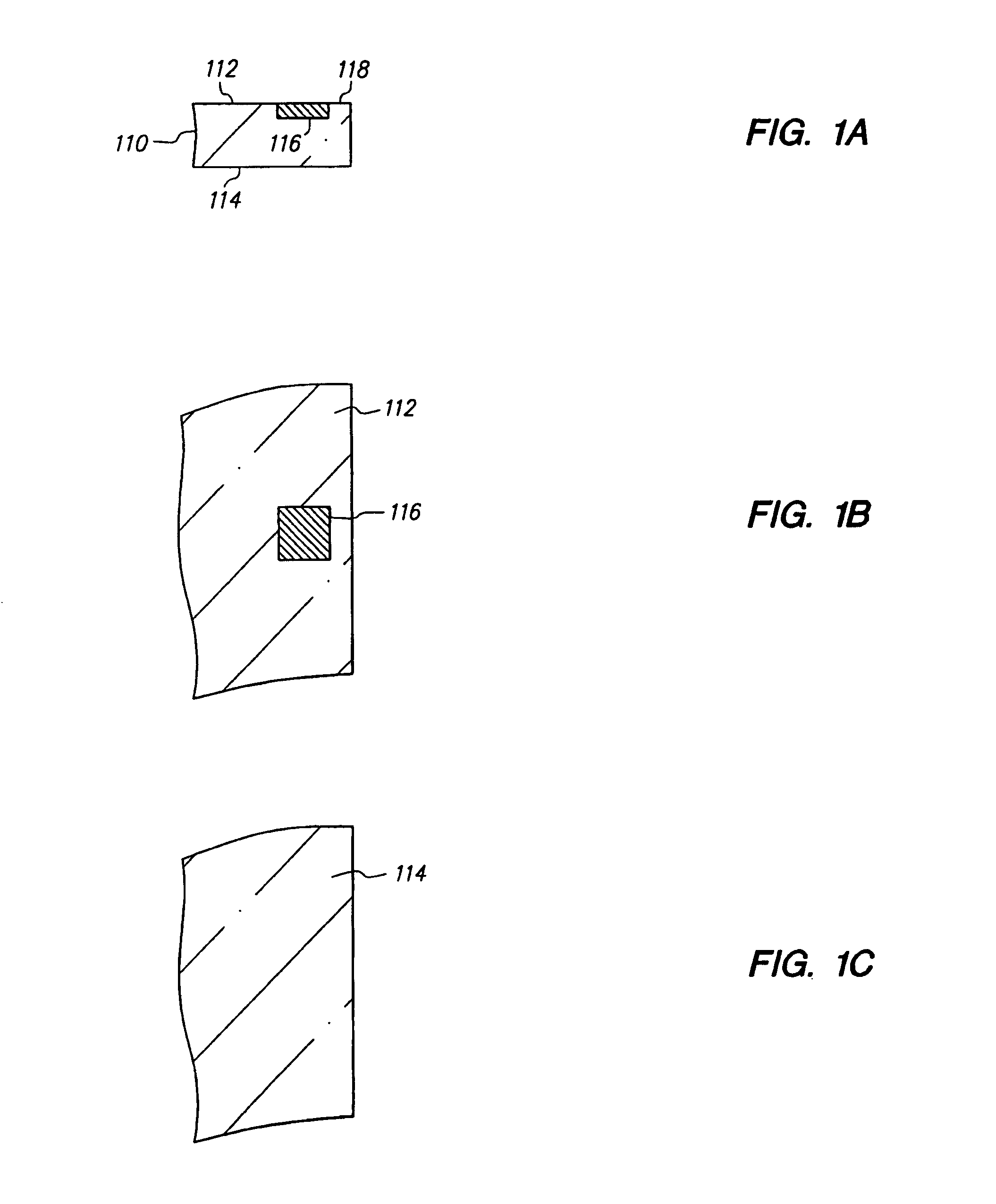

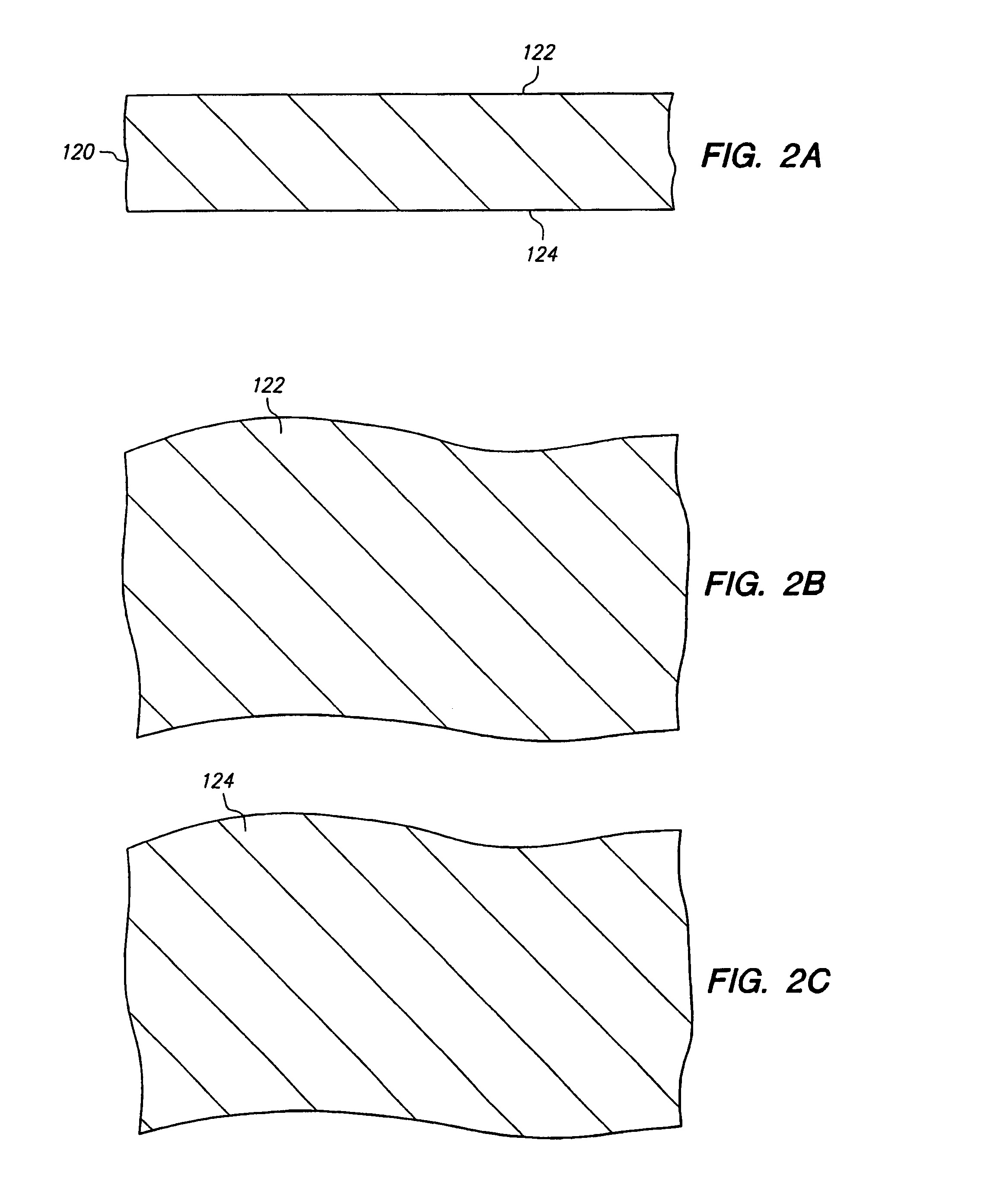

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line and a metal particle, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The routing line extends laterally beyond the metal particle towards the chip, and the chip and the metal particle are embedded in the encapsulant and extend vertically beyond the routing line in the same direction.

Owner:BRIDGE SEMICON

Portable drug delivery device having an encapsulated needle

ActiveUS7780636B2Easy and swift needle operationEasy to useAmpoule syringesPressure infusionSkin surfaceMedical device

The present invention relates to medical devices which are adapted for application to a skin surface of a user and comprise a transcutaneous device which is supplied in a sterile condition. Thus, a medical device is provided, comprising a mounting surface adapted for application to the skin of a subject, a first portion having a first end adapted to penetrate the skin of the subject, and a second portion in fluid communication with the first portion and having a second end. The device further comprises enclosure means being transformable from an initial configuration encapsulating the first and second portions in an initial aseptic state, to a second configuration in which the ends of the first and second portions are allowed to communicate with the exterior through the enclosure means, wherein the enclosure means does not enclose the mounting surface.

Owner:NOVO NORDISK AS

Semiconductor chip assembly with laterally aligned bumped terminal and filler

InactiveUS7417314B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSealant

Owner:BRIDGE SEMICON

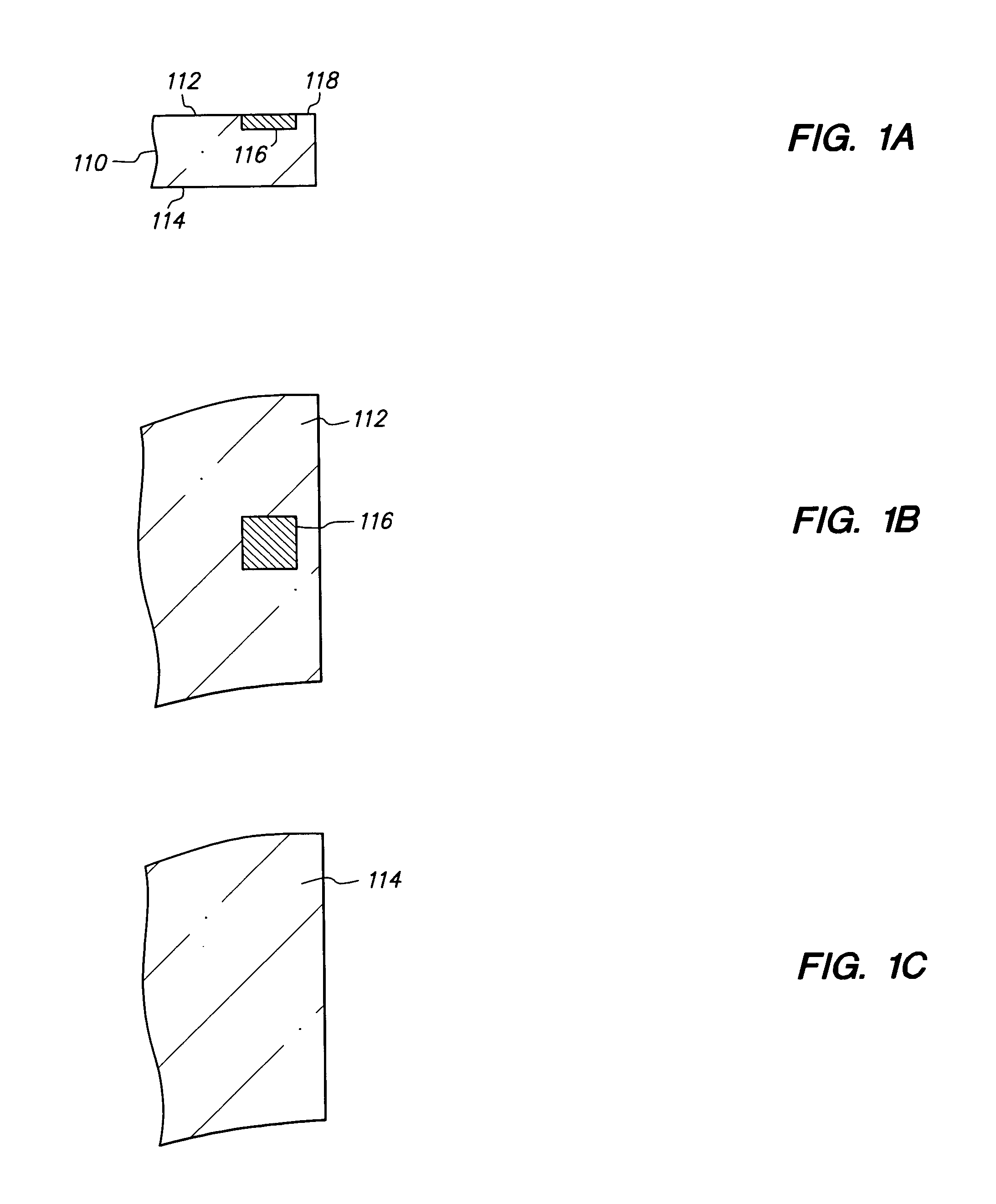

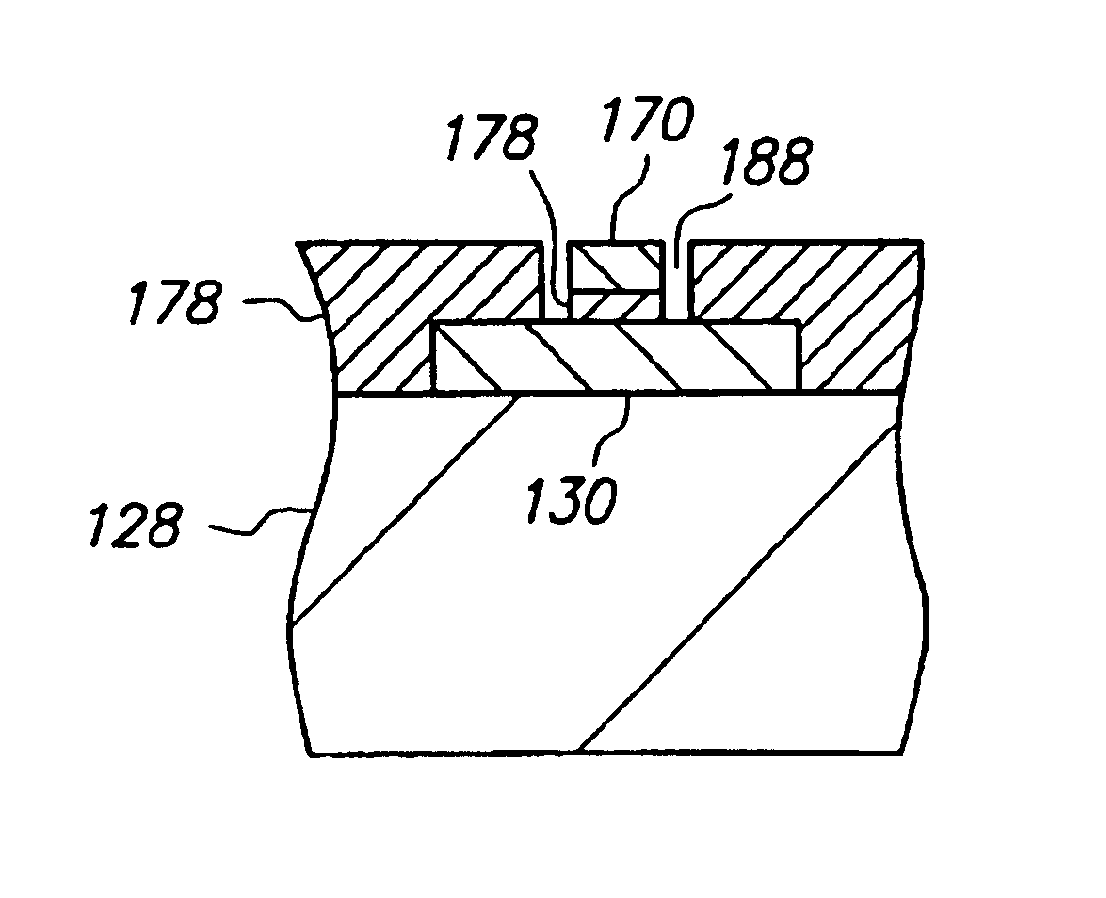

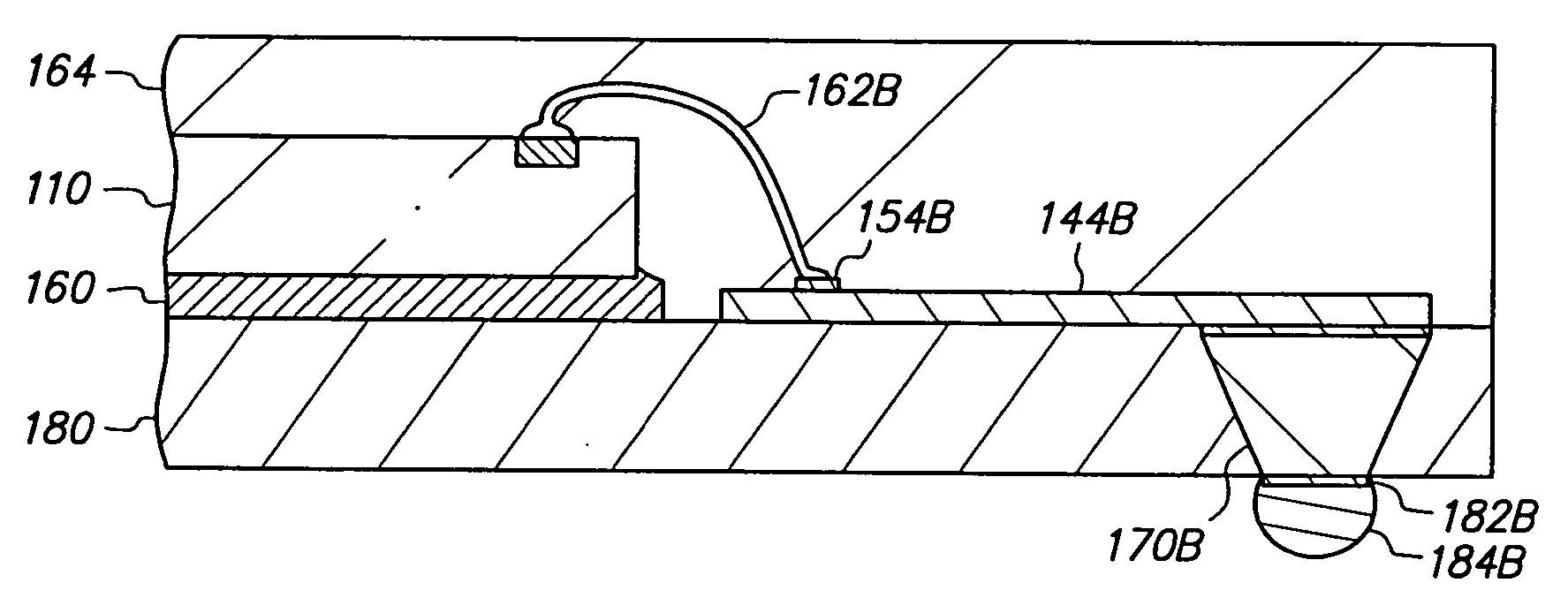

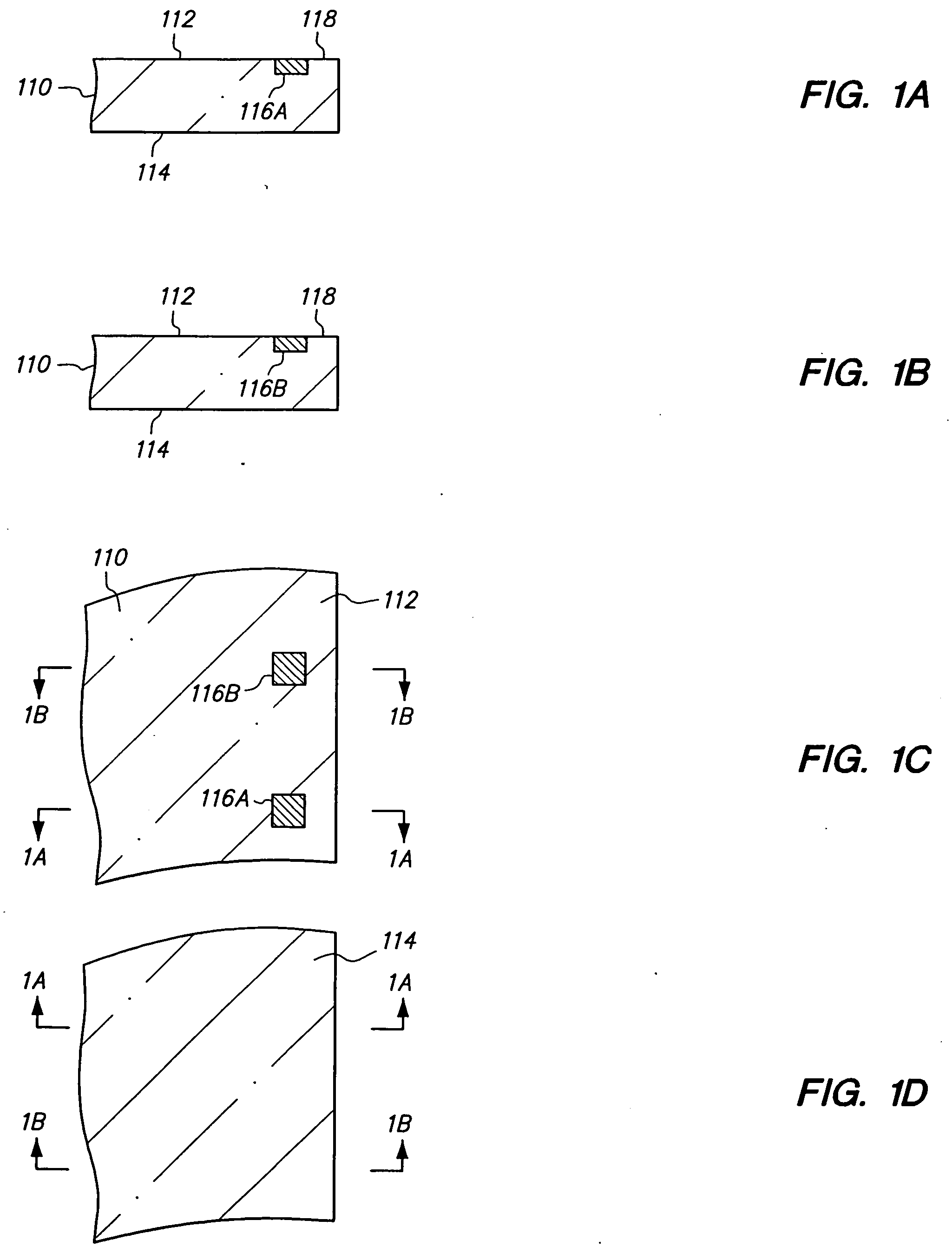

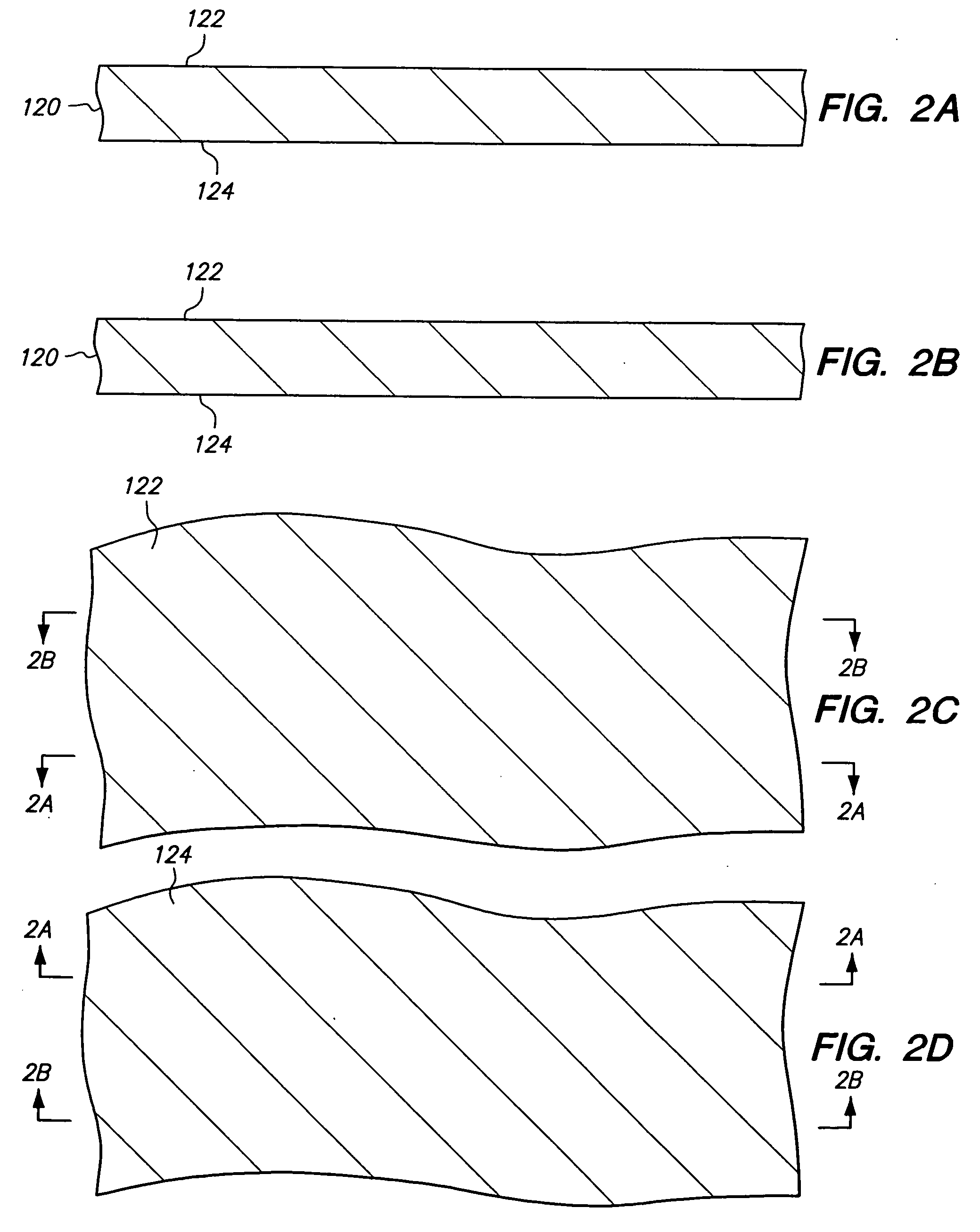

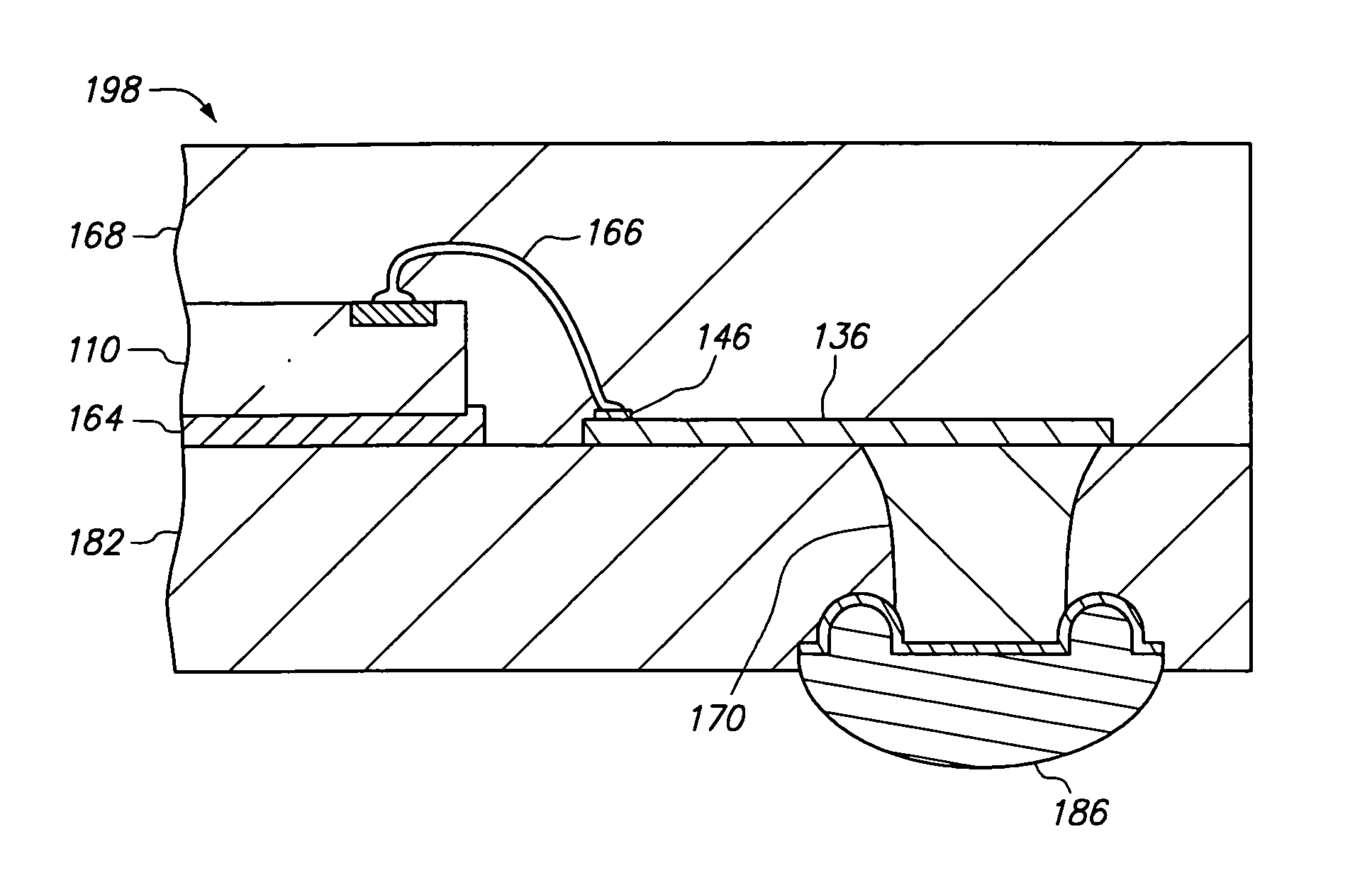

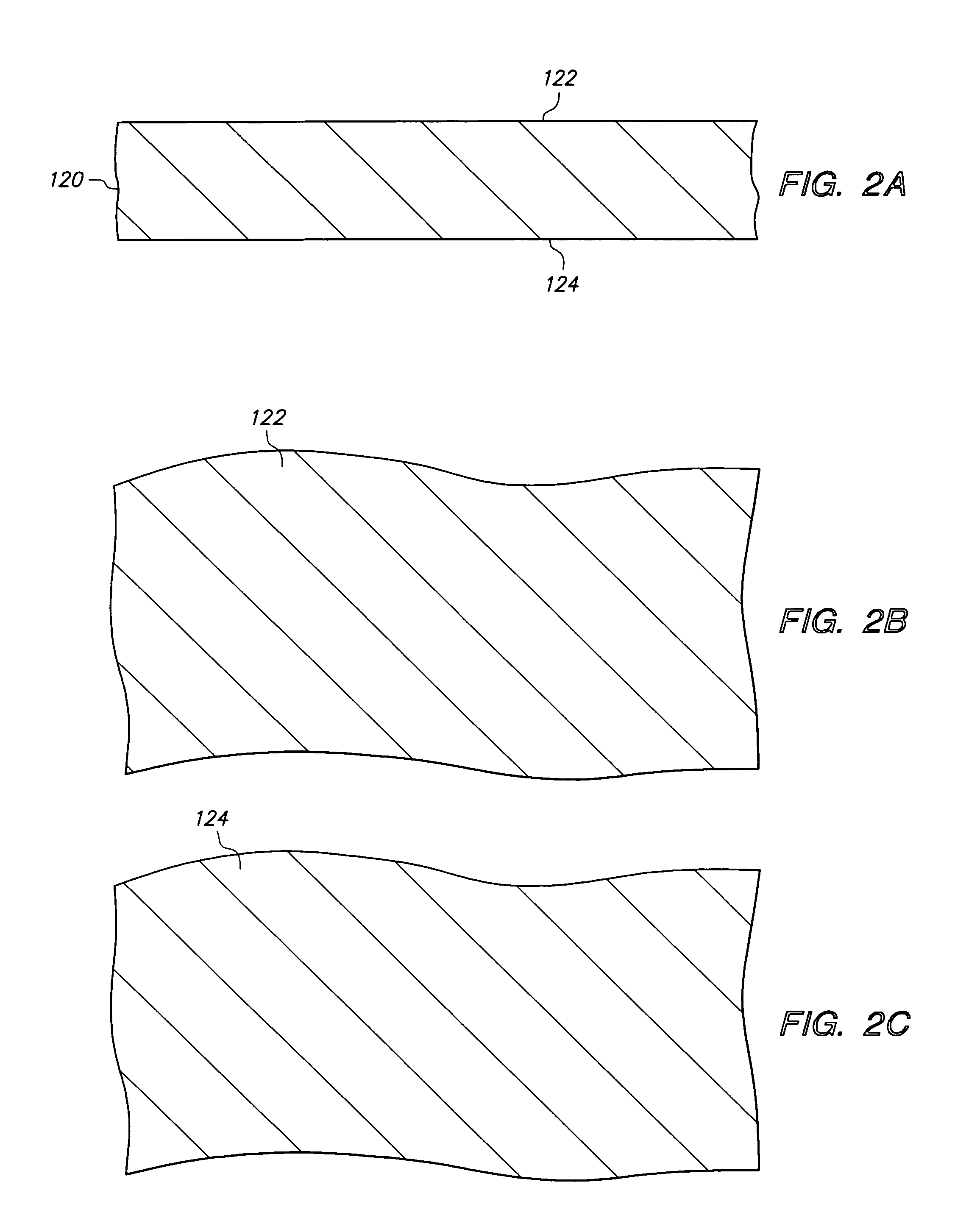

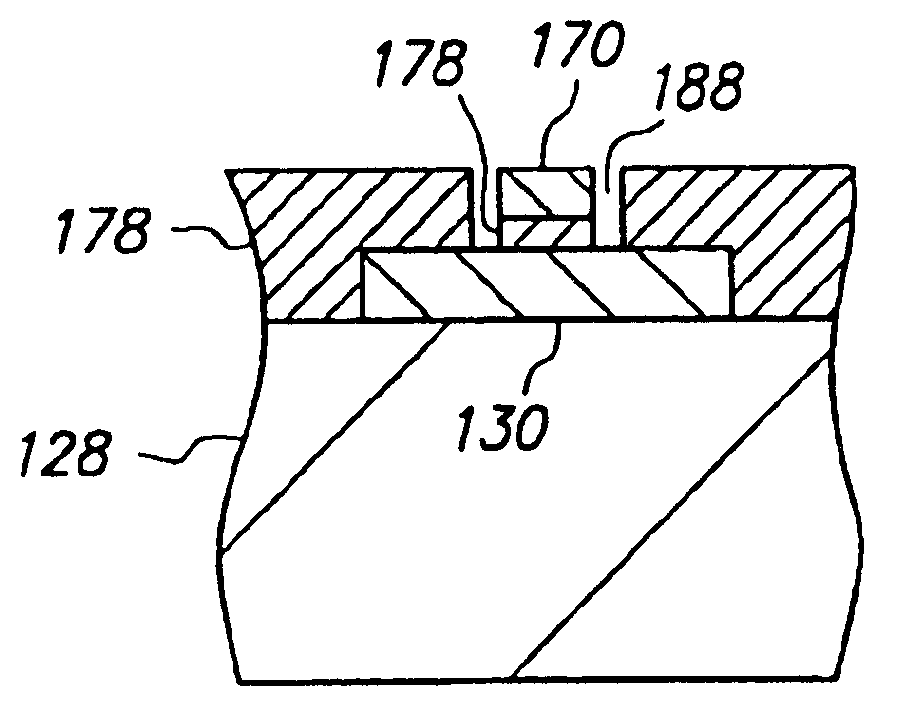

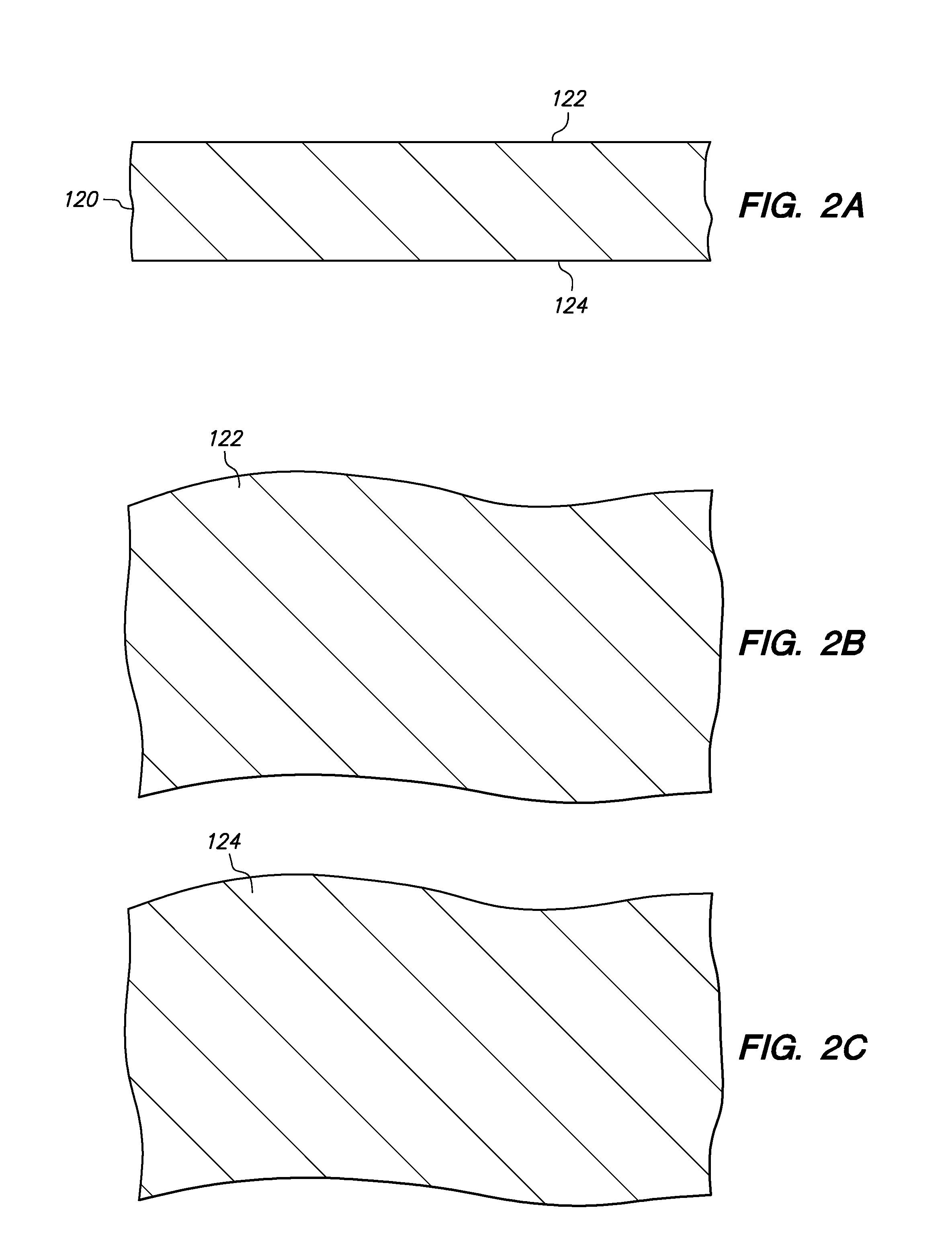

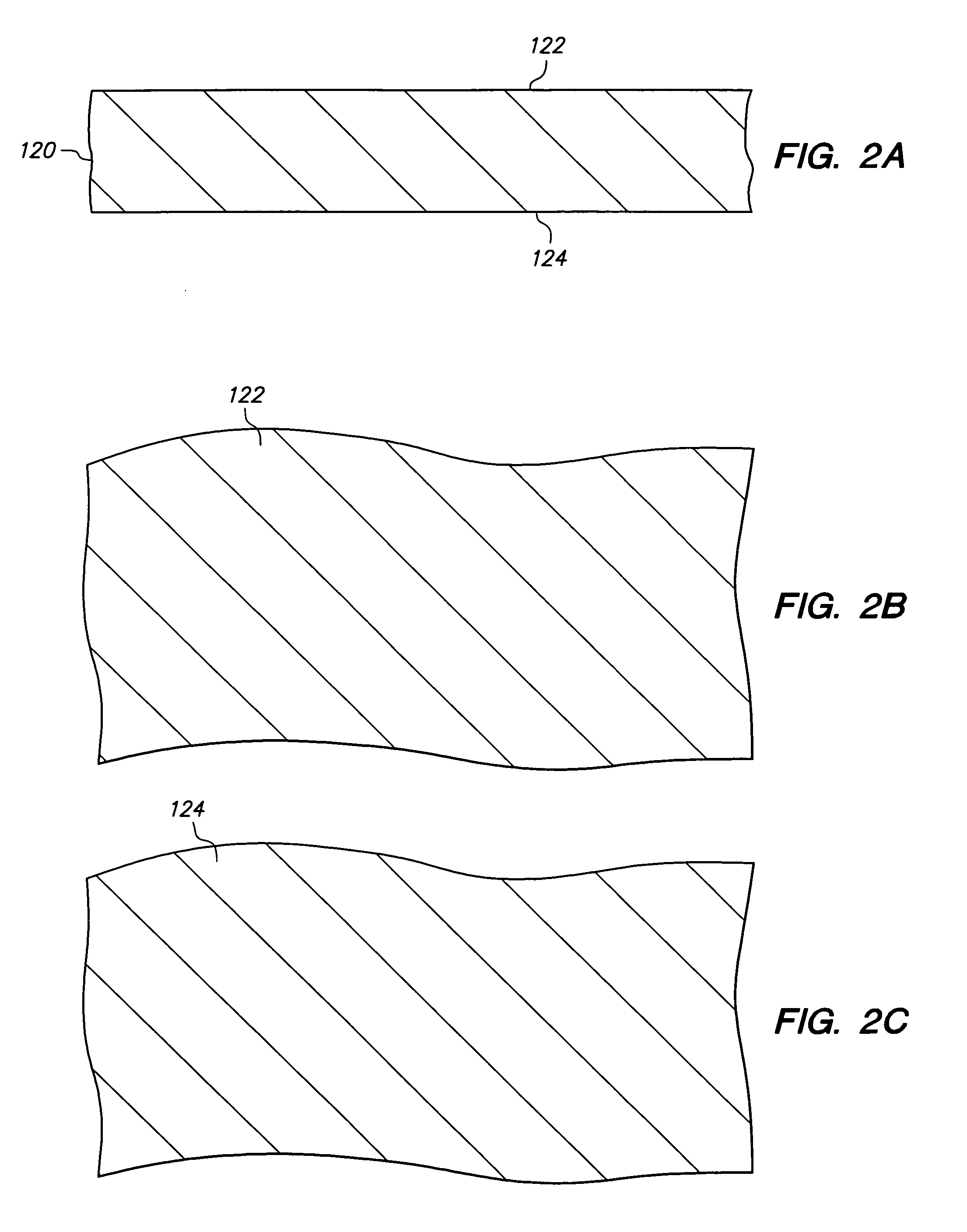

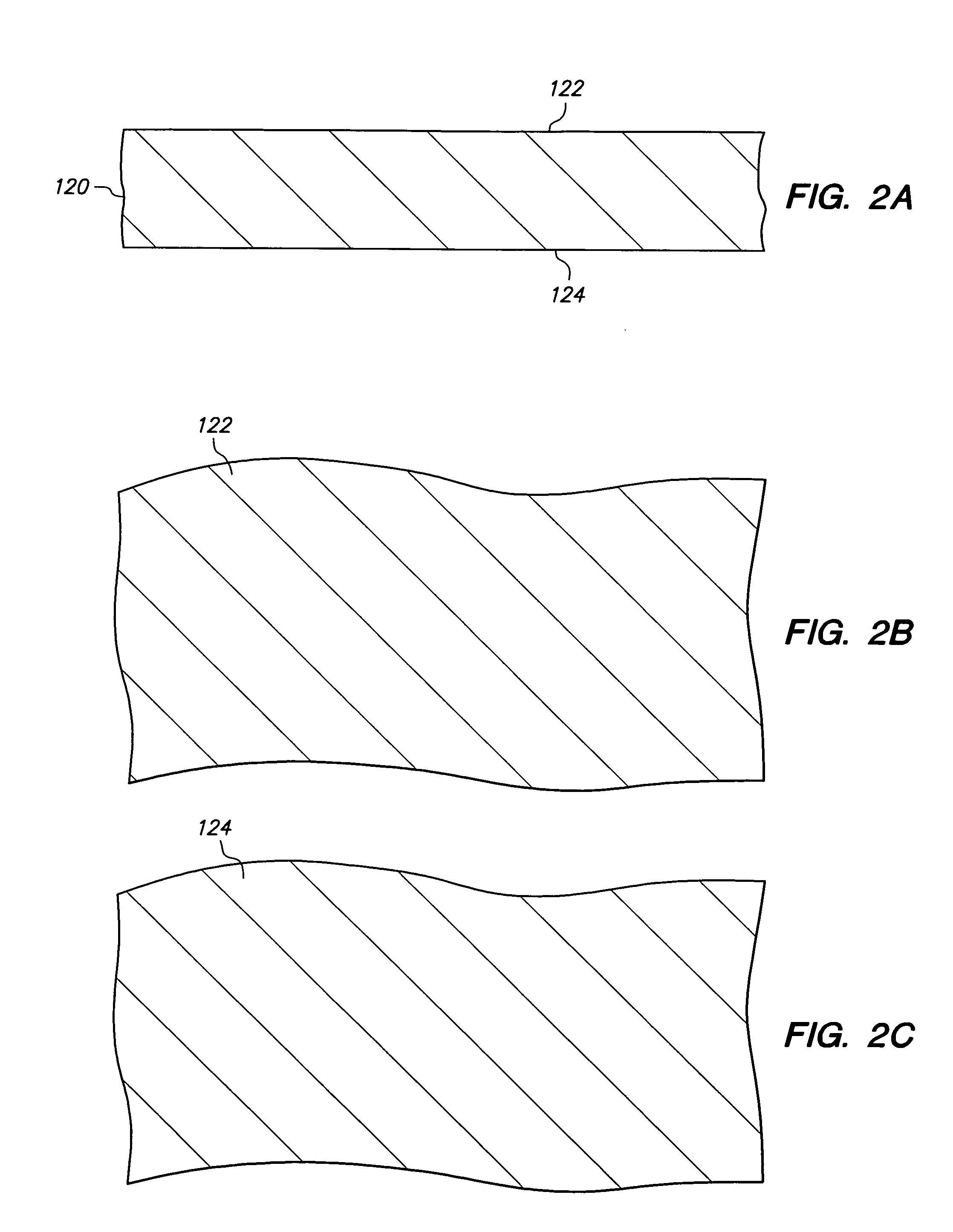

Semiconductor chip assembly with chip in substrate cavity

InactiveUS6876072B1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

A semiconductor chip assembly includes a semiconductor chip that includes first and second opposing major surfaces, wherein the first surface of the chip includes a conductive pad, a substrate that includes first and second opposing major surfaces, wherein the first and second surfaces of the substrate include a conductive terminal and a dielectric base, the conductive terminal extends through the dielectric base to the first and second surfaces of the substrate, a cavity extends from the first surface of the substrate into the substrate, the first surfaces of the chip and the substrate face in a first direction, the second surfaces of the chip and the substrate face in a second direction, and the chip extends into the cavity, a conductive trace in an electrically conductive path between the conductive terminal and the pad, and an adhesive disposed between the conductive trace and the chip, the conductive trace and the substrate, and the chip and the substrate.

Owner:BRIDGE SEMICON

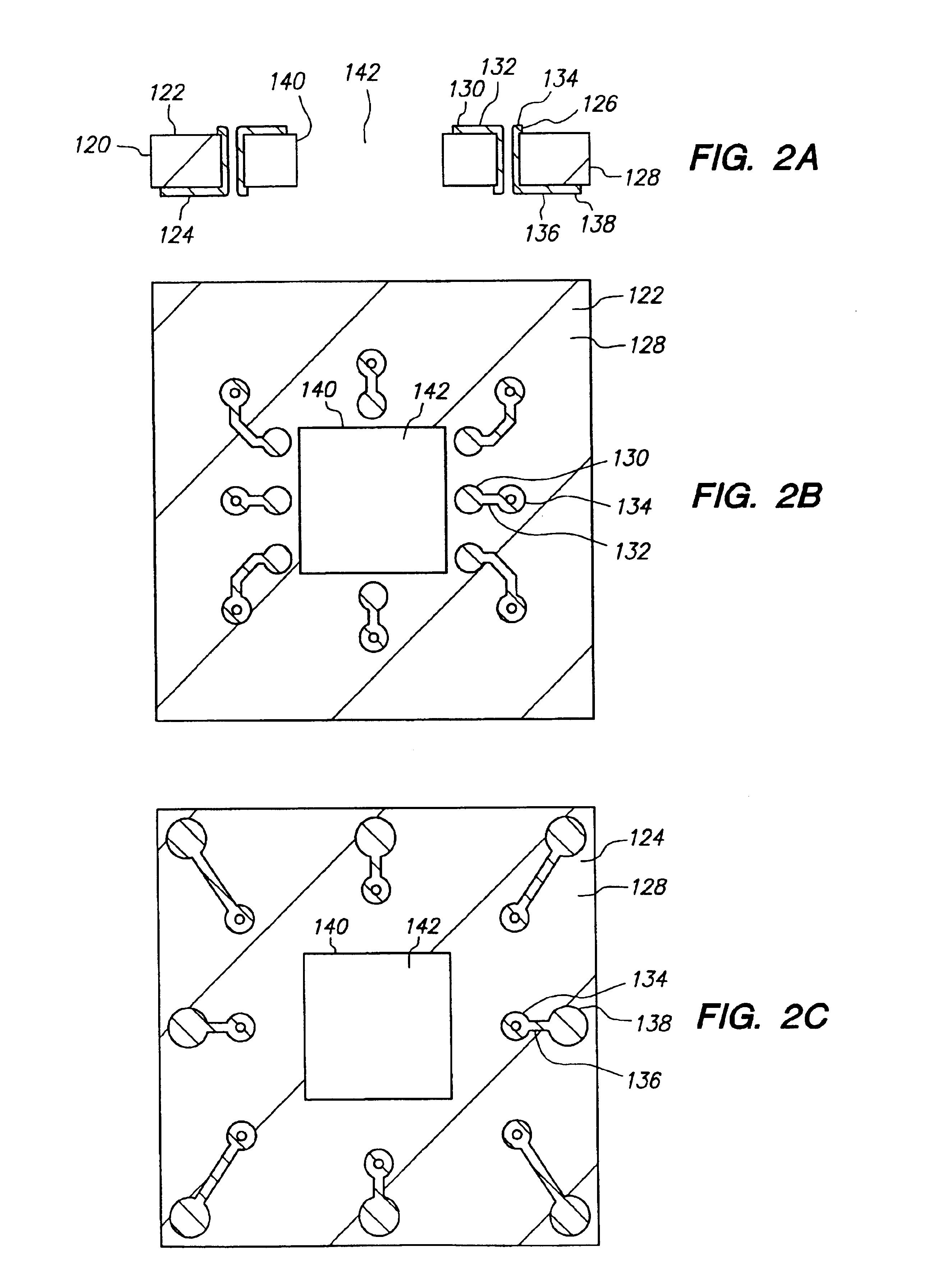

Semiconductor chip assembly with welded metal pillar of stacked metal balls

InactiveUS7446419B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line and a metal pillar, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The chip and the metal pillar are embedded in the encapsulant, the routing line extends laterally beyond the metal pillar towards the chip, and the metal pillar is welded to the routing line and includes stacked metal balls that are welded together.

Owner:BRIDGE SEMICON

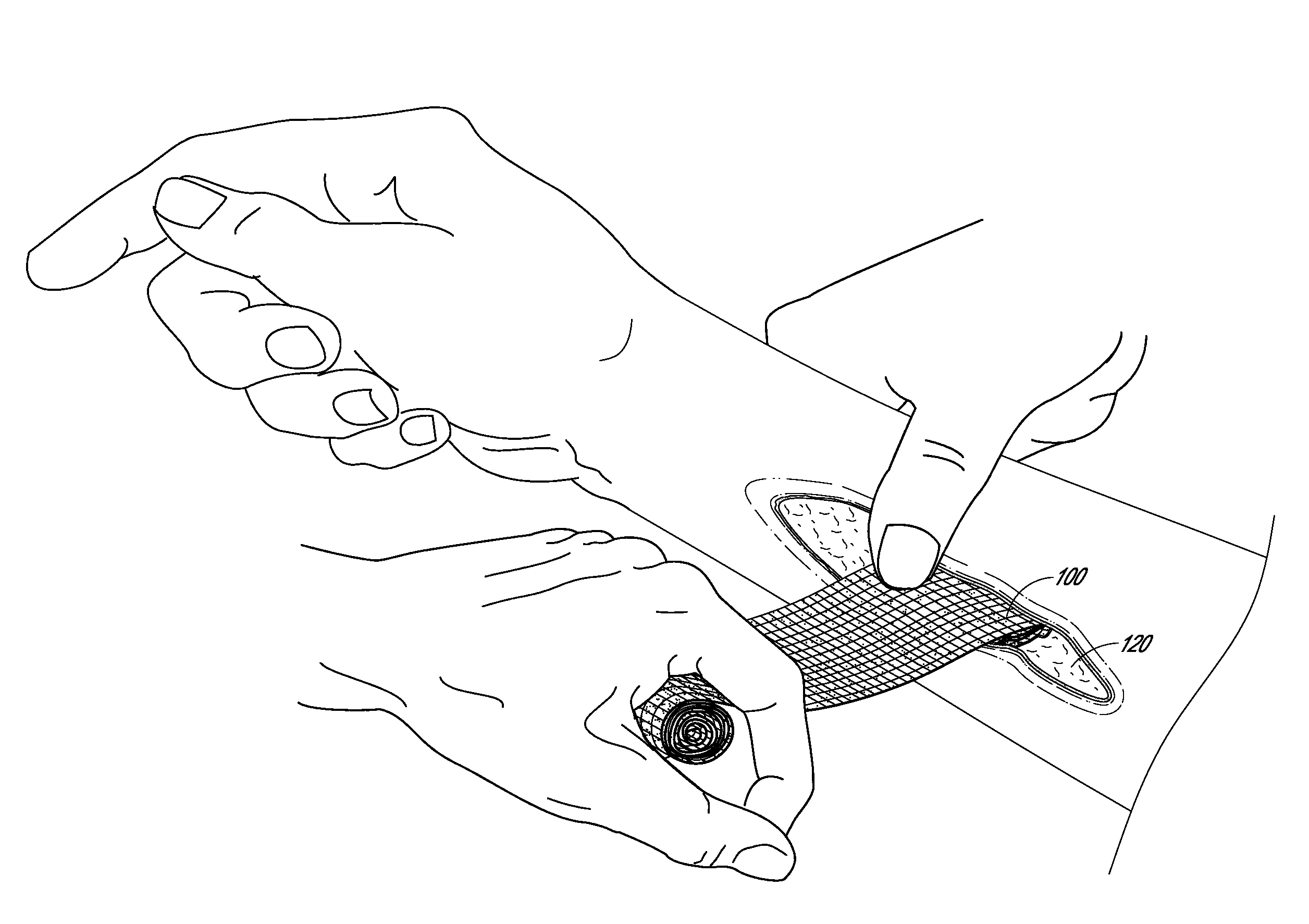

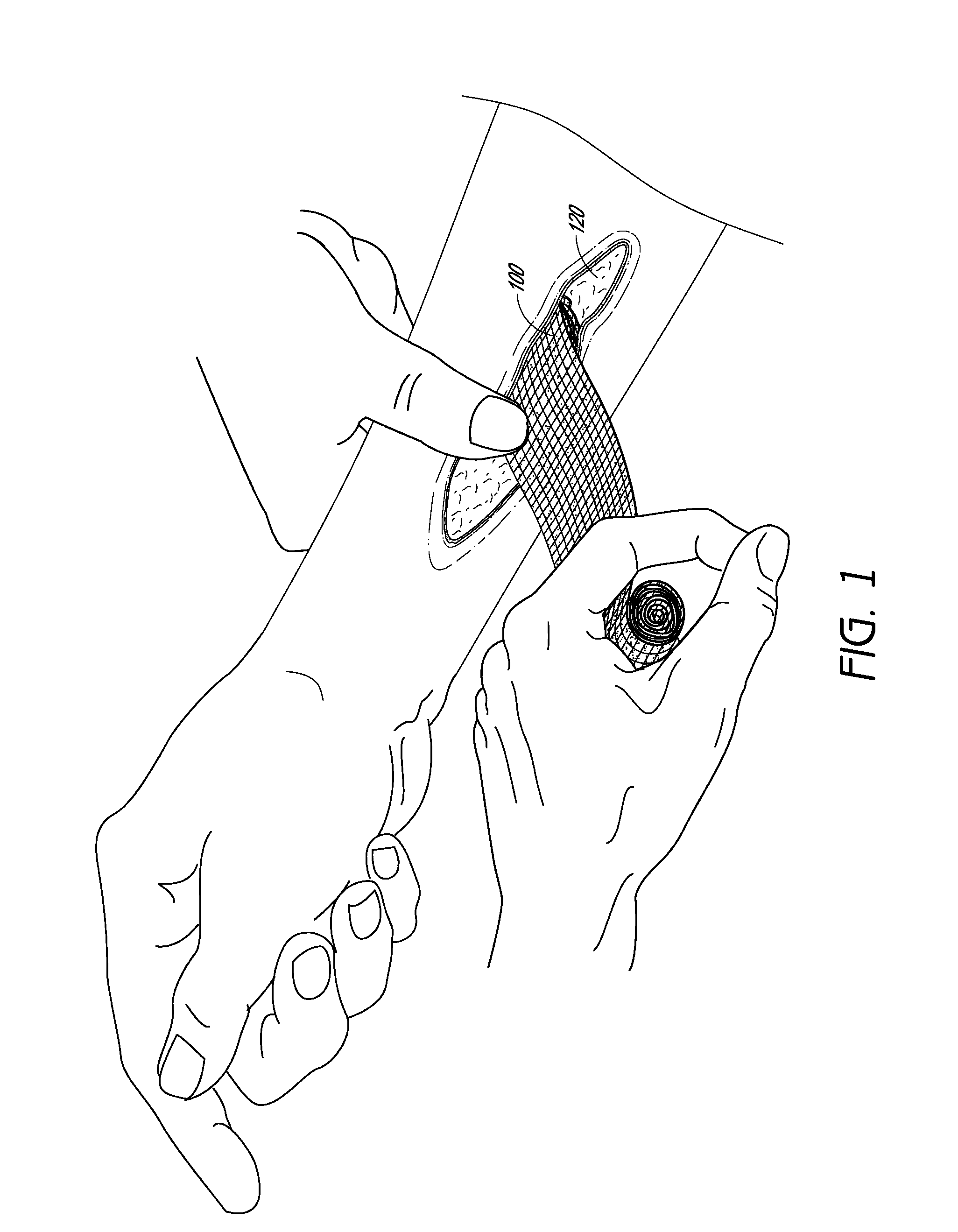

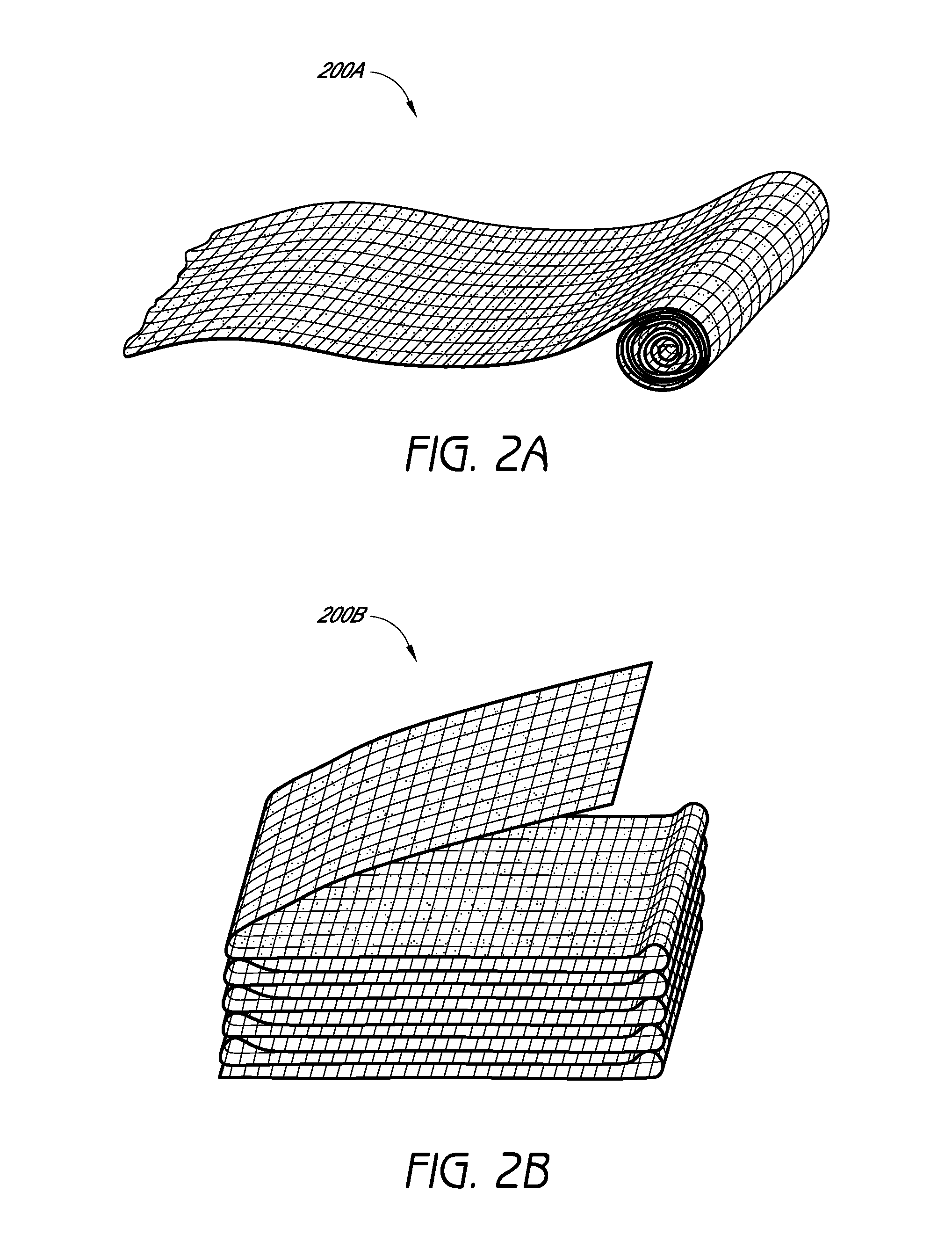

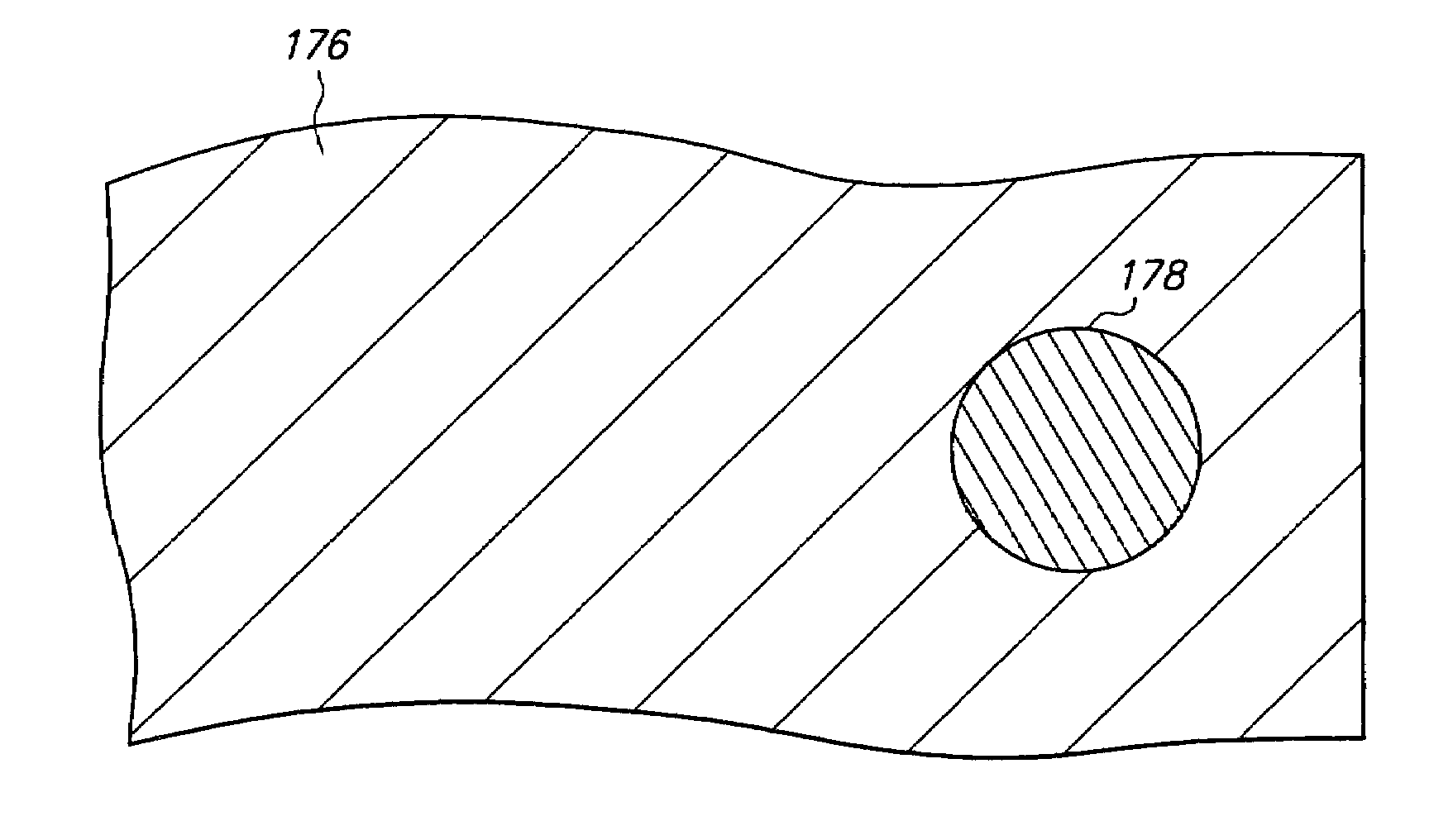

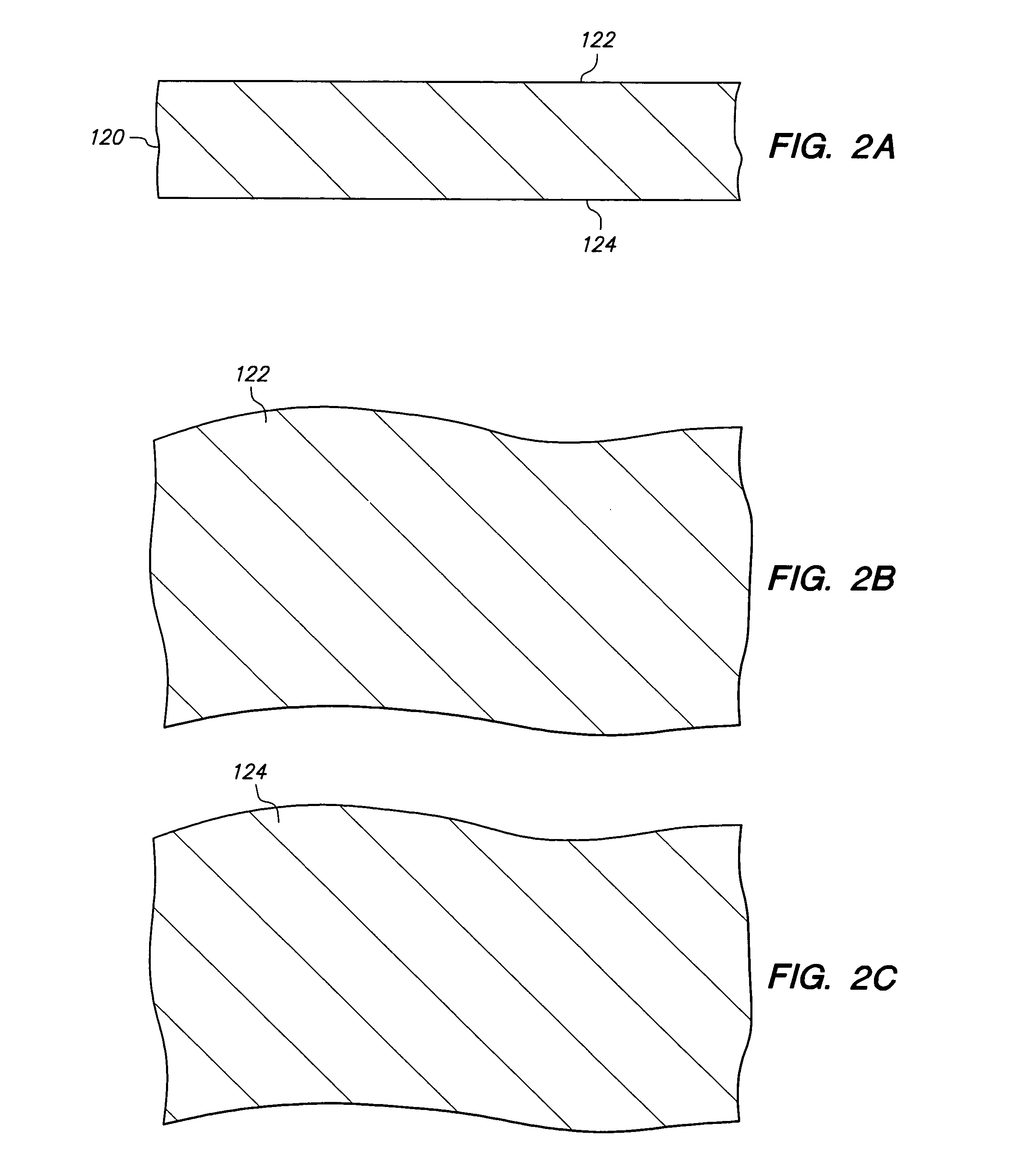

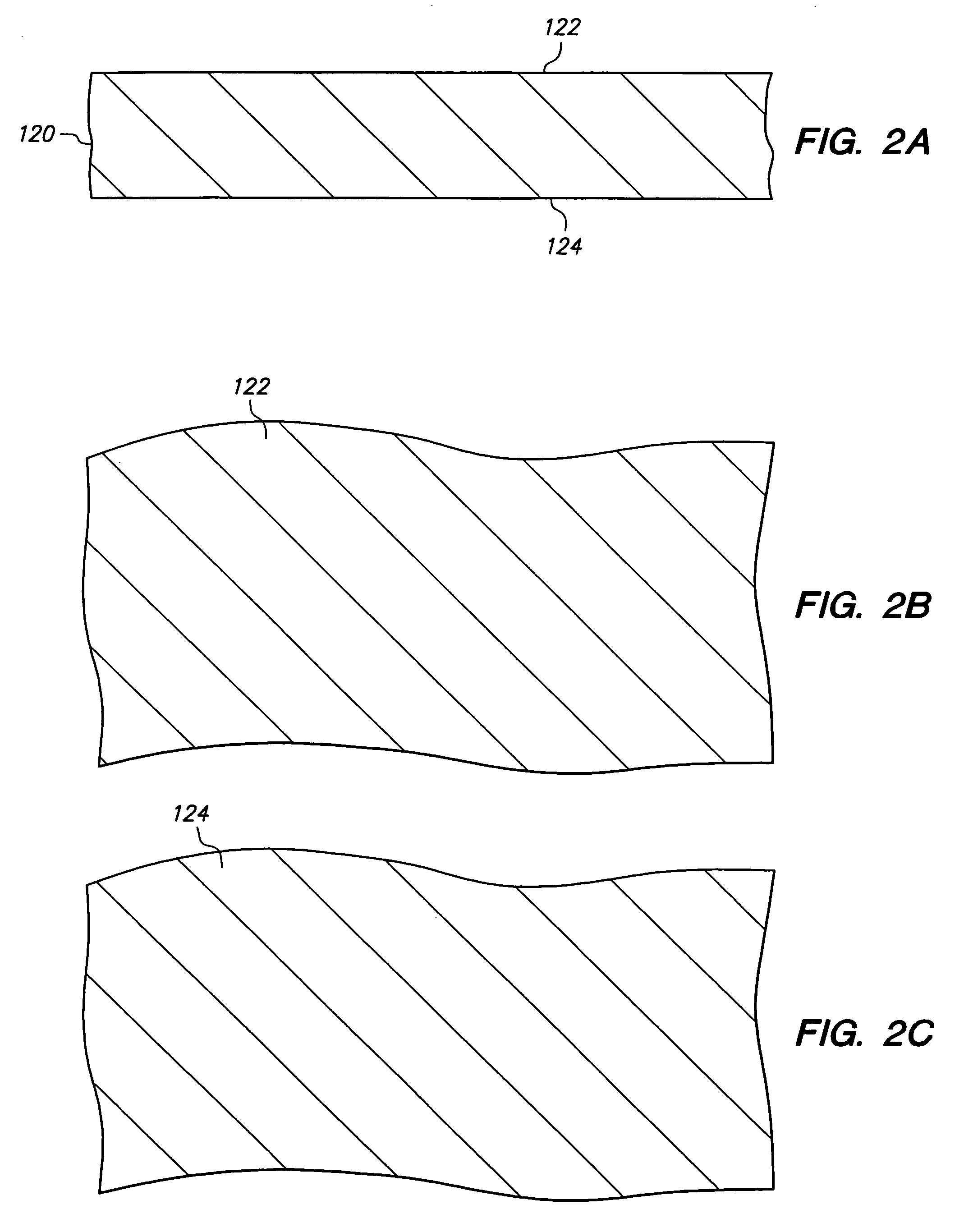

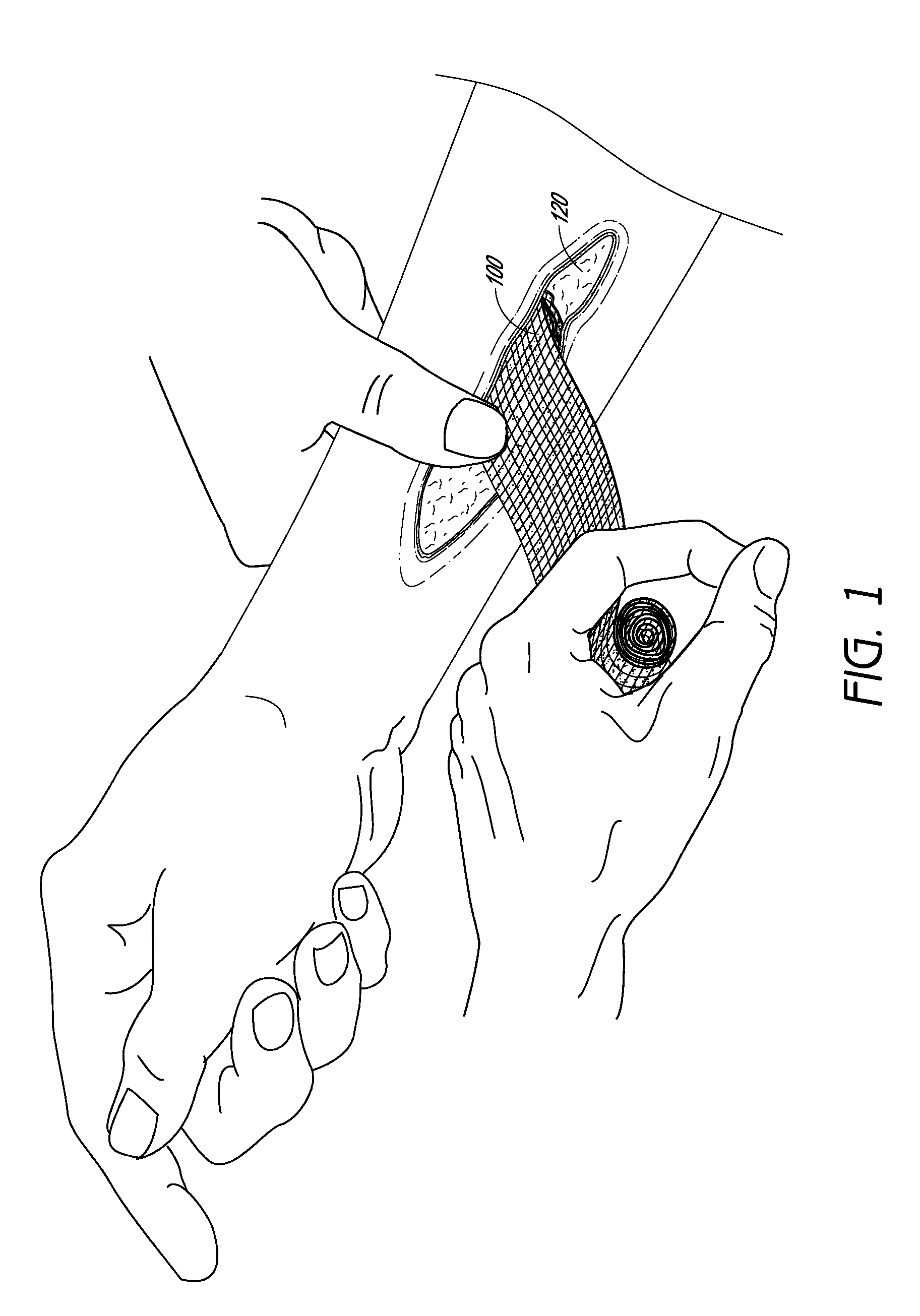

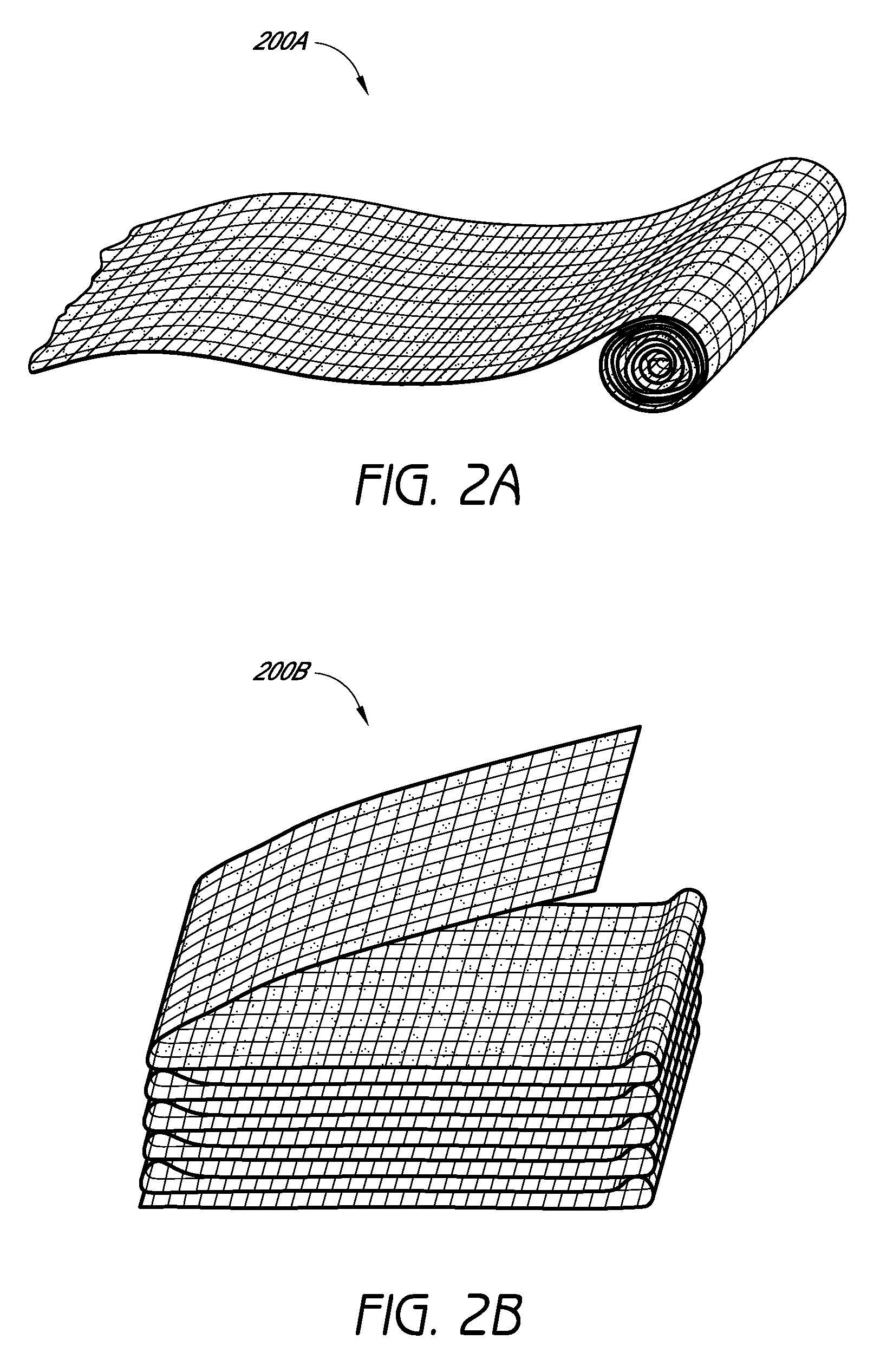

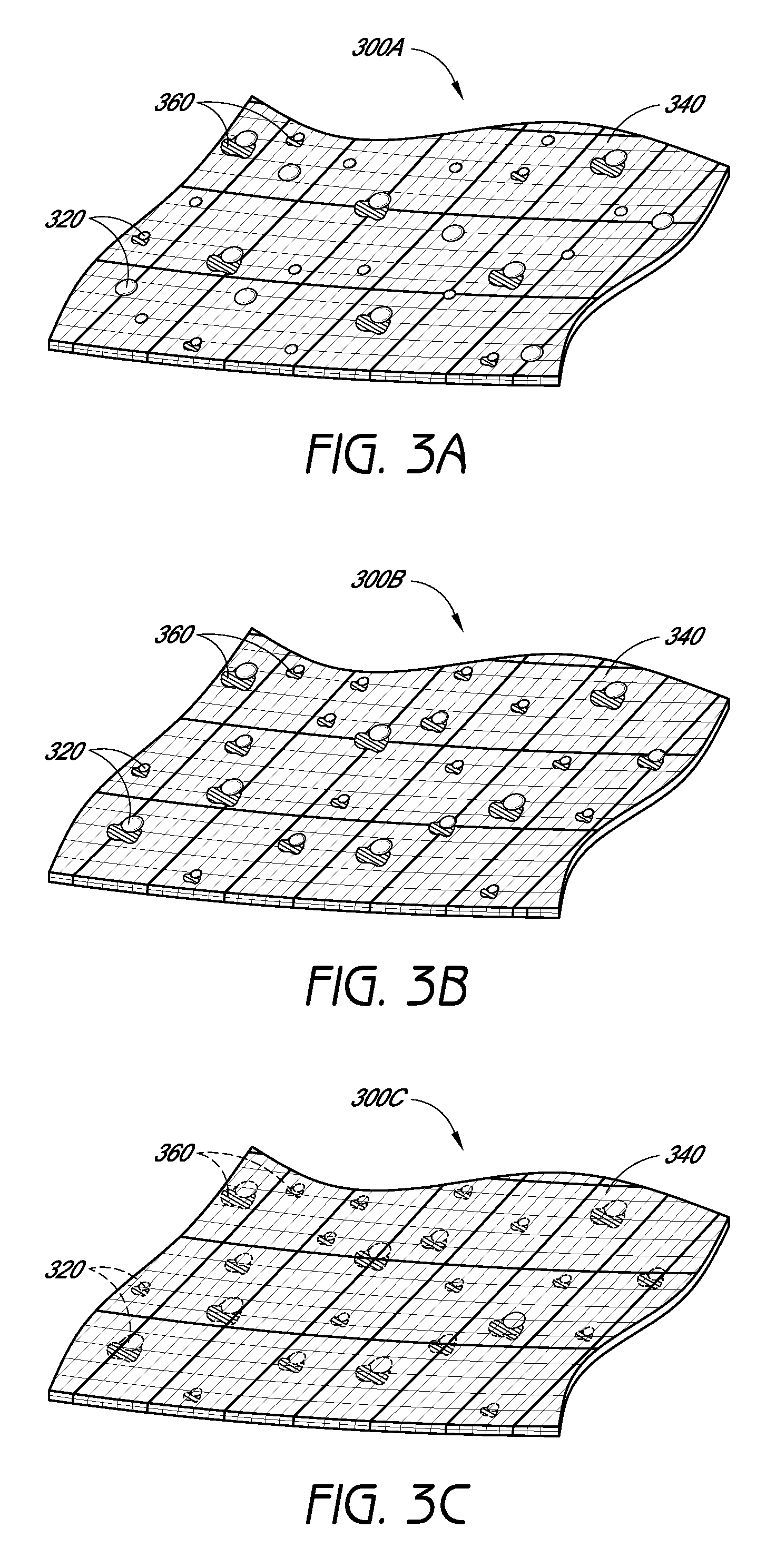

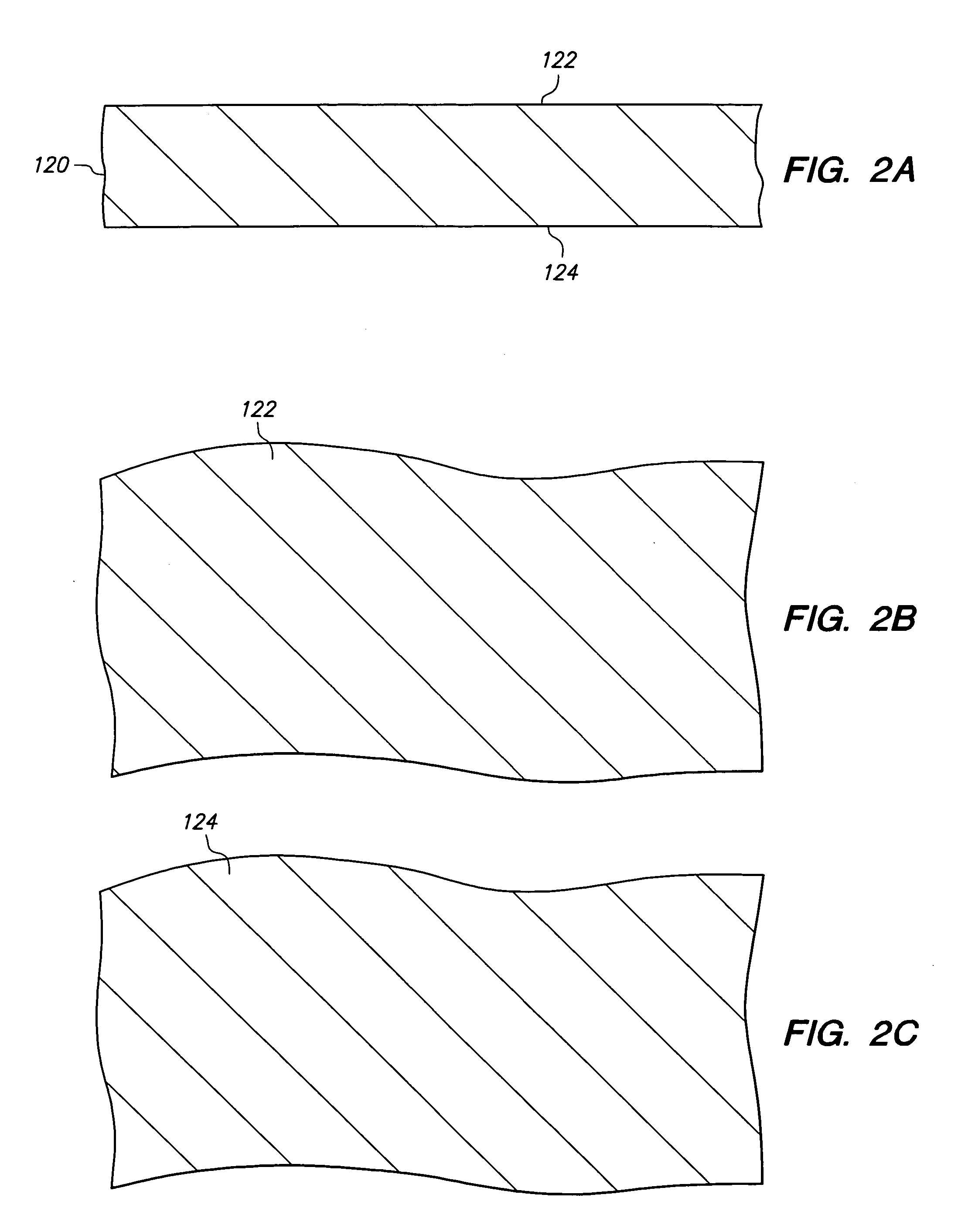

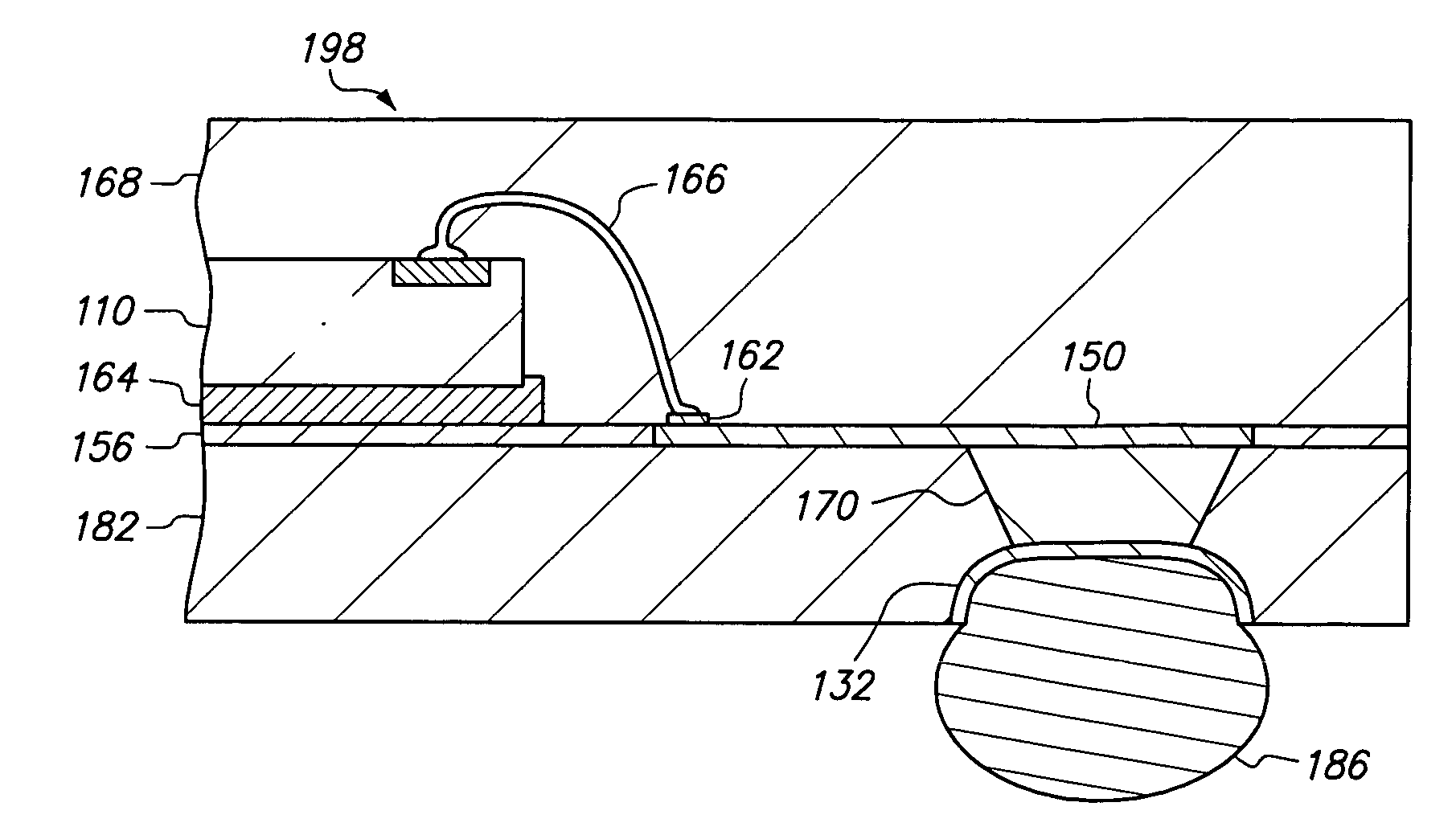

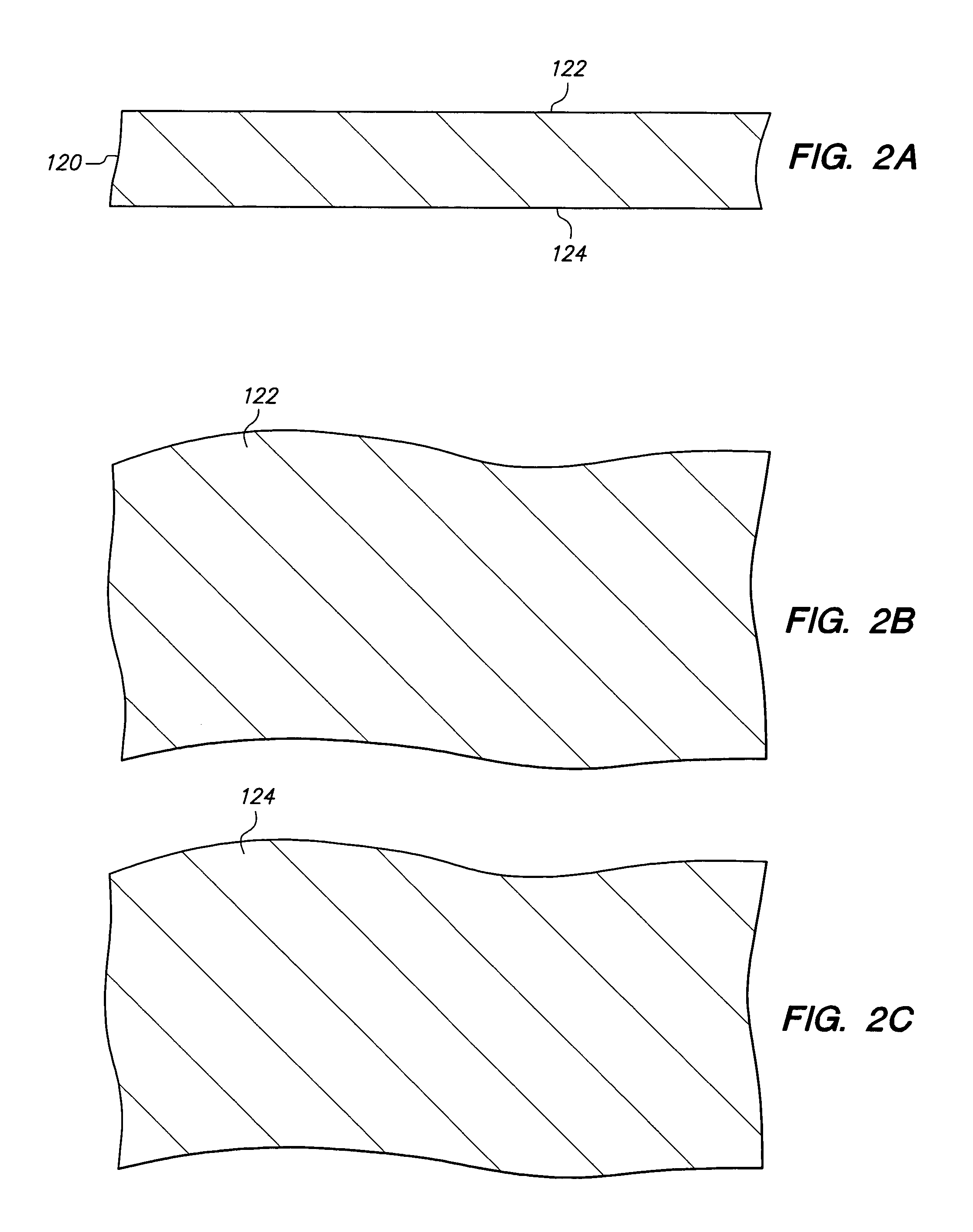

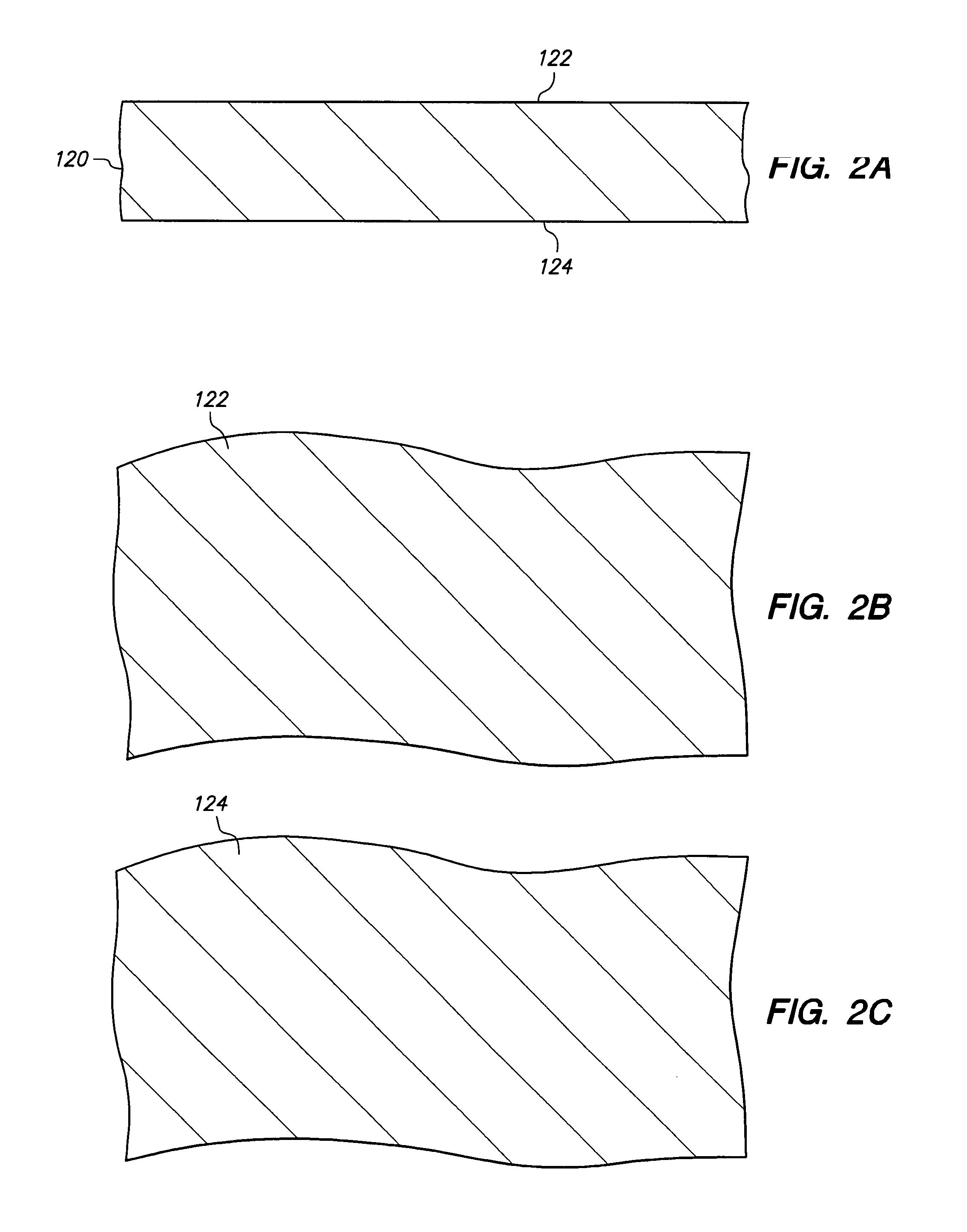

Hemostatic devices

ActiveUS20130344131A1Reduce the amount requiredConvenient and cost-effective for manufacturingBiocidePowder deliveryFiberSolubility

Hemostatic devices for promoting blood clotting can include a substrate (e.g., gauze, textile, sponge, sponge matrix, one or more fibers, etc.), a hemostatic material disposed thereon such as kaolin clay, and a binder material such as crosslinked calcium alginate with a high guluronate monomer molar percentage disposed on the substrate to substantially retain the hemostatic material material. When the device is used to treat a bleeding wound, at least a portion of the clay material comes into contact with blood to accelerate clotting. Moreover, when exposed to blood, the binder has low solubility and retains a majority of the clay material on the gauze. A bandage that can be applied to a bleeding wound to promote blood clotting includes a flexible substrate and a gauze substrate mounted thereon.

Owner:TELEFLEX LIFE SCI LTD

Semiconductor chip assembly with carved bumped terminal

InactiveUS7132741B1Enhancing mechanical supportImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line, a bumped terminal and a metal filler, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The routing line is contiguous with and integral with the bumped terminal and extends laterally beyond the bumped terminal and the metal filler, and the metal filler contacts the bumped terminal in a cavity that extends through the bumped terminal.

Owner:BRIDGE SEMICON

Method of making a semiconductor chip assembly with an embedded metal particle

InactiveUS7015128B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes mechanically attaching a semiconductor chip that includes a conductive pad to a routing line, mechanically attaching and electrically connecting a metal particle to the routing line, wherein the routing line extends laterally beyond the metal particle towards the chip and the chip and the metal particle extend vertically beyond the routing line in the same direction, forming an encapsulant after attaching the chip and the metal particle to the routing line wherein the chip and the metal particle are embedded in the encapsulant, and forming a connection joint that electrically connects the routing line and the pad.

Owner:BRIDGE SEMICON

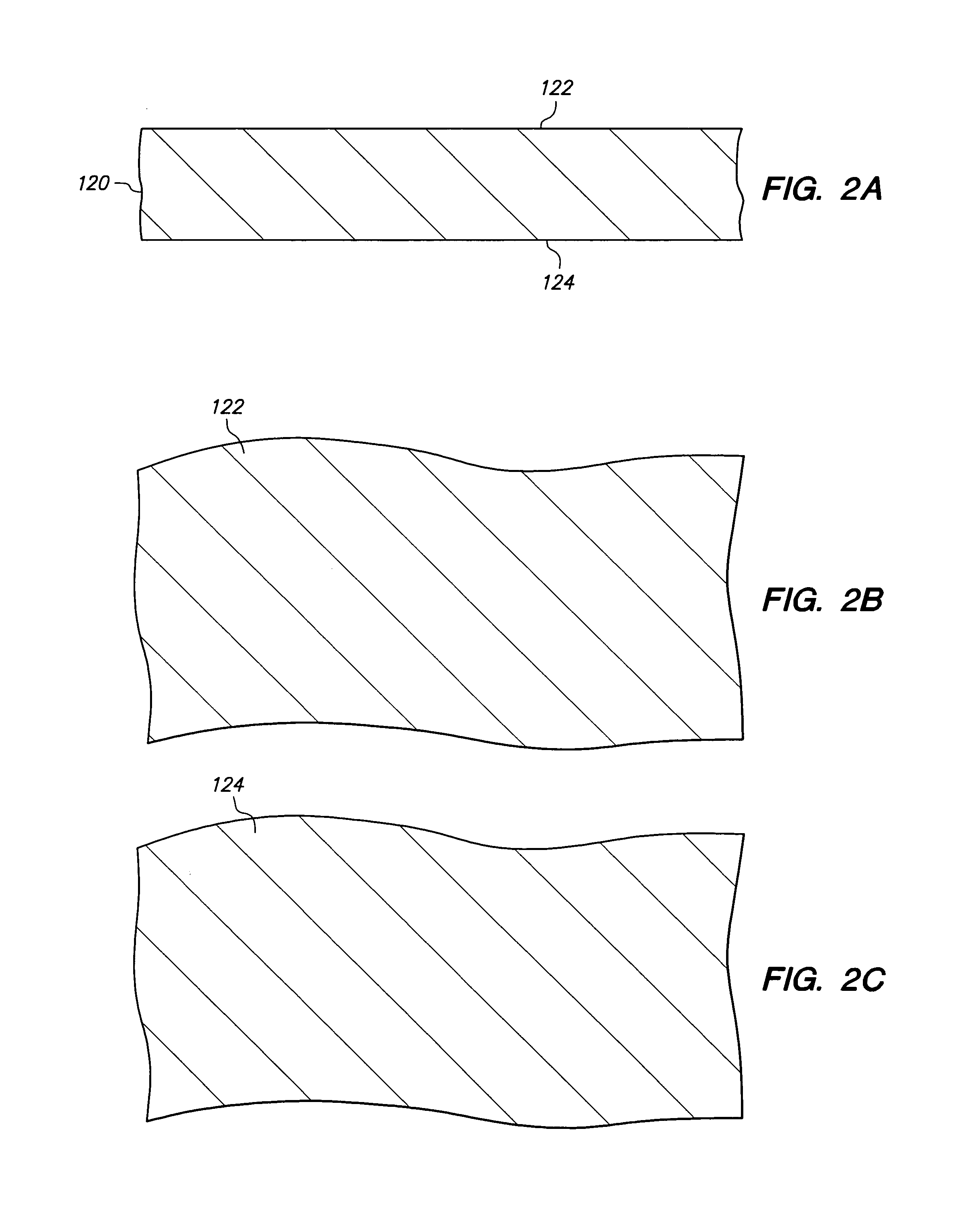

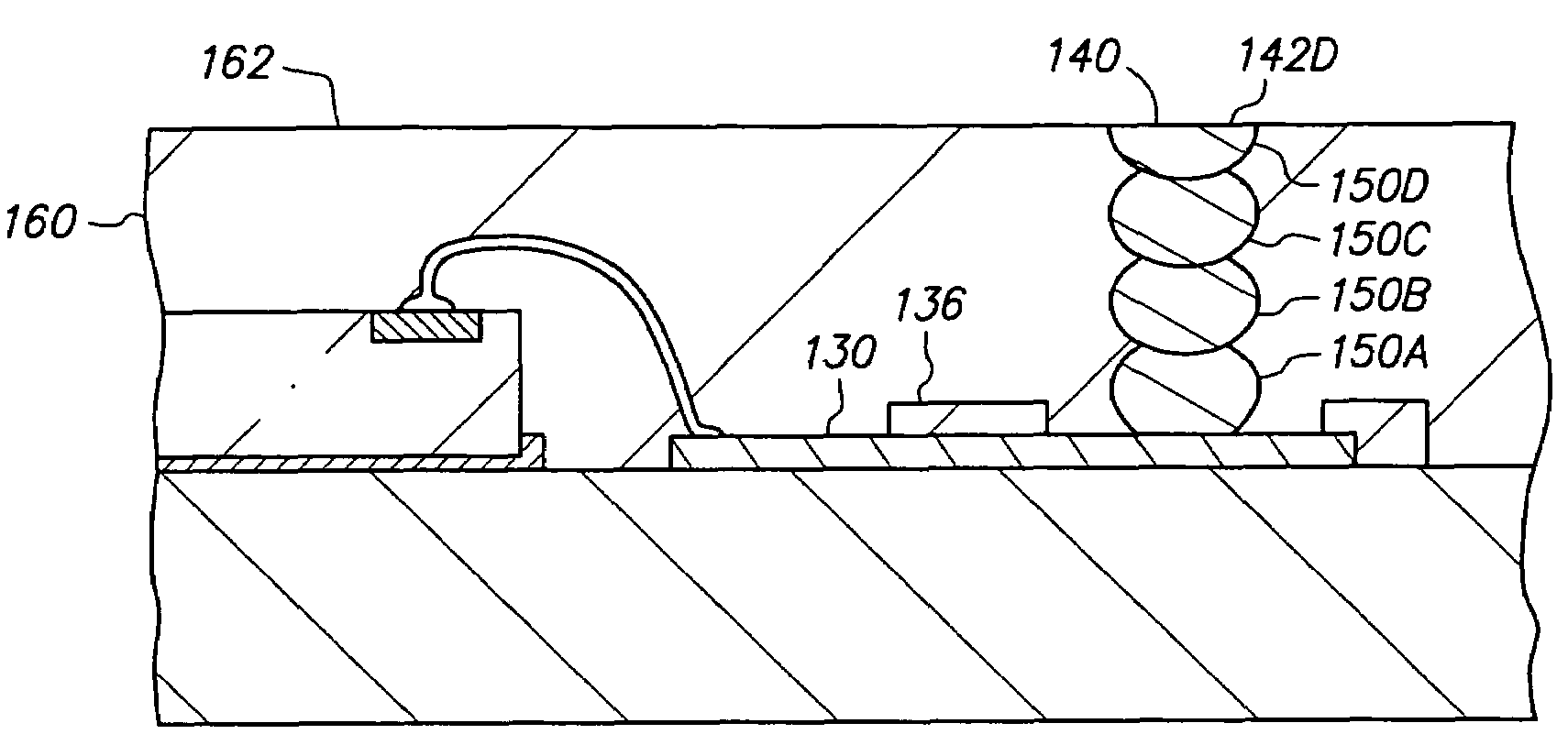

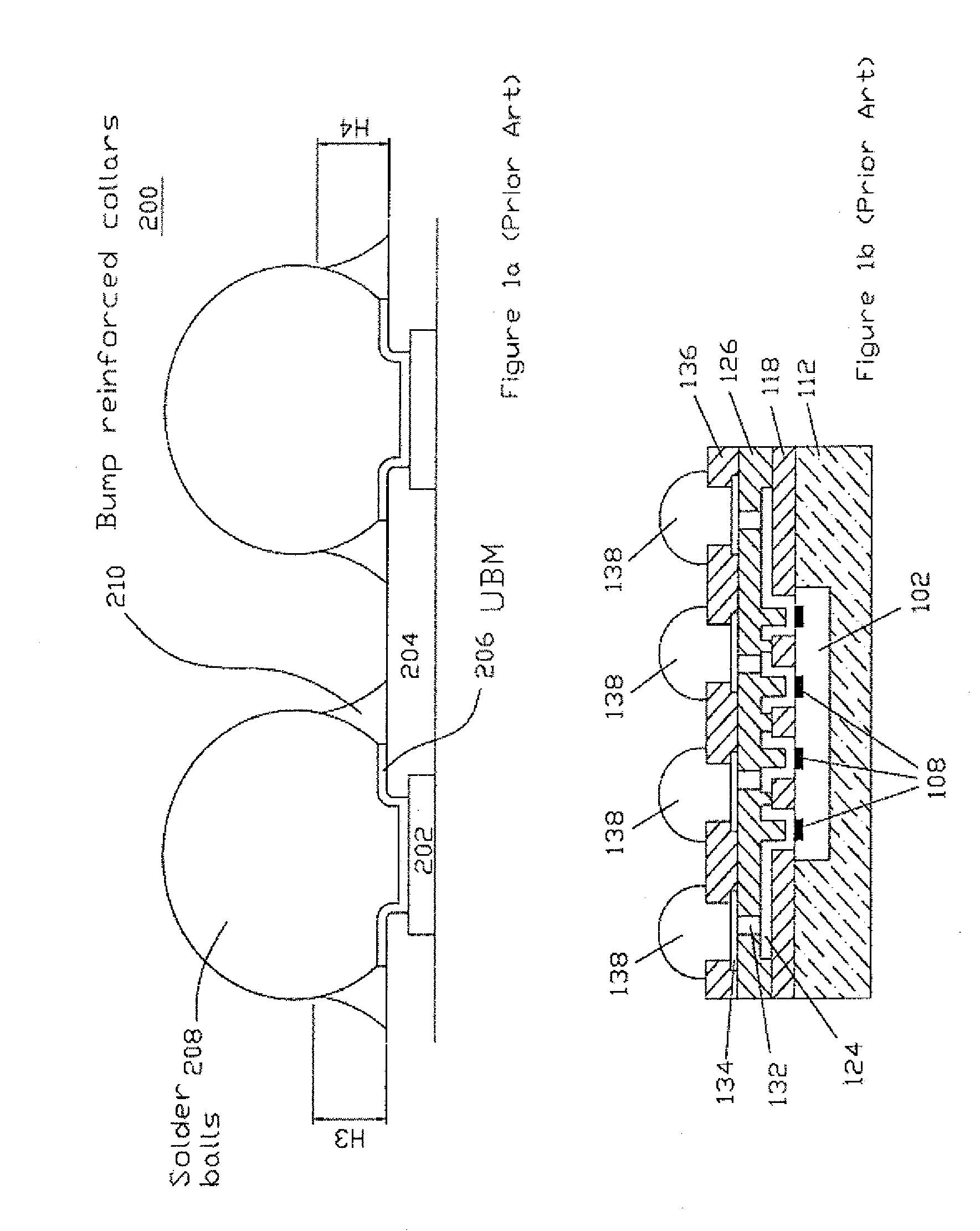

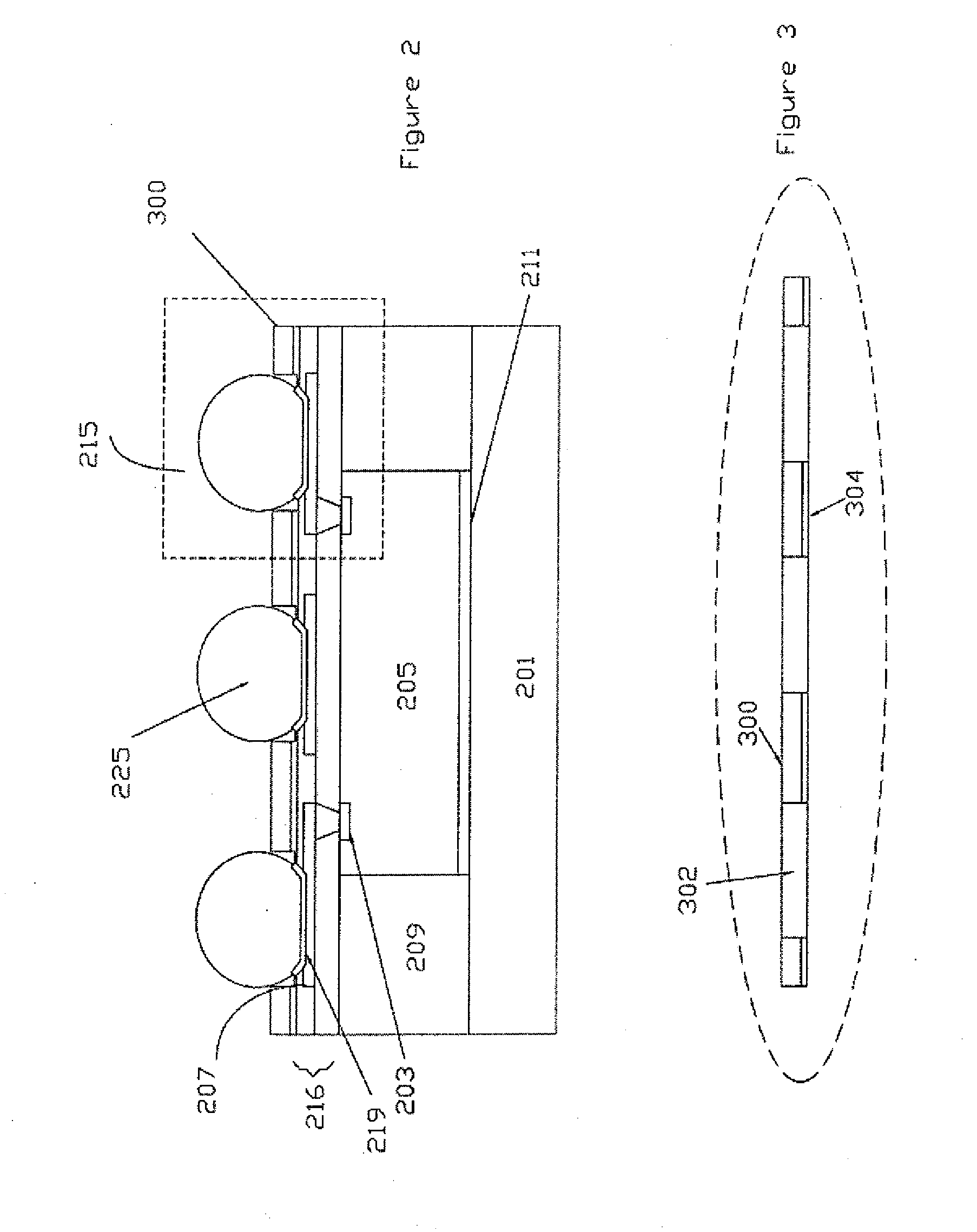

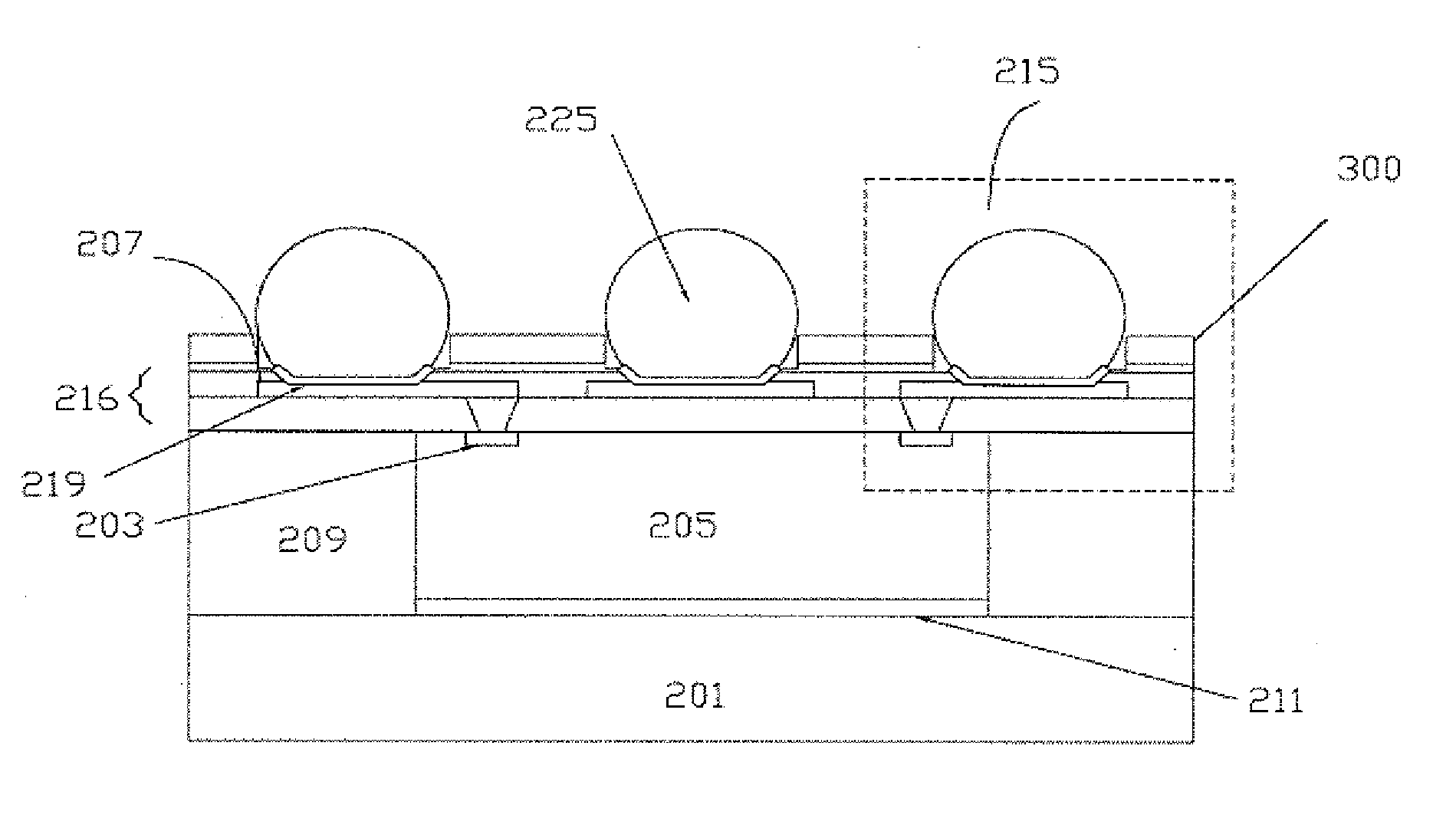

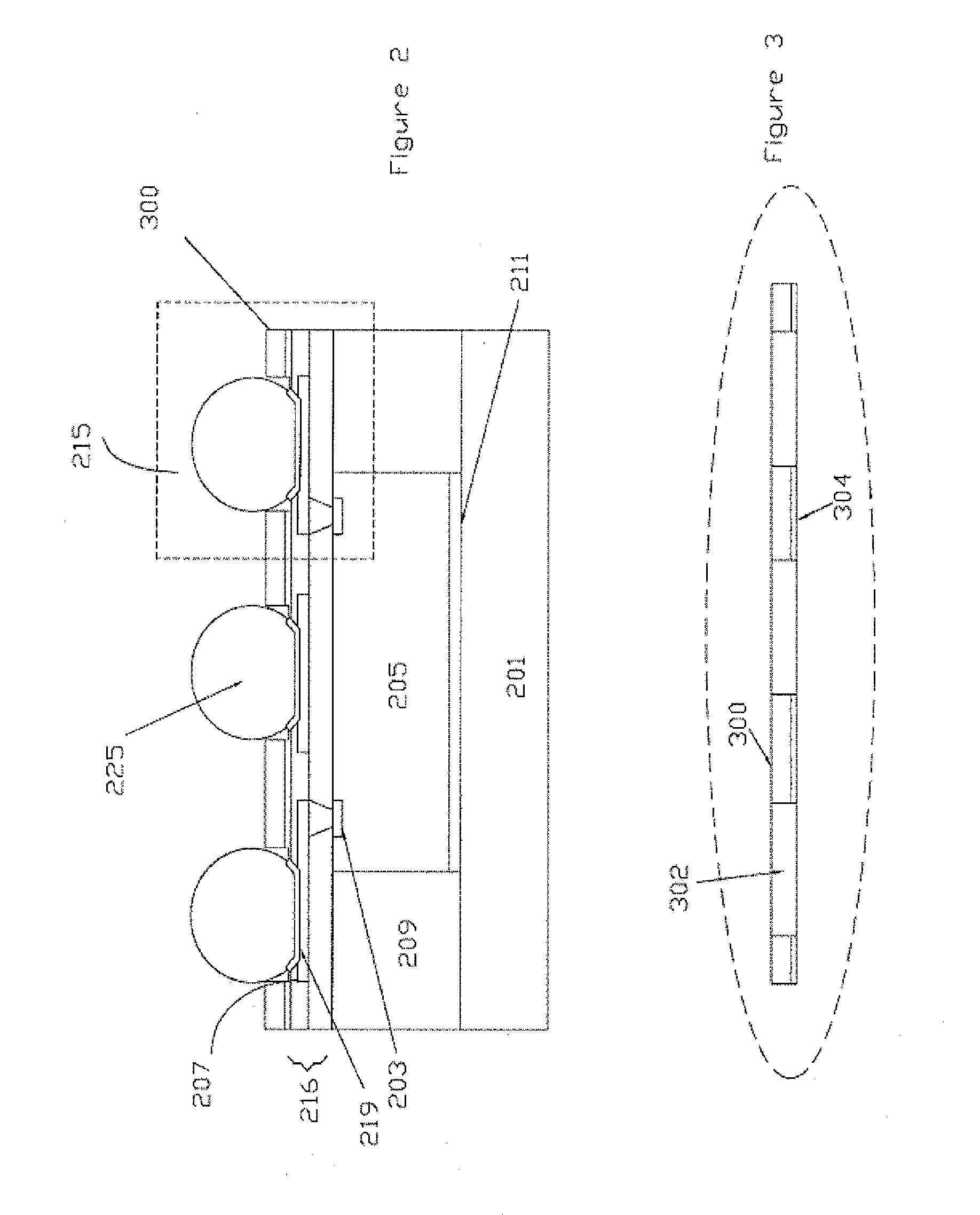

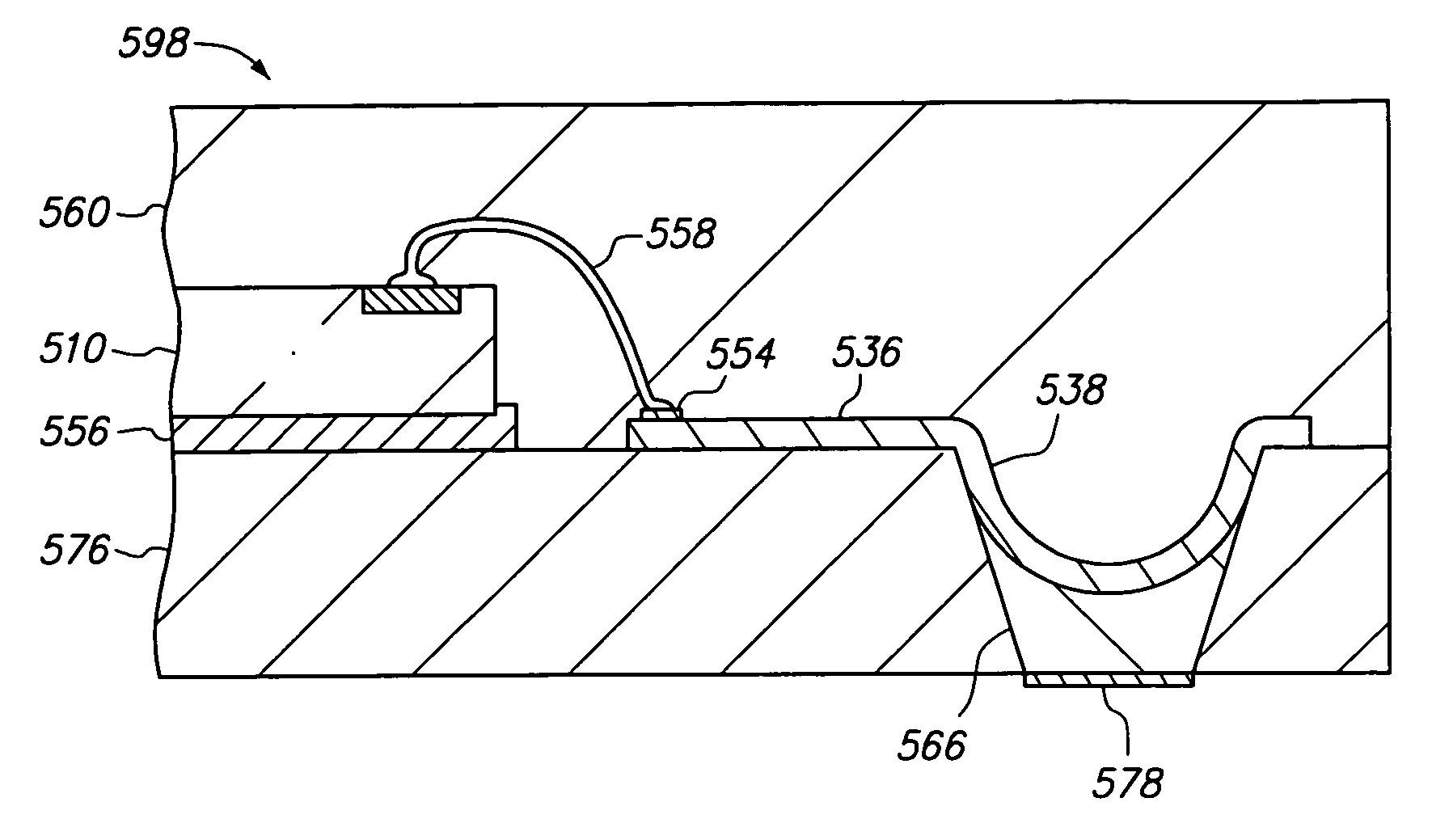

Inter-connecting structure for semiconductor package and method of the same

InactiveUS20090096098A1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

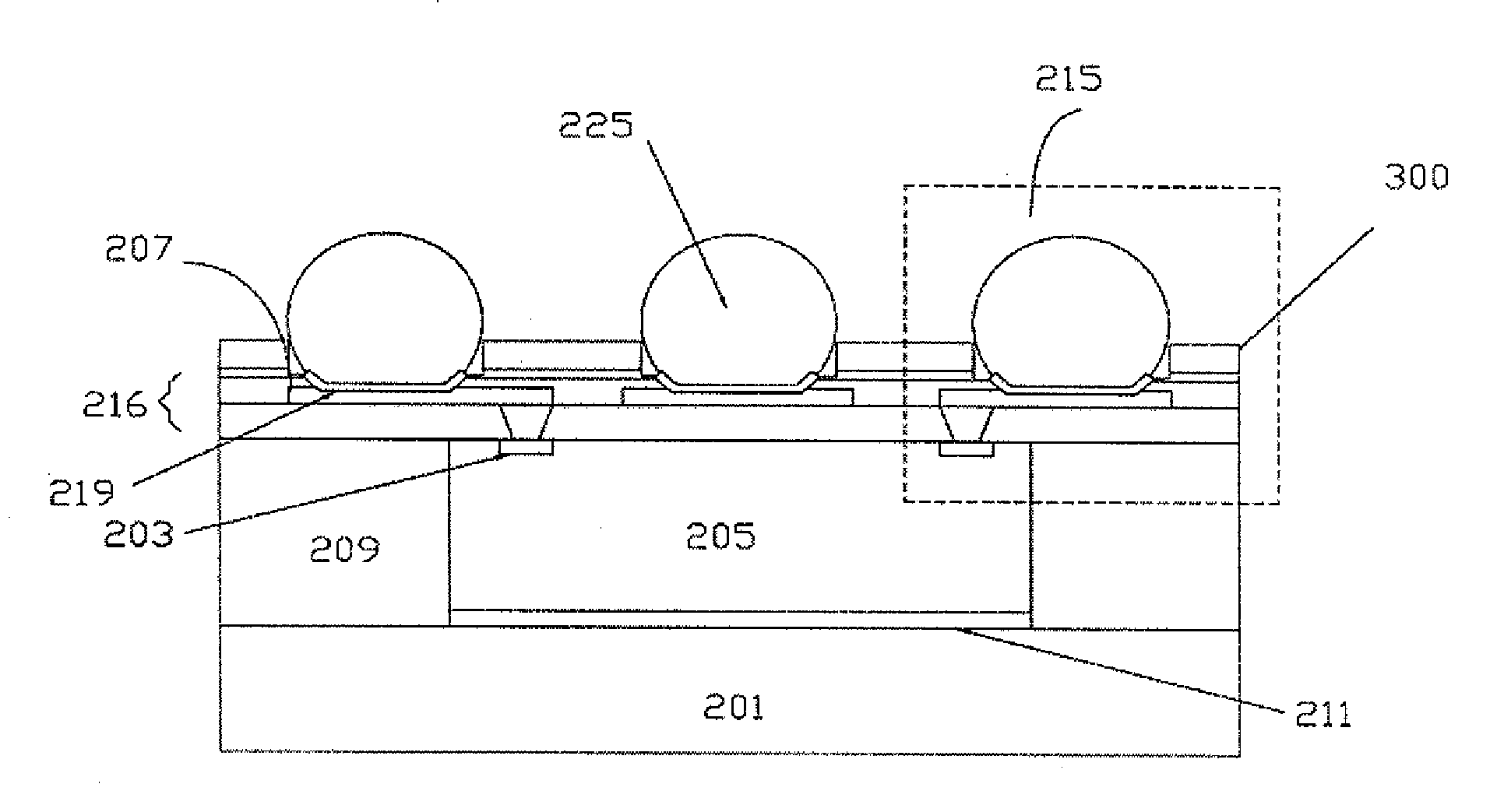

The interconnecting structure for a semiconductor die assembly comprises a build-up layers having RDL formed therein formed over a die having die pads formed thereon, wherein the RDL is coupled to the die pads; an isolation base having ball openings attached over the build-up layer to expose ball pads within the build-up layers; and conductive balls placed into the ball openings of the isolation base and attached on the ball pads within the build-up layers.

Owner:ADVANCED CHIP ENG TECH

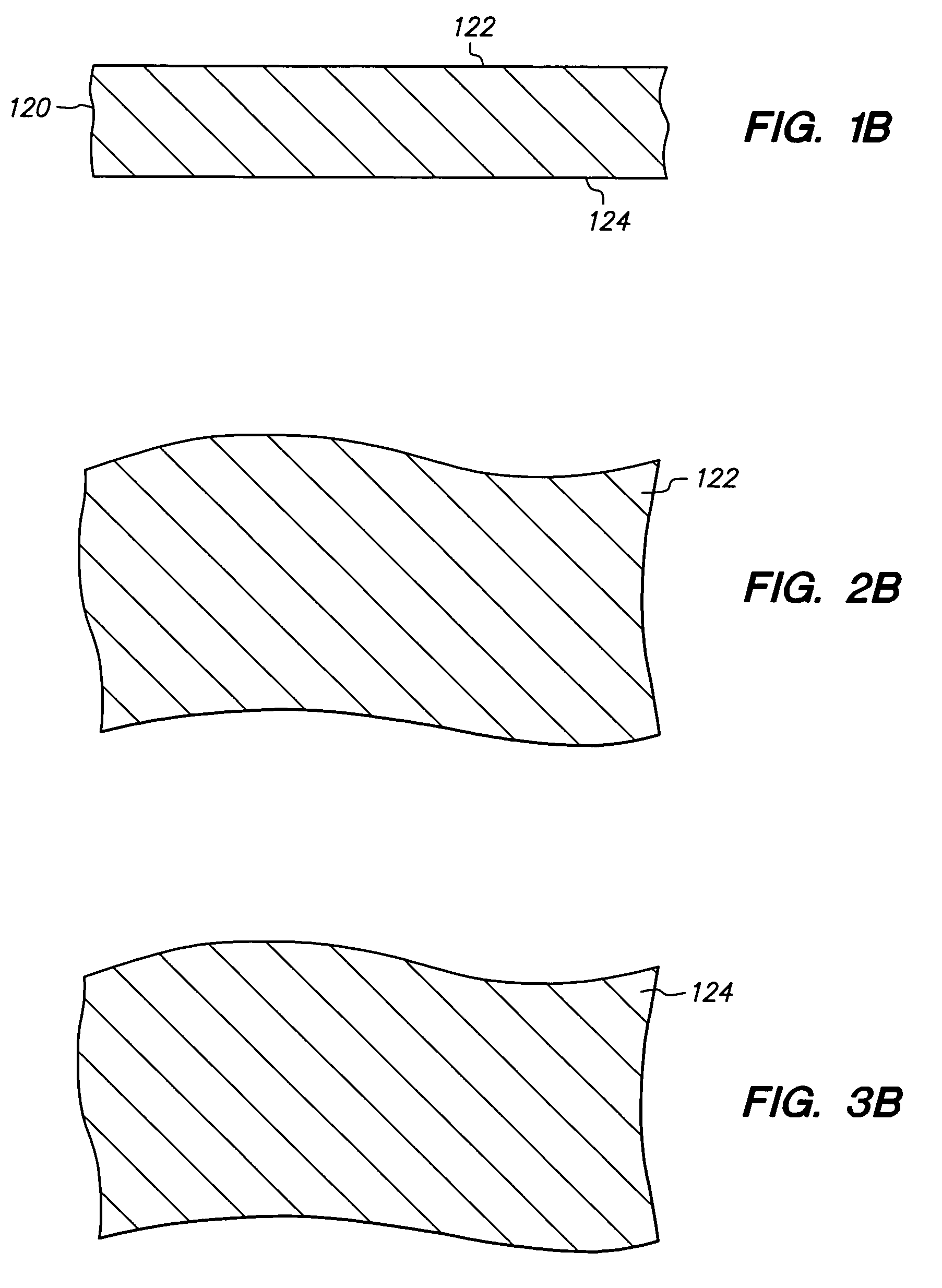

Method of making a semiconductor chip assembly with chip and encapsulant grinding

InactiveUS7993983B1Improve cooling effectRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes mechanically attaching a semiconductor chip to a routing line, then forming an encapsulant that covers the chip, then grinding the encapsulant without grinding the chip and then grinding the encapsulant and the chip such that the encapsulant and the chip are laterally aligned.

Owner:BRIDGE SEMICON

Semiconductor chip assembly with bumped metal pillar

InactiveUS7129575B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line, a bumped terminal and a metal pillar, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The routing line is contiguous with the bumped terminal and extends laterally beyond the bumped terminal and the metal pillar, and the metal pillar contacts and extends vertically beyond the bumped terminal.

Owner:BRIDGE SEMICON

Method of making a semiconductor chip assembly using multiple etch steps to form a pillar after forming a routing line

InactiveUS20060166406A1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesCompound (substance)Semiconductor chip

A method of making a semiconductor chip assembly includes providing a metal base that includes a metal plate and a metal layer, providing a routing line that contacts the metal layer and an etch mask that contacts the metal plate, providing a semiconductor chip that includes a conductive pad, mechanically attaching the chip to the routing line, electrically connecting the routing line to the pad, and etching the metal base using a first wet chemical that is selective of the metal plate and then a second wet chemical etch that is selective of the metal layer and the etch mask to form a pillar from an unetched portion of the metal base that contacts the routing line.

Owner:BRIDGE SEMICON

Semiconductor chip assembly with precision-formed metal pillar

InactiveUS7319265B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSealant

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line and a metal pillar, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The metal pillar includes tapered sidewalls with first and second sidewall portions and a spike, and the first and second sidewall portions are concave arcs that are adjacent to one another at the spike.

Owner:BRIDGE SEMICON

Method of connecting a conductive trace to a semiconductor chip using conductive adhesive

InactiveUS7264991B1Relieve pressureImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorAdhesive

A method of connecting a conductive trace to a semiconductor chip includes providing a semiconductor chip that includes a conductive pad, providing a conductive trace, then disposing a conductive adhesive between the conductive trace and the chip, thereby mechanically attaching the conductive trace to the chip such that the conductive trace overlaps the pad and the conductive adhesive contacts and is sandwiched between and electrically connects the conductive trace and the pad, and then removing a portion of the conductive adhesive such that the conductive adhesive still contacts and is sandwiched between and electrically connects the conductive trace and the pad and the conductive adhesive no longer electrically connects the conductive trace to a conductor external to the chip.

Owner:BRIDGE SEMICON

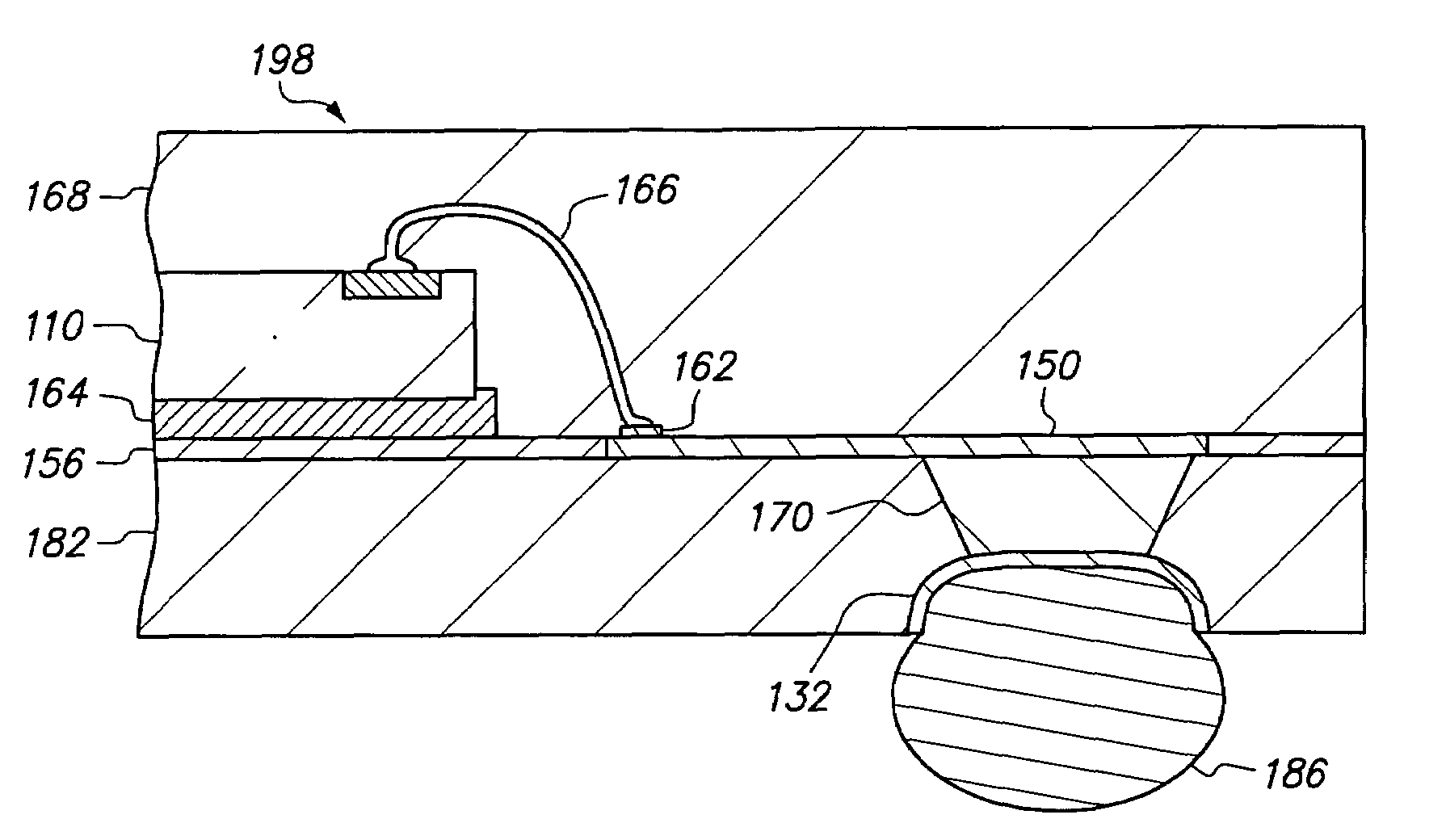

Method of making a semiconductor chip assembly with a conductive trace and a substrate

InactiveUS6872591B1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes providing a semiconductor chip, a conductive trace and a substrate, wherein the chip includes first and second opposing major surfaces and a conductive pad, the pad extends to the first surface of the chip, the substrate includes first and second opposing major surfaces, a conductive terminal and a dielectric base, the conductive terminal extends through the dielectric base to the first and second surfaces of the substrate, a cavity extends from the first surface of the substrate into the substrate, the first surfaces of the chip and the substrate face in a first direction, the second surfaces of the chip and the substrate face in a second direction, and the chip extends into the cavity, and then electrically connecting the conductive terminal to the pad using the conductive trace.

Owner:BRIDGE SEMICON

Inter-connecting structure for semiconductor package and method of the same

InactiveUS20090096093A1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The interconnecting structure for a semiconductor die assembly comprises a build-up layers having RDL formed therein formed over a die having die pads formed thereon, wherein the RDL is coupled to the die pads; an isolation base having ball openings attached over the build-up layer to expose ball pads within the build-up layers; and conductive balls placed into the ball openings of the isolation base and attached on the ball pads within the build-up layers.

Owner:ADVANCED CHIP ENG TECH

Hemostatic devices

ActiveUS9072806B2Reduce the amount requiredConvenient and cost-effective for manufacturingPharmaceutical delivery mechanismDisinfectionFiberKaolin clay

Owner:TELEFLEX LIFE SCI LTD

Method of making a semiconductor chip assembly with an interlocked contact terminal

InactiveUS7232707B1Improve protectionStable supportFinal product manufactureSemiconductor/solid-state device detailsSemiconductor chipEngineering

Owner:BRIDGE SEMICON

Method of making a semiconductor chip assembly with a metal containment wall and a solder terminal

InactiveUS7419851B2Reduce contact areaImprove protectionFinal product manufactureSemiconductor/solid-state device detailsSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes providing a metal base, a routing line, a metal containment wall and a solder layer in which the metal containment wall includes a cavity and the solder terminal contacts the metal containment wall in the cavity, mechanically attaching a semiconductor chip to the routing line, forming a connection joint that electrically connects the routing line and the pad, etching the metal base to reduce contact area between the metal base and the routing line and between the metal base and the metal containment wall, and providing a solder terminal that includes the solder layer.

Owner:BRIDGE SEMICON

Method of making a semiconductor chip assembly with metal pillar and encapsulant grinding and heat sink attachment

InactiveUS7811863B1Improve cooling effectRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSealant

A method of making a semiconductor chip assembly includes mechanically attaching a semiconductor chip to a routing line, forming a metal pillar on the routing line, forming an encapsulant that covers the chip and the metal pillar, grinding the encapsulant without grinding the metal pillar, then grinding the encapsulant and the metal pillar such that the encapsulant and the metal pillar are laterally aligned, and then attaching a heat sink to the metal pillar.

Owner:BRIDGE SEMICON

Method of making a semiconductor chip assembly with a bumped metal pillar

InactiveUS7112521B1Enhancing mechanical supportImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes providing a metal base, a routing line and a bumped terminal, then mechanically attaching a semiconductor chip to the metal base, the routing line and the bumped terminal, then forming an encapsulant, and then etching the metal base to form a metal pillar that contacts the bumped terminal.

Owner:BRIDGE SEMICON

Semiconductor chip assembly with metal containment wall and solder terminal

InactiveUS7414319B2Reduce contact areaImprove protectionFinal product manufactureSemiconductor/solid-state device detailsSemiconductor chipEngineering

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line, a metal containment wall and a solder terminal, and a connection joint that electrically connects the routing line and the pad. The metal containment wall includes a cavity, and the solder terminal contacts the metal containment wall in the cavity and is spaced from the routing line.

Owner:BRIDGE SEMICON

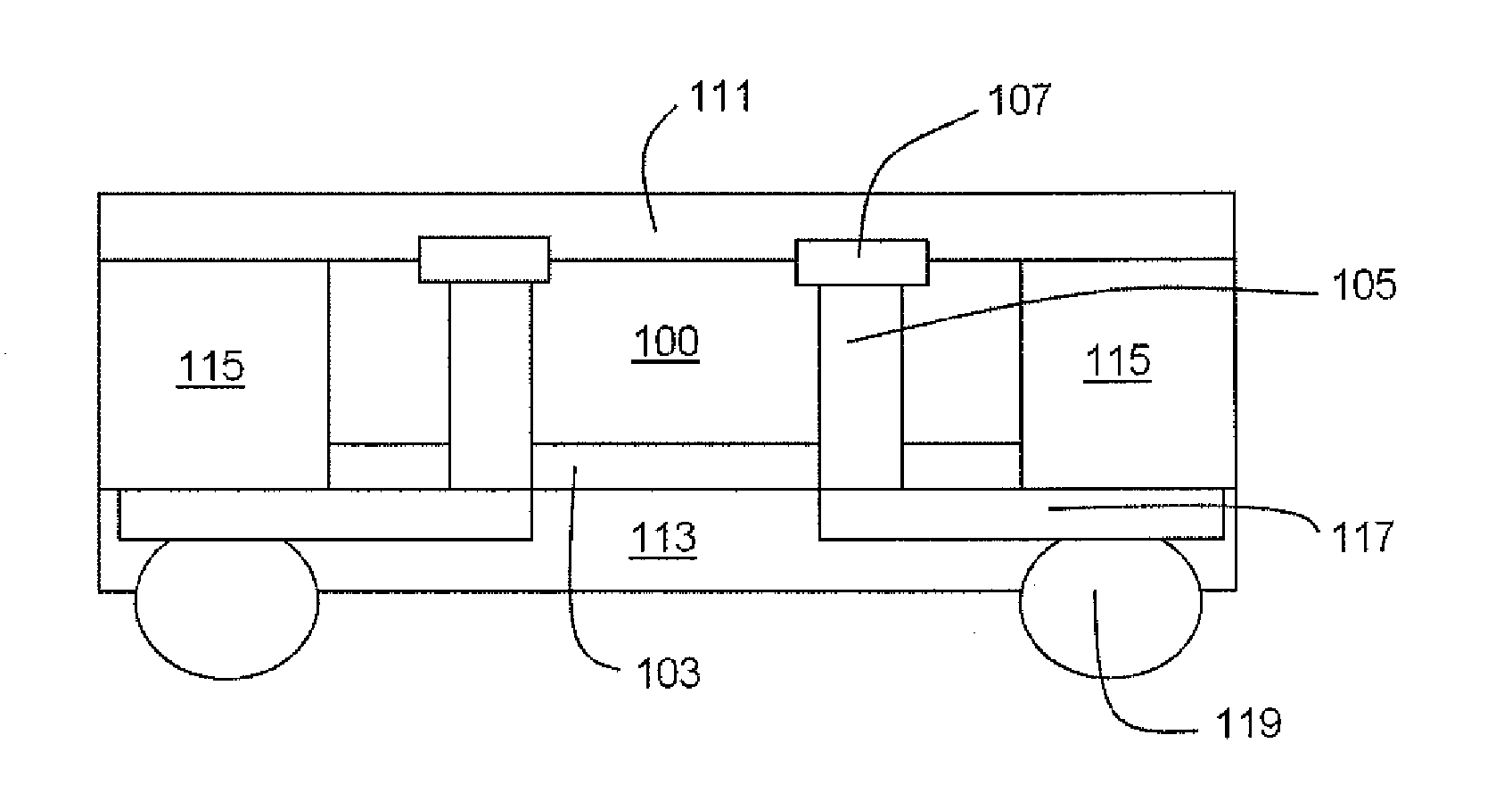

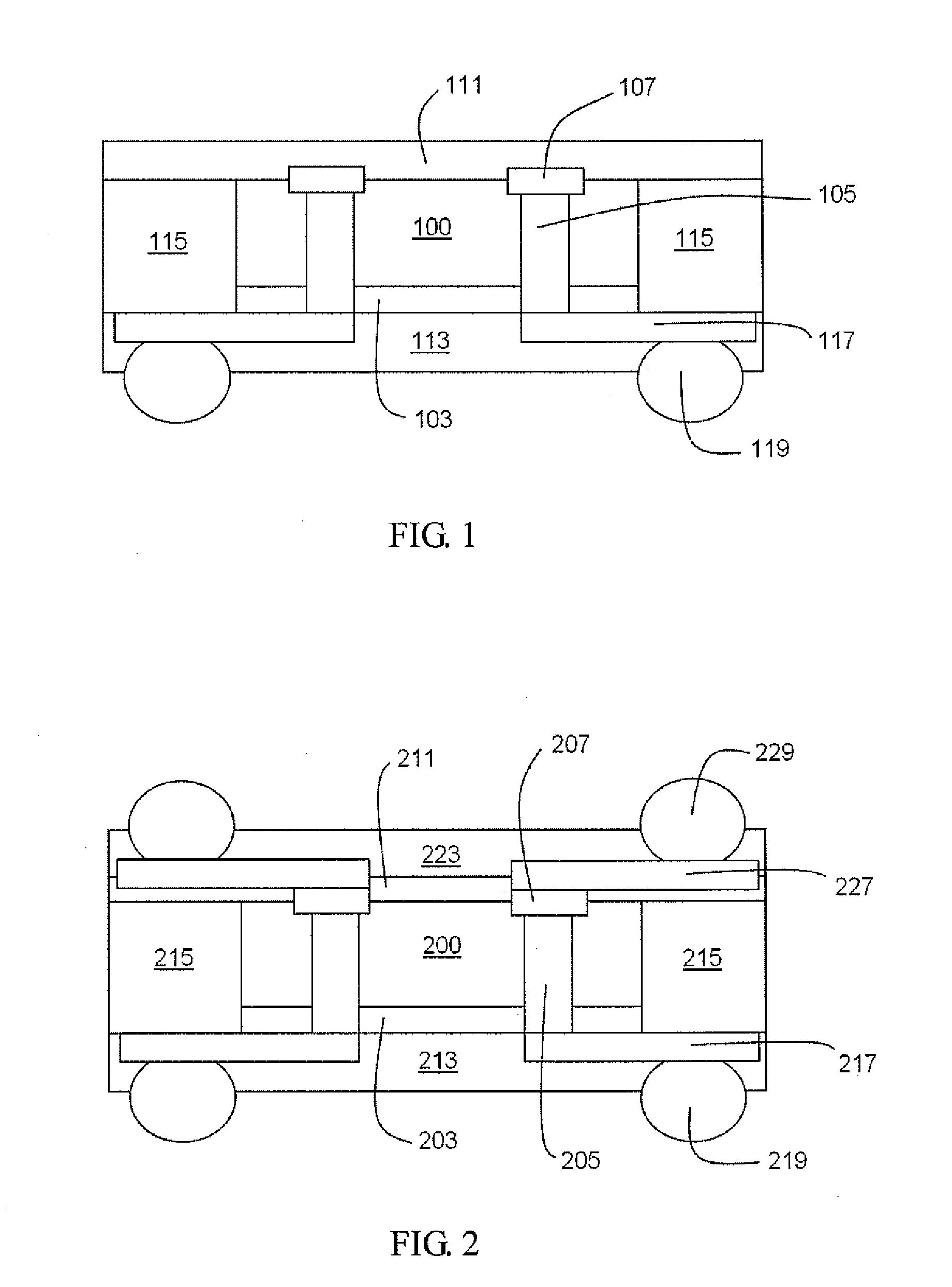

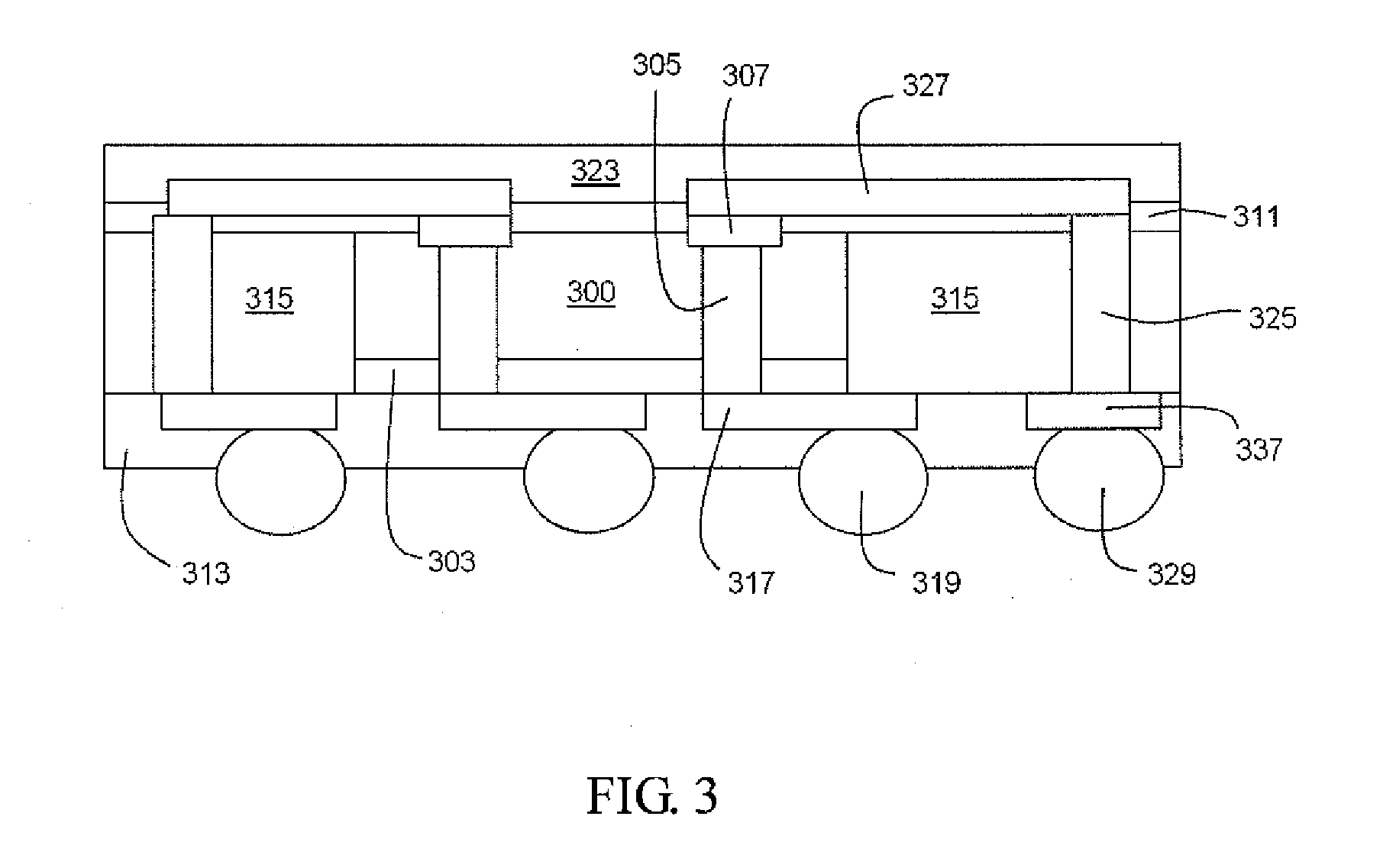

Package structure and manufacturing method thereof

ActiveUS20110108977A1Thickness minimizationMinimized in sizeSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerFilling materials

The present invention discloses a semiconductor device package structure with redistribution layer (RDL) and through silicon via (TSV) techniques. The package structure comprises an electronic element which includes a dielectric layer on a backside surface of the electronic element, a plurality of first conductive through vias across through the electronic element and the dielectric layer, and a plurality of conductive pads accompanying the first conductive through vias on an active surface of the electronic element; a filler material disposed adjacent to the electronic element; a first redistribution layer disposed over the dielectric layer and the filler material, and connected to the first conductive through vias; a first protective layer disposed over the active surface of the electronic element, the conductive pads, and the filler material; and a second protective layer disposed over the redistribution layer, the dielectric layer, and the filler material.

Owner:ADL ENERGY CORP

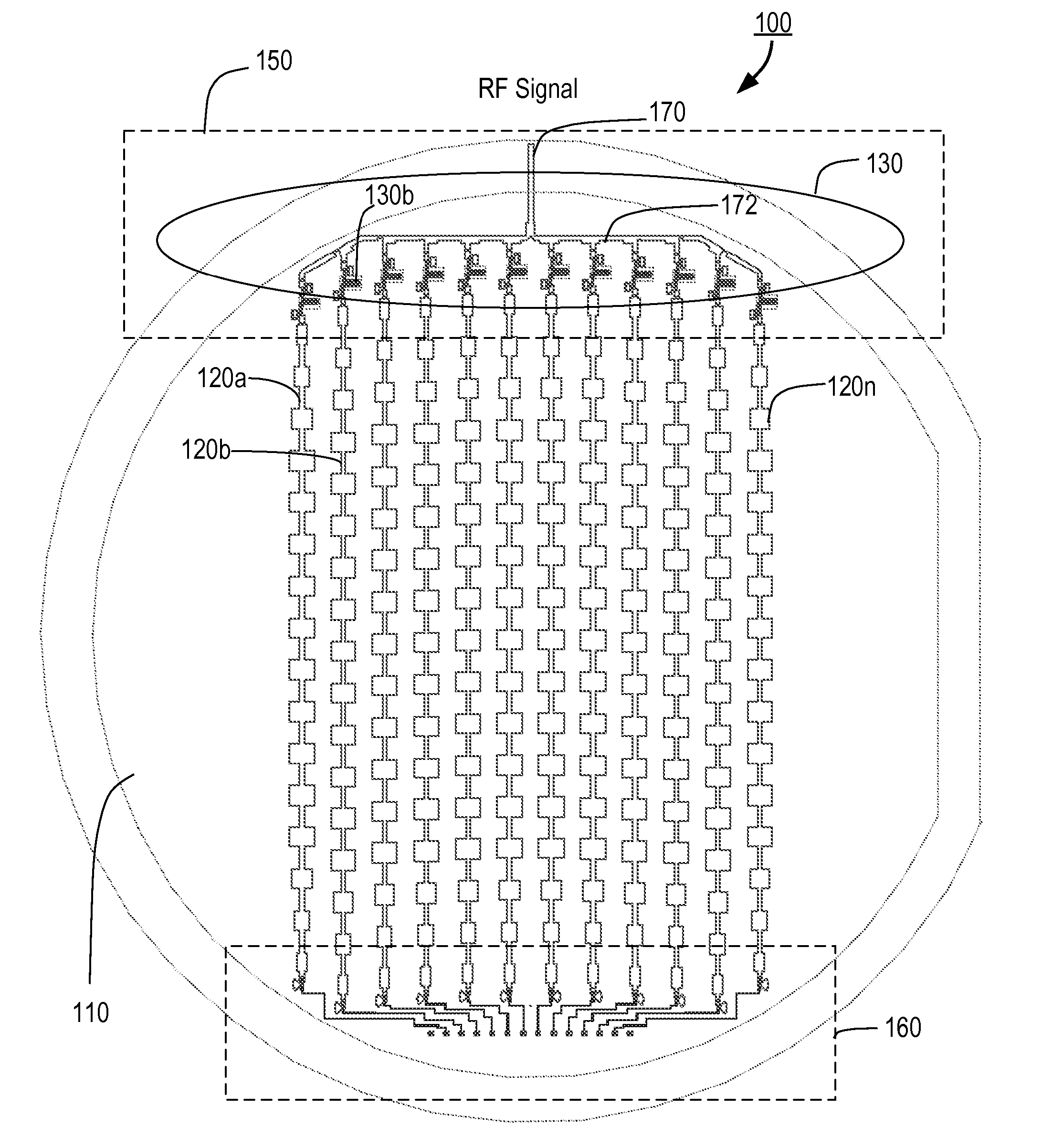

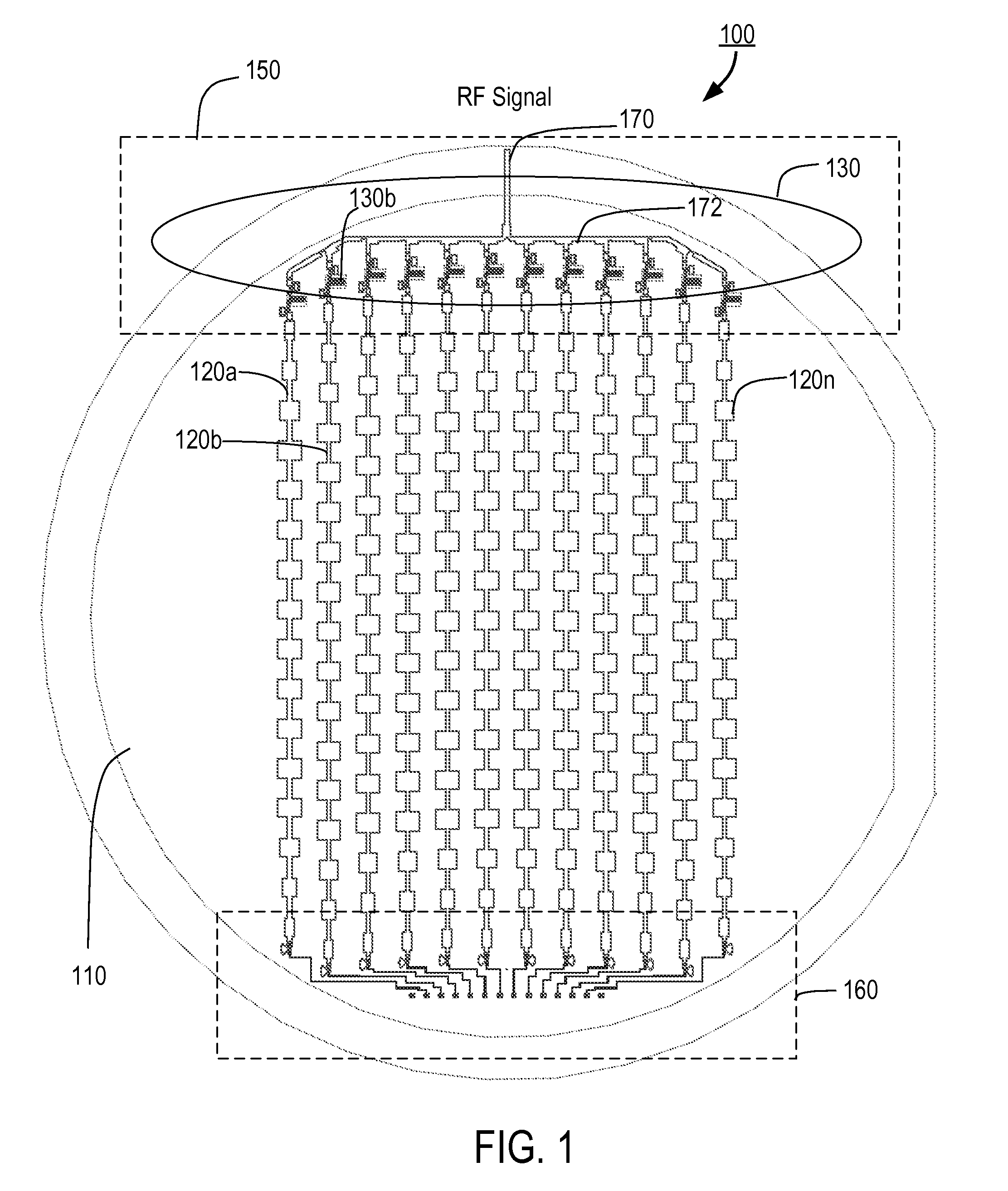

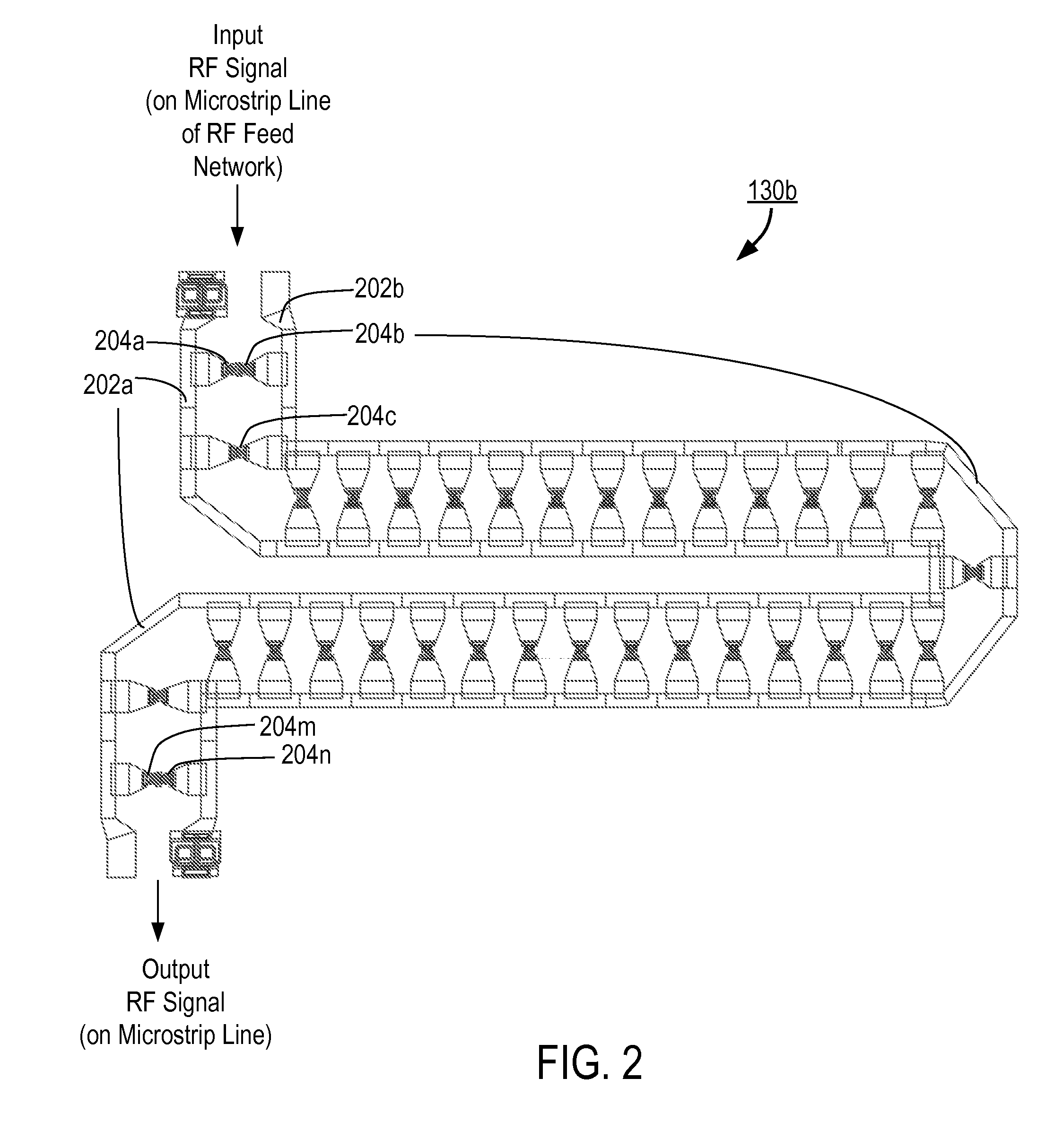

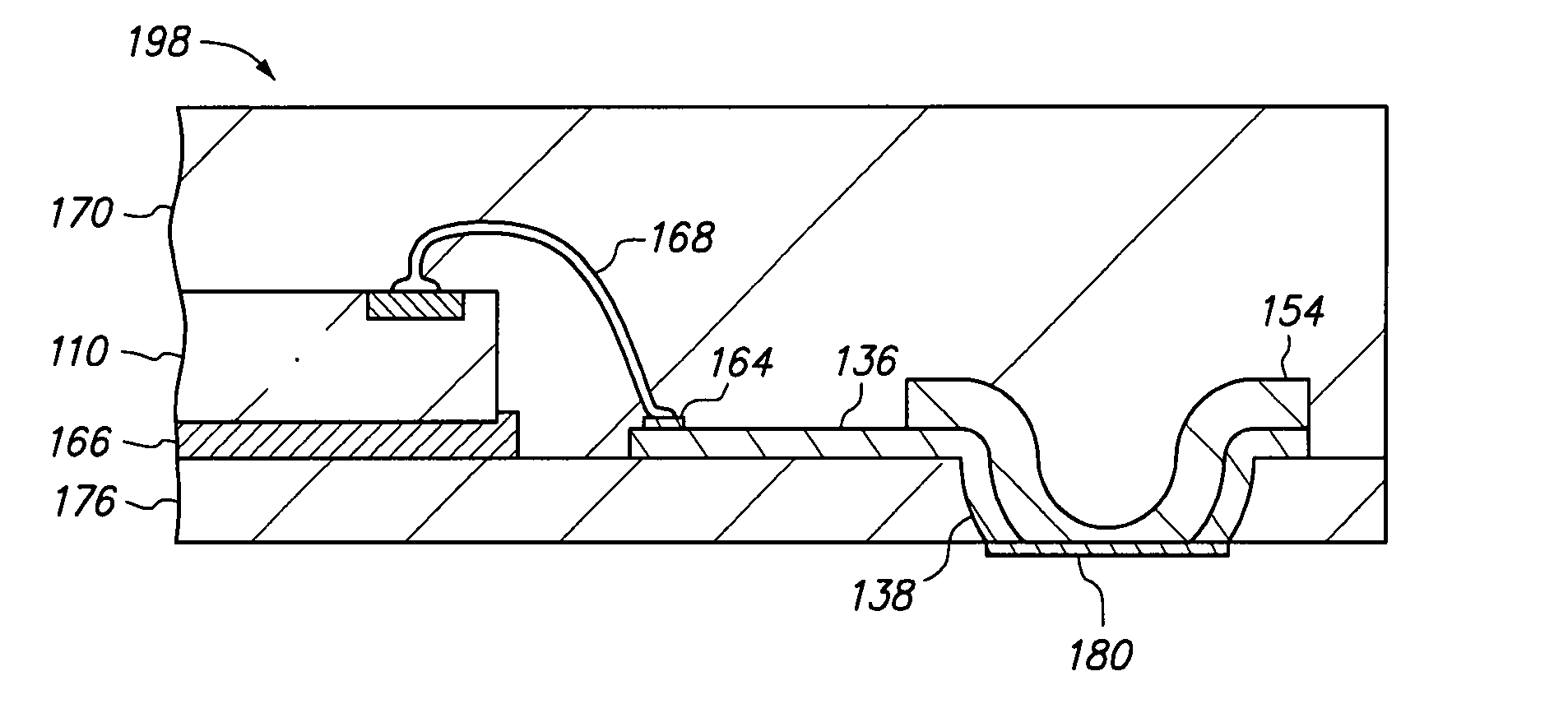

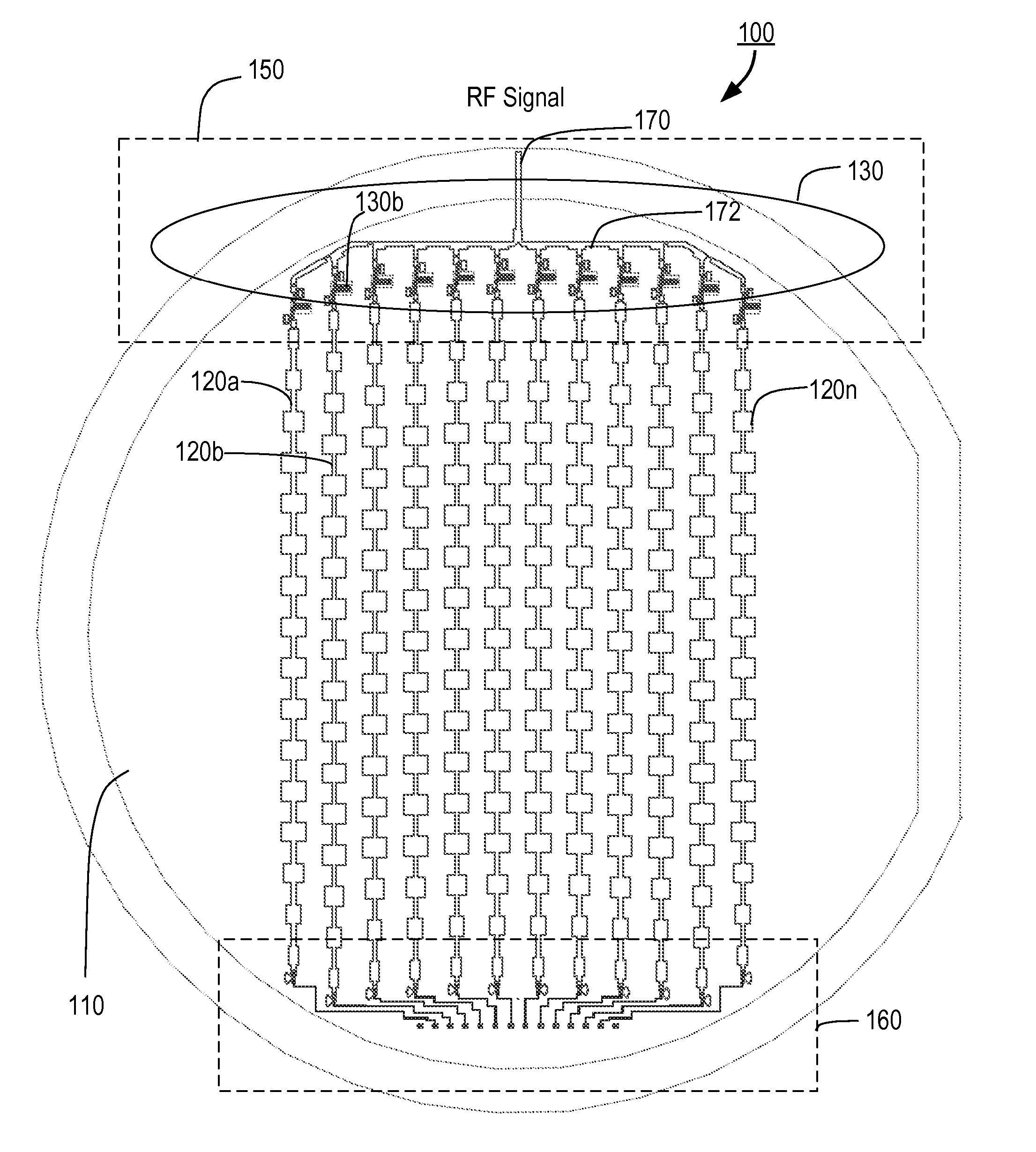

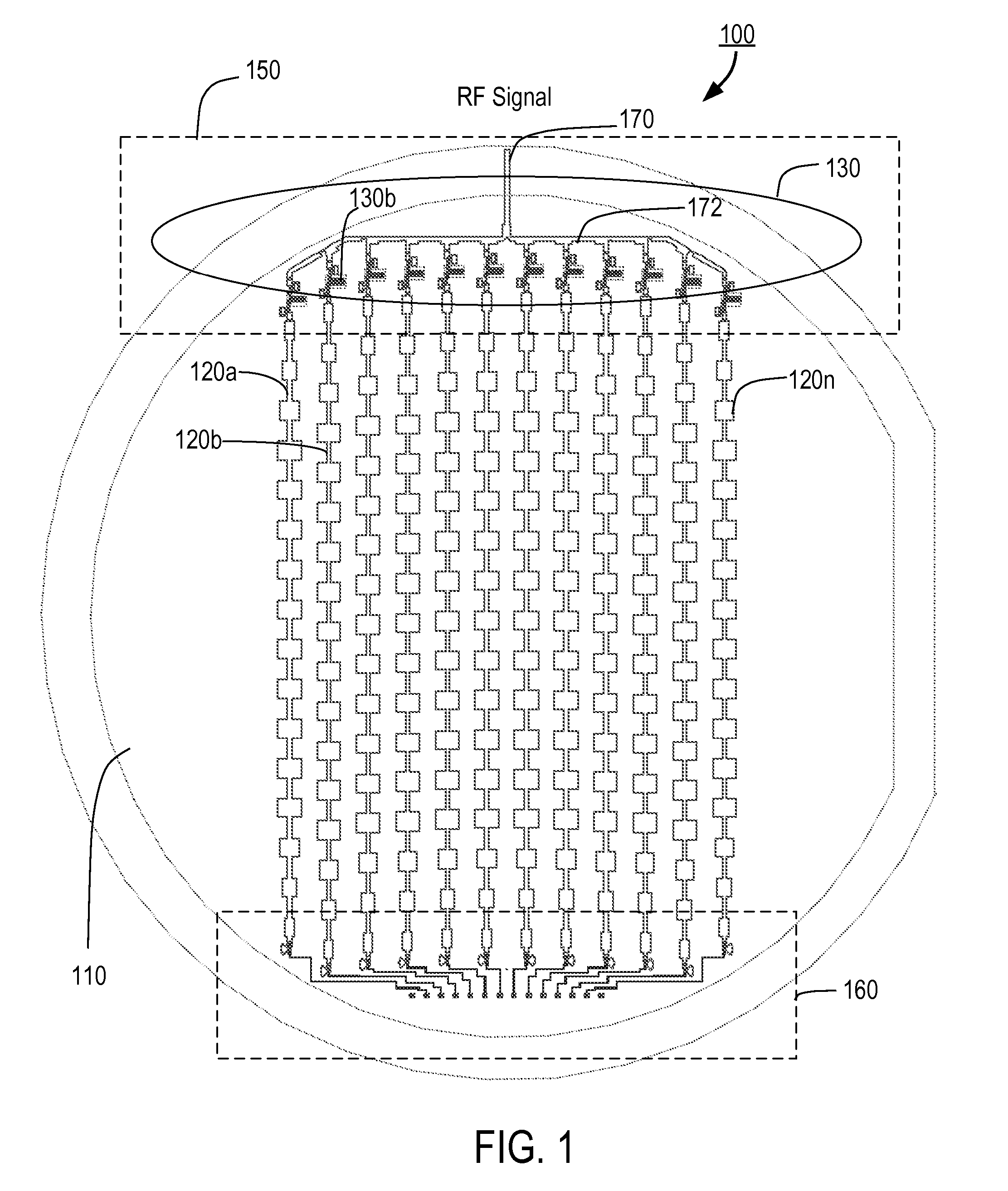

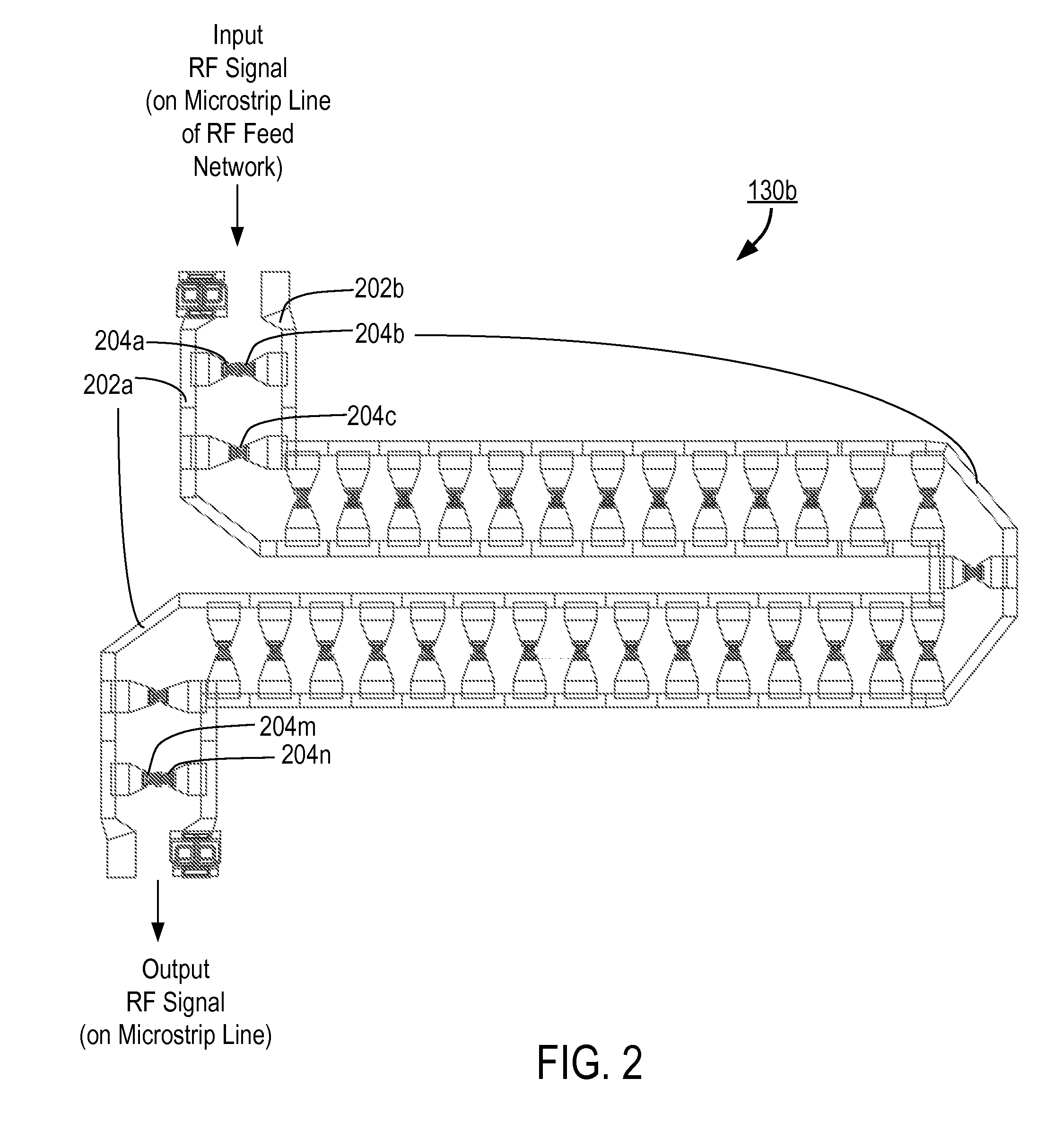

Wafer Scanning Antenna With Integrated Tunable Dielectric Phase Shifters

ActiveUS20070279294A1Reduce manufacturing costEasy to controlAntenna arraysSimultaneous aerial operationsElectrical connectionRadio frequency signal

A wafer antenna comprises a wafer substrate, a plurality of antenna elements integrated on the wafer substrate for radiating and receiving a radio frequency signal, an electrical connection integrated on the wafer substrate; a feed network integrated on the wafer substrate for distributing the RF signal from the electrical connection to the antenna elements and from the antenna elements to the electrical connection, and a plurality of tunable dielectric phase shifters integrated on the wafer substrate with each of the tunable dielectric phase shifters coupled to a corresponding one of the antenna elements and controlling the phase of the RF signal coupled to the corresponding one of the antenna elements.

Owner:MERCURY MISSION SYST LLC

Method of making a semiconductor chip assembly with a bumped terminal, a filler and an insulative base

InactiveUS7833827B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of making a semiconductor chip assembly includes providing a metal base, a routing line, a bumped terminal and a filler, wherein the routing line contacts the bumped terminal and the filler, then mechanically attaching a semiconductor chip to the metal base, the routing line, the bumped terminal and the filler, then forming an encapsulant, then etching the metal base to expose the bumped terminal, and then forming an insulative base that covers a peripheral portion of the bumped terminal.

Owner:BRIDGE SEMICON

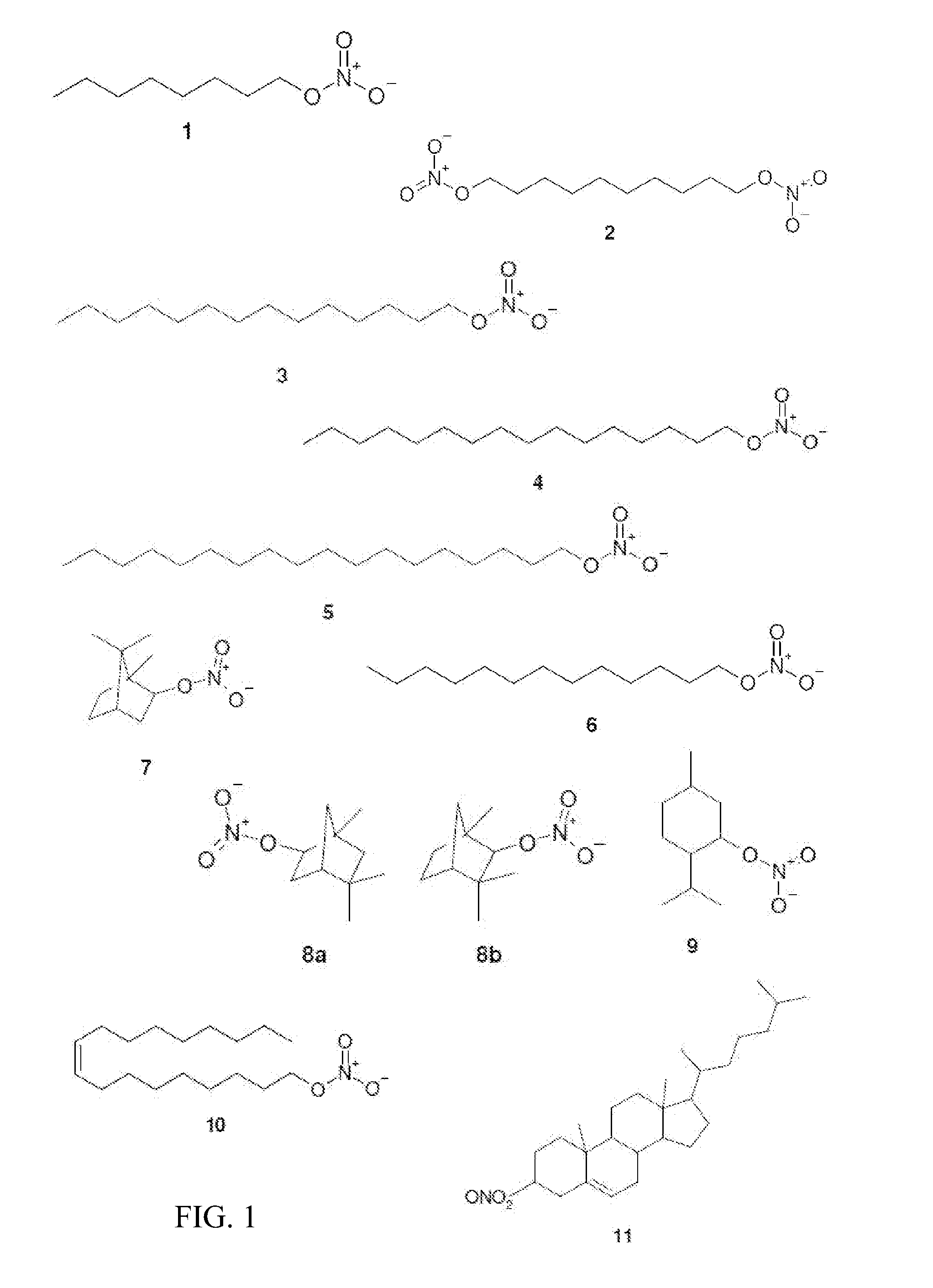

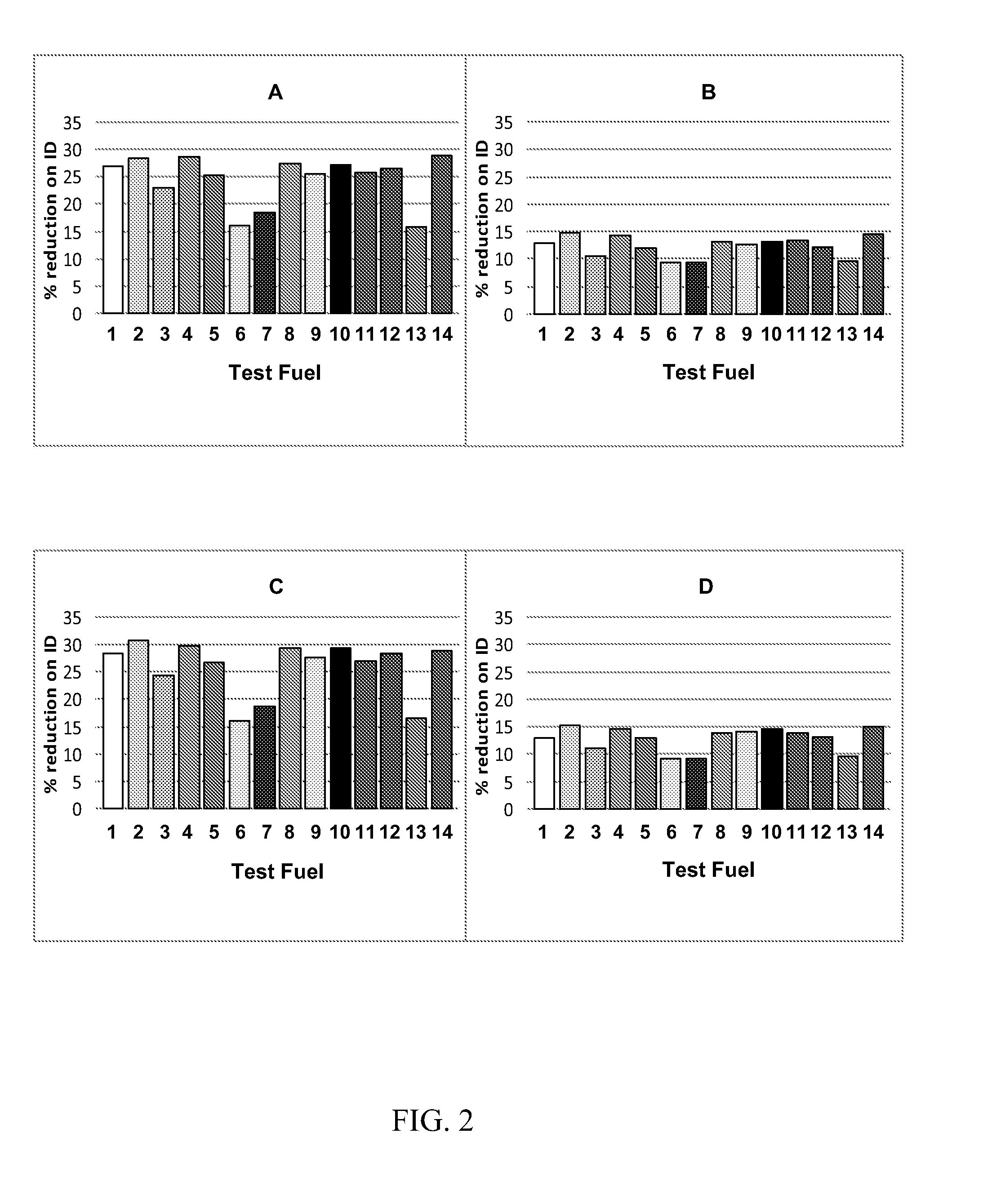

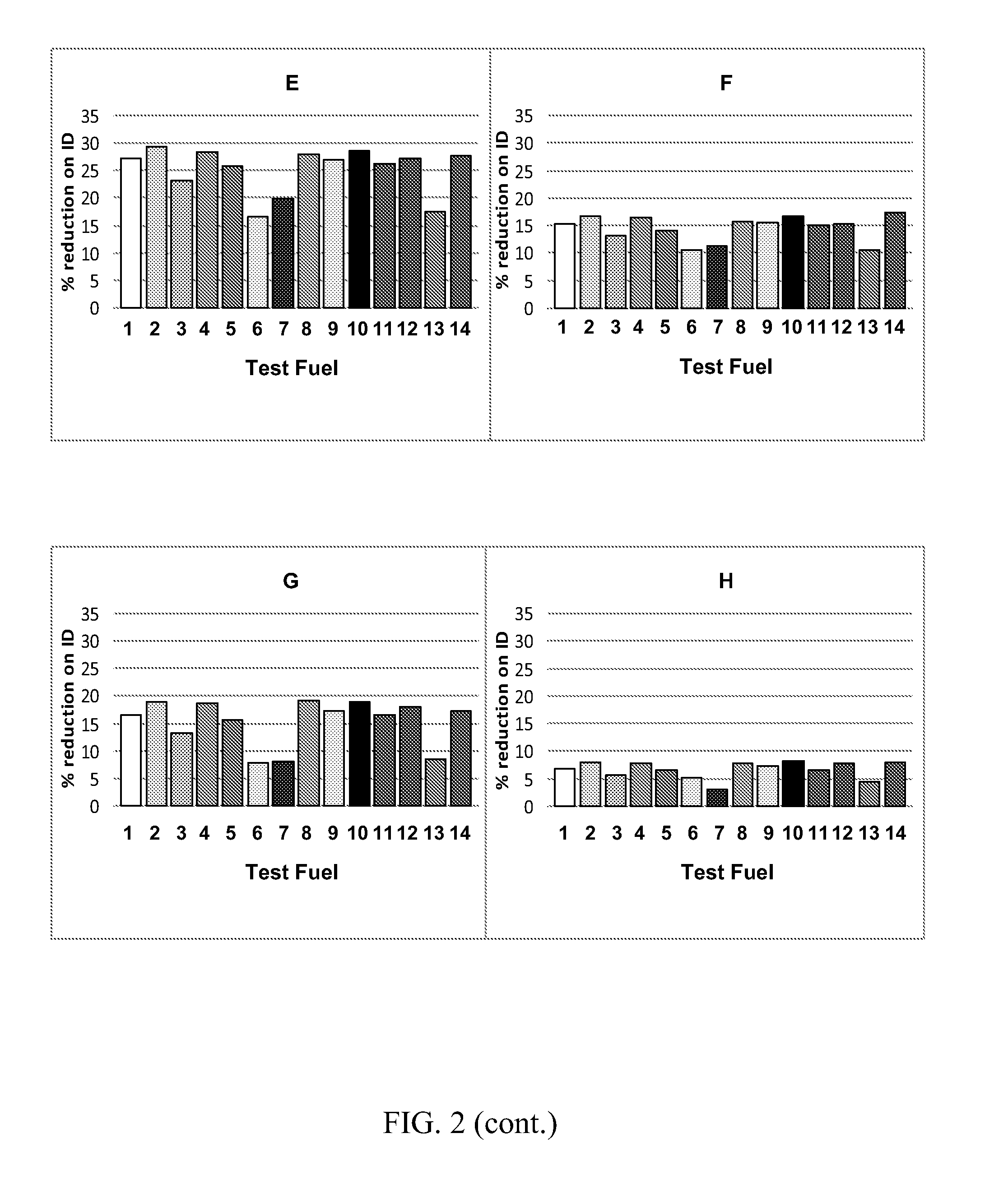

Organic nitrates as ignition enhancers

InactiveUS20130160354A1Similar and low volatilityConvenient and cost-effective for manufacturingLiquid carbonaceous fuelsFuel additivesIgnition delayOrganic nitrates

A diesel fuel composition comprising an organic nitrate is described. The organic nitrate may be a terpene nitrate. Methods of using an organic nitrate for achieving a desired cetane number, and uses of organic nitrates for the purpose of reducing the ignition delay of the fuel and / or for increasing its cetane number to a defined level are also described, as are methods of operating a compression ignition engine.

Owner:SHELL OIL CO

Package structure and manufacturing method thereof

ActiveUS8058102B2Thickness minimizationMinimized in sizeSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerFilling materials

The present invention discloses a semiconductor device package structure with redistribution layer (RDL) and through silicon via (TSV) techniques. The package structure comprises an electronic element which includes a dielectric layer on a backside surface of the electronic element, a plurality of first conductive through vias across through the electronic element and the dielectric layer, and a plurality of conductive pads accompanying the first conductive through vias on an active surface of the electronic element; a filler material disposed adjacent to the electronic element; a first redistribution layer disposed over the dielectric layer and the filler material, and connected to the first conductive through vias; a first protective layer disposed over the active surface of the electronic element, the conductive pads, and the filler material; and a second protective layer disposed over the redistribution layer, the dielectric layer, and the filler material.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor chip assembly with bumped terminal and filler

InactiveUS7425759B1Improve protectionStable supportSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSealant

Owner:BRIDGE SEMICON

Wafer scanning antenna with integrated tunable dielectric phase shifters

ActiveUS7633456B2Reduce manufacturing costEasy to controlAntenna arraysSimultaneous aerial operationsElectrical connectionRadio frequency signal

A wafer antenna comprises a wafer substrate, a plurality of antenna elements integrated on the wafer substrate for radiating and receiving a radio frequency signal, an electrical connection integrated on the wafer substrate; a feed network integrated on the wafer substrate for distributing the RF signal from the electrical connection to the antenna elements and from the antenna elements to the electrical connection, and a plurality of tunable dielectric phase shifters integrated on the wafer substrate with each of the tunable dielectric phase shifters coupled to a corresponding one of the antenna elements and controlling the phase of the RF signal coupled to the corresponding one of the antenna elements.

Owner:MERCURY MISSION SYST LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com