Process for preparing silicon nano-wire

A technology of silicon nanowires and nanowires, which is applied in the field of low-dimensional nanomaterial preparation, can solve the problems of complex technology, high requirements for growth conditions, and long growth time, and achieve the effects of wide application prospects, fast speed, and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0021] Embodiment 1, preparation silicon nanowire

[0022] Using ZnO nanowires as a mask to etch silicon nanowires includes the following steps:

[0023] 1) Place ZnO nanowires (about 150-200nm in diameter and more than 10 μm in length) in a small centrifuge tube, drop an appropriate amount of absolute ethanol, and then place them in an ultrasonic bath for ultrasonic treatment, so that the nanowires are dispersed into the ethanol solution, Thereby forming a suspension of ZnO nanowires;

[0024] 2) SOI (the basic parameters of the SOI substrate used are: the thickness of the top silicon layer is about 100nm; the top layer and the substrate silicon are both p-type semiconductor features, and the resistivity is about 1-10Ω cm; the thickness of the middle oxide layer is about 400nm) with acetone, ethanol, and deionized water, followed by ultrasonic cleaning, and then treated with piranha solution (98% concentrated sulfuric acid-30% hydrogen peroxide, volume ratio 3:1) in a 95°C w...

Embodiment 2

[0030] Embodiment 2, preparation silicon nanowire field effect tube

[0031] Silicon nanowires prepared by the method of the present invention can also be used to prepare silicon nanowire field effect transistors: using ZnO nanowires and photoresist patterns as masks, combined with ICP dry etching, ultraviolet lithography, and vacuum thermal evaporation Silicon nanowire field effect transistors were prepared on SOI substrates by conventional micromachining techniques such as stripping, metallization, etc. The main experimental process is shown in Figure 2, and the steps are as follows:

[0032] 1) Prepare the SOI substrate sample, and then ultrasonically clean it with acetone, ethanol, and deionized water in sequence, and then treat it with piranha solution (98% concentrated sulfuric acid-30% hydrogen peroxide, volume ratio 3:1) in a 95°C water bath for 30 minutes , and then drop the suspension of ZnO nanowires on the surface of the cleaned SOI substrate to disperse it;

[00...

Embodiment 3

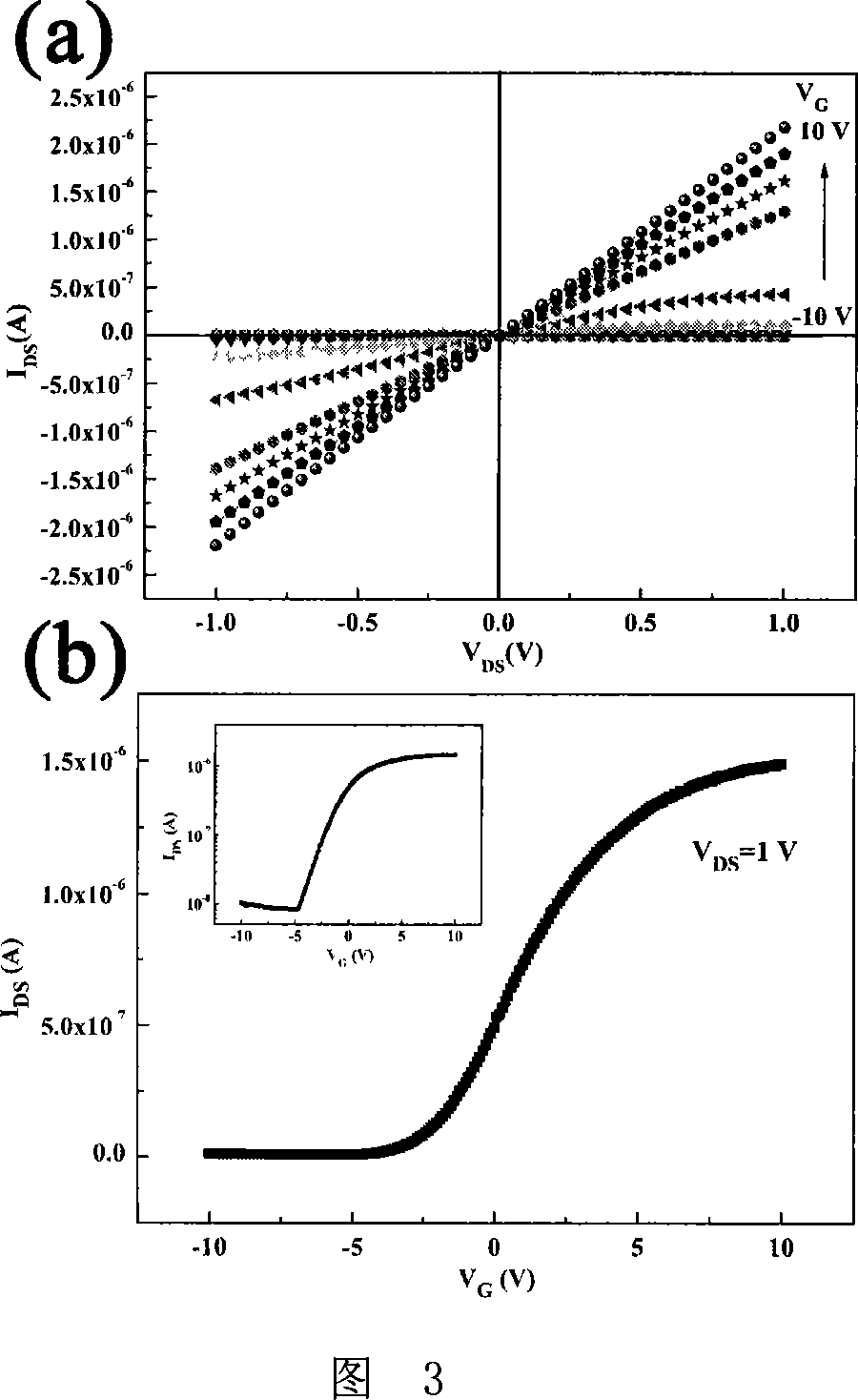

[0038] Embodiment 3, measuring the electrical performance of silicon nanowire field effect transistor

[0039] The silicon nanowire FET obtained in embodiment 2 has been electrically measured, and Fig. 3 (a) is the corresponding source-drain current voltage (I DS -V DS ) relationship measurement curve, the added grid voltage V G Varies from -10 to +10V in 2V steps. When the gate voltage V G When increasing from -10V to +10V, the source-drain current I DS Gradually increasing, showing typical n-type semiconductor field effect characteristics. When zero gate voltage, we can according to the size of the etched silicon line and the resistivity formula ρ = R WT L (W and T are the width and thickness of the silicon line, respectively, and the thickness of the silicon line is determined by the thickness of the top layer of silicon.) The resistivity of silicon is about 6Ω·cm. According to the relationship b...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com