Structure of high-density phase transition memory and process of preparation thereof

A phase-change memory and phase-change storage technology, applied in the field of micro-nano electronics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] On the cleaned P-type or N-type silicon wafer at 8-12 hours, the P / N junction or N / P junction is realized by conventional epitaxy technology. In order to reduce the series resistance of the N / P junction and the upper and lower circuits, by controlling the doping concentration of B and P of the N / P junction, it presents a concentration gradient centered on the N / P junction from the center to the surface. . Considering the subsequent CMP process, the thickness of the entire epitaxial layer is 300-600nm, and then through the optimization process of CMP, after the N / P junction on the silicon wafer is formed, the micro-region roughness is less than 10 Ȧ, and the whole wafer The average roughness (ttv) is less than 5 μm and the warpage of the whole piece is less than 20 μm, so as to meet the basic conditions of bonding.

[0043] Through the 45-180nm standard CMOS process, the CMOS silicon wafer of the peripheral circuit is realized. At the same time, in order to realize the ...

Embodiment 2

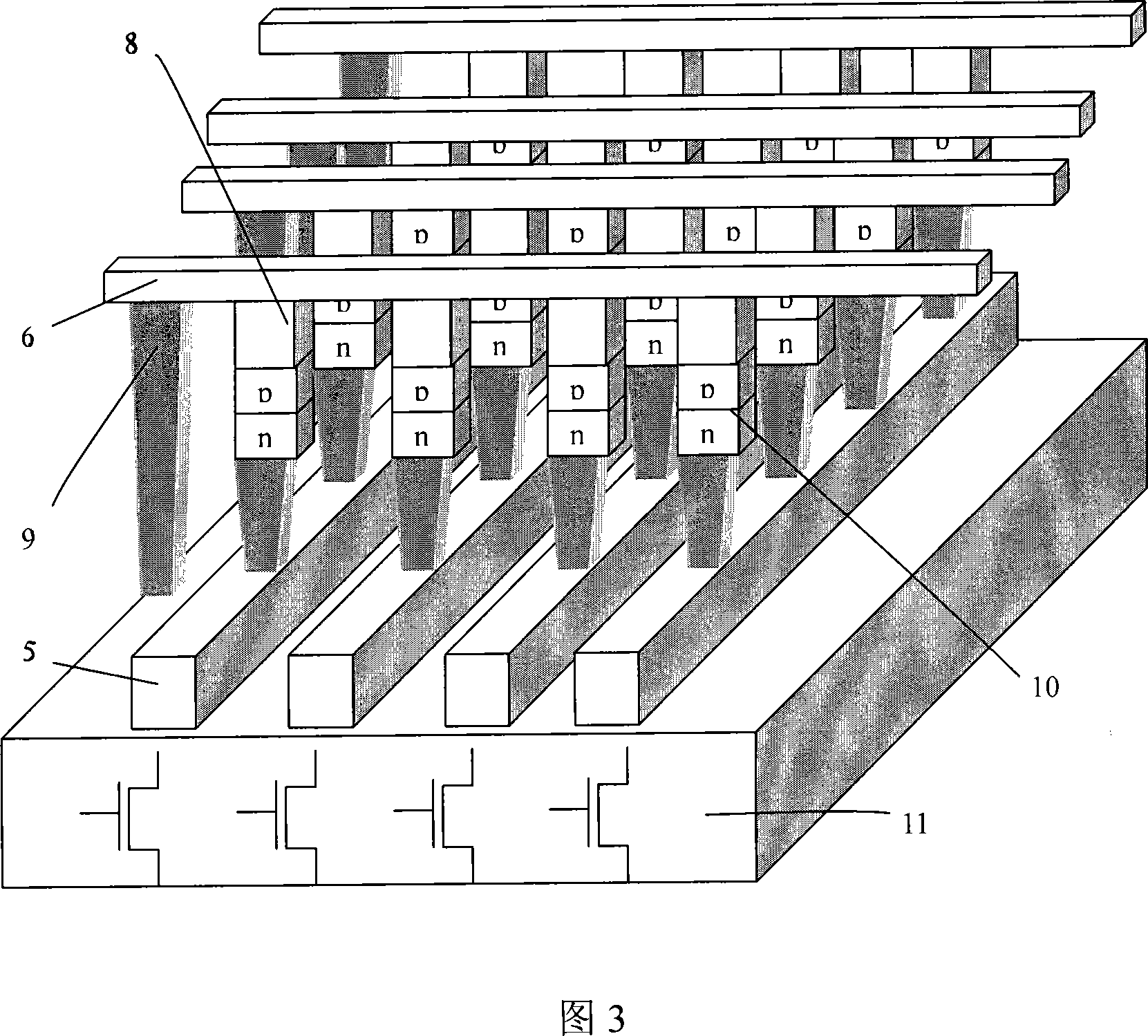

[0053] As shown in FIG. 3 , a three-dimensional schematic diagram of the integration of the structure of the 1D1R array and peripheral circuits is realized. When the word line is at a low level (logic "0" level), the diode is in a forward conduction state, and the current pulse generated by the lower peripheral circuit passes through the bit line through hole, is transmitted to the phase change memory unit through the bit line, and then passes through the diode Return to the lower peripheral circuit, thus forming a current loop. When the word line level is at a high level (logic "1" level), the diode is in a reverse cut-off state, and the current pulse sent by the lower peripheral circuit cannot form a current loop, that is, the peripheral circuit cannot operate on the phase-change memory unit. Through the logic control of the peripheral circuit, when the memory block is not selected, all the word lines of the memory block remain at high level, thereby reducing the dynamic pow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More