Bigrid power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device

A device and power technology, applied in the field of low-power MOS control semiconductor power devices, can solve the problems of reduced on-resistance and low concentration in the drift region, so as to reduce the on-resistance and power consumption, increase the current flow area, and shorten the current The effect of the conduction path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

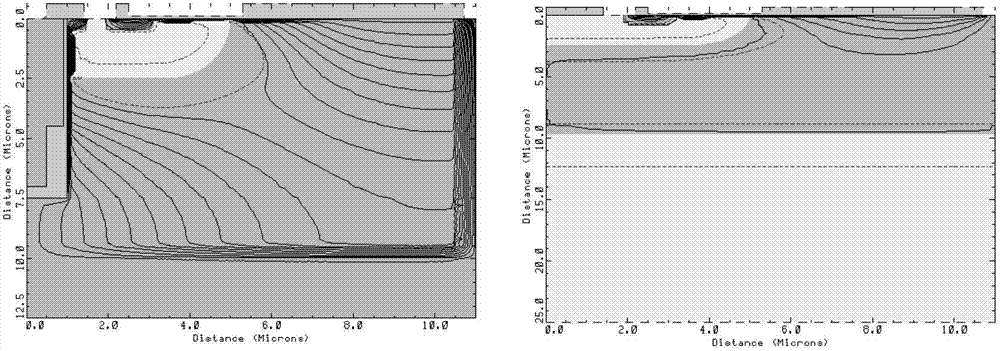

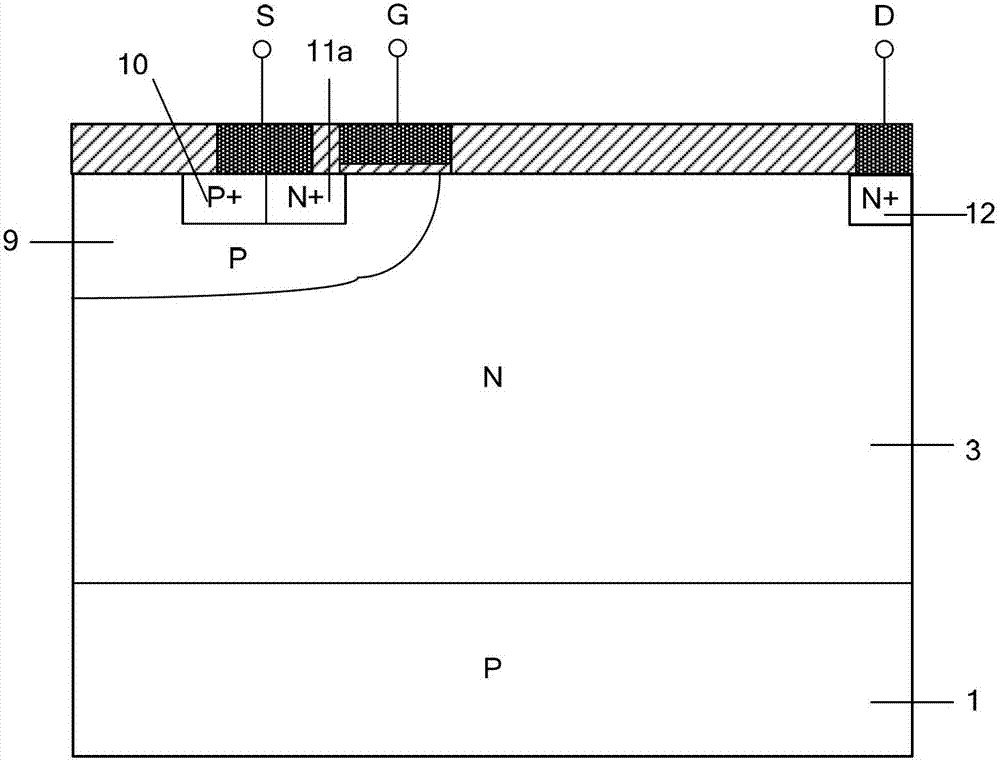

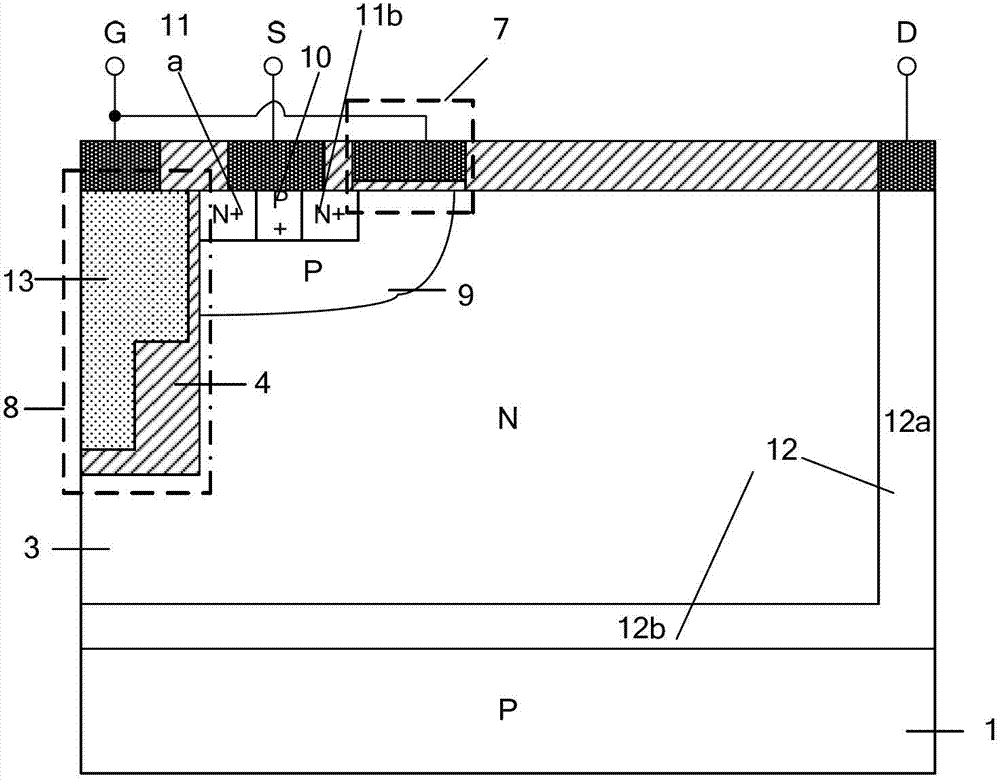

[0028] figure 1 It is a schematic diagram of the cross-sectional structure of a conventional LDMOS device for comparison; figure 2 It is a schematic diagram of the cross-sectional structure of an N-channel double-gate MOSFET device proposed by the present invention.

[0029] A dual-gate power MOSFET device such as figure 2 , including a P-type semiconductor substrate 1, an N-type semiconductor active layer 3, a planar gate structure 7, a trench gate structure 8, a source structure and a drain structure, wherein the top of the N-type semiconductor active layer 3 has a P-type semiconductor body area 9. The source structure includes a source metal, an N-type heavily doped semiconductor source contact region 11 and a P-type heavily doped semiconductor body contact region 10, wherein the N-type heavily doped semiconductor source contact region 11 includes N Type first heavily doped semiconductor source contact region 11a and N type second heavily doped semiconductor source co...

Embodiment 2

[0032] image 3 It is a schematic cross-sectional structure diagram of a dual-gate power MOSFET device (N-channel) provided by the present invention (with a uniform thickness of the trench gate dielectric). The difference between the embodiment 2 and the embodiment 1 is that the thickness of the trench gate dielectric 4 in the longitudinal direction is not in a stepped shape with the top thin and the bottom thick, but is made to be uniform in thickness. This is simpler than embodiment 1 in technology.

Embodiment 3

[0034] Figure 4 It is a schematic cross-sectional structure diagram of a dual-gate power MOSFET device (P channel) provided by the present invention (with a uniform thickness of the trench gate dielectric). Such as Figure 4 shown, which is the same as image 3 The only difference is that the semiconductor material conductivity type of the substrate 1, the active layer 3, the source regions 11a, 11b, the drain region 12, the body region 9 and the body contact region 10 of the device in this example and the N-channel double gate The corresponding area of the lateral MOSFET device is reversed. That is to say, the dual-gate MOSFET device with semiconductor buried layer of the present invention can be used to manufacture N-channel MOSFET devices and P-channel MOSFET devices.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More