Circuit device of graphene transistor and preparation method thereof

A circuit device and transistor technology, which is applied in the manufacture of transistors, circuits, semiconductors/solid-state devices, etc., can solve problems such as lack of molding and complexity, and achieve the effect of avoiding the reduction of electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

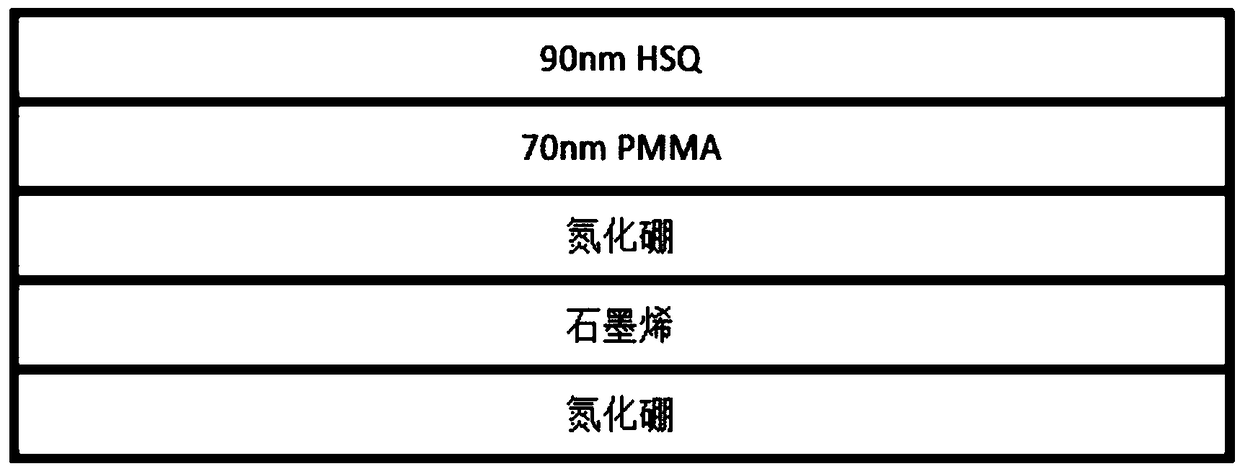

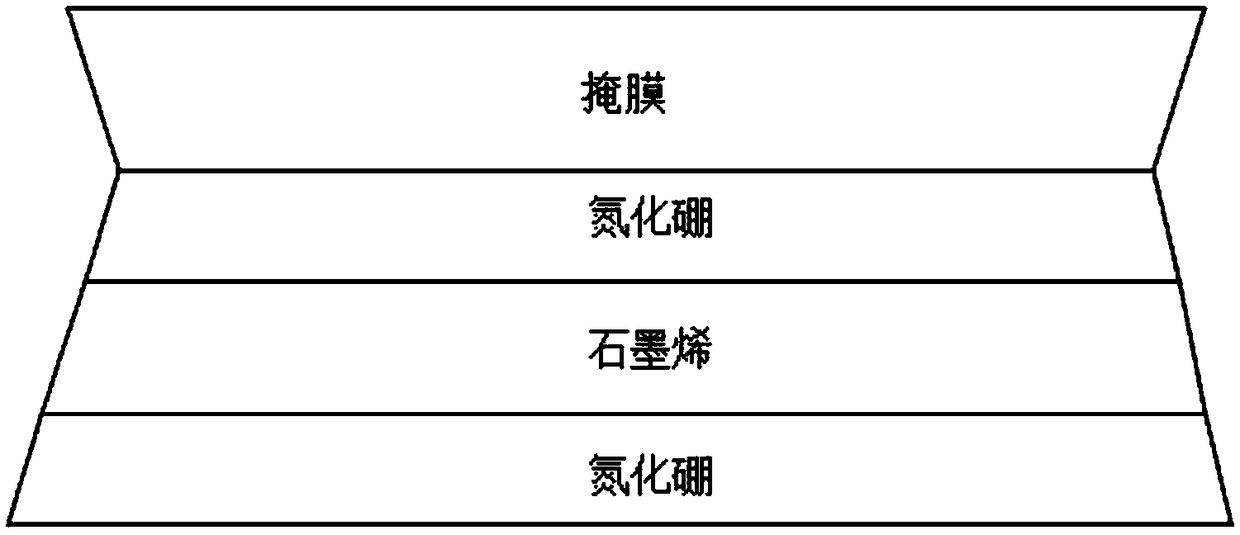

[0053] A boron nitride / graphene / boron nitride heterojunction is provided: in a CVD facility (available from Shenyang Keyi), boron is utilized on a 25 micron thick copper foil (available from CALCO) using a CVD method The precursor (available from Gelest, USA) grows a layer of boron nitride, the growth temperature is 1035 ° C, the growth time is 20 minutes, the boron precursor used is boron azine (available from Gelest, USA), by the carrier gas bubbling method It is brought into a high temperature region for growth, the carrier gas is argon or nitrogen, and the flow rate of the carrier gas is 0.5 sccm to obtain a boron nitride layer (0.3 nanometer thickness) on the copper foil. After the growth of the first layer of boron nitride was completed, nitrogen was introduced for purging for 30s. Then a 25-micron thick copper foil catalyst was placed 50 microns above the growth base copper foil, and methane (available from Linde gas) was introduced to start growing a graphene layer as ...

Embodiment 2

[0058] This embodiment provides another second electrode layer or even more electrode layers in order to realize some more complex functions on the graphene transistor circuit device (having one electrode layer) obtained in the above-mentioned embodiment 1. In order to provide an additional second electrode layer or more electrode layers, an oxide insulating layer needs to be grown between these electrode layers.

[0059] Specifically, on the graphene transistor circuit device obtained in Example 1, a 50 nm-thick aluminum oxide layer was grown on the electrode layer by the ALD method to serve as an oxide insulating layer. In the formed oxide insulating layer, five through holes were formed. After that, a second electrode layer is formed on the oxide insulating layer by the same process as in Embodiment 1 for forming the source, drain and gate electrode structures. Due to the existence of the oxide insulating layer, the second electrode layer will not be in direct contact with...

Embodiment 3

[0061] The same procedure as described in Example 1 obtained boron nitride / graphene / boron nitride heterojunctions grown on copper foil.

[0062] A layer of PMMA protective glue was spin-coated on the boron nitride / graphene / boron nitride heterojunction grown on the copper foil, the spin-coating speed was 3000 rpm, and the spin-coating time was 2 minutes. After spin coating, bake (KW-4AH-600), the baking temperature is 180℃, and the time is 5 minutes. The baked samples (ie, copper foil / heterojunction / PMMA layer) were horizontally placed in a 0.25 mol / L ammonium persulfate aqueous solution (purchased from Shanghai Shanghai Style) for 3 hours to etch away the copper foil. . After the copper foil is thoroughly etched, the combination of the PMMA layer and the heterojunction (ie, a thin film) will float on the surface of the aqueous solution. The film was pulled out with a PET sheet (purchased from Hefei Kejing) as the base, and the film and the base were attached. Let stand for ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More