Static random access memory

A static random access and memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of SRAM operating voltage is difficult to reduce, low integration, high heat generation, etc., to reduce sub-threshold swing, reduce The effect of heat and process structure is simple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

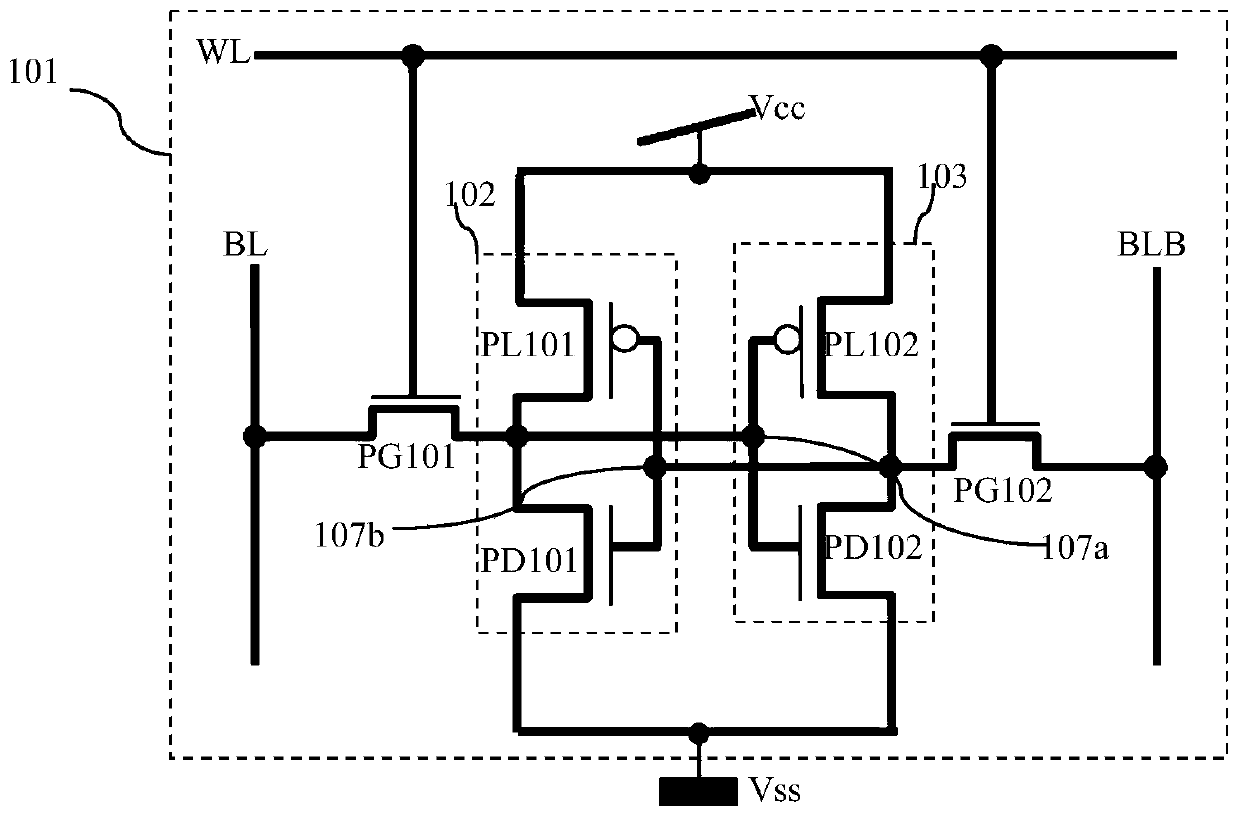

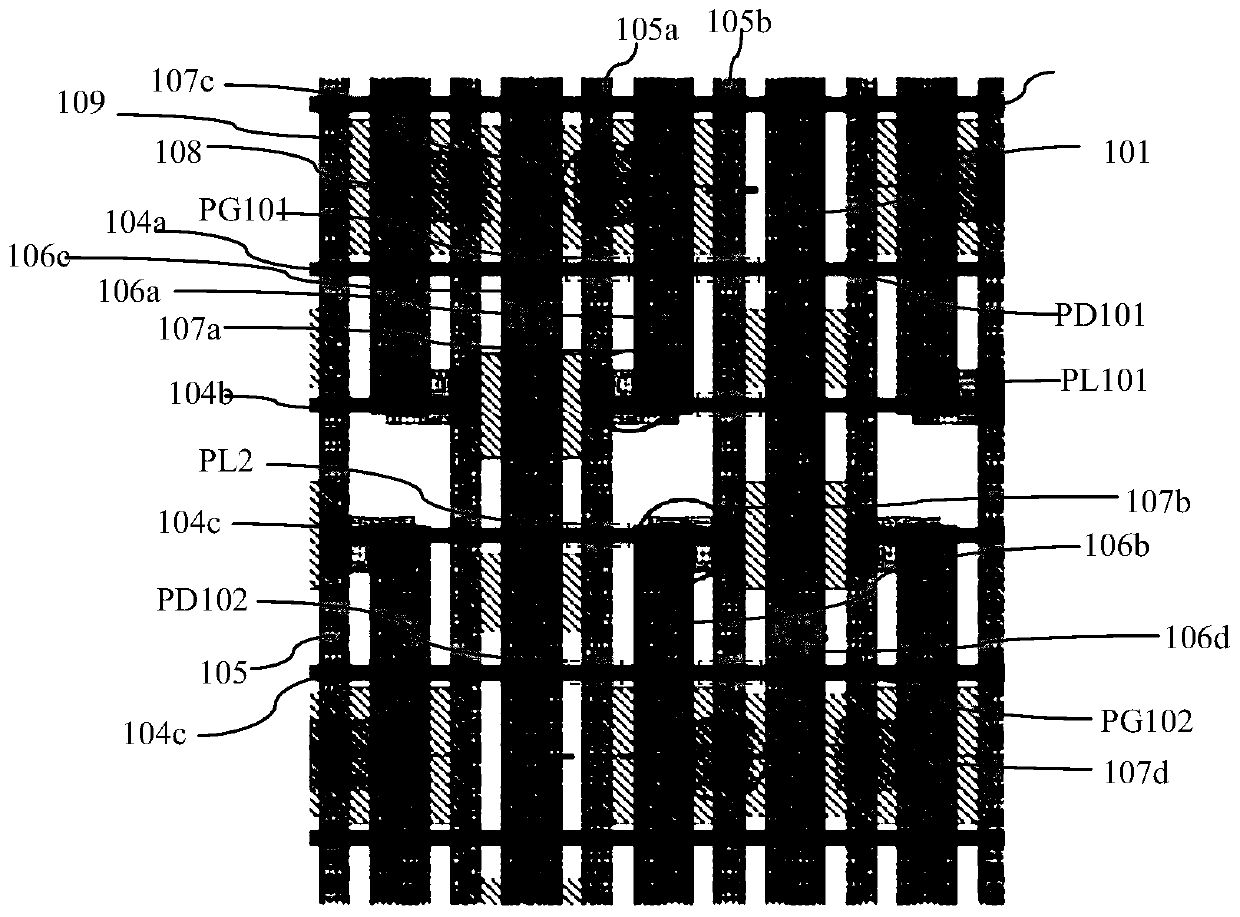

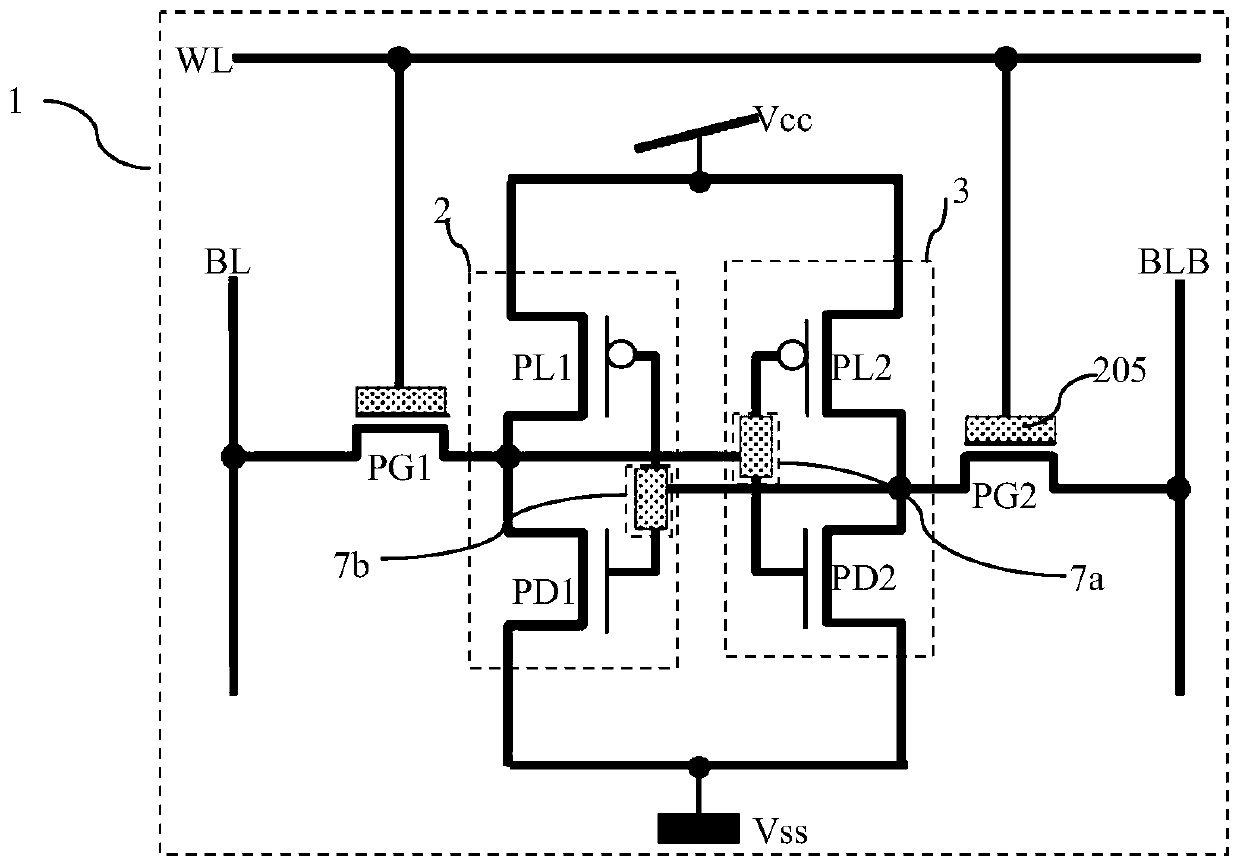

[0079] Such as image 3 Shown is a circuit diagram of the storage unit 1 of the static random access memory of the embodiment of the present invention; Figure 4 Shown is a schematic structural diagram of a fin field effect transistor used in an embodiment of the present invention; Figure 5 What is shown is the layout of the static random access memory of the embodiment of the present invention; the static random access memory of the embodiment of the present invention includes an array structure of a plurality of memory cells arranged in rows and columns.

[0080] Each storage unit 1 includes a first transfer tube PG1, a second transfer tube PG2, a first upper pull tube PL1, a second upper pull tube PL2, a first pull-down tube PD1, and a second pull-down tube PD2; The transmission tube PG1, the second transmission tube PG2, the first pull-down tube PD1, and the second pull-down tube PD2 are all NMOS tubes, and the first pull-up tube PL1 and the second pull-up tube PL2 All are P...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com