A kind of memristor and preparation method thereof

A memristor and low-resistance silicon substrate technology, which is applied in the field of micro-nano processing of semiconductor devices, can solve the problem that the magnitude of change of the high and low resistance of the memristor is not obvious, it is not easy to control the on and off state of the memristor, and the deposited film is not stable. Continuous and other issues, to achieve the effects of obvious on and off states, low cost, and good application benefits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

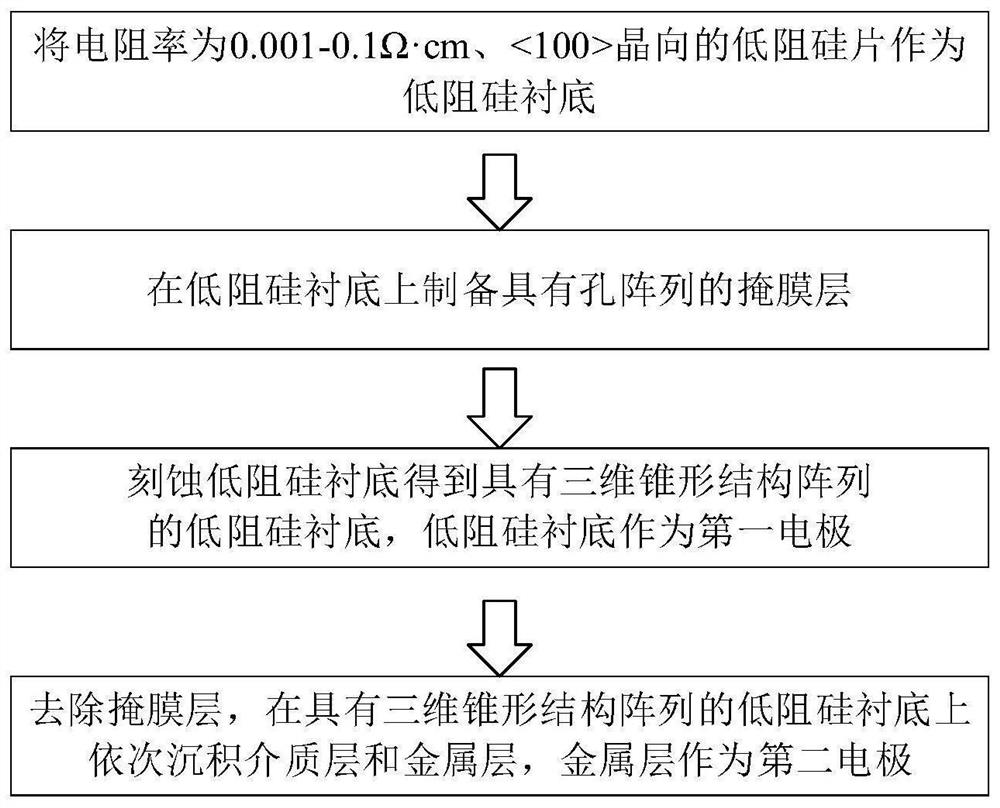

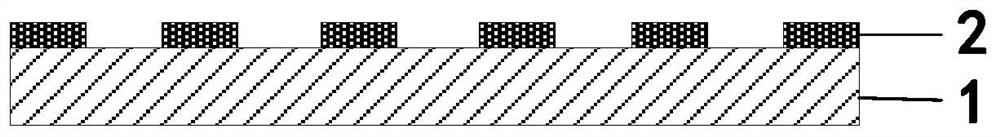

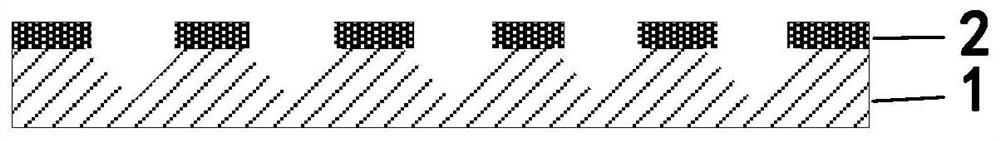

[0040] Such as figure 1 Shown, in embodiment 1, a kind of memristor preparation method specifically comprises the following steps:

[0041] S01: Prepare a dry and polished low-resistance silicon substrate with a resistivity less than 0.01Ω·cm as the low-resistance silicon substrate 1;

[0042] S02: Prepare a hole array patterned mask layer 2 on a low-resistance silicon substrate 1; specifically, an ordered mask layer 2 can be obtained by spin-coating a photoresist on the silicon surface, and exposing and developing by using double-beam interference lithography. Disc array photoresist pattern, and then deposit an etching mask layer 2 (wet etching protective layer) on the sample, specifically: spin-coat SXAR-P3500 / 6 positive photolithography on a low-resistance silicon substrate 1 The ratio of photoresist and diluent is 1:1.5 (volume ratio), uniform glue for 30s at a speed of 4000rpm (rotation per minute), to obtain a glue thickness of 230nm, and use double-beam interference p...

Embodiment 2

[0048] This embodiment has the same inventive concept as Embodiment 1, and provides a method for preparing a memristor. The method specifically includes the following steps:

[0049] S11: Prepare a dry and polished low-resistance silicon substrate with a resistivity of 0.01Ω·cm as the low-resistance silicon substrate 1;

[0050] S12: The cleaned and dried low-resistance silicon substrate 1 is sequentially treated with polydiallyldimethylammonium chloride (PDDA, 4%), deionized water, and blown dry with a nitrogen gun; Sodium xanthate (PSS, 3%), deionized water treatment, nitrogen gun blow-dry, then through amyl xanthate potassium (PAX, 2%) and deionized water treatment, nitrogen gun blow-dry, obtain surface has positive charge 1 sample of low-resistance silicon substrate;

[0051] S13: Drop a solution of colloidal balls with a diameter of 500nm (0.5% by mass fraction of microspheres) on the surface of the low-resistance silicon substrate 1 sample sheet in step S12, the colloi...

Embodiment 3

[0057] This embodiment has the same inventive concept as Embodiment 1 and Embodiment 2, and provides a method for preparing a memristor. The method specifically includes the following steps:

[0058] S21: Prepare a dry and polished low-resistance silicon substrate with a resistivity of 0.01Ω·cm as the low-resistance silicon substrate 1;

[0059] S22: Use 5ml of 800nm PS microspheres with 5% w / v, add 0.15ml of absolute ethanol, and assemble the closely arranged PS microspheres on the silicon wafer by the air-liquid surface assembly method;

[0060] S23: performing reactive ion etching on the sample sheet (performed in an oxygen environment), so that the closely arranged array of PS microspheres becomes a non-closely arranged array. The reaction rate can be adjusted by changing the power and the gas rate. For example, at 80W, 60mTorr gas pressure, the rate of oxygen gas is 120sccm, and the diameter of microspheres with a diameter of 800nm is reduced to 550nm after being etc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More