Field effect transistor and preparation method and application thereof

A technology of field-effect transistors and two-dimensional nanomaterials, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems affecting performance and power consumption value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

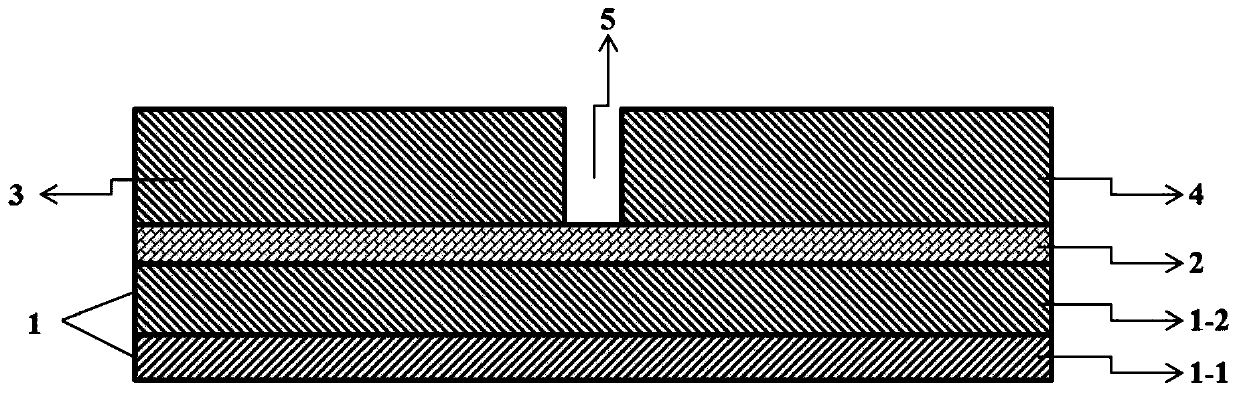

[0101] This embodiment provides a field effect transistor, the schematic cross-section of which is shown in figure 1 1 is an insulating substrate, 1-1 is silicon, 1-2 is silicon oxide, 2 is a two-dimensional nanomaterial layer, 3 is a source electrode, 4 is a drain electrode, and 5 is a conductive channel. The insulating substrate of the field effect transistor is a silicon / silicon oxide substrate, the material of the two-dimensional nano material layer is graphene, and both the source electrode and the drain electrode include a titanium adhesion metal layer and a gold electrode layer.

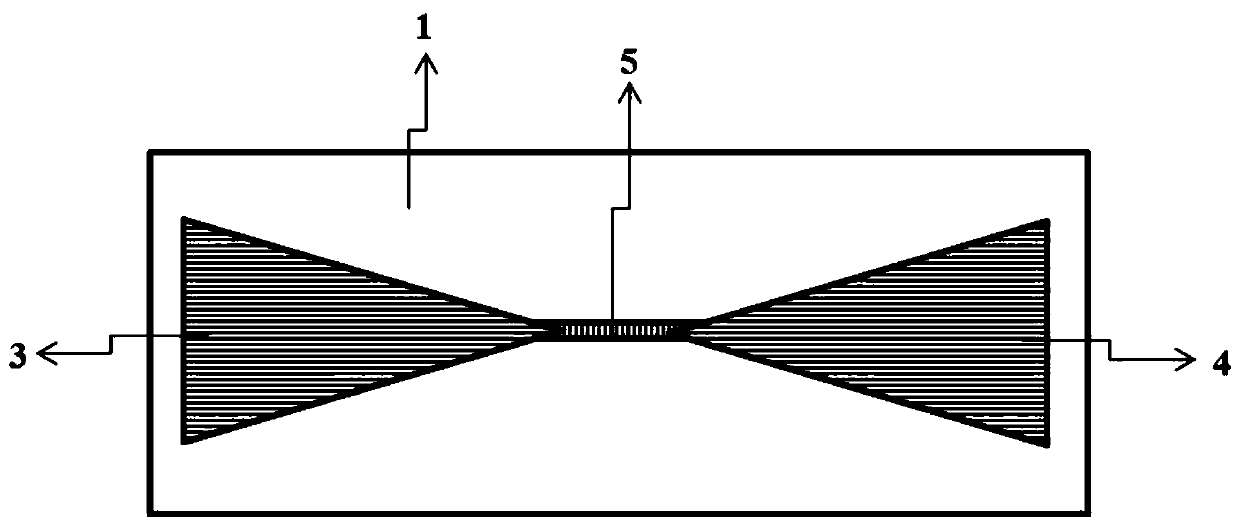

[0102] The top view of the field effect transistor is as figure 2 As shown, wherein, 1 is an insulating substrate, and the upper material is silicon oxide; 3 is a source electrode, and the upper material is gold; 4 is a drain electrode, and the upper material is gold; 5 is a conductive channel, and the upper material is graphene.

[0103] The preparation steps are as follows:

[0104] (1) C...

Embodiment 2

[0114] This embodiment provides a field effect transistor, the schematic cross-section of which is shown in Figure 6 As shown, wherein, 1 is an insulating substrate, 1-1 is silicon, 1-2 is hafnium oxide, 2 is a two-dimensional nanomaterial layer, 6 is a tunneling layer (two-dimensional boron nitride), and 3 is a source electrode, 4 is a drain electrode, and 5 is a conductive channel. The insulating substrate of the field effect transistor is a silicon / hafnium oxide substrate, the material of the two-dimensional nano material layer is molybdenum disulfide, and both the source electrode and the drain electrode include a titanium adhesion metal layer and a scandium electrode layer.

[0115] The preparation steps are as follows:

[0116] (1) Deposit a hafnium oxide insulating layer on heavily doped silicon (resistivity 0.0002Ω·cm): use atomic layer deposition equipment for deposition, the deposition thickness is 15nm, the deposition temperature is 160°C, and the source of hafniu...

Embodiment 3

[0124] This embodiment provides a field effect transistor, the schematic cross-section of which is shown in Figure 7 As shown, among them, 1 is an insulating substrate, 2 is a two-dimensional nanomaterial layer, 6 is a tunneling layer (two-dimensional boron nitride), 3 is a source electrode, 4 is a drain electrode, 5 is a conductive channel, and 7 is a top gate electrode. The insulating substrate of the field effect transistor is a sapphire substrate, the material of the two-dimensional nanomaterial layer is molybdenum disulfide, the source electrode and the drain electrode both include a titanium adhesion metal layer and a scandium electrode layer, and the top gate electrode includes a hafnium oxide insulating layer. layers and metal layers.

[0125] The preparation steps are as follows:

[0126] (1) Cut the sapphire insulating substrate into a size of 1cm×1cm, then ultrasonically clean it with acetone, isopropanol, and deionized water for 15 minutes, and dry it with nitro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More