Novel hybrid integration method

A hybrid integration and new method technology, applied in the field of optical integration, can solve problems such as end face reflection and three-dimensional alignment error, affecting coupling efficiency, affecting device performance, etc., to reduce optical loss and optical reflection, increase alignment tolerance, The effect of efficient optical coupling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

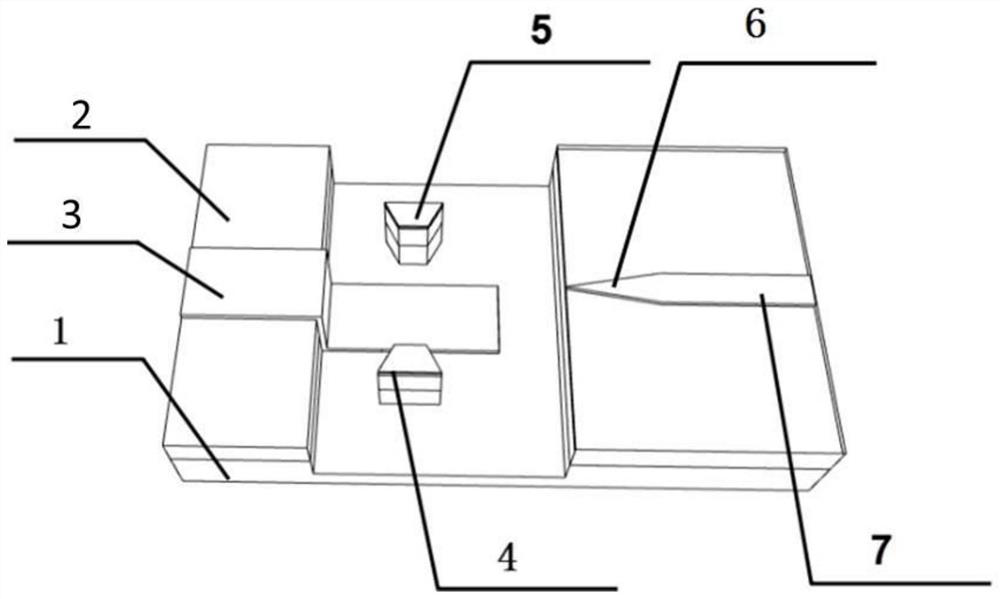

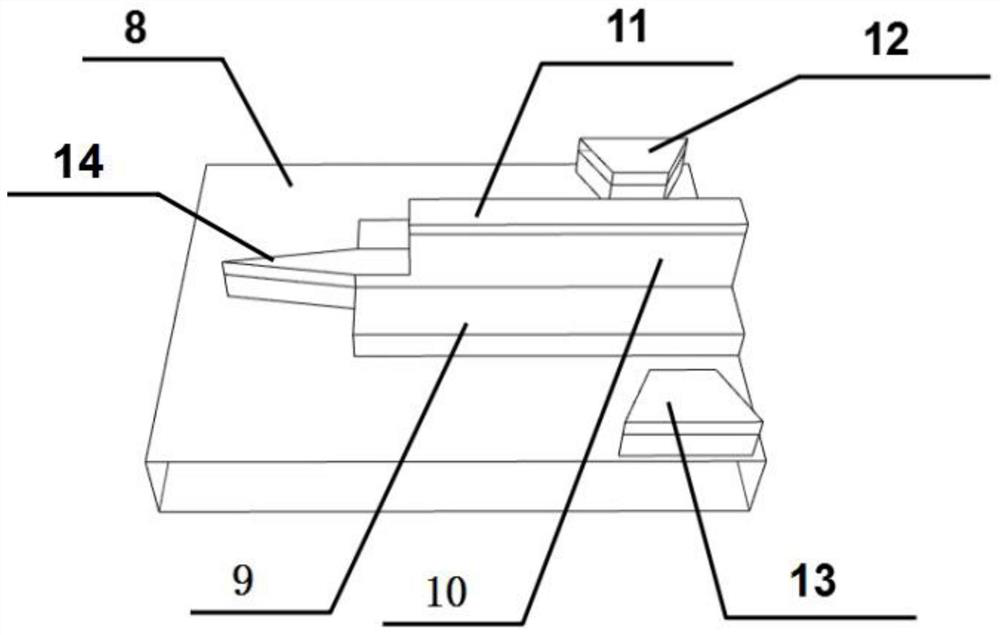

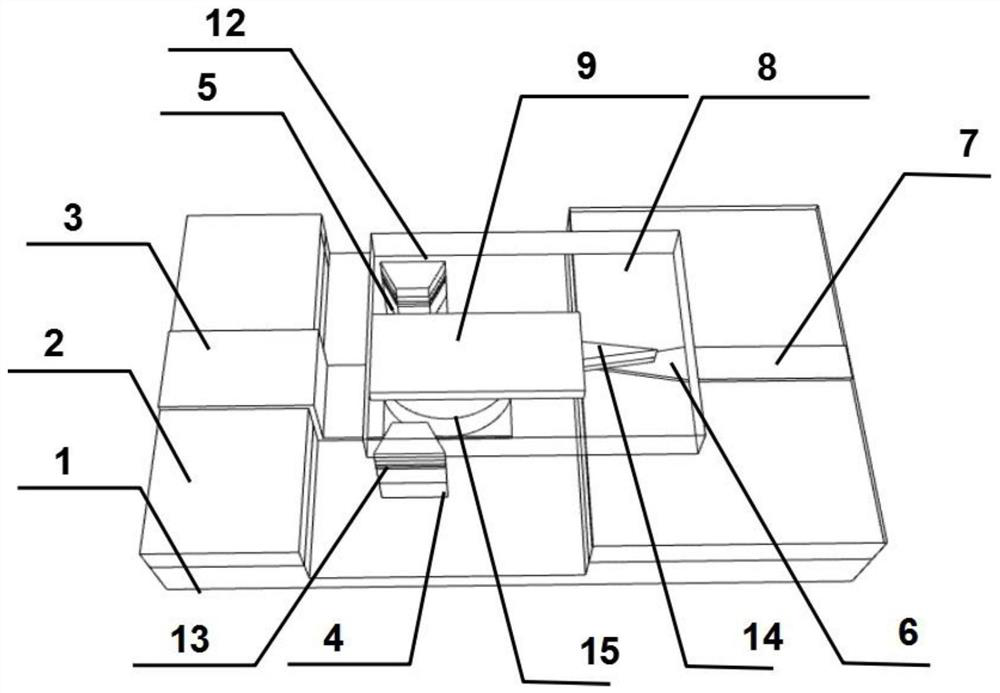

[0035] refer to Figure 1-12 , the present invention provides a new hybrid integration method, comprising the following steps:

[0036] Assembling the motherboard chip; the motherboard chip includes a motherboard chip body, the motherboard chip body is provided with a motherboard chip metal area 3, the motherboard chip vertically supports the assembly and the motherboard chip waveguide area, and the motherboard chip waveguide area contains Coupled motherboard chip coupling waveguide region 6;

[0037] Assembling the daughterboard chip; the daughterboard chip includes a daughterboard chip body, the daughterboard chip body is provided with a daughterboard chip metal area 11, the daughterboard chip vertical support assembly and the daughterboard chip waveguide area, the daughterboard chip waveguide area contains the daughterboard chip coupling waveguide region 14;

[0038] Assemble the integrated chip; the daughter board chip is bonded upside down on the top of the mother board...

Embodiment 2

[0074] According to attached Figure 13 As shown, in the second embodiment, on the basis of the first embodiment, the silicon-based waveguide chip is used as the daughter board chip, and the InP-based chip is used as the optical motherboard chip, which is opposite to the configuration of the mother-daughter chip in the first embodiment. The motherboard chip includes a motherboard chip body and a motherboard chip coupling area, the motherboard chip body includes a motherboard chip heat sink 25, and the top of the motherboard chip heat sink 25 is sequentially provided with an InP-based chip substrate 26, and an InP-based chip core layer 27. InP-based chip cover layer 28, InP-based chip metal area 29; the motherboard chip coupling area includes an InP-based chip coupling waveguide area 30; the motherboard chip is provided with a motherboard chip vertical support assembly, and the motherboard chip vertical support assembly includes But not limited to the fifth supporting member 31...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More