Semiconductor flip-chip package and method for the fabrication thereof

a technology of flip-chip and semiconductors, applied in the field of semiconductor flip-chip configuration, can solve the problems of inability to manufacture tools, failures, and stress build-up in the solder joints, and achieve the effect of disassembly from the substra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

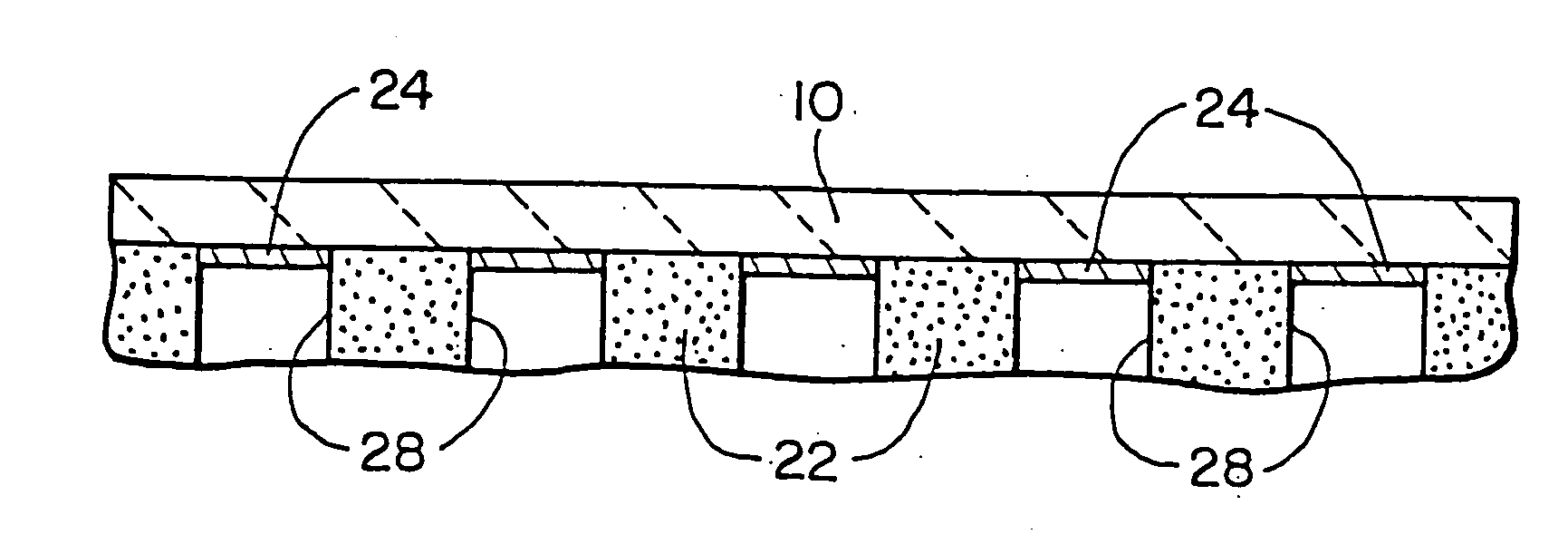

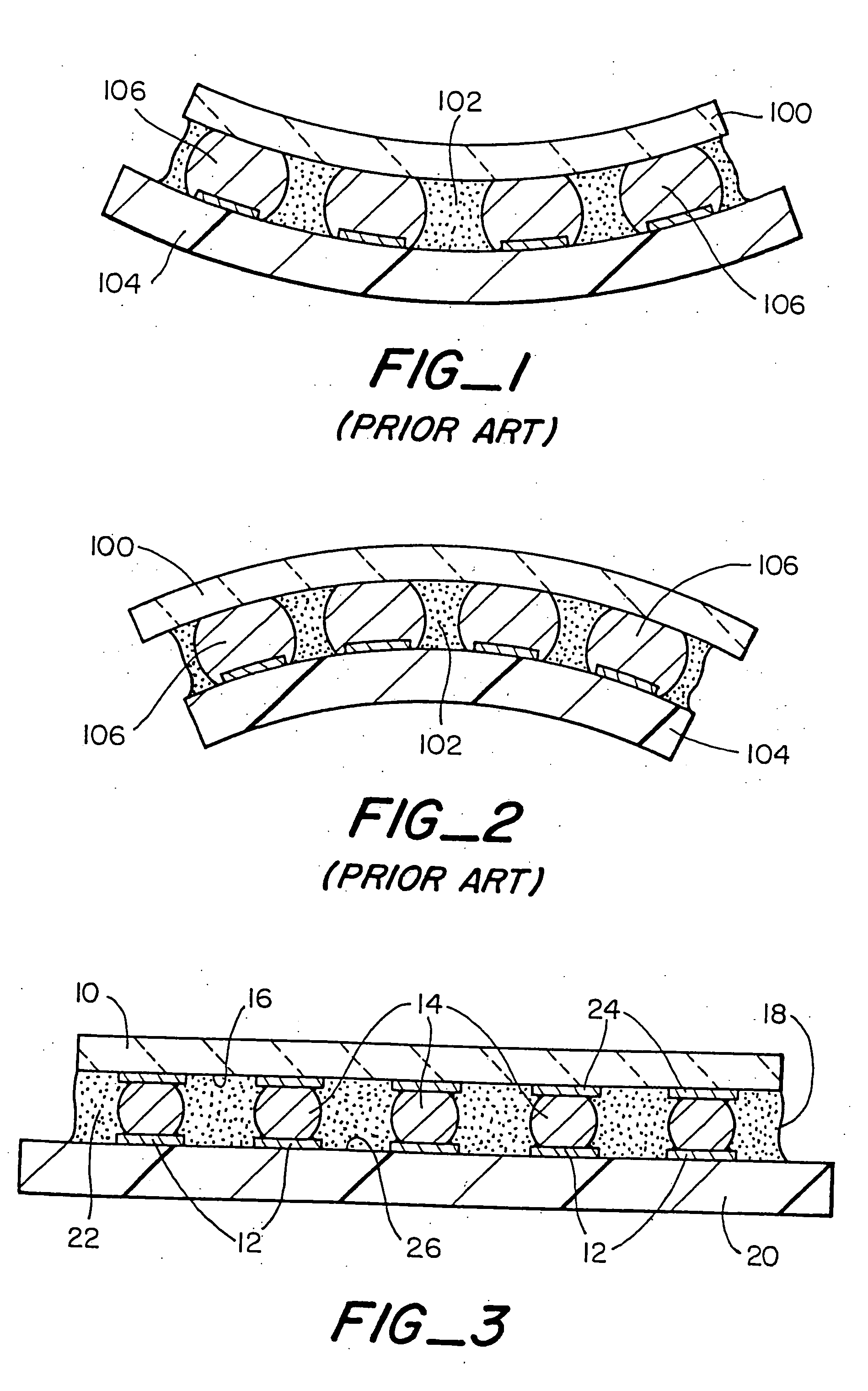

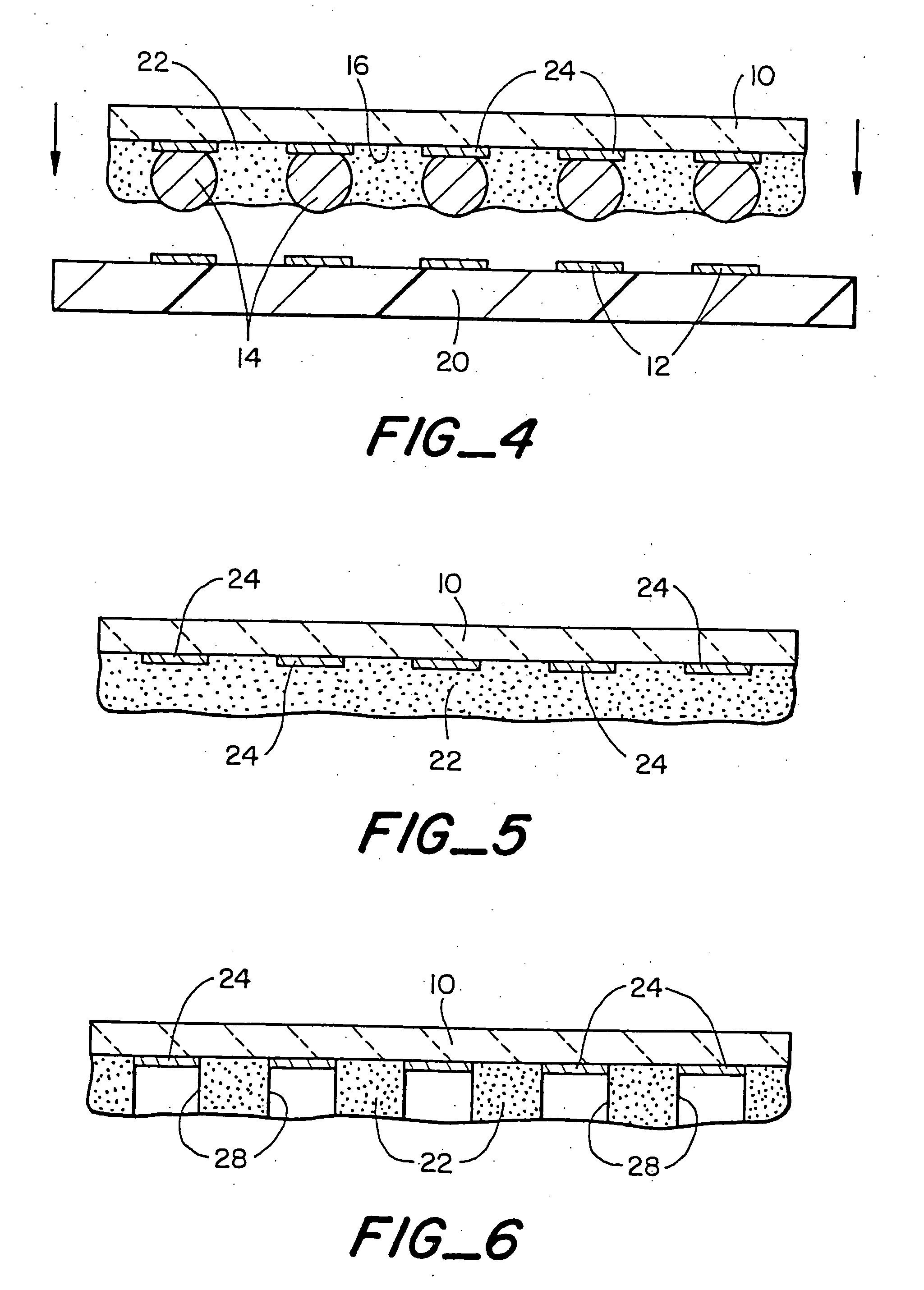

Image

Examples

example 1

Preparation of tris (maleic acid) glycerol monoester, a non-amine fluxing agent with the structure

[0130]

[0131] Three moles of maleic anhydride (294 grams) were heated in a flask at 80° C. until fully melted at which time one mole of glycerol (92 grams) was slowly added thereto. The composition was constantly stirred and maintained at 80° C. for three hours. The temperature was then raised to 110° C. for one hour to complete the reaction. Thereafter the product was allowed to cool to room temperature. The reactants were kept in a nitrogen atmosphere throughout. Monitoring the reaction on a Fourier-transform infrared spectrometer, the OH vibrational band at 3,400-3,500 cm−1 of the glycerol was observed to become minimized while an ester vibration band at 1,710-1,740 cm−1 appeared and maximized, indicating complete reaction of the glycerol and the anhydride. This fluxing agent is characterized by its low viscosity and high flux activity.

example 2

Preparation of tris (maleic acid) triethanolamine monoester: an amine fluxing agent, with the structure

[0132]

[0133] Three moles of maleic anhydride (294 grams) were heated in a flask at 80° C. until fully melted at which time one mole of triethanolamine (149 grams) was slowly added thereto over the course of one hour, so that gelation did not occur. The composition was constantly stirred and maintained at 80° C. To ensure that the reaction went to completion, the product was maintained at 80° C. with constant stirring for an additional hour. The reactants were kept in a nitrogen atmosphere throughout. Then the product was allowed to cool to room temperature. Monitoring the reaction on a Fourier-transform infrared spectrometer, the OH vibrational band at 3,400-3,500 cm−1 of the triethanolamine was observed to become minimized while an ester vibration band at 1,710-1,740 cm−1 appeared and maximized, indicating complete reaction of the triethanolamine and the anhydride.

[0134] This fl...

example 3

Preparation of methyl meso-erythritol tetramaleic acid monoester

[0135] 39 g maleic anhydride was heated to 80° C. until all the maleic anhydride was melted before 12.2 g of meso-erythritol was added under mechanical stirring. The temperature was then raised to 130° C. for 30 minutes followed by cooling down to 80˜90° C. for 2 hours. The reaction is:

PUM

| Property | Measurement | Unit |

|---|---|---|

| Tg | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| temperatures | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More