Mixed technology integrated device comprising complementary LDMOS power transistors, CMOS and vertical PNP integrated structures having an enhanced ability to withstand a relatively high supply voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

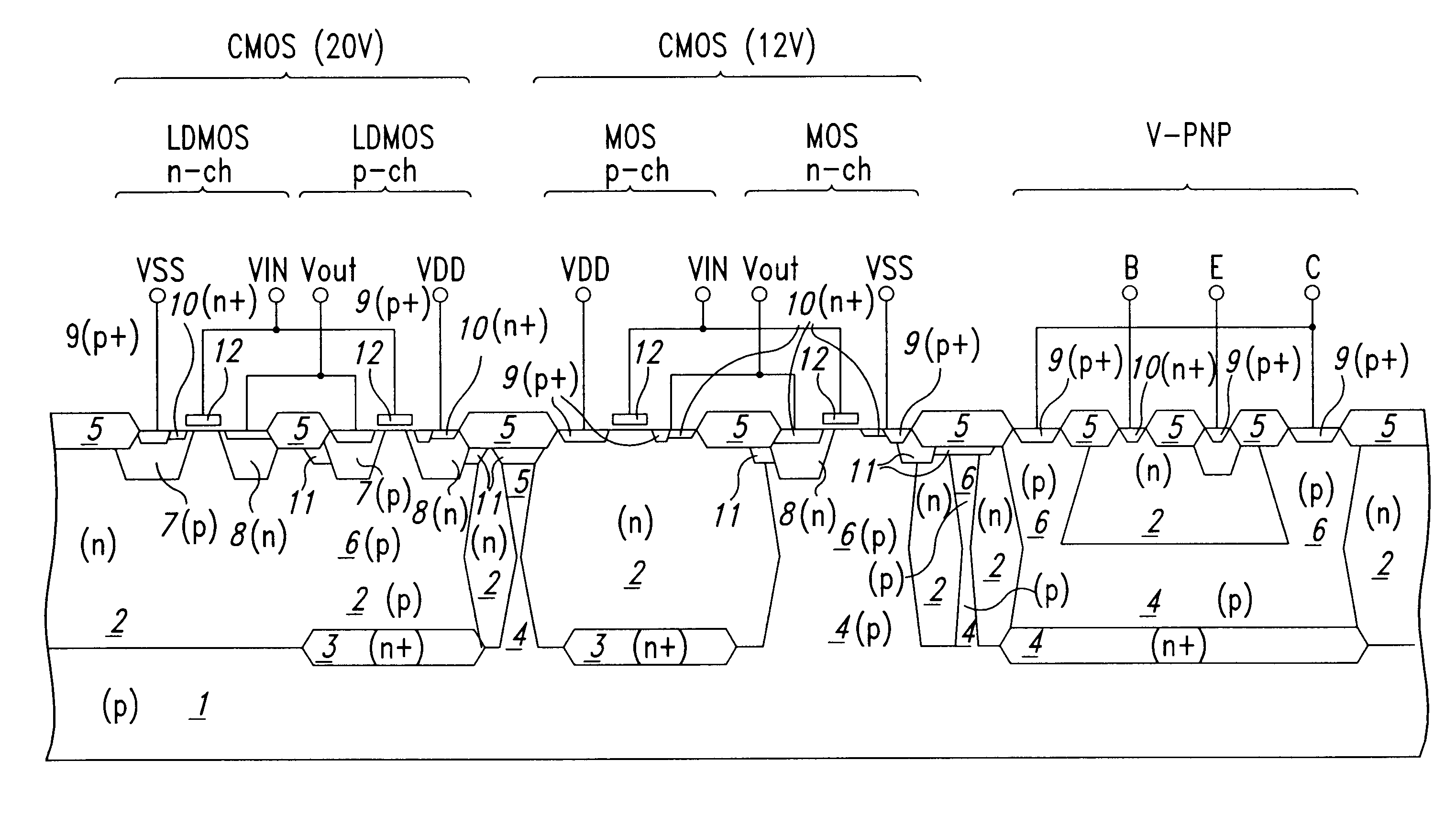

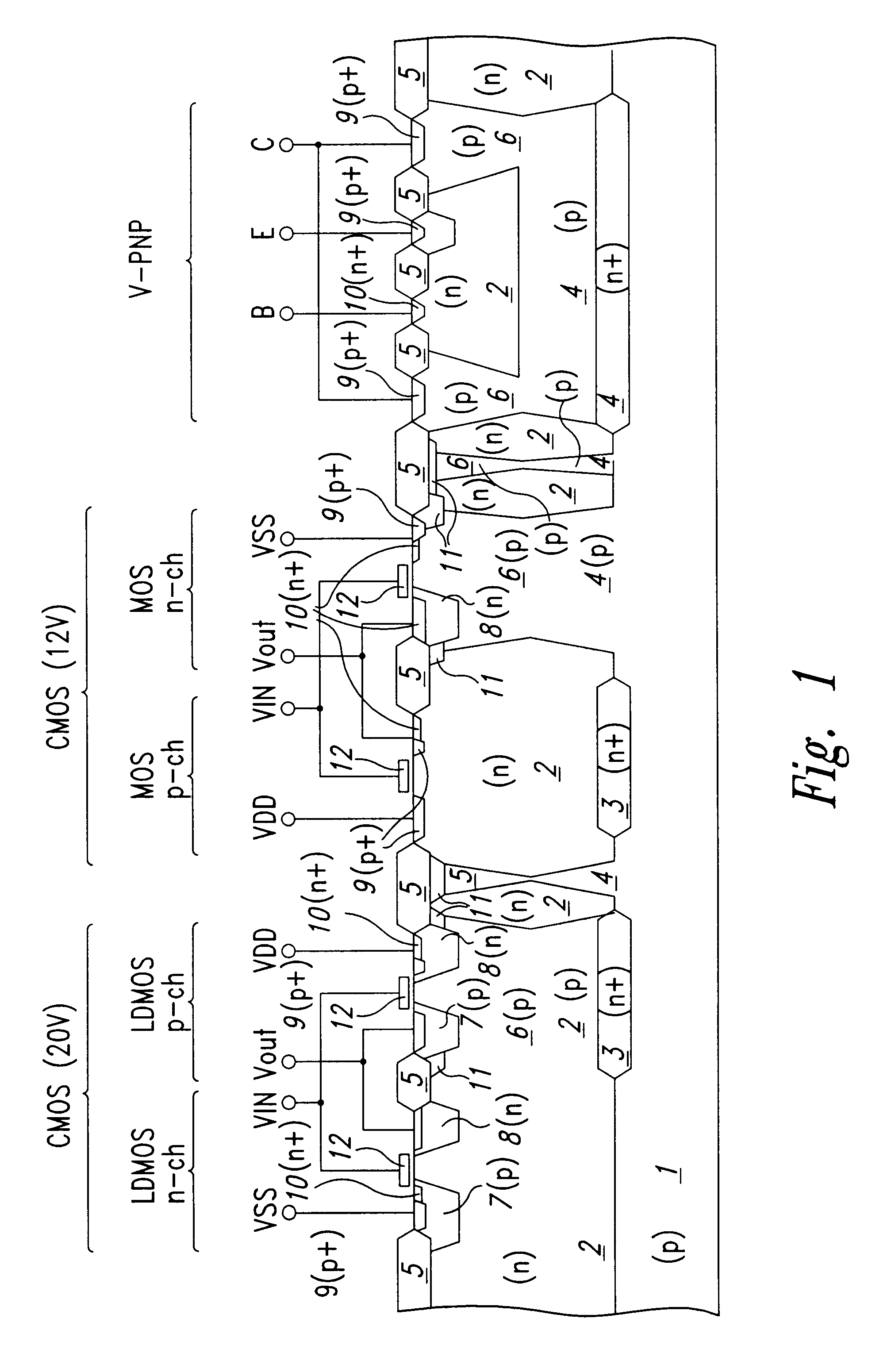

An hypothetical partial cross section of an integrated "smart power" type integrated device, wherein it is relatively easy to put in evidence, though in a schematic way, the aspects of the invention, is shown in FIG. 1. The depicted cross section does not include VDMOS power transistors, which may be easily imagined present in a different zone of the integrated device from the zone shown in the partial cross section of the figure, wherein two different CMOS structures are depicted, a first structure formed by an n-channel and a p-channel LDMOS transistor and a second structure formed by a p-channel and by an n-channel MOS transistor, and the structure of an isolated collector, vertical PNP bipolar transistor.

The device comprises a p-type silicon substrate 1 on which an epitaxial n-type silicon layer 2 has been grown after doping with arsenic and / or with boron certain areas defined on the surface of the monocrystalline silicon substrate 1 in order to form the n.sup.+ buried layers 3 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More