Etching method

A main etching and over-etching technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of uneven etching lines, offset or weaken the PR-loading effect, and no micro-loading effect, etc. achieve the effect of improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Generally, the gate structure of a Dynamic Random-Access Memory (DRAM) is a composite gate composed of polysilicon and metal silicide, for example, a stacked gate with tungsten silicide as the upper layer and doped polysilicon as the lower layer. In this embodiment, the etching method will be described in detail with the background of the forming process of the gate structure of the DRAM.

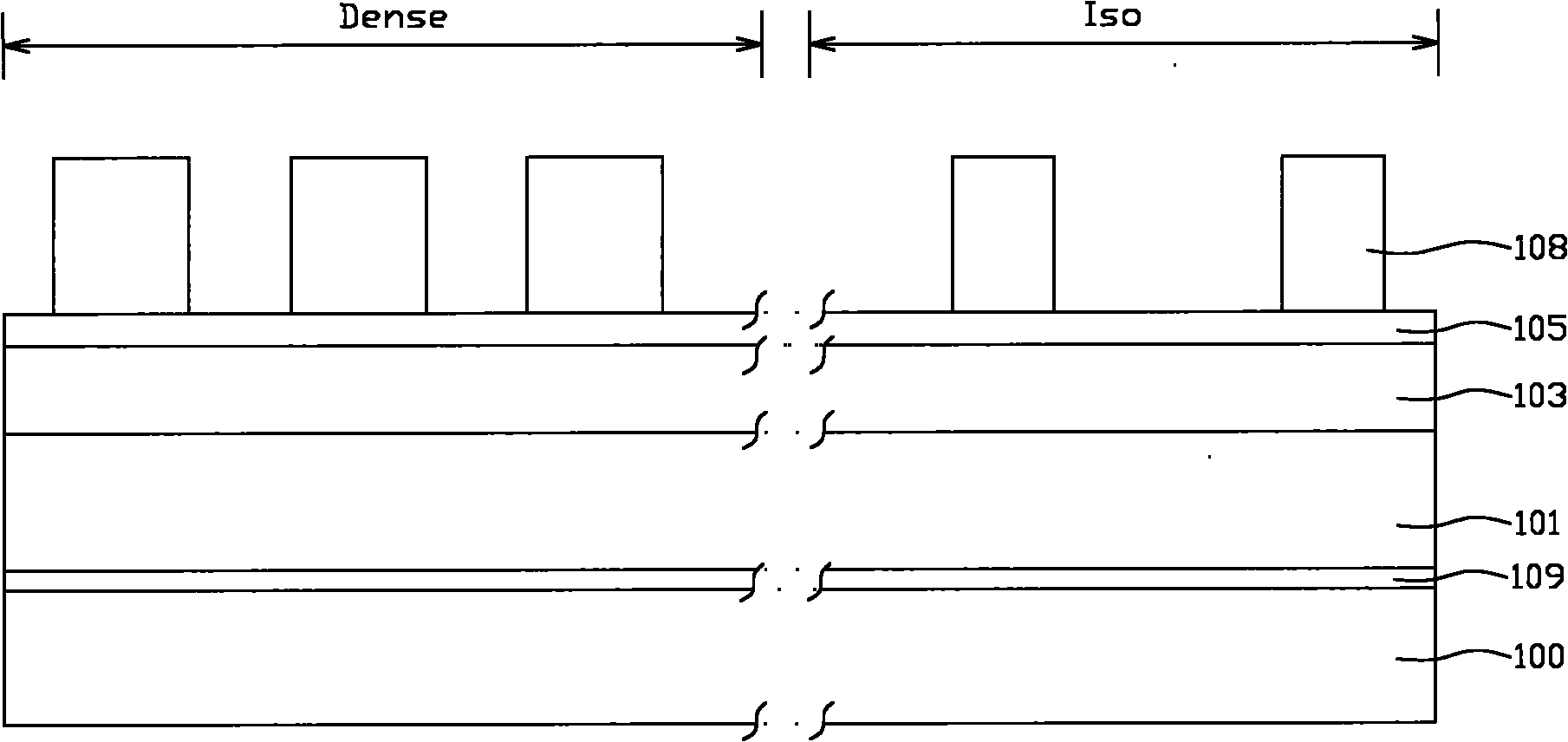

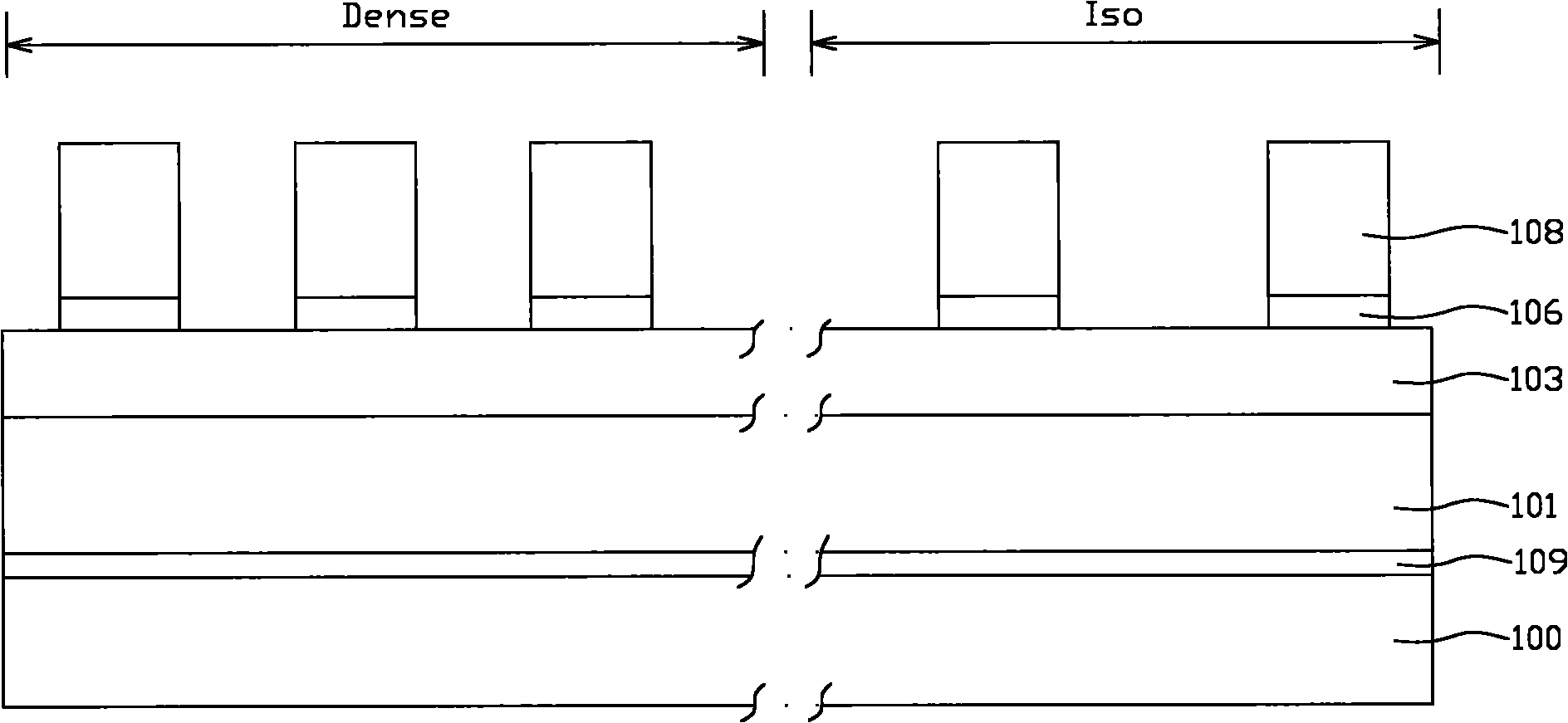

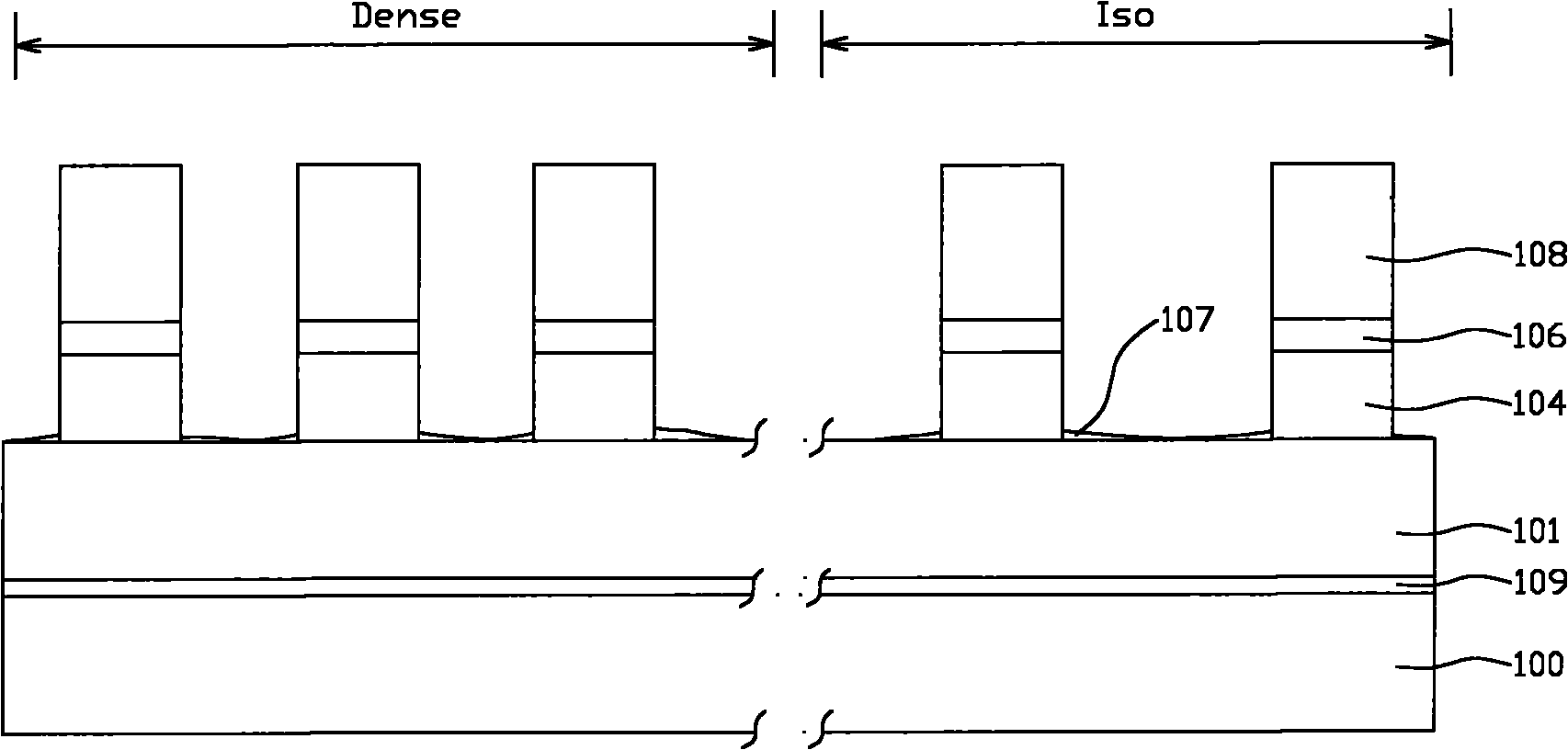

[0045] Figure 1 to Figure 5 It is a schematic diagram of the etching method described in this implementation, Figure 6 It is a flowchart of the etching method.

[0046] The etching method includes:

[0047] refer to figure 1 As shown, as in step S1, a semiconductor wafer 100 is provided, and the semiconductor wafer 100 may include elemental semiconductors, such as silicon or silicon germanium (SiGe) of single crystal, polycrystalline or amorphous structure, and may also include compound semiconductors, such as silicon carbide , indium antimonide, lead telluride, indium arsenide...

Embodiment 2

[0068] Different from DRAM, usually the gate structure of metal oxide semiconductor (Metal Oxide Semiconductor, MOS) device is only one layer of polysilicon gate. The etching method described above will be described.

[0069] Figure 9 to Figure 12 It is a schematic diagram of the etching method described in this implementation.

[0070] The etching method includes:

[0071] refer to figure 1 As shown, a semiconductor wafer 200 is provided, and the semiconductor wafer 200 has active regions (not shown) for forming source and drain electrodes of MOS devices, and shallow regions for isolating and insulating different active regions. Trench isolation structure (not shown in the figure), the composition of the semiconductor wafer 200 is the same as that of Embodiment 1, and may include elemental semiconductors or compound semiconductors, which will not be listed one by one;

[0072] The exposed surface of the semiconductor wafer 200 is covered with a gate dielectric layer 209...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More