Patents

Literature

67results about How to "Uniform line width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

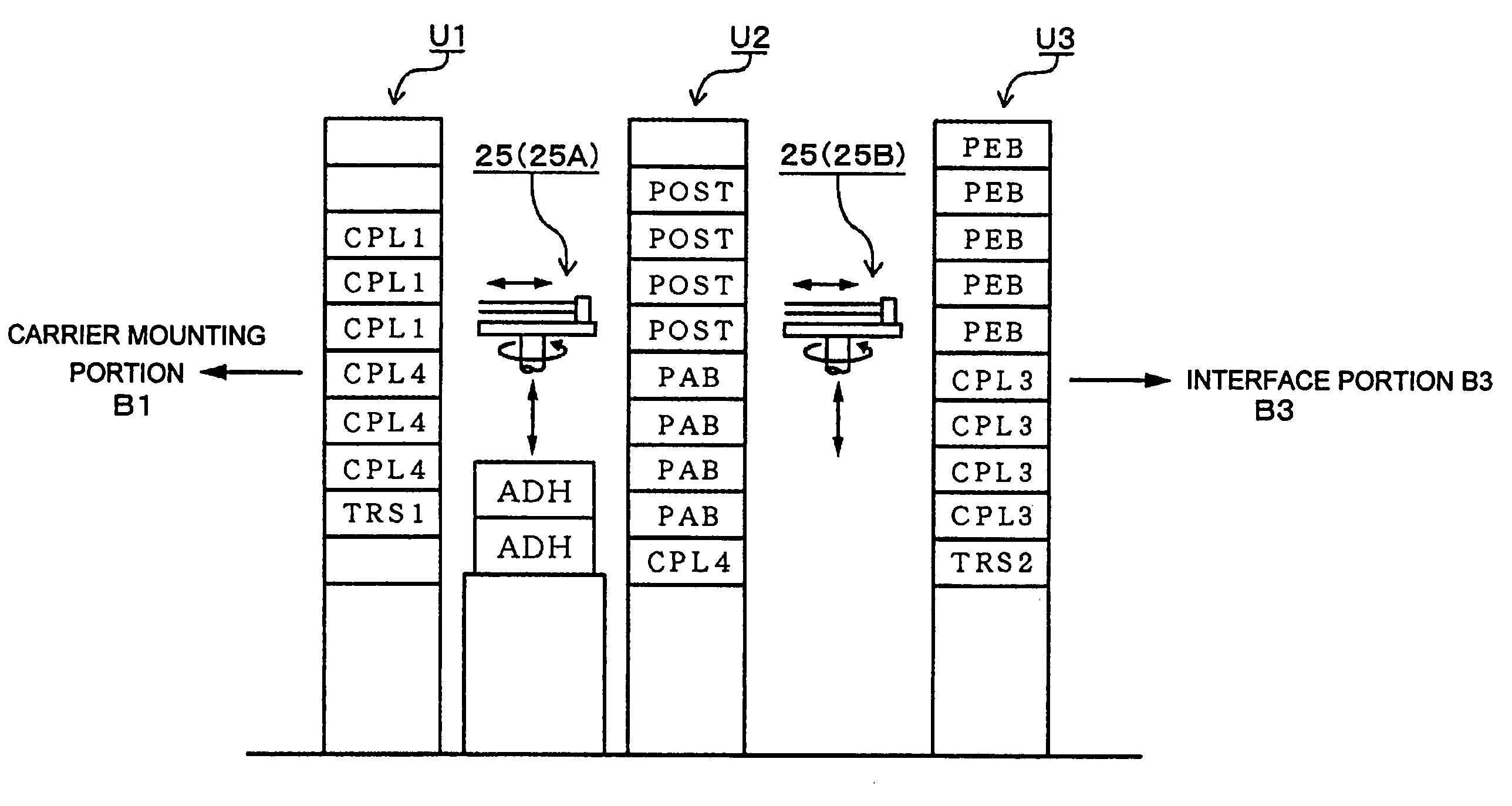

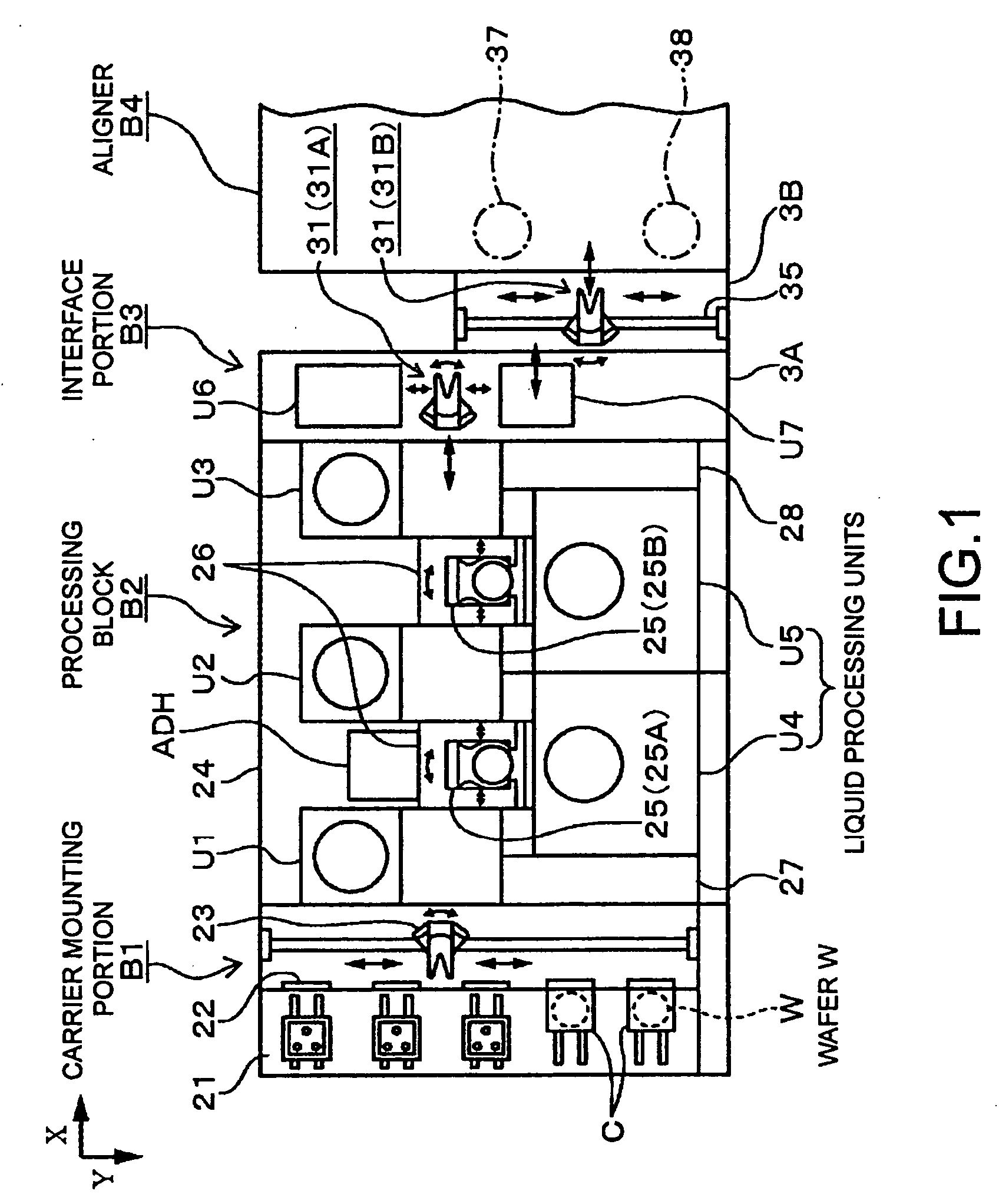

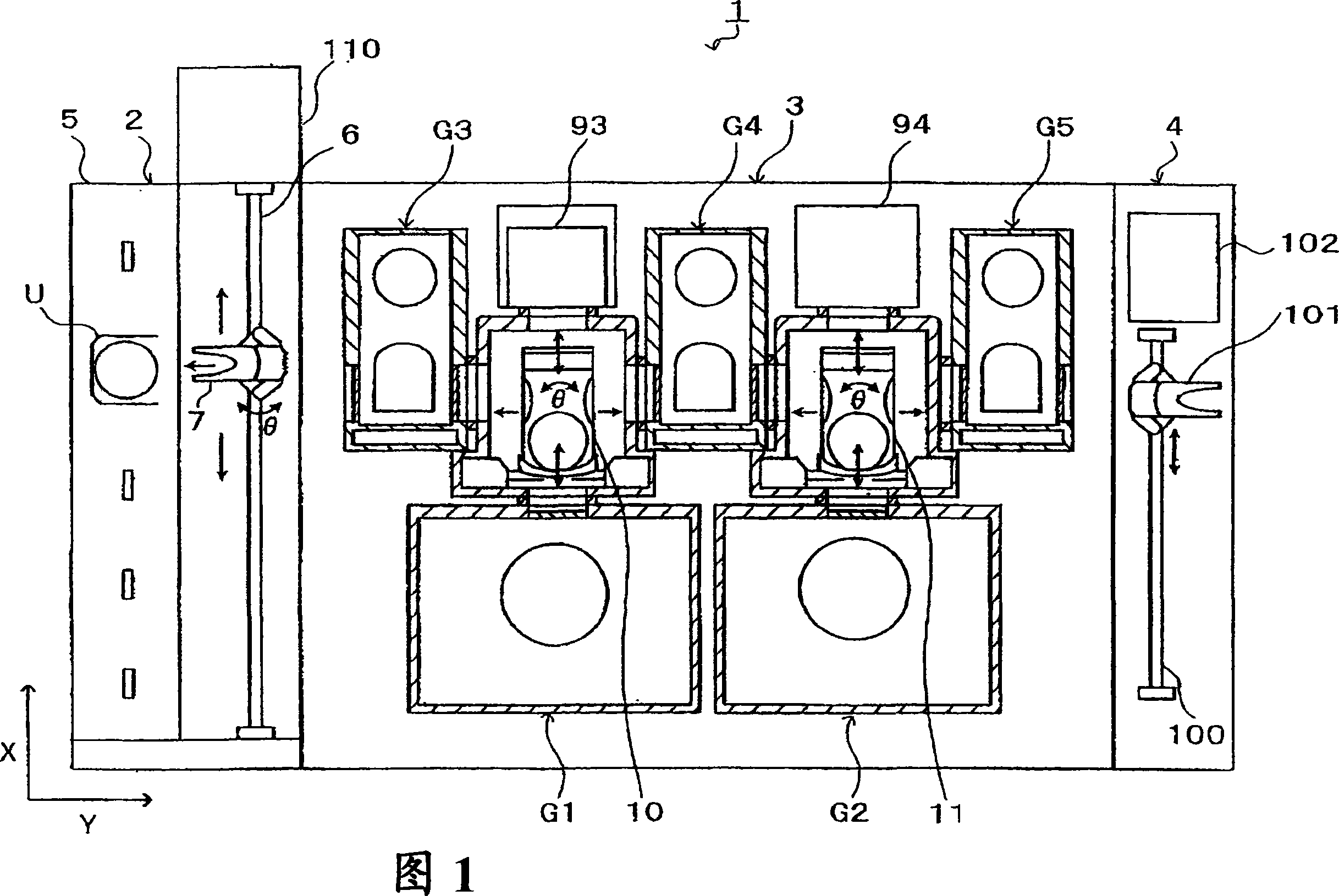

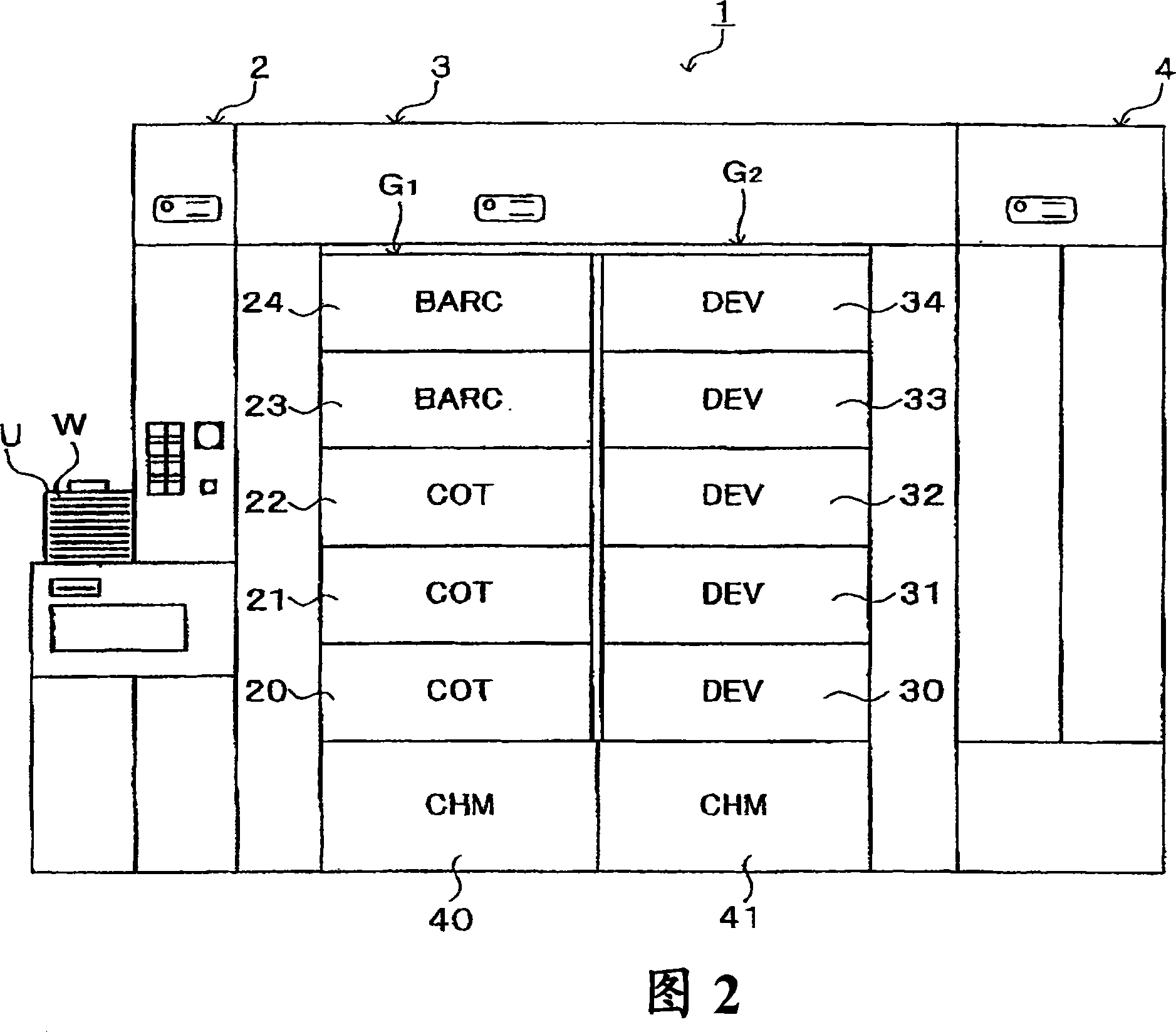

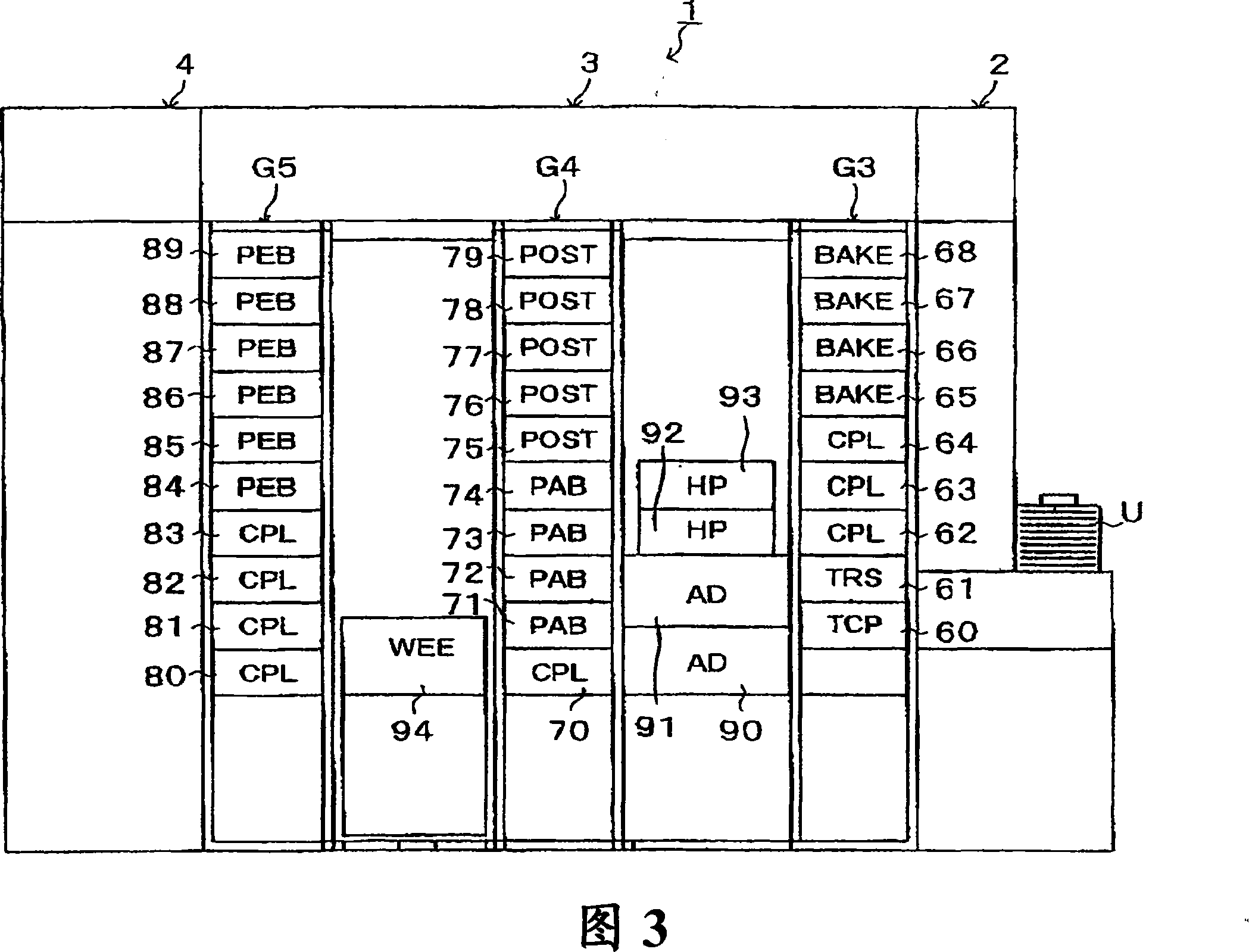

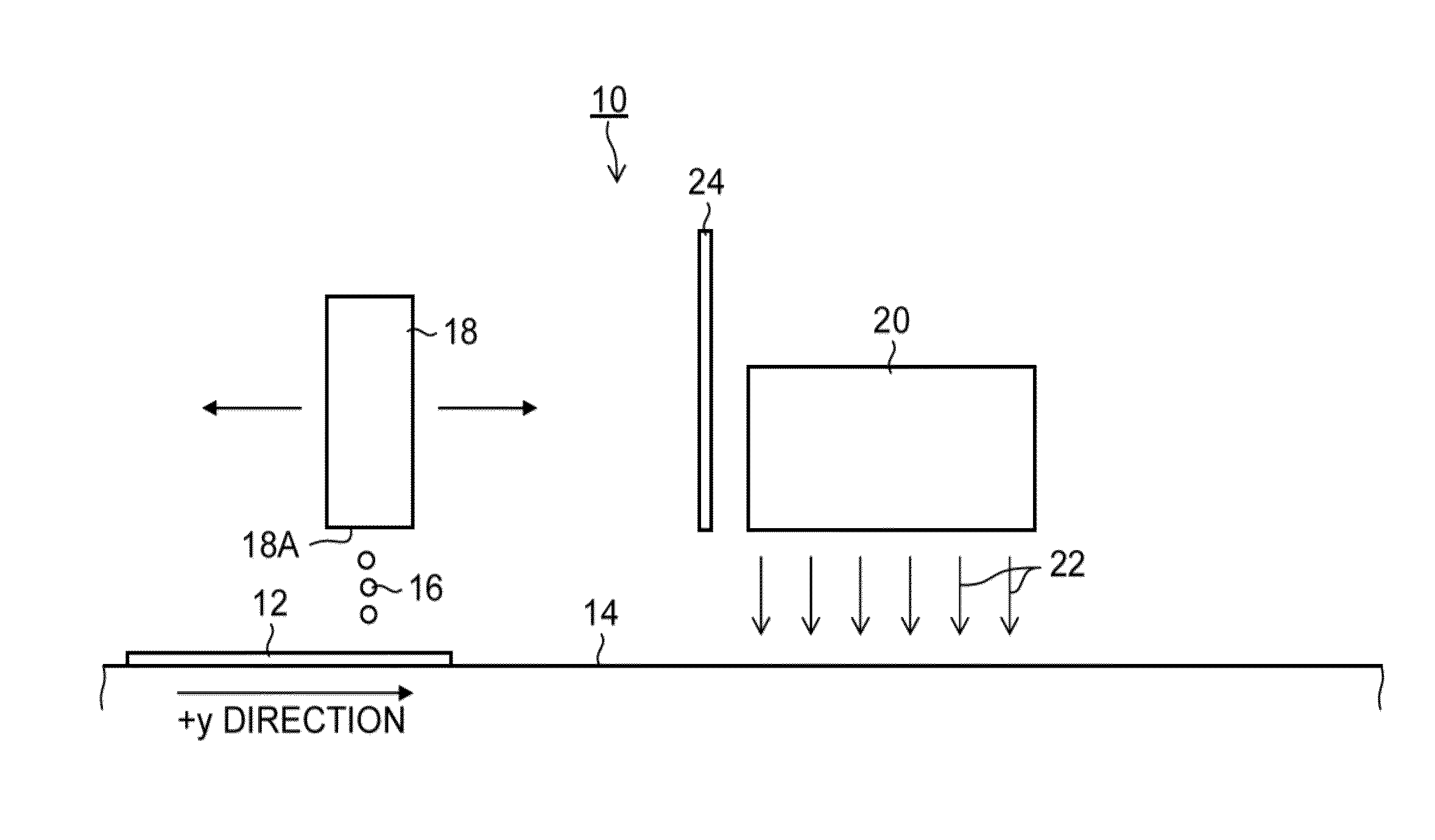

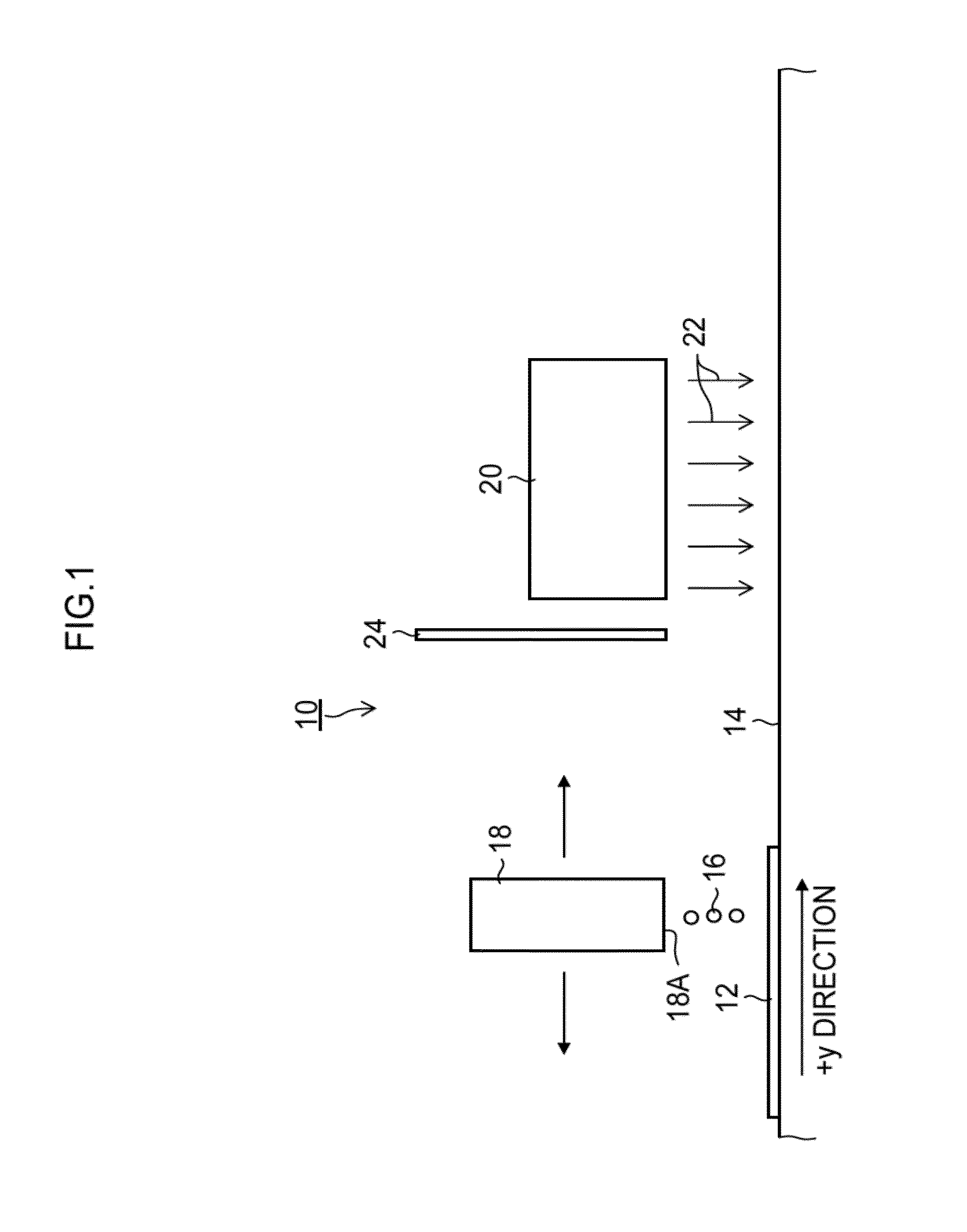

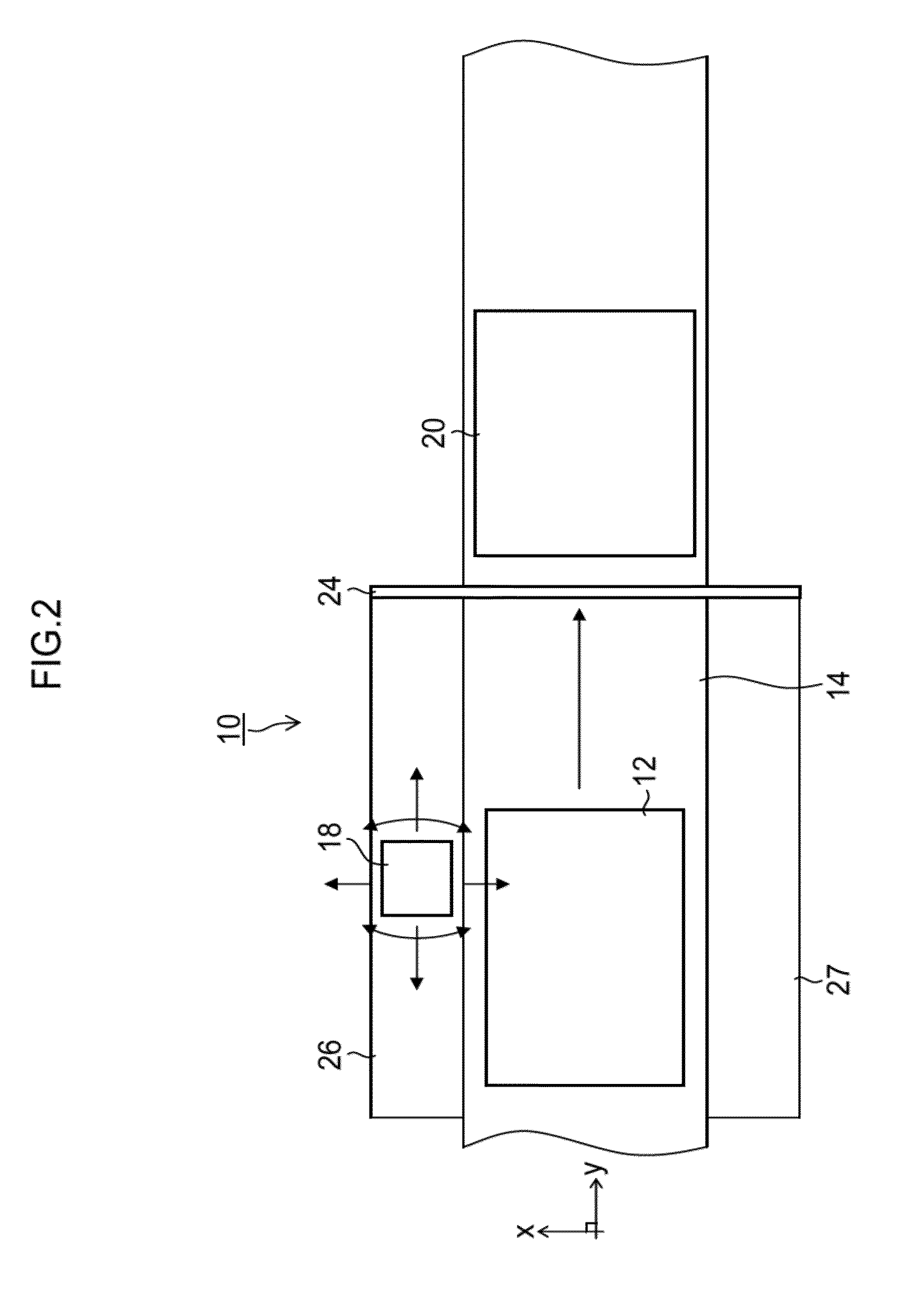

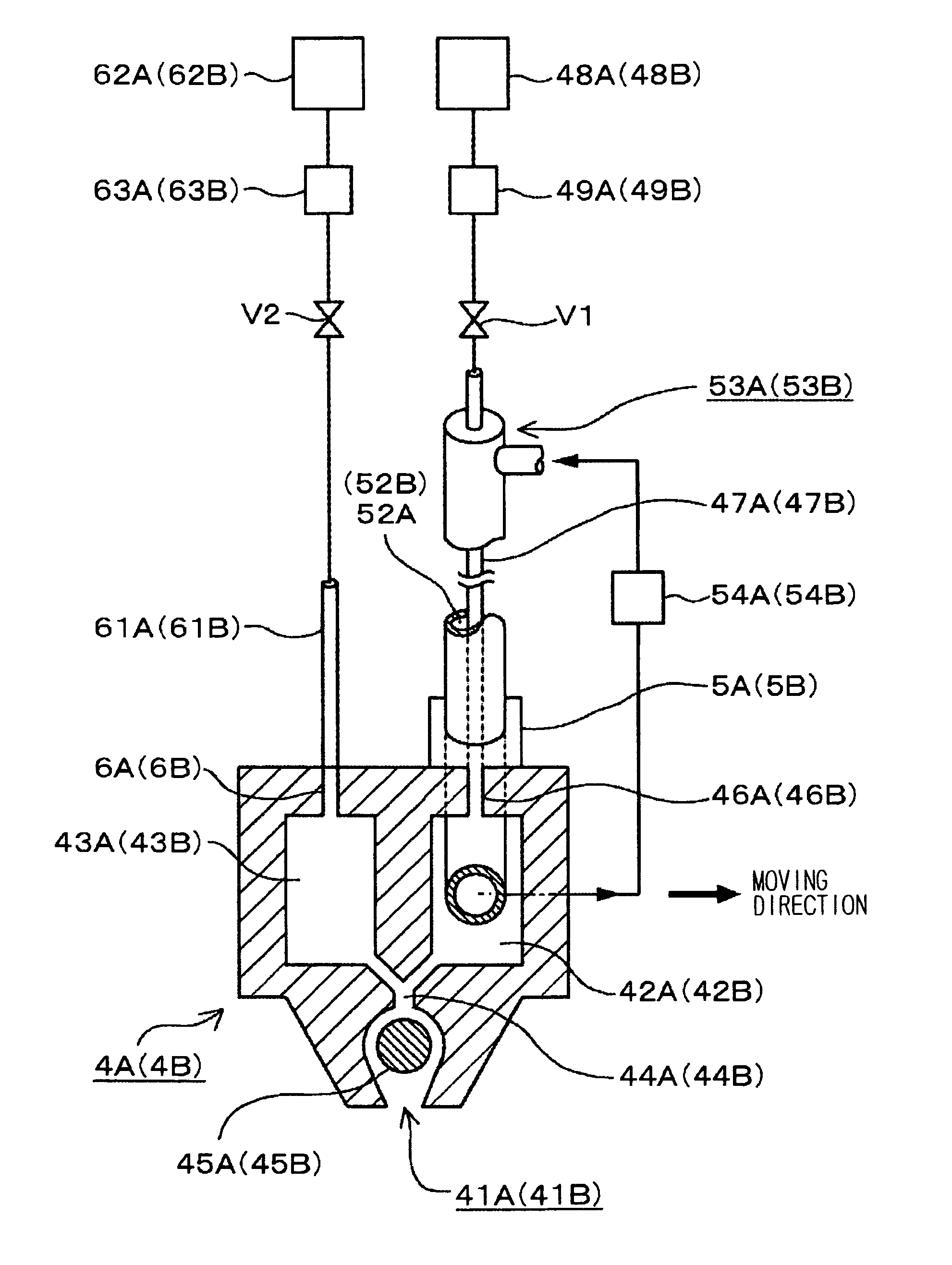

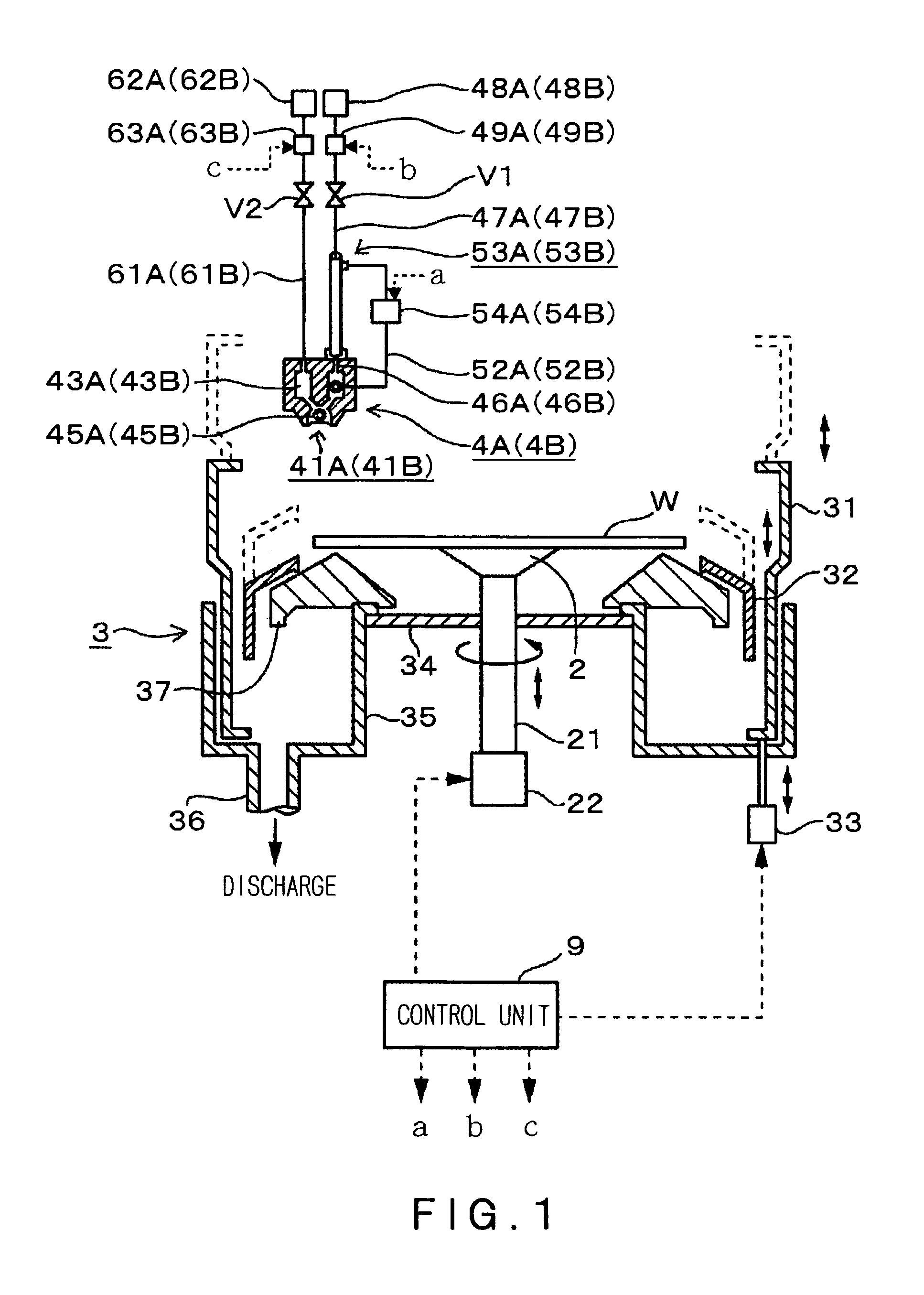

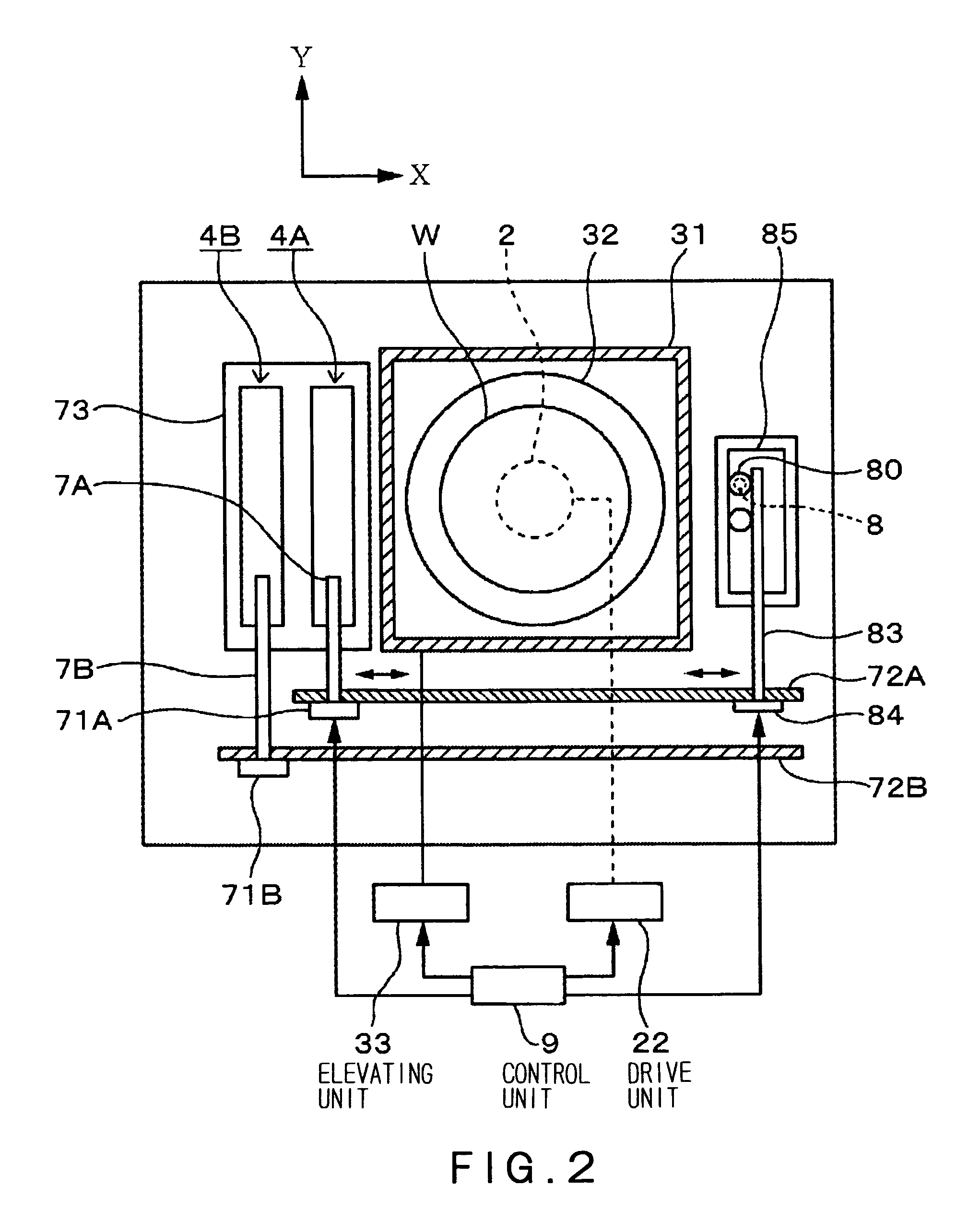

Substrate processing system, coating/developing apparatus, and substrate processing apparatus

InactiveUS7379785B2Substrates can be prevented from beingQuick uninstallSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusResistComputer module

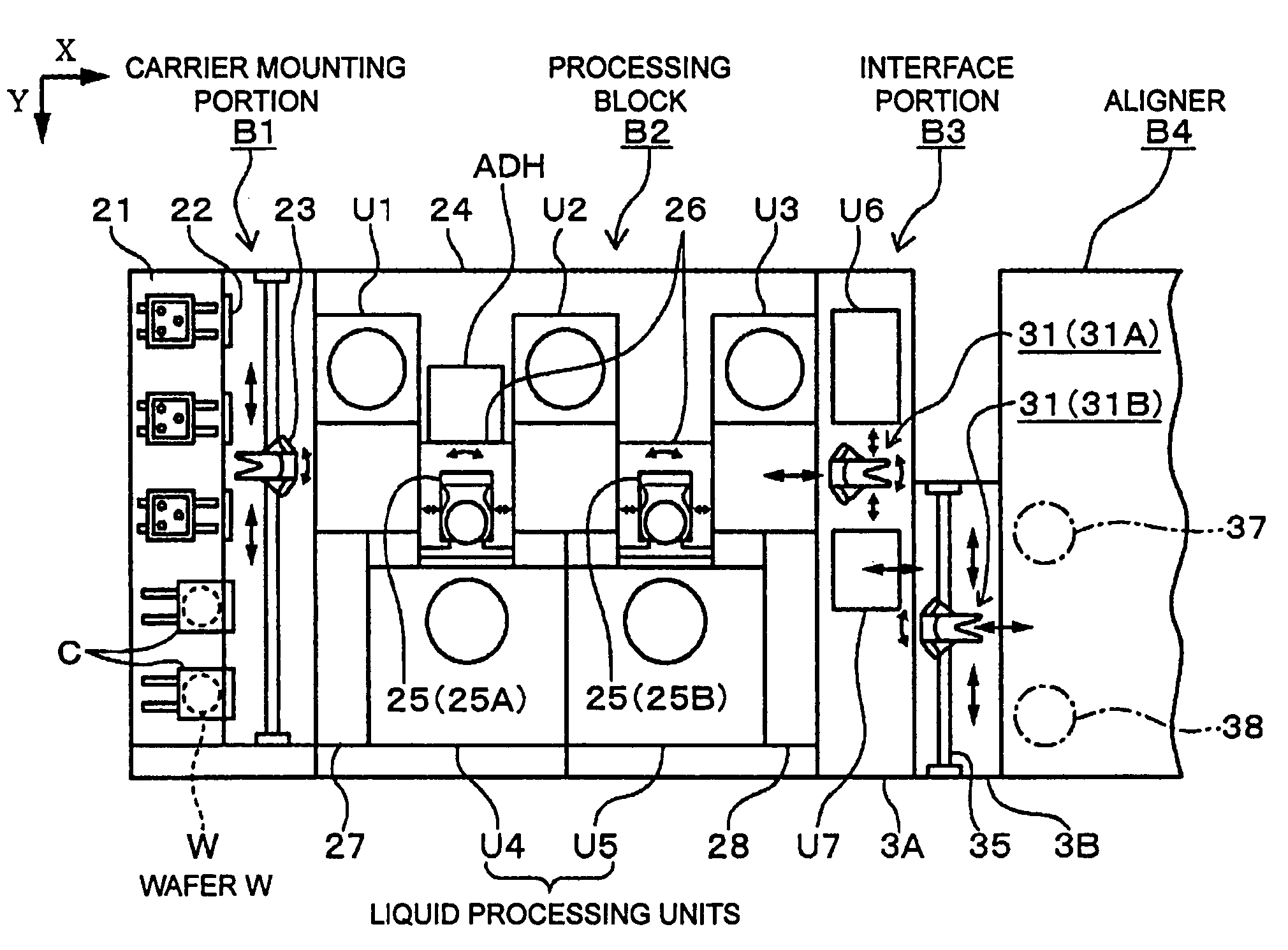

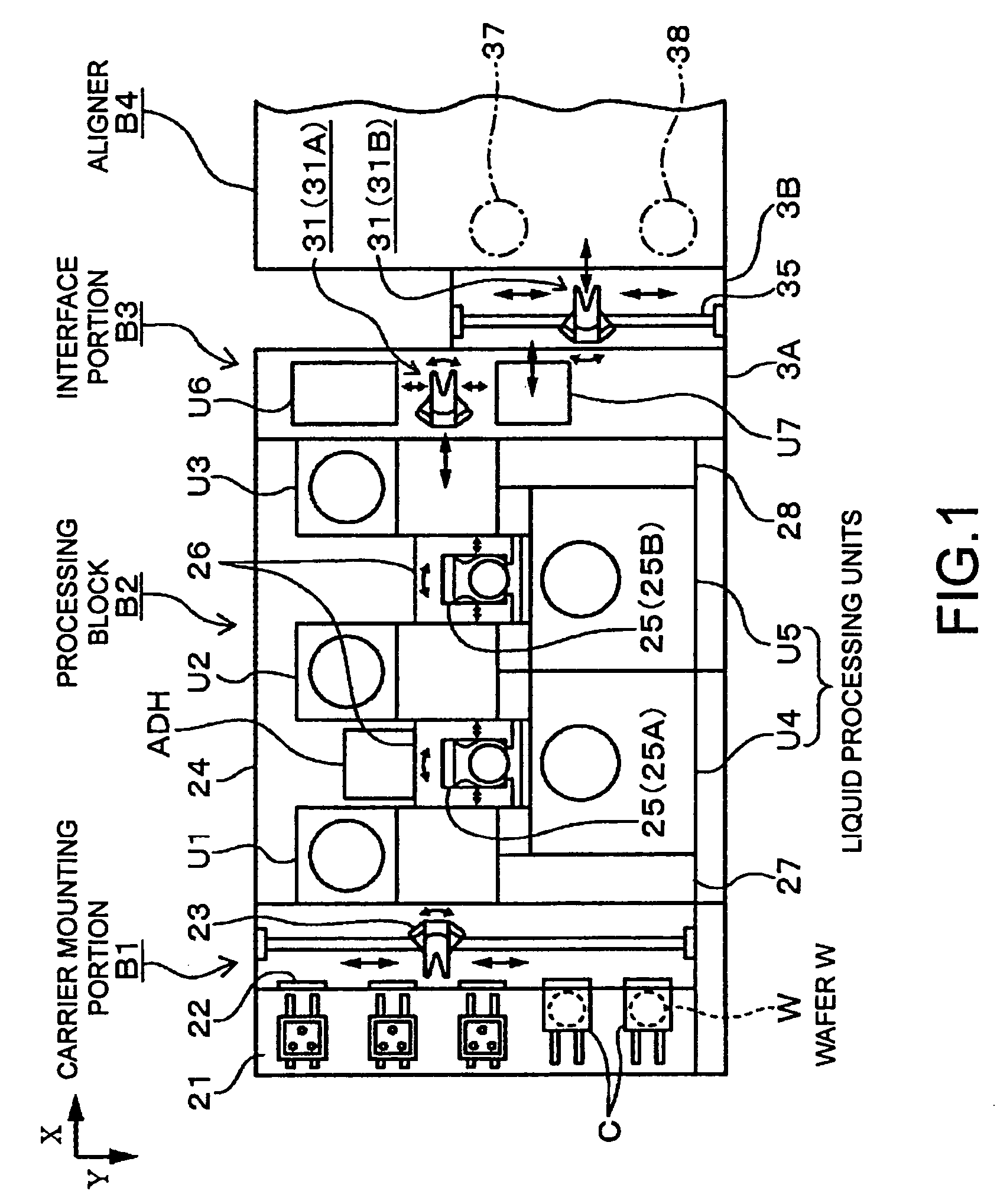

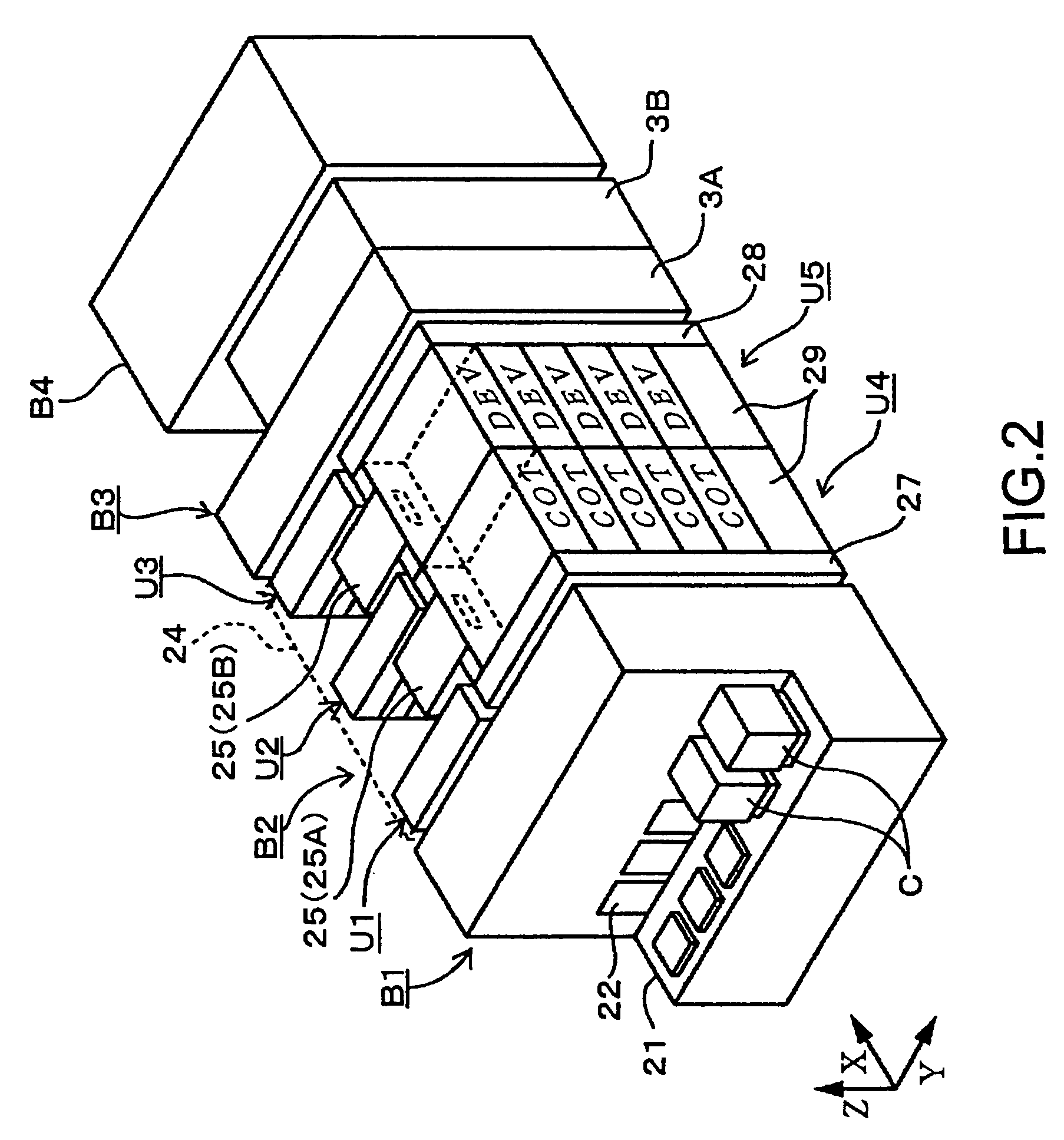

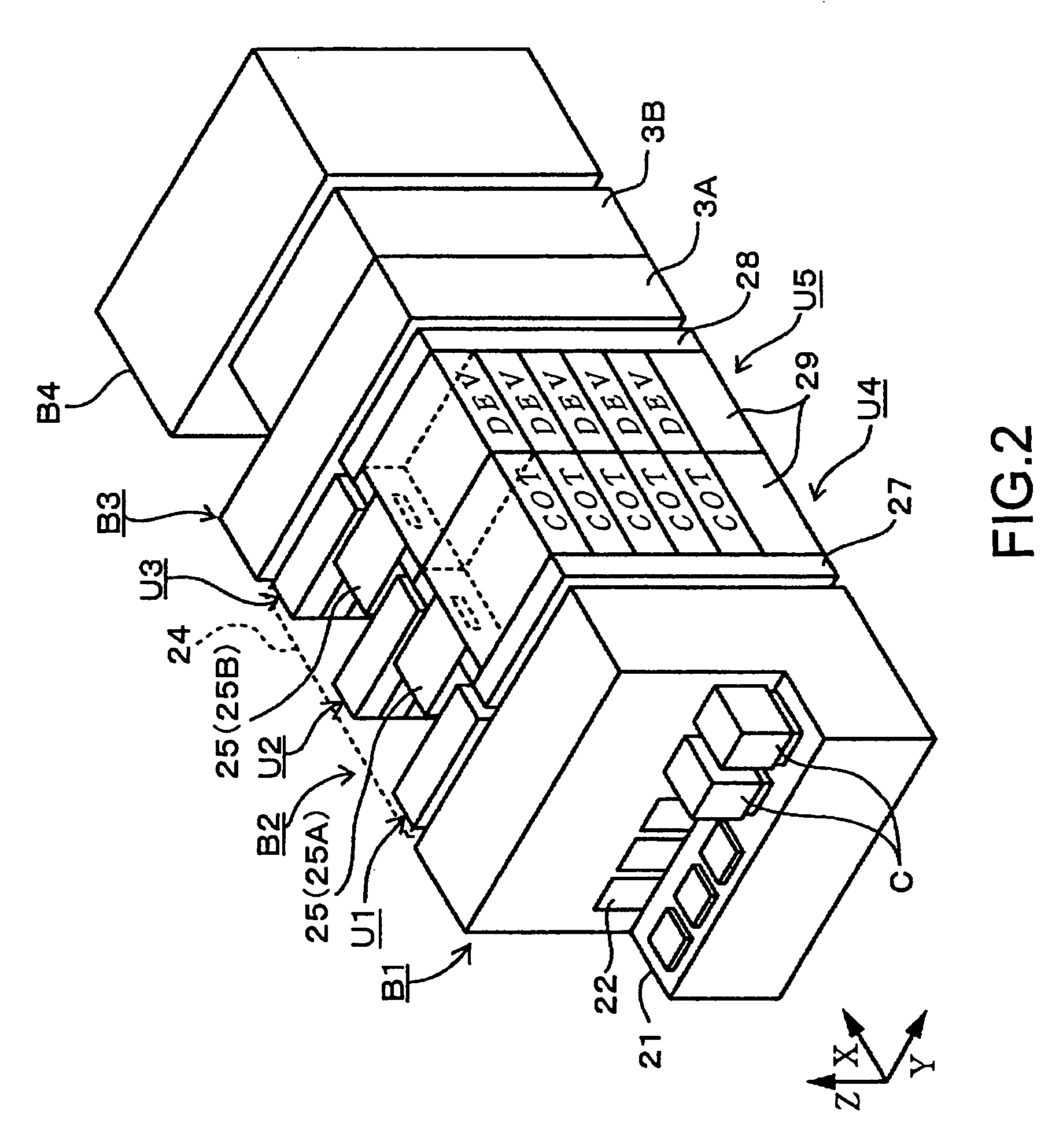

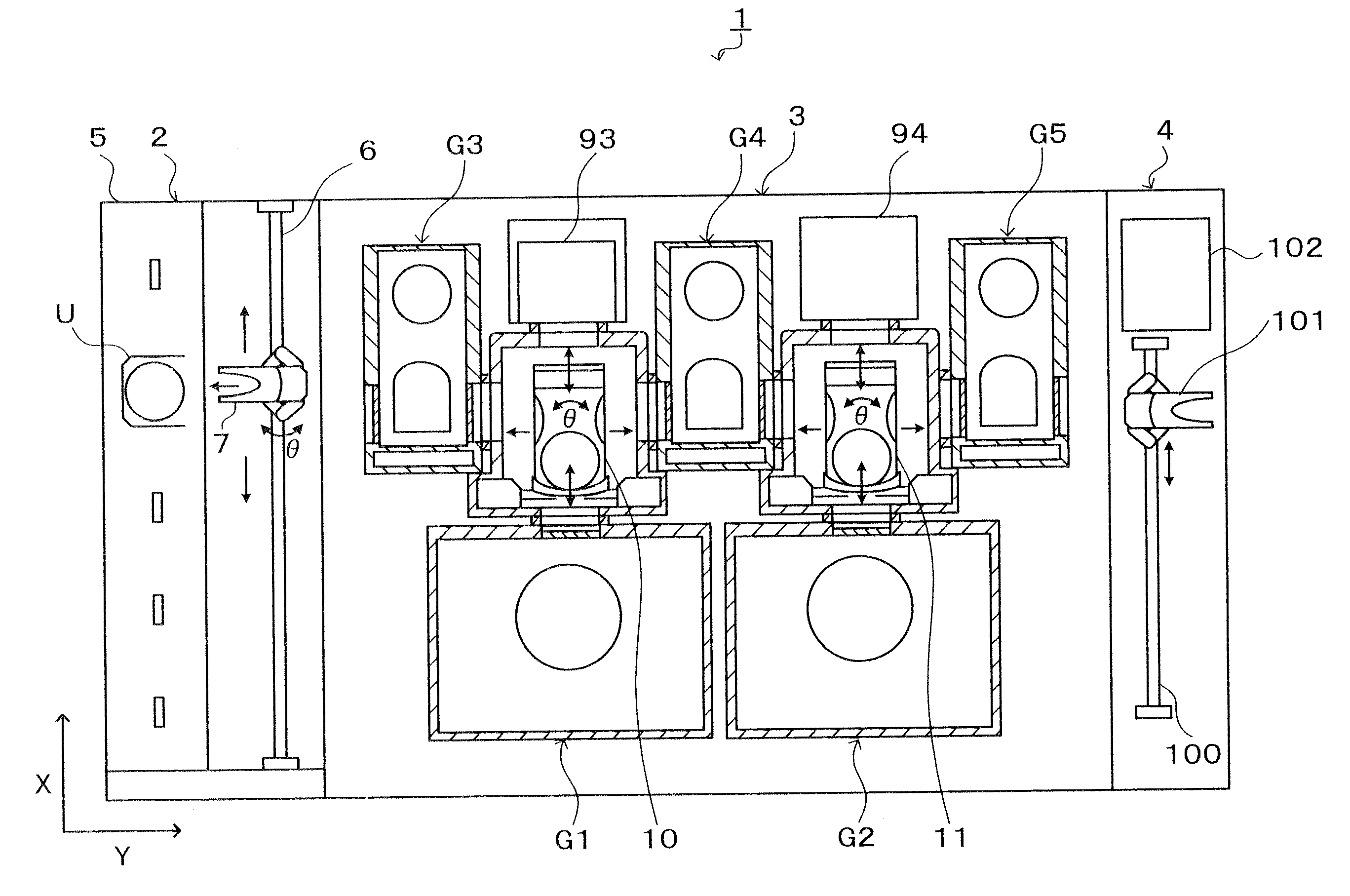

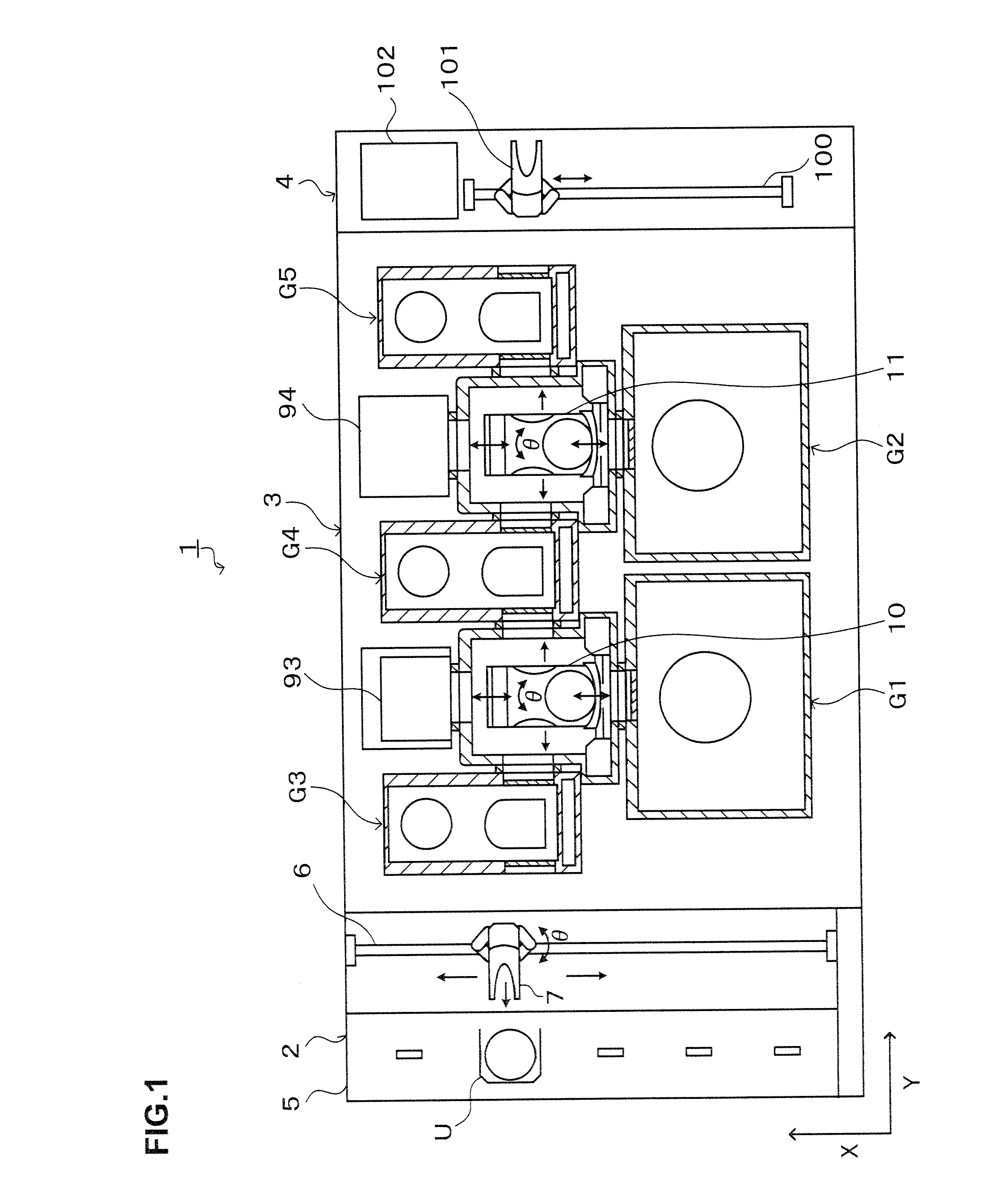

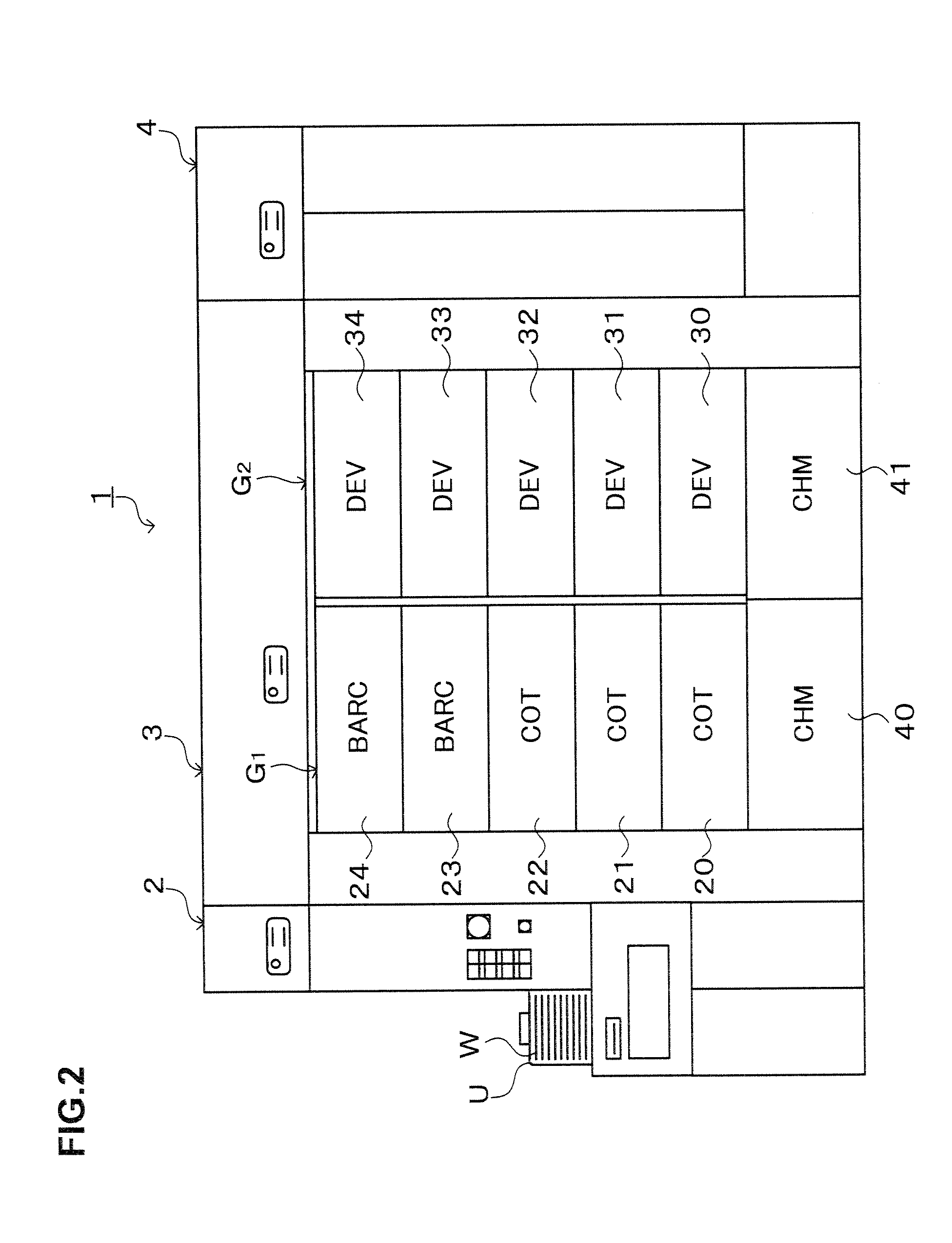

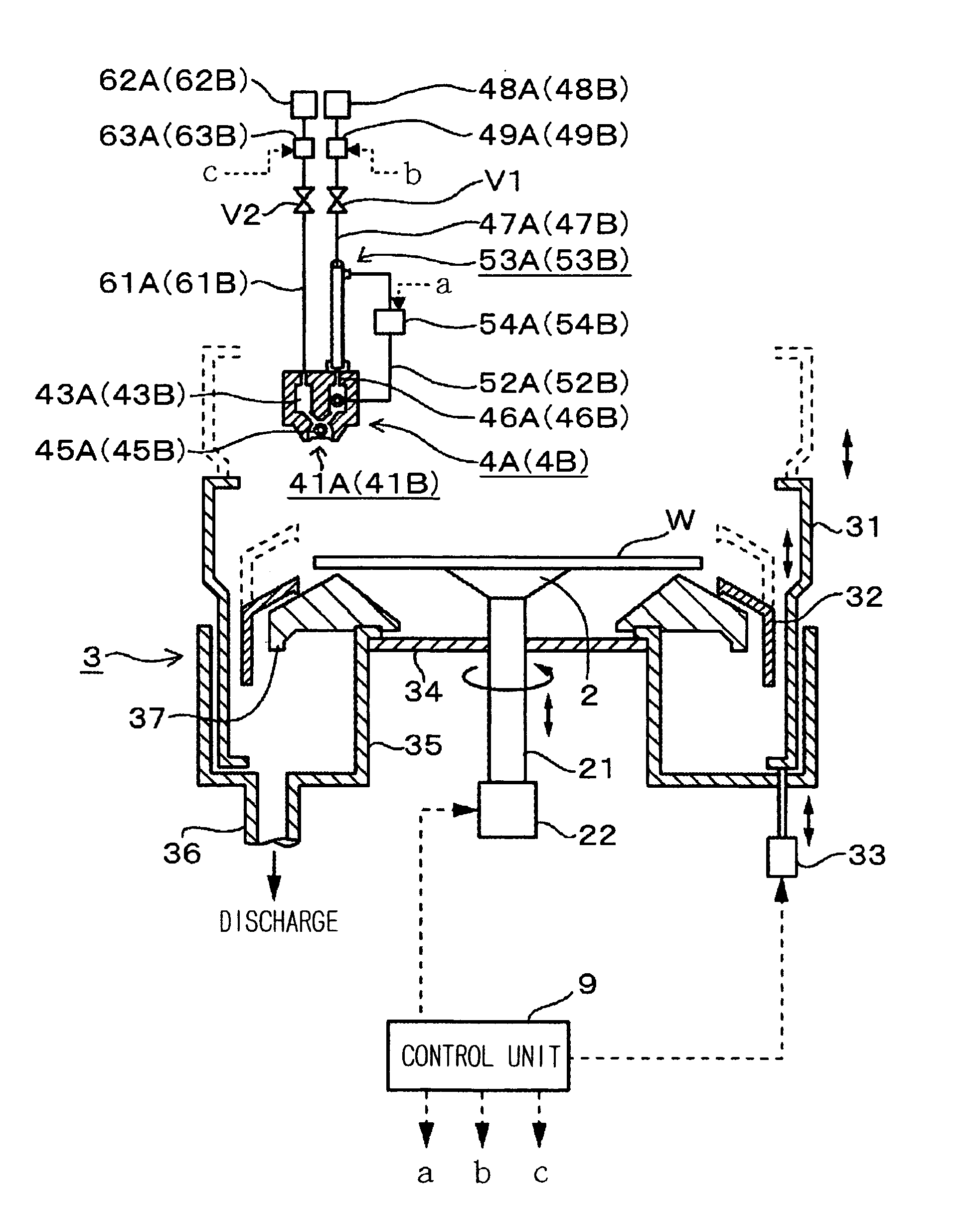

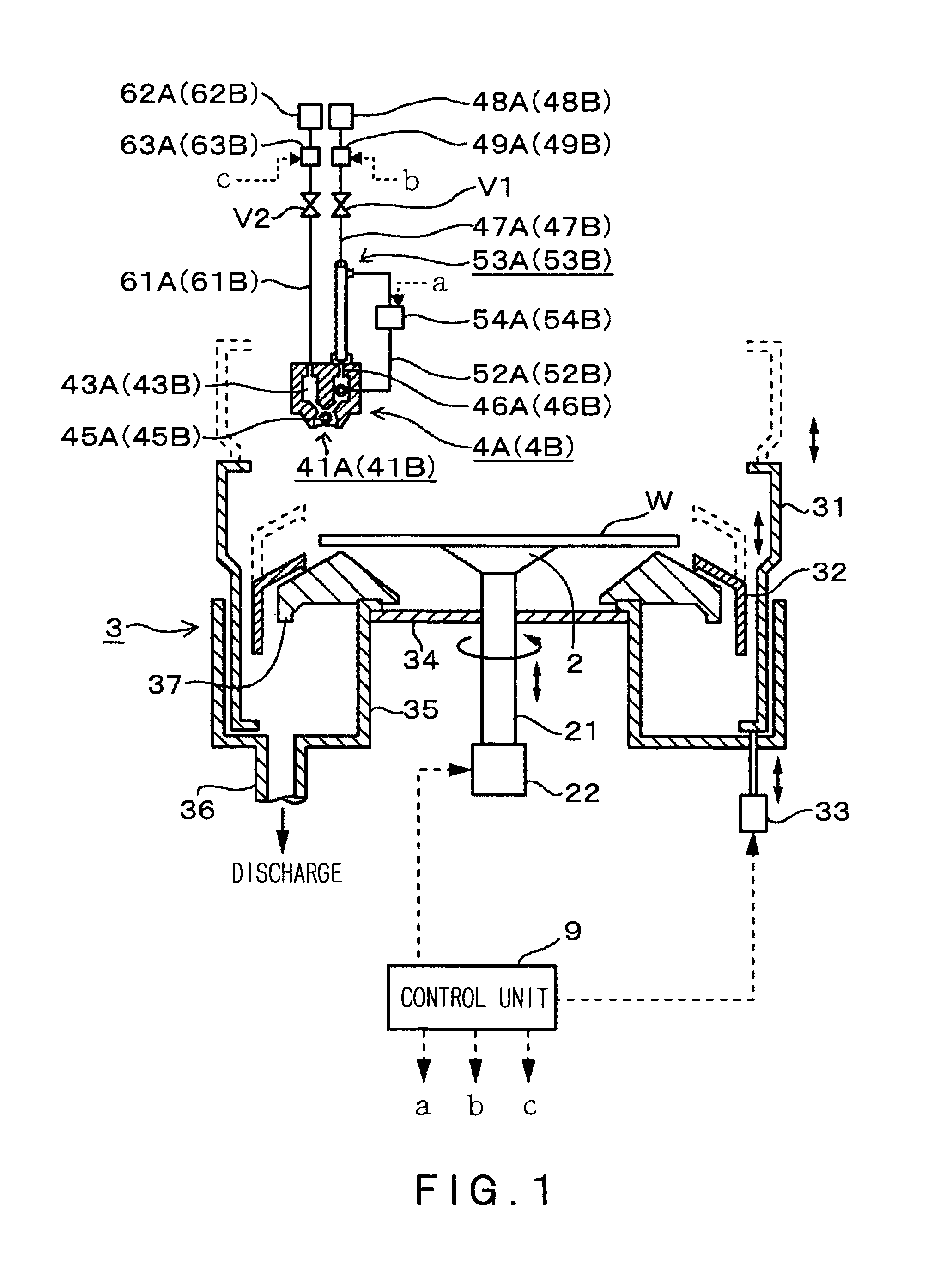

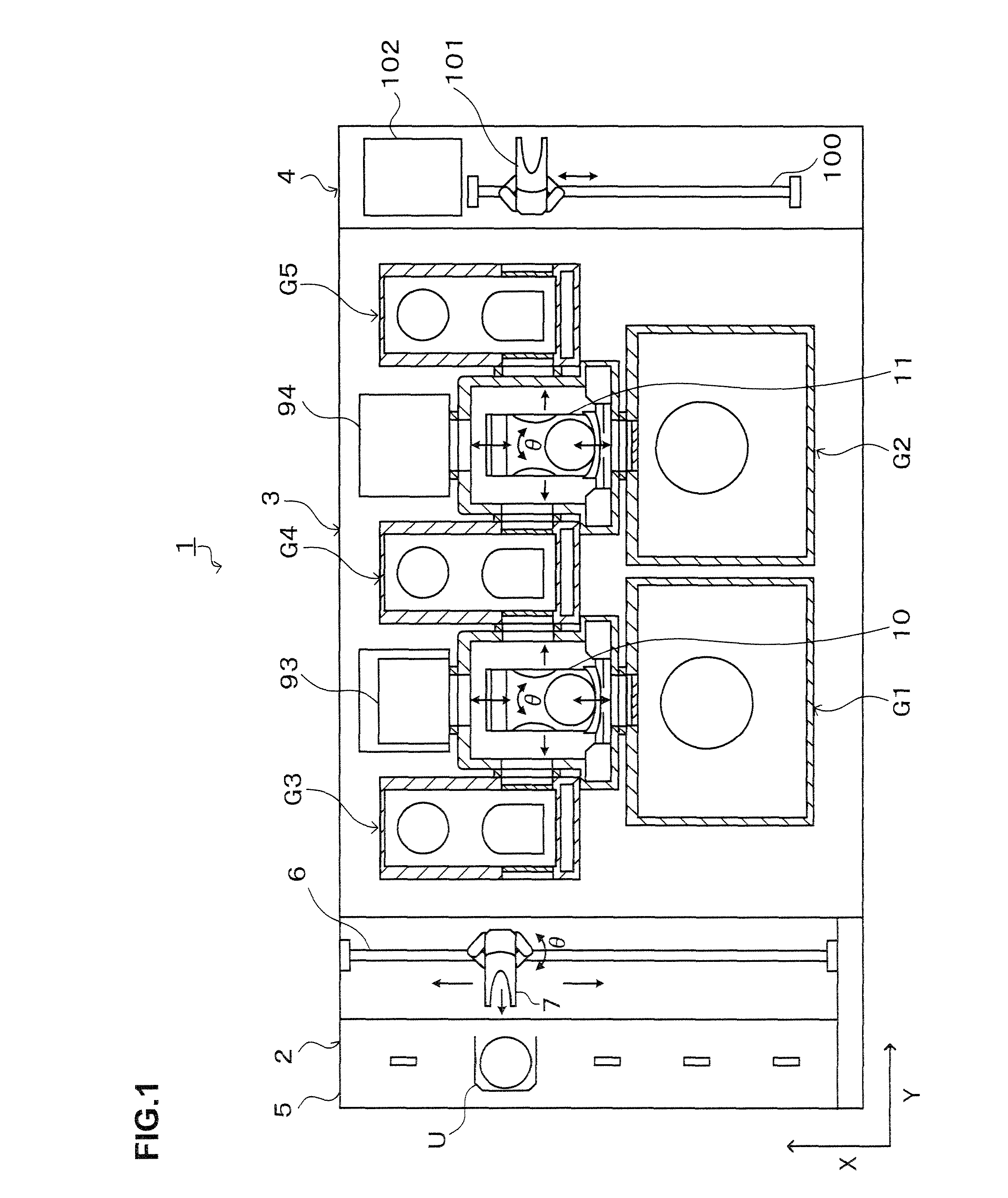

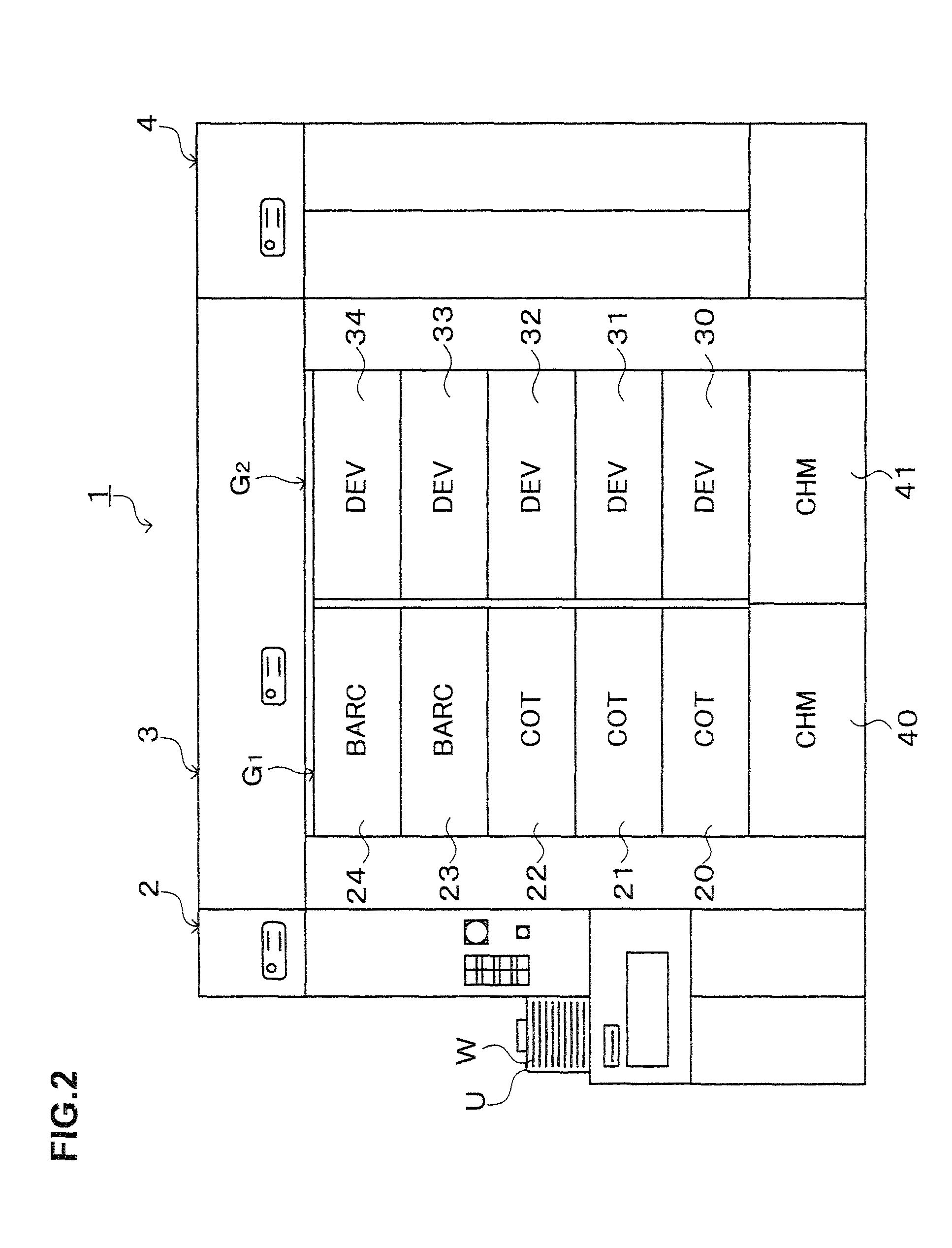

In a coating and developing apparatus that forms a resist film on substrates such as semiconductor wafers, and develops substrates exposed by an aligner, times after the aligner unloads substrates until heating units (PEB) start heating the substrates are kept uniform. Exposed wafers are prevented from being left stagnant in an interface portion disposed between a region in which resist is coated and developed and the aligner. In the region in which resist is coated and developed, a first transferring means that successively executes transportation cycles to transfer substrates from upstream side modules to downstream side modules in a flow of processes of substrates. N heating units (PEB) are disposed (n is for example 5). Exposed wafers loaded into the heating units (PEB) are unloaded by the first transferring means after (n−1) cycles including the transferring cycle of the first transferring means have elapsed.

Owner:TOKYO ELECTRON LTD

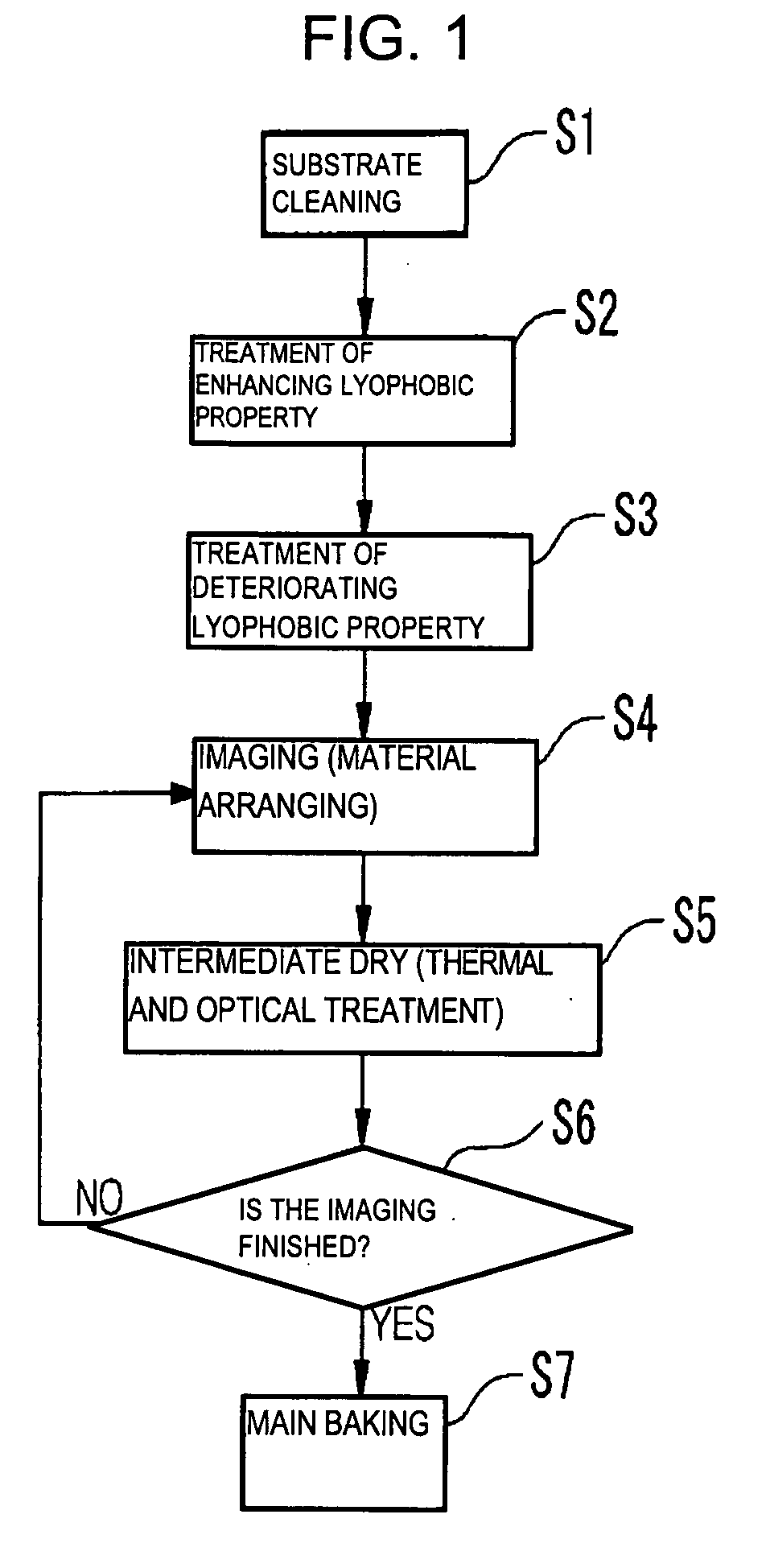

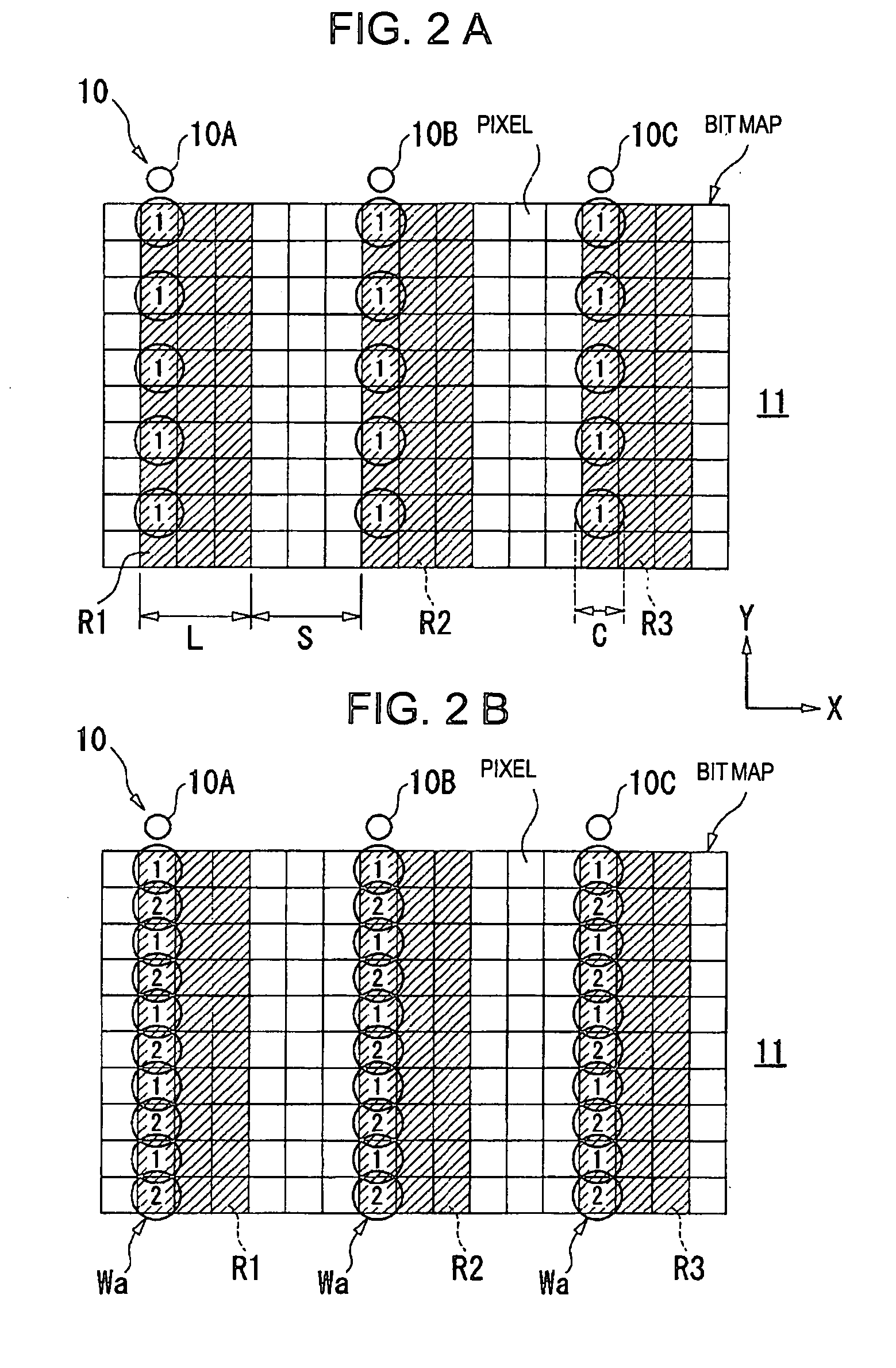

Pattern forming method, pattern forming apparatus, device manufacturing method, conductive film wiring, electro-optical device, and electronic apparatus

InactiveUS20050031836A1Without lack of uniformity in appearanceImprove electrical characteristicsTransistorSolid-state devicesEngineeringElectron

Owner:SEIKO EPSON CORP

Wafer processing system, coating/developing apparatus, and wafer, processing apparatus

InactiveUS20050287821A1Uniform timingSubstrates can be prevented from beingSemiconductor/solid-state device manufacturingCharge manipulationResistEngineering

In a coating and developing apparatus that forms a resist film on substrates such as semiconductor wafers, and develops substrates exposed by an aligner, times after the aligner unloads substrates until heating units (PEB) start heating the substrates are kept uniform. Exposed wafers are prevented from being left stagnant in an interface portion disposed between a region in which resist is coated and developed and the aligner. In the region in which resist is coated and developed, a first transferring means that successively executes transportation cycles to transfer substrates from upstream side modules to downstream side modules in a flow of processes of substrates. N heating units (PEB) are disposed (n is for example 5). Exposed wafers loaded into the heating units (PEB) are unloaded by the first transferring means after (n−1) cycles including the transferring cycle of the first transferring means have elapsed.

Owner:TOKYO ELECTRON LTD

Temperature control method of heat processing plate, computer storage medium, and temperature control apparatus of heat processing plate

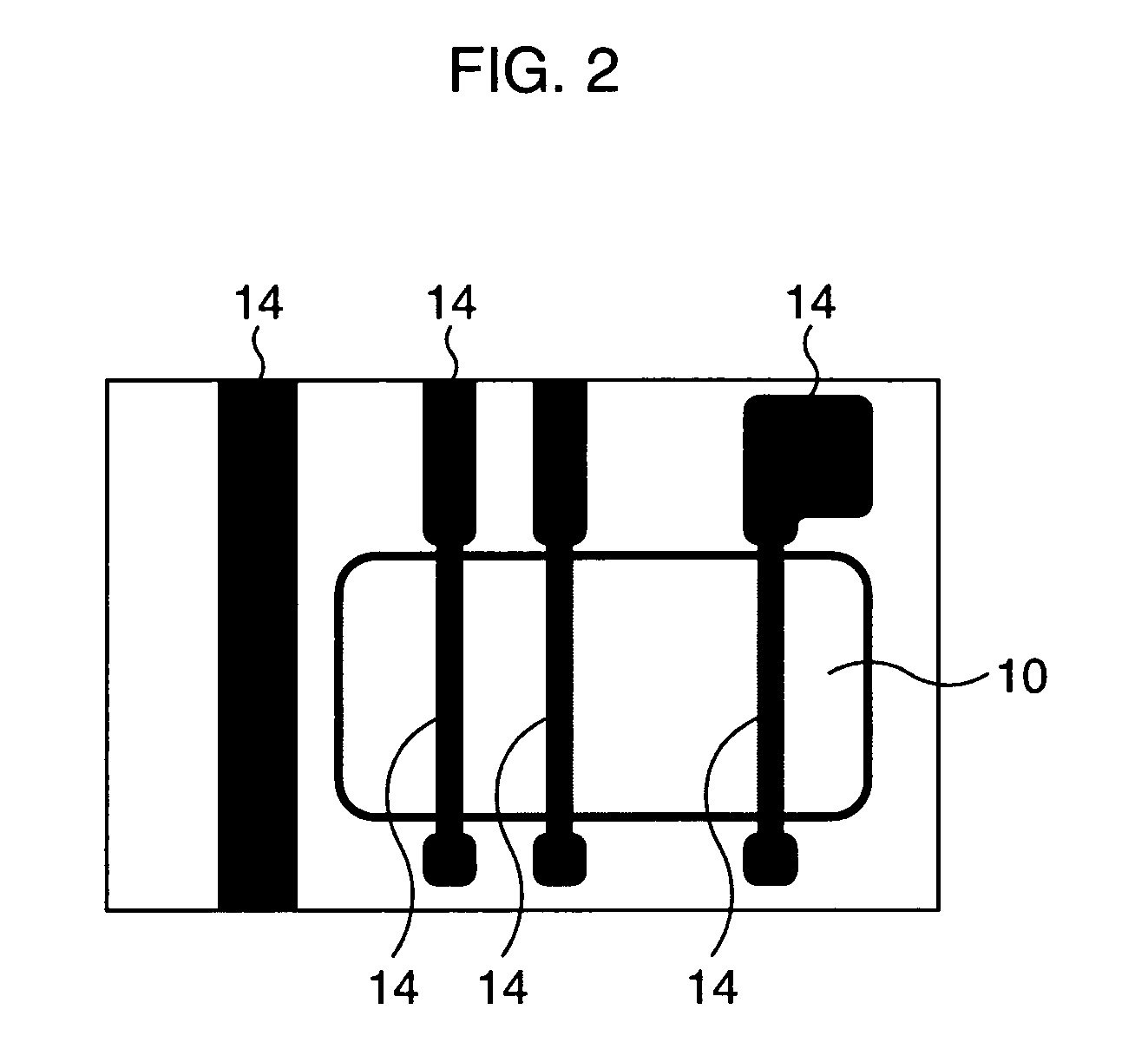

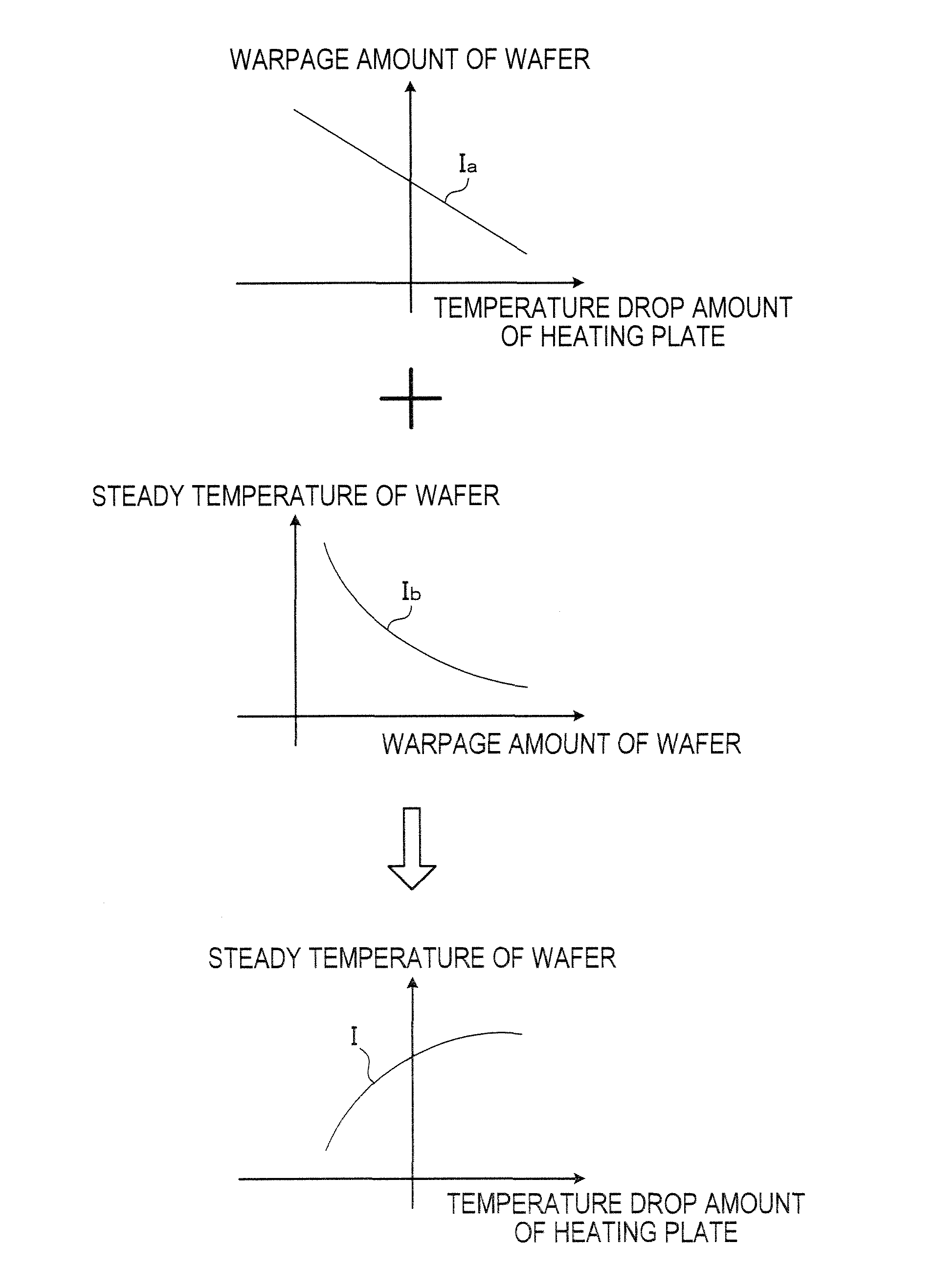

ActiveUS20070272680A1Uniform line widthIncrease spacingDrying solid materials with heatSemiconductor/solid-state device manufacturingTemperature controlEngineering

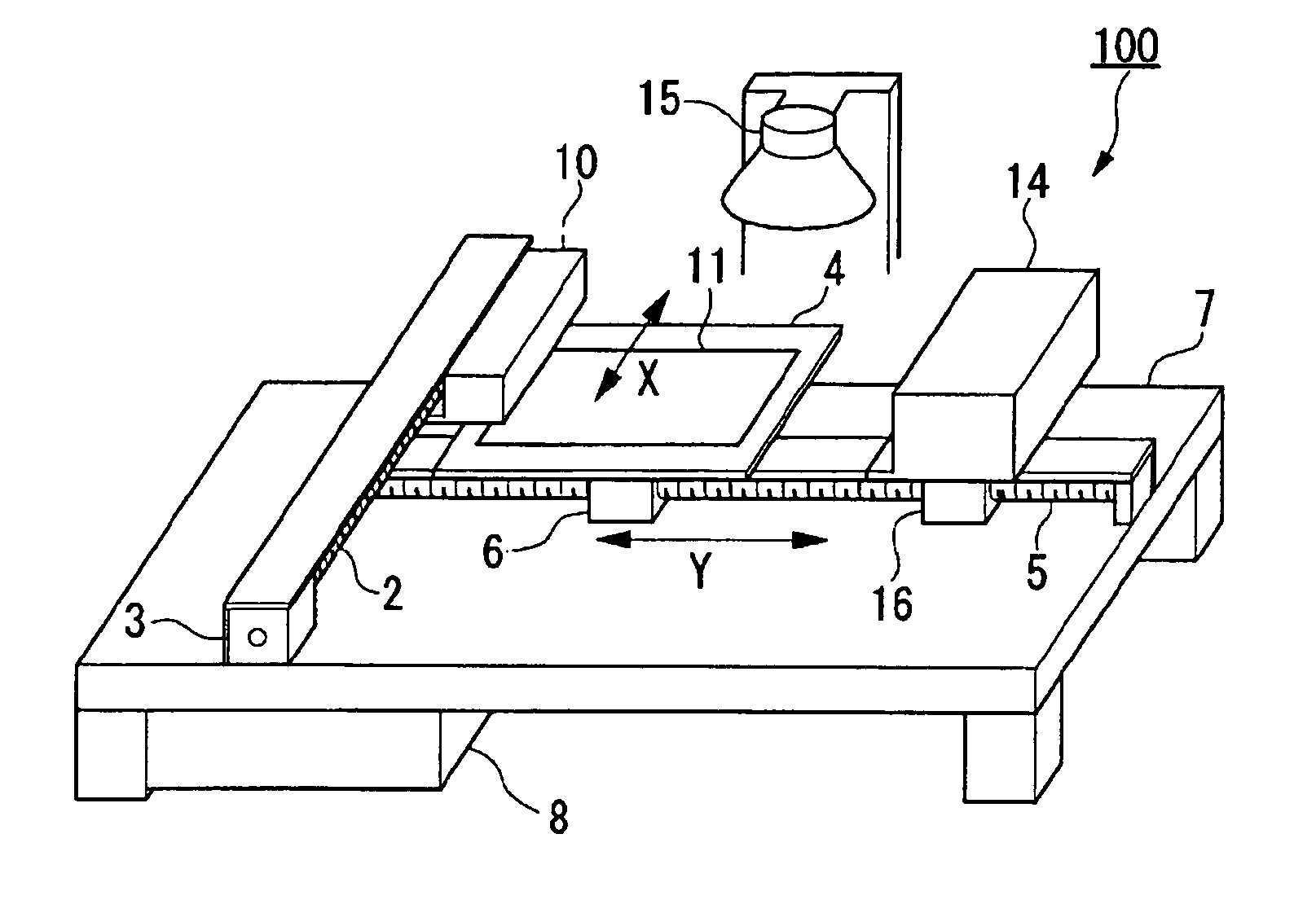

In the present invention, temperature drop amounts of heating plate regions when the substrate is mounted on a heating plate are detected to detect a warped state of the substrate. From the temperature drop amounts of the heating plate regions, correction values for set temperatures of the heating plate regions are calculated. The calculation of the correction values for the set temperatures of the heating plate regions is performed by estimating steady temperatures within the substrate to be heat-processed on the heating plate from the temperature drop amounts of the heating plate regions using a correlation obtained in advance. From the estimated steady temperatures within the substrate and the temperature drop amounts of the heating regions, the correction values for the set temperatures of the heating plate regions are calculated. Based on the correction values for the set temperatures, the set temperatures of the heating plate regions are changed.

Owner:TOKYO ELECTRON LTD

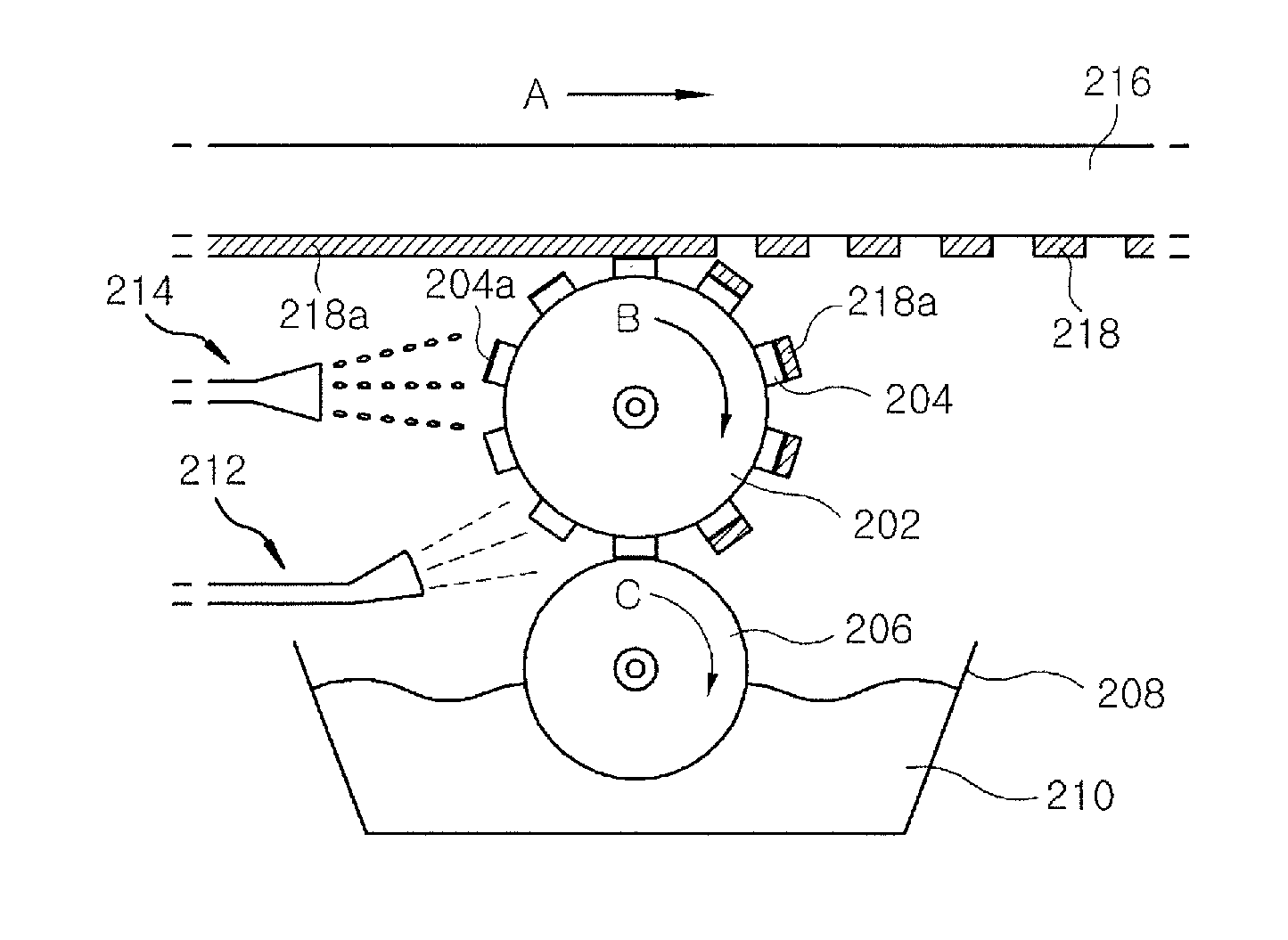

Developing device and developing method

InactiveUS20070184178A1Uniform line widthPrevent in developmentMovable spraying apparatusSemiconductor/solid-state device manufacturingResistTime segment

The temperature of a developing solution is varied depending on the type of resist or the resist pattern. The developing solution is applied while scanning a developer nozzle having a slit-shaped ejection port that has a length matching the width of the effective area of the substrate. After leaving the substrate with the developing solution being coated thereon for a predetermined period of time, a diluent is supplied while scanning a diluent nozzle, thereby substantially stopping the development reaction and causing the dissolved resist components to diffuse. A desired amount of resist can be quickly dissolved through the control of the developing solution temperature, while the development can be stopped before the dissolved resist components exhibit adverse effect through the supply of the diluent a predetermined timing, whereby achieving a pattern having a uniform line width and improved throughput.

Owner:TOKYO ELECTRON LTD

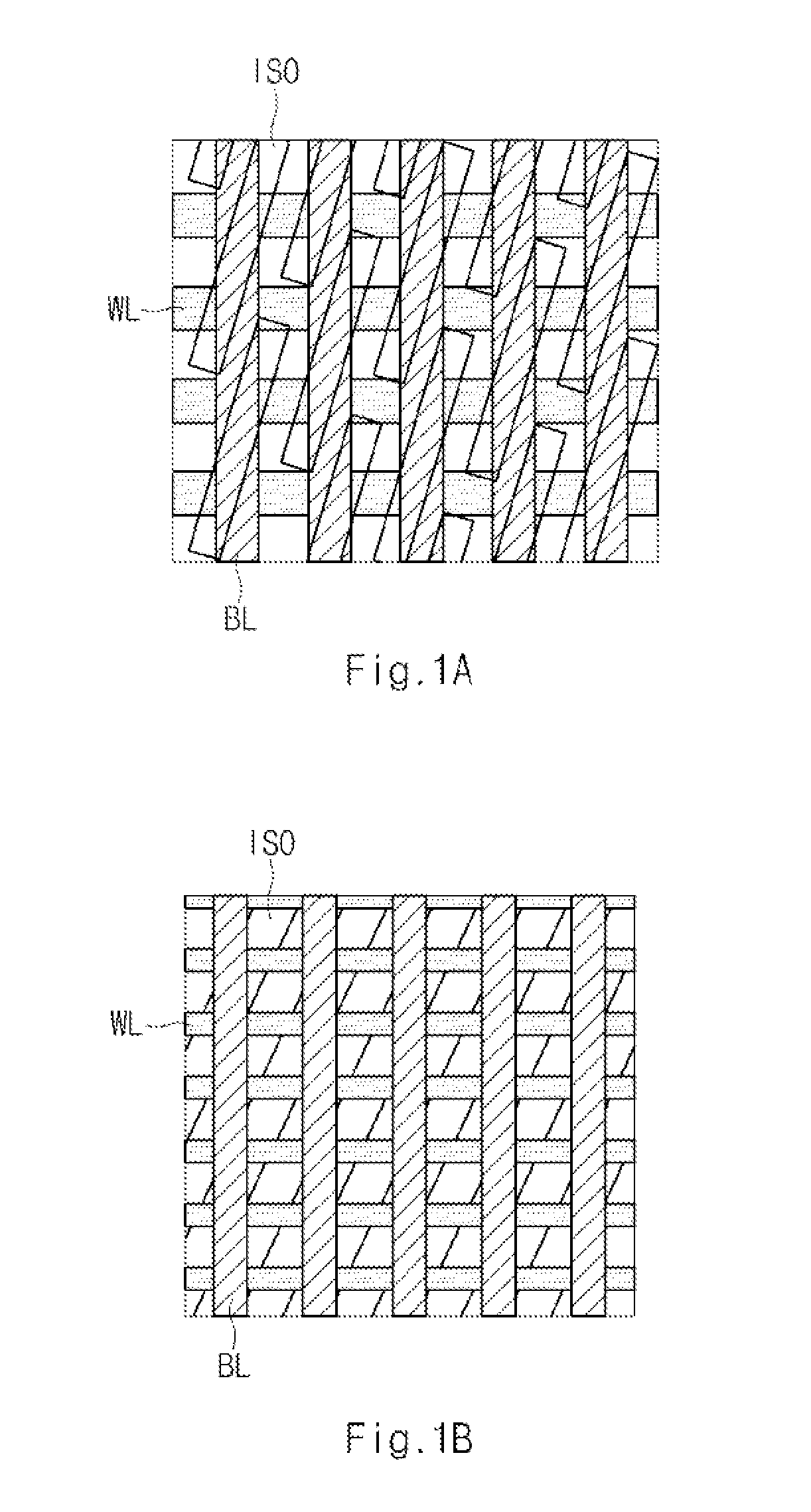

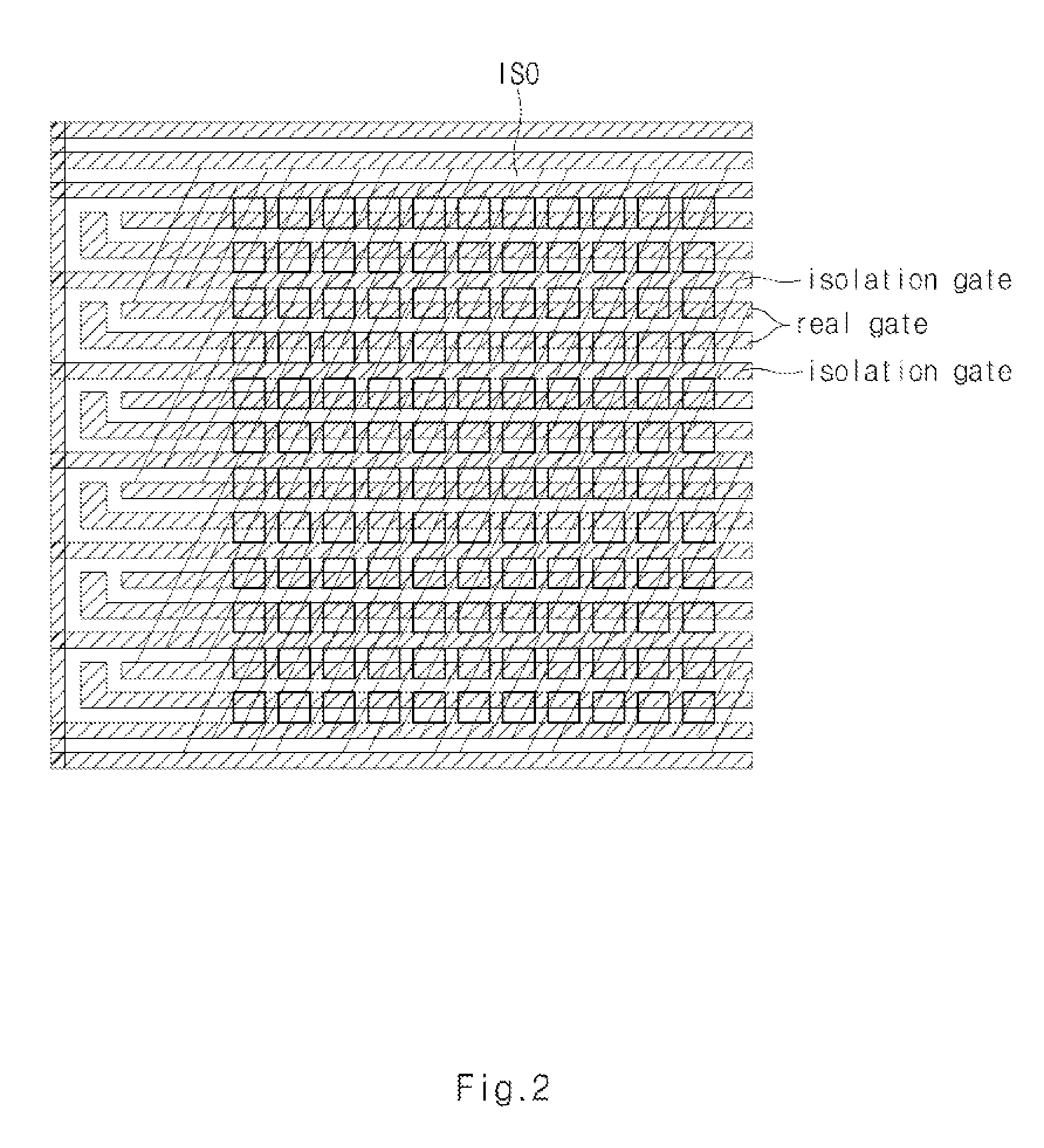

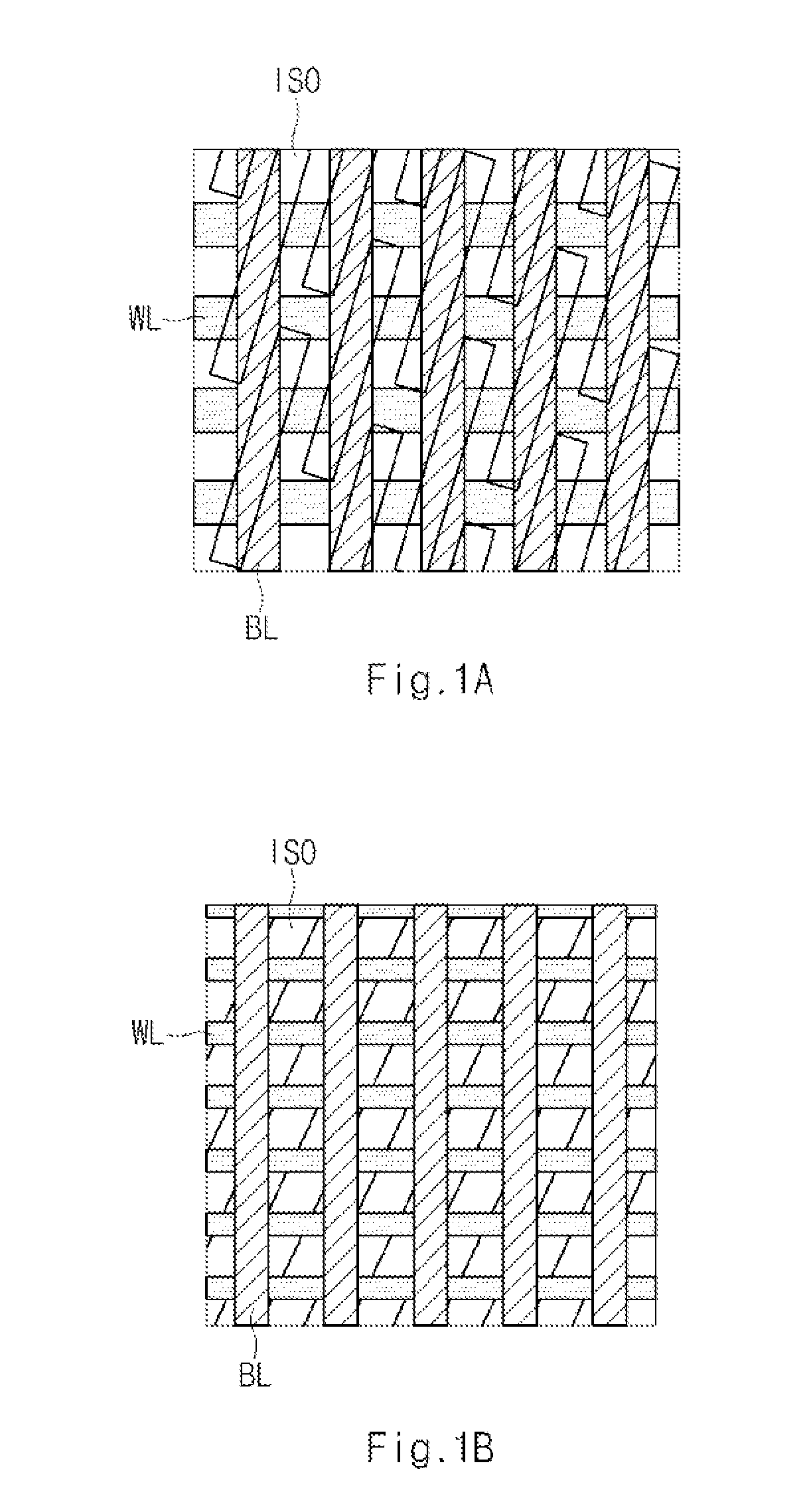

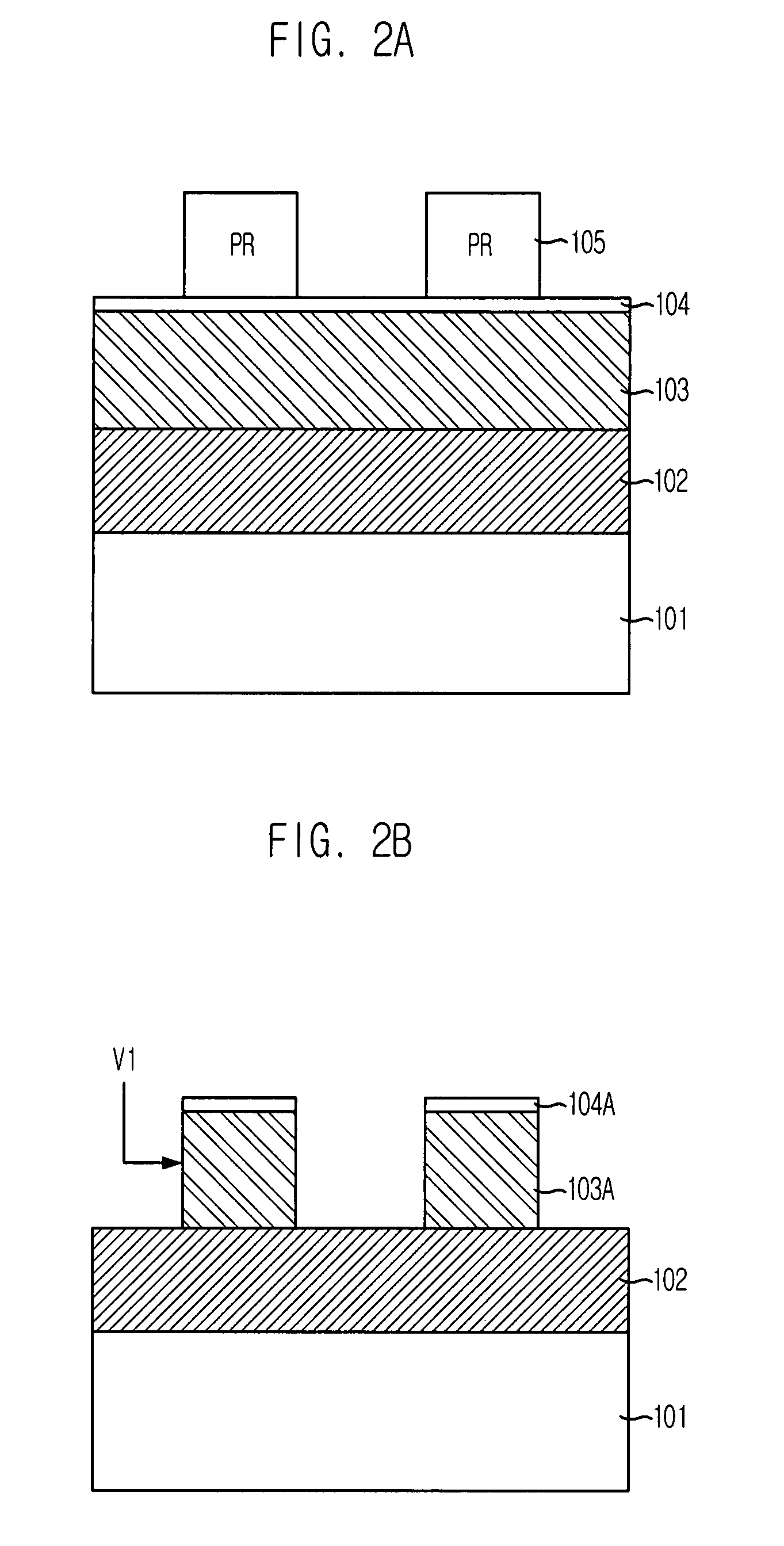

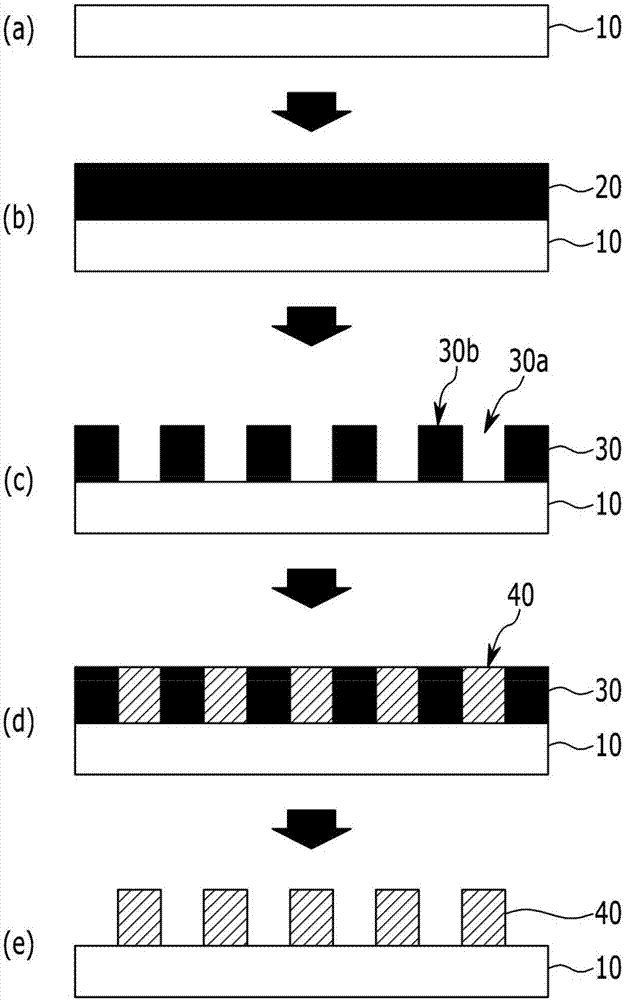

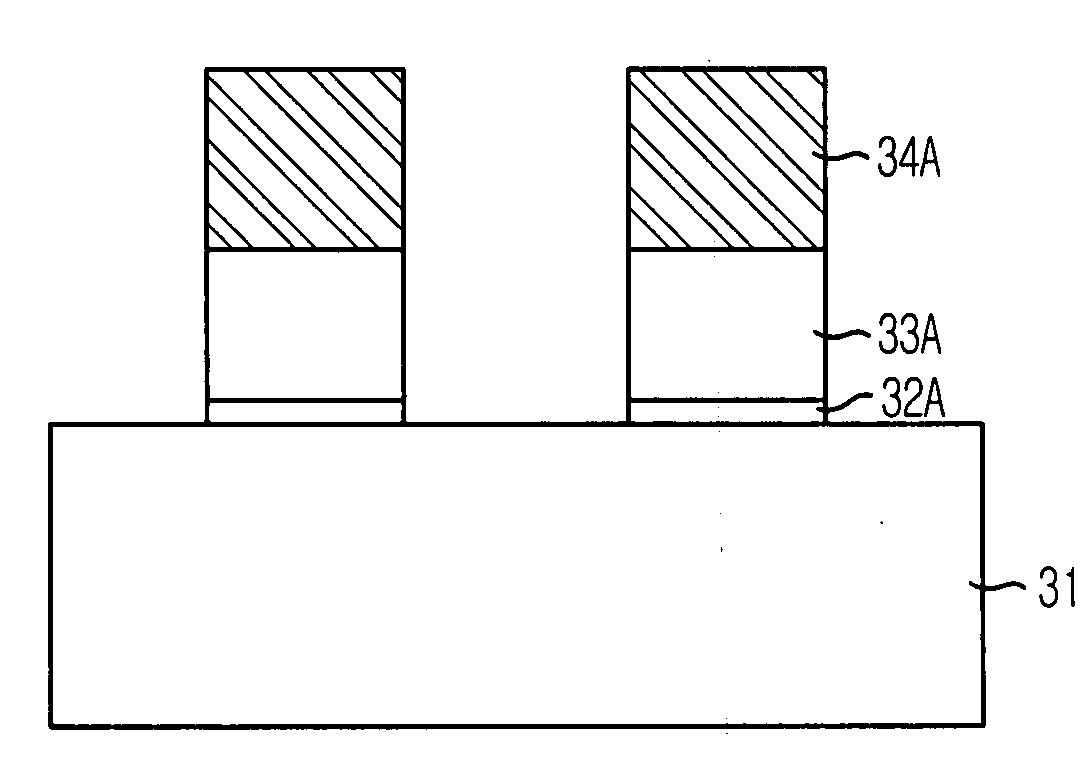

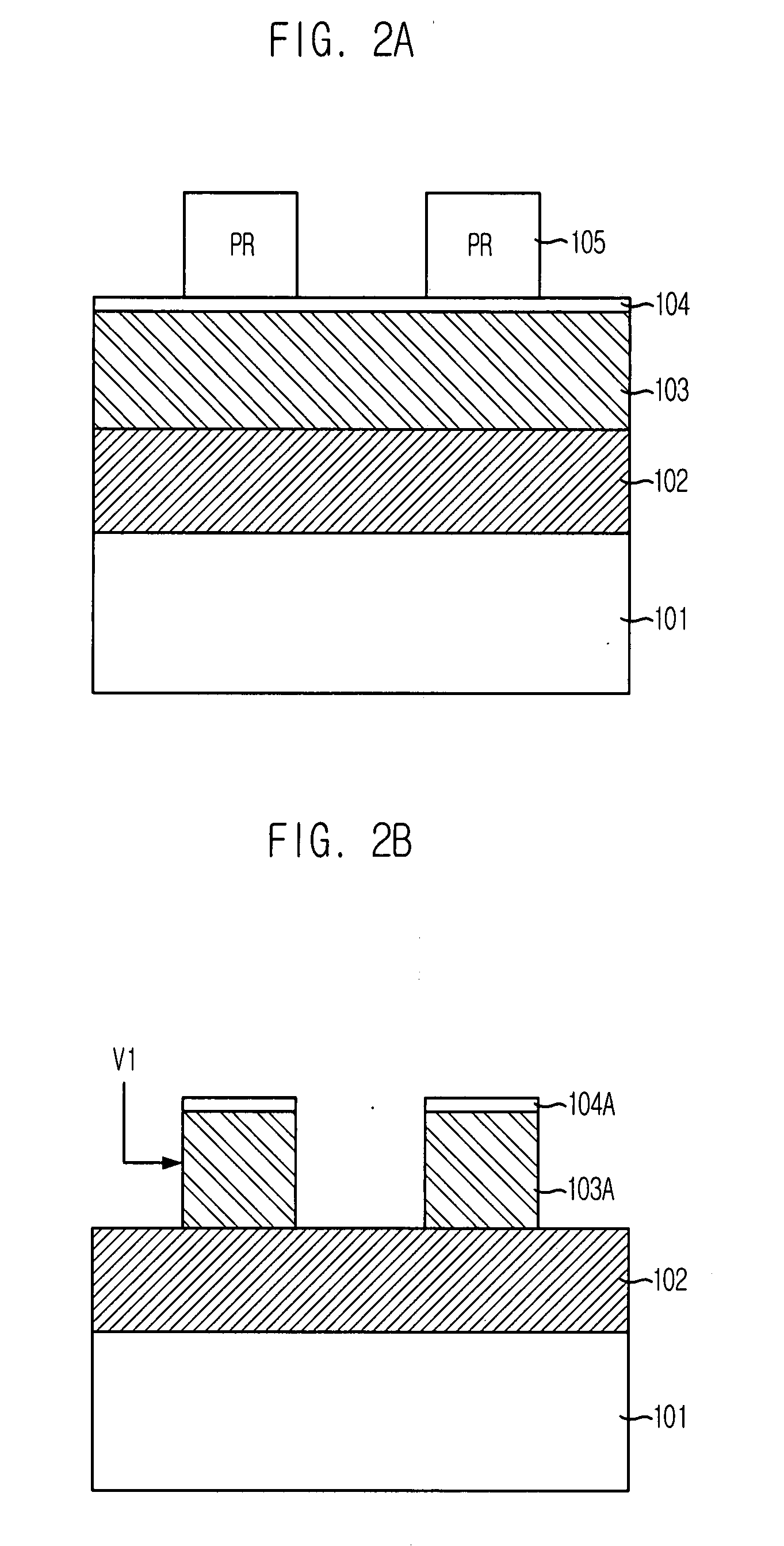

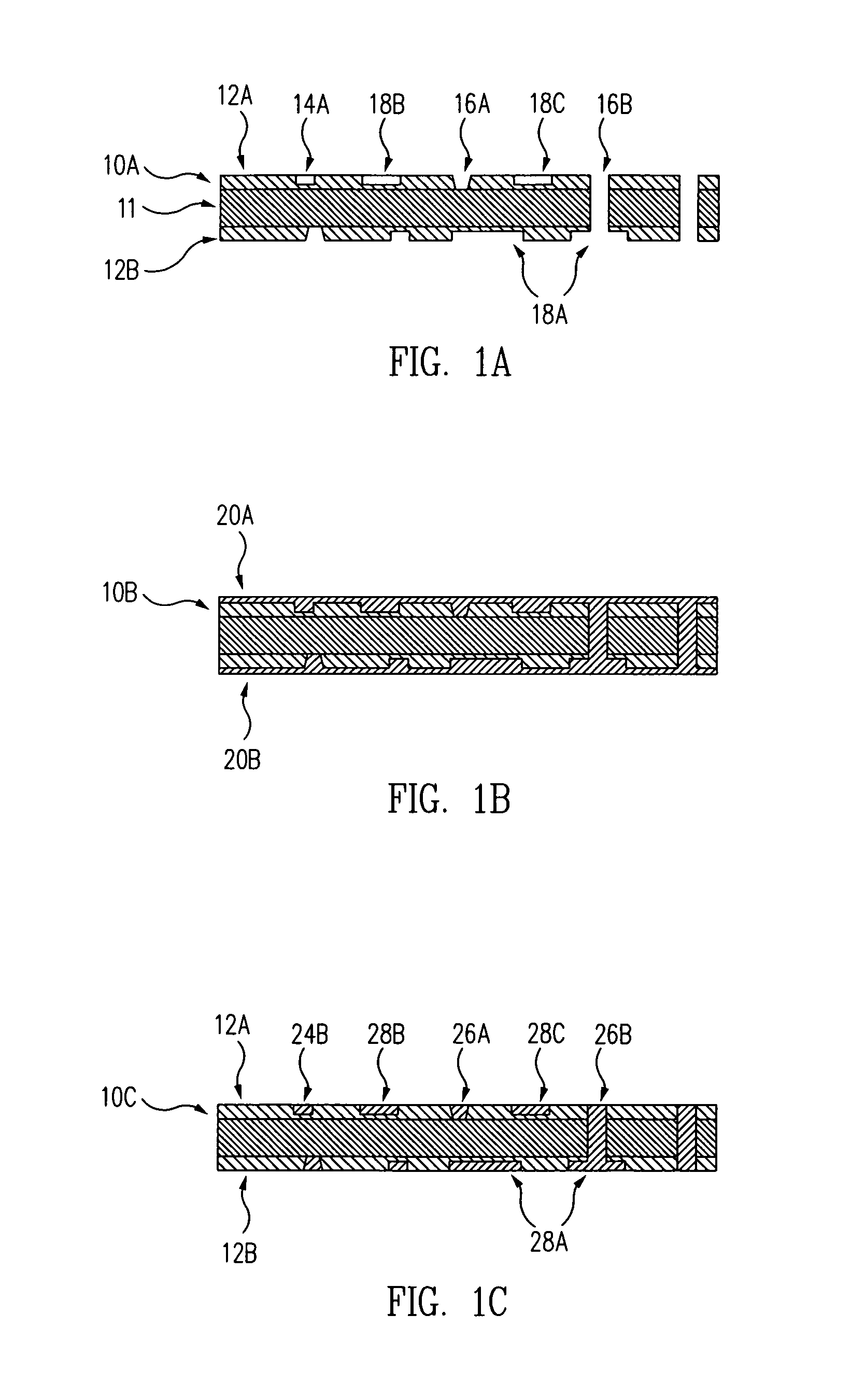

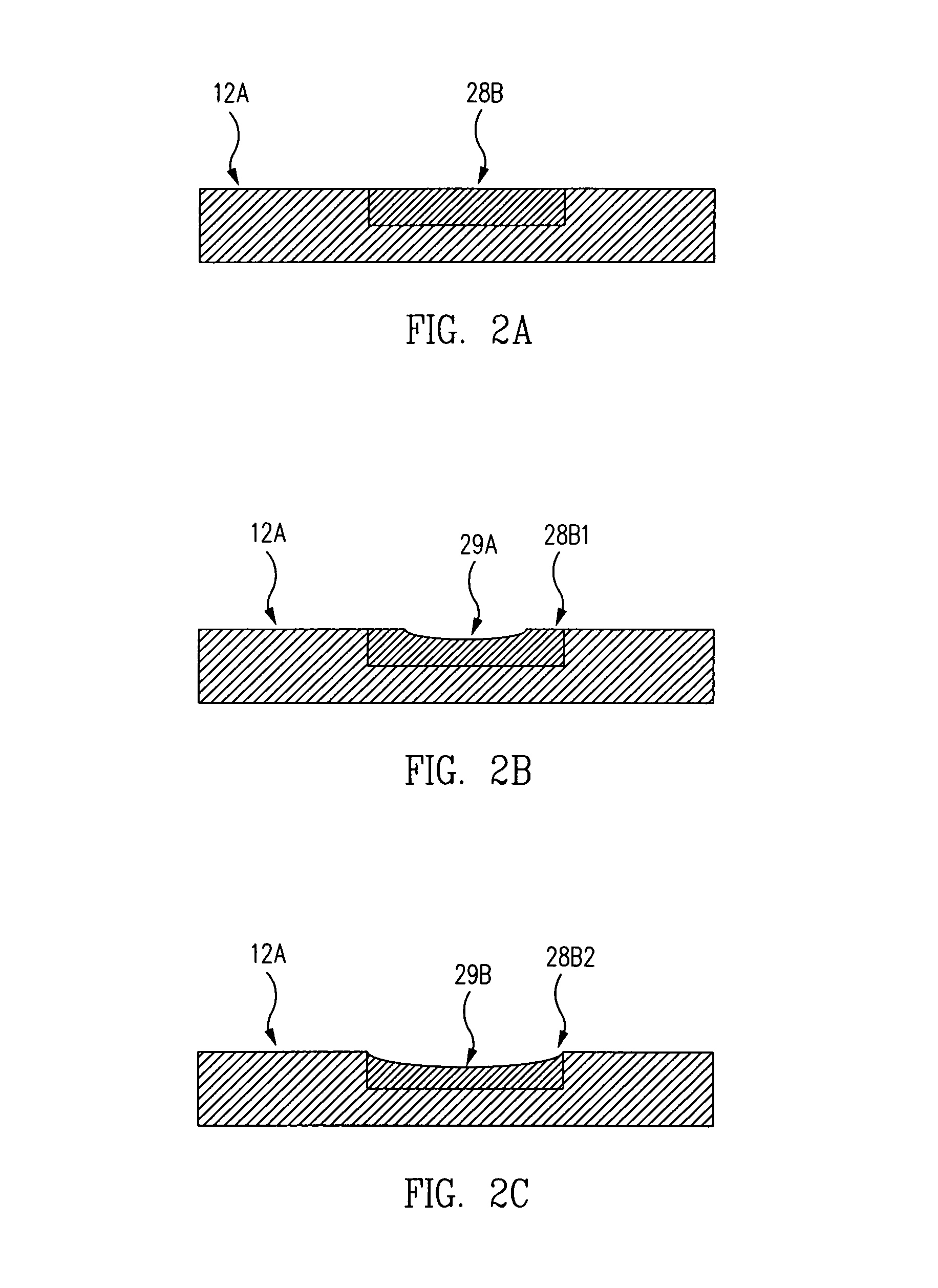

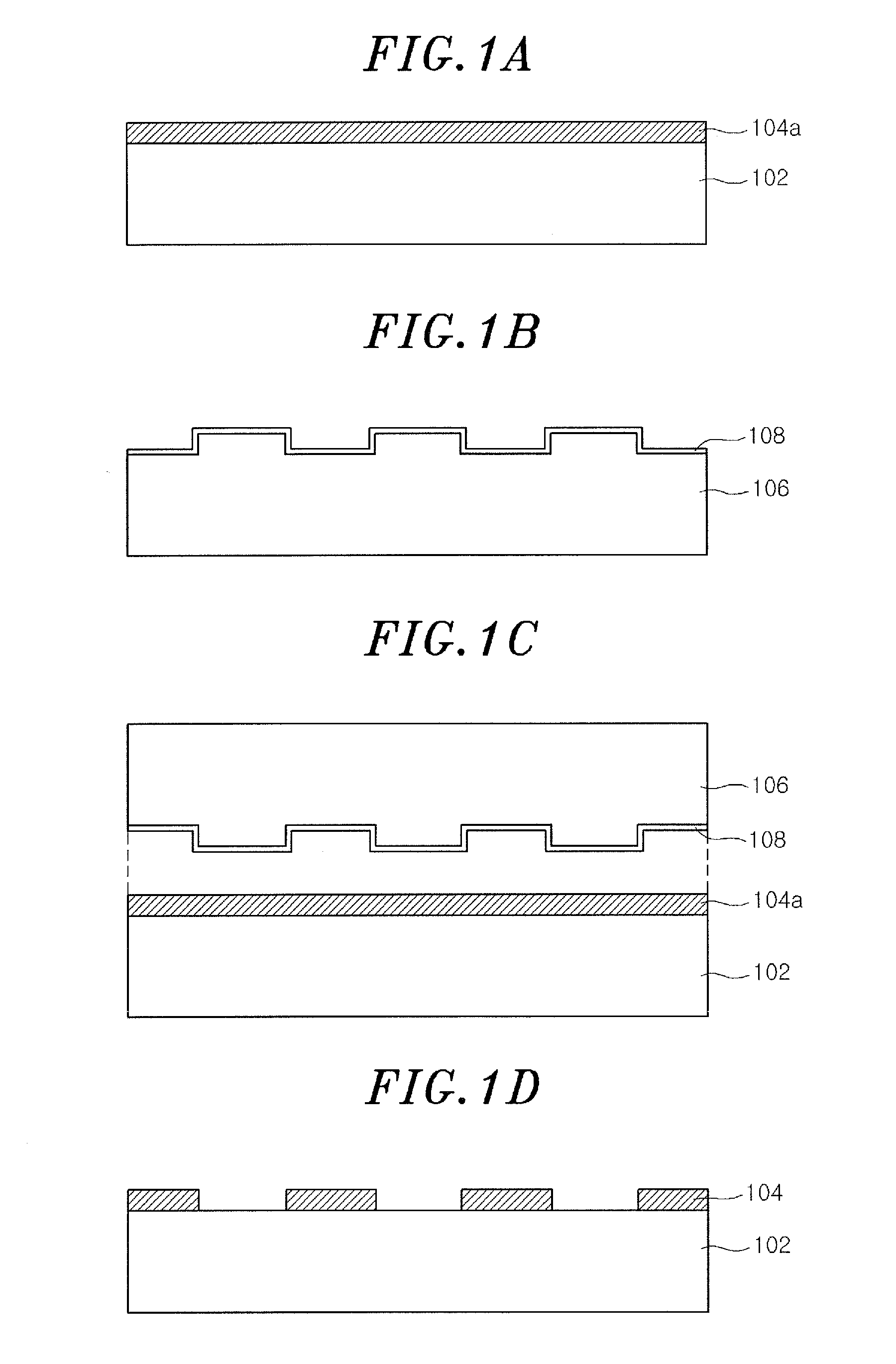

Method for forming fine pattern of semiconductor device using double spacer patterning technology

InactiveUS8999848B2Uniform line widthSolid-state devicesSemiconductor/solid-state device manufacturingFine lineEngineering

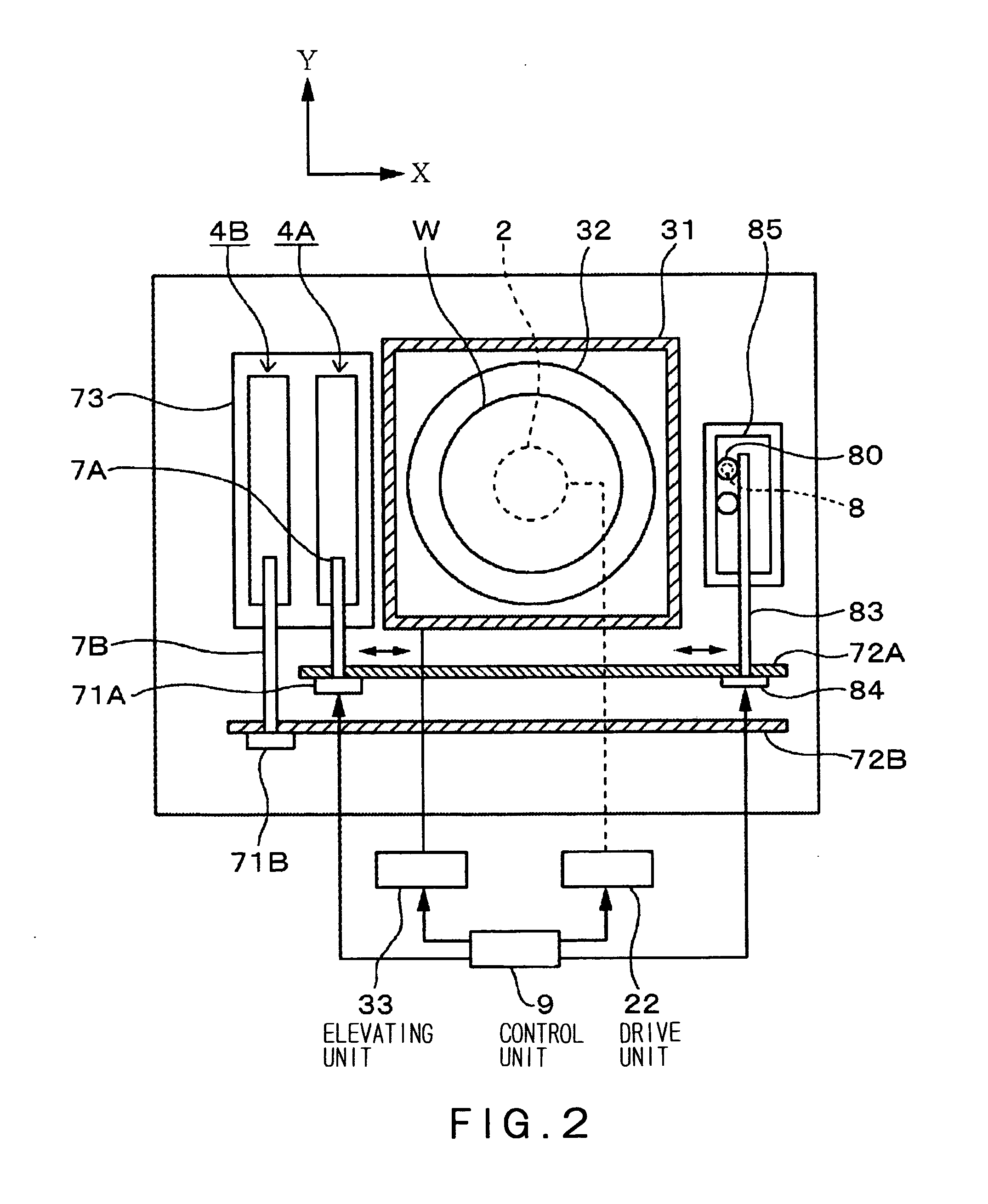

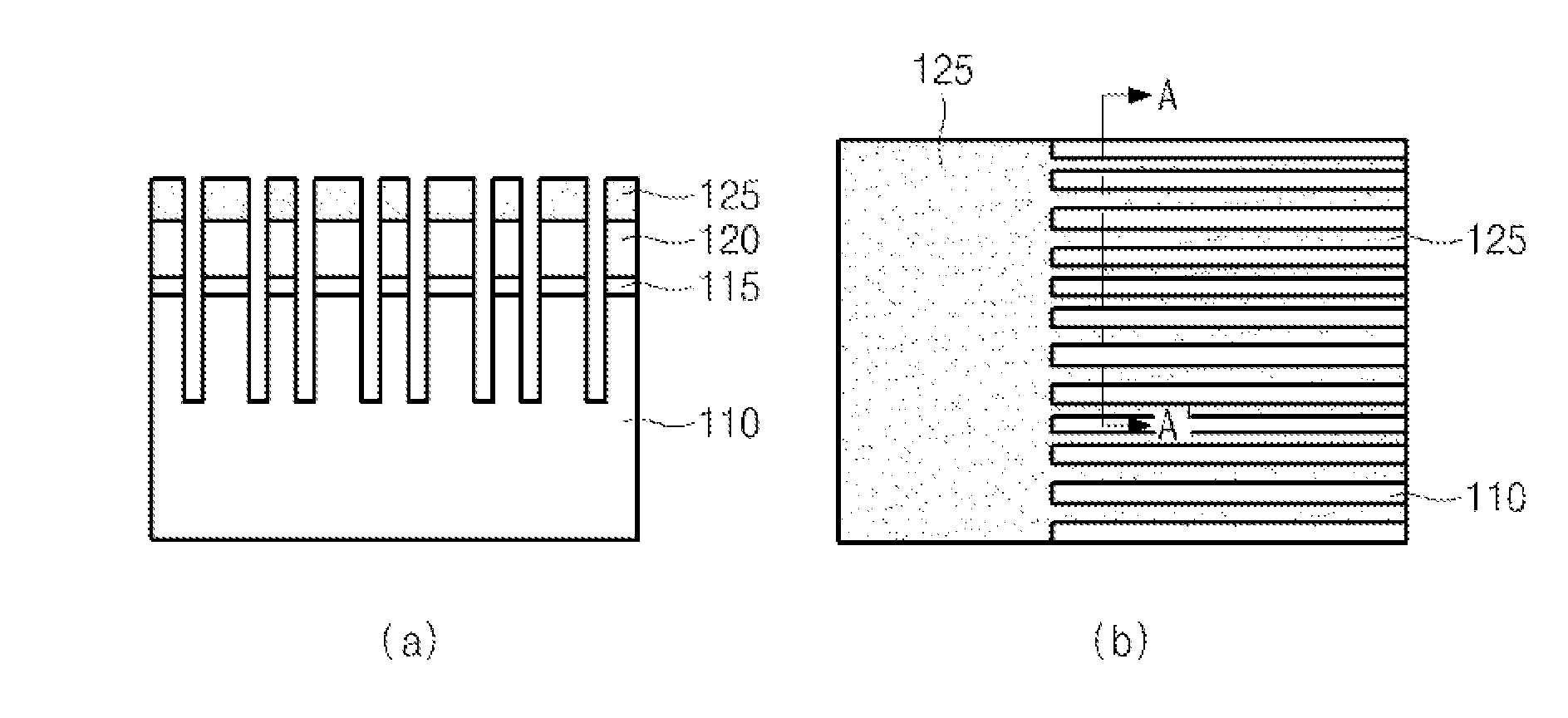

A method of forming a fine pattern of a semiconductor device using double SPT process, which is capable of implementing a line and space pattern having a uniform fine line width by applying a double SPT process including a negative SPT process, is provided. The method includes a first SPT process and a second SPT process and the second SPT process includes a Negative SPT process.

Owner:SK HYNIX INC

Method for forming fine pattern of semiconductor device using double spacer patterning technology

InactiveUS20140017889A1Uniform line widthSolid-state devicesSemiconductor/solid-state device manufacturingFine lineDevice material

A method of forming a fine pattern of a semiconductor device using double SPT process, which is capable of implementing a line and space pattern having a uniform fine line width by applying a double SPT process including a negative SPT process, is provided. The method includes a first SPT process and a second SPT process and the second SPT process includes a Negative SPT process.

Owner:SK HYNIX INC

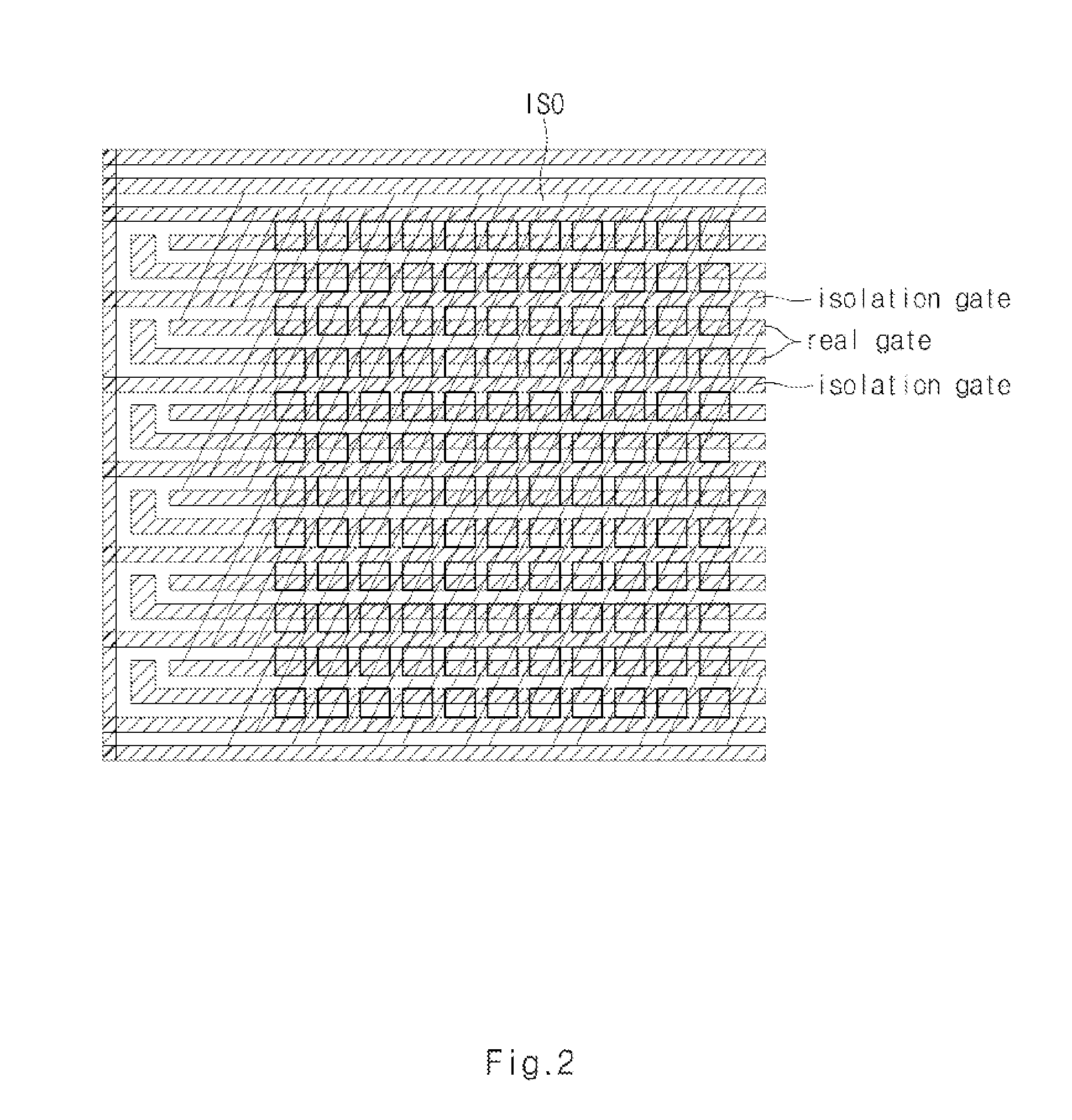

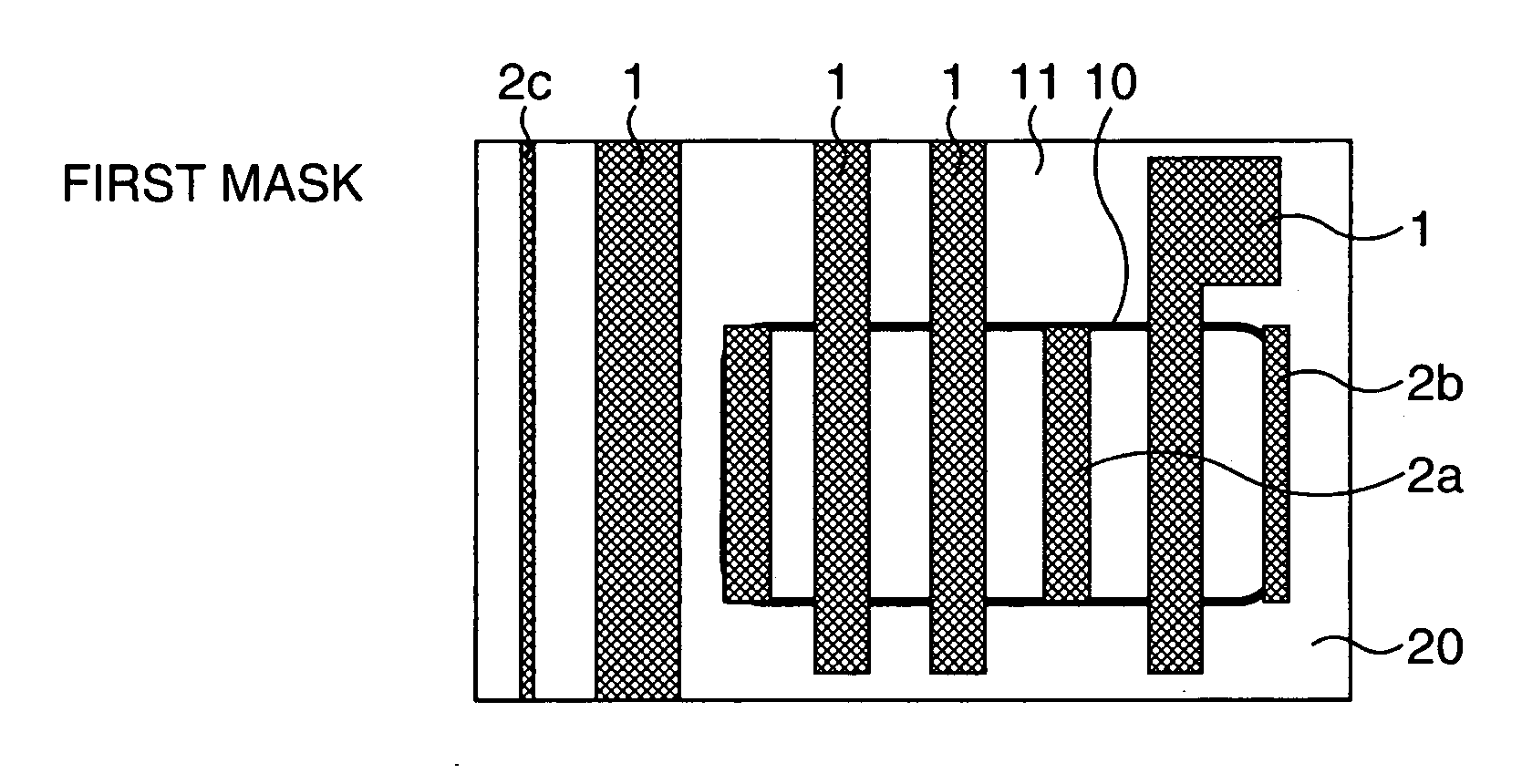

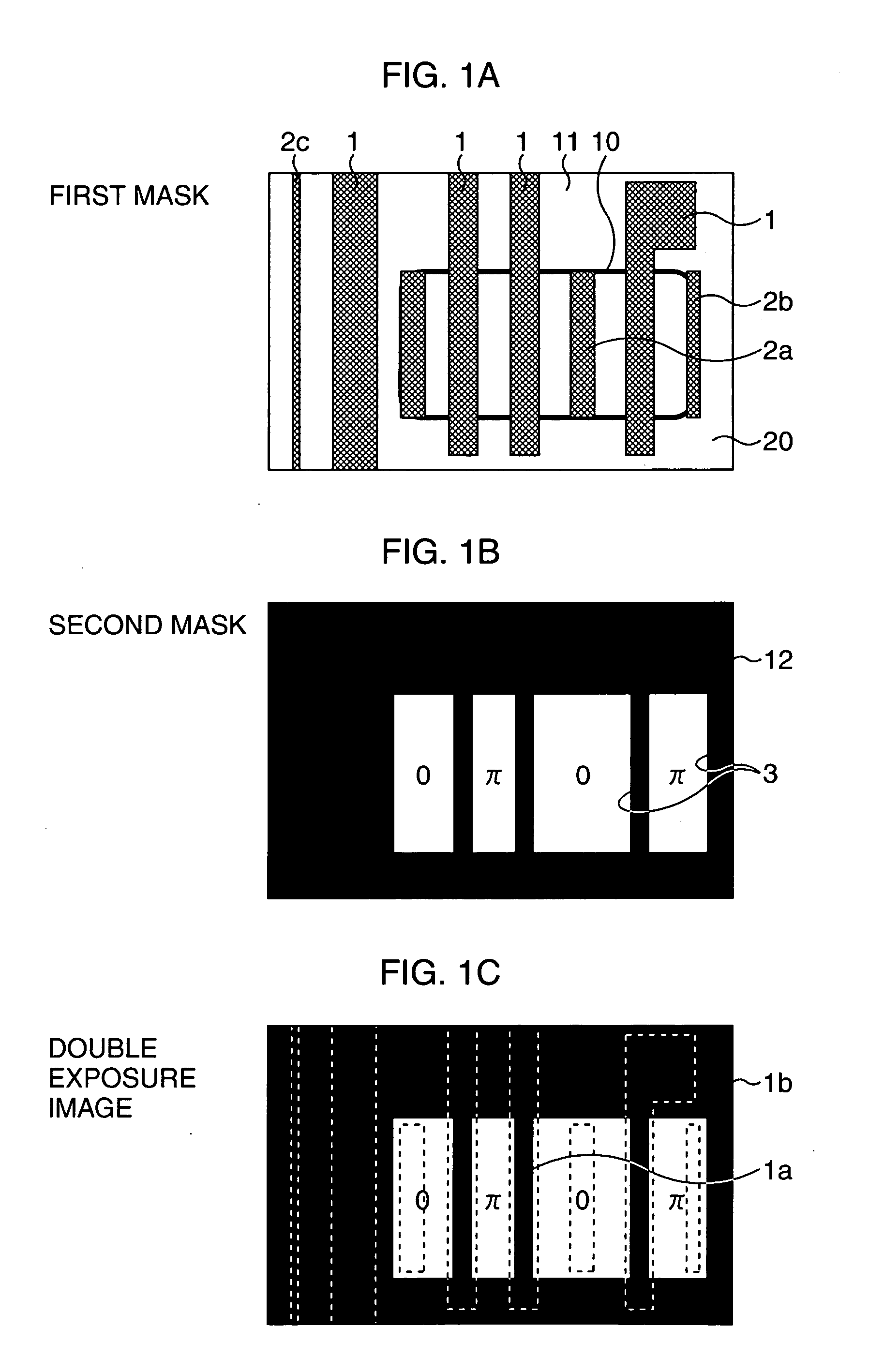

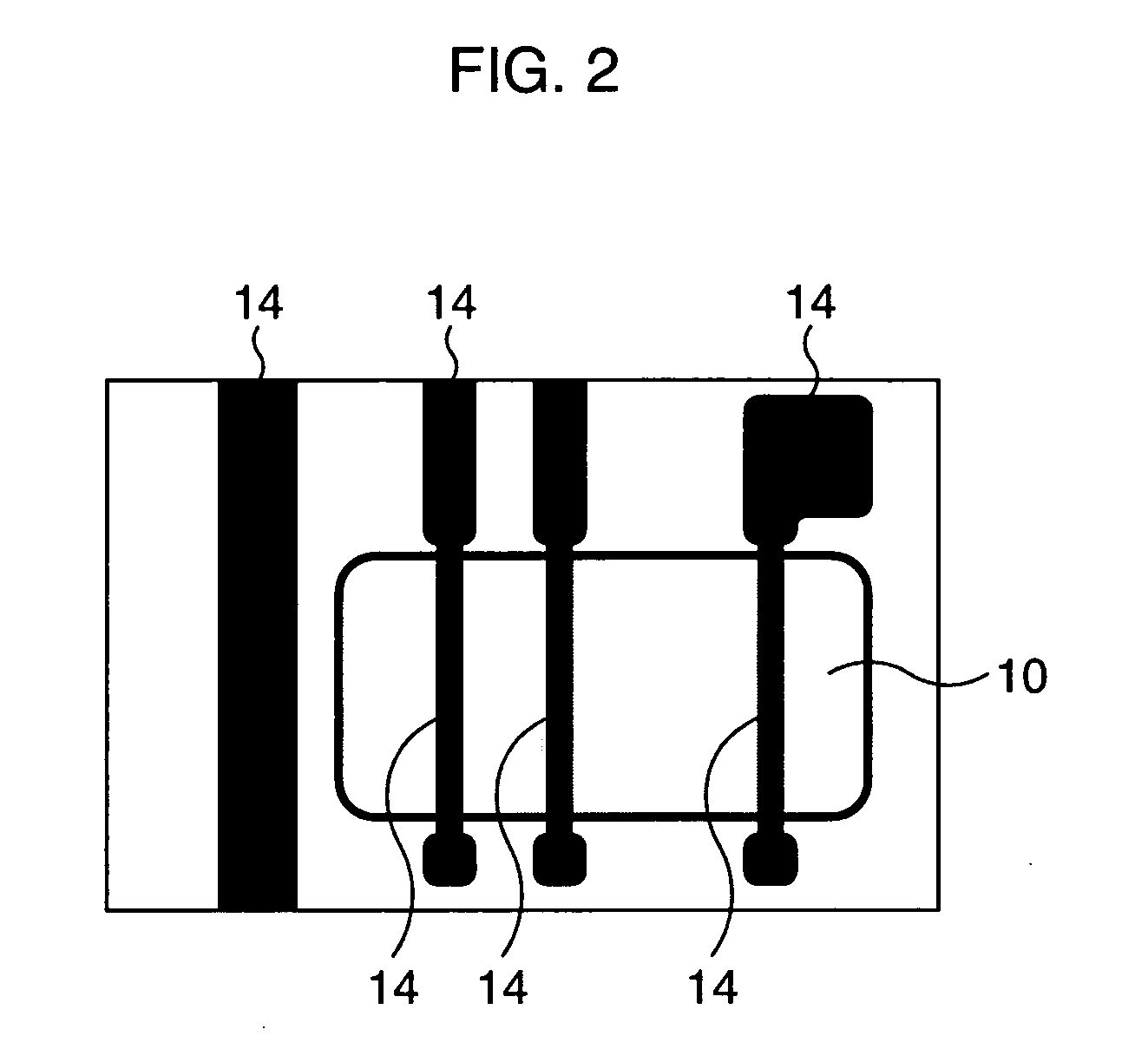

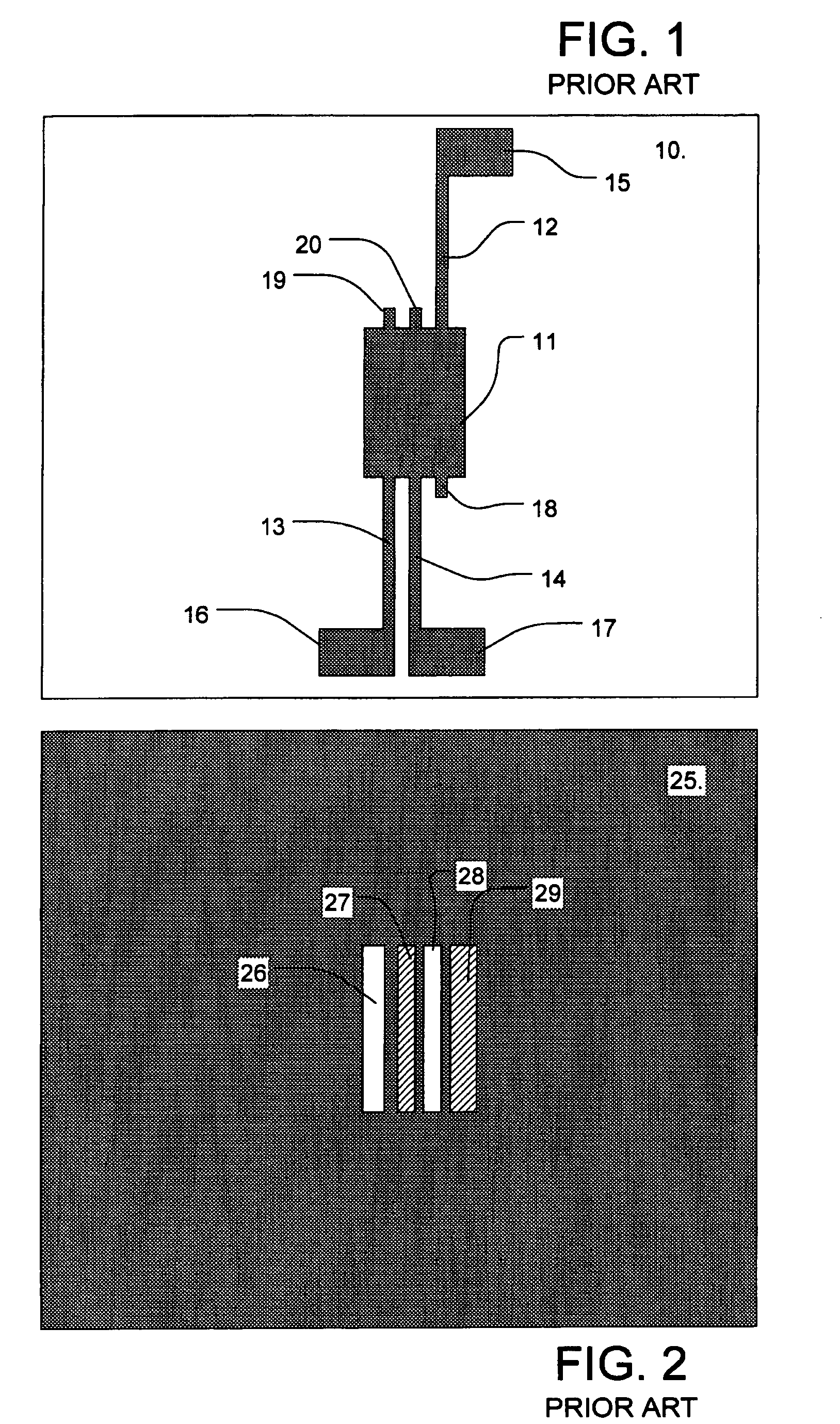

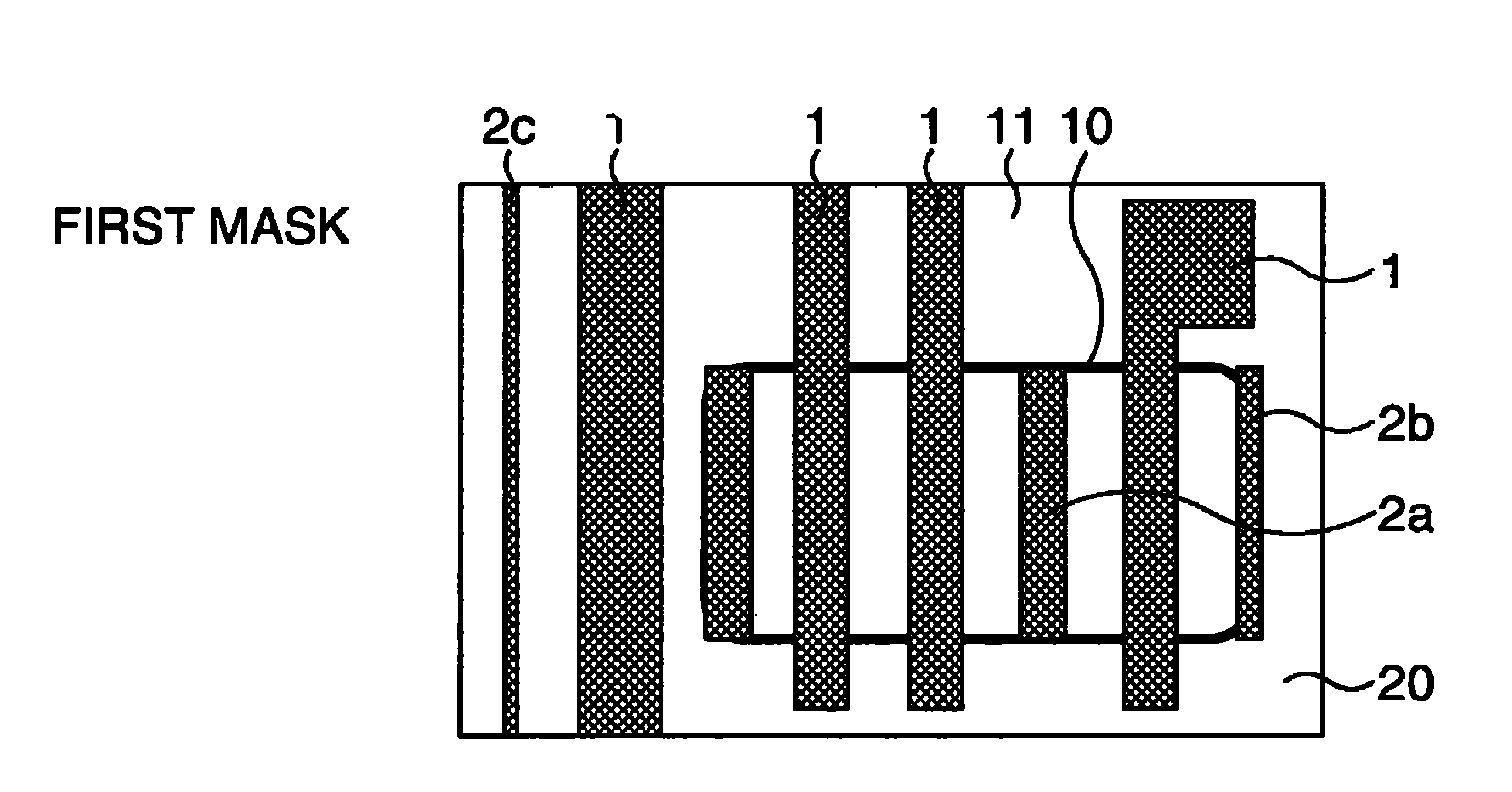

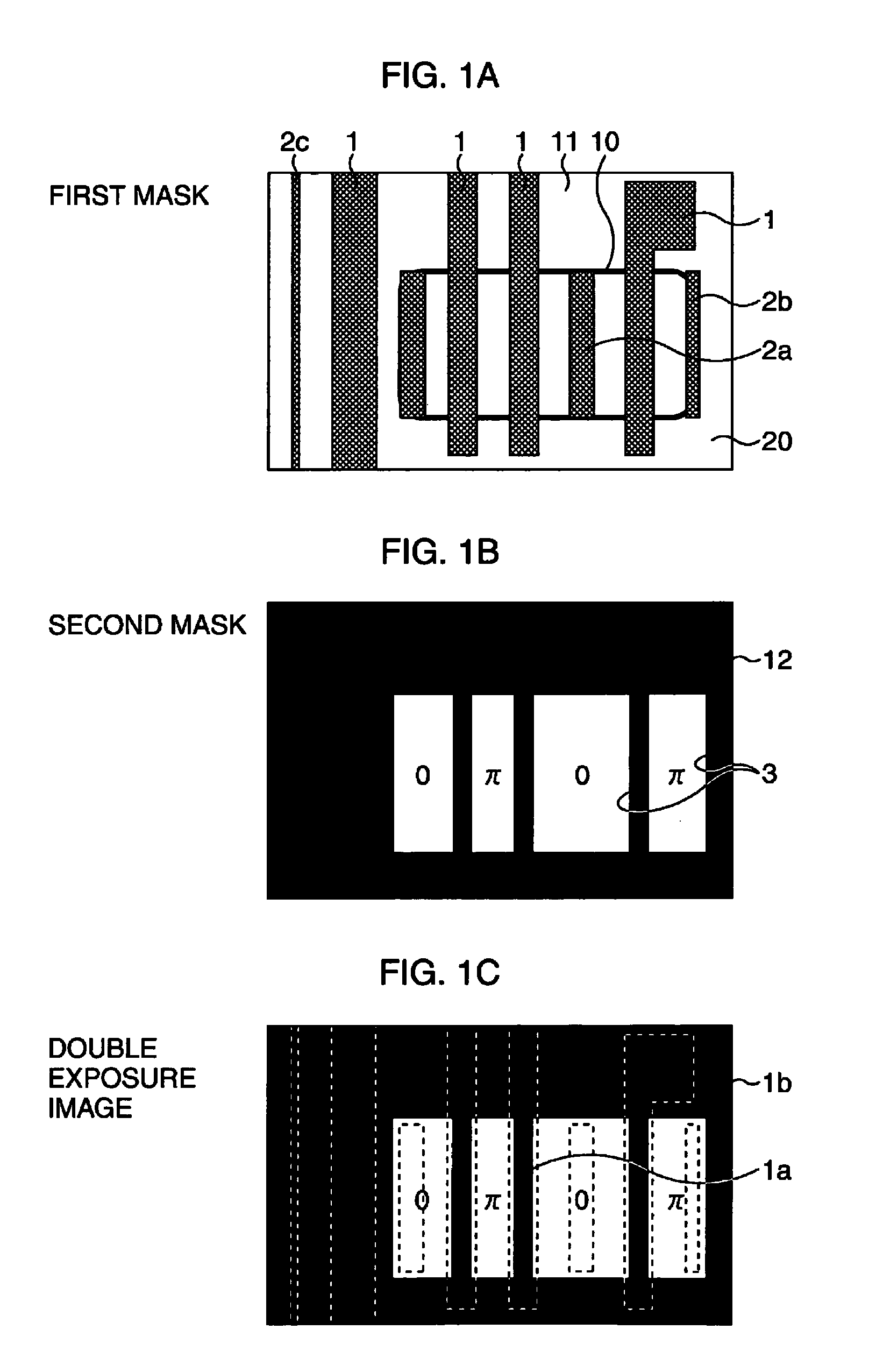

Photomask and manufacturing method of semiconductor device

InactiveUS20050164129A1Improve reliabilityHighly uniform line widthPhoto-taking processesSemiconductor/solid-state device manufacturingDevice materialImage resolution

A double exposure process is performed using a halftone phase shift mask (11) including gate patterns (1), assist patterns (2a) and (2b) with different resoluble line widths, and an assist pattern (2c) with a line width equal to or smaller than a resolution limit which are respectively inserted into portions in each of which a distance between the gate patterns (1) is large, and a Levenson phase shift mask (11) including shifter patterns (3) corresponding to the gate patterns (1) of the photomask 11. On this occasion, the assist patterns (2a), (2b), and (2c) are erased and only the gate patterns (1) are transferred. Consequently, when patterns are transferred by the double exposure process, a common depth of focus of the patterns is improved and highly uniform line widths are realized, which makes it possible to manufacture a highly reliable semiconductor device.

Owner:FUJITSU SEMICON LTD

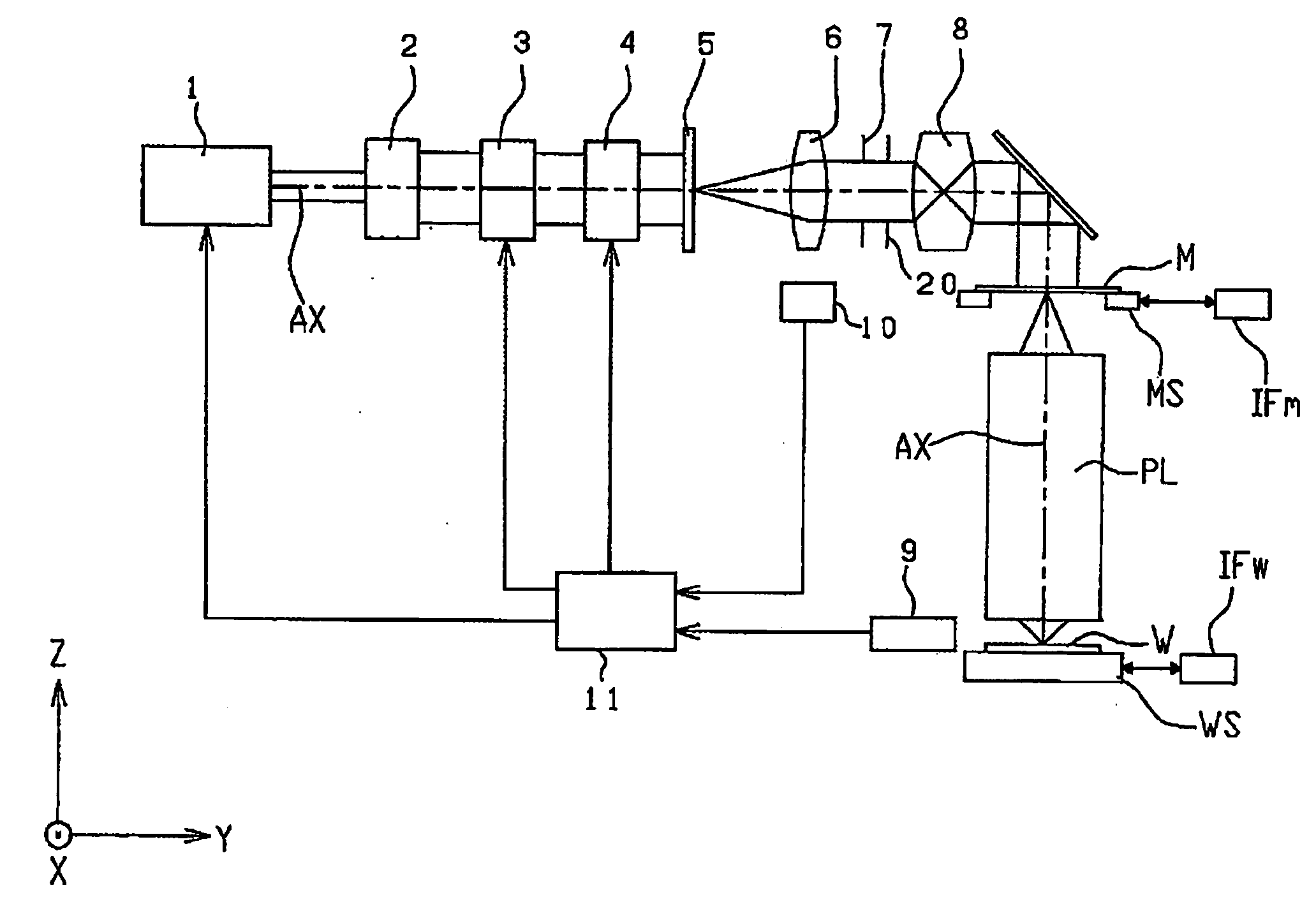

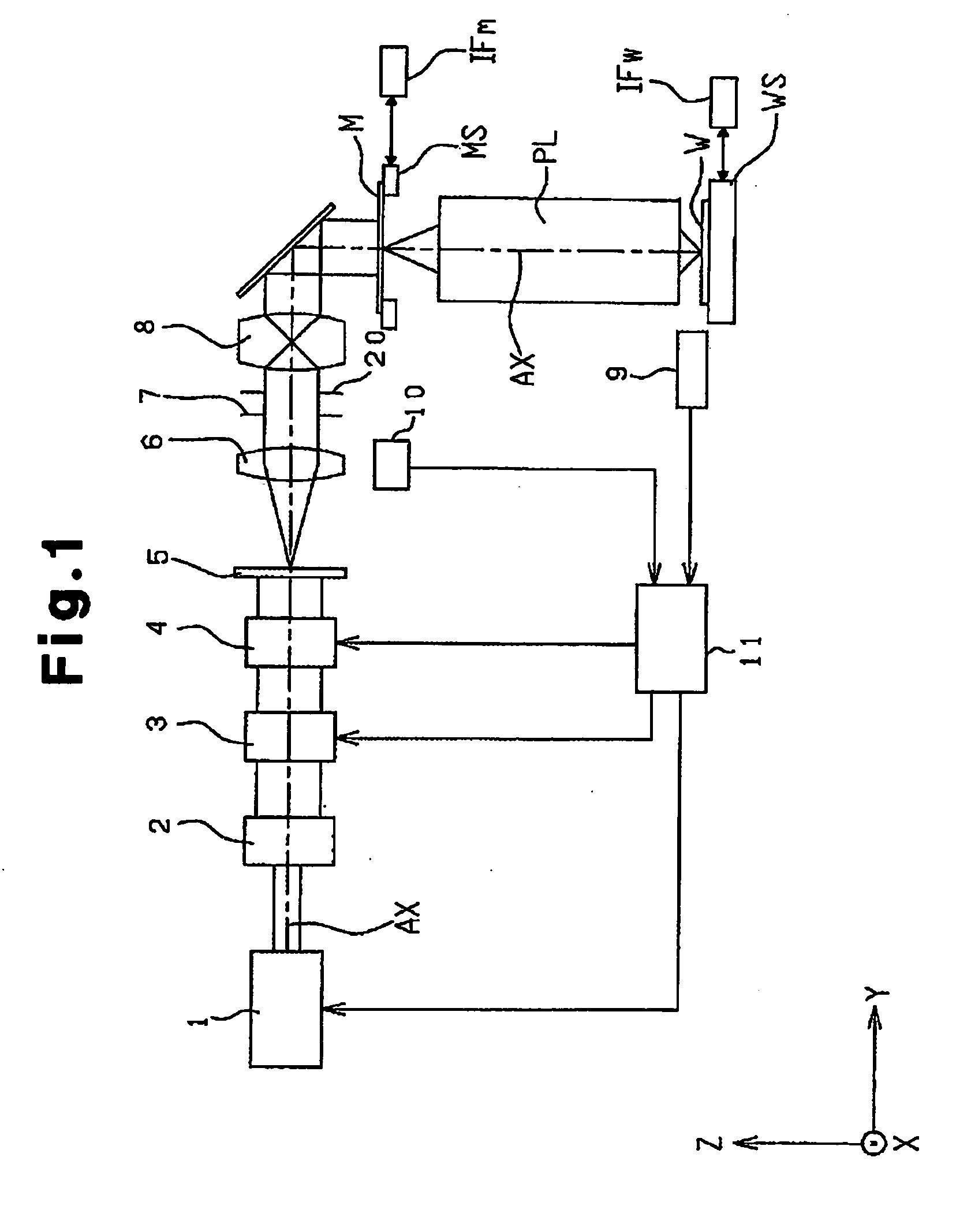

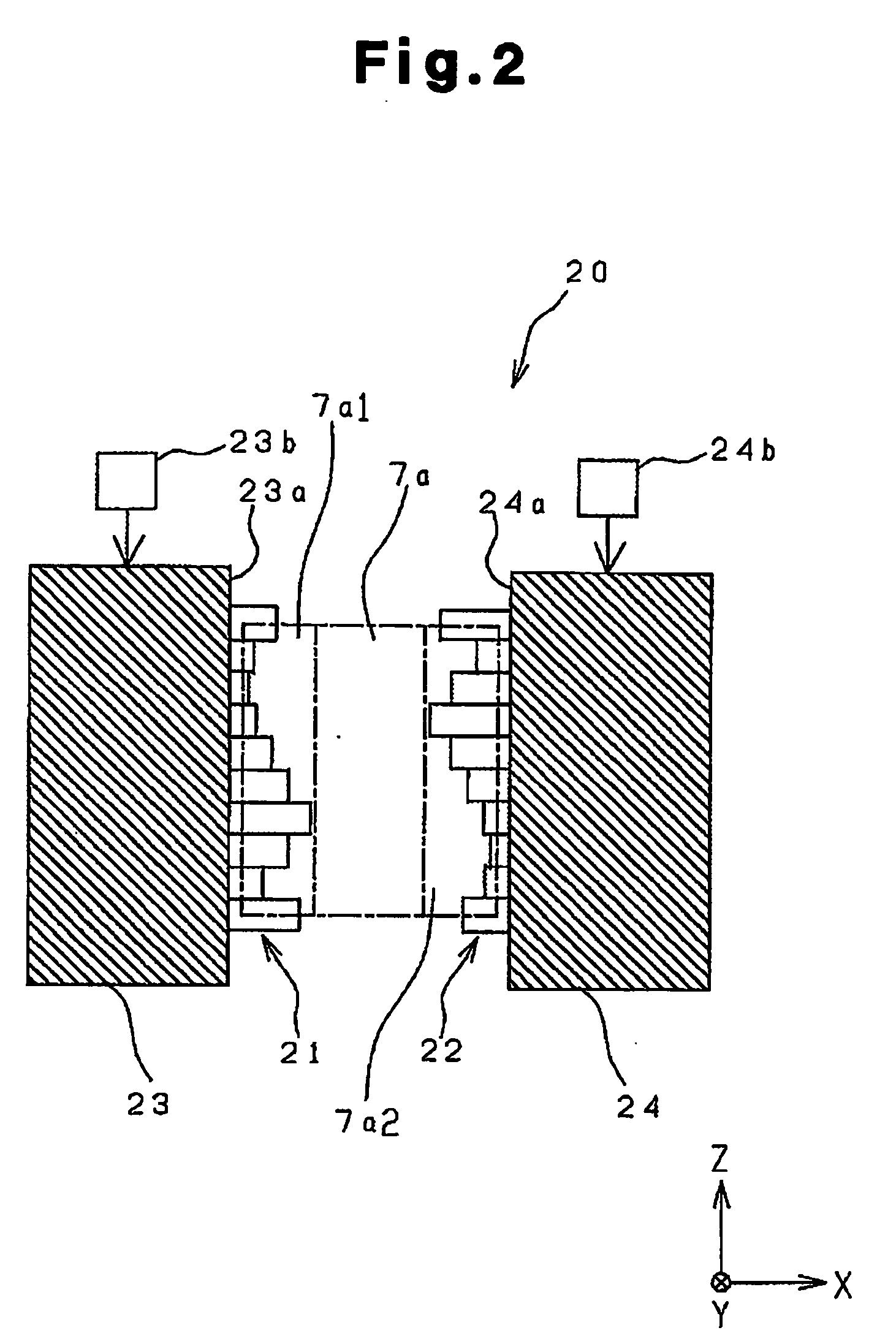

Variable slit device, illumination device, exposure apparatus, exposure method, and device manufacturing method

InactiveUS20090073404A1Uniform line widthQuick changeSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLight beamLight intensity

A variable slit device for forming illumination light having a slit shape extending in a longitudinal direction and a lateral direction. A first light intensity setting unit sets a first light intensity distribution, which is the light intensity distribution of a peripheral portion, which is one of a pair of peripheral portions extending along the longitudinal direction of the slit shape. A second light intensity setting unit sets a second light intensity distribution, which is the light intensity distribution of a peripheral portion, which is the other one of the pair of peripheral portions. Selection members select a first portion of a light beam that has the first light intensity distribution and a second portion of the light beam that has the second light intensity distribution.

Owner:NIKON CORP

Temperature setting method for heat treating plate, temperature setting device for heat treating plate, program and computer-readable recording medium recording program

ActiveCN101120434AUniform line widthForm evenlySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingLine widthEngineering

Temperature setting of a thermal plate is performed so that the line width of a resist pattern is uniformly formed within a wafer. The thermal plate of a PEB unit is divided into a plurality of thermal plate regions so that the temperature can be set for each of the thermal plate regions. A temperature correction value for adjusting the temperature within the wafer mounted on the thermal plate is set for each of the thermal plate regions of the thermal plate. The temperature correction value for each of the thermal plate regions of the thermal plate is set after calculation by a calculation model created from a correlation between a line width of the resist pattern formed by thermal processing on the thermal plate and the temperature correction value. The calculation model M calculates the temperature correction value to make the line width uniform within the wafer, based on a line width measured value of the resist pattern.

Owner:TOKYO ELECTRON LTD

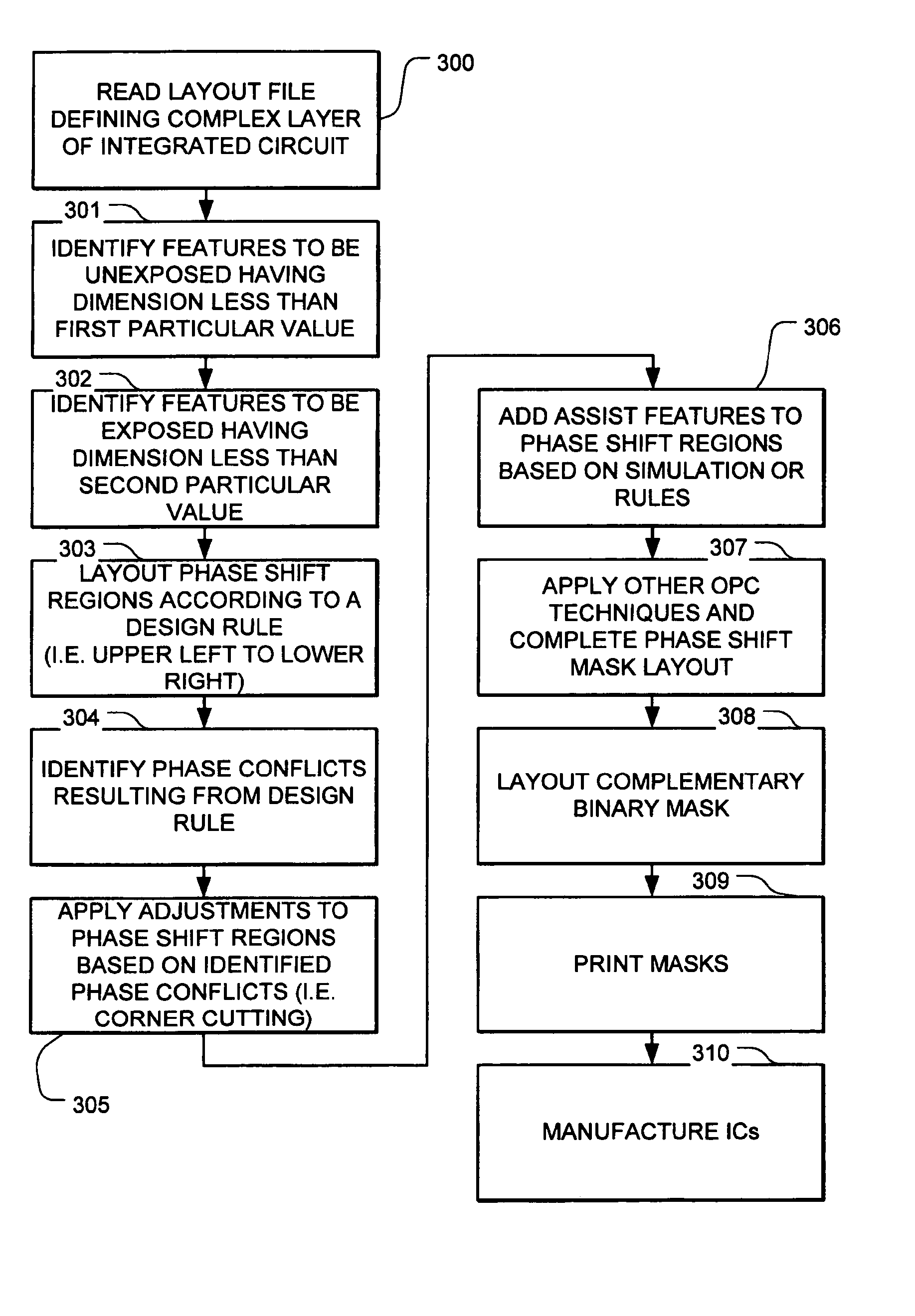

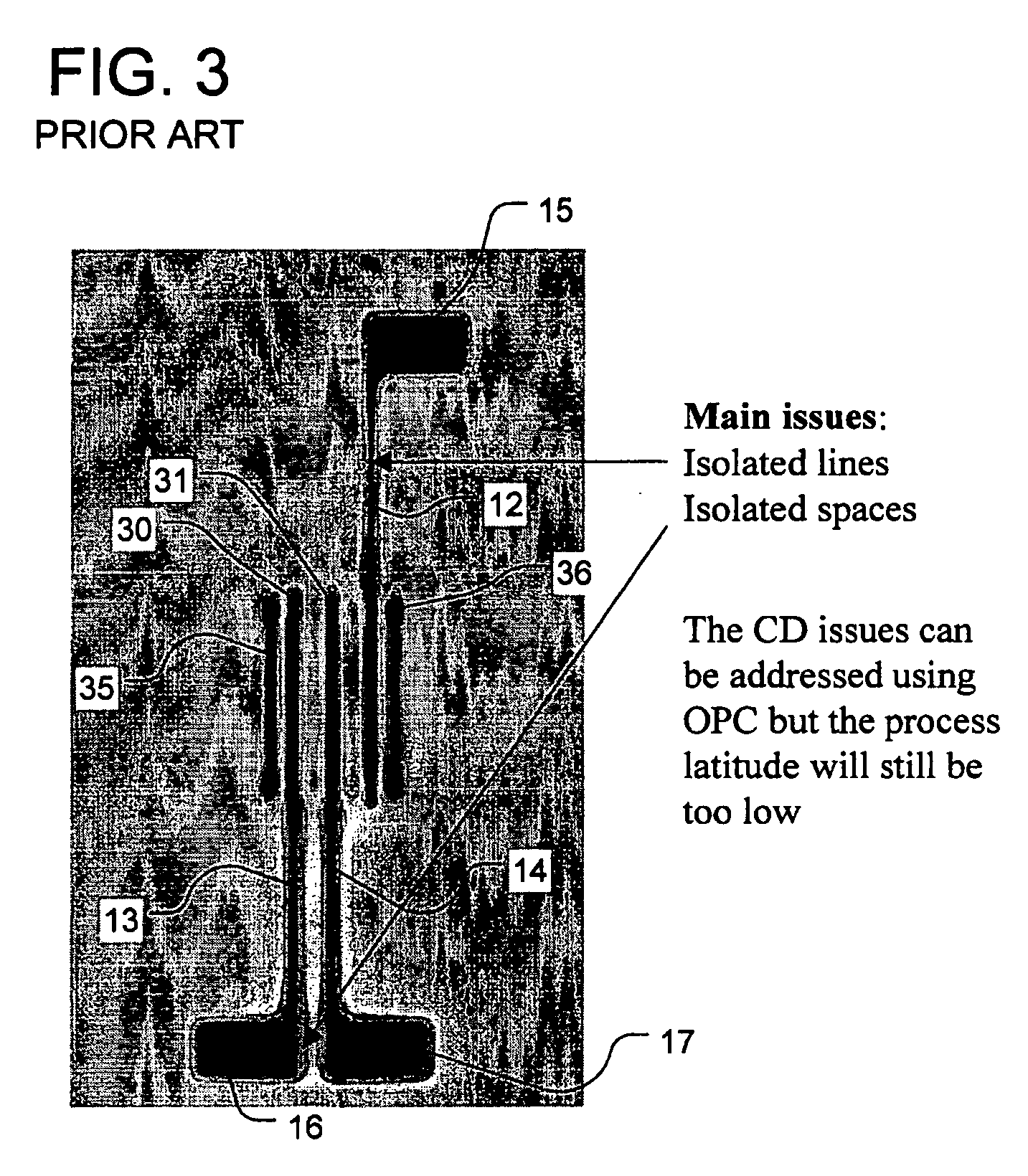

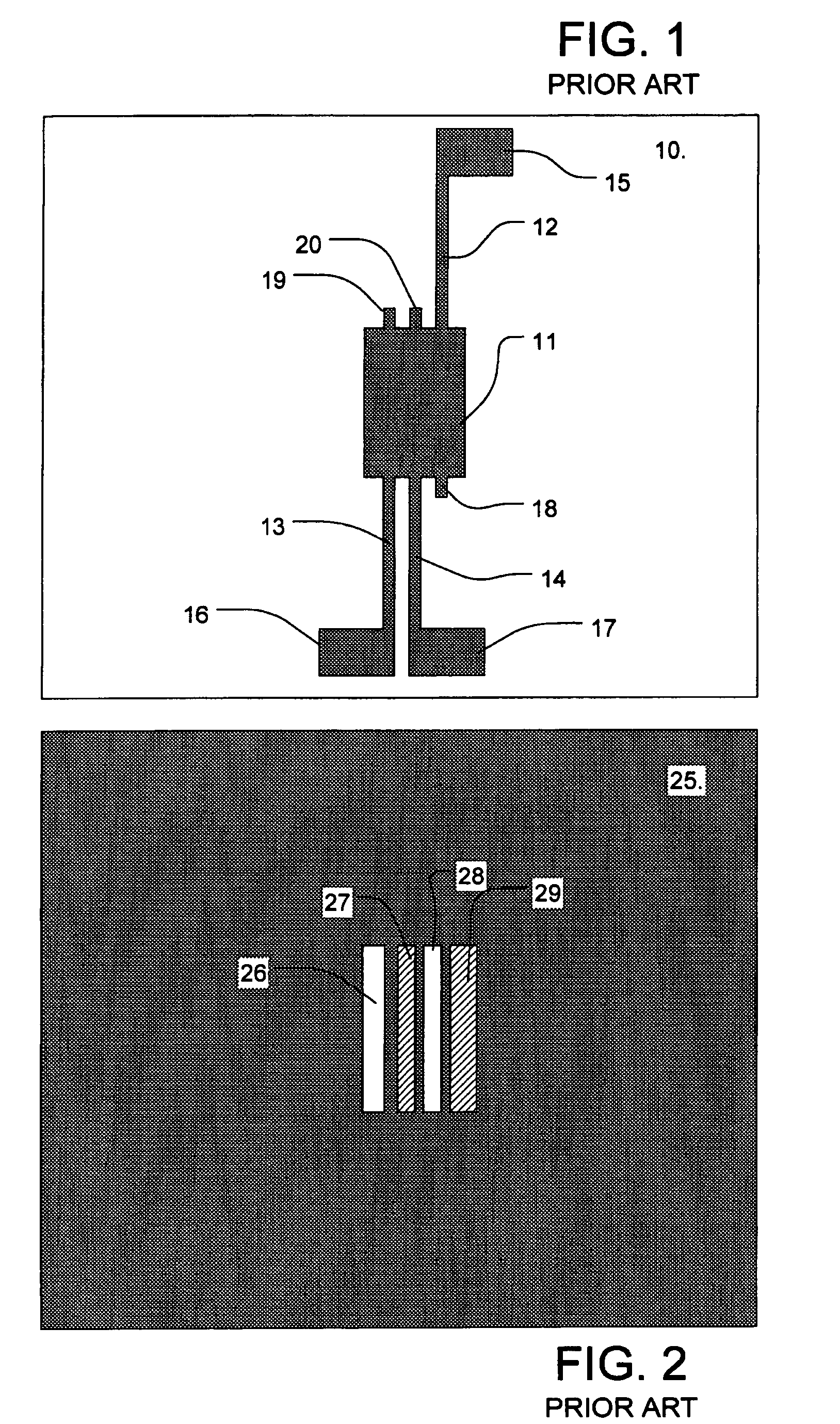

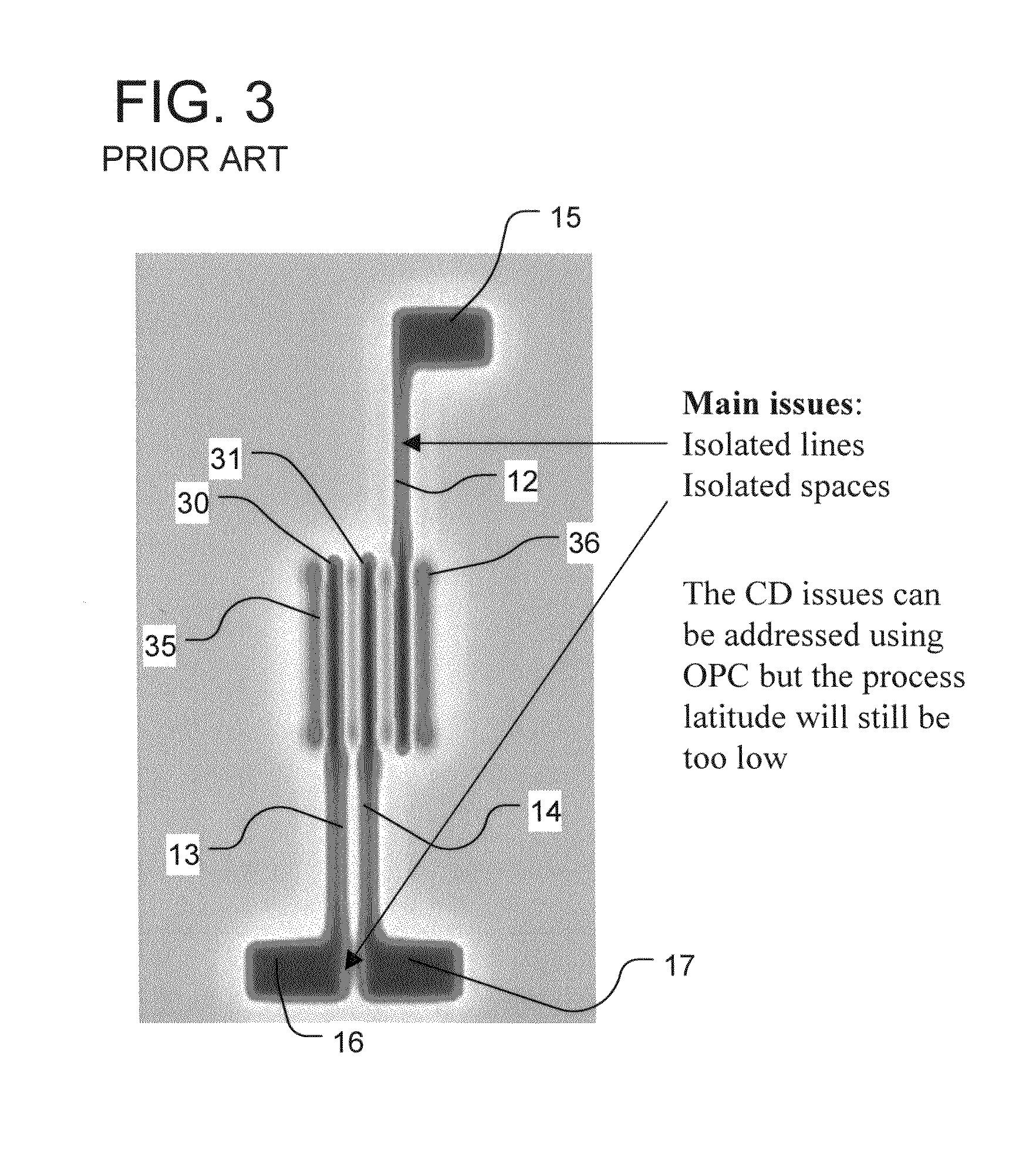

Phase shift mask including sub-resolution assist features for isolated spaces

InactiveUS20050042527A1Prevent and minimize phase conflictImproved small dimension structureOriginals for photomechanical treatmentSpecial data processing applicationsPhase shiftedEngineering

Owner:SYNOPSYS INC

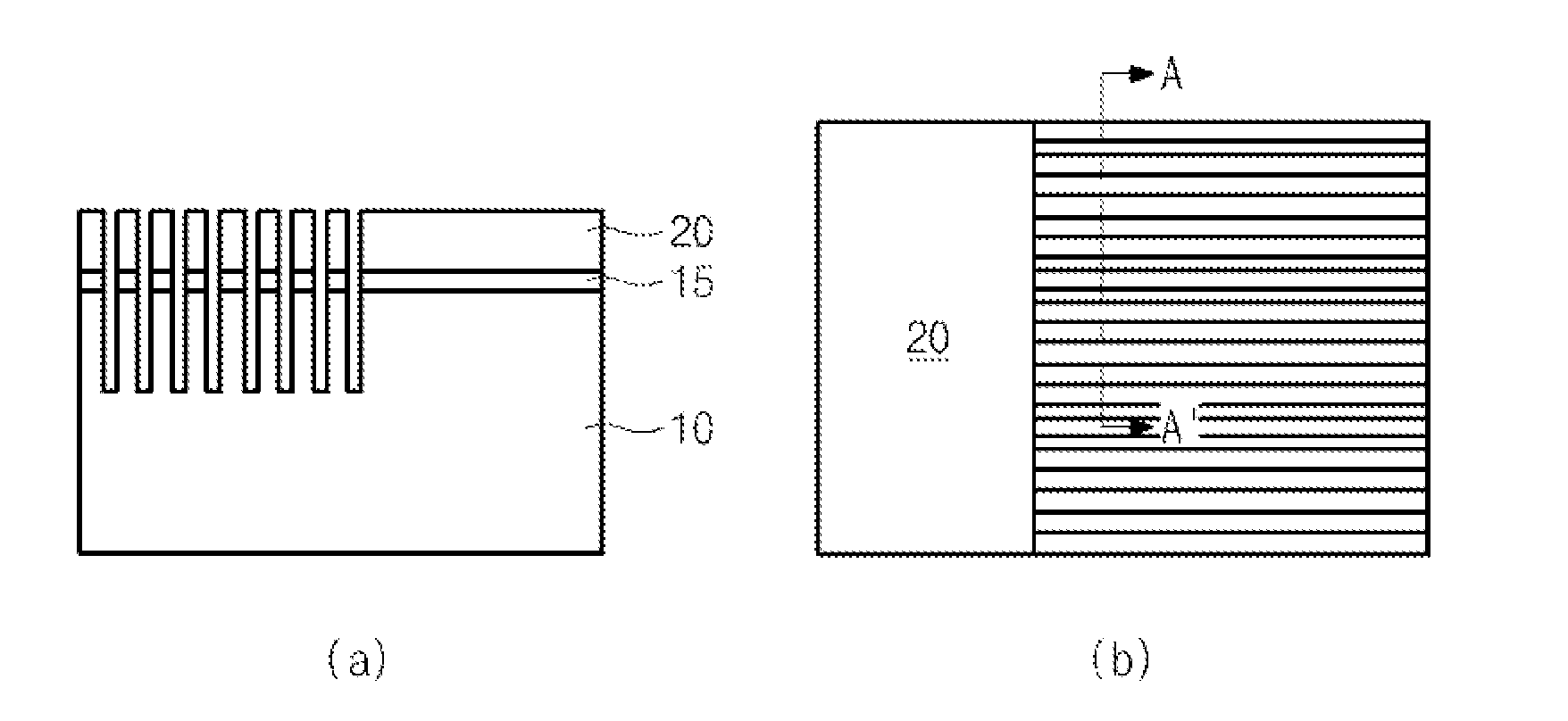

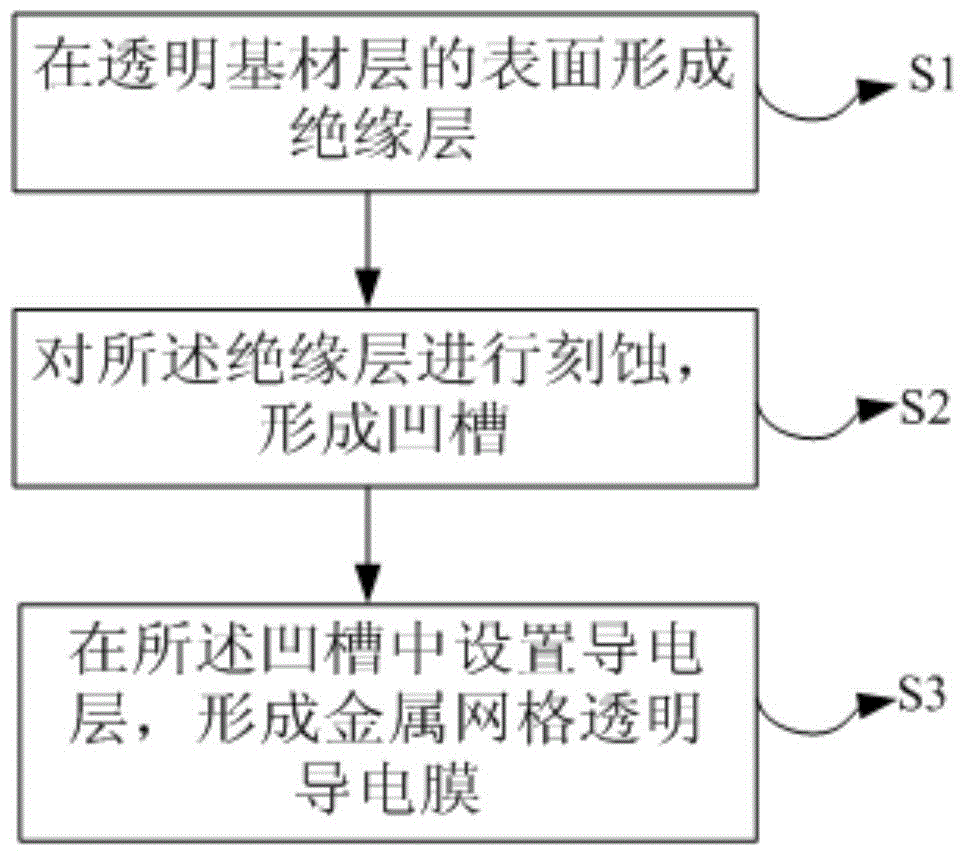

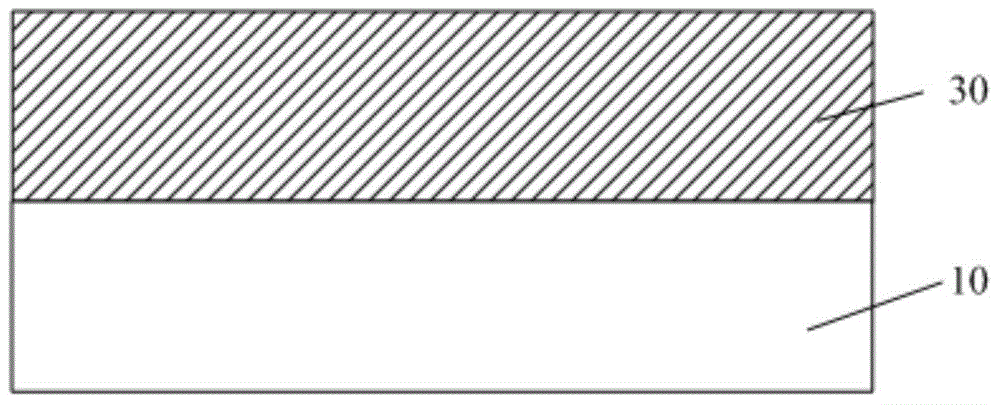

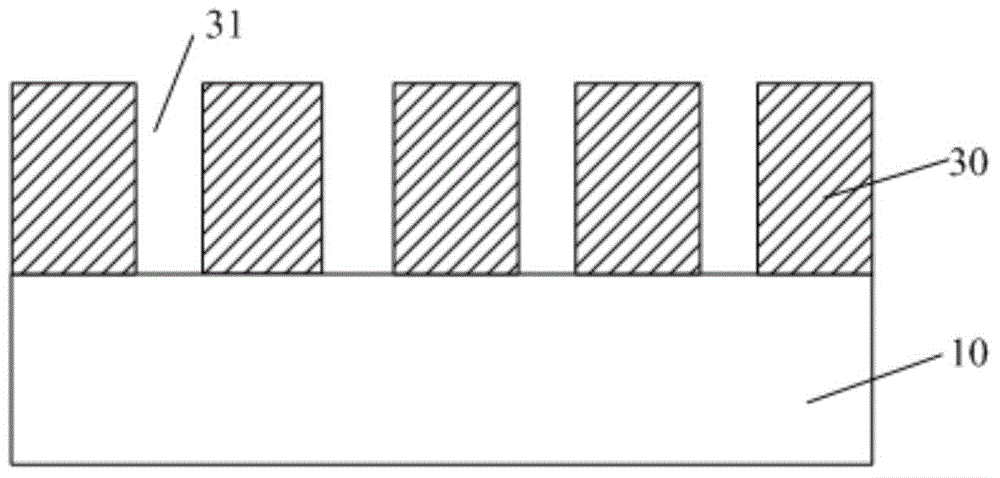

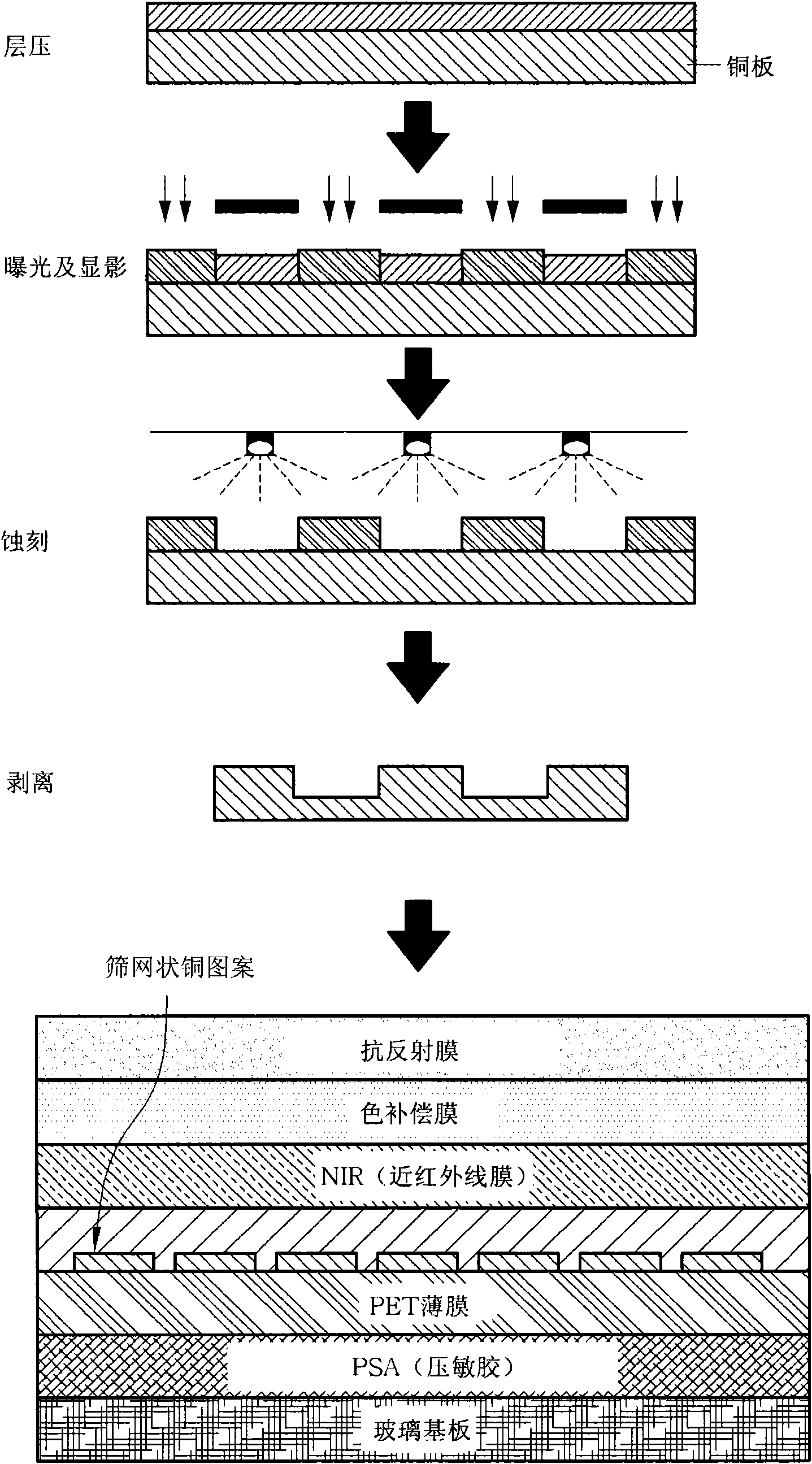

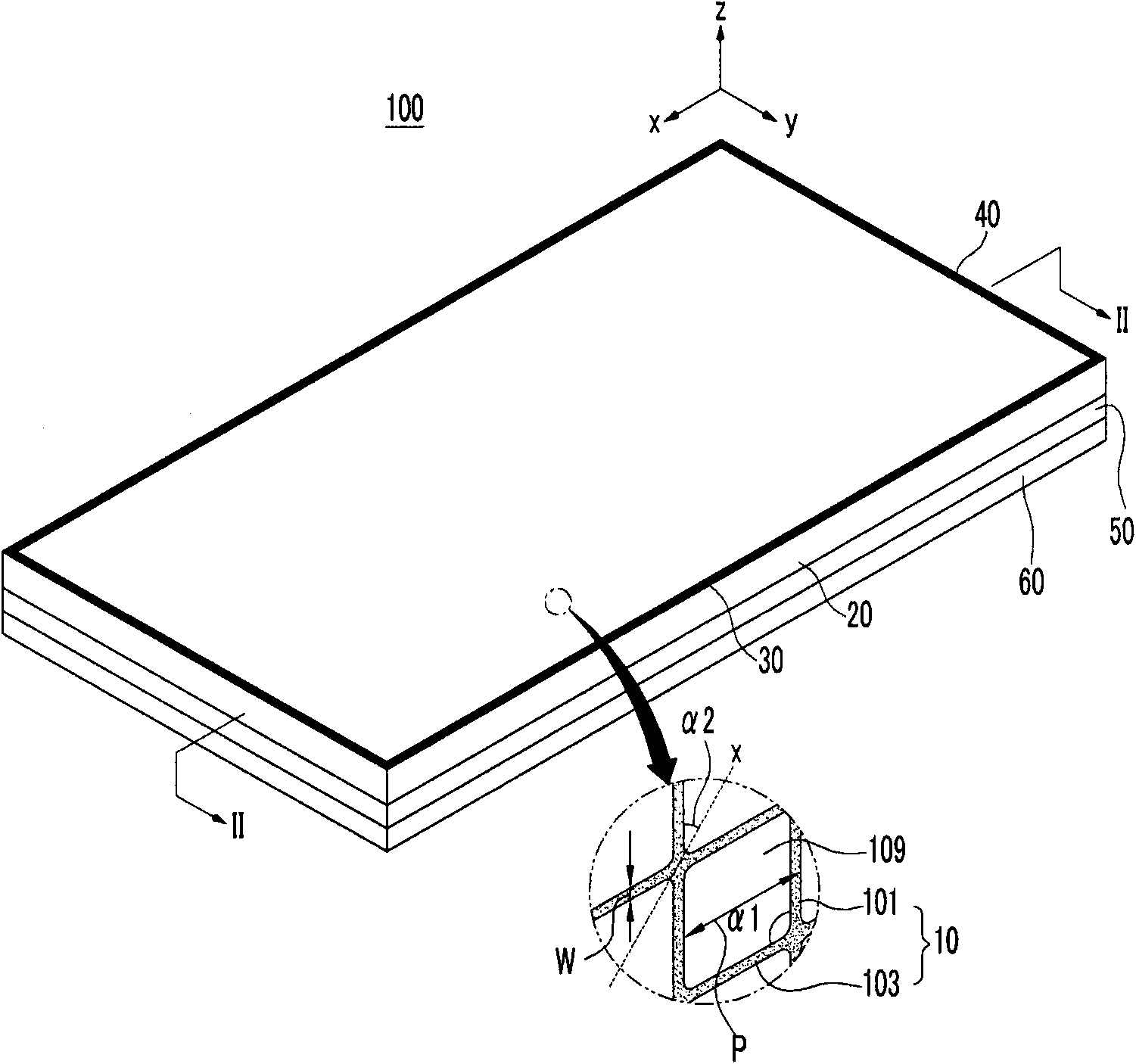

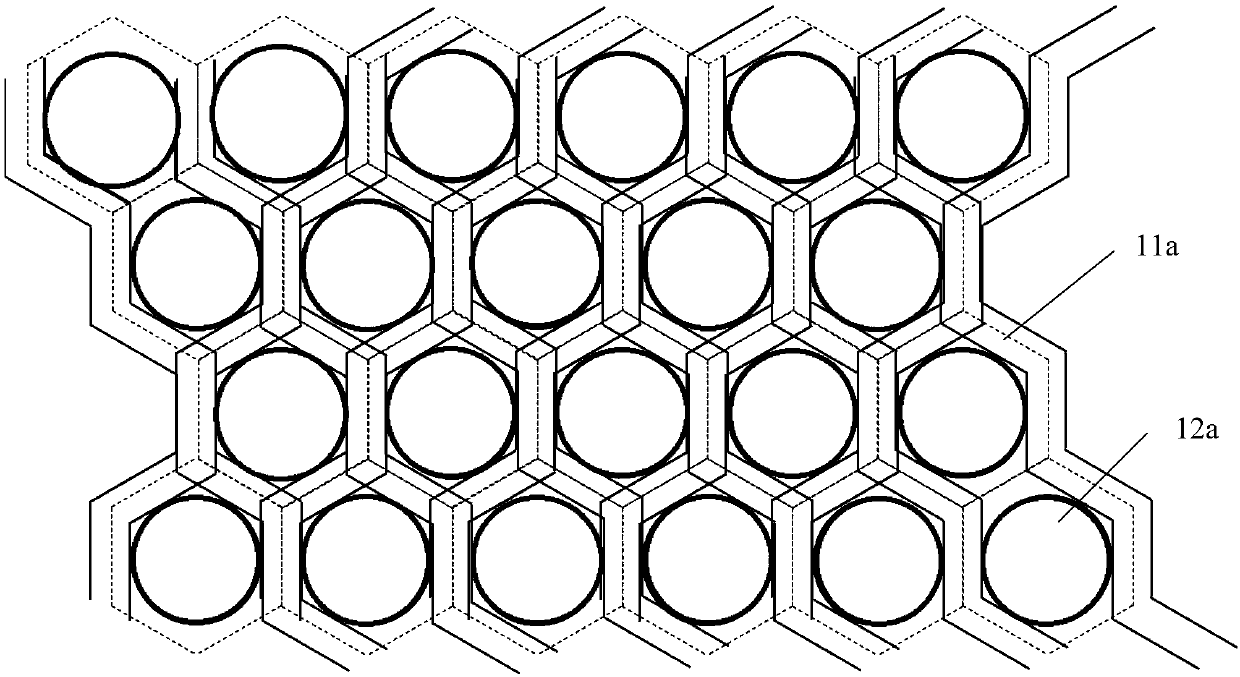

Metal grid transparent conducting film, preparation method thereof and capacitive touch screen

InactiveCN105045455AUniform line widthImprove visibilityInput/output processes for data processingLine widthTransparent conducting film

The invention provides a metal grid transparent conducting film, a preparation method thereof and a capacitive touch screen. The preparation method of the metal grid transparent conducting film includes the steps that S1, insulating layers are formed on the surface of a transparent base material layer; S2, the insulating layers are etched, so that grooves are formed; S3, conducting layers are arranged in the grooves, and accordingly the metal grid transparent conducting film is formed. The metal grid transparent conducting film prepared through the method is even in line width, and the micron grade and even hundreds-of-nanometer grade can be achieved. The preparation method is suitable for mass production of metal grid transparent conducting films, and the yield of the metal grid transparent conducting films can be increased.

Owner:ZHANGJIAGANG KANGDE XIN OPTRONICS MATERIAL

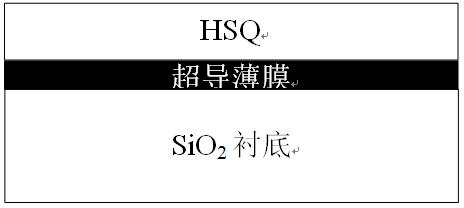

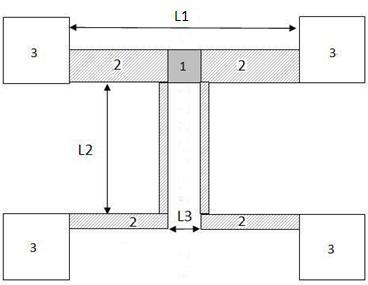

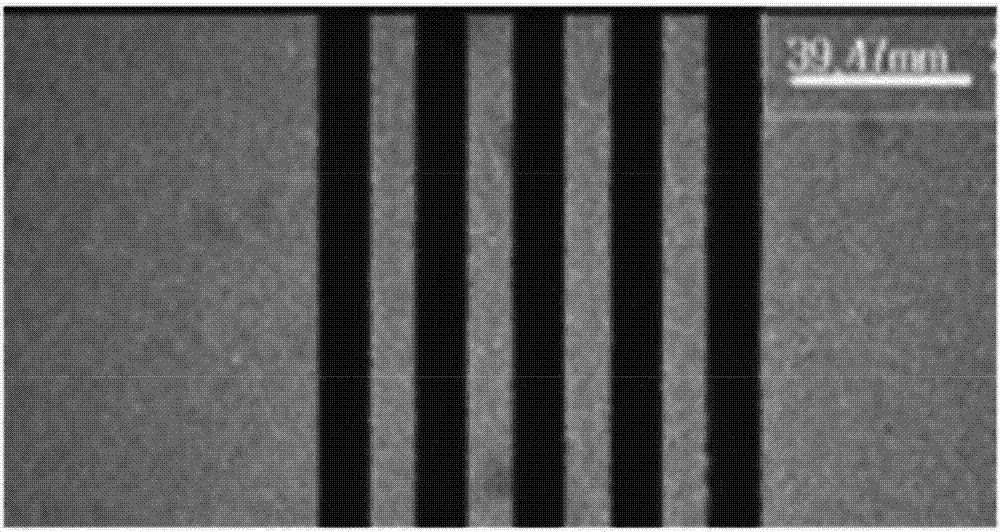

Method for preparing superconductive nanometer device by negative electron beam resist exposure process

ActiveCN102653392AStable performanceUniform line widthDecorative surface effectsChemical vapor deposition coatingPhysicsElectrical measurements

The invention discloses a method for preparing a superconductive nanometer device by a negative electron beam resist exposure process. The method mainly comprises the following steps of: spinning a hydrogen silsesquioxane (HSQ) resist on a superconductive thin film; pre-drying; designing an exposure graph; exposing by two steps; developing; fixing; and etching. By using the method, the superconductive nanometer device which is stable in performance and uniform in line width and has the minimum line width of 15 nm can be prepared. Residues do not exist in an electrode region after the etching step is performed by setting an exposure amount in different regions and changing the thickness of an exposure product in the corresponding region, so that electrical measurement is facilitated. HSQ has high anti-etching performance and is suitable to serve as an etching mask of a hard superconductive metal material, so that the etching selection ratio can be increased. An electrode and the device are obtained through one-time etching; no contact potential difference exists between the electrode and the device; and the success rate of the device is high. Furthermore, a plurality of independent micro electric bridges are exposed on the same thin film, so that the efficiency of integrating and measuring the electric bridges can be improved, and the material utilization rate is increased; and the superconductive nanometer device has great significance for research on nanometer structures made of rare materials.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

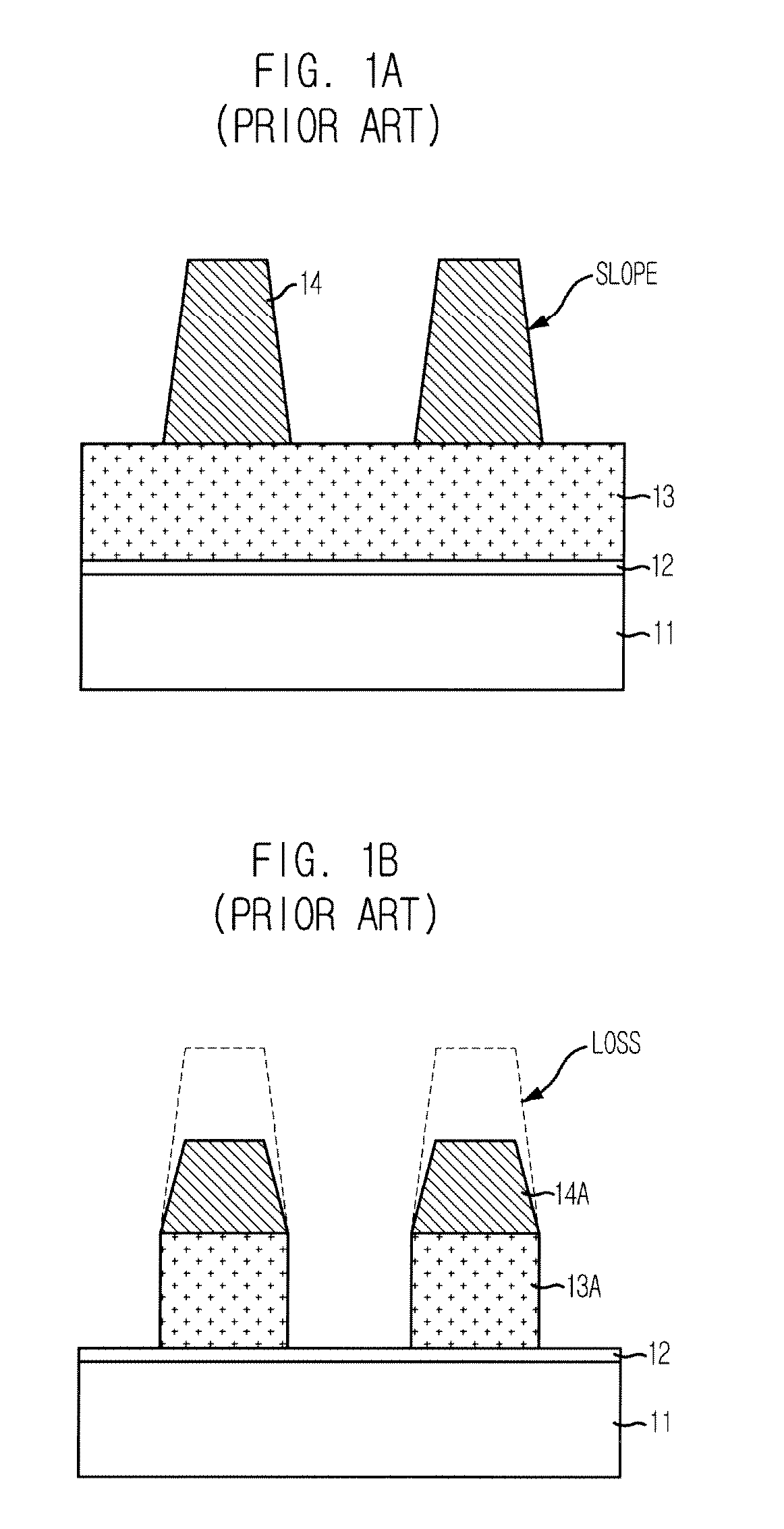

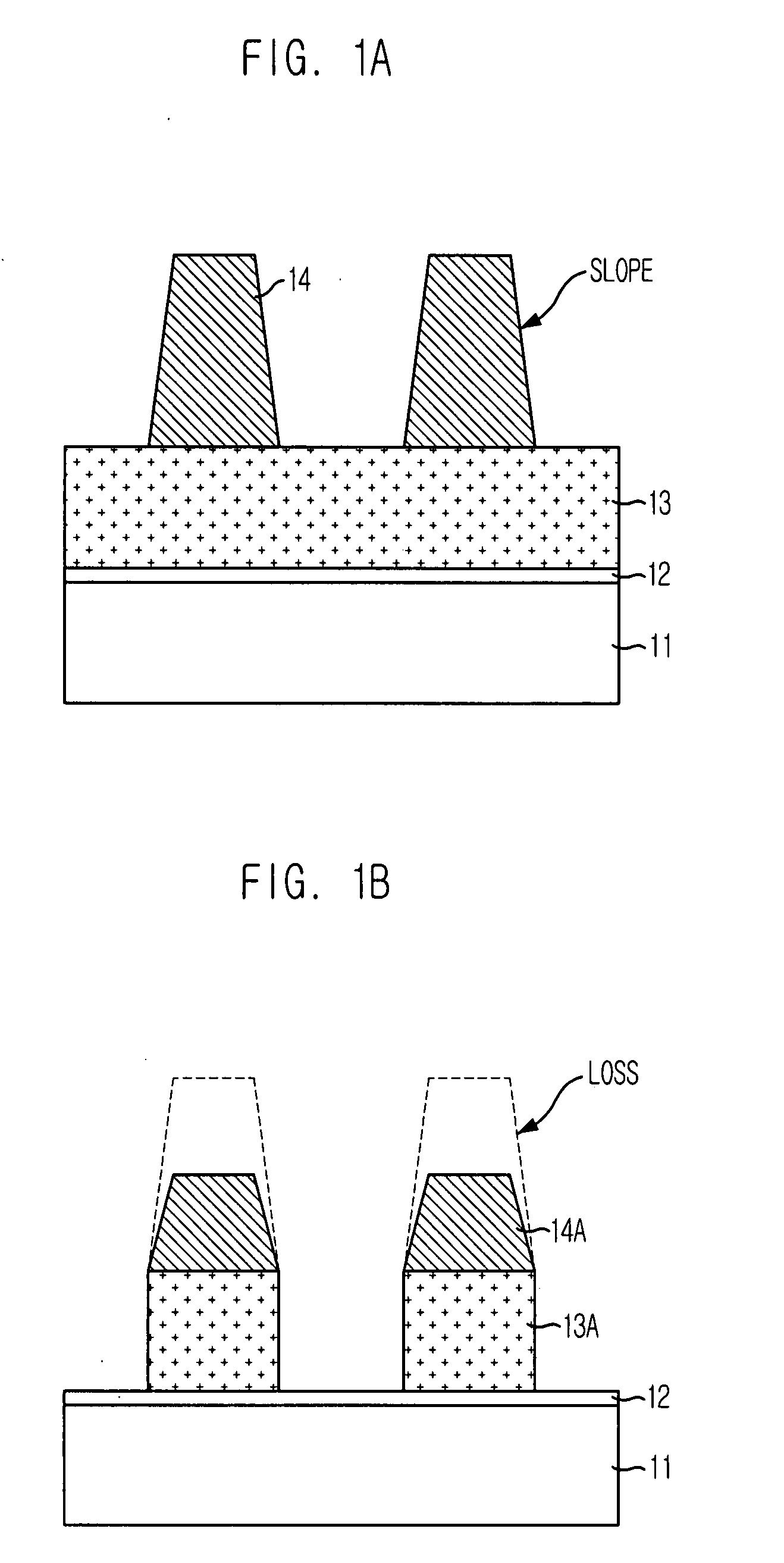

Etching method using hard mask in semiconductor device

InactiveUS7807574B2Reducing a loss on a hard maskUniform line widthNon-mechanical controlsSemiconductor/solid-state device manufacturingNitrideSemiconductor

Owner:SK HYNIX INC

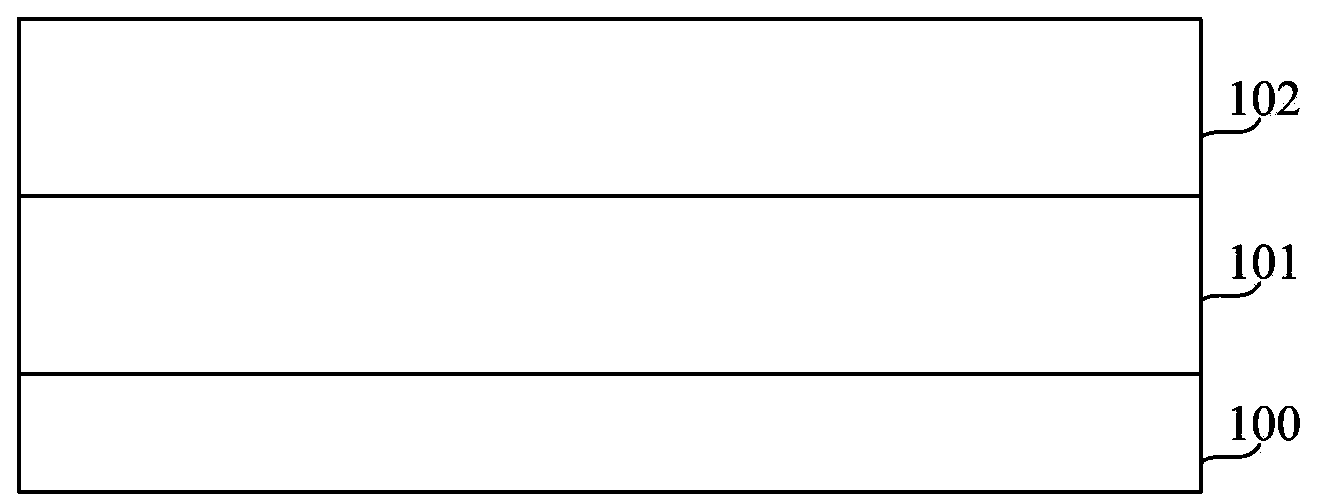

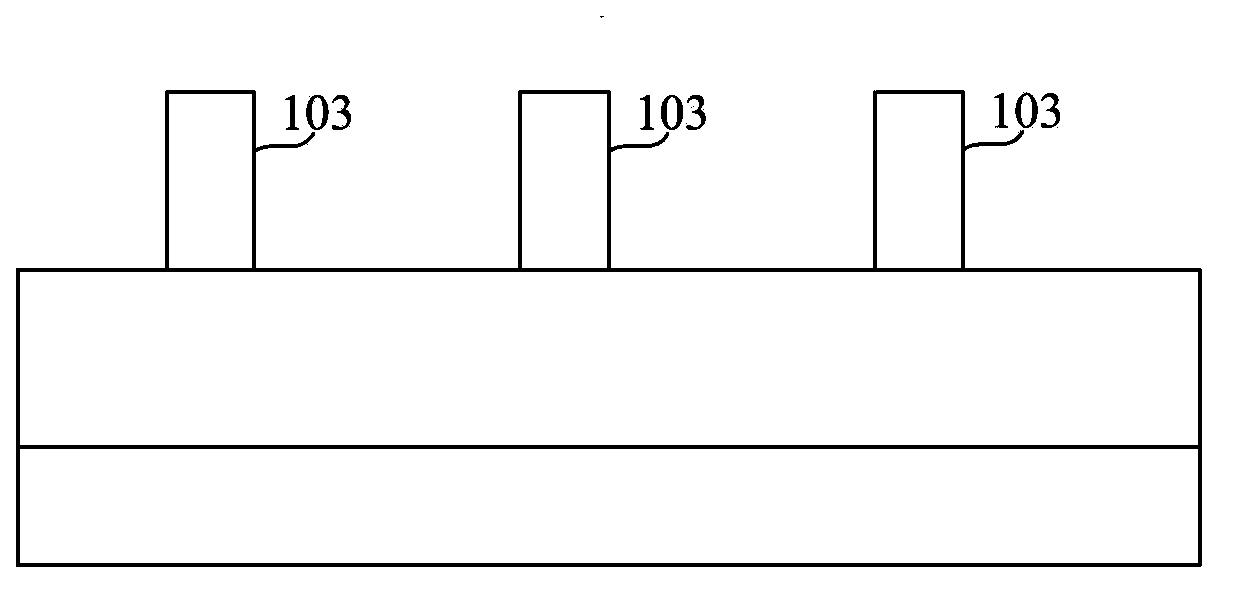

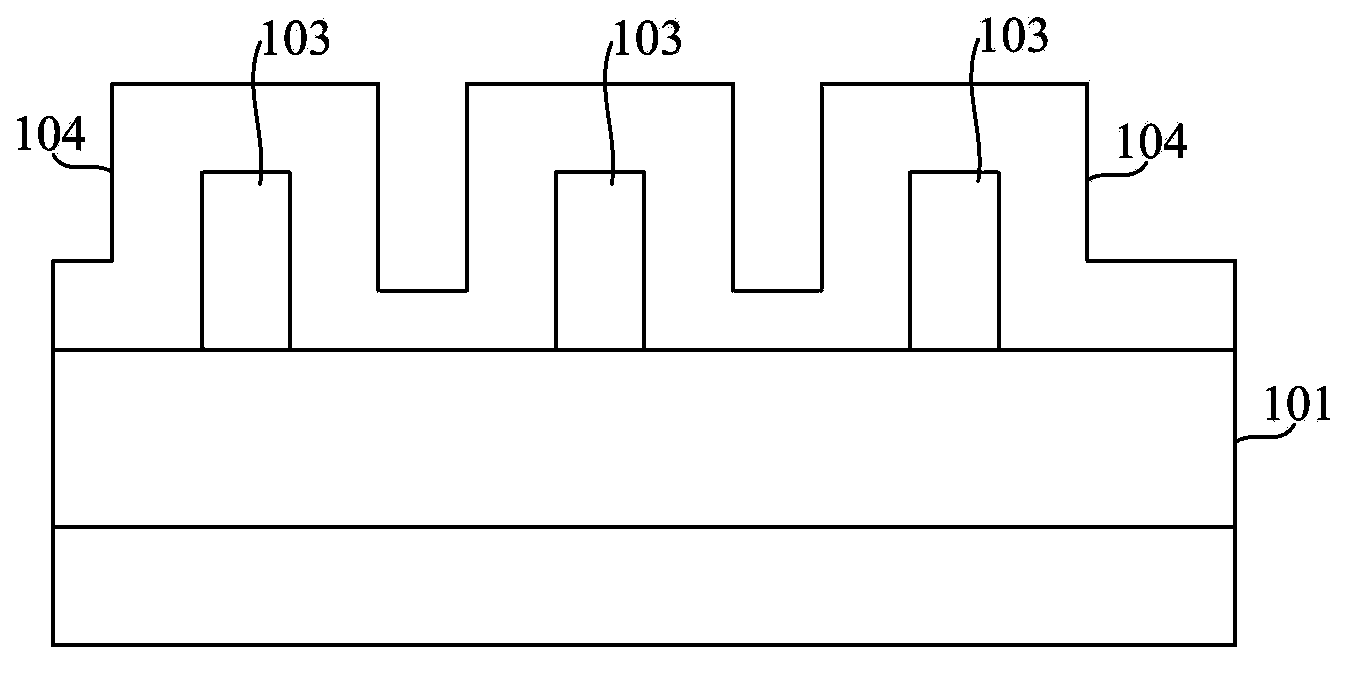

Pattern forming method

ActiveCN103915332AHigh precisionUniform arrangement densitySemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A pattern forming method comprises the steps that a film layer and an etching barrier layer placed on the film layer are formed on a substrate; a plurality of first patterns, which are arrayed in parallel at equal intervals, of a first line are formed on the etching barrier layer; a second line is formed on the side wall of the first line, wherein the line width of the second line is equal to the line width of the first line, and the second line is made of materials different from that of the first line; a third line is formed in the side wall of the second line, and the line width of the third line is equal to the line width of the first line; a fourth line is arranged on the side wall of the third line in an epitaxial growth mode, the line width of the fourth line is equal to the line width of the first line, and the fourth line is made of materials different from that of the third line; the parts, which are not covered with the first line, the second line, the third line and the fourth line, of the etching barrier layer are removed to expose the film layer; a fifth line is arranged on the film layer in an epitaxial growth mode, and the fifth line is made of materials different from that of the fourth line; the second line and the fourth line are removed, and the patterns which are finally formed comprise the first line, the second line and the fifth line. The patterns have even array density and a good line width, and therefore a semiconductor device formed by the patterns is good in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

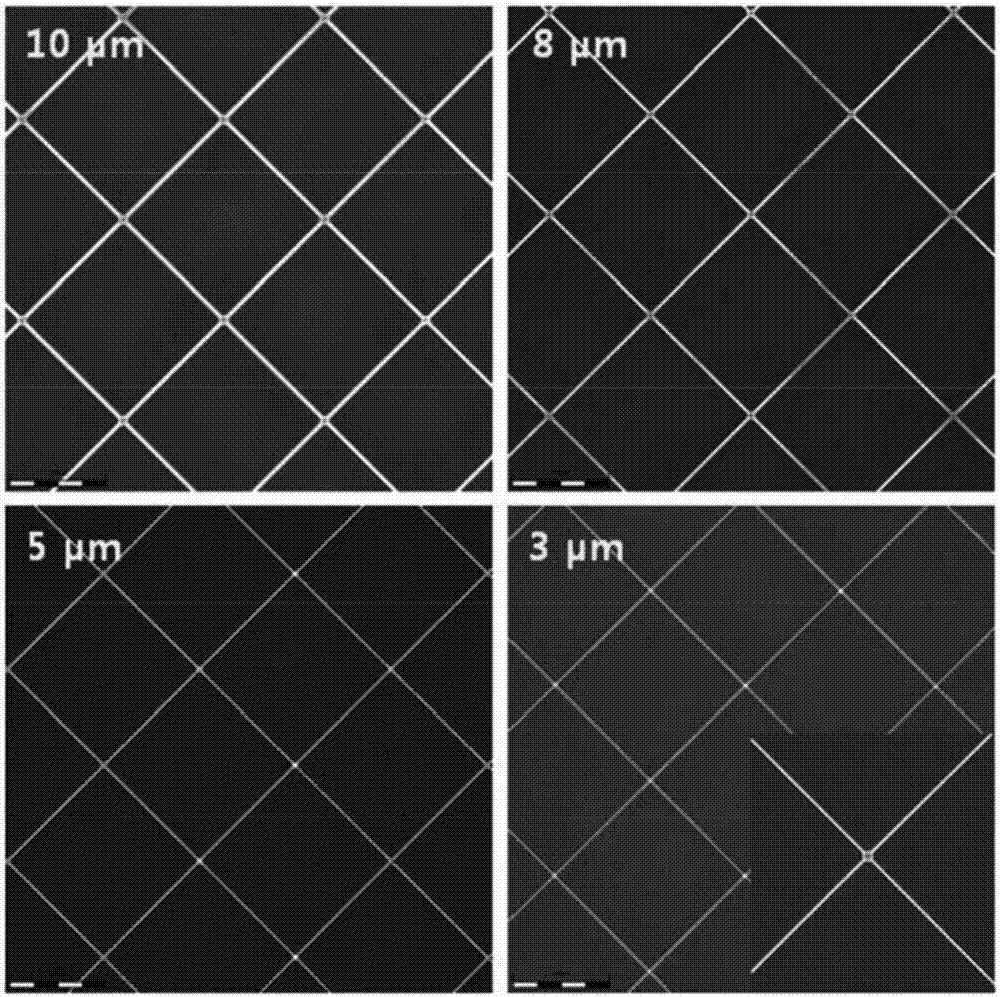

Method for forming electrode patterns and electrode patterns

InactiveCN107003787AHigh resolutionUniform line widthConductive layers on insulating-supportsPhotomechanical apparatusMicroelectrodeEngineering

The present invention relates to a method for forming electrode patterns. The method for forming the electrode patterns of the present invention is applicable to various devices which require microelectrode patterning and, particularly, is useful to be applicable to forming a touch sensor provided in a touch screen panel (TSP).

Owner:DONGJIN SEMICHEM CO LTD

Phase shift mask including sub-resolution assist features for isolated spaces

InactiveUS7585595B2Improved small dimension structureUniform line widthOriginals for photomechanical treatmentSpecial data processing applicationsPhase shiftedEngineering

Owner:SYNOPSYS INC

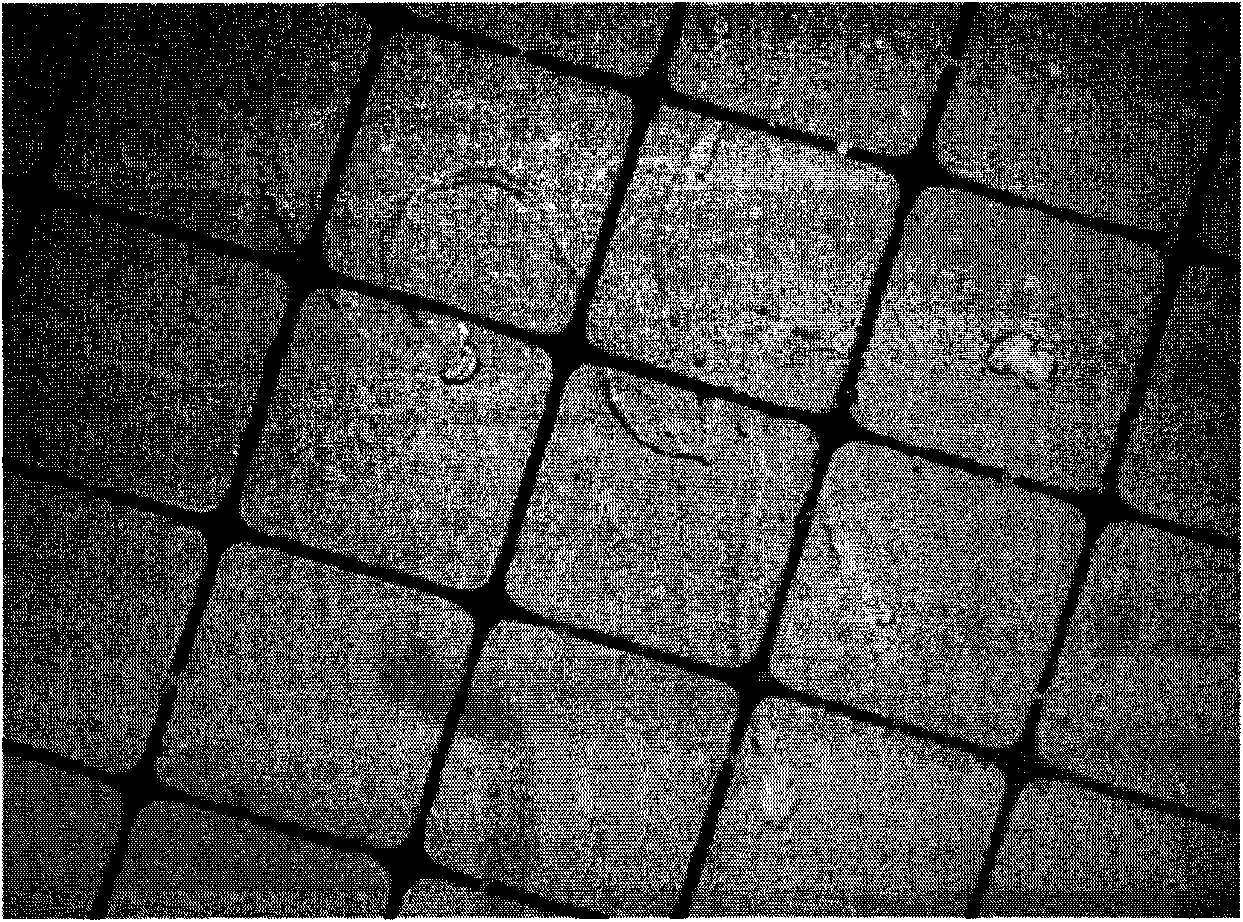

Electromagnetic wave preventing filter, manufacturing method thereof and display comprising the filter

InactiveCN101600332AReduce reflectionReduce the problem of poor moisture resistanceMagnetic/electric field screeningScreening apparatusElectromagnetic electron waveDisplay device

The present invention relates to an electromagnetic wave preventing filter and a display with the same. The electromagnetic wave preventing filter comprises the following components: a transparent strengthened glass substrate which has a tin surface with more tin abundance and has an air surface with less tin abundance compared with the tin surface; and an electromagnetic wave shielding part which is formed on the tin surface of the transparent strengthened substrate with a screen mesh shape. The filter is used for shielding the electromagnetic wave in a plasma display panel. Furthermore the external light reflection can be reduced and the blackness can be increased according to appropriate yellowing phenomenon of the conductive metal in the tin surface and the electromagnetic shielding part. Additionally the wet fastness problem can be reduced furthest even the printing layer in the final product is exposed in the external gas environment.

Owner:DONGJIN SEMICHEM CO LTD

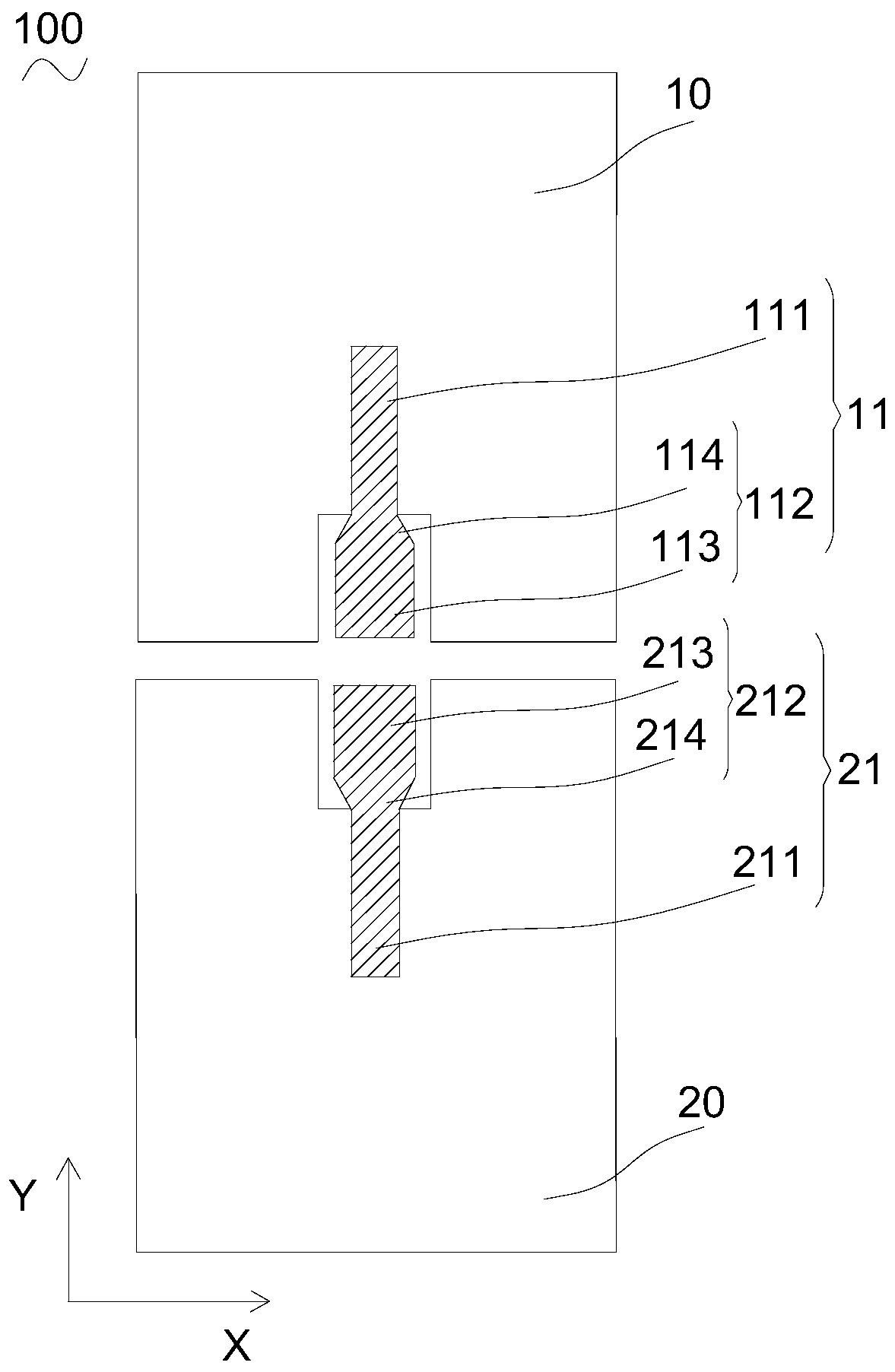

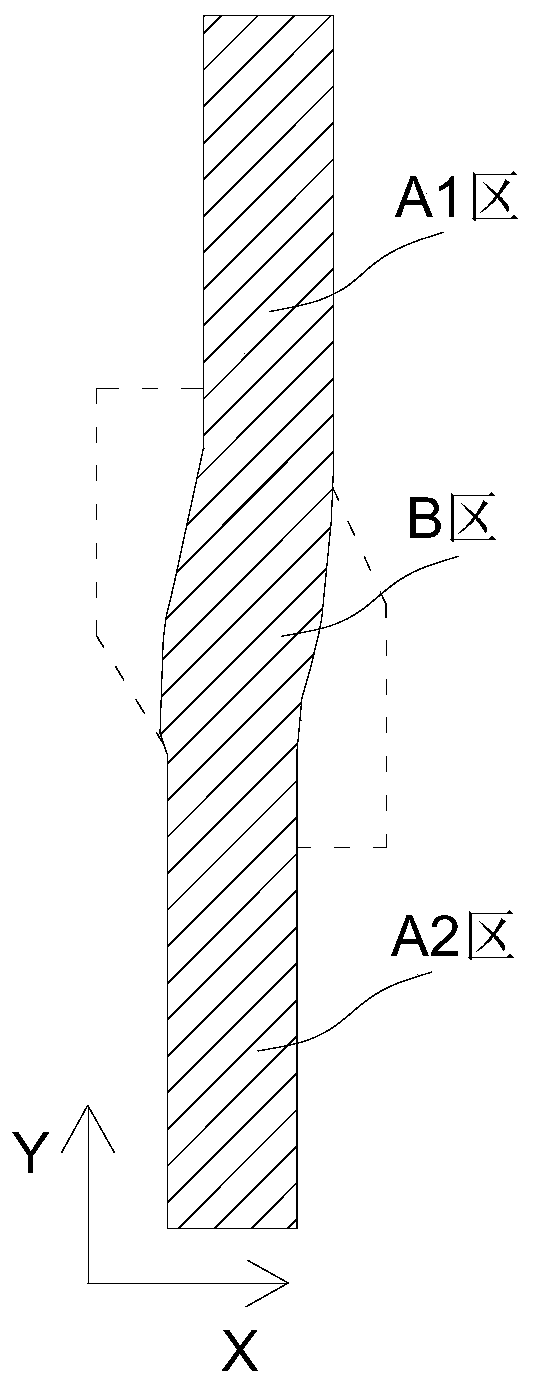

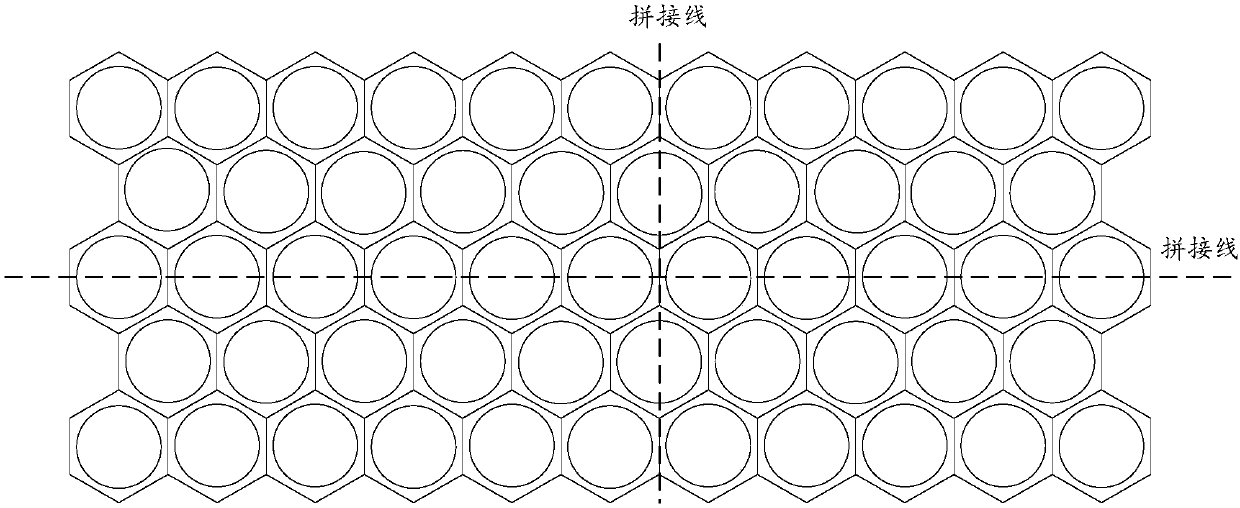

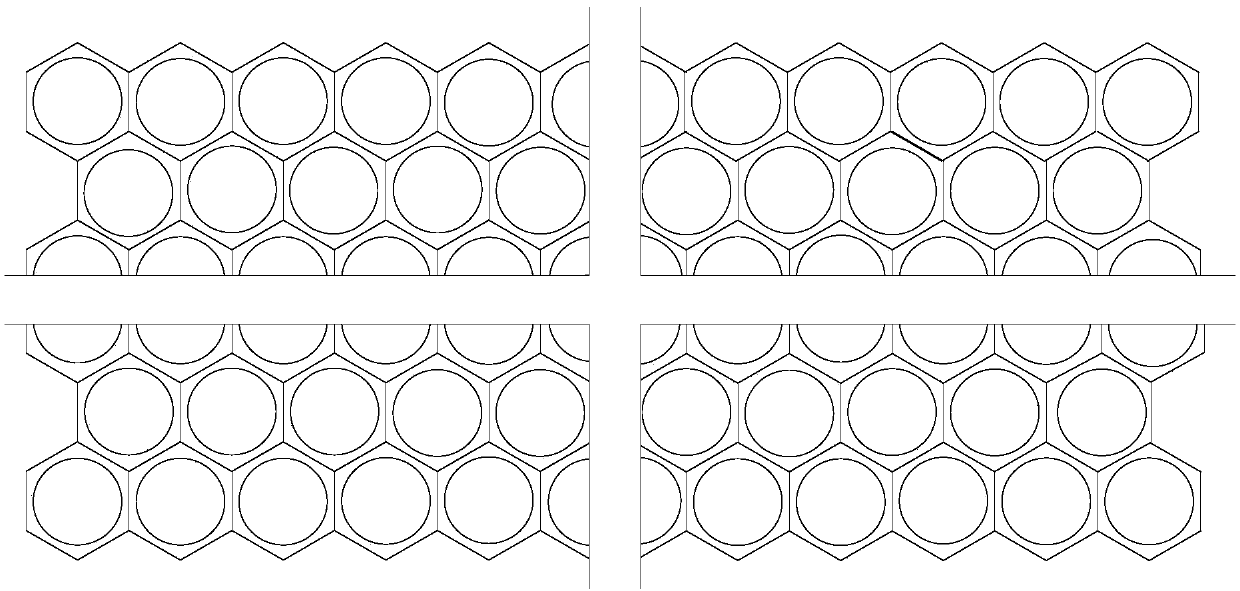

Mask plate, splicing exposure method and substrate

ActiveCN111025842AUniform line widthSolve the problem of split screen displayFinal product manufacturePhotomechanical exposure apparatusLine widthEngineering

The invention relates to a mask plate, a splicing exposure method and a substrate, and the mask plate comprises: a first mask plate which is provided with a first shading region which comprises a first non-splicing segment and a first splicing segment, wherein the first non-splicing segment and the first splicing segment are connected with each other in a first direction; a second mask plate whichis provided with a second shading area, wherein the second shading area comprises a second non-splicing segment and a second splicing segment which are connected with each other in the first direction, the line widths of the first non-splicing segment and the second non-splicing segment in the second direction are equal, and the previous projection of the first non-splicing segment on the planewhere the film layer to be exposed is located and the later projection of the second non-splicing segment on the plane where the film layer to be exposed is located are staggered in the second direction, the line width of at least one of the first splicing segment and the second splicing segment is greater than that of the first non-splicing segment, the first direction and the second direction are perpendicular to each other and parallel to the mask plate. Therefore, the line widths of the virtual patterns formed on the photoresist layer at all positions are equal, and the line widths of thefinally formed metal patterns are ensured to be equal.

Owner:YUNGU GUAN TECH CO LTD

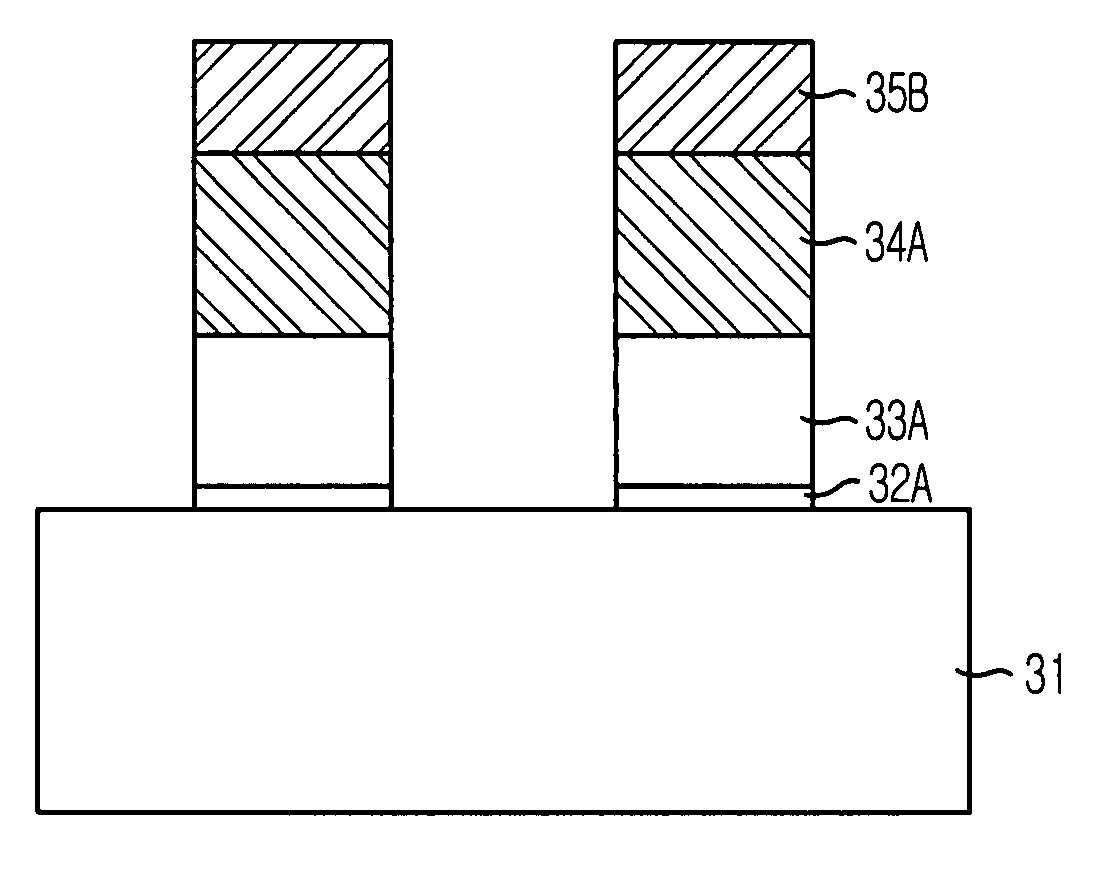

Etching method using hard mask in semiconductor device

InactiveUS20080160771A1Uniform line widthReduce lossesNon-mechanical controlsSemiconductor/solid-state device manufacturingNitrideSemiconductor

An etching method in a semiconductor device includes forming a nitride-based first hard mask layer over a target etch layer, forming a carbon-based second hard mask pattern over the first hard mask layer, etching the first hard mask layer using the second hard mask pattern as an etch barrier to form a first hard mask pattern, cleaning a resultant structure including the first hard mask pattern, and etching the target etch layer using the second hard mask pattern as an etch barrier.

Owner:SK HYNIX INC

Mask plate and exposure method

ActiveCN111381434AUniform line widthLower requirementPhotomechanical exposure apparatusMicrolithography exposure apparatusGraphicsImaging quality

The invention provides a mask plate and an exposure method. The mask plate comprises a first mask pattern and a second mask pattern which are complementary, wherein the first mask pattern comprises aplurality of first strip-shaped patterns extending along a first direction; the second mask pattern comprises a plurality of second strip-shaped patterns extending along a second direction; the firstdirection is crossed with the second direction; in the exposure method, the first mask pattern and the second mask pattern are employed respectively to sequentially execute twice exposure processes onthe LED substrate, so that after alignment overlapping of the formed exposure patterns, a PSS pattern can be generated; compared with a traditional splicing mode, the method has the advantages that the line widths of all the pattern areas are consistent, so that the requirement for image quality is lowered, and an exposure view field does not need to be reduced.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

Line image forming method and apparatus

ActiveUS20120026225A1Improve linearitySatisfactory line shapeDuplicating/marking methodsTypewritersEngineeringContact angle

A line image forming method includes the steps of: ejecting a plurality of droplets of liquid sequentially from an inkjet head, the liquid containing a functional component; and depositing the droplets of the liquid onto a non-permeable medium, the deposited droplets becoming joined together on the non-permeable medium to form a line pattern of the liquid, wherein a receding contact angle of the liquid with respect to the non-permeable medium being not larger than 10°.

Owner:FUJIFILM CORP

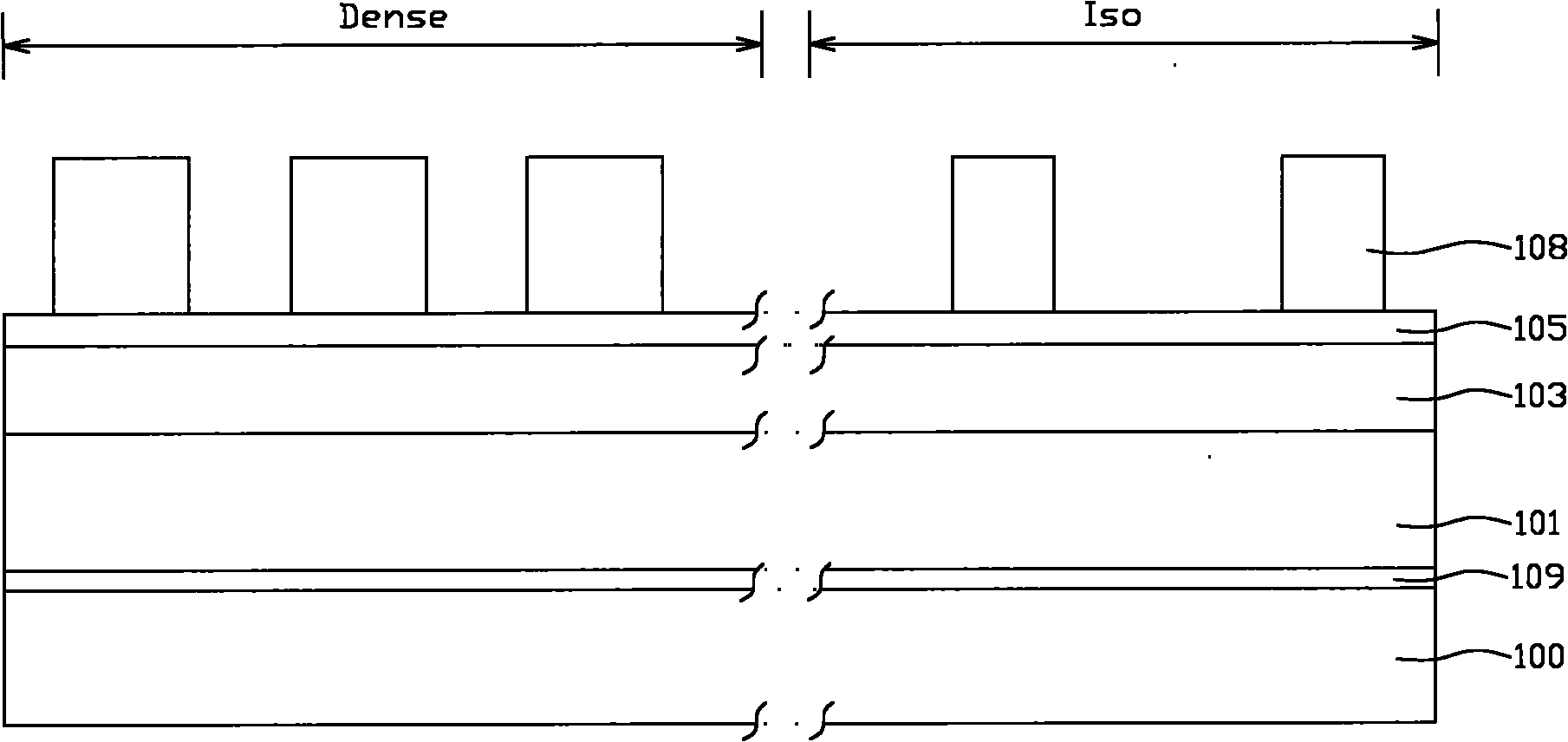

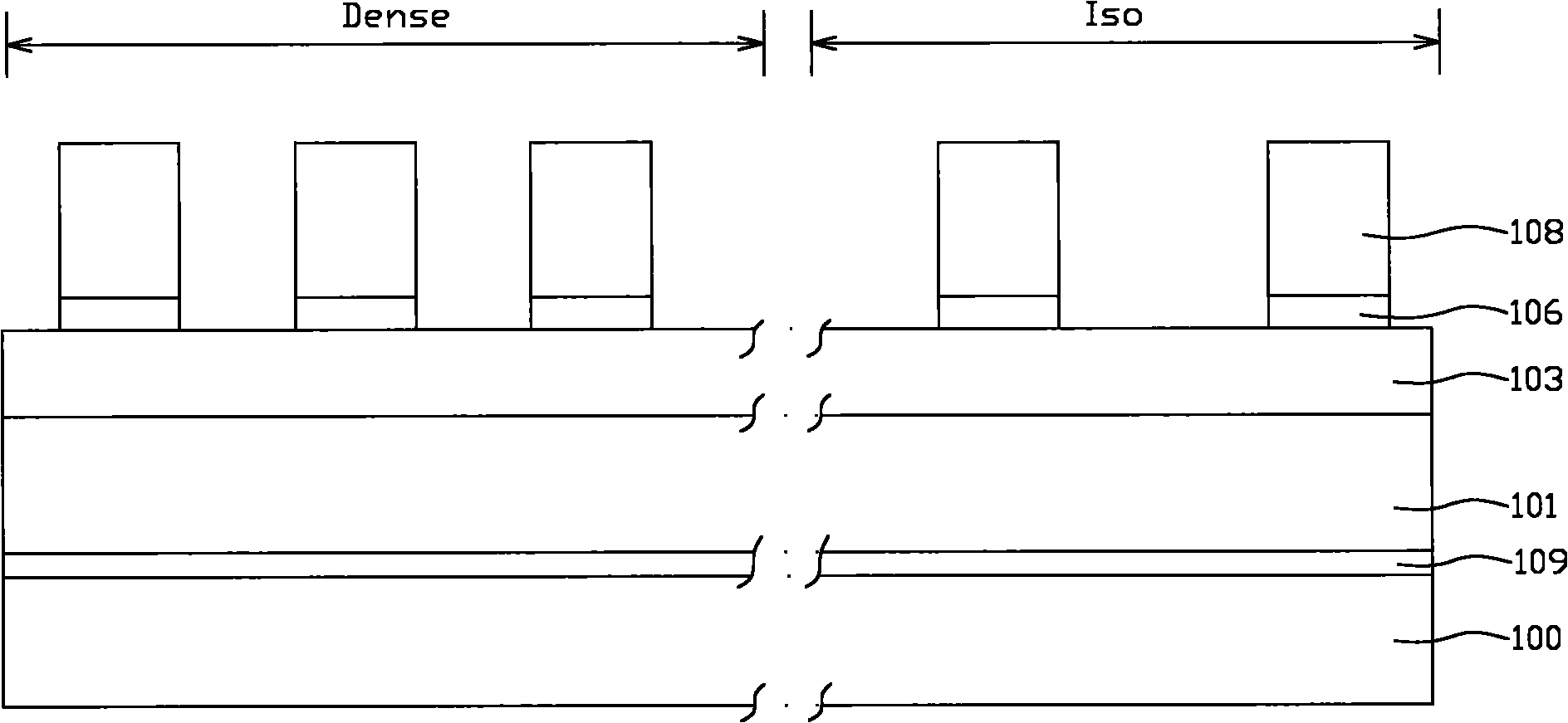

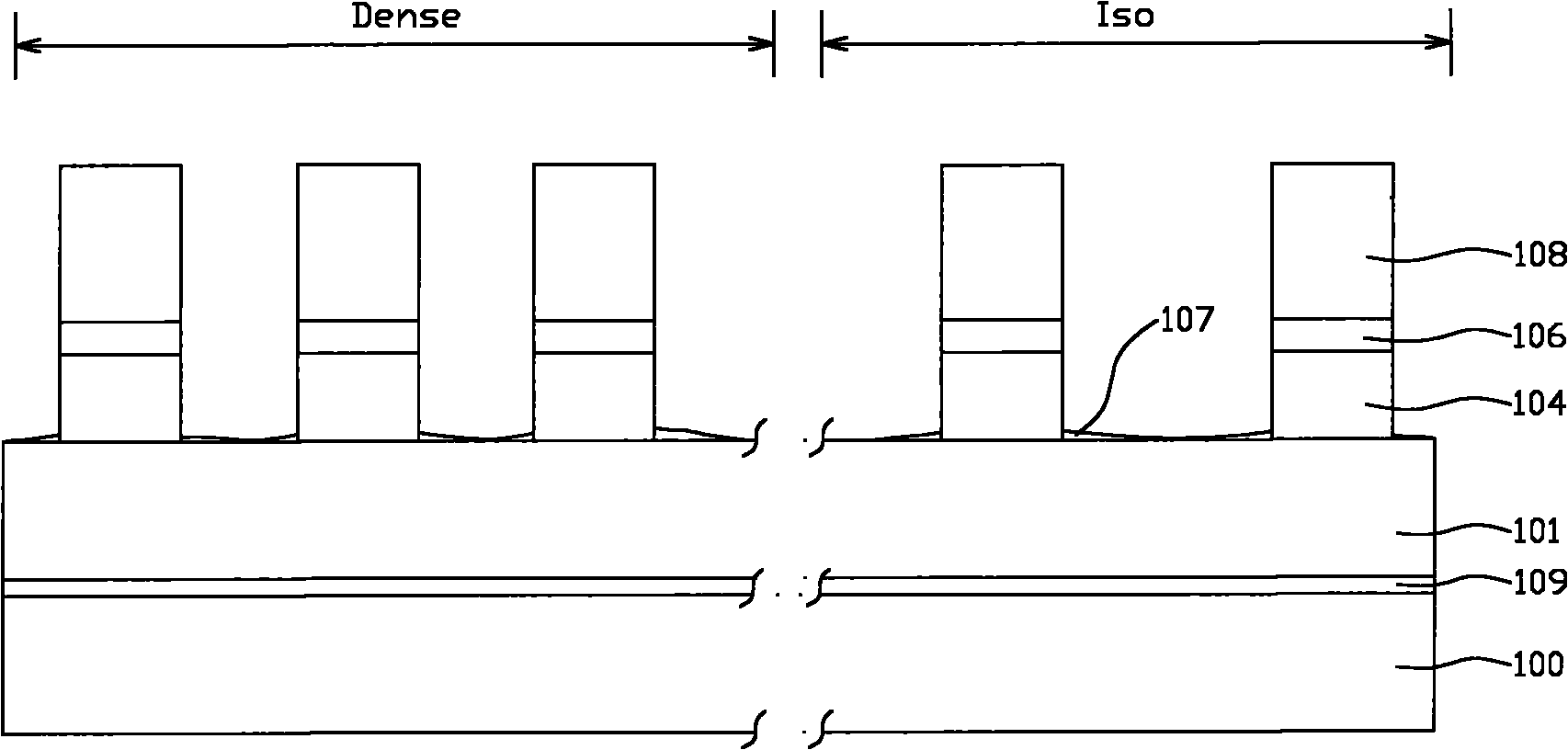

Etching method

ActiveCN101777485AIncrease line widthEtch inhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLine width

The invention provides an etching method, which comprises steps of primary etching, main etching and over etching; and in the primary etching, the mixed gas of fluorine-based gas and chlorine-based gas forms plasmas, wherein the fluorine-based gas is one or combination of at least two of CF4, Ch2F2 and CHF3; and the chlorine-based gas is one or combination of at least two of Cl2, CH2Cl2 and CH3Cl. In the etching method, the chlorine-based gas serving as the etching gas is increased in the primary etching step, so that the shrinkage of the line width of lines of patterns in a Dense area is greater than that of the line width of lines of patterns in an Iso area, which is opposite to a condition that the line width of the lines of the patterns in the Dense area is greater than that in the Iso area caused by the PR-loading effect; therefore, the influence of the PR-loading effect on the line width uniformity is compensated finally, and uniform AEI line width is obtained at each position of a semiconductor chip.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

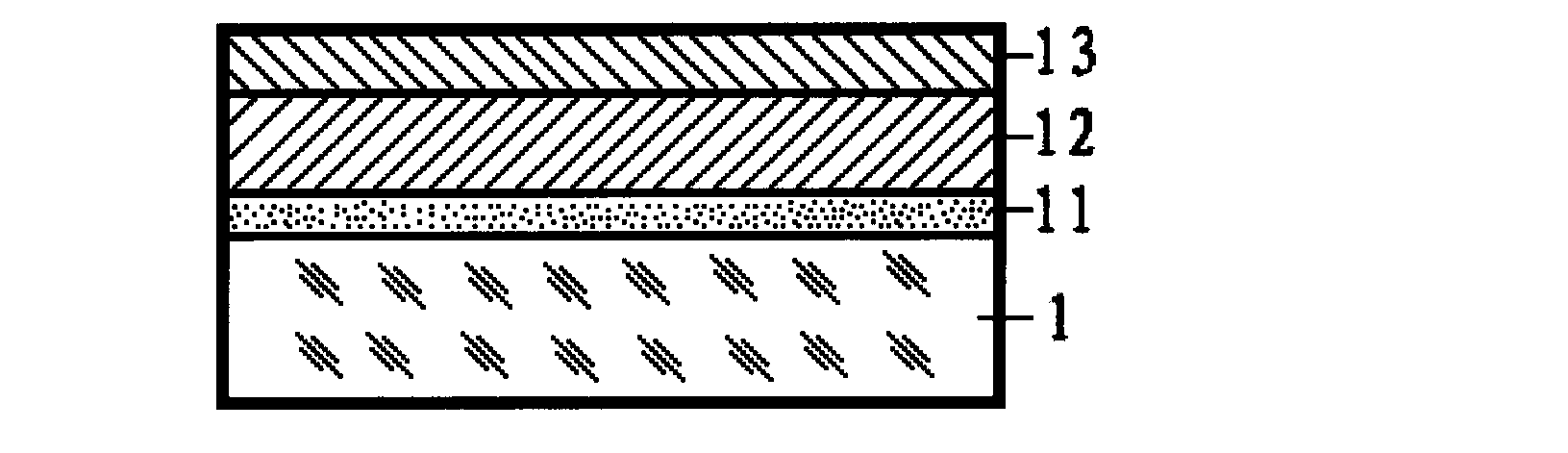

Photomask with novel three-layer-film structure, and preparation method thereof

ActiveCN103235480AGood blocking effectGood etching effectGlass/slag layered productsOriginals for photomechanical treatmentIonFilm structure

The invention discloses a photomask with a novel three-layer-film structure, and a preparation method thereof. The photomask with the novel three-layer-film structure comprises a glass substrate, a barrier layer, a shading film layer, and an antireflection film layer. At least one layer in the three layers of films comprises a carbon component. According to the preparation method, one or more Cr target materials are provided; with a vacuum magnetron sputtering method, the barrier layer, the shading film layer, and the antireflection film layer are respectively plated on the glass substrate. With the method provided by the invention, a recess problem caused by sodium ion diffusion can be solved. Compared with a three-layer-film structure in prior art, the photomask with the novel three-layer-film structure can ensure etching time and good etching speed. Also, only one Cr target material is needed to be provided during the preparation process.

Owner:湖南普照信息材料有限公司 +1

Photomask and manufacturing method of semiconductor device

InactiveUS7790335B2Increase depth of focusHighly reliable semiconductorPhoto-taking processesSemiconductor/solid-state device manufacturingDevice materialImage resolution

A double exposure process is performed using a halftone phase shift mask (11) including gate patterns (1), assist patterns (2a) and (2b) with different resoluble line widths, and an assist pattern (2c) with a line width equal to or smaller than a resolution limit which are respectively inserted into portions in each of which a distance between the gate patterns (1) is large, and a Levenson phase shift mask (11) including shifter patterns (3) corresponding to the gate patterns (1) of the photomask 11. On this occasion, the assist patterns (2a), (2b), and (2c) are erased and only the gate patterns (1) are transferred. Consequently, when patterns are transferred by the double exposure process, a common depth of focus of the patterns is improved and highly uniform line widths are realized, which makes it possible to manufacture a highly reliable semiconductor device.

Owner:FUJITSU SEMICON LTD

Temperature control method of heat processing plate, computer storage medium, and temperature control apparatus of heat processing plate

ActiveUS8242417B2Uniform line widthIncrease spacingDrying solid materials with heatSemiconductor/solid-state device manufacturingTemperature controlEngineering

Owner:TOKYO ELECTRON LTD

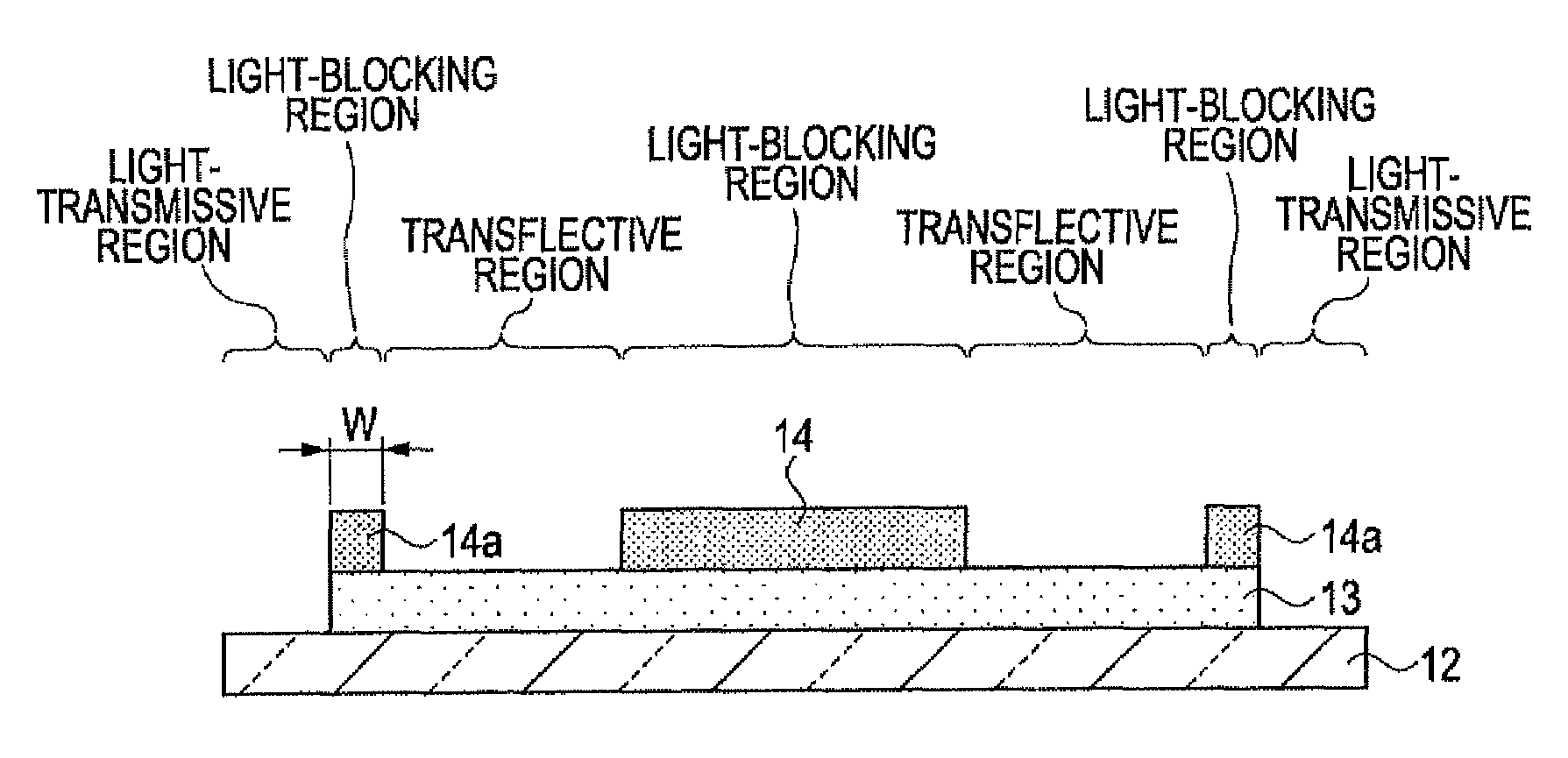

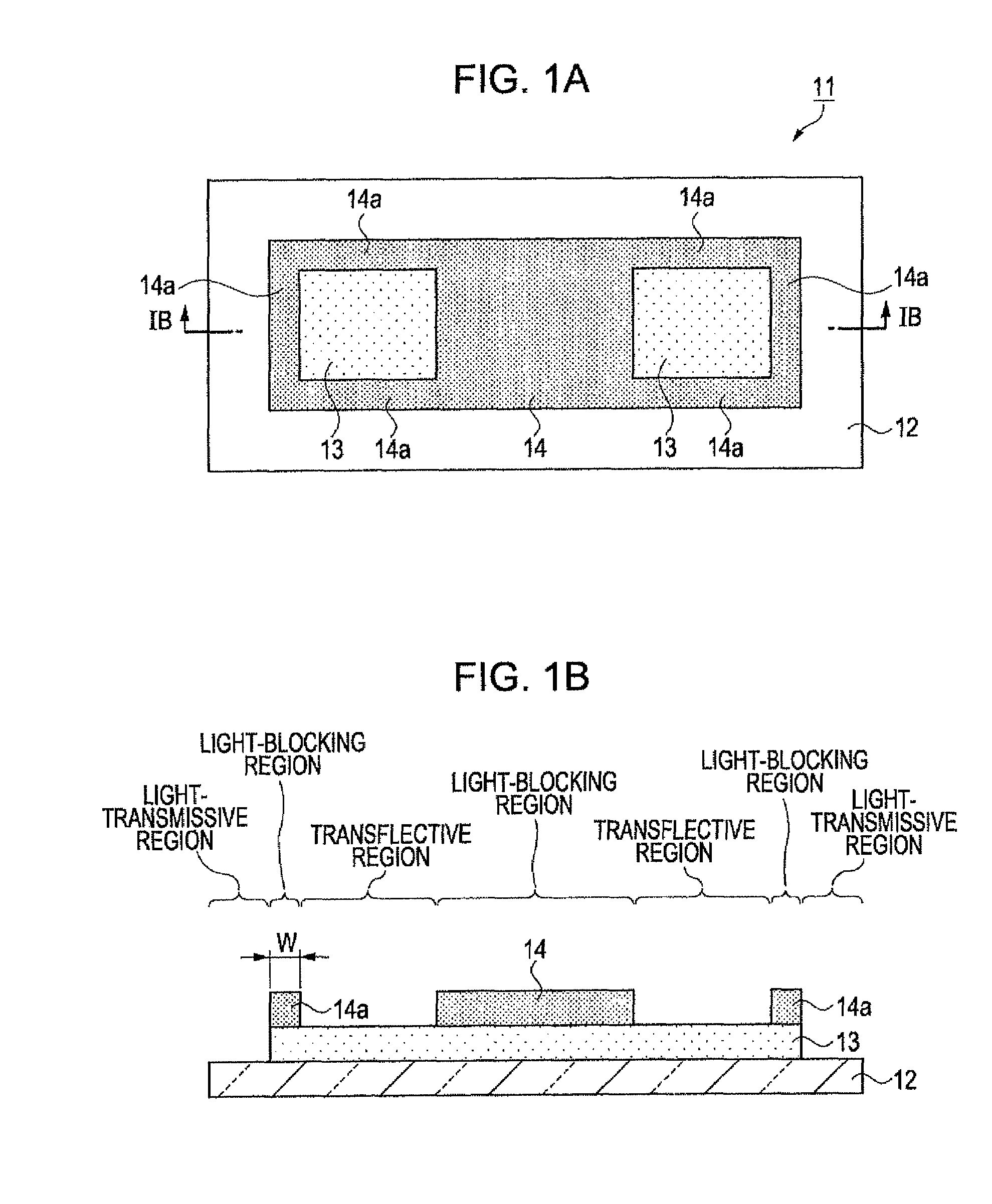

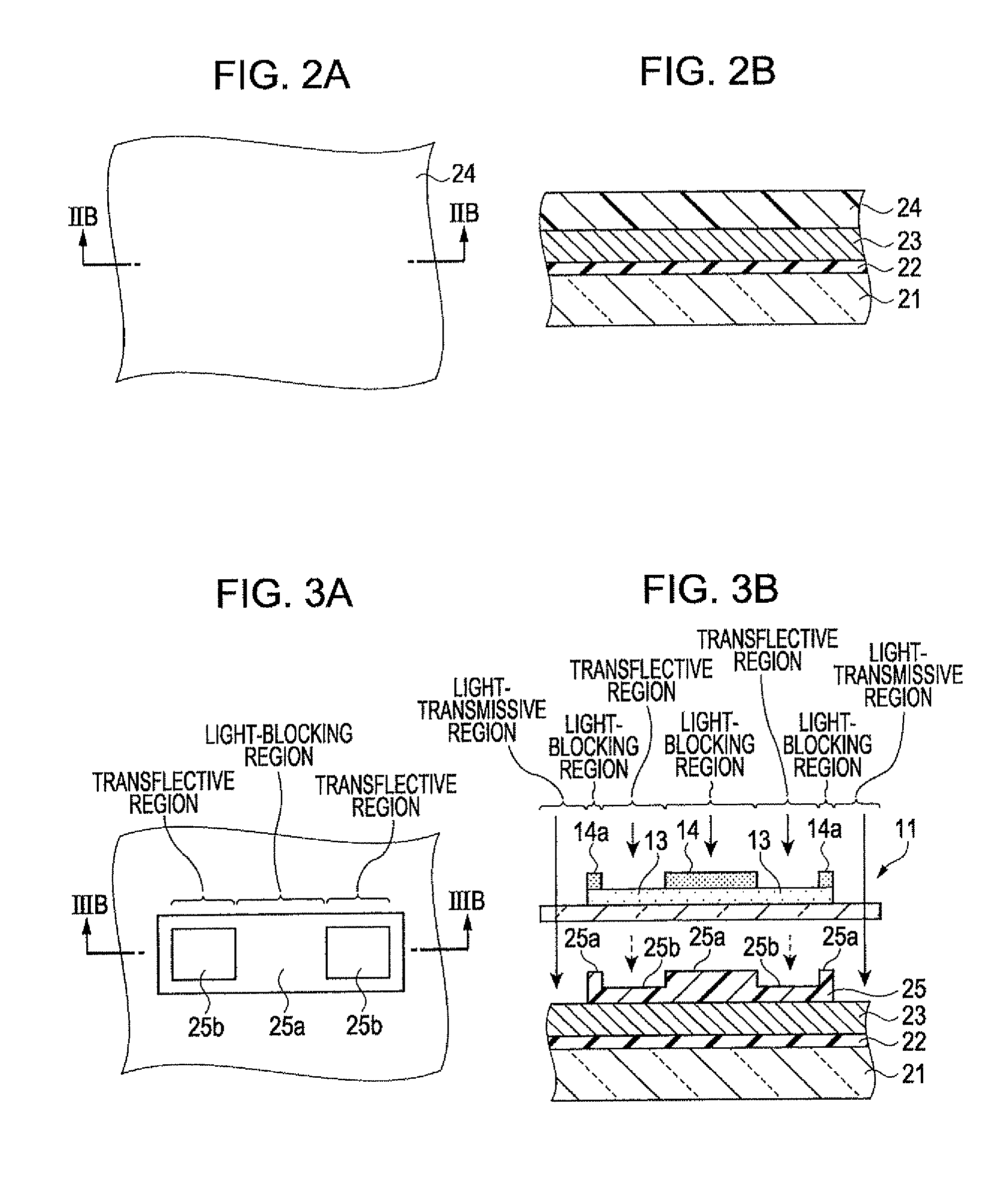

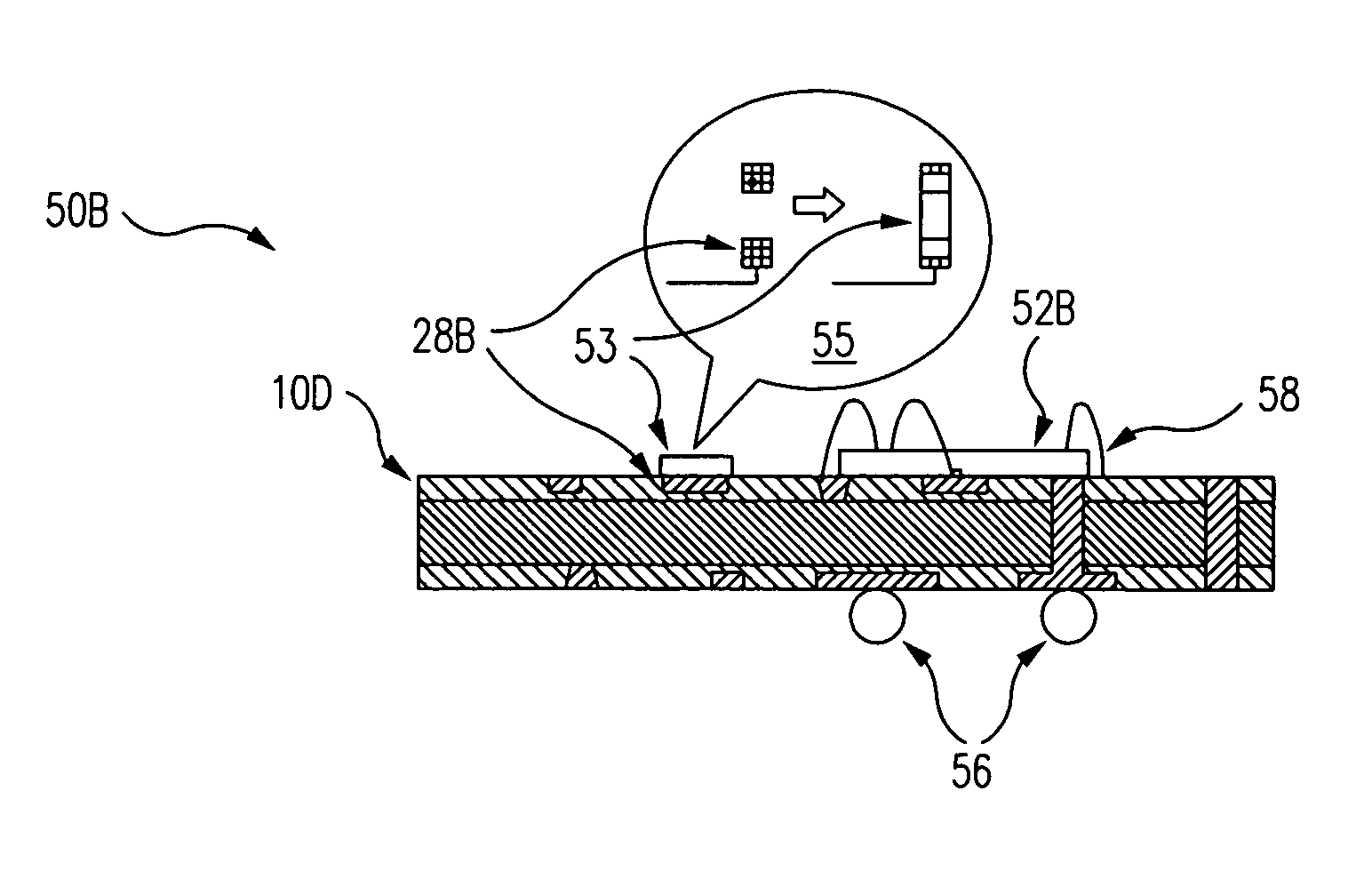

Photomask, semiconductor device, and method for manufacturing semiconductor device

InactiveUS7939229B2Unnecessary lightUniform line widthTransistorPhotomechanical apparatusSemiconductorPhotomask

A photomask includes a light-blocking section that blocks light and also includes a light intensity difference section that controls the intensity of light. The light-blocking section is disposed between the light intensity difference section and a light-transmissive region transmitting light.

Owner:SEIKO EPSON CORP

Semiconductor package substrate fabrication method

InactiveUS7501338B1Reduce contiguous conductive area of landReduce amountInsulating substrate metal adhesion improvementPrinted circuit aspectsHigh densityLine width

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Developing device and developing method

InactiveUS7918182B2Uniform line widthPrevent in developmentMovable spraying apparatusSemiconductor/solid-state device manufacturingResistDiluent

Owner:TOKYO ELECTRON LTD

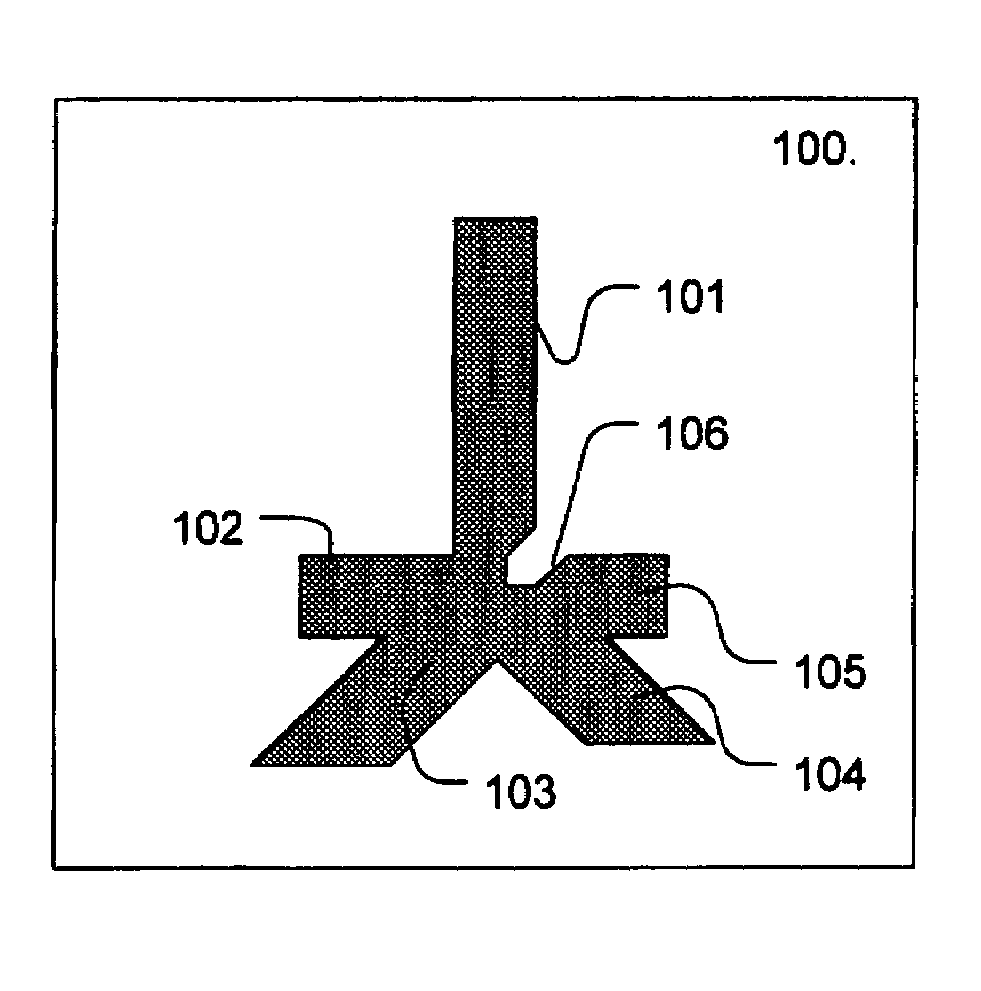

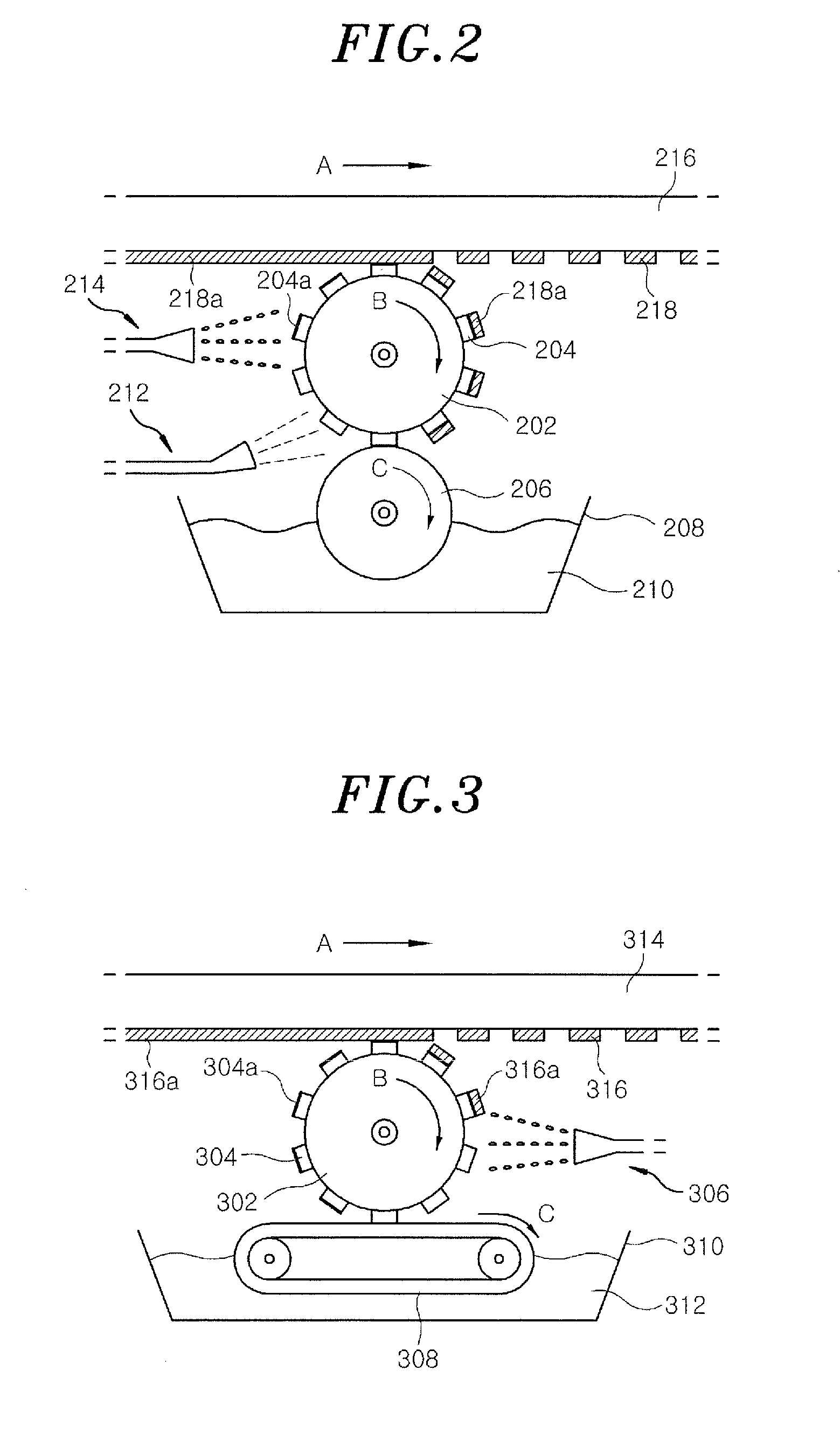

Method and apparatus for forming a graphene pattern using peel-off technique

InactiveUS20150132488A1Uniform line widthEasy to makeLayered productsLaminationLine widthOptoelectronics

The present invention relates to a graphene pattern forming method using a delamination technique employing a polymer stamp. The technique is adequate for forming a graphene pattern having a an arbitrary target pattern. According to the present invention, a portion of a graphene layer formed on a substrate is physically and selectively delaminated using the polymer stamp to simply and easily form a desired graphene pattern having a uniform line width on the substrate. Also, a portion of the graphene layer formed on the substrate is physically and selectively delaminated in a roll-to-roll manner using a rotating body stamp or by using a stamp having a large area to simply and easily form a desired graphene pattern having a uniform line width on the a substrate having a large area.

Owner:KOREA RES INST OF CHEM TECH