Trench field effect transistor and manufacturing method thereof

A field-effect transistor and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as device performance degradation and switching speed reduction, and achieve enhanced current density, increased turn-on speed, and improved switching. effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

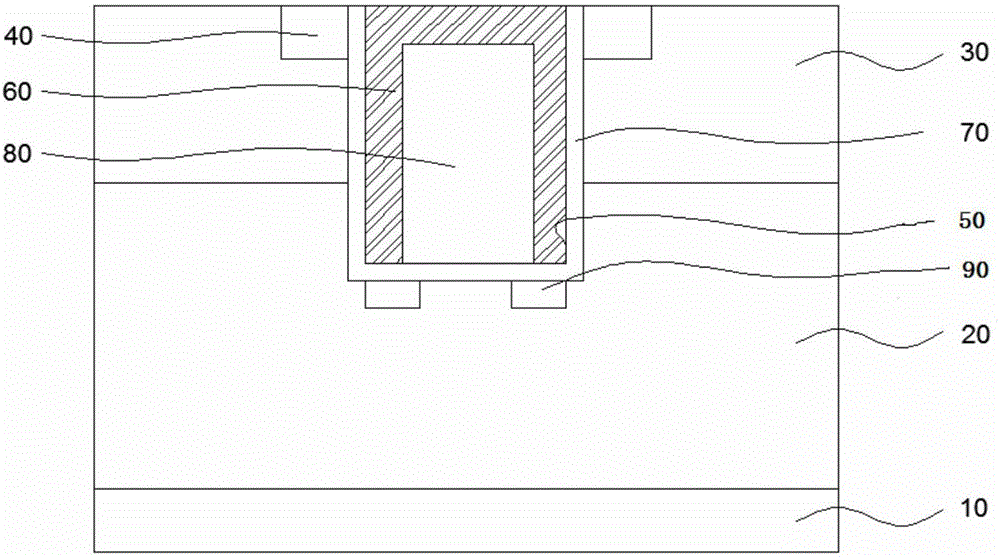

[0035] Such as figure 1 As shown, the trench field effect transistor of this embodiment includes a substrate 10, an n- epitaxial layer 20 formed on the surface of the substrate 10, a p-type body region 30 formed on the surface of the n-epitaxial layer 20, The top of the p-type body region 30 is provided with an n+ active region 40, and the trench 50 extends through the n+ active region 40 and the p-type body region 30 until the n- epitaxial layer 20, and the trench 50 has A polysilicon gate 60 and a gate oxide layer 70, the gate oxide layer 70 is formed on the surface of the trench 50, and the trench 50 also includes an insulating dielectric layer 80 with a dielectric constant not greater than that of the gate oxide layer 70, and the insulating dielectric layer The layer 80 divides the side of the polysilicon gate 60 close to the bottom of the trench 50 into two parts that are respectively close to the p-type body region 30 on both sides, and the bottom of the trench 50 corres...

no. 2 example

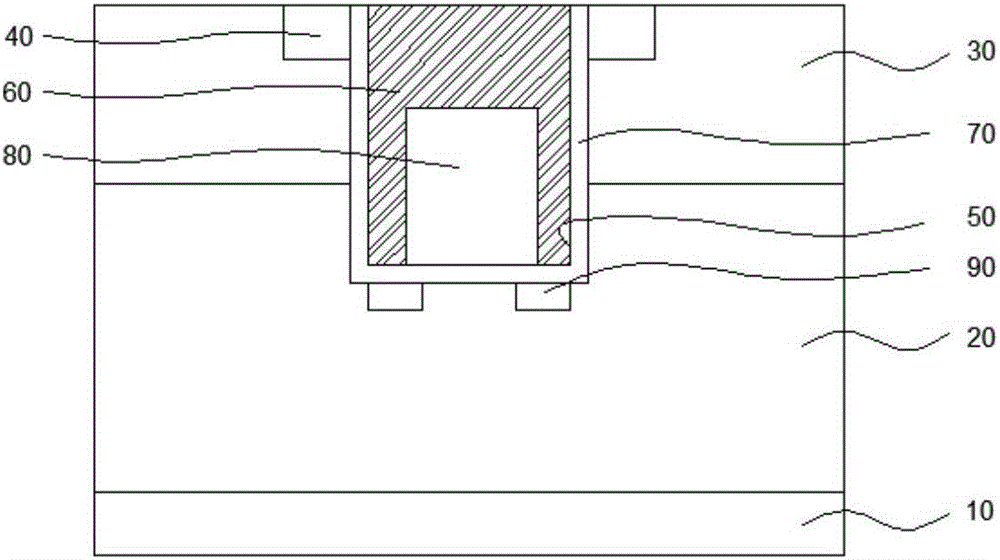

[0049] Such as figure 2 As shown, in the second embodiment, compared with the first embodiment, the distance from the top of the insulating dielectric layer 80 to the bottom of the trench 50 is greater than the distance from the bottom of the n+ active region 40 to the bottom of the trench 50, so that the entire p-type body region 30 corresponds to The current density of the polysilicon gate 60 is uniformly enhanced, which better increases the turn-on speed.

no. 3 example

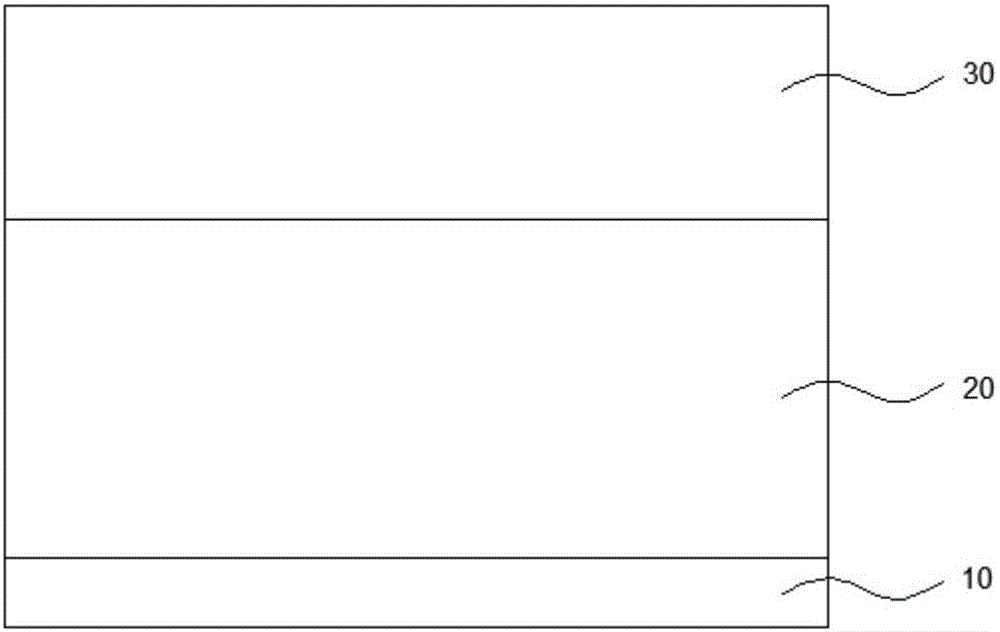

[0051] Such as image 3 As shown, compared with the first embodiment, the p-type doped region 90 is continuously formed at the bottom of the trench 50 in the third embodiment, which increases the resistance to the high voltage of the polysilicon gate 60 and can simplify doping to form p The process of the type doped region 90.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More