Metal oxide semiconductor device and manufacturing method thereof

A technology of oxide semiconductors and production methods, which is applied in the direction of semiconductor/solid-state device manufacturing, transistors, electrical components, etc., to achieve the effects of improving surface potential, facilitating industrialized mass production, and good economic benefits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

[0108] Compared with the first embodiment, the manufacturing method sequence and corresponding process of the metal oxide semiconductor device of the second embodiment are different. The manufacturing method of embodiment two comprises:

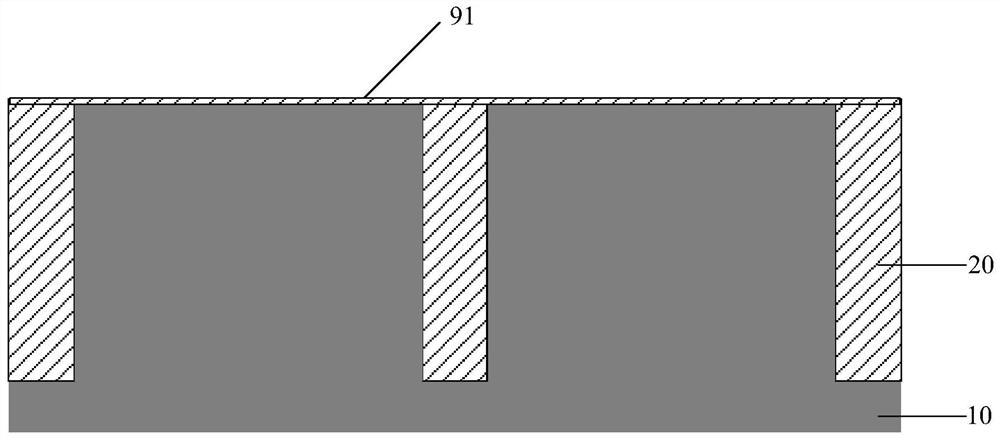

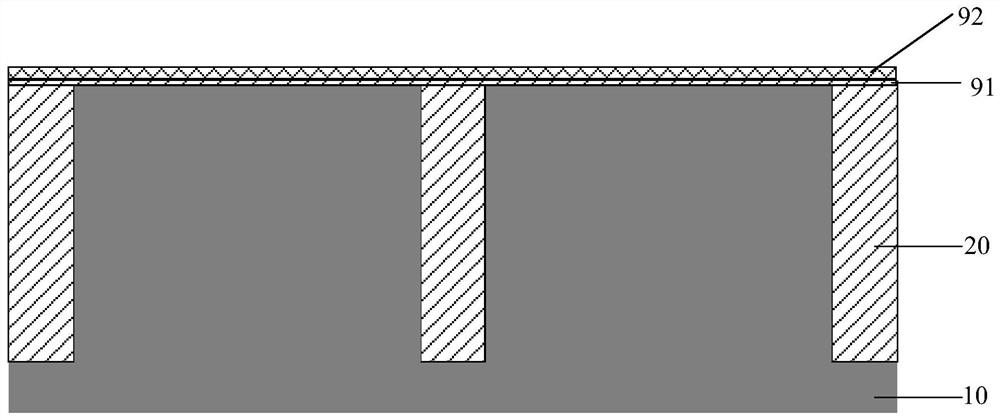

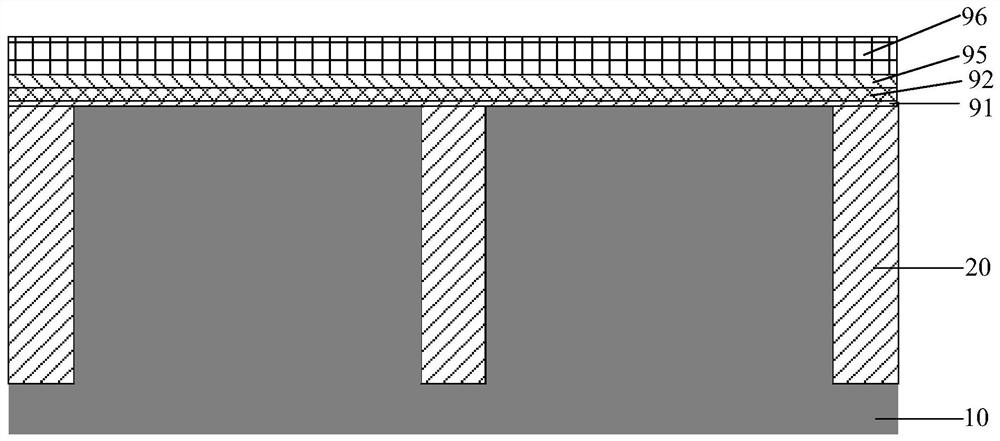

[0109] Step 1: Form the N-type MOSFET region and the P-type MOSFET region separated by the shallow trench isolation region 20 on the substrate 10, form a dummy gate oxide layer 41 and deposit a polysilicon dummy gate 96 thereon; deposit hard mask 30, such as Figure 16 shown.

[0110] Step 2: Photolithography and etching to form a gate stack structure, such as Figure 17 shown.

[0111] Step 3: forming sidewalls 1-71 and N-type and P-type source and drain extension regions 51 and 52; forming sidewalls 2-72 and N + Type and P + Type source and drain regions 53 and 54; form source and drain region silicide 55, such as Figure 18 shown.

[0112] Step 4: Deposit oxide and silicon nitride interlayer dielectric layer 80, and CMP interlayer d...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More