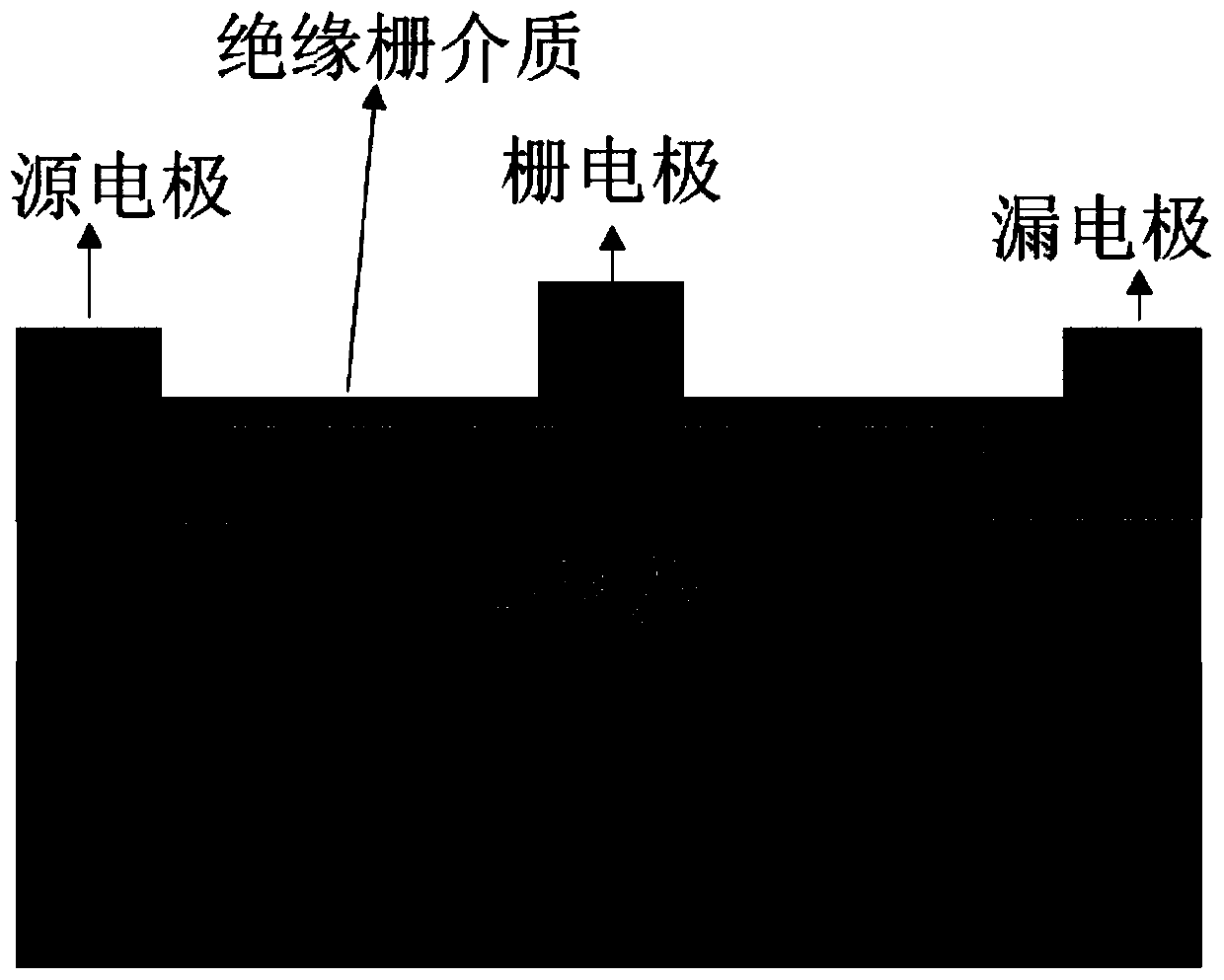

Enhanced Ga2O3 metal oxide semiconductor field effect transistor and manufacturing method thereof

A technology of field-effect transistors and oxide semiconductors, which is applied in the field of microelectronics, can solve the problems of reducing the carrier concentration under the gate, etching damage on the surface of the concave gate, and affecting device performance, etc., so as to reduce the carrier concentration and reduce the Interface state density, the effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

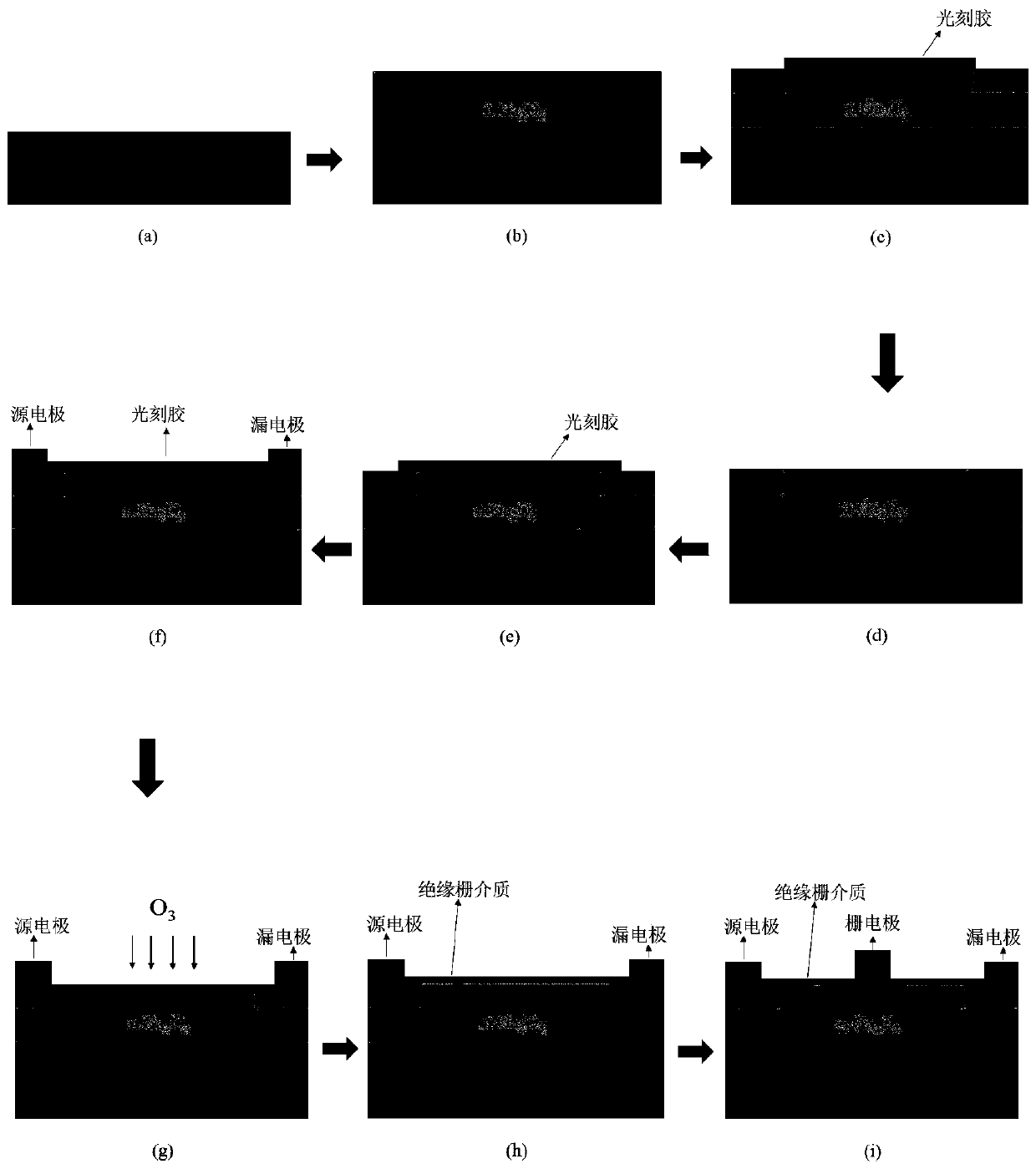

[0031] Embodiment 1, making n-type Ga 2 o 3 The thickness of the epitaxial layer is 150nm, and the electron concentration is 2.0×10 16 cm -3 , a field effect transistor with an insulating gate dielectric thickness of 10nm.

[0032] Step 1, cleaning the substrate, such as figure 2 (a).

[0033] The sapphire substrate is selected, cleaned with acetone solution first, then with ethanol solution, and finally with flowing deionized water and blown dry with high-purity nitrogen.

[0034] Step 2, grow n-type Ga on the substrate 2 o 3 epitaxial layer, such as figure 2 (b).

[0035] 2a) Put the cleaned sapphire substrate into the reaction chamber of the PLD equipment, set the partial pressure of oxygen in the reaction chamber to 0.01mbar, the temperature to 500°C, and the target material in the reaction chamber to be (AlGa) 2 o 3 , the distance between the sample to be grown and the target material is set to 4cm, and the energy density of the laser is set to 2J / cm 2 , the ...

Embodiment 2

[0055] Embodiment 2, making n-type Ga 2 o 3 The thickness of the epitaxial layer is 230nm, and the electron concentration is 2.0×10 17 cm -3 , a field effect transistor with an insulating gate dielectric thickness of 20nm.

[0056] Step 1, cleaning the substrate, such as figure 2 (a).

[0057] The specific implementation method of this step is the same as Step 1 in Example 1.

[0058] Step 2, growing n-type Ga on the substrate 2 o 3 epitaxial layer, such as figure 2 (b).

[0059] 2.1) Put the cleaned sapphire substrate into the reaction chamber of the PLD equipment, set the partial pressure of oxygen in the reaction chamber to 0.02mbar, the temperature to 600°C, and the target material in the reaction chamber to be (AlGa) 2 o 3 , the distance between the sample to be grown and the target material is set to 4cm, and the energy density of the laser is set to 3J / cm 2 , the pulse frequency is 4Hz, and the total number of pulses is 7000 times;

[0060] 2.2) The thickn...

Embodiment 3

[0078] Embodiment 3, making n-type Ga 2 o 3 The thickness of the epitaxial layer is 300nm, and the electron concentration is 1.0×10 18 cm -3 , a field effect transistor with an insulating gate dielectric thickness of 30nm.

[0079] Step A, the substrate is cleaned, such as figure 2 (a).

[0080] Mg-doped Ga 2 o 3 The substrate was first cleaned with acetone solution, then with ethanol solution, and finally with flowing deionized water and dried with high-purity nitrogen.

[0081] Step B, growing n-type Ga on the substrate 2 o 3 epitaxial layer, such as figure 2 (b).

[0082] Put the cleaned sapphire substrate into the reaction chamber of the PLD equipment first, and use the method of laser deposition to grow on the substrate with a thickness of 300nm and an electron concentration of 1.0×10 18 cm -3 n-type Ga 2 o 3 film, to obtain n-type Ga 2 o 3 epitaxial layer.

[0083] The growth process conditions are: the oxygen partial pressure in the reaction chamber i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More