Single electron memory having carbon nano tube structure and process for making it

A carbon nanotube structure and technology of carbon nanotubes, applied in the direction of nanostructure manufacturing, nanotechnology, nanotechnology, etc., can solve problems that plague traditional memory such as power consumption, limited integration, instability of MOS field effect transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

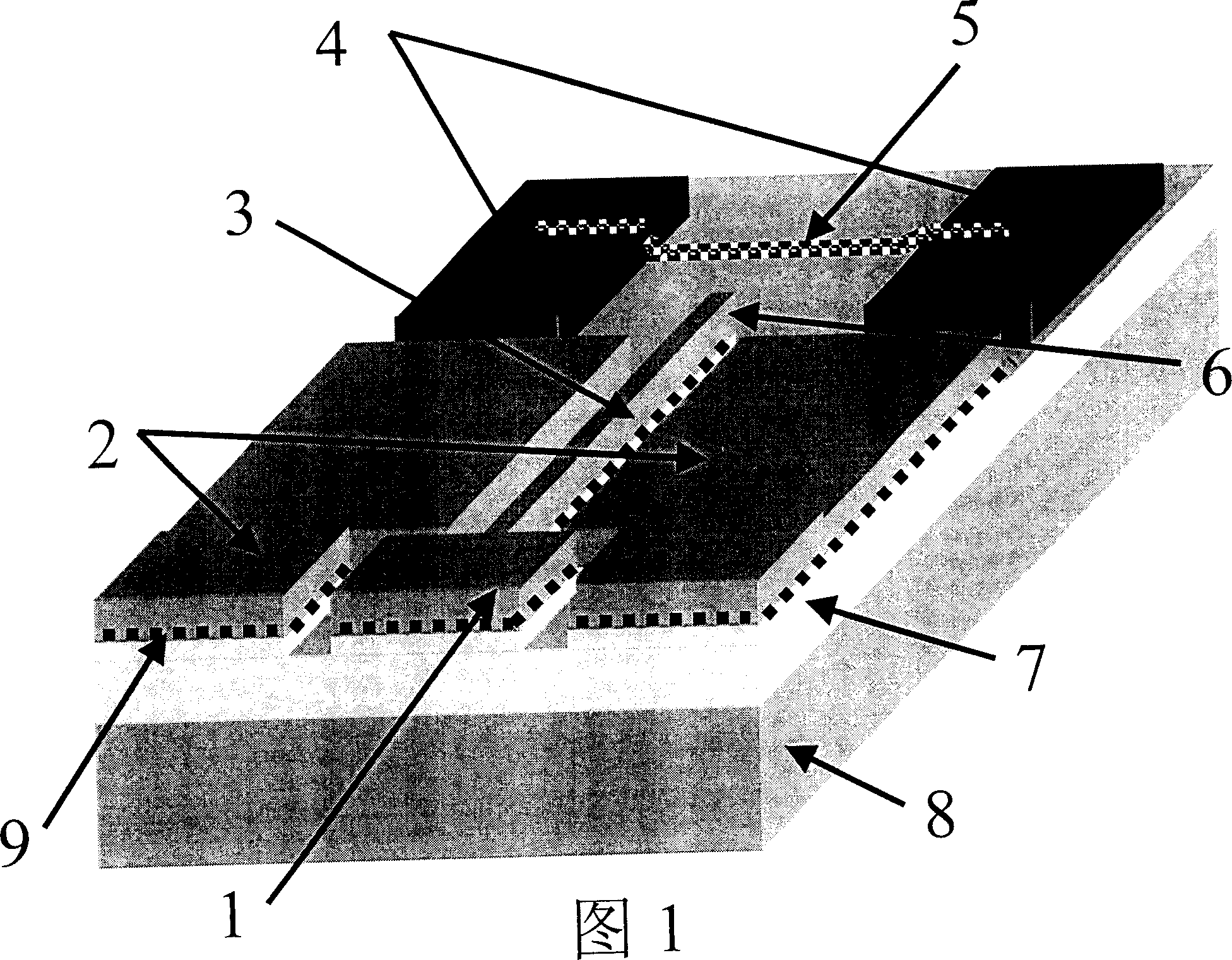

[0047] According to Fig. 1, the single-electron memory with carbon nanotube structure of the present invention is produced.

[0048] Select semi-insulating GaAs as the substrate, and use molecular beam epitaxy (MBE) to grow a GaAs buffer layer with a thickness of 1 micron. The method of molecular beam epitaxy MBE is used to form a GaAs layer 9 containing silicon delta doped on the buffer layer, and this layer is deposited on the GaAs buffer layer with an area density of 1×10 12 cm -2 Silicon and a 50 nm thick GaAs layer grown on it.

[0049] The data line pin 1 , the control gate 2 of the nanowire and the nanowire 3 are prepared by electron beam photolithography and dry etching technology. The depth of the dry etching is 70 nanometers, that is, the δ-doped GaAs layer and part of the buffer layer 7 are etched, as shown in FIG. 1 . The pin width of the data line is 80 nanometers; the size of the control gate of each nanowire is 80 nanometers wide and 80 nanometers long; the l...

Embodiment 2

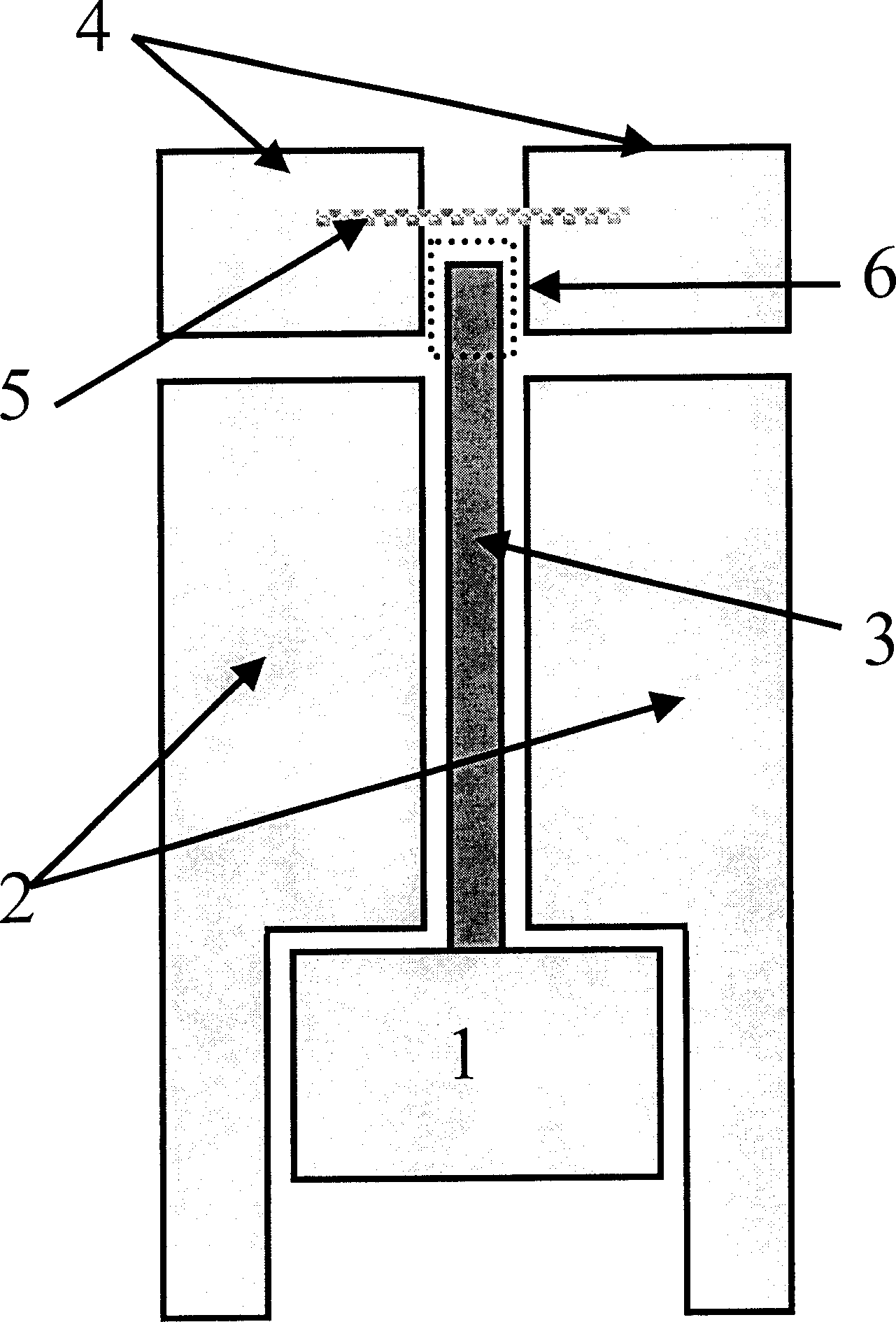

[0052] According to Fig. 8, the single-electron memory with carbon nanotube structure of the present invention is fabricated.

[0053] The preparation method of the data line pin 1 , the control gate 2 of the nanowire and the nanowire 3 is the same as that of the first embodiment.

[0054] Using photolithography, evaporation and lift-off techniques, gold electrodes were prepared, including two carbon nanotube transistor electrodes 4 with a thickness of 20 nanometers, a width of 50 nanometers, and a length of 100 nanometers, with a distance of 90 nanometers between them. Place catalysts (Fe, Co, Ni and their alloys) on the inner side of the electrode 4 of the carbon nanotube transistor with the probe manipulation technology of the atomic force microscope, and grow the carbon nanotube 5 in situ so that it is in contact with the electrode 4 of the carbon nanotube transistor. If the contact is not good, FIB technology can be used to deposit platinum to form a good ohmic contact be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More