Highly selective doped oxide etchant

a technology of doped oxide and high selectiveness, applied in the field of capacitor structure formation methods, can solve the problems of weak structural strength of the container, subject to collapse, and high process temperature, and achieve the effect of relatively slow etching rate and low cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

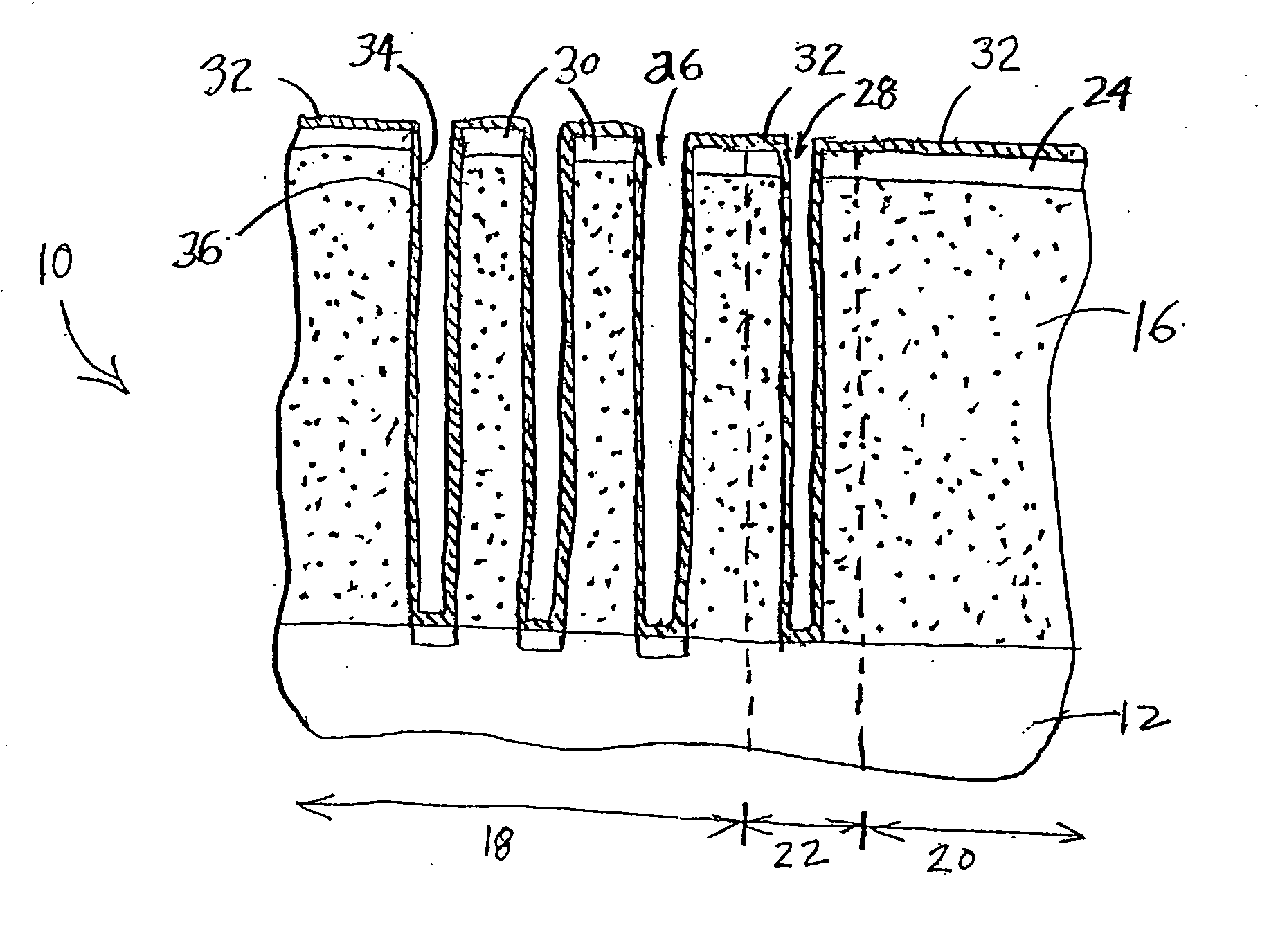

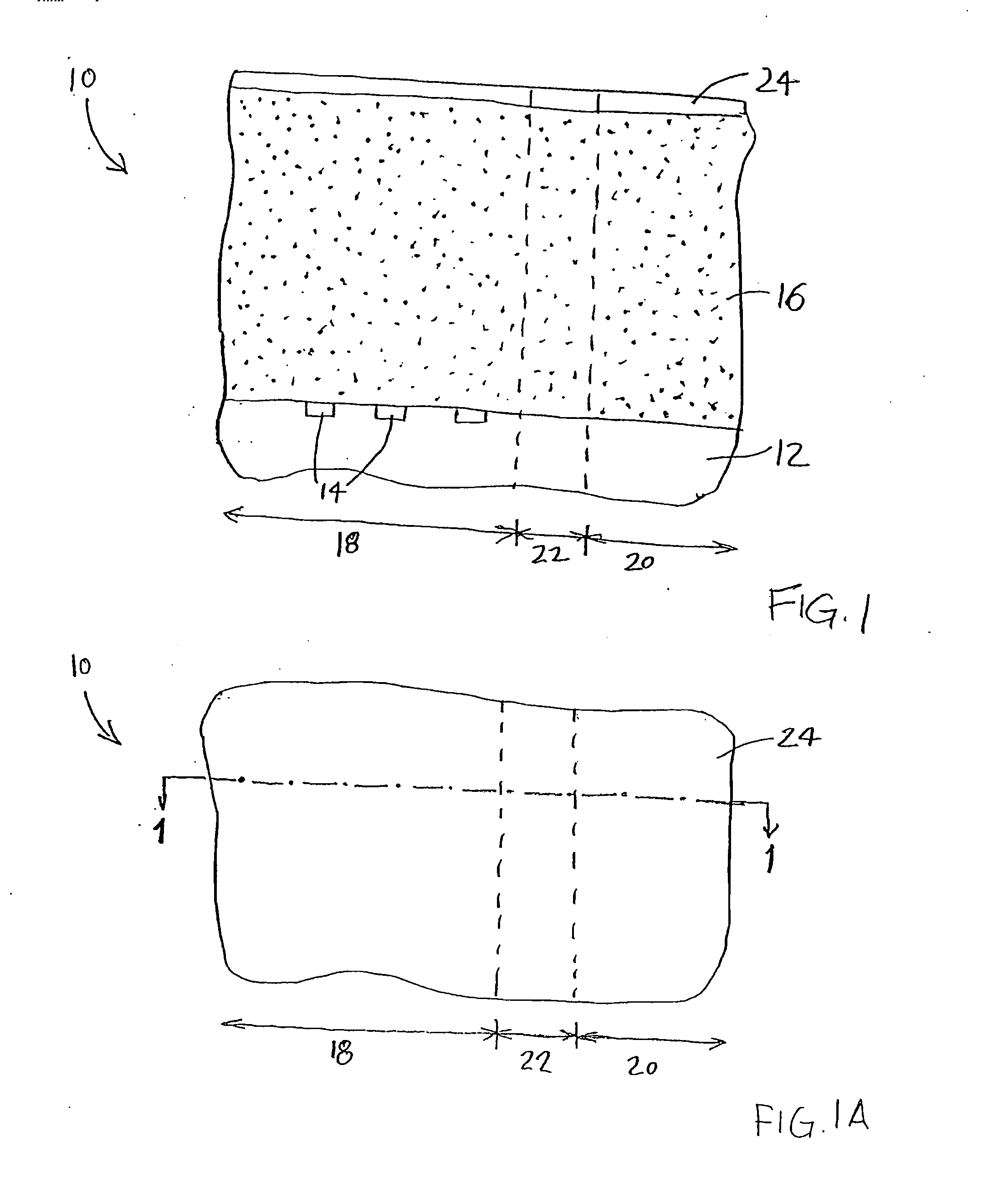

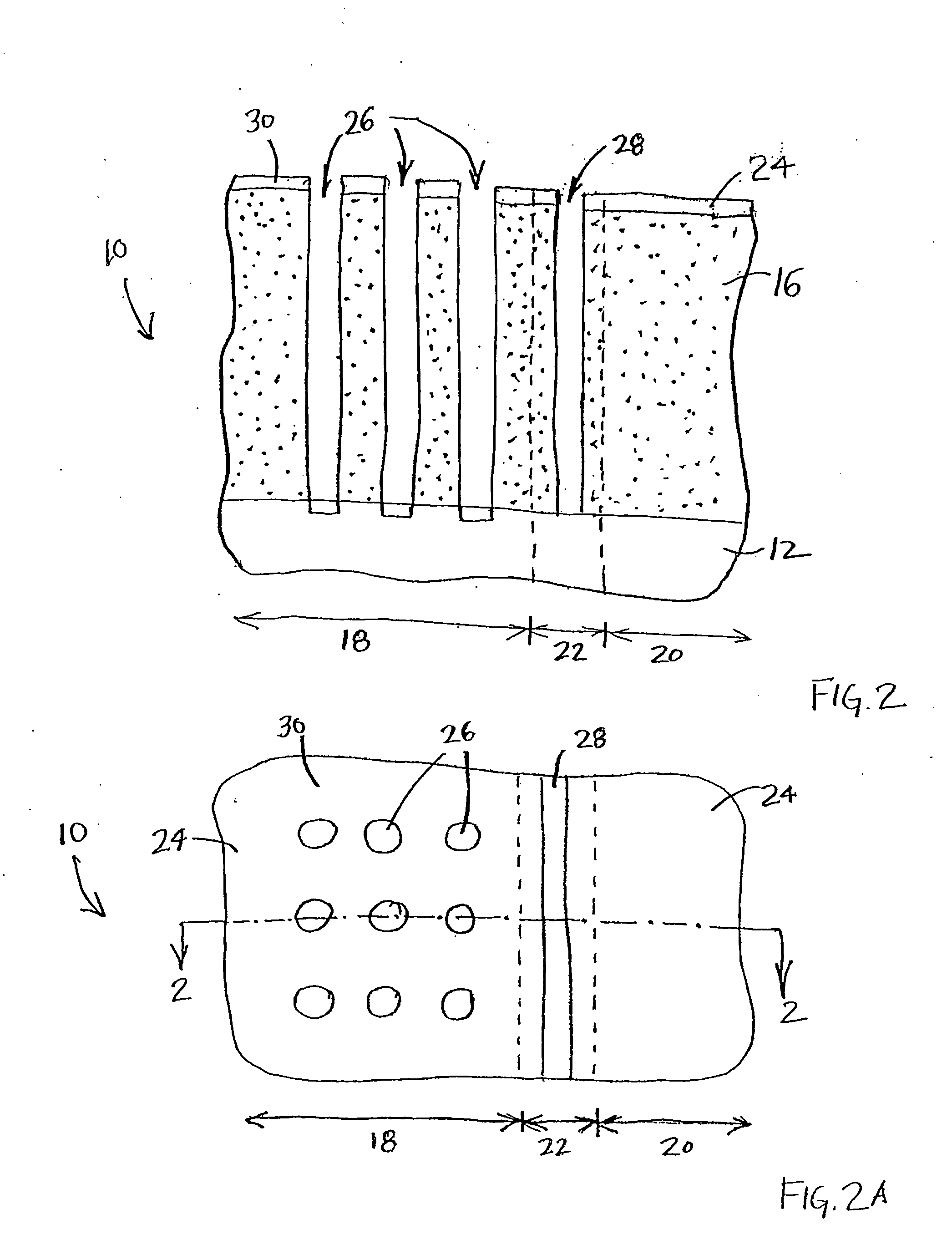

Image

Examples

example

[0055] The following example was conducted to study the effect of varying etchant formulations and v / v ratios of components on the selective removal of PSG relative to a low temperature silicon nitride (DCS SiN) and a high temperature silicon nitride (HCD SiN).

[0056] Wafers were provided with exposed layers of PSG and silicon nitride (DCS SiN or HCD SiN), and immersed for 30 seconds in a bath containing the etch solution shown in the table below. The bath temperature was room temperature (i.e., 23° C.).

[0057] The results are shown in the table below.

Selectivity1Etch Rates (Å / min)PSG:DCS-PSG:HCD-DCS SiNHCD SiNEtchant solutionRatio (v)SiNSiNPSG(725° C.)(600° C.)DI:HF (49%)210:1˜200:1˜50:1˜9600˜48˜190(comparative)DI:HF (49%):HNO3310:1:1.5˜400:1˜60:1˜14000˜35˜230(comparative)PA:HF (49%)410:1˜1200:1 ˜270:1 ˜47000˜40˜180PA:HF (49%):HNO3410:1:1 Unknown˜330:1 ˜20000Unknown˜60

1PSG = phosphosilicate glass; DSC-SiN = dichlorosilane silicon nitride (high temperature deposition); HCD-SiN = ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| dielectric constant | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More