Silicon wafer back metallization structure and manufacturing process thereof

A technology of backside metallization and silicon wafers, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problem of poor coordination of subsequent packaging processes, failure to achieve low-cost stability, and existence of warping or debris And other problems, to achieve good conductivity, good adhesion, improve the effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

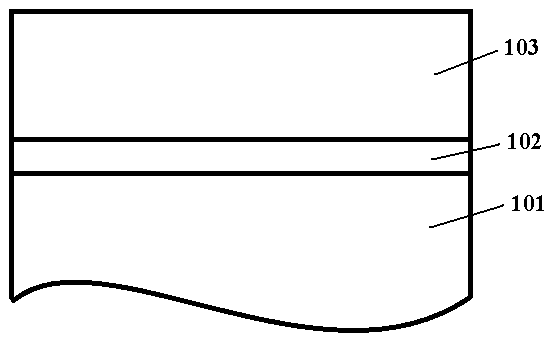

[0024] The metallization structure on the backside of the silicon wafer is as figure 1 shown. The first metal layer 102 is hafnium with a thickness of 300 nm, and the second metal layer 103 is gold with a thickness of 2000 nm. The processing steps are: front protection, back thinning, back polishing, cleaning, magnetron sputtering at a rate of 5 nm / s to prepare a hafnium layer, and evaporation at a rate of 3 nm / s to prepare a gold layer.

Embodiment 2

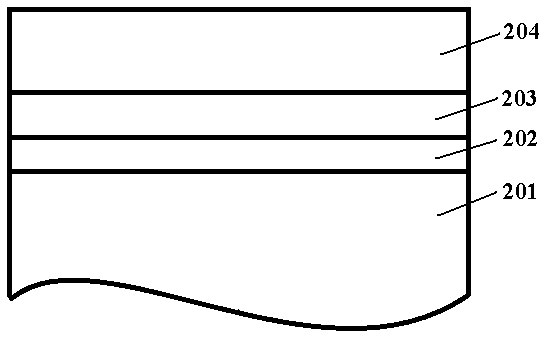

[0026] The metallization structure on the backside of the silicon wafer is as figure 2 shown. The first metal layer 202 is hafnium with a thickness of 30 nm, the second metal layer 203 is nickel with a thickness of 600 nm, and the third metal layer 204 is silver or gold with a thickness of 2000 nm. The processing steps are: front protection, back thinning, back polishing, cleaning, electron beam evaporation at a rate of 0.5 nm / s to prepare a hafnium layer, magnetron sputtering at a rate of 15 nm / s to prepare a nickel layer, and a rate of 10 nm / s to prepare a hafnium layer. nm / s rate for magnetron sputtering to prepare gold layer or 15 nm / s rate for magnetron sputtering to prepare silver layer.

Embodiment 3

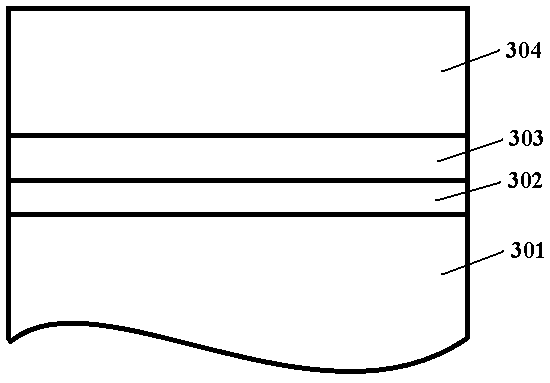

[0028] The metallization structure on the backside of the silicon wafer is as image 3 shown. The first metal layer 302 is hafnium with a thickness of 200nm, the second metal layer 303 is a gold-germanium alloy with a thickness of 500nm, and the third metal layer 304 is silver or gold with a thickness of 100nm. The processing steps are: front protection, back thinning, back polishing, cleaning, magnetron sputtering at a rate of 15 nm / s to prepare a hafnium layer, evaporation at a rate of 0.5 nm / s to prepare a gold germanium layer, and a rate of 0.5 nm / s to prepare a gold germanium layer. / s to prepare a gold layer or evaporate at a rate of 3 nm / s to prepare a silver layer.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More