Enhanced high-electron-mobility transistor based on ferroelectric group III nitride polarization reversion

A technology with high electron mobility and polarization reversal, which is applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of no ferroelectric properties and limitations, and achieve low lattice mismatch, film and interface quality Good, growth process compatible effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

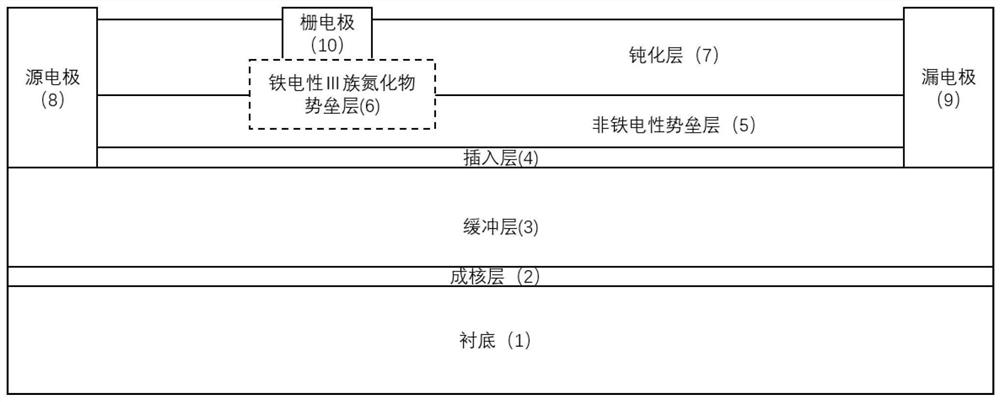

[0032] When the non-ferroelectric barrier layer 5 is omitted, the ferroelectric Group III nitride barrier layer 6 is a complete layer with both ends connected to the source electrode 8 and the drain electrode 9 and covers the insertion layer 4 . The preparation of the device can be realized through the following steps:

[0033] Metal-organic chemical vapor deposition (MOCVD) was used to sequentially deposit an AlN nucleation layer 2 with a thickness of 50 nm, a GaN buffer layer 3 with a thickness of 1.5 μm, an AlN insertion layer 4 with a thickness of 1.5 nm and a thickness of 40 nm on a Si substrate 1. Al 0.64 sc 0.36 N ferroelectric group III nitride barrier layer 6; then use photolithography process and electron beam evaporation process to make source electrode 8 and drain electrode 9; then use electron beam evaporation process to form ferroelectric group III nitride barrier layer 6 Deposit the gate electrode on top, or use photolithography process and electron beam evapo...

Embodiment 2

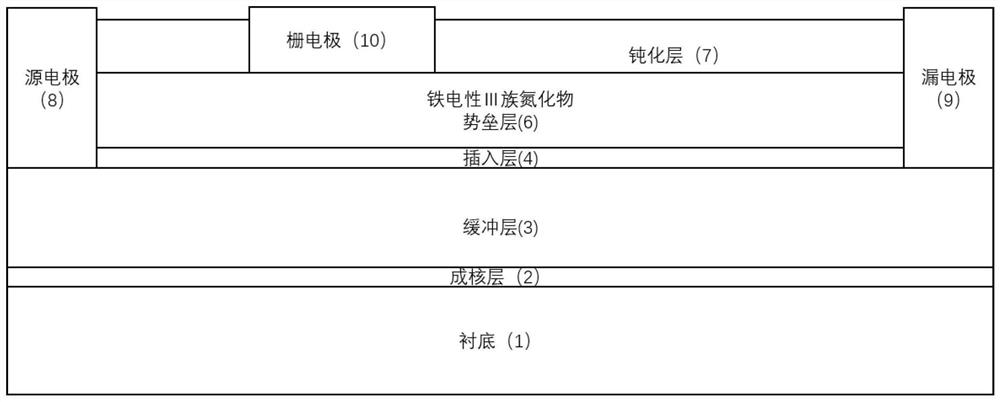

[0035] When the non-ferroelectric barrier layer 5 is not omitted, and the ferroelectric III-nitride barrier layer 6 is partially or completely embedded in the non-ferroelectric barrier layer 5, the device can be prepared by the following steps:

[0036] Metal-organic chemical vapor deposition (MOCVD) was used to sequentially deposit an AlN nucleation layer 2 with a thickness of 60 nm, a GaN buffer layer 3 with a thickness of 2 μm, an AlN insertion layer 4 with a thickness of 1.5 nm, and a GaN layer with a thickness of 30 nm on a Si substrate 1. Al 0.2 Ga 0.8 N non-ferroelectric barrier layer 5; then use photolithography process and electron beam evaporation process to make source electrode 8 and drain electrode 9; then etch groove on barrier layer 5, the groove depth is 20nm, and use molecular Beam epitaxy (MBE) deposits Al with a thickness of 40nm in the etched groove 0.65 sc 0.35 N ferroelectric group III nitride barrier layer 6; then deposit the gate electrode on the fer...

Embodiment 3

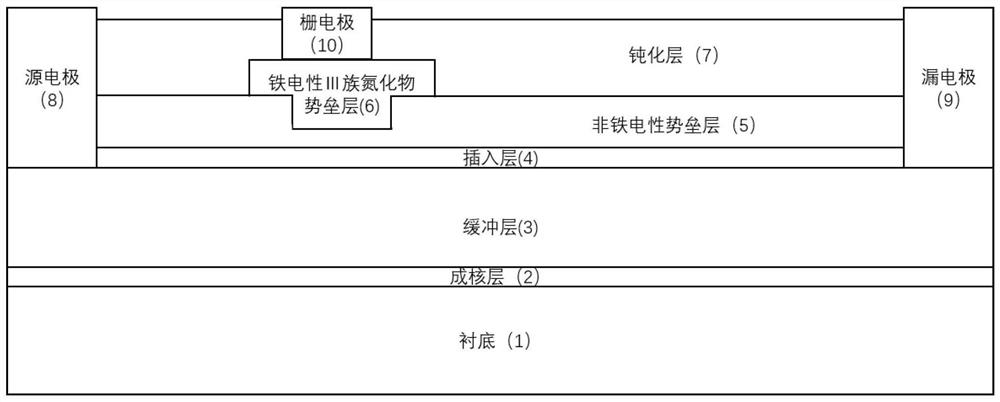

[0038] When the non-ferroelectric barrier layer 5 adopts group III nitrides without ferroelectric properties, and the ferroelectric group III nitride barrier layer 6 is completely embedded in the barrier layer 5, the preparation of the device is realized by the following steps:

[0039] Metal-organic chemical vapor deposition (MOCVD) was used to sequentially deposit an AlN nucleation layer 2 with a thickness of 70 nm, a GaN buffer layer 3 with a thickness of 2.5 μm, an AlN insertion layer 4 with a thickness of 1 nm, and a GaN intercalation layer with a thickness of 30 nm on a sapphire substrate 1. al 0.25 Ga 0.75 N non-ferroelectric barrier layer 5; then use photolithography process and electron beam evaporation process to make source electrode 8 and drain electrode 9; then implant doped modified ions Er, And perform activation diffusion, the diffusion depth is 20nm, so that the non-ferroelectric barrier layer 5 in this part of the region has ferroelectric properties, and the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More