Semiconductor devices with copper interconnects and composite silicon nitride capping layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

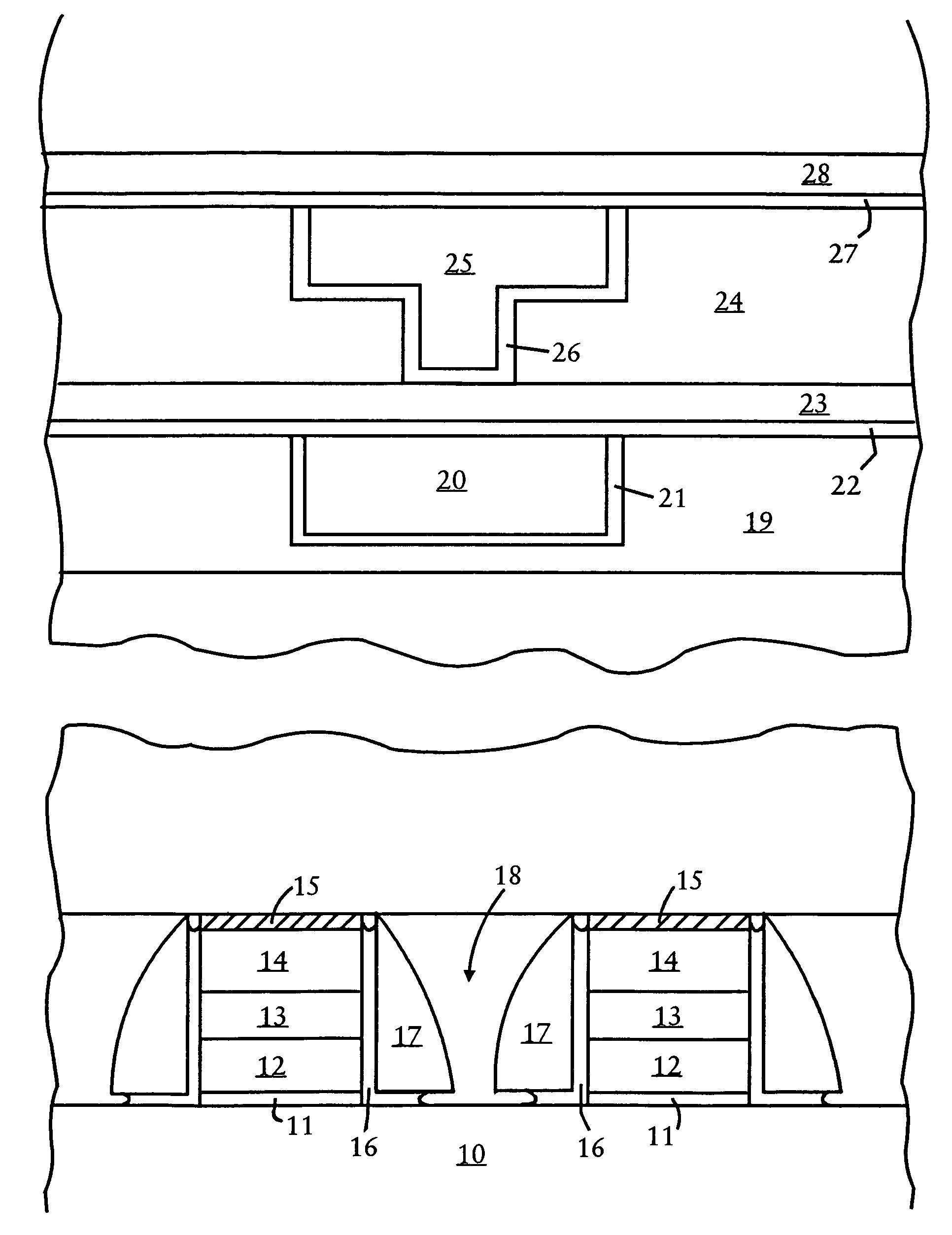

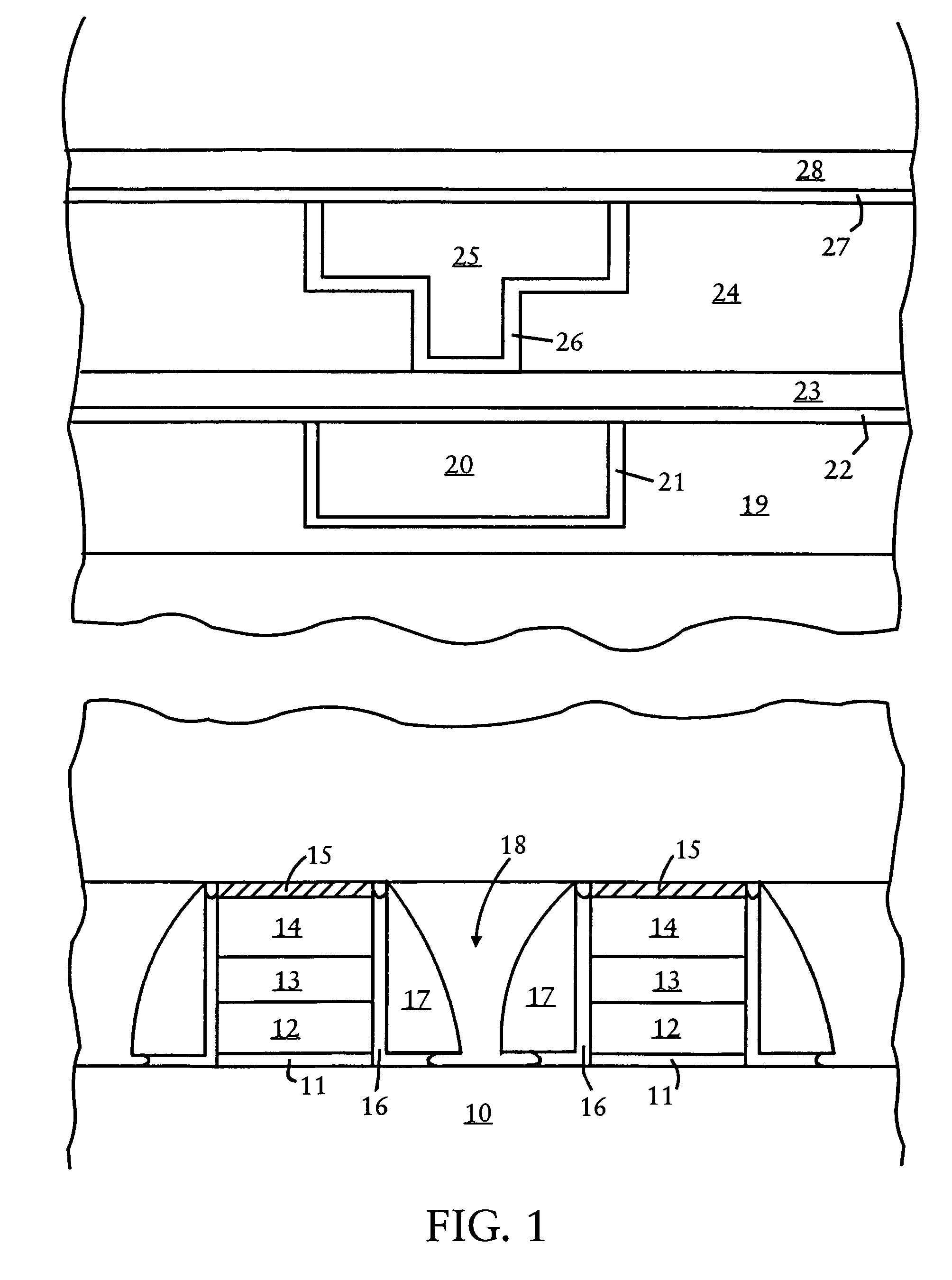

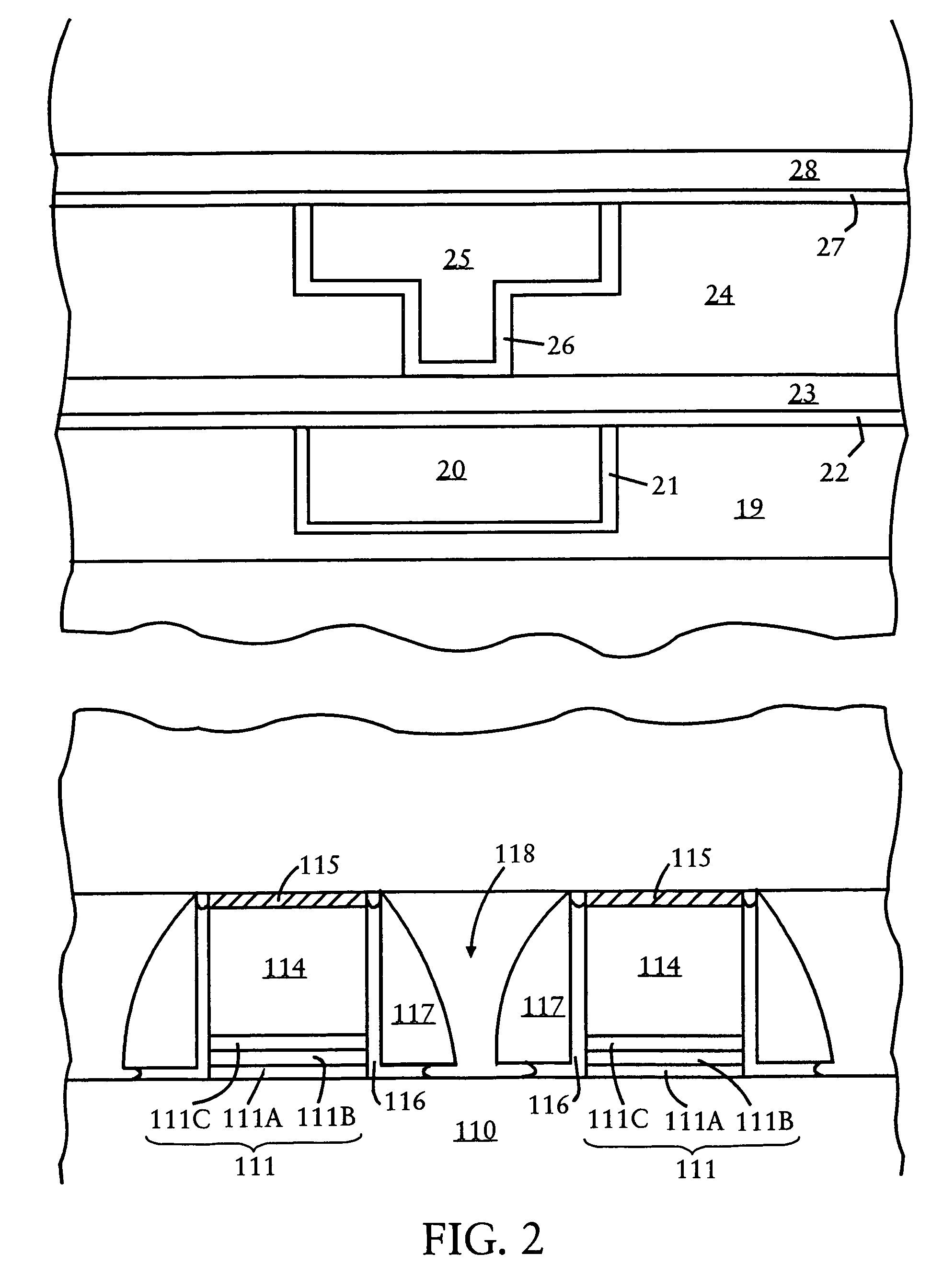

[0018]The present invention addresses and solves various reliability problems attendant upon conventional semiconductor fabrication techniques. These problems arise as semiconductor memory device dimensions continue to shrink, making it increasingly more difficult to effectively getter mobile ion contaminants, such as hydrogen. The hydrogen contamination problem becomes exacerbated when integrating copper interconnect technology with flash memory devices. It was found that conventionally deposited silicon nitride capping layers exhibit a relatively high degree of Si—H bonding, such as about 0.3% to about 0.9%, thereby generating charge loss problems for miniaturized flash technology. It was also found that the conventionally deposited silicon nitride layers do not adequately adhere to inlaid copper subsequent to implementing Cu CMP processing, even when the Cu surface is treated with an ammonia plasma. Such poor adhesion exacerbates electromigration issues.

[0019]The present inventio...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Fraction | aaaaa | aaaaa |

| Fraction | aaaaa | aaaaa |

| Fraction | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More