Insulating layer upper semiconductor structure with low dielectric constant as insulation buried layer and its method

A technology of low dielectric constant and insulating buried layer, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc. Large equivalent impedance, reduced capacitance, suitable for low noise effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

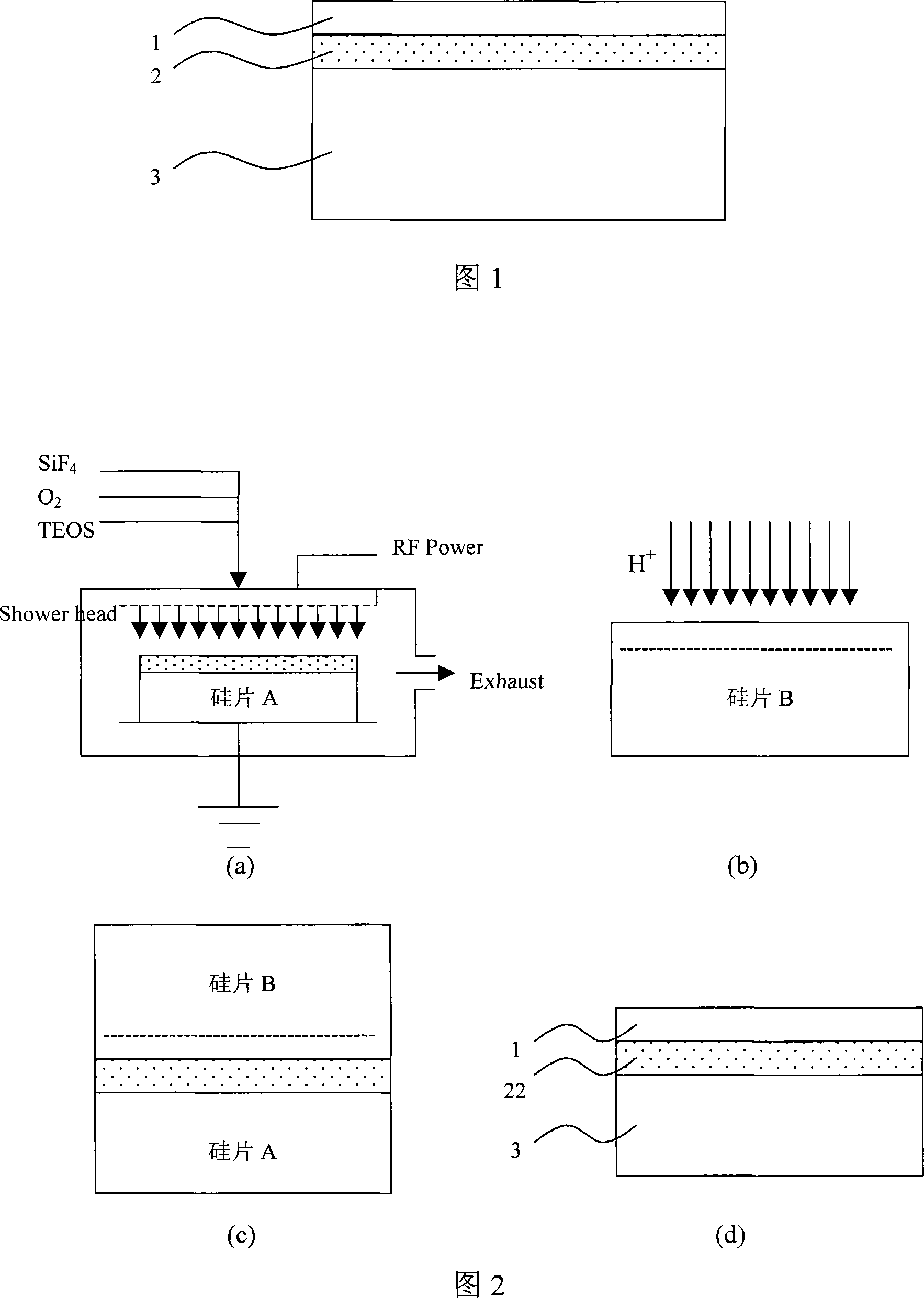

[0038] Embodiment 1: A method for fabricating an SOI structure containing a low dielectric constant SiOF buried layer.

[0039] 1. Using n-type (100) silicon wafer A as the substrate material, SiOF film was prepared by plasma enhanced chemical vapor deposition (PECVD), as shown in Figure 2(a), with TEOS, SiF 4 , O 2 As the raw material, the flow rate is 20sccm, 40sccm, 40sccm respectively, the pressure in the reaction chamber is 90Pa, and the substrate temperature is 400°C;

[0040] 2. In order to ensure the bonding quality, the silicon wafer A deposited with the SiOF film is chemically mechanically polished to reduce the surface roughness to below 1nm;

[0041] 3. Perform H on silicon wafer B + Injection, as shown in Figure 2(b), the injection dose is 6E16cm -2 , the injection energy is 140keV;

[0042]4. The two silicon wafers are bonded by plasma activation at room temperature, as shown in Fig. 2(c). Before bonding, the silicon wafer is cleaned by RCA, and then the sur...

Embodiment 2

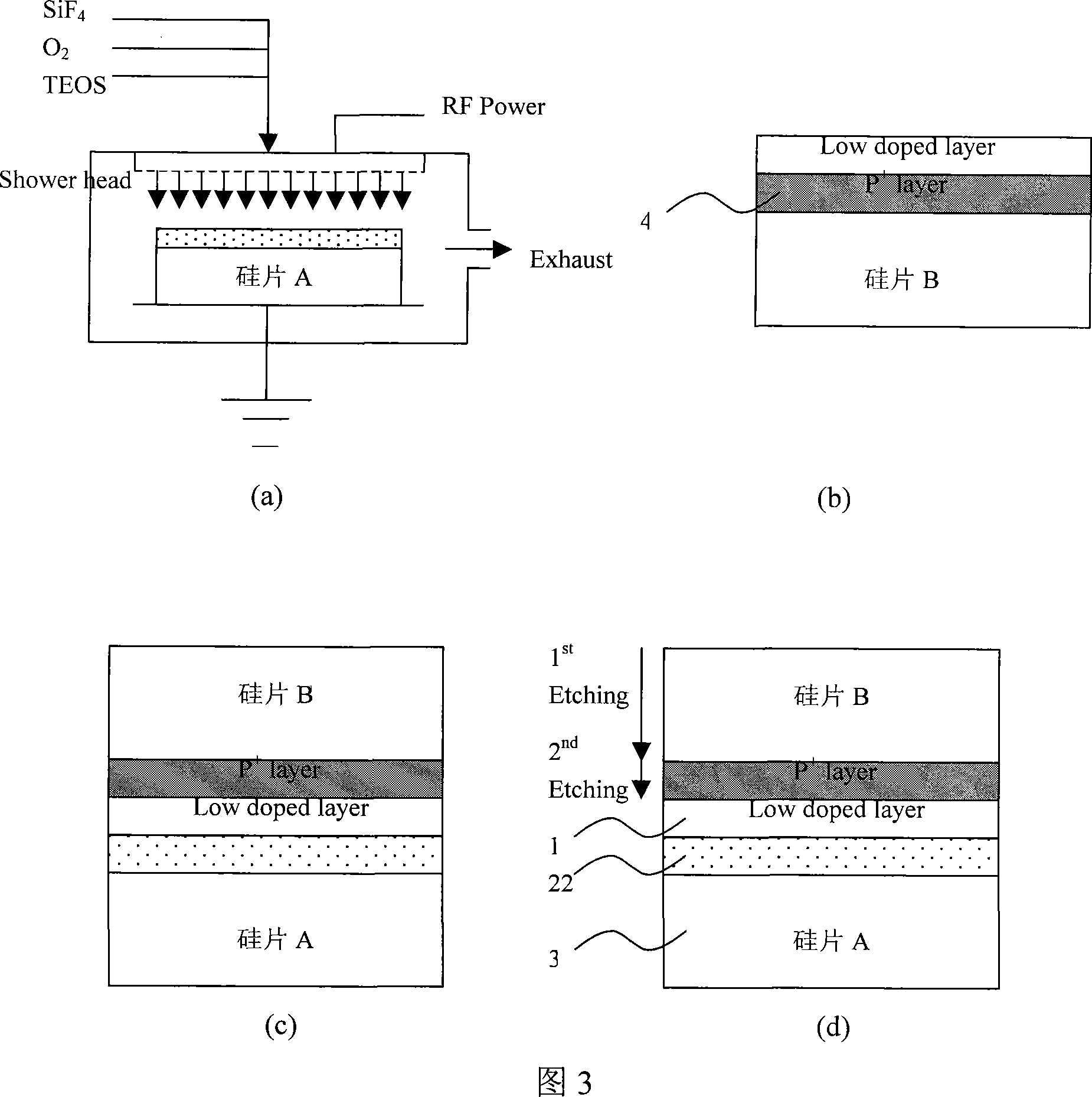

[0045] Embodiment 2: A method for fabricating an SOI structure containing a low dielectric constant SiOF buried layer.

[0046] 1. Using n-type (100) silicon wafer A as the substrate material, SiOF film was prepared by plasma enhanced chemical vapor deposition (PECVD), as shown in Figure 3(a), with TEOS, SiF 4 , O 2 As the raw material, the flow rate is 20sccm, 40sccm, 40sccm respectively, the pressure in the reaction chamber is 90Pa, and the substrate temperature is 400°C;

[0047] 2. In order to ensure the bonding quality, the silicon wafer A deposited with the SiOF film is chemically mechanically polished to reduce the surface roughness to below 1nm;

[0048] 3. Epitaxial layer of 200nm P on silicon wafer B + The silicon layer is used as an etching stop layer, and a 50nm low-doped silicon layer is epitaxially, as shown in Figure 3(b);

[0049] 4. Perform room temperature plasma activated bonding of two silicon wafers, as shown in Figure 3(c). Before bonding, the silicon...

Embodiment 3

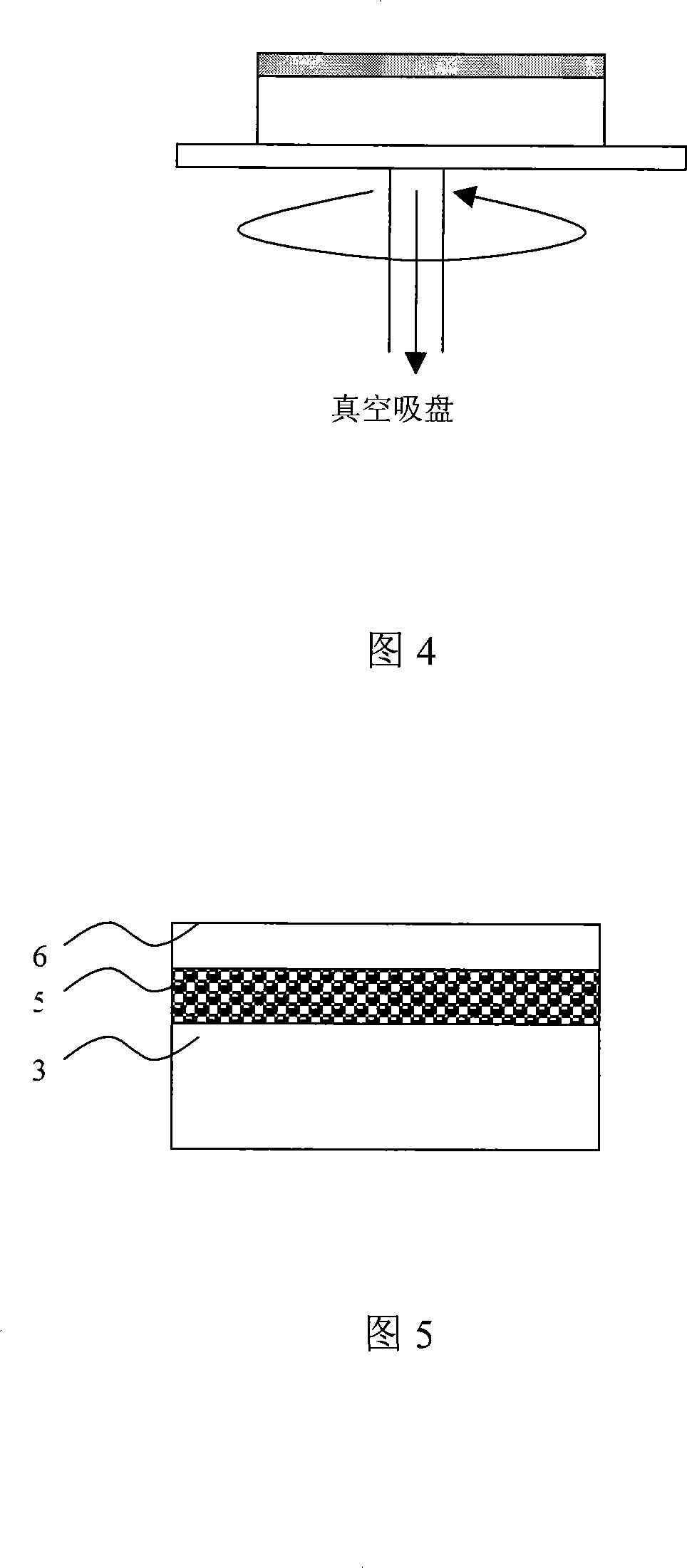

[0052] Embodiment 3: A method for preparing an SOI structure of a low dielectric constant SiOF buried layer.

[0053] 1. This example is exactly the same as Example 1, only the SiOF film is prepared by the sol-gel method, and the process parameters and conditions for the preparation. Organic compounds, the precursor solution was spin-coated on the silicon wafer at a spin-coating rate of 2500rpm, and then annealed at 400°C to prepare a SiOF film (Figure 4).

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More