Dual-SOI-structured MEMS pressure sensor chip and manufacturing method thereof

A pressure sensor and chip technology, which is applied to the measurement of fluid pressure by changing ohmic resistance, and the measurement of the property force of piezoelectric resistance materials. The effect of stability and no leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

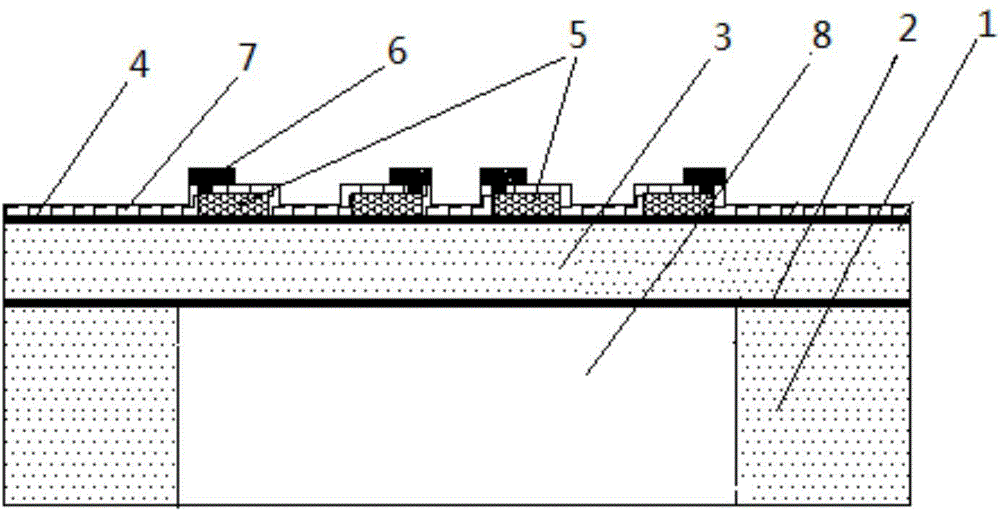

[0013] The present invention provides a dual SOI structure MEMS pressure sensor chip, see figure 1 , Including: SOI substrate silicon wafer, the SOI substrate silicon wafer includes a bottom P-type or N-type substrate silicon wafer 1, an SOI insulating isolation dielectric layer 2 and a single crystal silicon pressure sensitive film 3; the insulating isolation dielectric layer 2, for example An oxide layer is generated for thermal oxidation; after polishing the single-crystal silicon pressure sensitive film 3, an insulating isolation dielectric layer 4 is grown, and the insulating isolation dielectric layer 4 can be an oxide layer or a nitride layer; a low temperature α is deposited on the insulating isolation dielectric layer 4 -The silicon film is doped by ion implantation and then etched into a bridge resistor 5, which is annealed at 1000-1100°C; the monocrystalline silicon layer 3, the insulating isolation dielectric layer 4, and the α-silicon film layer 5 constitute the top ...

Embodiment 2

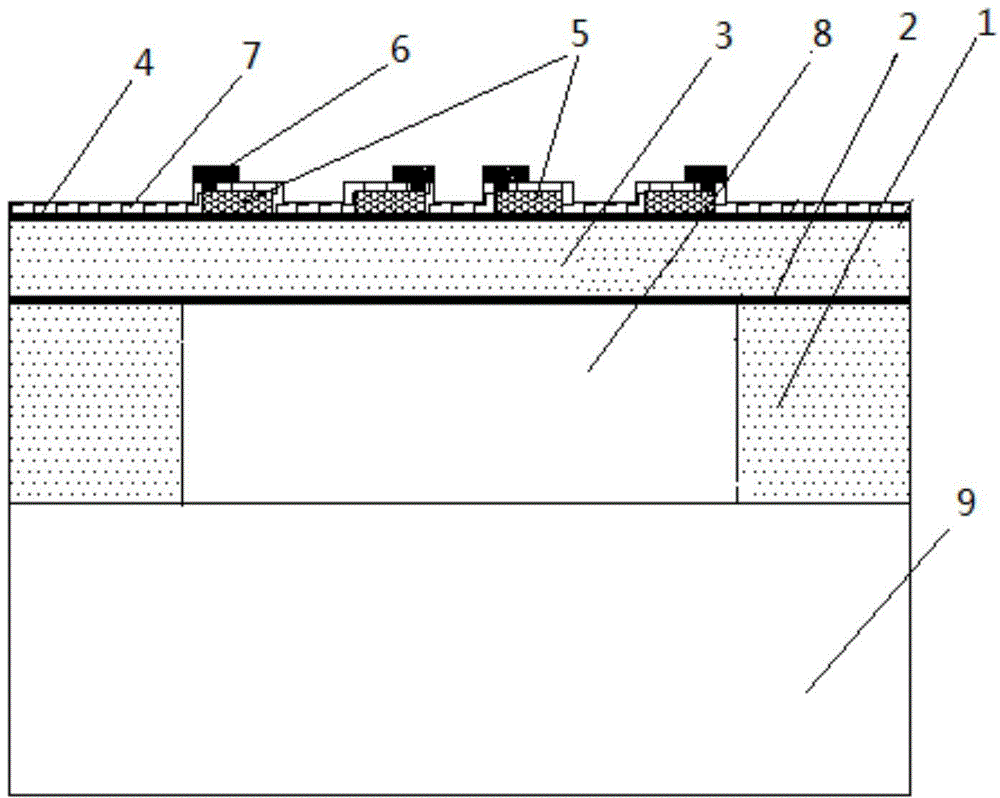

[0015] The present invention also provides an absolute pressure double SOI structure MEMS pressure sensor chip, see figure 2 , The same structure and components as in embodiment 1 will not be repeated, the difference is: after forming the gauge pressure chip pressure reference cavity 8 on the silicon substrate 1 through the ICP deep etching process, the glass sheet 9 is bonded on the back of the SOI substrate , To form an absolute pressure sensor chip structure.

Embodiment 3

[0017] The method for manufacturing a MEMS pressure sensor chip with a dual SOI structure provided by the present invention includes the following steps:

[0018] (1) Determine the size of the chip and sensitive film according to the pressure range requirements, determine the linear stress area on the pressure sensitive film through theoretical calculation, arrange the α-silicon resistor and metal interconnection, and make the photolithography to complete the design;

[0019] (2) P type or N type The crystal orientation silicon wafer is thermally oxidized, and then bonded to form an SOI substrate silicon wafer. The SOI substrate silicon wafer includes a P-type or N-type substrate silicon wafer 1, an insulating isolation dielectric layer of an SOI structure, and a monocrystalline silicon pressure Sensitive membrane type 3;

[0020] (3) Perform thinning and polishing processes on the top monocrystalline silicon 3 of the SOI substrate silicon wafer to reduce the thickness of the monocr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More