Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of low temperature, impurity activation rate of semiconductor devices is not ideal, etc., to reduce the lifetime of minority carriers, improve the conduction voltage drop, Effect of Reducing Switching Loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

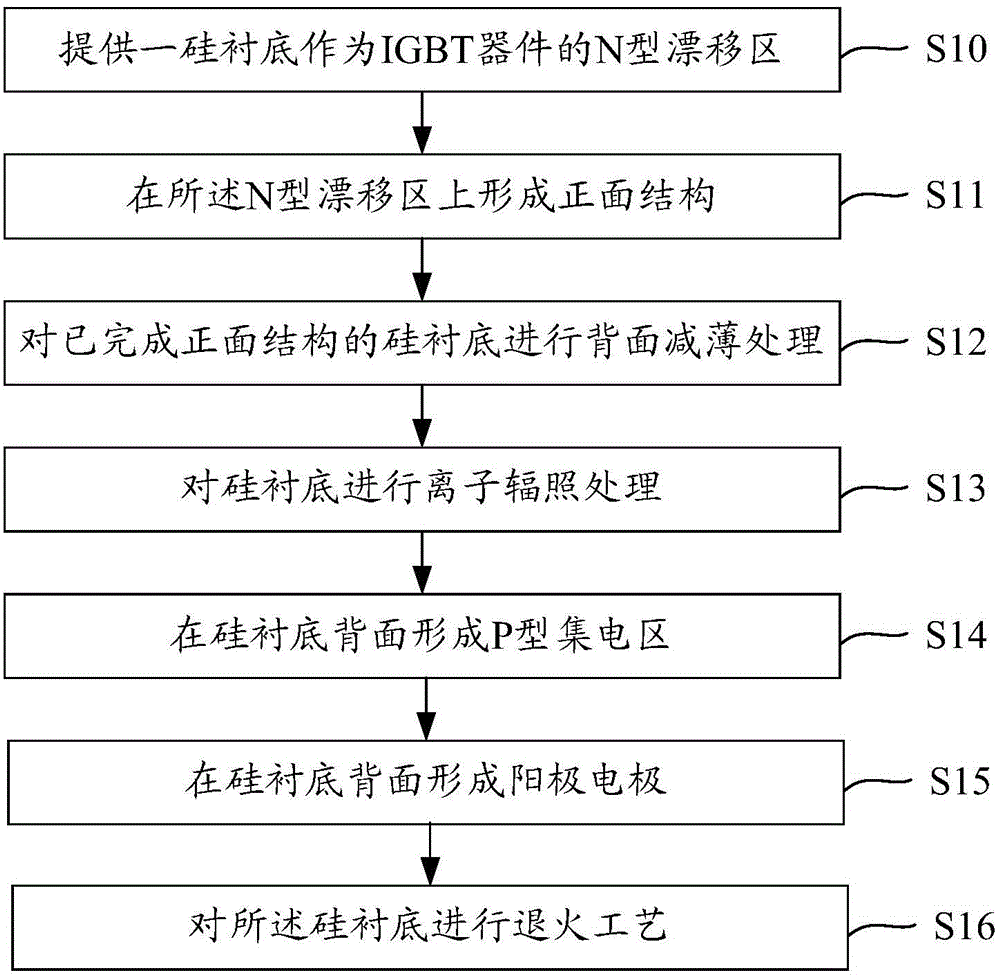

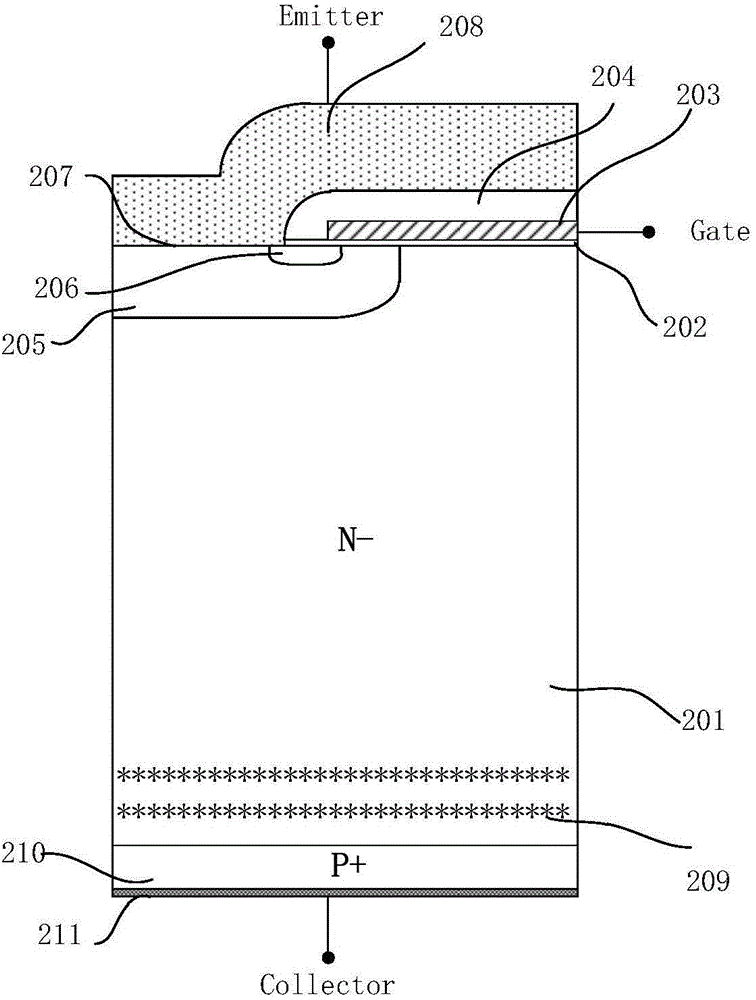

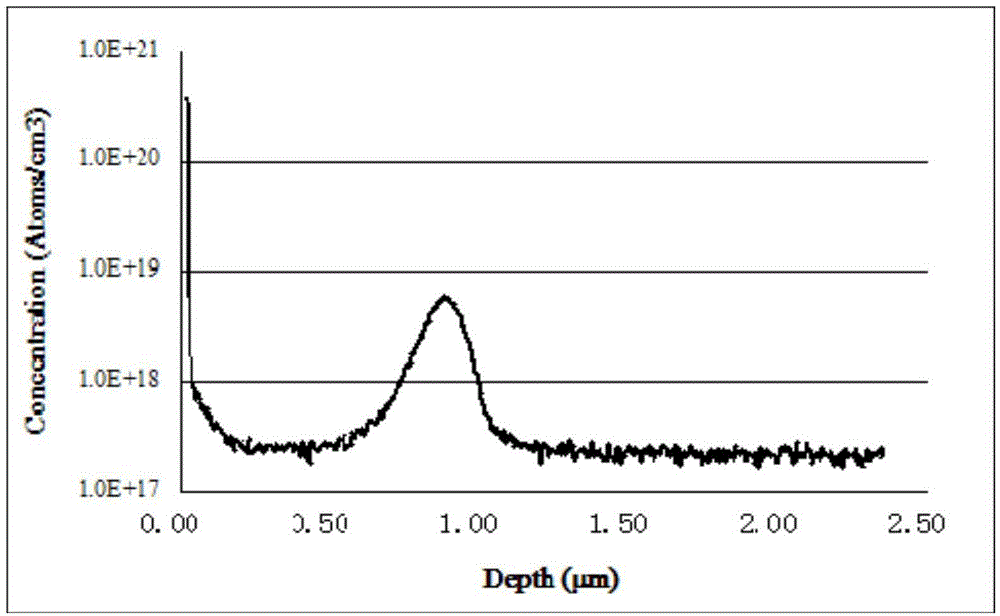

[0035] Take NPT type IGBT device as an example below, combined with attached Figure 1~3 The manufacturing method of the semiconductor device provided by the present invention is described in detail. The IGBT is a composite power device of MOS and BJT, and the NPT IGBT refers to a four-layer structure IGBT device.

[0036] First, perform step S10 to provide a silicon substrate as the N-type drift region 201 of the IGBT device. The silicon substrate can be a CZ wafer (Czochralski monocrystalline silicon wafer) obtained by the Czochralski method, or a pass-through region. The doping concentration of FZ wafers (zone-melting monocrystalline silicon wafers) obtained by the melting method can be freely selected. In this embodiment, the silicon substrate is N-type For the silicon wafer with crystal orientation, the resistivity of the silicon substrate is preferably between 20 and 80 ohm*cm.

[0037] Next, step S11 is performed to form a front structure on the N-type drift region 201. T...

Embodiment 2

[0046] Take NPT type PIN diode as an example, combined Figure 4~5 The manufacturing method of the semiconductor device provided by the present invention is described in detail. The PIN diode refers to a device in which a layer of intrinsic semiconductor is sandwiched between a P-type semiconductor and an N-type semiconductor.

[0047] First, perform step S30 to provide a silicon substrate as the N-type drift region 401 of the PIN diode. The silicon substrate can be a CZ silicon wafer obtained by the Czochralski method or an FZ silicon wafer obtained by the zone melting method. , Its doping concentration can be freely selected. In this embodiment, the silicon substrate is N-type For the silicon wafer with crystal orientation, the resistivity of the silicon substrate is preferably between 20 and 80 ohm*cm.

[0048] Next, step S31 is performed to form a front surface structure on the N-type drift region 201. The front structure includes: a P+ anode region 402 and a cathode electr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More