Thermal annealing for Cu seed layer enhancement

a technology of cu alloy and enhancement layer, which is applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of reducing production throughput, increasing the rxc delay caused by the interconnect wiring, and severe requirements for semiconductor fabrication technology, etc., to reduce voids, enhance the film, and reduce the resistance of cu or cu alloy interconnects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]The present invention addresses and solves various problems attendant upon forming metallized interconnects, such as Cu or Cu alloy interconnects, particularly, damascene structures in dielectric layer(s) having a dielectric constant less than about 3.9. As employed throughout this application, the symbol Cu is intended to encompass high purity elemental copper as well as Cu-based alloys, such as Cu alloys containing minor amounts of tantalum, indium, tin, zinc, manganese, titanium, magnesium, chromium, titanium, germanium, strontium, platinum, magnesium, aluminum or zirconium.

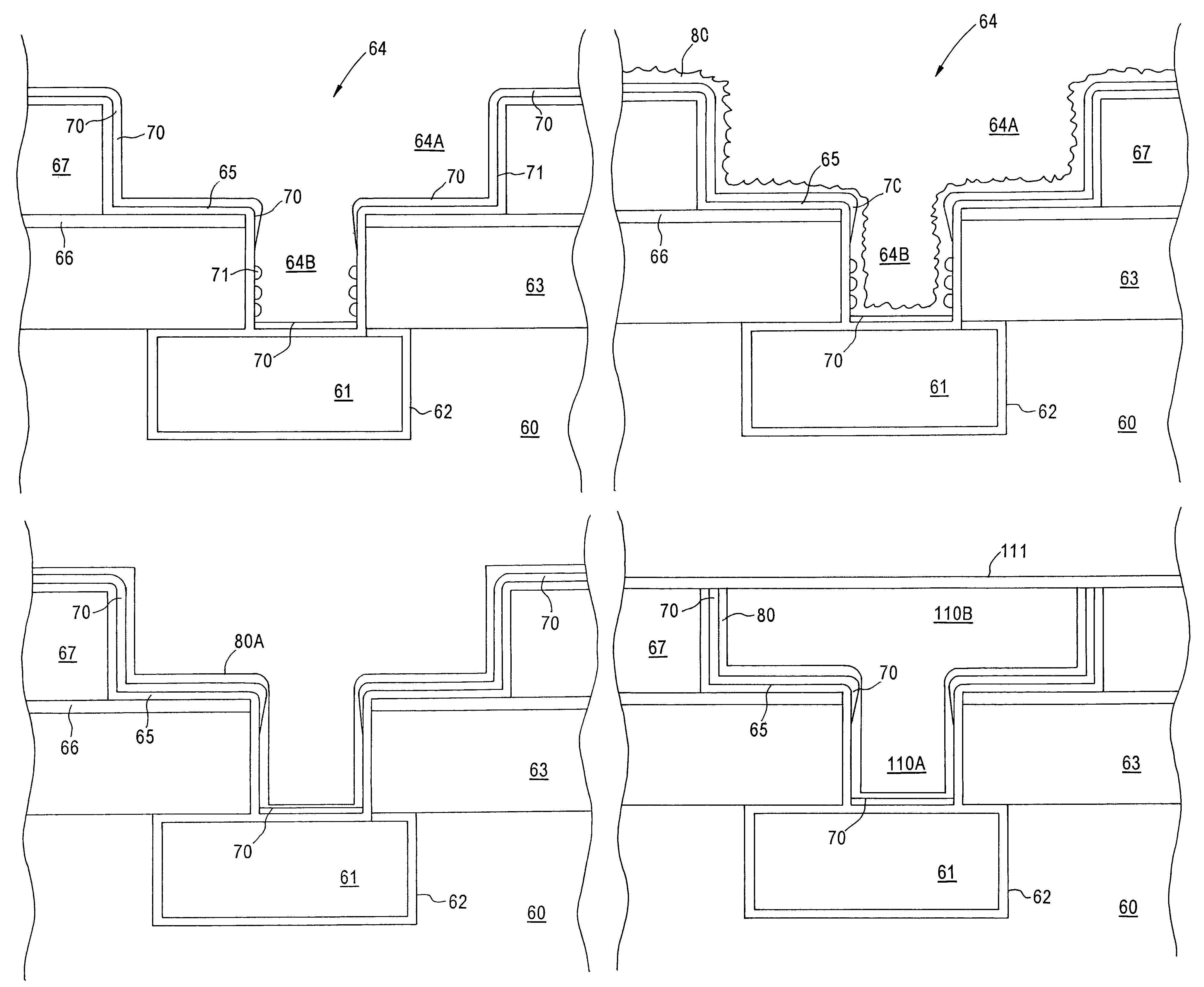

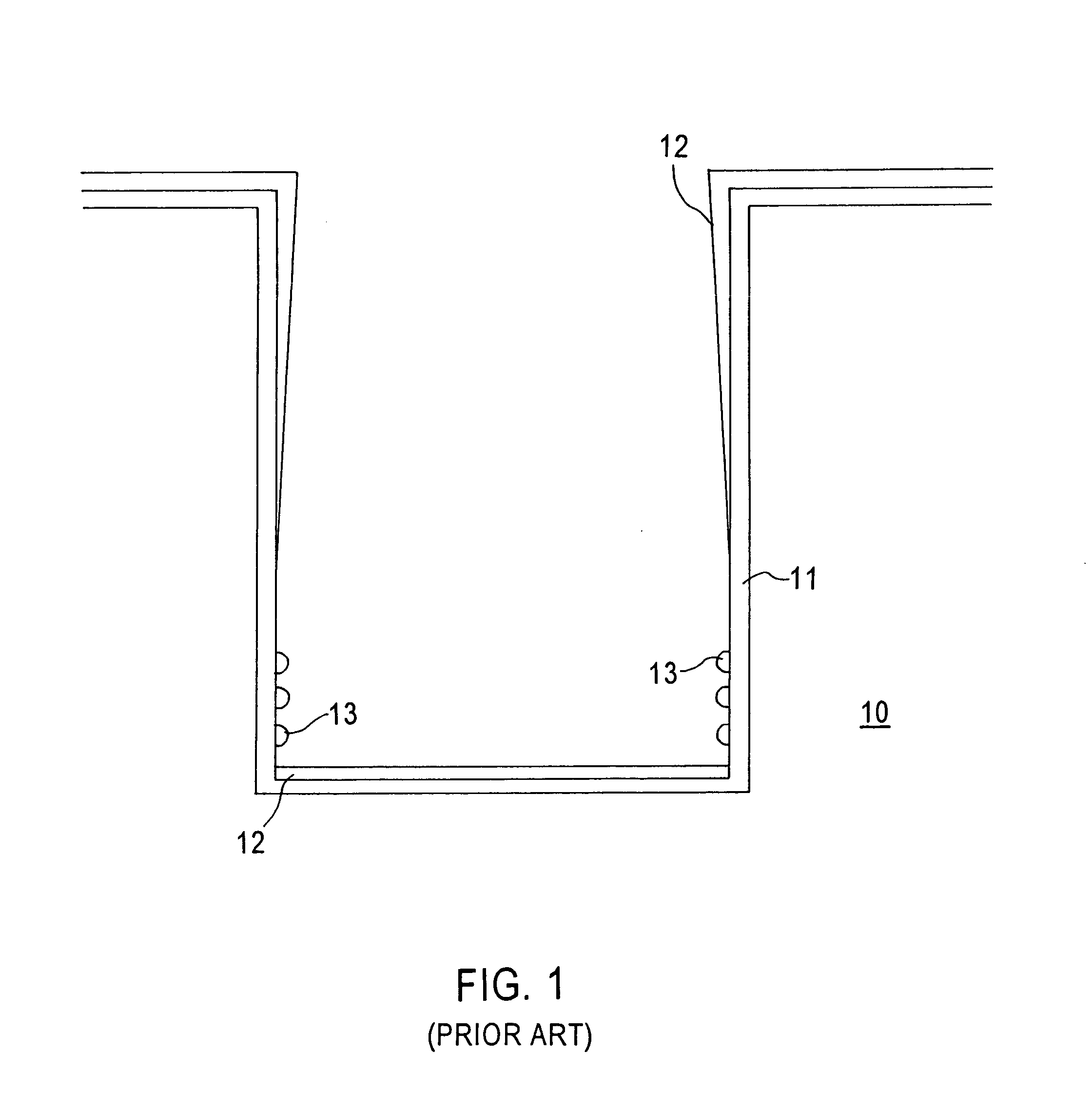

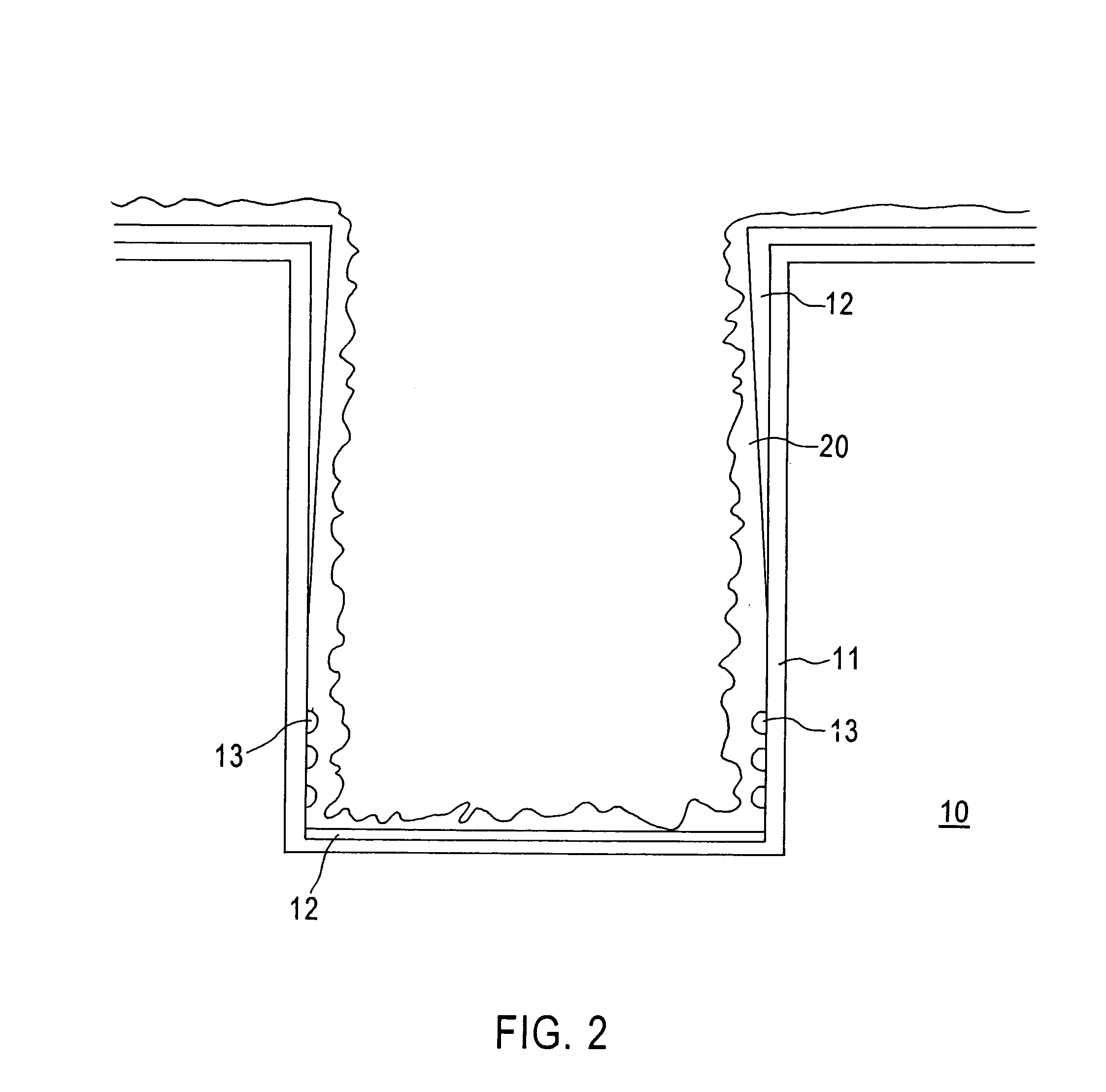

[0020]As design rules are scaled down into the deep sub-micron range, such as about 0.12 micron and under, reliability and contact resistance issues associated with interconnects, particularly Cu interconnects, become increasingly significant. Reliability and contact resistance issues stem, in part, from the inability to deposit a continuous seed layer for Cu deposition, particularly as the dimensions sh...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More