Patents

Literature

34results about "Logarithmic/exponential functions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

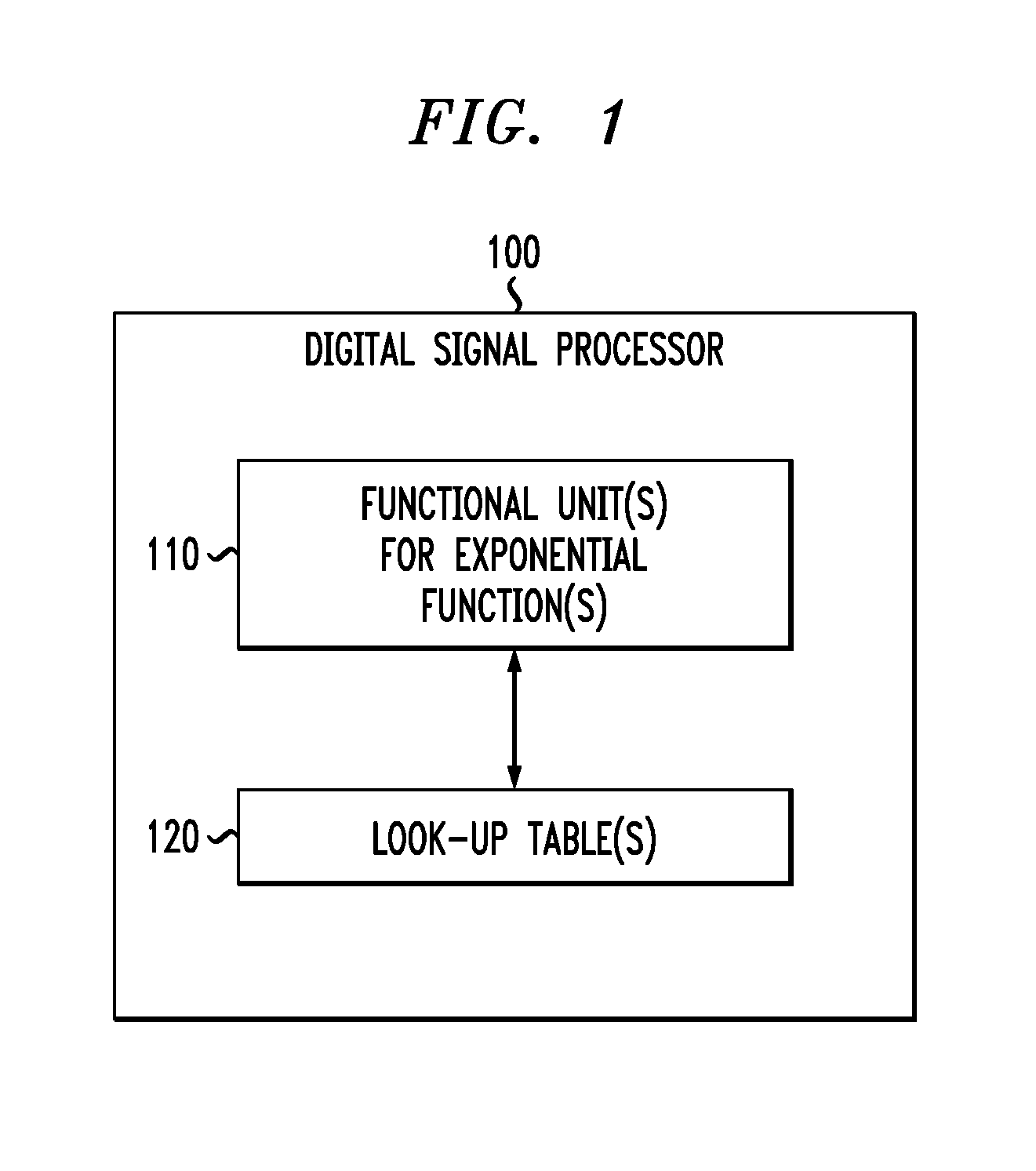

Digital signal processor having instruction set with an xK function using reduced look-up table

ActiveUS9207910B2Logarithmic/exponential functionsComputation using non-contact making devicesDigital signal processingIndex function

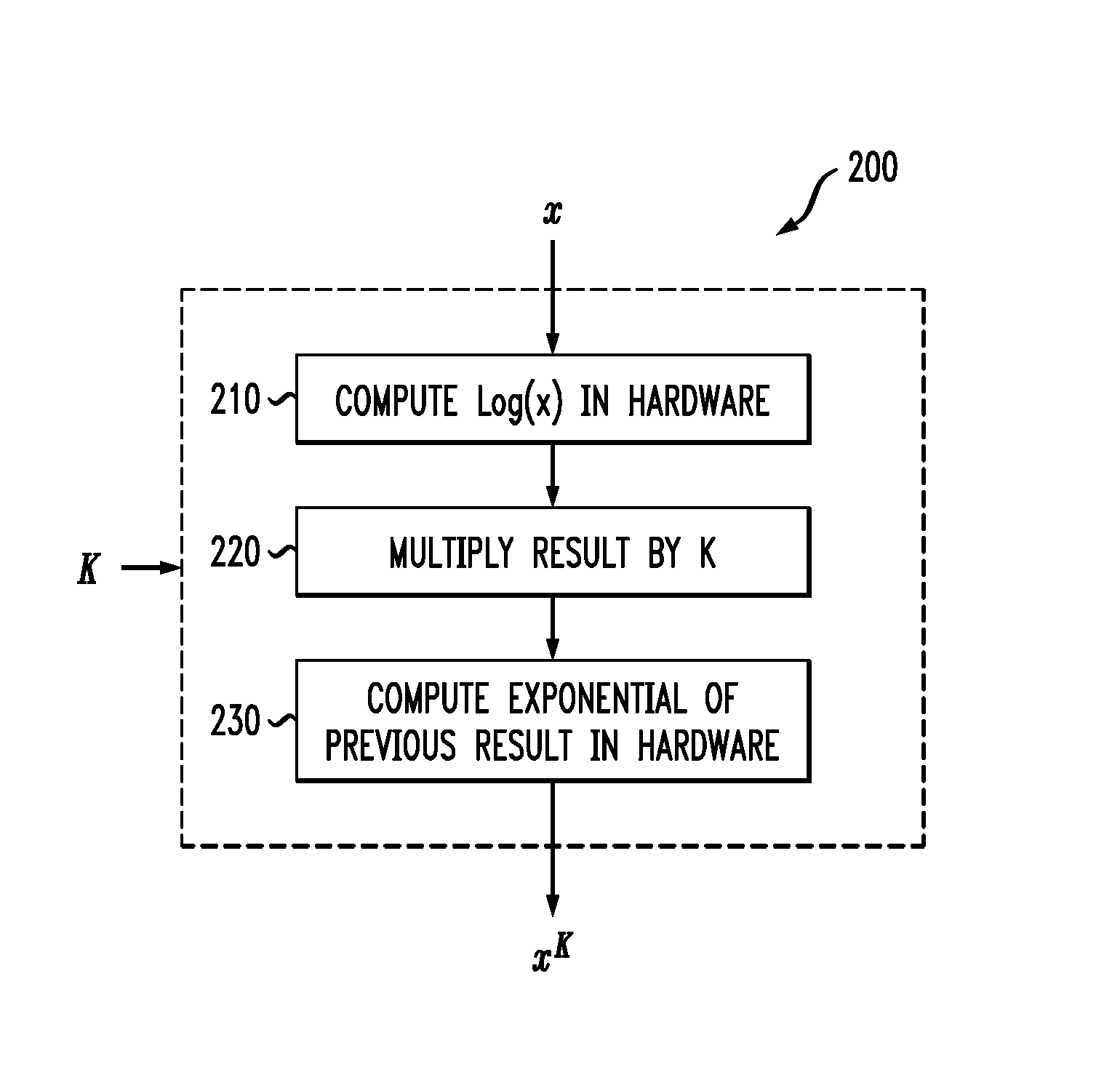

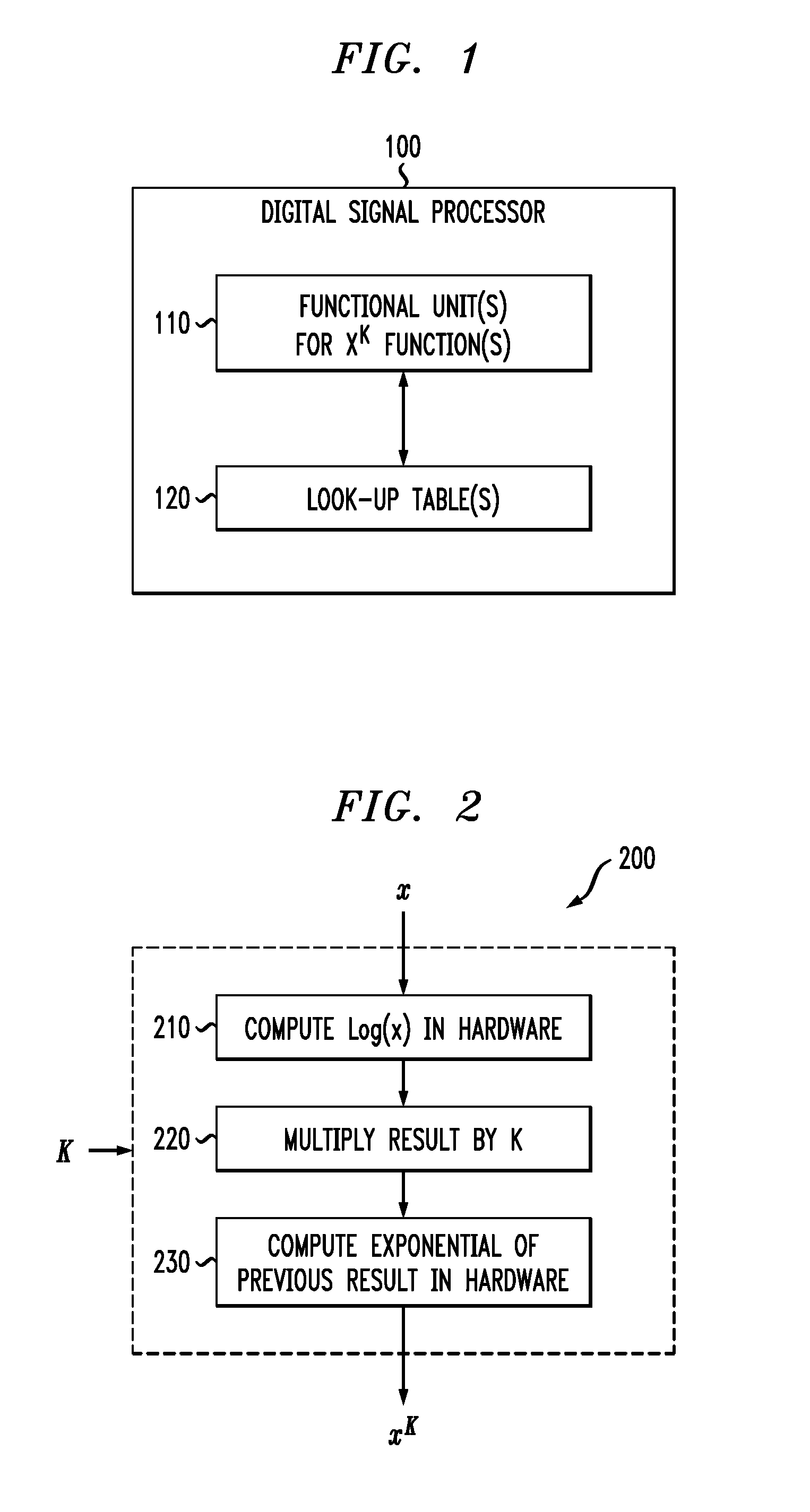

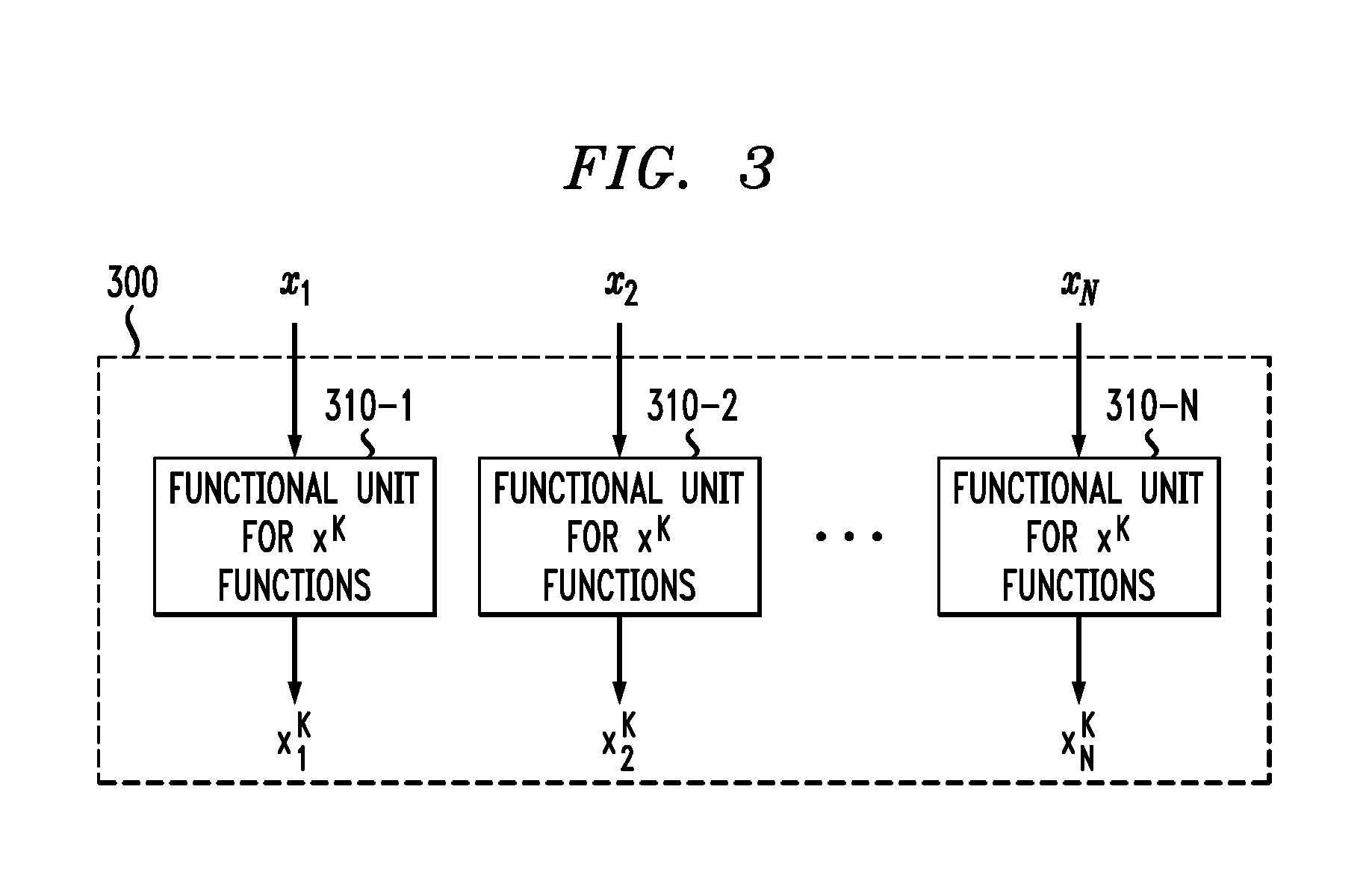

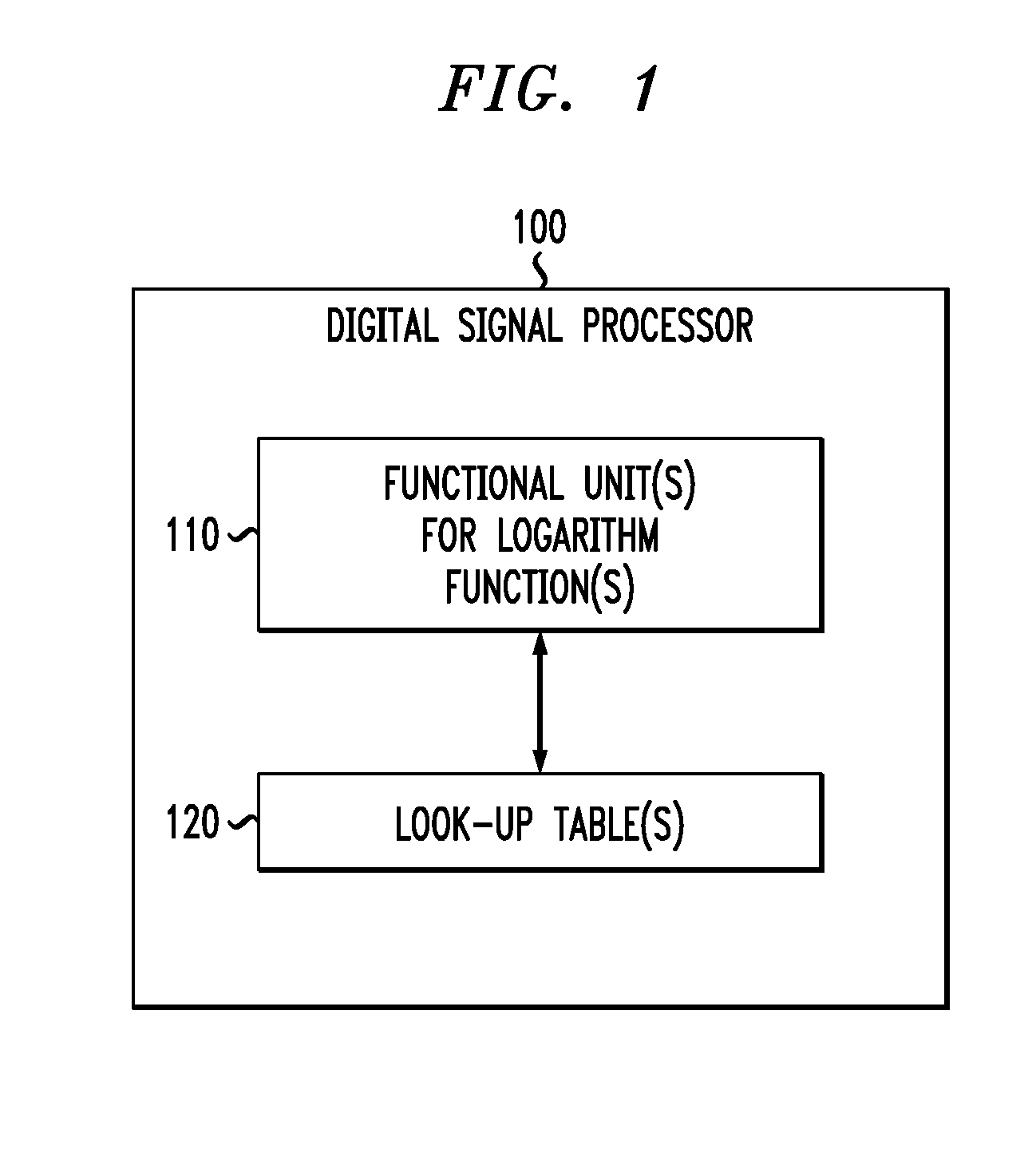

A digital signal processor is provided having an instruction set with an xK function that uses a reduced look-up table. The disclosed digital signal processor evaluates an xK function for an input value, x, by computing Log(x) in hardware; multiplying the Log(x) value by K; and determining the xK function by applying an exponential function in hardware to a result of the multiplying step. One or more of the computation of Log(x) and the exponential function employ at least one look-up table having entries with a fewer number of bits than a number of bits in the input value, x.

Owner:INTEL CORP

Method and system for approximating sine and cosine functions

Owner:ATI TECH INC

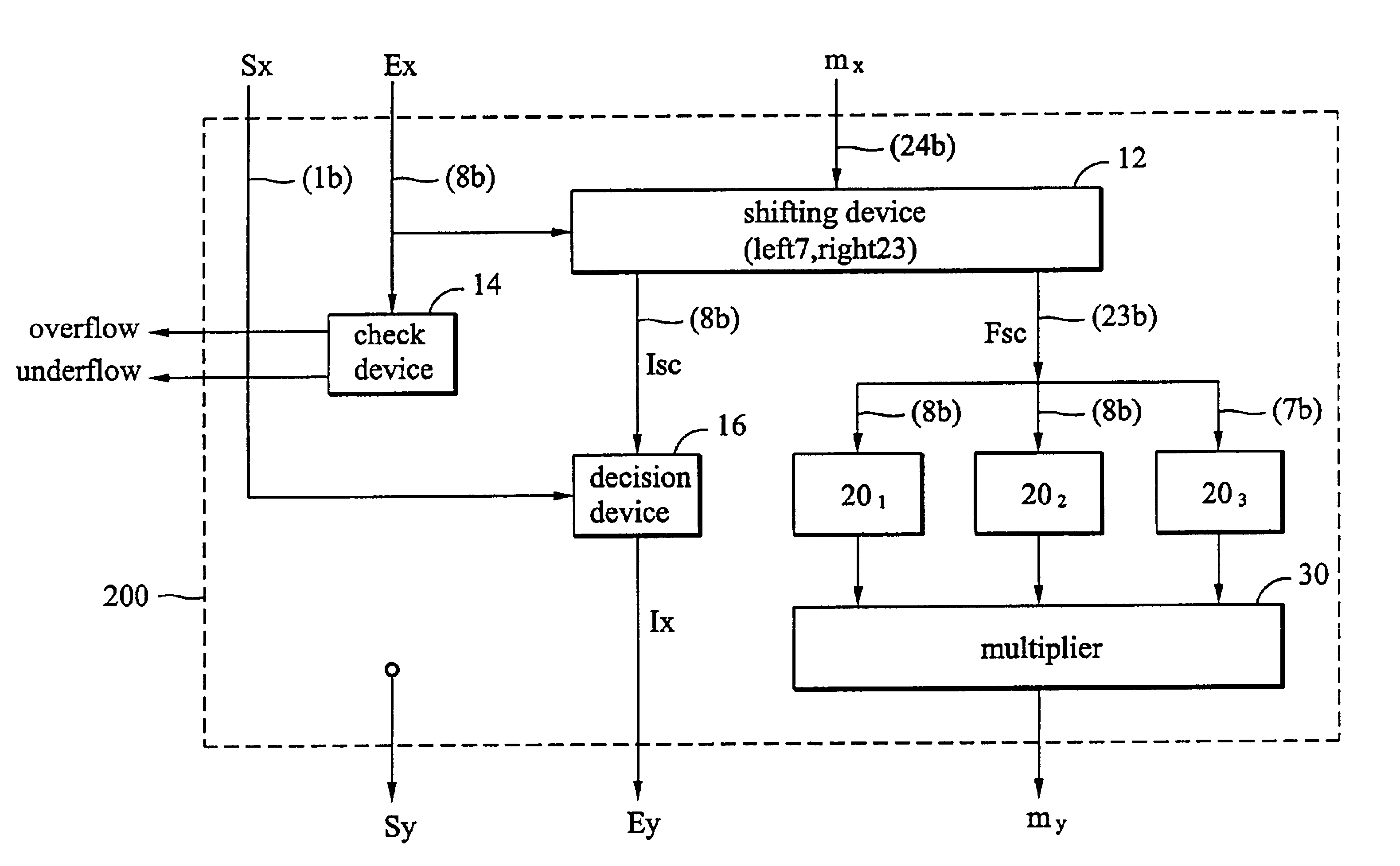

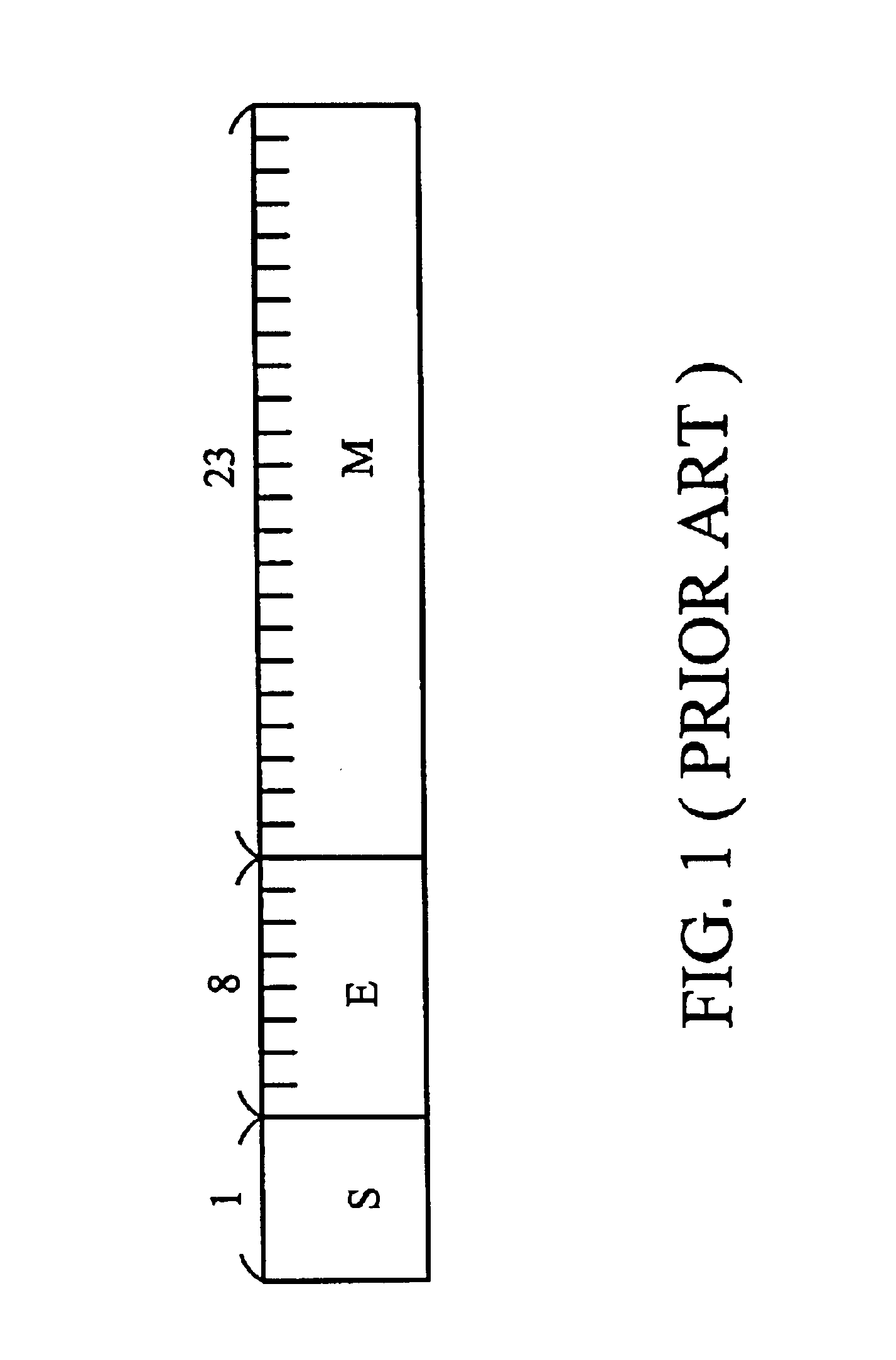

Apparatus and method for calculating an exponential calculating result of a floating-point number

InactiveUS6910059B2Computations using contact-making devicesLogarithmic/exponential functionsFloating pointComputer science

Owner:SILICON INTEGRATED SYSTEMS

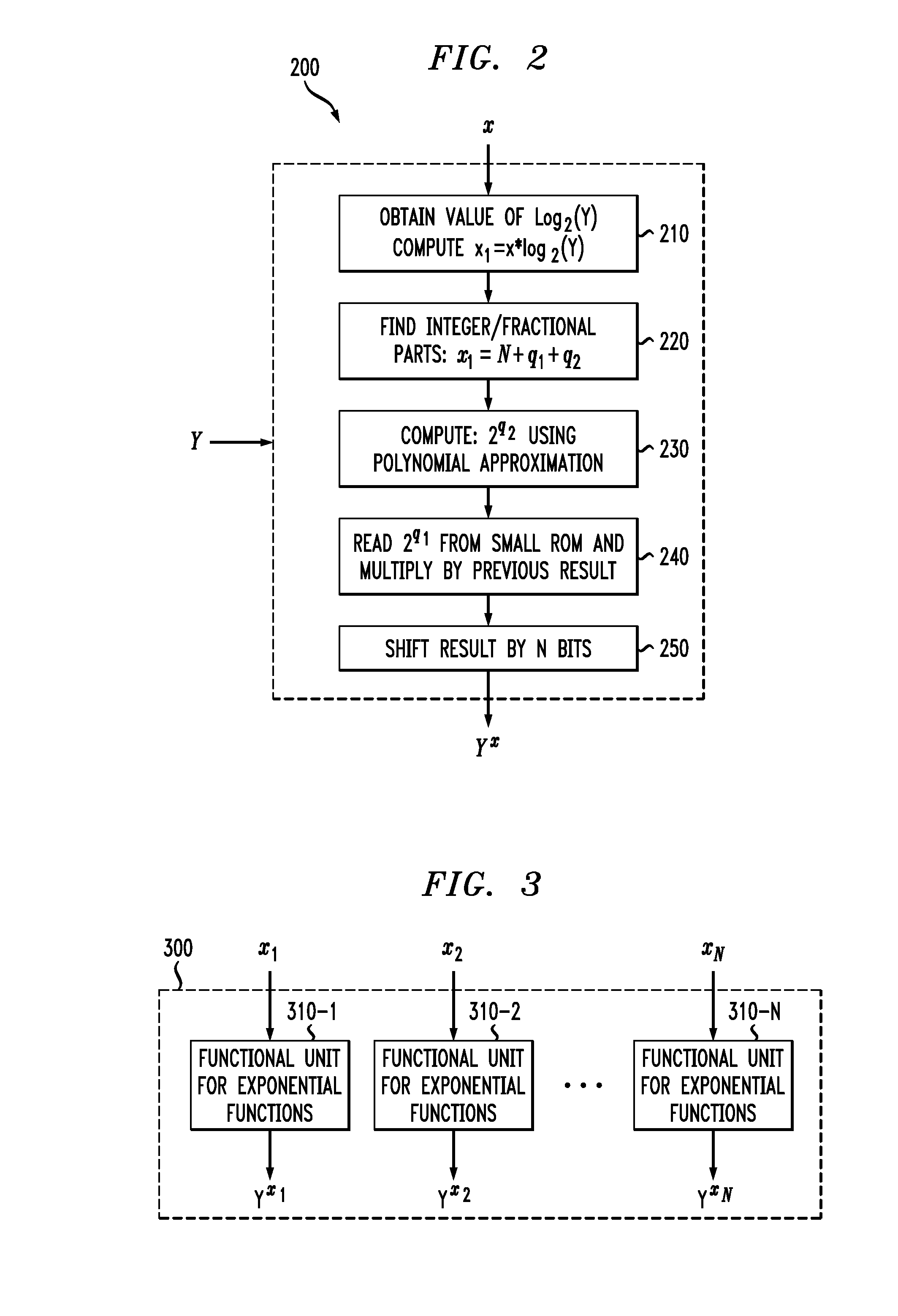

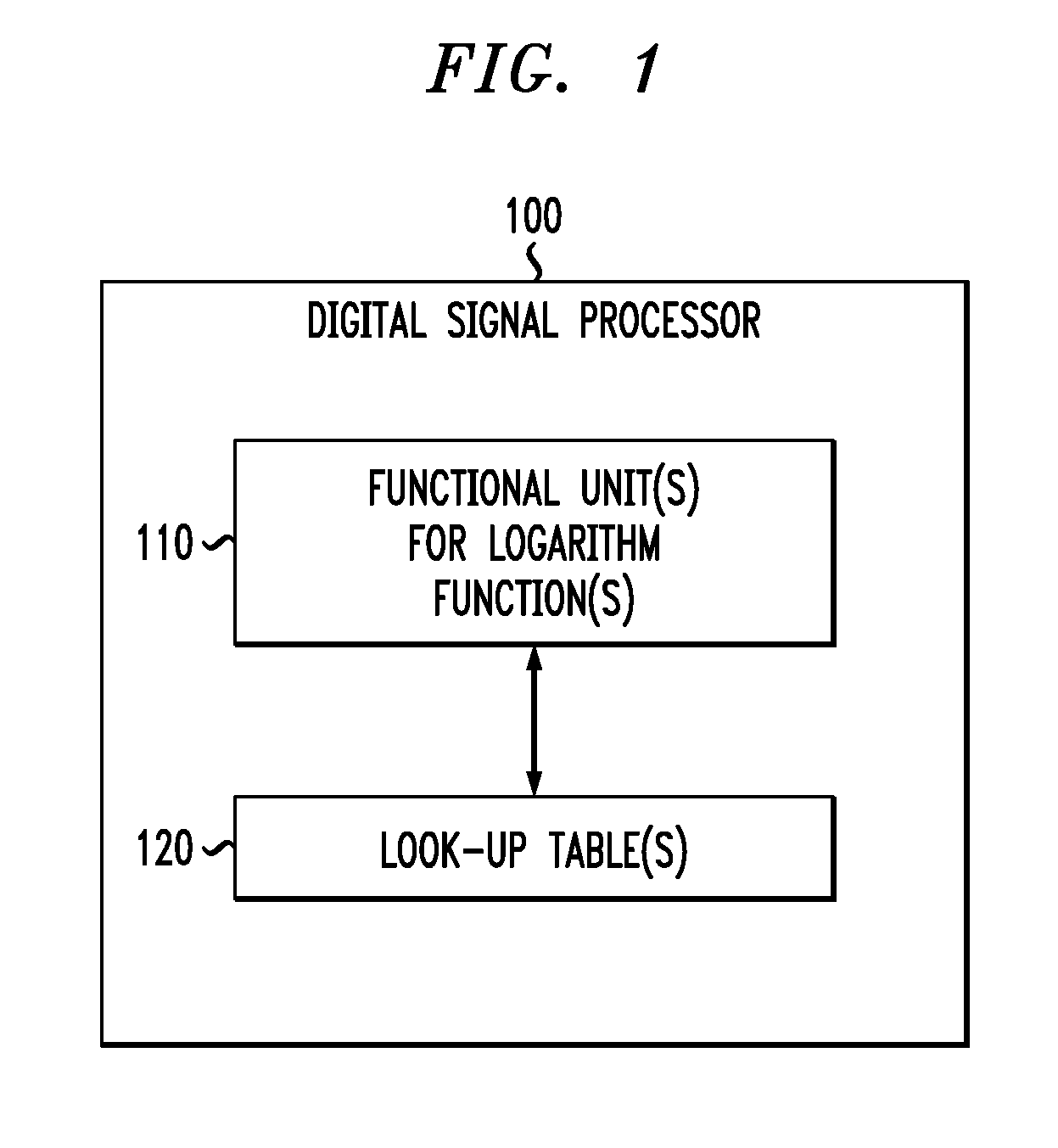

Digital Signal Processor Having Instruction Set With An Exponential Function Using Reduced Look-Up Table

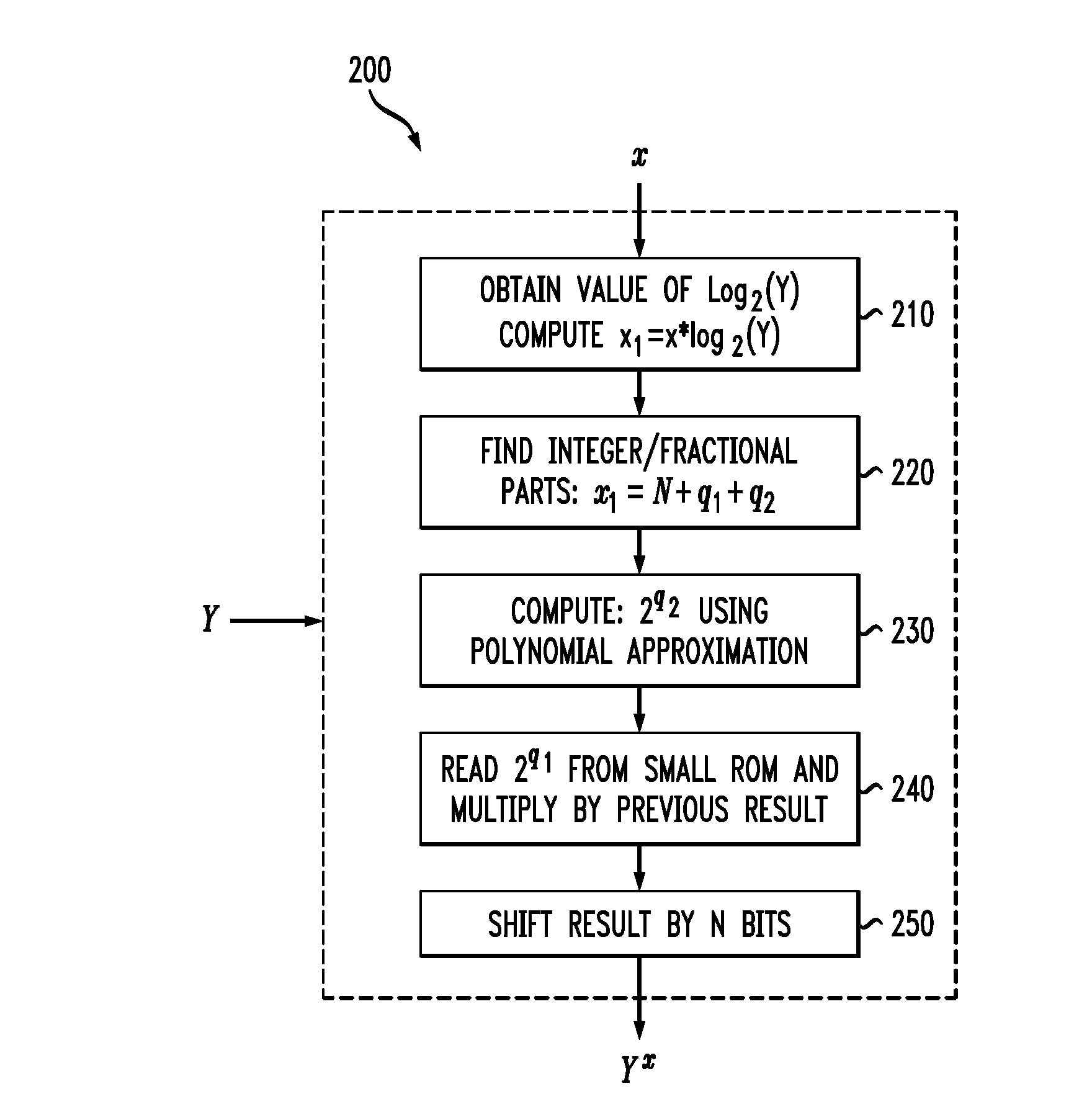

InactiveUS20100198894A1Logarithmic/exponential functionsComputation using non-contact making devicesAlgorithmInstruction set

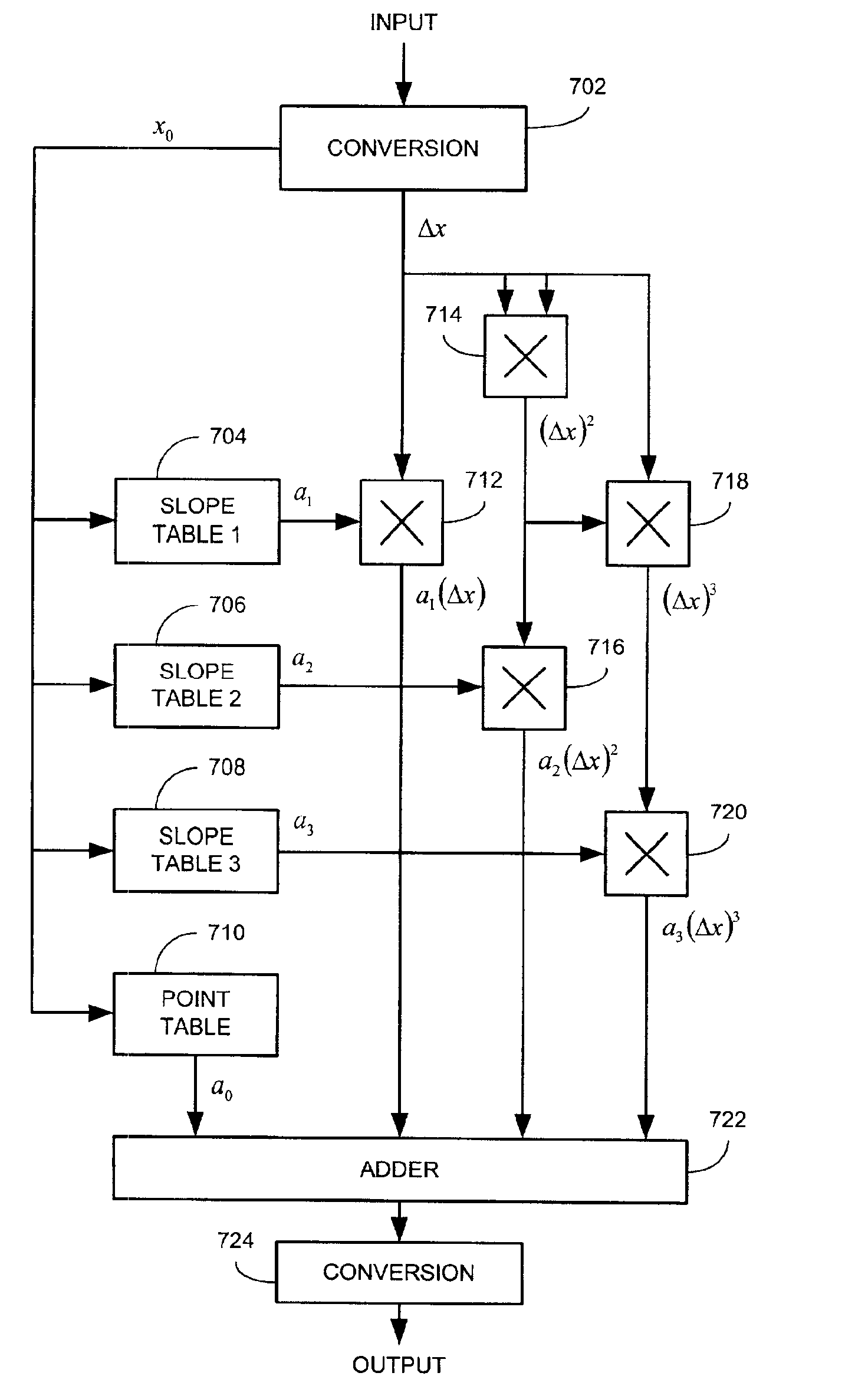

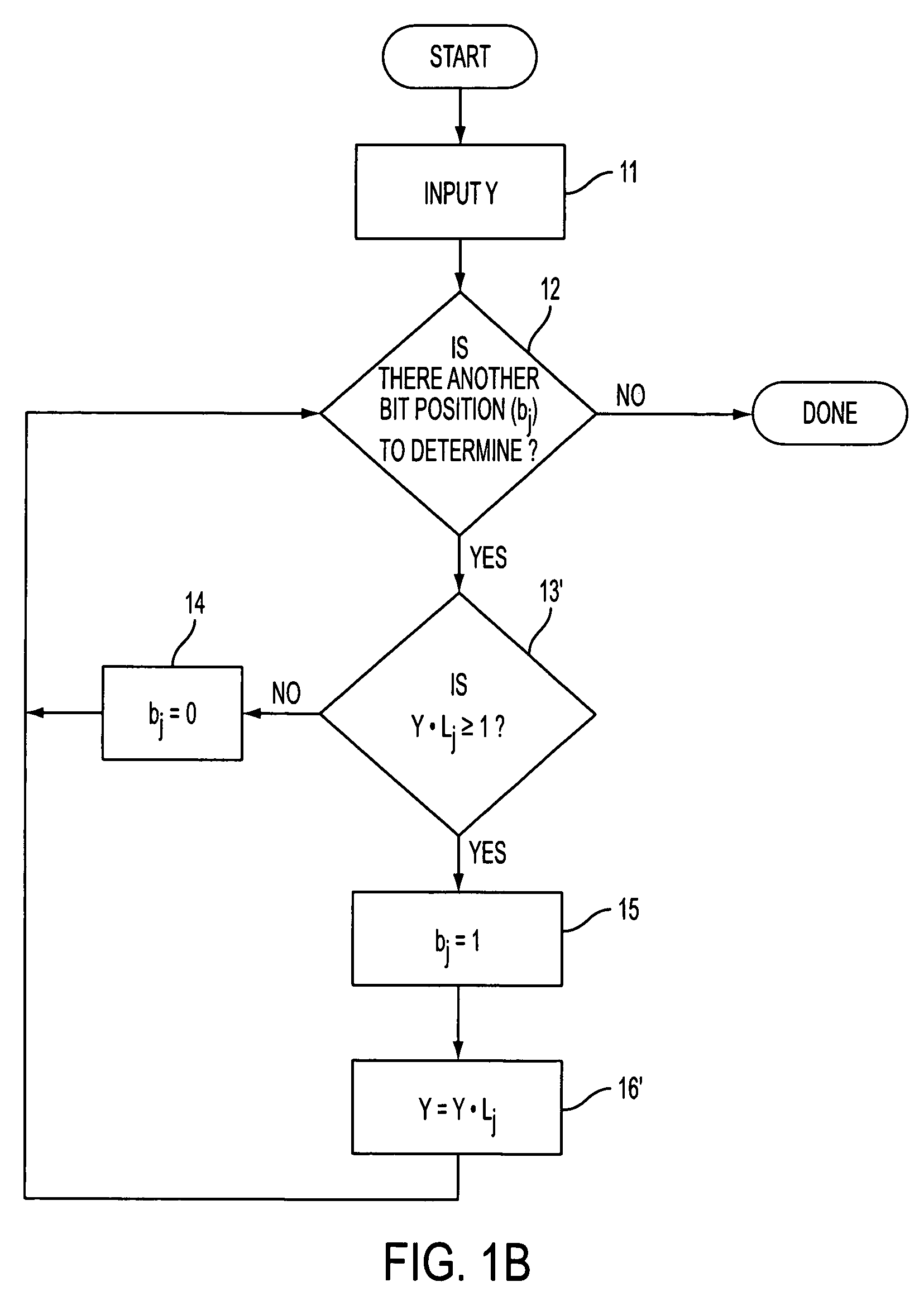

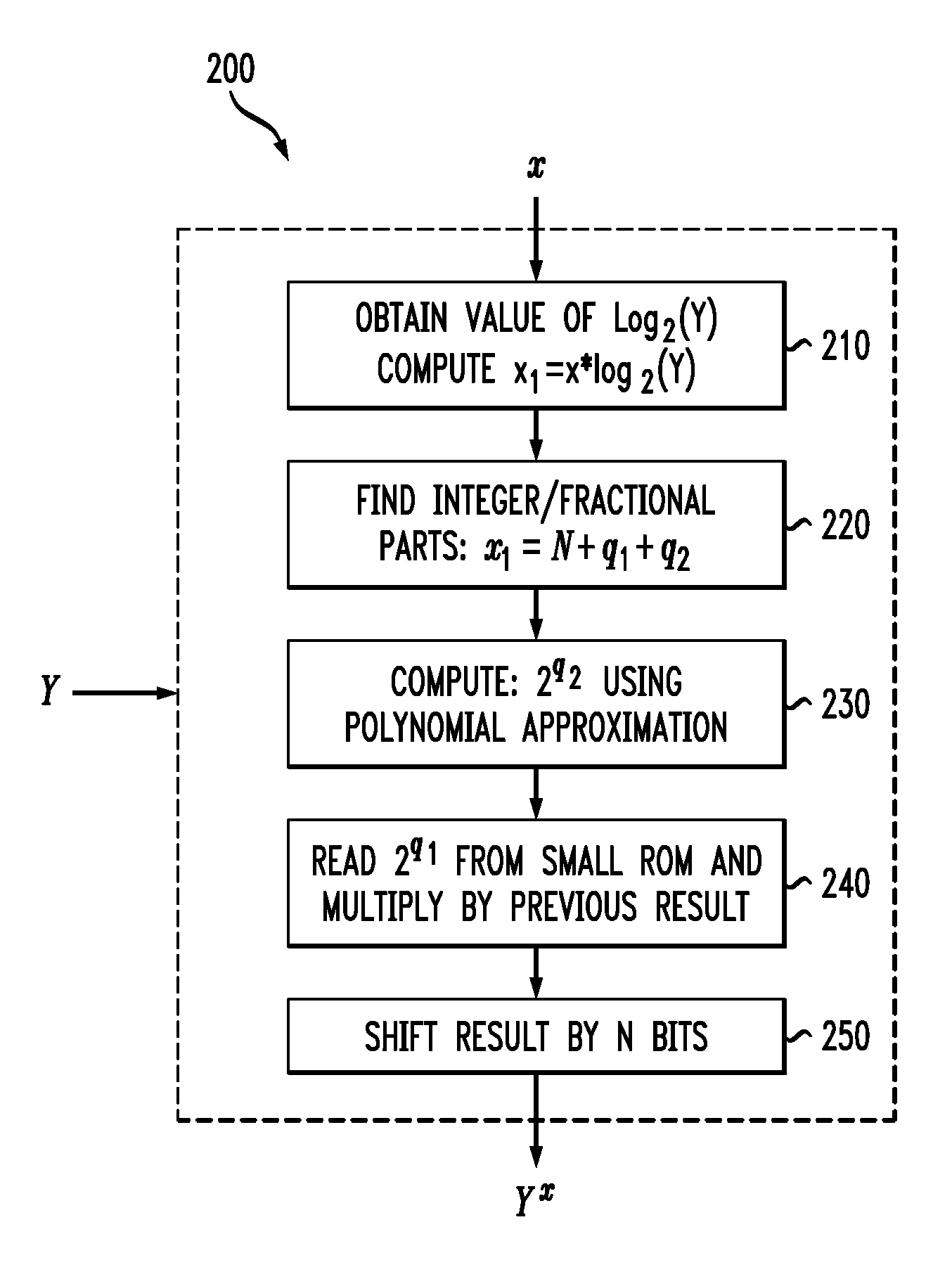

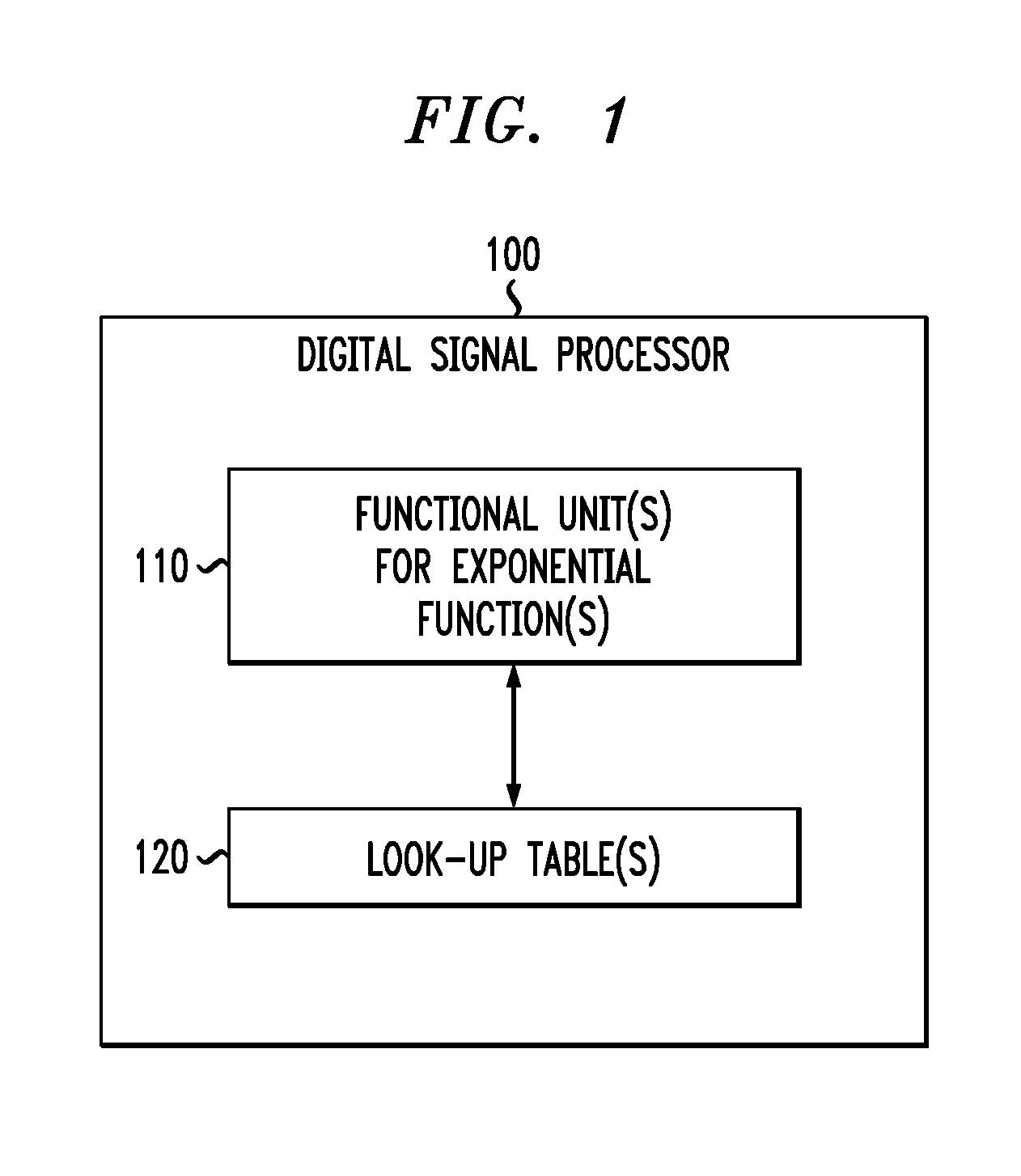

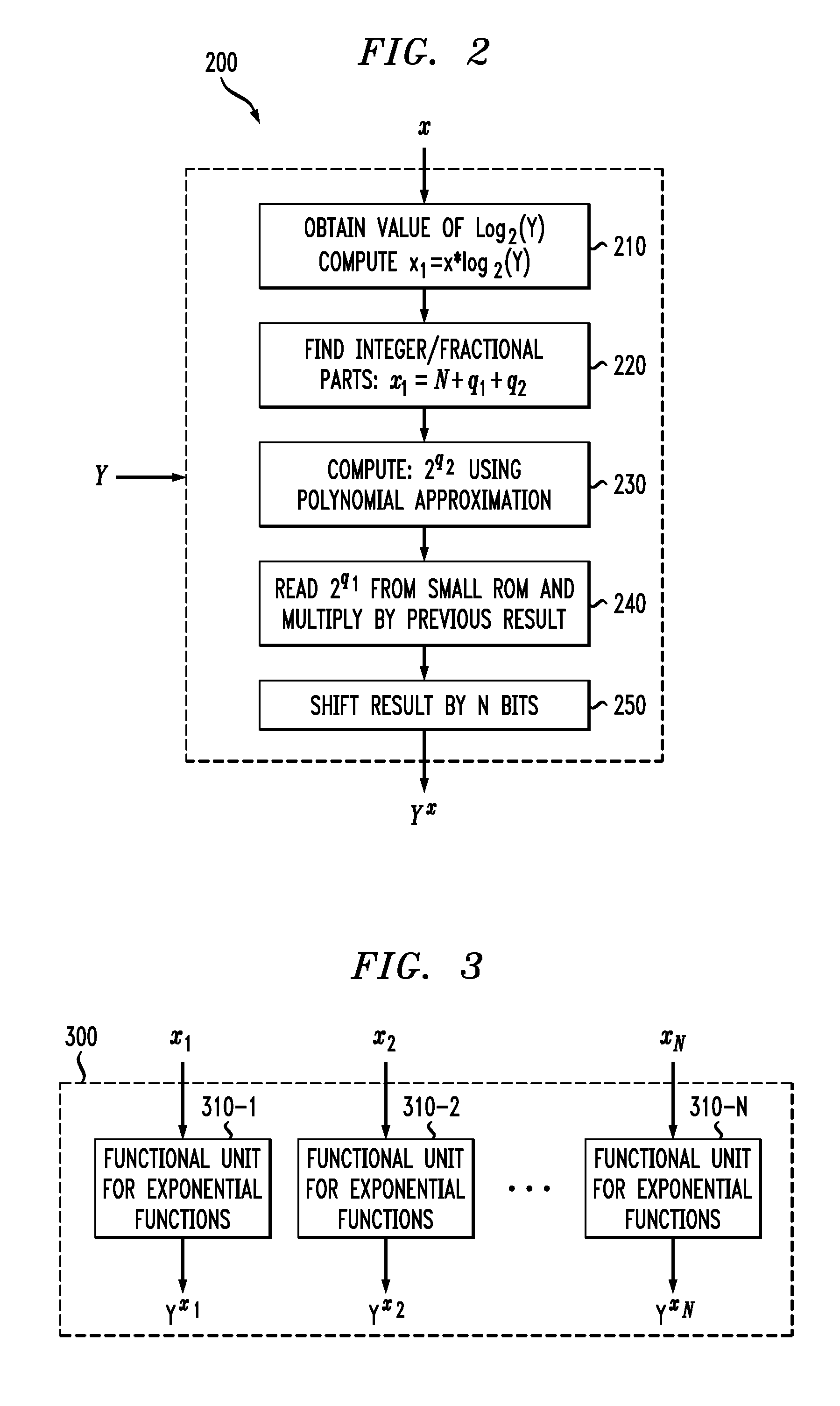

A digital signal processor is provided having an instruction set with an exponential function that uses a reduced look-up table. The disclosed digital signal processor evaluates an exponential function for an input value, x, by decomposing the input value, x, to an integer part, N, a first fractional part, q1, larger than a specified value, x0, and a second fractional part, q2, smaller than the specified value, x0; computing 2q<sub2>2 < / sub2>using a polynomial approximation, such as a cubic approximation; obtaining 2q<sub2>1 < / sub2>from a look-up table; and evaluating the exponential function for the input value, x, by multiplying 2q<sub2>2< / sub2>, 2q<sub2>1 < / sub2>and 2N together. Look-up table entries have a fewer number of bits than a number of bits in the input value, x.

Owner:INTEL CORP

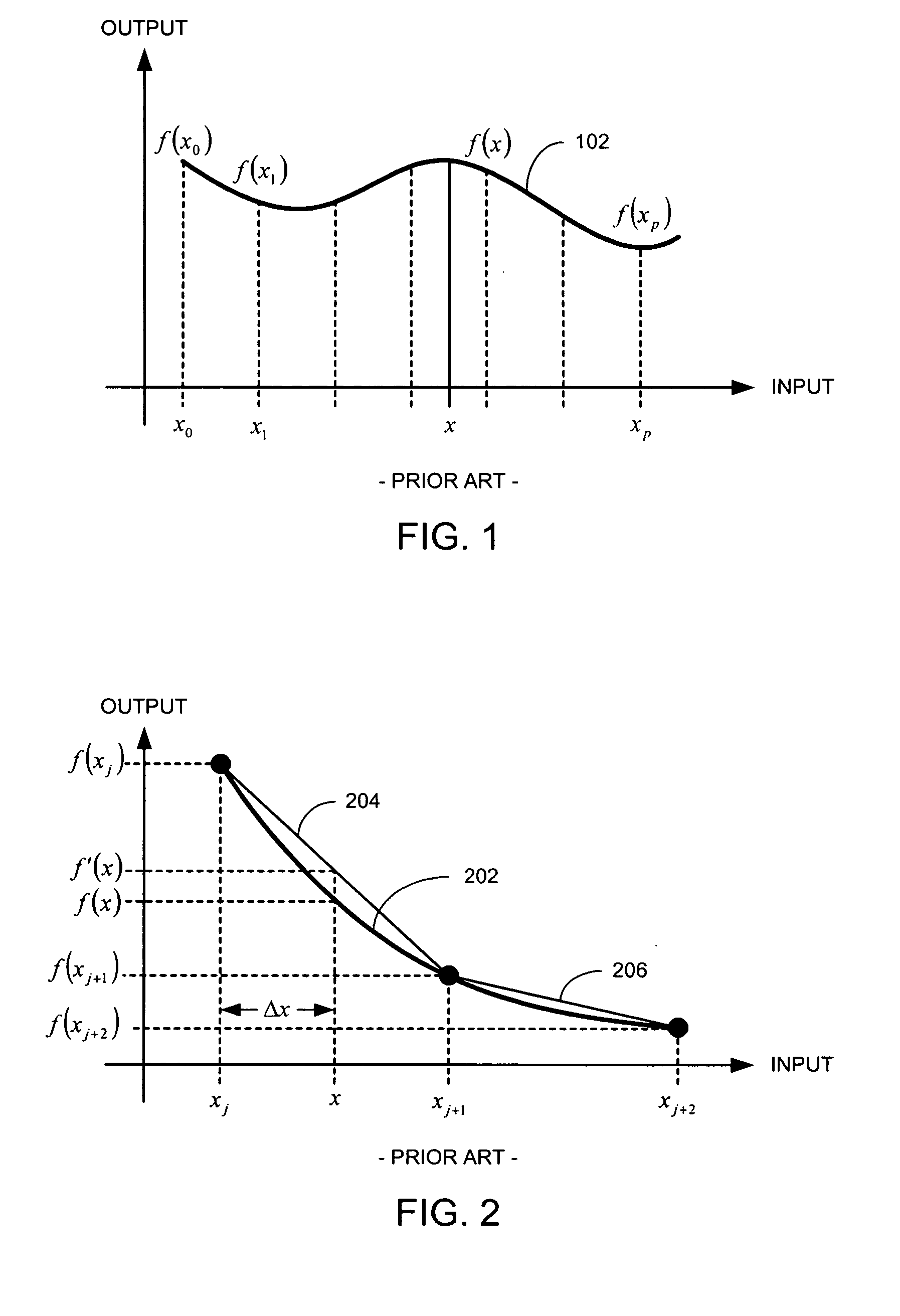

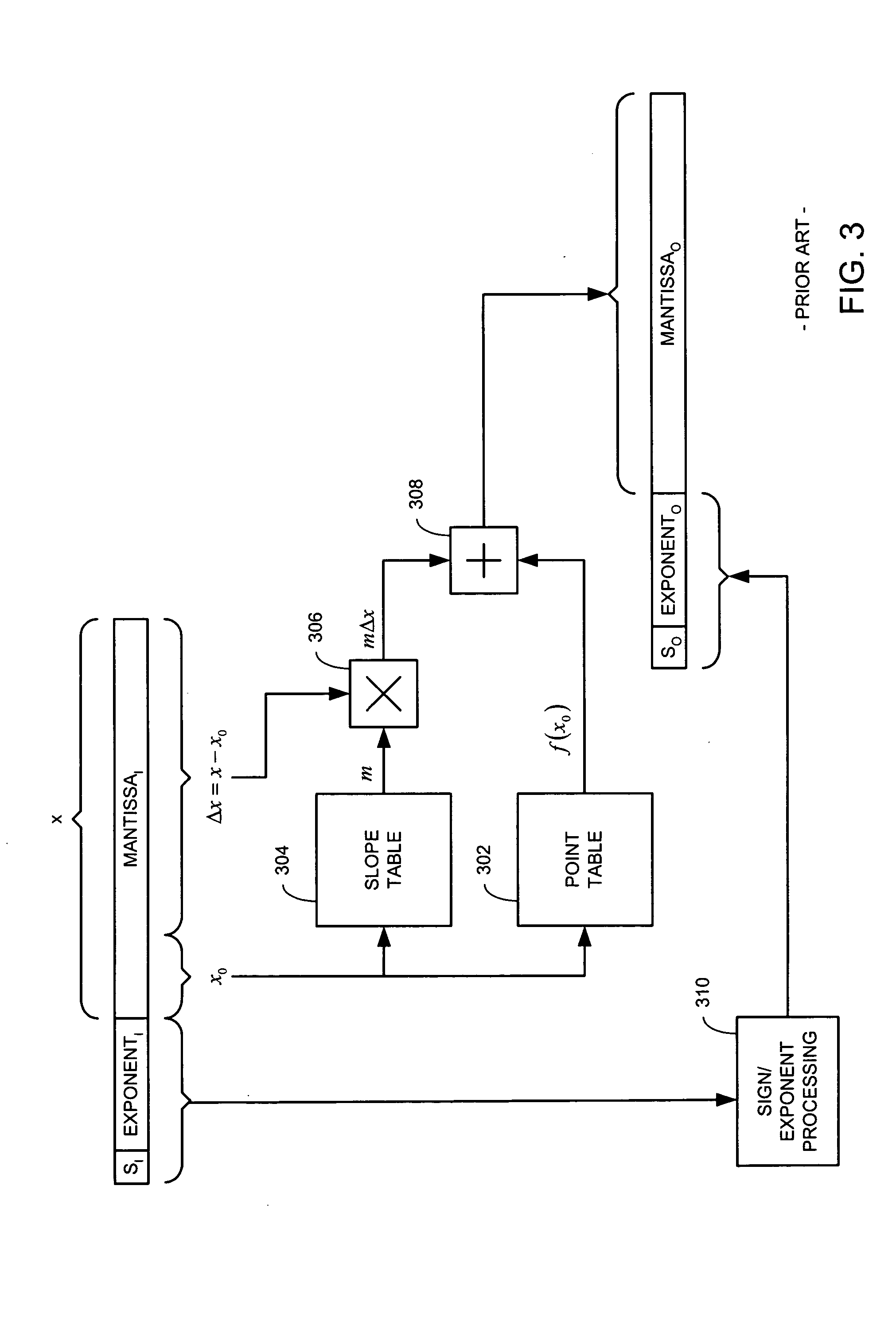

Technique for approximating functions based on lagrange polynomials

InactiveUS6976043B2Logarithmic/exponential functionsReciprocal functionsComputer scienceFunction approximation

Owner:ATI TECH INC

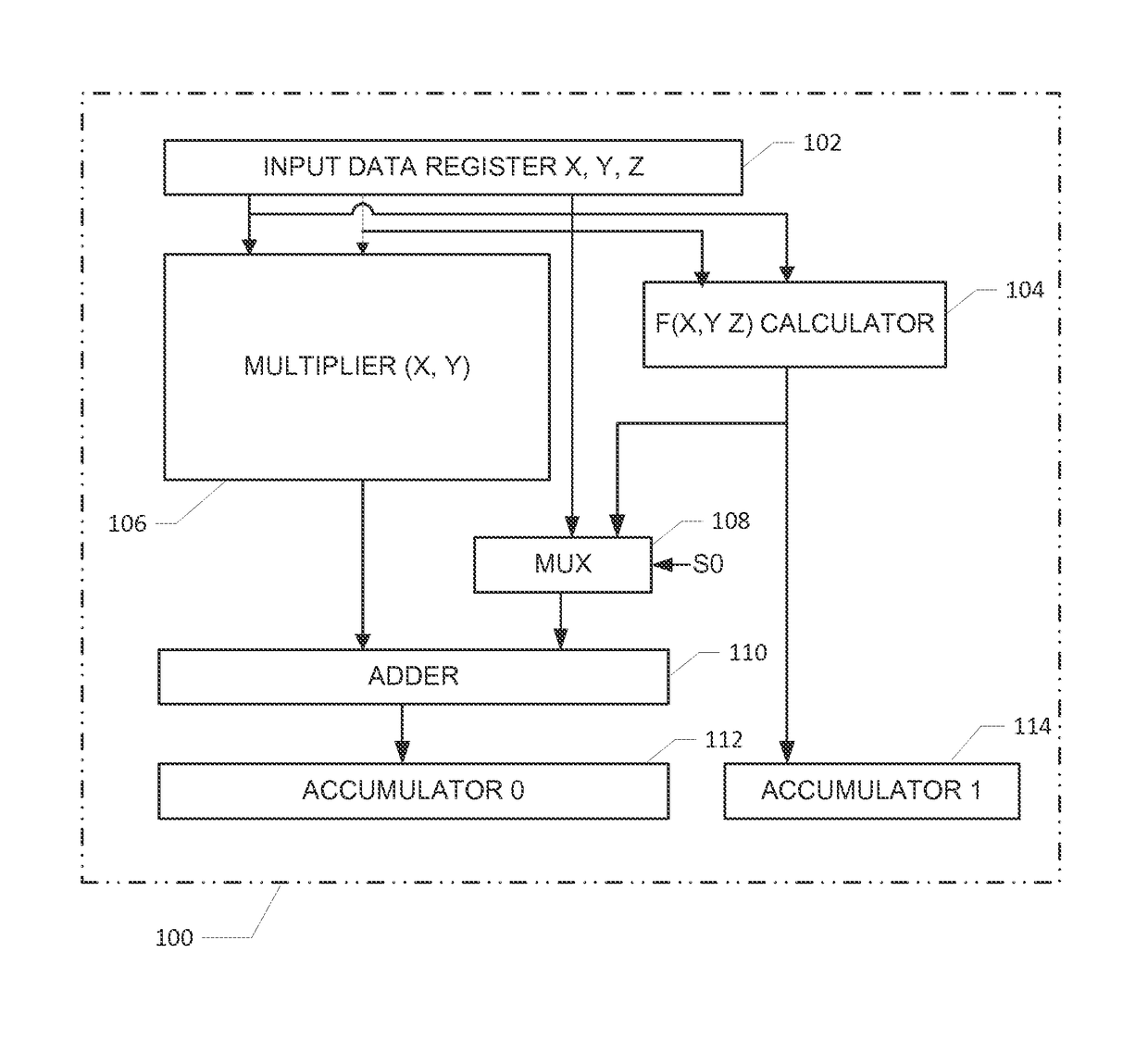

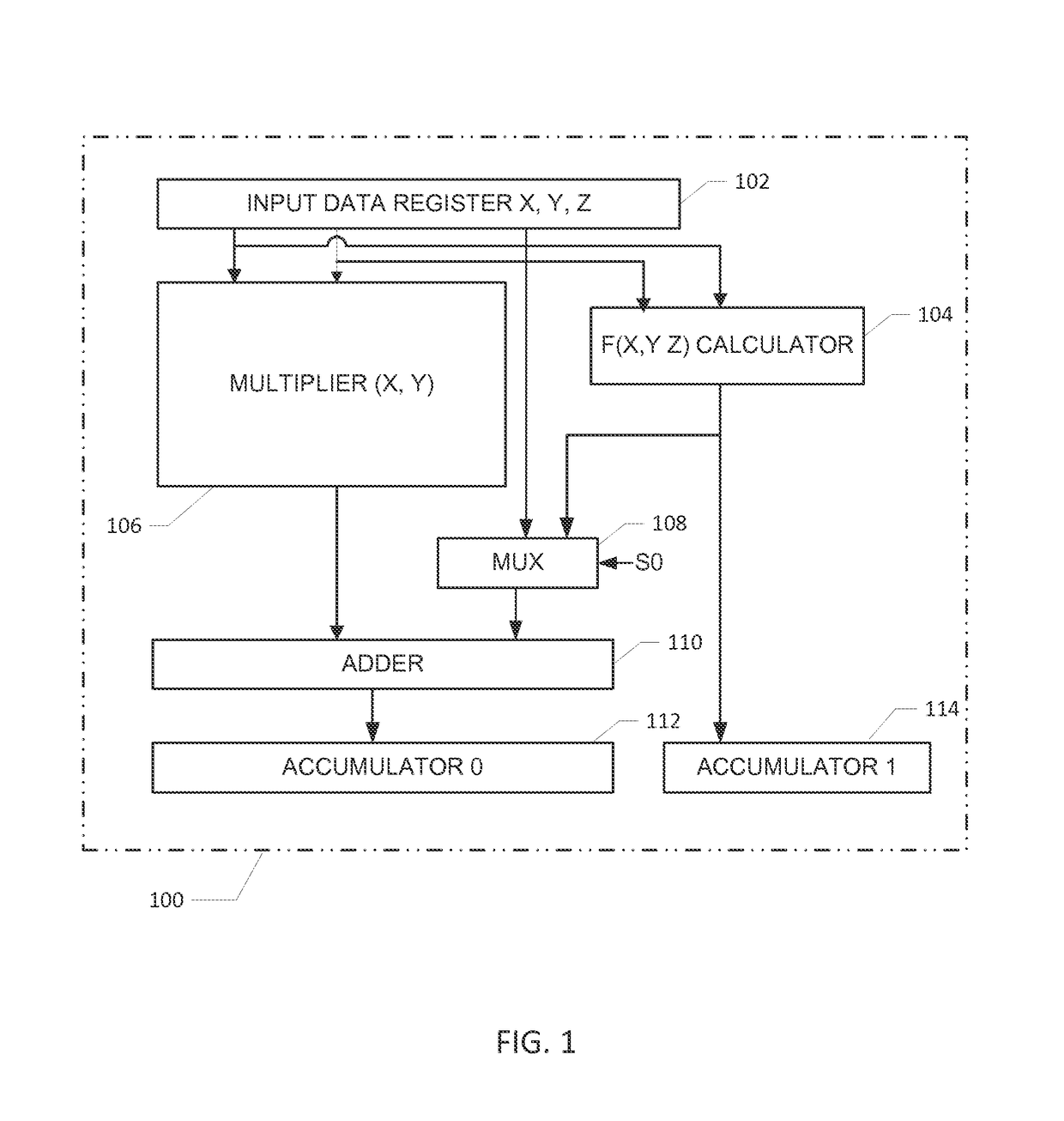

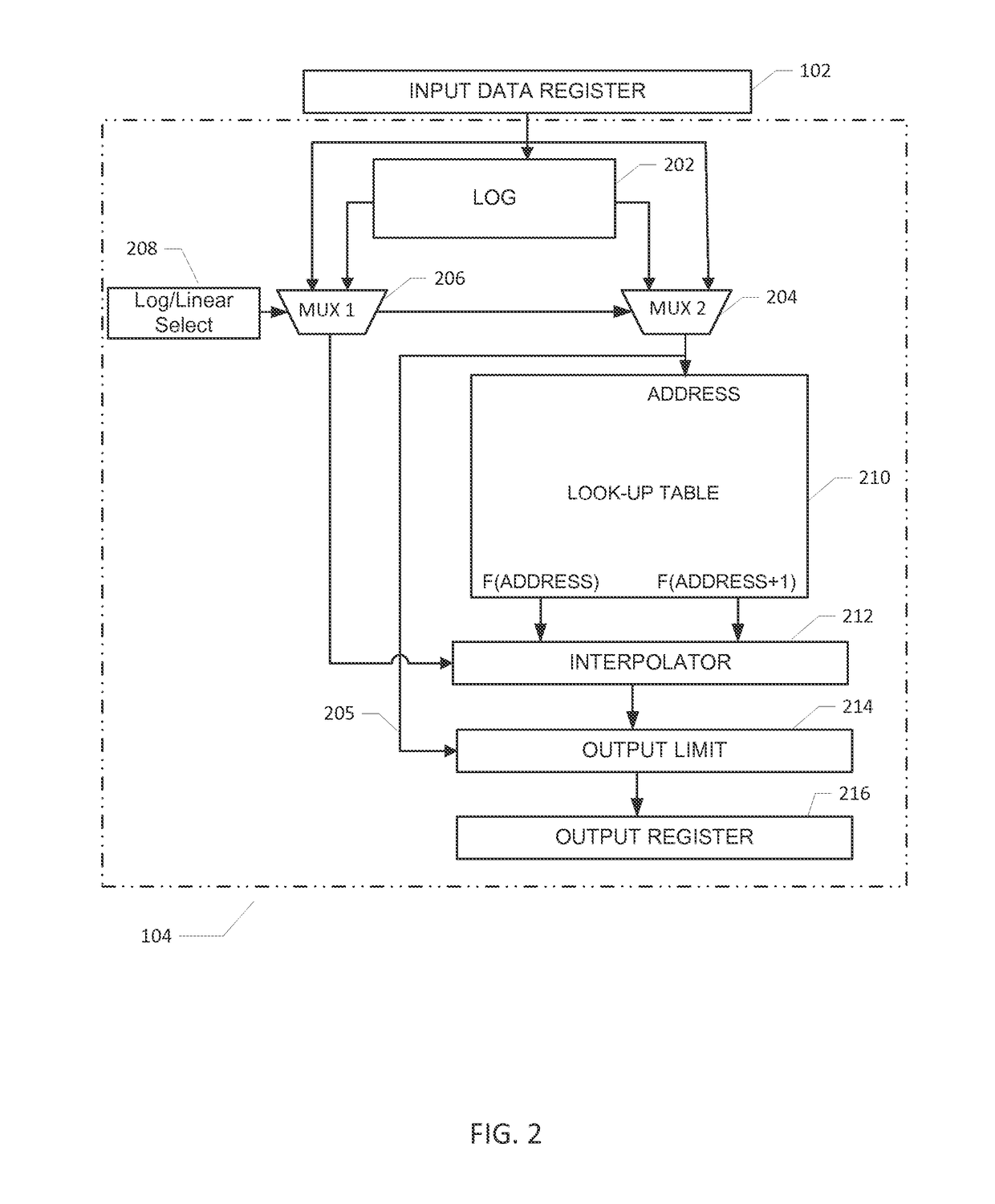

Datapath circuit for digital signal processors

ActiveUS20140067889A1Easy accessFast executionLogarithmic/exponential functionsDigital computer detailsDatapath circuitsComputer architecture

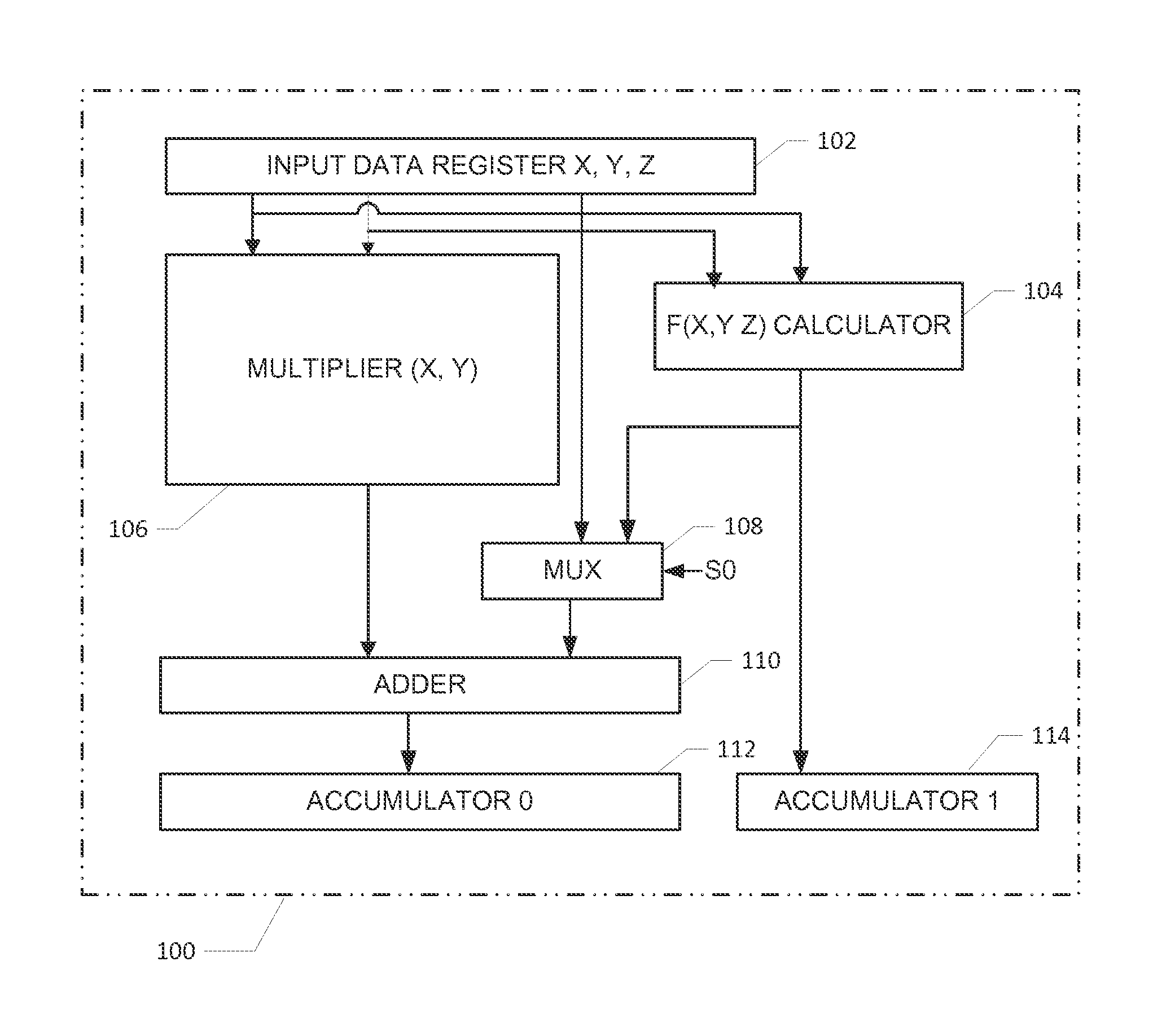

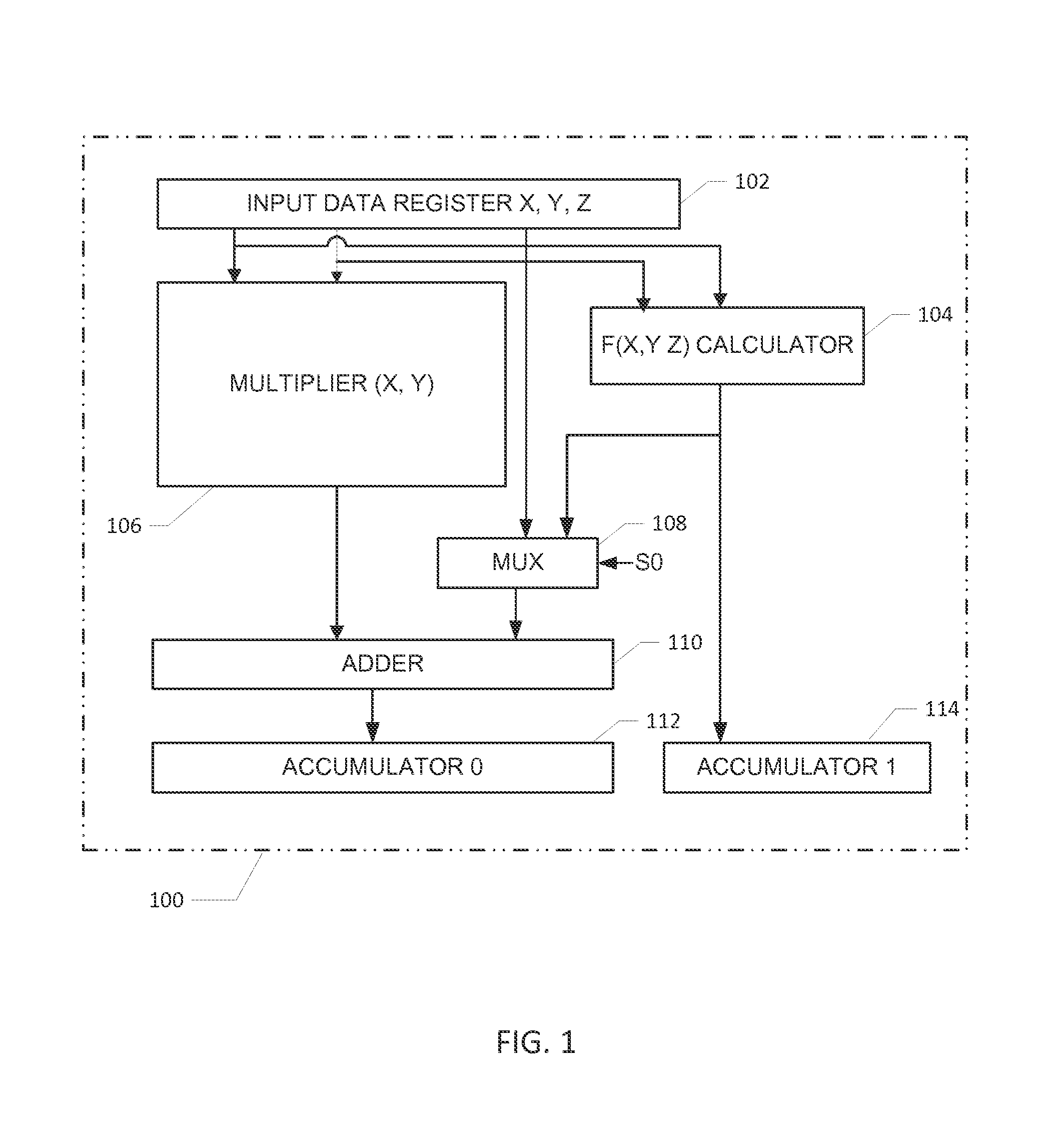

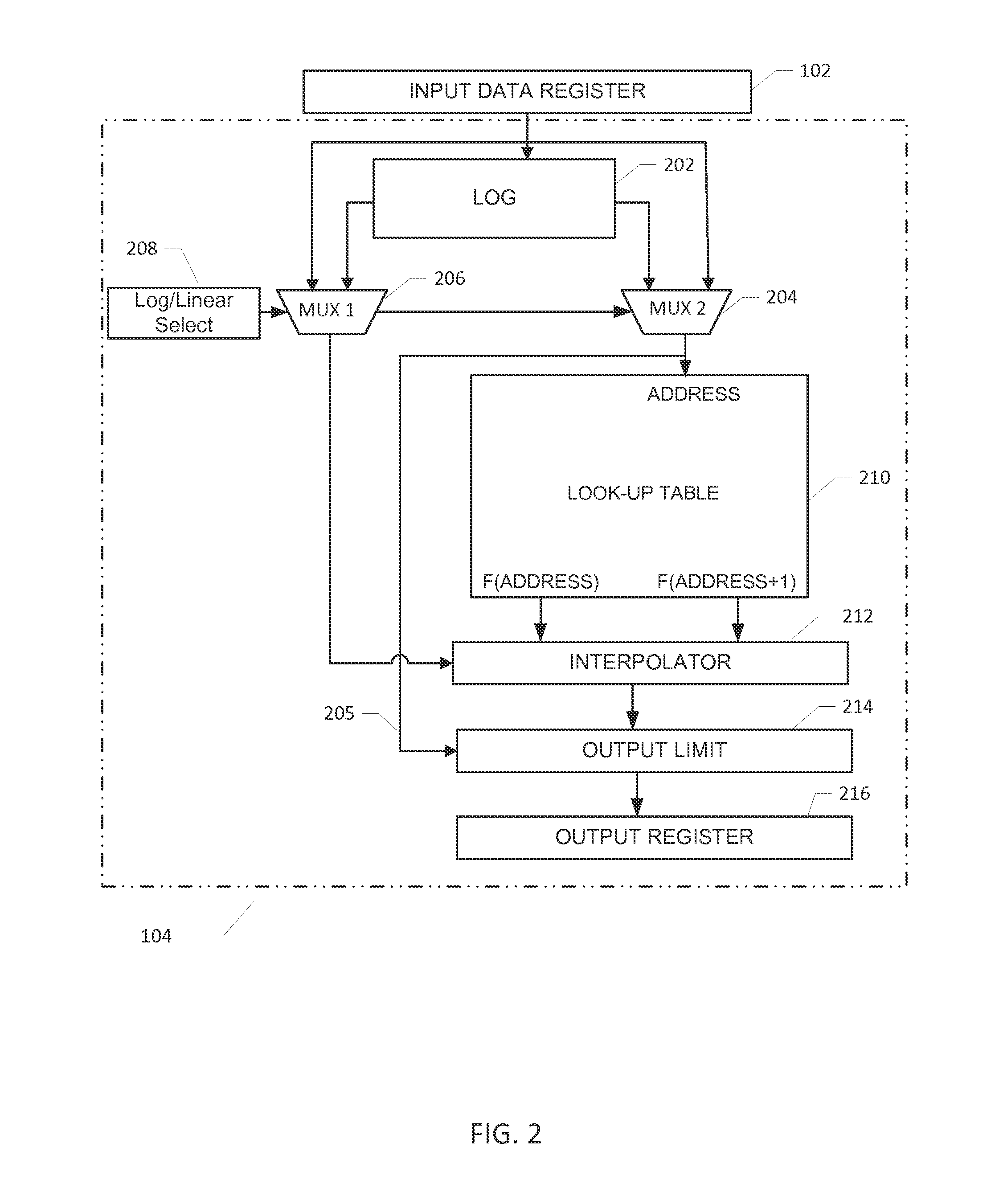

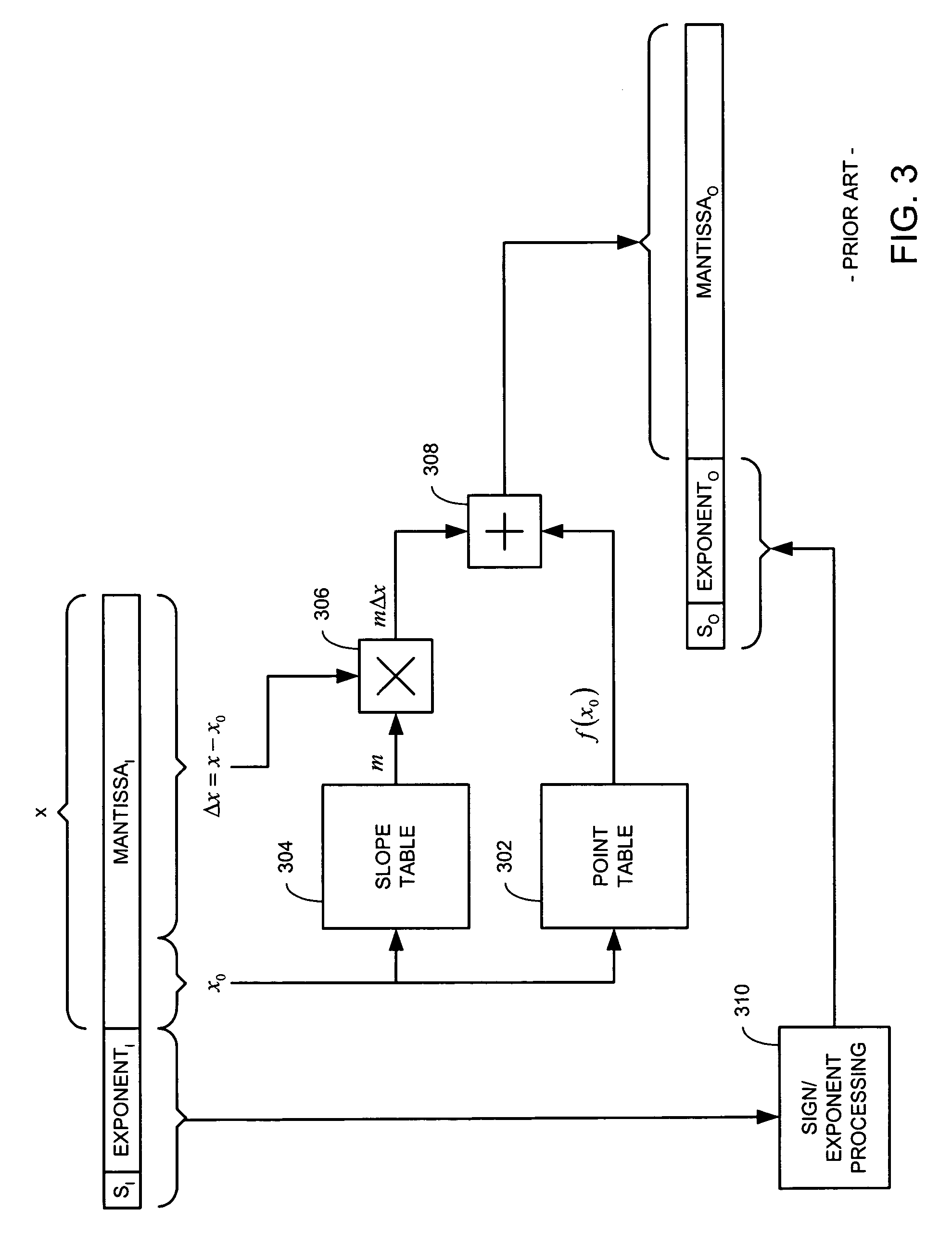

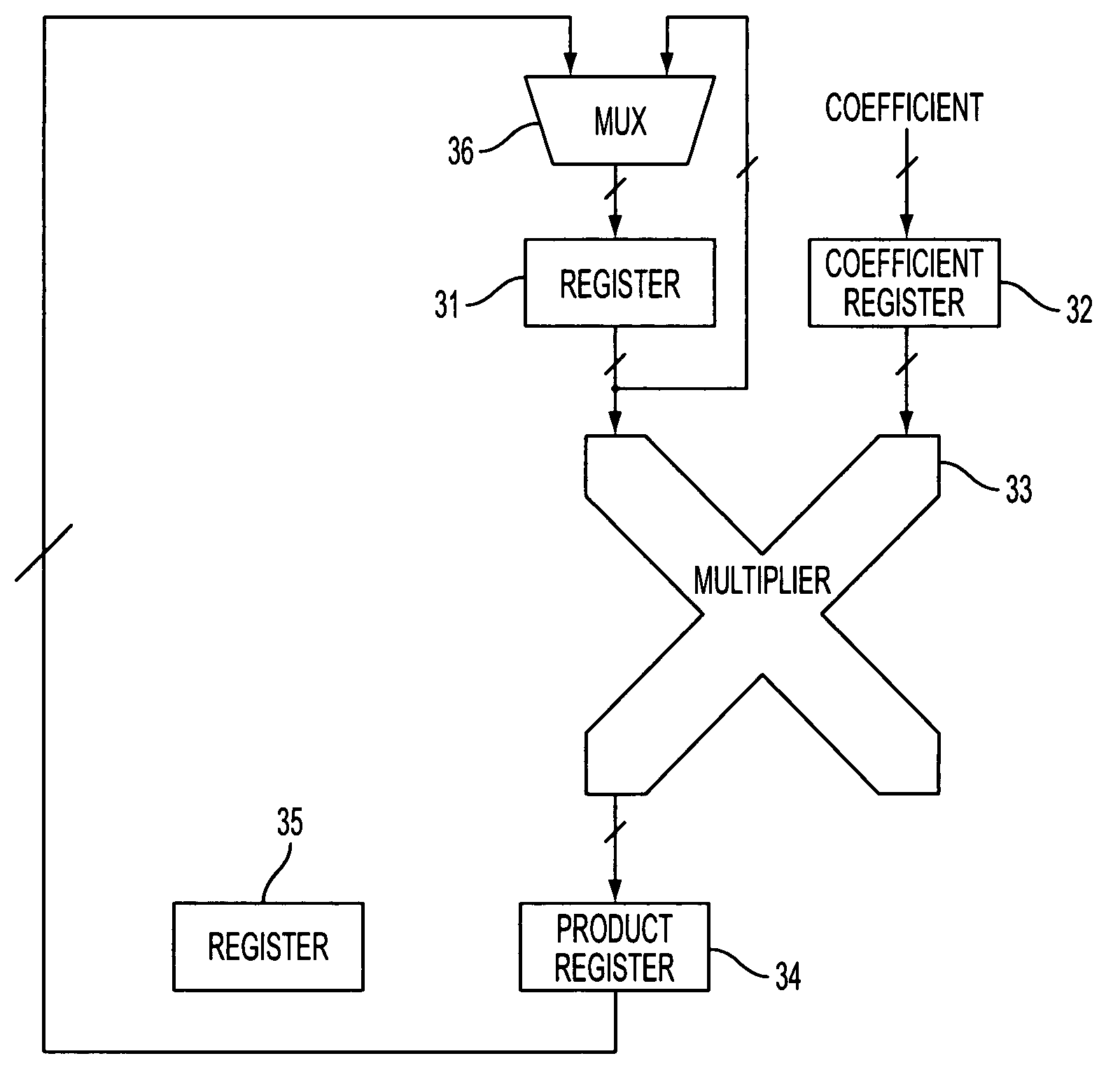

A datapath circuit may include a digital multiply and accumulate circuit (MAC) and a digital hardware calculator for parallel computation. The digital hardware calculator and the MAC may be coupled to an input memory element for receipt of input operands. The MAC may include a digital multiplier structure with partial product generators coupled to an adder to multiply a first and second input operands and generate a multiplication result. The digital hardware calculator may include a first look-up table coupled between a calculator input and a calculator output register. The first look-up table may include table entry values mapped to corresponding math function results in accordance with a first predetermined mathematical function. The digital hardware calculator may be configured to calculate, based on the first look-up table, a computationally hard mathematical function such as a logarithm function, an exponential function, a division function and a square root function.

Owner:ANALOG DEVICES INT UNLTD

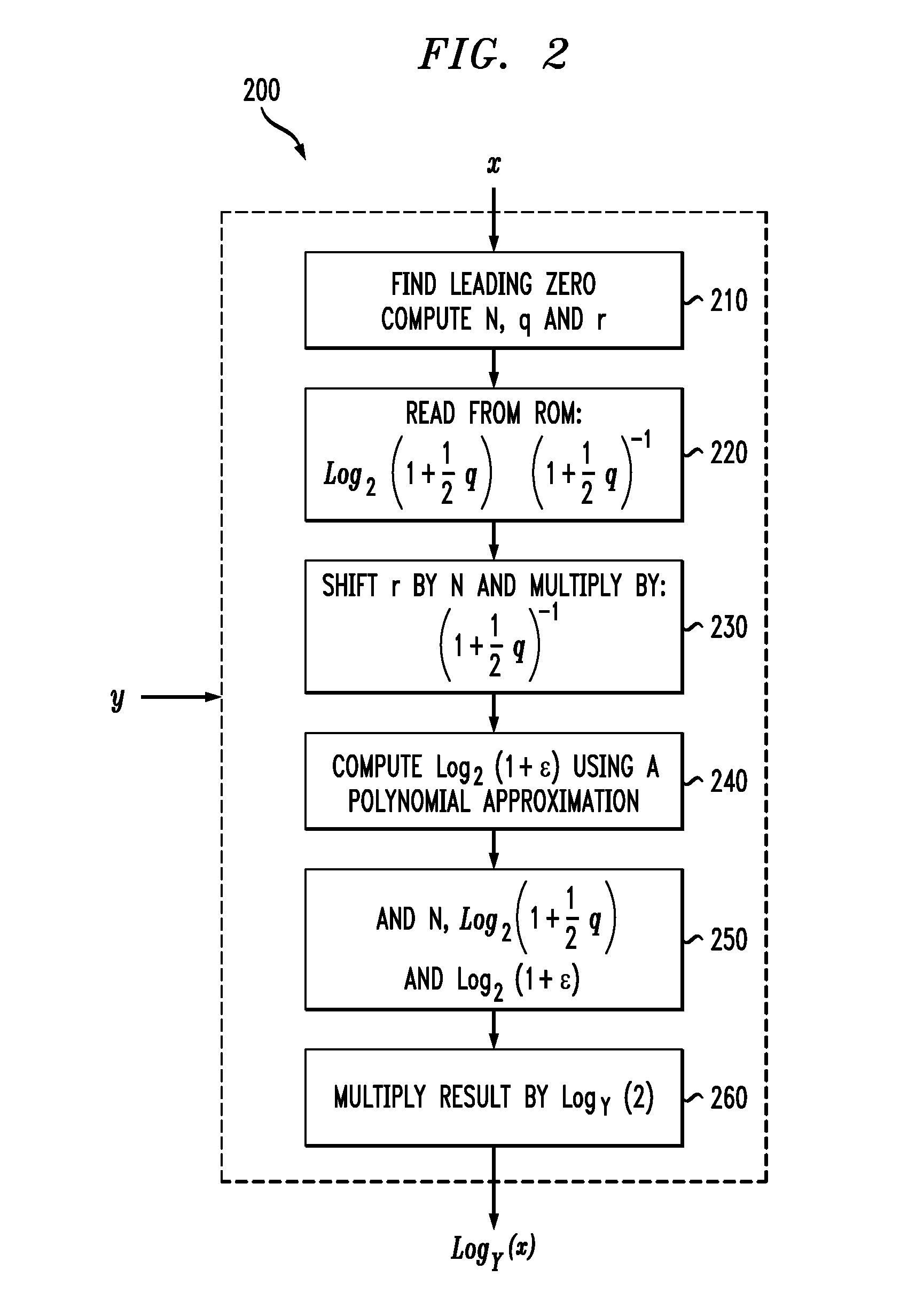

Digital Signal Processor Having Instruction Set With A Logarithm Function Using Reduced Look-Up Table

ActiveUS20100198895A1Reduced look-up tableLogarithmic/exponential functionsComputation using non-contact making devicesComputer scienceInstruction set

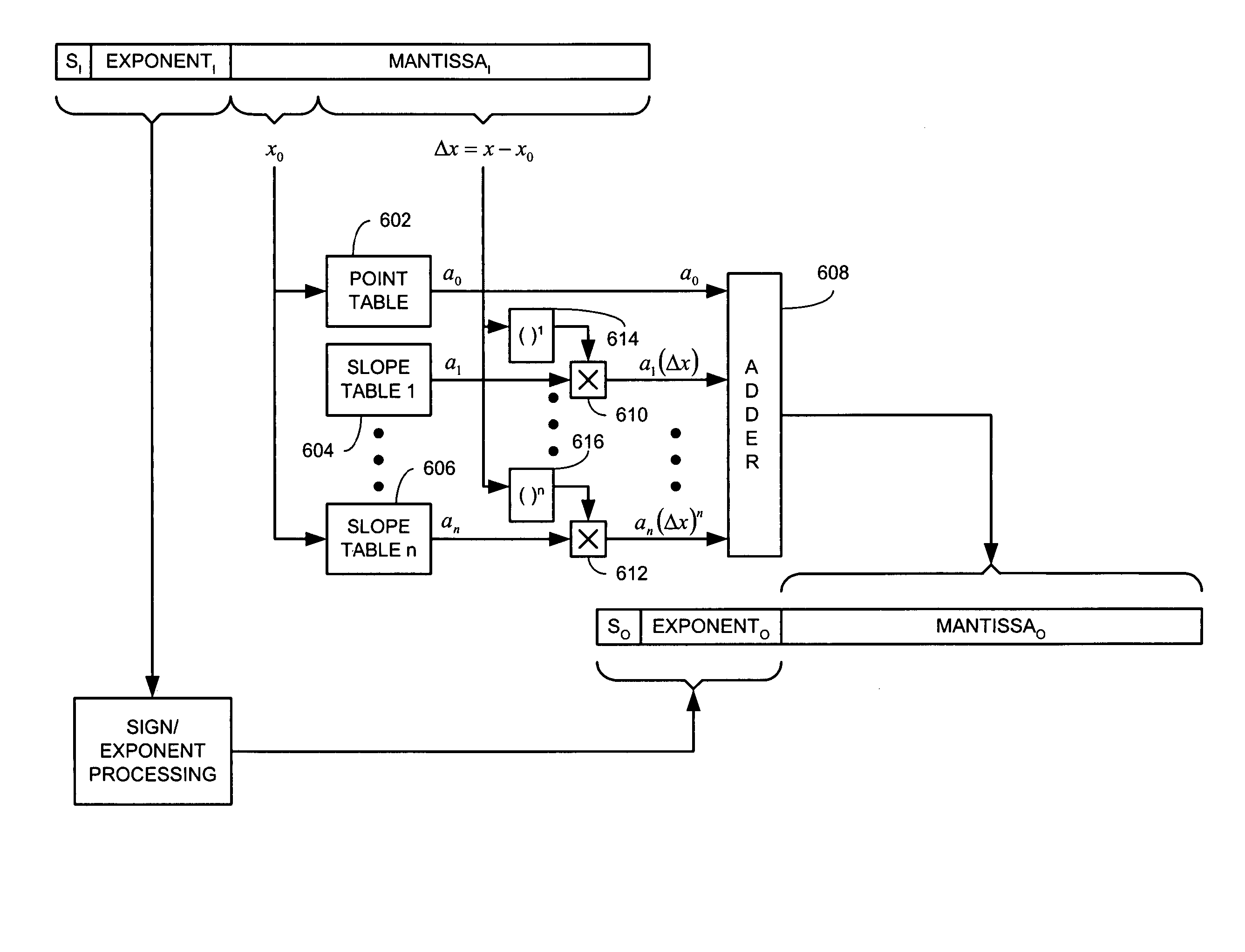

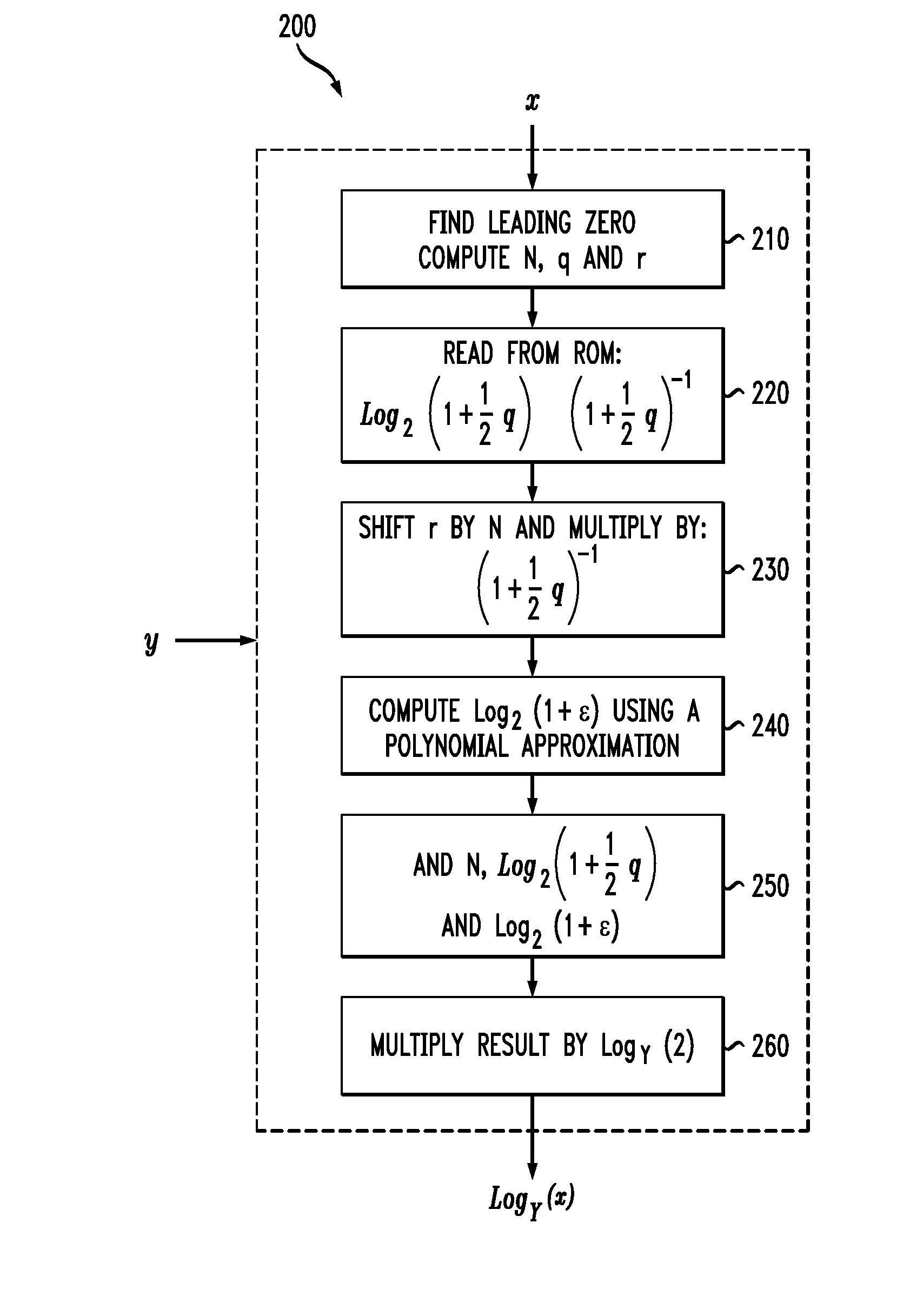

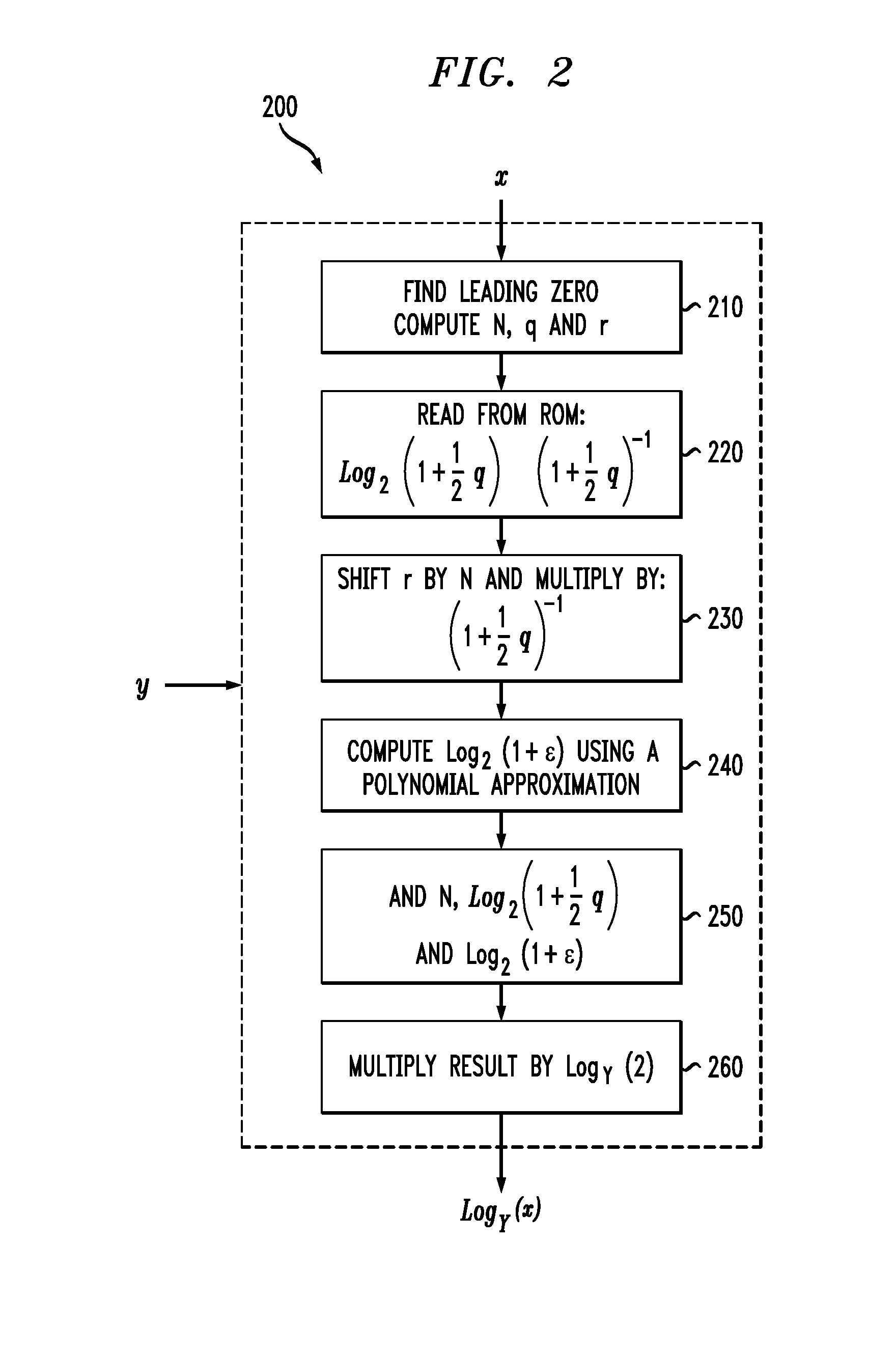

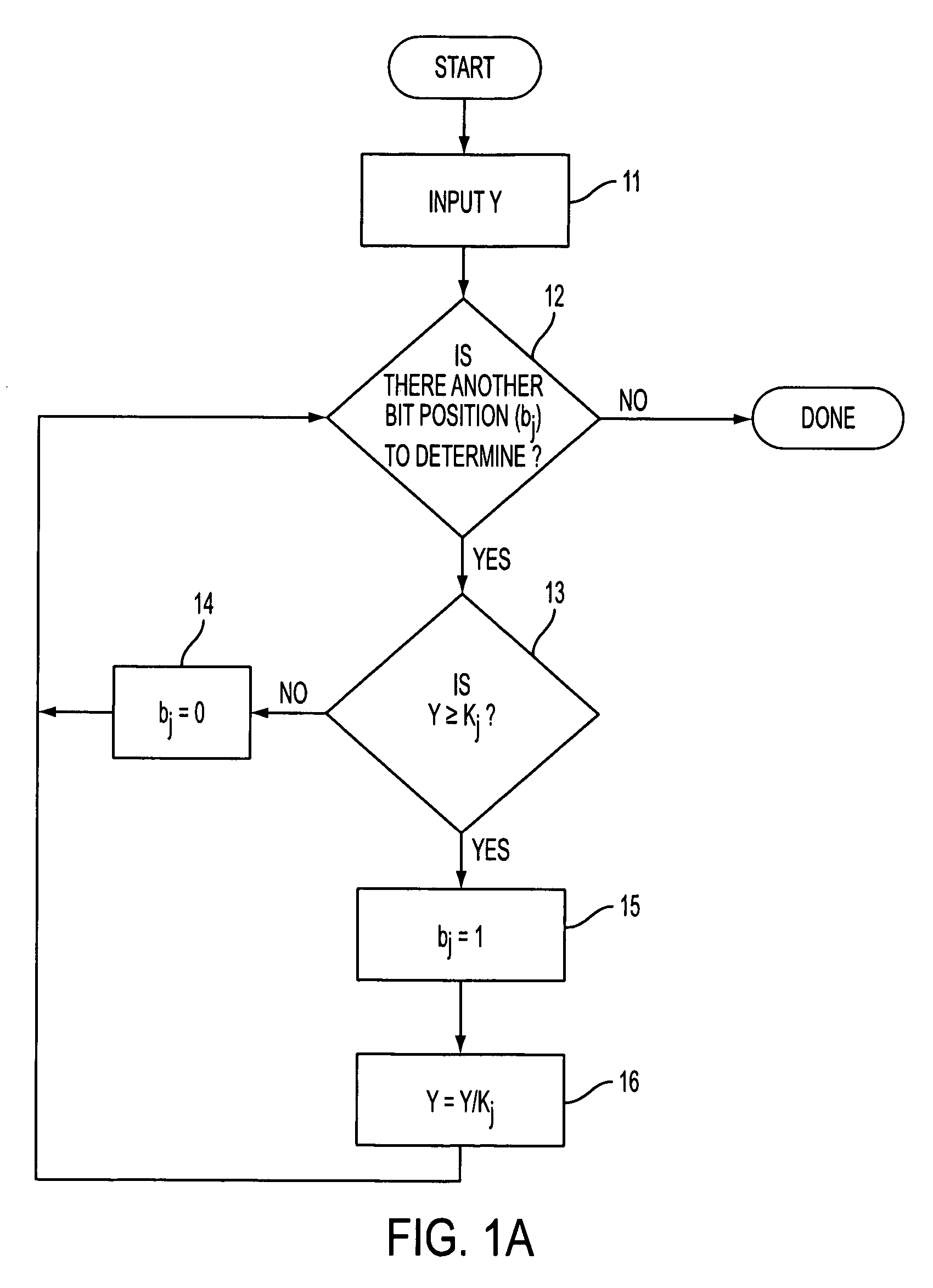

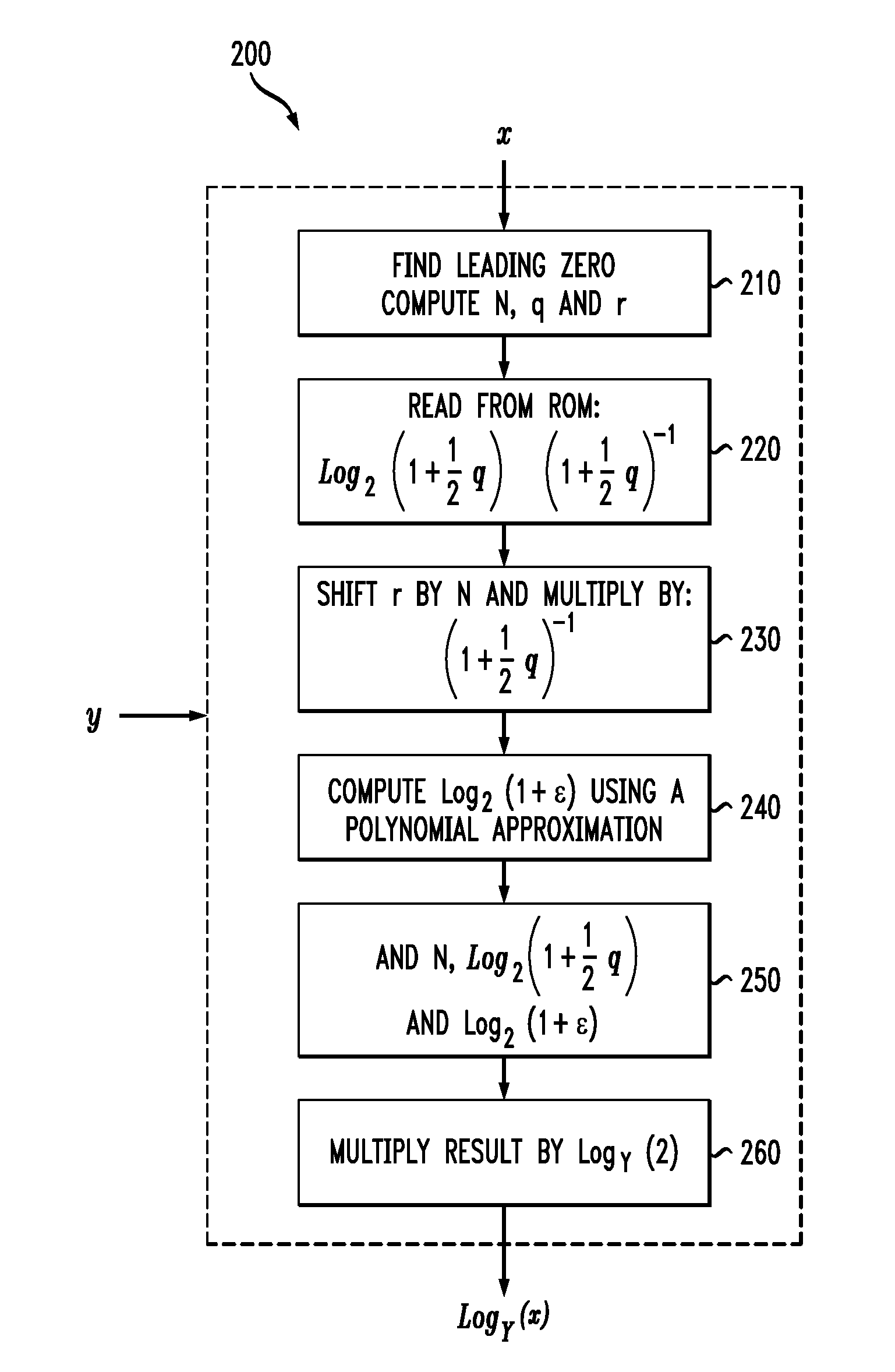

A digital signal processor is provided having an instruction set with a logarithm function that uses a reduced look-up table. The disclosed digital signal processor evaluates a logarithm function for an input value, x, by decomposing the input value, x, to a first part, N, a second part, q, and a remaining part, r, wherein the first part, N, is identified by a position of a most significant bit of the input value, x, and the second part, q, is comprised of a number of bits following the most significant bit, wherein the number is small relative to a number of bits in the input value, x; obtaining a valueLog2(1+12q)from a first look-up table based on the second part, q; computing an epsilon term, ε, using the expression2-N1+12qr;evaluating an expression Log2 ( 1+ε) using a polynomial approximation, such as a cubic approximation; and determining the logarithm function for the input value, x, by summing the values of N,LogZ(1+12q)and Log2(1+ε).

Owner:INTEL CORP

Method and system for approximating sine and cosine functions

Owner:ATI TECH INC

Multipurpose arithmetic functional unit

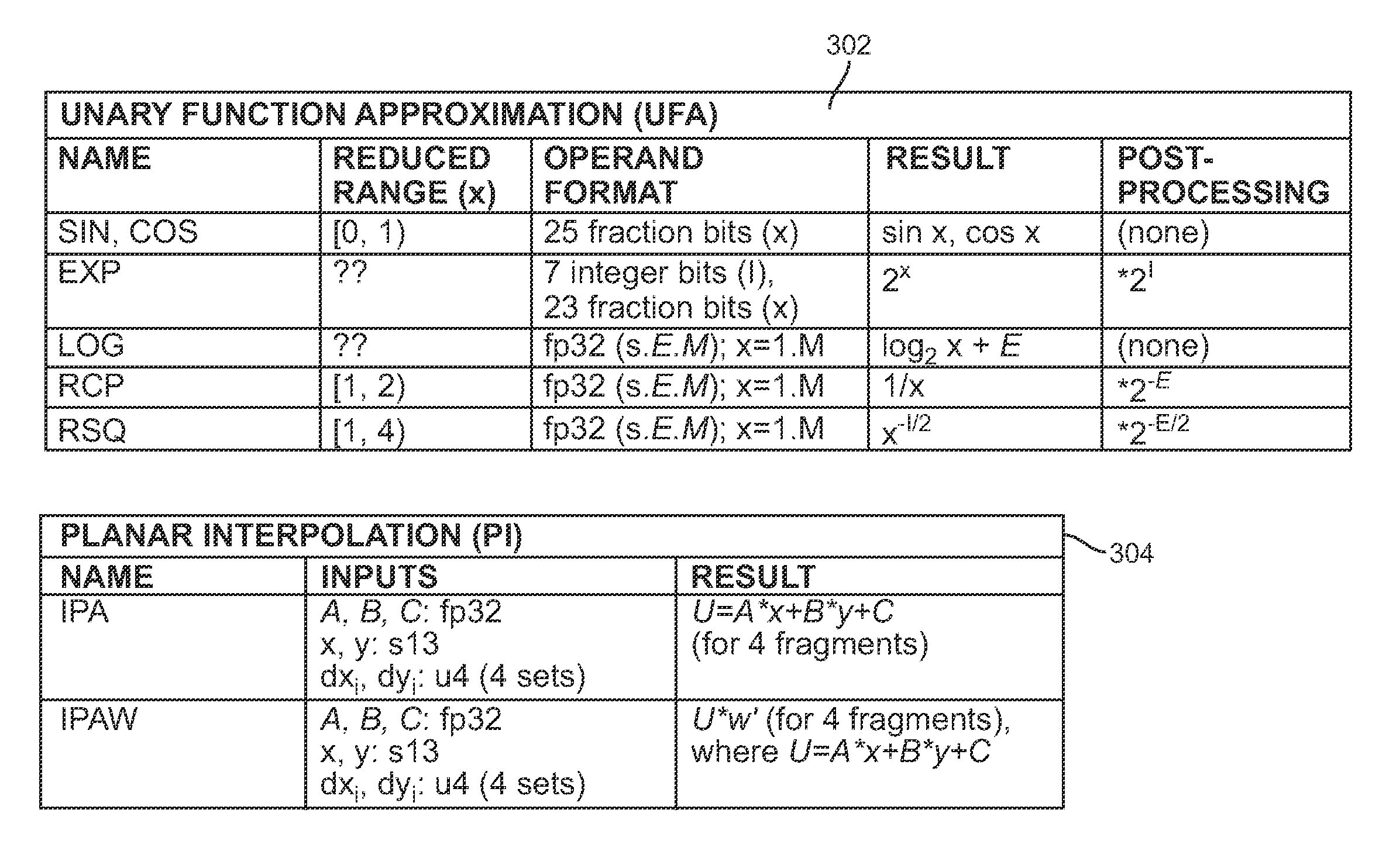

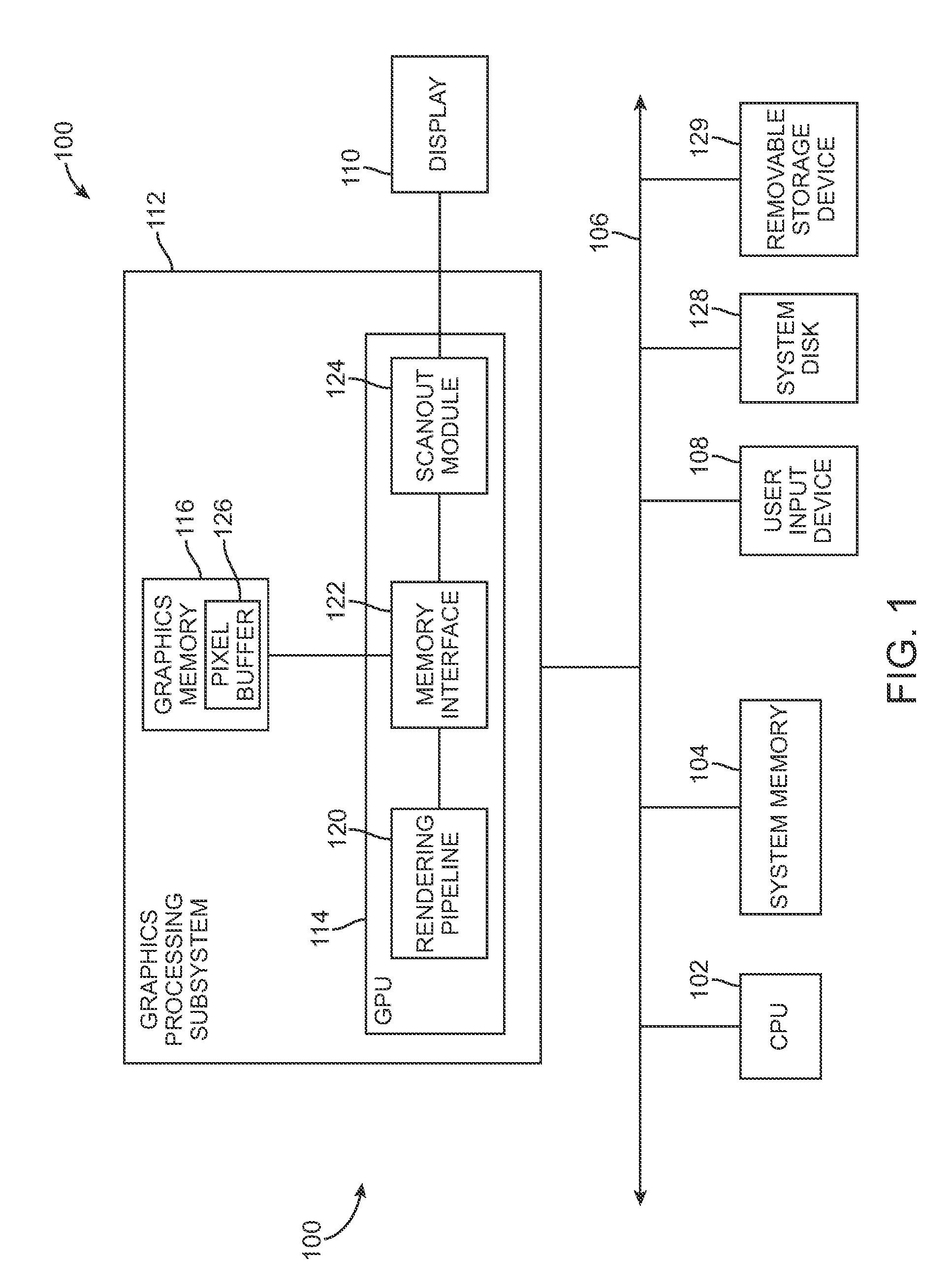

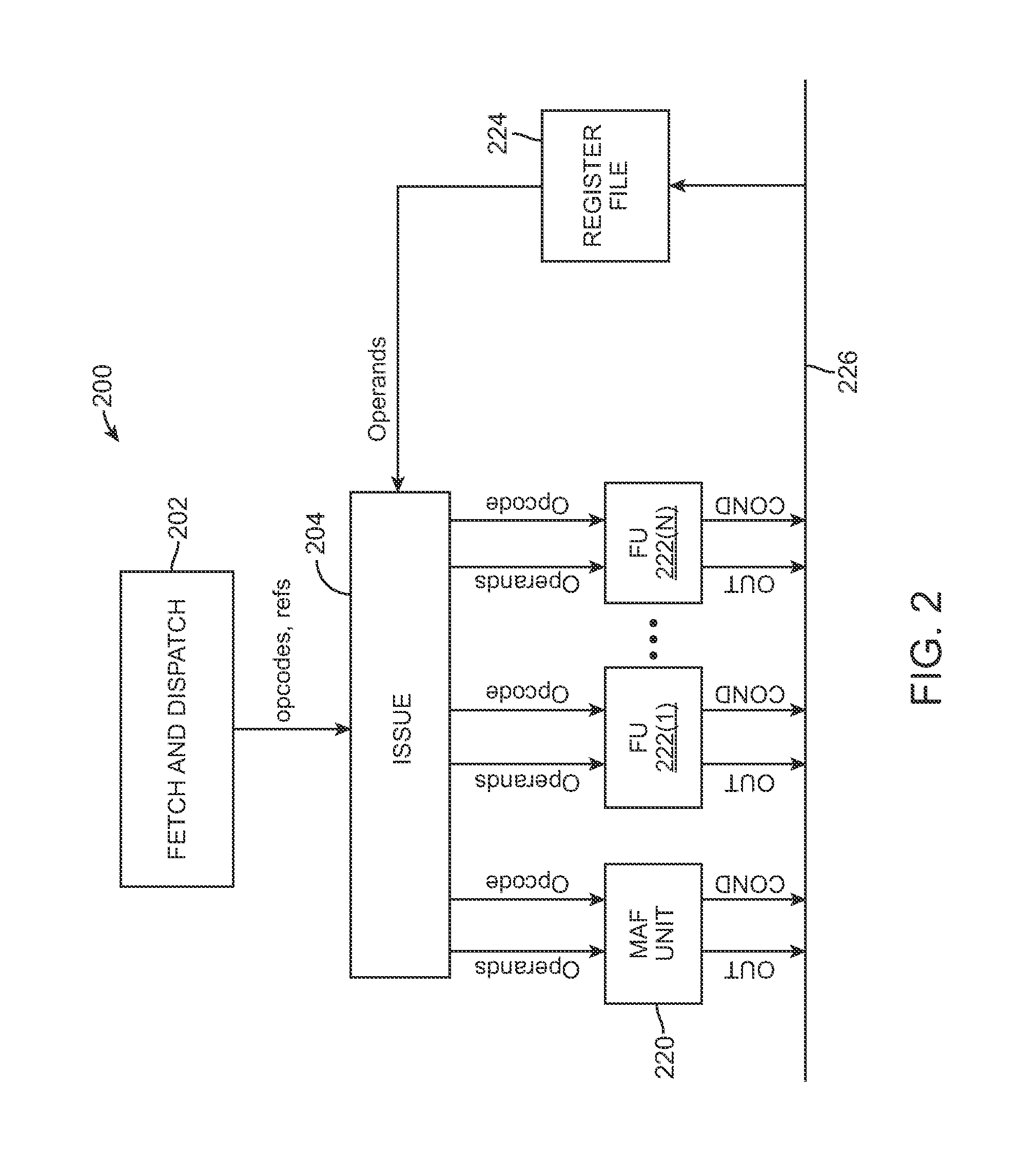

ActiveUS8190669B1Trigometric functionsComputations using contact-making devicesOperandUnary function

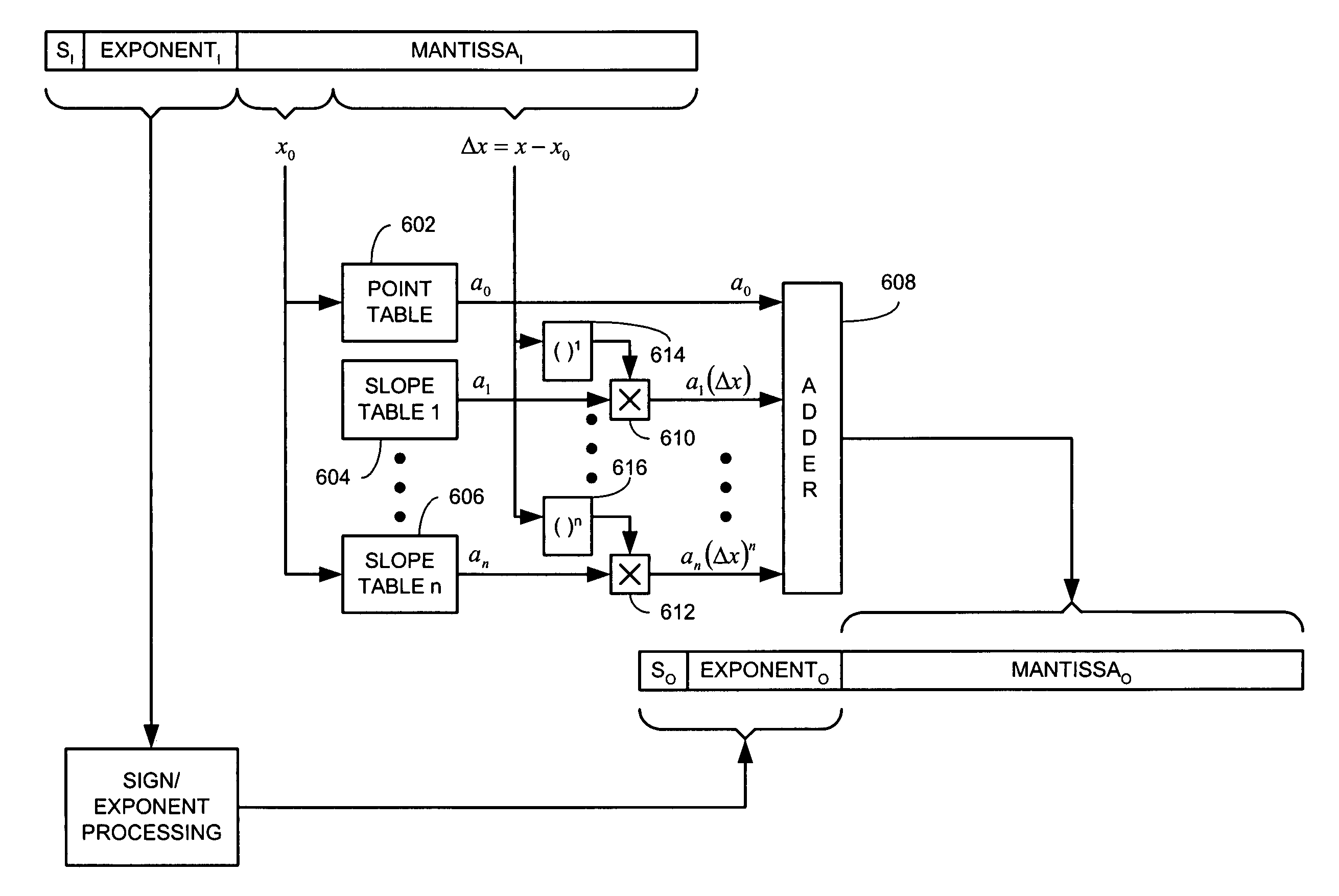

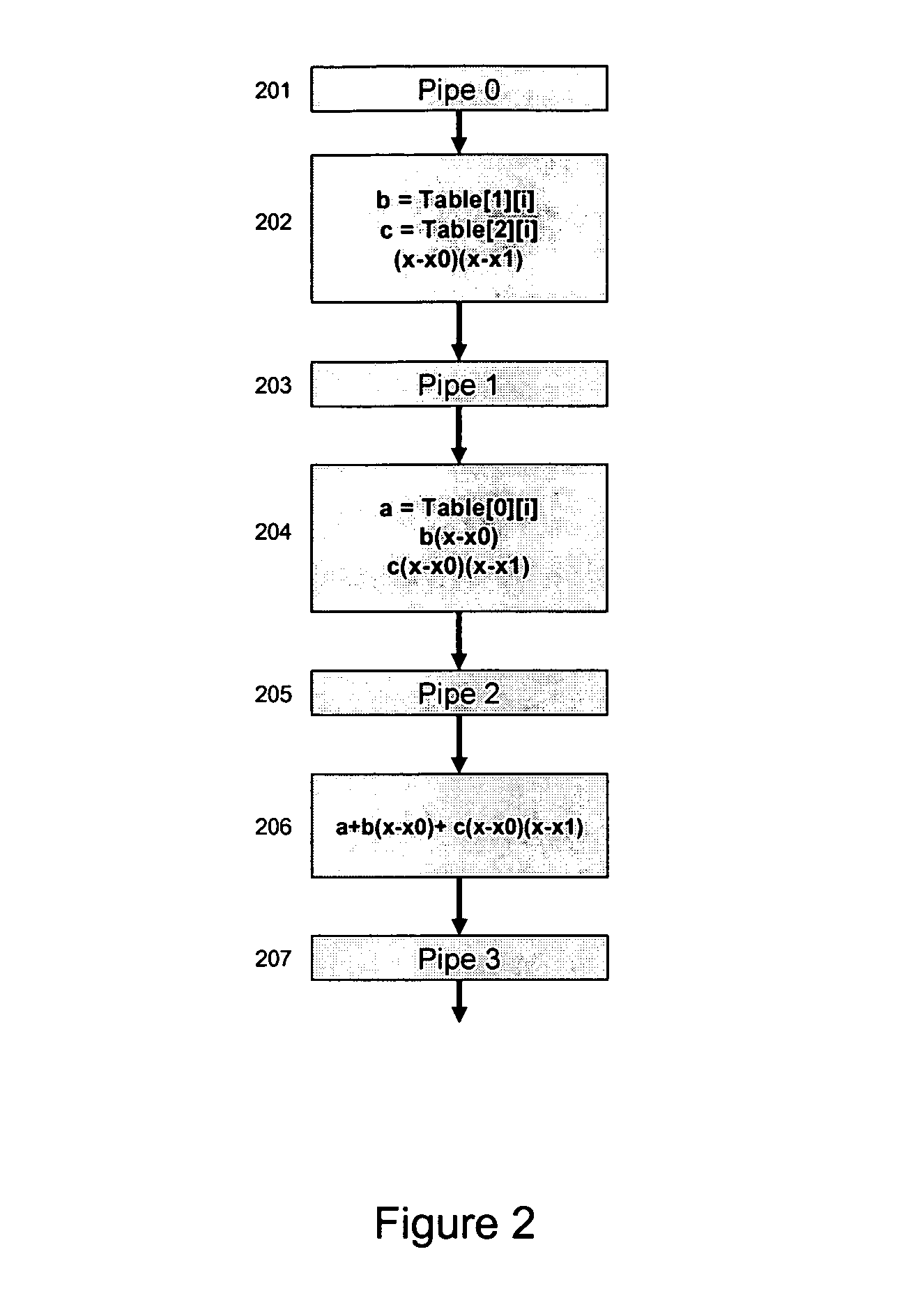

Multipurpose arithmetic functional units can perform planar attribute interpolation and unary function approximation operations. In one embodiment, planar interpolation operations for coordinates (x, y) are executed by computing A*x+B*y+C, and unary function approximation operations for operand x are executed by computing F2(xb)*xh2+F1(xb)*xh+F0(xb), where xh=x−xb. Shared multiplier and adder circuits are advantageously used to implement the product and sum operations for both classes of operations.

Owner:NVIDIA CORP

Datapath circuit for digital signal processors

ActiveUS9753695B2Fast executionLeveling precisionLogarithmic/exponential functionsComputation using non-denominational number representationDatapath circuitsDigital signal processing

Owner:ANALOG DEVICES INT UNLTD

Systems and methods for computing mathematical functions

ActiveUS20150012578A1Logarithmic/exponential functionsReciprocal functionsTheoretical computer scienceOpcode

Owner:VIVANTE CORPORATION

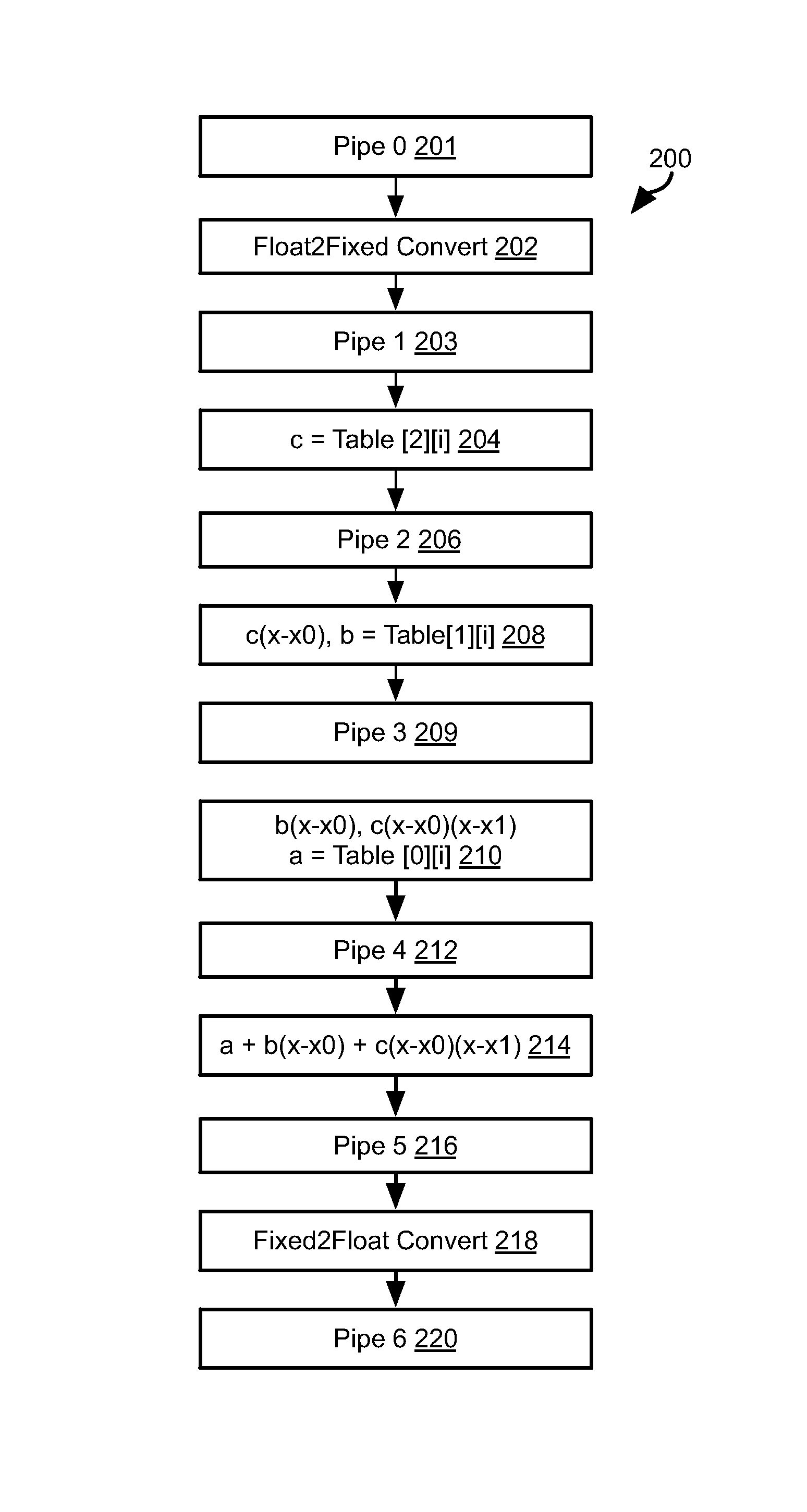

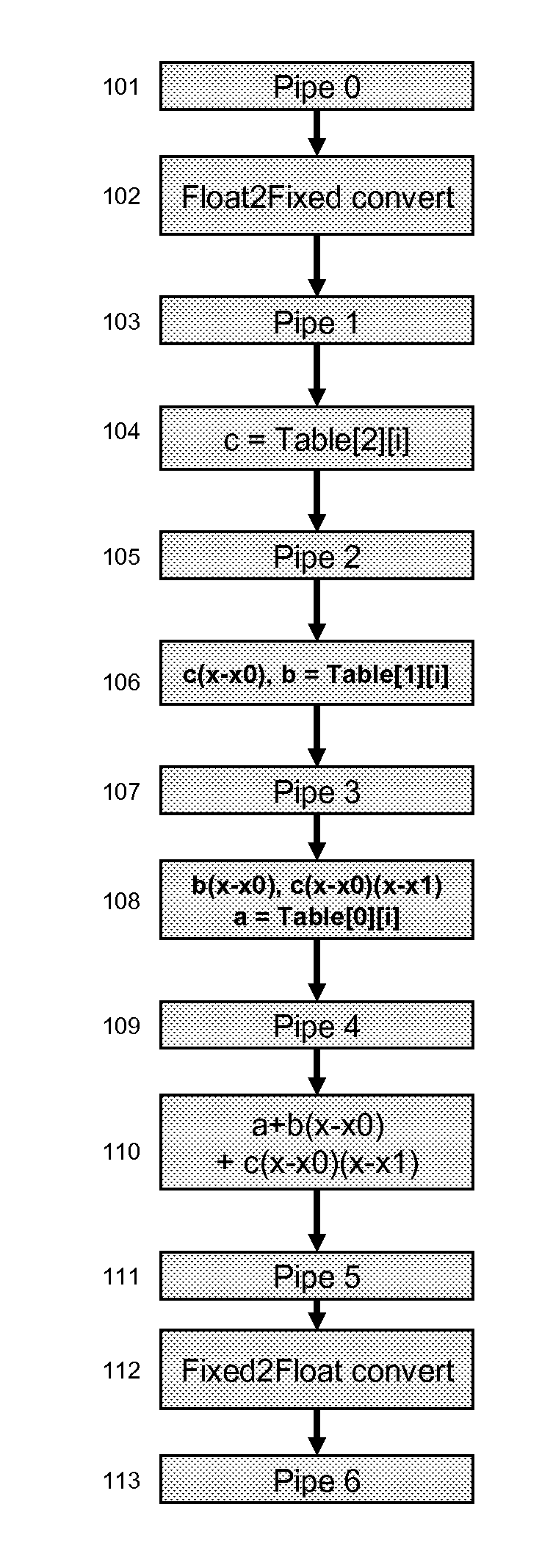

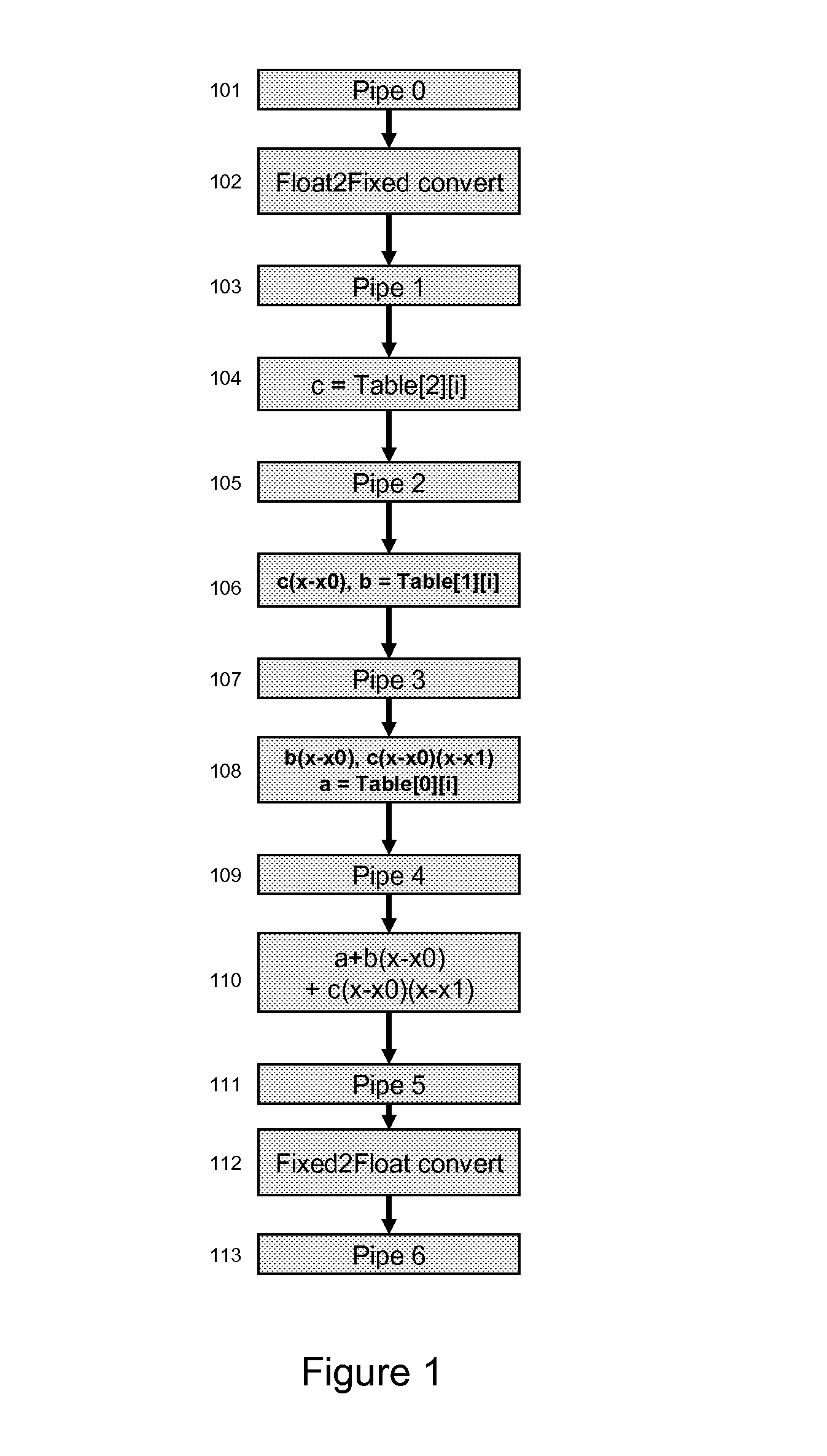

Systems and methods for computing mathematical functions

ActiveUS8346831B1Logarithmic/exponential functionsReciprocal functionsAssociated functionTheoretical computer science

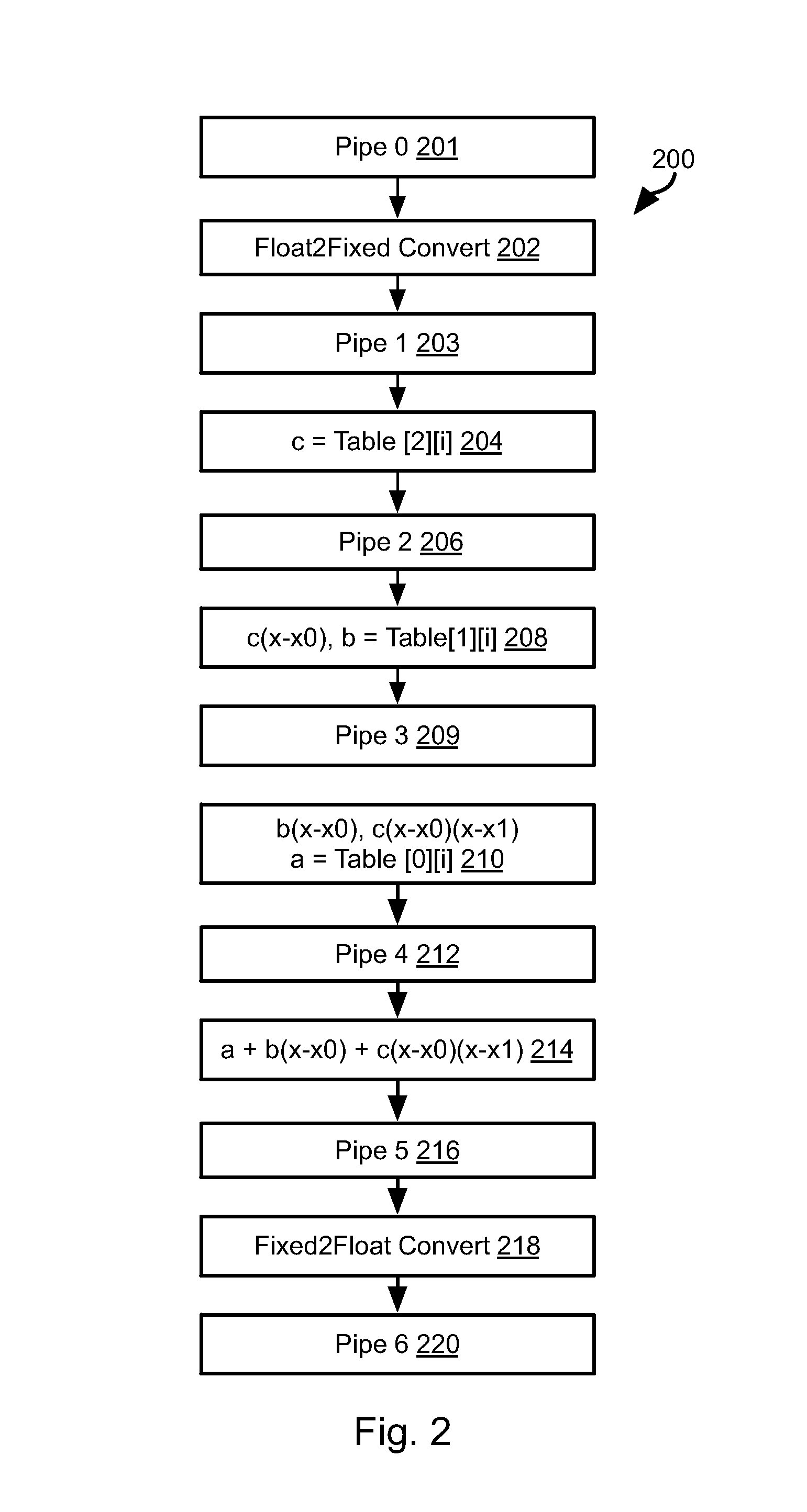

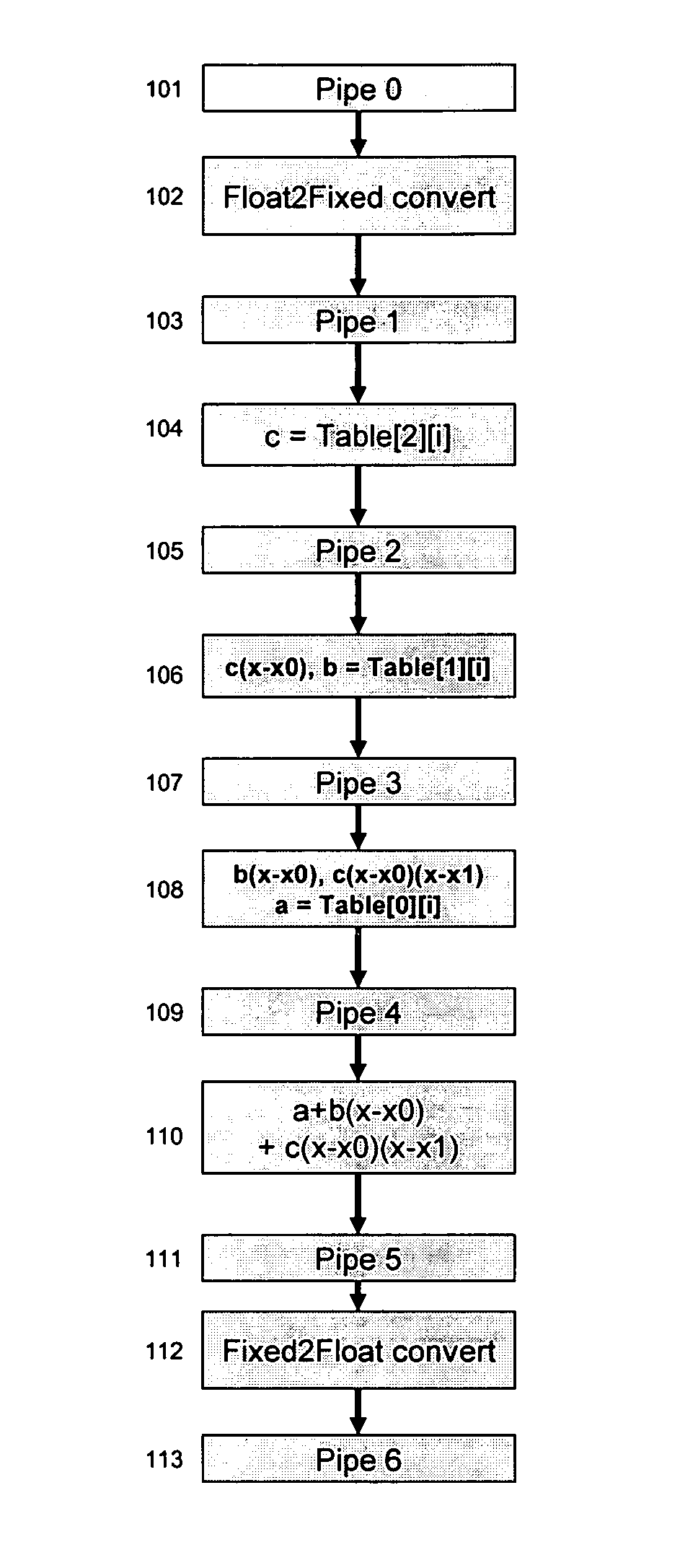

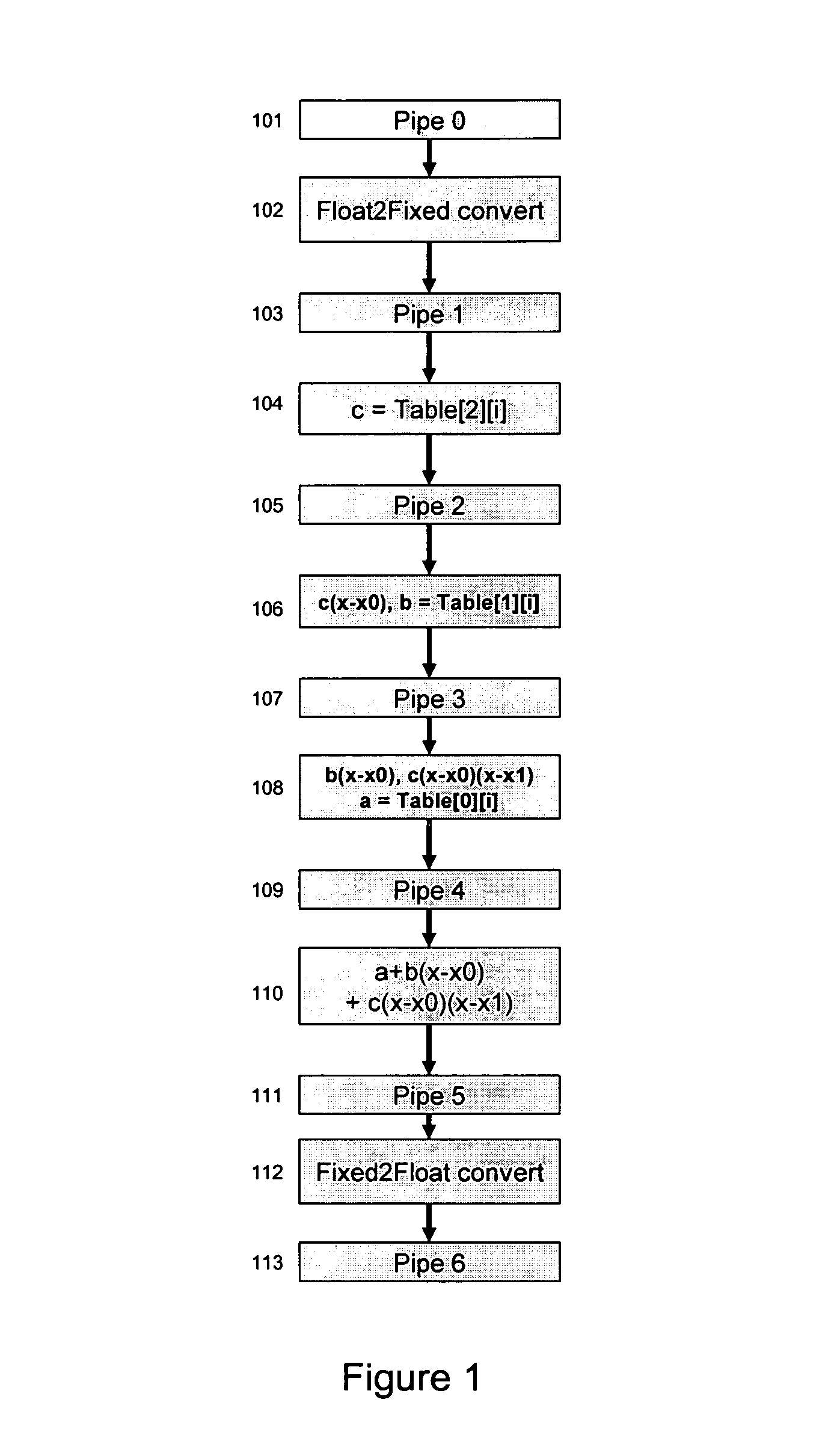

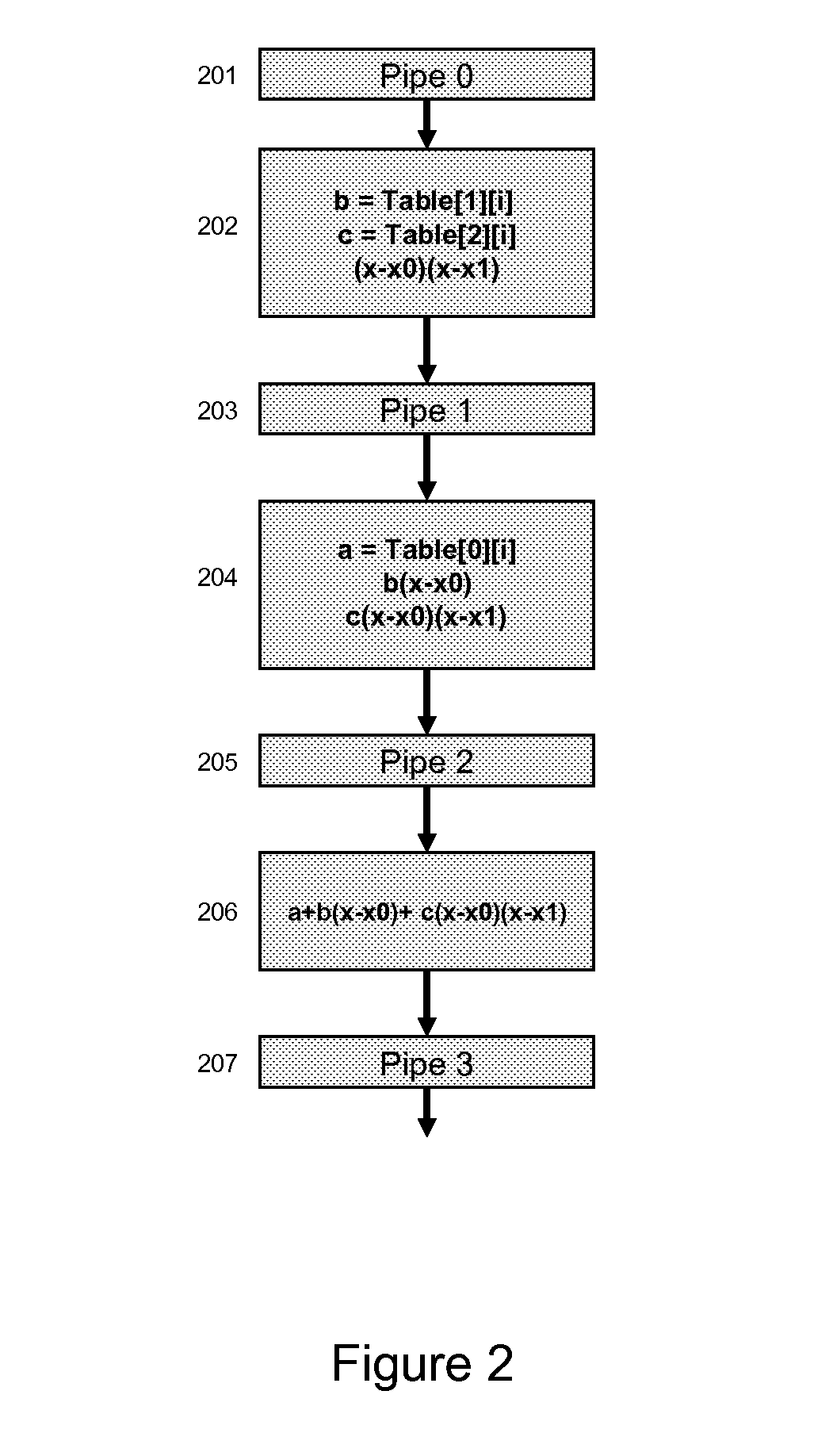

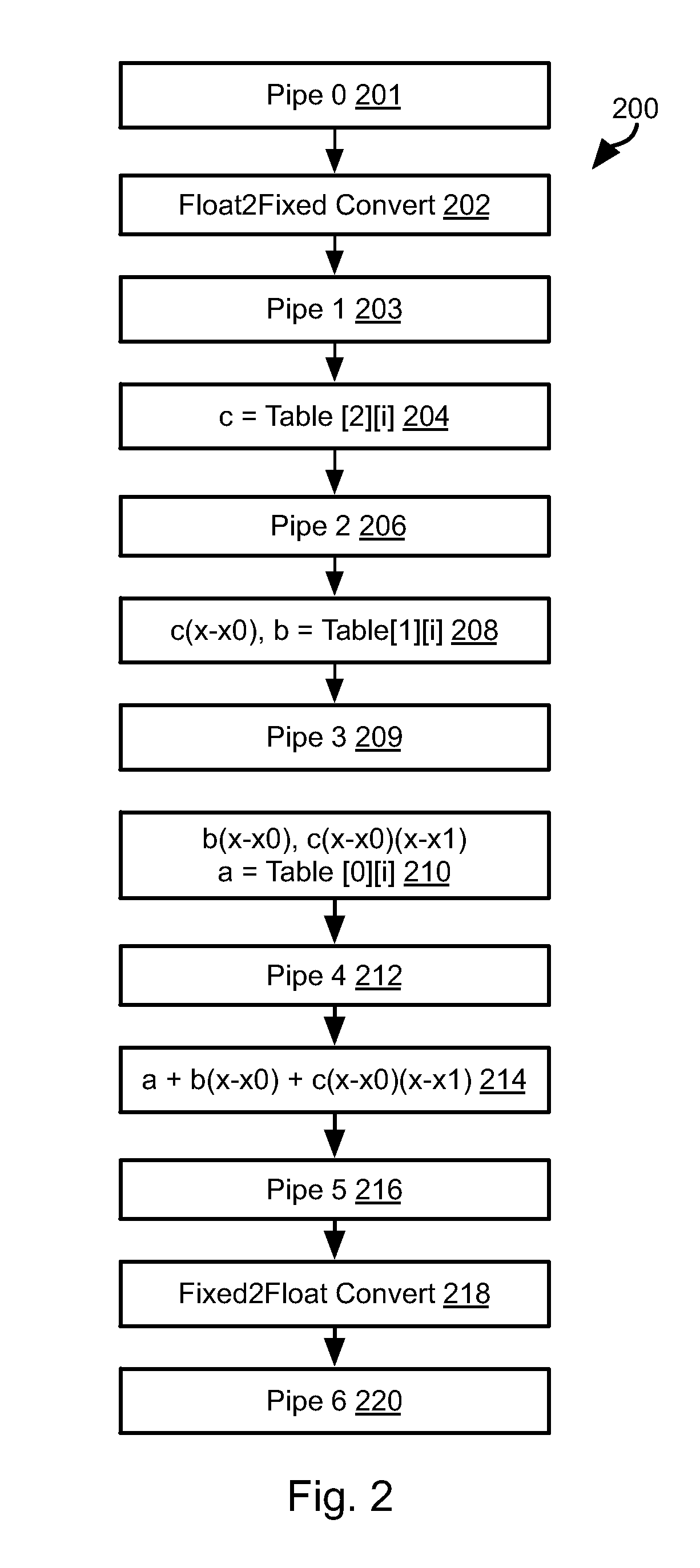

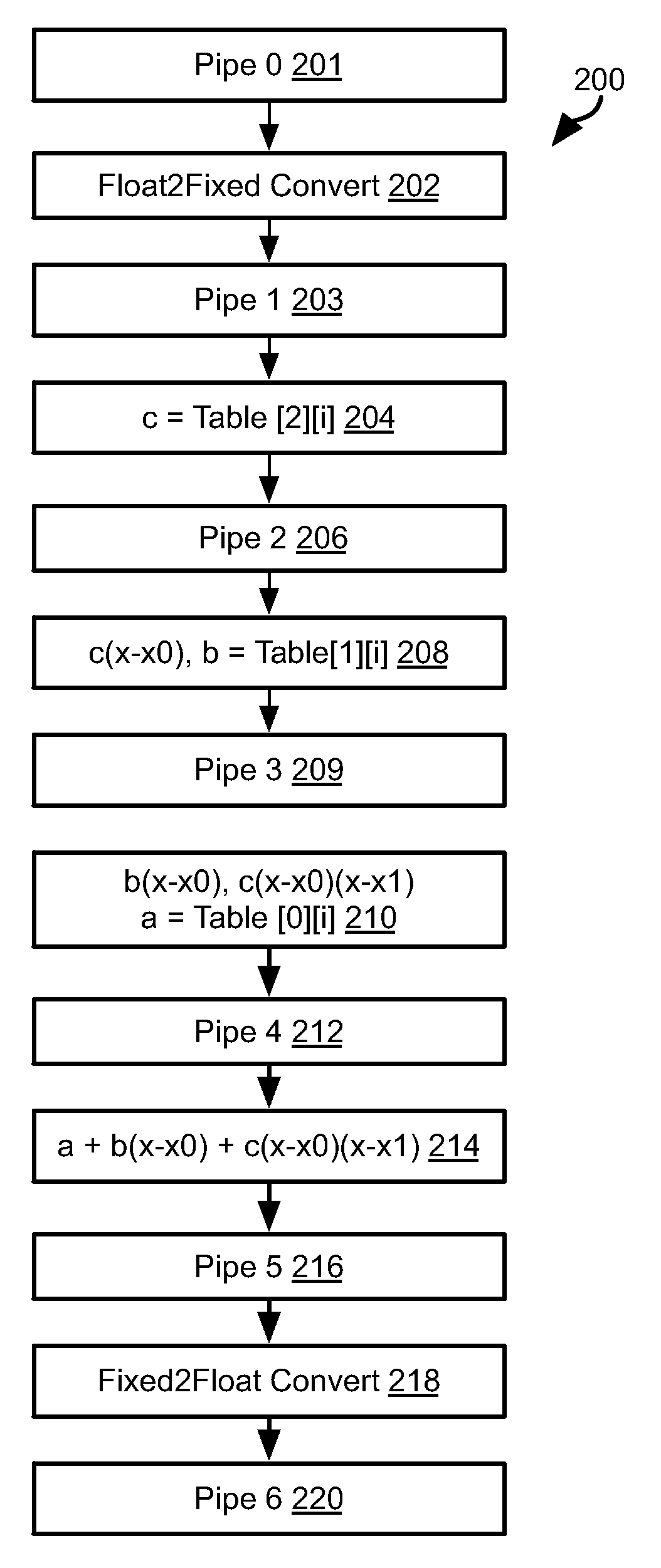

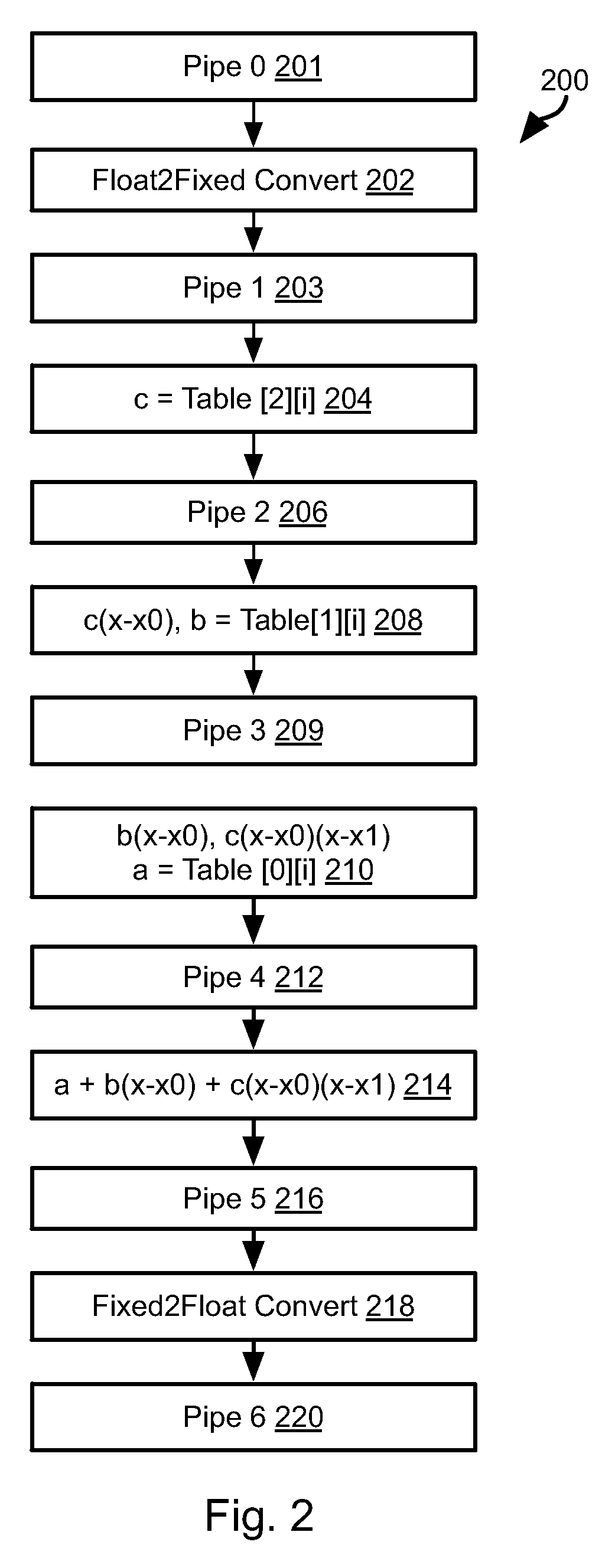

Mathematical functions are computed using a single hardware pipeline that performs polynomial approximation of second degree or higher. The single hardware pipeline includes multiple stages. Several data tables are used on the computations. The data tables are associated with a reciprocal, square root, exponential, or logarithm function. The data tables include data associated with implementing the associated function. The single hardware pipeline computes at least one of the functions associated with the data tables.

Owner:VIVANTE CORPORATION

Computation of logarithmic and exponential functions

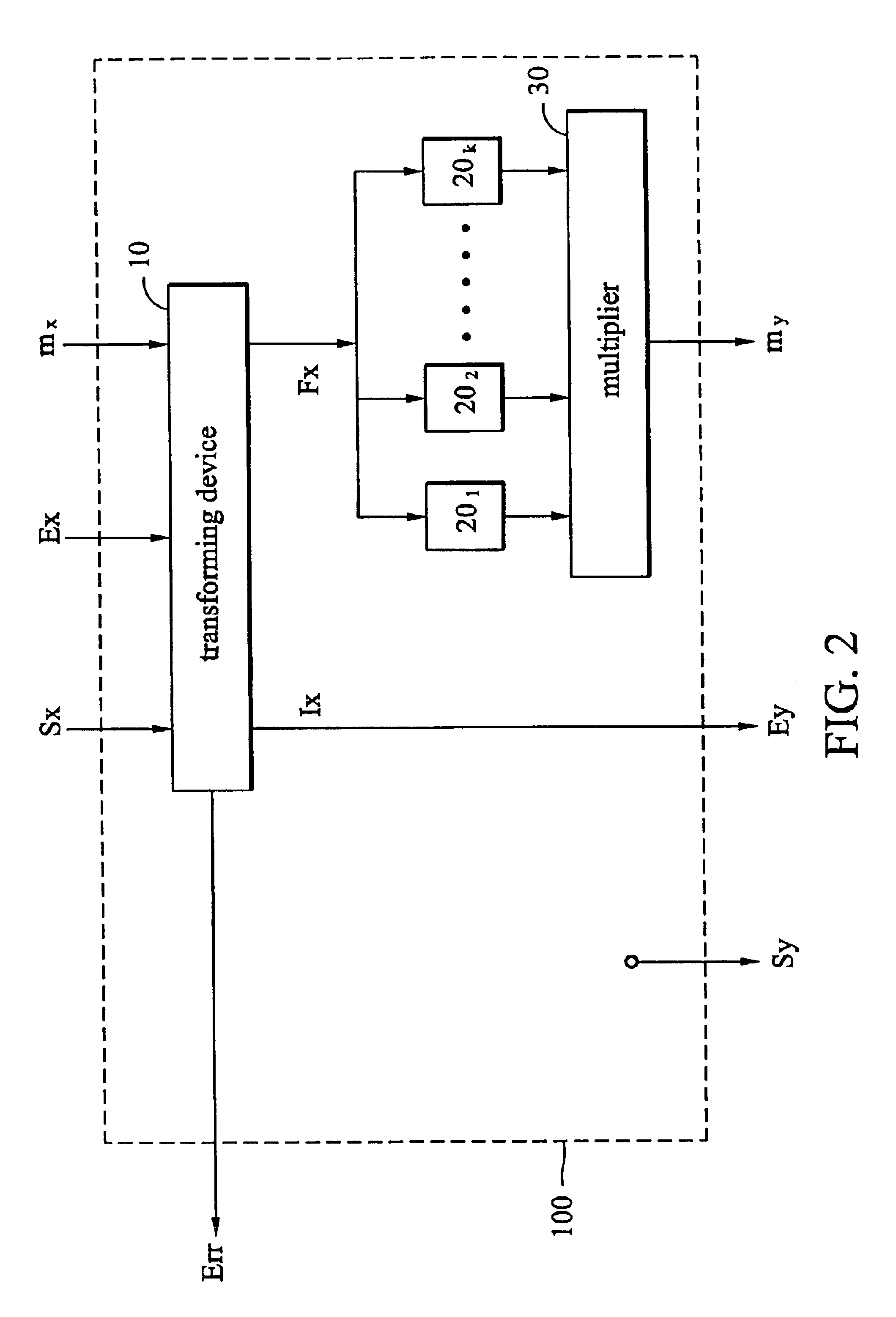

InactiveUS20050177605A1Logarithmic/exponential functionsDigital function generatorsIndex functionIntermediate product

Owner:INTEL CORP

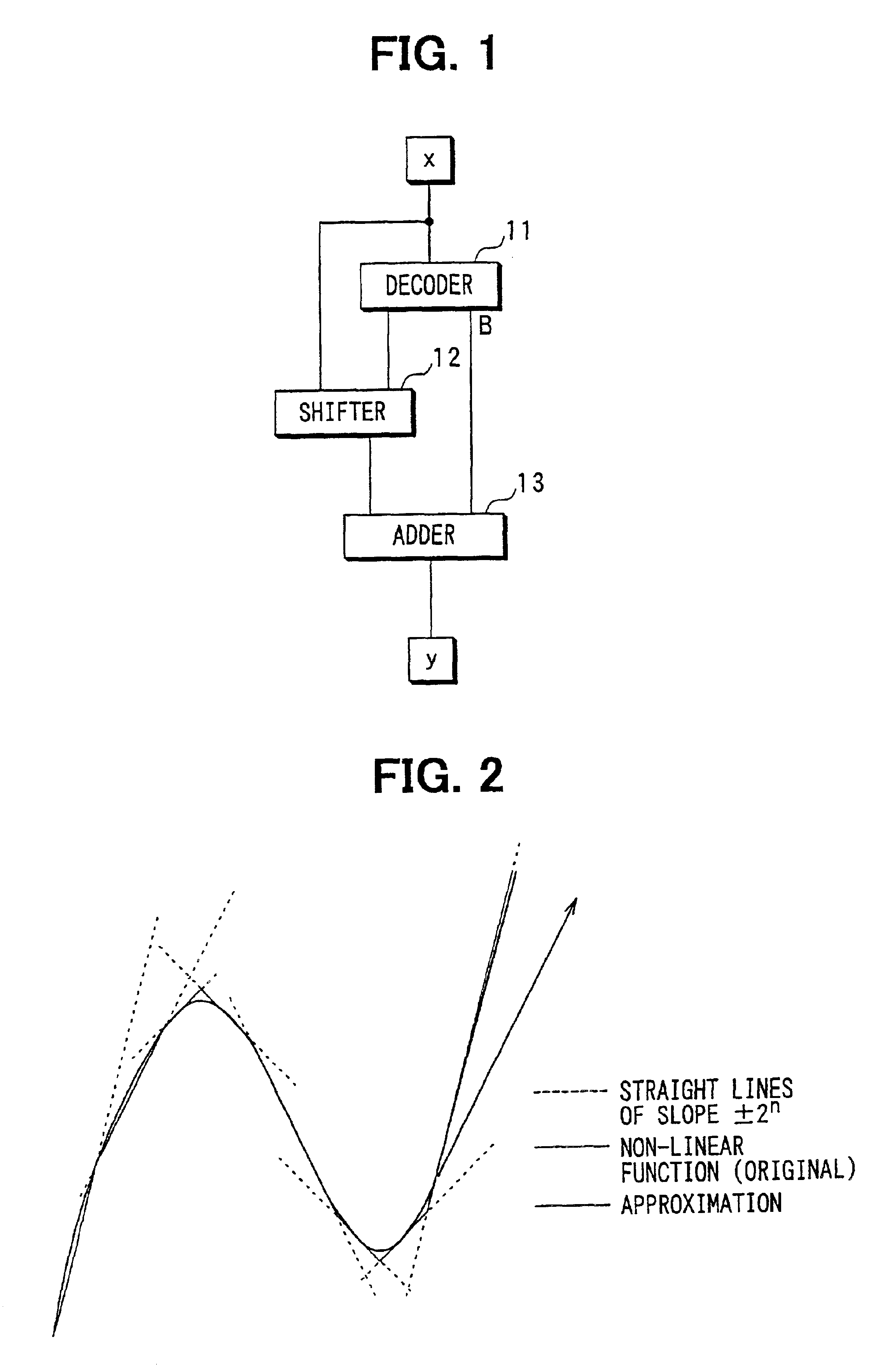

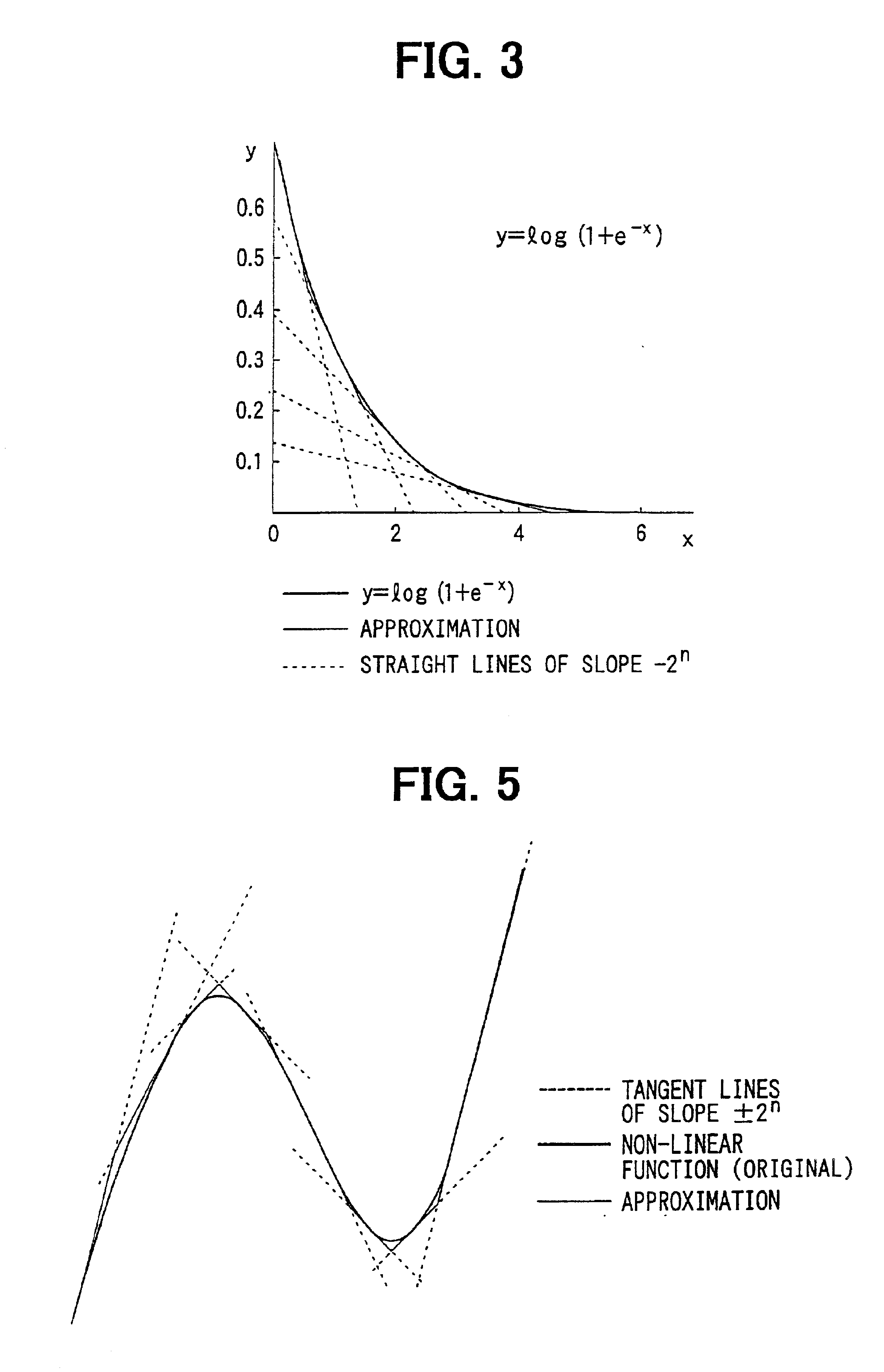

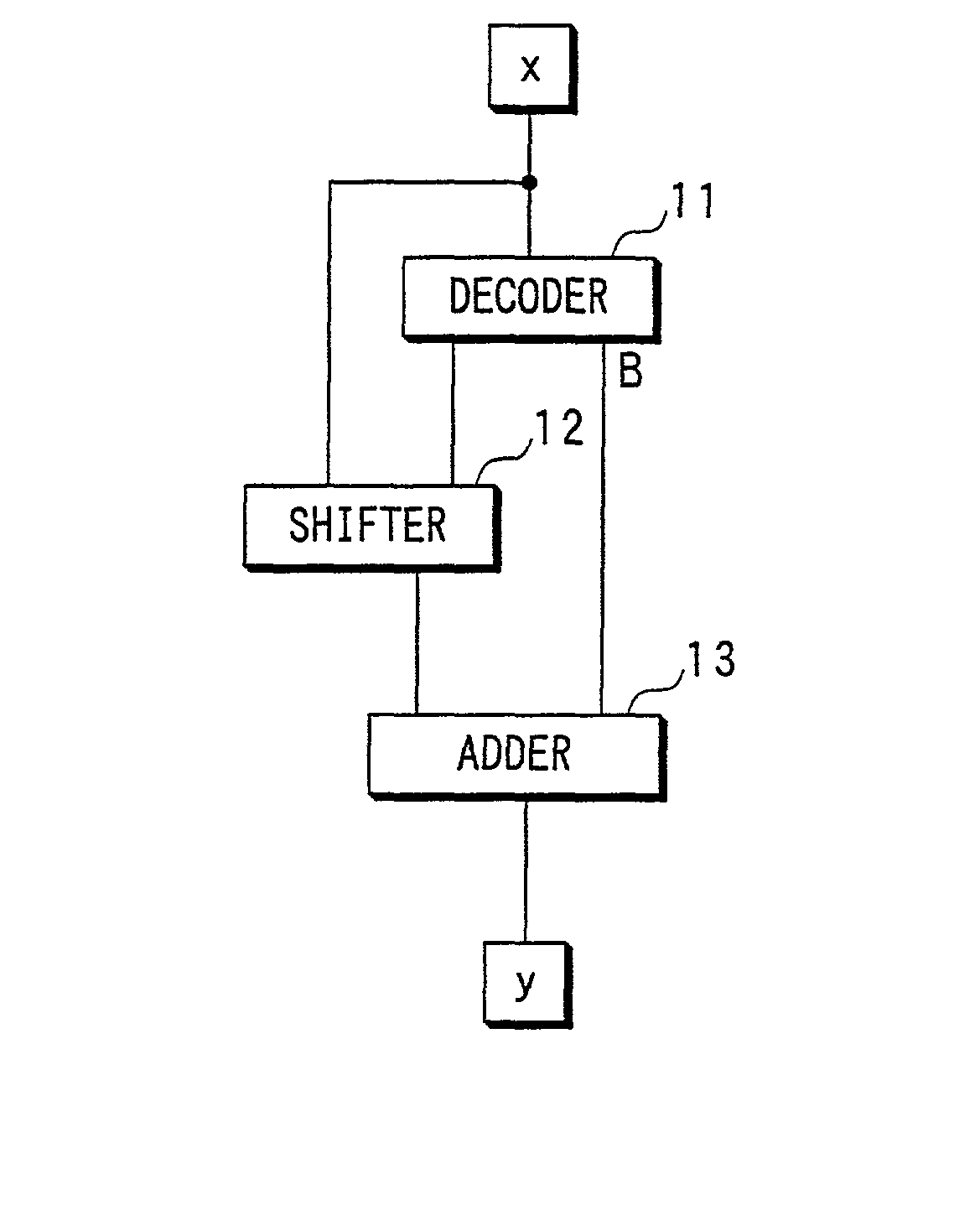

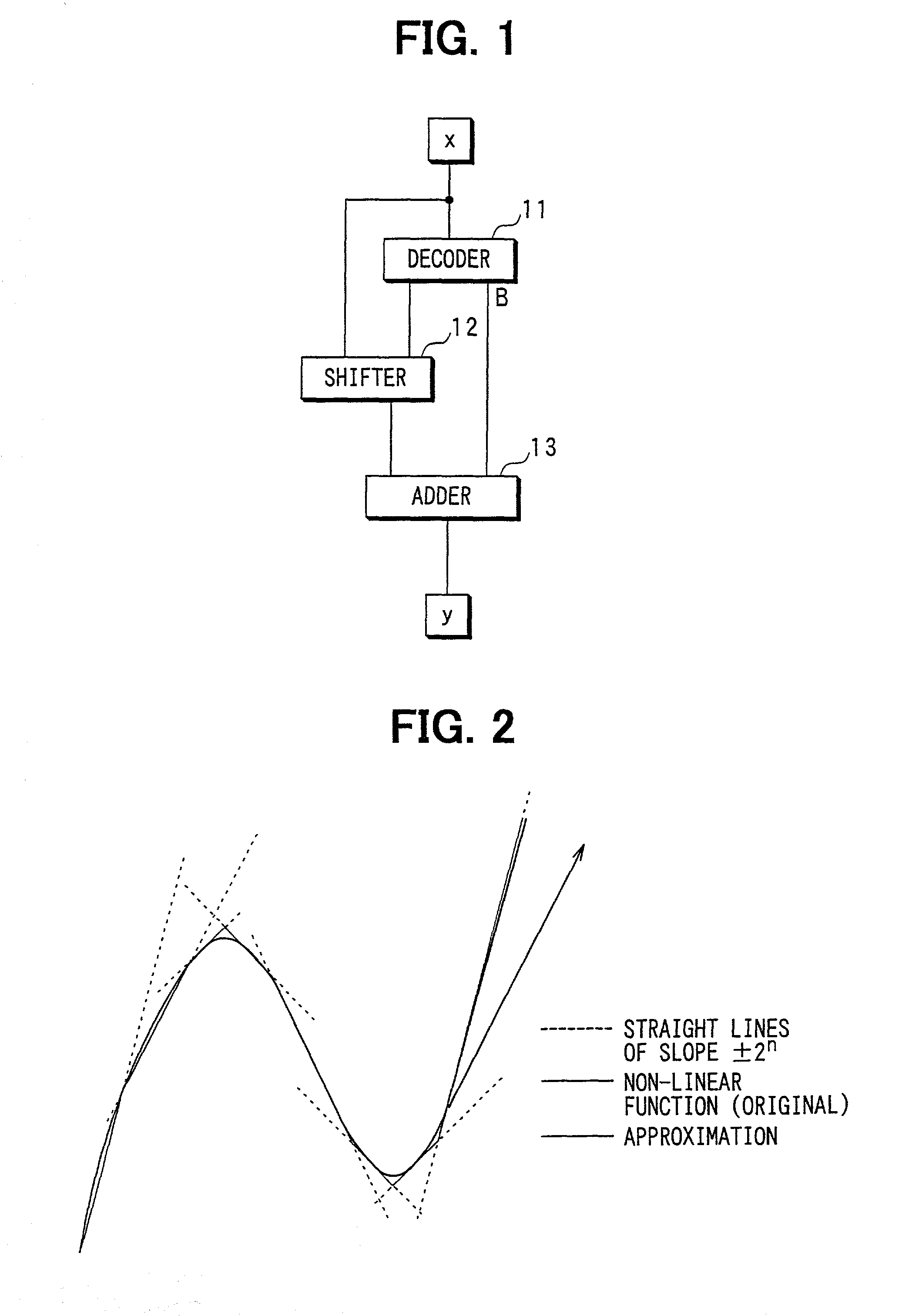

Approximate calculator for non-linear function and map decoder using same

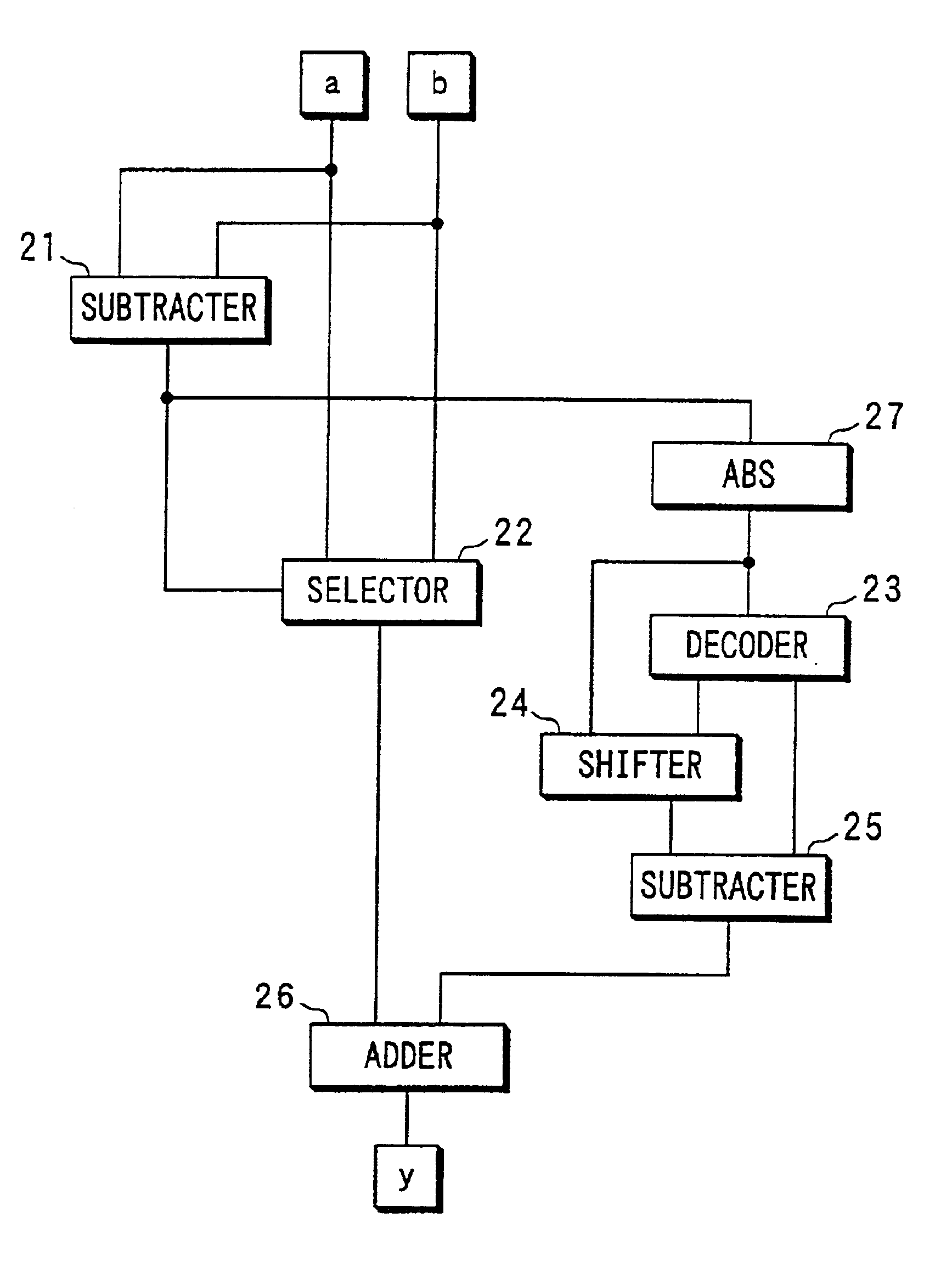

InactiveUS6922711B2Implemented by a relatively small circuitLogarithmic/exponential functionsOther decoding techniquesApproximate computingComputer science

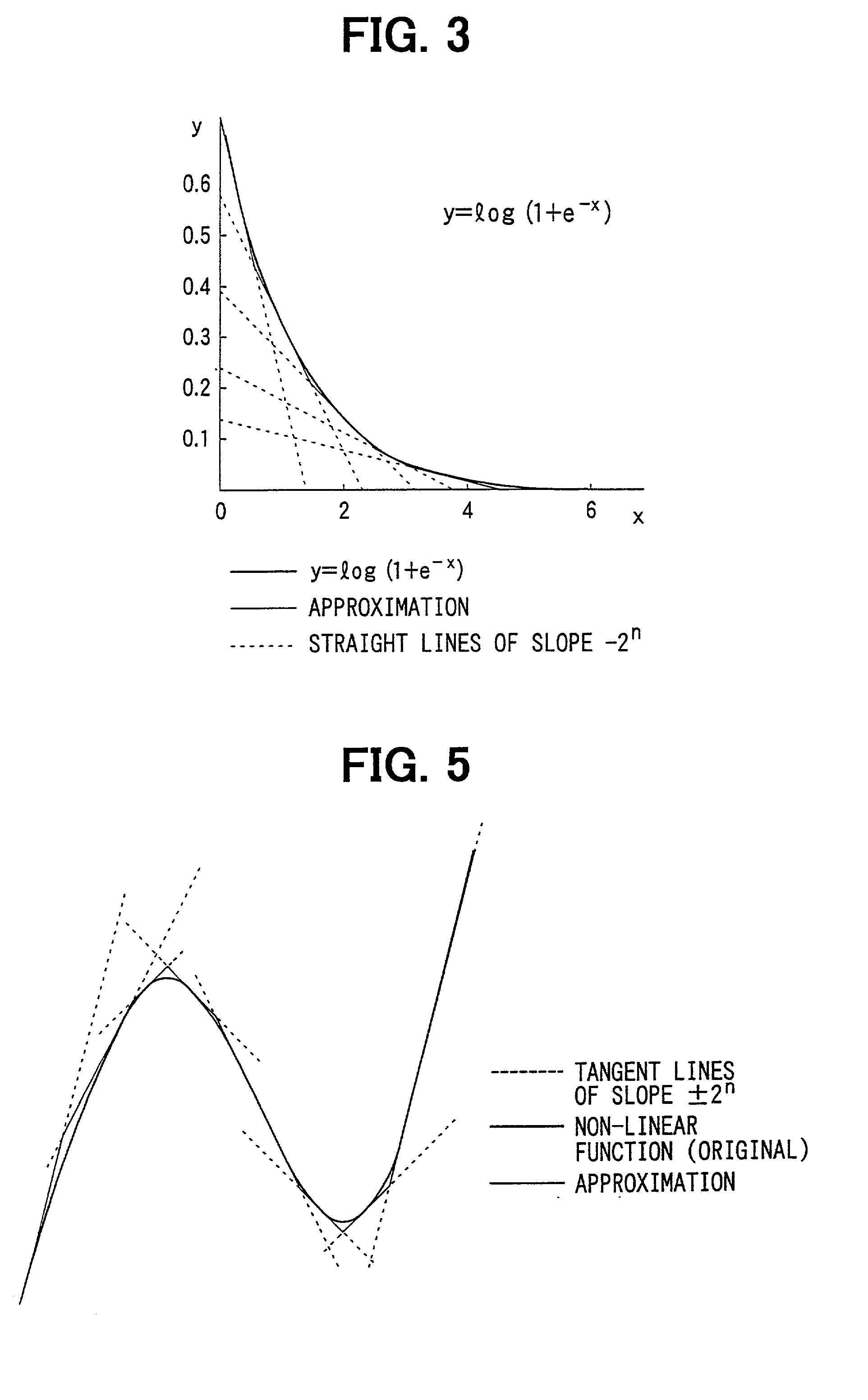

A calculator calculates an approximate value of a function Y=log (1+e−x) using input data x. In the calculator, a decoder outputs m-bit data that represents a value corresponding to the slope of a straight line, and further outputs intercept data of the straight line. The straight line interpolates the function Y=log (1+e−x) for an interval that includes the input data x as an X-value, and has a slope of −2n. The intercept data represents Y-intercept of the straight line. A shifter shifts the input data x by |n| bits based on the m-bit data, and provides the resultant value as first term data. An adder generates the sum of the first term data and the intercept data, and outputs the generated sum as an approximate value of the function log Y=(1+e−x)

Owner:DENSO CORP

Single datapath floating point implementation of RCP, SQRT, EXP and LOG functions and a low latency RCP based on the same techniques

InactiveUS20130091189A1Logarithmic/exponential functionsReciprocal functionsTheoretical computer scienceLatency (engineering)

Owner:VIVANTE CORPORATION

Systems and methods for computing mathematical functions

Mathematical functions are computed in a single pipeline performing a polynomial approximation (e.g. a quadratic approximation, or the like) using data tables for RCP, SQRT, EXP or LOG using a single pipeline according and opcodes. SIN and COS are also computed using the pipeline according to the approximation ((−1)̂IntX)*Sin(π*Min(FracX, 1.0−FracX) / Min(FracX, 1.0−FracX). A pipeline portion approximates Sin(π*FracX) using tables and interpolation and a subsequent stage multiplies this approximation by FracX. For input arguments of x close 1.0. LOG 2(x−1) / (x−1) is computed using a first pipeline portion using tables and interpolation and subsequently multiplied by (x−1). A DIV operation may also be performed with input arguments scaled up to avoid underflow as needed. Inverse trigonometric functions may be calculated using a pre-processing stage and post processing stage in order to obtain multiple inverse trigonometric functions from a single pipeline.

Owner:VIVANTE CORPORATION

Digital signal processor having instruction set with an exponential function using reduced look-up table

InactiveUS9128790B2Logarithmic/exponential functionsComputation using non-contact making devicesDigital signal processingAlgorithm

A digital signal processor is provided having an instruction set with an exponential function that uses a reduced look-up table. The disclosed digital signal processor evaluates an exponential function for an input value, x, by decomposing the input value, x, to an integer part, N, a first fractional part, q1, larger than a specified value, x0, and a second fractional part, q2, smaller than the specified value, x0; computing 2q<sub2>2 < / sub2>using a polynomial approximation, such as a cubic approximation; obtaining 2q<sub2>1 < / sub2>from a look-up table; and evaluating the exponential function for the input value, x, by multiplying 2q<sub2>2< / sub2>, 2q<sub2>1 < / sub2>and 2N together. Look-up table entries have a fewer number of bits than a number of bits in the input value, x.

Owner:INTEL CORP

Digital signal processor having instruction set with a logarithm function using reduced look-up table

ActiveUS9170776B2Logarithmic/exponential functionsComputation using non-contact making devicesDigital signal processingInstruction set

A digital signal processor is provided having an instruction set with a logarithm function that uses a reduced look-up table. The disclosed digital signal processor evaluates a logarithm function for an input value, x, by decomposing the input value, x, to a first part, N, a second part, q, and a remaining part, r, wherein the first part, N, is identified by a position of a most significant bit of the input value, x, and the second part, q, is comprised of a number of bits following the most significant bit, wherein the number is small relative to a number of bits in the input value, x; obtaining a valueLog2(1+12q)from a first look-up table based on the second part, q; computing an epsilon term, ε, using the expression2-N1+12qr;evaluating an expression Log2 (1+ε) using a polynomial approximation, such as a cubic approximation; and determining the logarithm function for the input value, x, by summing the values of N,LogZ(1+12q)and Log2(1+ε).

Owner:INTEL CORP

Approximate calculator for non-linear function and map decoder using same

InactiveUS20020129072A1Implemented by a relatively small circuitLogarithmic/exponential functionsOther decoding techniquesApproximate computingComputer science

A calculator calculates an approximate value of a function Y=log (1+e.sup.-X) using input data x. In the calculator, a decoder outputs m-bit data that represents a value corresponding to the slope of a straight line, and further outputs intercept data of the straight line. The straight line interpolates the function Y=log (1+e.sup.-X) for an interval that includes the input data x as an X-value, and has a slope of -2.sup.n. The intercept data represents Y-intercept of the straight line. A shifter shifts the input data x by .vertline.n.vertline. bits based on the m-bit data, and provides the resultant value as first term data. An adder generates the sum of the first term data and the intercept data, and outputs the generated sum as an approximate value of the function log Y=(1+e.sup.-X)

Owner:DENSO CORP

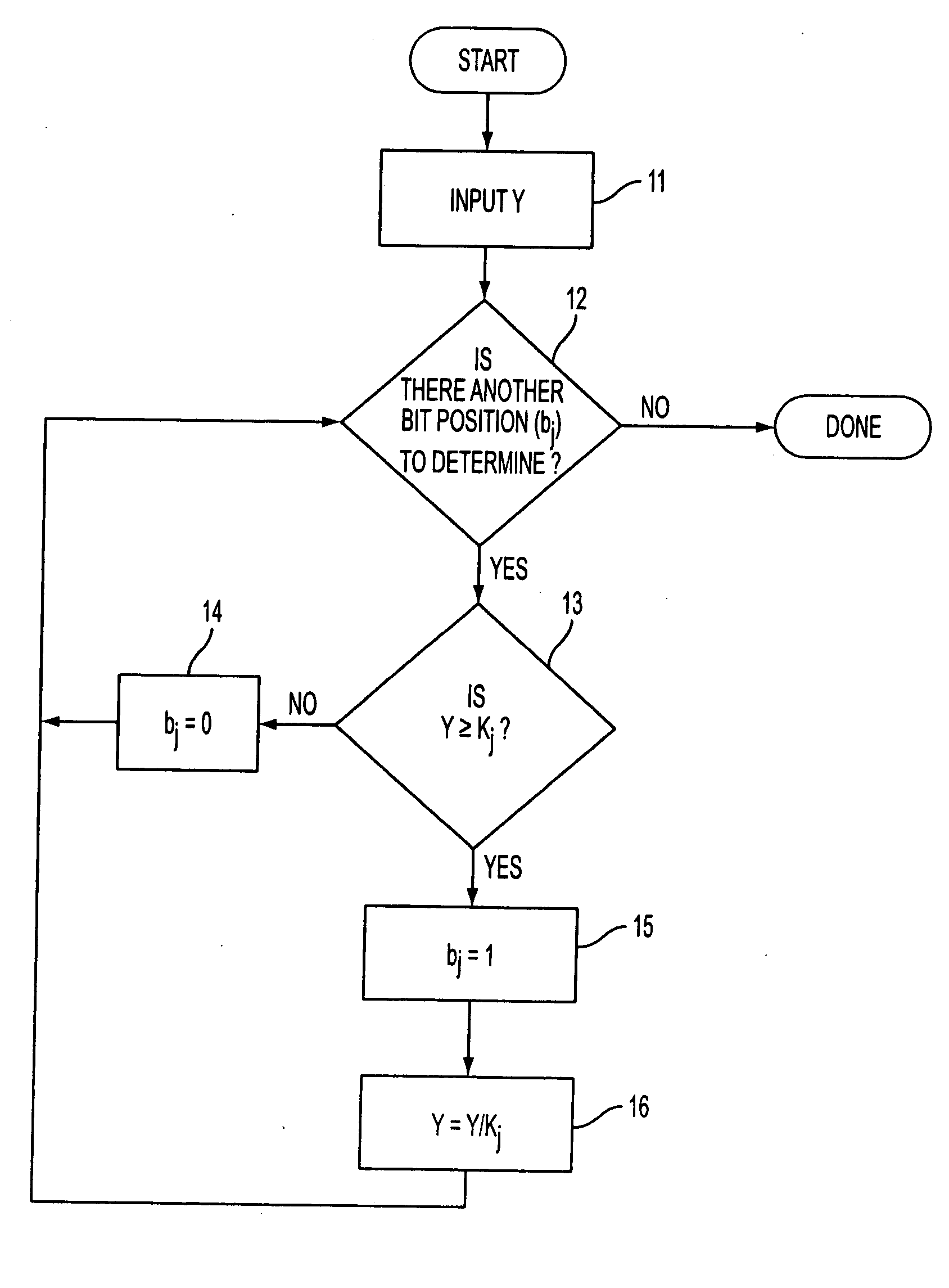

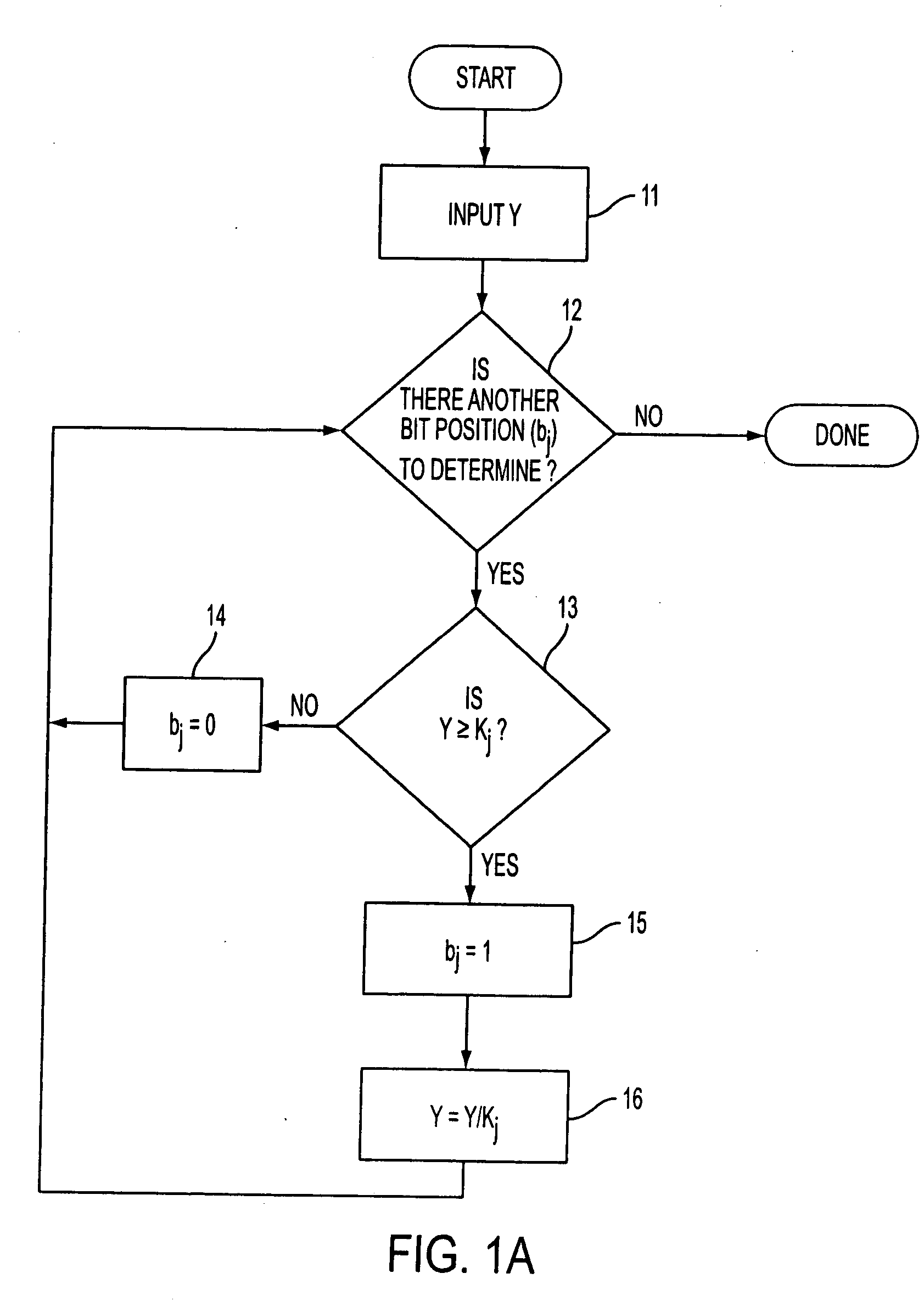

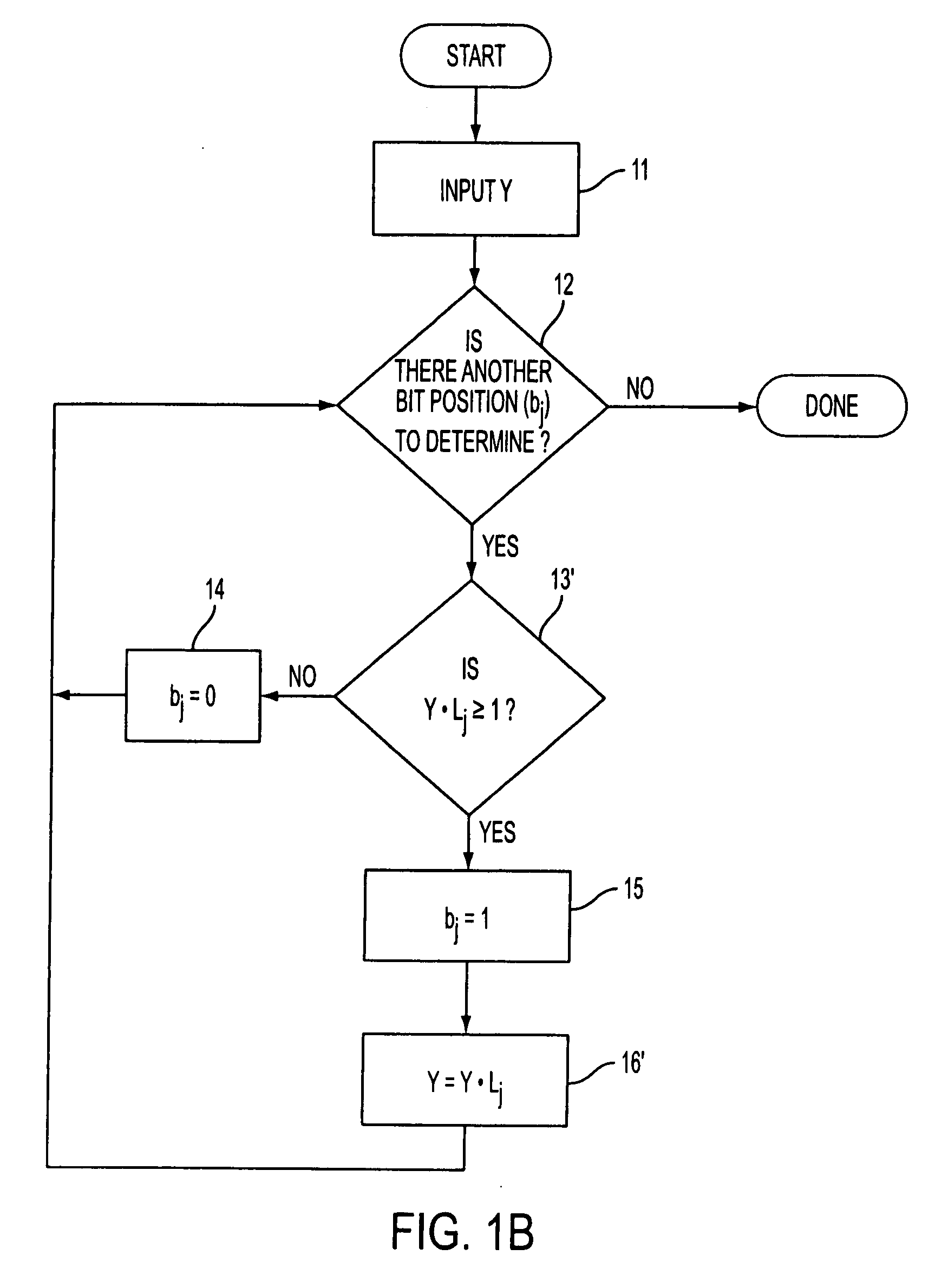

Method for base two logarithmic estimation

InactiveUS20050138095A1Logarithmic/exponential functionsDigital function generatorsGeneral purposeTheoretical computer science

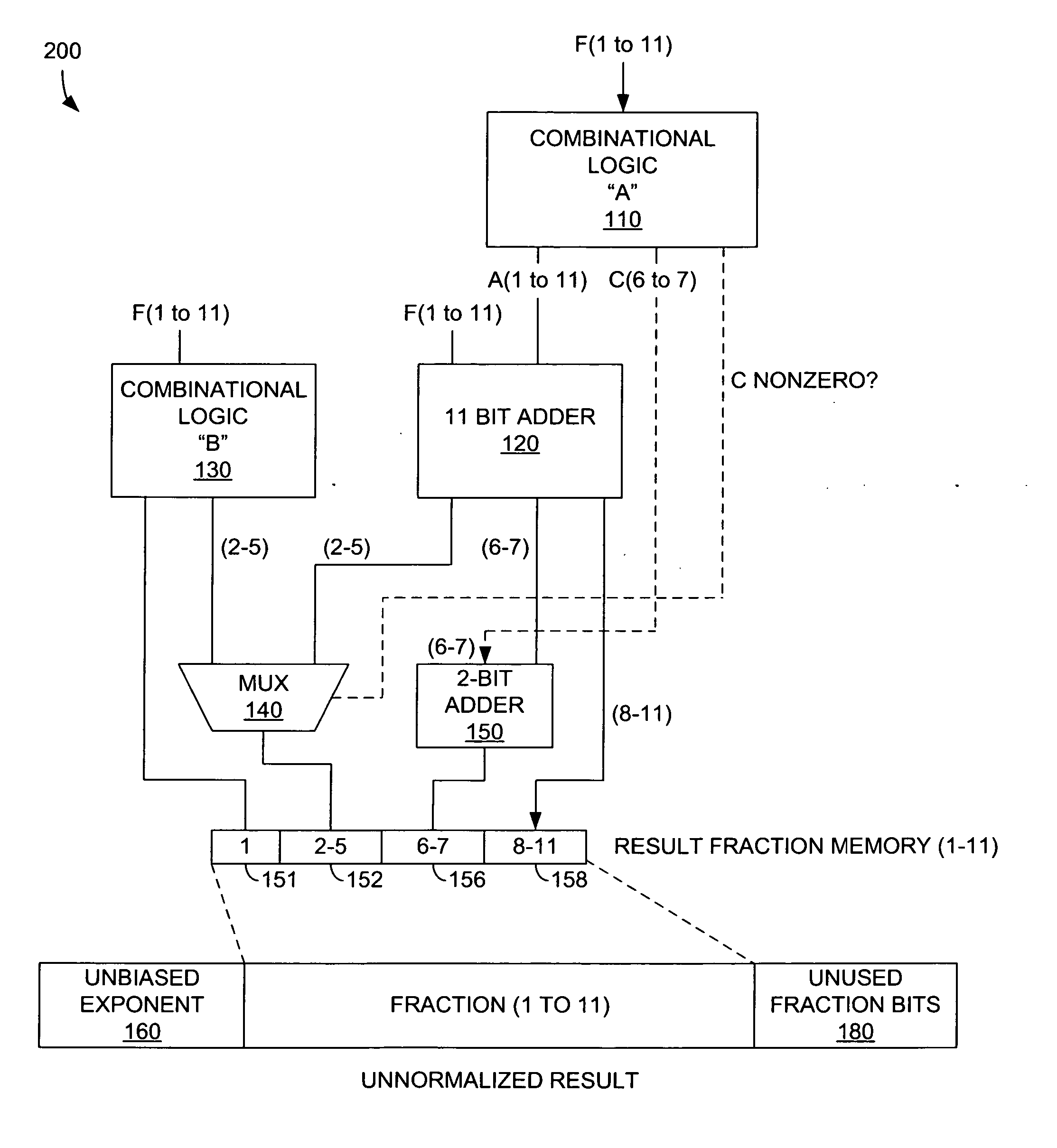

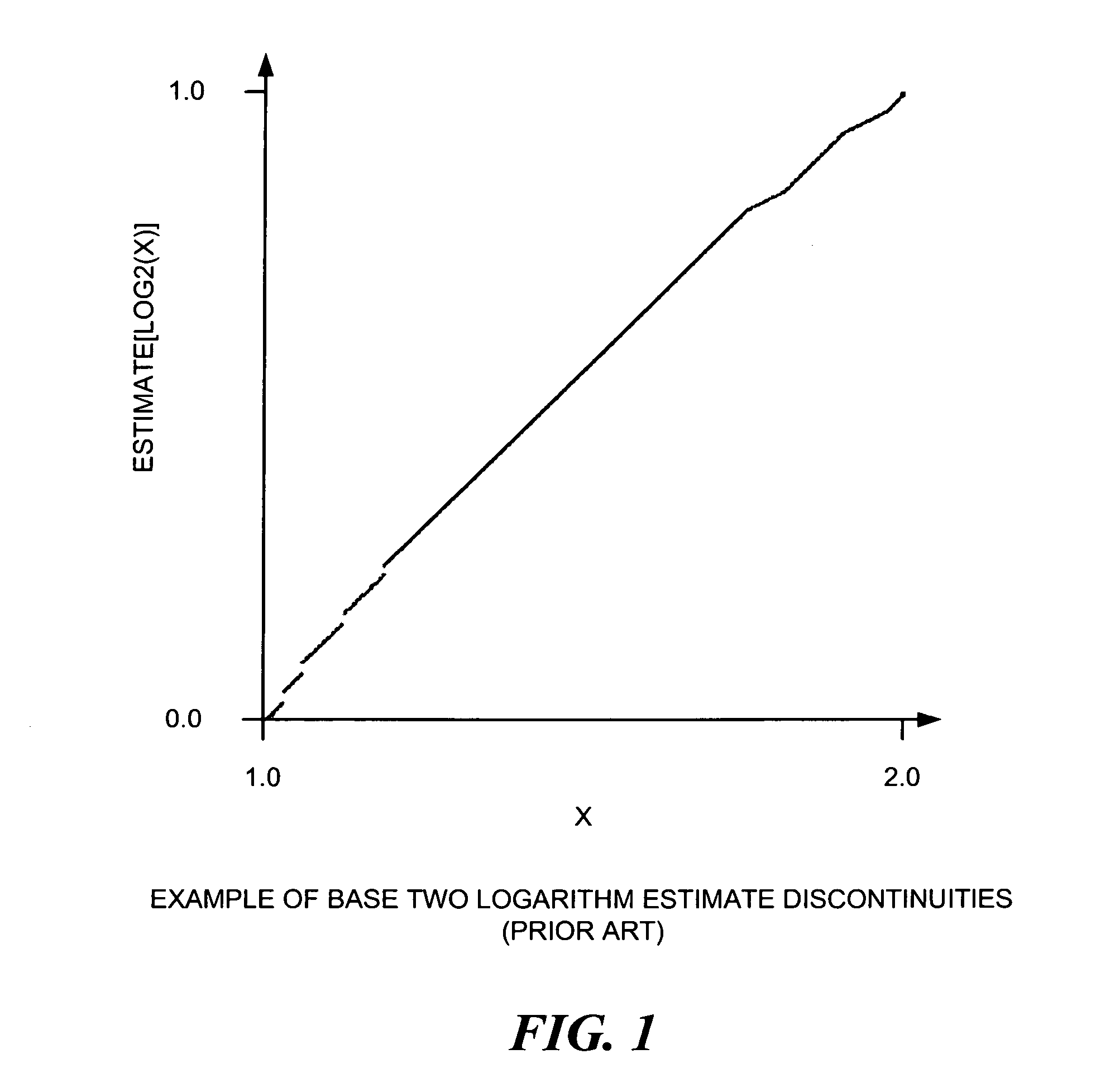

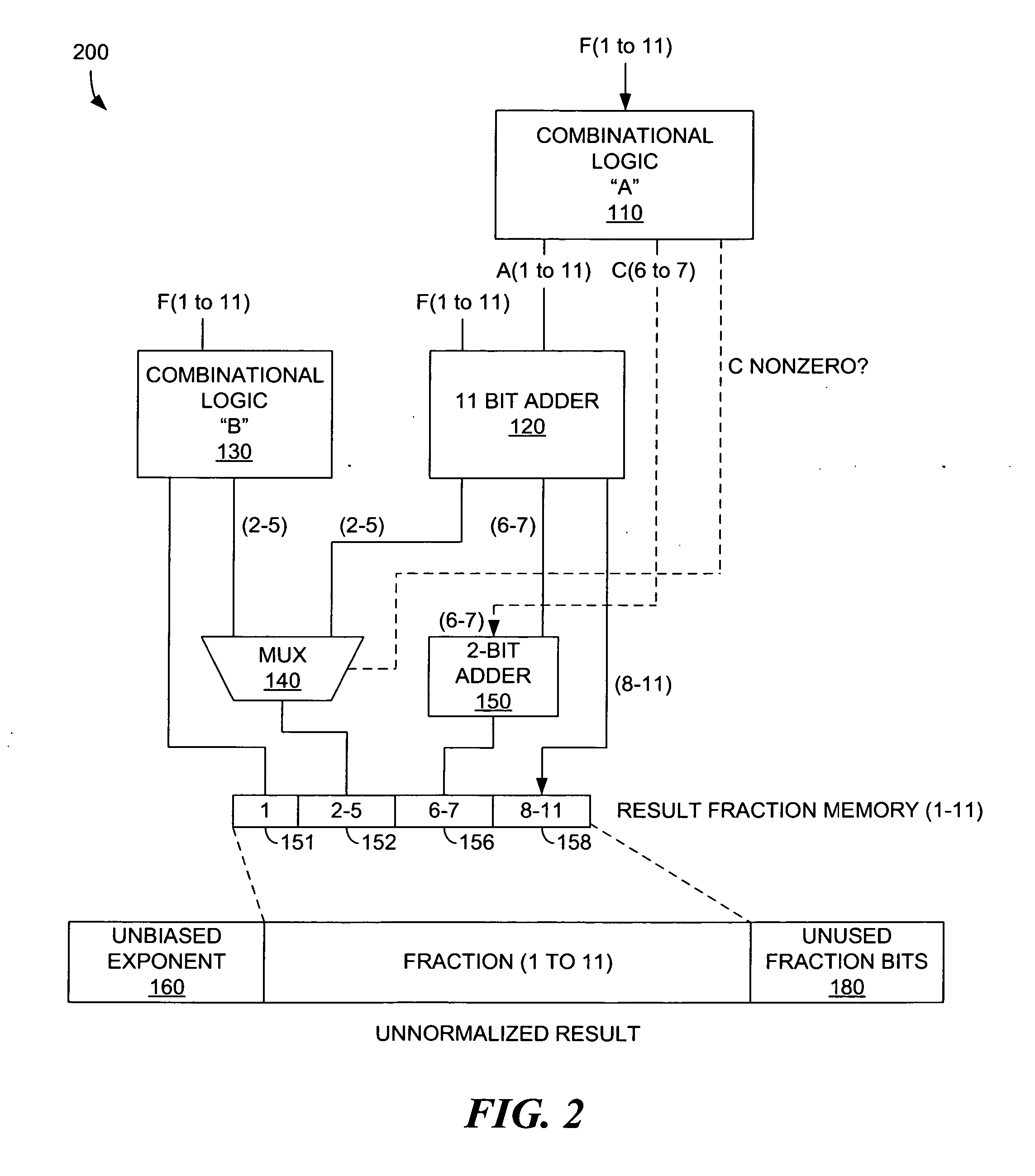

The present invention provides for implementing a base two logarithmic estimation function in a general purpose processor. The present invention provides for partitioning an input value into a biased exponent value and a mantissa. Whether the biased exponent value is negative is determined. A first intermediate value from the mantissa is generated using custom combinational logic. A second intermediate value from the mantissa is generated using custom combinational logic. An unnormalized result fraction value from the first and second intermediate value and the mantissa is generated using custom combinational logic. This unnormalized result fraction and the unbiased exponent of the input are concatenated and normalized to form the final result.

Owner:IBM CORP

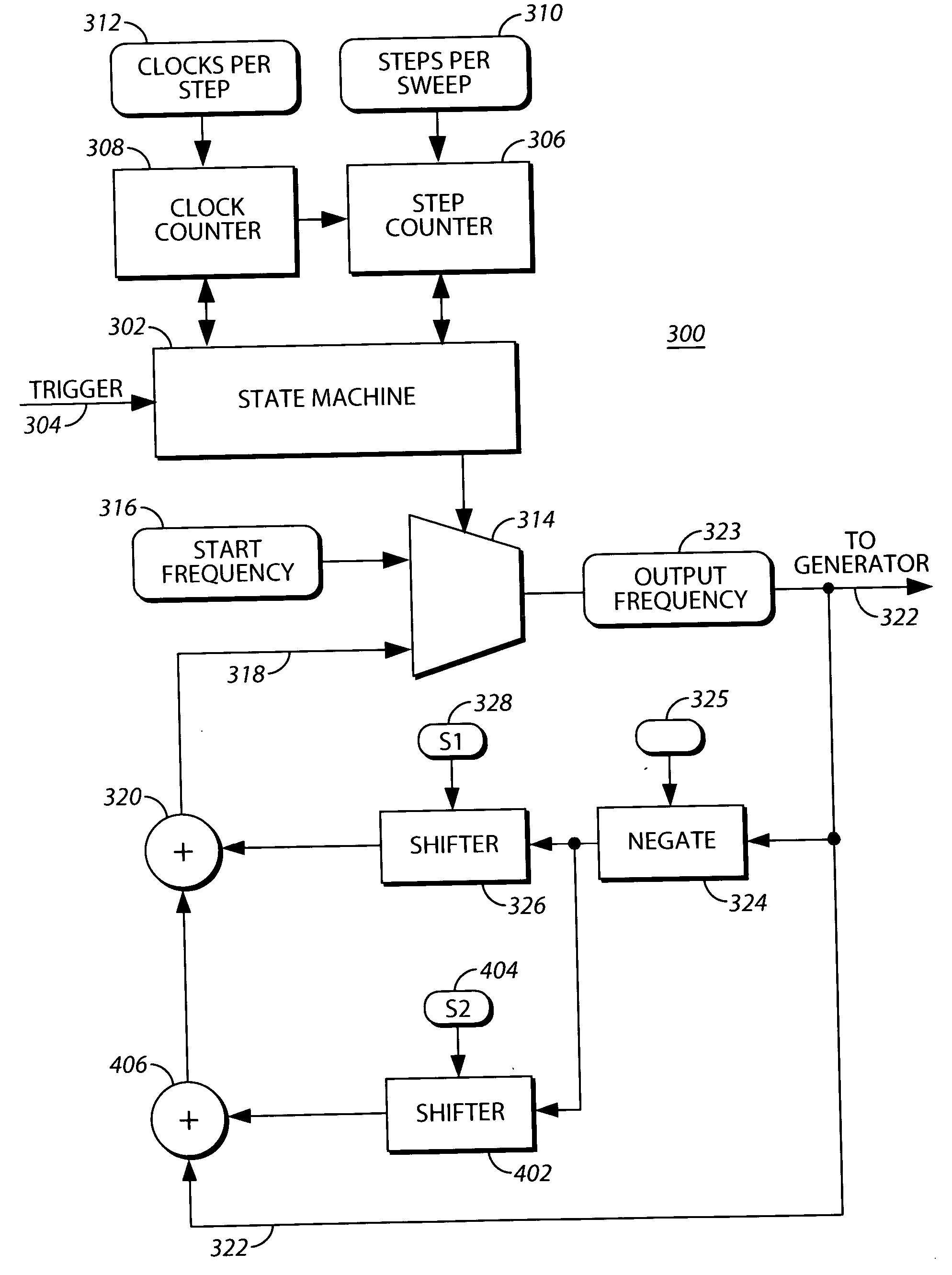

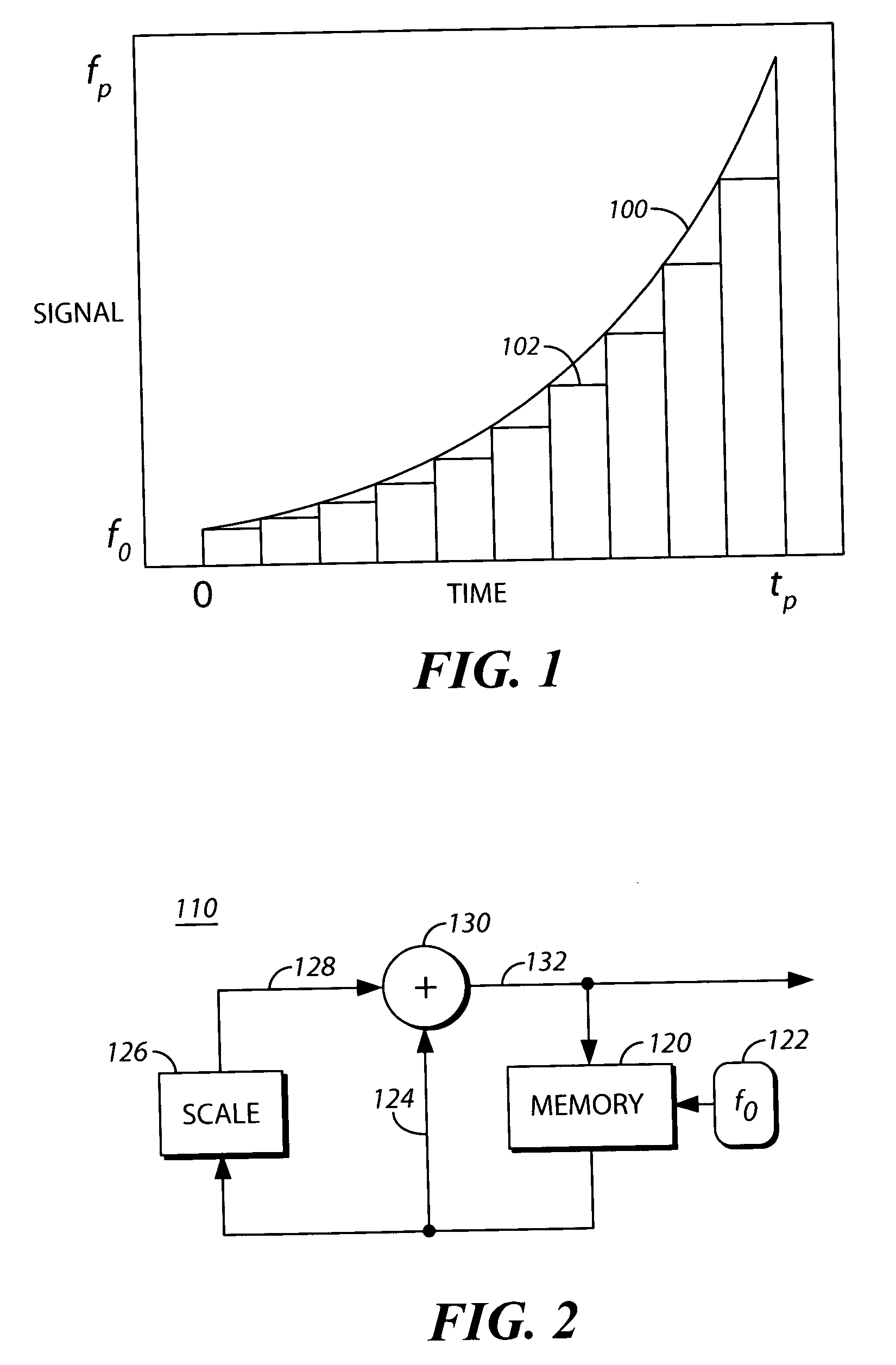

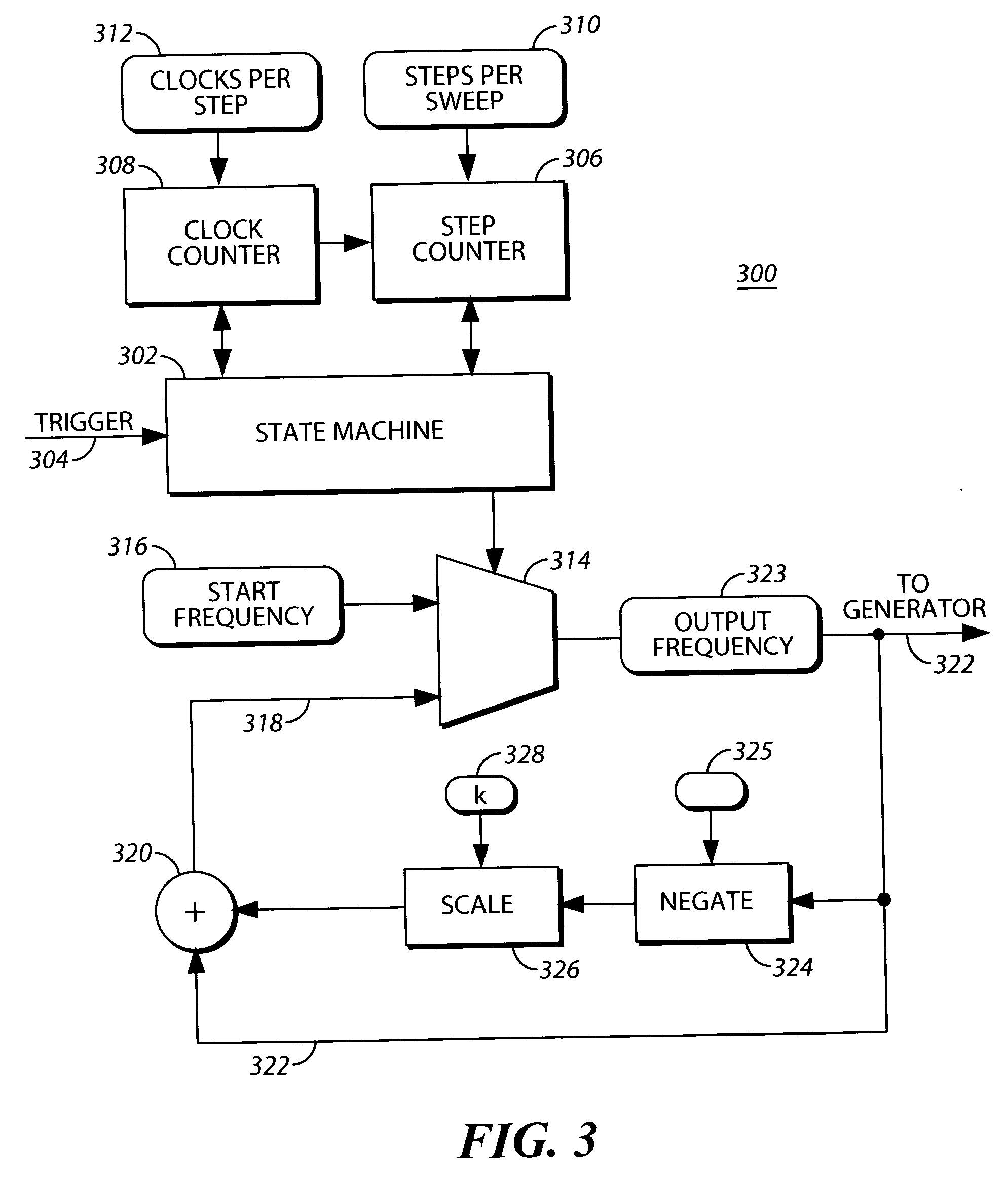

Method and apparatus for producing an exponential signal

InactiveUS20050080830A1Logarithmic/exponential functionsDigital function generatorsScale unitSignal generator

An exponential signal generator having a memory, a scale unit and an adder. A value stored in the memory is scaled and added to itself to produce a new value for storing in the memory. The exponential signal is represented by the exponential value.

Owner:AGILENT TECH INC

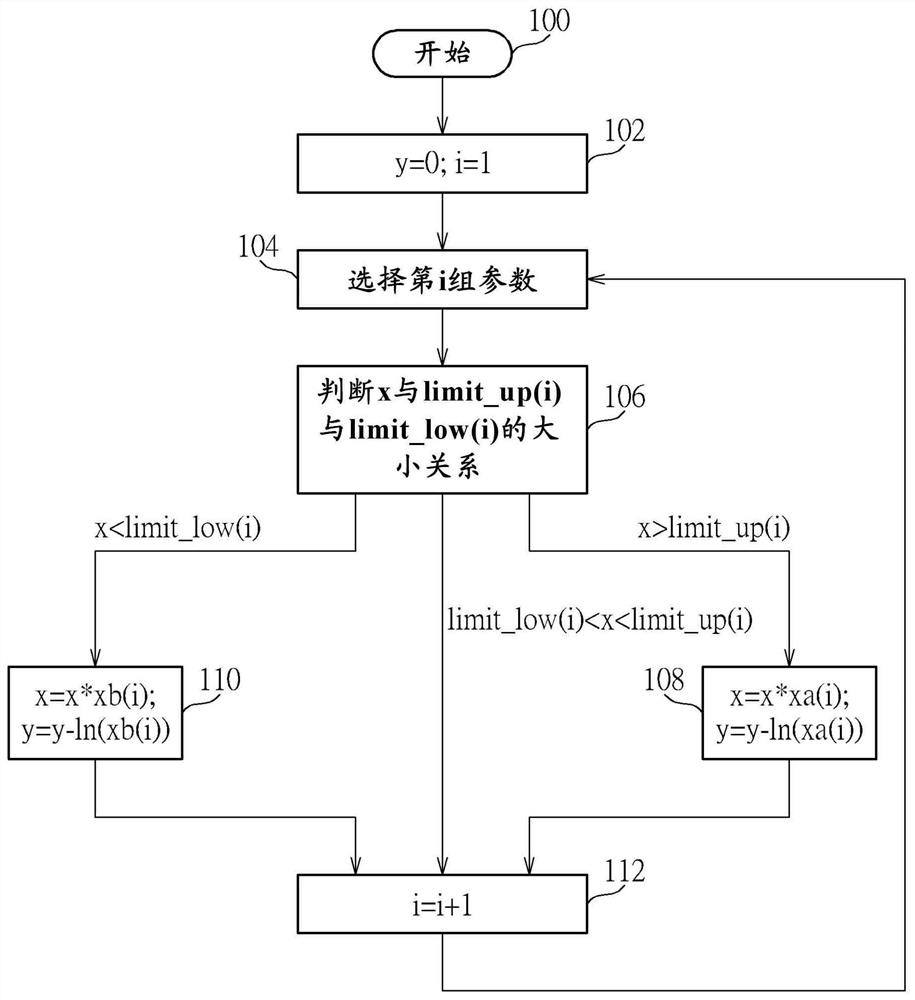

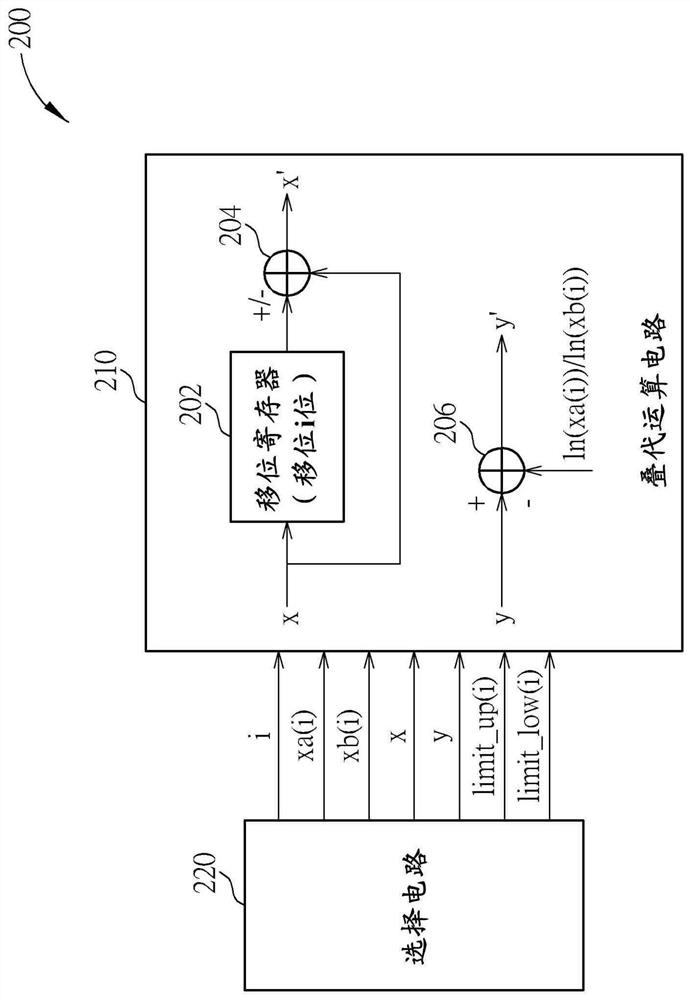

Logarithm calculation method and logarithm calculation circuit

PendingUS20210365239A1Simple circuit designLogarithmic/exponential functionsDigital data processing detailsAlgorithmLogit

Owner:REALTEK SEMICON CORP

Computation of logarithmic and exponential functions

InactiveUS20070174378A1Logarithmic/exponential functionsDigital function generatorsLogitComputer science

Owner:INTEL CORP

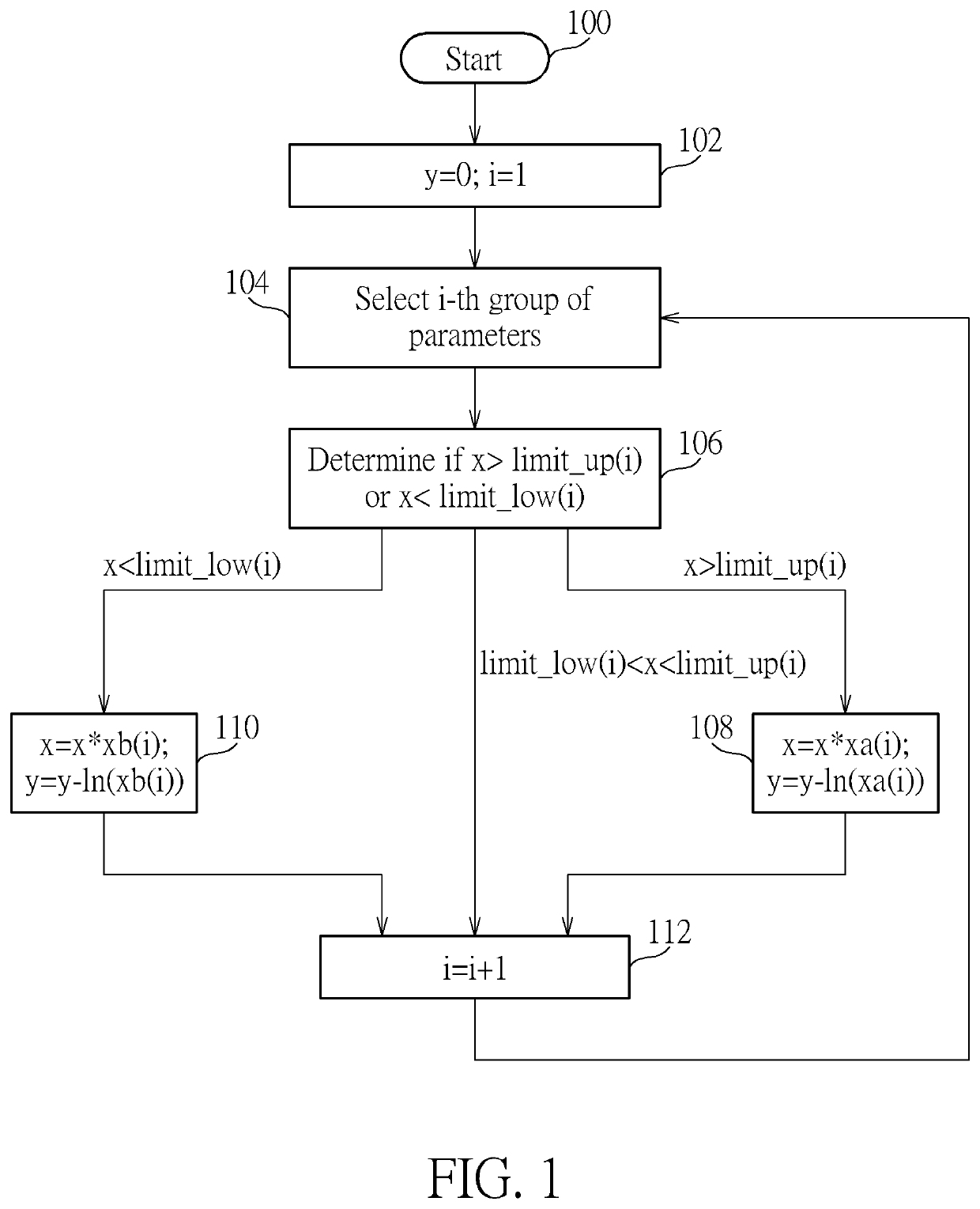

Calculation processor and calculation method

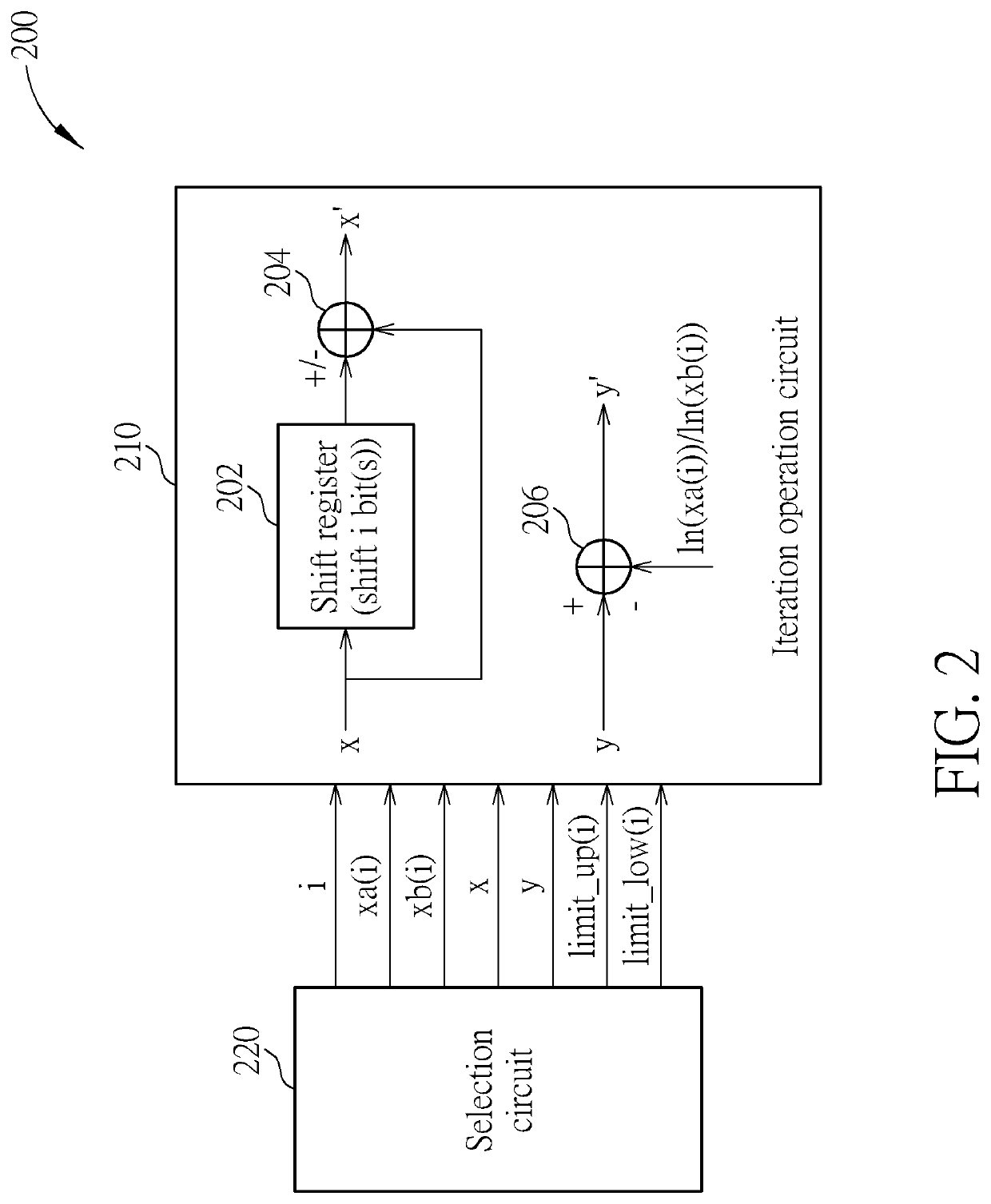

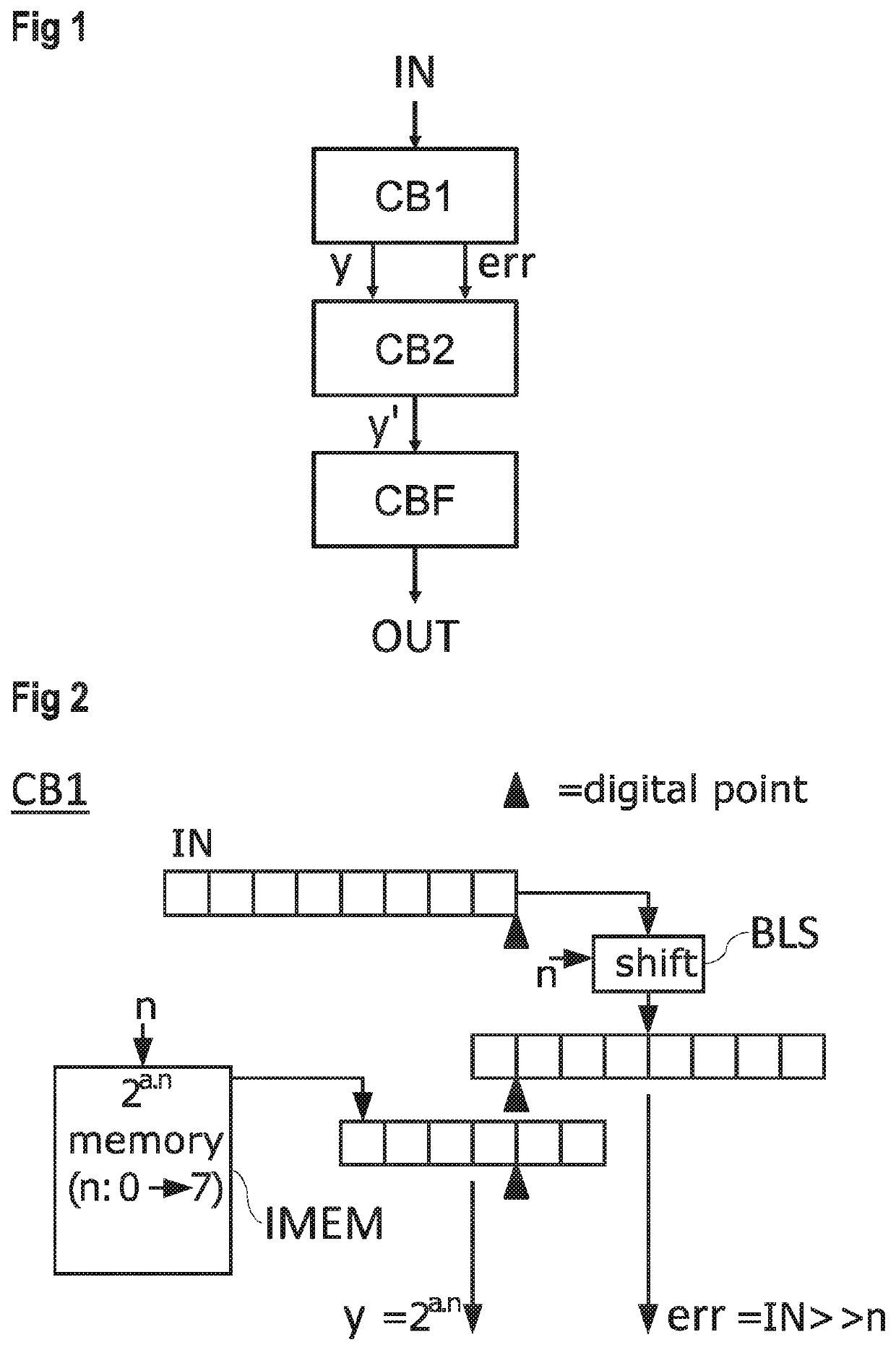

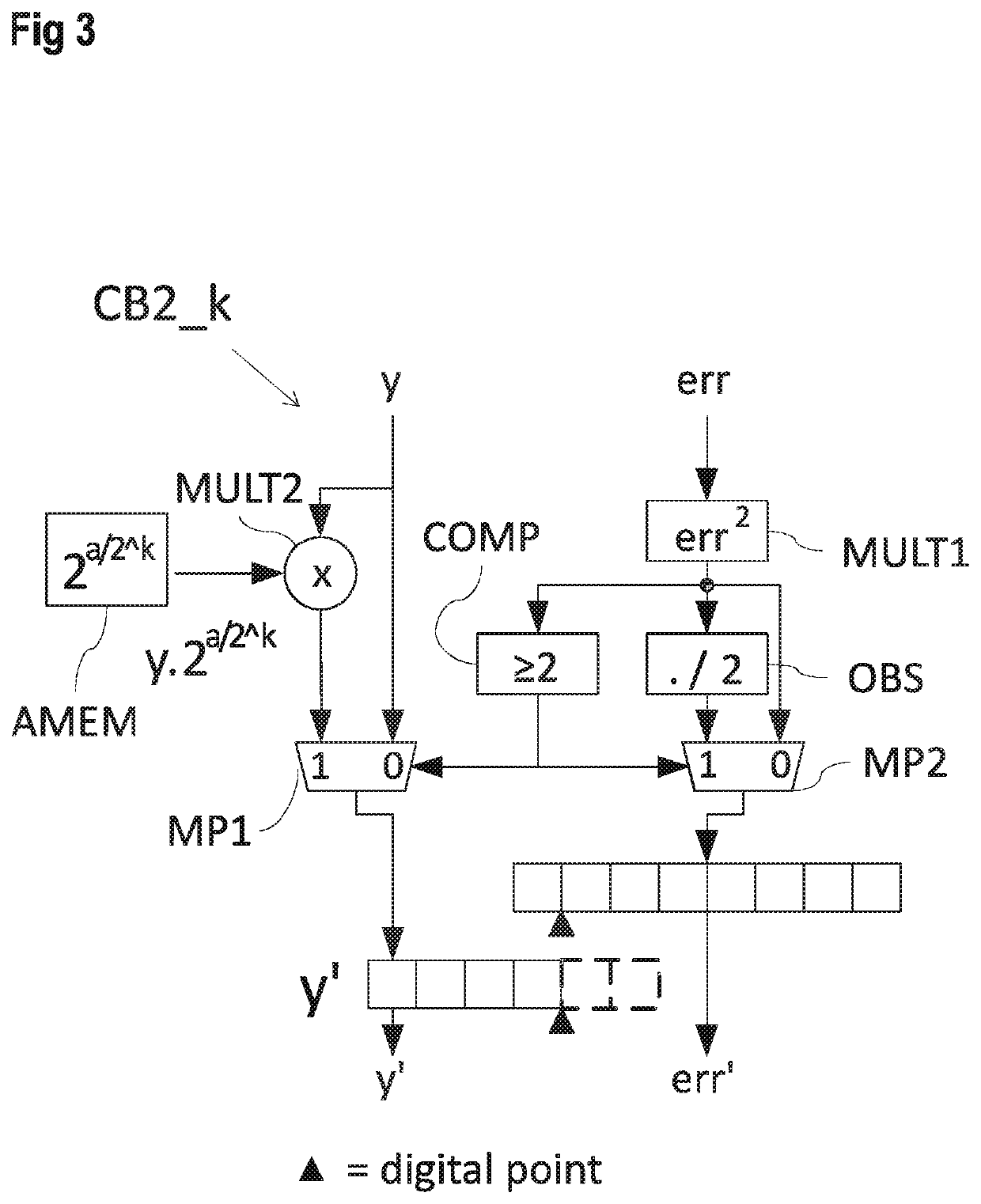

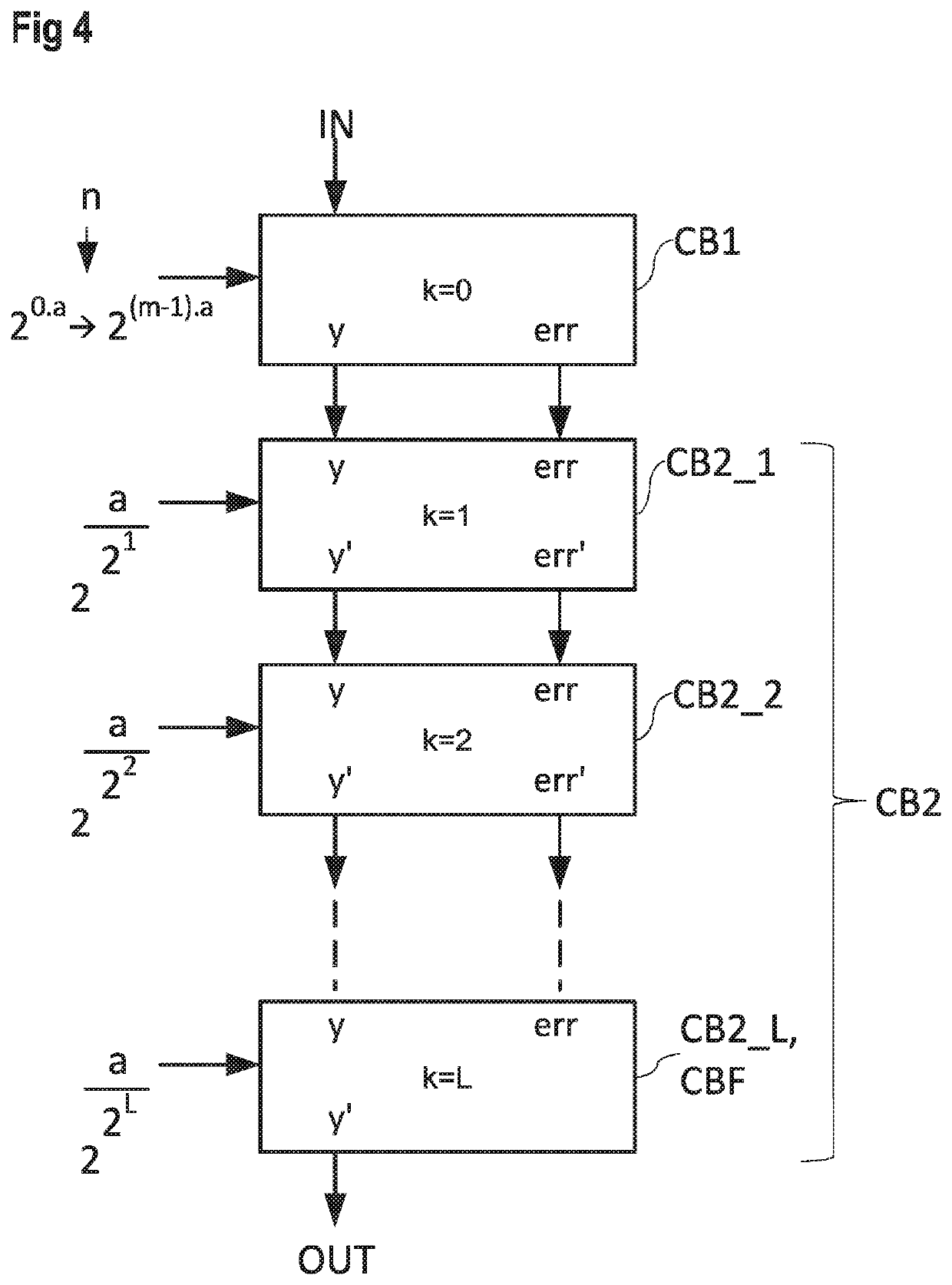

ActiveUS20210373853A1Easy to calculateLogarithmic/exponential functionsDigital data processing detailsAlgorithmDigital input

A calculation processor for determining a digital output value (OUT) from a digital input value (IN) based on an exponent value a, the processor comprising a first calculation block (CB1), a second calculation block (CB2) and a final calculation block (CBF). The first calculation block (CB1) initializes an intermediate value and an error value depending on a position of a Most Significant Bit of a significant part of the input value. The second calculation block is configured to perform repeatedly, until an exit criterion is fulfilled, the incrementation of a counter value, the determination of a power error value based on the error value and, if the power error value is larger than or equal to an error threshold, adjustment of the intermediate value y by multiplying the intermediate value with an adaptation value and setting the error value to the power error value divided by the base value. If the power error value is smaller than the error threshold, the error value is set to the power error value. The final calculation block is configured to set the output value to the intermediate value.

Owner:AMS AG

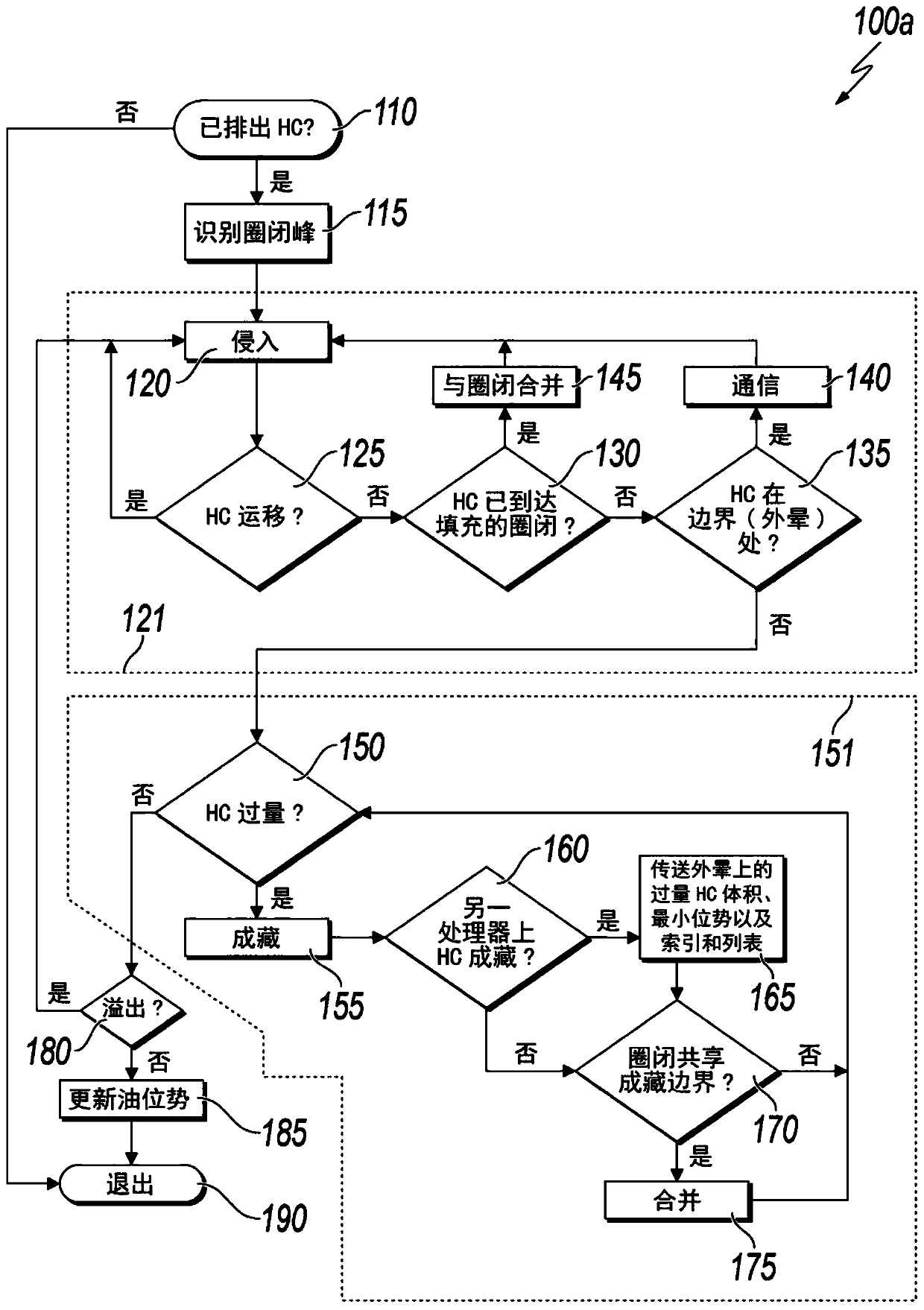

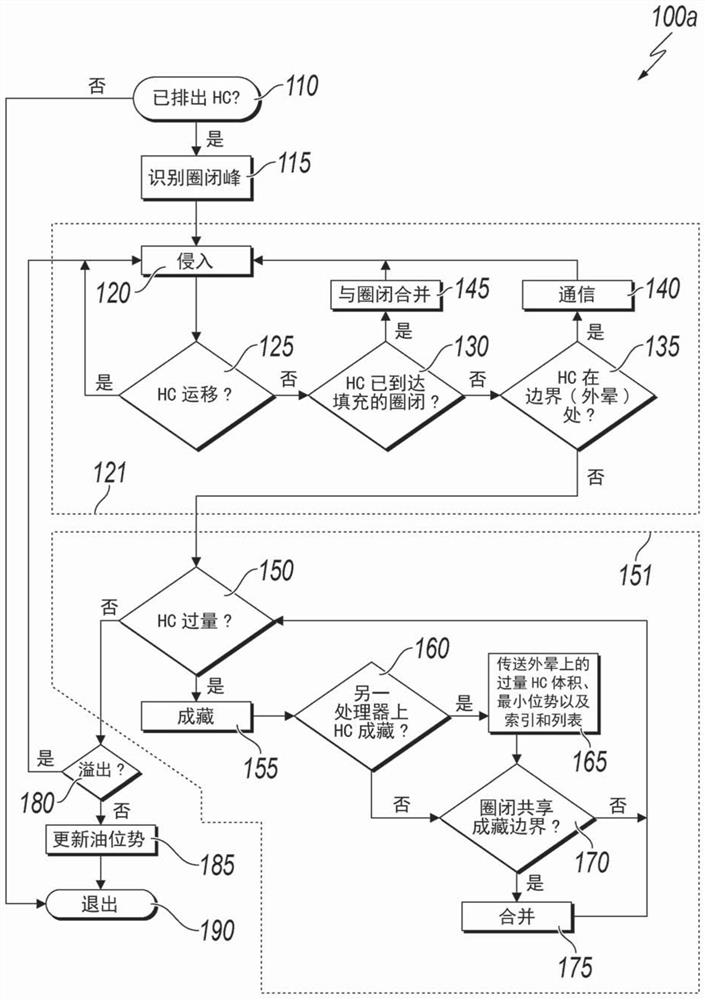

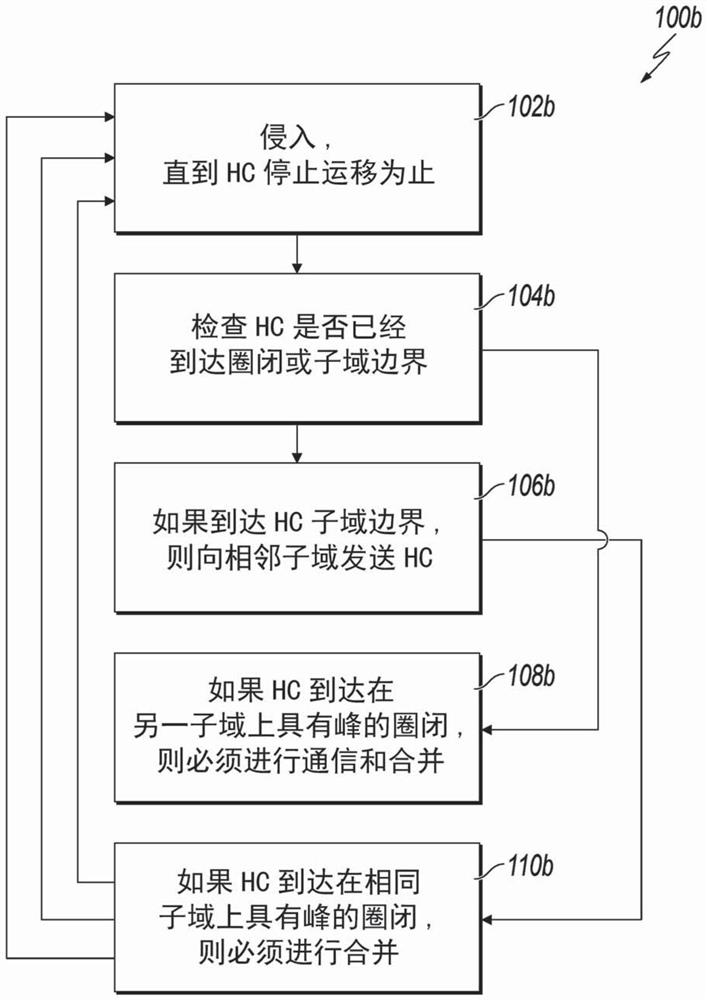

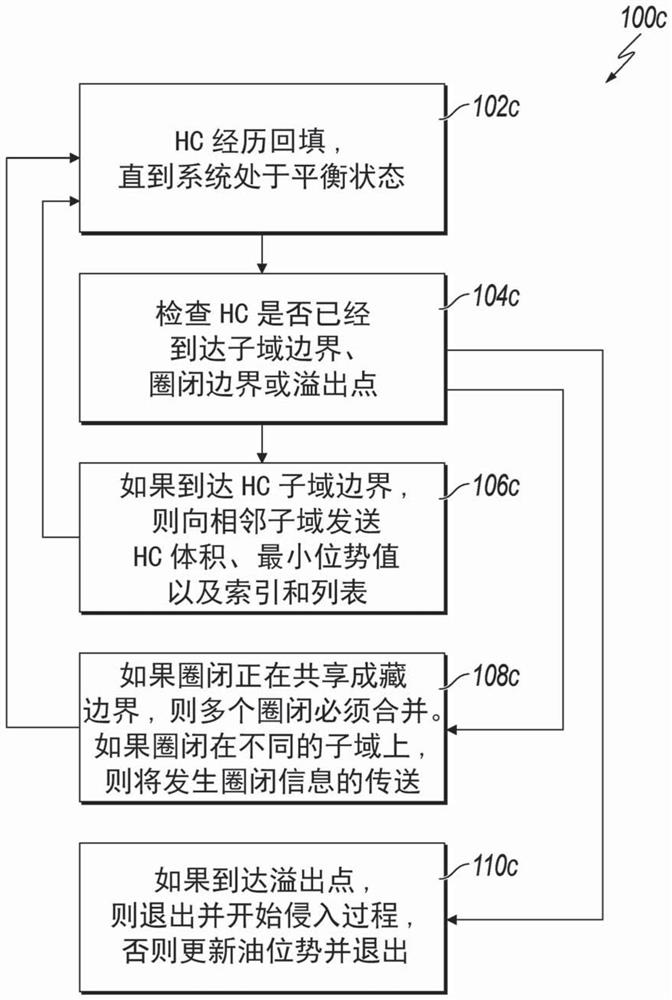

Parallel-processing of invasion percolation for large-scale, high-resolution simulation of secondary hydrocarbon migration

ActiveCN110998370ACapabilities for high-resolution migration simulationsImprove computing powerLogarithmic/exponential functionsSeismologySoil sciencePetroleum oil

A parallel-processing hydrocarbon (HC) migration and accumulation methodology is applied to basin data to determine migration pathways and traps for high-resolution petroleum system modeling. HC is determined in parallel to have been expelled in source rocks associated with a plurality of grid cells divided into one or more subdomains. Potential trap peaks are identified within the plurality of grid cells. An invasion percolation (IP) process is performed until the HC stops migrating upon arrival to the plurality of trap peaks. A determination is made as to whether the grid cells containing HCcontains an excess volume of HC. An accumulation process is performed to model the filling of the HC at a trap associated with the identified potential trap peaks. The trap boundary cell list is updated in parallel together with an HC potential value. Trap filling terminates when excess HC is depleted or a spill point is reached.

Owner:SAUDI ARABIAN OIL CO

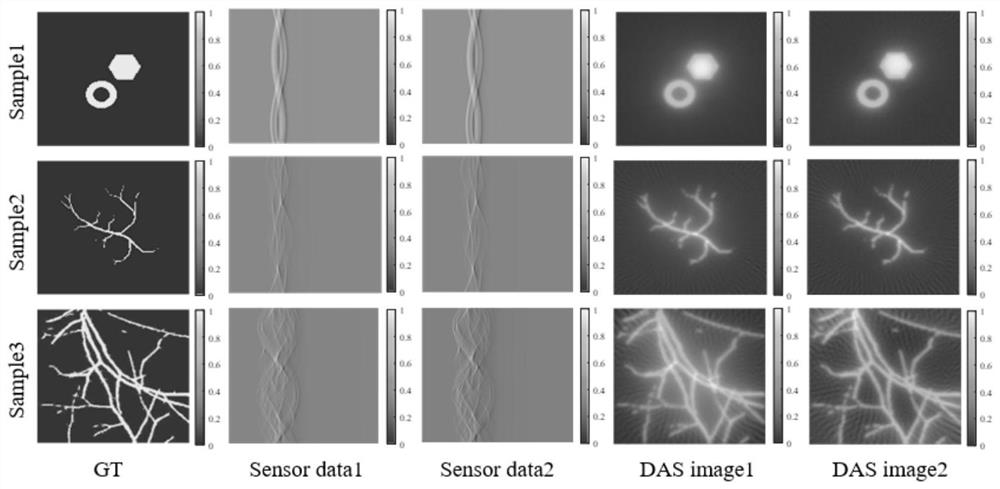

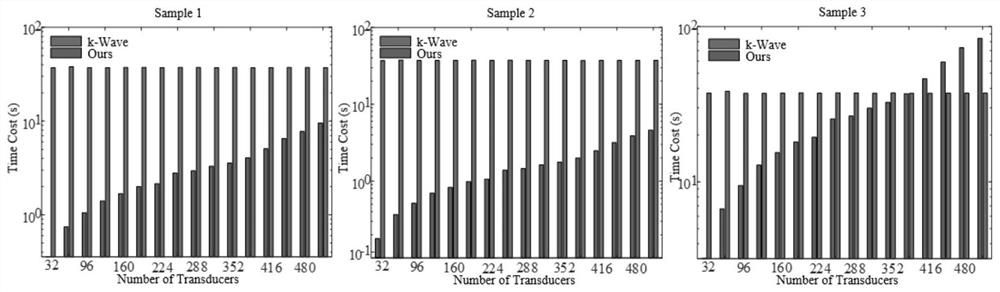

Photoacoustic effect simulation method based on sound wave superposition

ActiveCN112560274AReduce running timeLogarithmic/exponential functionsDiagnostic recording/measuringAcoustic wavePhoto acoustic

The invention discloses a photoacoustic effect simulation method based on sound wave superposition. According to the method, an initial pressure distribution grid is divided into a plurality of pixelpoints, photoacoustic signals independently generated by each pixel point are calculated respectively, and then the overall photoacoustic signals are calculated according to the wave superposition principle. According to the method provided by the invention, a complex photoacoustic equation is converted into simple cyclic superposition operation, so that the running time is greatly shortened. In most cases, the running time of the method provided by the invention is far shorter than the calculation time of k-Wave.

Owner:SHANGHAI TECH UNIV

Systems and methods for computing mathematical functions

ActiveUS9600236B2Logarithmic/exponential functionsReciprocal functionsTheoretical computer scienceComputational mathematics

Owner:VIVANTE CORPORATION

Logarithm calculation method and logarithm calculation circuit

PendingCN113721886ASimple designLogarithmic/exponential functionsDigital data processing detailsAlgorithmCalculation methods

Owner:REALTEK SEMICON CORP

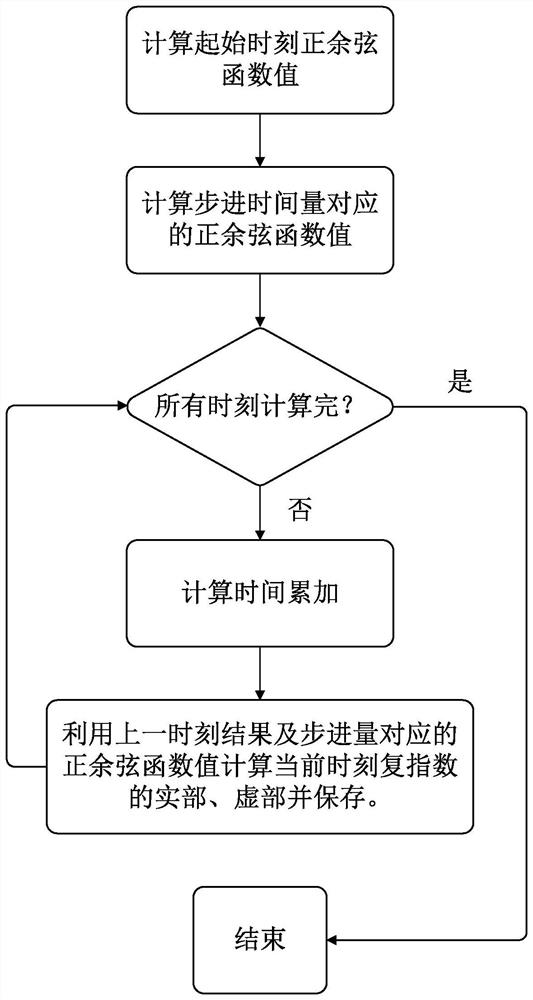

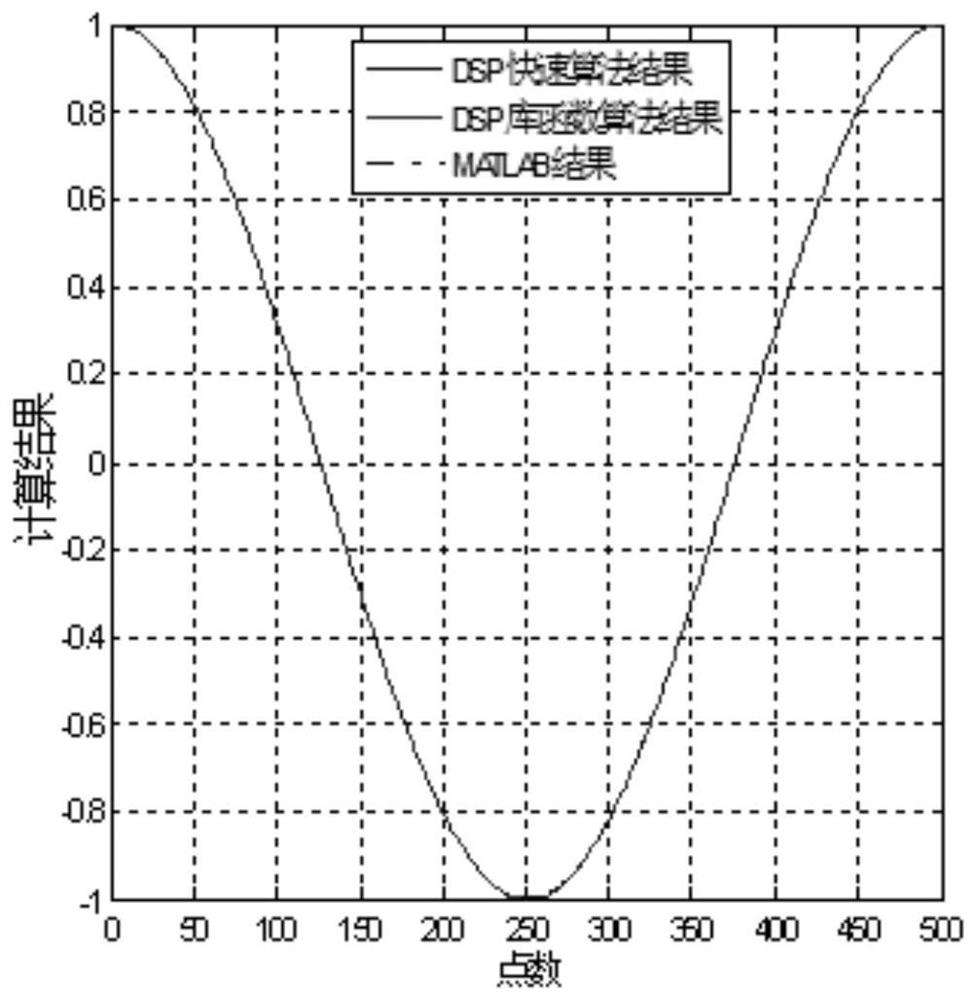

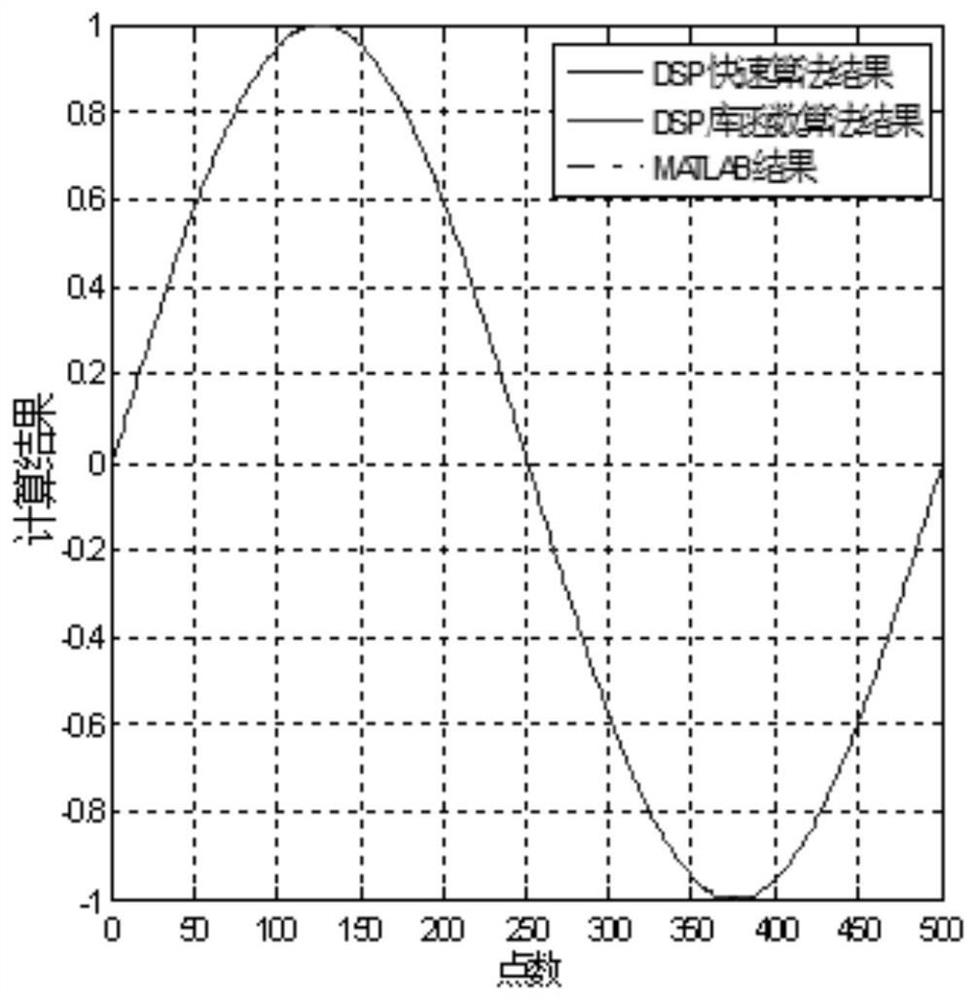

Digital frequency shift processing method based on DSP processing platform

PendingCN114063976AReduce lossesImprove computing efficiencyLogarithmic/exponential functionsDigital function generatorsControl engineeringFrequency shift

The embodiment of the invention relates to a digital frequency shift processing method based on a DSP processing platform. The digital frequency shift processing method based on the DSP processing platform comprises the following steps: calculating sine / cosine function values corresponding to a starting moment and a stepping moment to obtain complex index values corresponding to the starting moment and the stepping moment; and calculating the complex exponent value at the current moment by using the complex exponent value at the previous moment and the sine / cosine function value corresponding to the stepping quantity. According to the embodiment of the invention, because the precision loss caused by product and addition and subtraction is small, the complex complex exponent operation is converted into simple product and addition and subtraction operation, and the method can greatly improve the operation efficiency under the conditions that a large amount of storage space is not needed and the operation precision is ensured.

Owner:西安黄河机电有限公司

Parallel Processing of Invasive Seepage for Large-Scale High-Resolution Simulation of Secondary Oil and Gas Migration

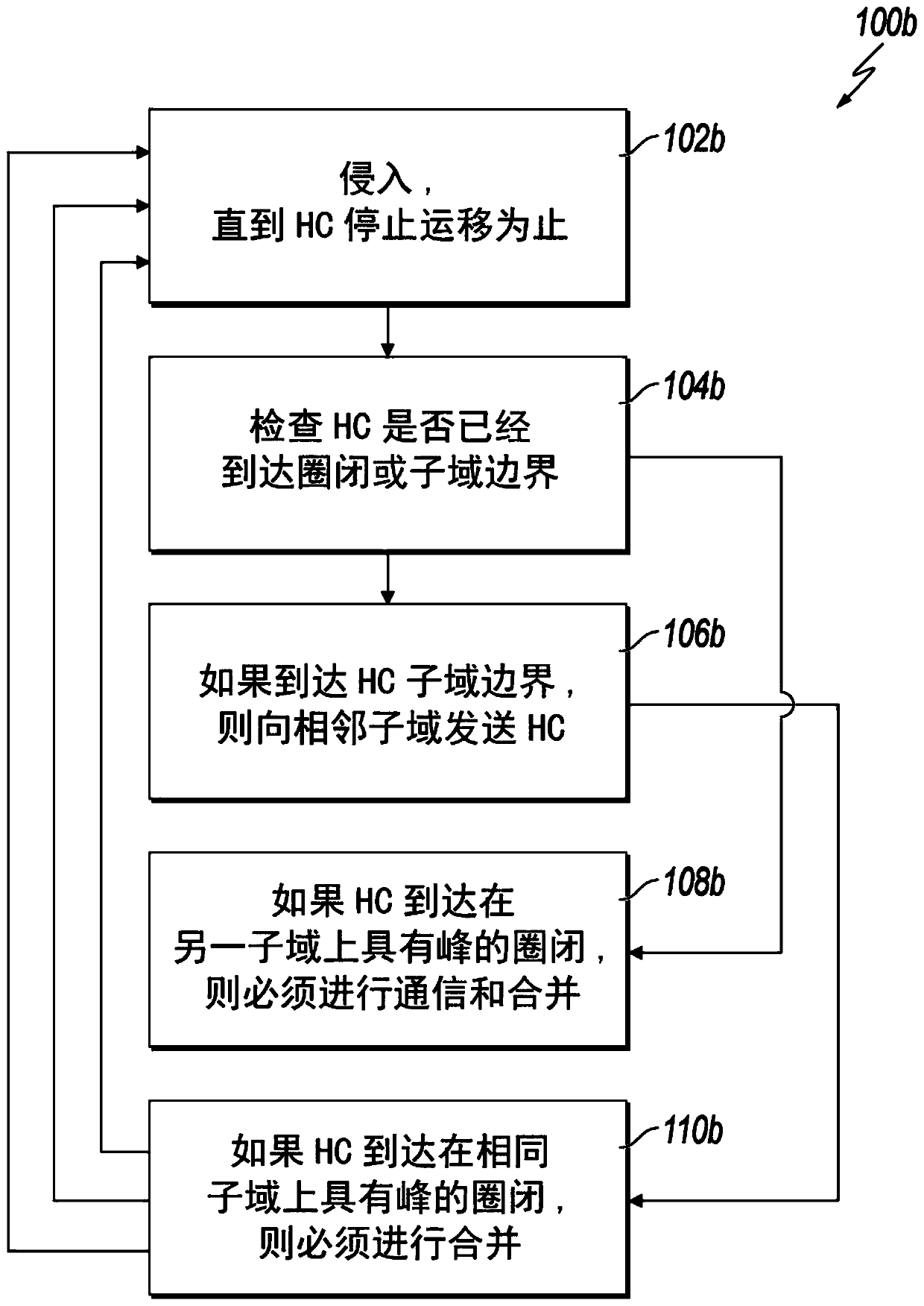

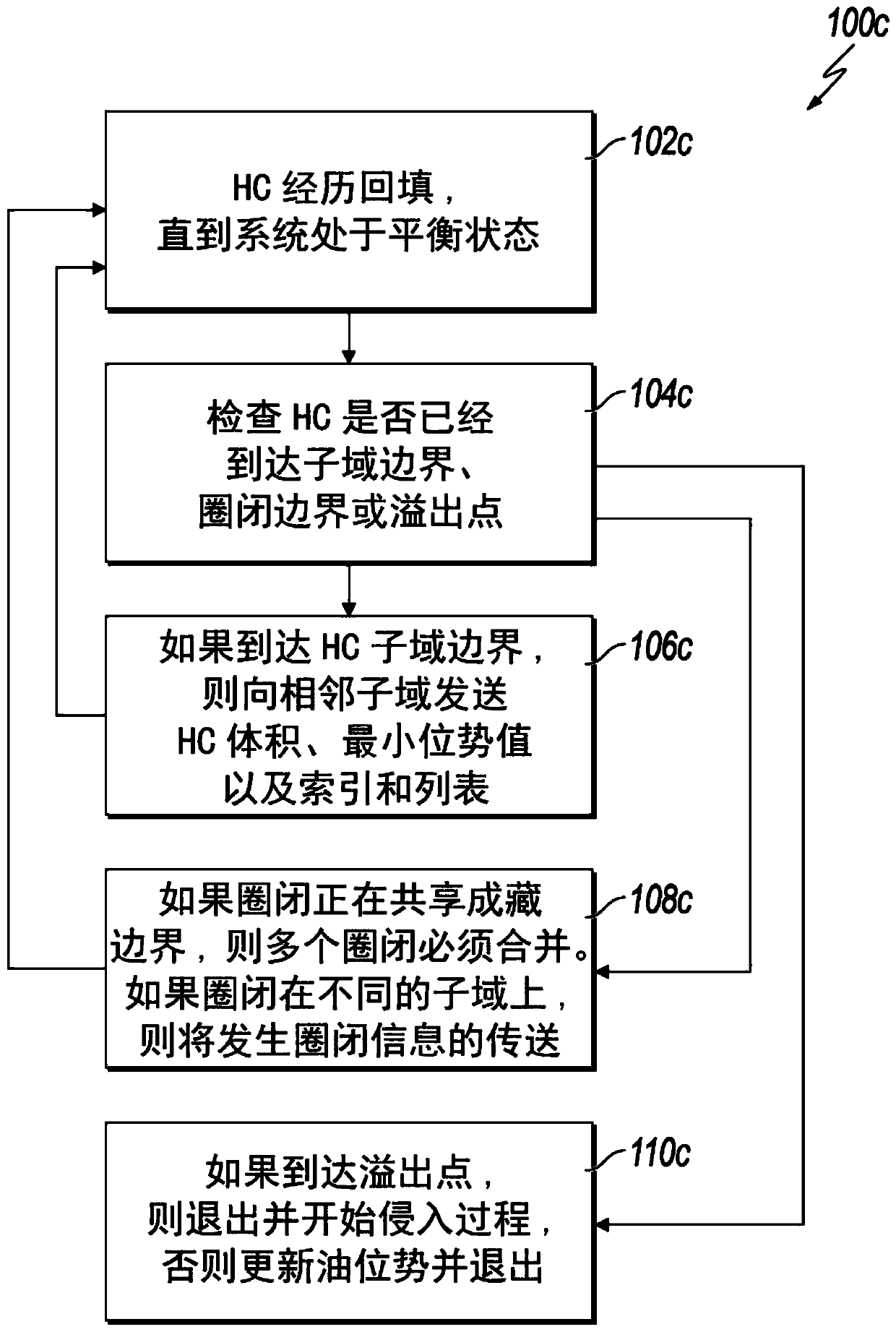

A parallel approach to hydrocarbon (HC) migration and accumulation is applied to basin data to determine migration paths and traps for high-resolution petroleum system modeling. In parallel, it is determined that HC has been drained from source rock associated with a plurality of grid cells divided into one or more subdomains. Identify potential trap peaks within multiple grid cells. An intrusive percolation (IP) process was performed until the HC ceased to migrate after reaching multiple trapped peaks. Determine if grid cells containing HC contain excess HC volume. The accumulation process is performed to model the filling of HC at the traps associated with the identified geopotential trap peaks. The list of trap boundary cells is updated together with the HC potential values in parallel. Trap filling was terminated when the excess HC was depleted or the overflow point was reached.

Owner:SAUDI ARABIAN OIL CO