A micron-scale single crystal copper interconnect structure and preparation method thereof

An interconnection structure, single crystal copper technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. Improve the electroplating process and other problems to achieve the effects of excellent electrical conductivity, guaranteed transmission performance, and elimination of contributions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] The preparation of the copper interconnect structure is simplified, and the most critical technology is to grow micron-scale single crystal copper needles from the phosphorous-containing copper seed layer. Other technologies are Damascus process, TSV process, and copper pillar bump process. normal operation. Therefore, the specific preparation operations are as follows:

[0045] (1) Use phosphorus-containing copper sheet instead of phosphorus-containing copper seed layer as the electroplating base. The phosphorous-containing copper sheet used is a commercial copper sheet produced by Kobelco Corporation of Japan, and contains 0.03 wt % of phosphorous.

[0046] (2) In the degreasing solution, the phosphorous copper sheet was cathode degreasing at a current density of 3ASD for 20 seconds, and rinsed with deionized water. The formula of degreasing liquid is 40g / L sodium hydroxide, 20g / L sodium carbonate, 1g / L sodium lauryl sulfate.

[0047] (3) The phosphor-containing co...

Embodiment 2

[0053] The difference between this embodiment and Embodiment 1 is that the sweep speed and interval are different, and the others are the same.

[0054] The specific differences are as follows: the scanning speed used in this embodiment is 1mV / s, and the scanning interval is 0.2-0.4V.

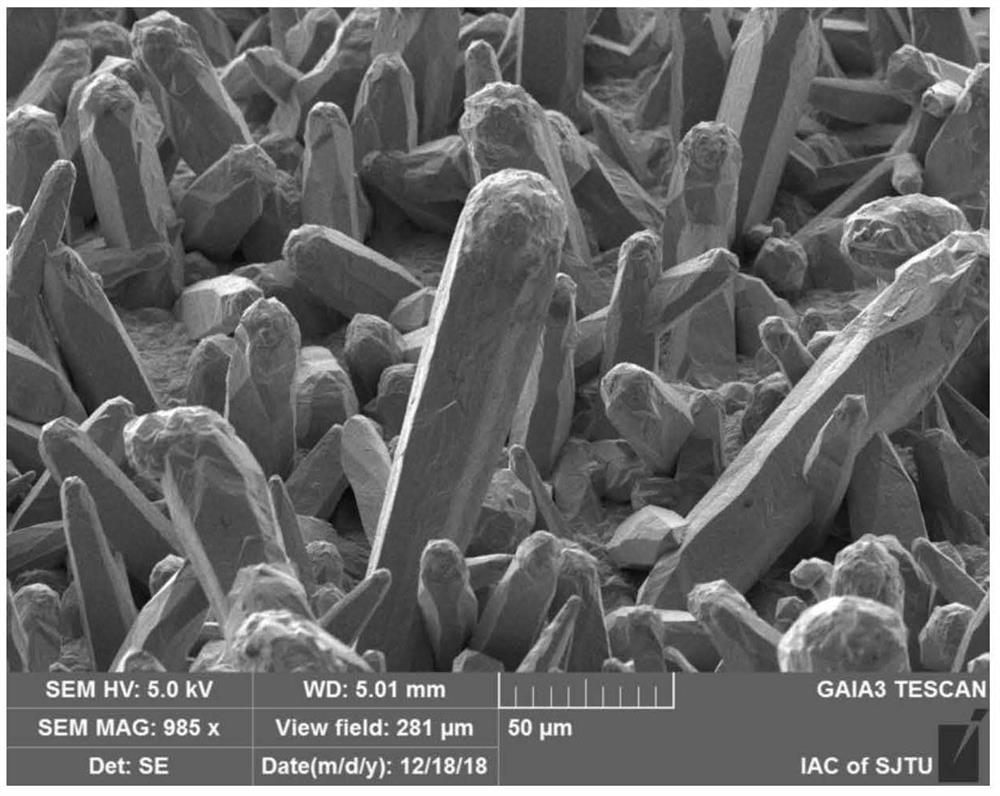

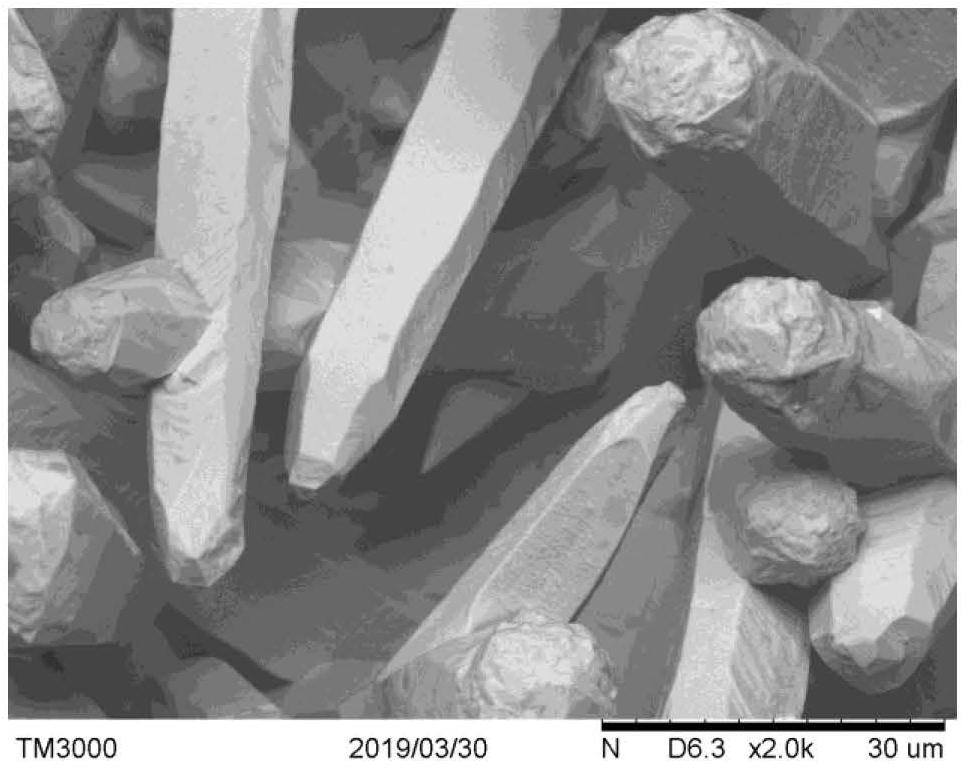

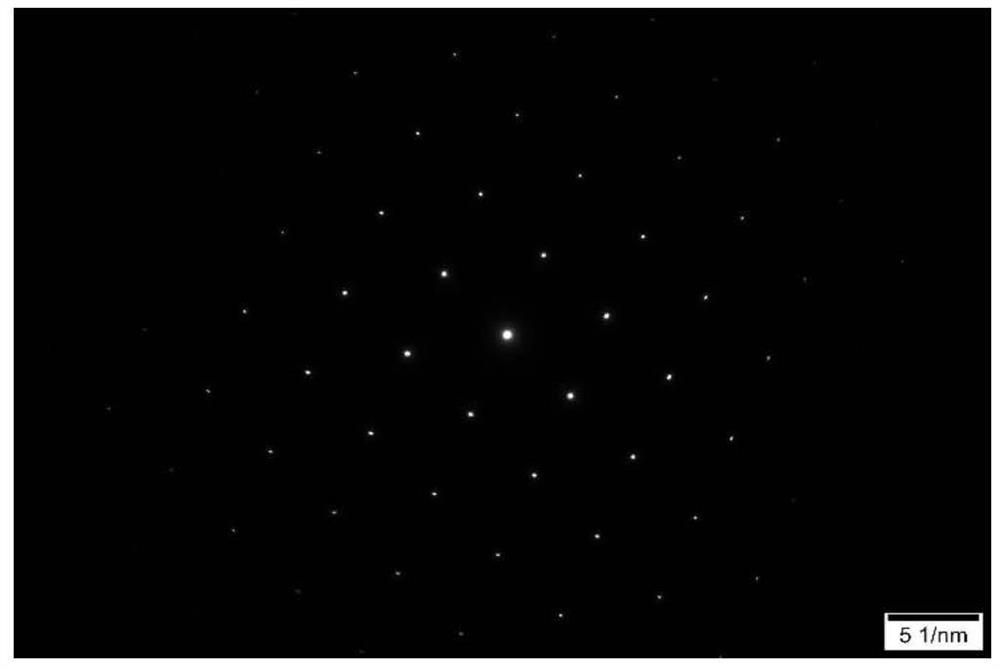

[0055] The resulting copper needles were longitudinally sectioned with FIB and imaged under FIB, as in Figure 4 shown. It can be seen that the width of the copper needle is 2-6 μm and the length is 5-25 μm. The color of the cross-section of a single copper needle is uniform and consistent, not as messy as the copper layer at the bottom, which can also indicate that the copper needle is a complete single crystal structure.

Embodiment 3

[0057] The present embodiment provides a method for preparing a micron-scale single-crystal copper interconnect structure using Damascus technology, including the following steps:

[0058] (1) Deposit a dielectric layer, the dielectric layer is a four-layer structure of silicon nitride-silicon oxide-silicon nitride-silicon oxide, located on the lower copper layer; A barrier layer is deposited by chemical vapor deposition on the inner sidewalls and bottoms of the through holes and trenches of the layer;

[0059] (2) The phosphorus-containing copper seed layer is deposited by the vacuum evaporation method with good deposition direction above the barrier layer parallel to the dielectric layer; the phosphorus content is about 0.03wt%;

[0060] (3) Pickling the phosphorous copper seed layer with dilute sulfuric acid with a volume fraction of 20% for 10s, and then applying a reverse current of 0.05A for 2000s to slightly dissolve the surface of the seed layer to ensure that the phos...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More