Silicon carbide epitaxial wafer and process for production thereof, silicon carbide bulk substrate for epitaxial growth purposes and process for production thereof, and heat treatment apparatus

一种热处理装置、制造方法的技术,应用在晶体生长、单晶生长、单晶生长等方向,能够解决自由度限制、晶片面均匀性降低、器件特性恶化等问题,达到良好生产性、平坦性好、缩短制作时间的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

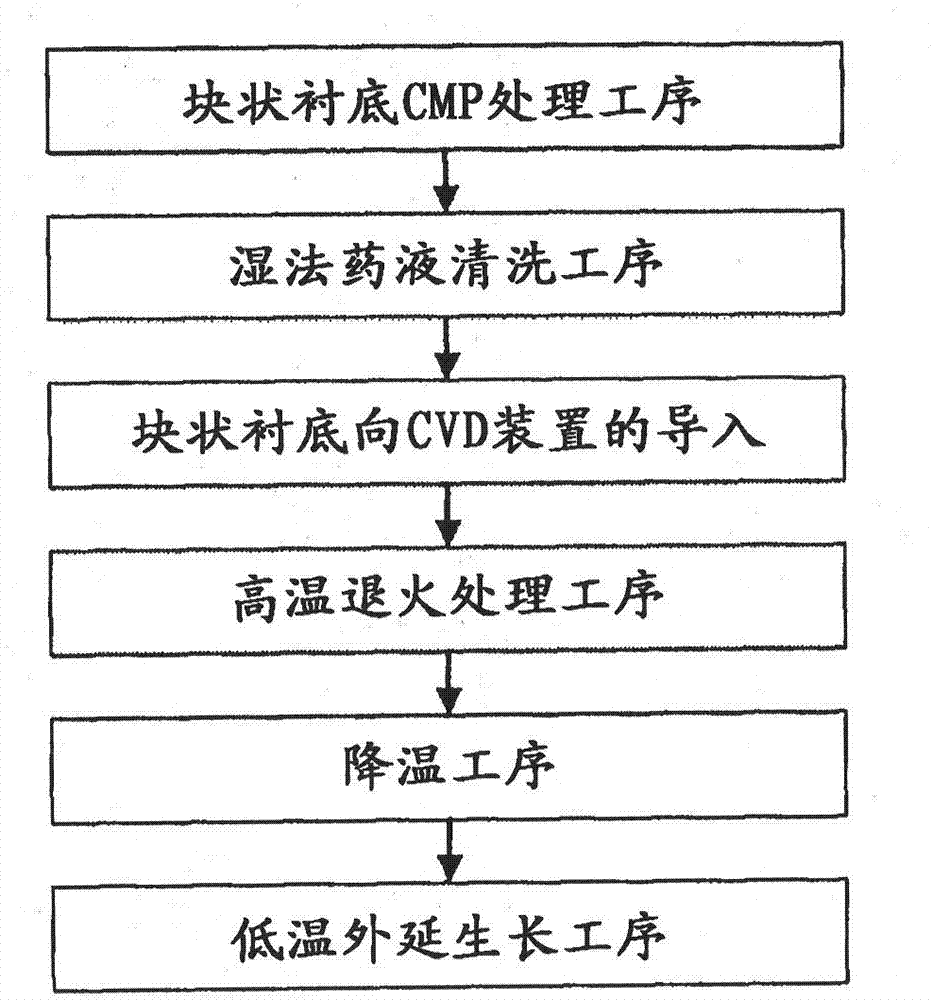

[0070] figure 1 It is a process flowchart showing the manufacturing procedure of the SiC epitaxial wafer in Embodiment 1 of the present invention.

[0071] The SiC bulk substrate used in the present invention is a 4H-SiC type substrate, which is inclined at an angle smaller than about 5 degrees from to the direction. In addition, the direction of inclination is not strictly limited to the direction, and a substrate of a specification that inclines in other directions may be used.

[0072] First, the SiC bulk substrate is planarized (CPM treatment) by preliminarily mechanical polishing and chemical mechanical polishing using an acidic or alkaline chemical solution. The planarized SiC bulk substrate is cleaned with ultrasonic waves using acetone or the like to remove organic substances adhering to the surface. Next, sulfuric acid and hydrogen peroxide aqueous solutions were mixed at a volume ratio of 5:1, and the SiC bulk substrate was immersed in the mixed solution heated ...

Embodiment approach 2

[0103] In the first embodiment, the annealing temperature dependence of the surface state of the SiC bulk substrate was described in detail. Generally, in the annealing treatment, the annealing temperature T1 and the treatment time t are important factors. That is, the above two parameters must be considered simultaneously for the effect of the annealing treatment on the wafer. In general, it can be said that the higher the annealing temperature T1 and the longer the treatment, the greater the degree of heat treatment. That is, the product of the annealing temperature T1 and the annealing time t, T1×t, directly indicates the degree of heat treatment. In addition, as described above, the experimental results in Table 1 also teach that the optimum treatment time t changes according to the annealing temperature T1. That is, as a principle, the higher the annealing temperature T1 and the shorter the processing time t, the defect density tends to decrease.

[0104] The treatment...

Embodiment approach 3

[0109] In Embodiment 1 and Embodiment 2, the annealing temperature dependence of the surface state of the epitaxial wafer, and the dependence of the defect density on the annealing temperature T1 and the annealing time t are described in detail. That is, a method for obtaining a high-quality epitaxial growth layer having a low defect density and good surface flatness has been described.

[0110] On the other hand, in an actual device, in addition to the aforementioned defect density and surface flatness, it is also important that the concentration of N-type residual impurities in the epitaxial growth layer be small as an index of high quality of the epitaxial wafer.

[0111] Here, "N-type residual impurities" refer to N-type impurities that are not desired to be contained in the epitaxial growth layer during epitaxial growth. N-type residual impurities are caused by, for example, nitrogen remaining in the air inside the CVD apparatus, gas discharged from a heat insulating mate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| annealing point | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More