Self-aligned double-layer channel metallic oxide thin film transistor and manufacturing method thereof

An oxide film and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of not being able to meet the requirements of data circuit driving, affecting device reliability and power consumption, and device off-state current change. Large and other problems, to reduce parasitic capacitance, achieve self-alignment, high on-state current effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

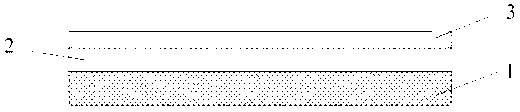

[0067] A specific example of the manufacturing method of the thin film transistor of the present invention is as follows Figure 1 to Figure 7 shown, including the following steps:

[0068] Such as figure 1 As shown, the substrate 1 used is a glass substrate or a flexible substrate, and a 60nm high-resistivity metal oxide semiconductor indium gallium zinc oxide (IGZO) film 2 is grown on the substrate by magnetron sputtering; A 5nm low-resistivity indium tin oxide film (ITO)3 was grown by sputtering.

[0069] Such as figure 2 As shown, the photoresist 4 is spin-coated, and the indium tin oxide and indium gallium zinc oxide thin films are photolithographically and etched; the photoresist 4 is removed by ultrasonication with acetone.

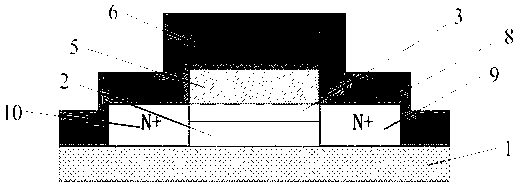

[0070] Such as image 3 As shown, on the low-resistivity indium tin oxide film 3, a layer of 200nm silicon oxide film 5 (that is, the gate dielectric layer) is deposited by plasma enhanced chemical vapor deposition (PECVD); then magnetron spu...

Embodiment 2

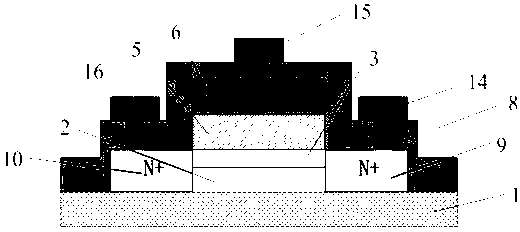

[0076] Another specific example of the manufacturing method of the thin film transistor of the present invention is as follows Figure 8 to Figure 14 shown, including the following steps:

[0077] Such as Figure 8 As shown, the substrate 1 used is a glass substrate, and a layer of 80nm high-resistivity metal oxide semiconductor indium gallium zinc oxide (IGZO) film 2 is grown on the substrate by magnetron sputtering; and then grown by magnetron sputtering A 15nm low-resistivity indium tin oxide film (ITO)3.

[0078] Such as Figure 9 As shown, the photoresist 4 is spin-coated, and the indium tin oxide and indium gallium zinc oxide thin films are photolithographically and etched; the photoresist 4 is removed by ultrasonication with acetone.

[0079] Such as Figure 10 As shown, a 300nm silicon oxide film 5 is deposited on the low-resistivity indium tin oxide film 3 by plasma enhanced chemical vapor deposition (PECVD); then a 300nm metal layer is grown by magnetron sputteri...

Embodiment 3

[0085] Another specific example of the manufacturing method of the thin film transistor of the present invention is as follows Figure 15 to Figure 22 shown, including the following steps:

[0086] Such as Figure 15 As shown, the substrate 1 used is a flexible substrate, and a layer of 100nm SiO is grown on the substrate 1 by plasma enhanced chemical vapor deposition (PECVD). 2 buffer layer 17.

[0087] Such as Figure 16 As shown, a layer of 40nm high-resistivity metal oxide semiconductor indium gallium zinc oxide (IGZO) film 2 is grown by magnetron sputtering on the substrate deposited with a buffer layer; then a layer of 5nm is grown by magnetron sputtering low-resistivity indium tin oxide (ITO) films 3 .

[0088] Such as Figure 17 As shown, the photoresist 4 is spin-coated, and the indium tin oxide and indium gallium zinc oxide thin films are photolithographically and etched; the photoresist 4 is removed by ultrasonication with acetone.

[0089] Such as Figure 18...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More