Capacitance structure and preparation method of a hybrid nanocrystalline memory

A nanocrystal and memory technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., to achieve the effects of inhibiting chemical reactions, good chemical stability and thermal stability, and improving storage density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

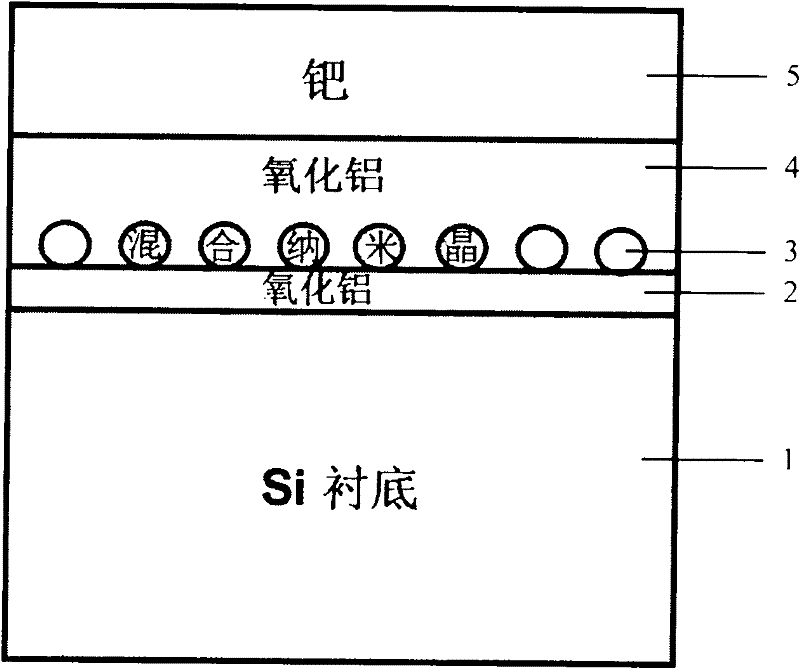

[0036] The following is an example of preparing ruthenium and ruthenium oxide mixed nanocrystal storage capacitors by adopting the storage capacitor structure and preparation method provided by the present invention.

[0037] A P-type single crystal silicon chip with (100) crystal orientation is used as a substrate, and the resistivity of the silicon chip is 8-12 ohm·cm. After the silicon wafer has undergone standard cleaning, it is placed in an atomic layer deposition system, and then the surface of the silicon wafer is modified with trimethylaluminum gas for 60 minutes at a temperature of 300°C. Al was then grown by atomic layer deposition 2 o 3 Nano film as tunneling layer, Al 2 o 3 The thickness is 9 nm. Next, magnetron sputtering a ruthenium metal film with a thickness of 2 nanometers on the tunneling layer, and then rapid thermal annealing at 800° C. for 30 seconds in a mixed atmosphere of nitrogen and trace oxygen to form mixed nanocrystals of ruthenium and rutheniu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More