Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the field of microelectronics, can solve the problems that ordinary lithography machines cannot meet the process requirements and increase the difficulty of lithography process, and achieve the effects of improving electric field distribution, reducing electrode size, and increasing breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

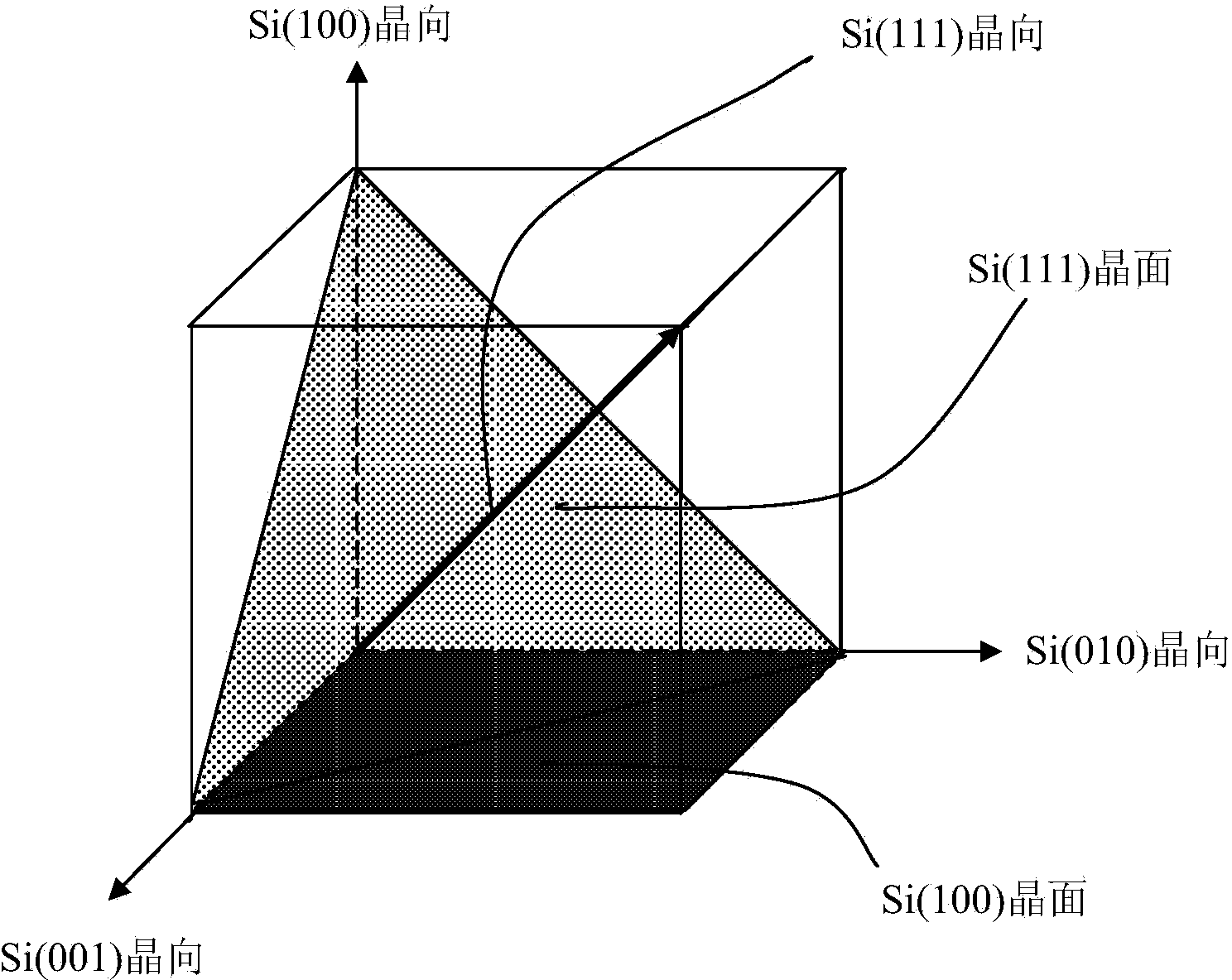

[0069] As shown in Figure 2 (a), the semiconductor device includes: a substrate 1; a gallium nitride semiconductor layer 2 on the substrate 1; an additional layer 3 of silicon semiconductor on the semiconductor layer 2; A groove formed by etching; an electrode 4 formed at the groove. In this embodiment, the substrate 1 may be silicon, silicon carbide, germanium, silicon-on-sapphire or sapphire. In this embodiment, the semiconductor device can be a Schottky diode, or a metal insulator field effect transistor (MISFET), including a metal oxide field effect transistor (MOSFET), or a metal semiconductor field effect transistor (MESFET), high Electron Mobility Transistor (HEMT) or Heterojunction Field Effect Transistor (HFET). In this embodiment, the semiconductor layer may be any one or a combination of silicon, germanium, gallium arsenide, gallium nitride, aluminum nitride, aluminum gallium nitride, and aluminum gallium indium nitrogen.

[0070] Such as Figure 2(b) , 2(c) , 2...

Embodiment 2

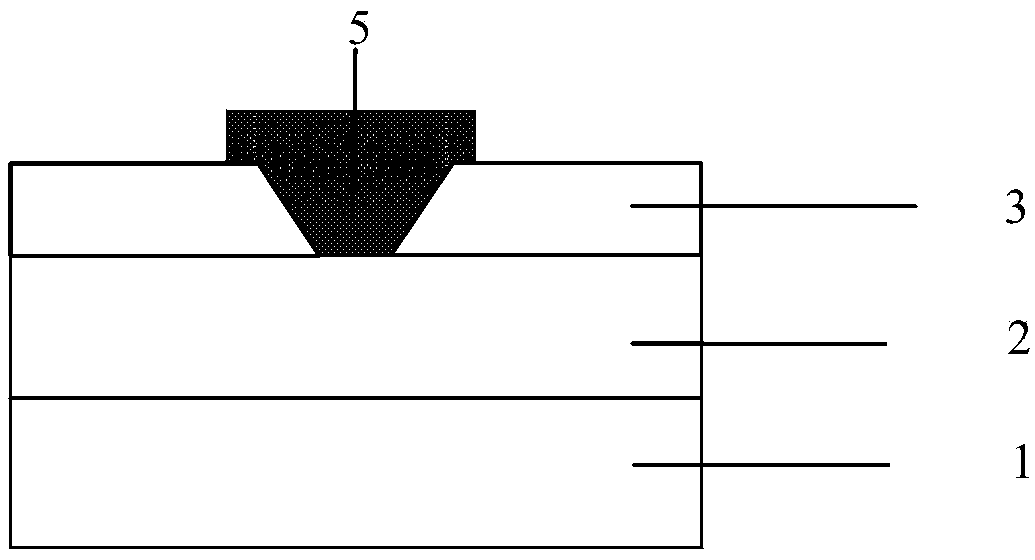

[0073] The semiconductor device includes: a substrate 1 , a semiconductor layer 2 , a passivation layer 3 , an additional layer 4 and an electrode 5 . This implementation mode is different from Example 1 in that a passivation dielectric layer 3 is added between the semiconductor layer 2 and the additional layer 4 . The passivation dielectric layer 3 may comprise one or a combination of silicon nitride, silicon germanium nitrogen, silicon aluminum gallium nitrogen, silicon aluminum oxide, aluminum magnesium oxygen nitrogen, silicon aluminum nitrogen and silicon dioxide.

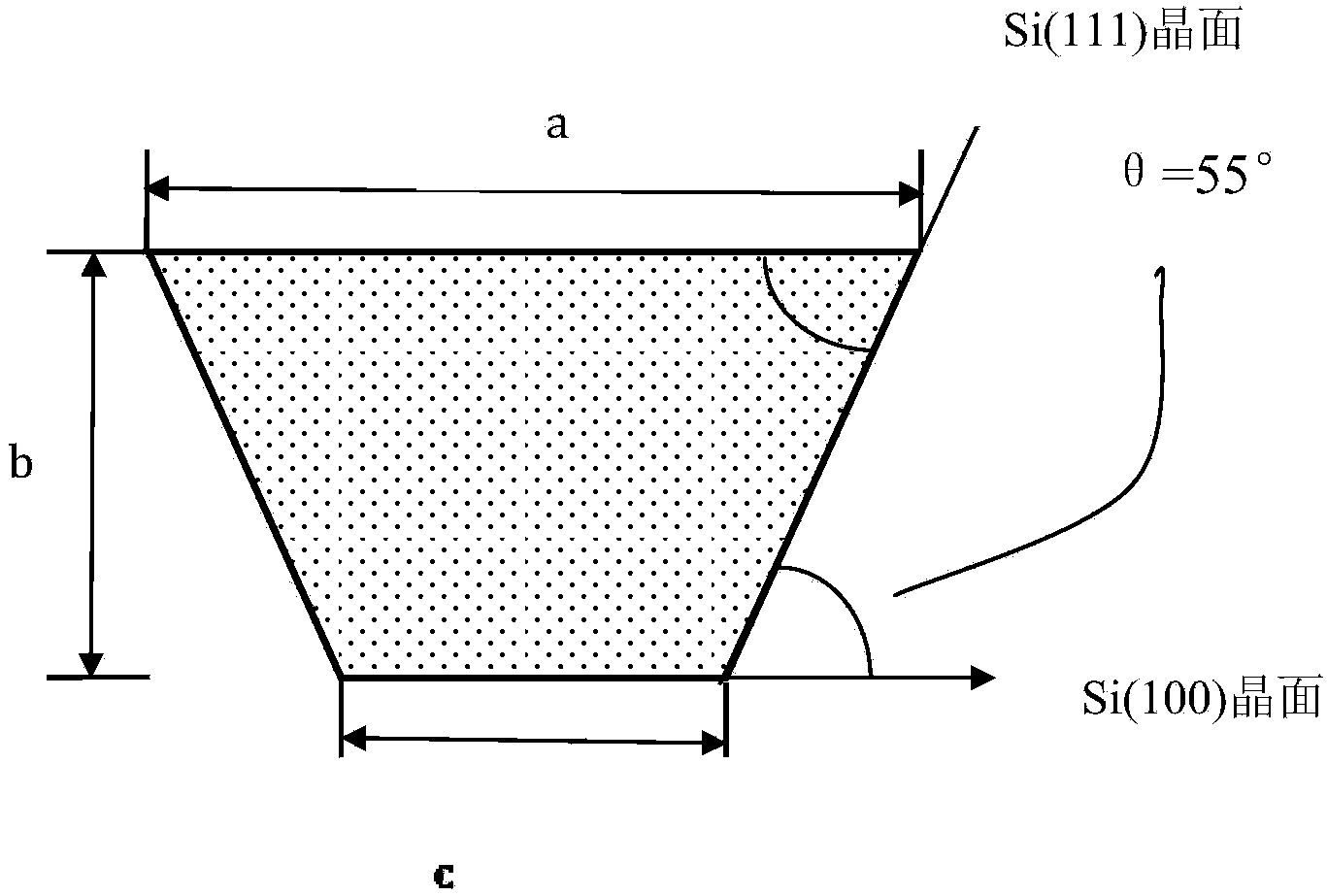

[0074] As shown in Figure 3(a), Figure 3(b), Figure 3(c) and Figure 3(d), after forming an inverted trapezoidal electrode groove by etching the additional layer 4, that is, the silicon (100) thin film semiconductor layer, The size of the electrode groove can be greatly reduced. Then, by etching the silicon nitride passivation layer 3 below the trapezoidal groove, the groove of the silicon nitride layer 3 form...

Embodiment 3

[0076] The semiconductor device includes: a substrate 1 , a semiconductor layer 2 , a passivation layer 3 , an additional layer 4 and an electrode 5 . Compared with Example 2, the difference of this embodiment is that, as Figure 4 As shown, a passivation dielectric layer 3 is added between the active semiconductor layer 2 and the silicon additional layer 4, and after the electrode metal with improved structure is formed in the electrode groove, the silicon additional layer 4 is oxidized to form a silicon dioxide layer 4, and The silicon additional layer 4 is not removed. In this way, a silicon dioxide layer 4 can be added on the passivation layer 3 to function as a dielectric layer and a protective layer. The passivation dielectric layer 3 may comprise one or a combination of silicon nitride, silicon germanium nitrogen, silicon aluminum gallium nitrogen, silicon aluminum oxide, aluminum magnesium oxygen nitrogen, silicon aluminum nitrogen and silicon dioxide. Other structur...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More