Germanium-painting structure for insulating layer of mixed graphical monocrystaline silicon as well as method and application thereof

A technology of germanium and single crystal silicon on the insulating layer, which is applied in the field of microelectronics, can solve the problems of large leakage current, small band gap, and difficulty in obtaining high-quality single crystal germanium compared with silicon, so as to reduce leakage current and improve work efficiency. Speed, the effect of promoting optoelectronic integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0018] Embodiment 1: The preparation method of low-temperature GeOI structure film.

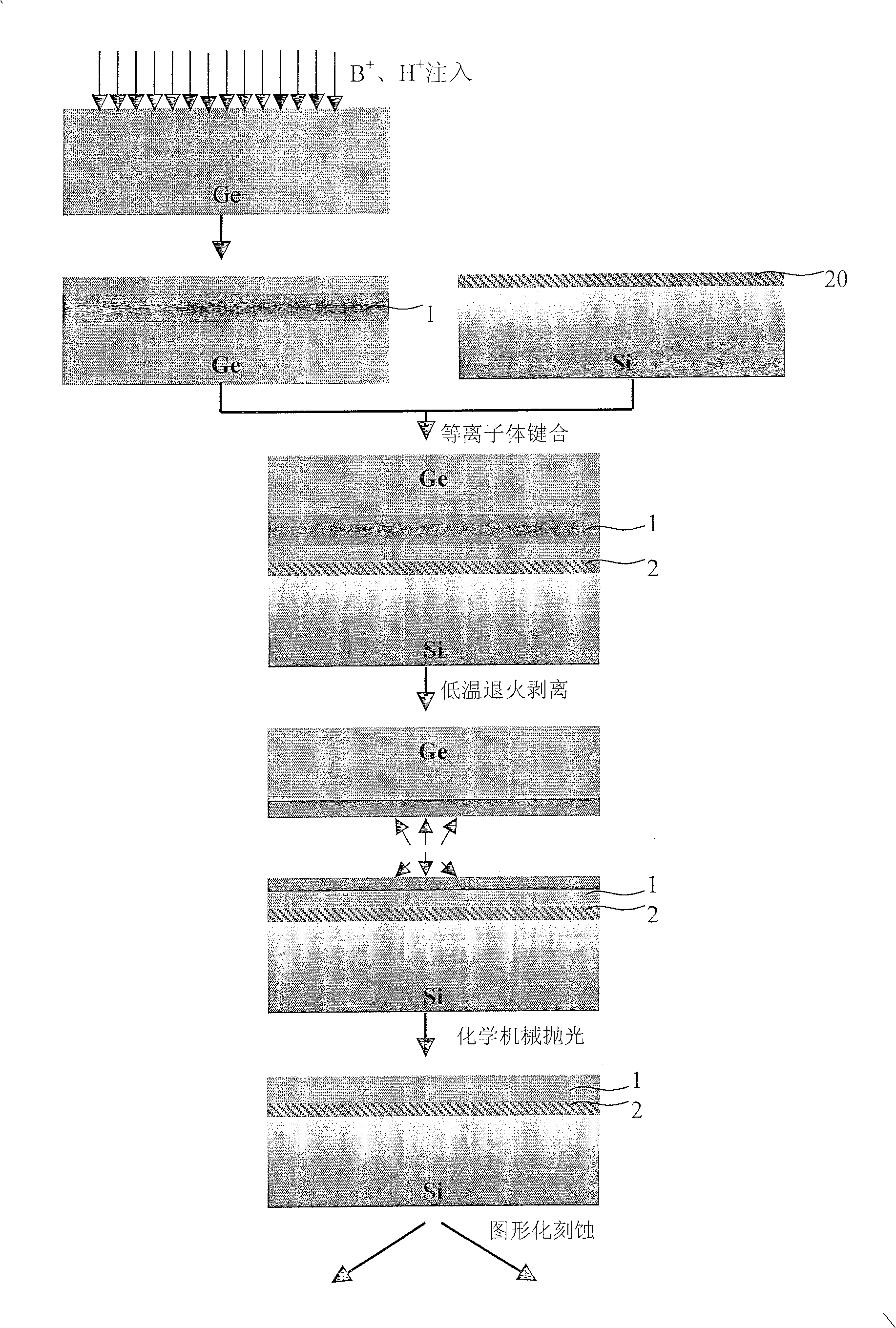

[0019] The steps are shown in Figure 1:

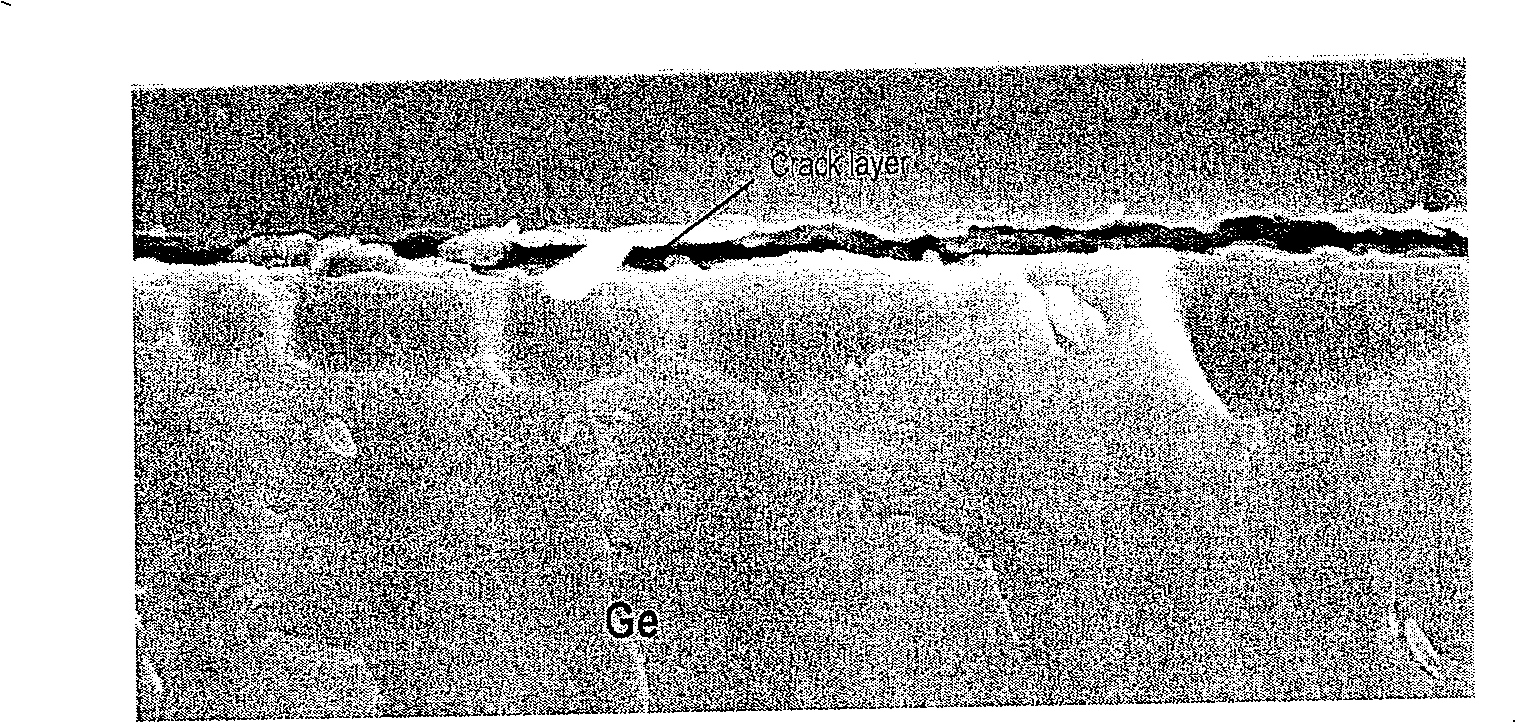

[0020] 1. Boron ion, hydrogen ion implantation: Firstly, the dose is implanted on the germanium wafer with a dose of 5×10 15 cm -2 of boron ions, and then implanted 5×10 16 cm -2 Hydrogen ions, 10 are defect layers caused by co-implantation of boron ions and hydrogen ions into germanium wafers.

[0021] 2. Plasma bonding: chemically clean the silicon wafer covered with silicon dioxide film and the germanium wafer implanted with perboron hydride ions to remove surface sticking dirt, and then activate the surface with low-temperature nitrogen plasma after drying. The nitrogen plasma activation conditions are: air pressure 0.4 mbar, plasma power 100W, high-purity nitrogen gas flow rate 80 sccm. After activation, rinse with deionized water for 6 seconds, rinse with megasonic water for 6 seconds and then spin dry, then bond the two pieces face to face...

Embodiment 2

[0024]Embodiment 2: A method for preparing a GeOI structure of mixed patterned single crystal silicon.

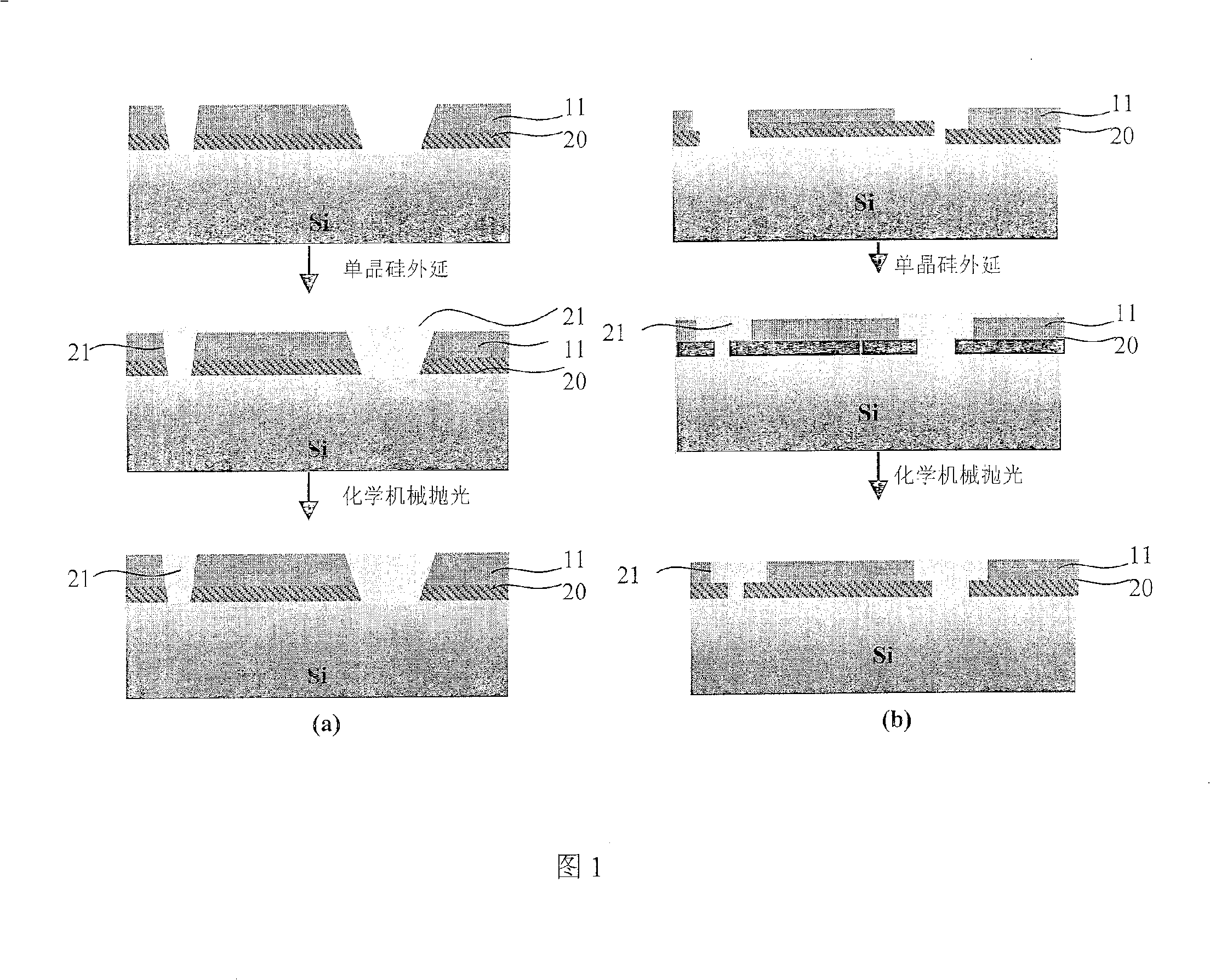

[0025] 1. Pattern the germanium (GeOI) thin film on the insulating layer obtained in Example 1 according to the requirements, and use the same window mask to etch the top layer of germanium and the lower oxide layer. Reactive ion etching or wet etching is used to remove the top germanium layer and the underlying silicon dioxide insulating buried layer to expose the patterned bottom substrate (100) silicon.

[0026] 2. Use ultra-high vacuum chemical vapor deposition (UHVCVD) to perform epitaxy on the etched window to obtain a GeOI structure containing patterned silicon, in which the single crystal silicon is in the (100) crystal orientation.

[0027] 3. Use CMP to remove the excess epitaxial silicon and silicon dioxide protective layer on the top layer of germanium, and polish the surface, finally as shown in Figure 1(a).

Embodiment 3

[0028] Embodiment 3: GeOI structures of different insulating buried layers and preparation of silicon on patterned insulating layers with different crystal orientations.

[0029] 1. In embodiment 1, can select to deposit the substrate silicon chip of different insulating buried layers, as silicon nitride, aluminum nitride, a kind of of aluminum oxide or diamond-like carbon, or the compound structure that is formed by them to improve buried layer thermal conductivity. The crystal orientation of the substrate silicon wafer determines the crystal orientation of the epitaxial silicon, which can be (110) or (100). (100) substrates can be selected for electron-type working devices on patterned silicon, and (110) substrates can be selected for hole-type working devices.

[0030] 2. Similar to the method of embodiment 2, the germanium (GeOI) film on the insulating layer obtained in embodiment 1 is subjected to patterning photolithography according to requirements, and the window of e...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More