Patents

Literature

120 results about "Bit interleaved coded modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

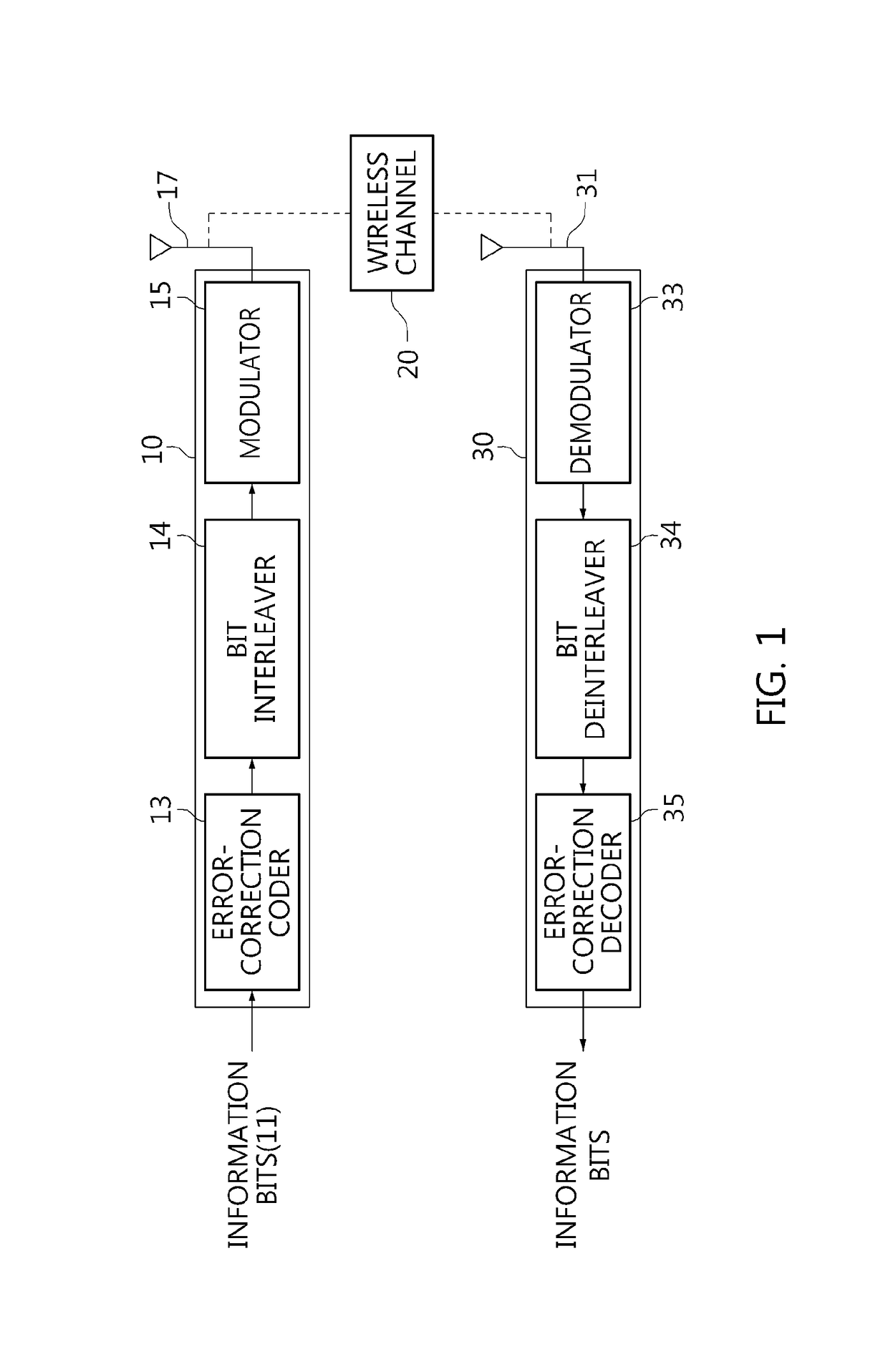

Apparatus and method for transmitting bit-interleaved coded modulation signals in an orthogonal frequency division multiplexing system

InactiveUS20060250944A1Improve overall utilizationReduce complexityModulated-carrier systemsOrthogonal multiplexBit interleaved coded modulationModulation order

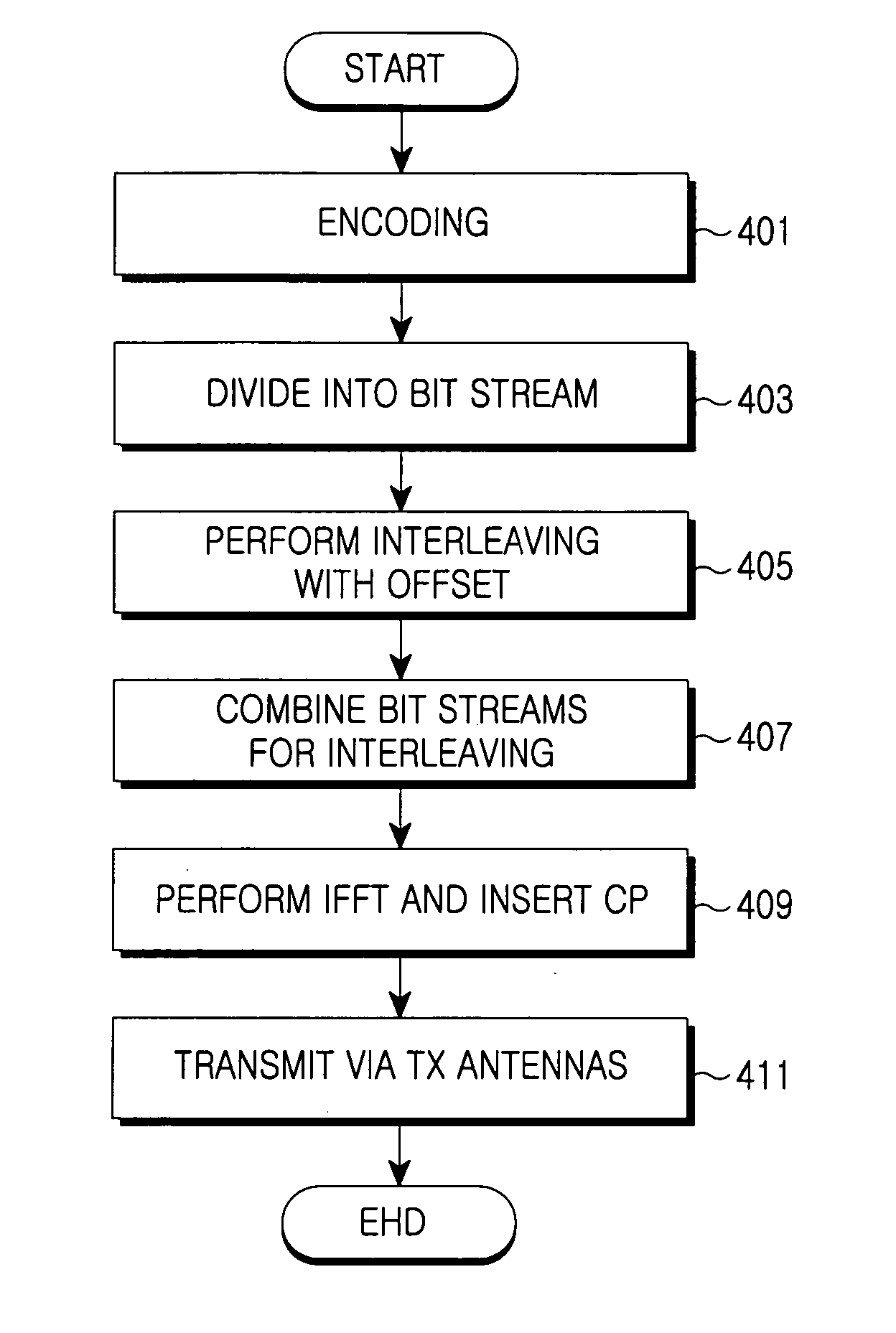

Disclosed is an apparatus for transmitting a bit-interleaved coded modulation (BICM) signal in an orthogonal frequency division multiplexing (OFDM) system. A serial-to-parallel (S / P) converter generates bit streams using coded bits according to the number of transmission antennas and a modulation order of a predetermined modulation scheme. An interleaver applies at least one offset to the bit streams and performs interleaving on the offset-applied bit streams. A combiner combines the interleaved bit streams according to the number of transmission antennas.

Owner:SAMSUNG ELECTRONICS CO LTD

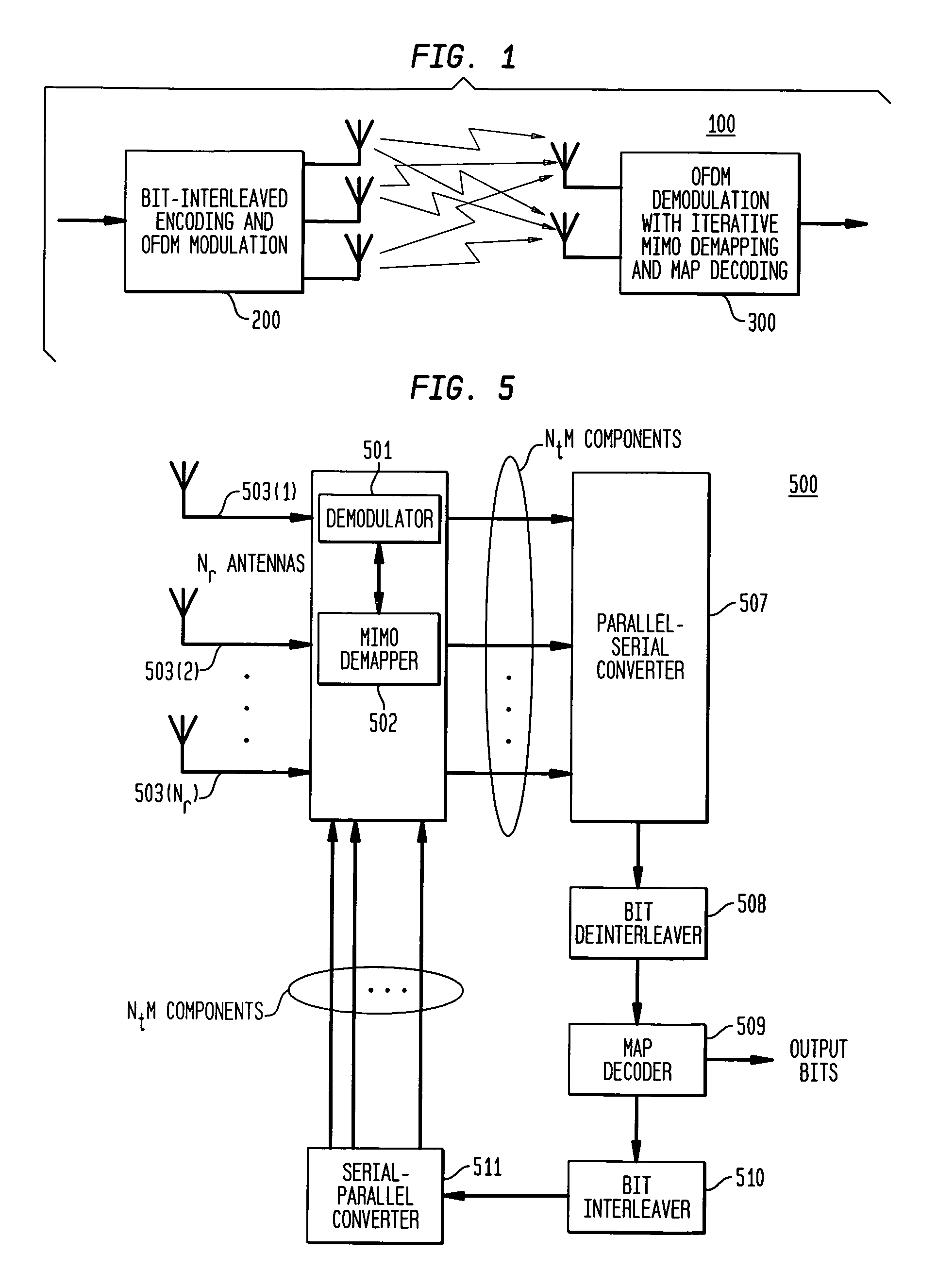

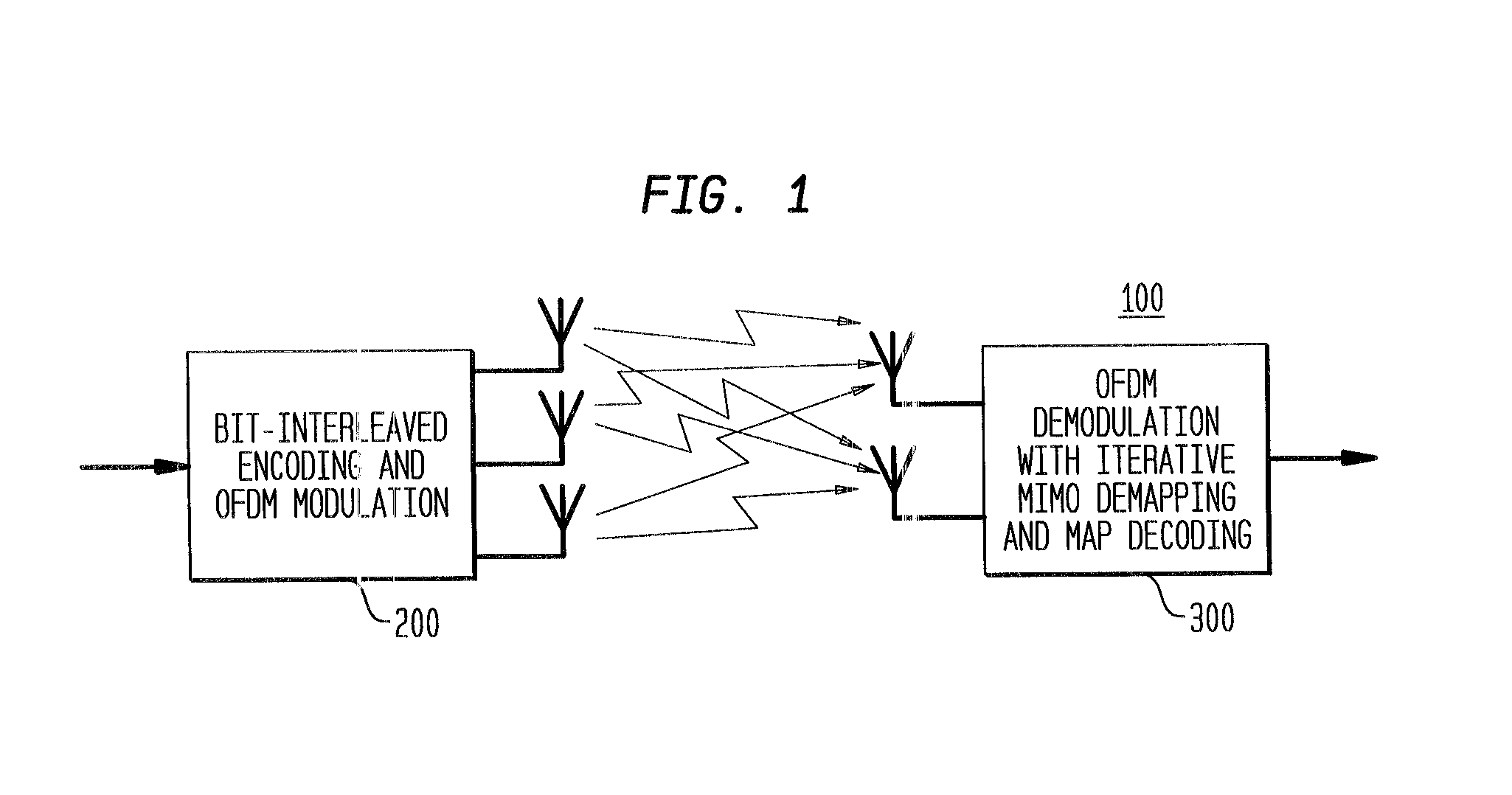

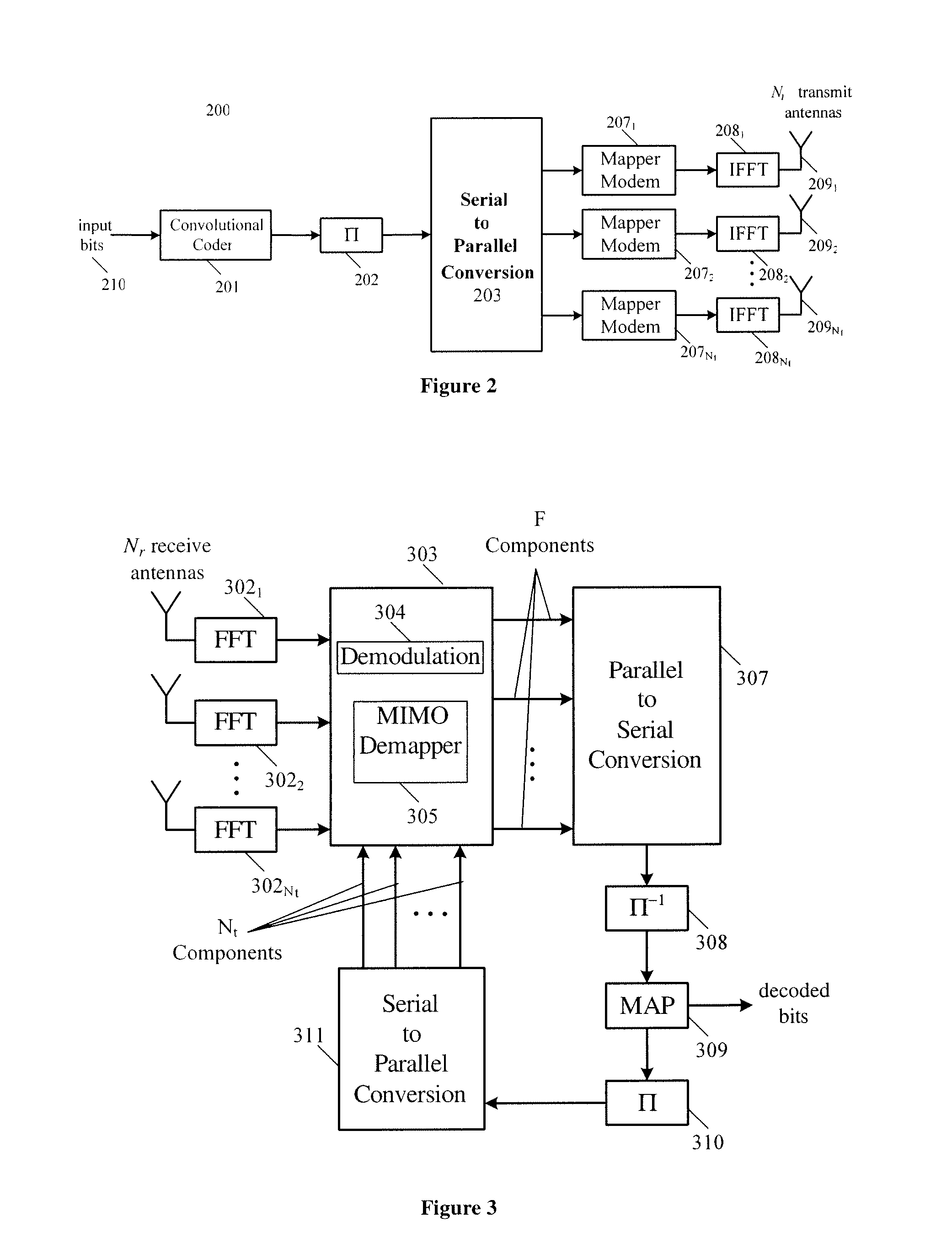

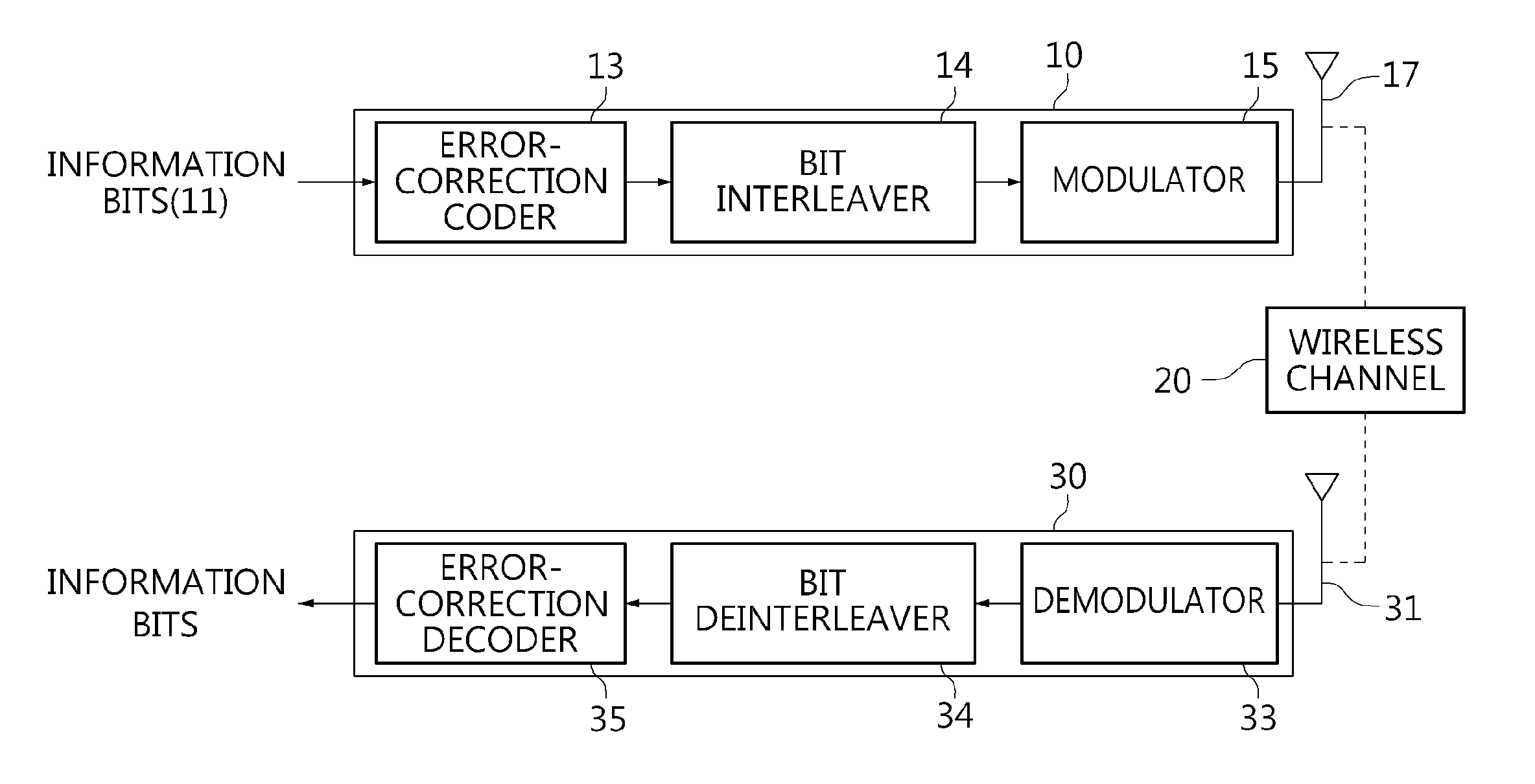

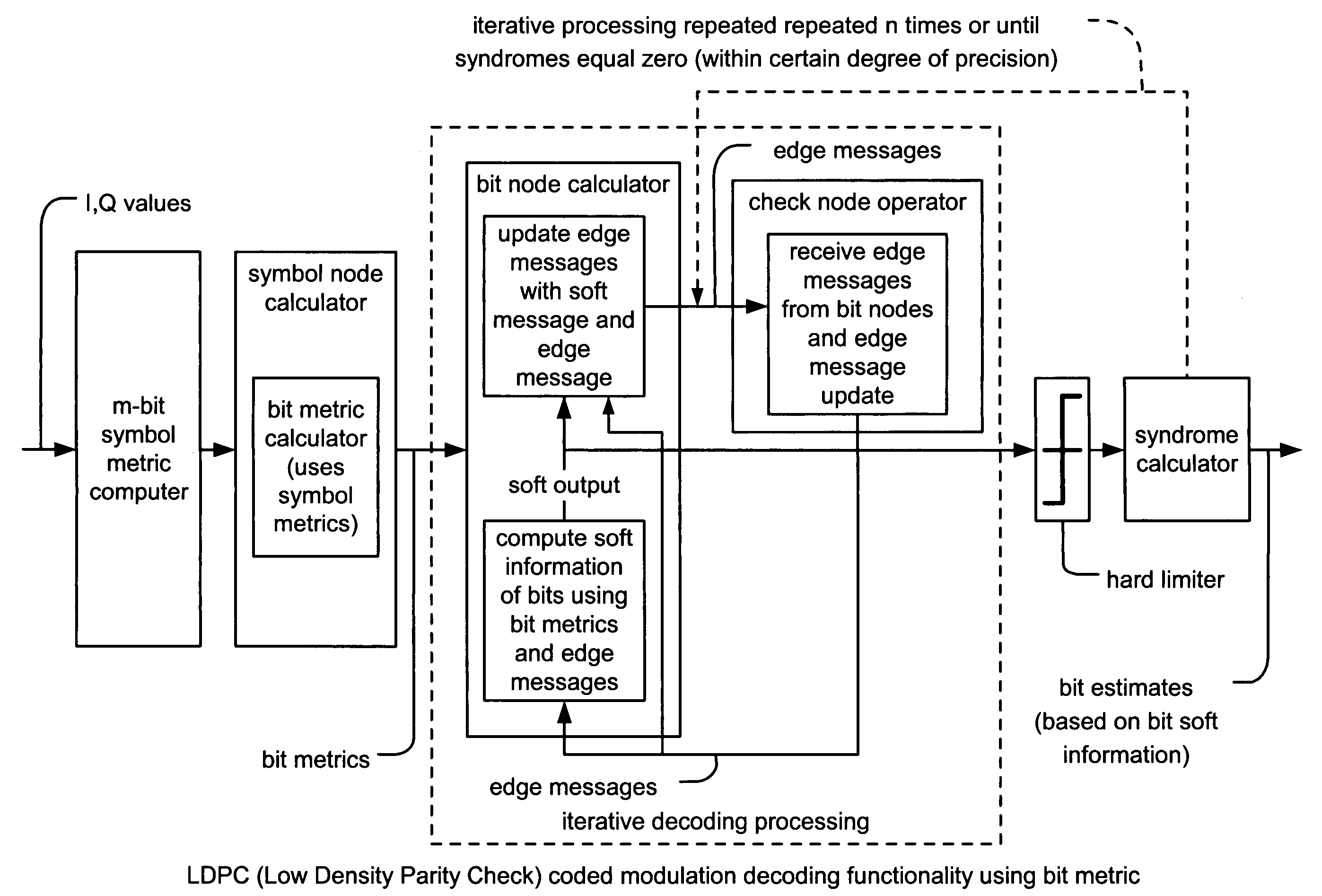

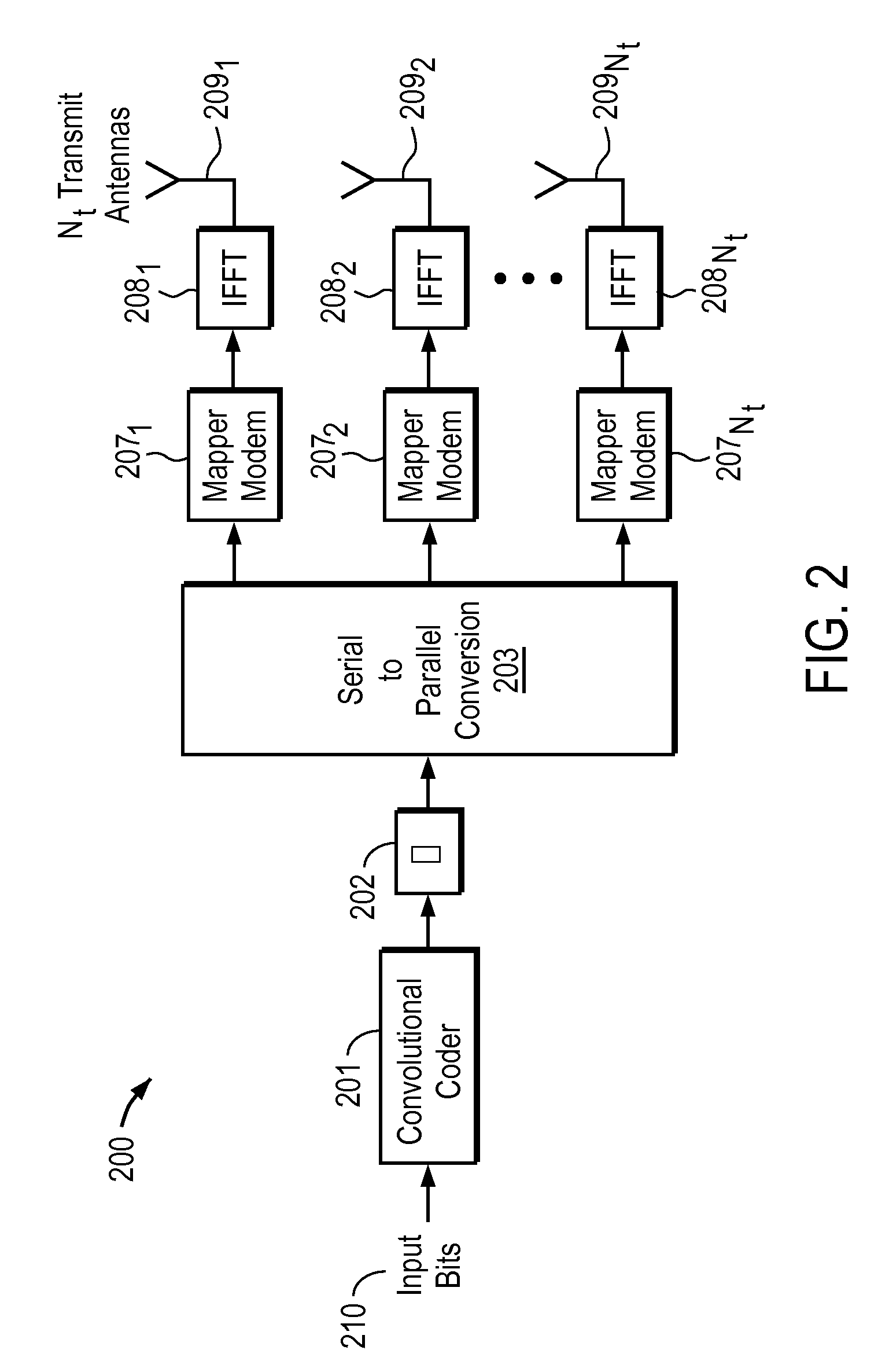

Reduced complexity receiver for space-time- bit-interleaved coded modulation

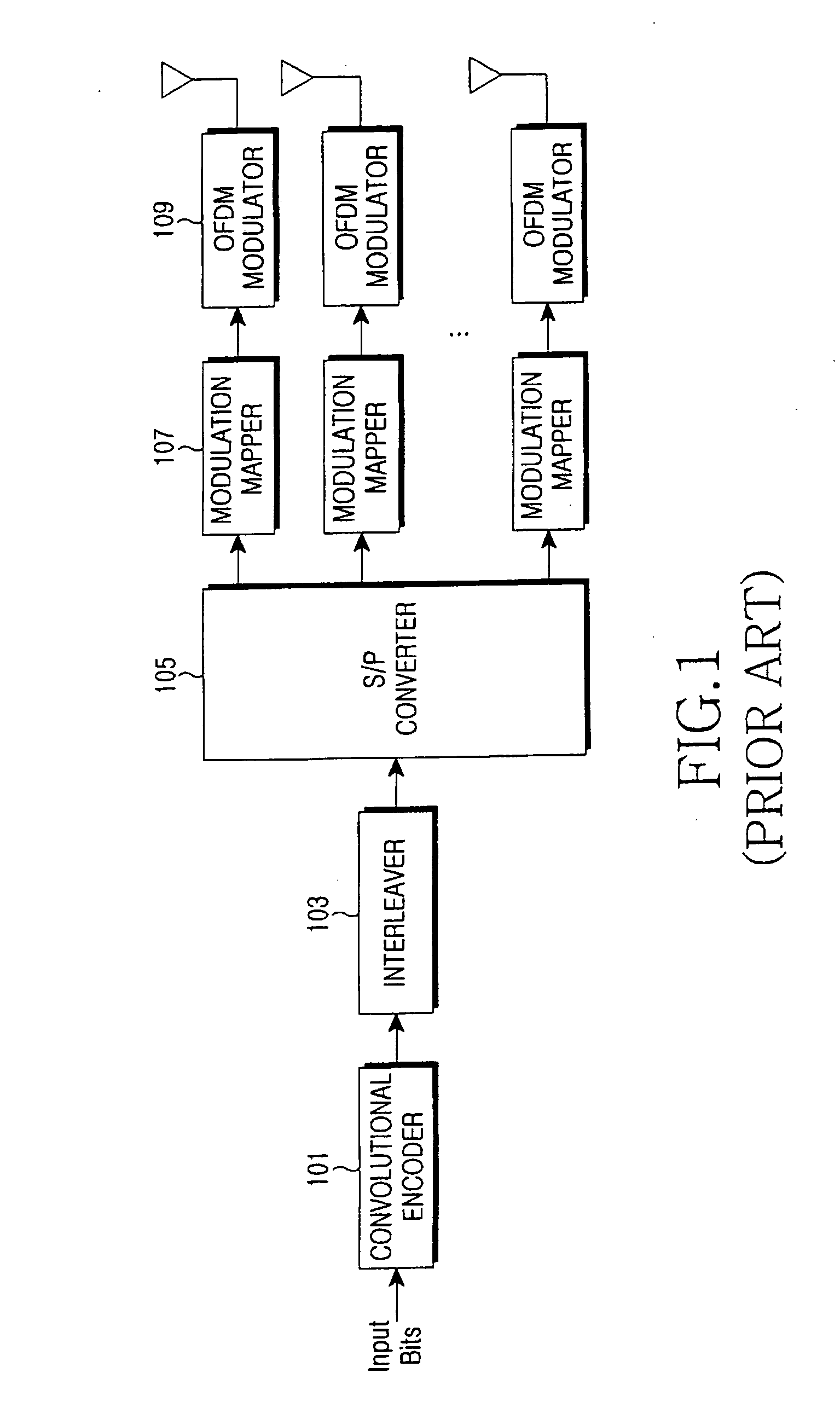

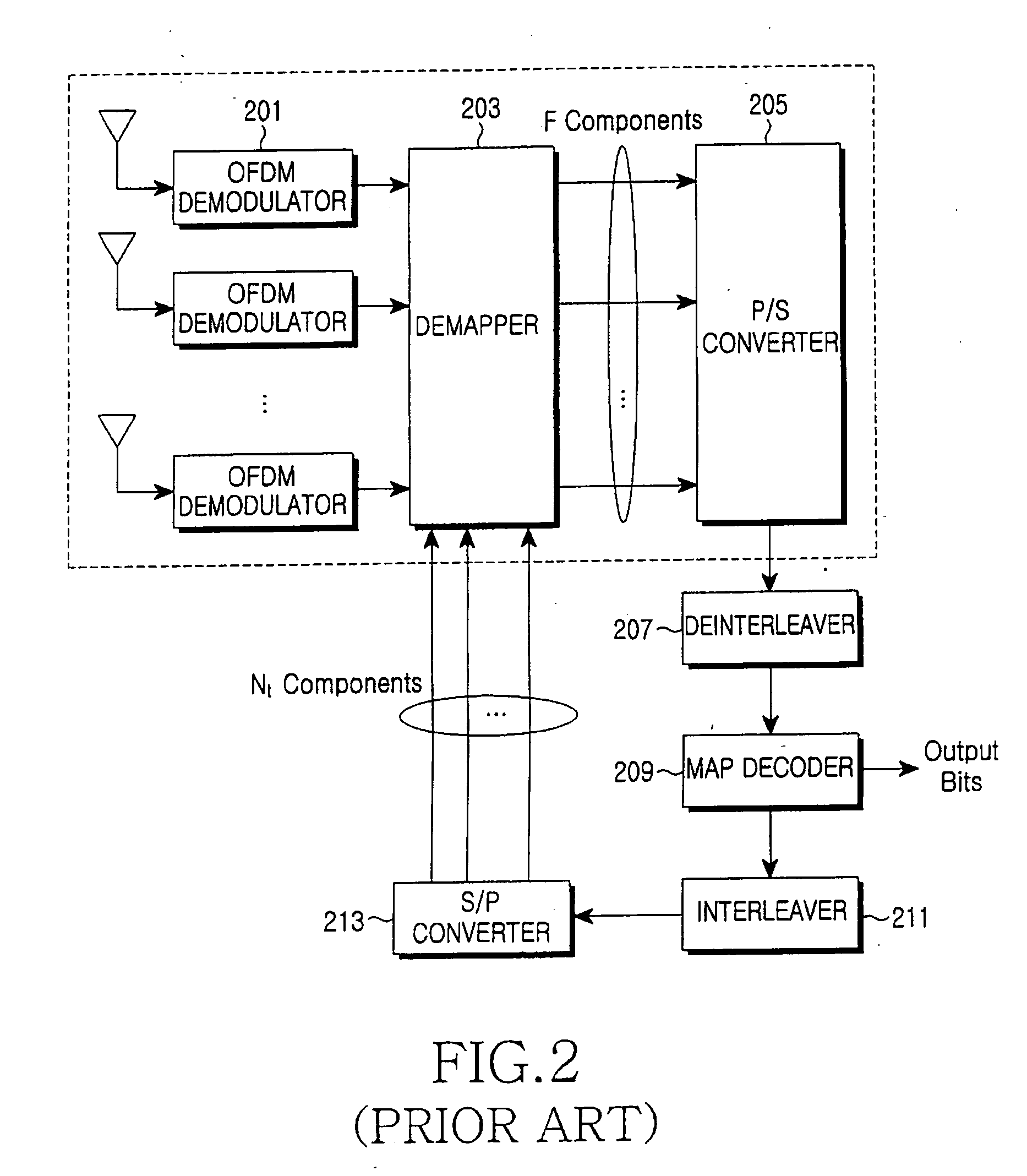

InactiveUS7095812B2Improve bit error rate performanceReduce in quantityData representation error detection/correctionCode conversionMulti inputRadio channel

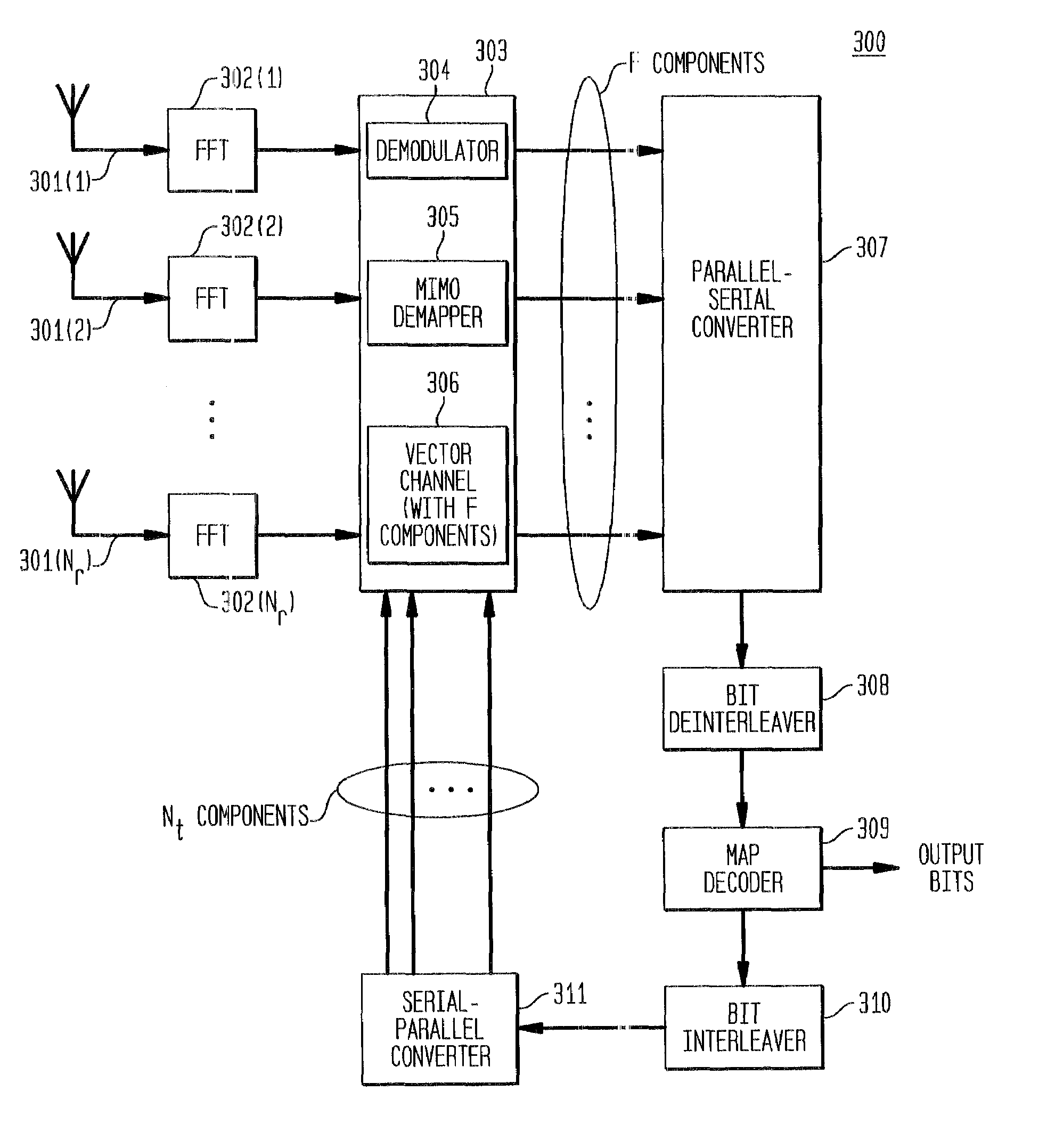

A system employs space-time coding characterized at the transmitter by bit-interleaved coded modulation (BICM) combined with modulating several streams of the BICM encoded data for transmission over two or more antennas. Space-time coding techniques improve transmission efficiency in radio channels by using multiple transmit and / or receive antennas and coordination of the signaling over these antennas. Bit-interleaved coded modulation provides good diversity gain with higher-order modulation schemes that employ binary convolutional codes. A receiver demodulates the received signals and applies multi-input, multi-output (MIMO) demapping to estimate the BICM encoded bitstream. After deinterleaving of the BICM encoded bitstream, maximum a posteriori (MAP) decoding is applied to the resulting bit stream to generate soft output values. By applying well-known turbo-decoding principles to iteratively demap and decode, the overall receiver performance is significantly improved. The MIMO demapping and MAP decoding processes exchange likelihood information to improve the bit error rate performance over several iterations of demapping / decoding. By generating tentative decisions for transmitted bits, the overall number of evaluations used for demapping may be reduced.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

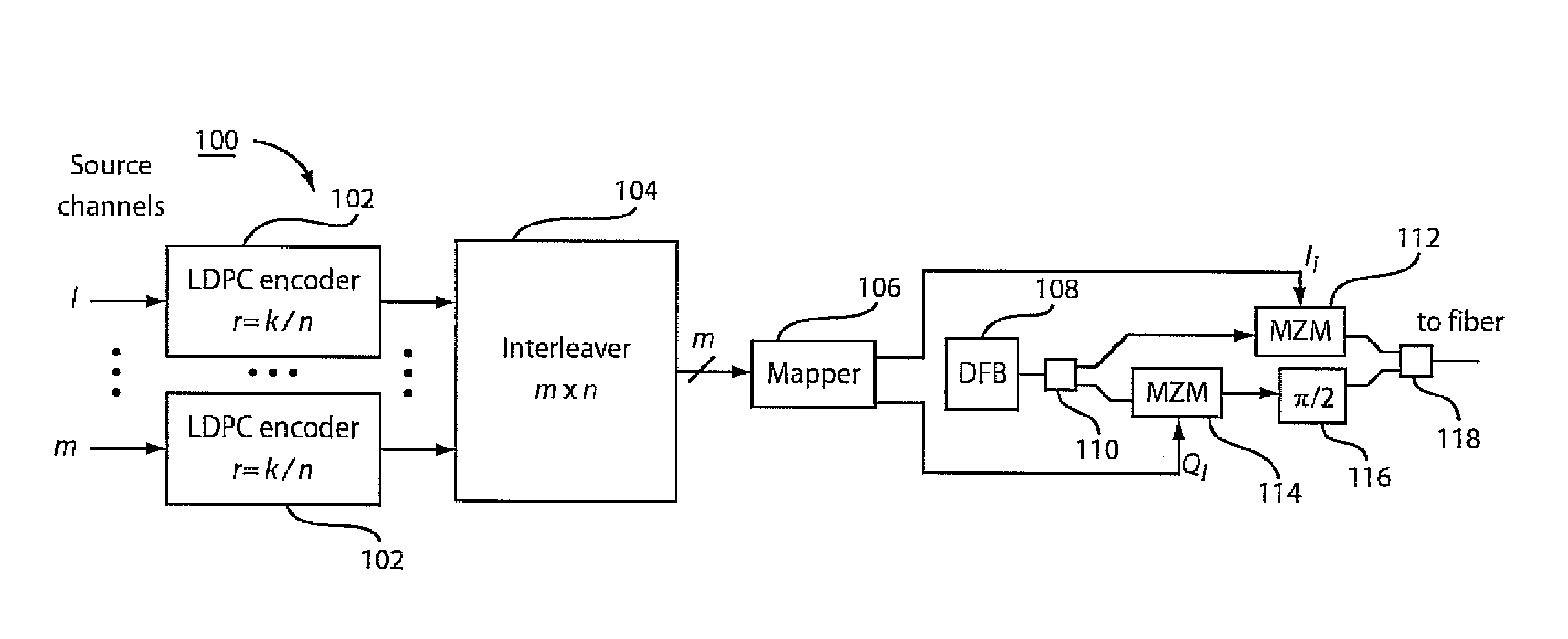

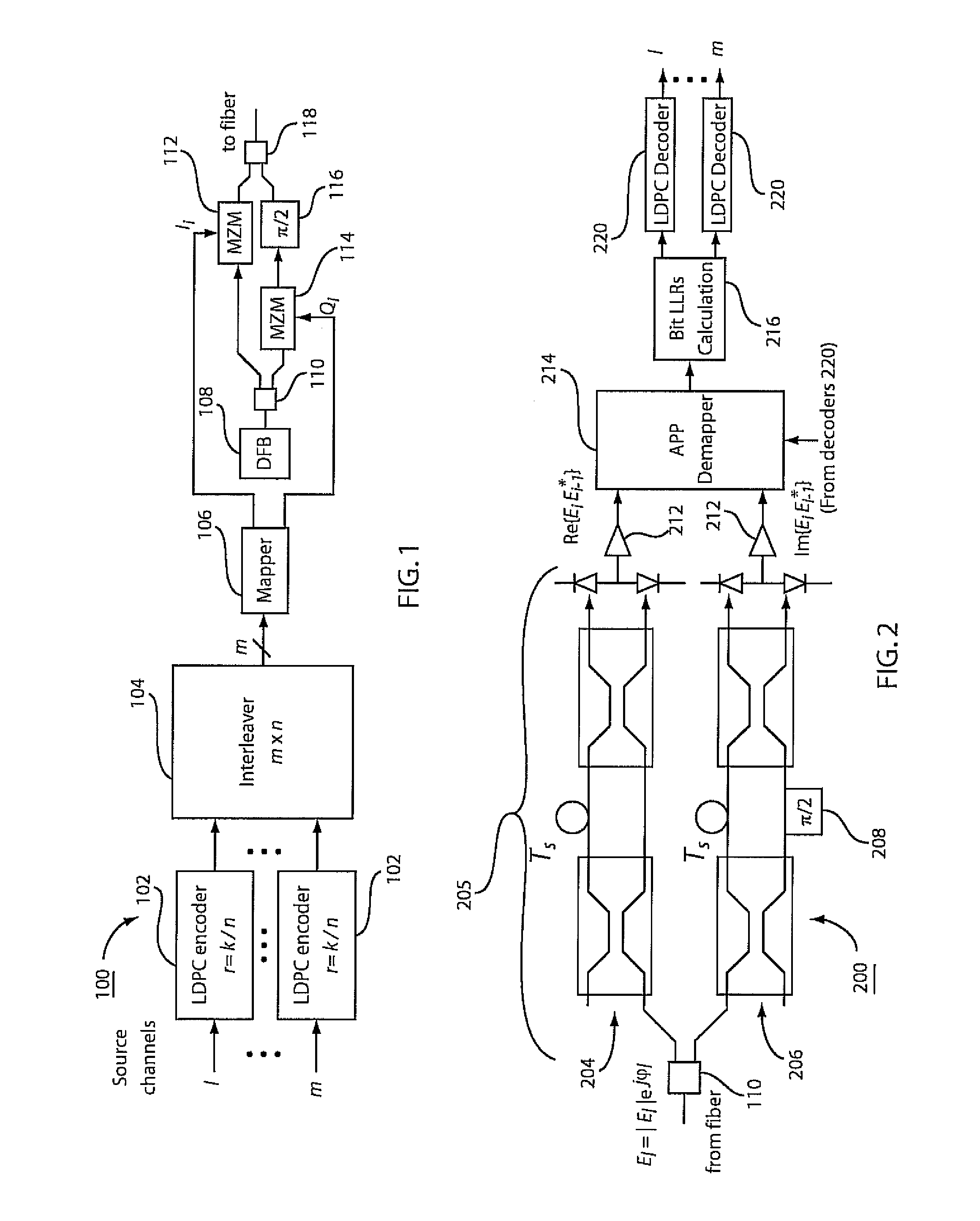

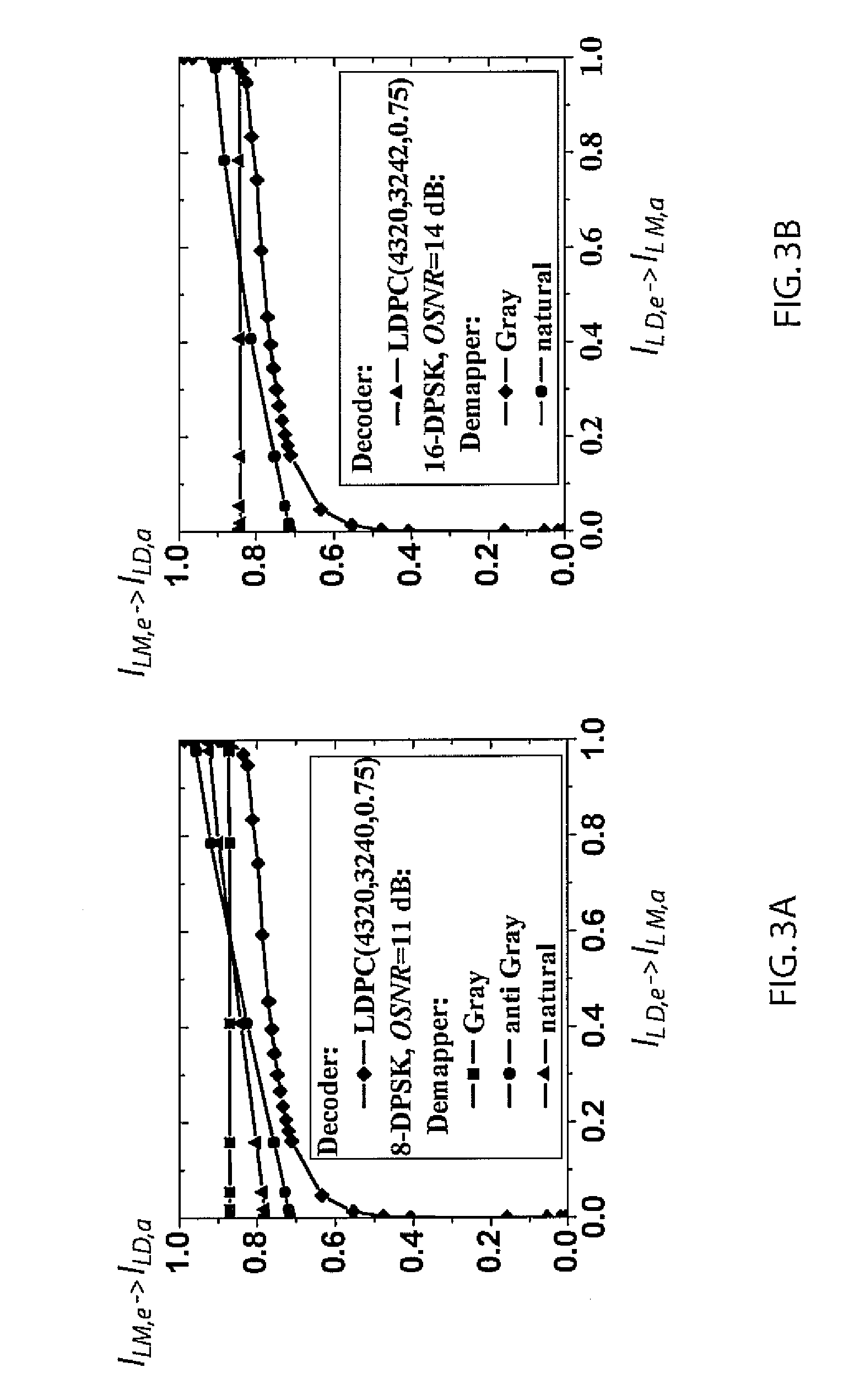

Bit-interleaved ldpc-coded modulation for high-speed optical transmission

ActiveUS20080163025A1Easy to implementImprove toleranceElectronic circuit testingError correction/detection using LDPC codesConstellationBit interleaved coded modulation

A transmitter includes a plurality of encoders configured to receive source bit streams from m information sources, each of the plurality encoders including identical (n,k) low-density parity check (LDPC) codes of code rate r=k / n, where k is a number of information bits and n is codeword length. An interleaver is configured to collect m row-wise codewords from the plurality of encoders, and a mapper is configured to receive m bits at a time column-wise from the interleaver and to determine an M-ary signal constellation point. A modulator is configured to modulate a light source in accordance with the output of the mapper at a transmission rate Rs / r (Rs—the symbol rate, r—the code rate). A receiver and transmission and receiving methods are also disclosed.

Owner:NEC CORP

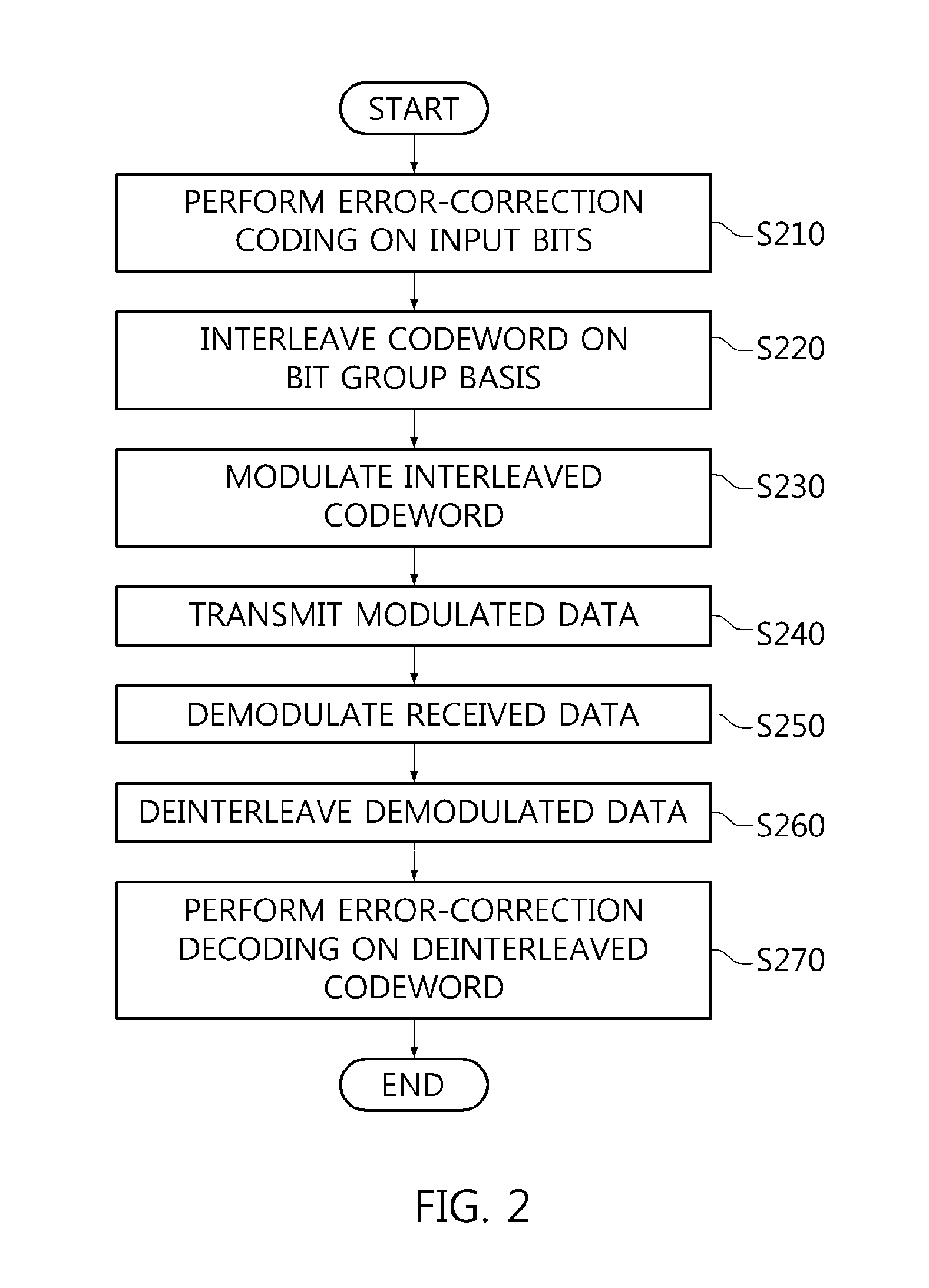

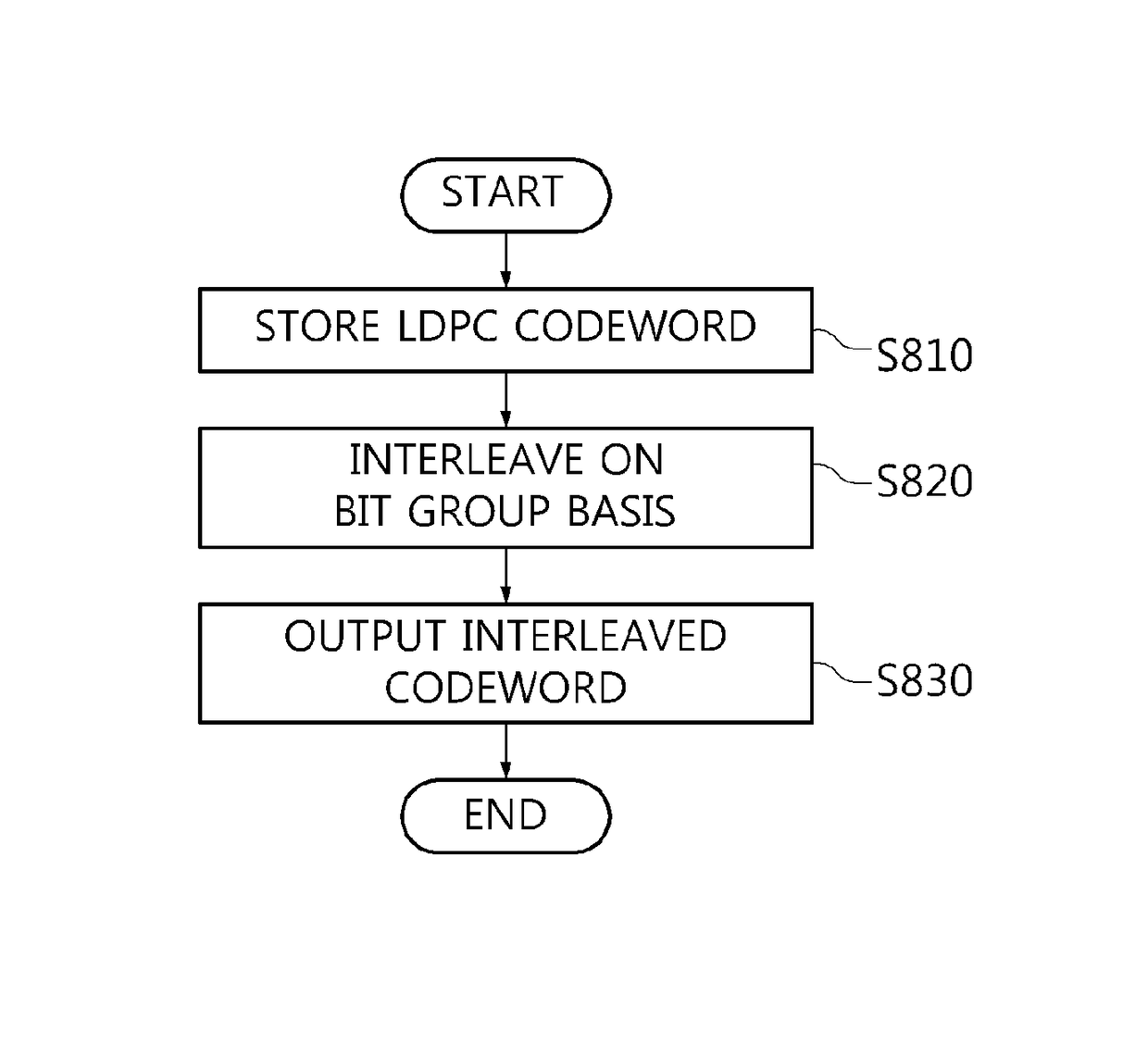

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and 256-symbol mapping, and bit interleaving method using same

ActiveUS20150256202A1Effective distributionEfficiently distributedError correction/detection using LDPC codesBurst error correctionSymbol mappingParallel computing

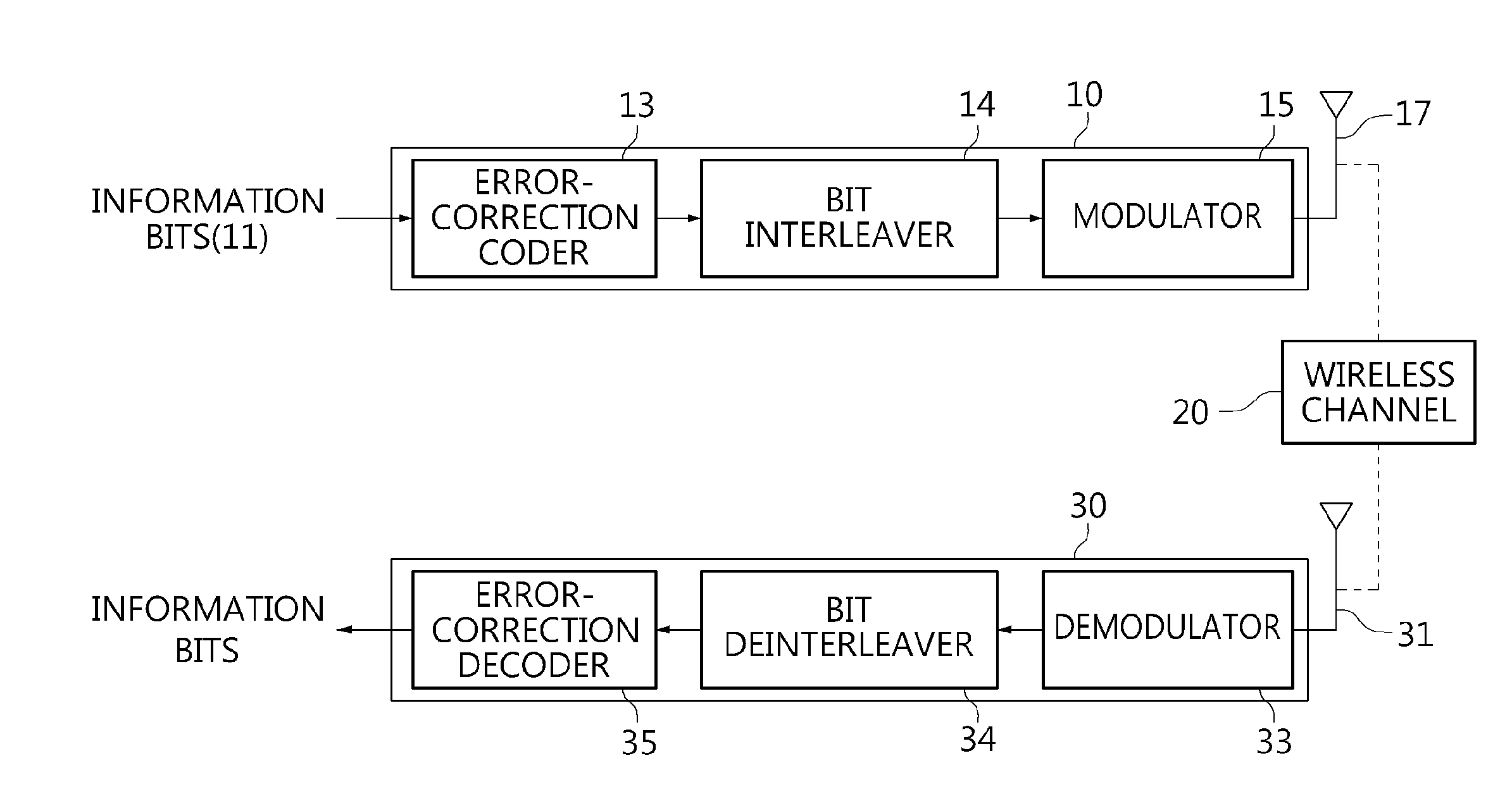

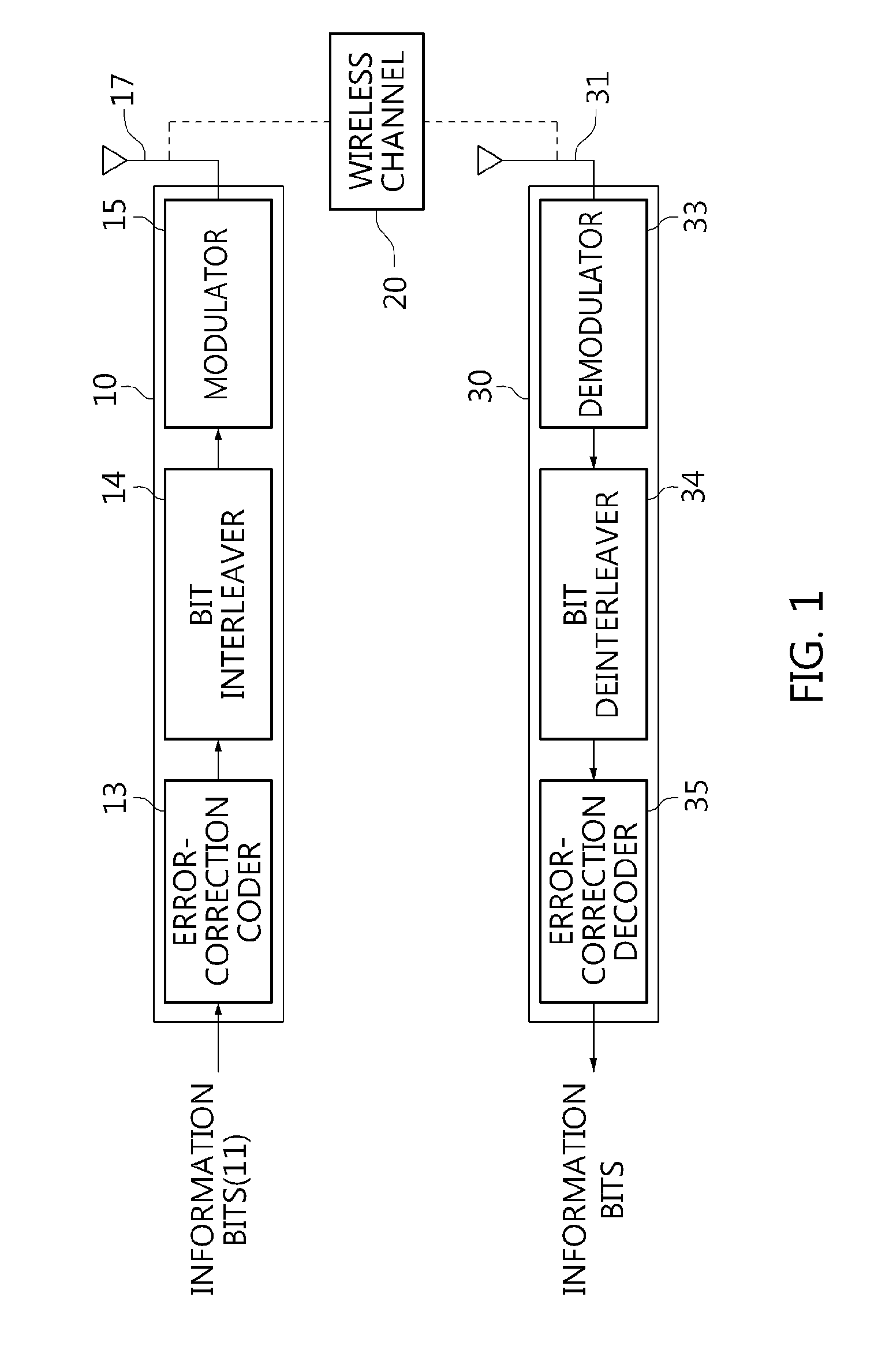

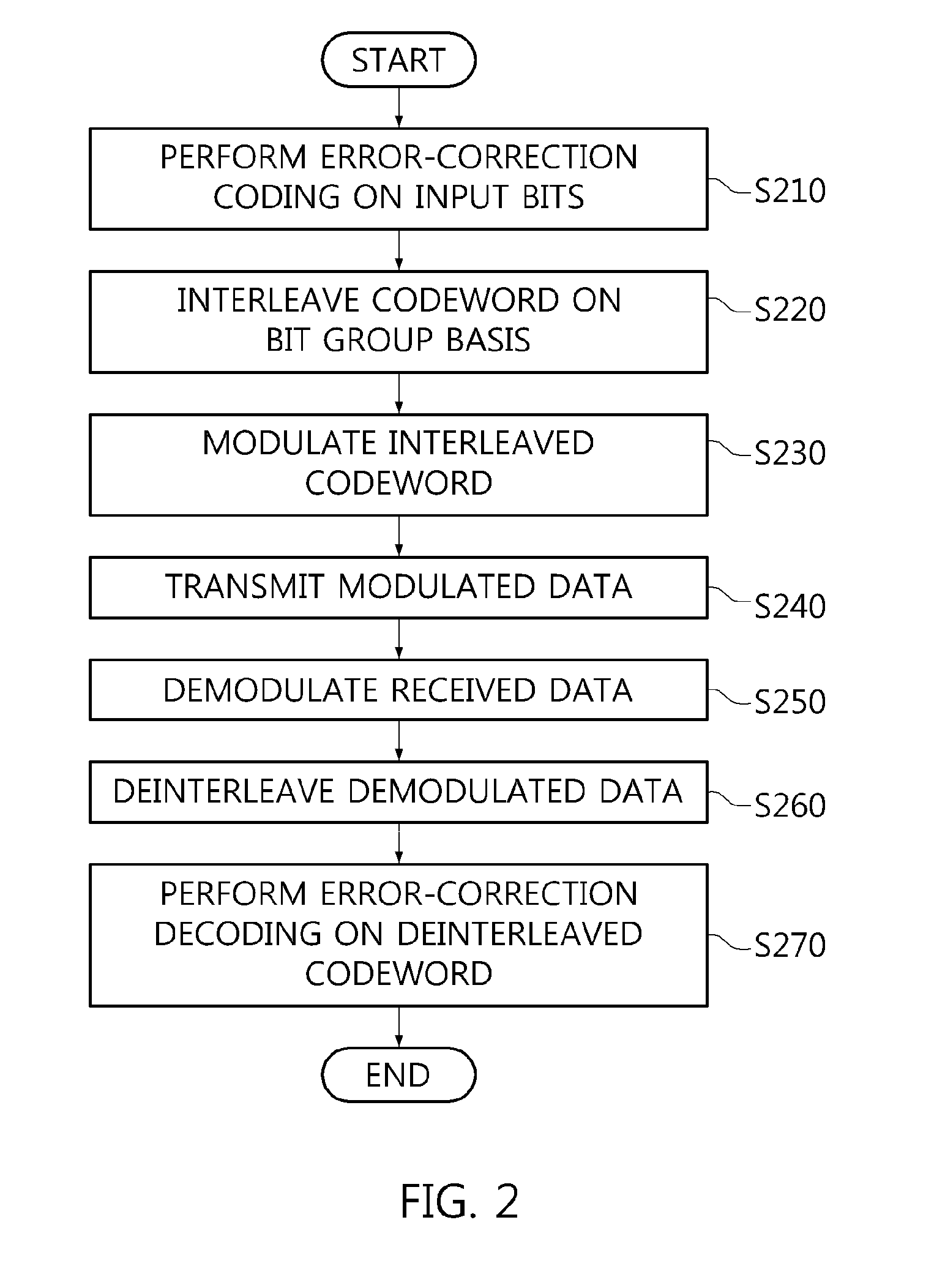

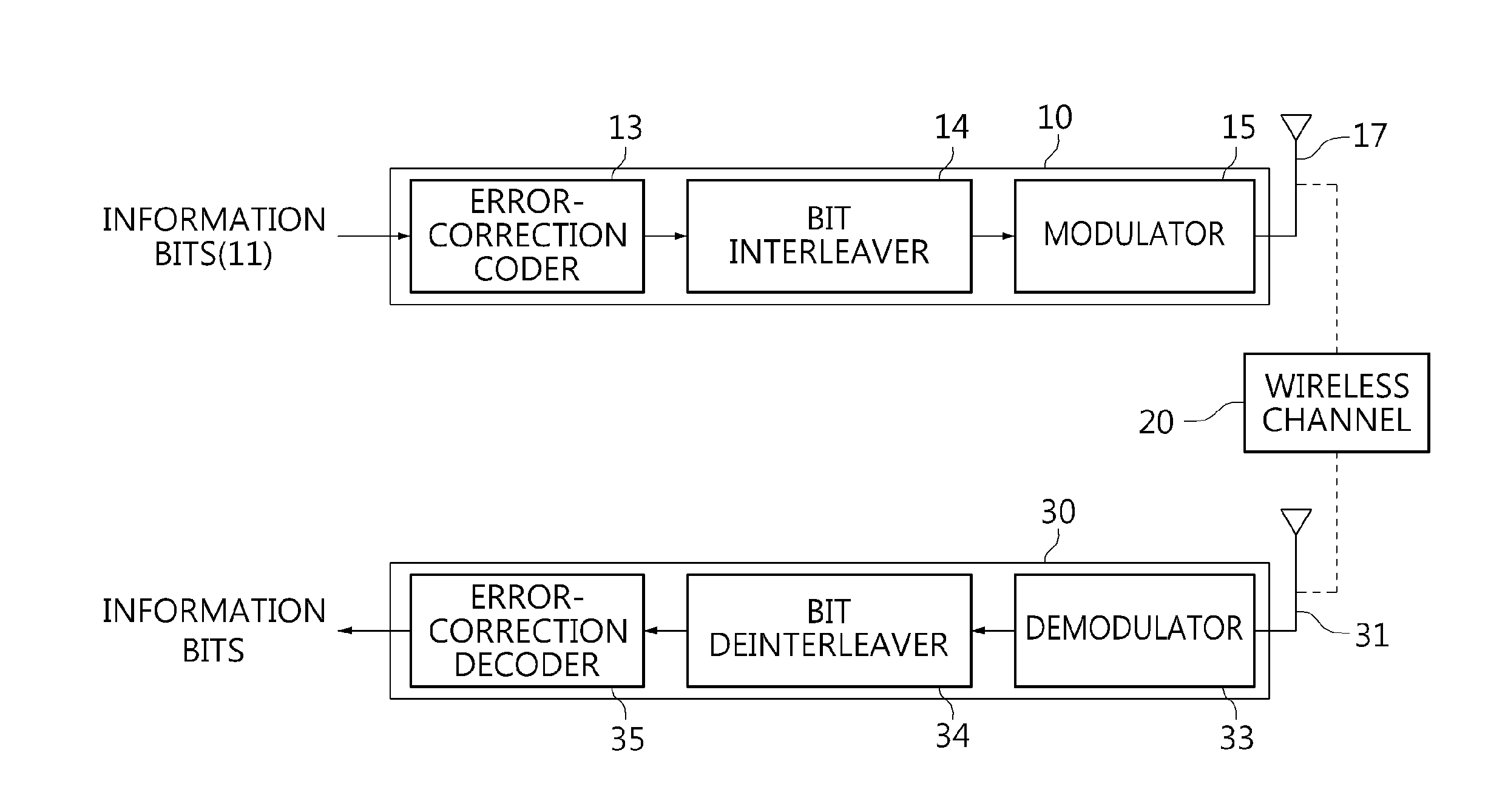

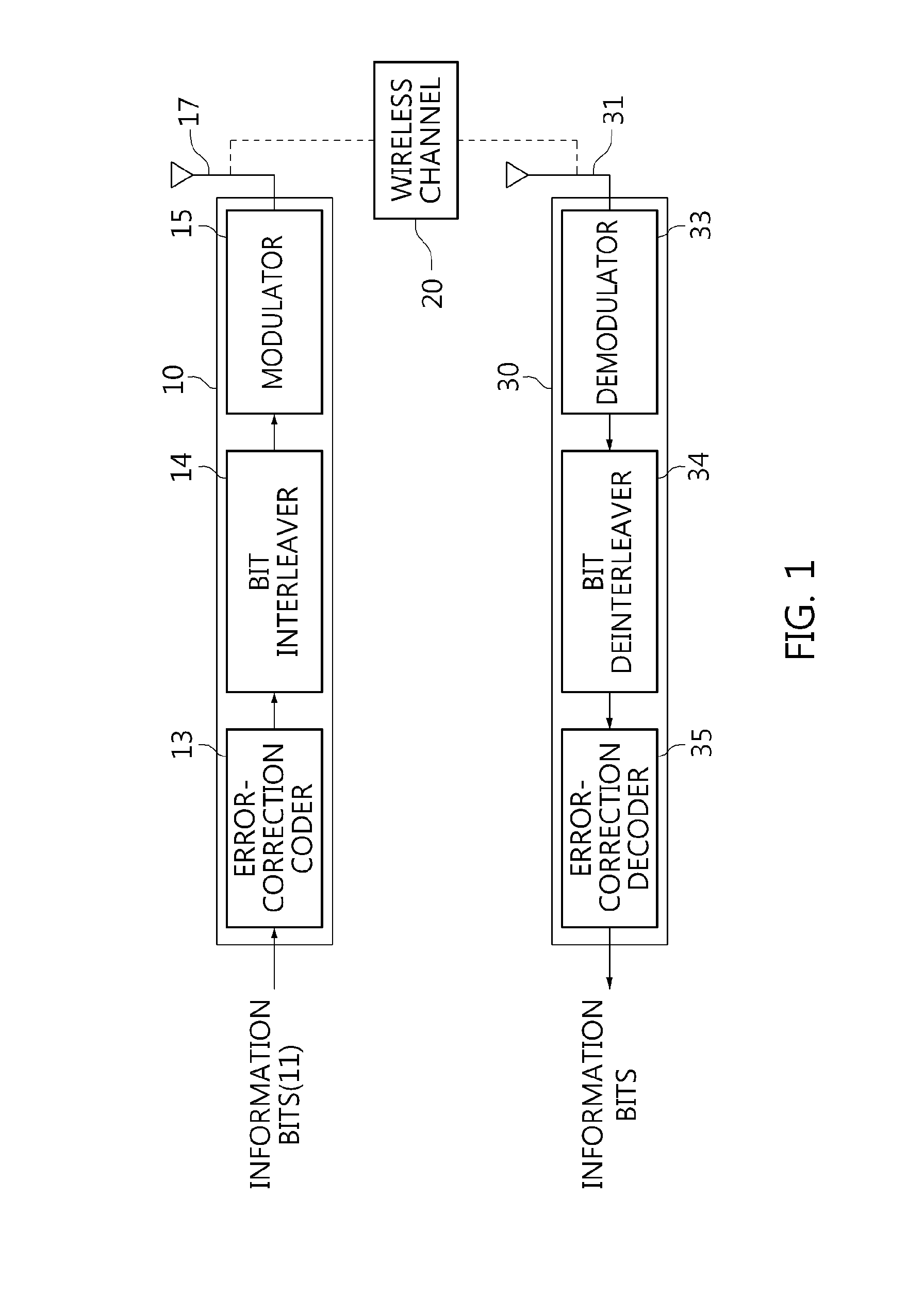

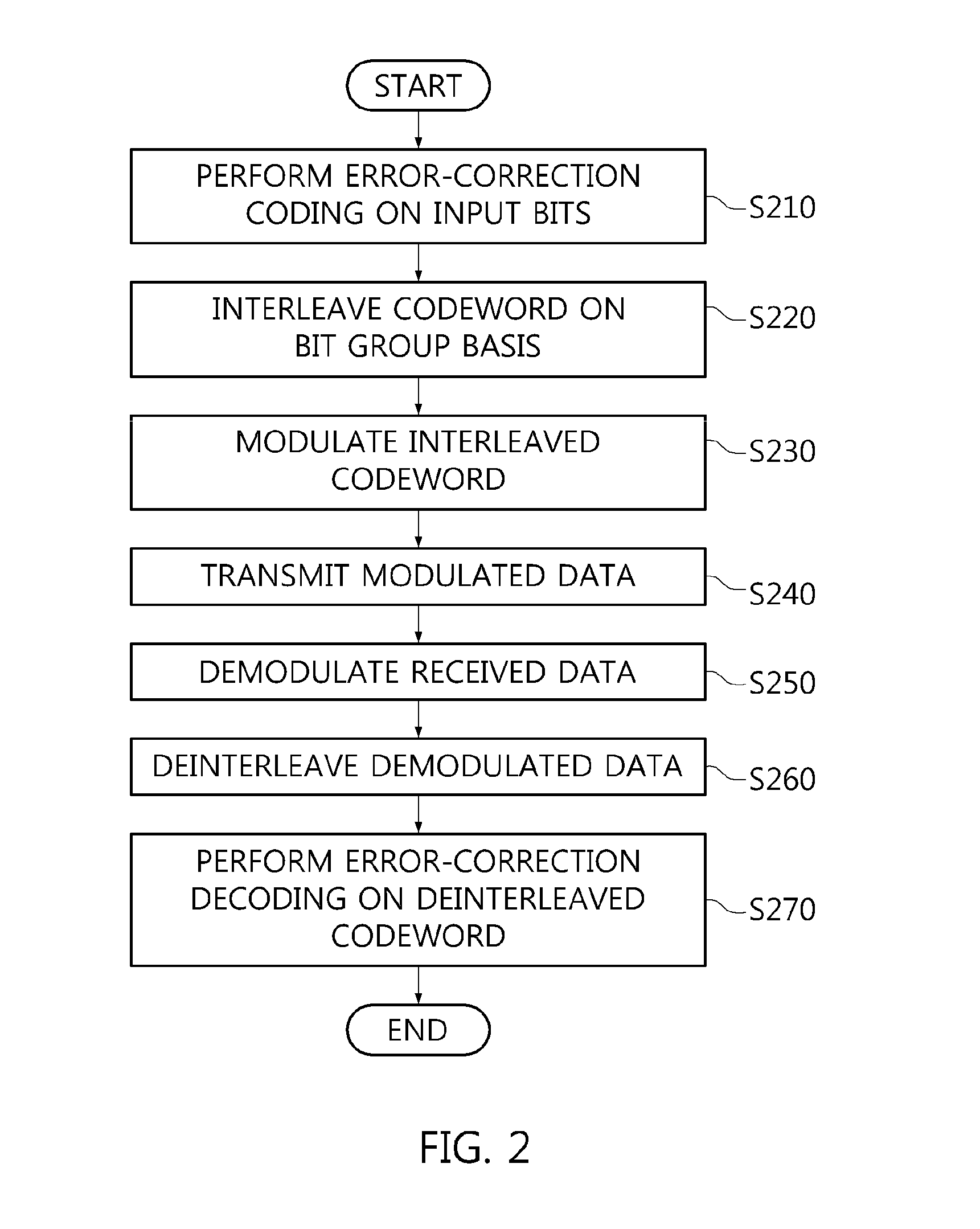

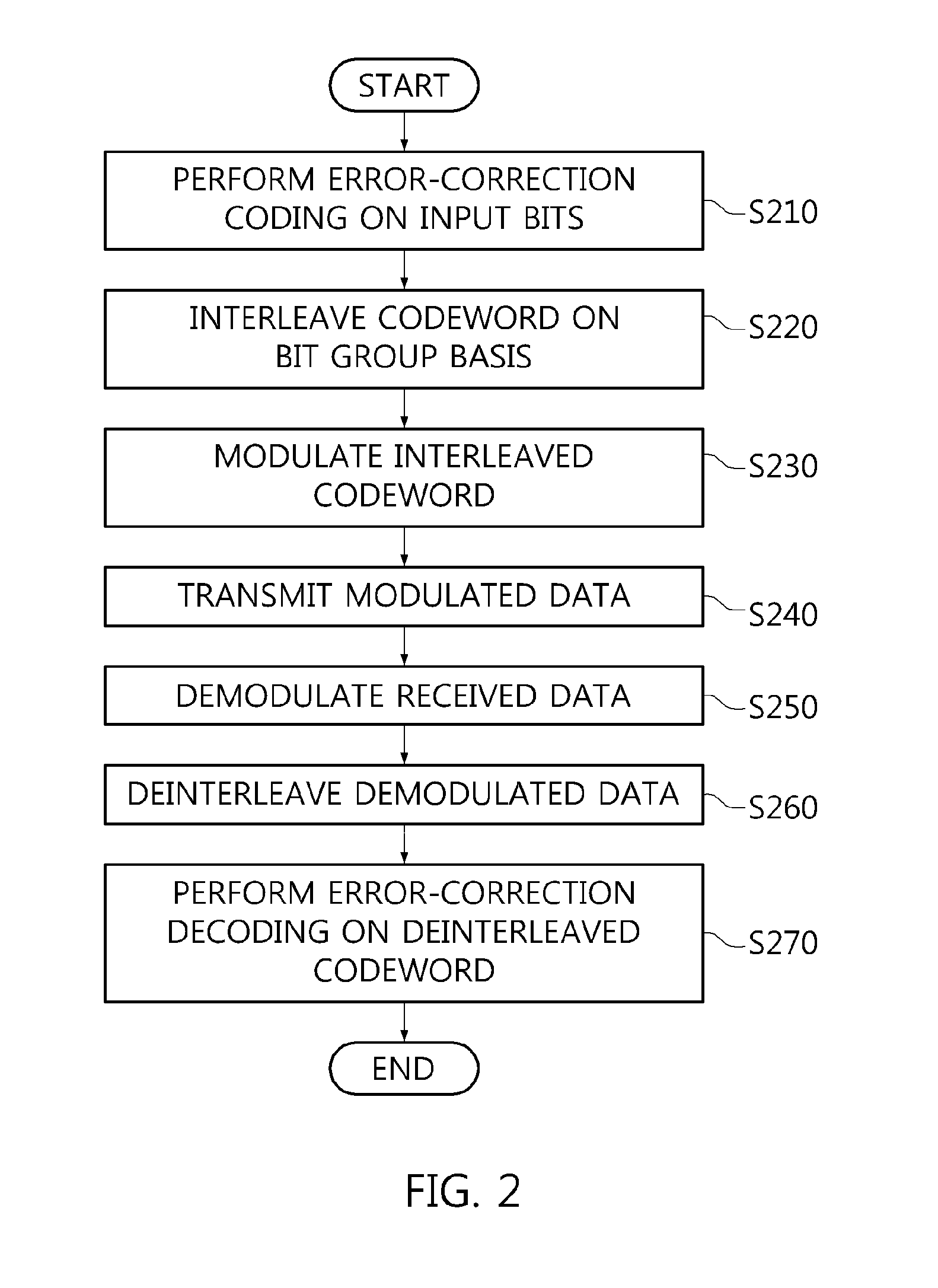

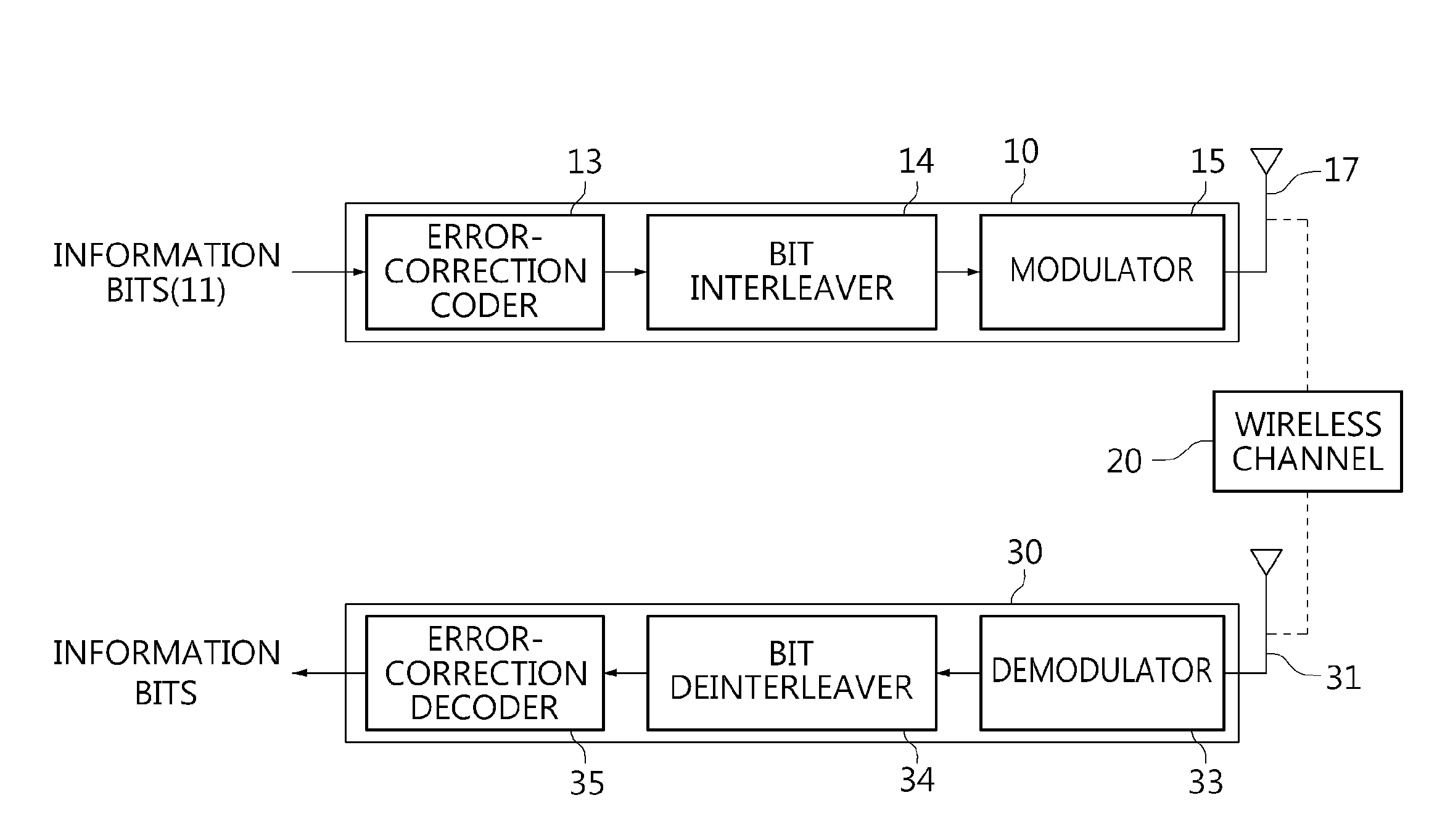

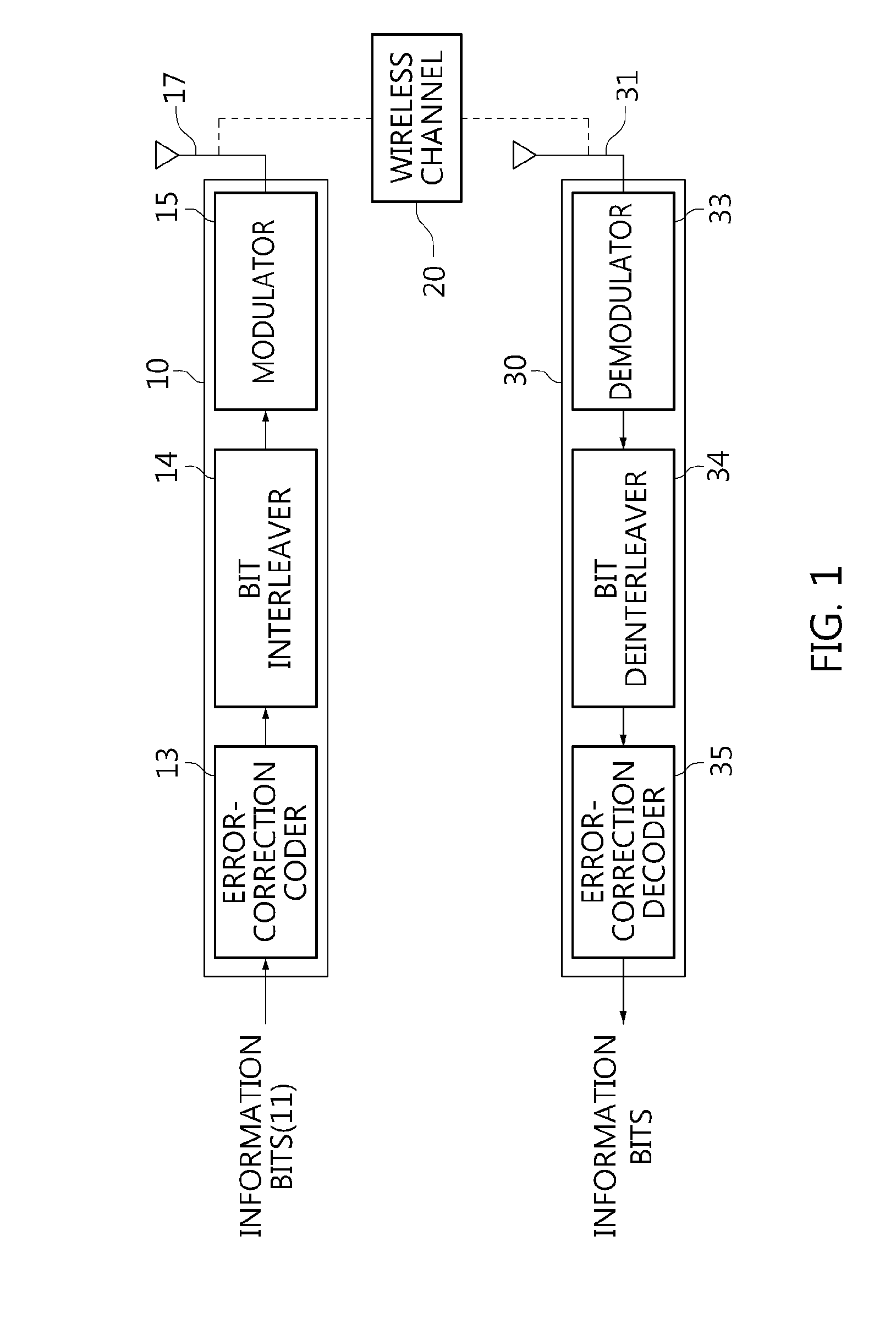

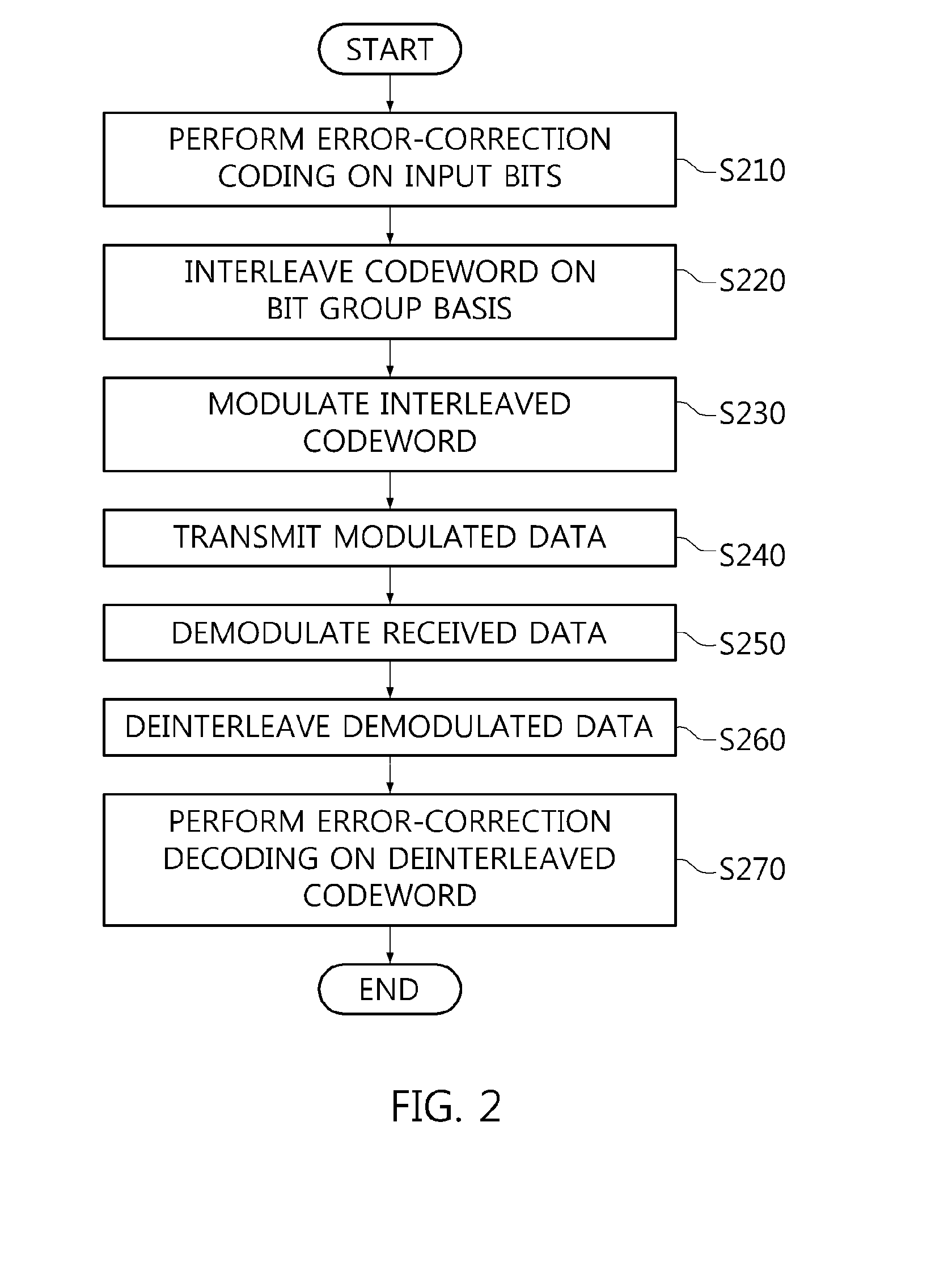

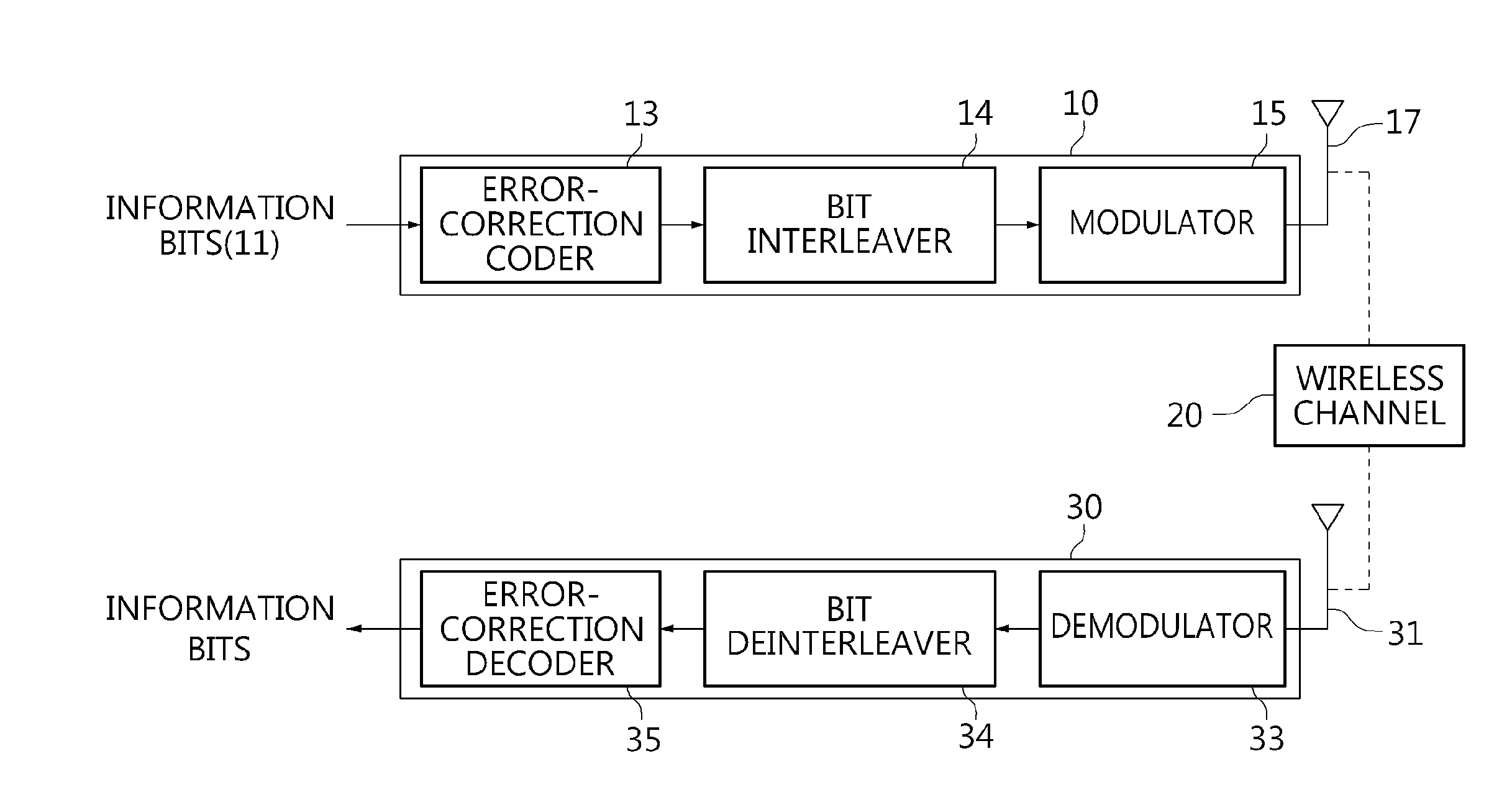

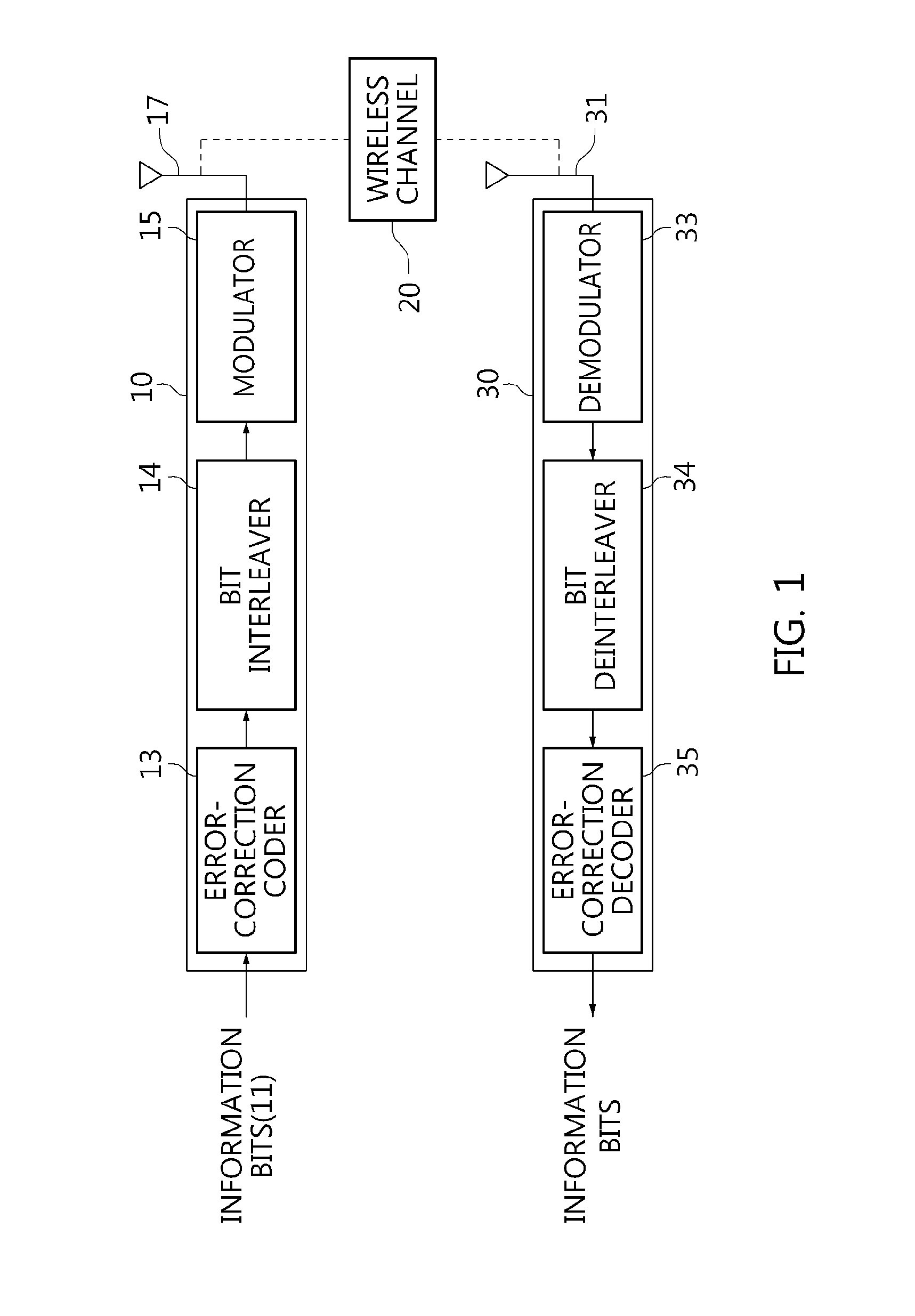

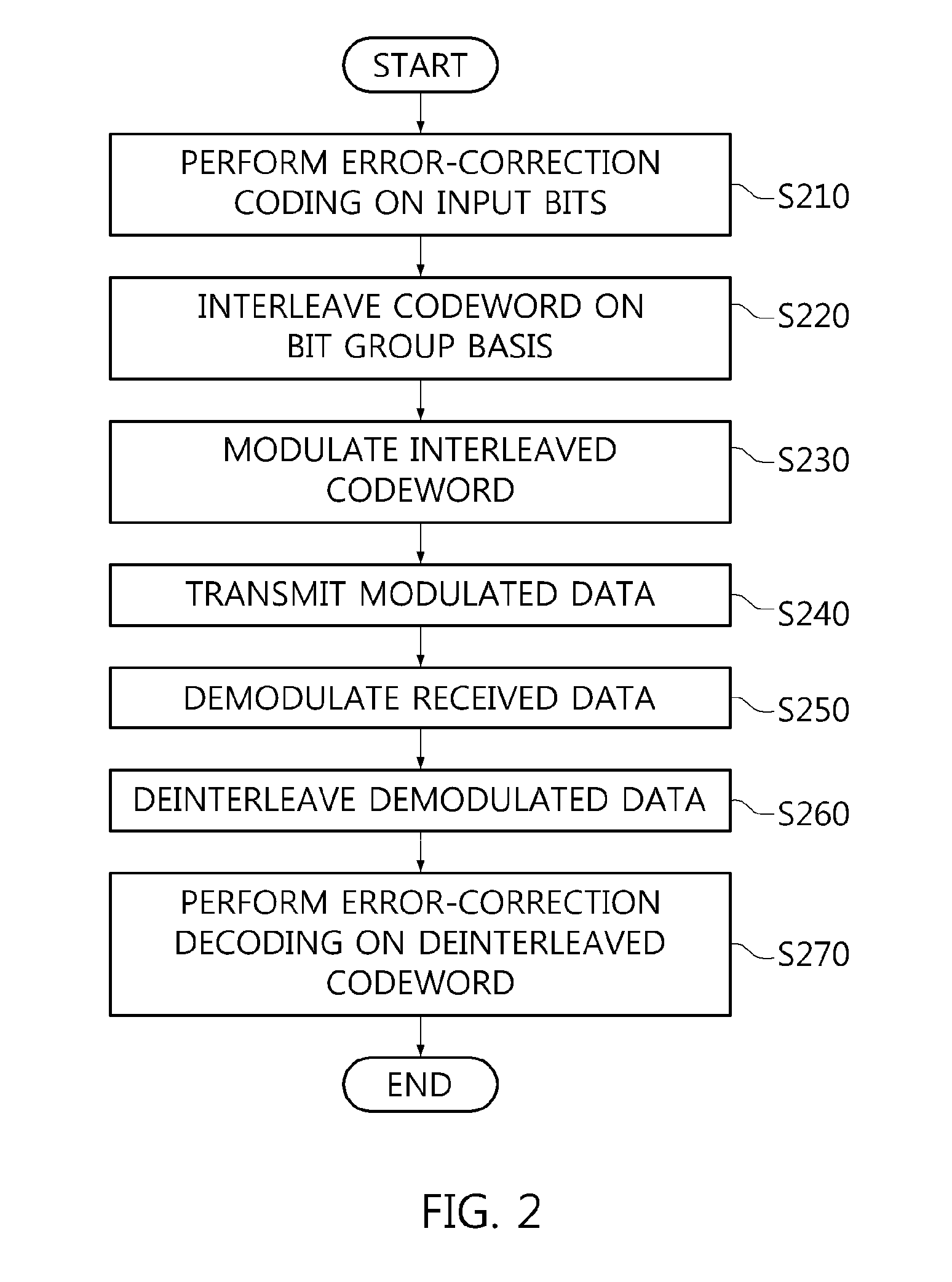

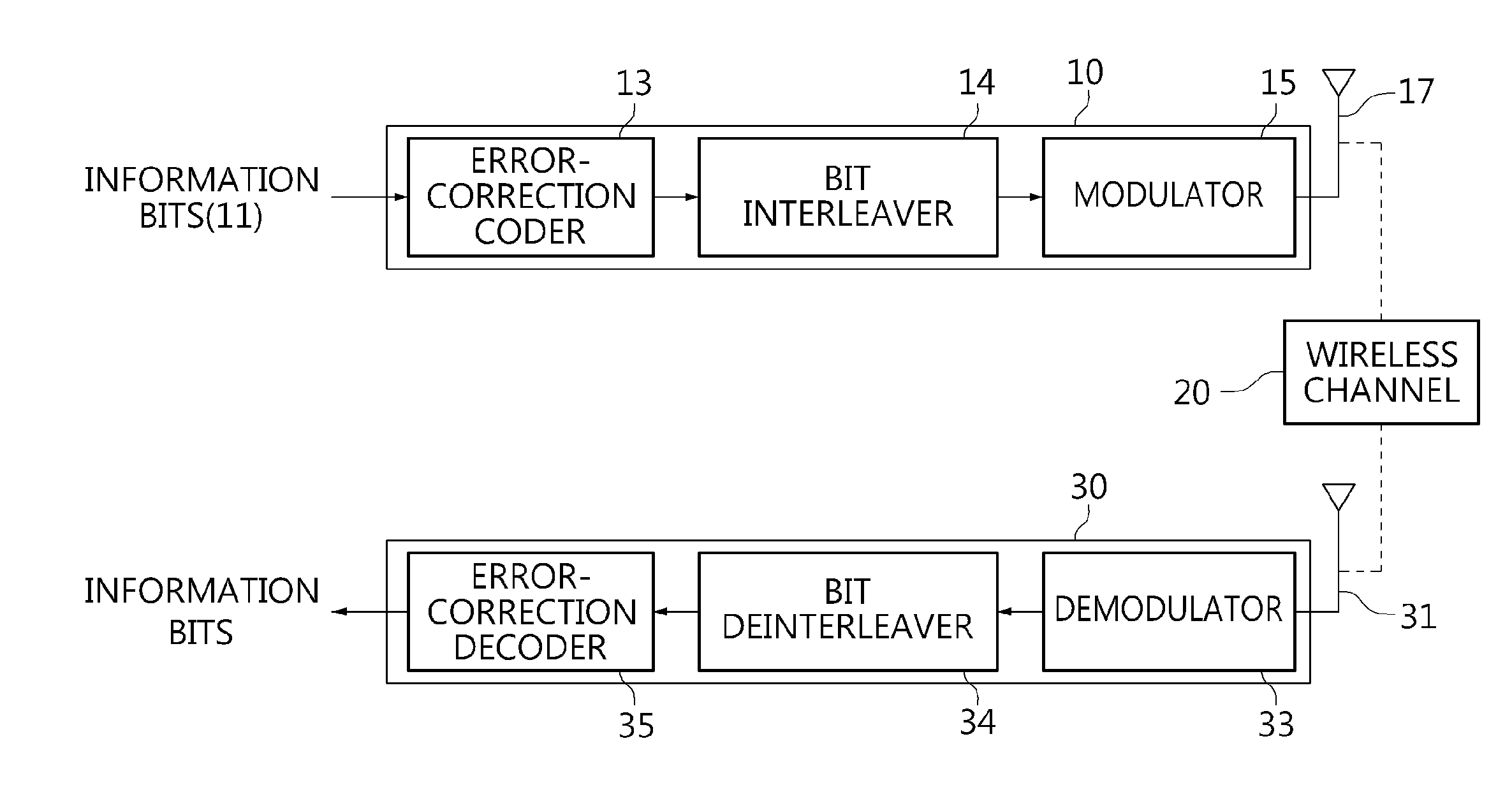

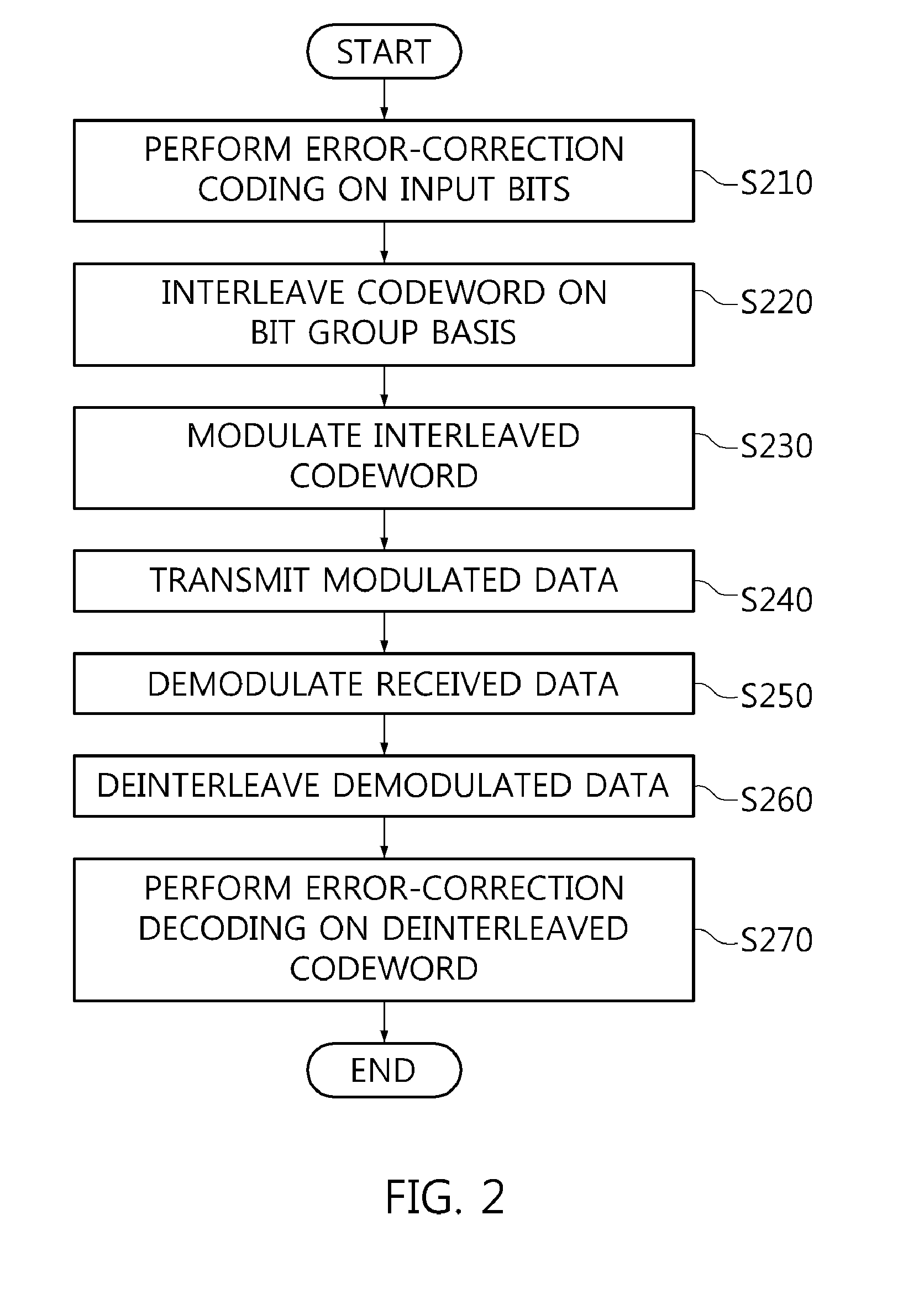

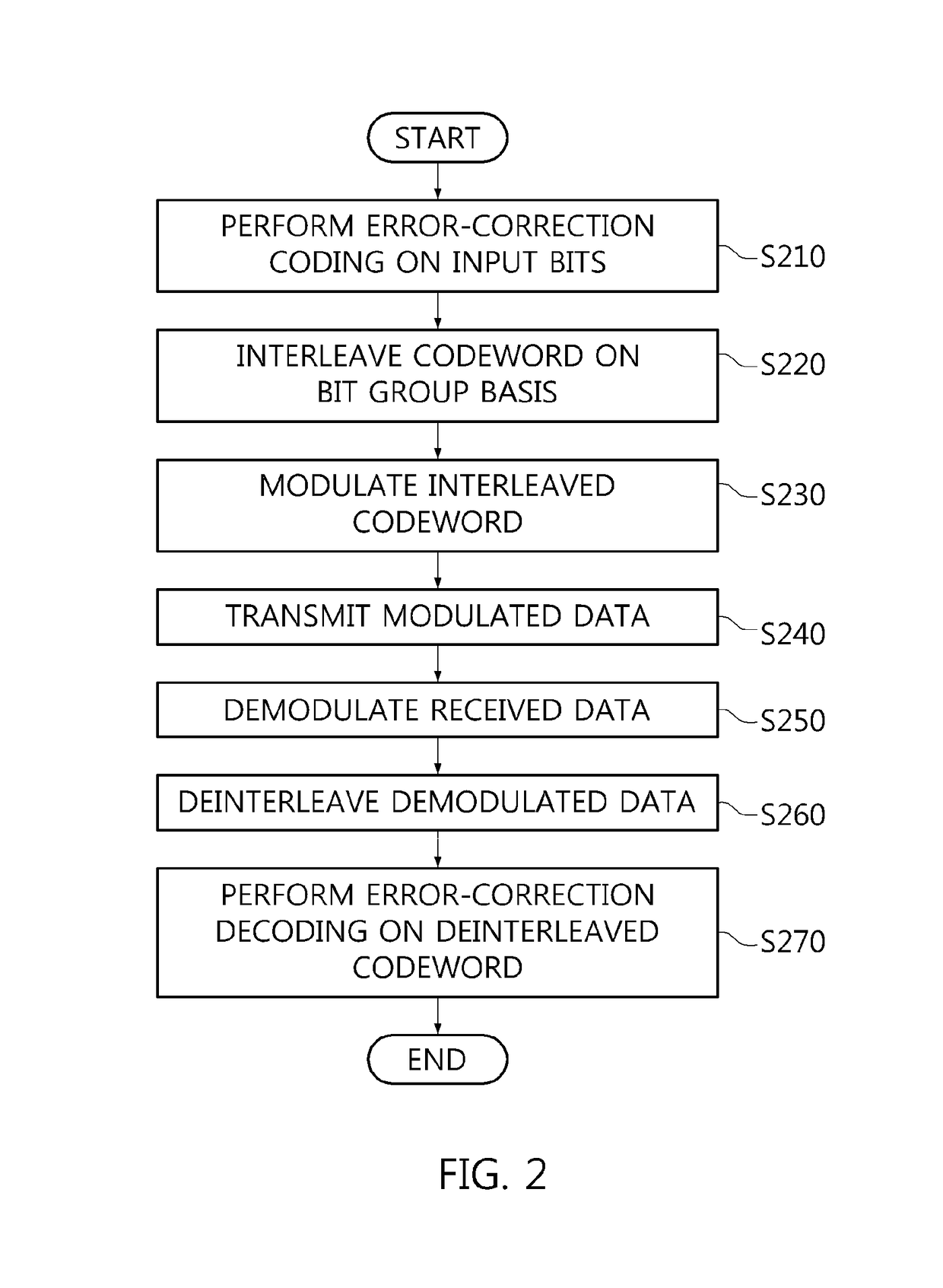

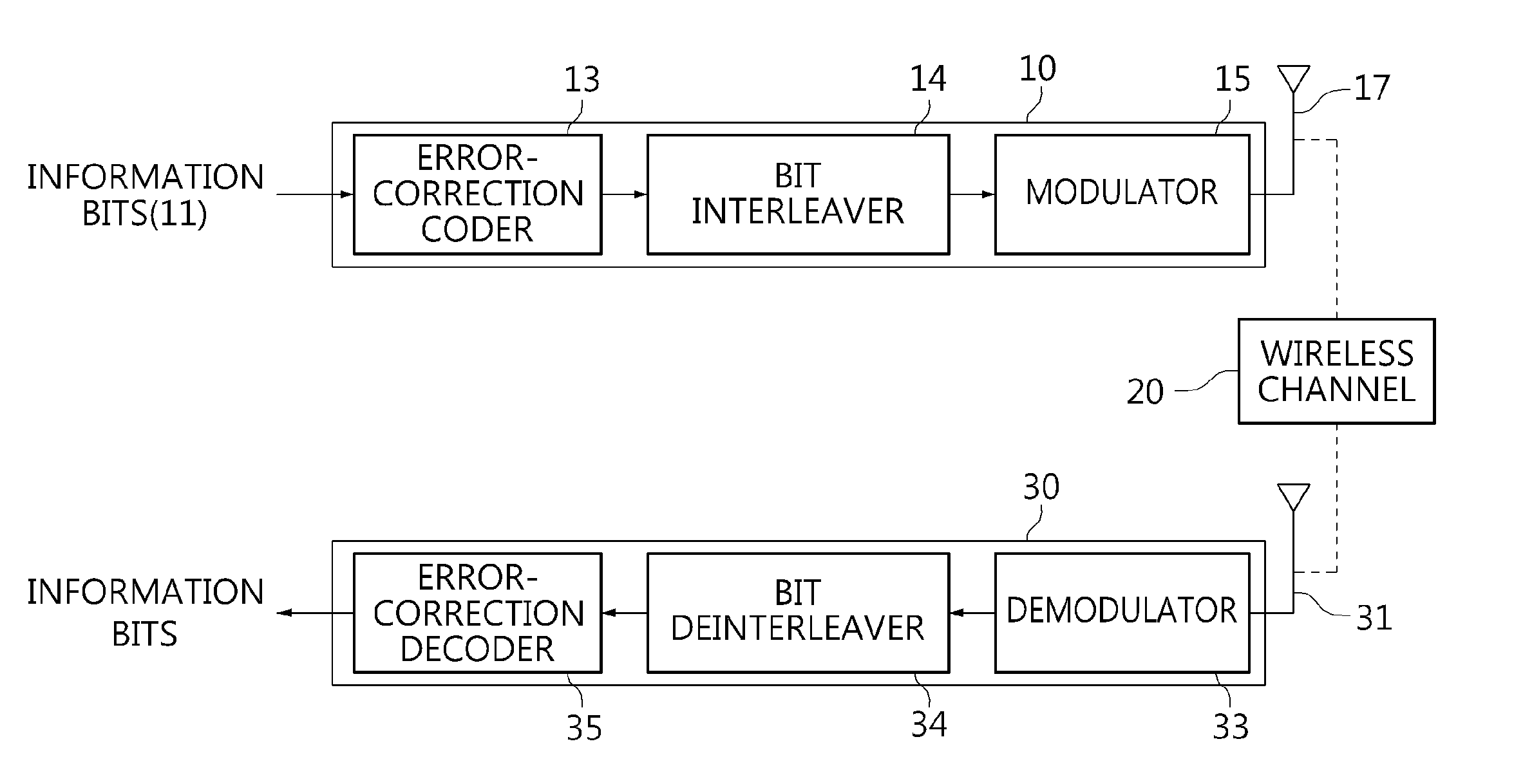

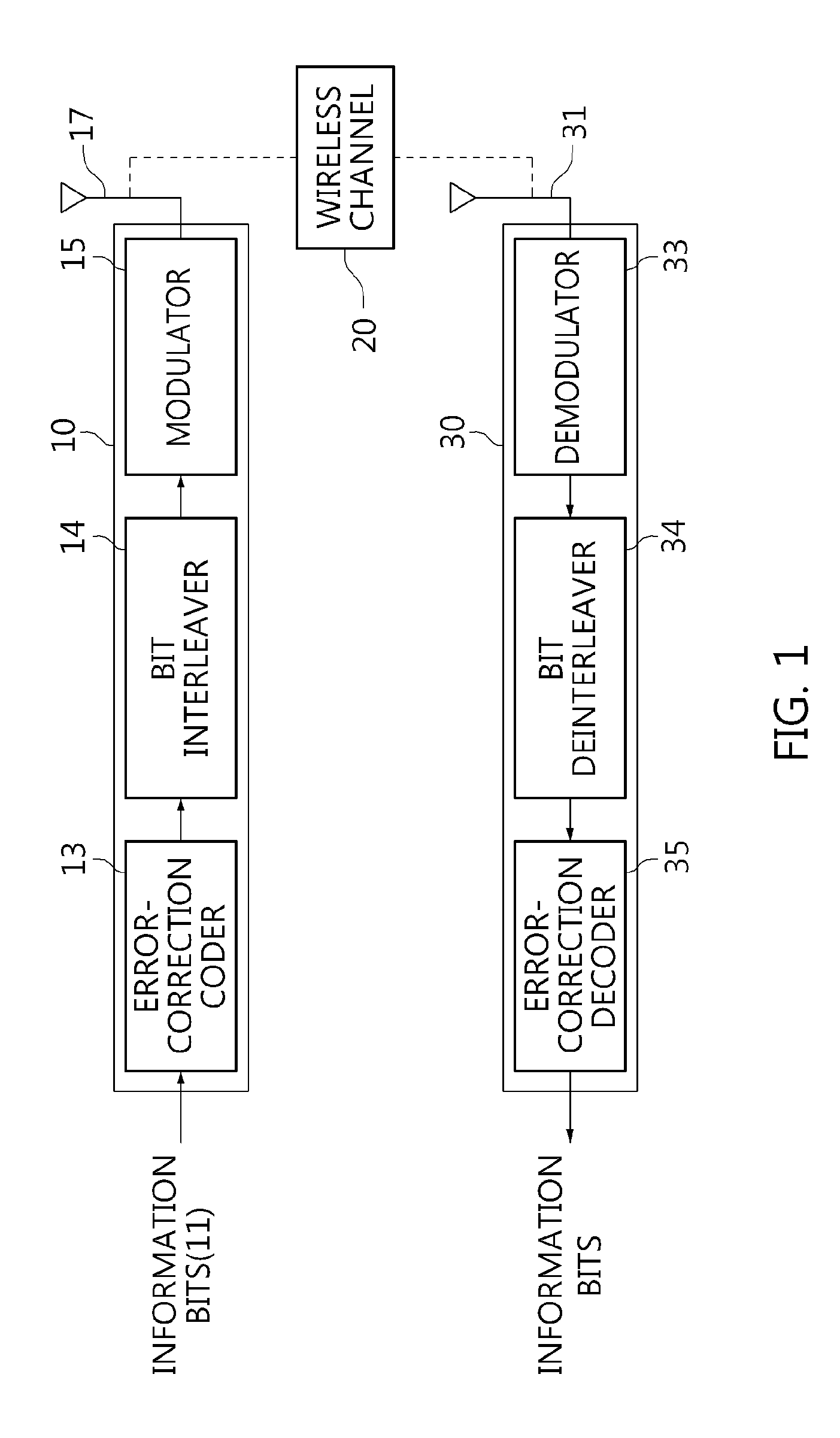

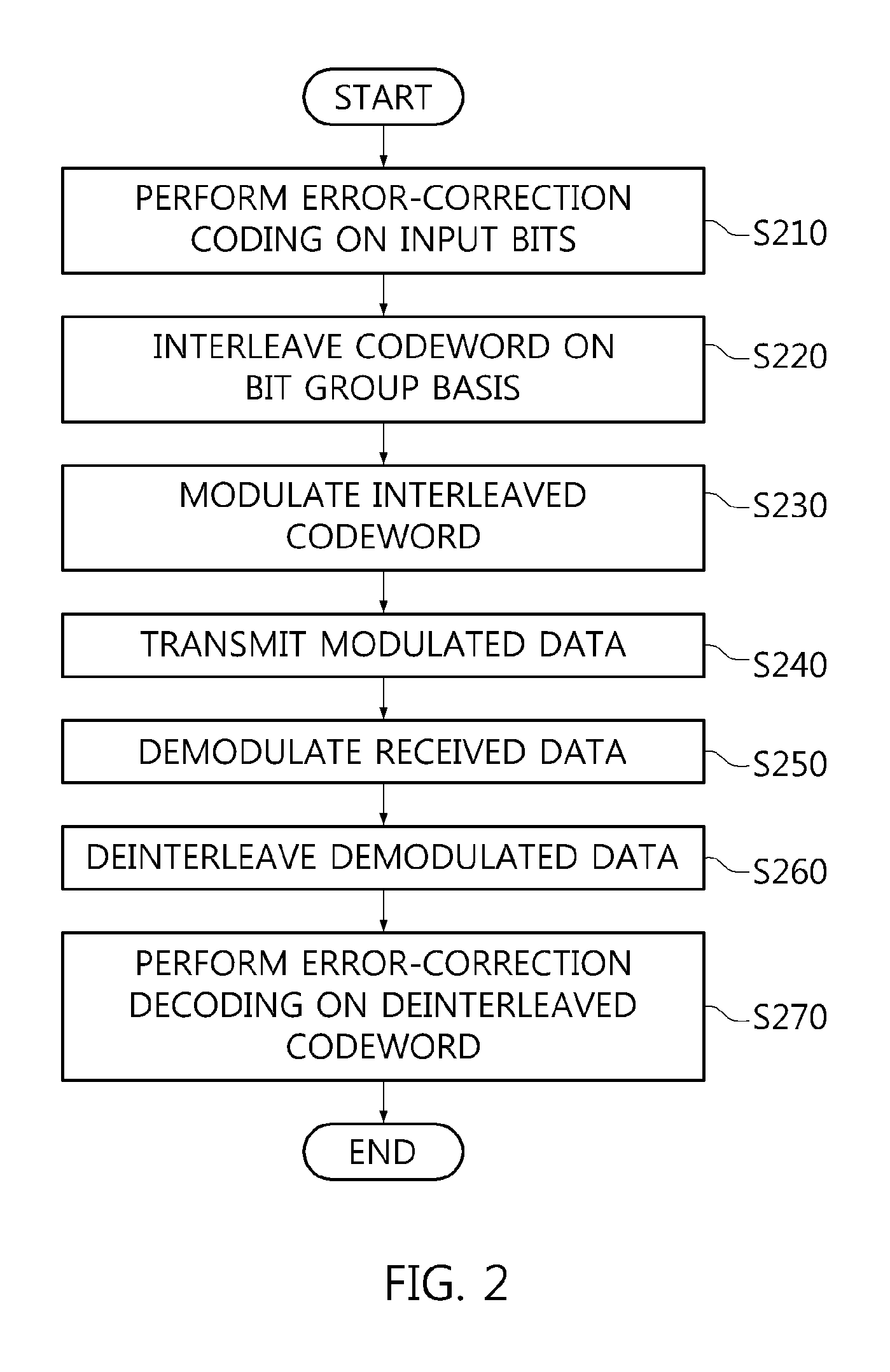

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 4 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 256-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 7/15 and quadrature phase shift keying, and bit interleaving method using same

ActiveUS20150214982A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow-density parity-check codeLow density

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 7 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for quadrature phase shift keying (QPSK) modulation.

Owner:ELECTRONICS & TELECOMM RES INST

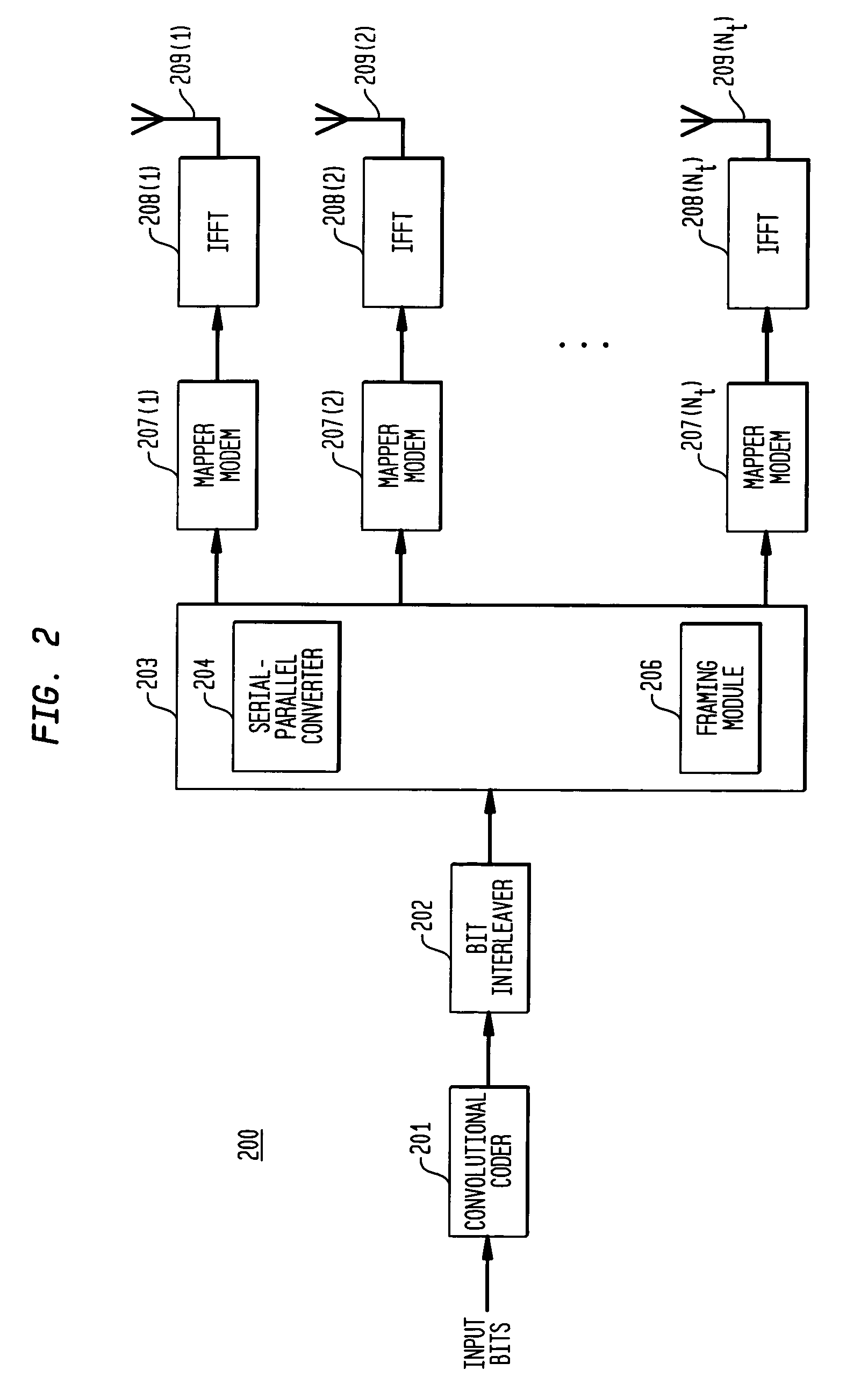

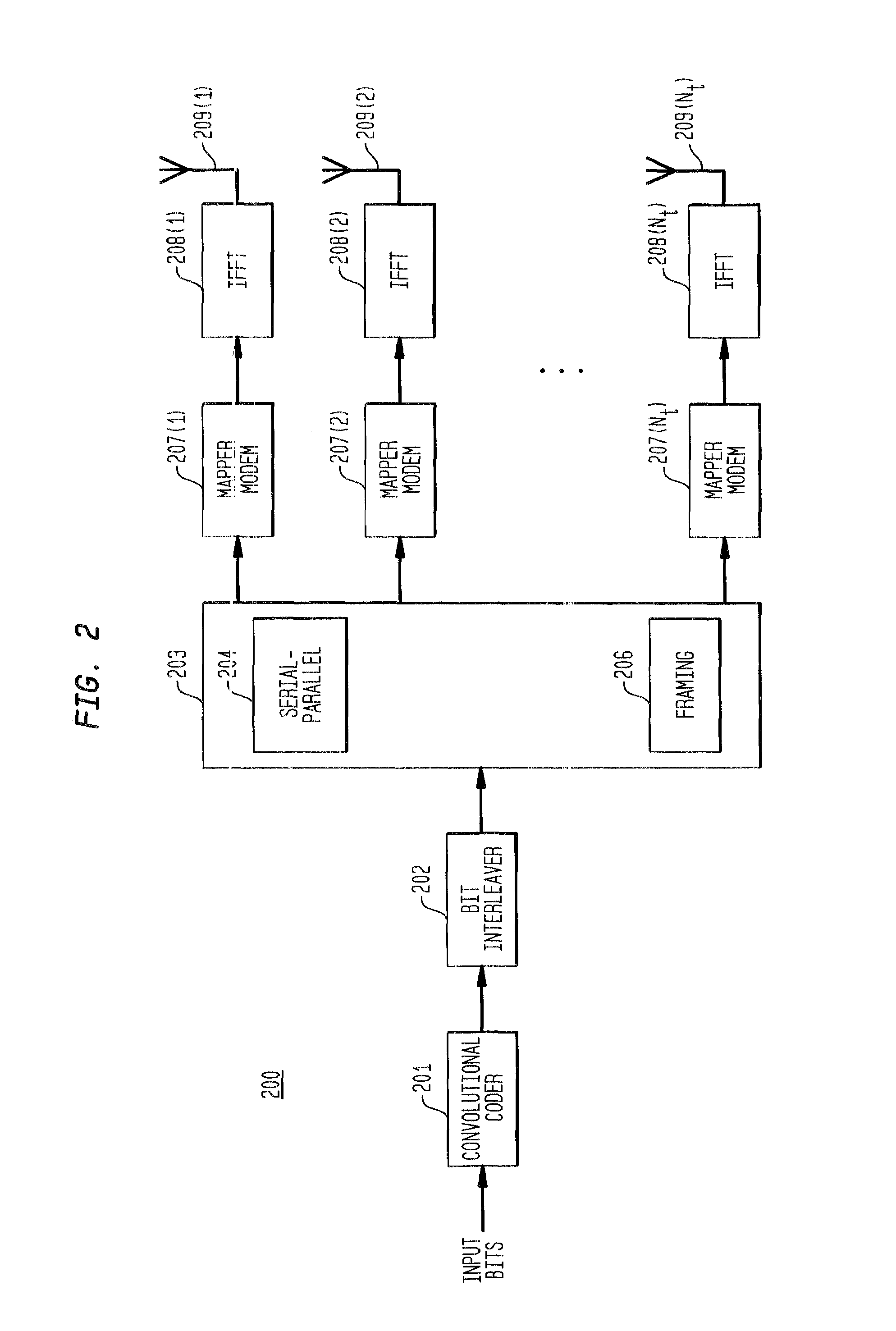

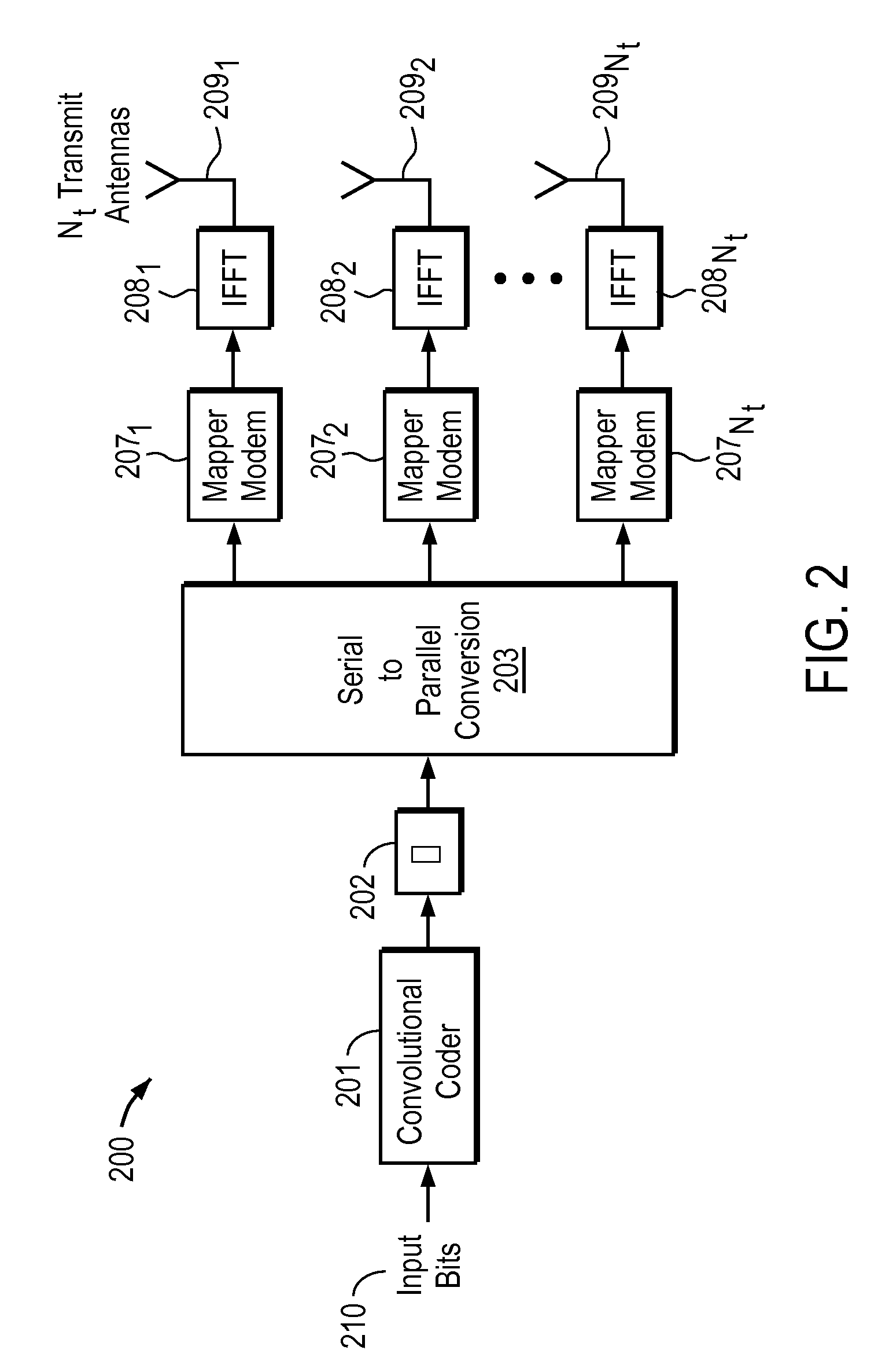

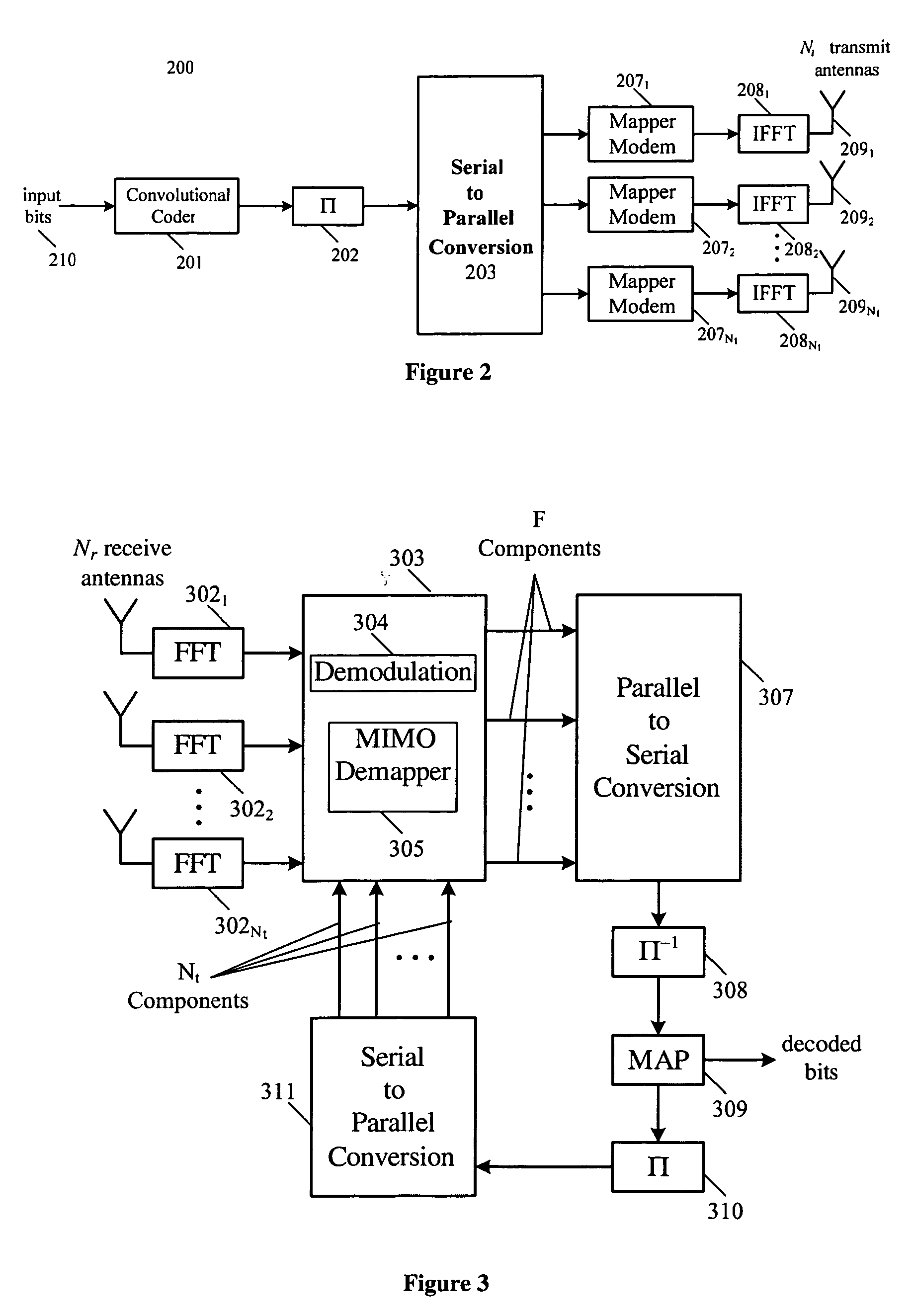

Space-time bit-interleaved coded modulation for wideband transmission

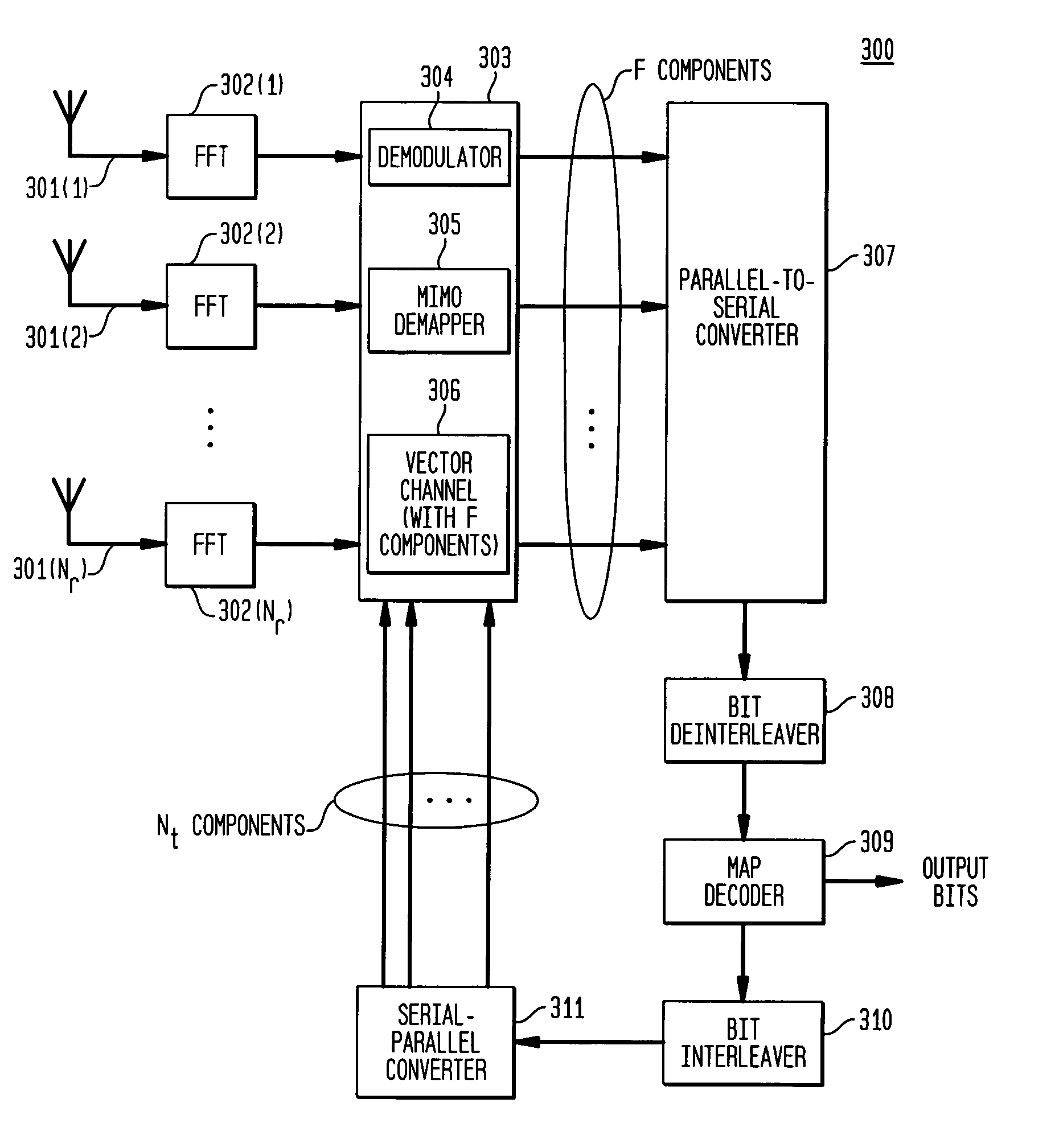

ActiveUS7359313B2Improve bit error rate performancePhase-modulated carrier systemsOrthogonal multiplexMulti inputBroadband transmission

A system employs space-time coding characterized at the transmitter by bit-interleaved coded modulation (BICM) combined with multi-carrier Orthogonal Frequency Division Multiplexing (OFDM) modulation. Space-Time coding techniques improve transmission efficiency in radio channels by using multiple transmit and / or receive antennas and coordination of the signaling over these antennas. Bit-interleaved coded modulation provides good diversity gain with higher-order modulation schemes that employ binary convolutional codes. OFDM modulation allows for wideband transmission over frequency selective radio channels. A receiver demodulates the OFDM signal and applies multi-input, multi-output (MIMO) demapping to estimate the BICM encoded bitstream. After deinterleaving of the BICM encoded bitstream, maximum a posteriori (MAP) decoding is applied to the resulting bit stream to generate soft output values. The MIMO demapping and MAP decoding processes exchange likelihood information to improve the bit error rate performance over several iterations of demapping / decoding. By applying well-known turbo-decoding principles to iteratively demap and decode, the overall receiver performance is significantly improved.

Owner:AVAGO TECH INT SALES PTE LTD

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 4096-symbol mapping, and bit interleaving method using same

ActiveUS20150280747A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsSymbol mappingLow-density parity-check code

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 5 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 4096-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 16-symbol mapping, and bit interleaving method using same

ActiveUS20150236722A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsSymbol mappingParallel computing

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 3 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 16-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 3/15 and quadrature phase shift keying, and bit interleaving method using same

ActiveUS20150341048A1Efficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow-density parity-check codeLow density

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 16200 and a code rate of 3 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for quadrature phase shift keying (QPSK) modulation.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 3/15 and 1024-symbol mapping, and bit interleaving method using same

ActiveUS20150270854A1Effective distributionEfficiently distributedError correction/detection using LDPC codesCode conversionBit interleaved coded modulationSymbol mapping

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 3 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 1024-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 5/15 and 64-symbol mapping, and bit interleaving method using same

ActiveUS20150236720A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsComputer hardwareSymbol mapping

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 5 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 64-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

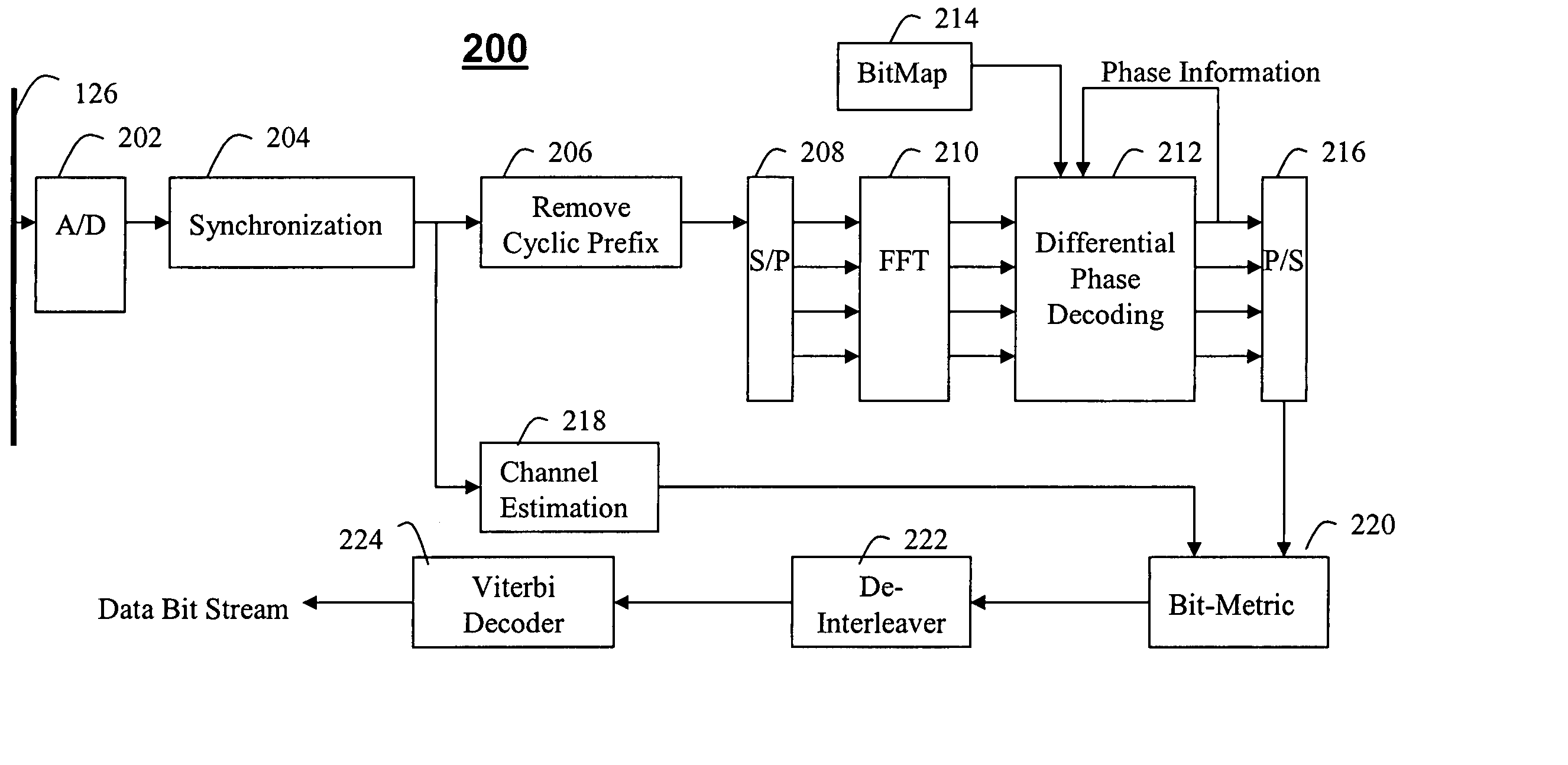

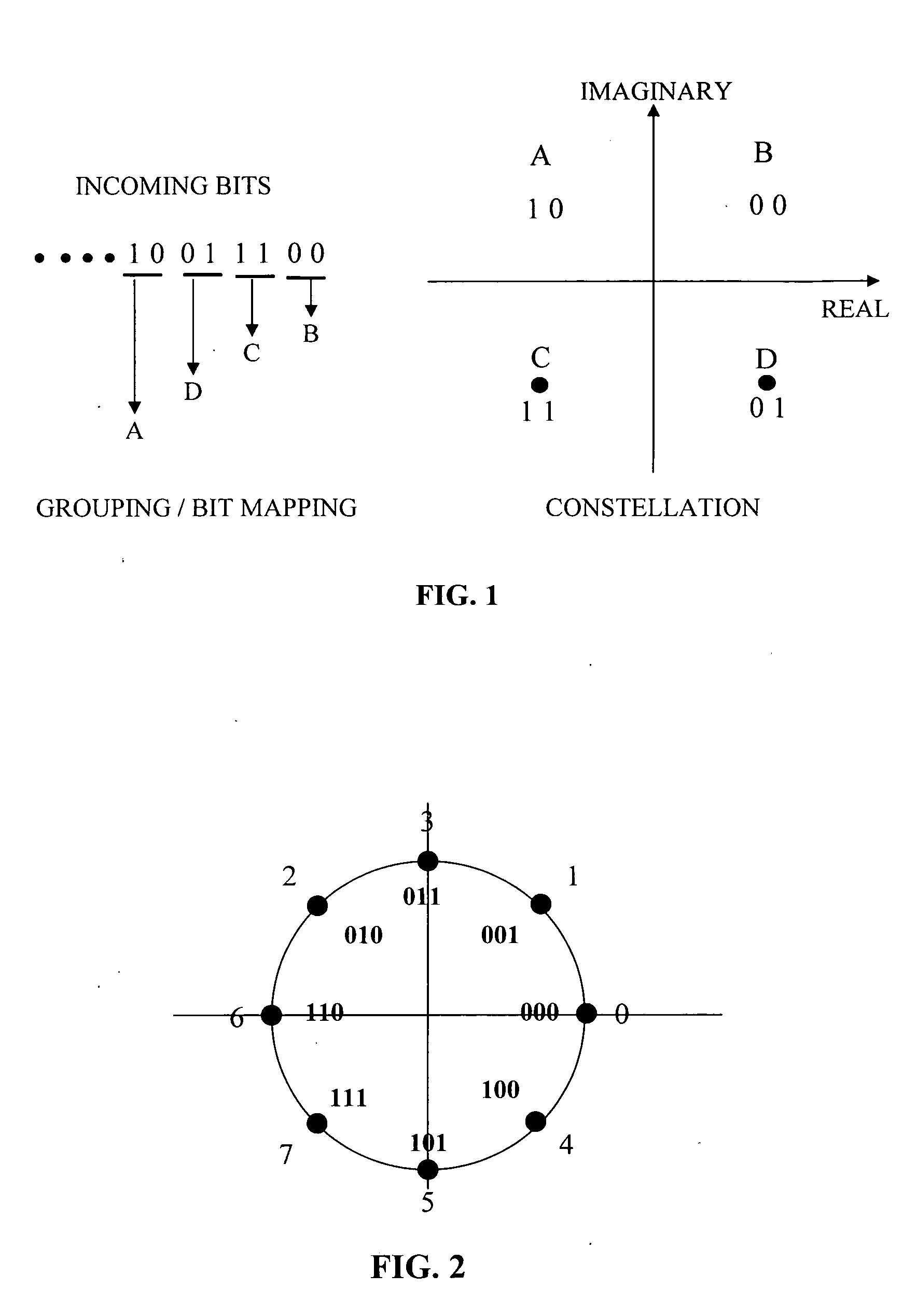

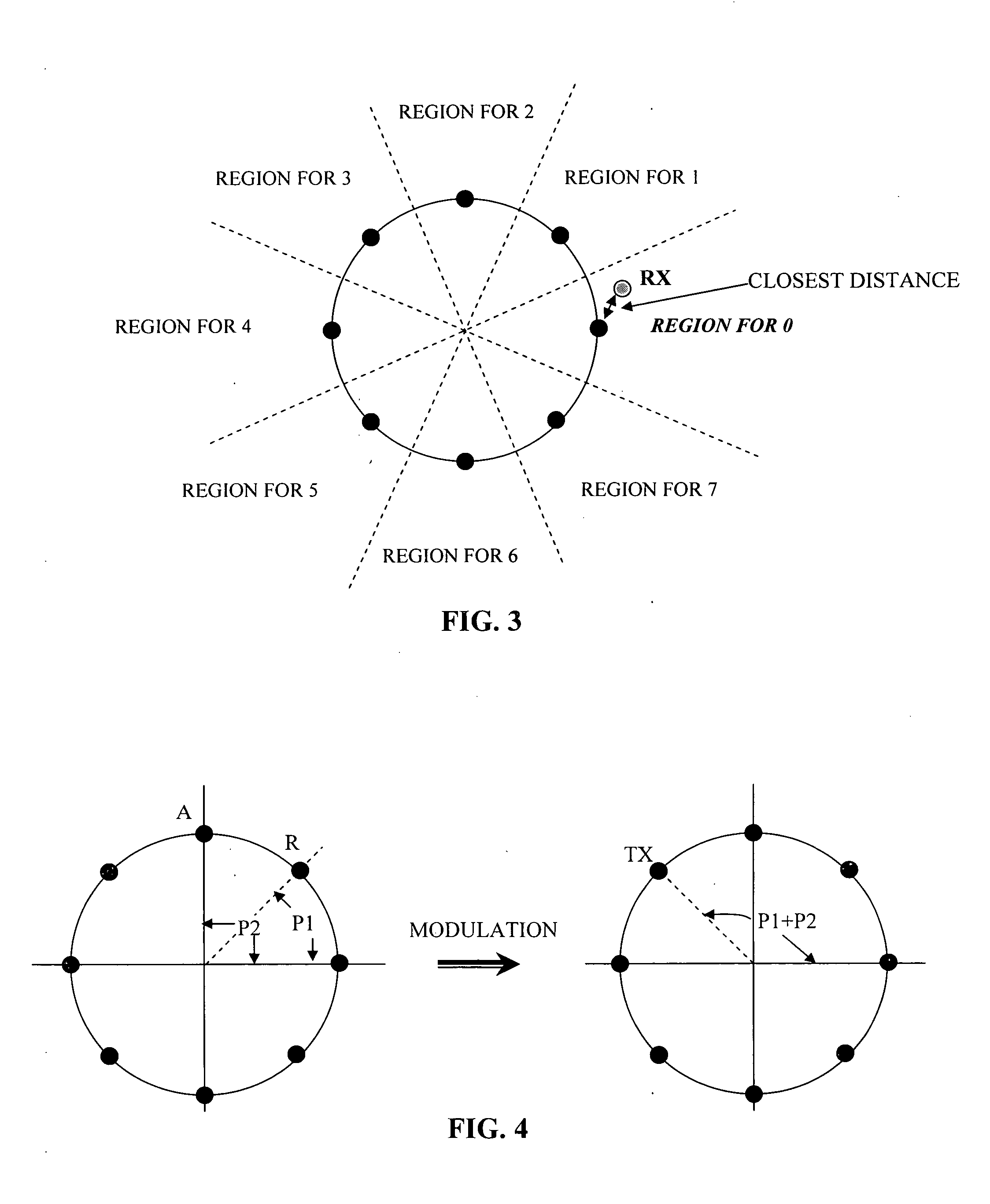

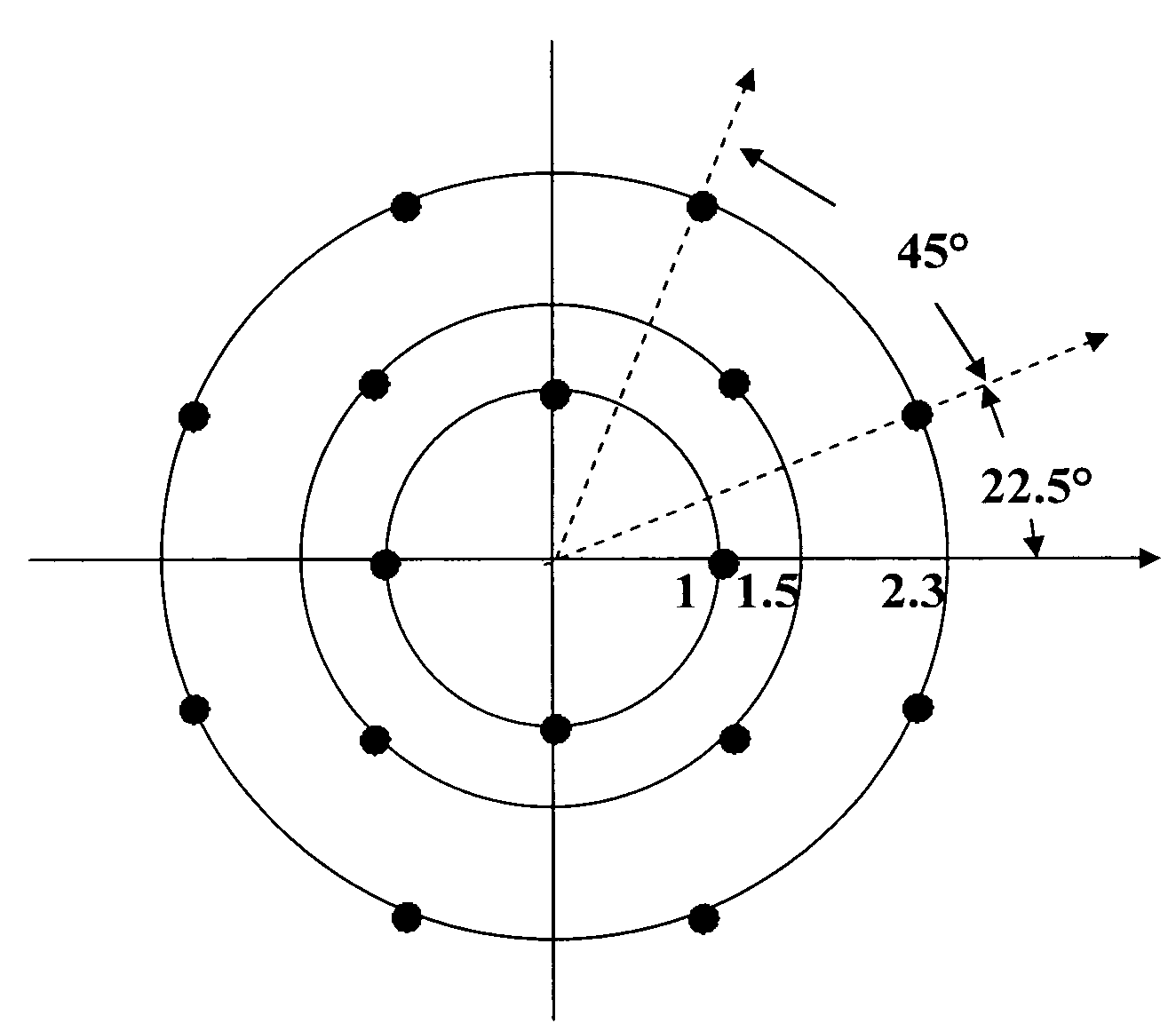

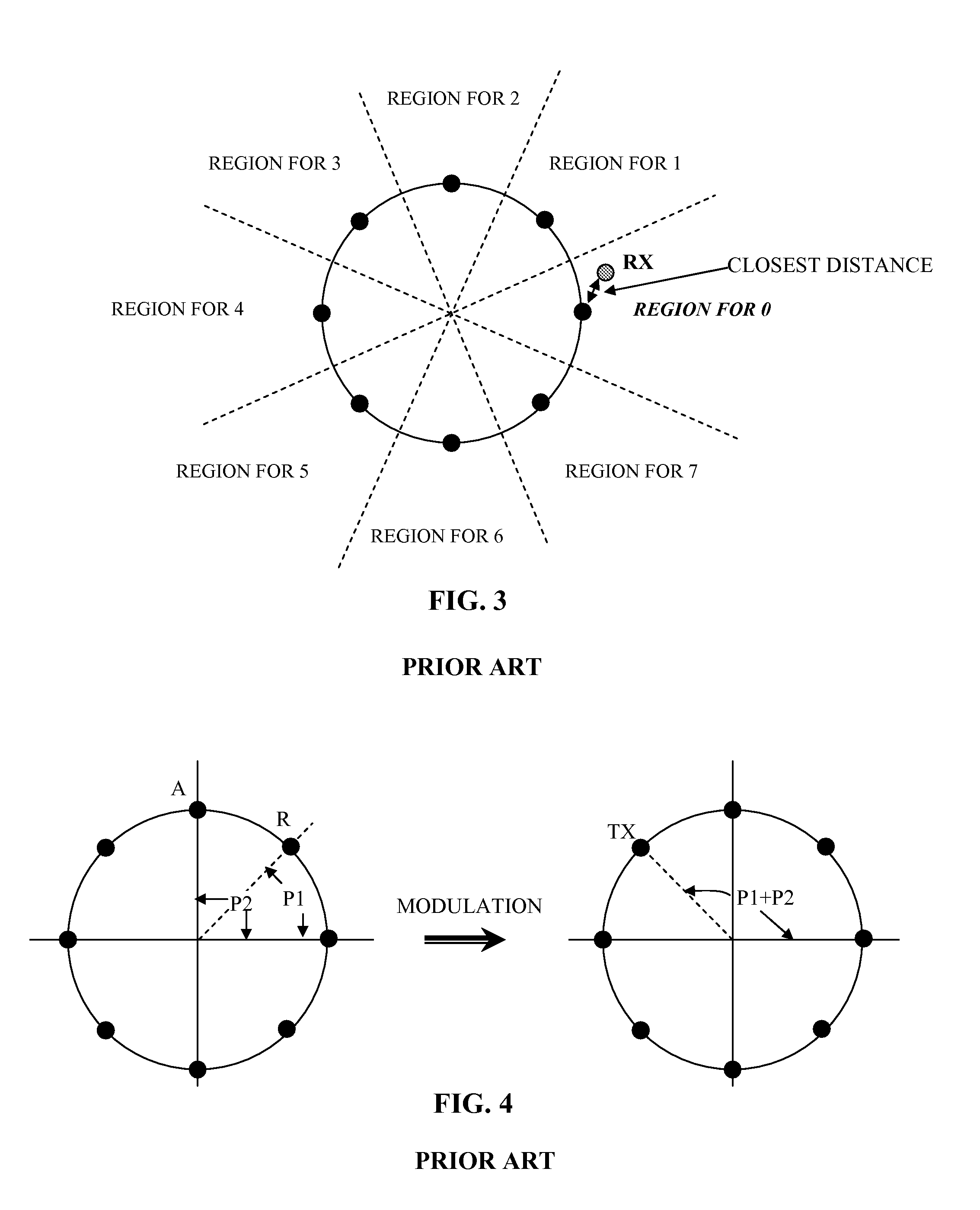

Multi-layer differential phase shift keying with bit-interleaved coded modulation and OFDM

InactiveUS20050111590A1Increase data rateEfficient methodAngle modulationSecret communicationEngineeringDifferential modulation

An efficient system and method for modulation and demodulation to achieve a high data rate using Bit-Interleaved Coded Modulation and OFDM uses either a coherent or a non-coherent transmission scheme using differential modulation. In order to maintain a high data rate impervious to sudden phase changes, a communication system uses an efficient constellation having multiple rings with different sizes and modulation / demodulation schemes utilizing this constellation. In power line communications, the channel gain information is obtained easily at a receiver (100) while the phase information is not. Thus, the communication system uses an absolute magnitude and differential phase coding for modulation and demodulation of the signals.

Owner:UNIV OF FLORIDA RES FOUNDATION INC +1

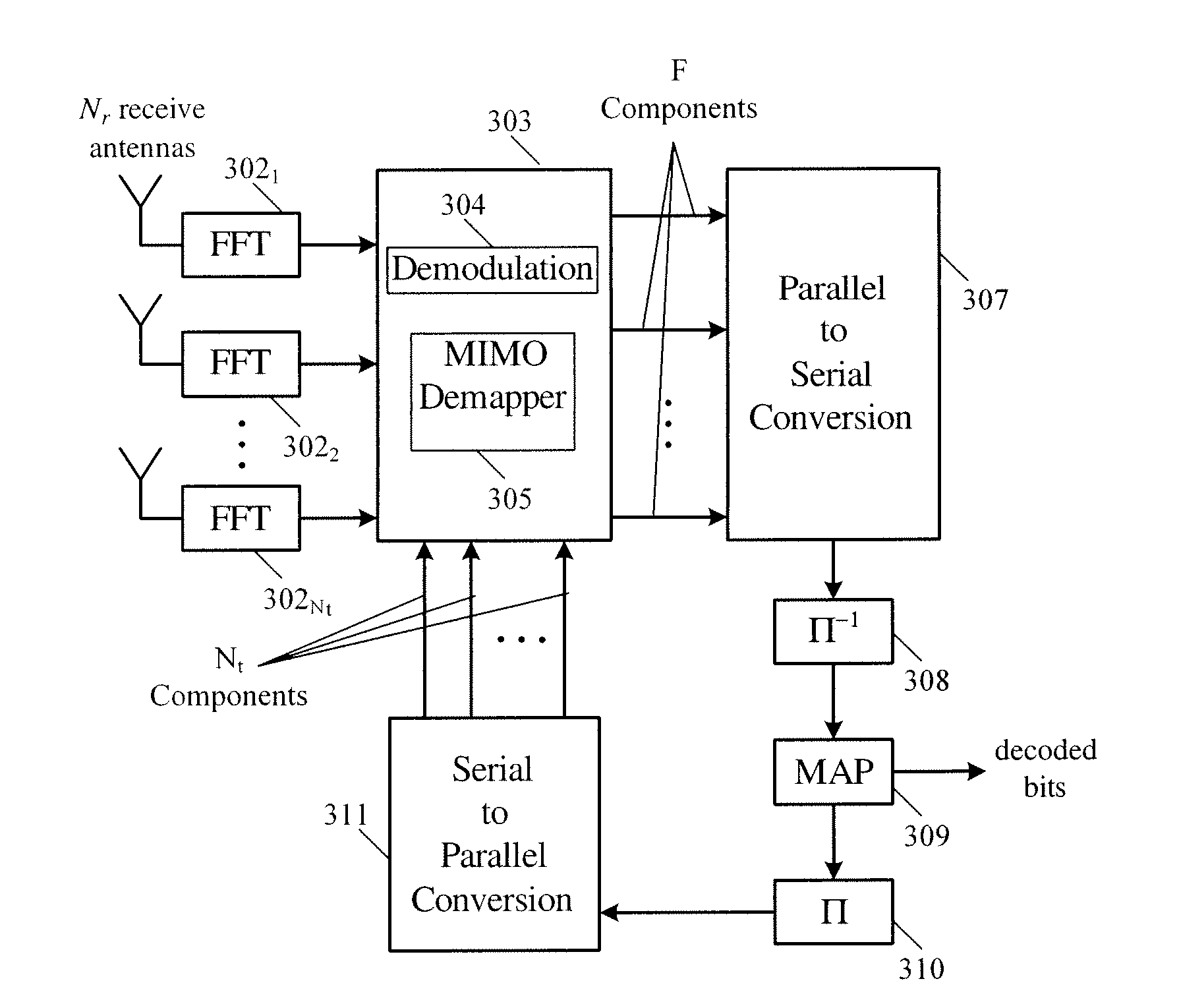

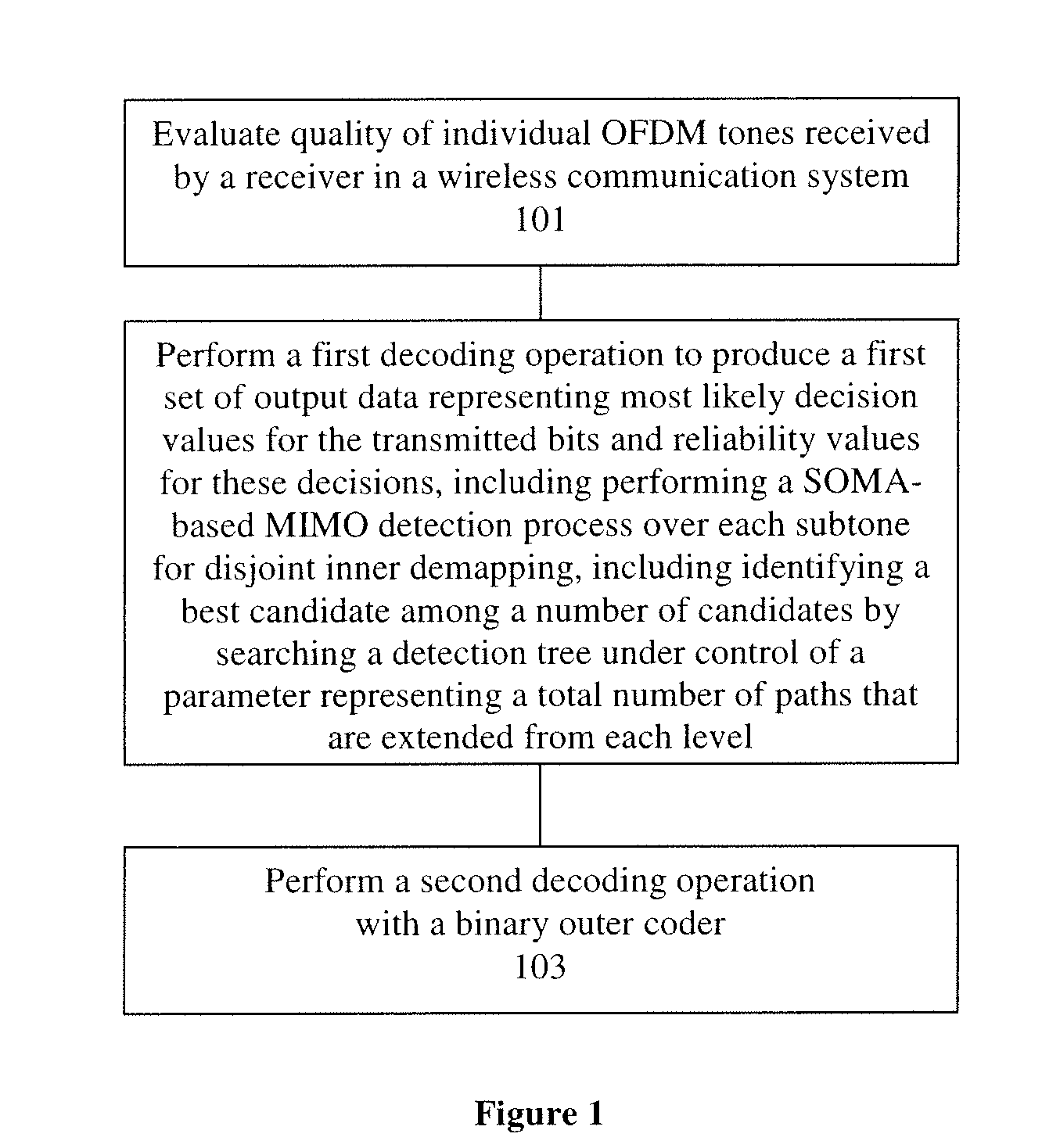

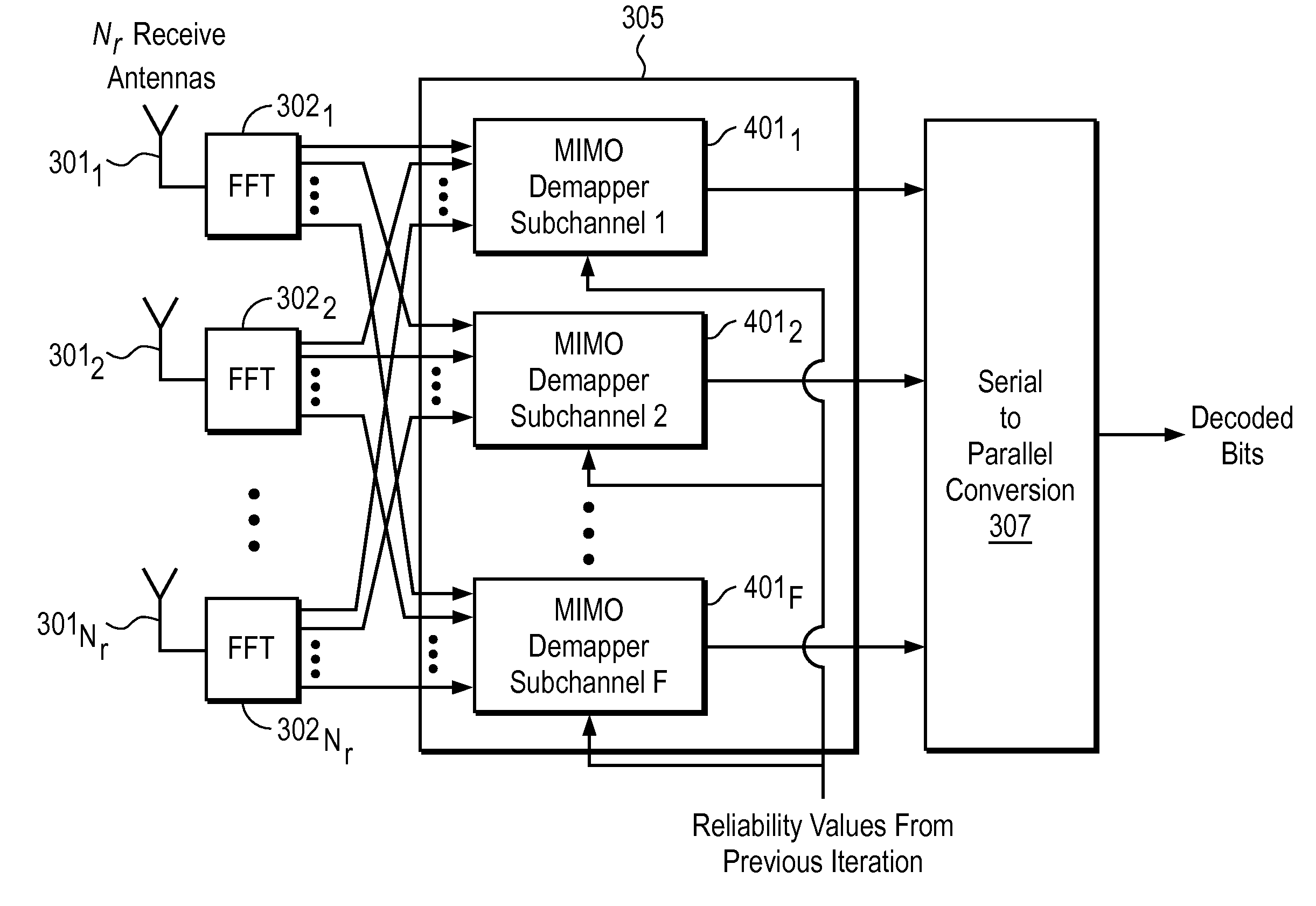

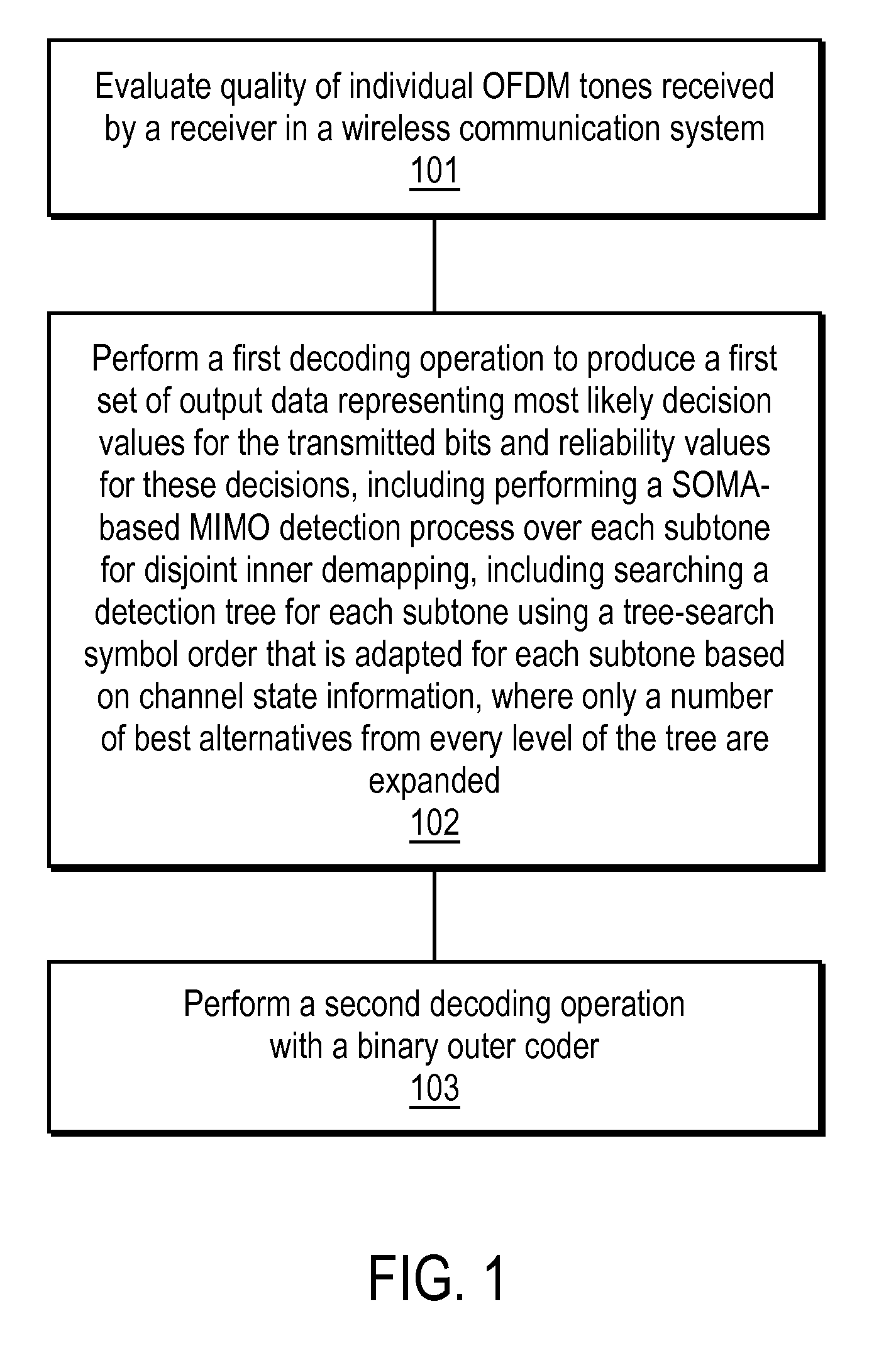

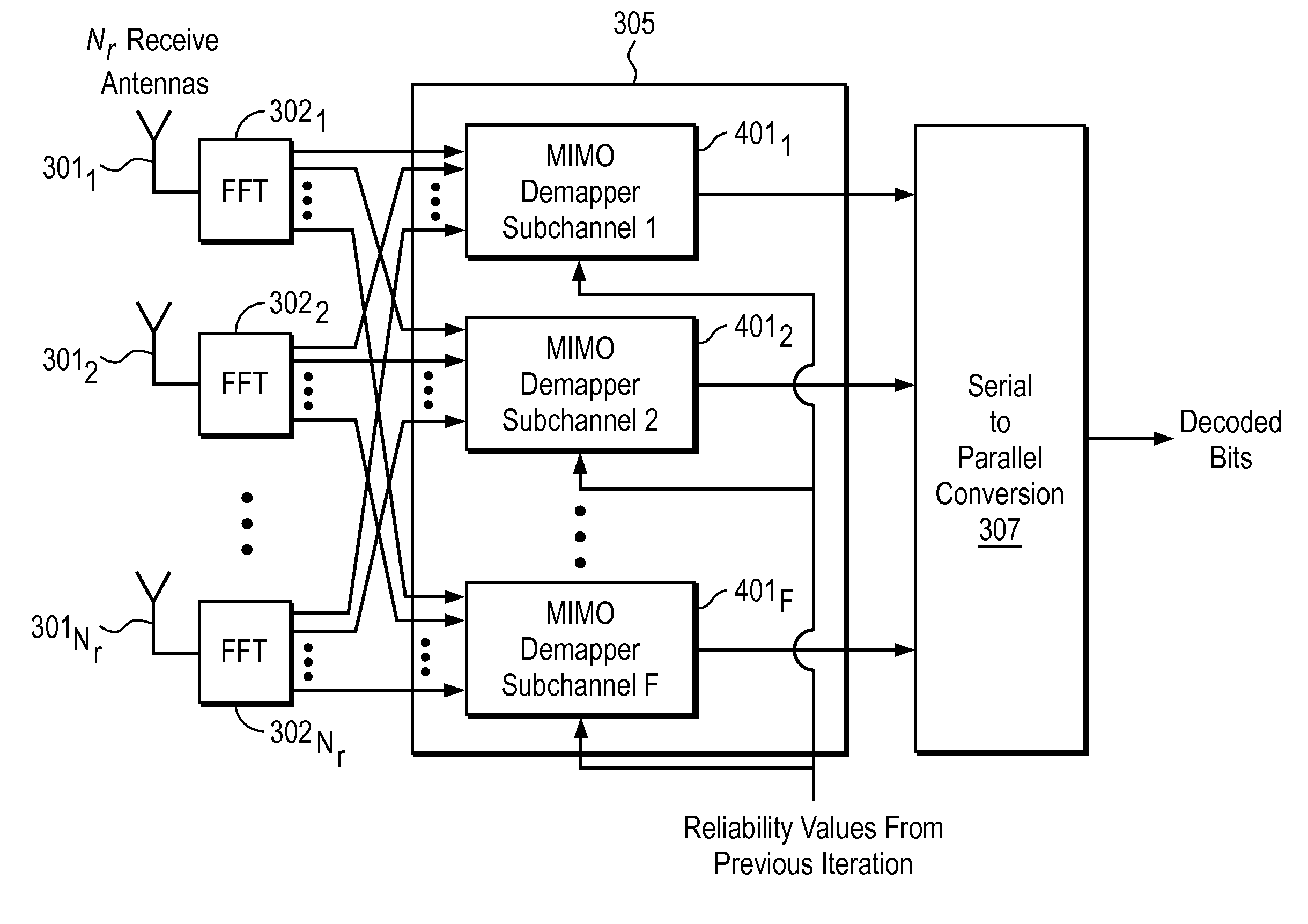

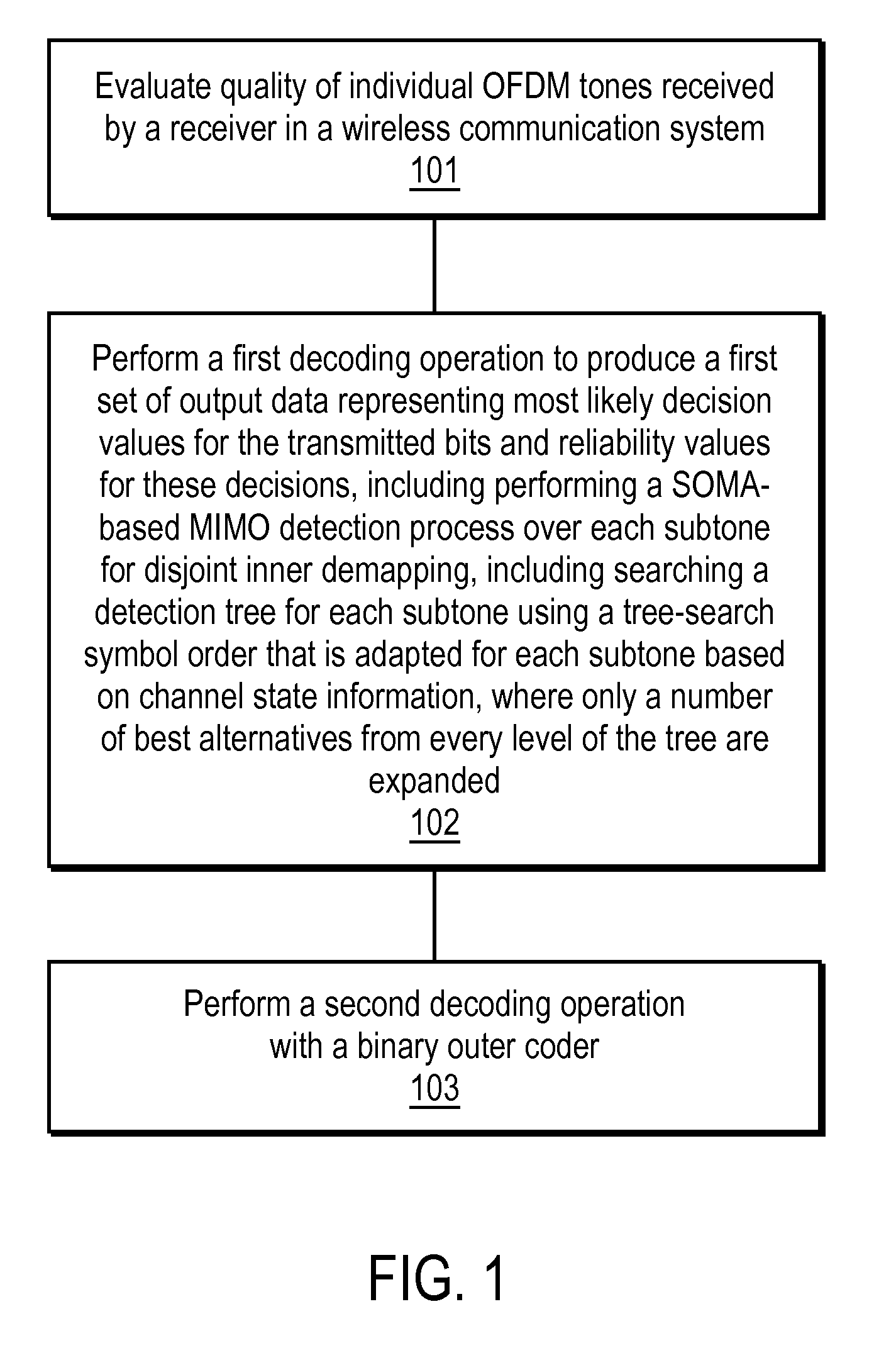

Adaptive soft output m-algorithm receiver structures

InactiveUS20090285323A1Diversity/multi-antenna systemsForward error control useCommunications systemEngineering

A method and apparatus is disclosed herein for adaptive soft output M-algorithm receiver structures. In one embodiment, a device for use in a wireless communication system includes a transmitter, and comprises of a receiver to receive information-bearing signals from the transmitter wirelessly transmitted using OFDM and bit interleaved coded modulation, where the receiver comprises an inner decoder structure having a soft output M-algorithm (SOMA) based multiple-in multiple-out (MIMO) joint demapper that uses a SOMA-based MIMO detection process to perform joint inner demapping over each subtone. The SOMA-based MIMO joint demapper is operable to identify a best candidate among a number of candidates by searching a detection tree under control of a parameter representing a total number of paths that are extended from each level, such that only a number of best alternatives from every level of the tree are expanded, wherein the SOMA-based MIMO detection process adapts one or more of the parameters based on tone quality.

Owner:NTT DOCOMO INC

Bit interleaver for low-density parity check codeword having length of 16200 and code rate of10/15 and 256-symbol mapping, and bit interleaving method using same

ActiveUS20150339191A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsSymbol mappingParallel computing

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 16200 and a code rate of 10 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 256-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Bit interleaver for low-density parity check codeword having length of 16200 and code rate of 4/15 and 16-symbol mapping, and bit interleaving method using same

ActiveUS20150339190A1Effective distributionEfficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsSymbol mappingParallel computing

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 16200 and a code rate of 4 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 16-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Tree position adaptive soft output m-algorithm receiver structures

ActiveUS20090213954A1Combined modulated pulse demodulationLine-faulsts/interference reductionChannel state informationCommunications system

A method and apparatus for tree position adaptive SOMA receiver structures are disclosed herein. In one embodiment, a device for use in a wireless communication system comprises a receiver to receive information-bearing signals from the transmitter wirelessly transmitted using OFDM and bit interleaved coded modulation, where the receiver includes an inner decoder structure having a soft output M-algorithm (SOMA) based multiple-in multiple-out (MIMO) joint demapper that uses a SOMA-based MIMO detection process to perform joint inner demapping over each tone, and wherein the SOMA-based MIMO joint demapper is operable to search a detection tree for each tone using a tree-search symbol order that is adapted for each tone based on channel state information and extrinsic information from the outer decoder, where only a number of best alternatives from every level of the tree are expanded.

Owner:NTT DOCOMO INC

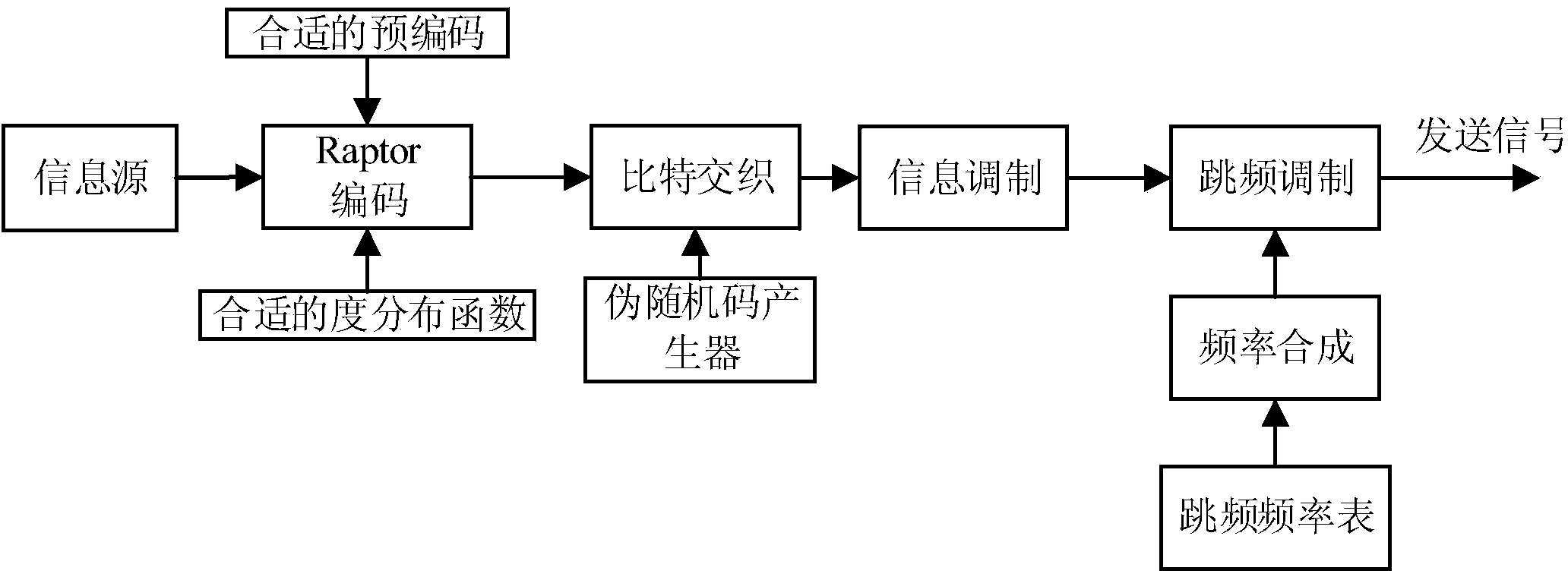

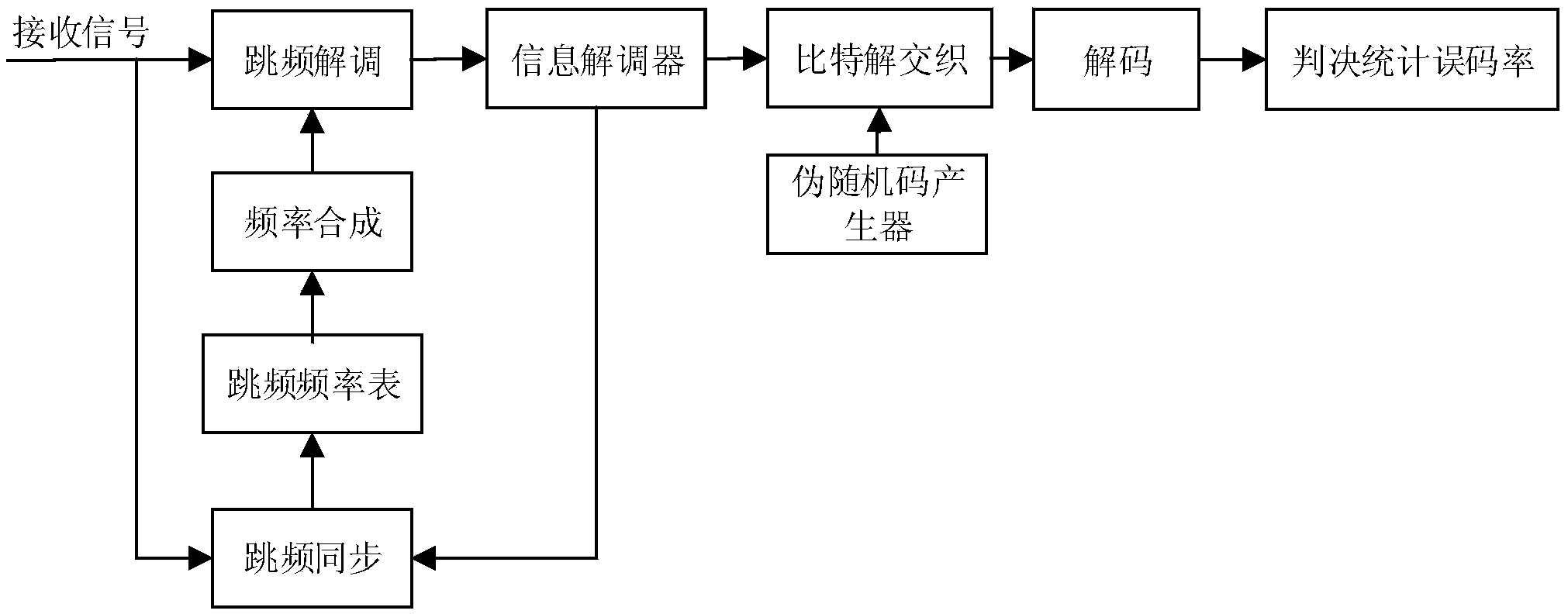

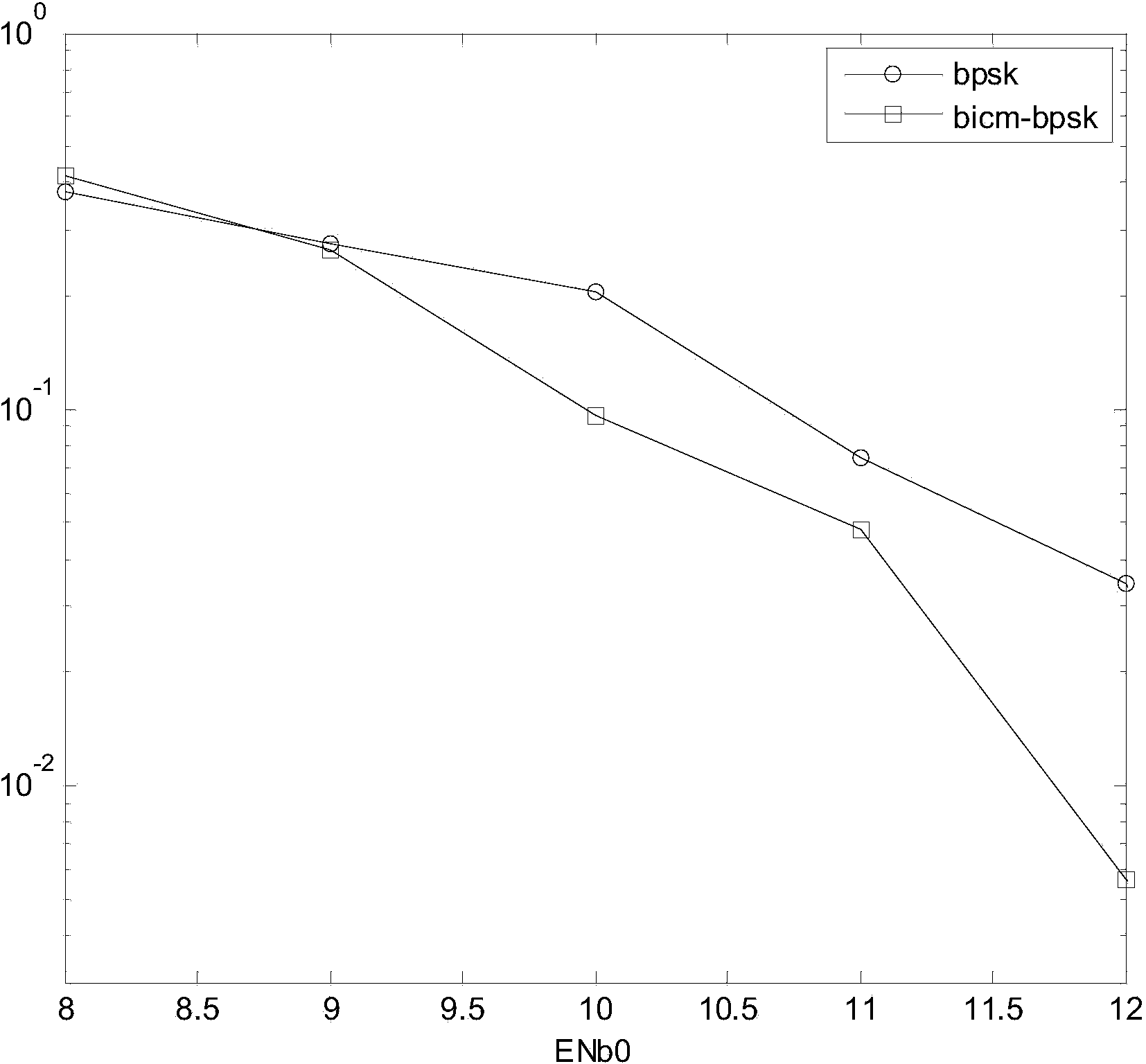

Frequency hopping fountain code system and transmission method thereof

InactiveCN103532663AImprove reliabilityTransmission rate impactError preventionCommunications systemFountain code

The invention relates to a frequency hopping fountain code system and a transmission method thereof, in particular to a transmission method of a frequency hopping fountain code system introduced by using a novel interweaving technology, and belongs to relevant technical fields of wireless communication systems, communication signal processing, channel coding and decoding and the like. The frequency hopping fountain code system can be used for transmitting data under the condition that a part of frequency points are blocked completely under the action of interference, so that the reliability of a communication system in a severe channel environment is enhanced. A bit-interleaved coded modulation technology is adopted, so that the bit error rate performance of the system is improved. Meanwhile, the redundancy is not increased, so that the rate of information transmission is not influenced. A bit-level interleaver is adopted, and can be used for encrypting under the condition that an interleaving rule cannot be obtained by an enemy, so that the safety of information transmission is enhanced.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

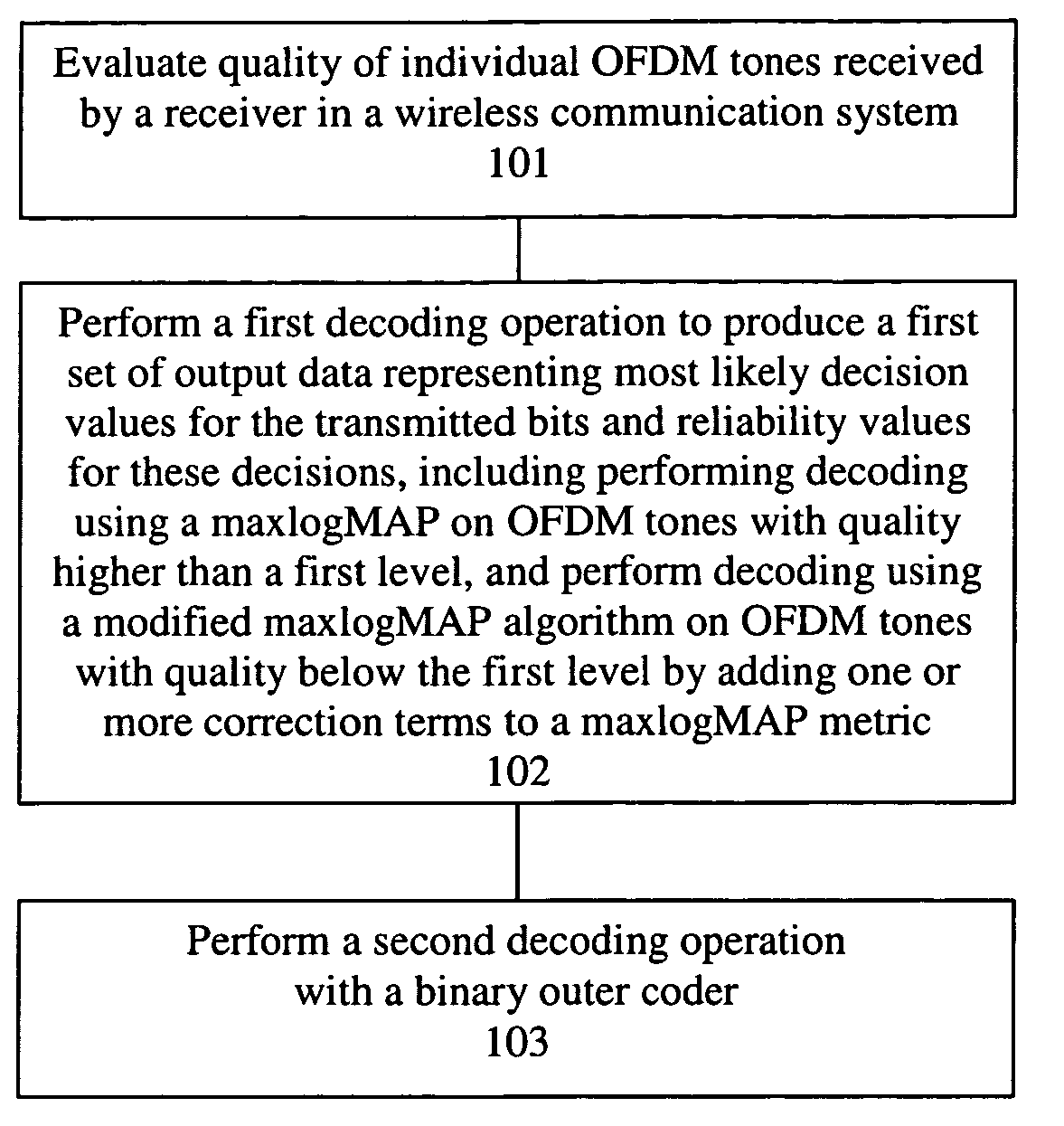

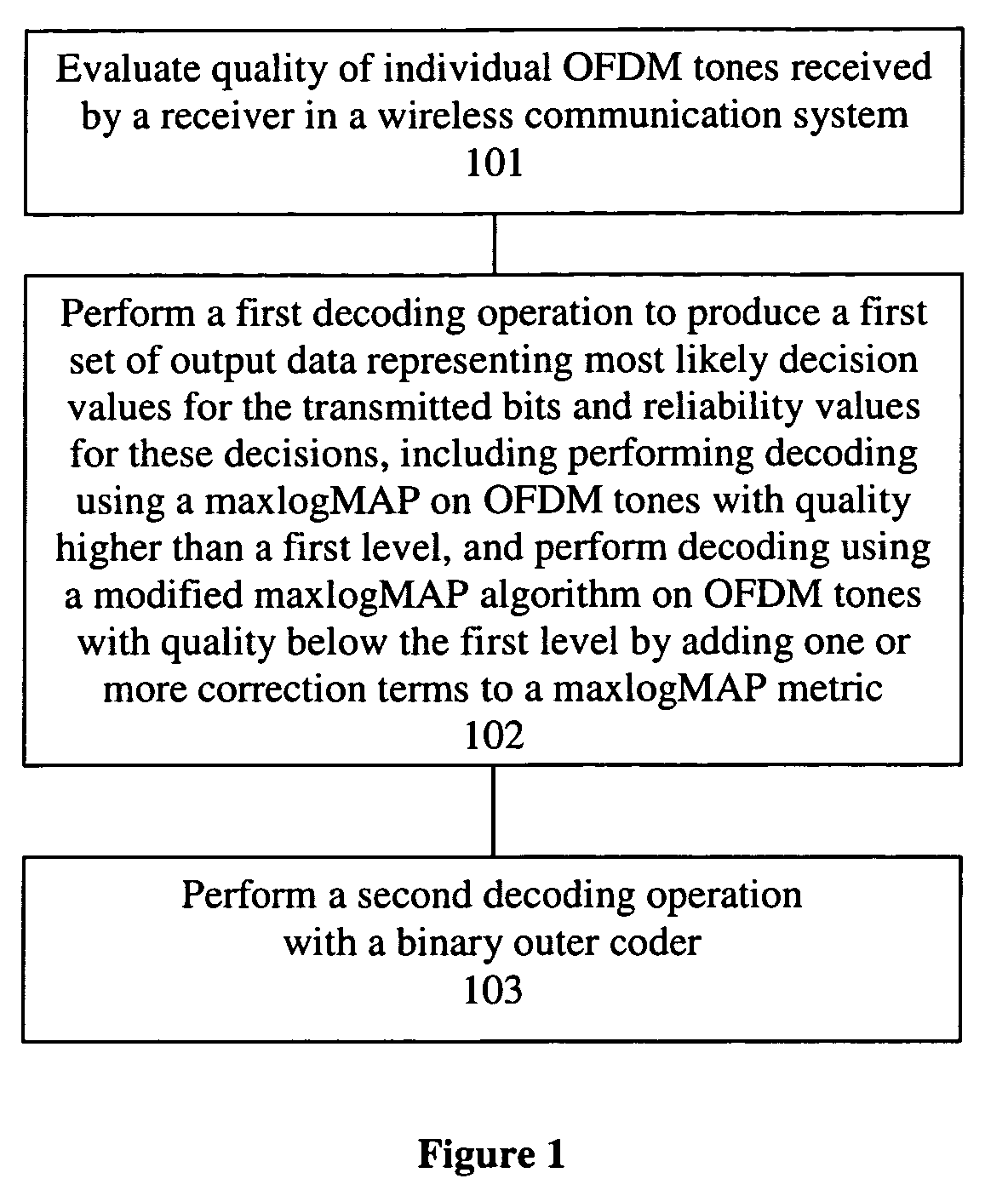

Adaptive maxlogmap-type receiver structures

ActiveUS20080285671A1Code conversionAmplitude-modulated carrier systemsEngineeringBit interleaved coded modulation

A method and apparatus is disclosed herein for adaptive MaclogMAP-type receiver structures. In one embodiment, a device comprises a receiver to receive information-bearing signals from the transmitter wirelessly transmitted using OFDM and bit interleaved coded modulation, and the receiver comprises an inner decoder structure having a multiple-in multiple-out (MIMO) joint demapper to perform most likely transmitted symbol estimation using a modified MaxLogMAP process that is operable to adapt a degree of metric correction based on quality of OFDM tones.

Owner:GOOGLE LLC

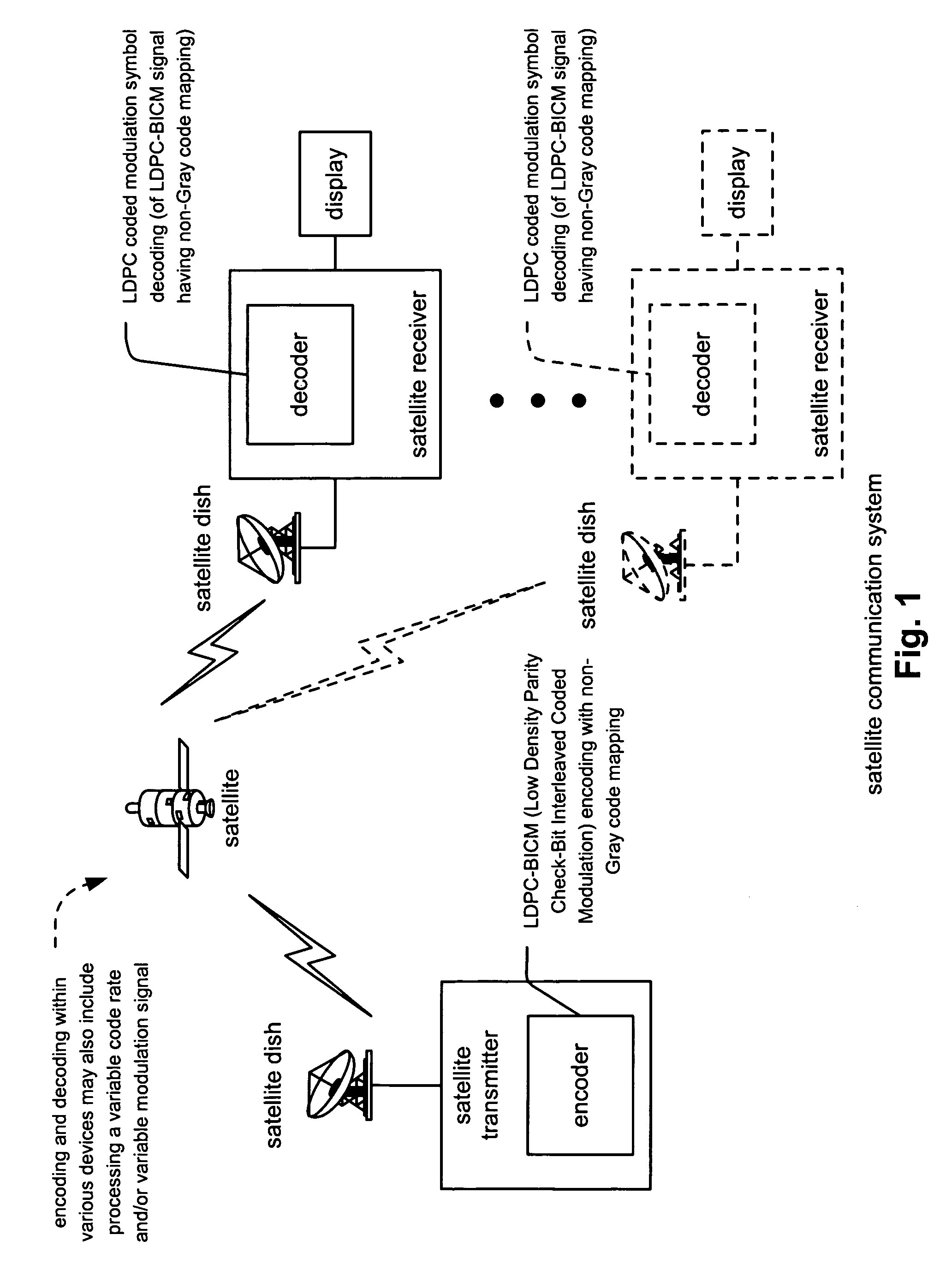

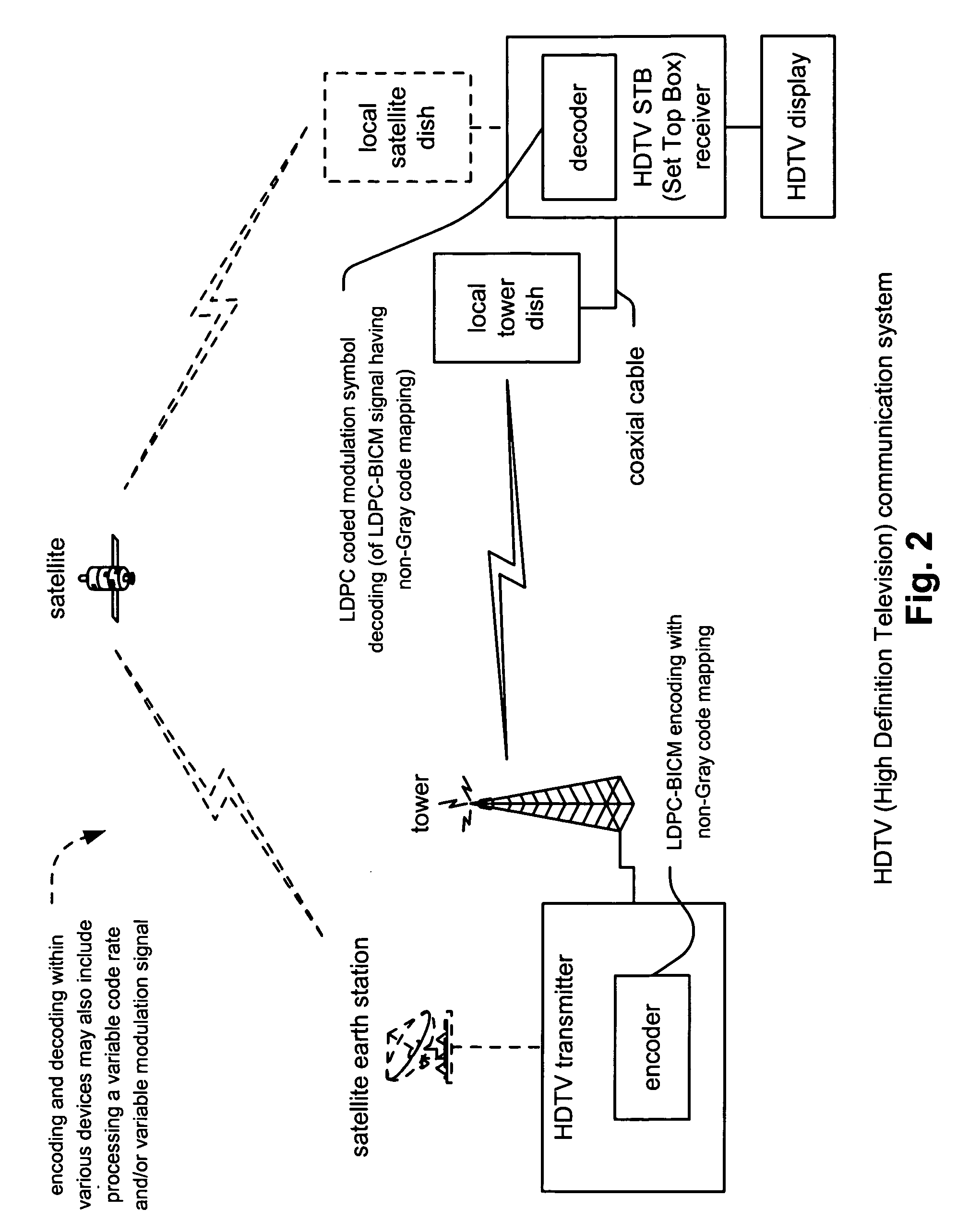

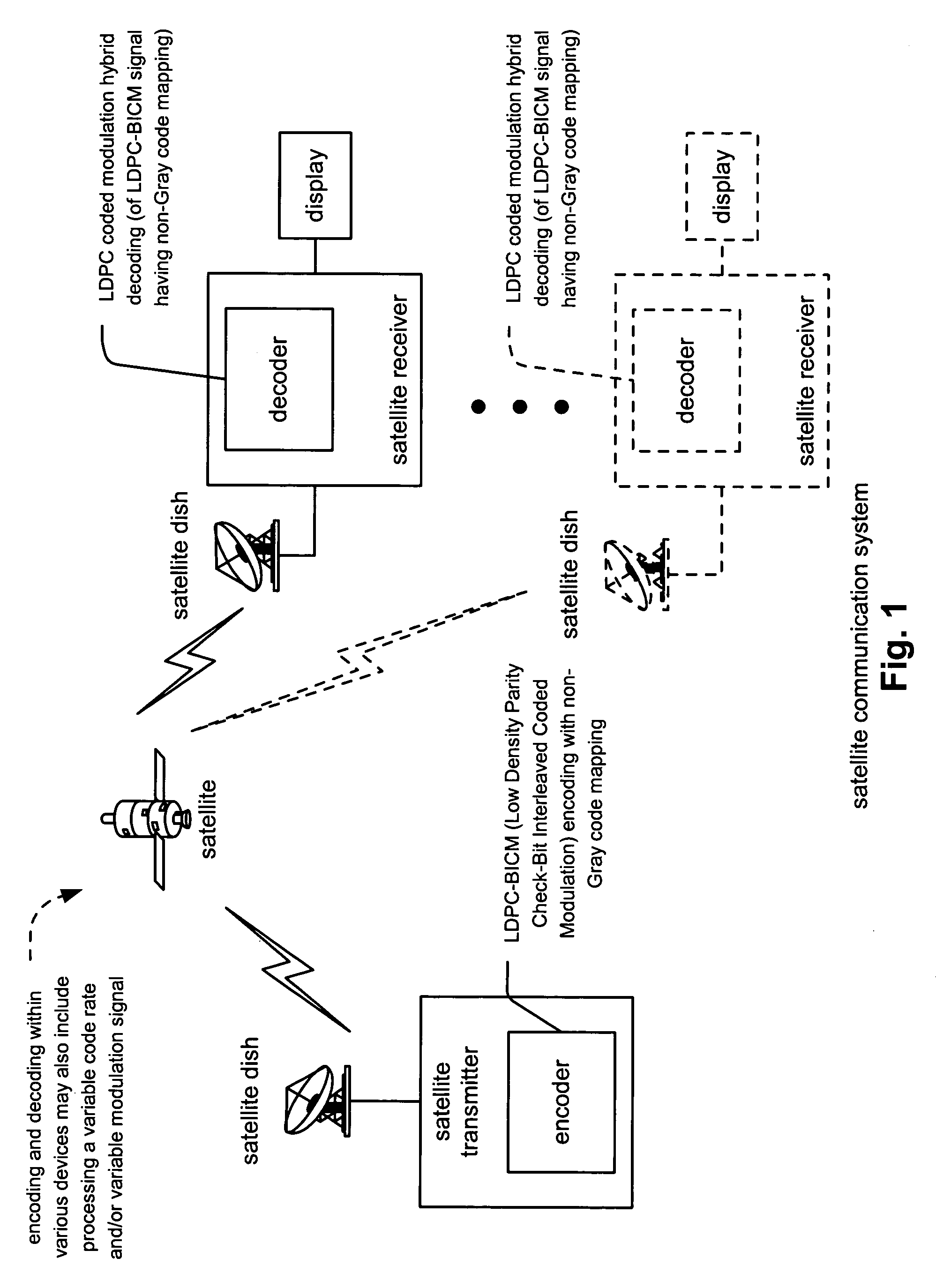

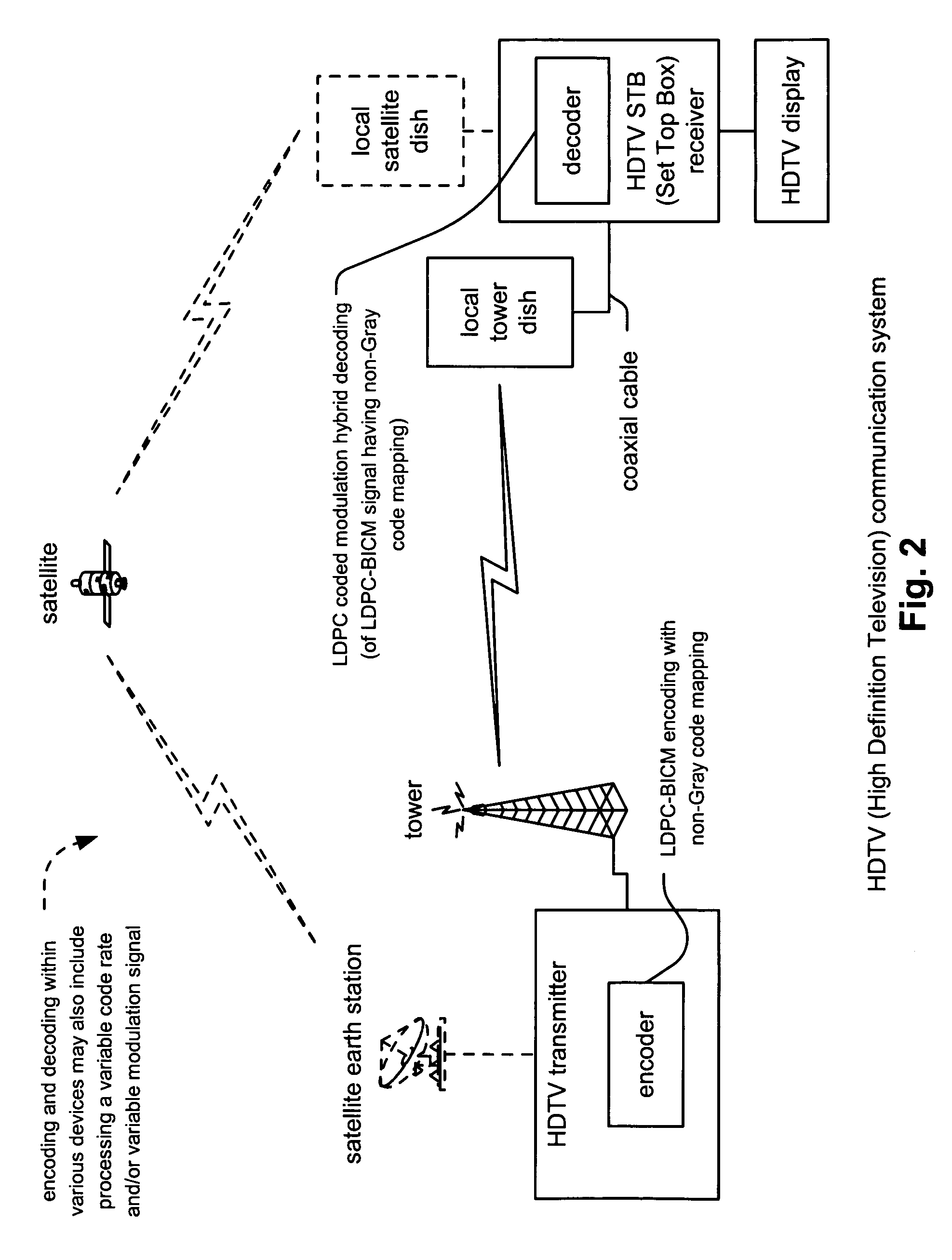

LDPC (Low Density Parity Check) coded modulation symbol decoding using non-Gray code maps for improved performance

InactiveUS7322005B2Reduce complexityError prevention/detection by using return channelOther decoding techniquesSymbol decodingTheoretical computer science

LDPC (Low Density Parity Check) coded modulation symbol decoding using non-Gray code maps for improved performance. Symbol decoding is supported by appropriately modifying an LDPC tripartite graph to eliminate the bit nodes thereby generating an LDPC bipartite graph (such that symbol nodes are appropriately mapped directly to check nodes thereby obviating the bit nodes). The edges that communicatively couple the symbol nodes to the check nodes are labeled appropriately to support symbol decoding of the LDPC coded modulation signal. In addition, the LDPC coded modulation symbol decoding can be employed to decode a signal that has been encoded using LDPC-BICM (Low Density Parity Check-Bit Interleaved Coded Modulation) encoding with non-Gray code mapping. By using the non-Gray code mapping, a performance improvement over such a system using only Gray code mapping may be achieved.

Owner:AVAGO TECH INT SALES PTE LTD

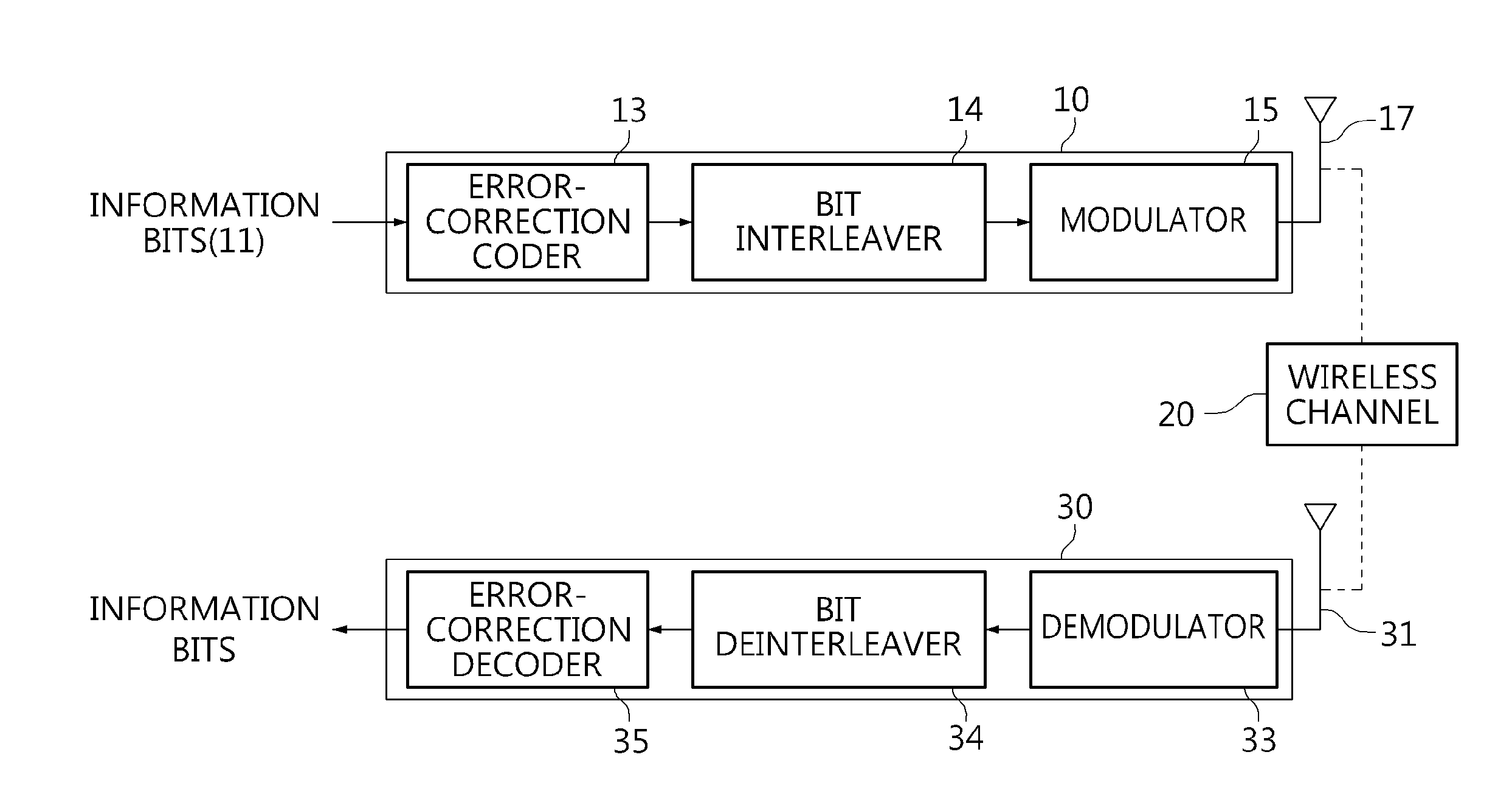

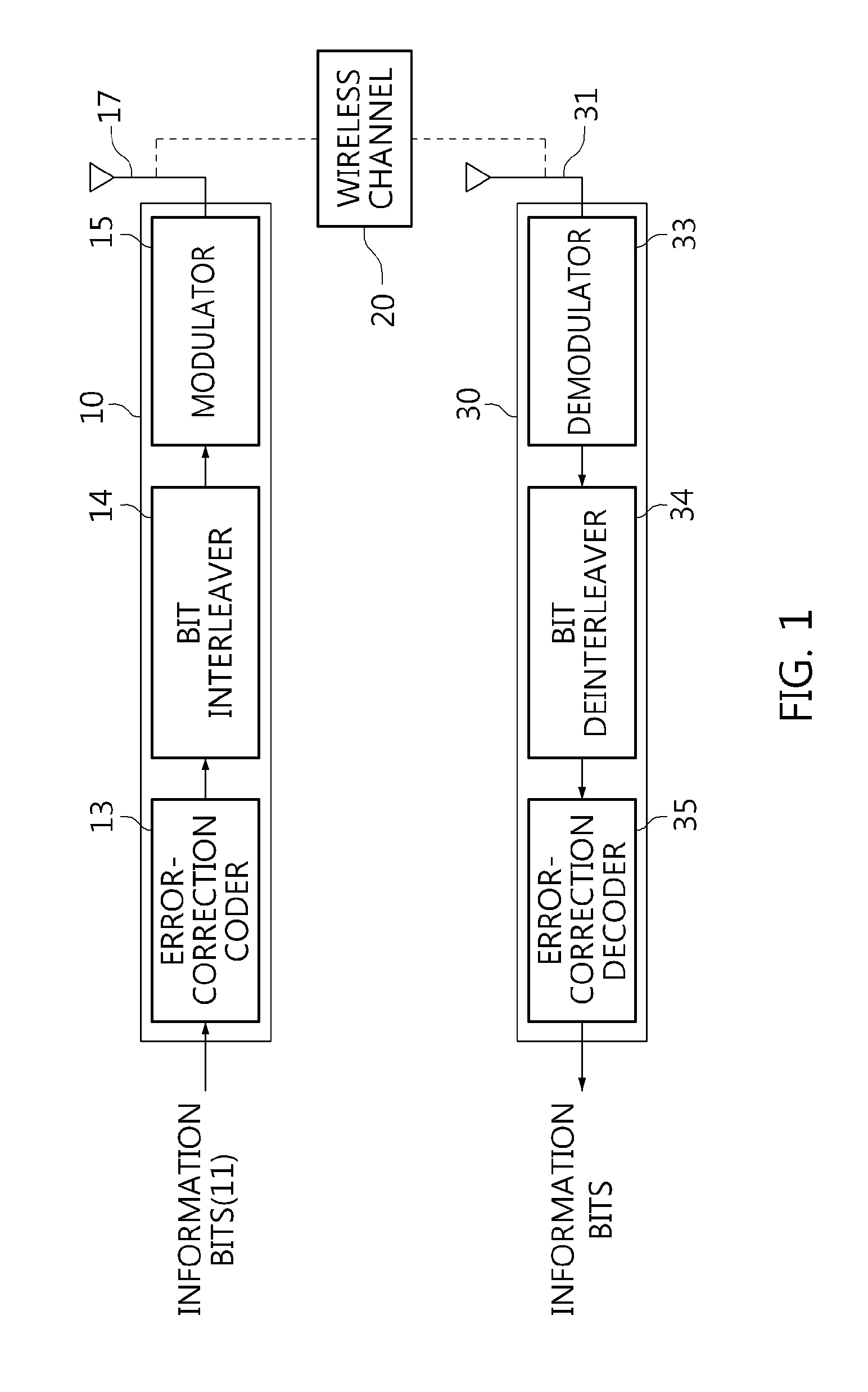

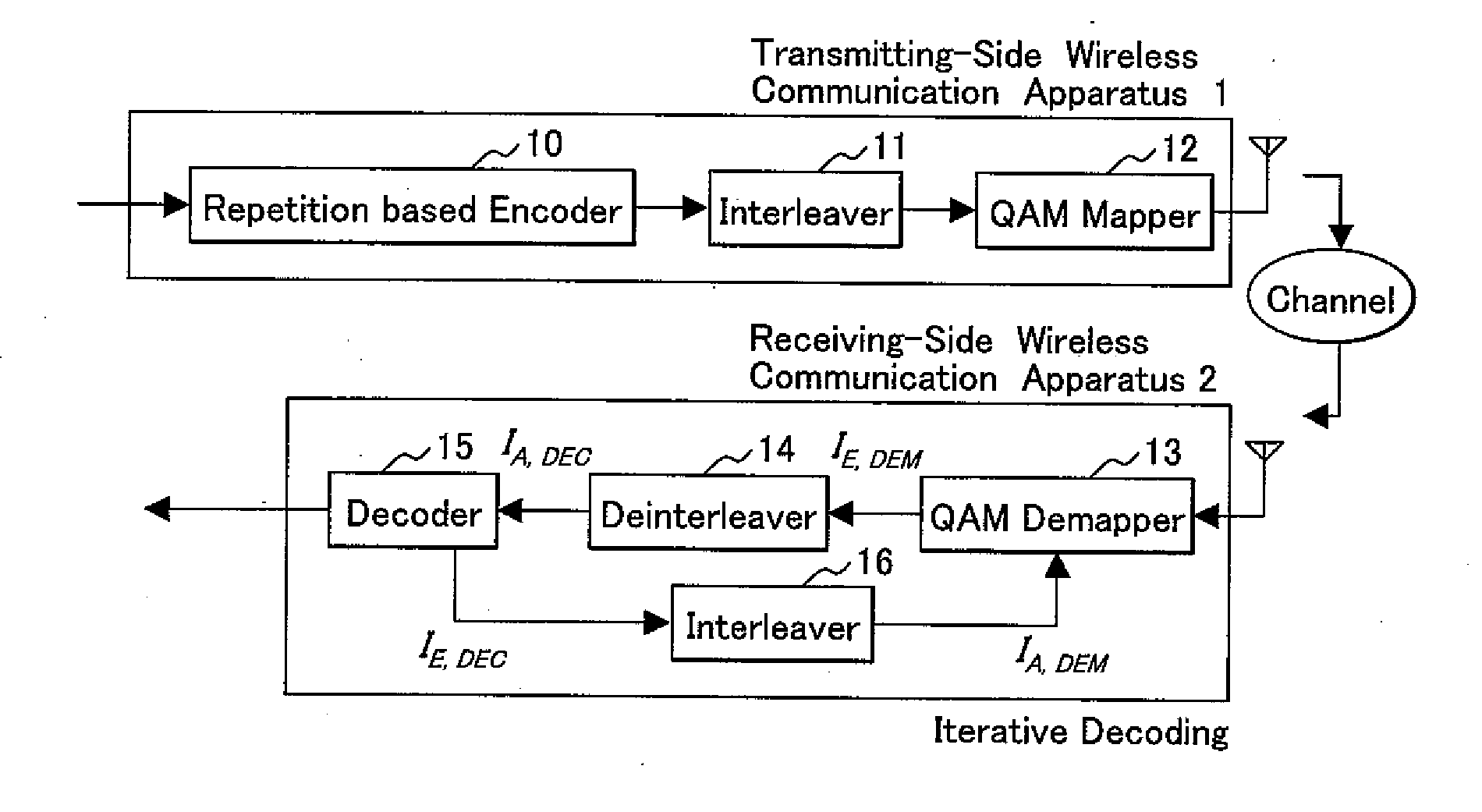

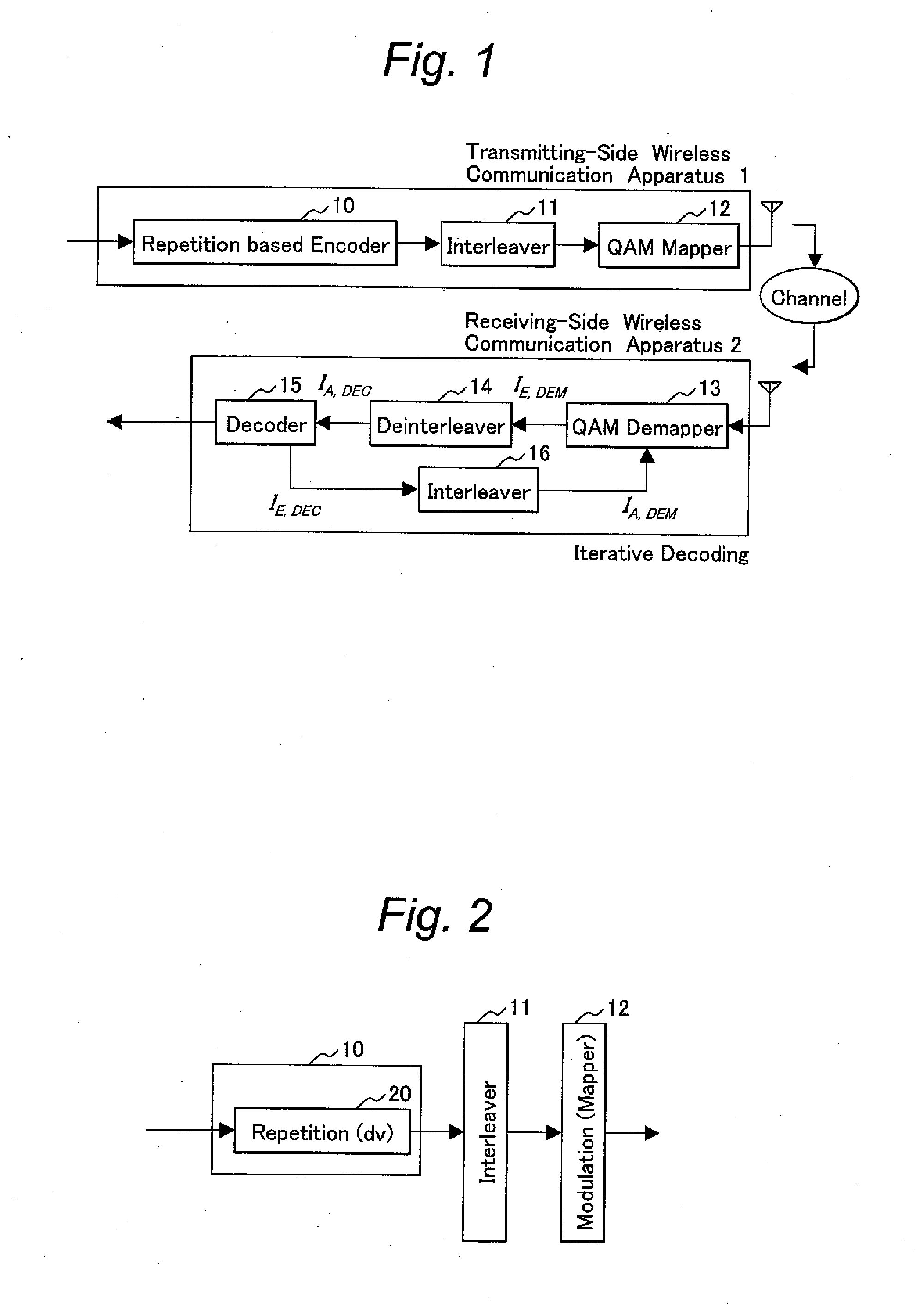

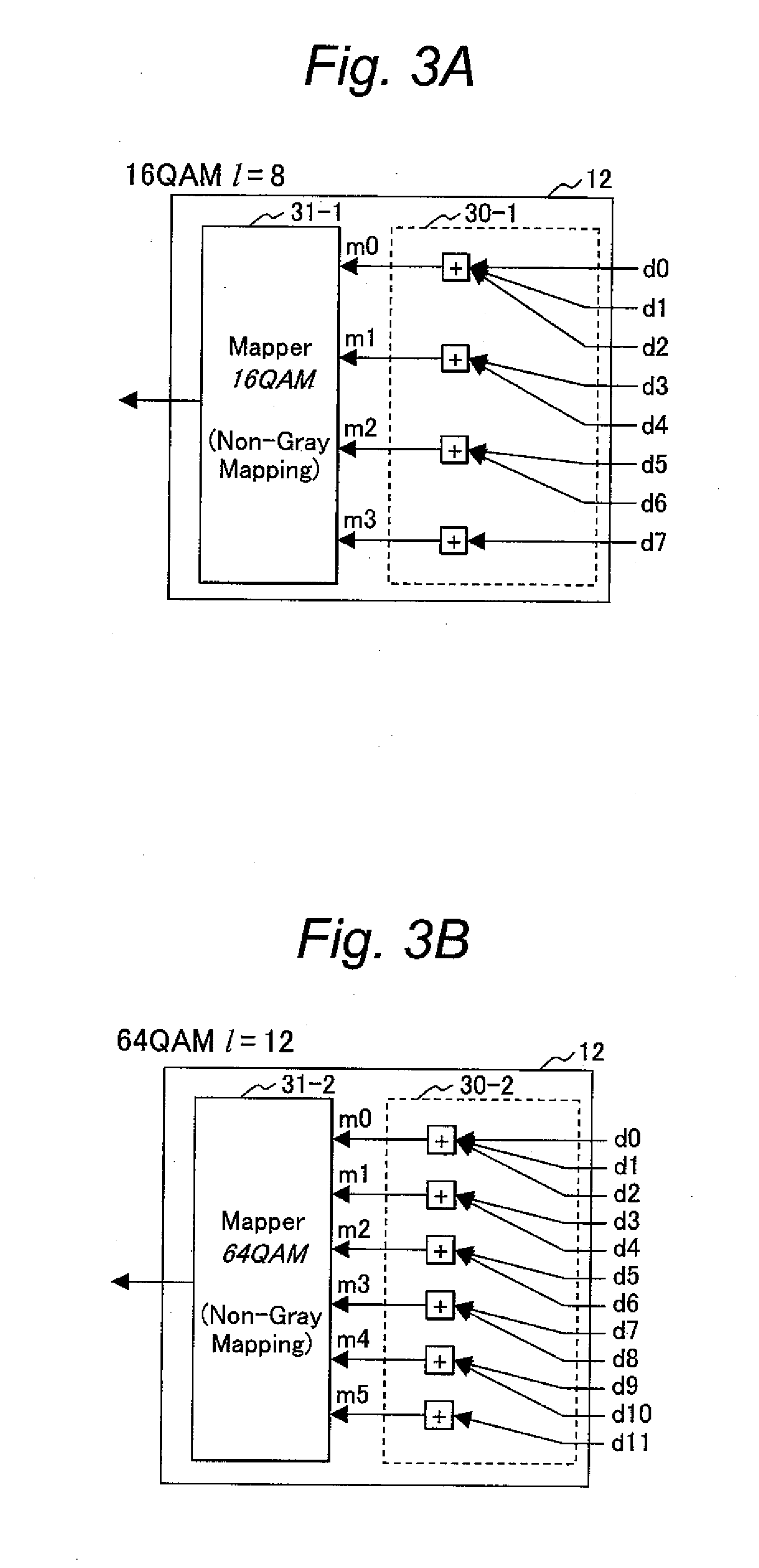

Encoding and modulating method, and decoding method for wireless communication apparatus

InactiveUS20100146365A1Loss in transmission speedReduce lossesError correction/detection using LDPC codesCode conversionDecoding methodsThinning

Provided is a bit interleaved coded modulation-iterative decoding (BICM-ID) technique suffering a small loss in a transfer rate. A BICM-ID technique allowing a decoder to treat a small processing quantity is also provided. Encoding is carried out according to a code based on an iterative code. Encoded bits are reordered during interleaving processing, subjected to multi-valued modulation through extended mapping, and then transmitted. The extended mapping includes number-of-bits thinning processing of thinning l bits into m bits (m<l), and non-gray mapping. During the number-of-bits thinning processing, at least one of a predetermined number of bits is determined with only one of interleaved bits.

Owner:KOKUSA ELECTRIC CO LTD

Receiver and signal processing method thereof

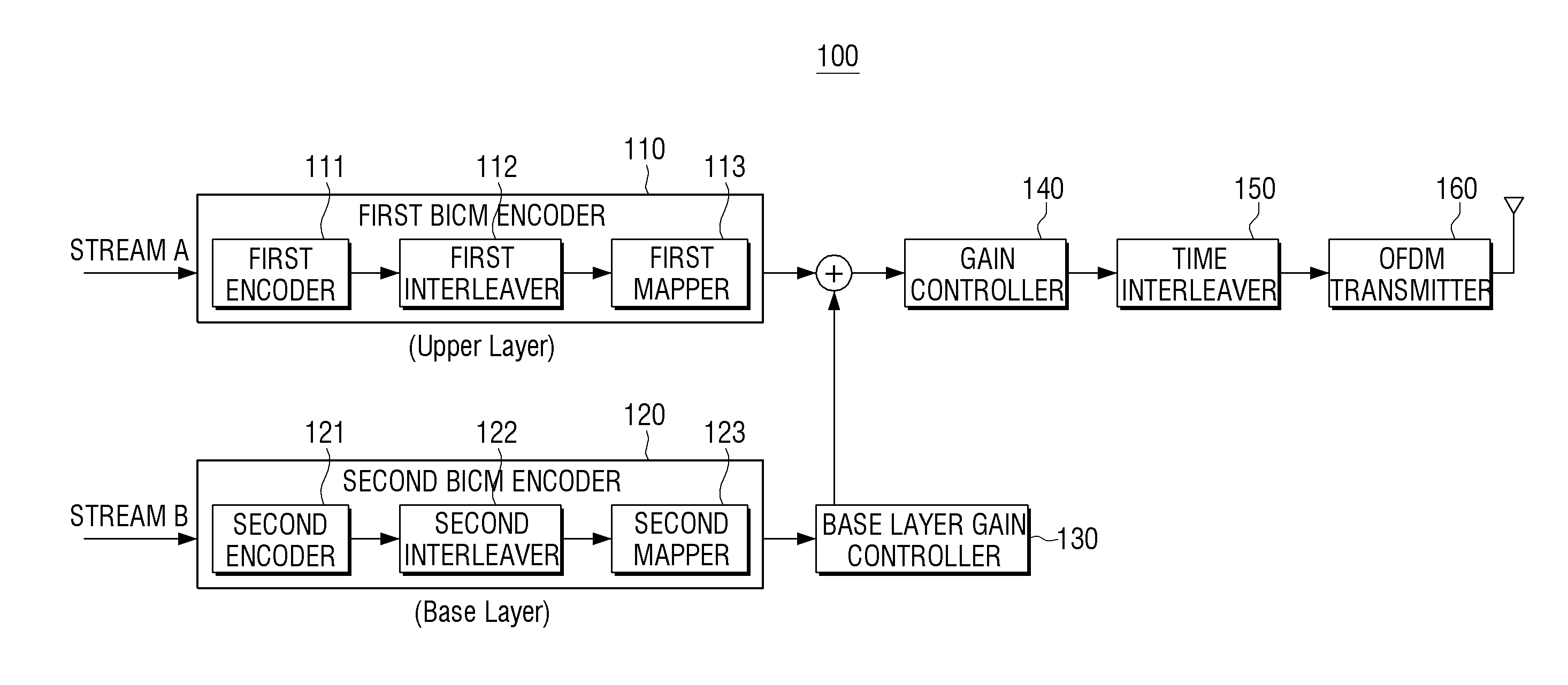

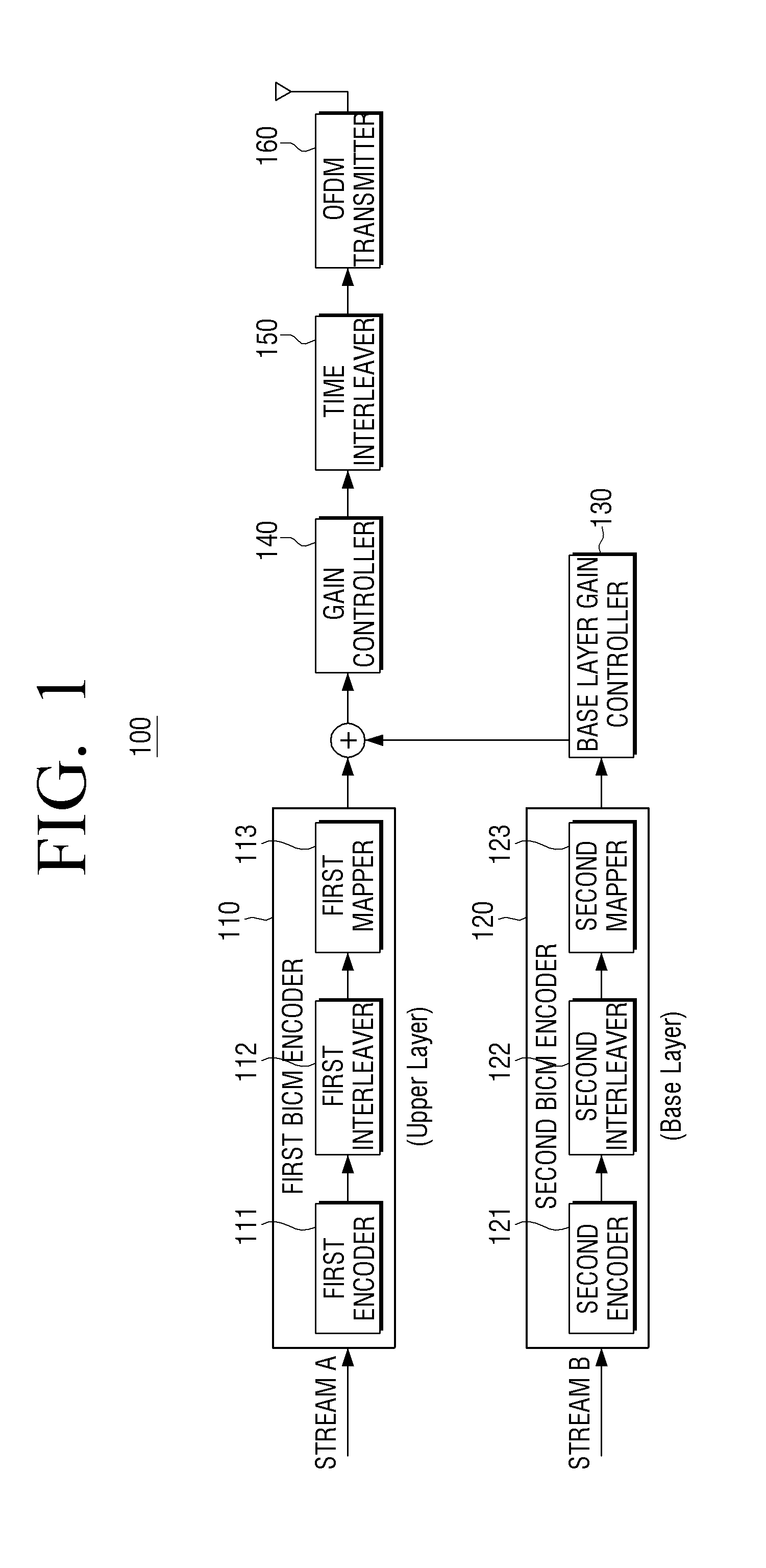

ActiveUS20160352462A1Faster base layer signal recoveryShorten the timeError correction/detection using concatenated codesError correction/detection using LDPC codesSuperposition codingBit interleaved coded modulation

Provided is a receiver which includes at least one processor configured to control or execute: a first Bit-Interleaved Coded Modulation (BICM) decoder configured to generate a first output signal corresponding to an upper layer signal by processing a first input signal which includes a superposition coding signal generated at a transmitter by superimposing the upper layer signal and a lower layer signal; a parity generator configured to generate at least one parity based on a result of the processing of the first input signal by the first BICM decoder; and a second BICM decoder configured to generate a second output signal corresponding to the lower layer signal by processing a second input signal which is generated using the parity generated by the parity generator.

Owner:SAMSUNG ELECTRONICS CO LTD

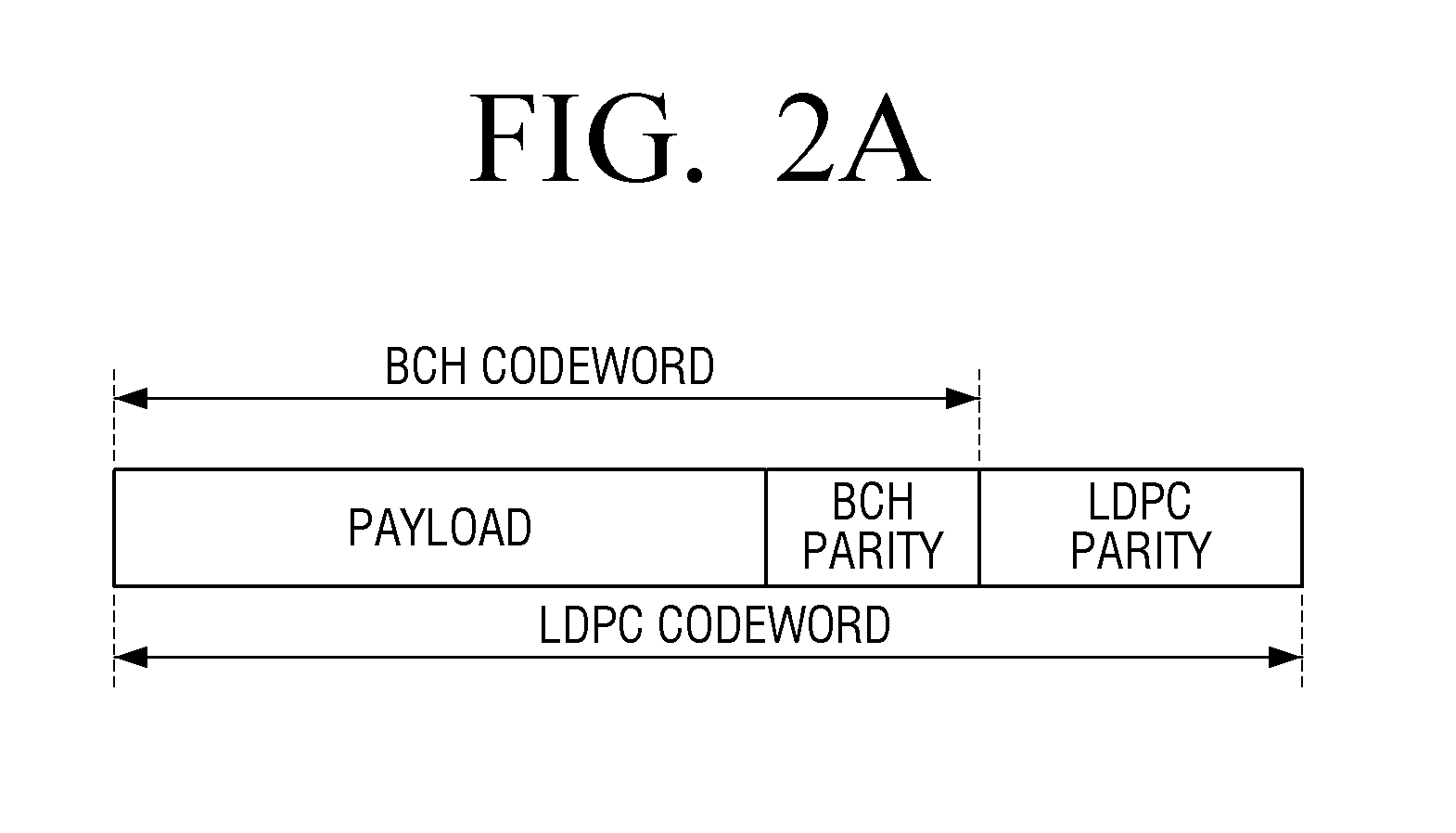

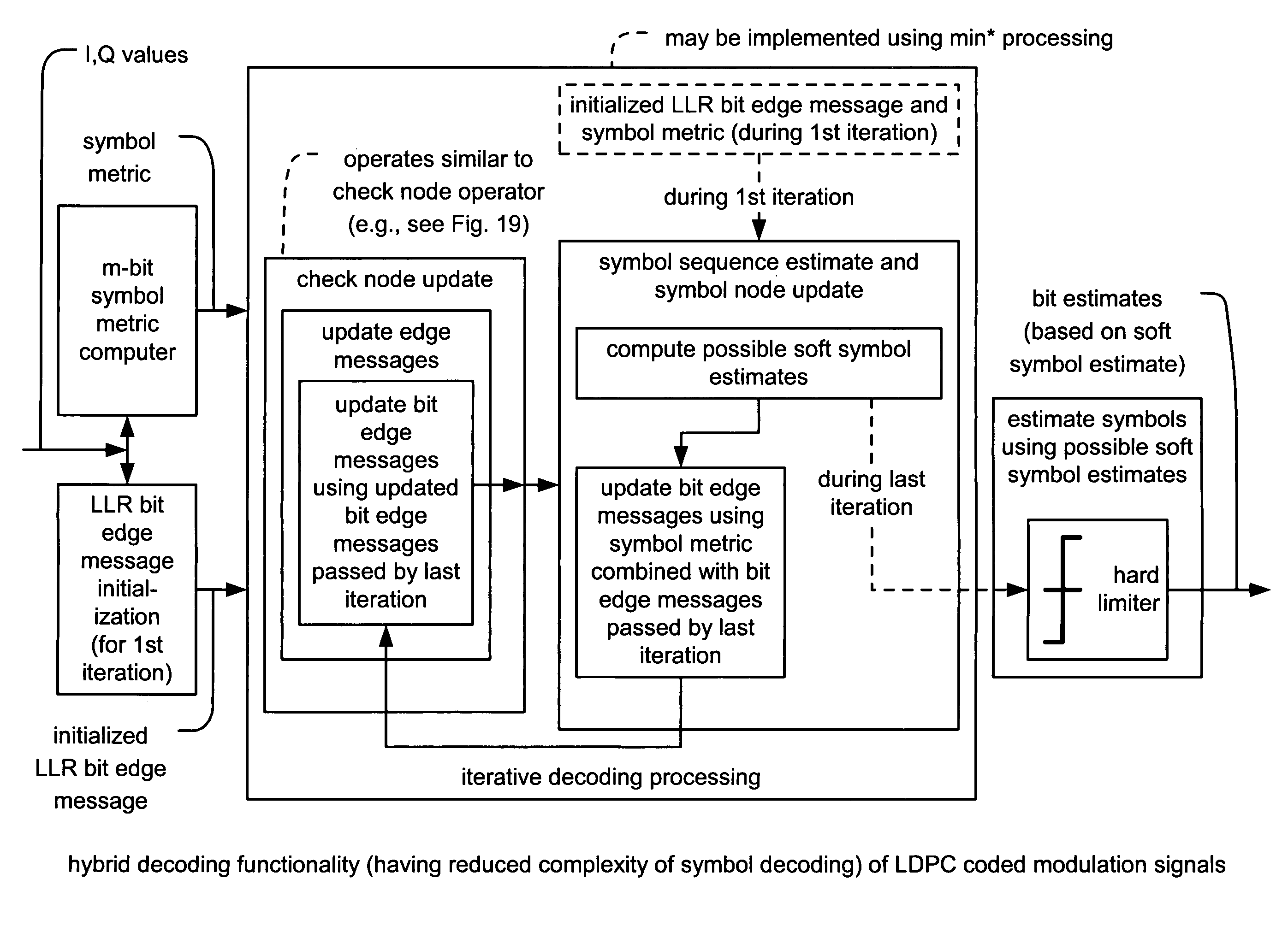

LDPC (Low Density Parity Check) coded modulation hybrid decoding using non-Gray code maps for improved performance

InactiveUS7383493B2Improve performanceError prevention/detection by using return channelOther decoding techniquesTheoretical computer scienceLow density

LDPC (Low Density Parity Check) coded modulation hybrid decoding using non-Gray code maps for improved performance. Check node updating and symbol node updating are successively and alternatively performed on bit edge messages for a predetermined number of decoding iterations or until sufficient degree of precision is achieved. The symbol node updating of the bit edge messages uses symbol metrics corresponding to the symbol being decoded and the bit edge messages most recently updated by check node updating. The check node updating of the bit edge messages uses the bit edge messages most recently updated by symbol node updating. The symbol node updating computes possible soft symbol estimates. LDPC coded modulation hybrid decoding can decode an LDPC-BICM (Low Density Parity Check-Bit Interleaved Coded Modulation) signal having a symbol mapped using non-Gray code mapping. By using the non-Gray code mapping, a performance improvement is achieved over an only Gray code mapping system.

Owner:AVAGO TECH INT SALES PTE LTD

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 2/15 and 64-symbol mapping, and bit interleaving method using same

ActiveUS9602138B2Efficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsComputer hardwareSymbol mapping

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 2 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 64-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Multi-layer differential phase shift keying with bit-interleaved coded modulation and OFDM

InactiveUS7324613B2Increase data rateReliable and high data rate transmissionAngle modulationSecret communicationDifferential modulationEngineering

Owner:UNIV OF FLORIDA RES FOUNDATION INC +1

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and quadrature phase shift keying, and bit interleaving method using same

ActiveUS9577790B2Efficiently distributedError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow-density parity-check codeLow density

Owner:ELECTRONICS & TELECOMM RES INST

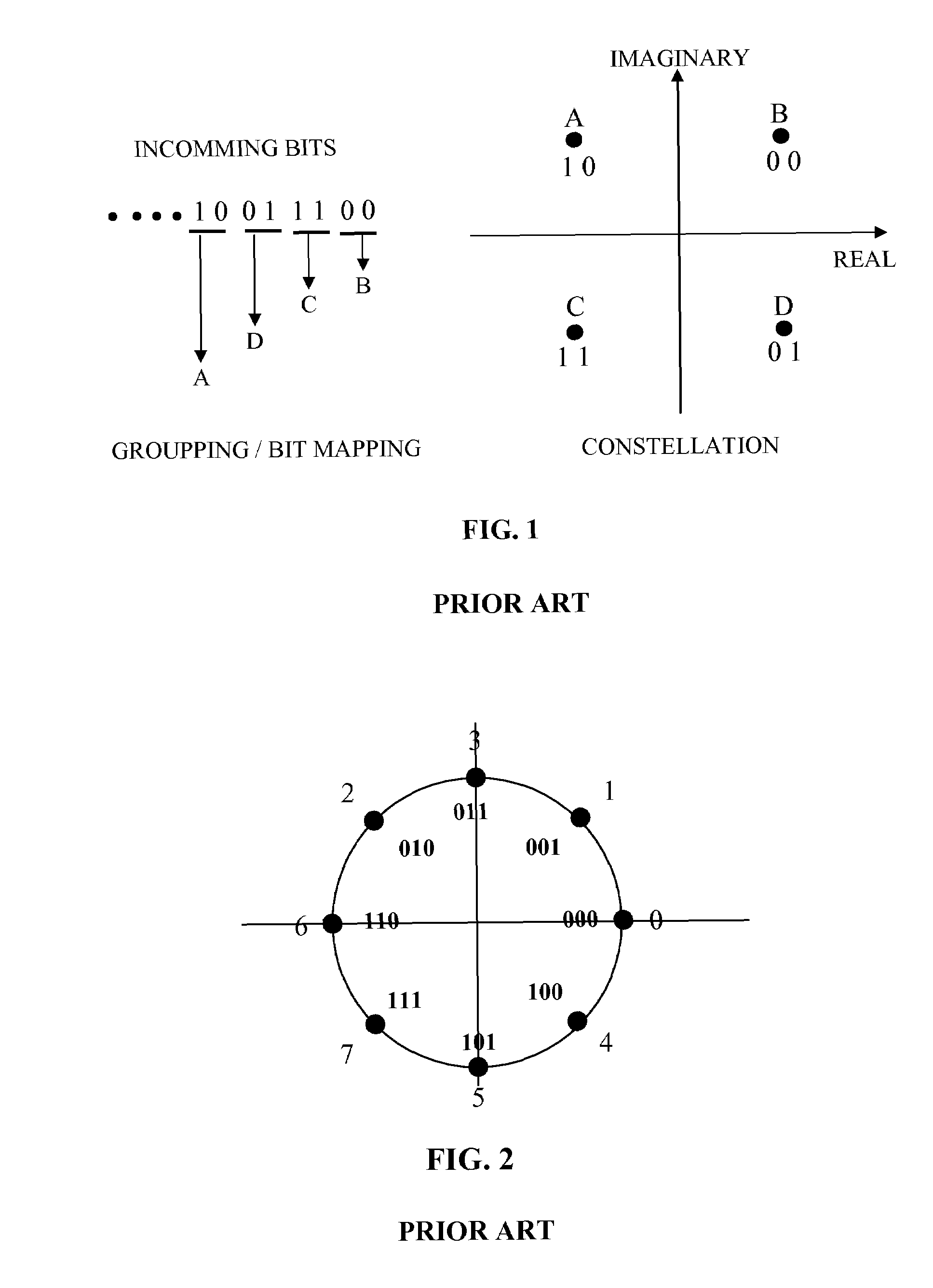

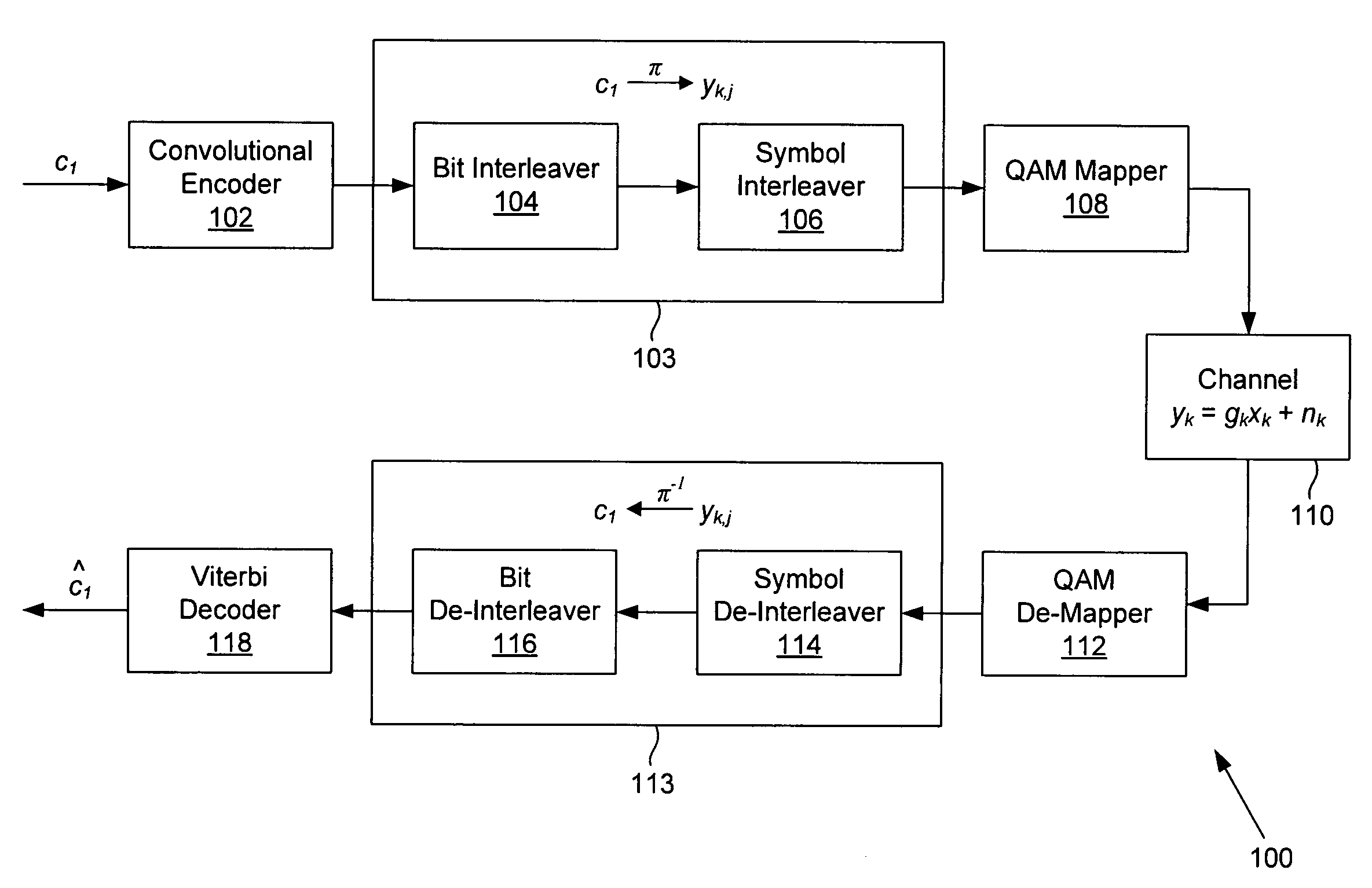

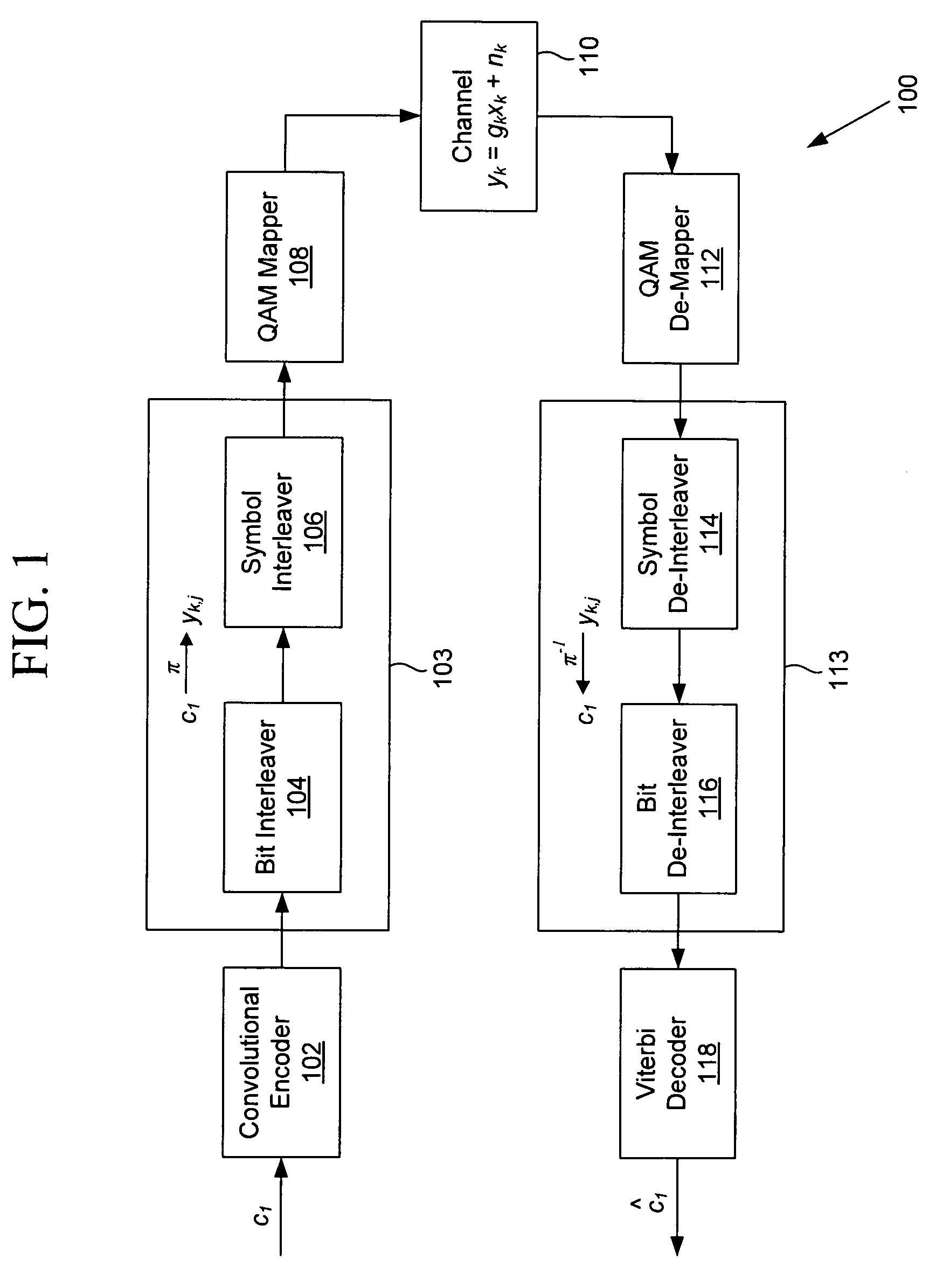

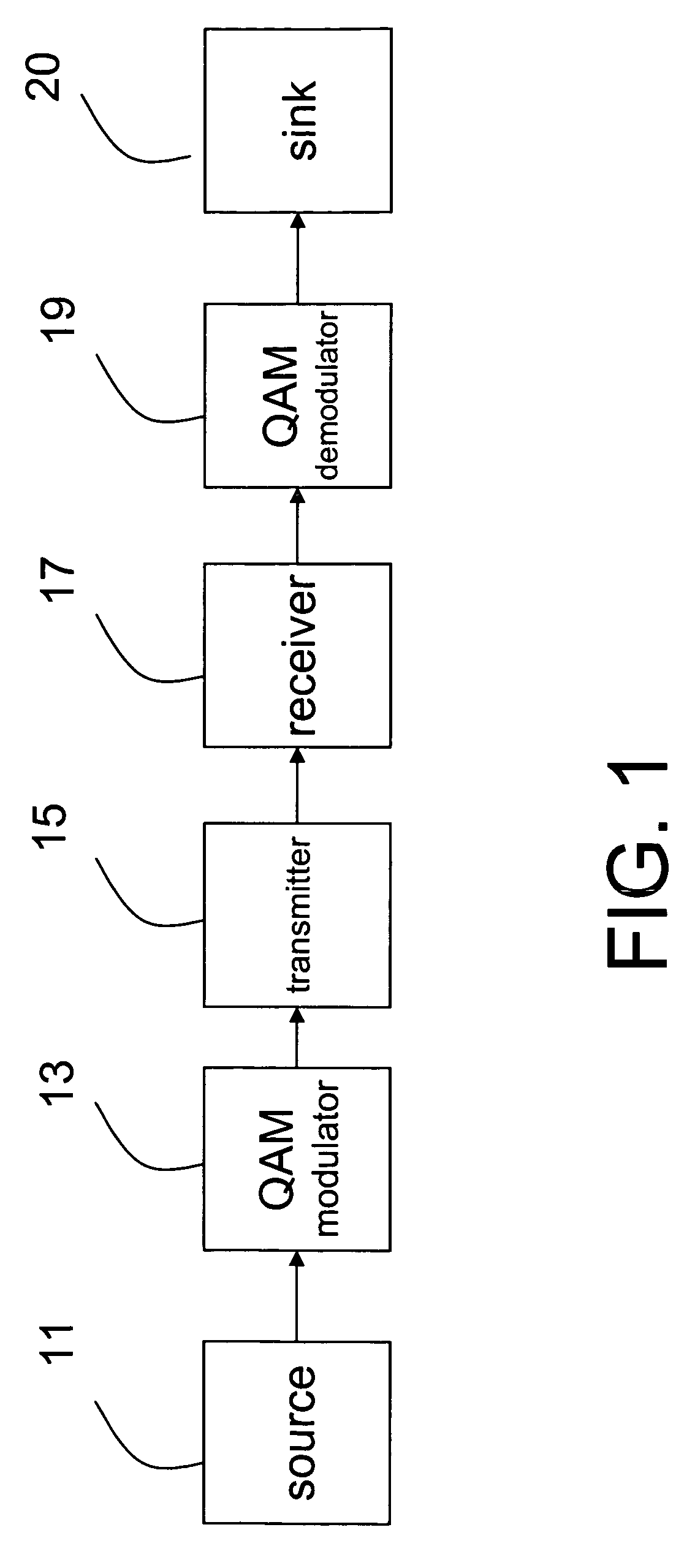

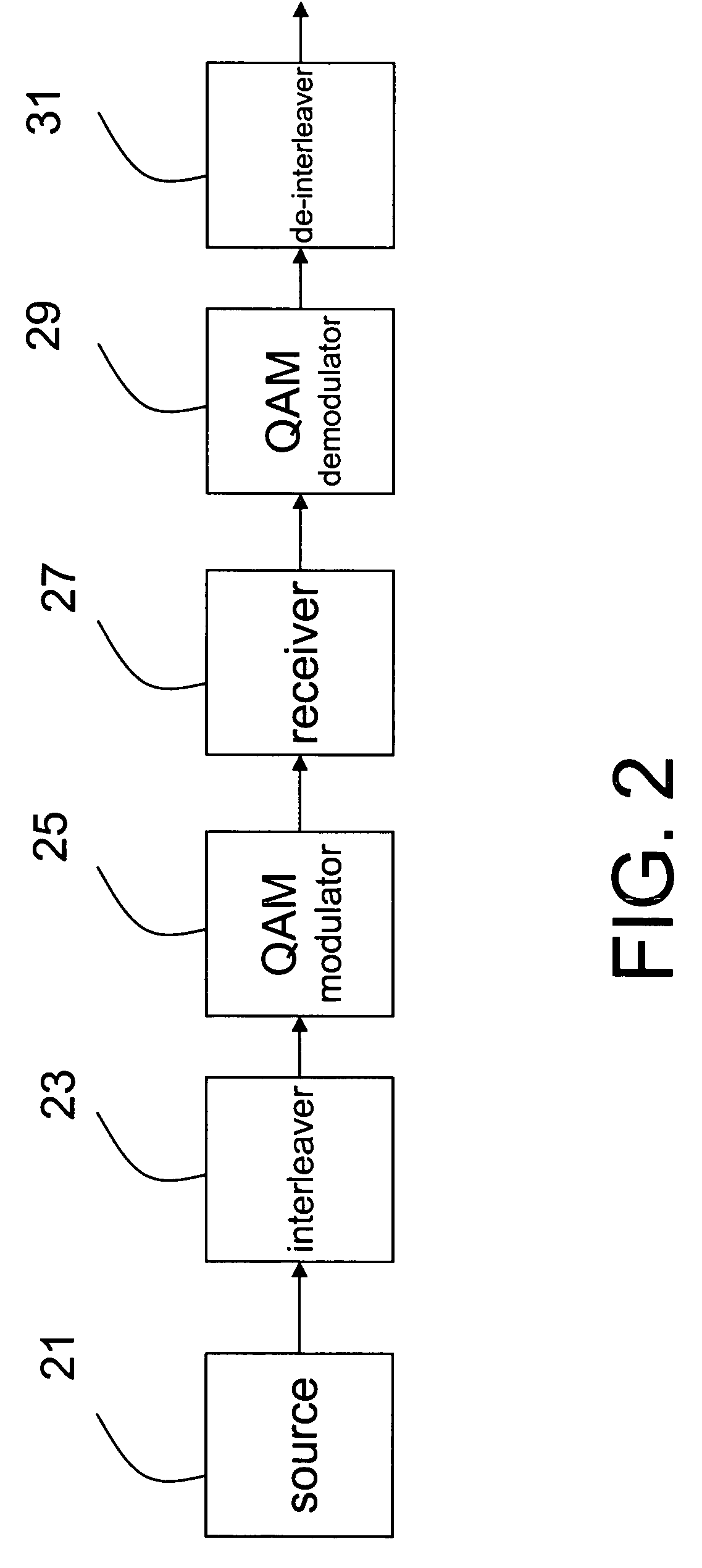

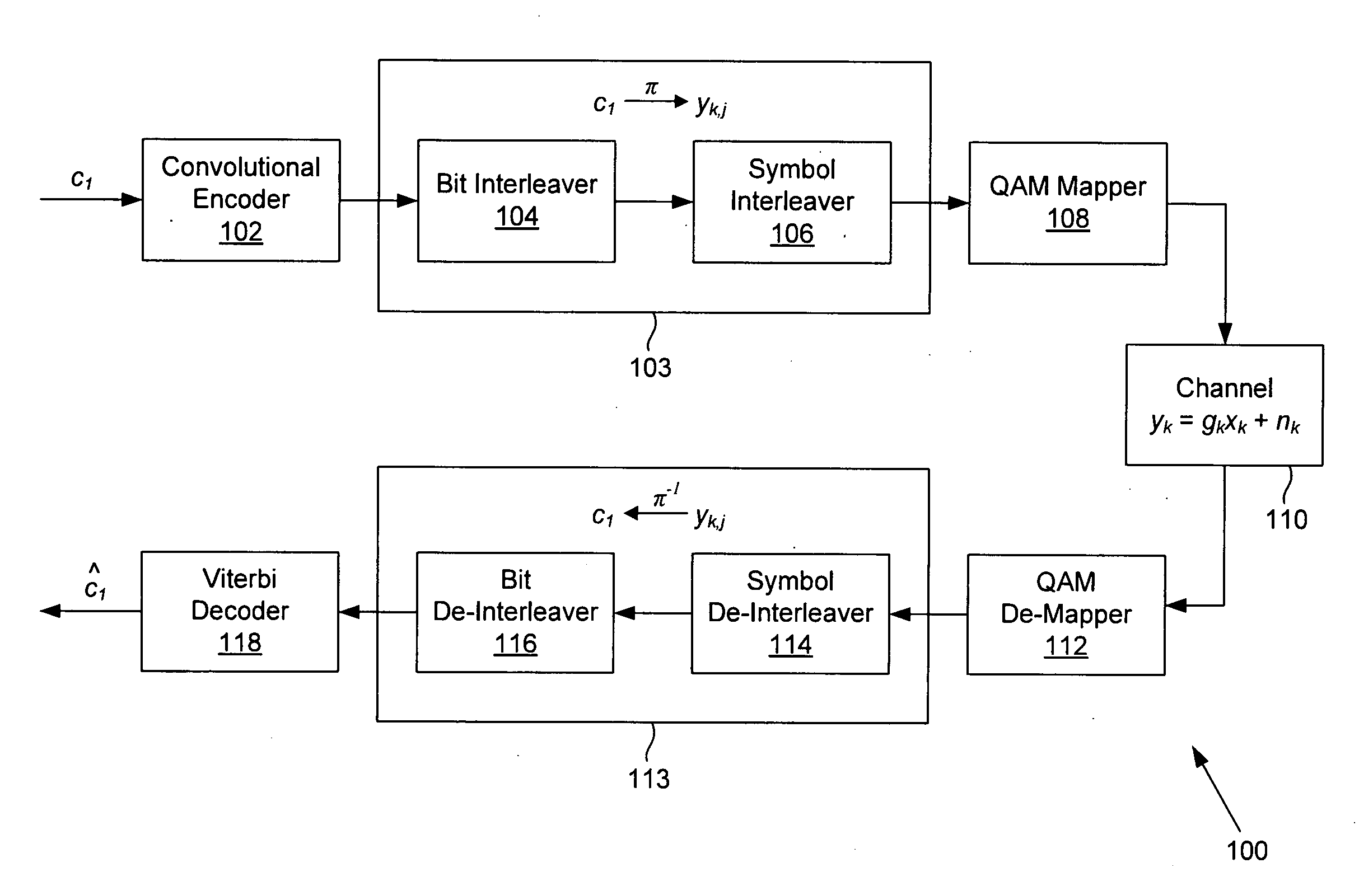

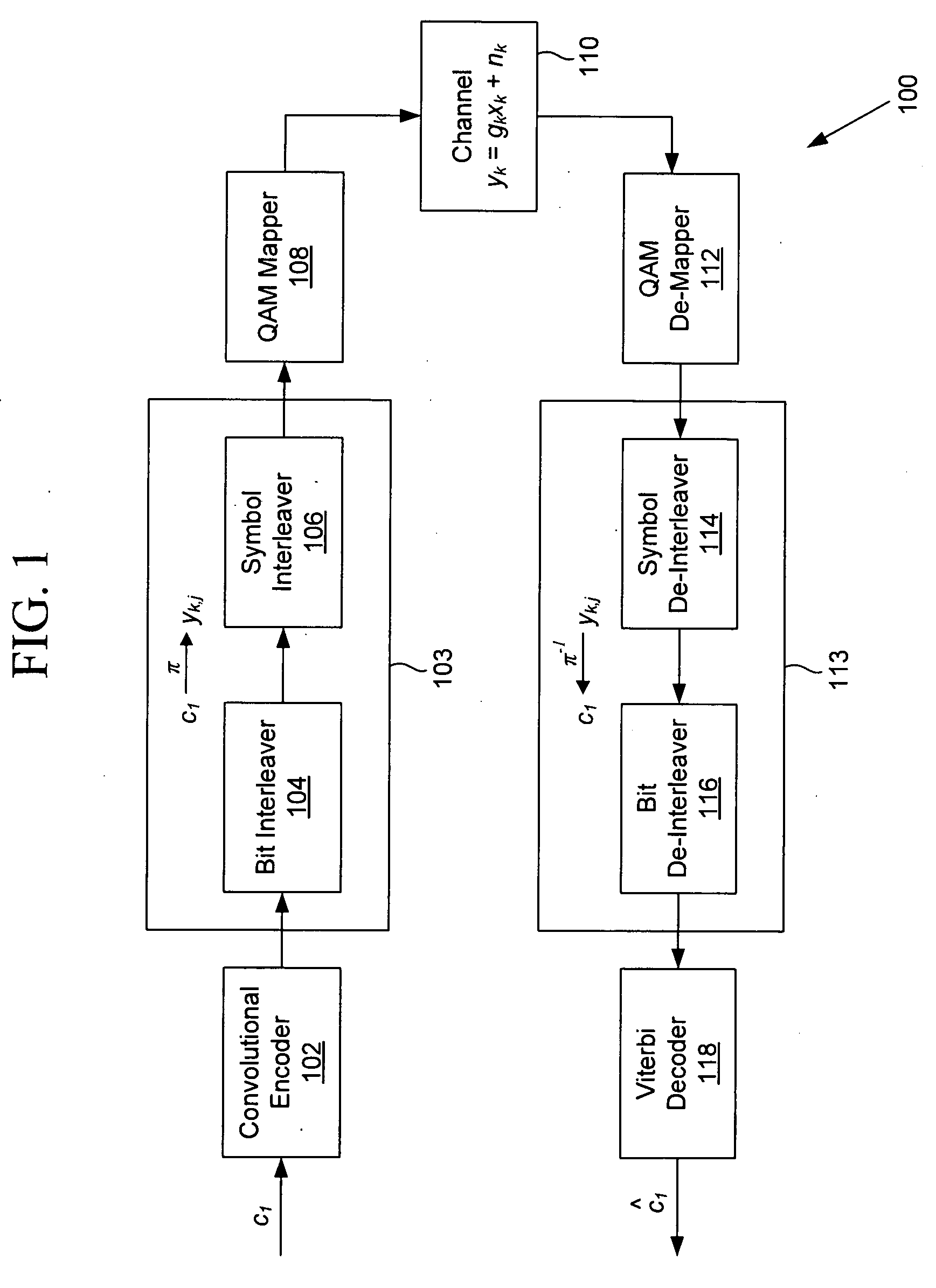

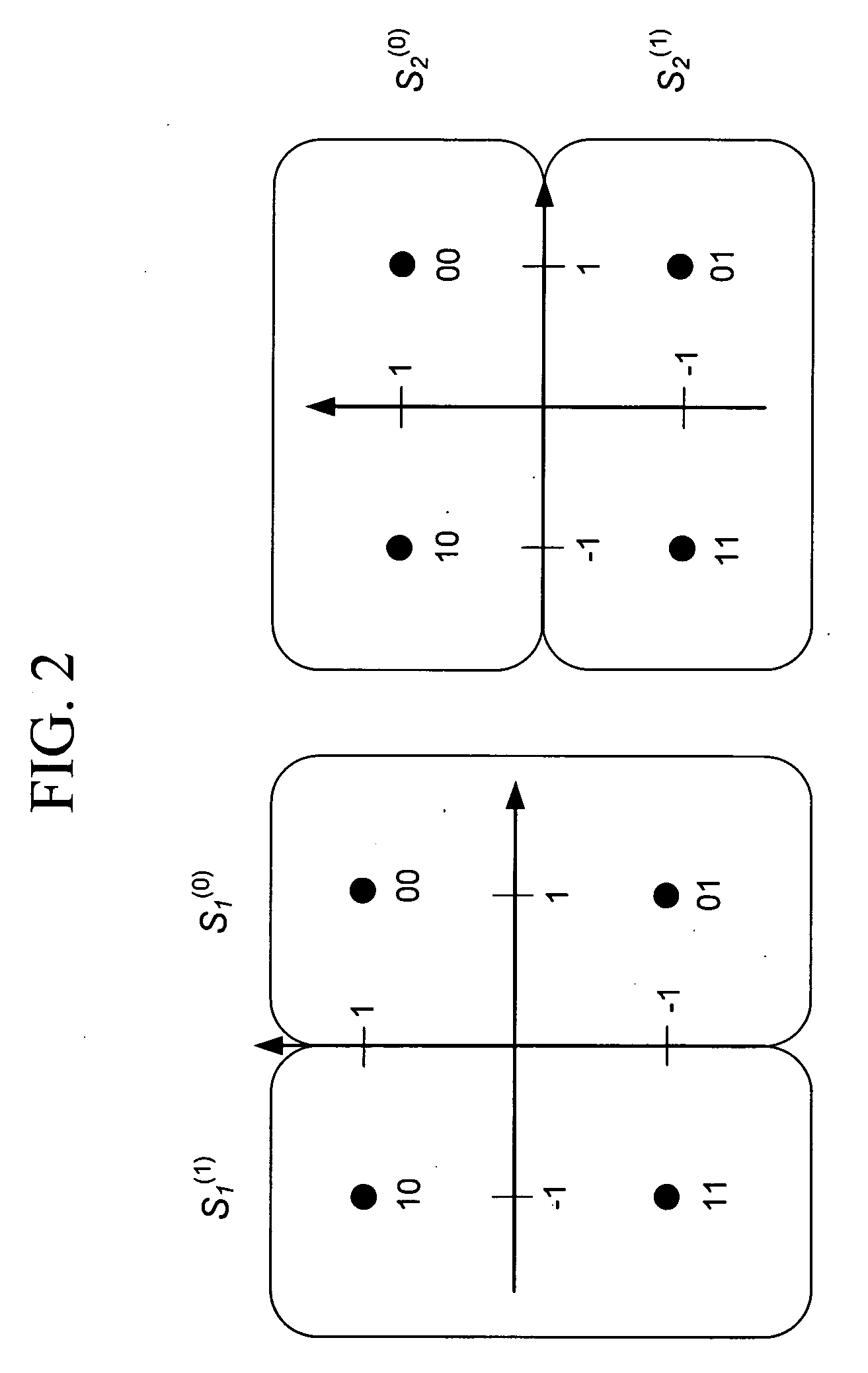

Low complexity soft-input Viterbi decoding for digital communication systems

ActiveUS7599441B2Amplitude-modulated carrier systemsAmplitude demodulationViterbi decoderCommunications system

A DVB-H bit-interleave coded modulation / demodulation system and method includes a convolutional encoder; an interleaver operatively connected to the convolutional encoder; a quadrature amplitude modulation (QAM) mapper operatively connected to the interleaver; a channel component operatively connected to the QAM mapper; a QAM demapper operatively connected to the channel component; a de-interleaver operatively connected to the QAM demapper; and a Viterbi decoder operatively connected to the de-interleaver. Preferably, the interleaver comprises a bit-wise interleaver and a symbol-wise interleaver operatively connected to the bit-wise interleaver. Preferably, the de-interleaver comprises a bit-wise de-interleaver; and a symbol-wise de-interleaver operatively connected to the bit-wise de-interleaver. The de-interleaver may be adapted to decode a soft decision metric for any of a QPSK, 16QAM, and 64QAM modulation. The de-interleaver may be adapted to decode a soft decision metric computation comprising a log-likelihood ratio soft decision metric of a binary bit stream of a signal.

Owner:ATMEL CORP

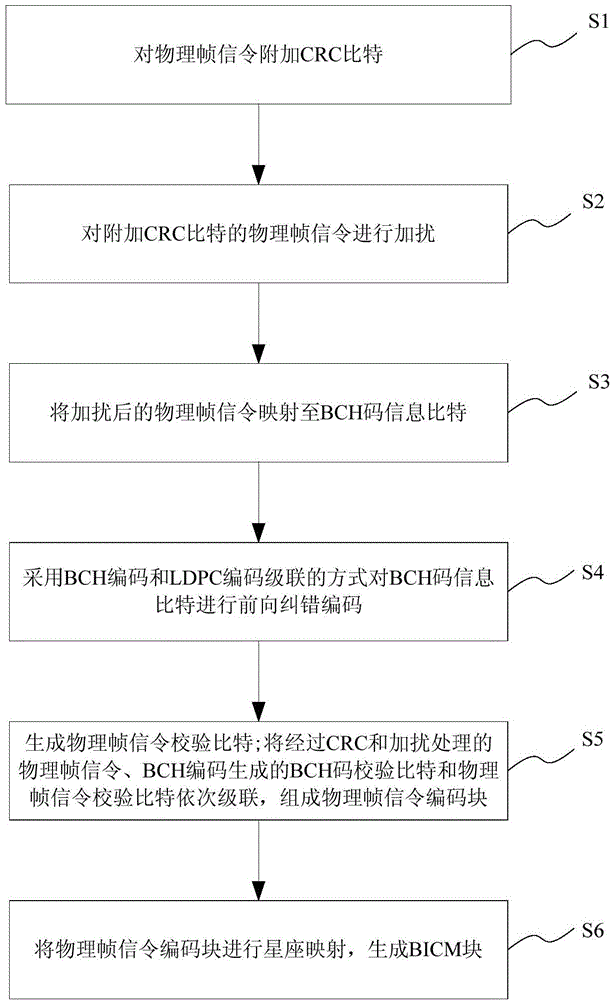

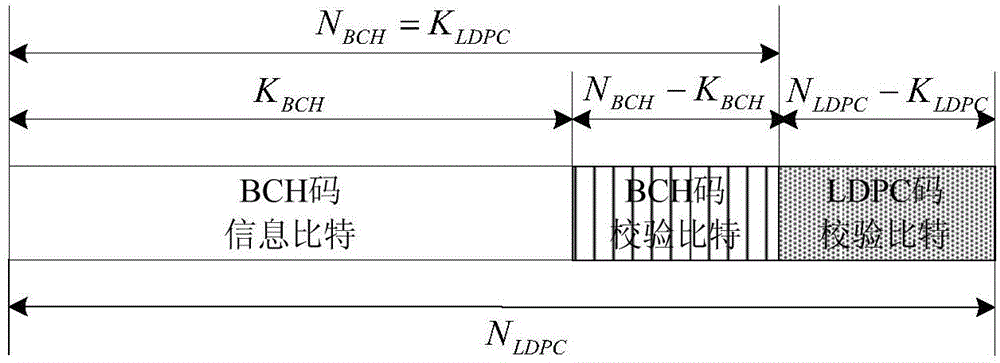

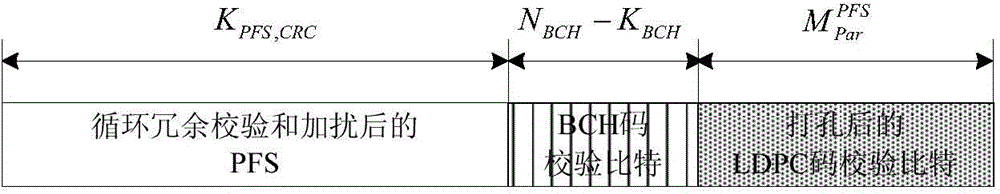

Method for encoding and modulating physical frame signaling channel in NGB-W system

ActiveCN104618067ASupport bitmapSupport generationSelective content distributionTransmission format adaptationCoding blockComputer hardware

The invention discloses a method for encoding and modulating a physical frame signaling channel in an NGB-W system. The method comprises the following steps of: adding CRC (cyclic redundancy code) bits to physical frame signaling and scrambling the physical frame signaling; mapping the scrambled physical frame signaling into BCH (Broadcast Channel) code information bits; performing forward error correction coding to the BCH code information bits by BCH coding and LDPC (Low Density Parity Check) coding cascade methods; generating physical frame signaling check bits and forming physical frame signaling coding blocks; performing constellation mapping to the physical frame signaling coding blocks to generate BICM (Bit Interleaved Coded Modulation) blocks. The method is characterized in that a forward error correction coding solution with a reasonable structure and parameters, and LDPC codes including a QC-Raptor-Like structure and approaching a Claude Elwood Shannon threshold are adopted, and bit mapping of information with the changeable signaling length, code rate control and coding block generation can be supported; the physical frame signaling with the changeable length can be protected so that the transmission reliability of the physical frame signaling is relatively steady along with the change of the signaling length.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Tree position adaptive soft output M-algorithm receiver structures

ActiveUS8325840B2Combined modulated pulse demodulationLine-faulsts/interference reductionChannel state informationCommunications system

A method and apparatus for tree position adaptive SOMA receiver structures are disclosed herein. In one embodiment, a device for use in a wireless communication system comprises a receiver to receive information-bearing signals from the transmitter wirelessly transmitted using OFDM and bit interleaved coded modulation, where the receiver includes an inner decoder structure having a soft output M-algorithm (SOMA) based multiple-in multiple-out (MIMO) joint demapper that uses a SOMA-based MIMO detection process to perform joint inner demapping over each tone, and wherein the SOMA-based MIMO joint demapper is operable to search a detection tree for each tone using a tree-search symbol order that is adapted for each tone based on channel state information and extrinsic information from the outer decoder, where only a number of best alternatives from every level of the tree are expanded.

Owner:NTT DOCOMO INC

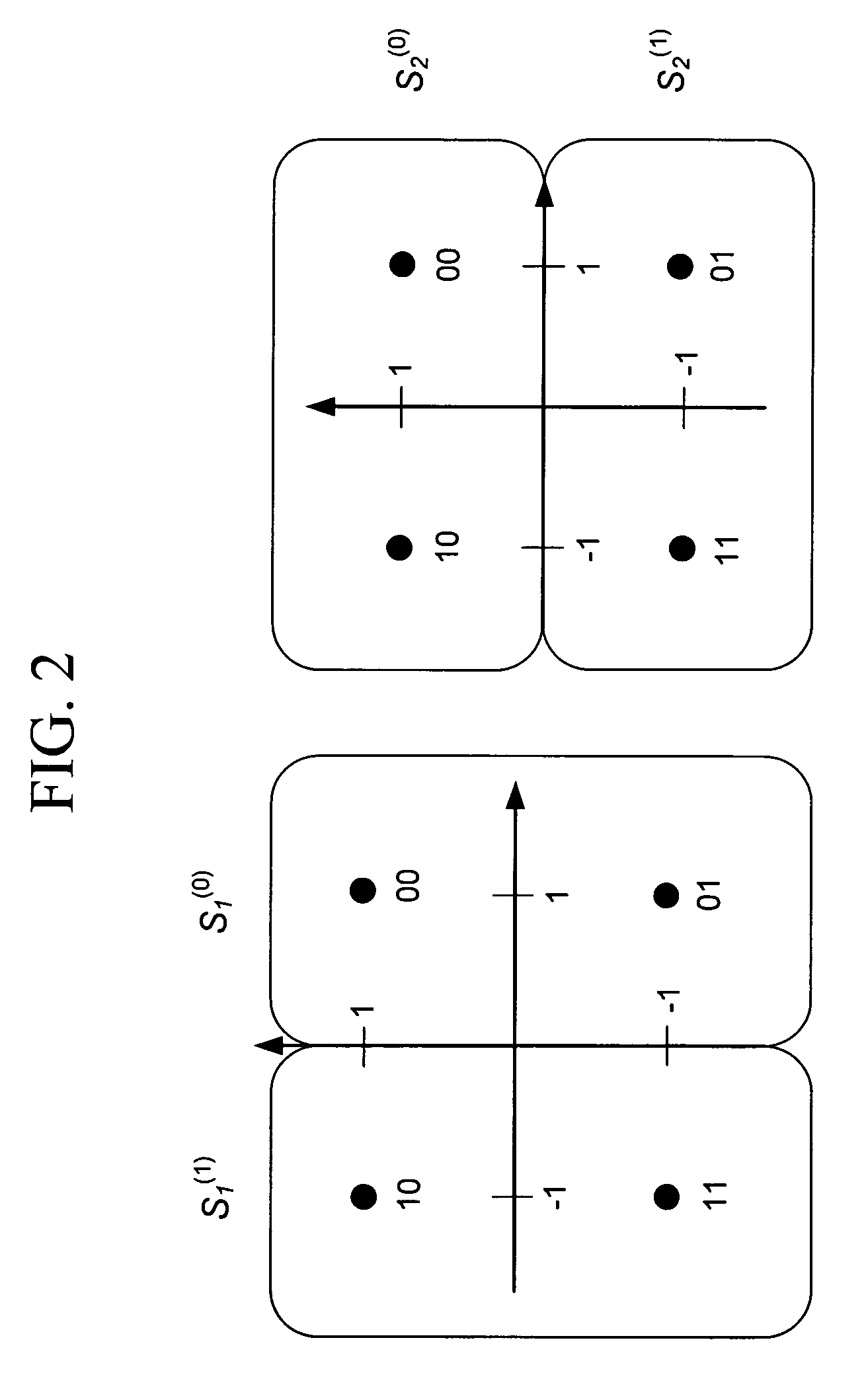

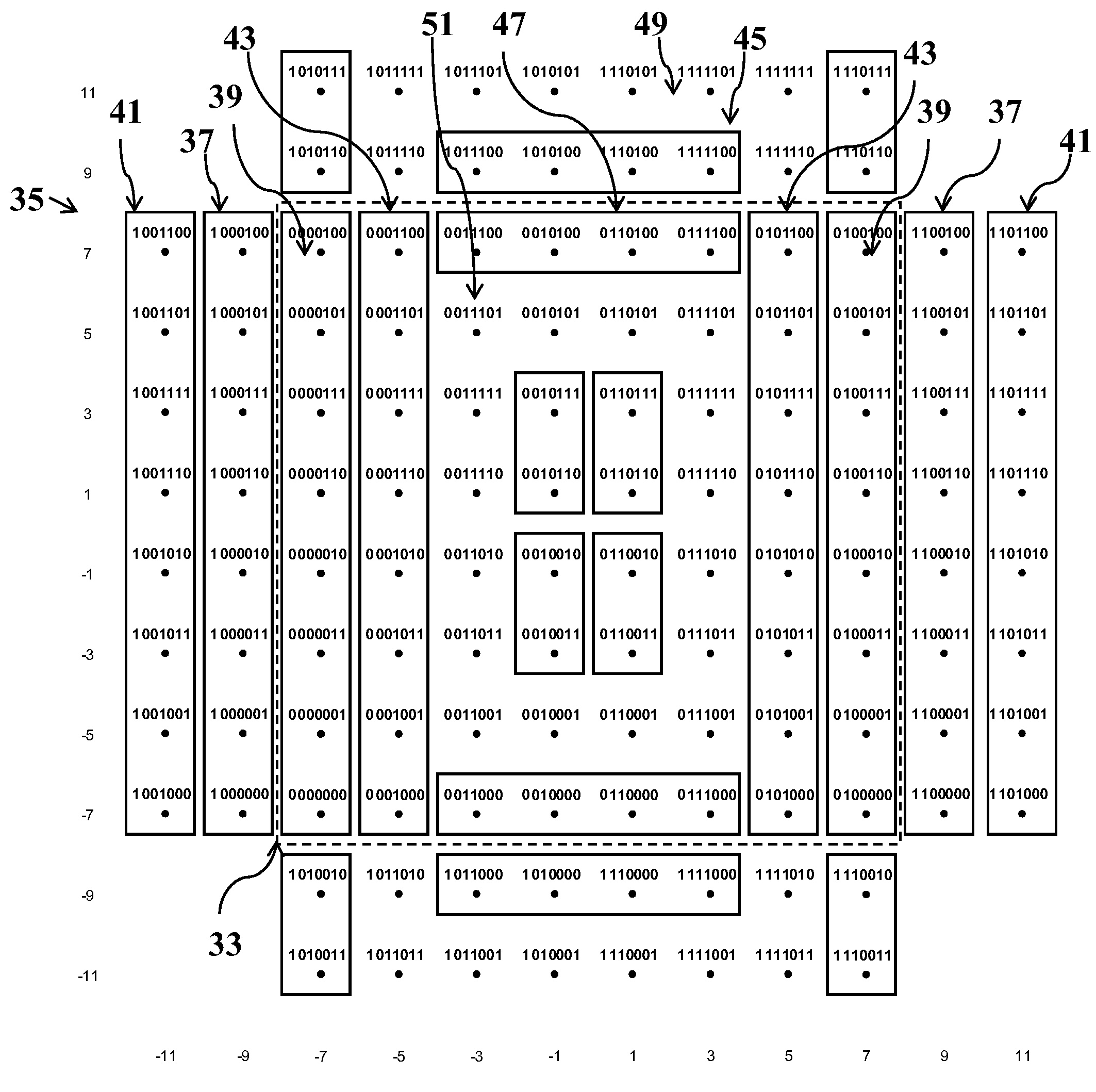

QAM mapping and bit labeling or bit-interleaved coded modulation

ActiveUS7535975B1Simultaneous amplitude and angle modulationAmplitude-modulated carrier systemsCommunications systemBit interleaved coded modulation

Methods and systems using a Gray-like labeled QAM cross-constellation are disclosed. In some embodiments a Gray-like labeled QAM cross-constellation is used in wireless communication systems.

Owner:WIONICS RES +1

Low complexity soft-input Viterbi decoding for digital communication systems

ActiveUS20070291864A1Amplitude-modulated carrier systemsAmplitude demodulationViterbi decoderCommunications system

A DVB-H bit-interleave coded modulation / demodulation system and method includes a convolutional encoder; an interleaver operatively connected to the convolutional encoder; a quadrature amplitude modulation (QAM) mapper operatively connected to the interleaver; a channel component operatively connected to the QAM mapper; a QAM demapper operatively connected to the channel component; a de-interleaver operatively connected to the QAM demapper; and a Viterbi decoder operatively connected to the de-interleaver. Preferably, the interleaver comprises a bit-wise interleaver and a symbol-wise interleaver operatively connected to the bit-wise interleaver. Preferably, the de-interleaver comprises a bit-wise de-interleaver; and a symbol-wise de-interleaver operatively connected to the bit-wise de-interleaver. The de-interleaver may be adapted to decode a soft decision metric for any of a QPSK, 16 QAM, and 64 QAM modulation. The de-interleaver may be adapted to decode a soft decision metric computation comprising a log-likelihood ratio soft decision metric of a binary bit stream of a signal.

Owner:ATMEL CORP