Metal-insulator-semiconductor (MIS) grid enhanced high electron mobility transistor (HEMT) device based on gallium nitride (GaN) and manufacture method of MIS grid enhanced HEMT device

An enhanced device technology, applied in the field of microelectronics, can solve the problems of low device reliability, high current density coexistence, device performance and reliability effects, etc., and achieve the effect of eliminating polarization effects and good enhanced characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

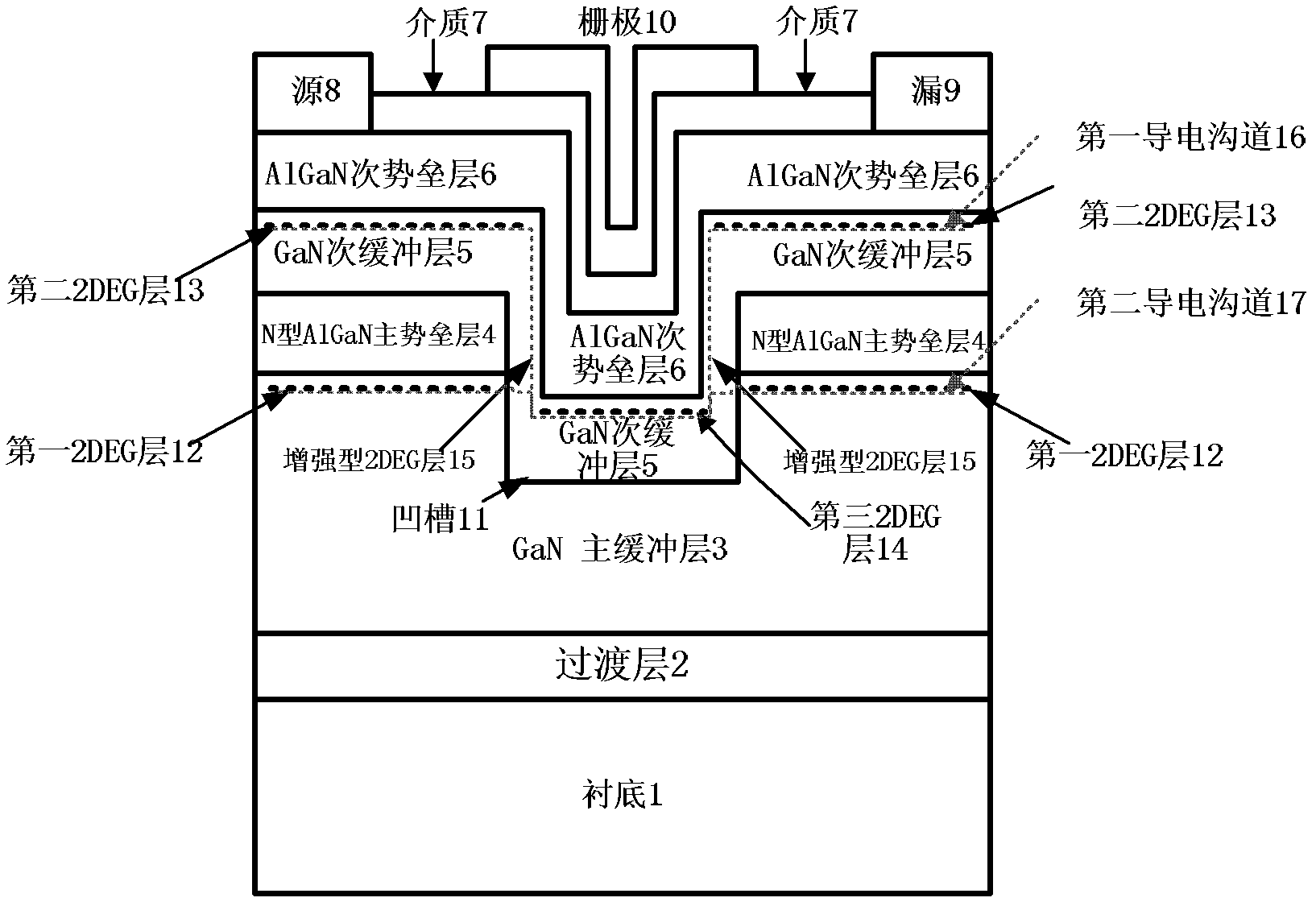

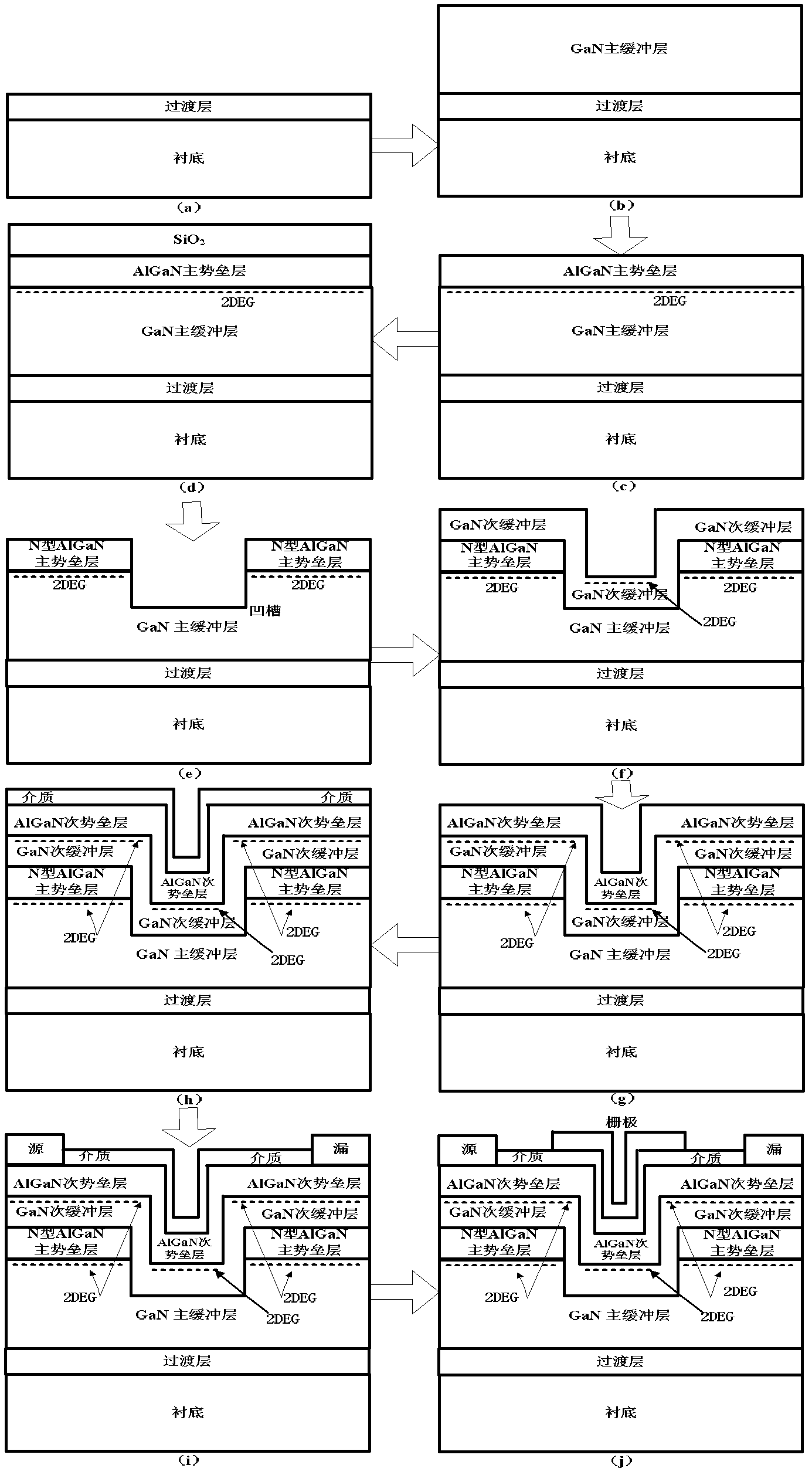

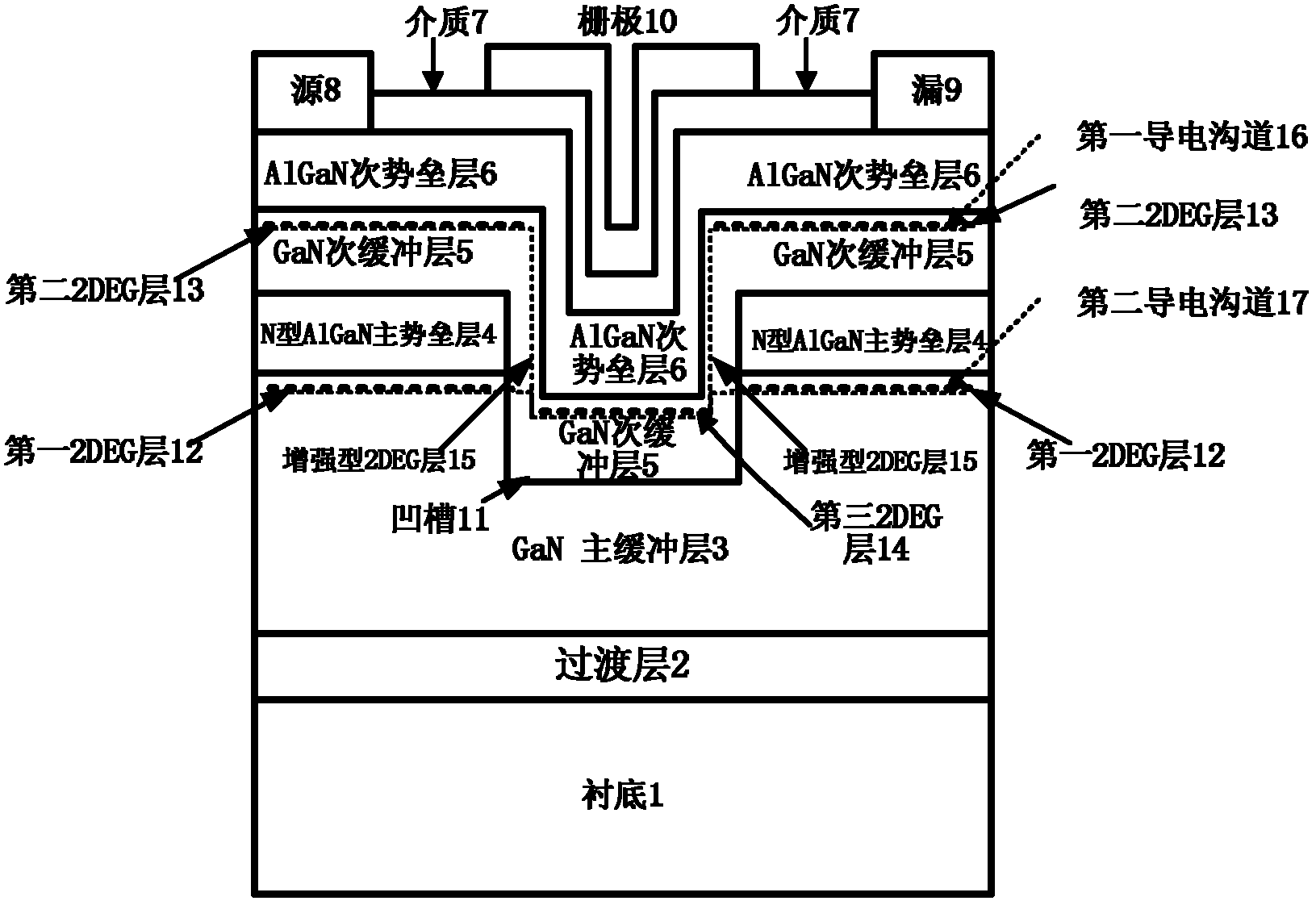

[0048] The substrate is made of sapphire, the transition layer is AlN, the thickness of the GaN main buffer layer is 1.5um, and the thickness of the Al 0.35 Ga 0.65 The thickness of the N main barrier layer is 16nm, the groove etching depth is 40nm, the thickness of the GaN sub-buffer layer is 20nm, Al 0.35 Ga 0.65 The GaN-based MIS gate-enhanced HEMT device with an N-time barrier layer thickness of 16nm and a gate dielectric layer thickness of 2nm is as follows:

[0049] Step 1, place the C-plane sapphire substrate in the metal organic chemical vapor deposition MOCVD reaction chamber, and evacuate the vacuum degree of the reaction chamber to 1×10 -2 Under Torr, heat treatment and surface nitriding of the sapphire substrate are carried out under the protection of a mixture of hydrogen with a flow rate of 1500 sccm and ammonia gas with a flow rate of 2000 sccm, with a heating temperature of 1050° C. and a pressure of 20 Torr.

[0050] Step 2, using MOCVD technology, under th...

Embodiment 2

[0071] The substrate is made of silicon carbide SiC, the transition layer is AlN, the thickness of the GaN main buffer layer is 2.5um, and the Al 0.27 Ga 0.73 The thickness of the N main barrier layer is 24nm, the groove etching depth is 90nm, the thickness of the GaN sub-buffer layer is 60nm, Al 0.27 Ga 0.73 The GaN-based MIS gate-enhanced HEMT device with an N-time barrier layer thickness of 24nm and a gate dielectric layer thickness of 8nm is as follows:

[0072] Step 1, place the silicon carbide SiC substrate in the MOCVD reaction chamber for heat treatment and surface nitriding. The process conditions are: the vacuum degree of the reaction chamber is 1×10 -2 Under Torr, the hydrogen flow rate is 1500 sccm, the ammonia gas flow rate is 3500 sccm, the heating temperature is 950° C., and the pressure is 40 Torr.

[0073] Step 2, using MOCVD technology, epitaxial AlN transition layer with a thickness of 150nm on the silicon carbide SiC substrate, such as figure 2 (a), th...

Embodiment 3

[0094] The substrate is made of sapphire, the transition layer is AlN, the thickness of the GaN main buffer layer is 3.5um, and the thickness of the Al 0.2 Ga 0.8 The thickness of the N main barrier layer is 36nm, the groove etching depth is 140nm, the thickness of the GaN sub-buffer layer is 100nm, Al 0.2 Ga 0.8 The GaN-based MIS gate-enhanced HEMT device with the thickness of the N-time barrier layer being 36nm and the thickness of the gate dielectric layer being 15nm, the steps are:

[0095] Step A, place the sapphire substrate in the metal organic chemical vapor deposition MOCVD reaction chamber, conduct heat treatment and surface nitriding on the sapphire substrate under the protection of the mixed gas of ammonia and hydrogen, and pump the vacuum degree of the reaction chamber to 1× 10 -2 Under Torr, the flow rate of hydrogen gas is 1500 sccm, the flow rate of ammonia gas is 2000 sccm, the heating temperature is 1050° C., and the pressure is 20 Torr.

[0096] Step B, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More