Patents

Literature

32results about How to "Guaranteed forwarding performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

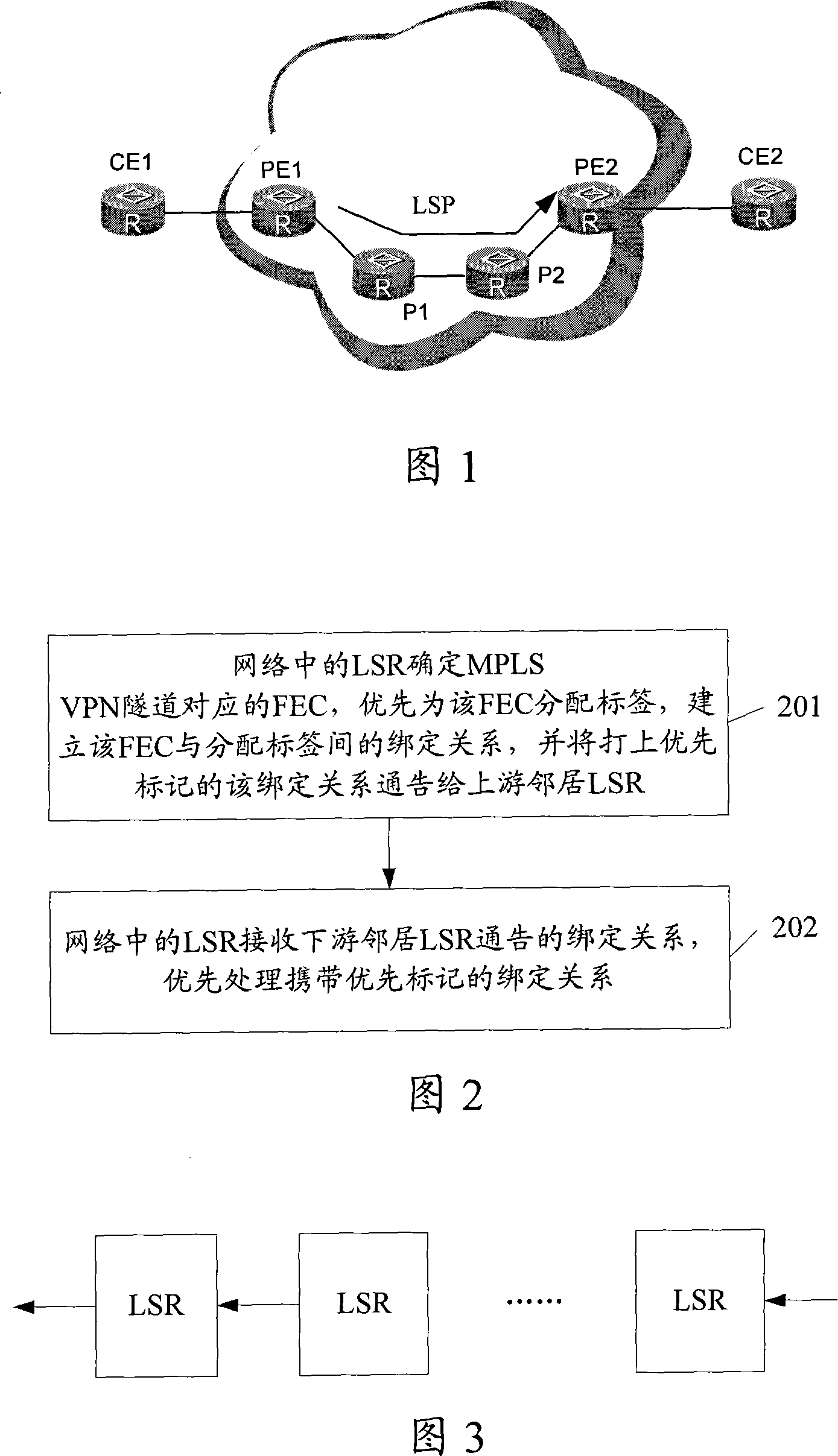

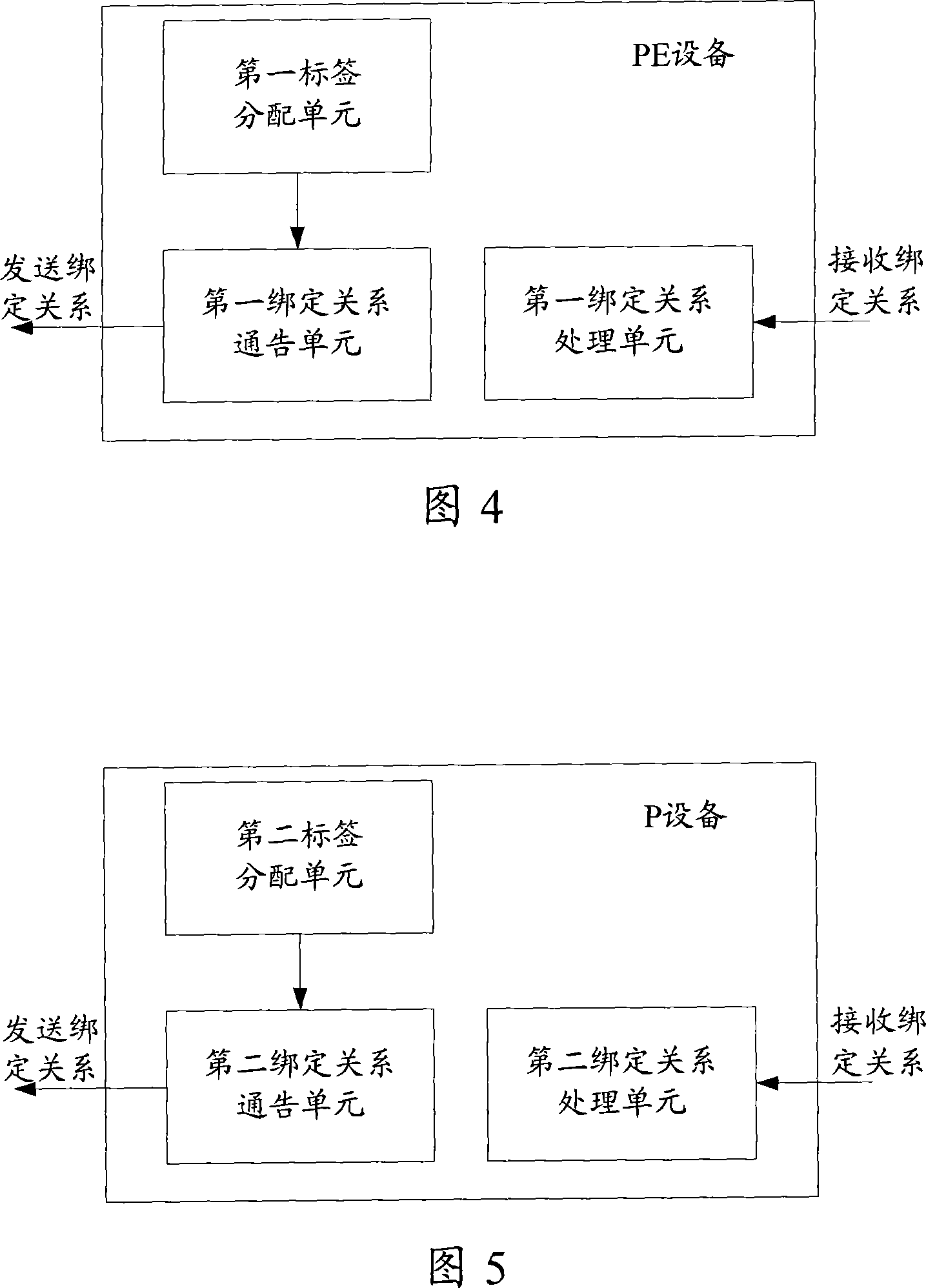

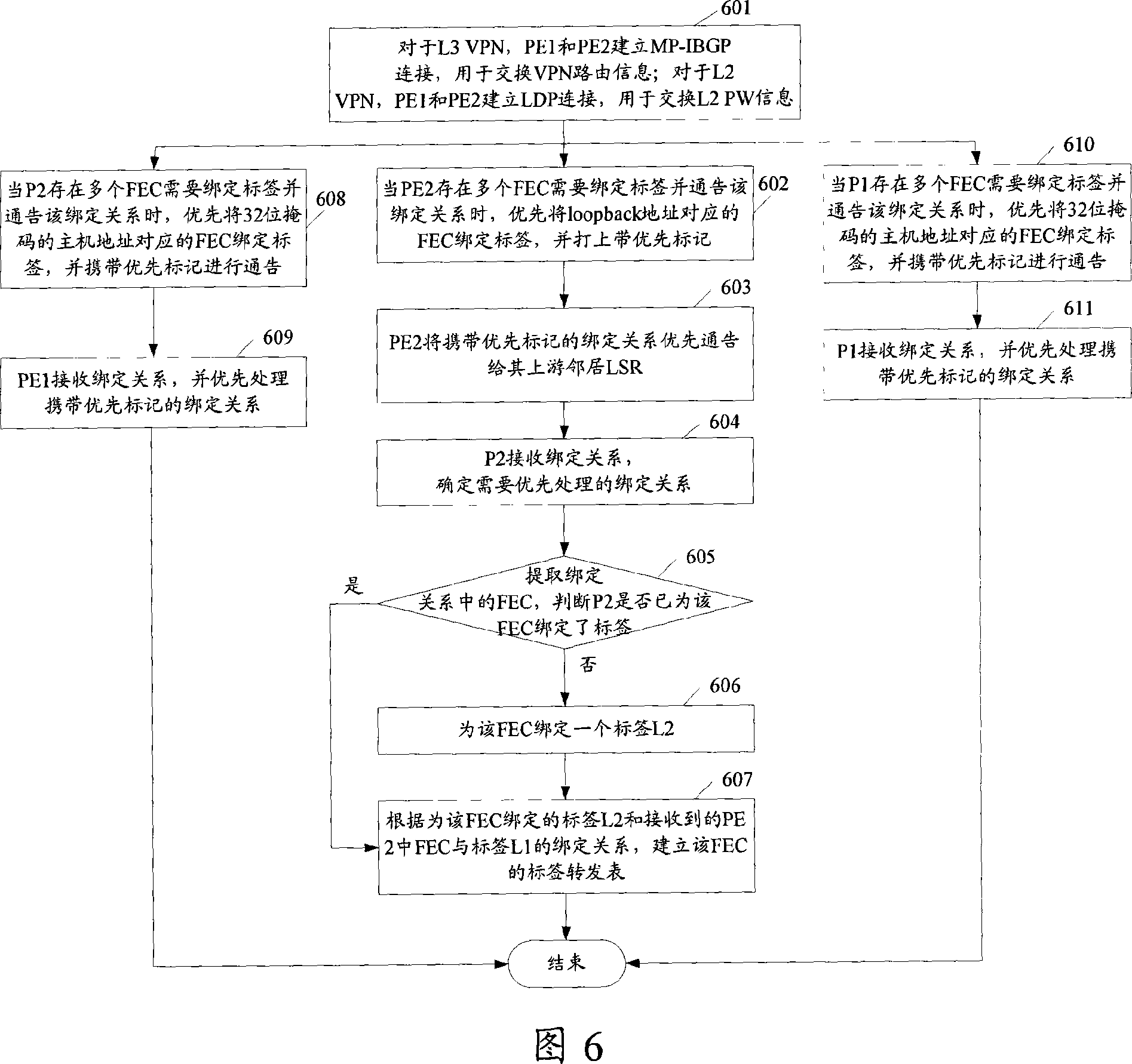

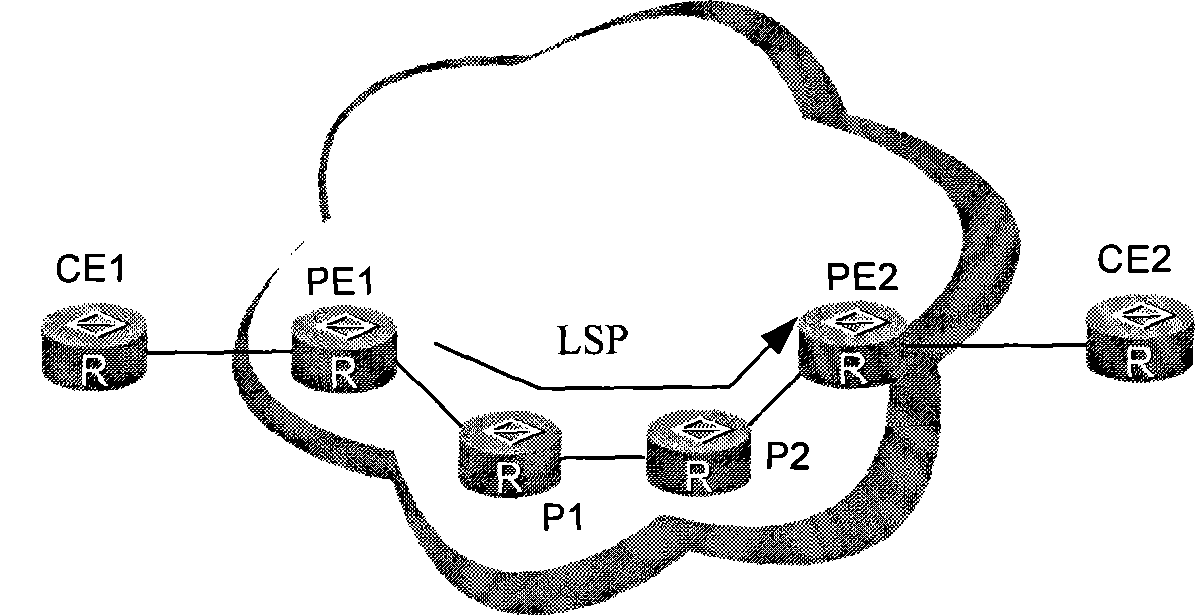

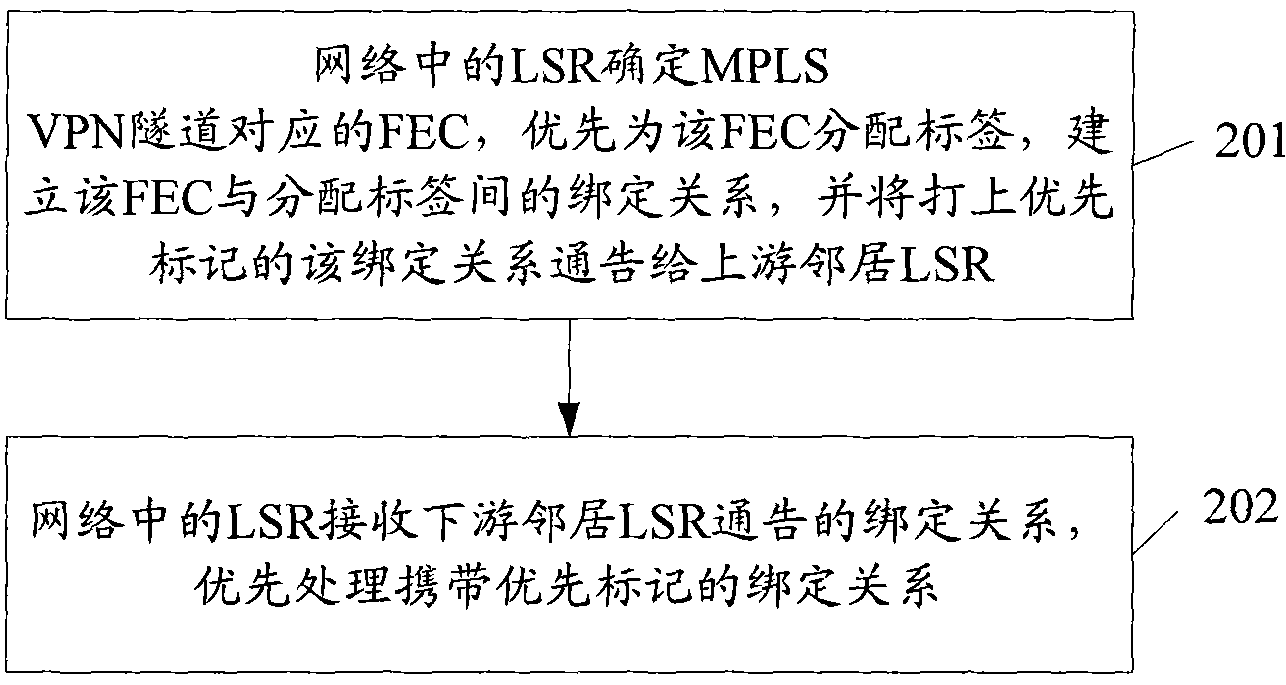

Label exchange route setting method, system and equipment of virtual special network channel

ActiveCN101090355AImprove build speedGuaranteed forwarding performanceNetworks interconnectionIp addressMPLS VPN

This invention discloses a method for setting up label switch path of MIPLS VPN tunnel including: a label switch router LSR in a network determines the forward equivalence FEC corresponding to the destination IP address of the MPLS VPN tunnel to distribute label to it firstly and set up a binding relation between the FEC and the distributed label and notifies the binding relation with the prior label to its upper reach LSR, which receives the binding relation notified by the lower reach LSR to process the binding relation with the prior label priorly. This invention also discloses a LSP set-up system and a device of the MPLS VPN tunnel.

Owner:XINHUASAN INFORMATION TECH CO LTD

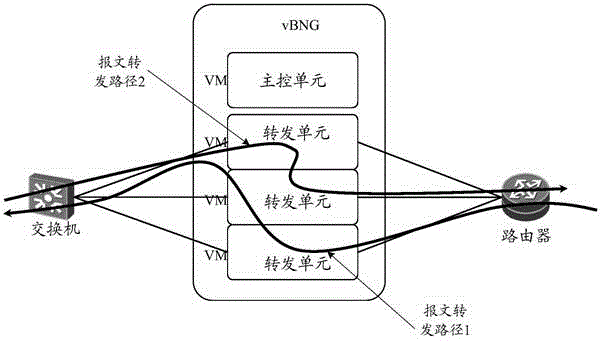

Message forwarding method, device and system

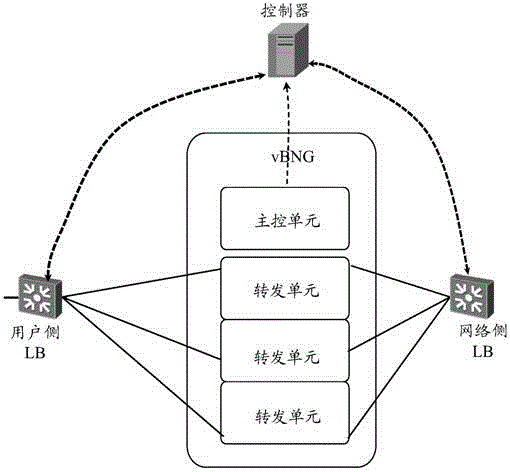

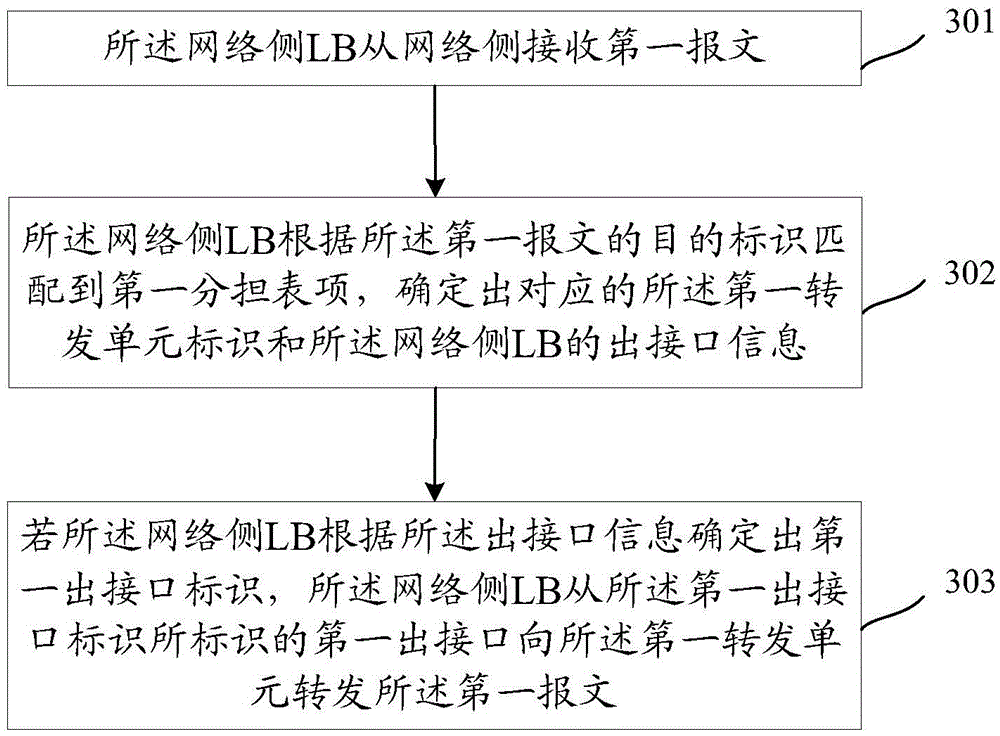

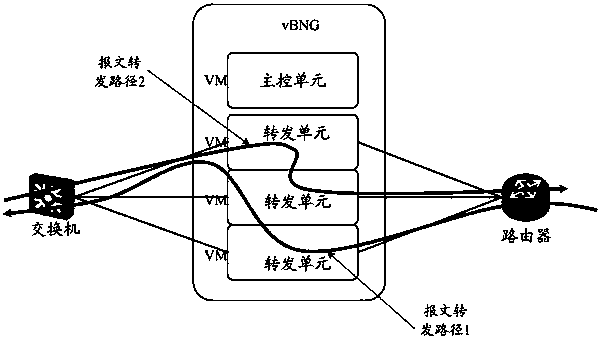

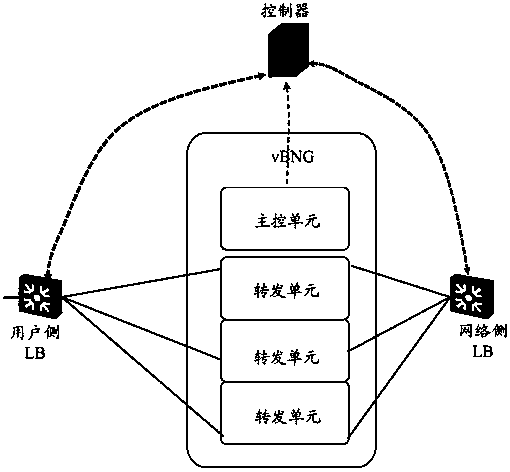

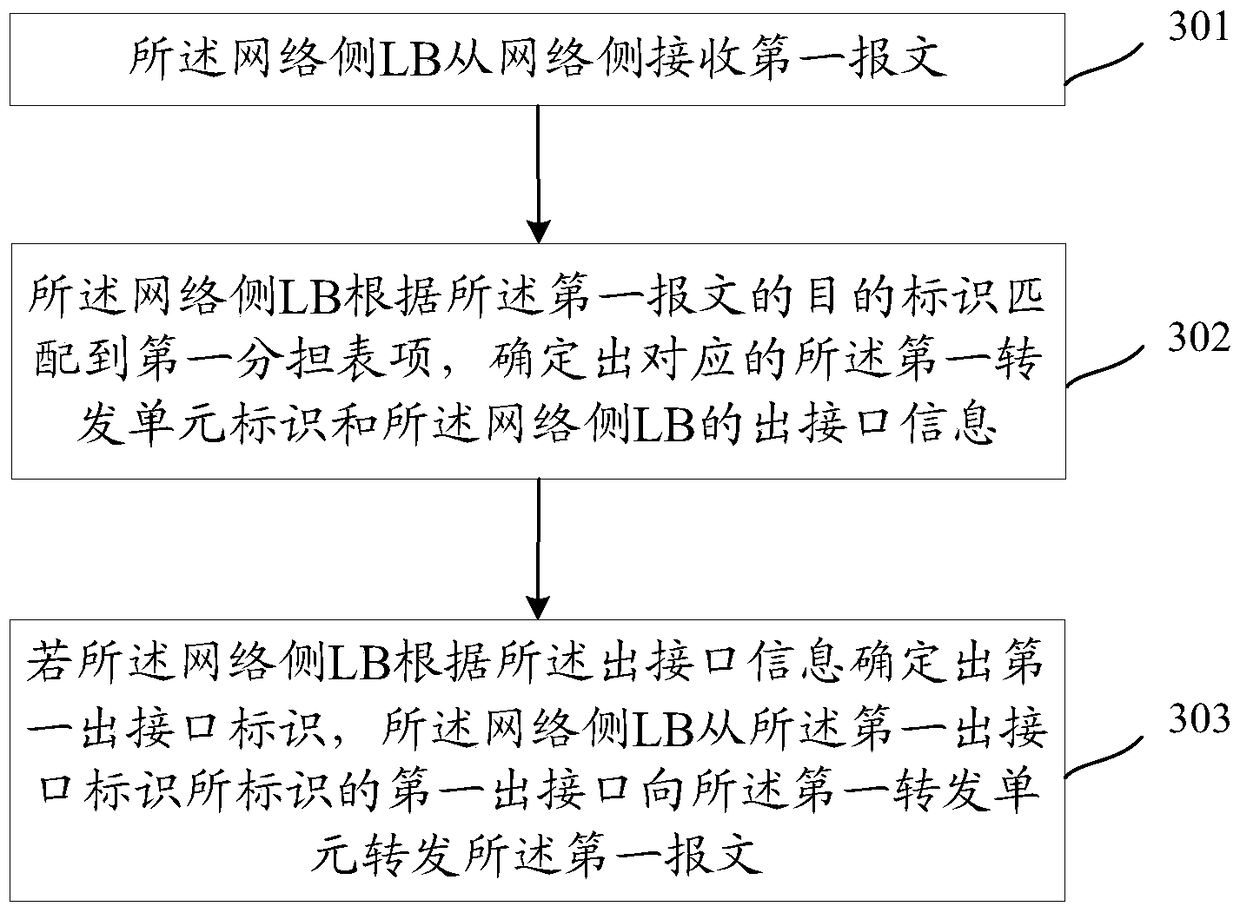

ActiveCN105634956AGuaranteed forwarding performanceReduce cross-VM forwardingData switching networksDistributed computingMessage forwarding

The invention discloses a message forwarding method, a device and a system. In a forwarding network including a controller, a user side LB, a vBNG and a network side LB, when the network side LB receives a first message forwarded from the network side to a target terminal of the user side, by matching a target identifier used for identifying the target terminal of the first message to a first sharing chart item, a pre-planned forwarding path from a first output port of the network side LB to a first forwarding unit for processing the launching of the target terminal can be determined, so the first message sent to the target terminal can be precisely forwarded to the first forwarding unit for processing the online of the target terminal; it is avoided that the message forwarded from the network side to the user side may be forwarded to an improper forwarding unit in the vBNG; occasions that messages received on the network side should be forwarded across VMs in the vBNG are avoided; and forwarding performance of the vBNG is ensured.

Owner:HUAWEI TECH CO LTD

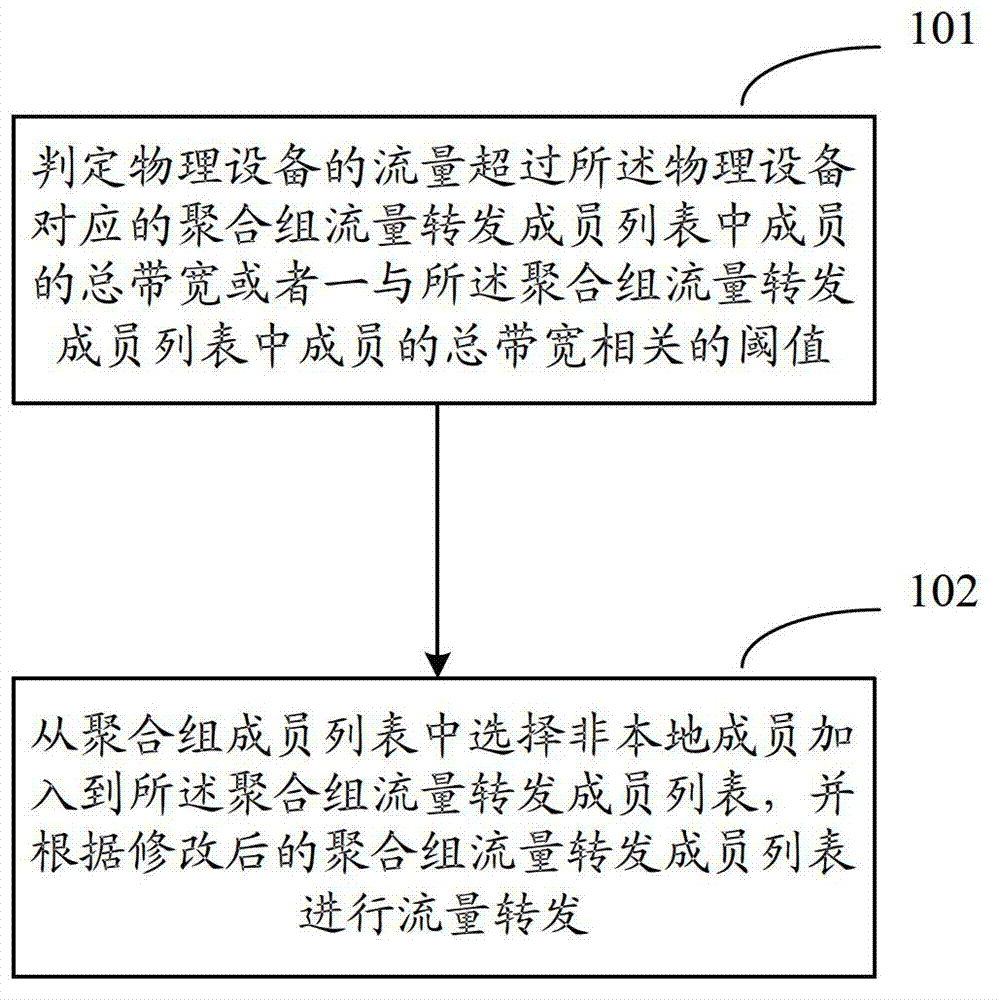

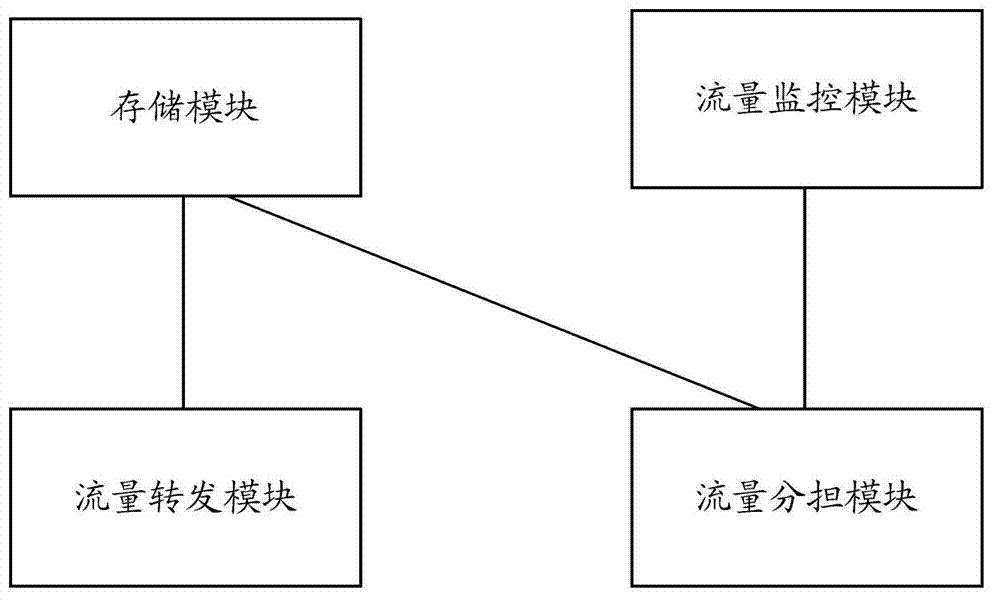

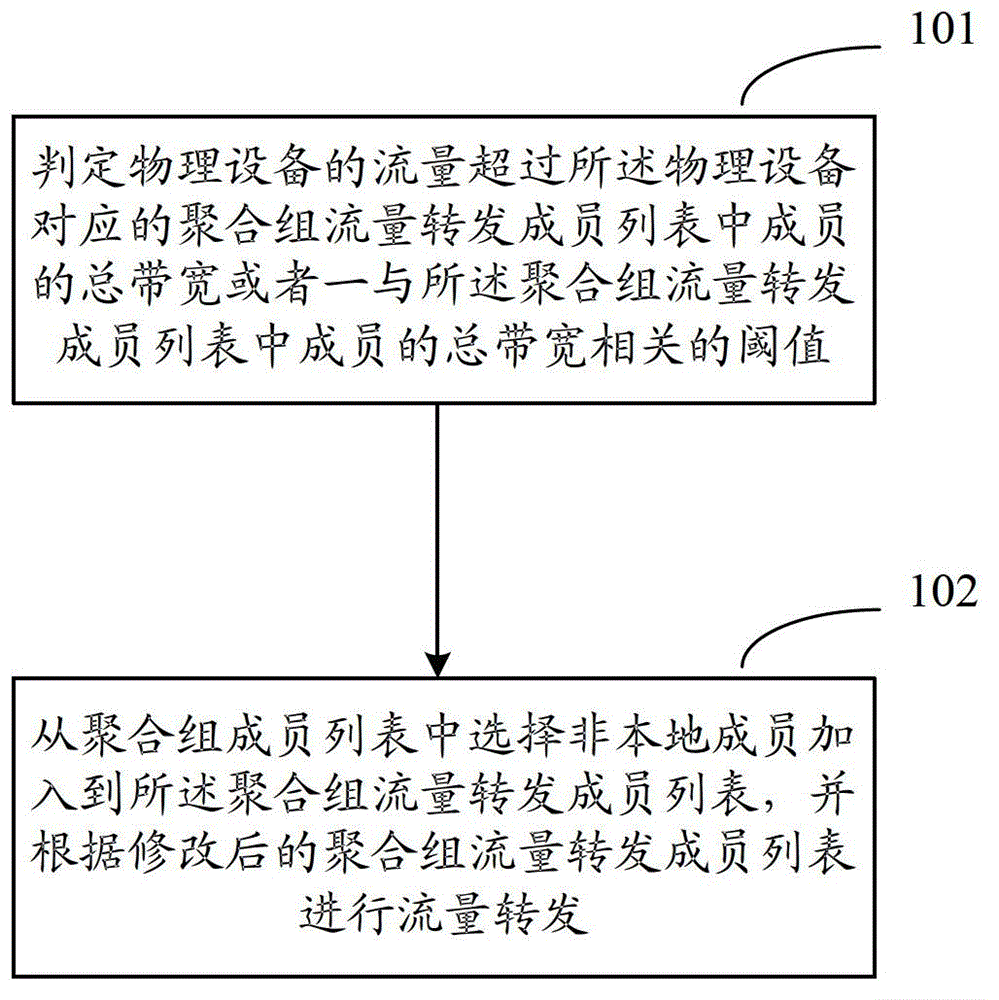

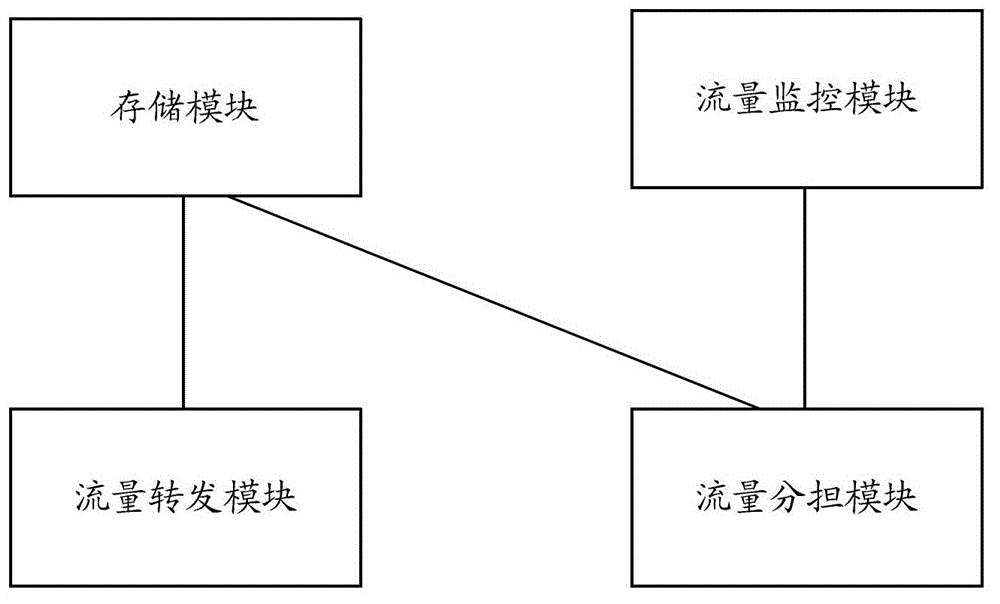

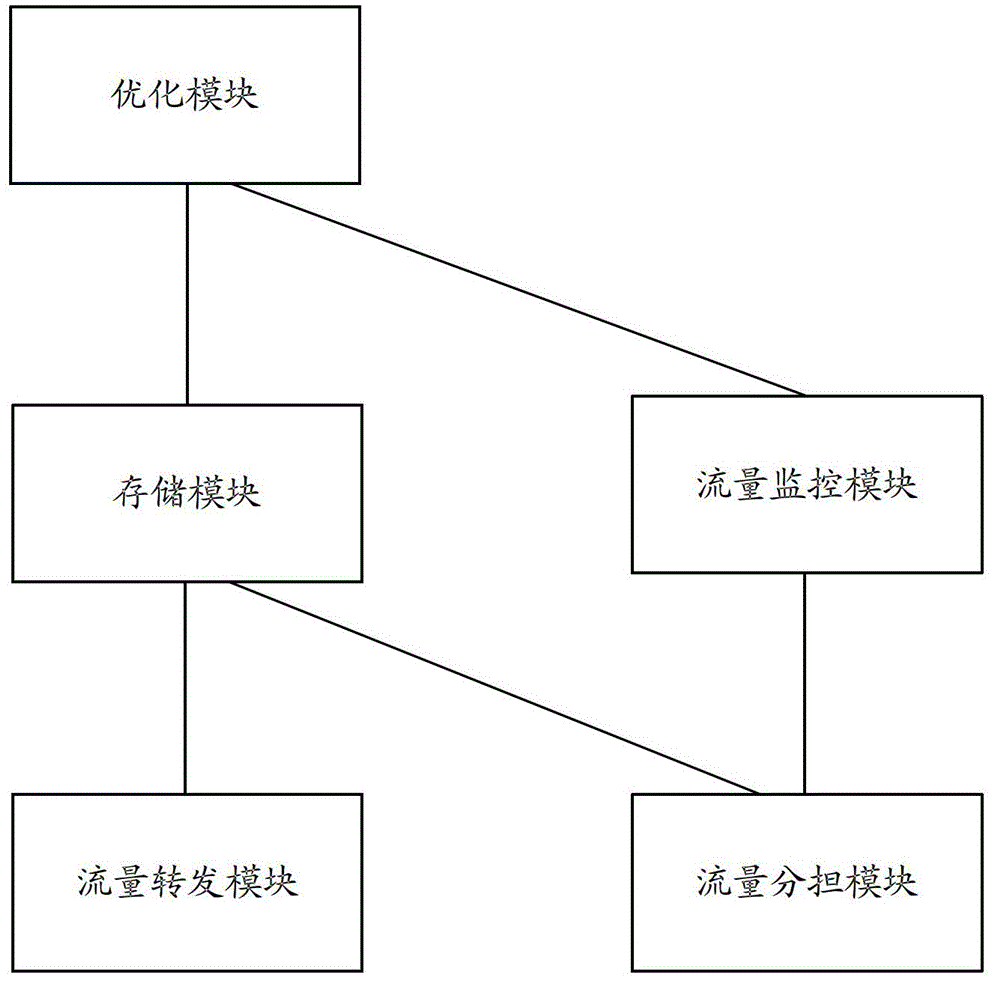

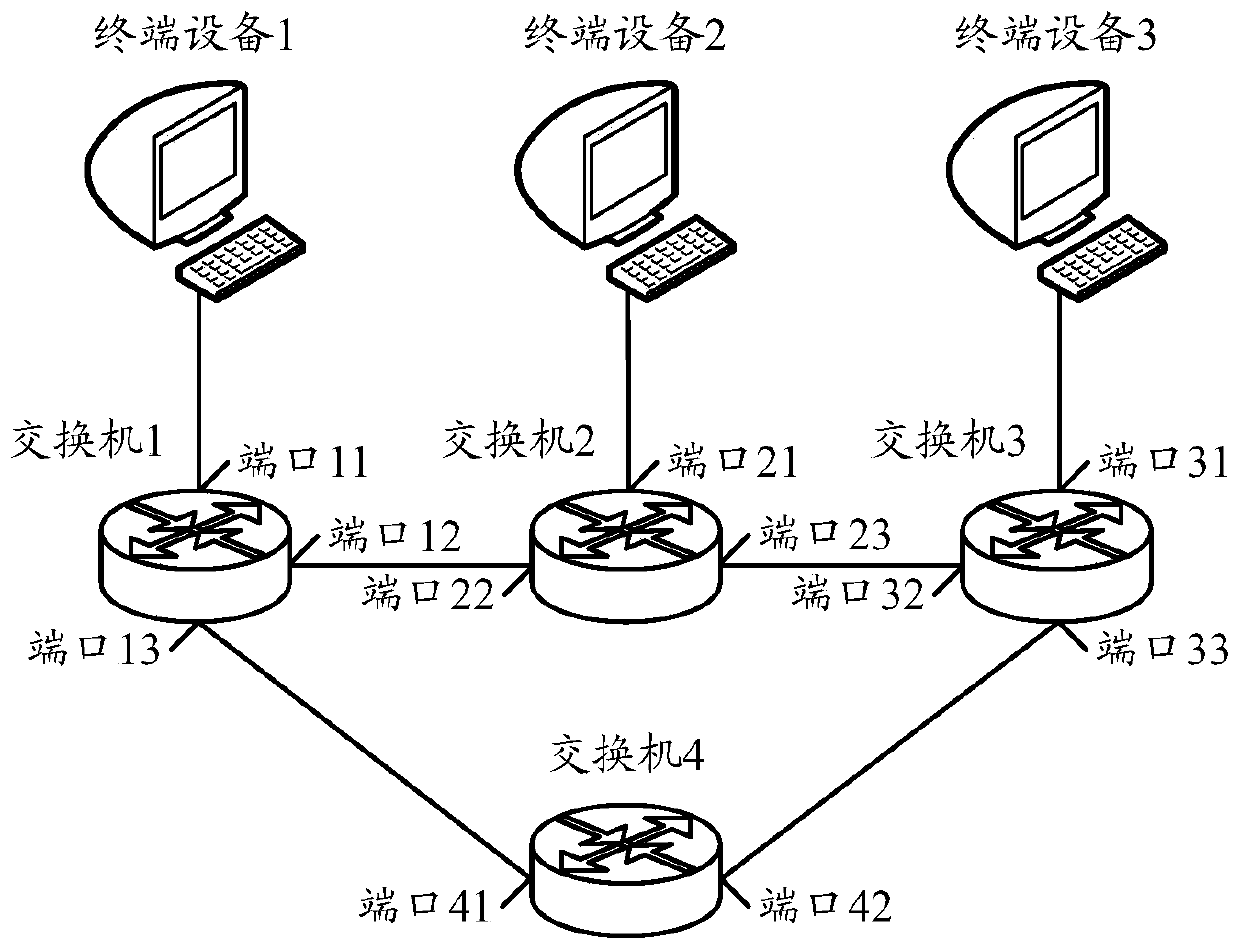

Method and system for forwarding traffic based on virtual switch cluster

ActiveCN102769568ARealize forwardingGuaranteed forwarding performanceNetwork topologiesData switching networksTraffic capacityVirtual switch

The invention discloses a method for forwarding traffic based on a virtual switch cluster. The method comprises the following steps of: setting an aggregation group member list which stores all member information of an aggregation group; setting an aggregation group traffic forwarding member list which stores information of aggregation group members which are used for forwarding the traffic, wherein the aggregation group traffic forwarding member list only comprises aggregation group local member information in an initial state; and determining that the traffic of physical equipment exceeds the total bandwidth of members in the aggregation group traffic forwarding member list, or exceeds a threshold value related to the total bandwidth, adding nonlocal members which are selected from the aggregation group member list to the aggregation group traffic forwarding member list, and forwarding the traffic according to the modified aggregation group traffic forwarding member list. The invention also discloses a system for forwarding the traffic based on the virtual switch cluster correspondingly. By the method and the system, the traffic can be forwarded in the scene of the virtual switch cluster on the premise of occupying limited bandwidth of a stack link as few as possible, so that the performance of traffic forwarding in the scene of the virtual switch cluster is ensured.

Owner:ZTE CORP

Method for implementing virtual MAC address in digital subscriber line access server equipment

InactiveCN1545265ANo forwarding performance impactGuaranteed forwarding performanceData switching by path configurationDigital subscriber lineComputer hardware

The invention provides a method that a DSLAM device implements virtual MAC addresses, including; when learning the basic functions and addresses of an exchanger, according to user configured VMAC mapping method, a DSLAM device generates a VMAC address corresponding to the user MAC address, and when configuring user data in a Radius or broadband connection sever, inputs user marked VMAC and binds it with user name. The invention completes a two-way MAC address conversion operation by hardware device in order to implement the only mark of the user, which ensures transmitting performance of the system.

Owner:GANGWAN NETWORK CO LTD

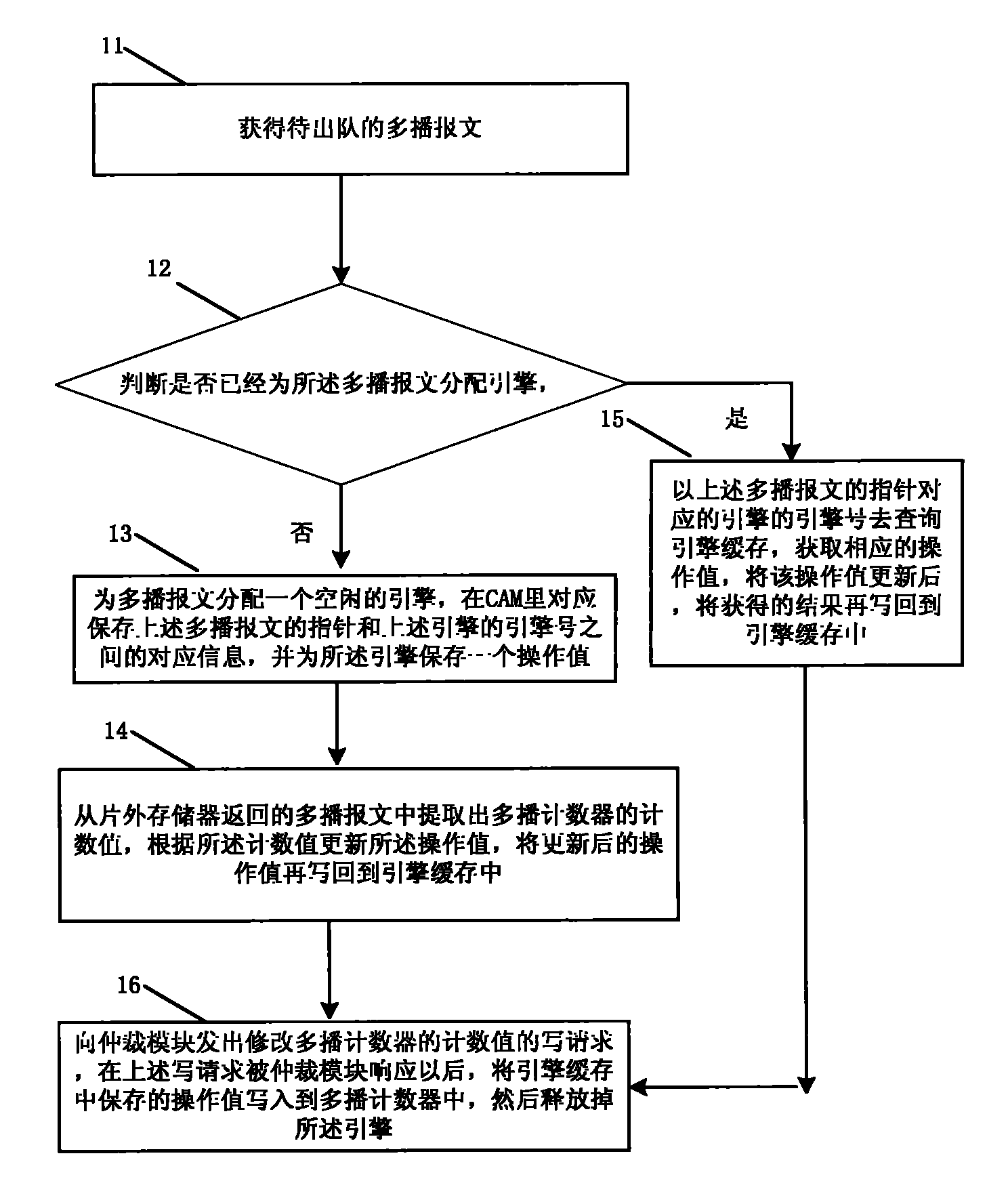

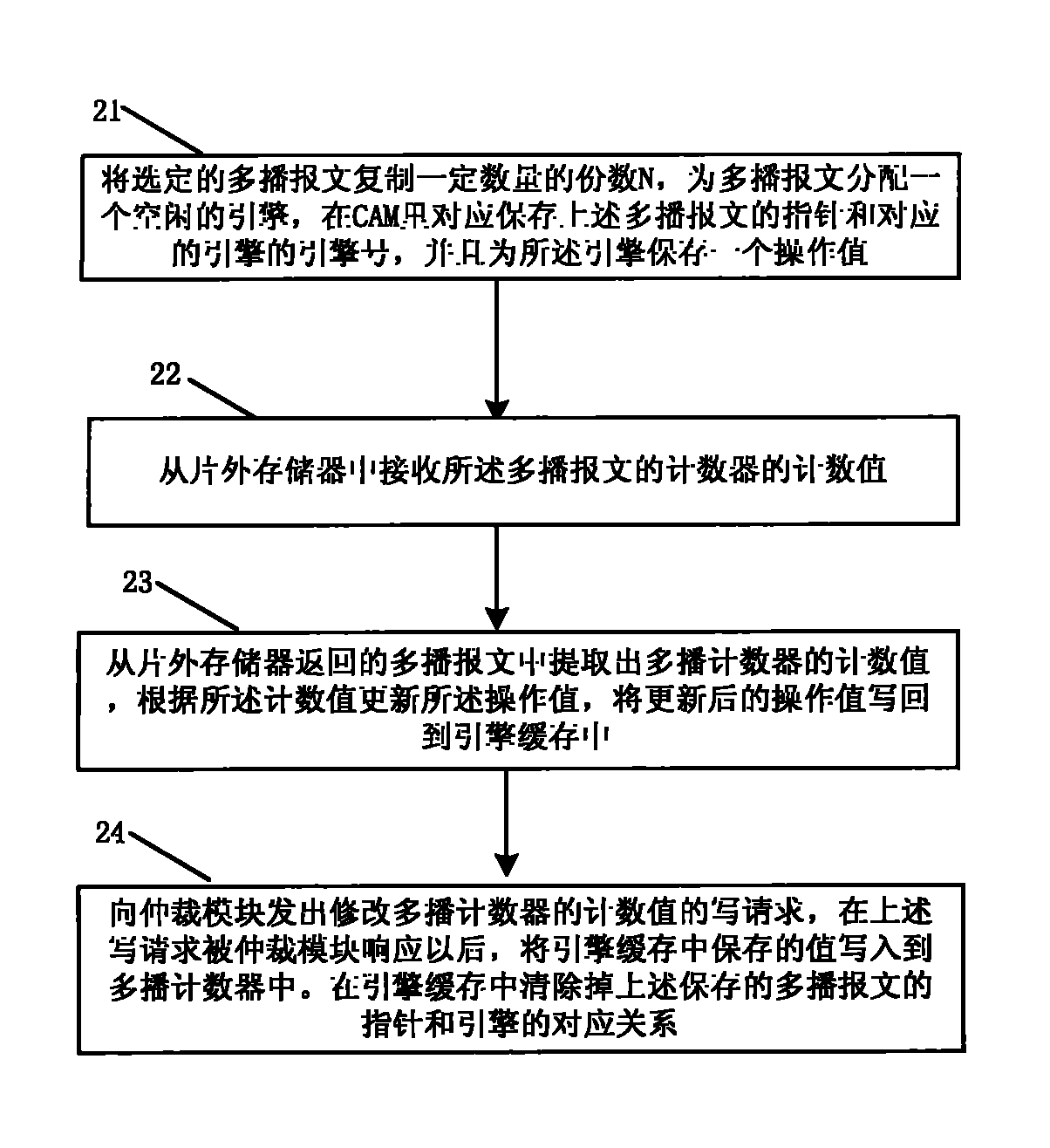

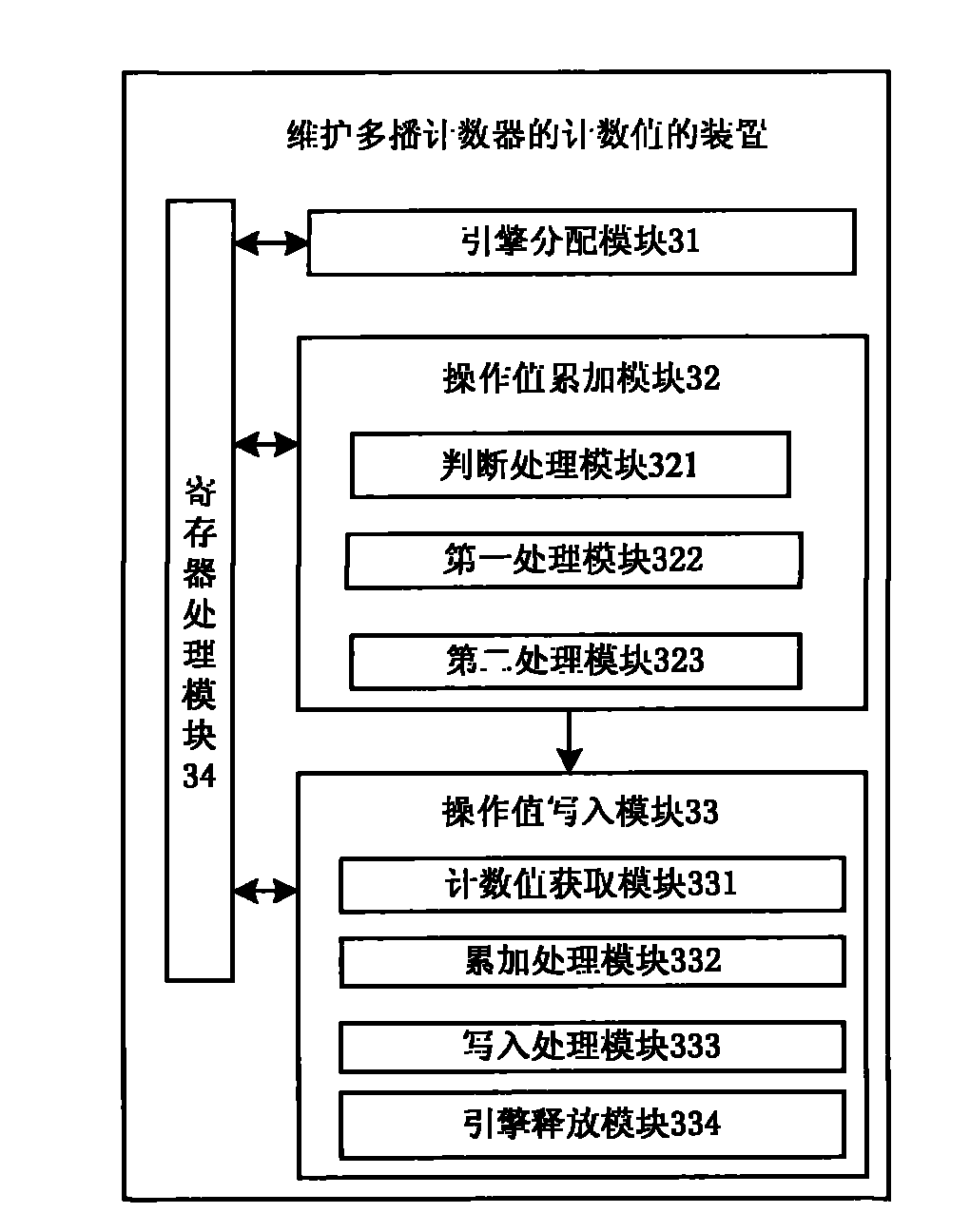

Method and device for maintaining count value of multicast counter

InactiveCN101848150AGuaranteed forwarding performanceAlleviate bandwidth impactData switching networksHigh rateHigh speed memory

The embodiment of the invention provides a method and a device for maintaining a count value of a multicast counter. The method mainly comprises the following steps: acquiring a multicast message to be dequeued, allocating an engine to the multicast message to be dequeued, and recording an operation value, wherein the operation value is used for recording the information of the quantity of the dequeued multicast messages; and updating the operation value based on the dequeuing situation of the other multicast messages, and updating the count value of the multicast counter based on the operation value. The invention can remit the impact of the large-quantity high-rate multicast messages on the bandwidth of the common high-speed memories of QDR, DDR and the like to a certain extent, and can ensure the message forwarding performance of the system.

Owner:HUAWEI TECH CO LTD

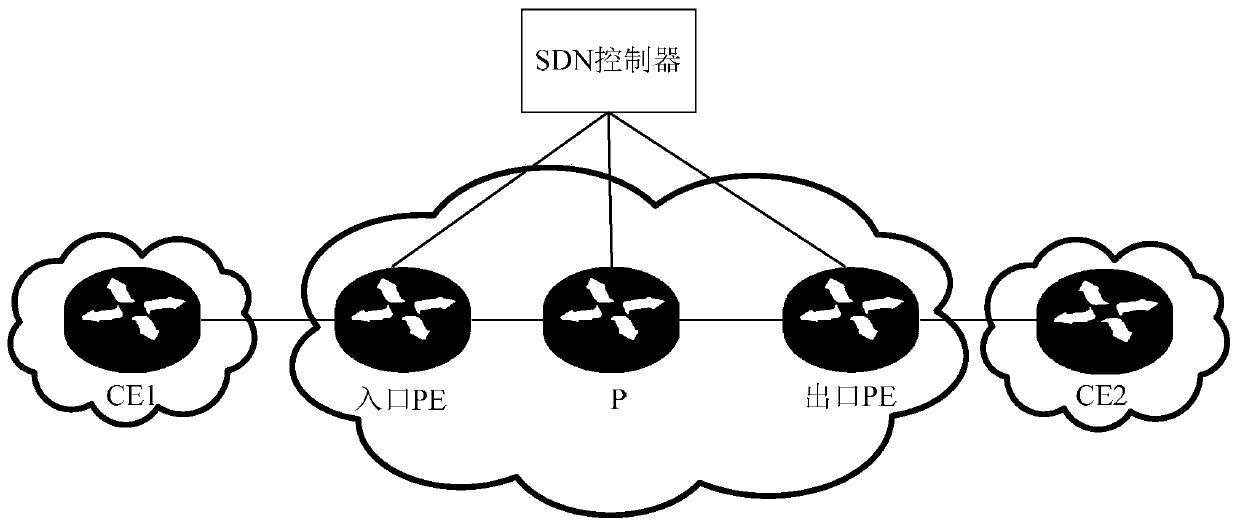

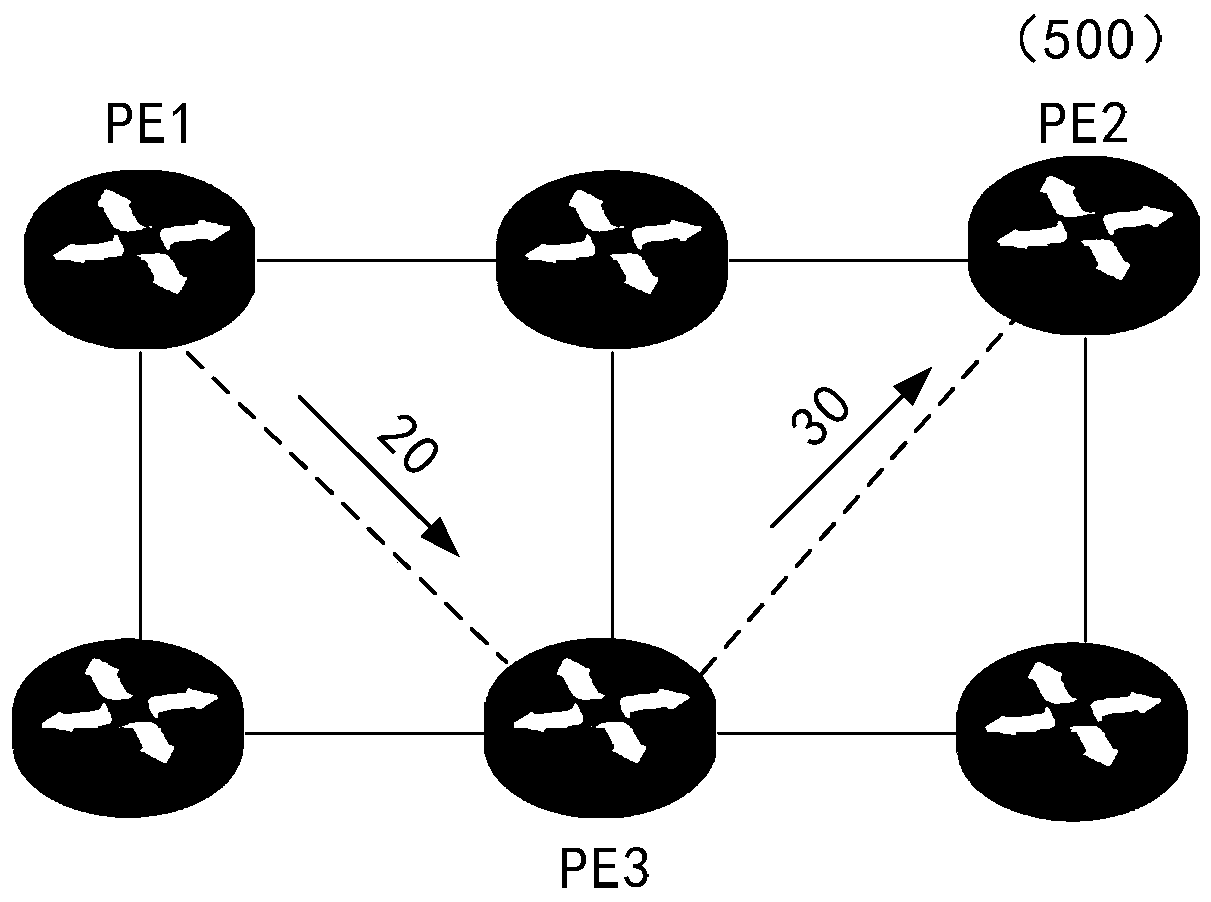

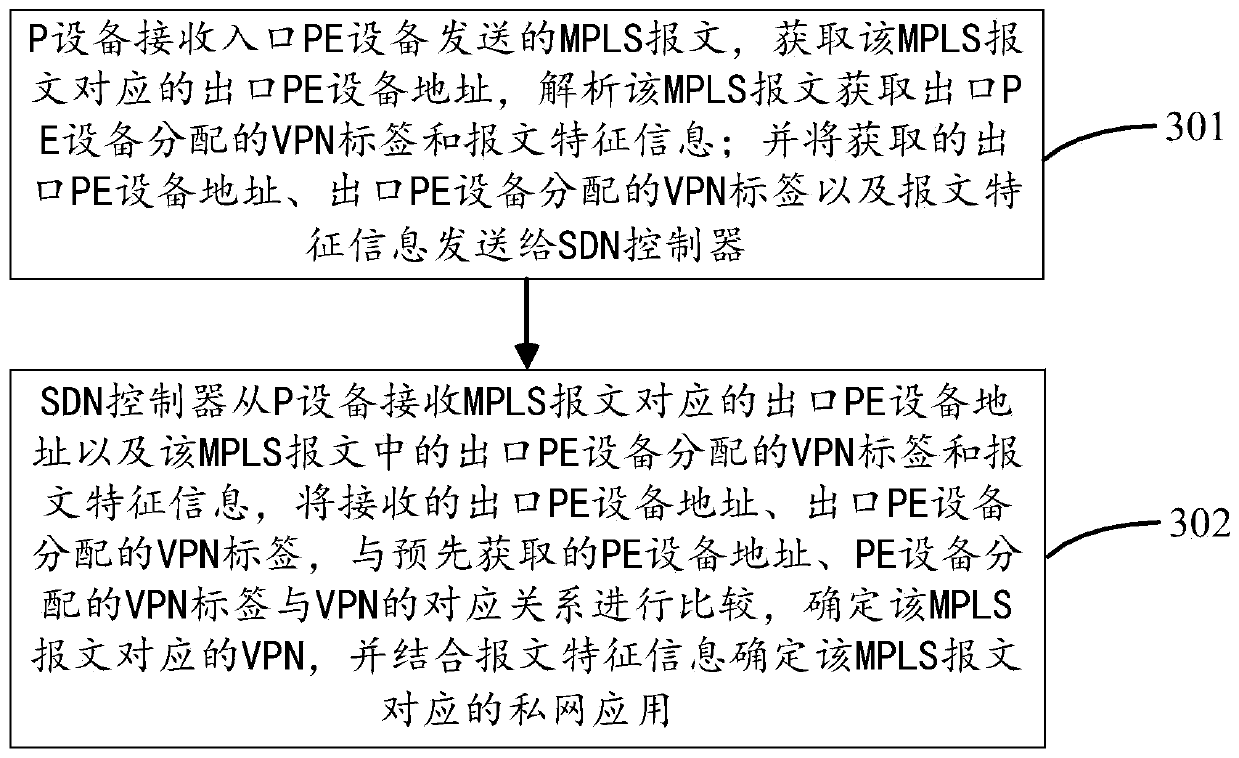

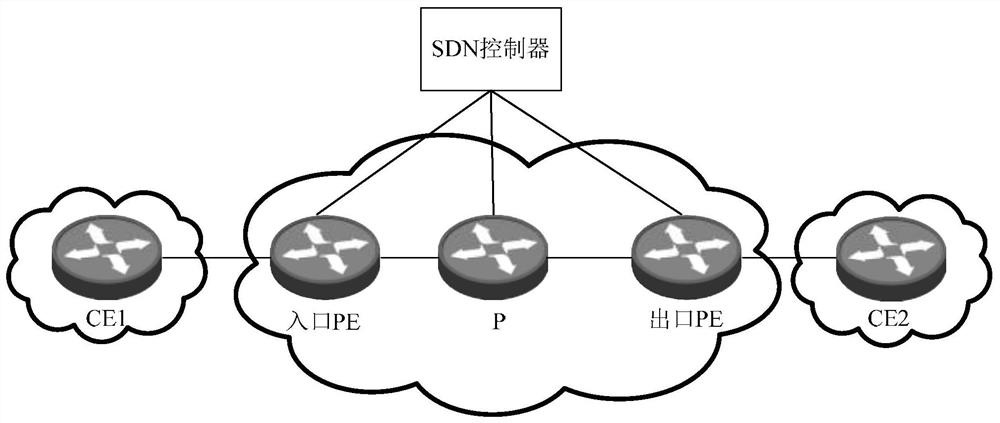

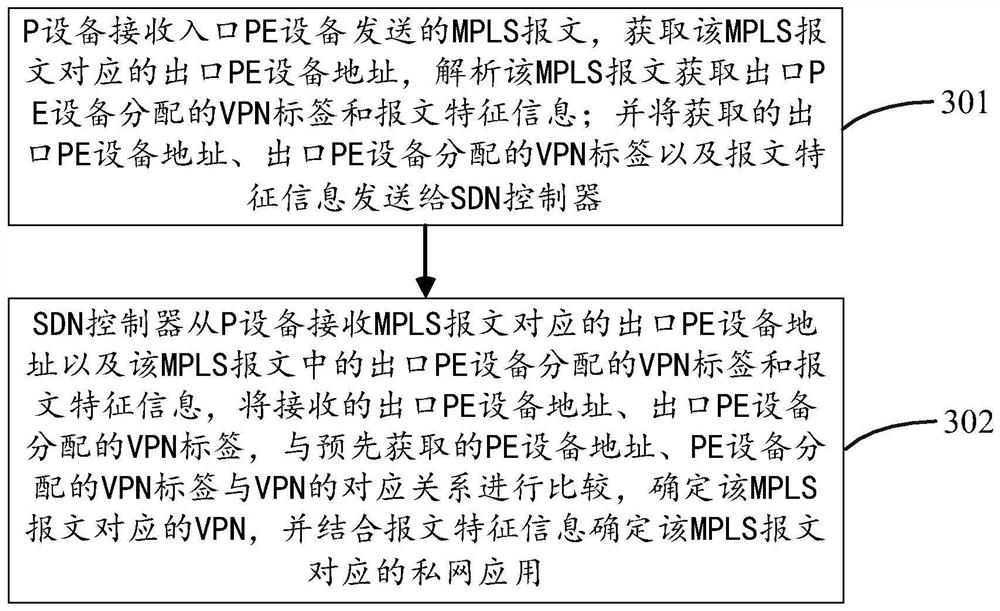

Private network application identification system and method, SDN controller and P equipment

ActiveCN110868352AUnlimited number of applicationsImprove scalabilityData switching networksPrivate networkServer

The embodiment of the invention discloses a private network application identification system and method, an SDN controller and P equipment, relates to the field of data communication, and realizes visualization of private network application traffic in a service provider network. The system at least comprises P equipment and an SDN controller, wherein the SDN controller is used for receiving an exit PE device address corresponding to the MPLS message and a VPN label and message feature information allocated by an exit PE device in the MPLS message from the P device, and sending the received export PE equipment address and the VPN label allocated by the export PE equipment to a VPN server, comparing the MPLS message with a pre-acquired PE device address and a corresponding relationship between a VPN label allocated by the PE device and the VPN, determining the VPN corresponding to the MPLS message, and determining a private network application corresponding to the MPLS message in combination with the message feature information.

Owner:MAIPU COMM TECH CO LTD

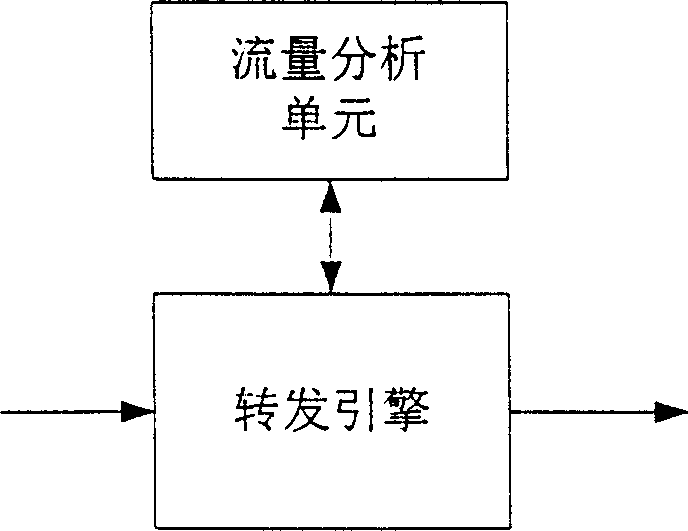

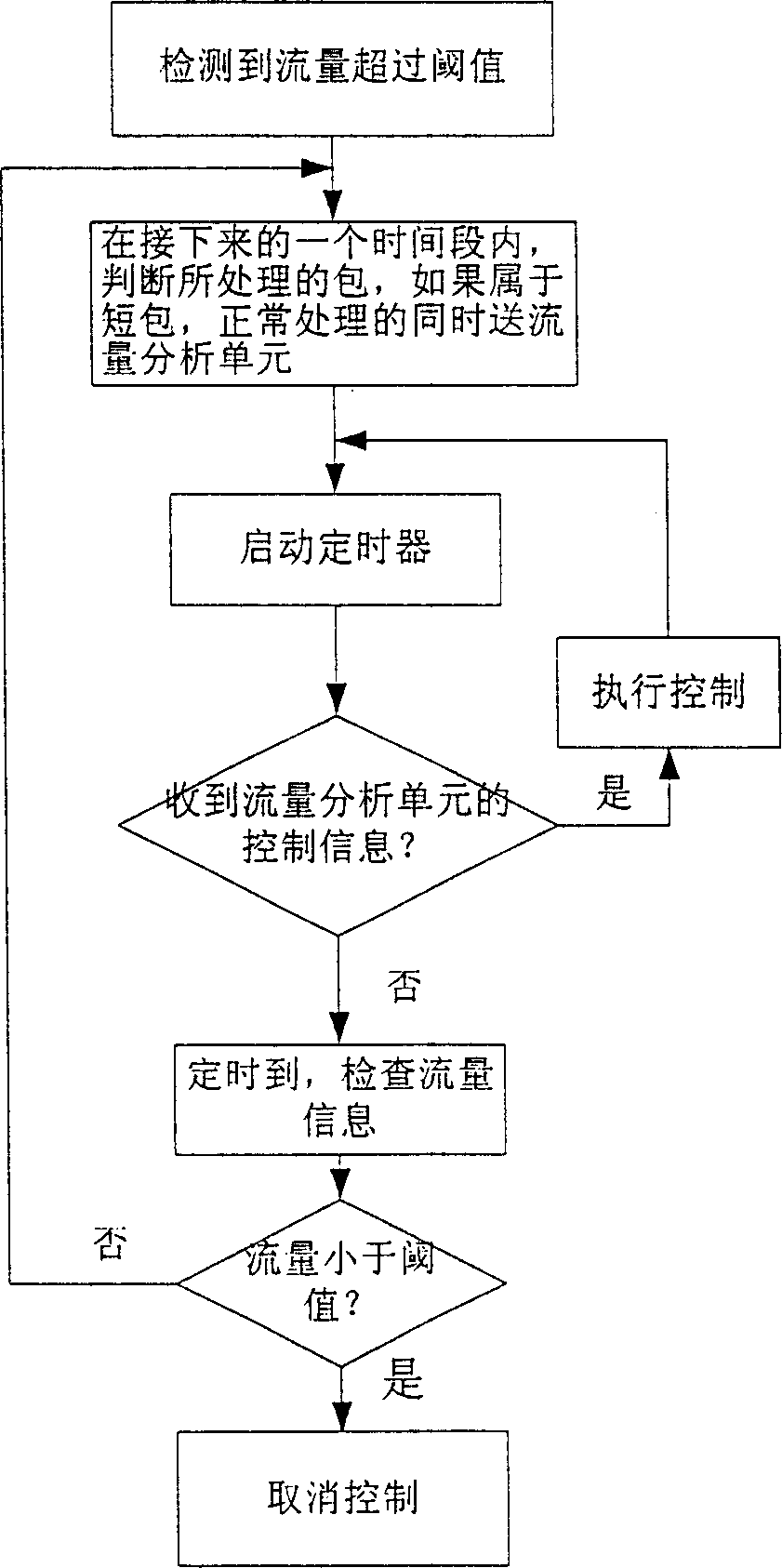

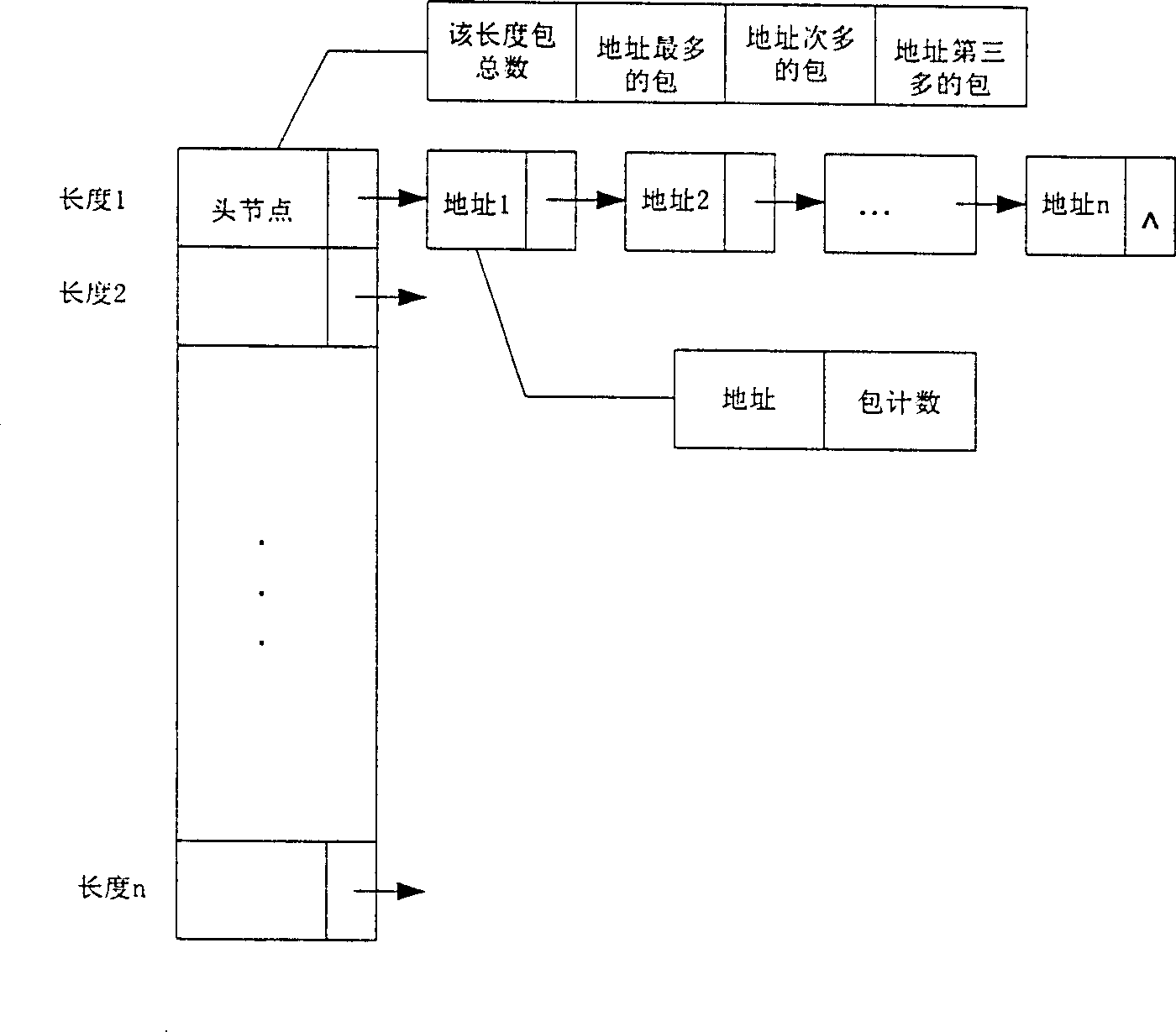

Device and method for realizing abnormal flow control

InactiveCN1282331CReduce loadGuaranteed forwarding performanceNumber-allocation/character-counting for messagesTraffic volumeTraffic analysis

The invention relates to a device and method for realizing abnormal flow control, in particular to a processing method for controlling abnormal flow in communication data forwarding equipment. The present invention consists of two functional modules. The forwarding engine is responsible for data forwarding and actual traffic detection and control processing. The traffic analysis unit performs statistical analysis according to the packets sent by the forwarding engine, and uses the analysis results to set the forwarding engine and control the forwarding engine. the behavior of. The real-time analysis in the method adopts a sampling method, that is, to analyze short packets within a certain period of time, rather than continuously and dynamically analyzing them. The invention greatly reduces the processing workload, and ensures the forwarding performance of the forwarding engine, can control the most common abnormal flow in the existing network environment, and has strong practical value in the field of data communication.

Owner:ZTE CORP

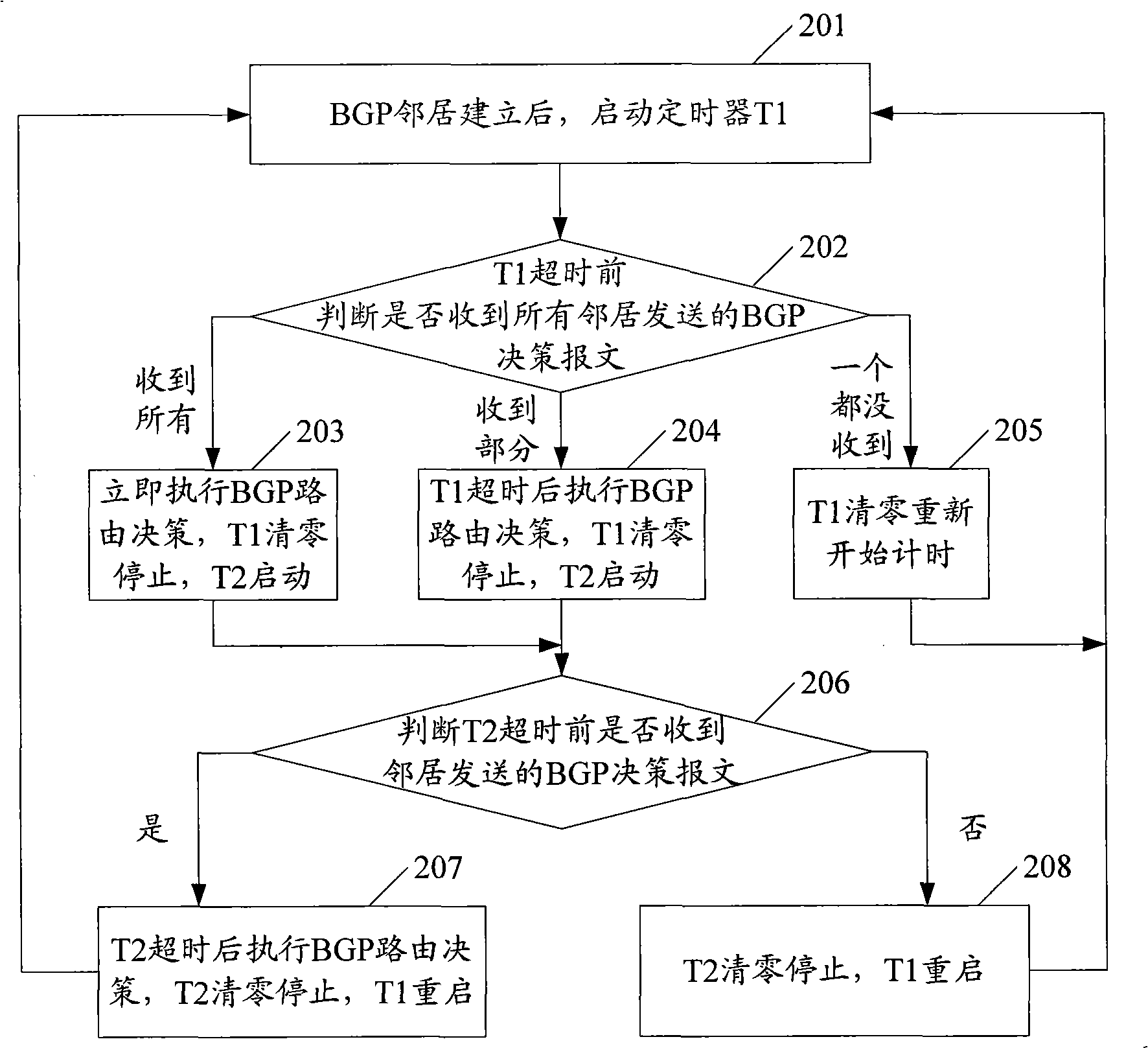

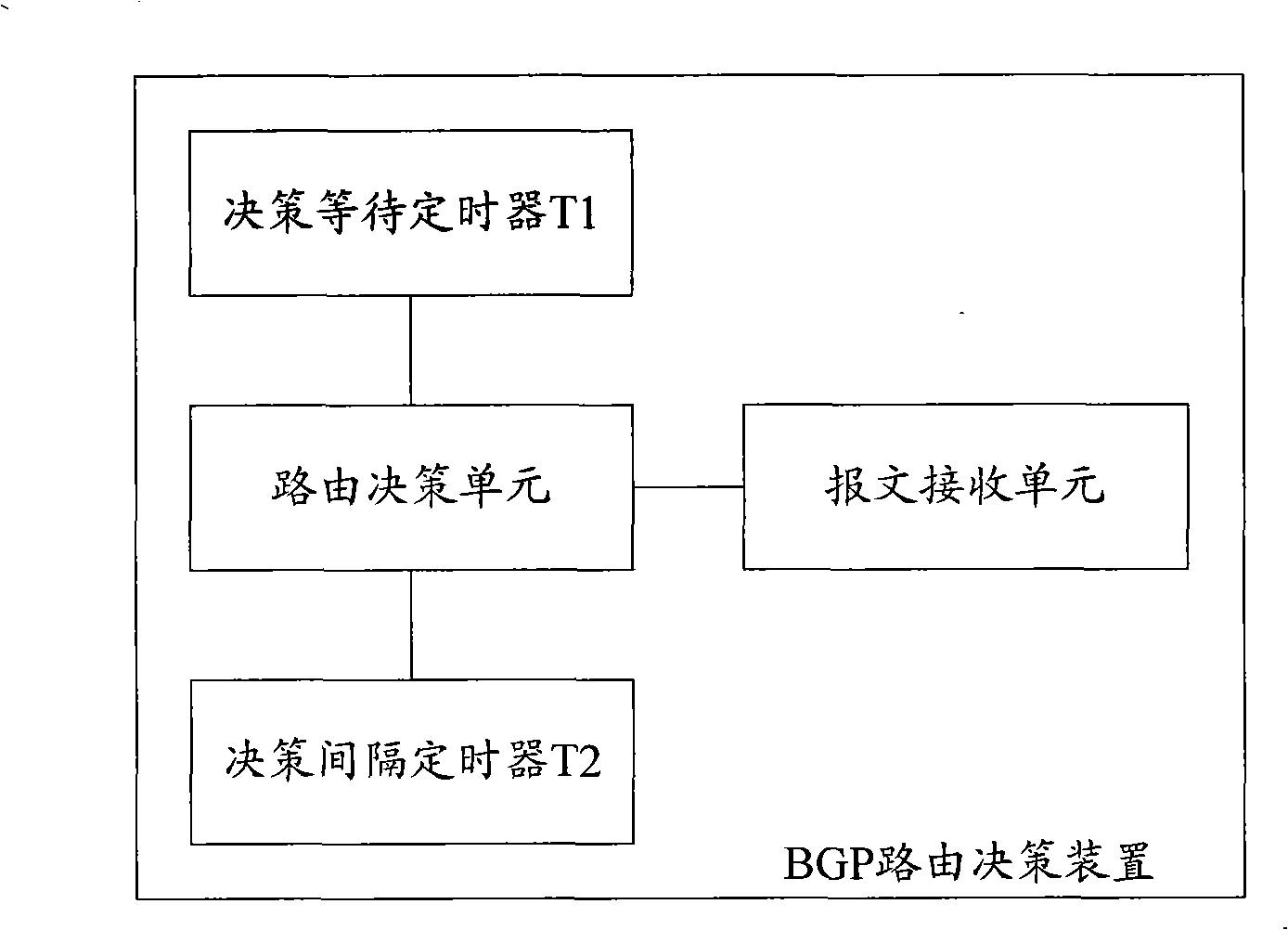

Method and apparatus for deciding BGP route

InactiveCN101304379AReduce occupancyGuaranteed forwarding performanceData switching networksRouting decisionBorder Gateway Protocol

Owner:NEW H3C TECH CO LTD

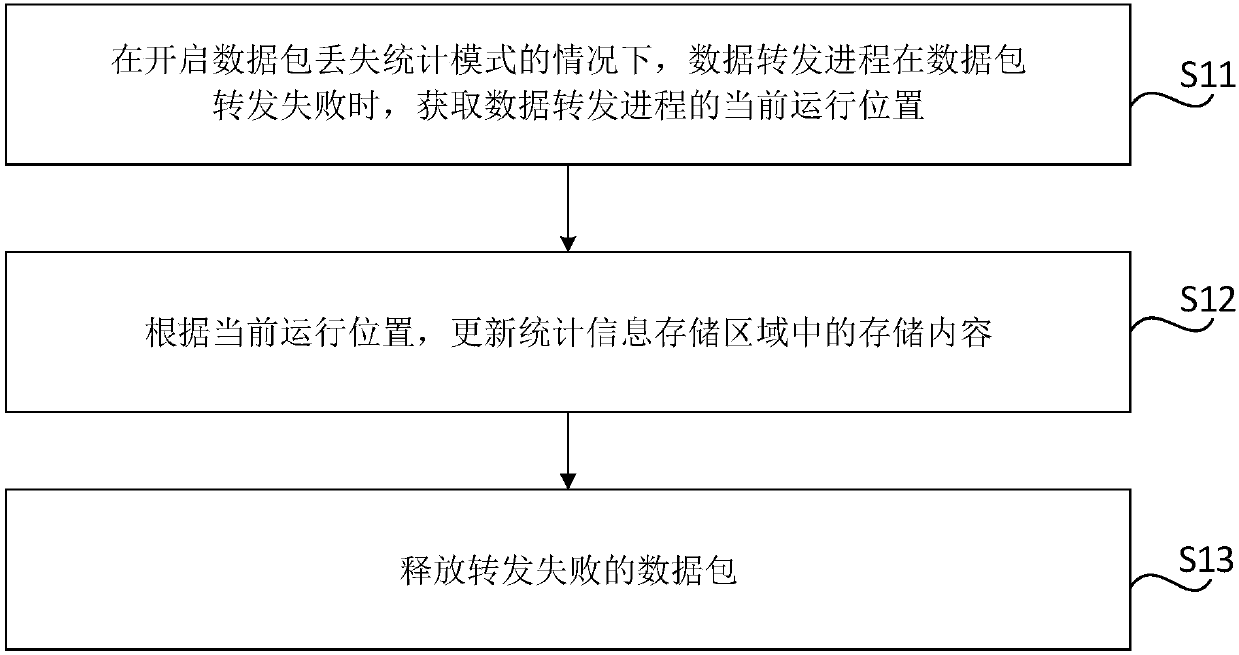

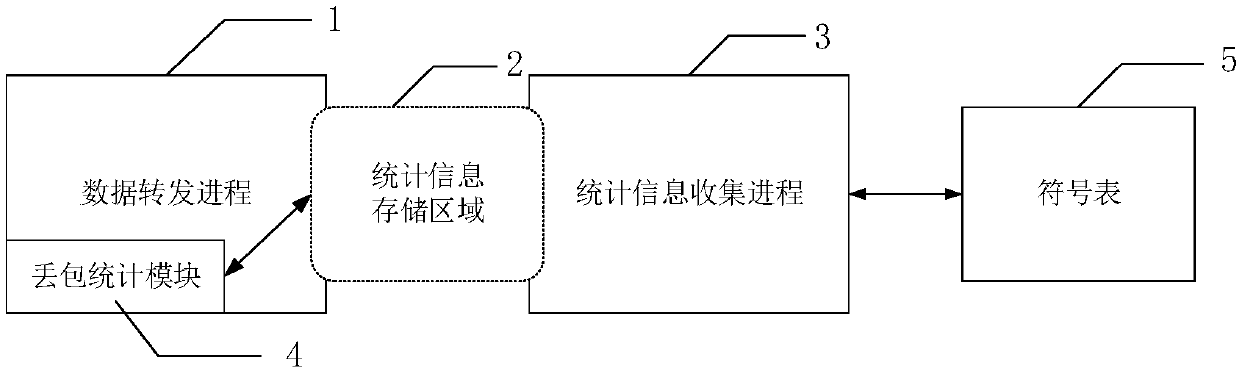

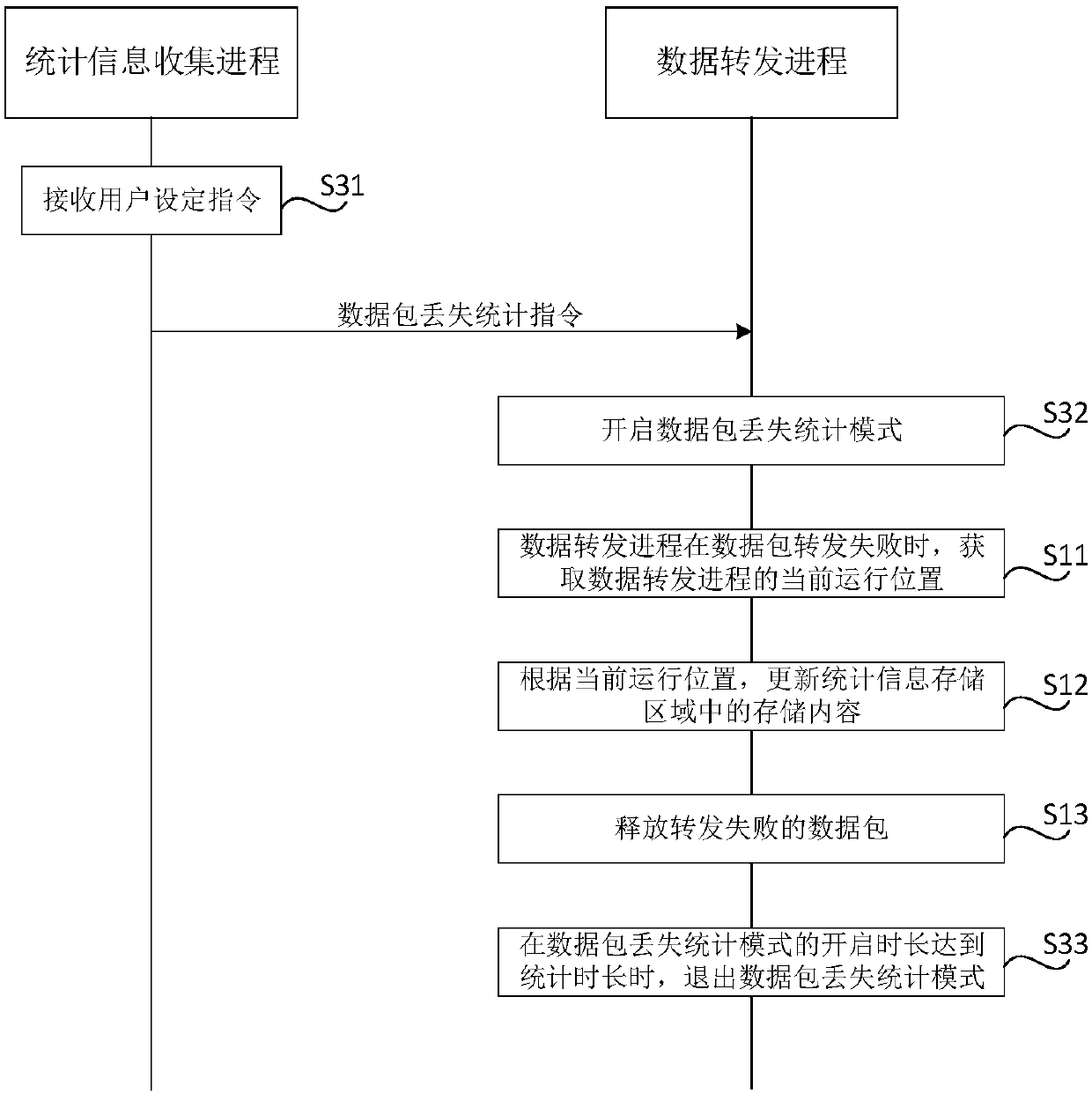

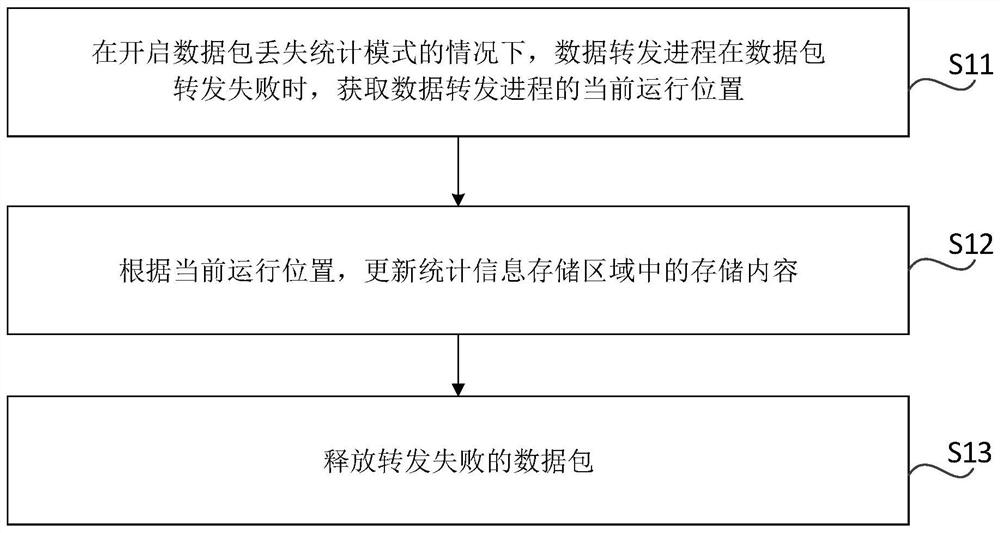

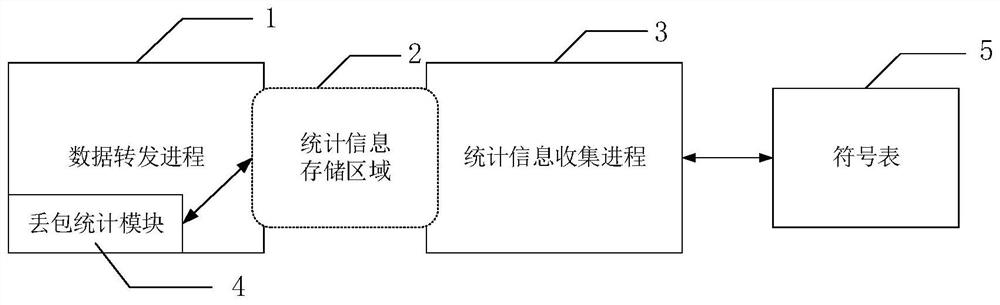

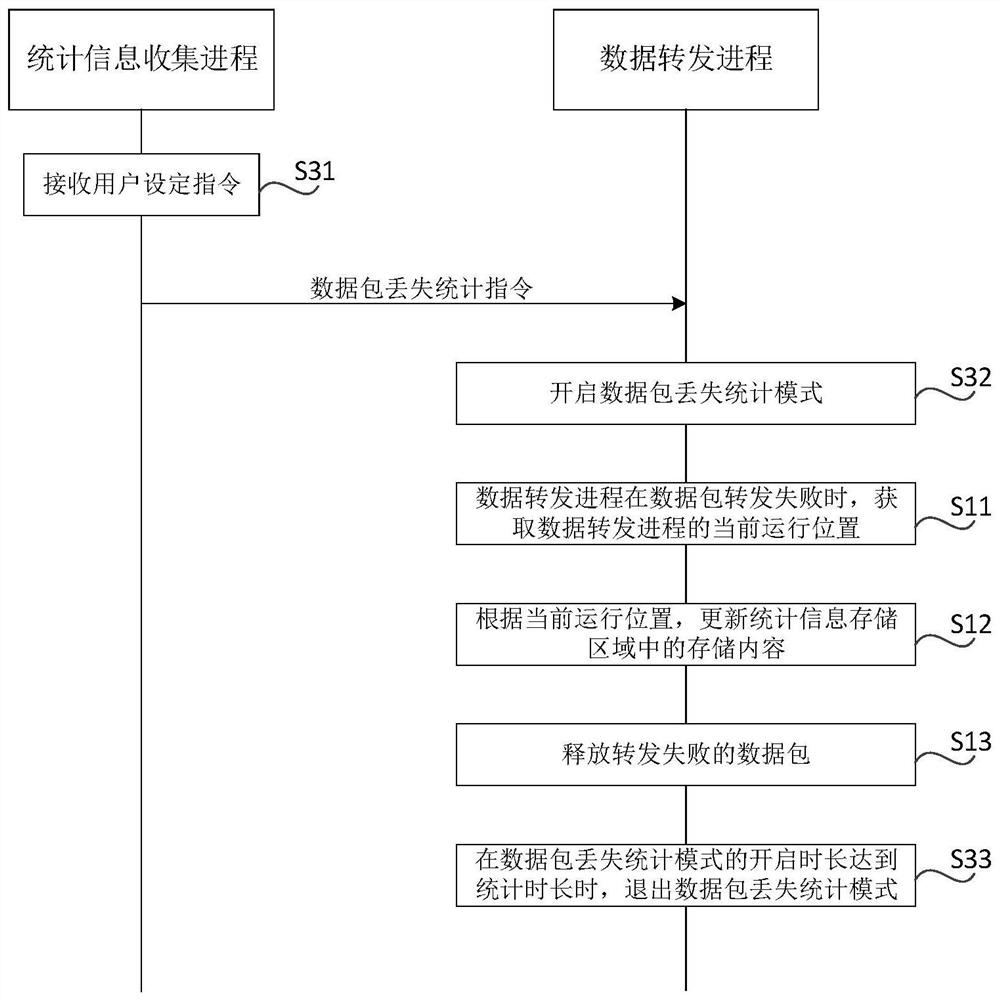

Method and system for processing data packet loss, readable storage medium and electronic equipment

ActiveCN107872363AGuaranteed forwarding performanceImprove stabilityData switching networksPacket lossTechnician

The invention relates to a method and a system for processing data packet loss, a readable storage medium and electronic equipment. The method includes acquiring current running locations of data forwarding processes when data packet forwarding fails in the data forwarding processes under the condition that data packet loss statistics modes are started; updating storage contents in statistical information storage regions according to the current running locations; releasing data packets which fail to be forwarded. The statistical information storage regions are used for storing running locations of the data forwarding processes whenever data packet forwarding fails and the frequencies of data packet forwarding failure at the running locations. According to the technical scheme, the method,the system, the readable storage medium and the electronic equipment have the advantages that workload on technicians can be effectively relieved, and data packet loss statistics can be carried out on the data packets which fail to be forwarded without modification on other codes after business logics are modified; the forwarding performance of data forwarding processes can be guaranteed, and thestability of the data forwarding processes can be improved.

Owner:NEUSOFT CORP

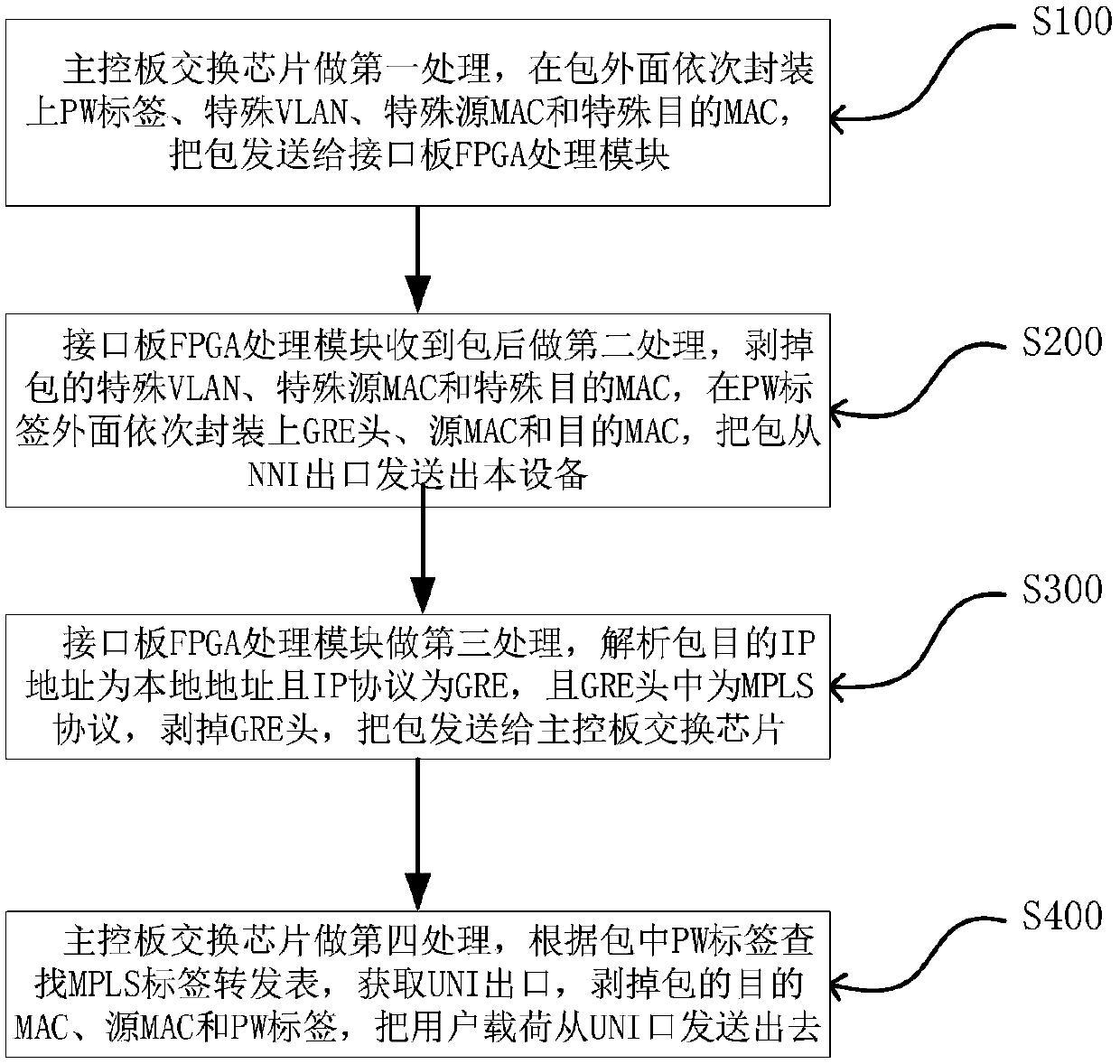

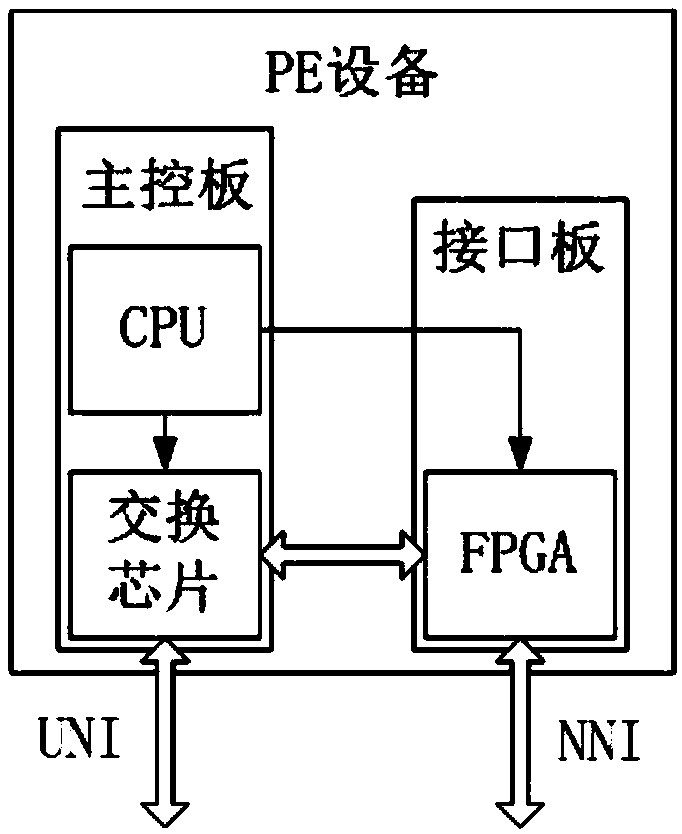

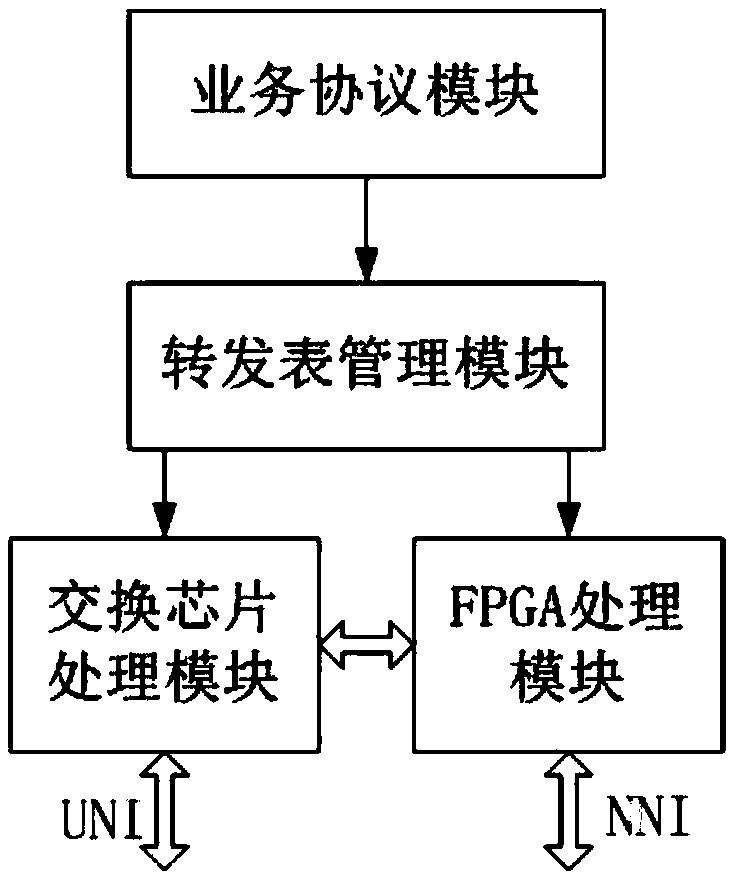

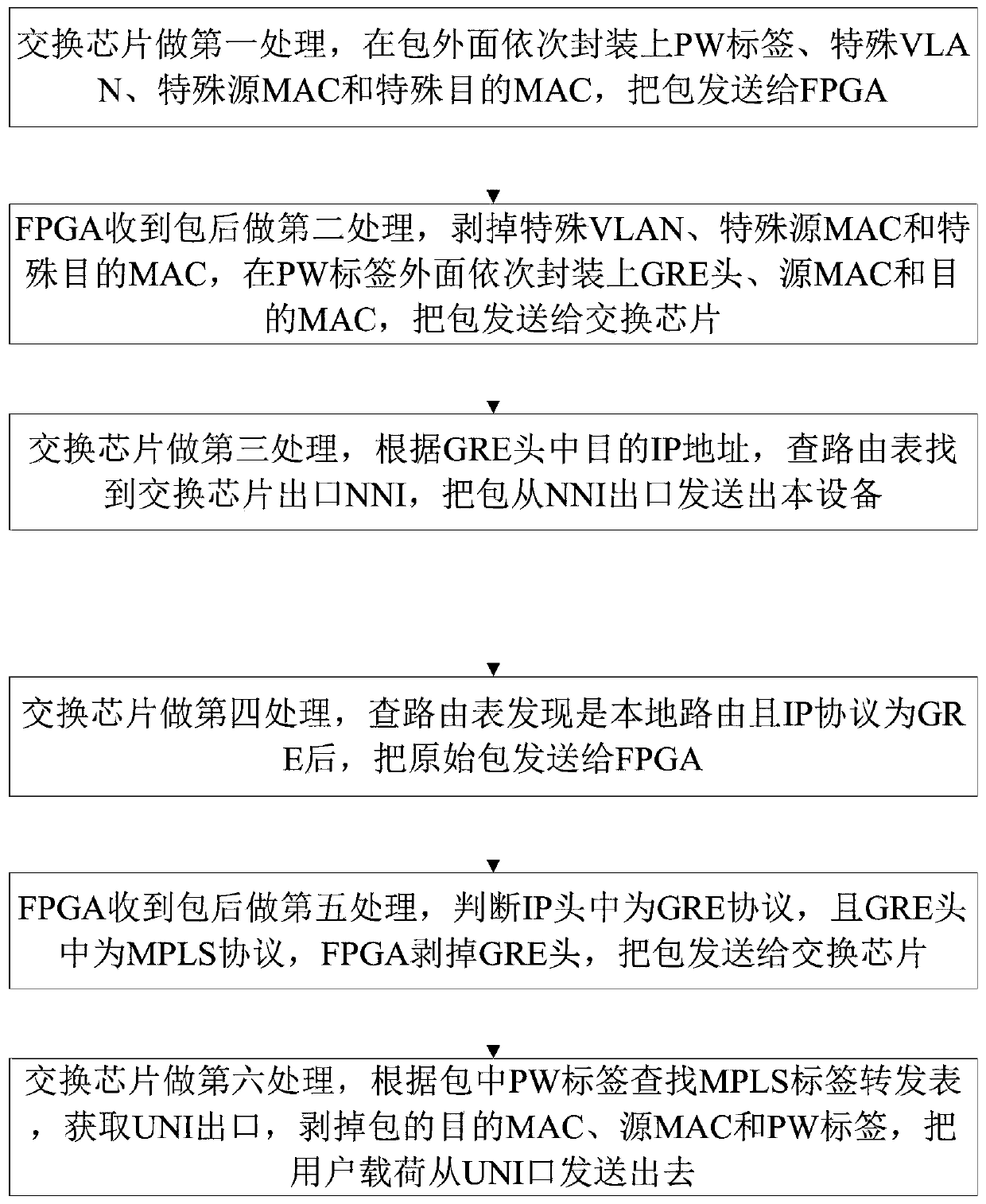

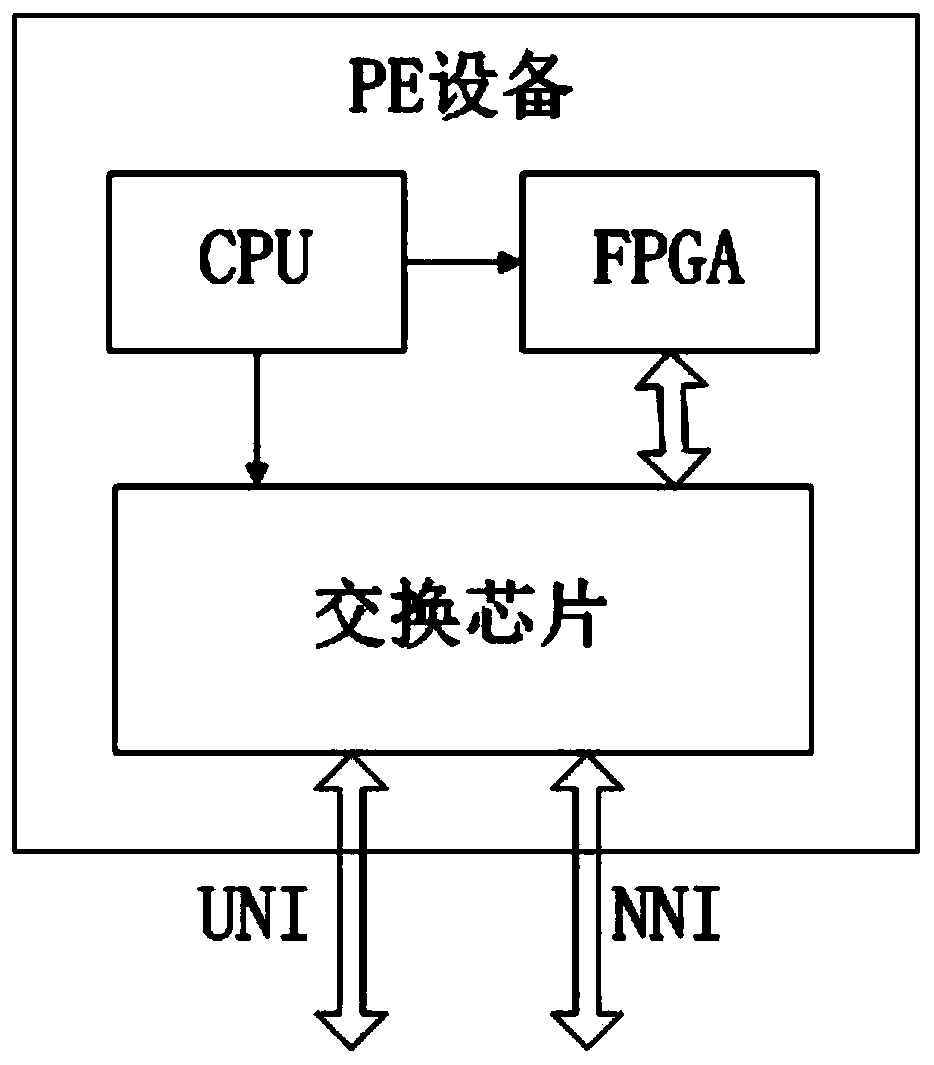

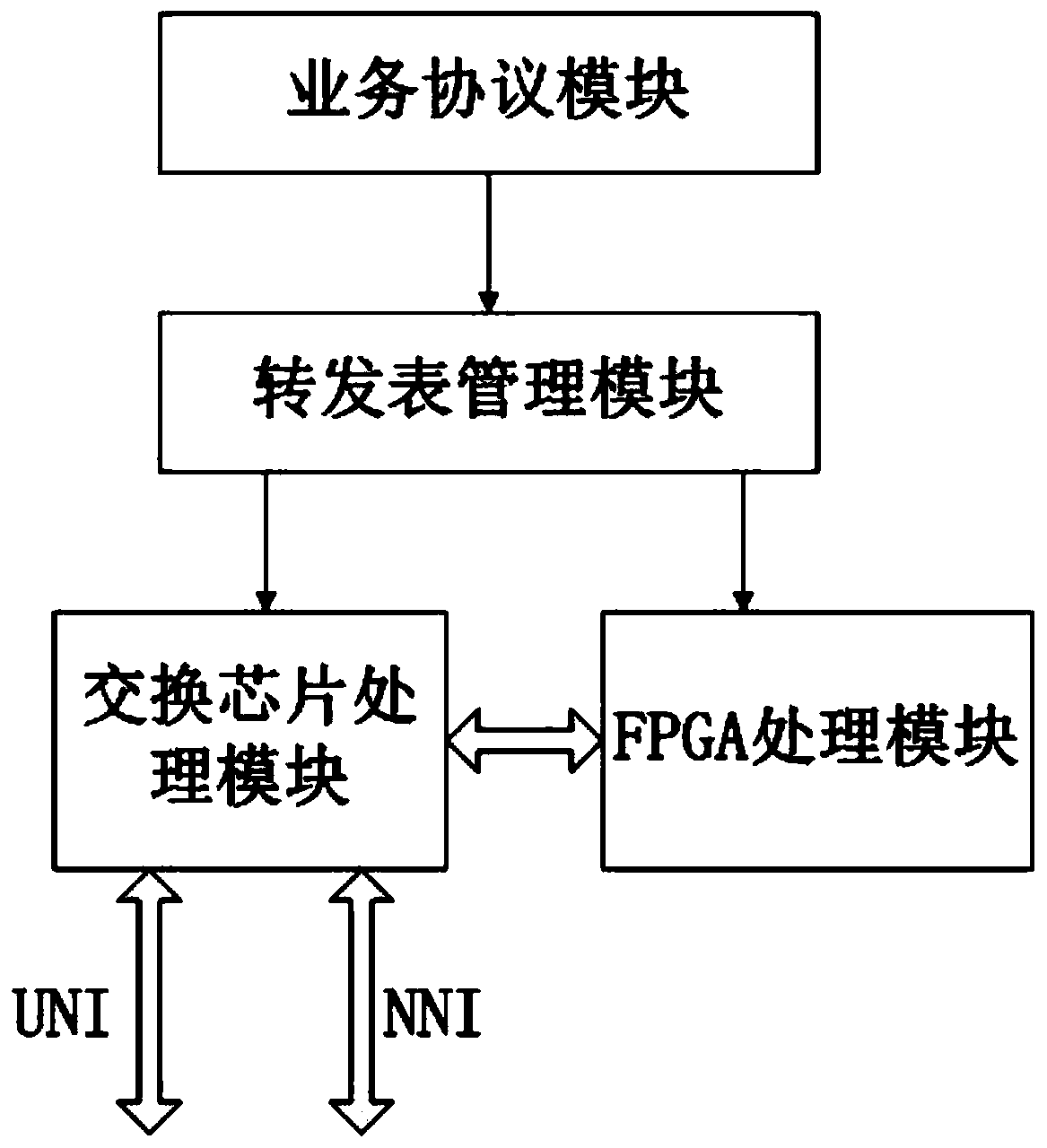

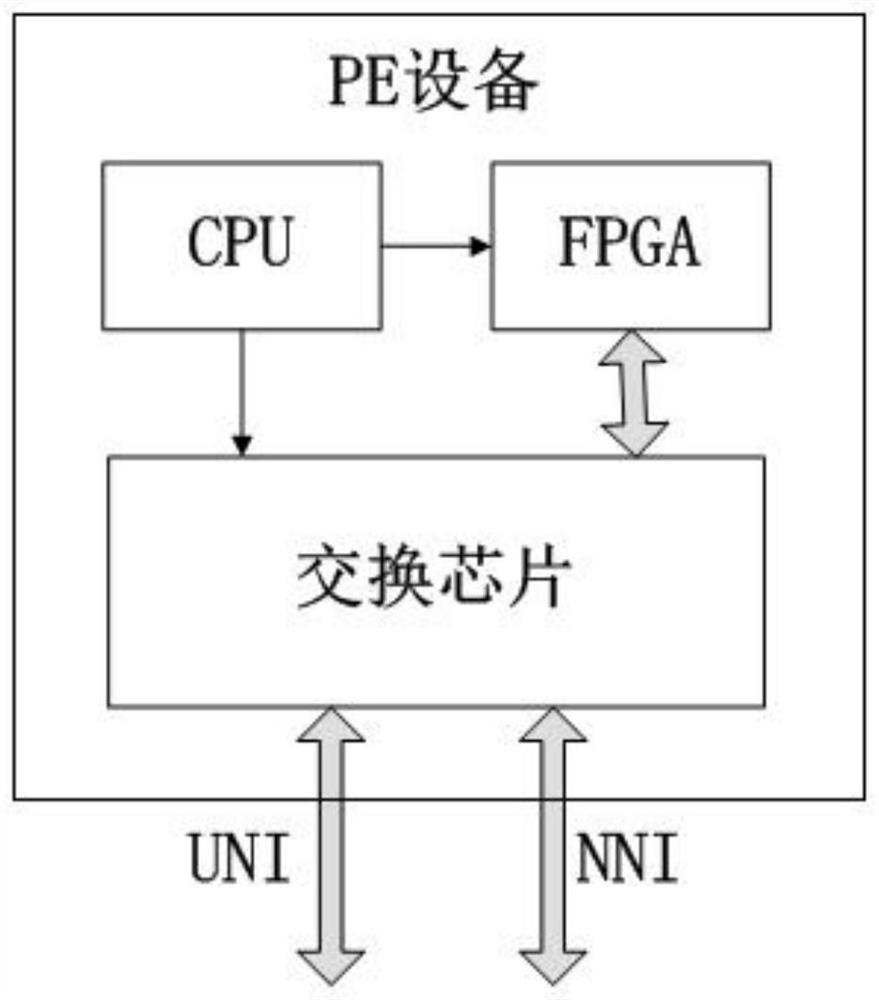

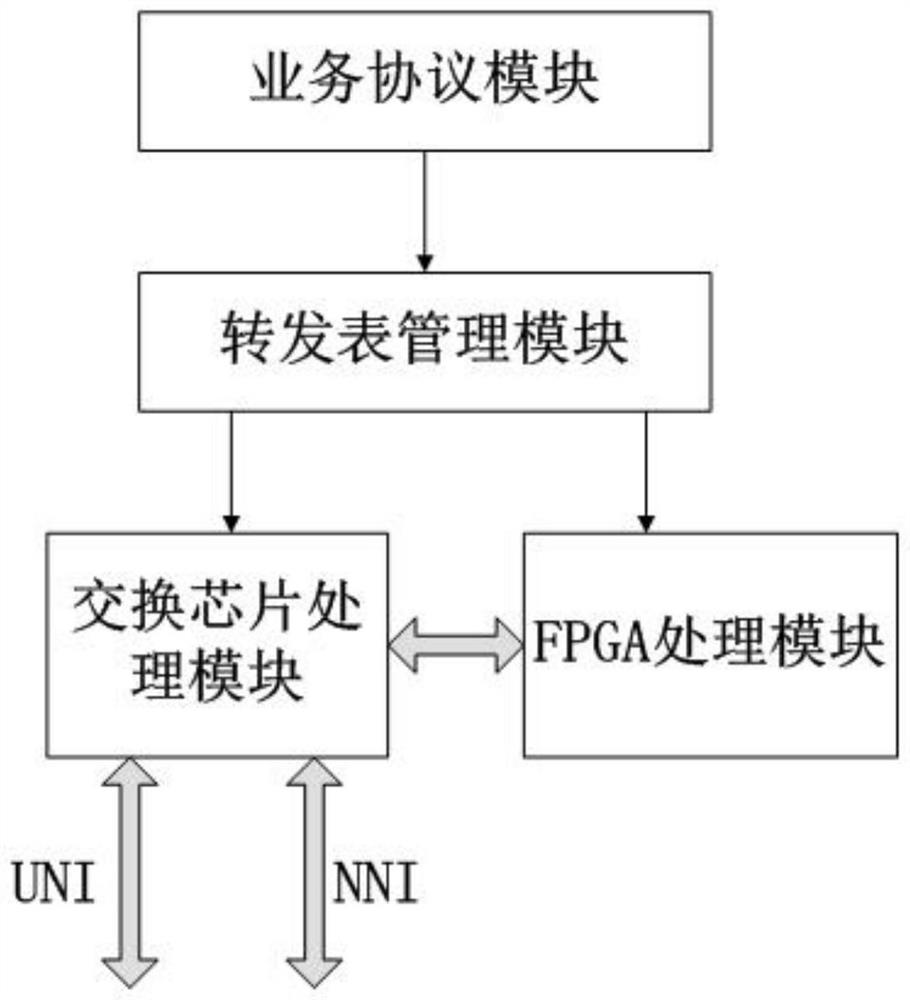

Method and device for VPWS message to traverse three-layer IP network

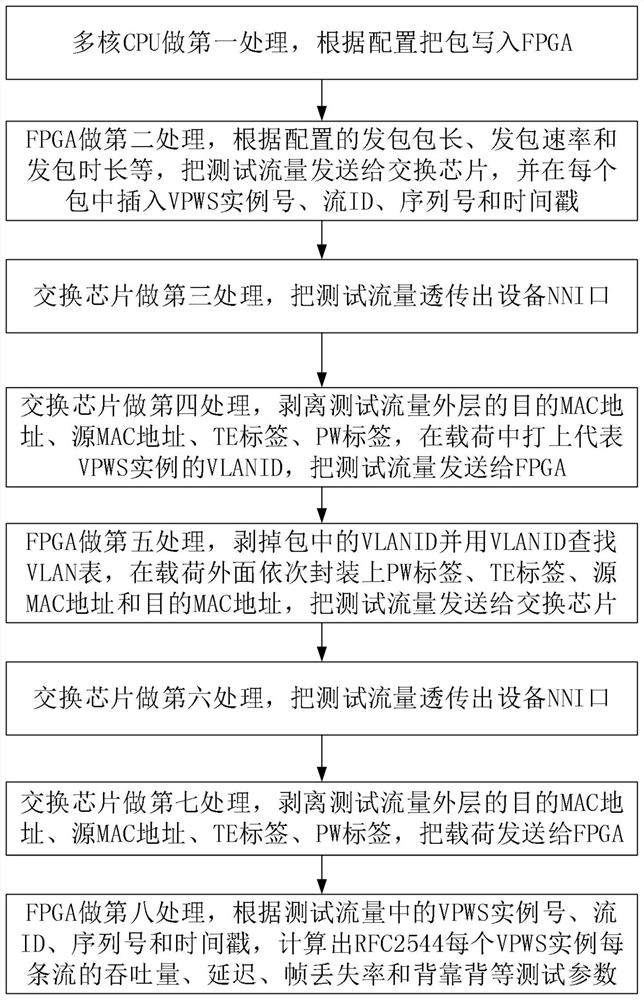

InactiveCN109587060ASolve the technical problem that the forwarding ability is too poor and the port cannot be line-speedGuaranteed forwarding performanceNetworks interconnectionRouting tableWire speed

The invention discloses a method and a device for a VPWS message to traverse a three-layer IP network. A control plane and a forwarding plane are included. A main control board multi-core CPU is takenas the core of the control plane, the multiple control plane protocols of a routing protocol, a LDP protocol, a GRE protocol and an ARP protocol are operated, and various table items including a routing table, an MPLS label table, a GRE session table, and an ARP table, which are required when the forwarding plane processes data, are generated. The forwarding plane is implemented by a main controlboard switching chip and an interface board FPGA. The main control board switch chip and the interface board FPGA are cooperated with each other to process a VPWS data packet. When an UNI interface receives the packet, the main control board switching chip is responsible for receiving the data packet, after corresponding processing, the data packet is sent to the interface board FPGA, and the FPGA packages and processes the data packet and then sends the data packet. When the NNI interface receives the packet, the interface board FPGA is responsible for receiving the data packet to carry outunpacking processing, and then the data packet is sent to the main control board switching chip, and the main control board switching chip processes the data packet and then sends the data packet out.The Wire-speed forwarding of VPWS over GRE can be realized and the forwarding performance of a device port is ensured.

Owner:ANHUI WANTONG POSTS & TELECOMM CO LTD

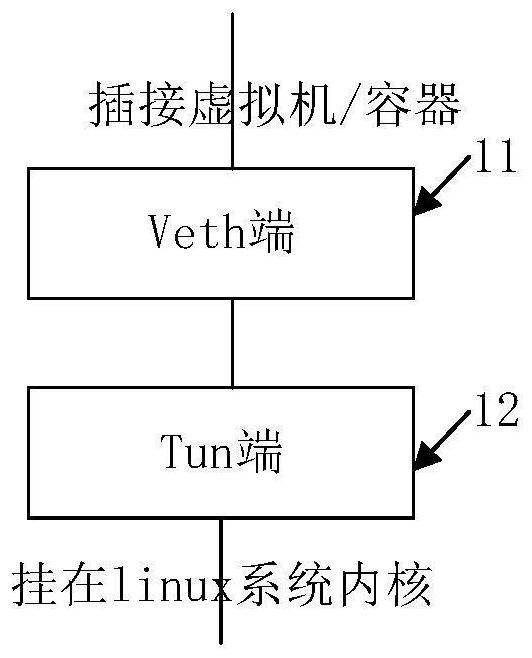

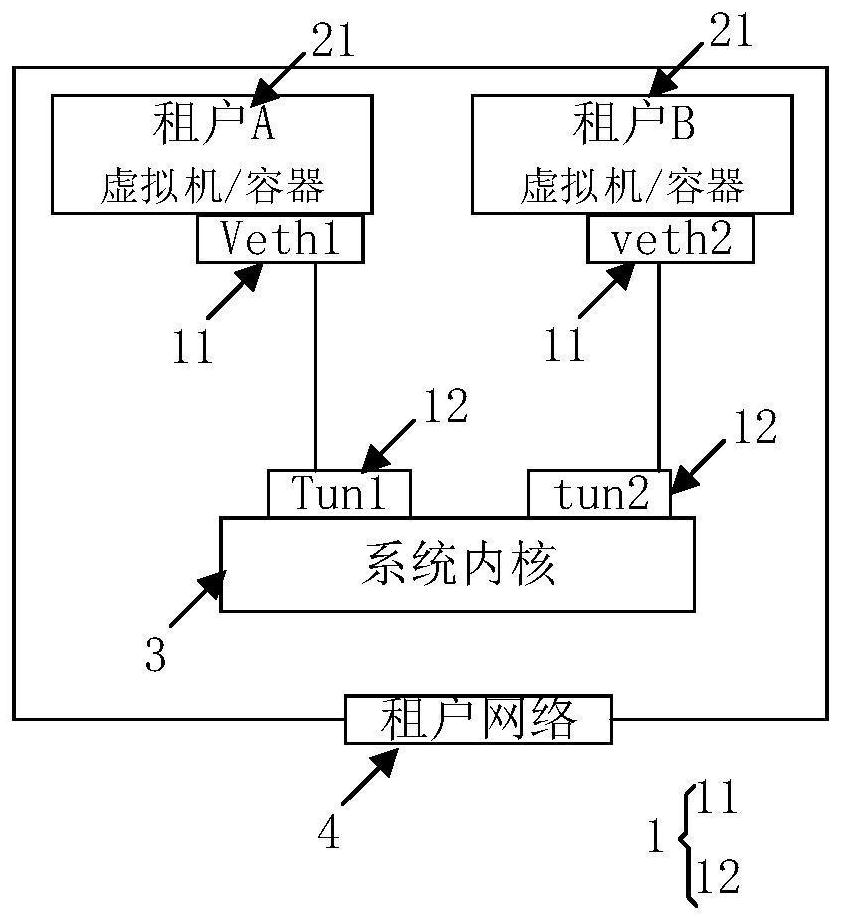

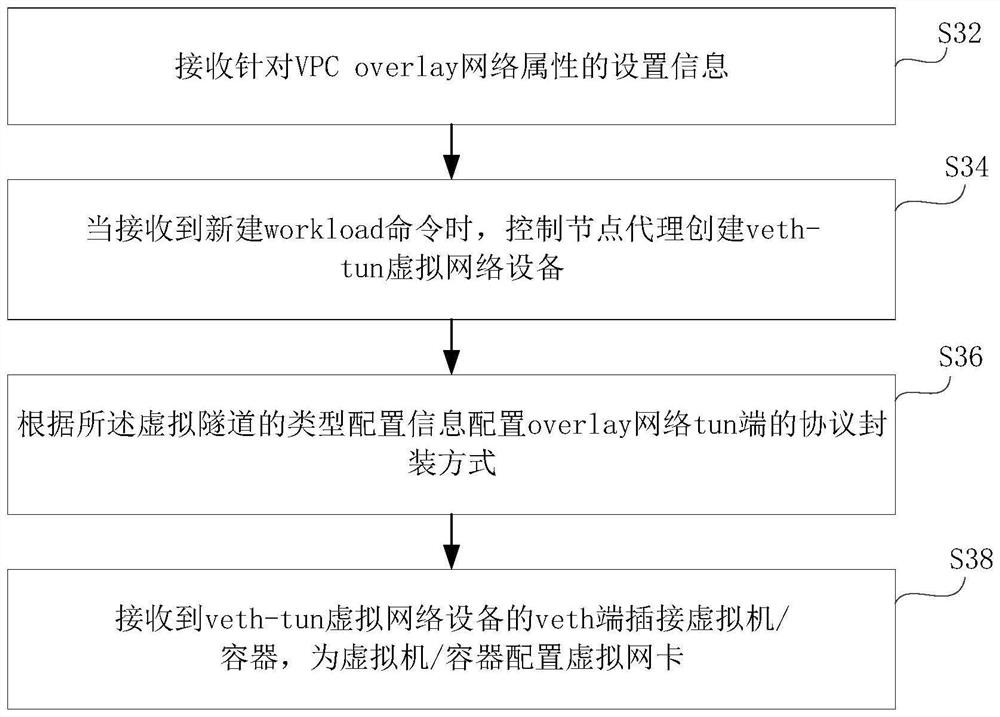

Virtual network equipment, virtual overlay network and configuration and message transmission method

PendingCN114448805AGuaranteed forwarding performanceReduce difficultyTransmissionThird partyNetwork addressing

The invention relates to virtual network equipment, a virtual overlay network and a configuration and message transmission method, and the virtual network equipment comprises a Vth end which is used for plugging a virtual machine / container and providing a virtual network card for the virtual machine / container; and the tun end is arranged in the linux system kernel, serves as a virtual tunnel configuration interface of the linux system kernel, configures the type of the virtual tunnel according to the received virtual tunnel type configuration information, and configures the identifier of the virtual tunnel according to the virtual tunnel identifier configuration information. The virtual overlay network constructed by the virtual network equipment provided by the invention does not depend on a third-party virtual switch OpenvSwitch, so that the forwarding performance of data traffic is effectively ensured. Therefore, when a plurality of tenants exist and the VPC network addresses of the plurality of tenants are overlapped, forwarding can also be performed based on the tun identifier, and the difficulty and workload of network configuration and network maintenance are reduced.

Owner:CHINA TELECOM CLOUD TECH CO LTD

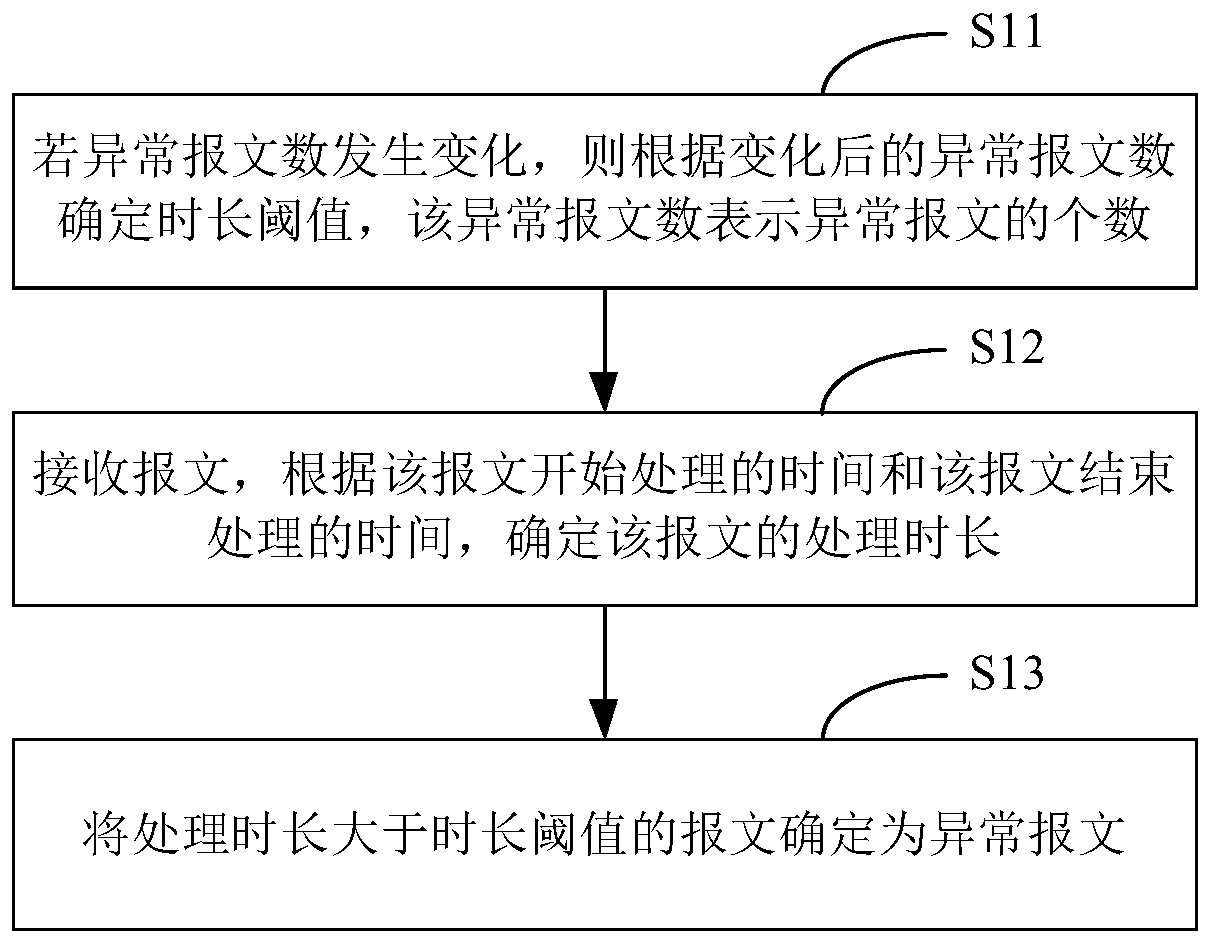

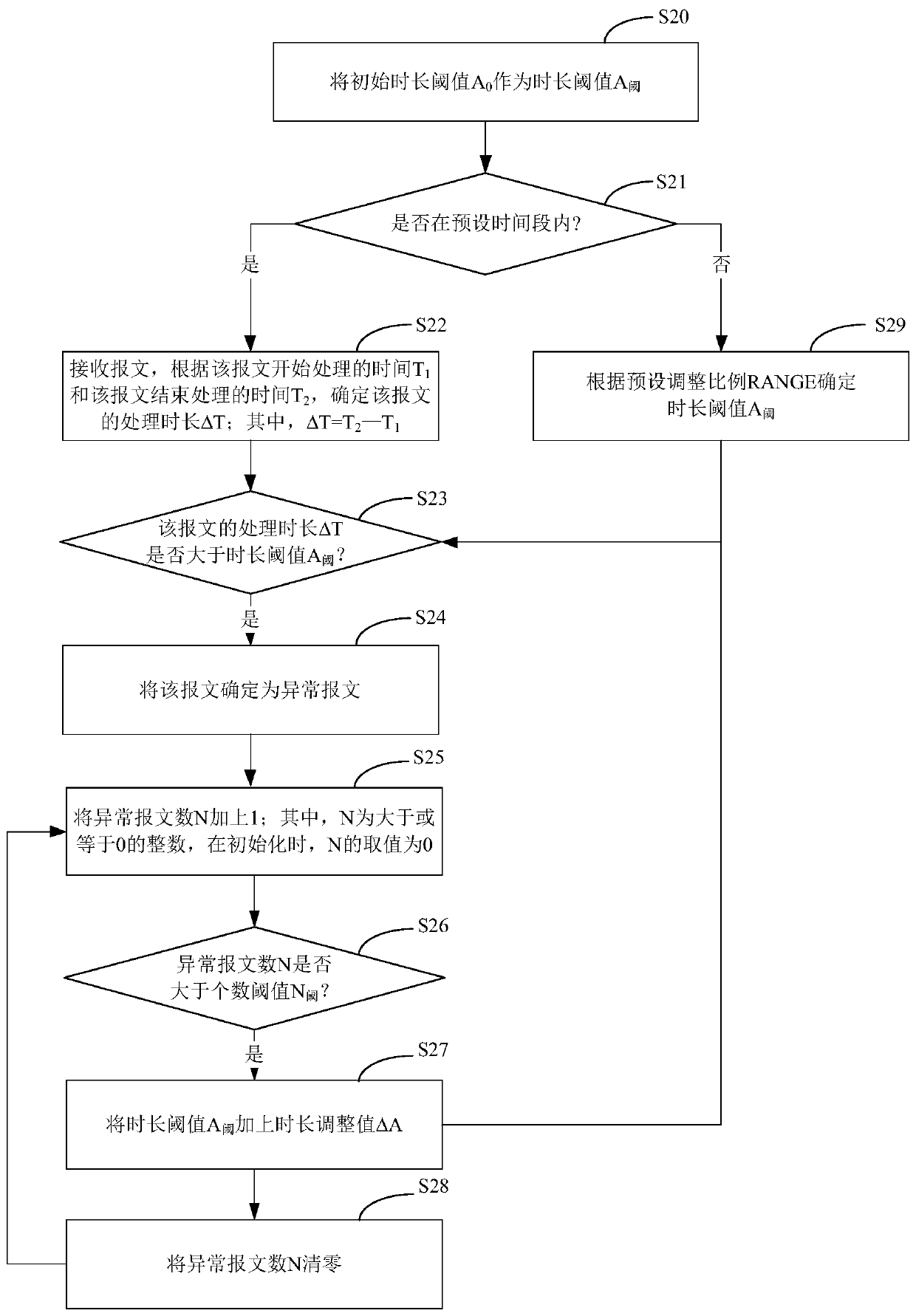

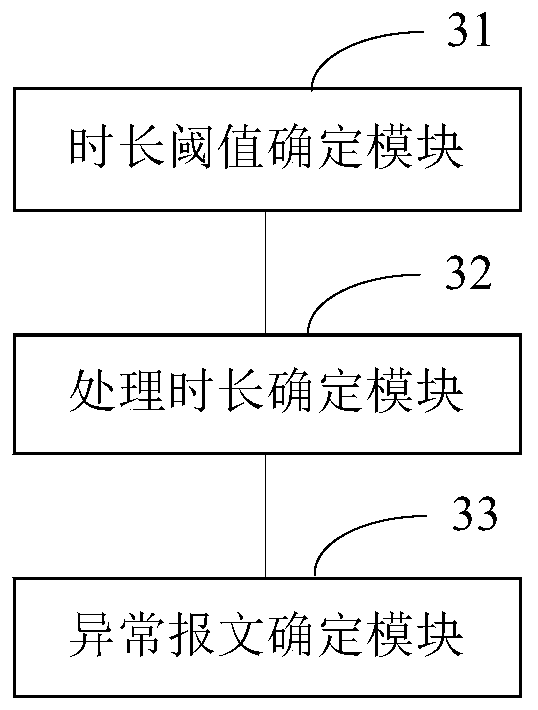

Abnormal message determination method, device and computer-readable storage medium

ActiveCN108650152BGuaranteed forwarding performanceImprove maintainabilityData switching networksDistributed computingIndustrial engineering

The invention relates to an abnormal message determination method and device. The abnormal message determination method is applied to network equipment, and comprises the following steps: if the abnormal message number is changed, determining a duration threshold according to the changed abnormal message number, wherein the abnormal message number is the number of the abnormal messages; receivingmessages, and determining processing durations of the messages according to the time when starting to process the messages and the time when the processing of the messages is finished; and determininga message whose processing duration is greater than the duration threshold as an abnormal message. According to the abnormal message determination method and the device provided by the invention, theduration threshold used for determining the abnormal messages in network equipment can be dynamically adjusted according to the abnormal message number, so that the abnormal messages that exist in anetwork and cause problems to the network equipment can not only be determined, but also the forwarding performance of the network equipment can be guaranteed, thereby improving the maintainability ofthe network equipment.

Owner:NEW H3C TECH CO LTD

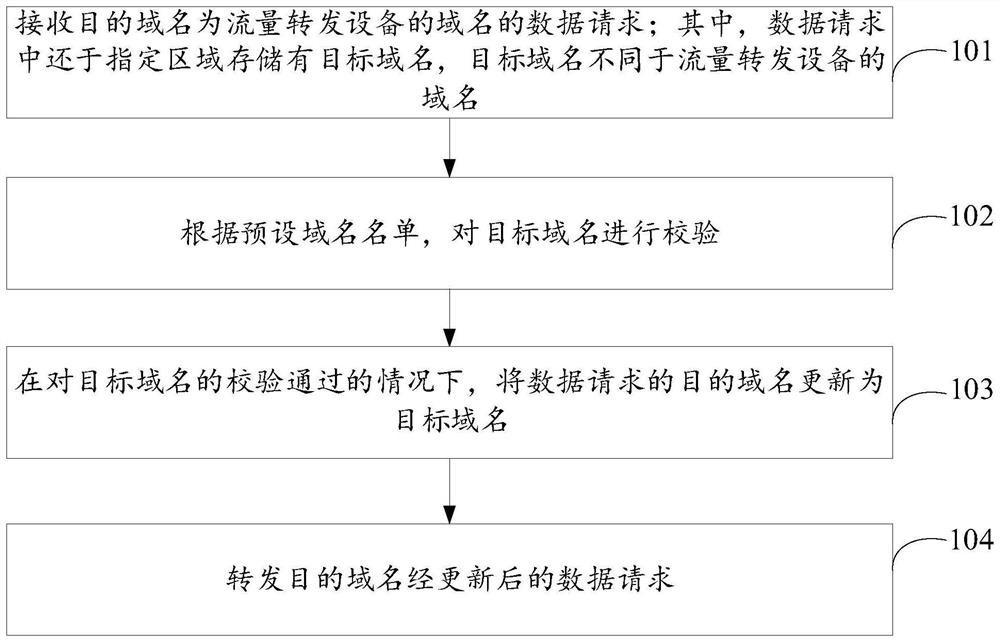

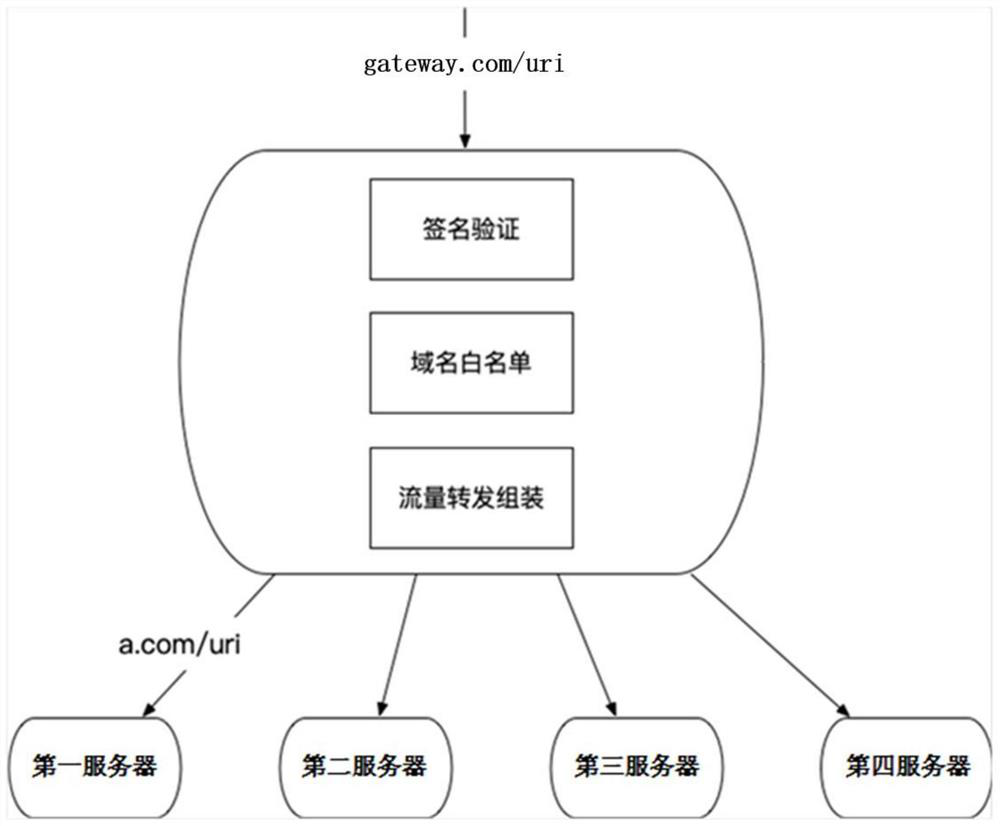

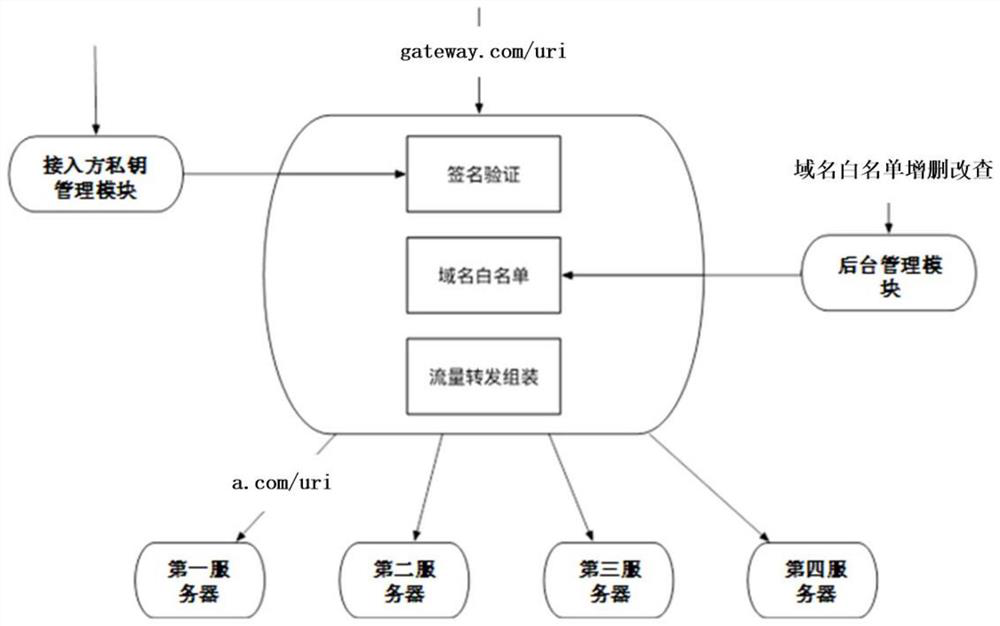

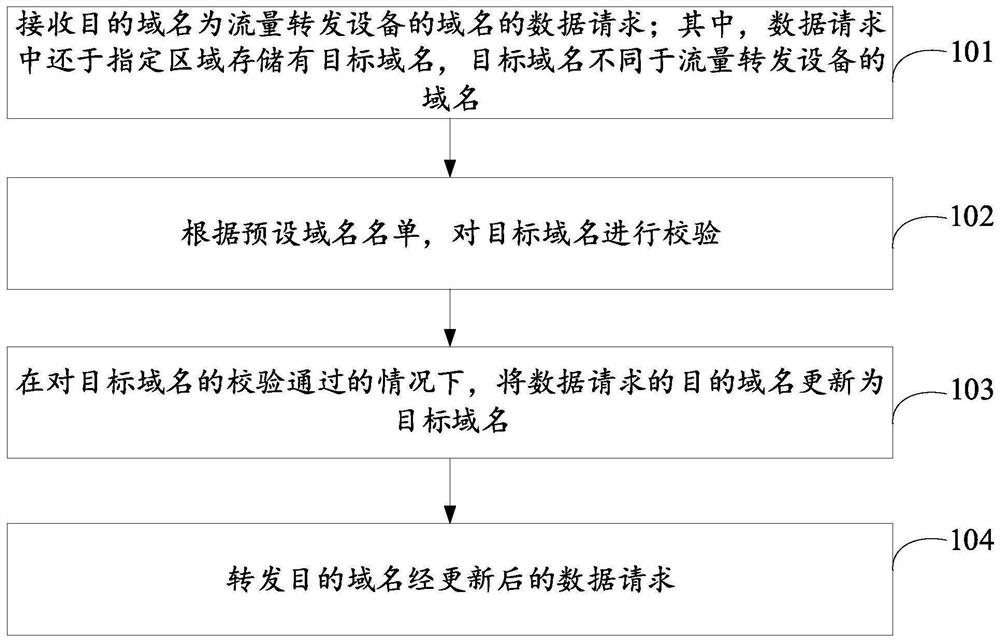

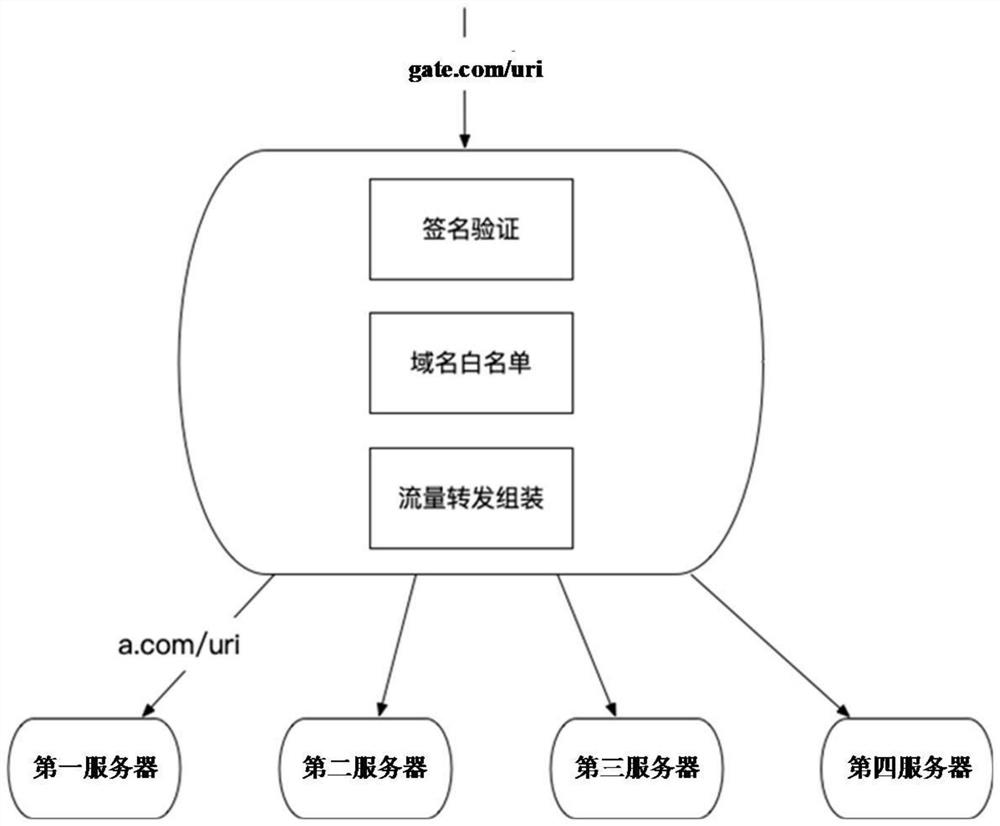

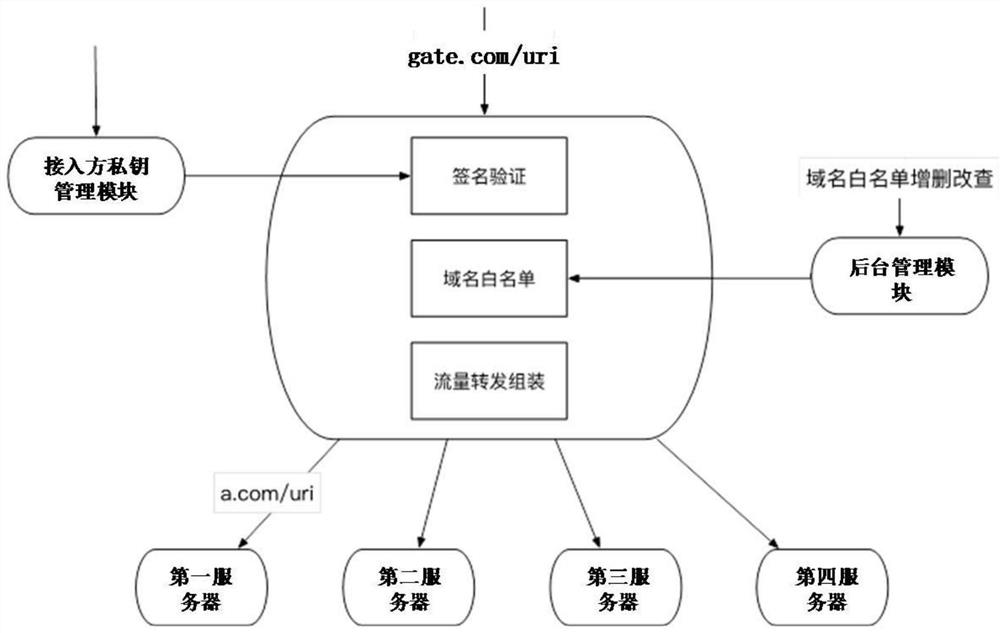

Data request processing method and device, storage medium and electronic device

ActiveCN112422429BGuaranteed forwarding performanceAvoid Path ConflictsSecuring communicationDomain namePathPing

The embodiment of the present disclosure discloses a data request processing method, device and computer-readable storage medium. The method is applied to a traffic forwarding device, and the method includes: receiving a data request whose destination domain name is the domain name of the traffic forwarding device; wherein, the data request also stores a target domain name in a designated area, and the target domain name is different from the domain name of the traffic forwarding device; according to Preset the list of domain names to verify the target domain name; if the verification of the target domain name is passed, update the target domain name of the data request to the target domain name; forward the updated data request of the target domain name. The embodiment of the present disclosure does not need to apply for a dedicated path for each server in the backend service system, which is very convenient to implement, can avoid path conflicts, and is also conducive to ensuring traffic forwarding performance.

Owner:BEIKE TECH CO LTD

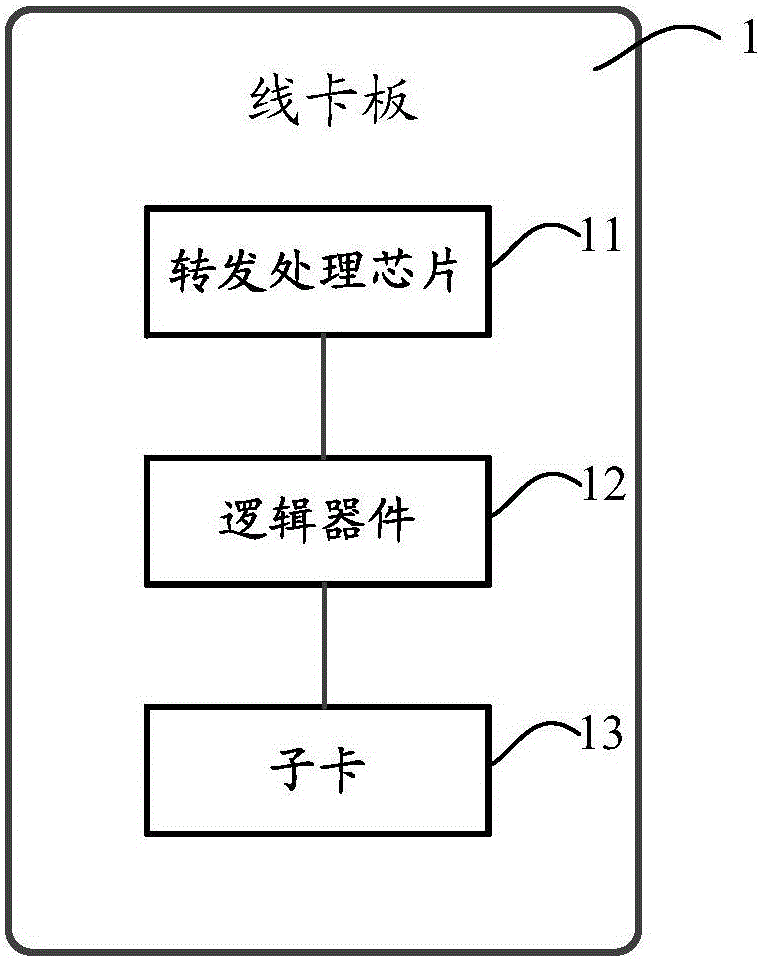

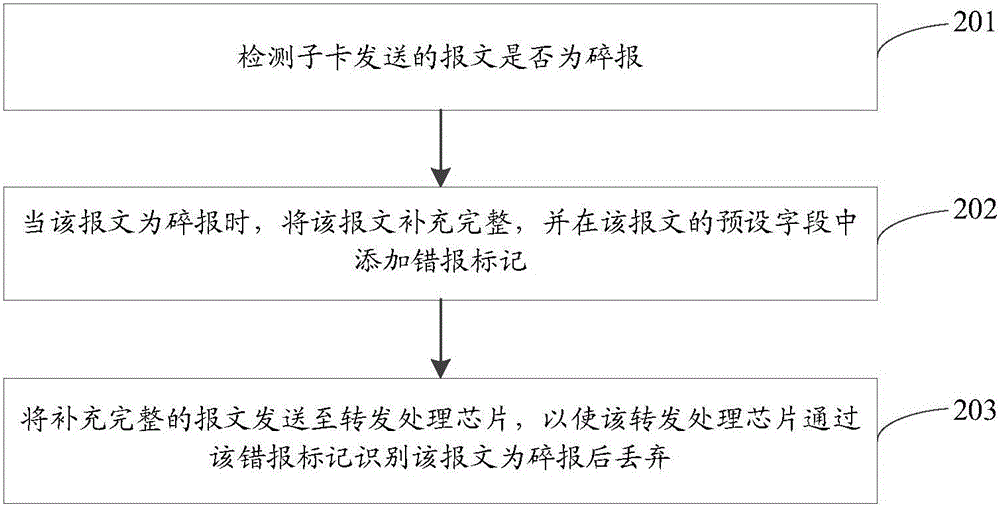

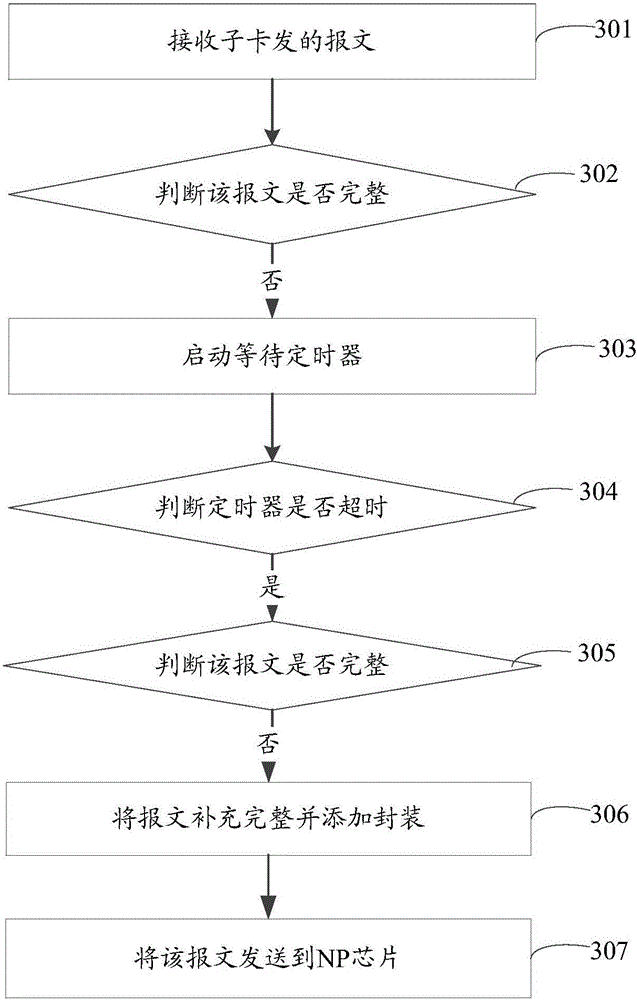

Method and device for processing broken message

InactiveCN105591986AAvoid shockGuaranteed forwarding performanceData switching networksComputer hardwareError reporting

The invention provides a method and a device for processing broken messages. The method is applied to a logic device, which is used for transmitting messages between a daughter card and a forwarding processing chip. The method comprises the steps of: detecting whether a message sent by the daughter card is a broken message; completing the message if the message is a broken one, and adding an error-reporting flag in a preset field of the message; and sending the completed message to the forwarding processing chip, so that the forwarding processing chip discards the message after recognizing that the message is broken one by means of the error-reporting flag. Therefore, impact of broken messages on the forwarding processing chip can be avoided, and forwarding performance of the forwarding processing chip can be ensured.

Owner:NEW H3C TECH CO LTD

A traffic forwarding method and system based on a virtual switching cluster

ActiveCN102769568BRealize forwardingGuaranteed forwarding performanceNetwork topologiesData switching networksTraffic capacityVirtual switch

Owner:ZTE CORP

Data packet loss processing method, system, readable storage medium and electronic device

ActiveCN107872363BGuaranteed forwarding performanceImprove stabilityData switching networksData packPacket loss

The invention relates to a method and a system for processing data packet loss, a readable storage medium and electronic equipment. The method includes acquiring current running locations of data forwarding processes when data packet forwarding fails in the data forwarding processes under the condition that data packet loss statistics modes are started; updating storage contents in statistical information storage regions according to the current running locations; releasing data packets which fail to be forwarded. The statistical information storage regions are used for storing running locations of the data forwarding processes whenever data packet forwarding fails and the frequencies of data packet forwarding failure at the running locations. According to the technical scheme, the method,the system, the readable storage medium and the electronic equipment have the advantages that workload on technicians can be effectively relieved, and data packet loss statistics can be carried out on the data packets which fail to be forwarded without modification on other codes after business logics are modified; the forwarding performance of data forwarding processes can be guaranteed, and thestability of the data forwarding processes can be improved.

Owner:NEUSOFT CORP

Label exchange route setting method, system and equipment of virtual special network channel

ActiveCN101090355BImprove build speedGuaranteed forwarding performanceNetworks interconnectionIp addressMPLS VPN

This invention discloses a method for setting up label switch path of MIPLS VPN tunnel including: a label switch router LSR in a network determines the forward equivalence FEC corresponding to the destination IP address of the MPLS VPN tunnel to distribute label to it firstly and set up a binding relation between the FEC and the distributed label and notifies the binding relation with the prior label to its upper reach LSR, which receives the binding relation notified by the lower reach LSR to process the binding relation with the prior label priorly. This invention also discloses a LSP set-up system and a device of the MPLS VPN tunnel.

Owner:XINHUASAN INFORMATION TECH CO LTD

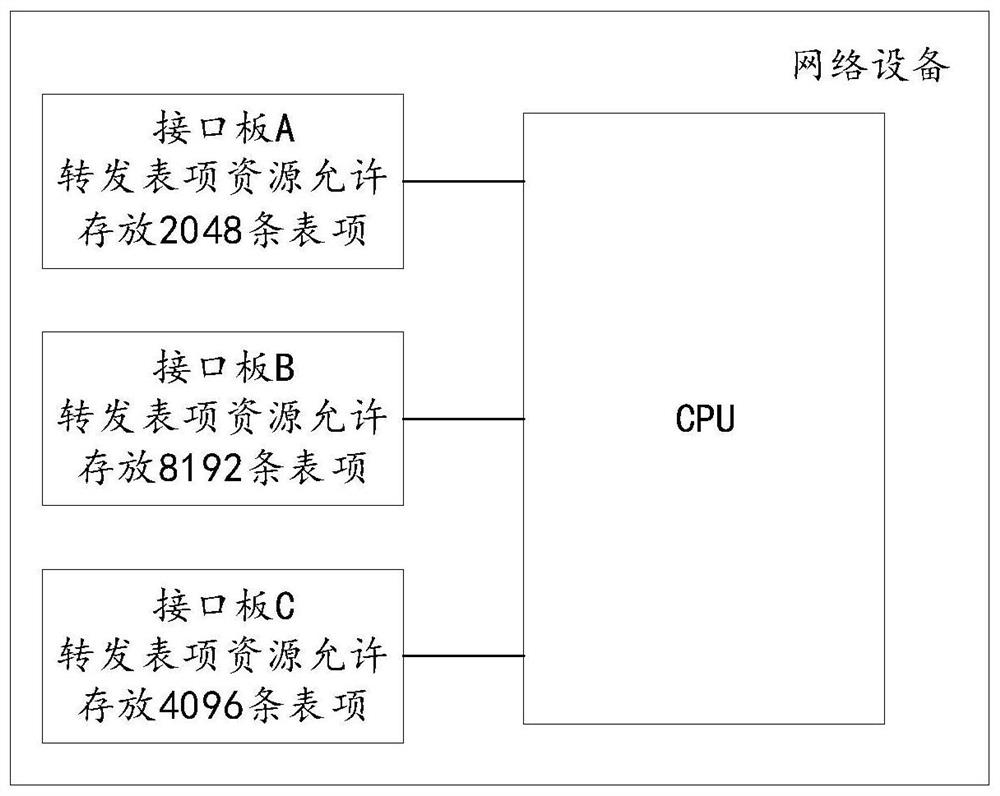

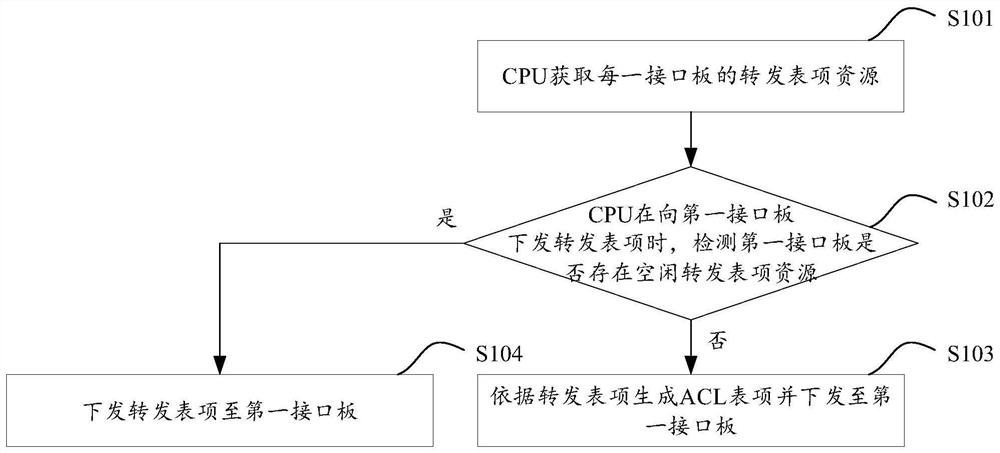

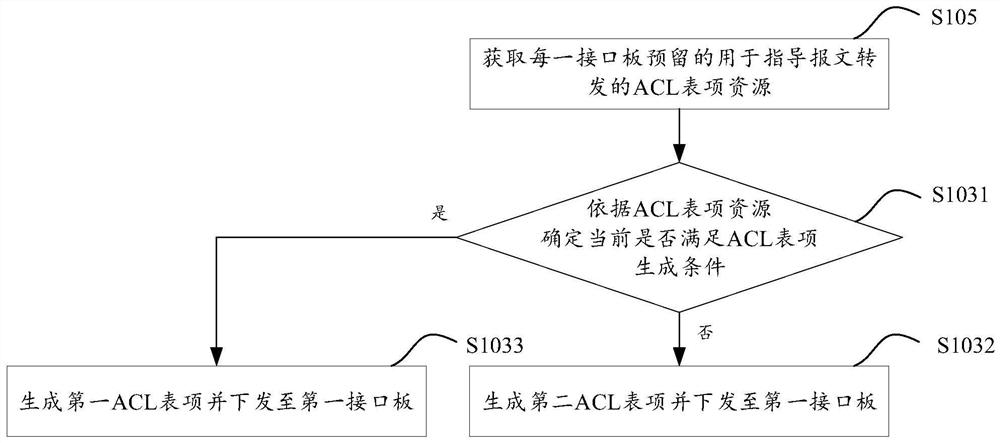

Message forwarding method and network device

The present application provides a message forwarding method and network equipment. The message forwarding method is applied to a network device, and the network device includes a CPU and at least two interface boards. The method includes: the CPU obtains the forwarding entry resource of each interface board; When posting an item, if it is detected that the first interface board no longer has idle forwarding table item resources, an ACL entry is generated based on the forwarding table item and sent to the first interface board, and the ACL entry is used to indicate the destination IP The packet whose address matches the IP address in the forwarding entry is forwarded to the second interface board, and the second interface board has idle forwarding entry resources. This application can achieve the effect that in the case of different sizes of forwarding table item resources of multiple interface boards, even if the interface board with smaller forwarding table item resources no longer has idle forwarding table item resources, the effect of normal forwarding of messages can still be guaranteed.

Owner:HANGZHOU DPTECH TECH

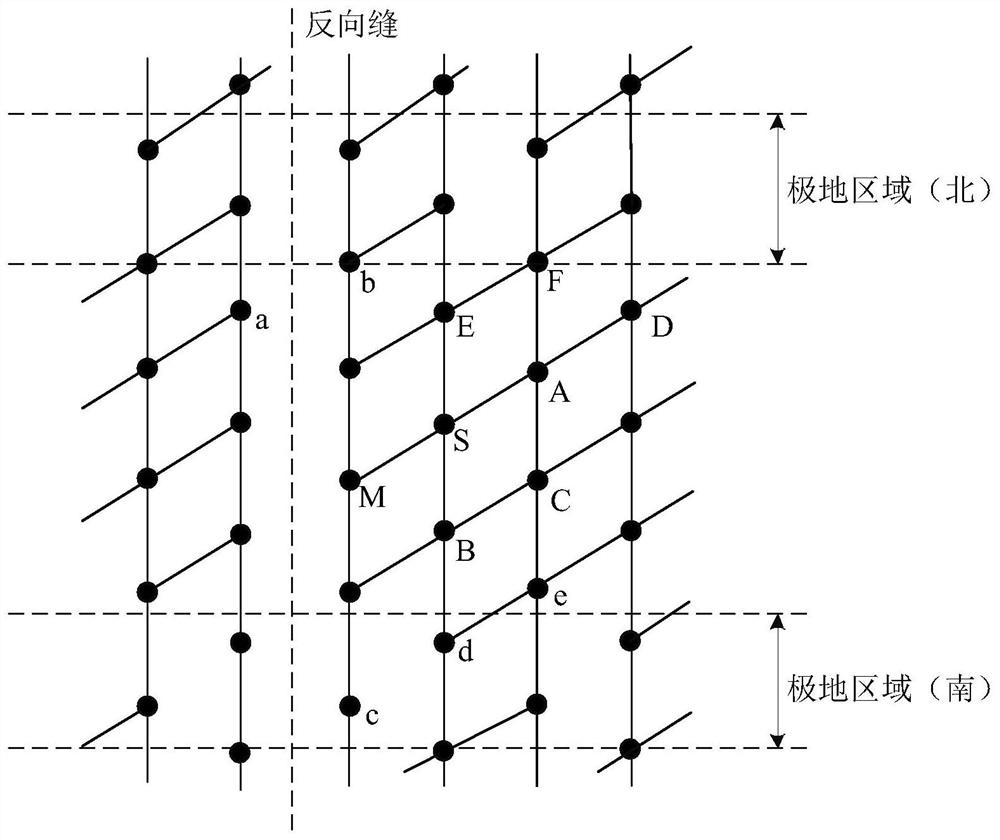

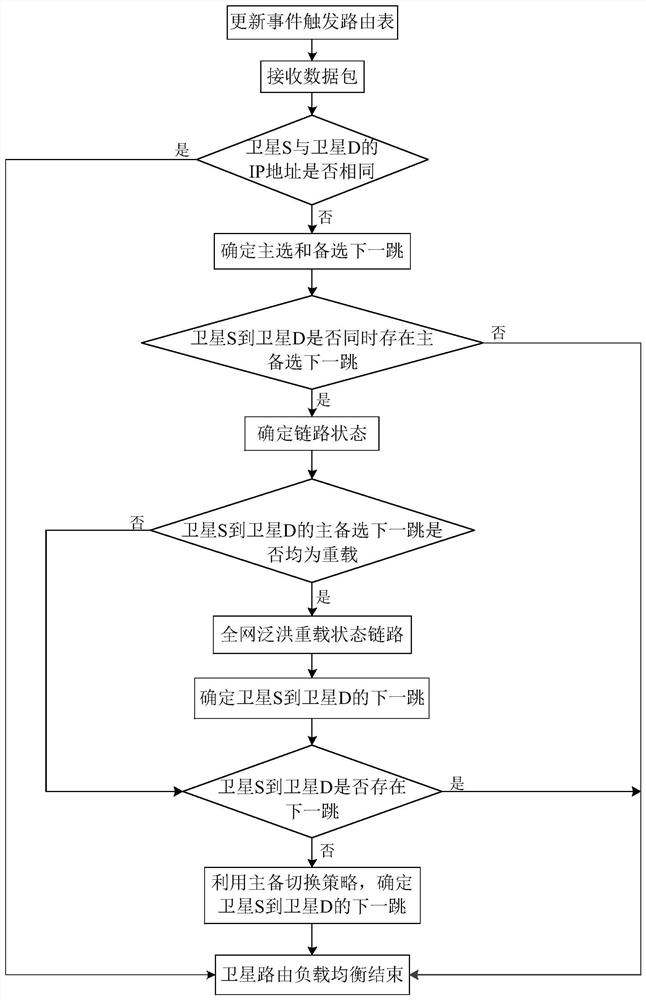

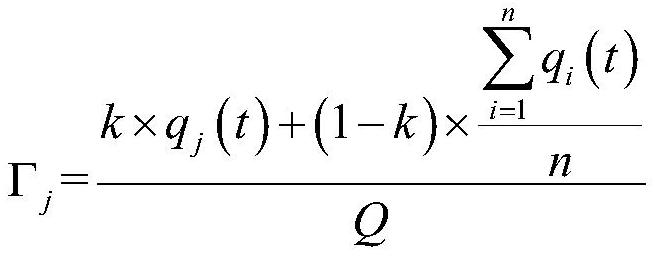

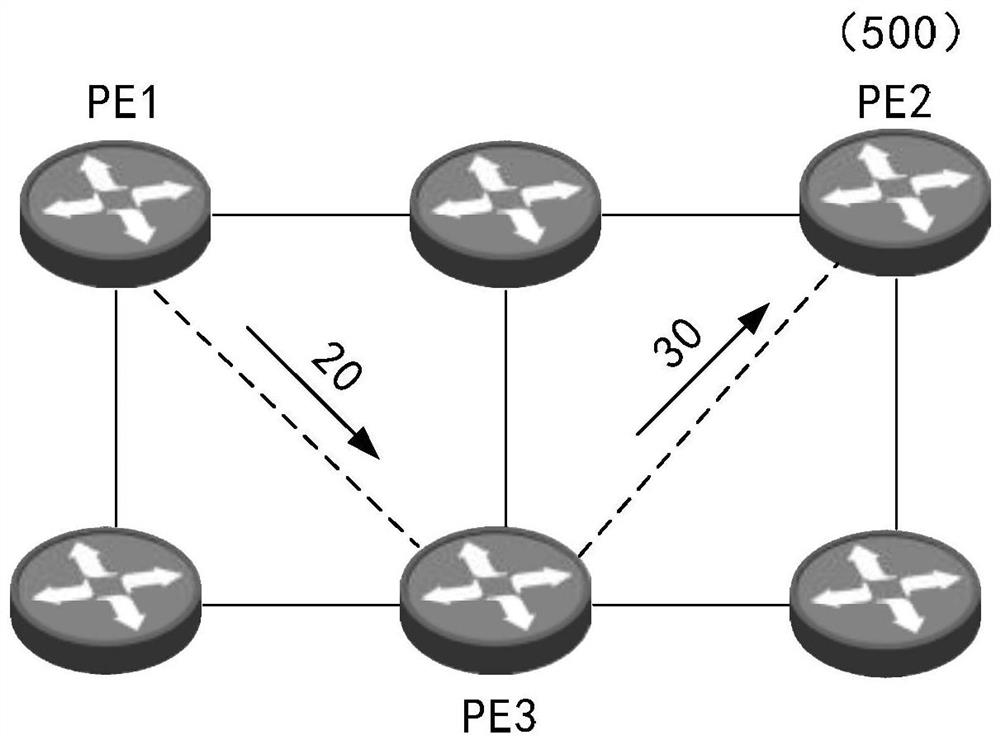

Event-triggered satellite routing load balancing method

ActiveCN109714270BOvercome storage pressure problemsReduce overheadRadio transmissionData switching networksEngineeringDistributed computing

The invention discloses an event-triggered satellite routing load balancing method. The specific implementation steps are as follows: when the satellite routes the received data packets, firstly perceive the change of the on-off state of the inter-satellite link in the whole network pre-saved by the satellite , to trigger the update of the routing table, and generate the routing table with the shortest and second shortest paths; When the heavy load is not available, the overload link information is flooded to the whole network, triggering other satellites in the whole network to update the route; finally, the next hop is determined for the data packets received by the satellite through the detour next hop strategy. The invention effectively saves the storage space, and can balance the network load according to the change of the link state, and deal with the overloaded link in time.

Owner:XIDIAN UNIV

A private network application identification system, method, SDN controller, and p-device

ActiveCN110868352BUnlimited number of applicationsImprove scalabilityTransmissionPrivate networkEngineering

The embodiment of the invention discloses a private network application identification system, method, SDN controller, and P equipment, relates to the field of data communication, and realizes visualization of private network application traffic in a service provider network. The system includes at least a P device and an SDN controller, wherein the SDN controller is configured to receive from the P device the egress PE device address corresponding to the MPLS message and the egress PE device allocation in the MPLS message compare the received address of the egress PE device and the VPN label assigned by the egress PE device with the pre-acquired PE device address, the corresponding relationship between the VPN label assigned by the PE device and the VPN, and determine The VPN corresponding to the MPLS message, and determine the private network application corresponding to the MPLS message in combination with the message feature information.

Owner:MAIPU COMM TECH CO LTD

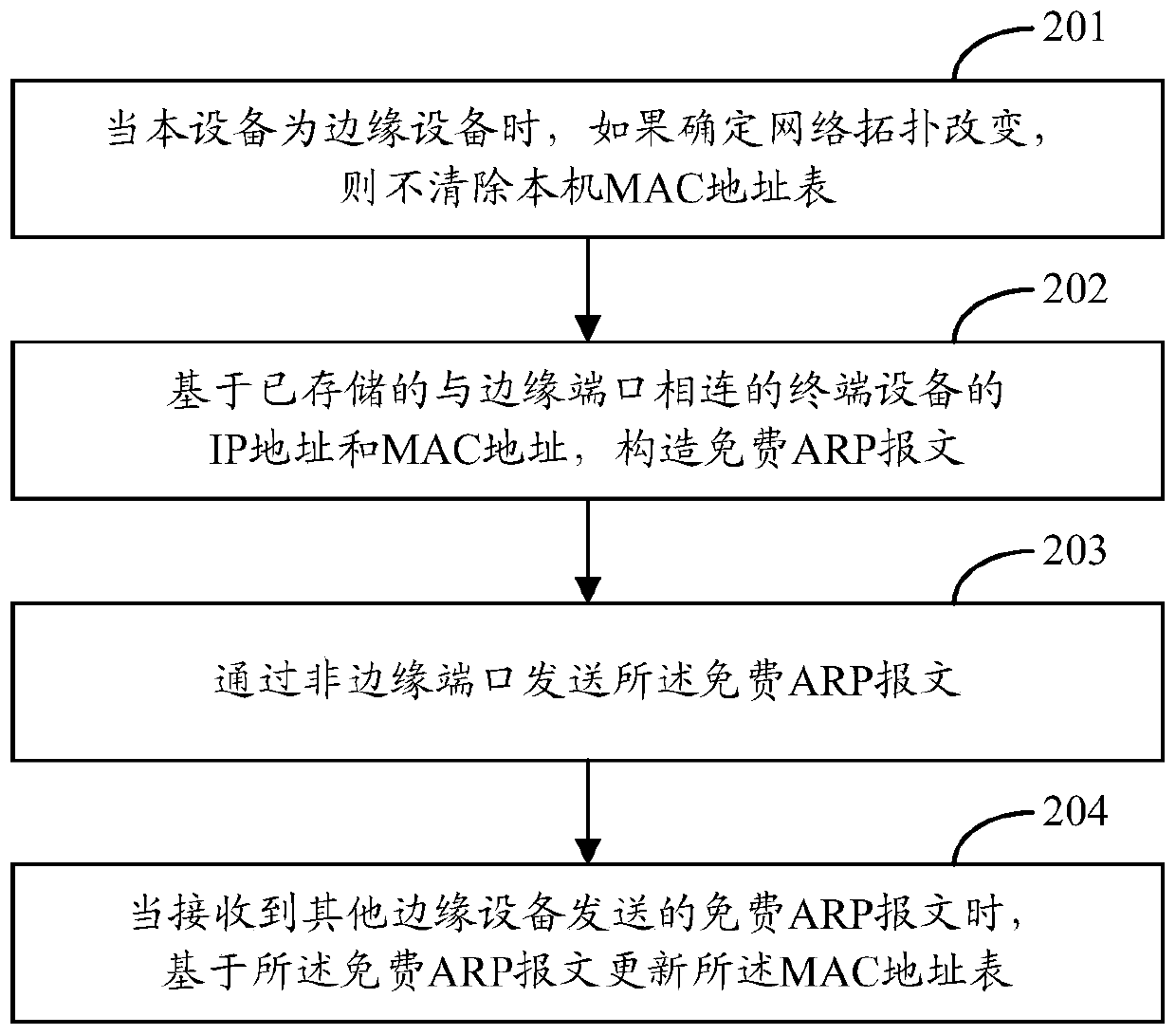

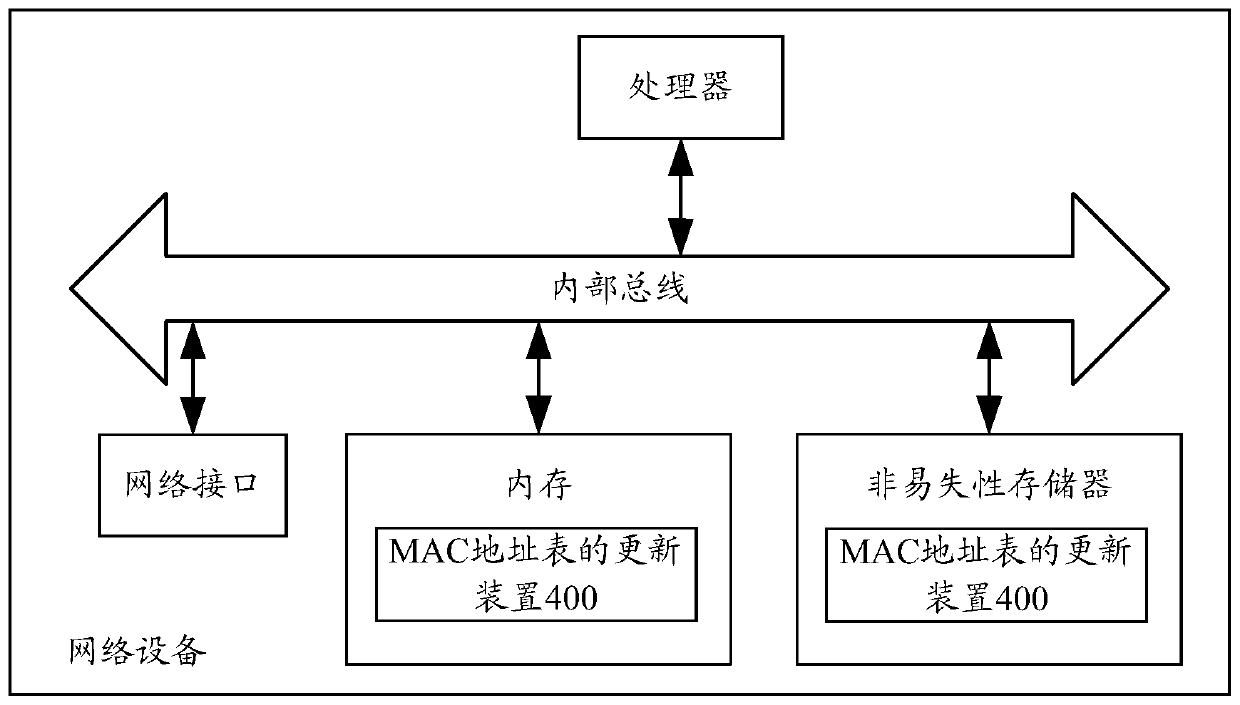

Method and device for updating mac address table

ActiveCN106506378BGuaranteed forwarding performanceImprove forwarding performanceData switching networksIp addressTerminal equipment

This application provides a method and device for updating a MAC address table, which are applied to network devices, including: when the device is an edge device, if it is determined that the network topology changes, the local MAC address table is not cleared; The IP address and the MAC address of the terminal device connected to the port construct a gratuitous ARP message; send the gratuitous ARP message through the non-edge port; when receiving the gratuitous ARP message sent by other edge devices, based on the gratuitous ARP message The document updates the MAC address table. The technical scheme of the present application can avoid long-term forwarding interruption among hosts in the network, and optimize the forwarding performance of network equipment.

Owner:HANGZHOU DPTECH TECH

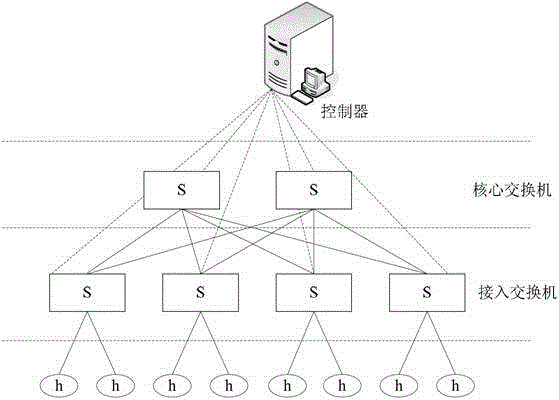

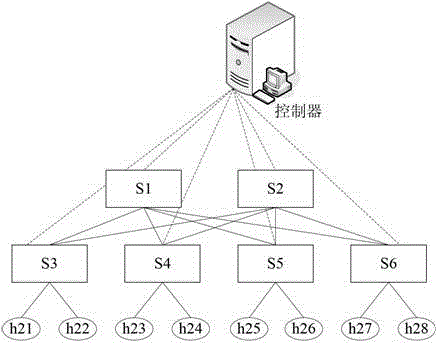

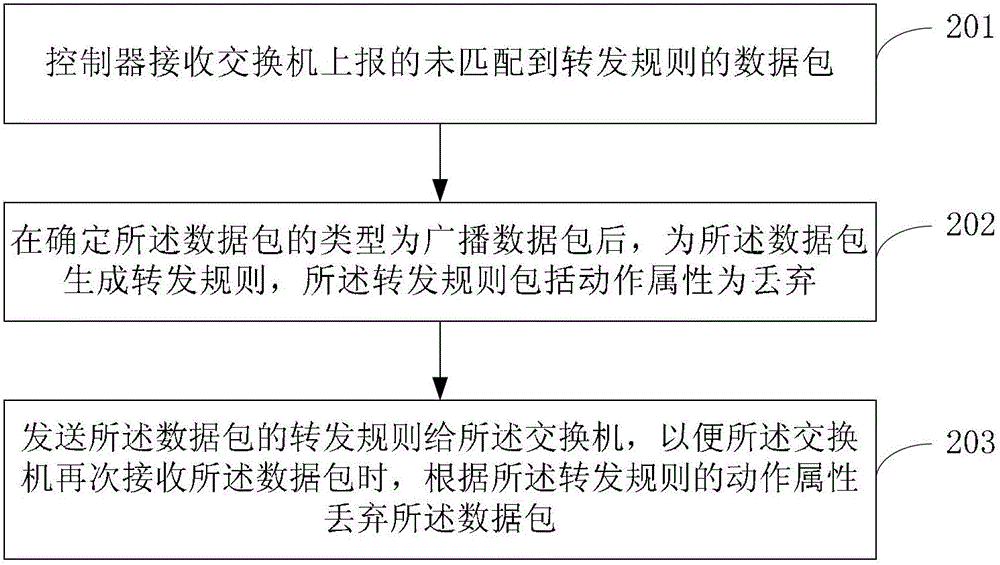

Data packet processing method, controller and system

ActiveCN103685009BAvoid rebroadcastingGuaranteed forwarding performanceData switching networksBroadcast packetBroadcast radiation

Owner:HUAWEI TECH CO LTD

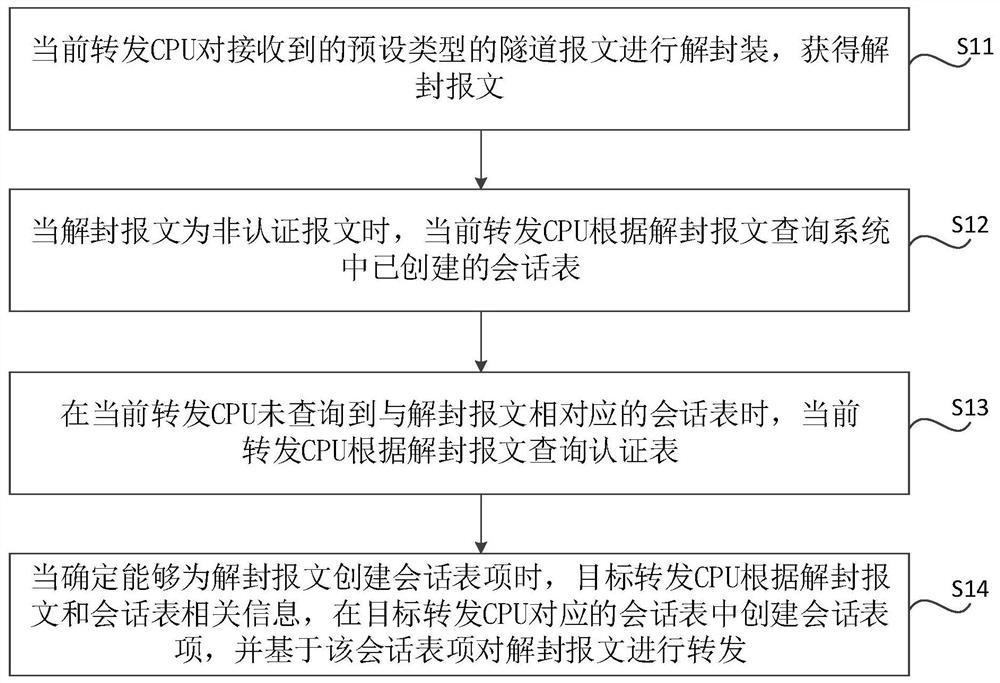

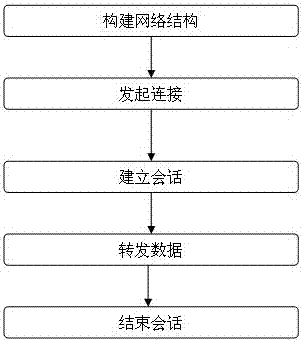

Tunnel message authentication and forwarding method and system

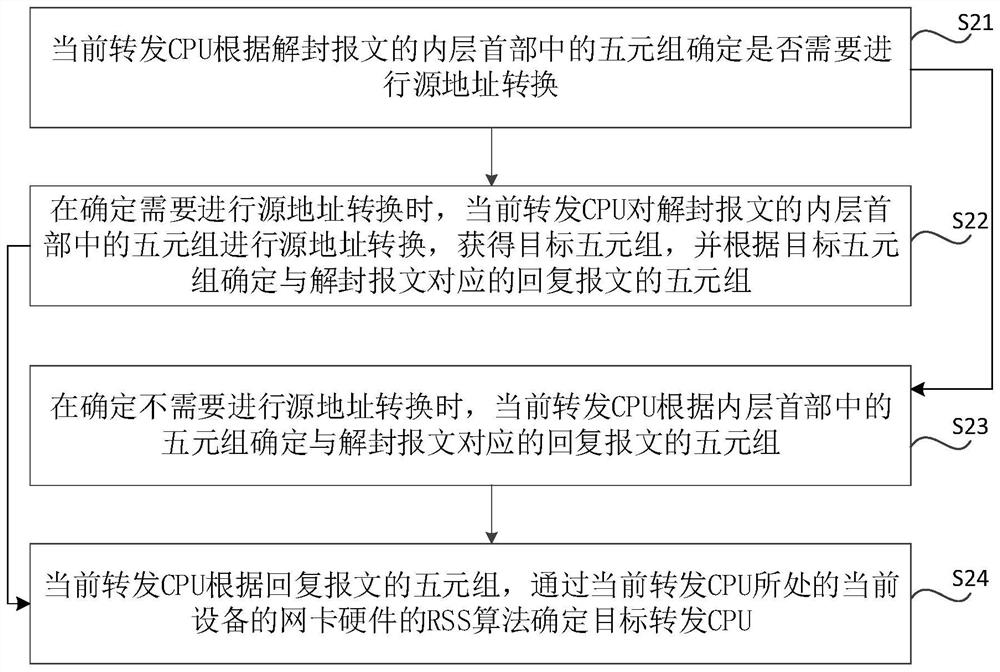

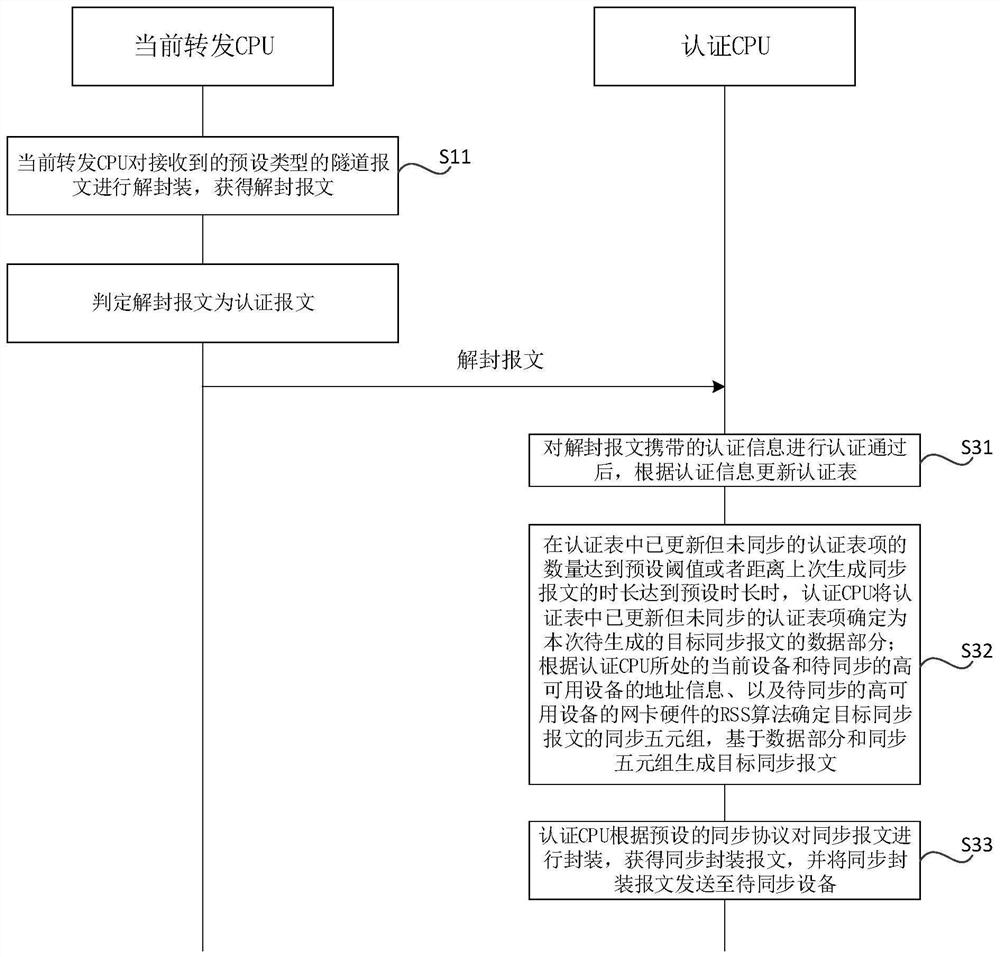

ActiveCN109194558BReduce switchingGuaranteed forwarding performanceNetworks interconnectionRelevant informationEngineering

The present disclosure relates to a tunnel message authentication forwarding method and system, the method comprising: the current forwarding CPU decapsulates the received preset type of tunnel message to obtain the decapsulated message; when the decapsulated message is not When authenticating a message, the current forwarding CPU queries the session table created in the system according to the decapsulated message; when the current forwarding CPU does not query the session table corresponding to the decapsulated message, the current forwarding CPU queries authentication table to determine whether a session entry can be created for the decapsulated packet; when it is determined that a session entry can be created for the decapsulated packet, the target forwarding CPU Create a session entry in the session table, and forward the decapsulated packet based on the session entry. Through the above technical solution, it is possible to effectively reduce the switching between CPUs, and also effectively reduce the amount of data maintenance, and improve the forwarding performance of the system.

Owner:NEUSOFT CORP

Data request processing method and device and computer readable storage medium

ActiveCN112422429AGuaranteed forwarding performanceAvoid Path ConflictsData switching networksDomain namePathPing

The embodiment of the invention discloses a data request processing method and device and a computer readable storage medium. The method is applied to flow forwarding equipment, and comprises the following steps: receiving a data request of which a target domain name is a domain name of the flow forwarding equipment, wherein a target domain name is further stored in the specified area in the datarequest, and the target domain name is different from the domain name of the flow forwarding equipment; verifying the target domain name according to a preset domain name list; updating the target domain name of the data request into the target domain name under the condition that the verification of the target domain name is passed; and forwarding the updated data request of the target domain name. According to the embodiment of the invention, there is no need to apply for a special path for each server in the back-end service system, the implementation is very convenient, path conflicts canbe avoided, and the flow forwarding performance can be ensured.

Owner:BEIKE TECH CO LTD

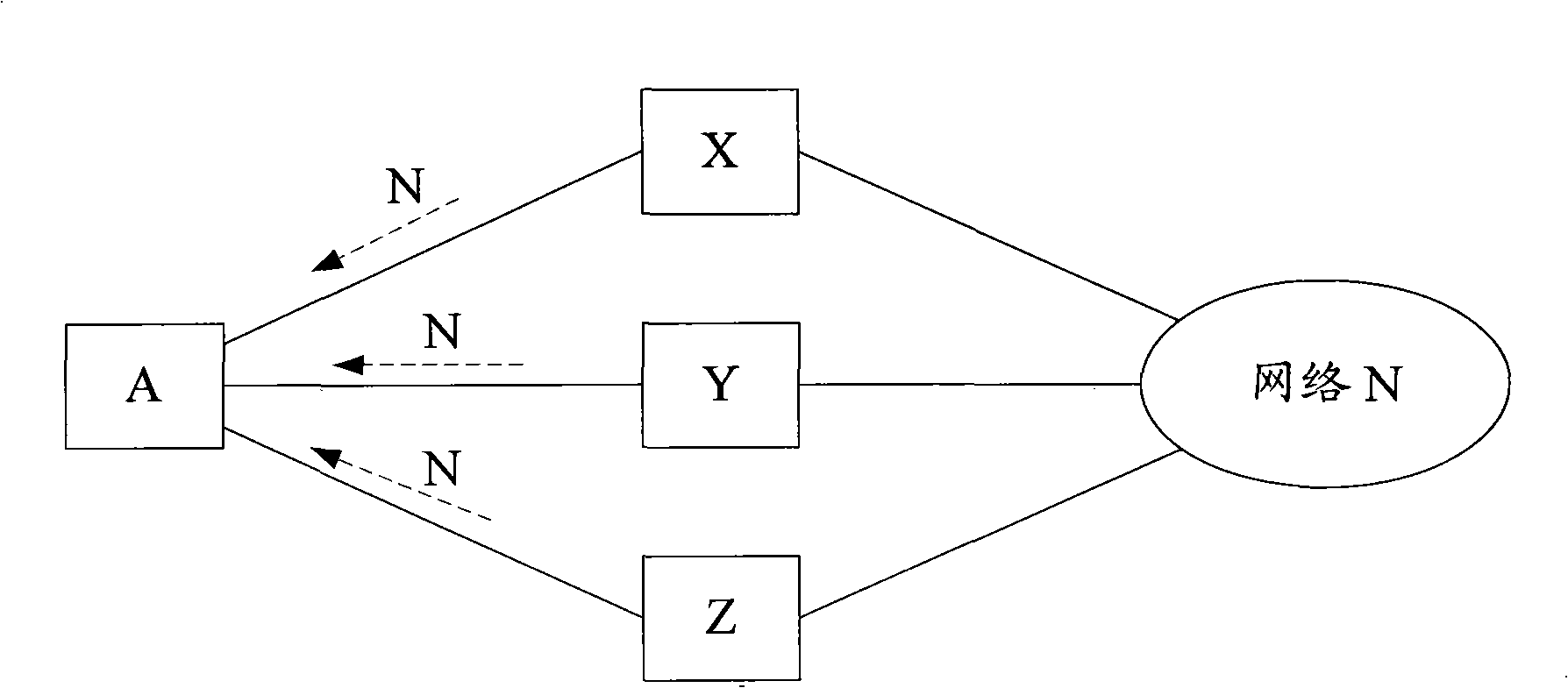

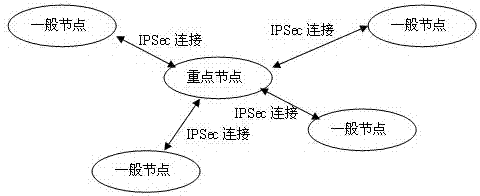

A VPN multi-party connection method based on ipsec

ActiveCN104253733BGuaranteed forwarding performanceEnable a secure connectionNetworks interconnectionNetwork packetIPsec

In the present invention, in the IPSec VPN that needs multi-party sessions, by dividing all nodes that need to be connected into key nodes and general nodes, and setting their affiliation, when initiating a multi-party session, the key nodes are forwarded, so that the data Passed between nodes participating in a multiparty session in a secure manner. The invention does not need to use any additional protocol, does not need to repackage and pack the data packets to be sent, and realizes multi-party conversation. Through the establishment of key nodes, it is only necessary to ensure the forwarding performance of key nodes, that is, to achieve multi-party secure connections to other general nodes, so that application environments such as enterprises can obtain efficient and economical operating modes.

Owner:BEIJING SAPLING TECH

A method and device for vpws message passing through three-layer ip network

ActiveCN108040135BRealize wire-speed forwardingGuaranteed forwarding performanceData switching networksData packComputer architecture

A method and device for VPWS messages to traverse a three-layer IP network, consisting of a control plane and a forwarding plane, with a multi-core CPU as the core of the control plane, running multiple control plane protocols such as routing protocols, LDP protocols, GRE protocols, and ARP protocols, and The various table items needed to generate the forwarding plane to process data packets include routing tables, MPLS label tables, GRE session tables, and ARP tables; the forwarding plane is implemented by switching chips and FPGAs, which cooperate with each other to process VPWS data packets, and switching chips Responsible for receiving data packets, after corresponding processing, send the data packets to the FPGA, FPGA processes the data packets and then sends them to the switch chip, and the switch chip performs final processing on the data packets and sends them out; the present invention uses the CPU as the core of the control plane to forward Various forwarding entries related to VPWS and GRE are written on the surface, and the switch chip and FPGA are used as the forwarding plane to cooperate with each other to process VPWS packets through the IP network, which can realize the wire-speed forwarding of VPWS over GRE and ensure the forwarding performance of the device port.

Owner:ANHUI WANTONG POSTS & TELECOMM CO LTD

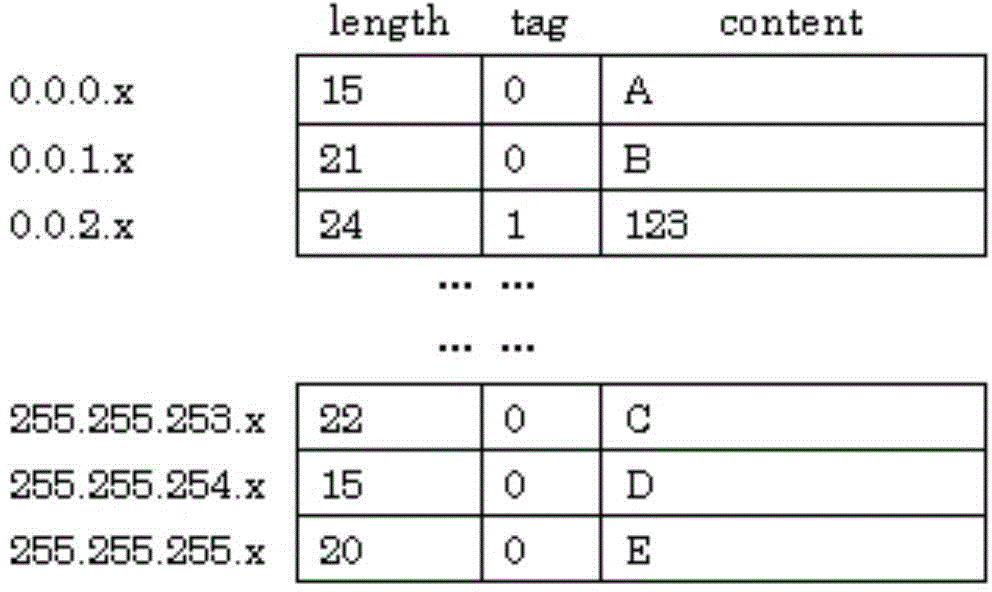

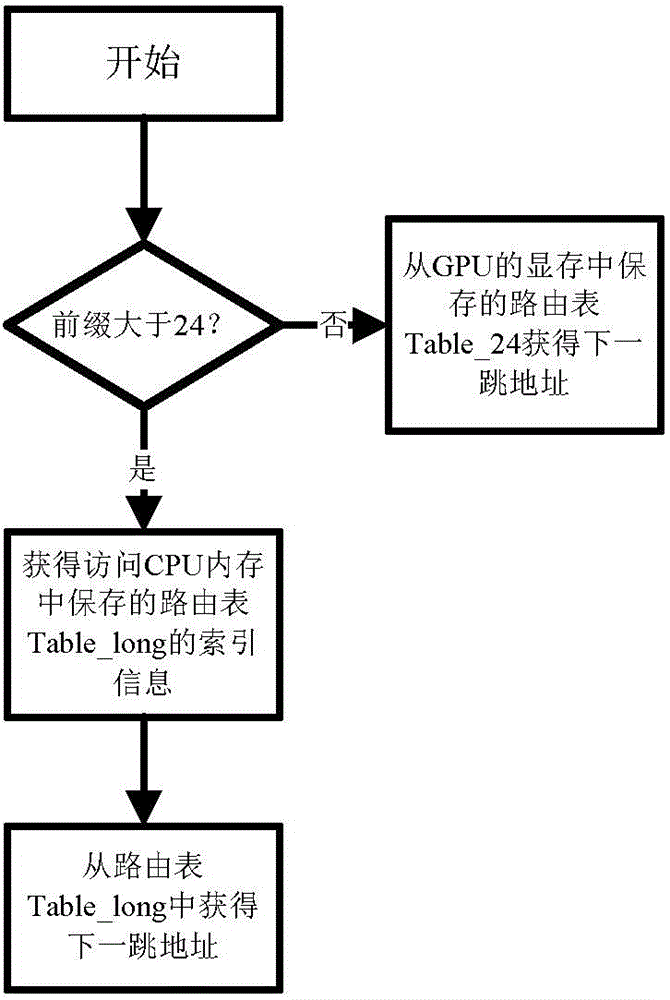

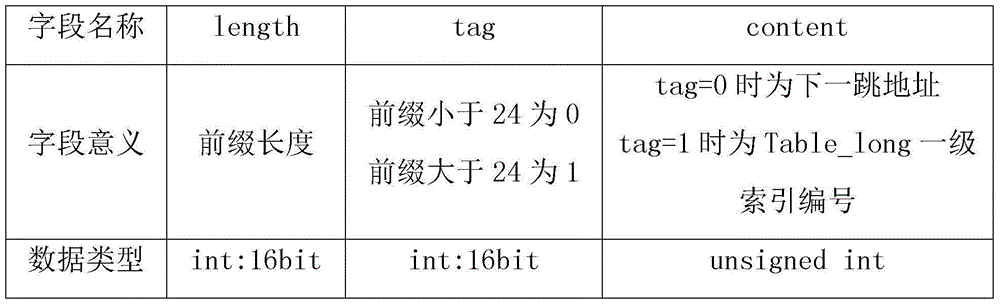

Routing method and device based on GPU

InactiveCN104539540AAvoid CPU bottlenecksGuaranteed forwarding performanceData switching networksSpecific program execution arrangementsGraphicsGraphic card

The invention provides a routing method based on a GPU. A routing table Table_24 is preserved in the GPU of a host display card, a routing table Table_long is preserved in a CPU of a host, when the prefix length of an inquired IP address is smaller than or equal to 24, a next-hop routing address is acquired from the routing table Table_24, or else access to the routing table Table_long is further conducted, and the next-hop routing address is acquired from the routing table Table_long. By the adoption of the method, design and implementation of a high-performance routing lookup forwarding engine are accelerated through the GPU, the CPU bottleneck of a software router is avoided, the defects in the performance of the software router are overcome, and high throughput is achieved.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

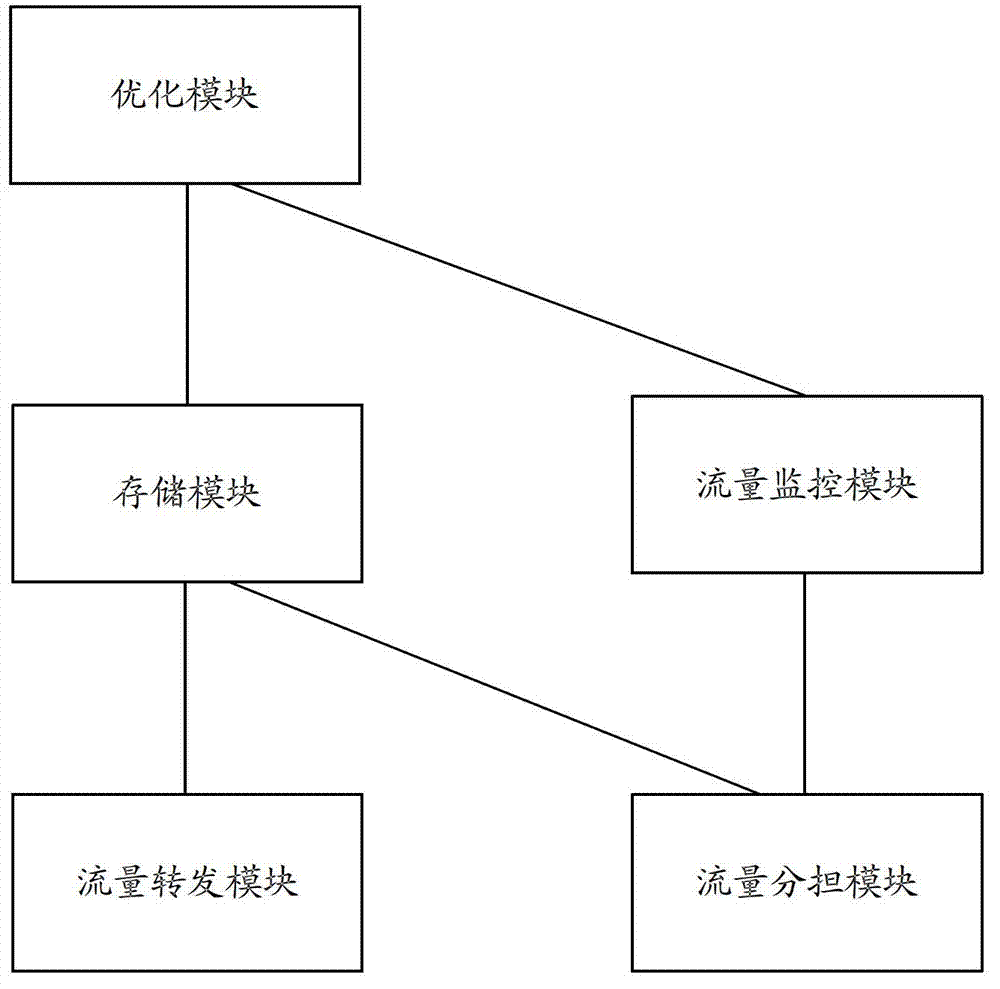

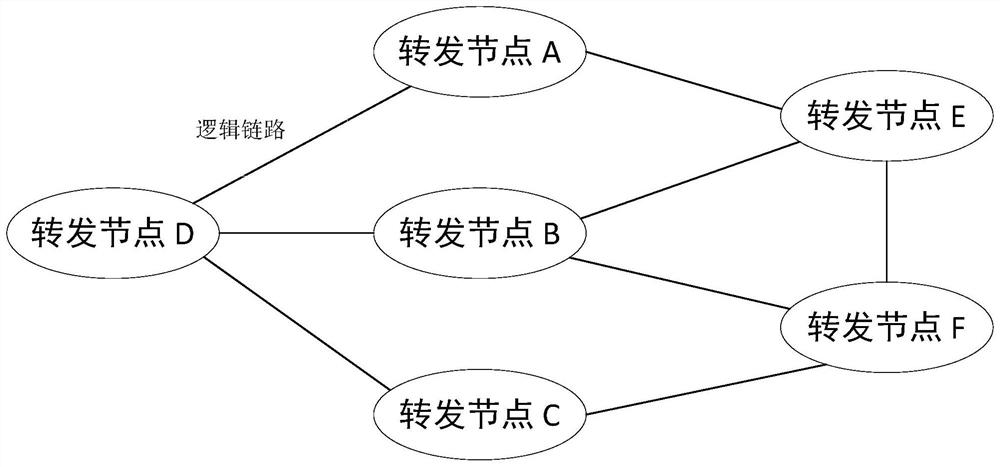

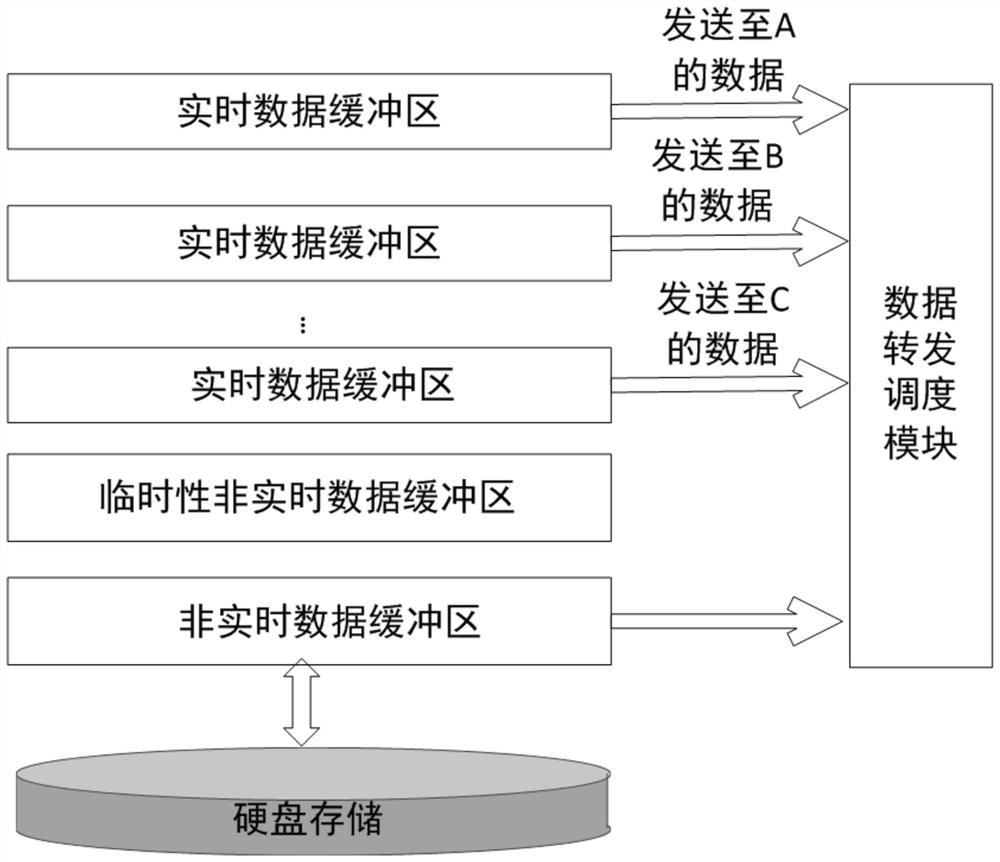

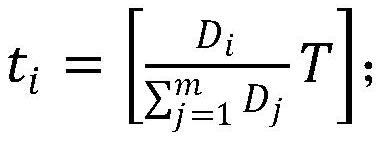

Application layer adaptive data forwarding system for distinguishing real-time and non-real-time data streams

PendingCN114760358AFlexible deployment capabilityImprove caching capacityTransmissionData packData stream

The invention discloses an application layer adaptive data forwarding system for distinguishing real-time and non-real-time data streams, belongs to the technical field of data forwarding, and aims to solve the technical problem of how to optimize application layer data forwarding based on an application layer and improve data forwarding performance. According to the technical scheme, the system comprises a data sending scheduling module, a hard disk storage, a temporary non-real-time data buffer area, a non-real-time data buffer area and a plurality of real-time data buffer areas; wherein the real-time data buffer area is used for storing real-time data received by a data port corresponding to the forwarding node; the temporary non-real-time data buffer area is used for storing data transferred from the non-real-time data buffer area; the non-real-time data buffer area is used for caching normally received non-real-time data; and the data sending scheduling module is used for taking out the data in the real-time data sending buffer area according to a specified strategy, checking a source address field and a target address field in the data packet application data unit, and forwarding the data to a next hop according to a routing table.

Owner:QILU UNIV OF TECH

A message forwarding method, device and system

ActiveCN105634956BGuaranteed forwarding performanceReduce cross-VM forwardingData switching networksDistributed computingPacket forwarding

Owner:HUAWEI TECH CO LTD

A method and device for implementing rfc2544 in vpws environment

ActiveCN108075949BRealize wire-speed forwardingGuaranteed forwarding performanceData switching networksData packWire speed

Owner:ANHUI WANTONG POSTS & TELECOMM CO LTD