Patents

Literature

35 results about "High-level design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

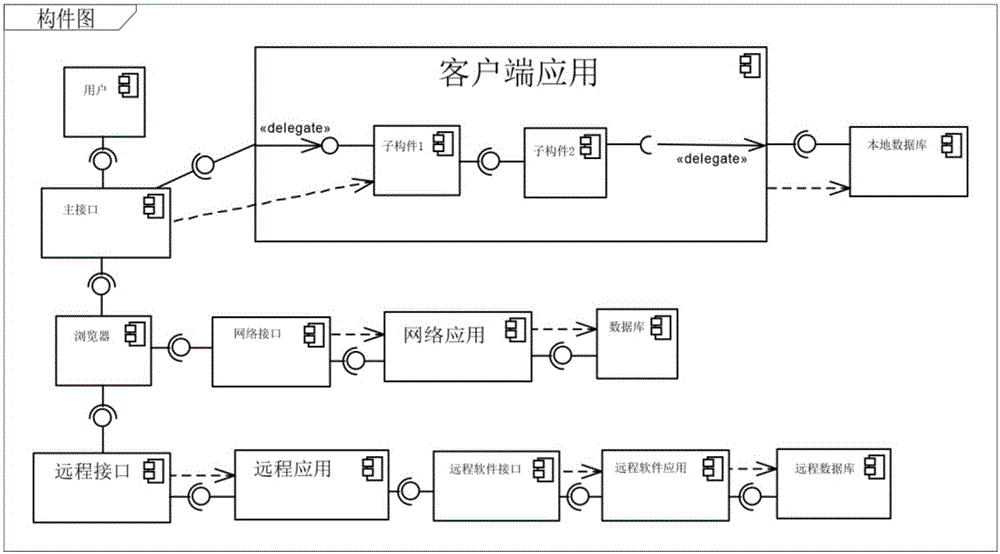

High-level design (HLD) explains the architecture that would be used for developing a software product. The architecture diagram provides an overview of an entire system, identifying the main components that would be developed for the product and their interfaces. The HLD uses possibly nontechnical to mildly technical terms that should be understandable to the administrators of the system. In contrast, low-level design further exposes the logical detailed design of each of these elements for programmers.

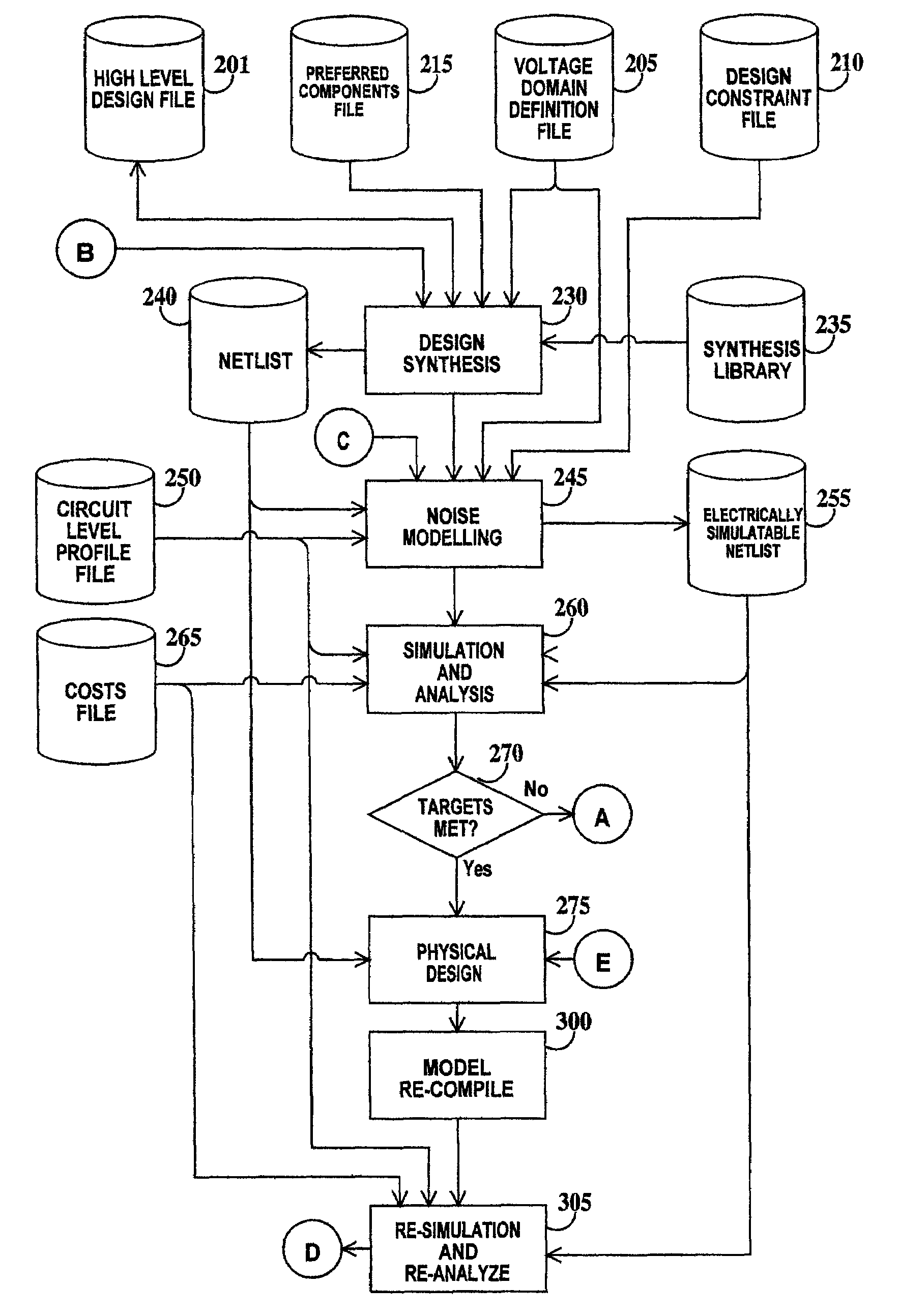

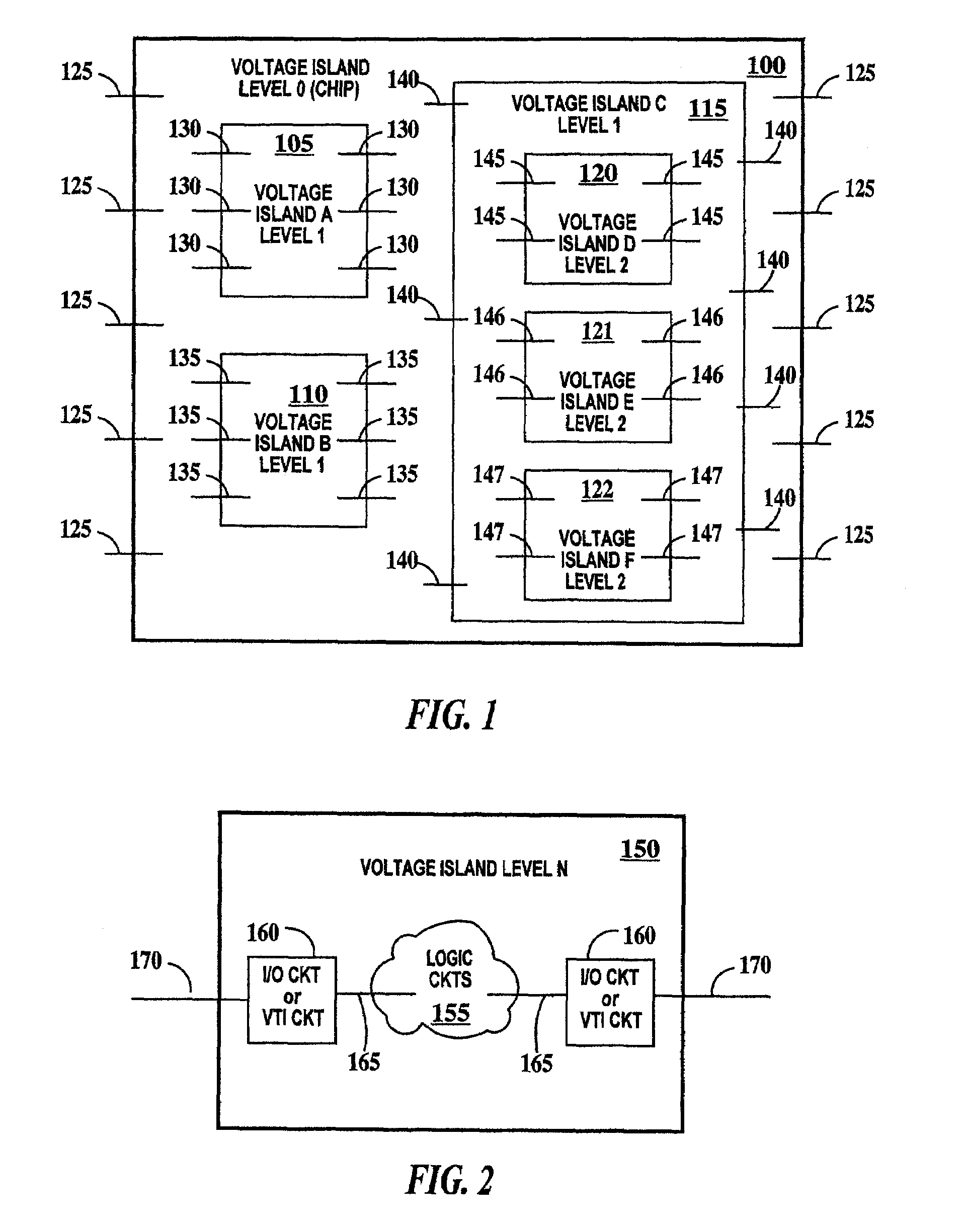

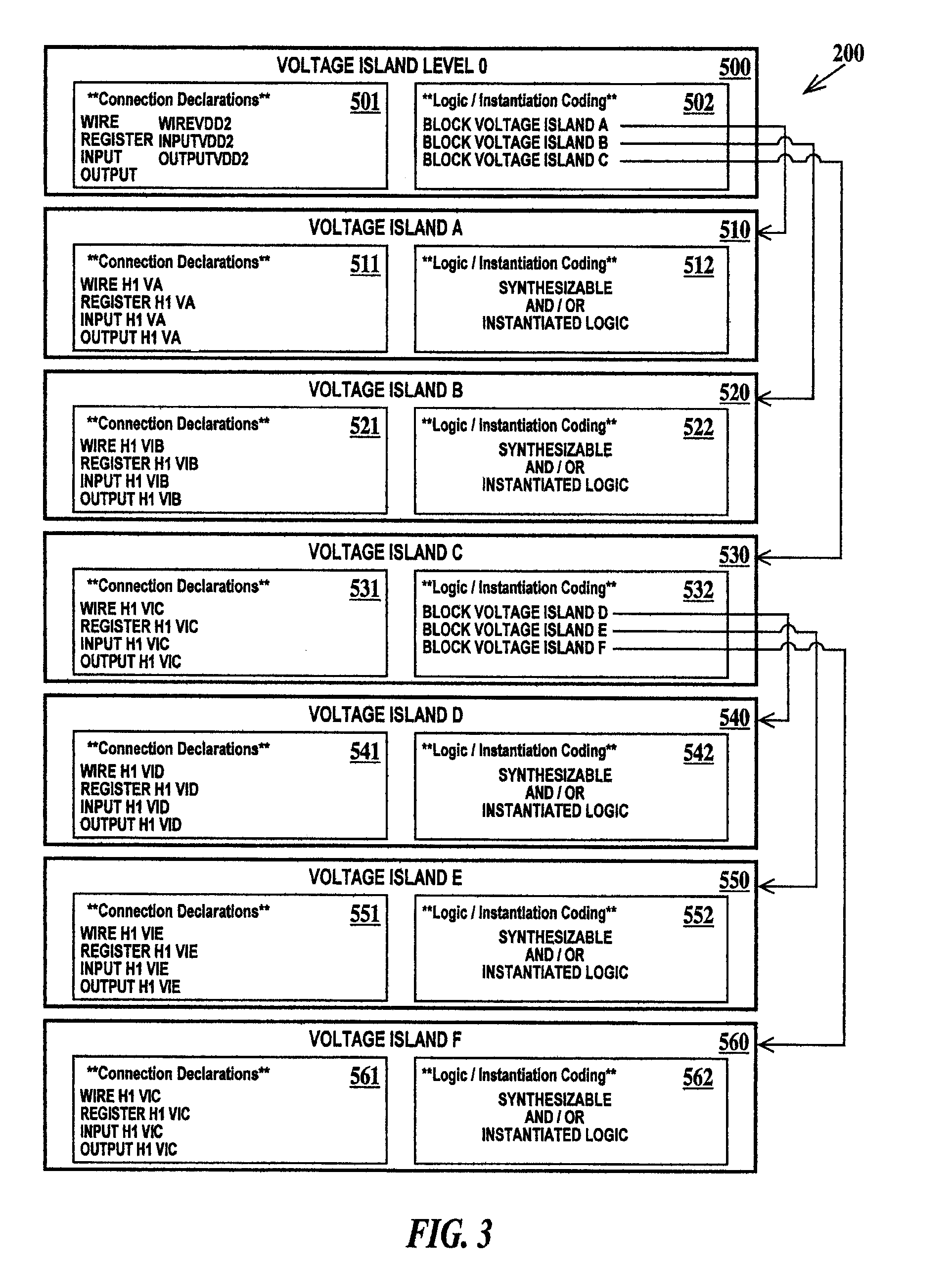

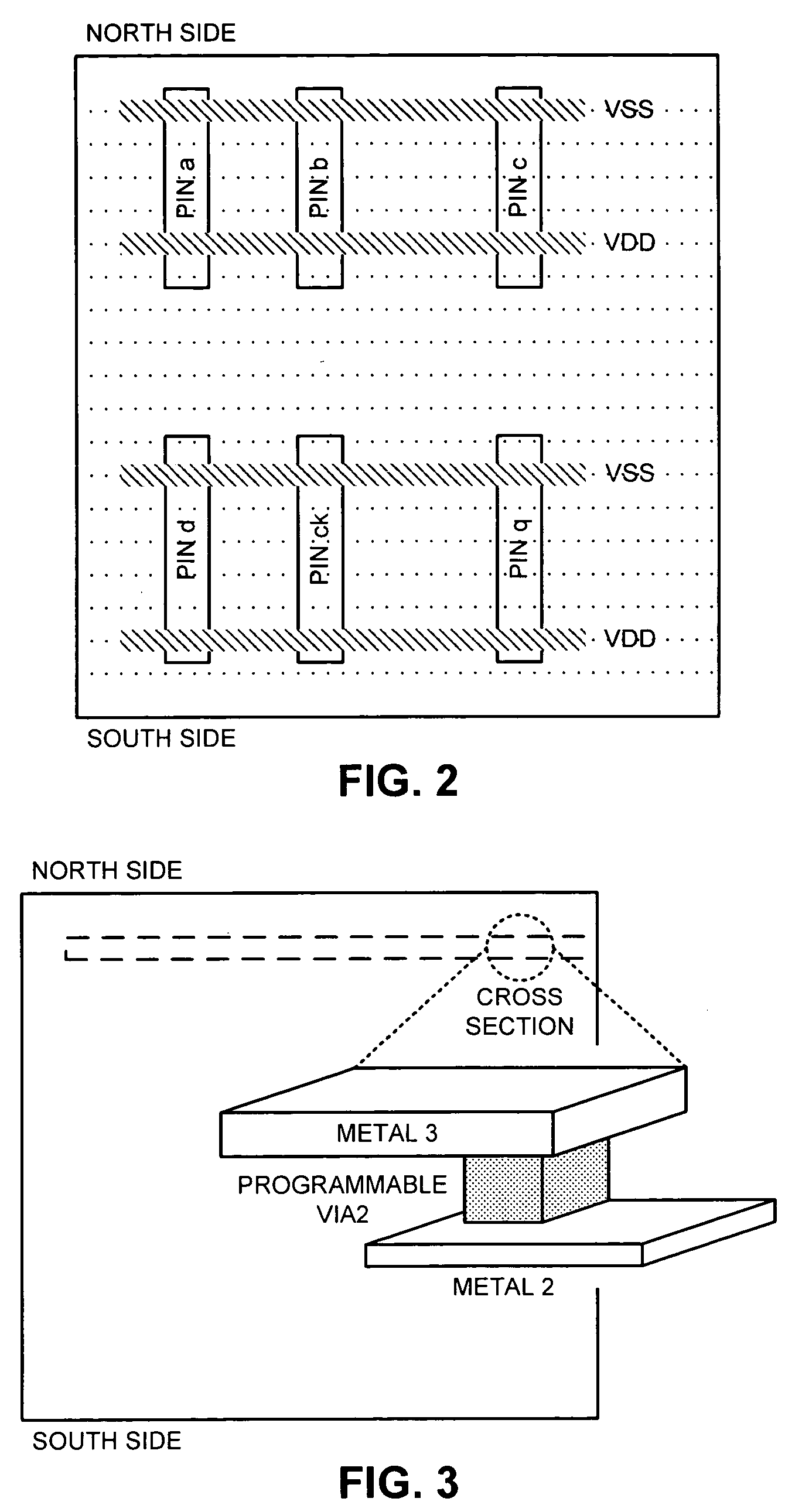

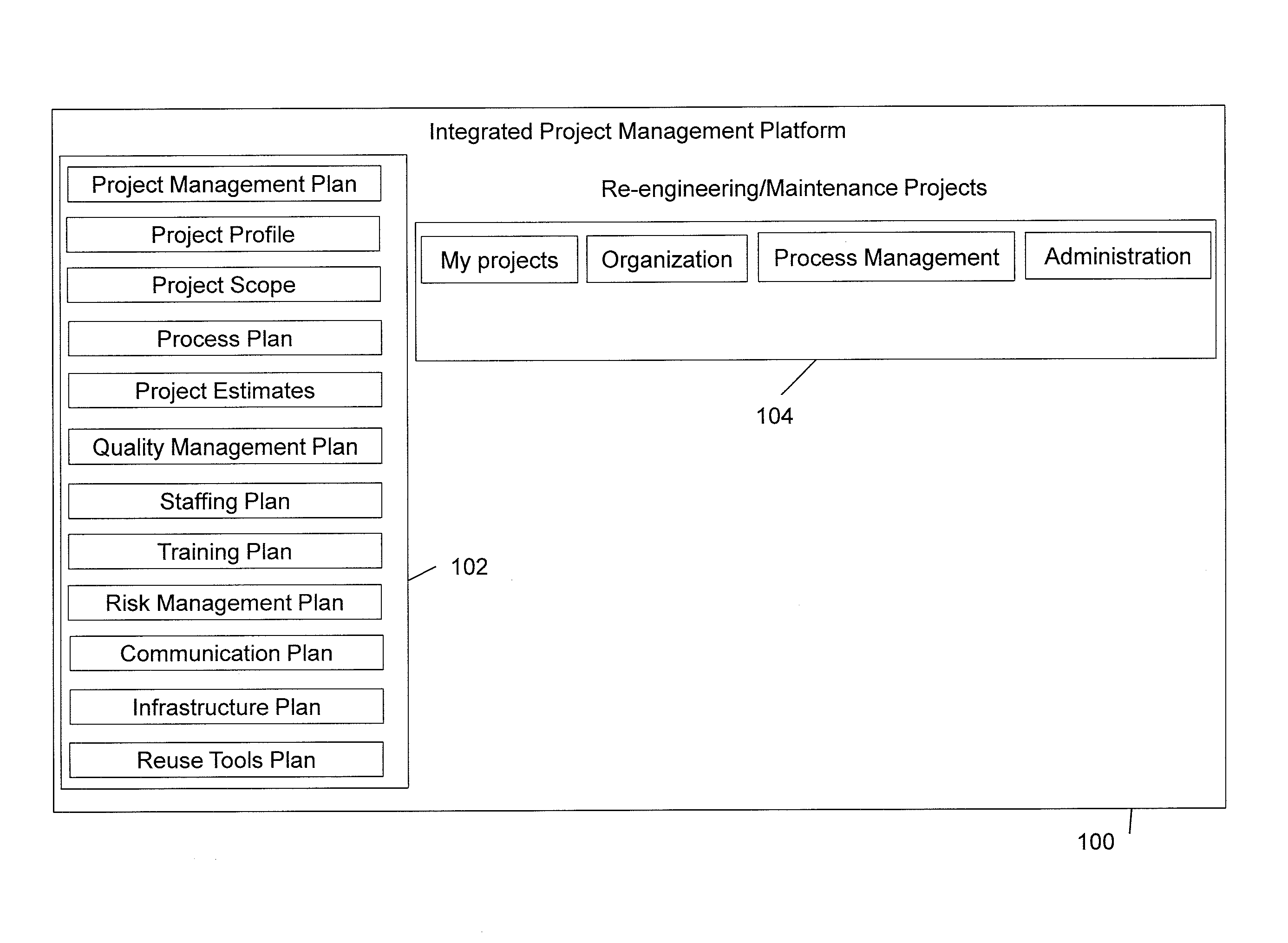

Method for designing an integrated circuit having multiple voltage domains

InactiveUS7000214B2Analogue computers for electric apparatusAnalogue computers for nuclear physicsSimulation noiseEngineering

Owner:INT BUSINESS MASCH CORP

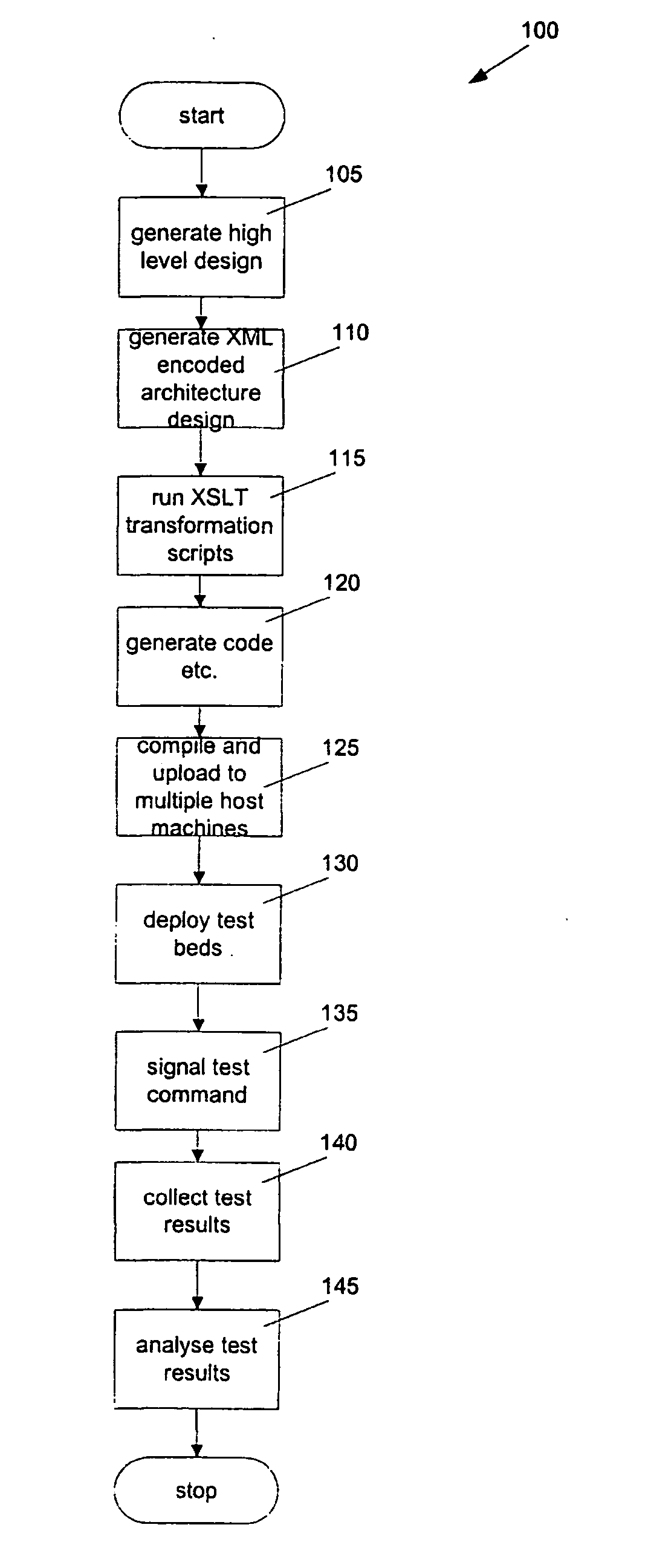

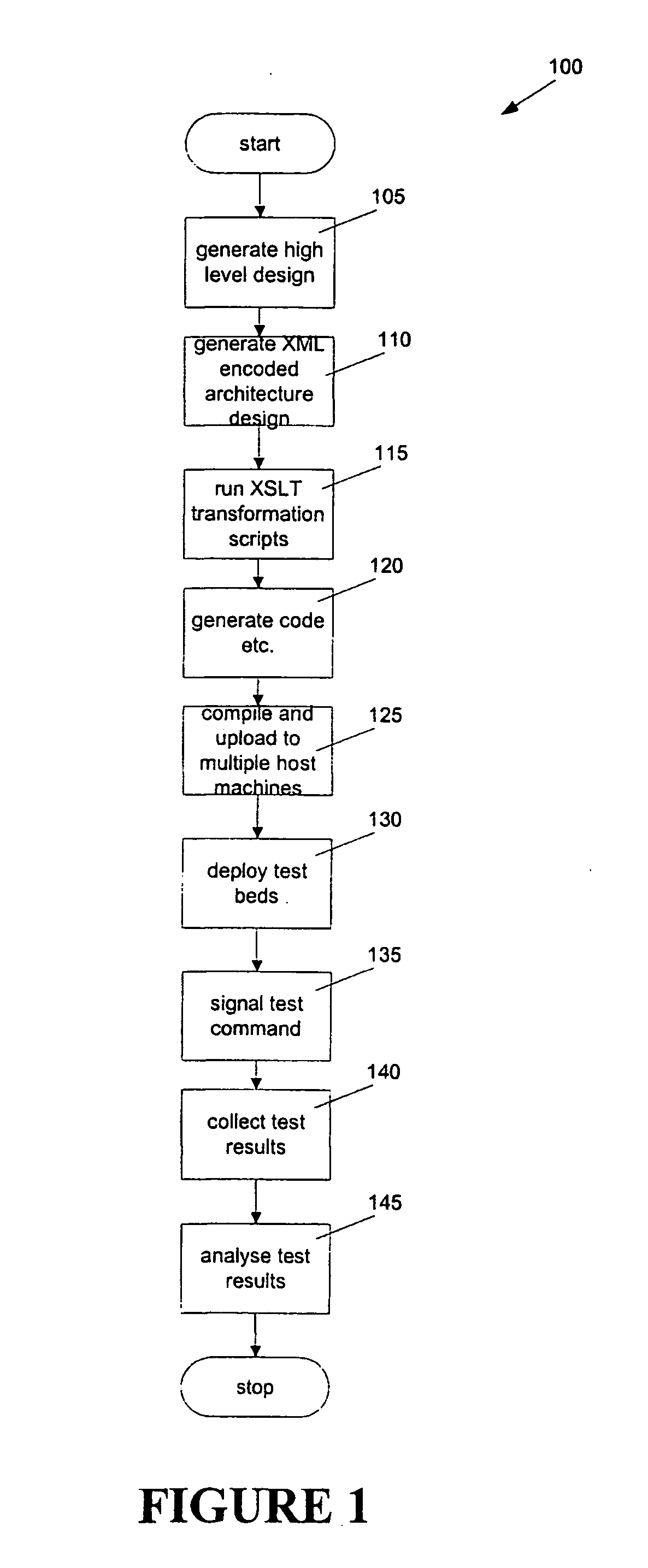

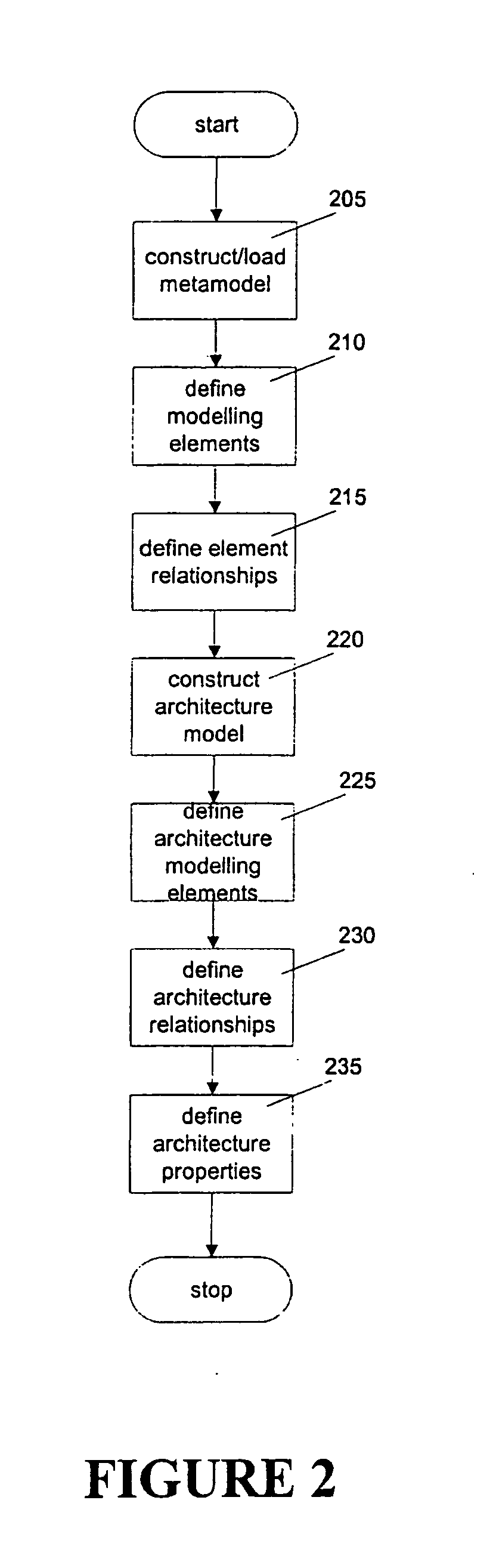

Software design system and method

InactiveUS20040237066A1Hardware monitoringSoftware testing/debuggingComputer architectureSoftware design

A method of generating a high level design of a distributed system test bed comprising the steps of defining a meta-model of the test bed; defining at least two architecture modelling elements within the meta-model to form an architecture model associated with the meta-model; defining at least one relationship between a pair of architecture modelling elements; defining properties associated with at least one of the architecture modeling elements; and storing the high level design in computer memory.

Owner:AUCKLAND UNISERVICES LTD

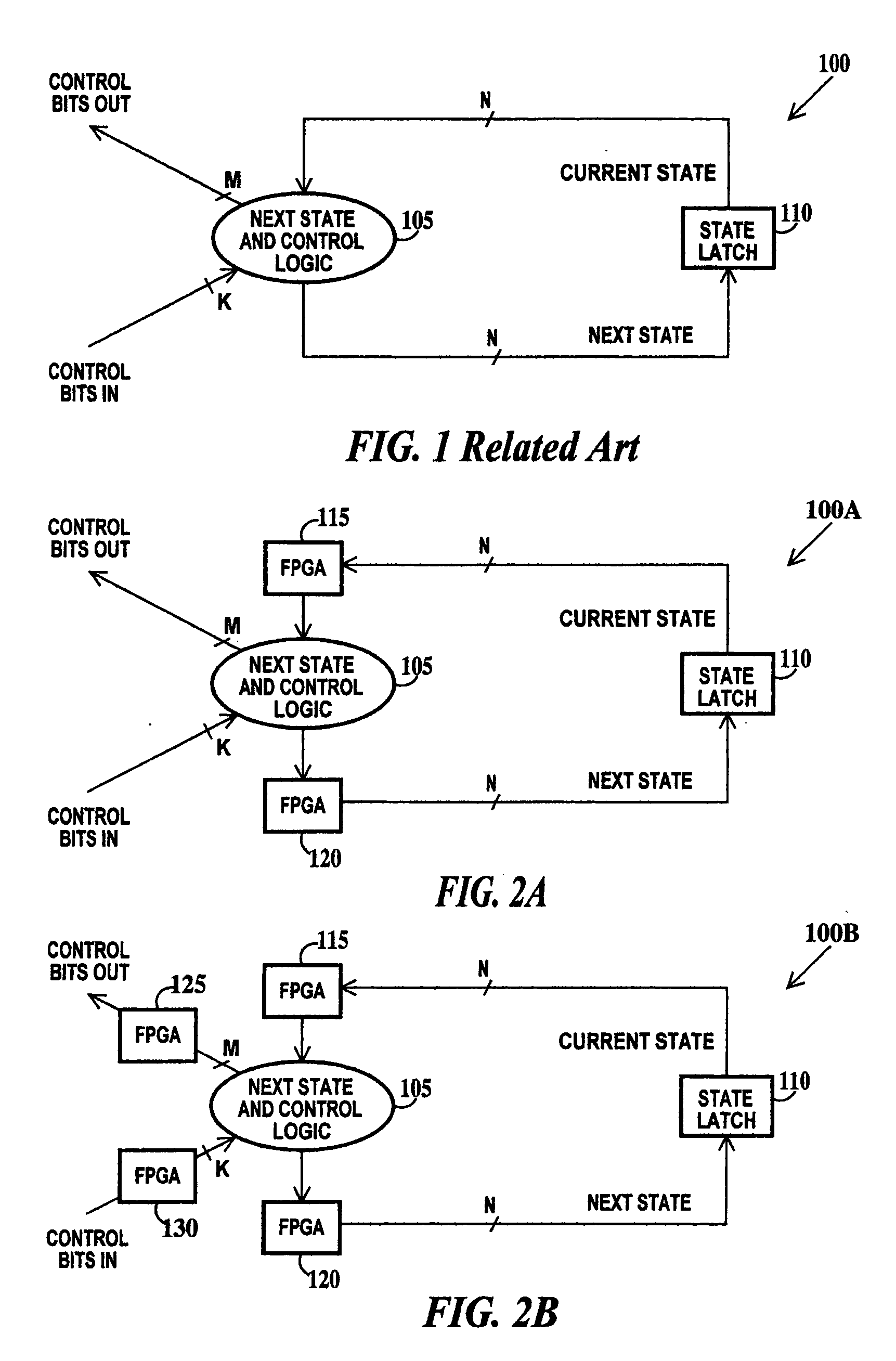

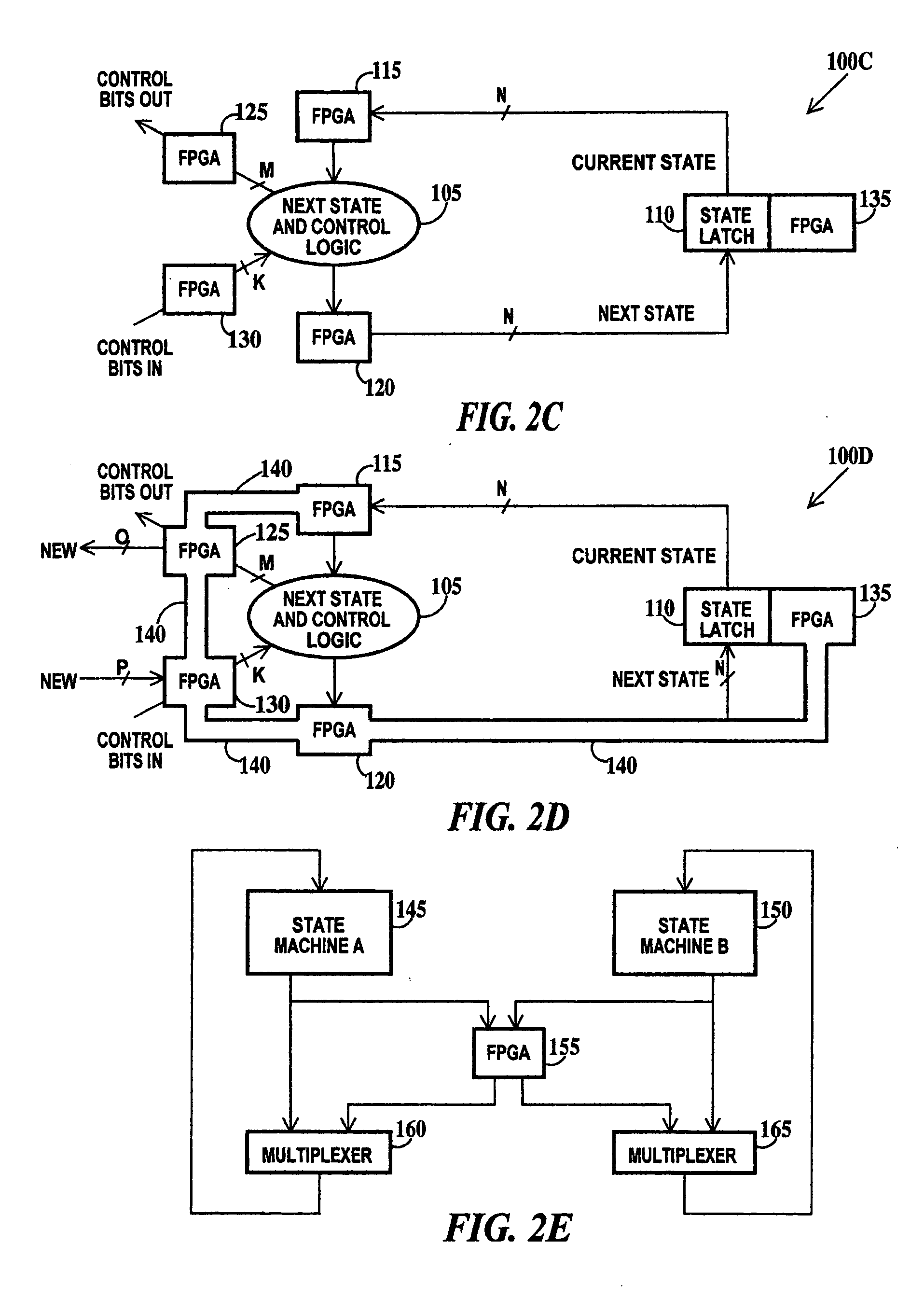

Method for modifying the behavior of a state machine

InactiveUS20050120323A1CAD circuit designSoftware simulation/interpretation/emulationProgrammable logic deviceHigh-level design

A method and system for modifying the function of a state machine having a programmable logic device. The method including: (a) modifying a high-level design of the state machine to obtain a modified high-level design of the state machine with a modified function; (b) generating a programmable logic device netlist from differences in the high-level design and the modified design; and (c) installing the modified function into the state machine by programming the programmable logic device based on the programmable logic device netlist.

Owner:IBM CORP

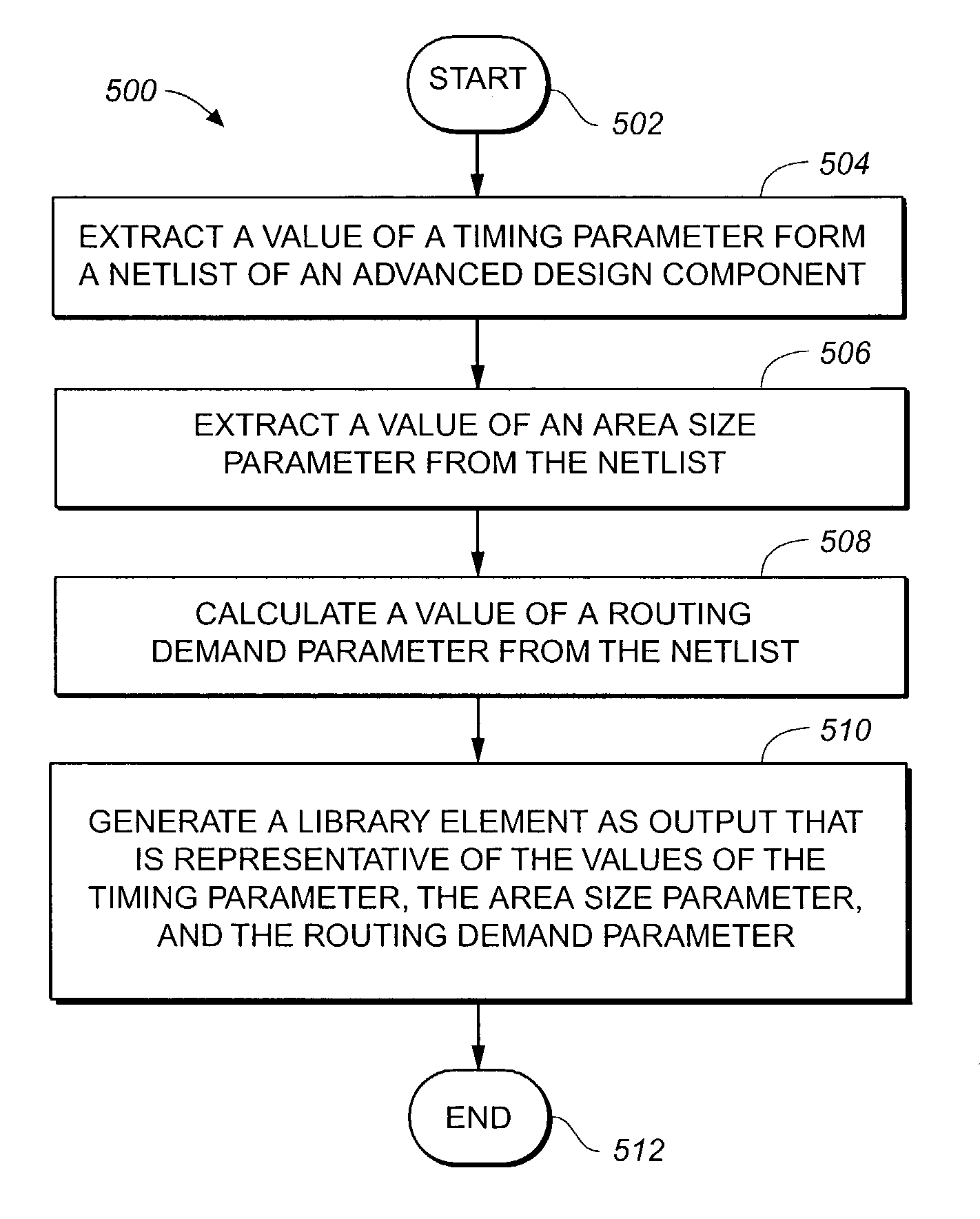

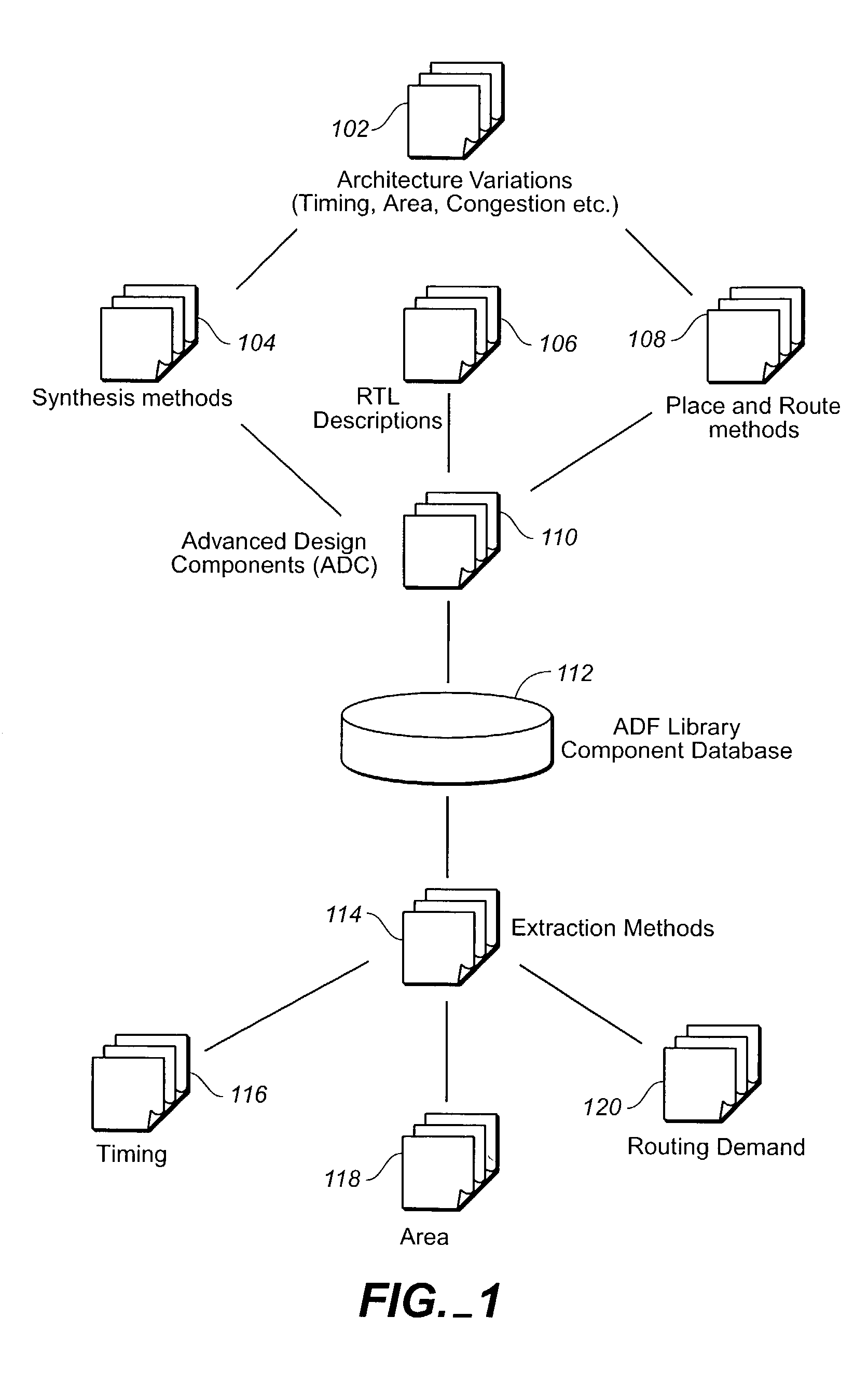

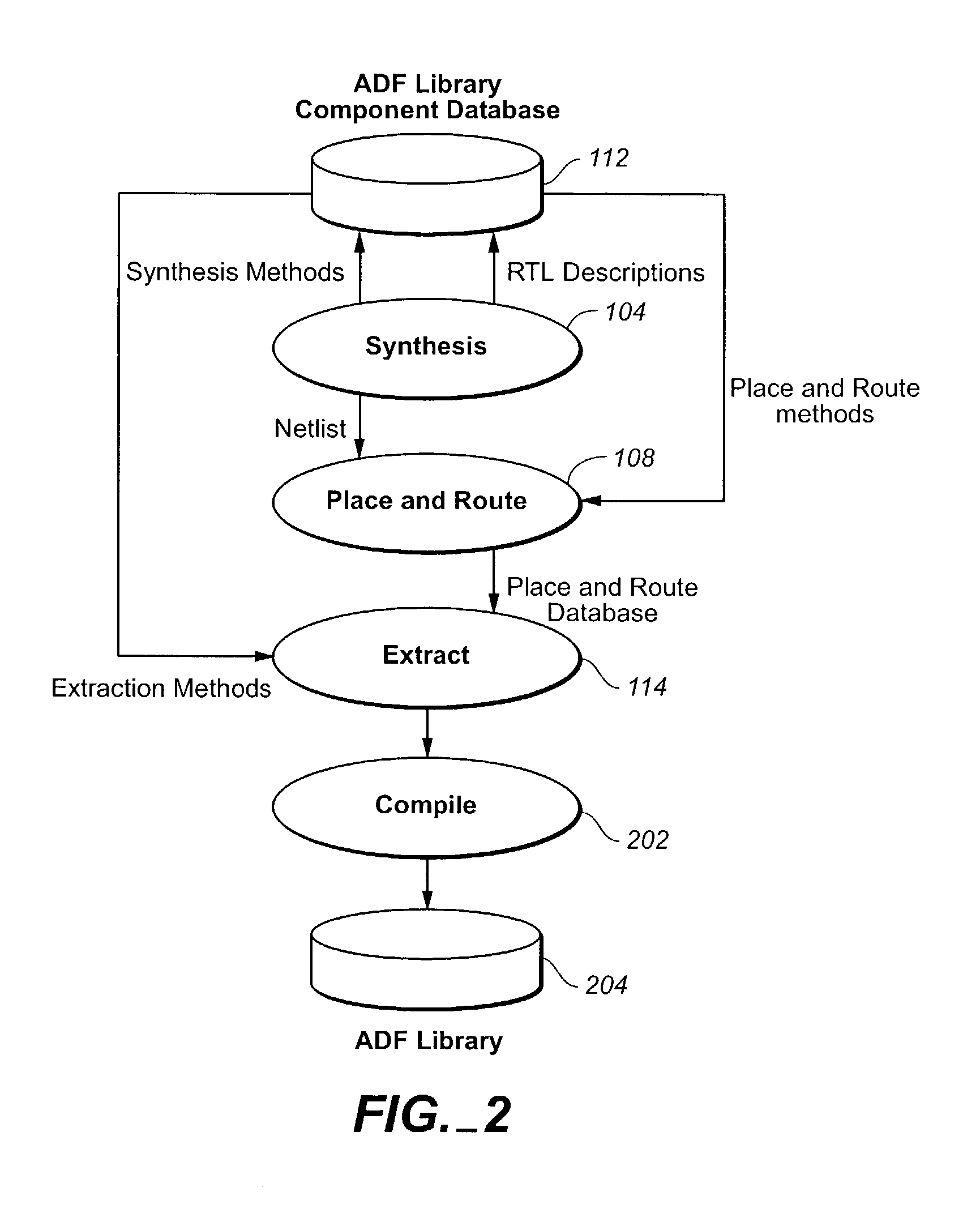

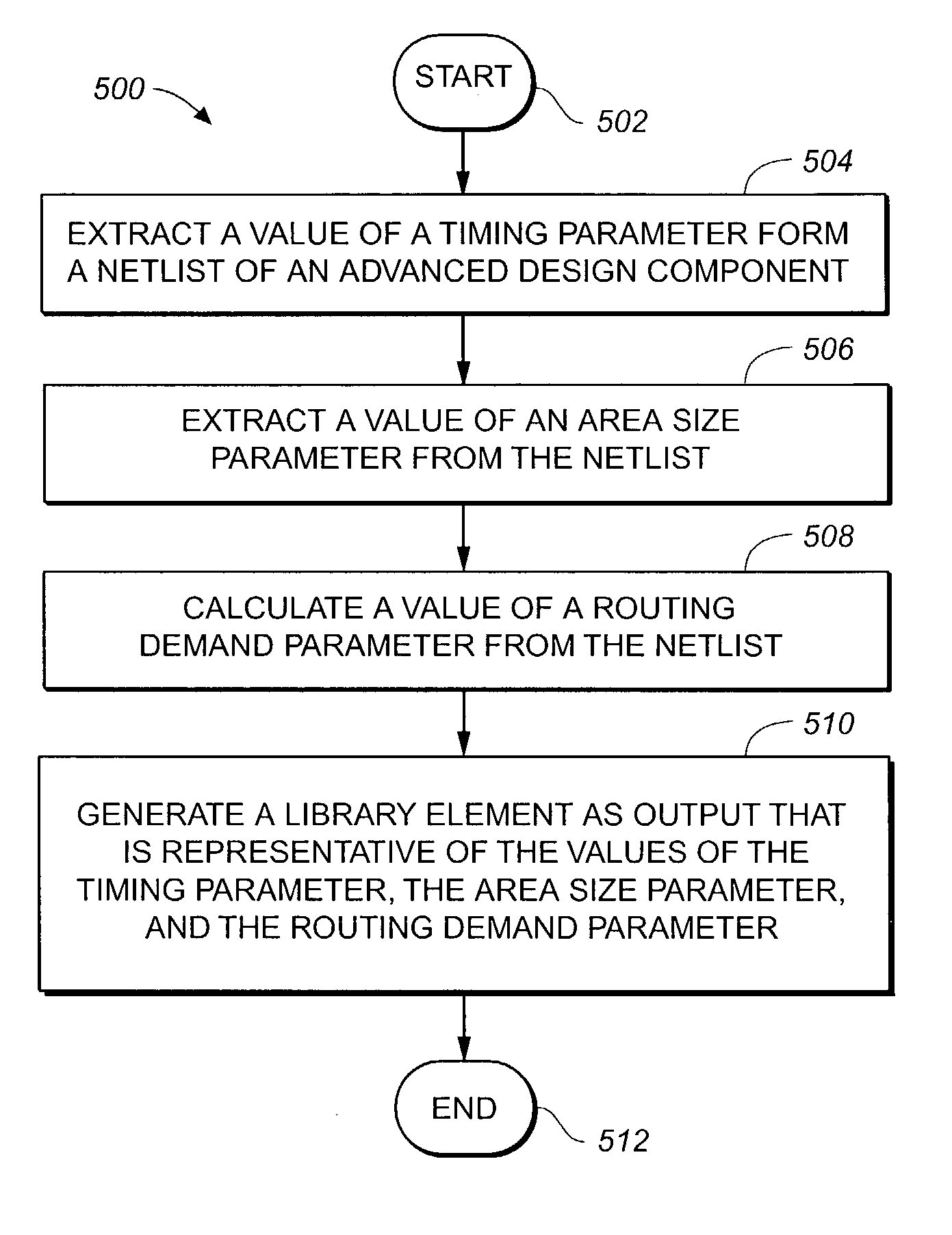

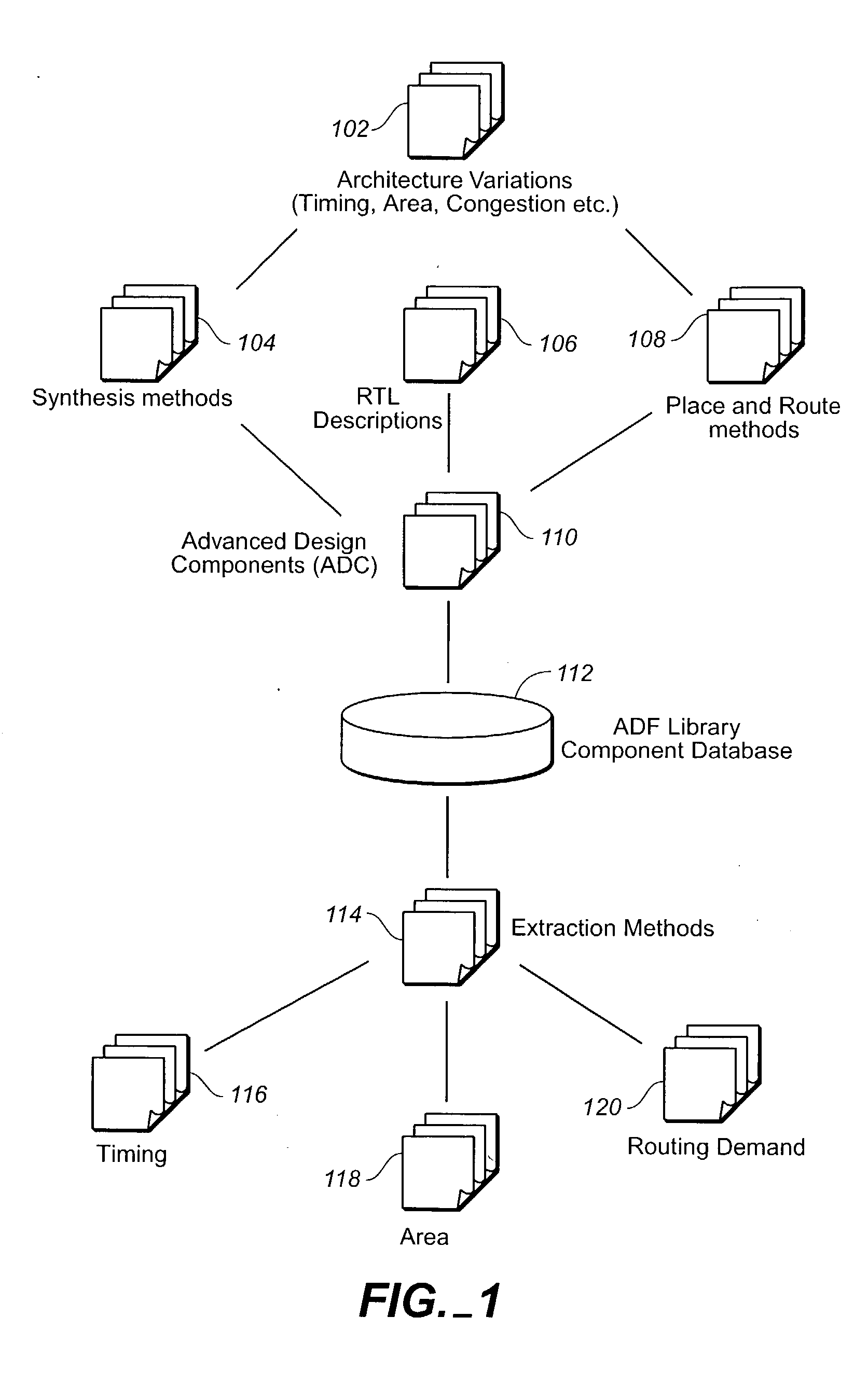

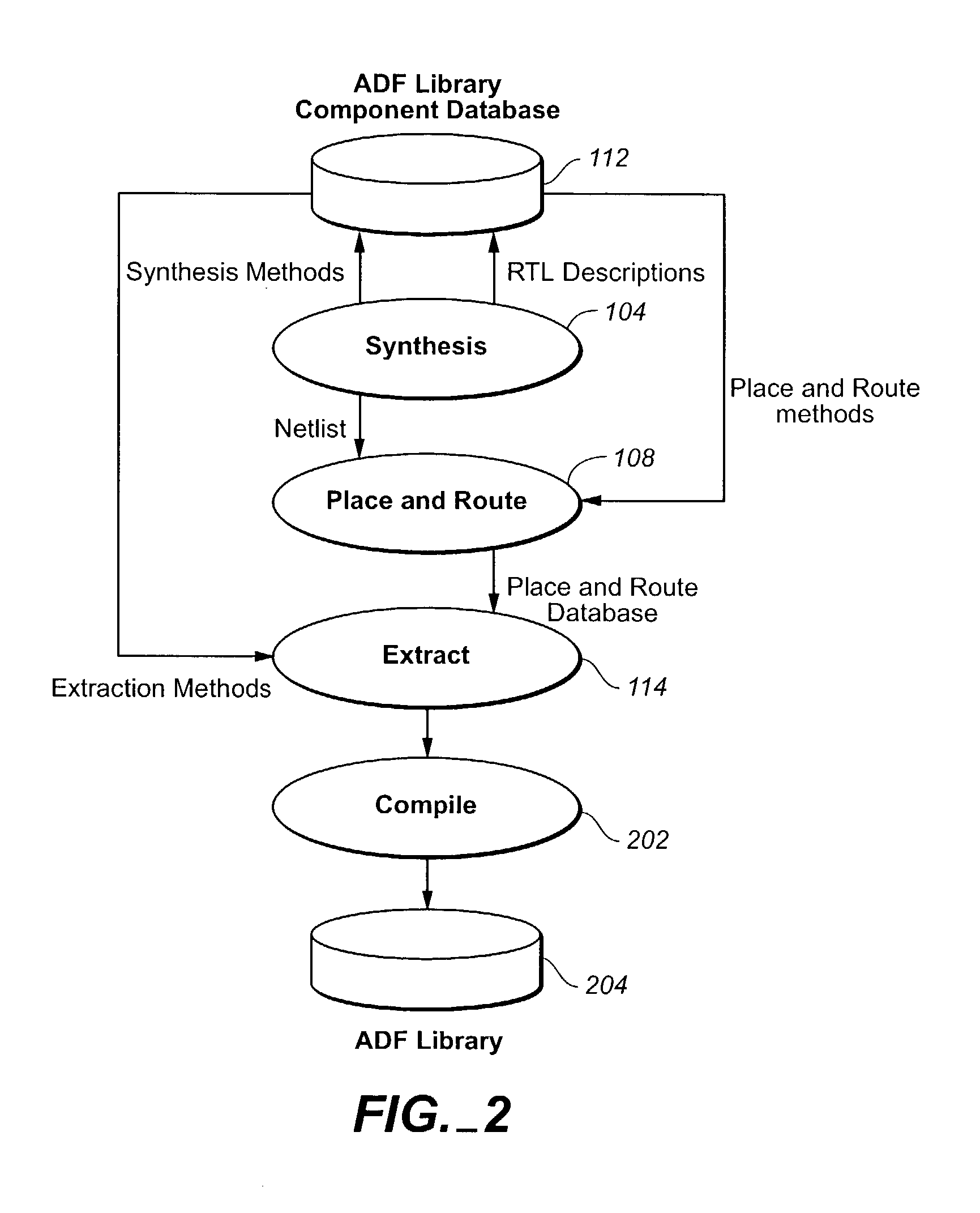

Advanced design format library for integrated circuit design synthesis and floorplanning tools

InactiveUS6990651B2CAD circuit designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit layout

An integrated circuit design library includes a timing parameter representative of a design element in an integrated circuit; an area size parameter representative of the design element in an integrated circuit; and a routing demand parameter representative of a number of connections required for the design element for each value of the timing parameter and the area size parameter.

Owner:BELL SEMICON LLC

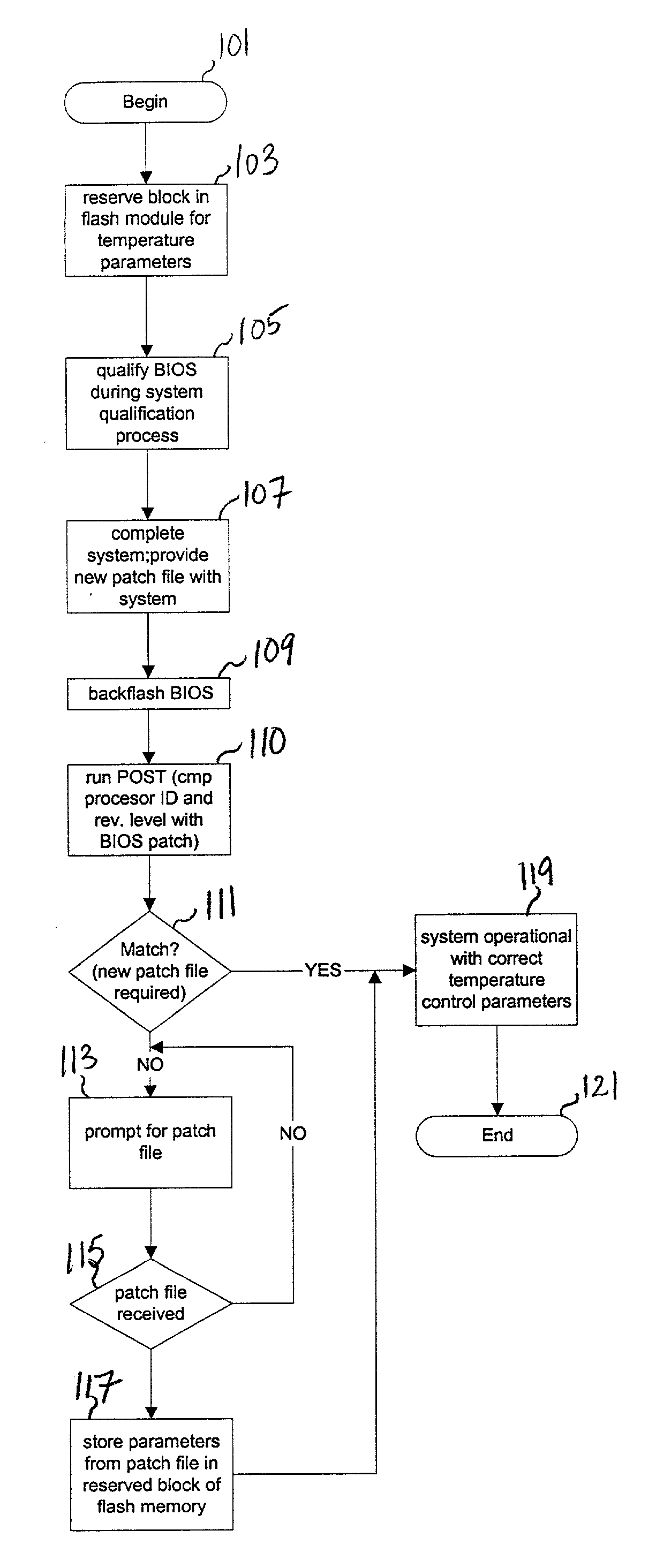

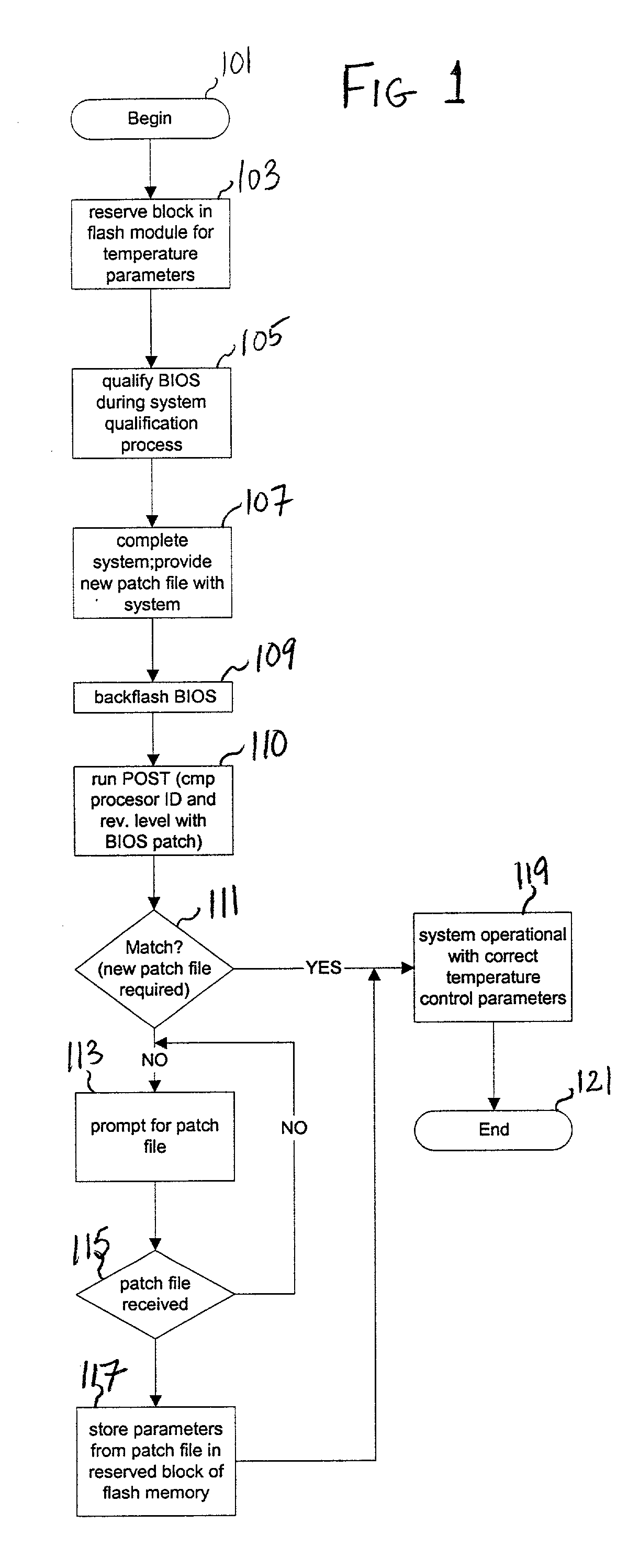

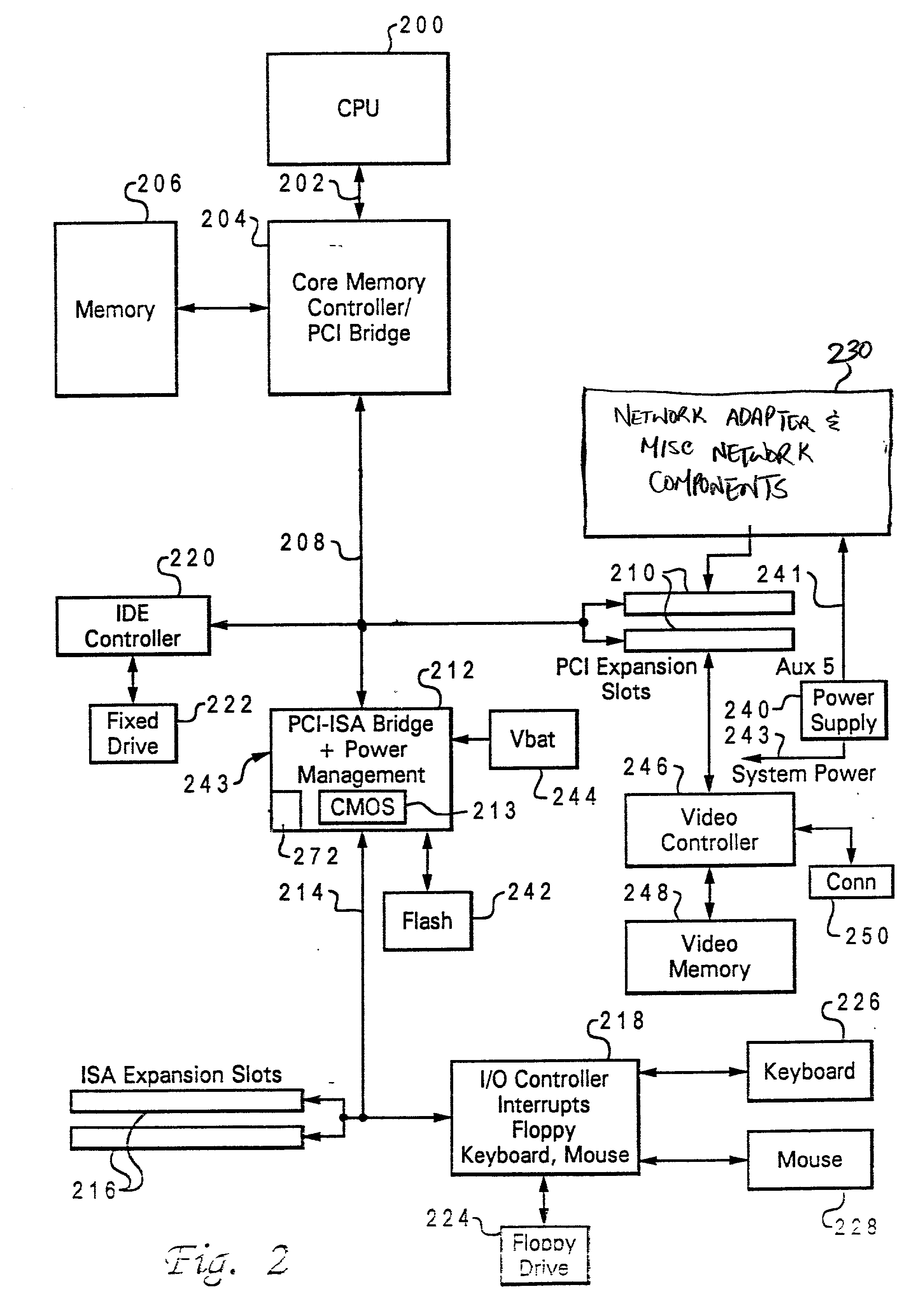

Method and system for providing a flexible temperature design for a computer system

A method and system for providing correct operational parameters for up-level design components utilized within a computer system after a low level basic input / output system (BIOS) code has been qualified. A patch file is created or obtained for a component that is added to a computer system after a BIOS code has been qualified for the computer system. The patch file includes the operating parameters (or profiles) of the component. The flash module is designed with a memory block reserved for holding data from the patch file, which can be updated independently of the rest of the flash module. The Advance Configuration Program Interface (ACPI) or advanced power management (APM) code of the computer system is modified to dynamically read the parameters from this memory block and update their respective functions accordingly. During set up of the computer system, the patch file is flashed into the reserved block of the flash module. The data is merged by the FLASH utility into the existing BIOS so that the computer system has the correct parameters for the particular component.

Owner:LENOVO PC INT

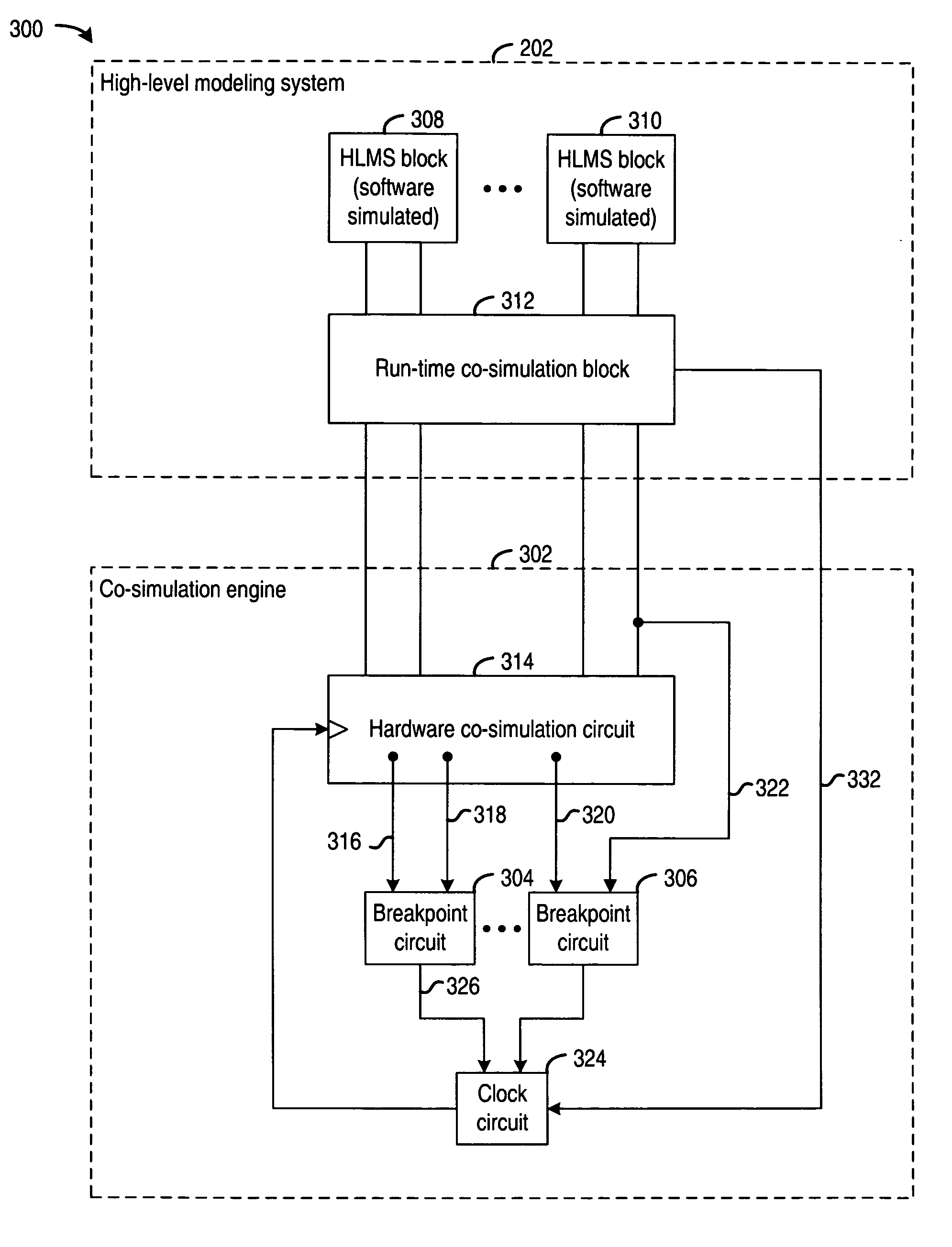

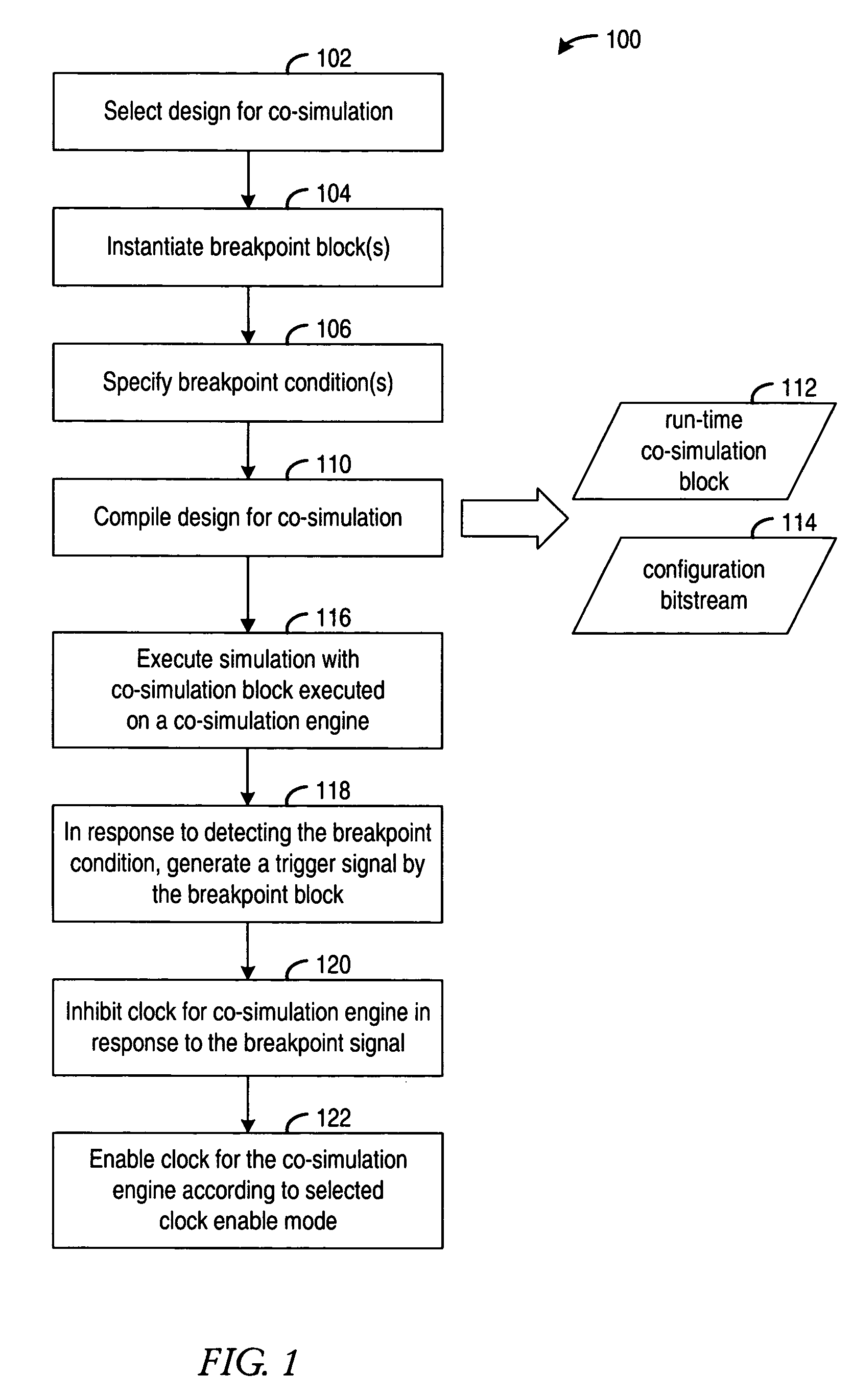

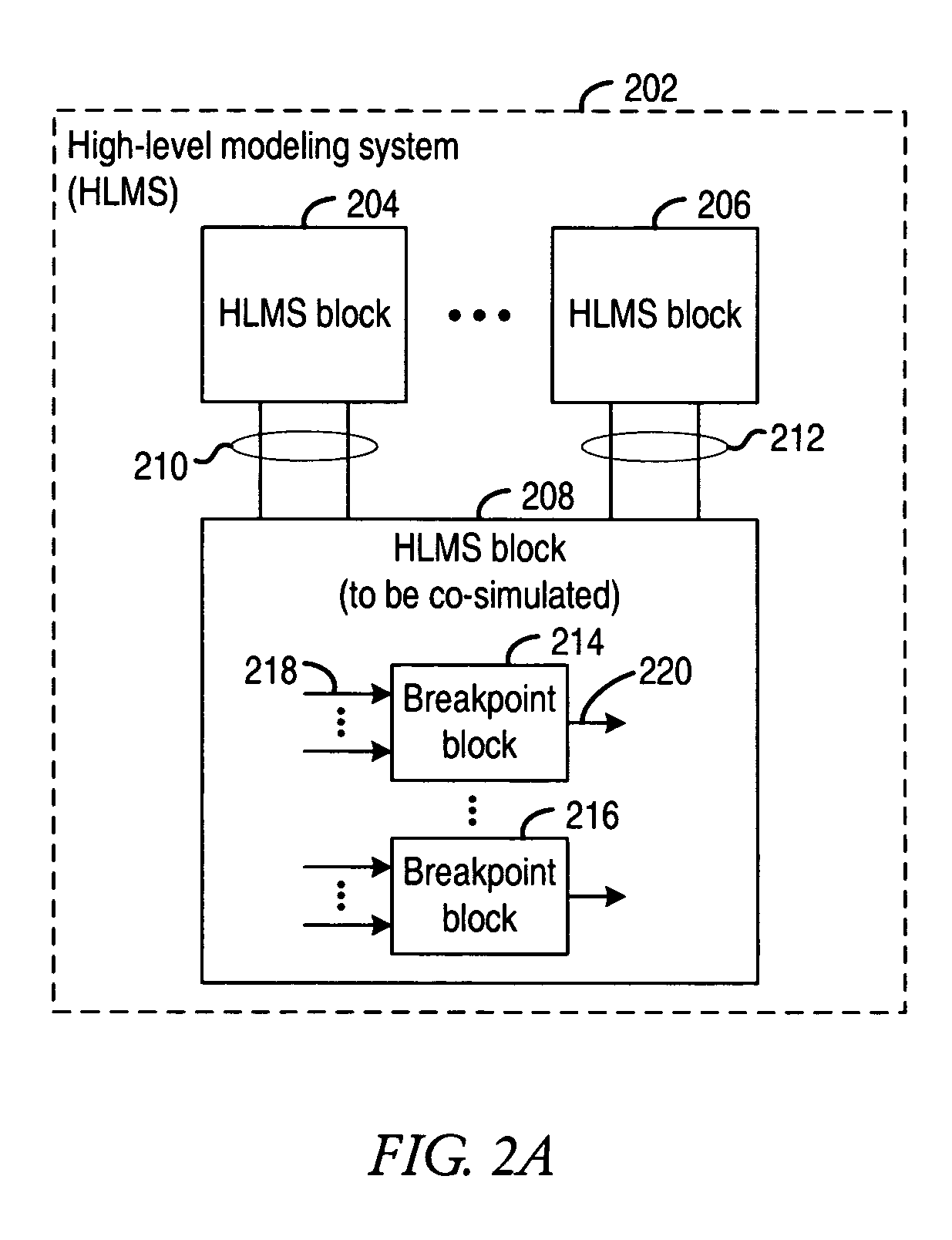

Hardware co-simulation breakpoints in a high-level modeling system

ActiveUS7346481B1Design optimisation/simulationCAD circuit designElectronic systemsHigh level modeling

Various approaches for controlling simulation of an electronic system are disclosed. In one approach, at least one breakpoint block is instantiated in a high-level design. The breakpoint block has an associated breakpoint condition driven by at least one signal of the design, and the design further includes at least one simulation block and at least one co-simulation block. The simulation block is simulated on a software-based simulation platform, and the co-simulation block and the breakpoint block are co-simulated on a hardware-based co-simulation platform. Advancement of a clock signal to the co-simulation block on the hardware-based co-simulation platform is inhibited in response to satisfaction of the breakpoint condition. After inhibiting the clock signal, advancement of steps of the clock signal is controlled on the co-simulation platform in one of a plurality of user-selectable clock advancement modes.

Owner:XILINX INC

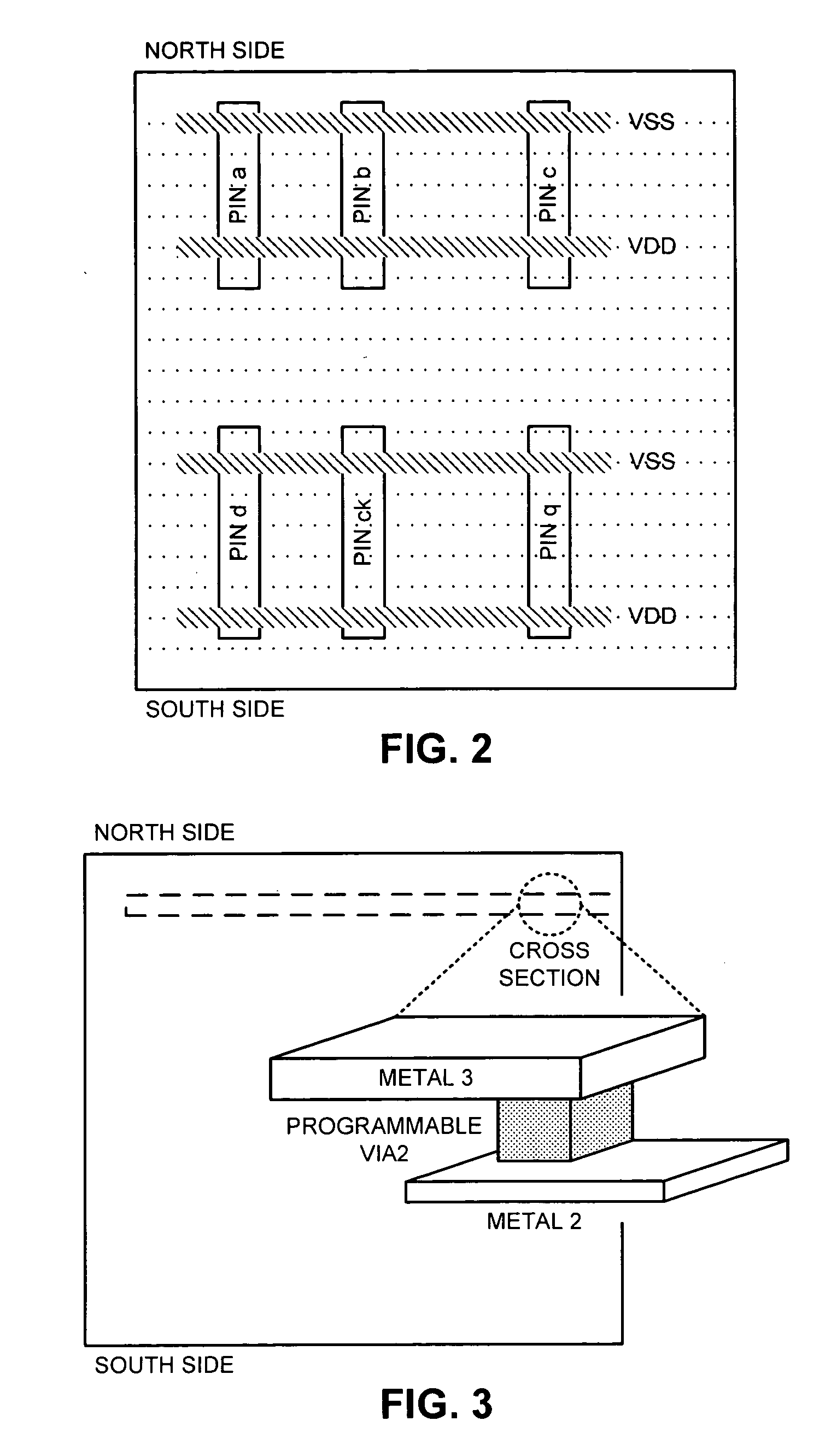

Method and apparatus for designing a circuit by describing logic design information with a hardware description language

InactiveUS6086625AEasy positioningImprove packaging efficiencyCAD circuit designProgram controlComputer architectureView based

A circuit design method and a circuit design apparatus of this invention allow a judgement from a broader view based on high-level design information inputted upon a logic design to determine a rough packaging design. A rough placement position of a function block cell, which can configure a circuit that is an object of the design, unit on a circuit is determined on the basis of abstract circuit information in an abstract level higher than that of packaging design basic cell obtained in a logic design. On the basis of the rough placement position and the abstract circuit information, the function block cell is two-dimensionally developed into the packaging design basic cell, and a packaging design of the circuit that is an object of the design is performed. The method and apparatus of this invention is applicable to a design of a circuit such as an LSI, a PWB, etc.

Owner:FUJITSU LTD

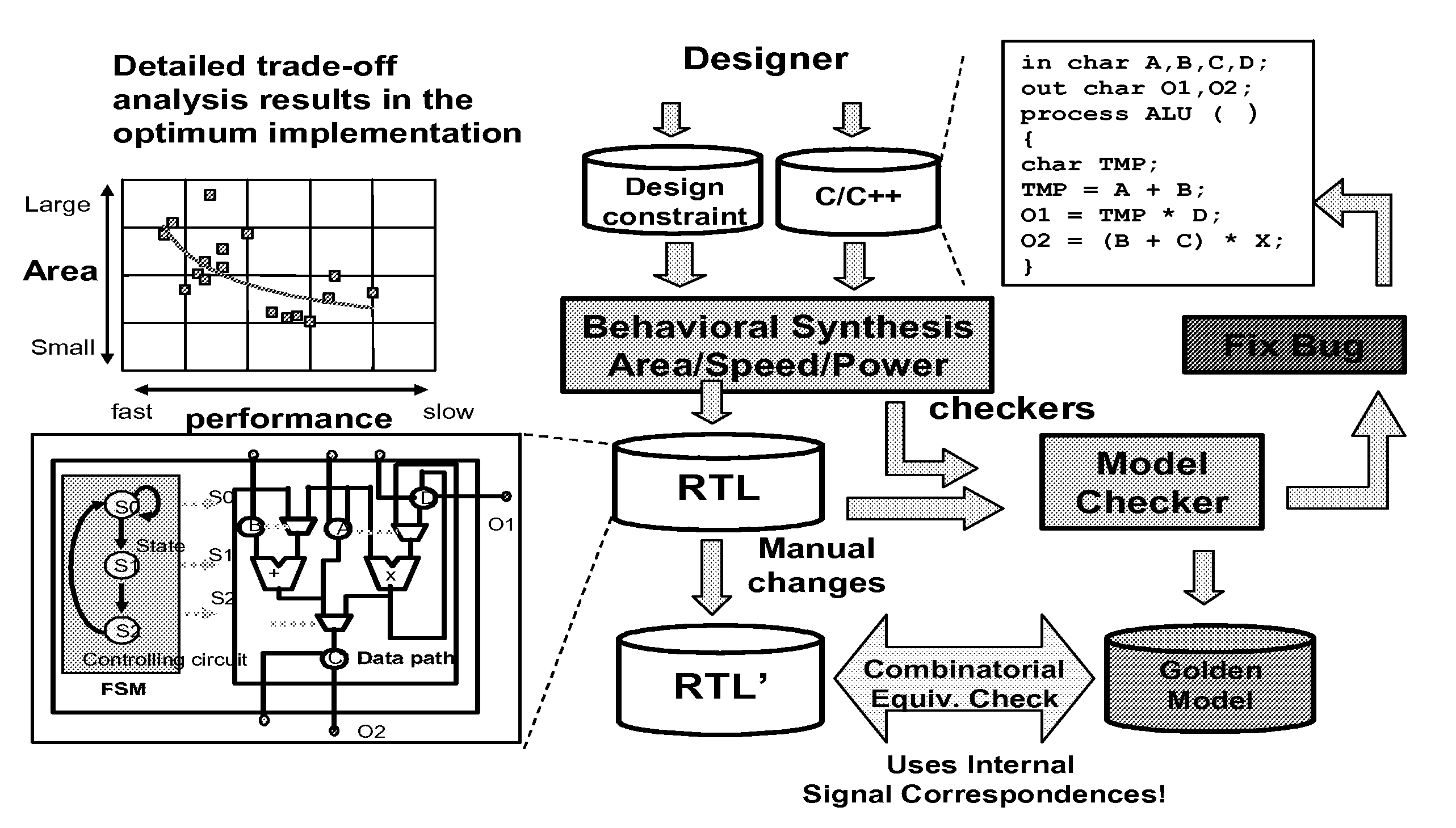

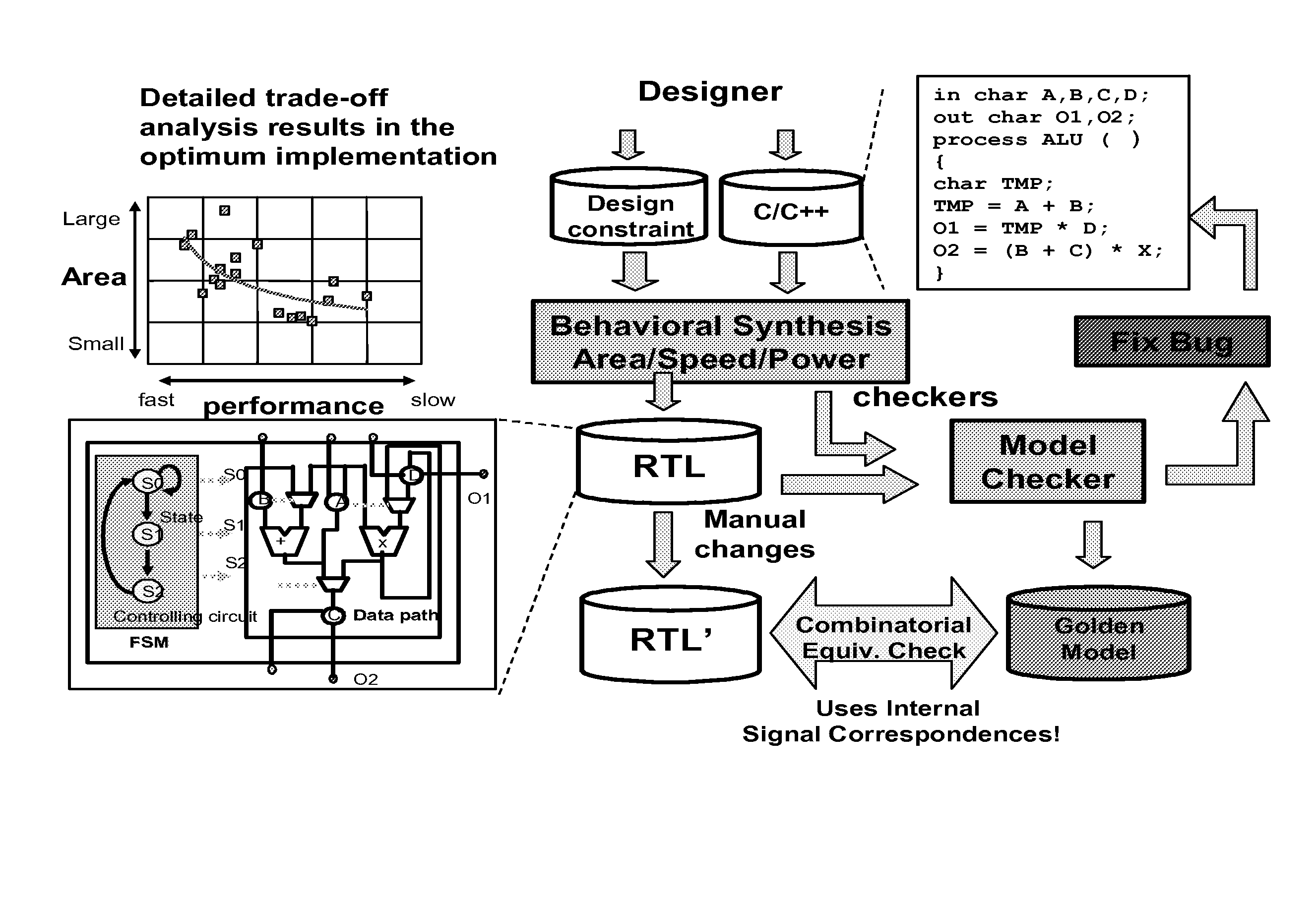

High-level synthesis for efficient verification

InactiveUS20070226666A1Use minimizedLimiting stepComputer aided designSoftware simulation/interpretation/emulationGuidelineExternal storage

Verification friendly models for SAT-based formal verification are generated from a given high-level design wherein during construction the following guidelines are enforced: 1) No re-use of functional units and registers; 2) Minimize the use of muxes and sharing; 3) Reduce the number of control steps; 4) Avoid pipelines; 5) Chose functional units from “verification friendly” library; 6) Re-use operations; 7) Perform property-preserving slicing; 8) Support “assume” and “assert” in the language specification; and 8) Use external memory modules instead of register arrays.

Owner:NEC CORP

Method and apparatus for power consumption analysis in global nets

InactiveUS7007256B2CAD circuit designSoftware simulation/interpretation/emulationTime domainEngineering

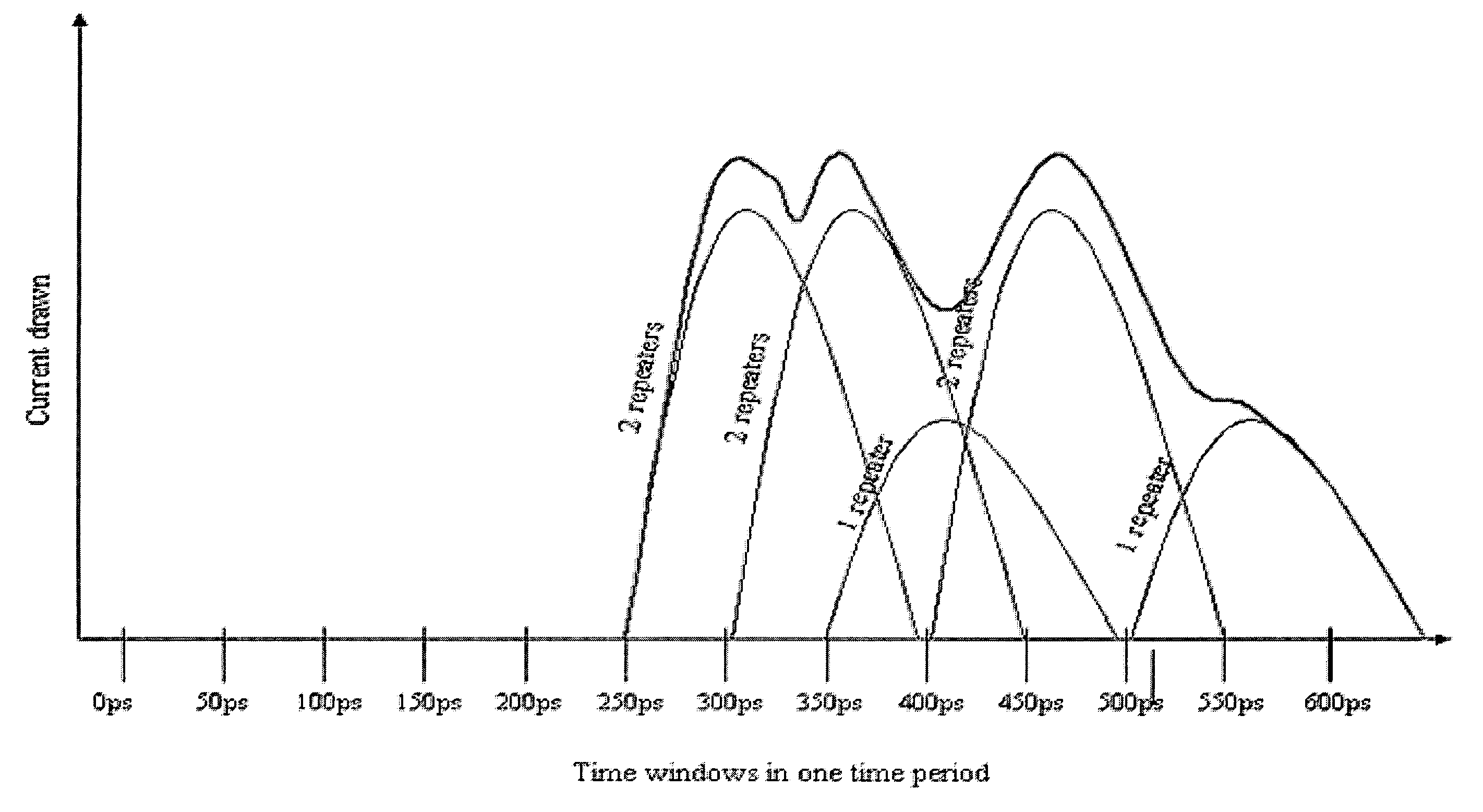

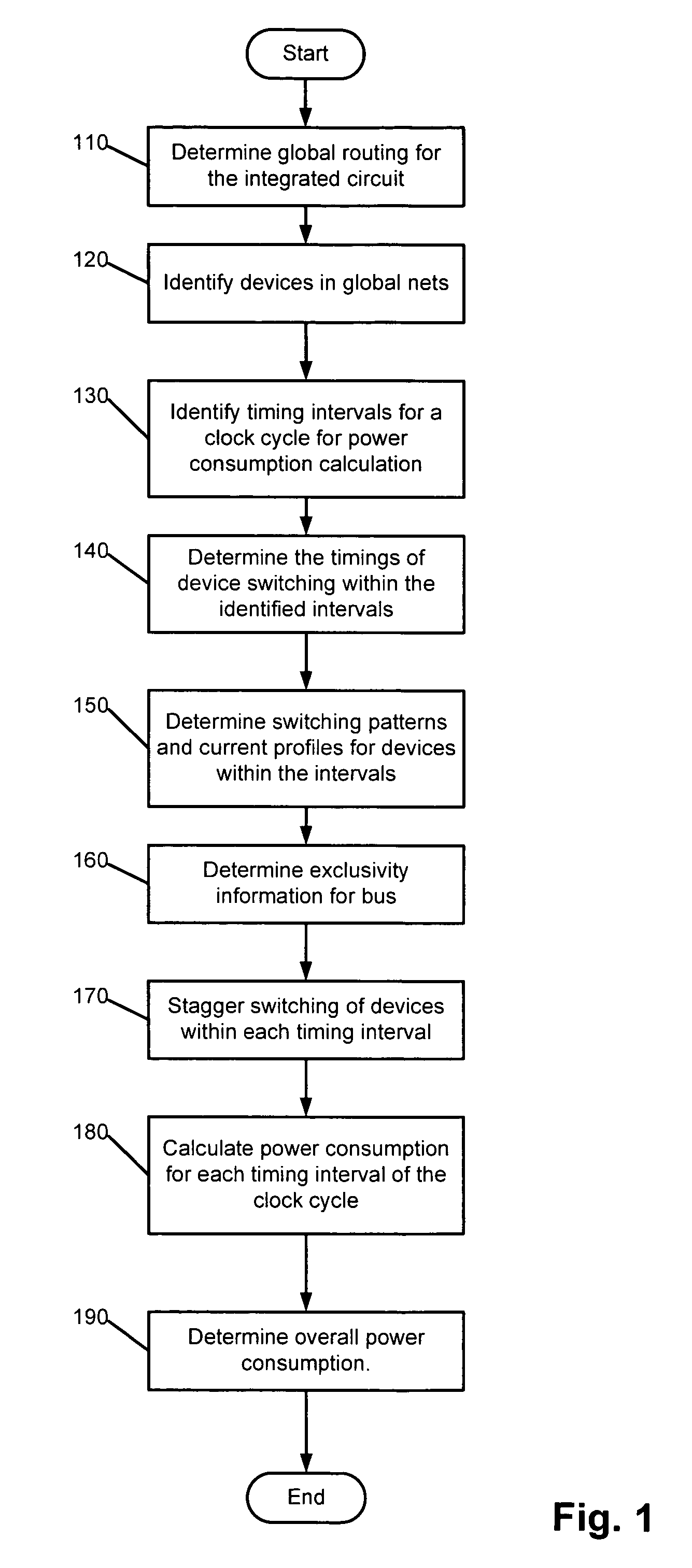

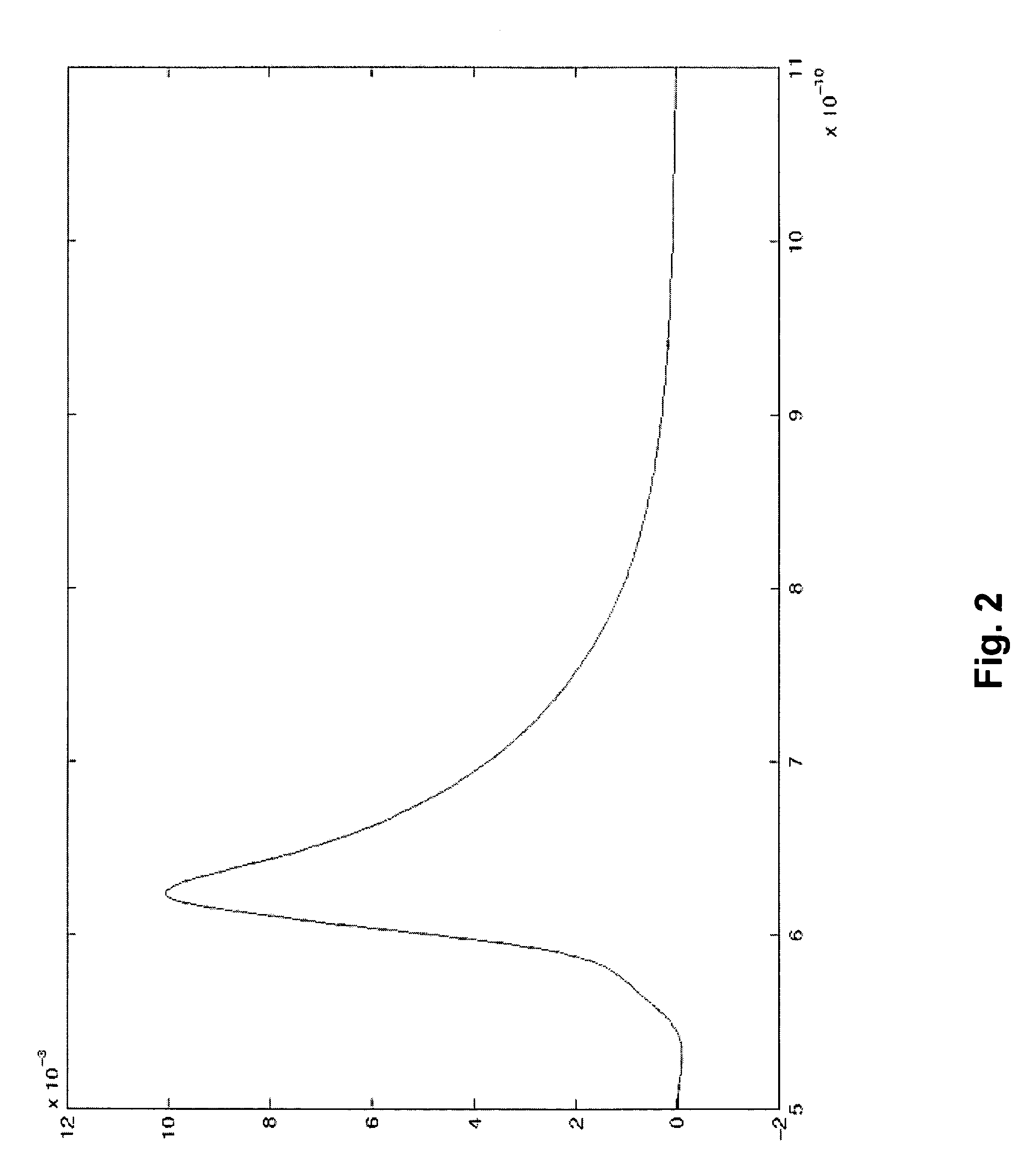

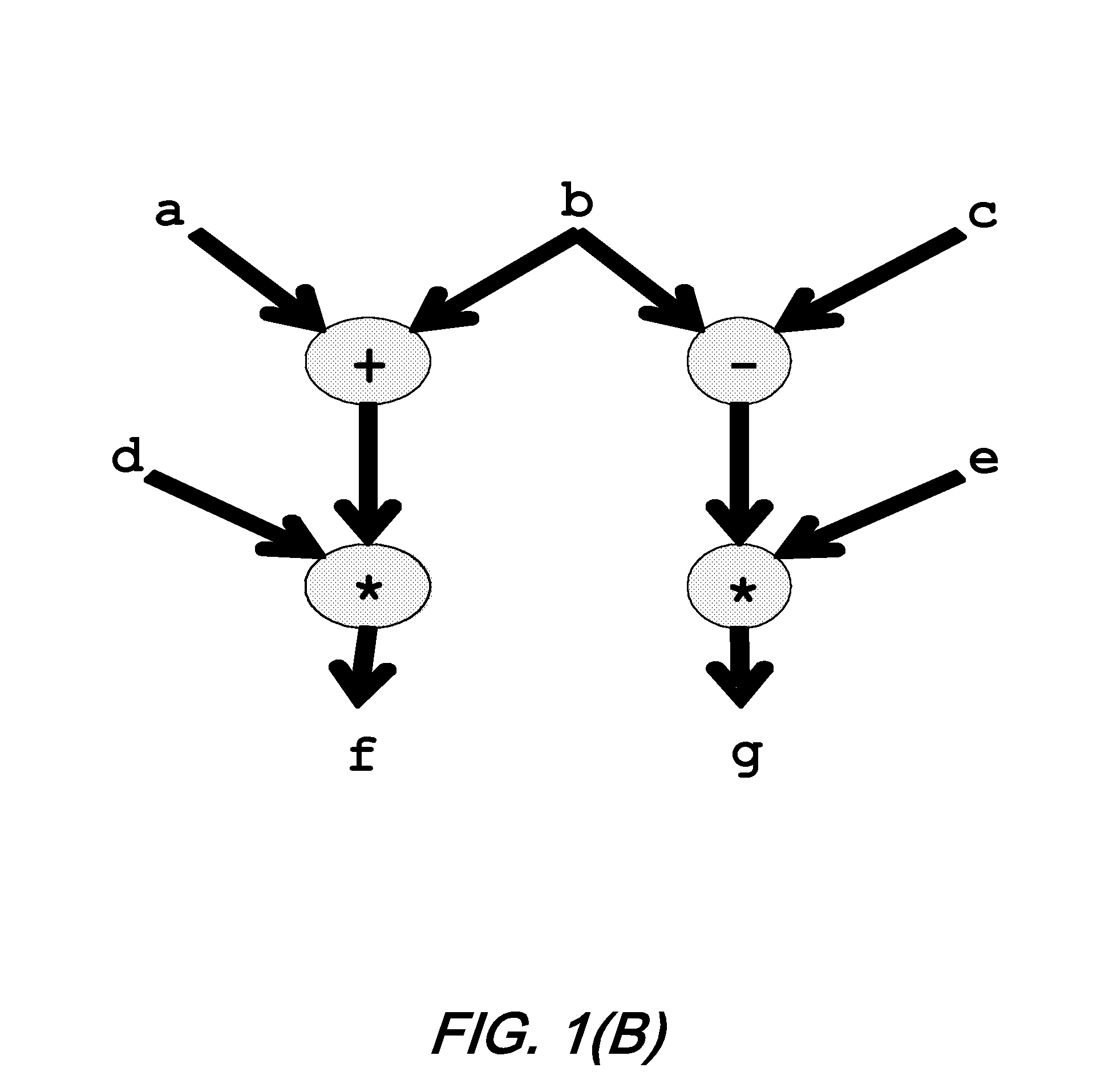

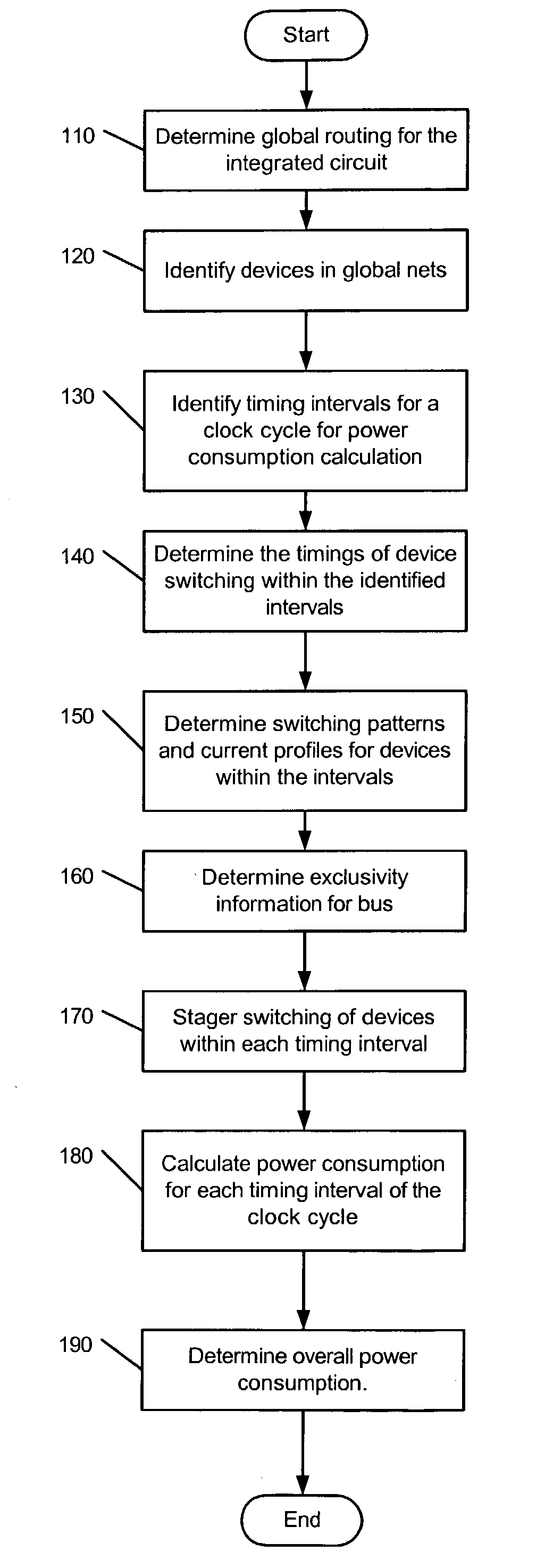

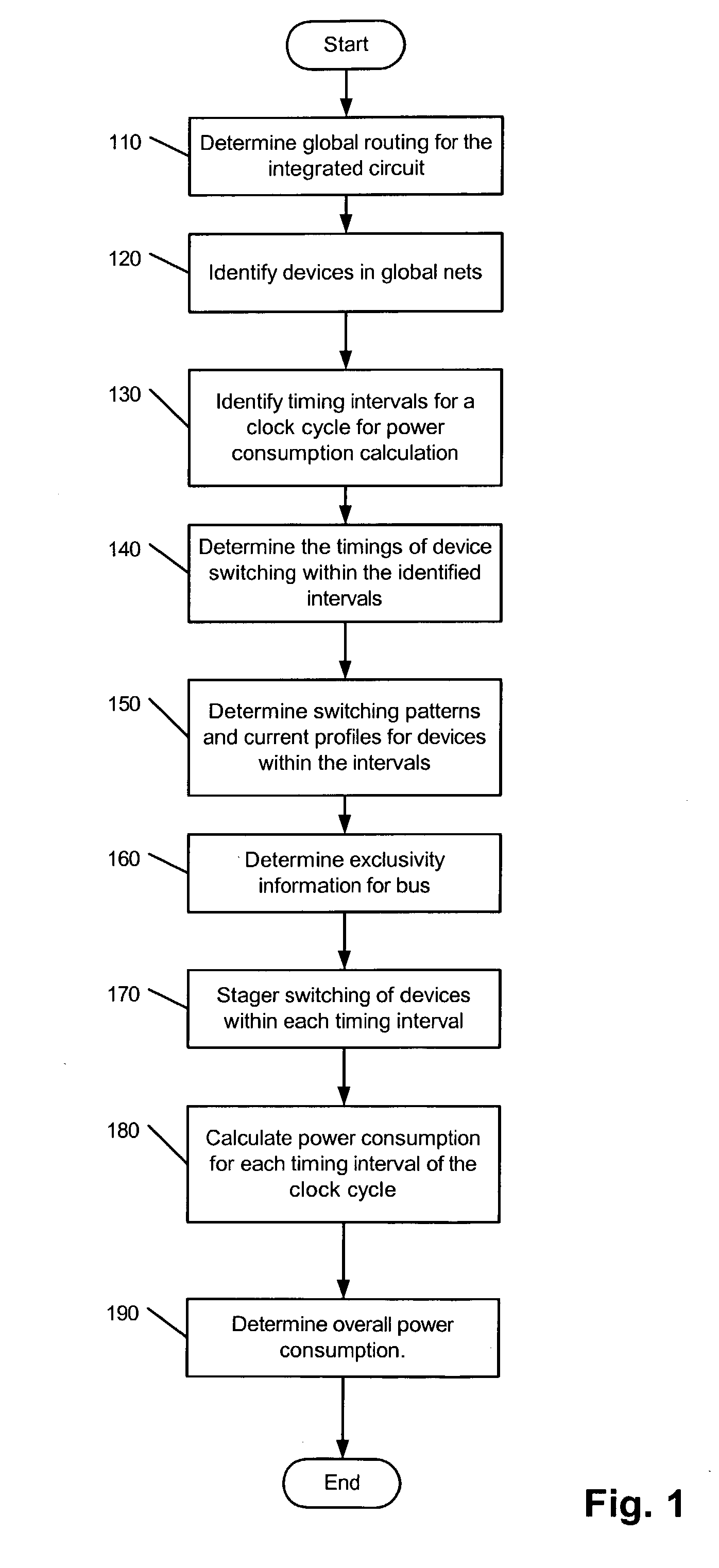

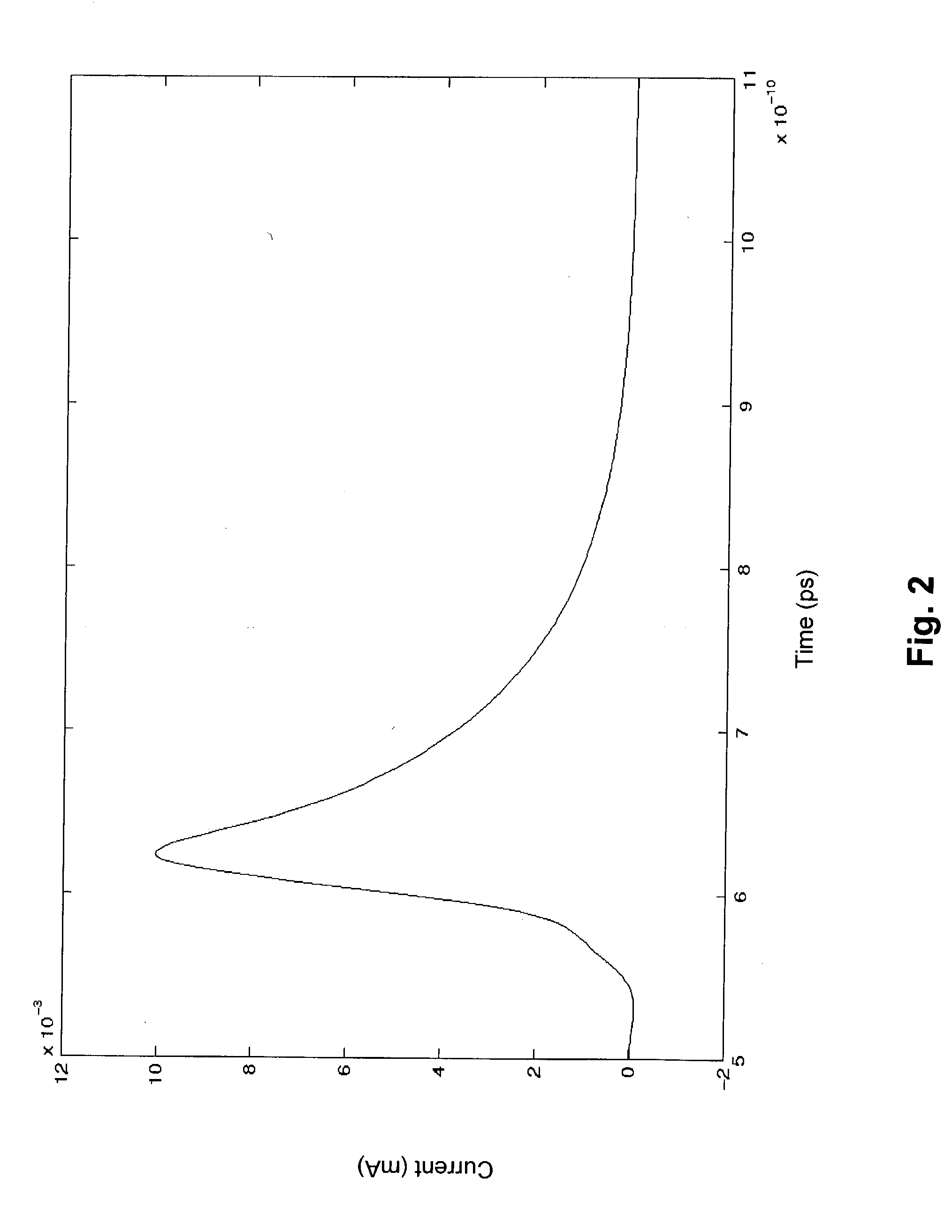

The present invention describes a method and an apparatus for determining switching power consumption of global devices (e.g., repeaters, flops or the like) in an integrated circuit design during high-level design phase after the global routing for the integrated circuit is available. The clock cycle is divided into various timing intervals and the timing reports are generated for each cycle to determine a time-domain staggered distribution of each device's switching activity within a given timing interval. Each device's switching activity is analyzed within the given timing interval (or segment thereof). The power consumption is determined for each device that switches in the given timing interval.

Owner:ORACLE INT CORP

System and method for automatically generating a hierarchical register consolidation structure

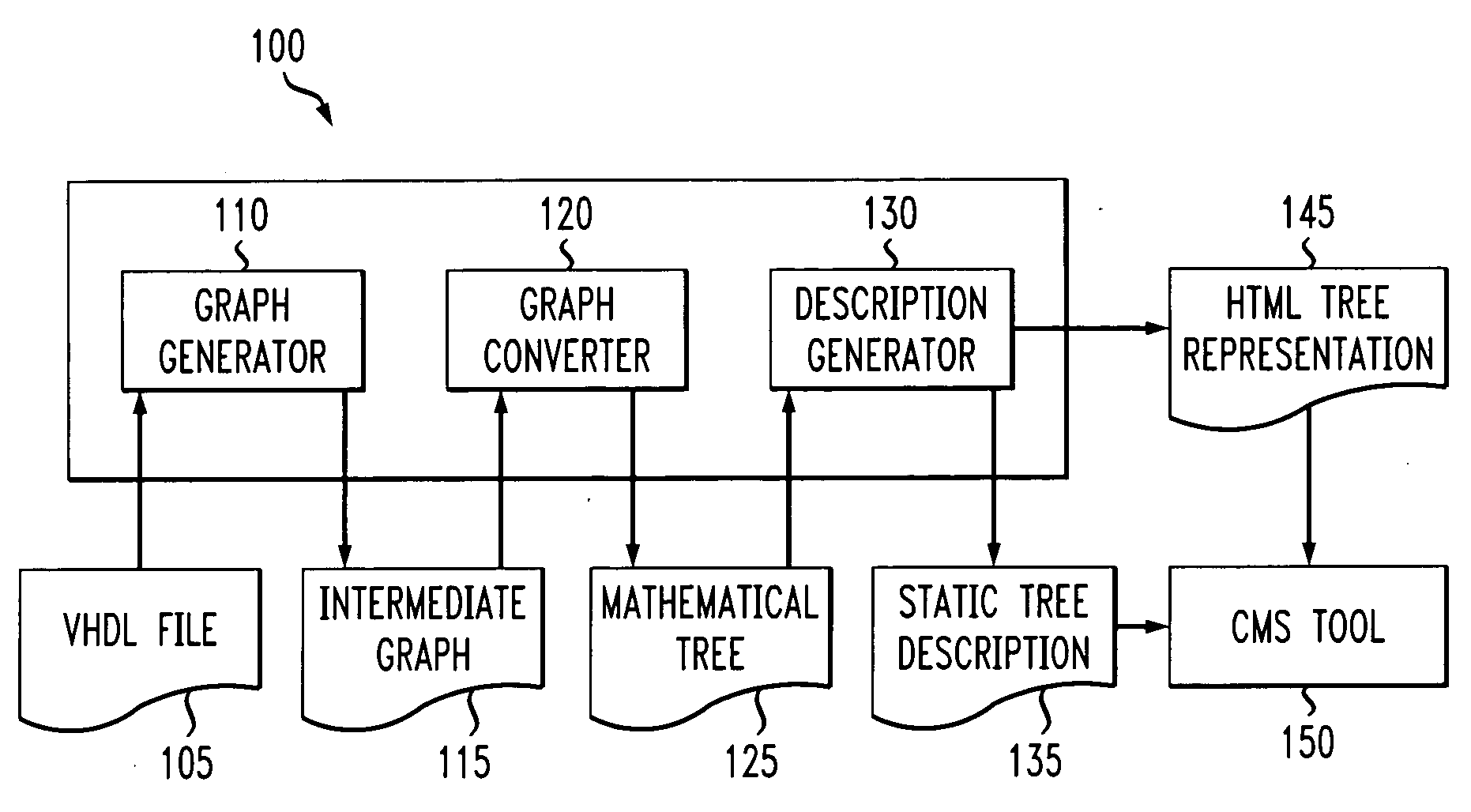

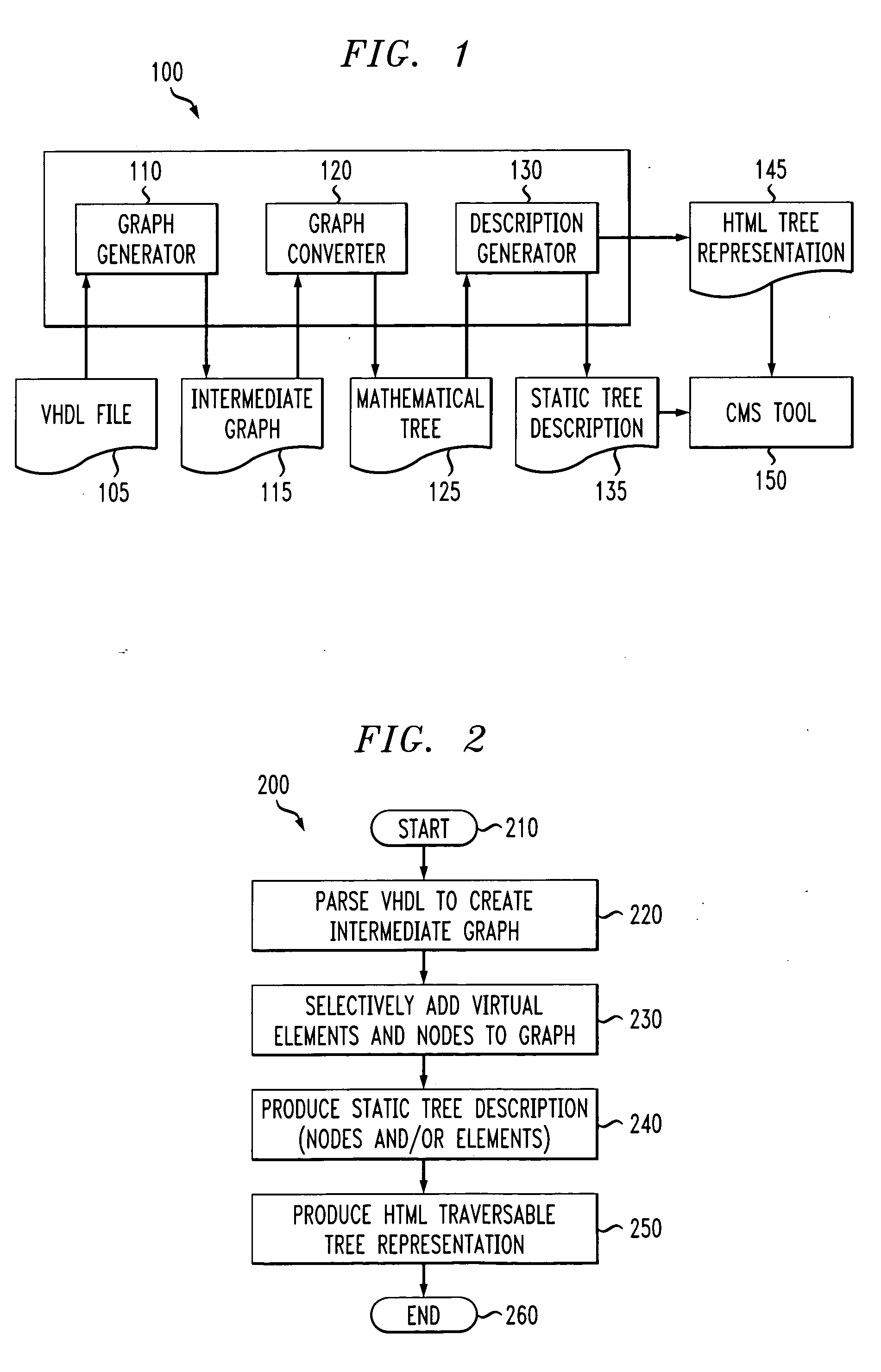

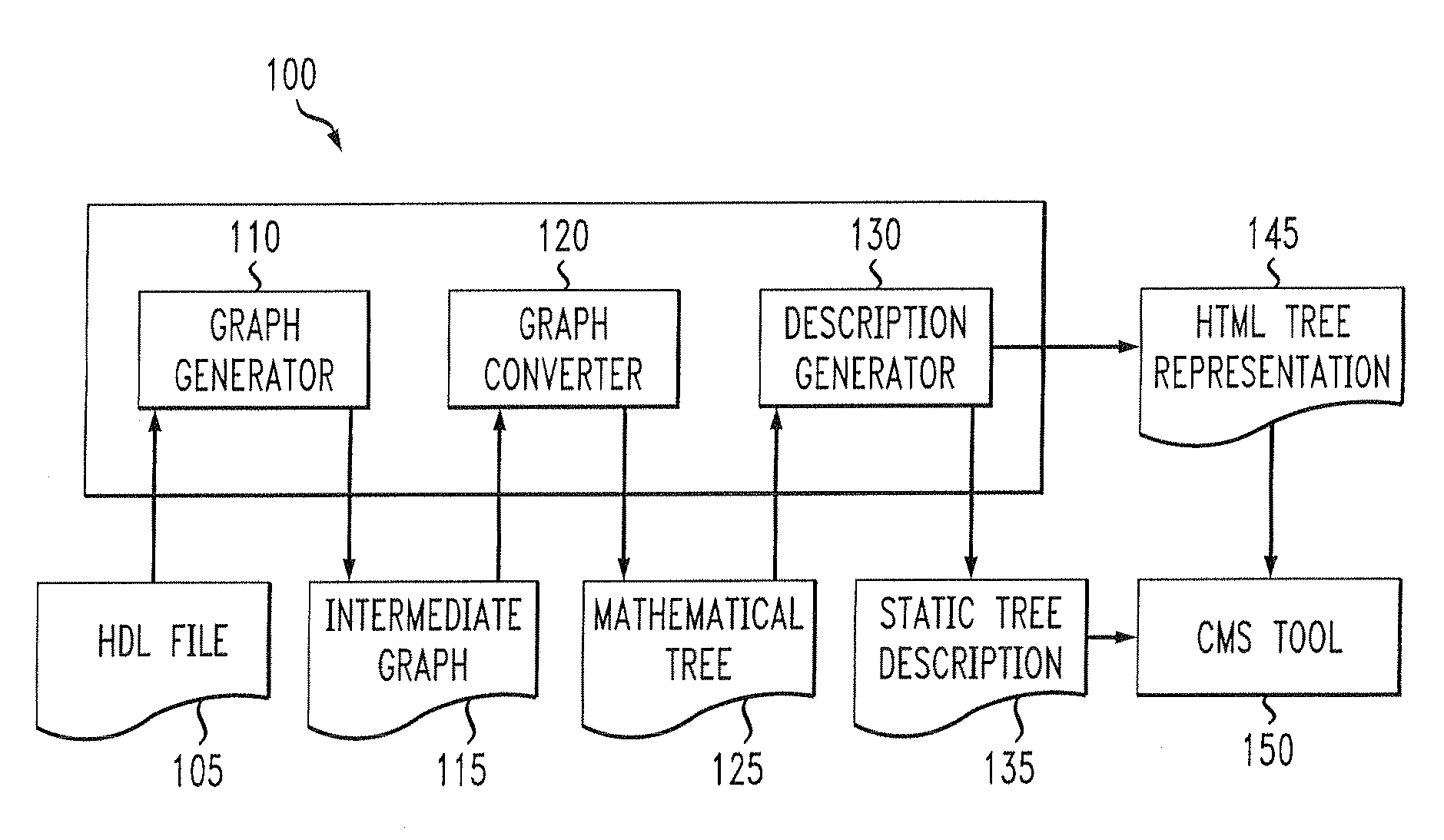

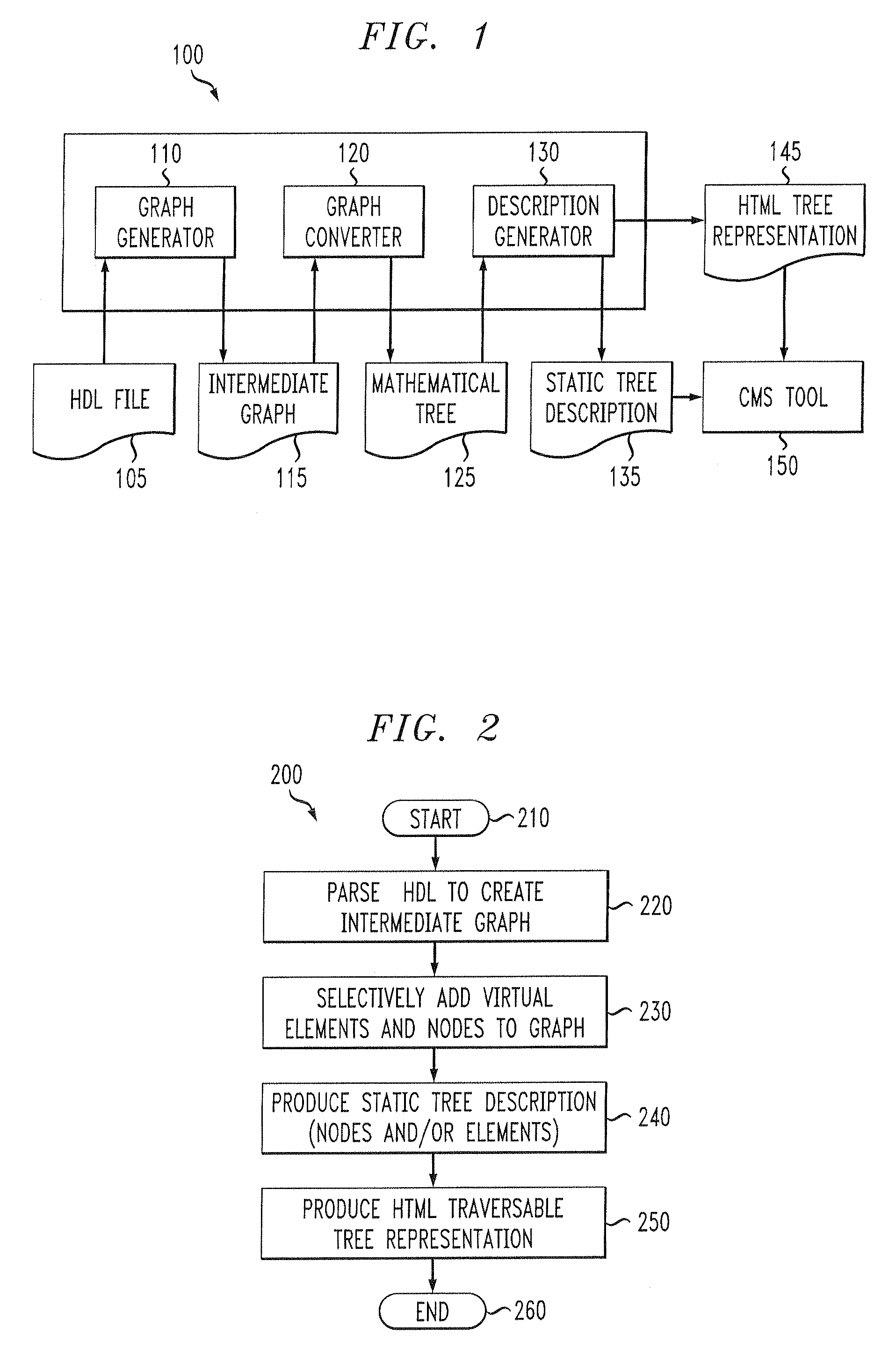

A system for, and method of, automatically generating a hierarchical register consolidation structure. In one embodiment, the system includes: (1) a graph generator that parses a High-level Design Language (HDL) file to generate an intermediate graph containing definitions of microprocessor-accessible registers, node interrelationships and summary bits and masks associated with alarm registers, (2) a graph converter, associated with the graph generator, that selectively adds virtual elements and nodes to the intermediate graph to transform the intermediate graph into a mathematical tree and (3) a description generator, associated with the graph converter, that employs the mathematical tree to generate a static tree description in a programming language suitable for use by a device-independent condition management structure.

Owner:AVAGO TECH INT SALES PTE LTD

System and method for automatically generating a hierarchical register consolidation structure

Owner:AVAGO TECH INT SALES PTE LTD

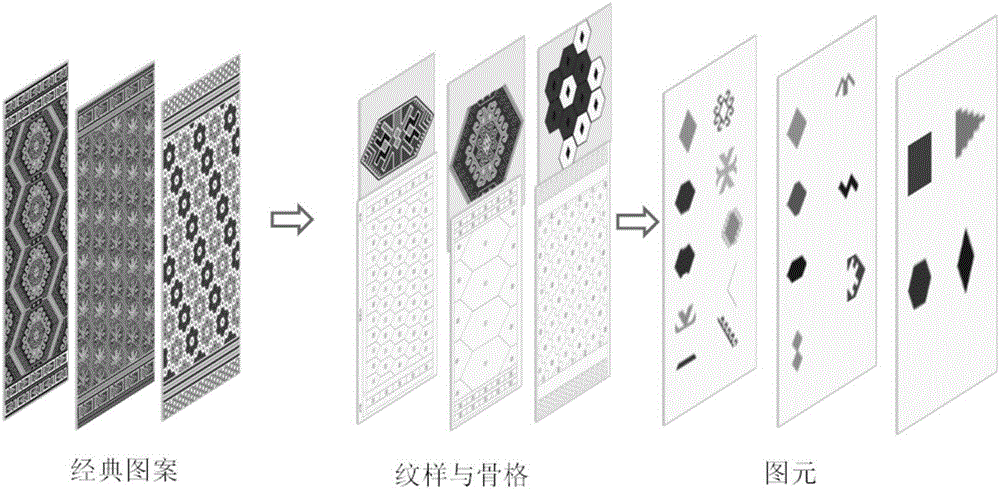

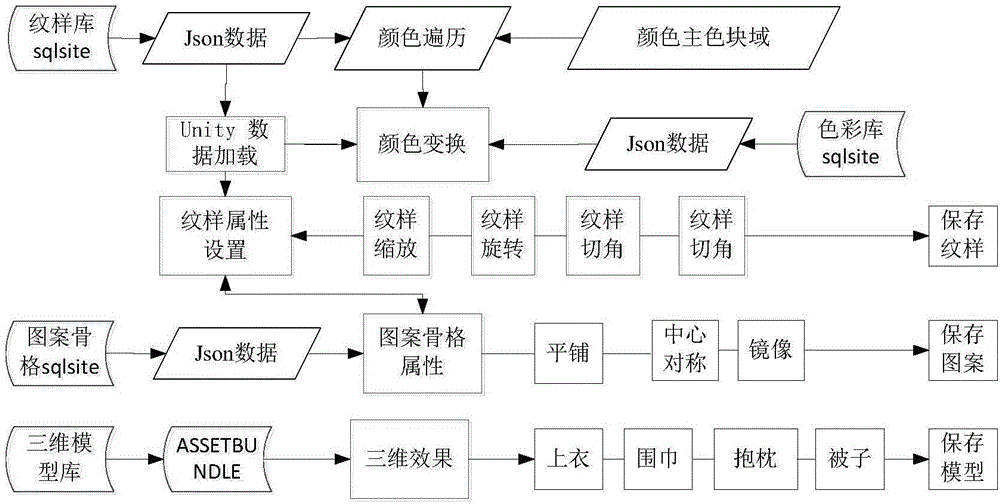

Unity 3D based Tujia brocade virtual design system

InactiveCN106709978ADesign optimisation/simulationSpecial data processing applicationsComputer moduleHigh-level design

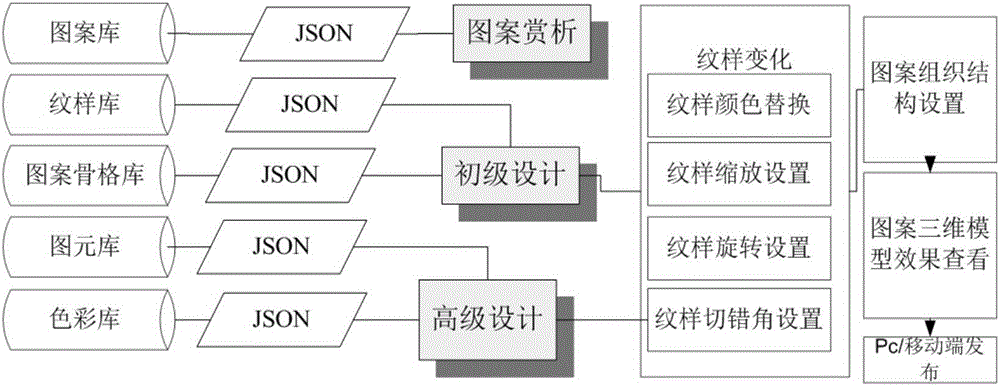

The invention discloses a Unity 3D based Tujia brocade virtual design system, which comprises basic resource libraries, a pattern appreciating and analyzing module, a primary design module and an advanced design module. According to the invention, digital processing and organizational structure segmentation are performed on classic works of Tujia brocade so as to form the basic resource libraries including a pattern library, a texture library, a color library, a pattern skeleton library and a primitive library; a user appreciates a series of classic Tujia brocade patterns, and then can perform primary design and advanced design after appreciating and analyzing the prior knowledge, textures and primitives in the basis resource libraries are called in innovative design in a virtual design system, and color replacement, rotation, scaling and tangential angle and alternate angle transformation are performed; a warp / weft ratio is set according to the pattern skeleton structure; and an innovative pattern is applied to a three-dimensional model, and a design result visualization system releases four operating environments such as Windows, Iphone, WebGL and Android by using a Unity 3D platform.

Owner:HUAZHONG NORMAL UNIV

Method and apparatus for designing an integrated circuit using a mask-programmable fabric

Owner:SYNOPSYS INC

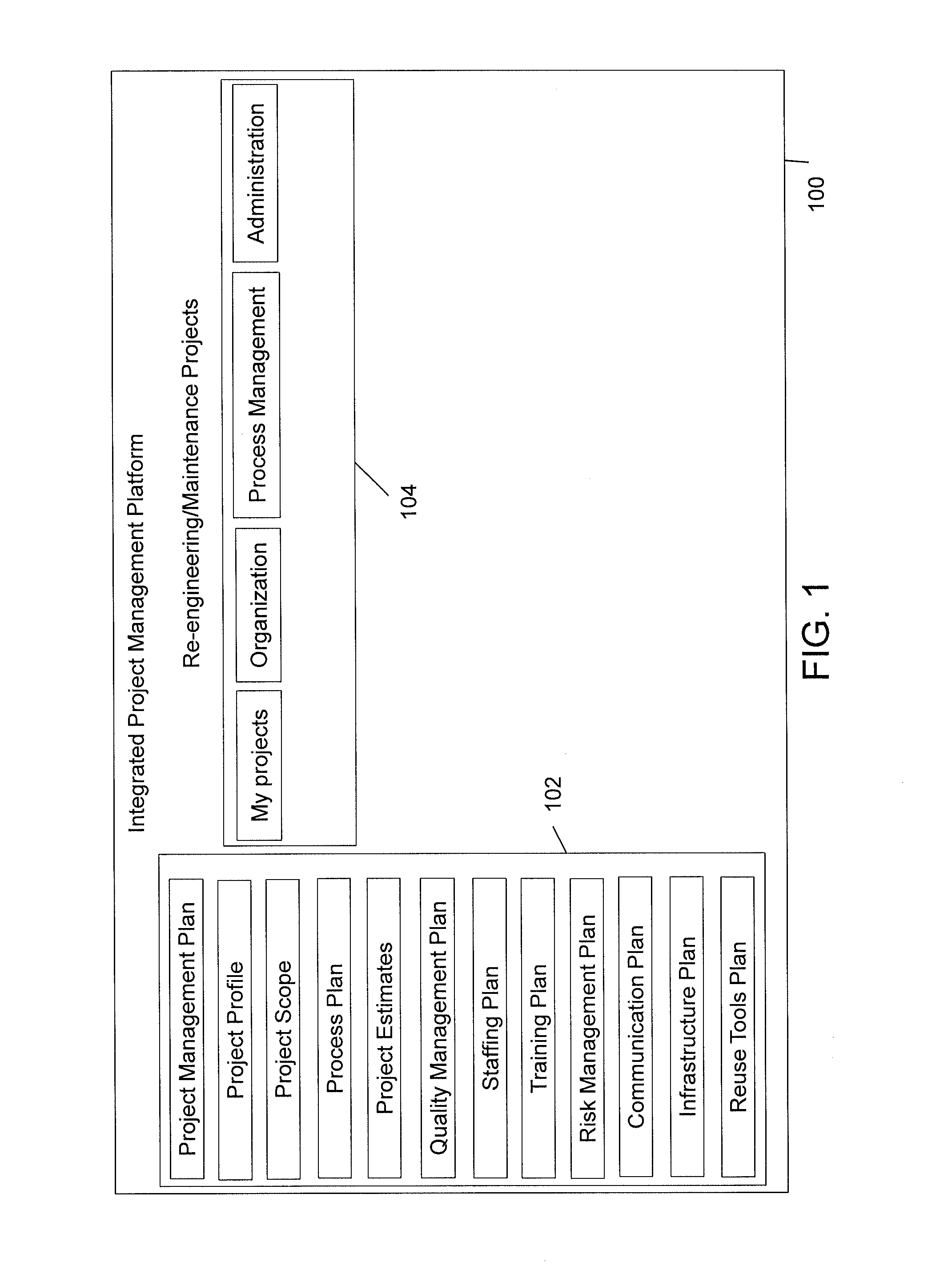

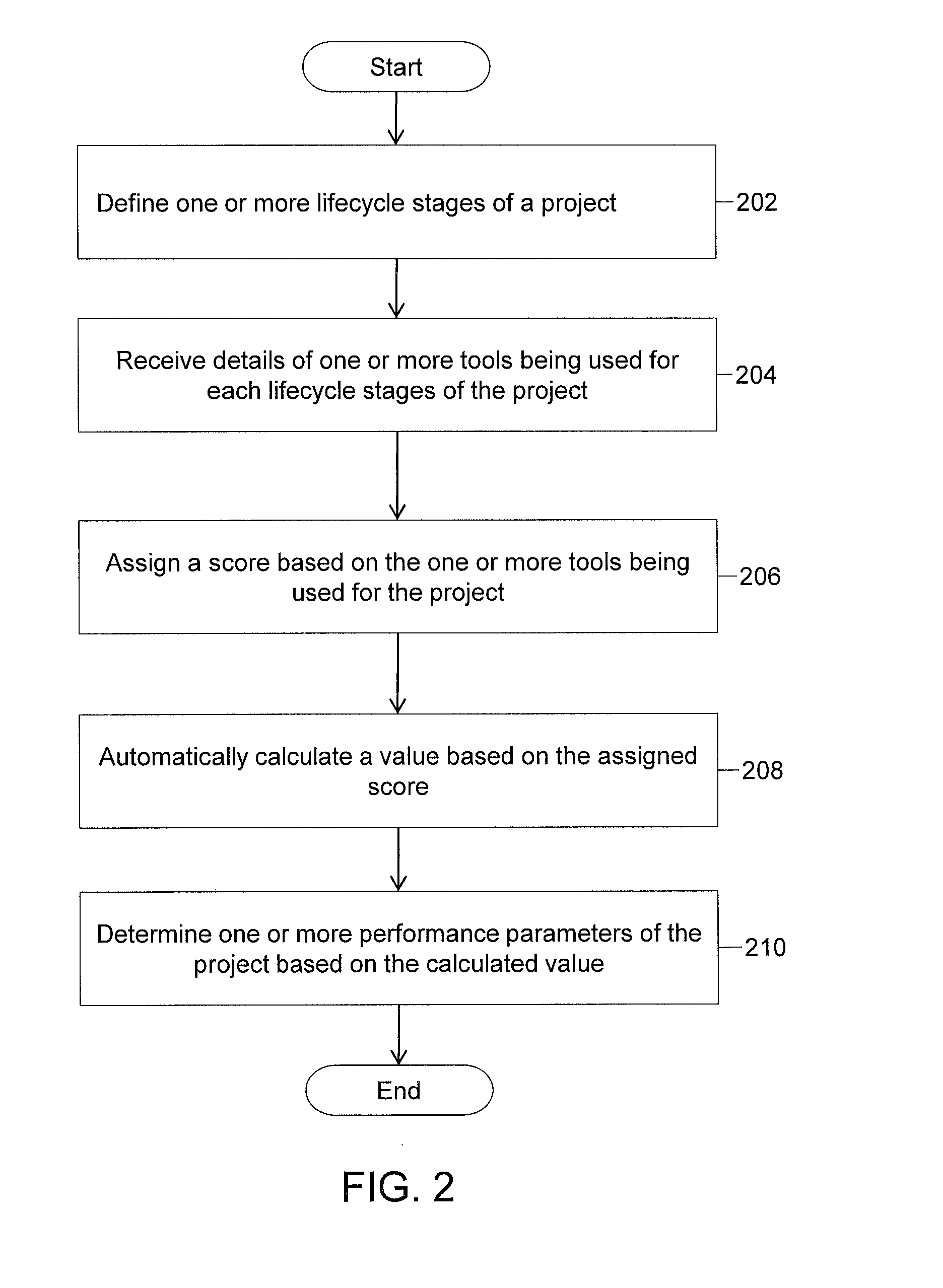

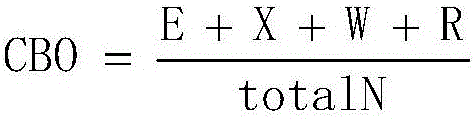

Method and system for determining performance parameters of software project based on software-engineering tools usage

A method and system have been disclosed for determining one or more performance parameters of a project. Various examples of the performance parameters of the project may include productivity, efficiency, and quality. The method described above includes defining one or more lifecycle stages of the project. Examples of the lifecycle stages of the project may include requirement analysis, high-level design, detailed design, build, integration test, system test, documentation, acceptance, installation, and post implementation. Further, the method includes receiving details of one or more tools being used for each lifecycle stages of the project. The method further includes assigning a score based on the one or more tools being used for the project. Further, the method also includes automatically calculating a value based on the assigned score. Thereafter, the performance parameters of the project are determined based on the calculated value.

Owner:INFOSYS LTD

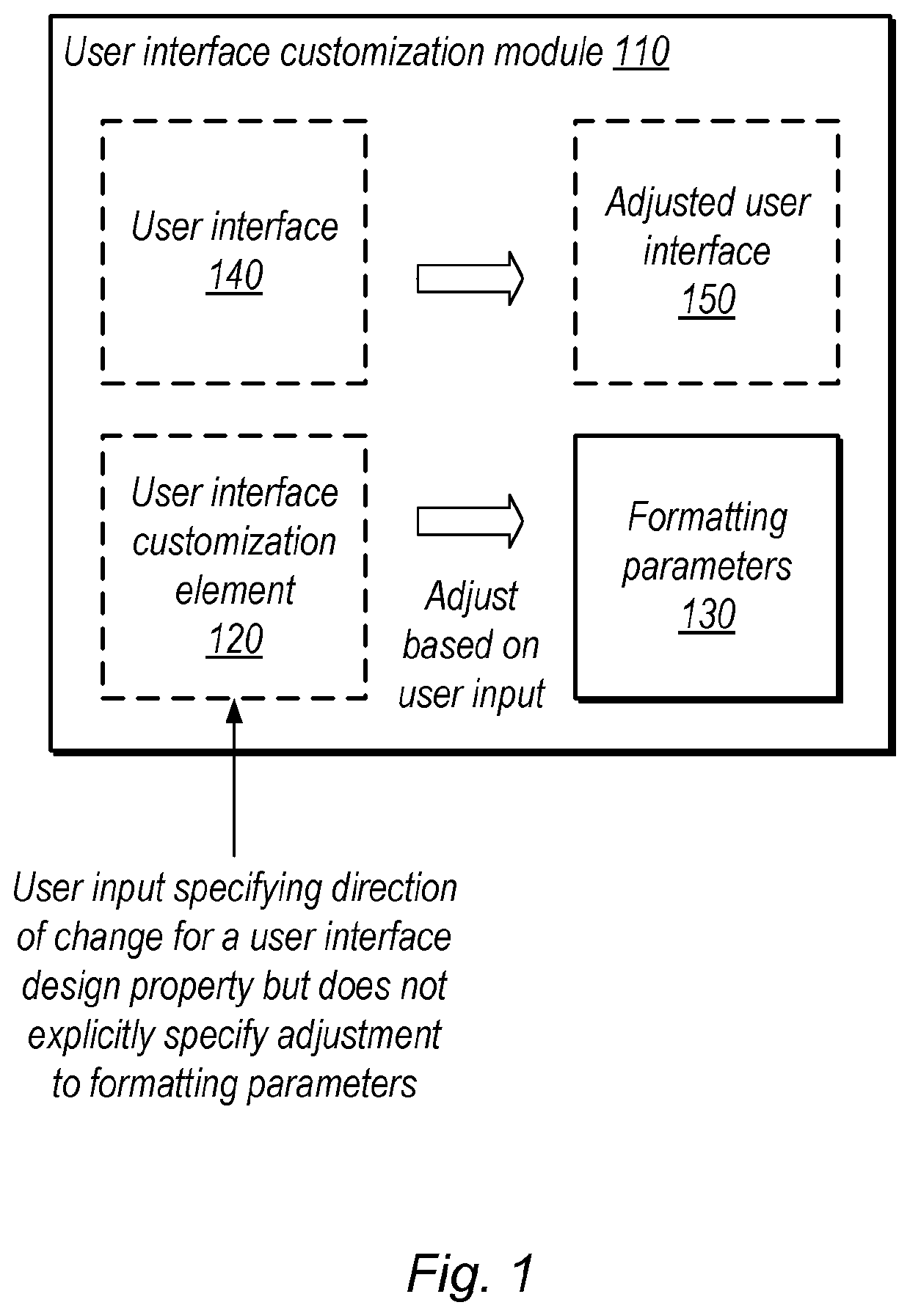

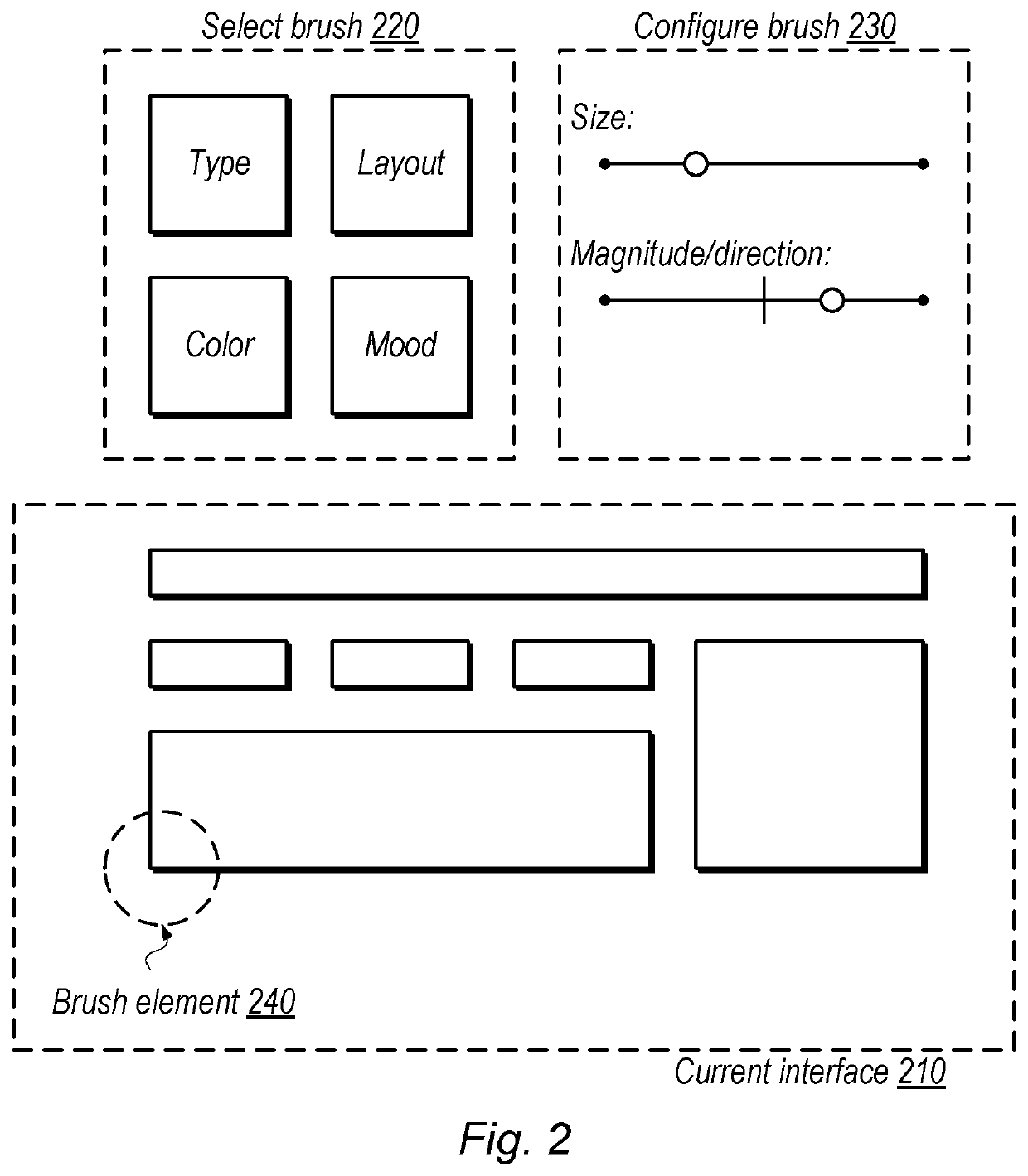

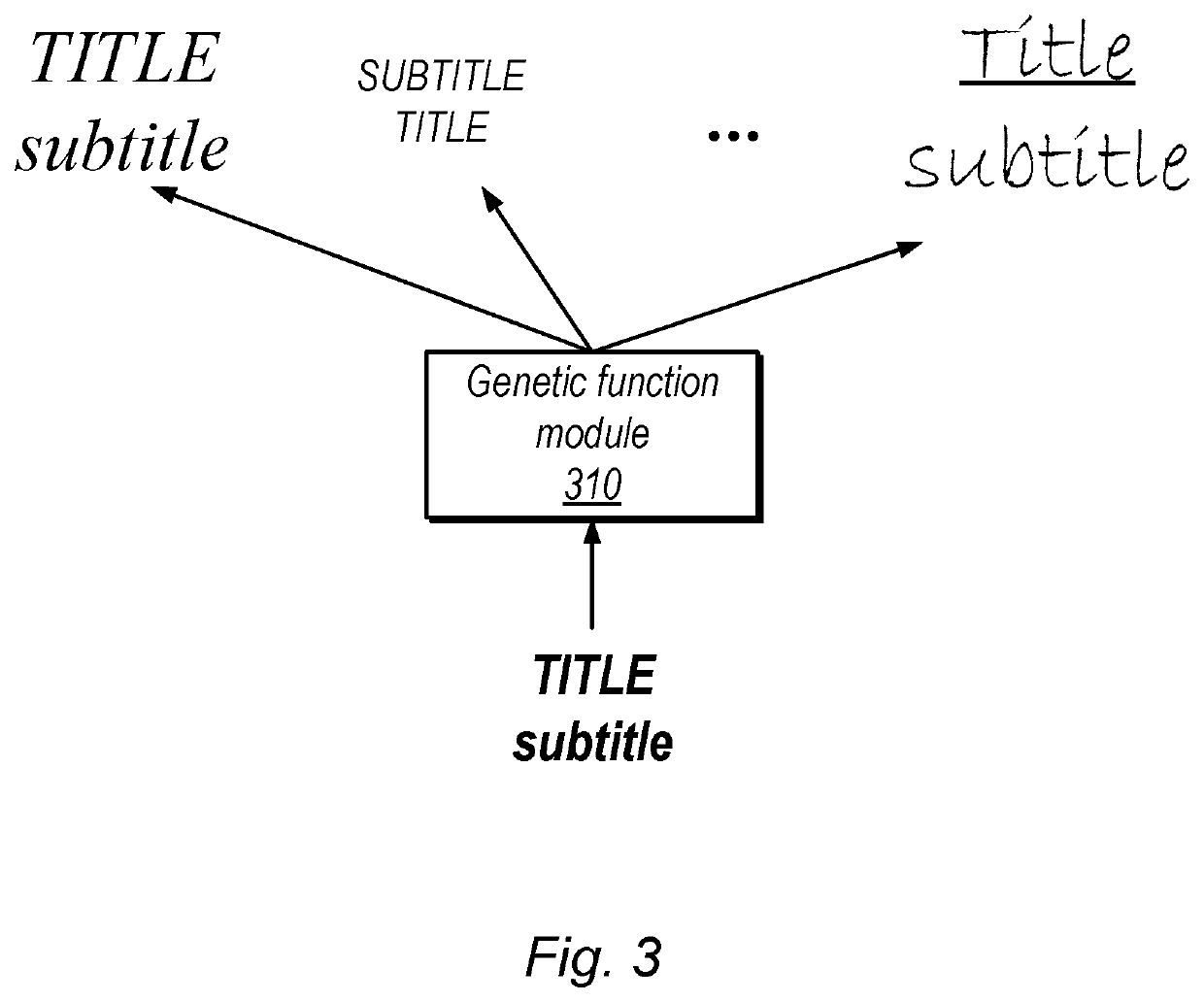

Design adjustment based on user-specified direction of change

Disclosed techniques relate to customization of user interface designs based on user input that specifies high-level design properties. In some embodiments, a system displays a user interface in a user interface customization program. In some embodiments, based on user input via a customization interface element that specifies a direction or change for a design property, the system performs an adjustment to formatting parameters for the user interface, where the user input does not explicitly specify the adjustment to the formatting parameters. The system may display an adjusted user interface that exhibits the adjusted formatting parameters.

Owner:SALESFORCE COM INC

Advanced design format library for integrated circuit design synthesis and floorplanning tools

InactiveUS20040230919A1CAD circuit designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit layout

An integrated circuit design library includes a timing parameter representative of a design element in an integrated circuit; an area size parameter representative of the design element in an integrated circuit; and a routing demand parameter representative of a number of connections required for the design element for each value of the timing parameter and the area size parameter.

Owner:BELL SEMICON LLC

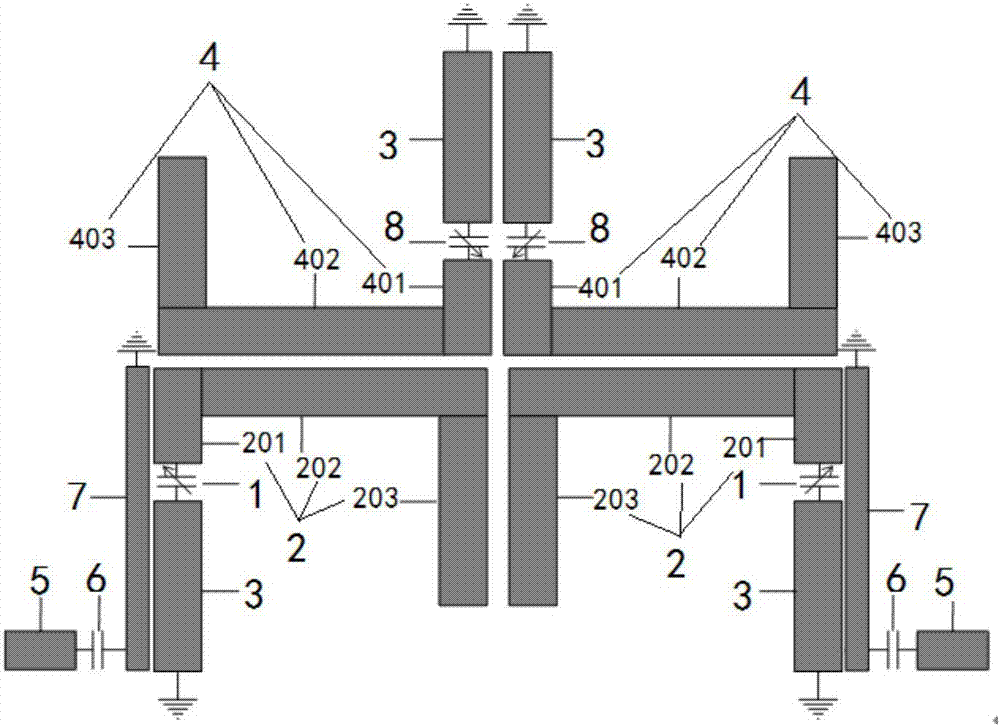

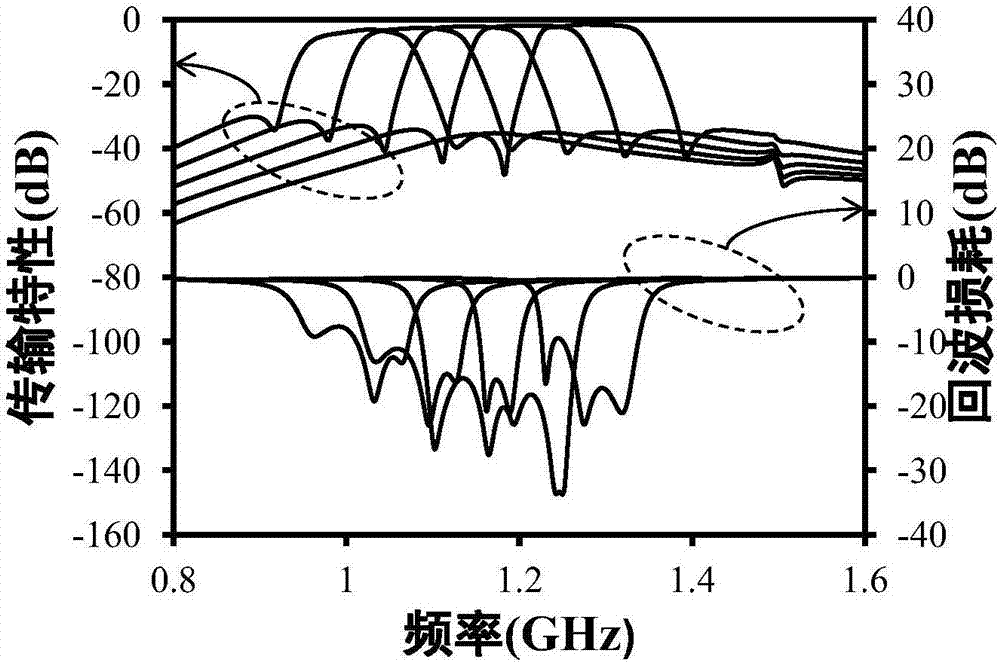

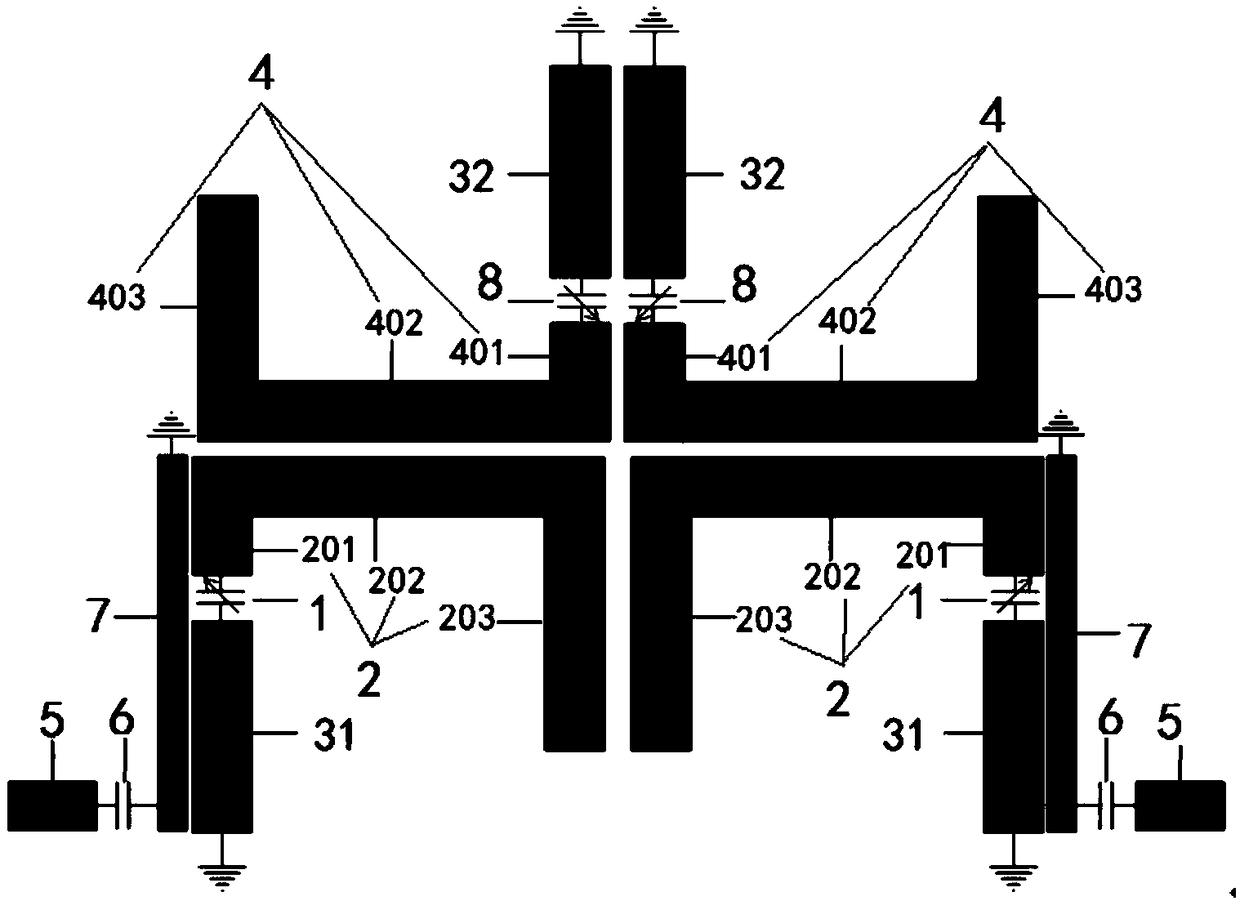

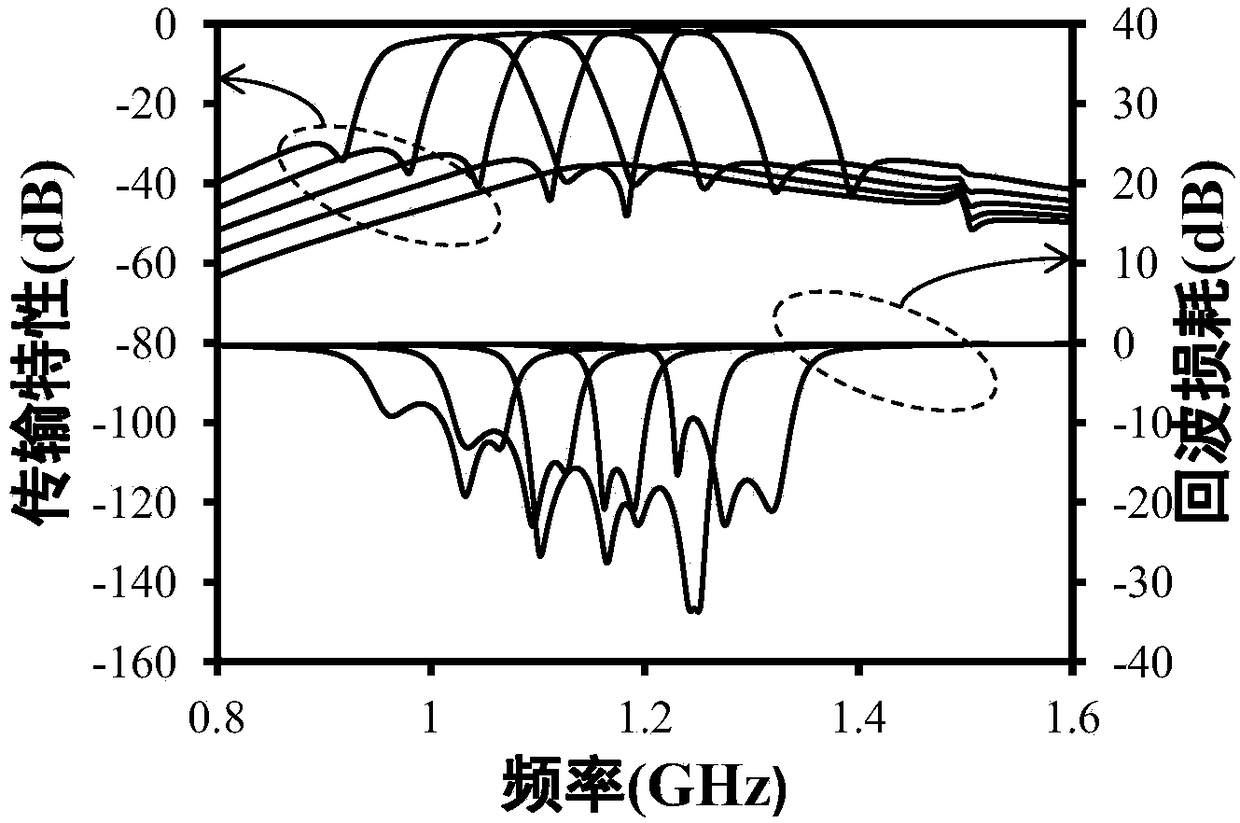

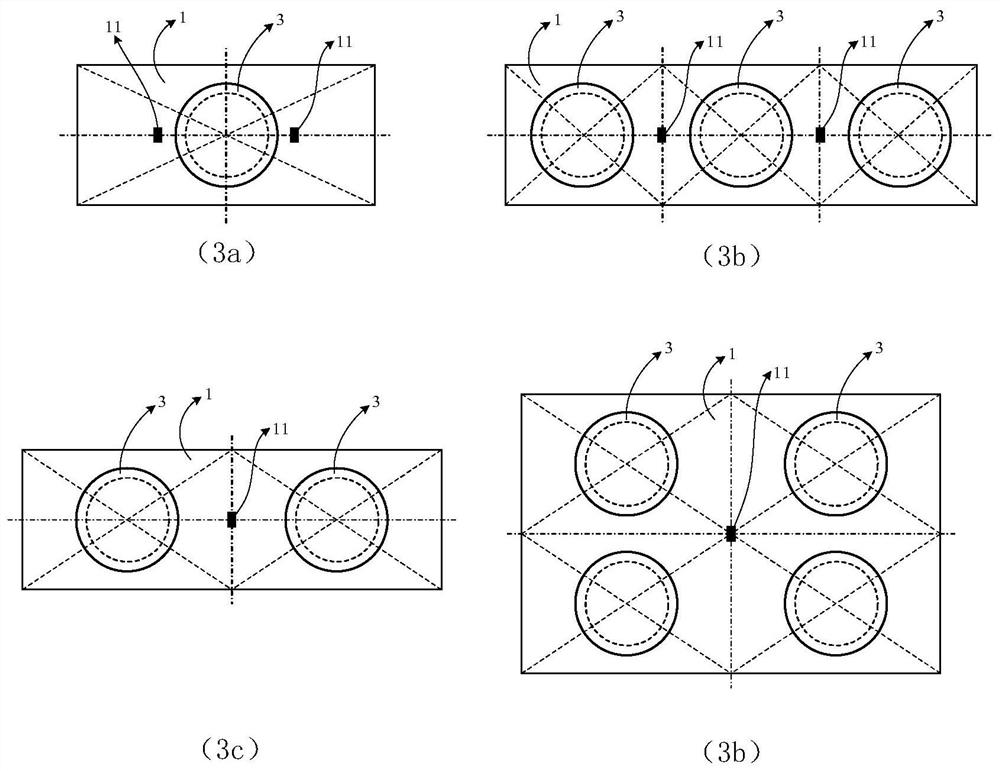

Cross-coupled structure-based high-order adjustable band-pass filter

ActiveCN106972227AImprove frequency selectivityEasy to adjustWaveguide type devicesDielectric substrateEngineering

The present invention discloses a cross-coupled structure-based high-order adjustable band-pass filter and belongs to the radio frequency device field. The cross-coupled structure-based high-order adjustable band-pass filter of the present invention comprises a dielectric substrate; the top surface of the dielectric substrate is provided with a metal microstrip structure; the bottom surface of the dielectric substrate is provided with a metal grounding plate; and the metal microstrip structure includes two feed lines which are in bilateral symmetry and four tunable resonators which are arranged between the two feed lines. Based on reasonable design structure, the four-order tunable band-pass filter has a constant absolute bandwidth. According to the filter, symmetrical transmission zero points are realized based on a cross-coupled structure, so that the selectivity of frequencies can be effectively improved; the insertion loss of an adjustment range can be effectively decreased; and high attenuation characteristics within stop bands can be realized. The cross-coupled structure-based high-order adjustable band-pass filter provided by the invention is applied to high-level design and is of practical significance.

Owner:SOUTHWEST JIAOTONG UNIV

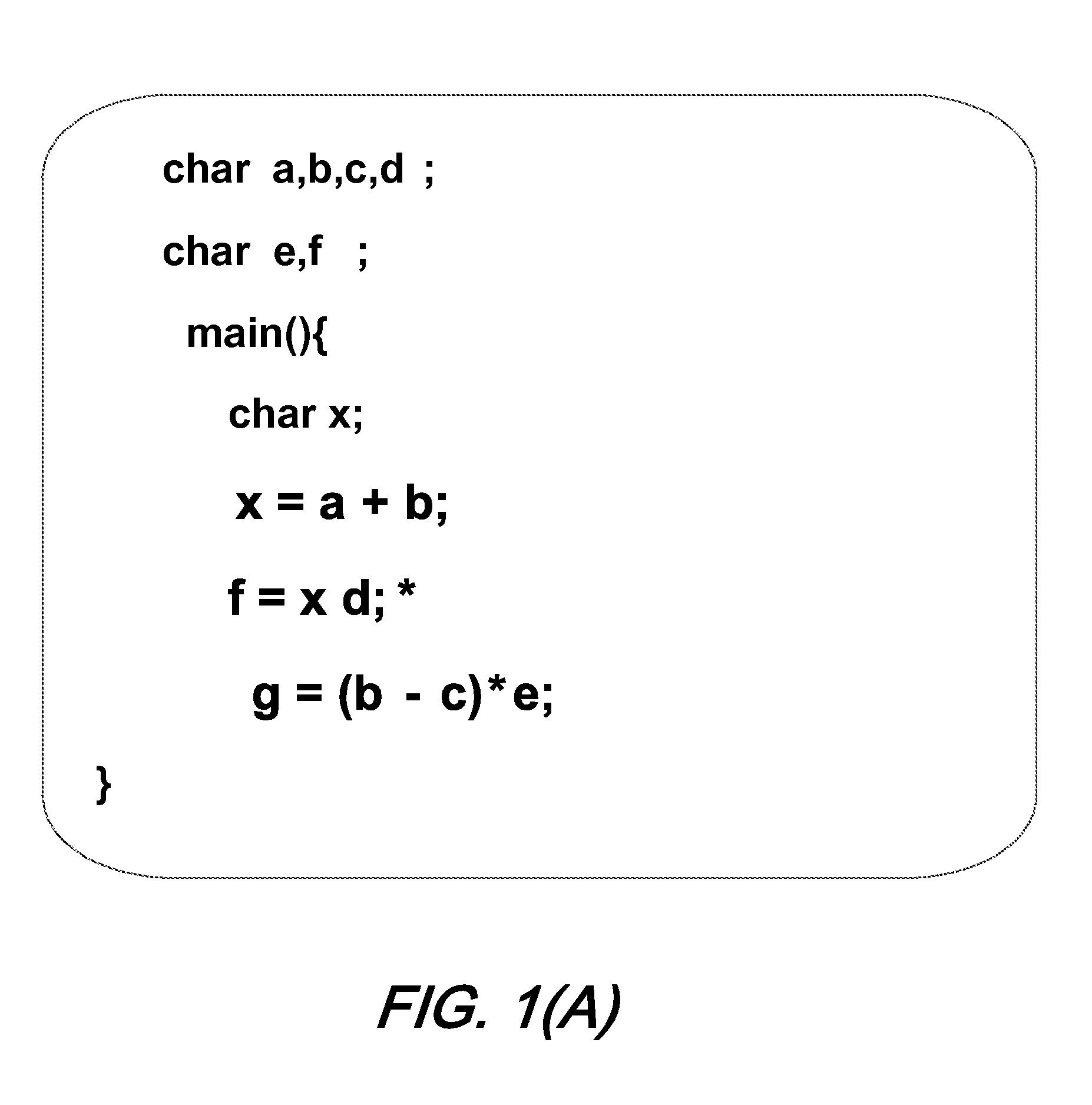

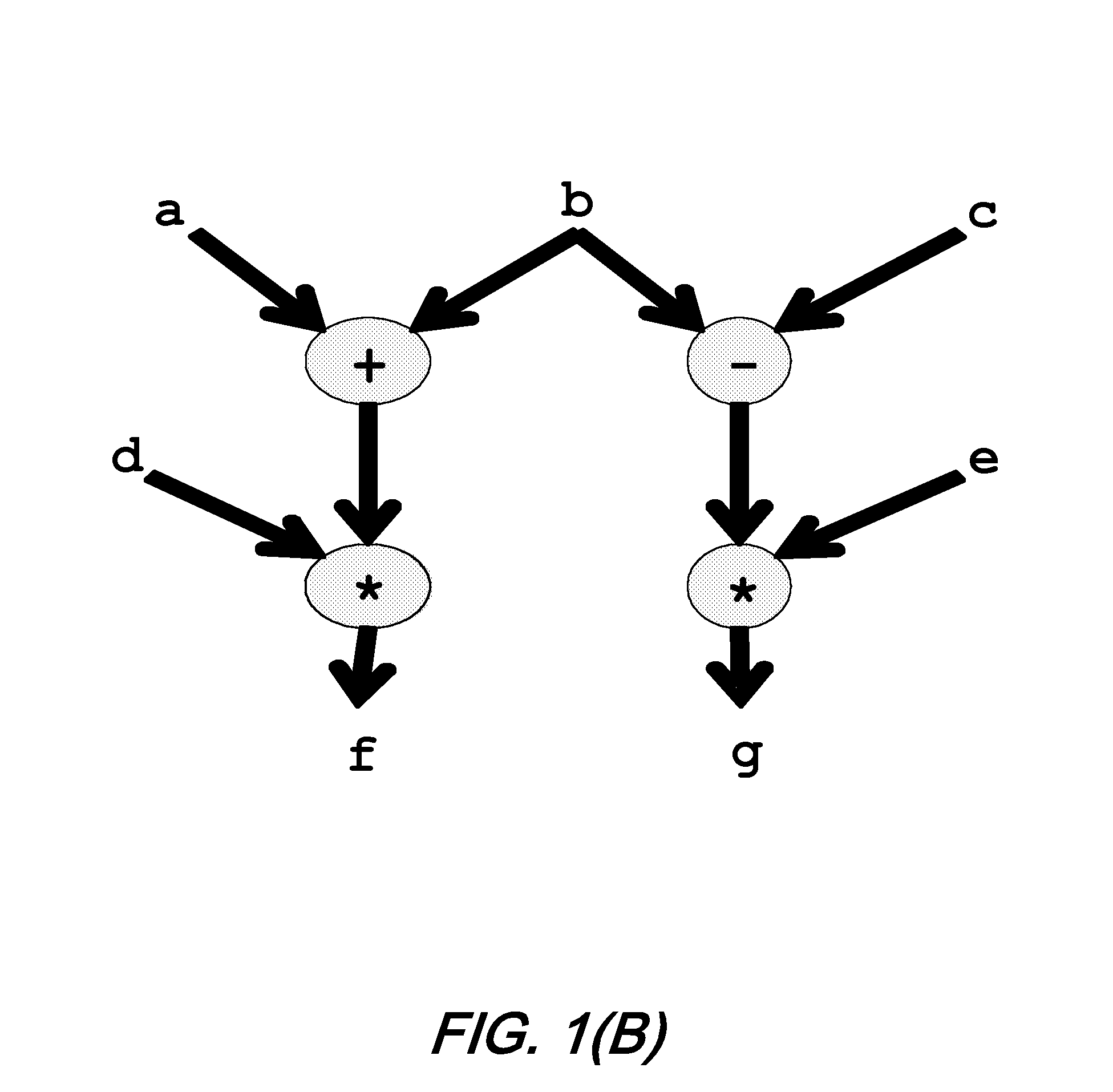

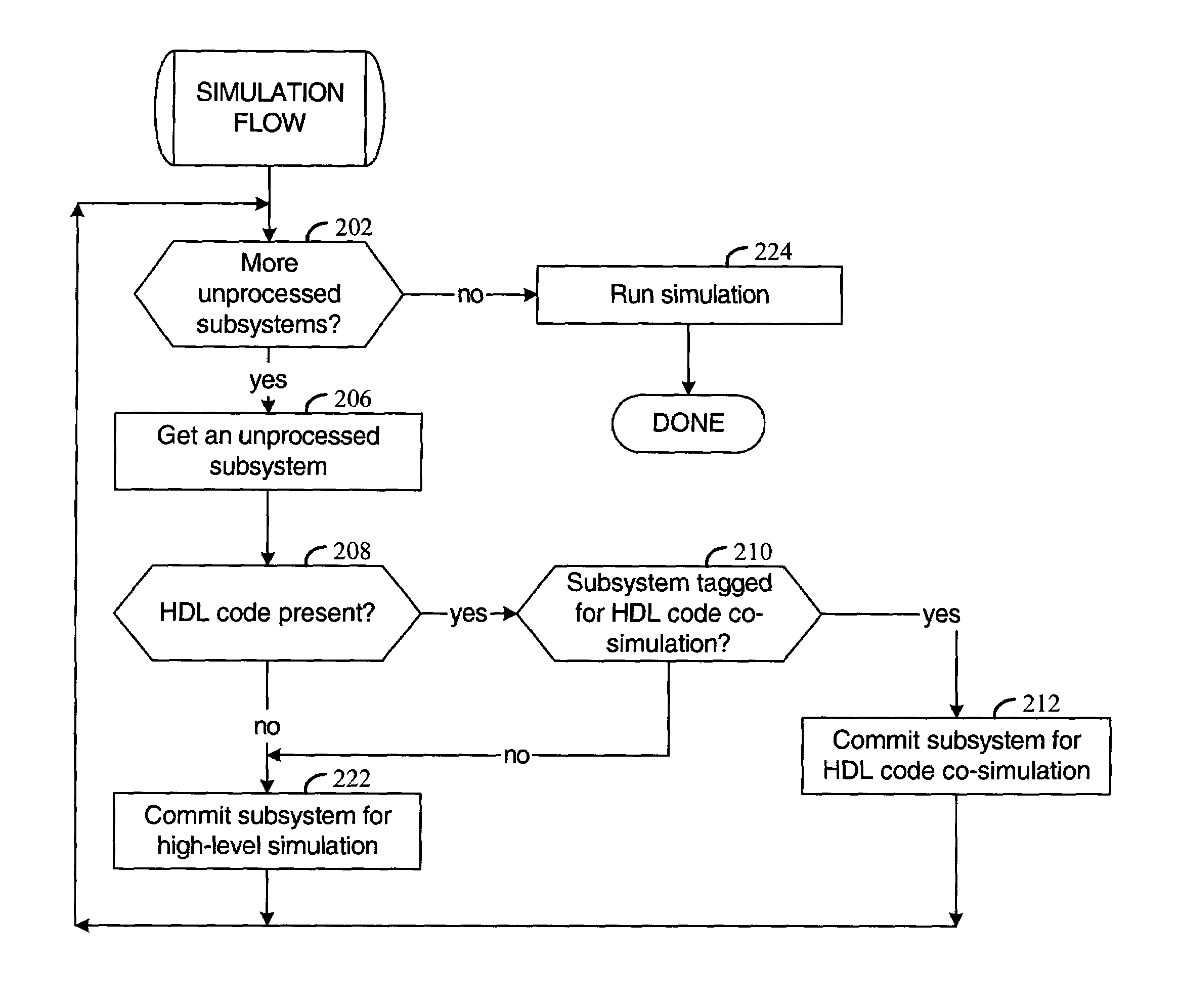

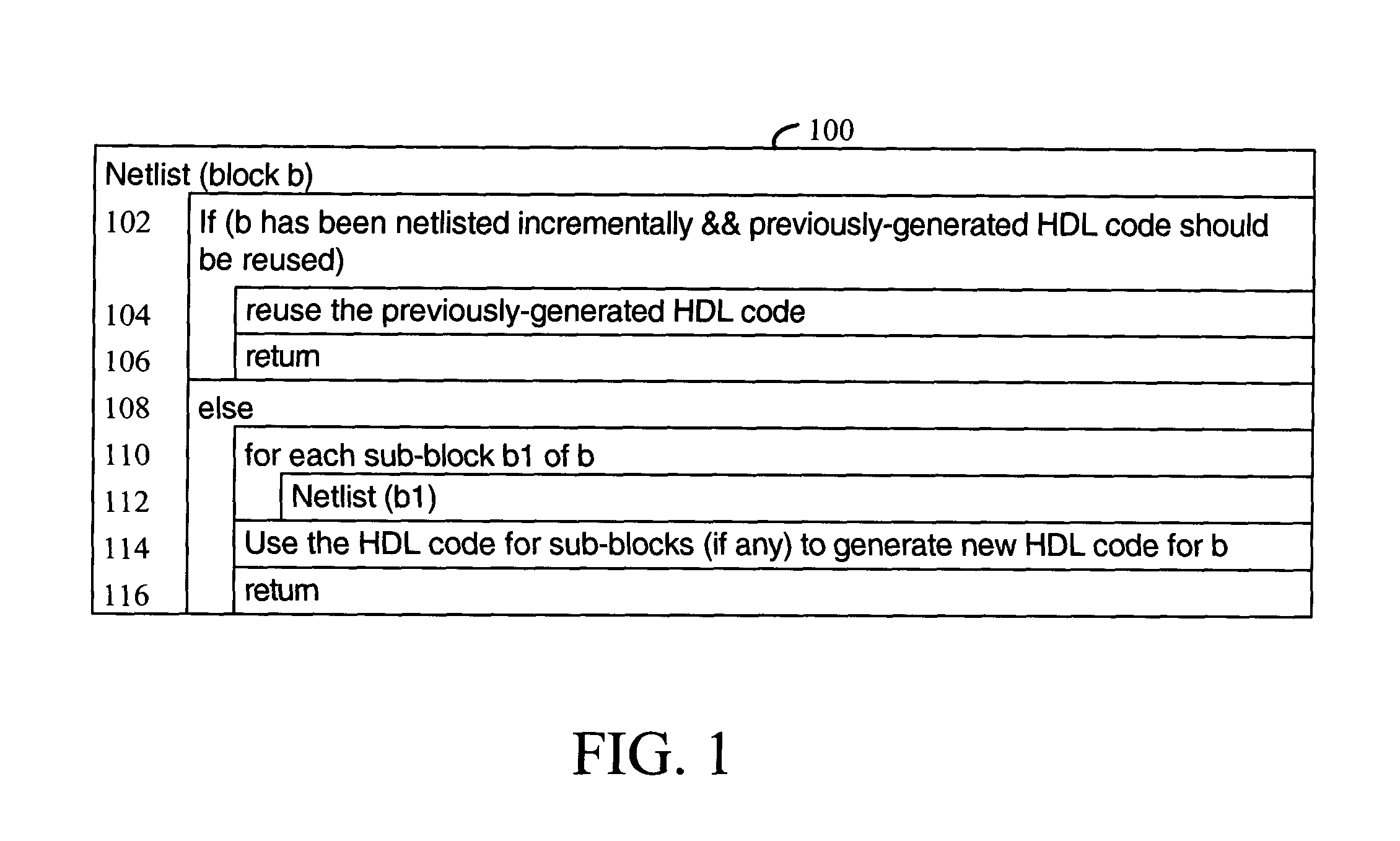

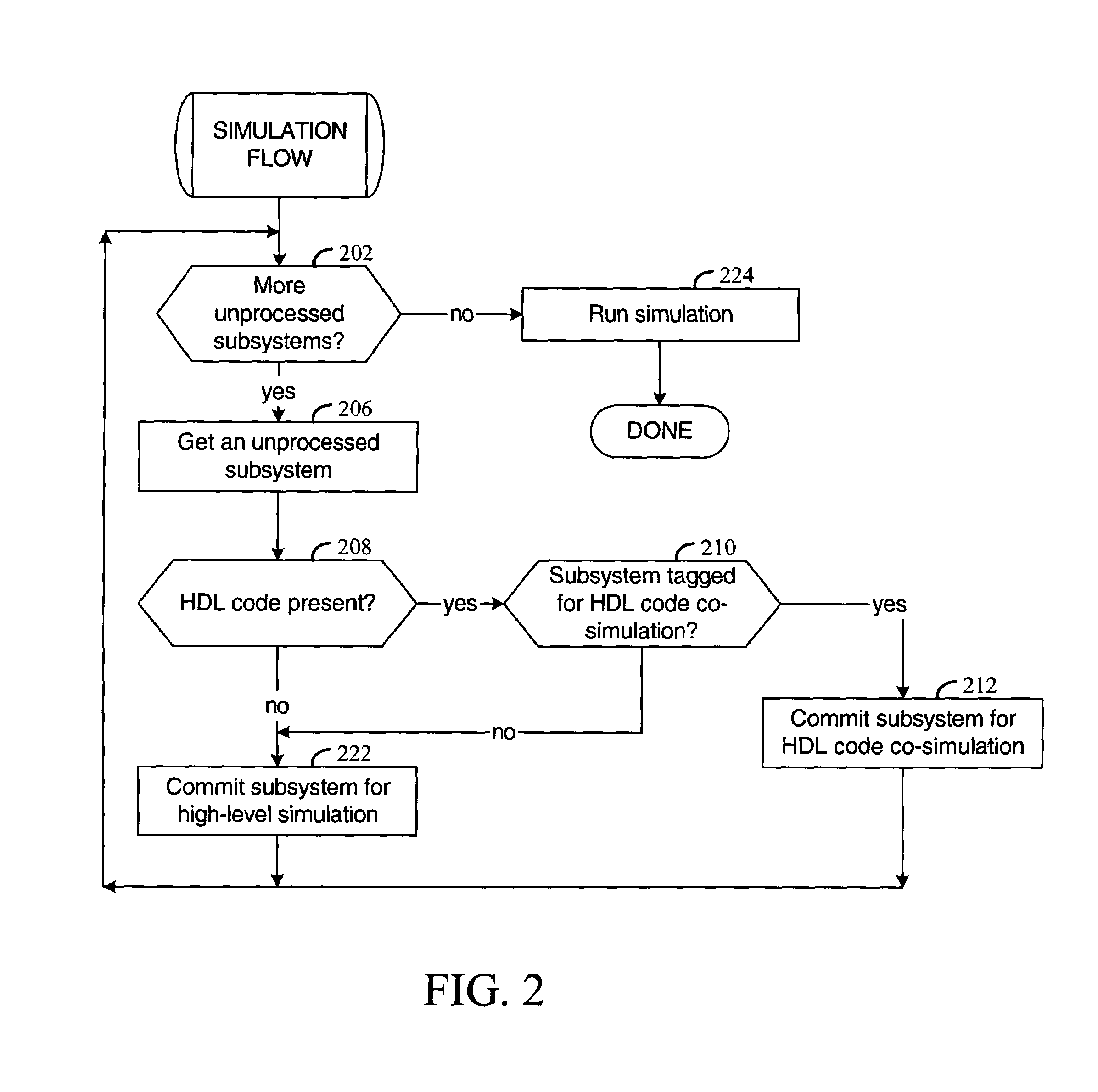

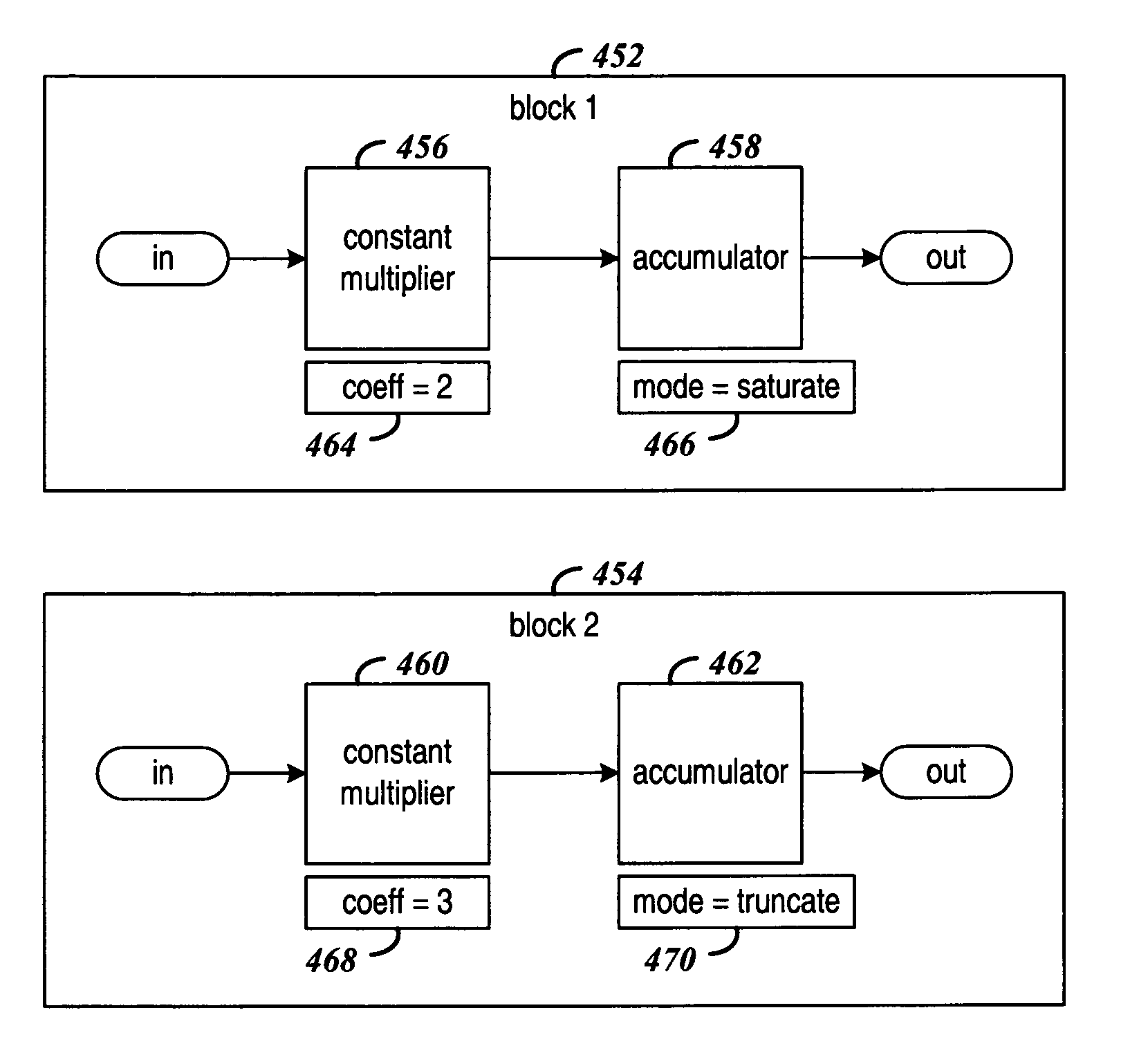

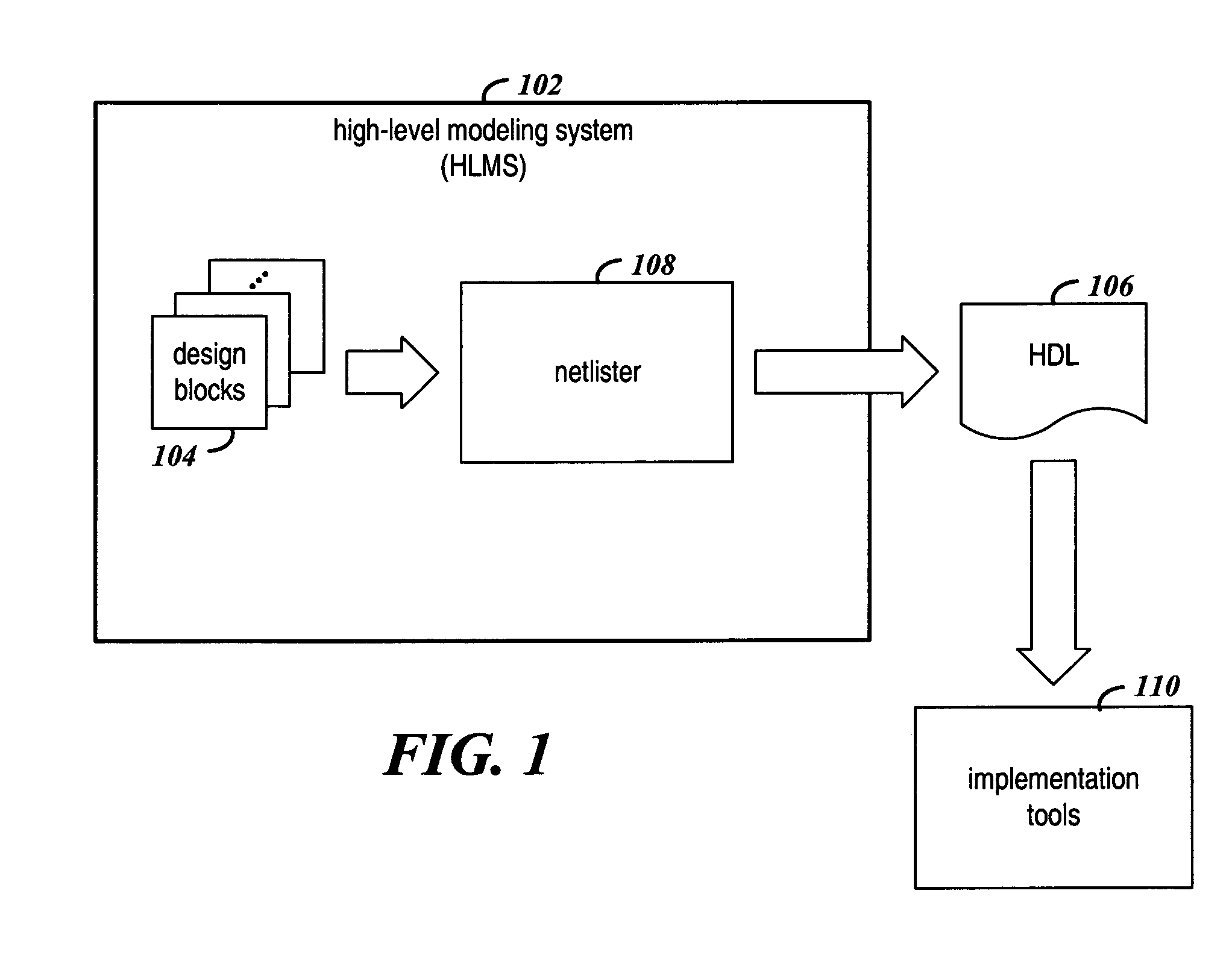

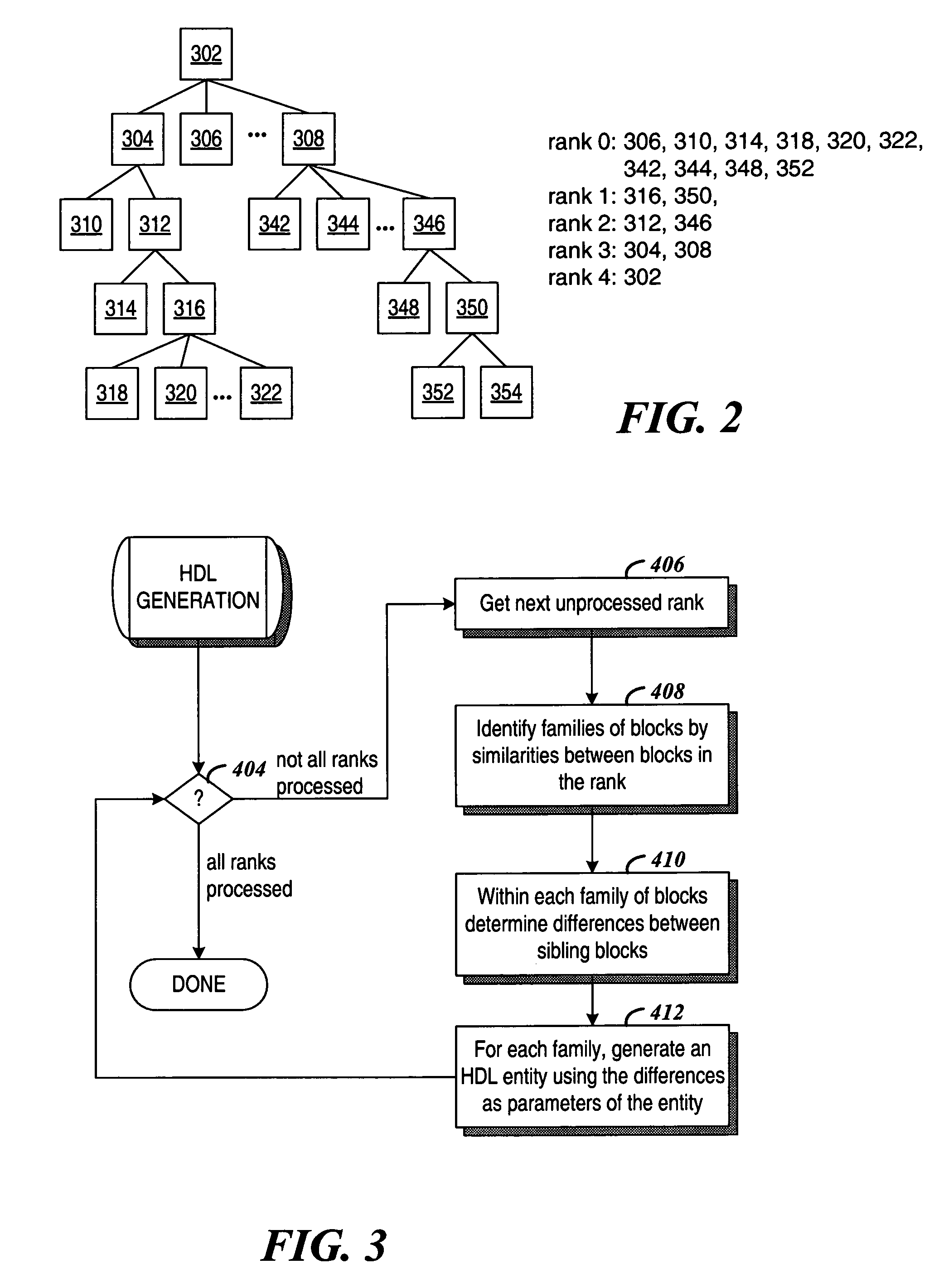

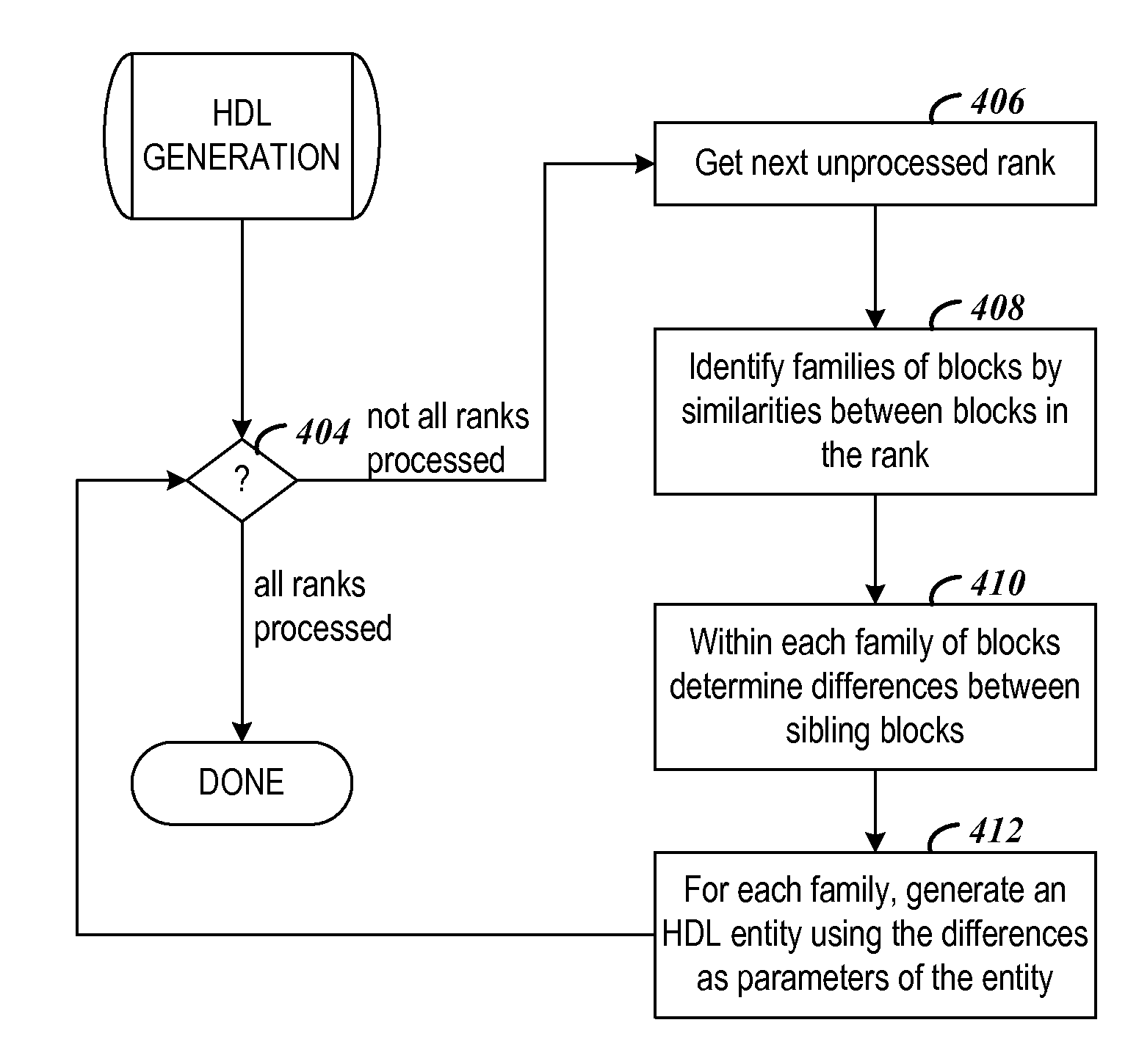

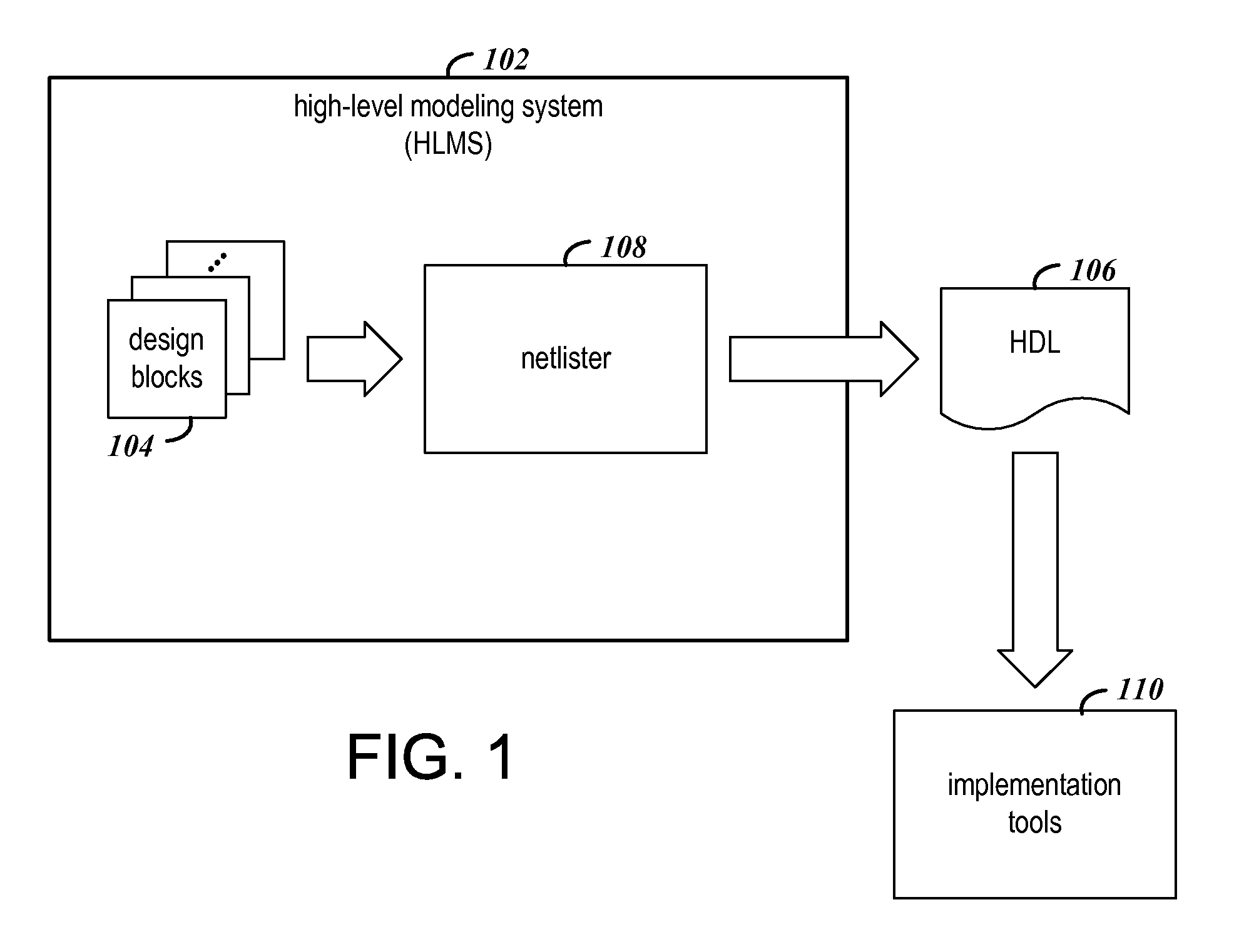

Incremental netlisting

ActiveUS7086030B1CAD circuit designSoftware simulation/interpretation/emulationProgramming languageHigh level modeling

Method and apparatus for preparing a design in a high-level modeling system. Hardware description language (HDL) code is generated for one or more of a plurality of high-level subsystems in a high-level design tagged by the user for HDL code generation. Previously generated HDL code may be reused instead of generating new HDL code for each subsystem tagged by the user for HDL code reuse.

Owner:XILINX INC

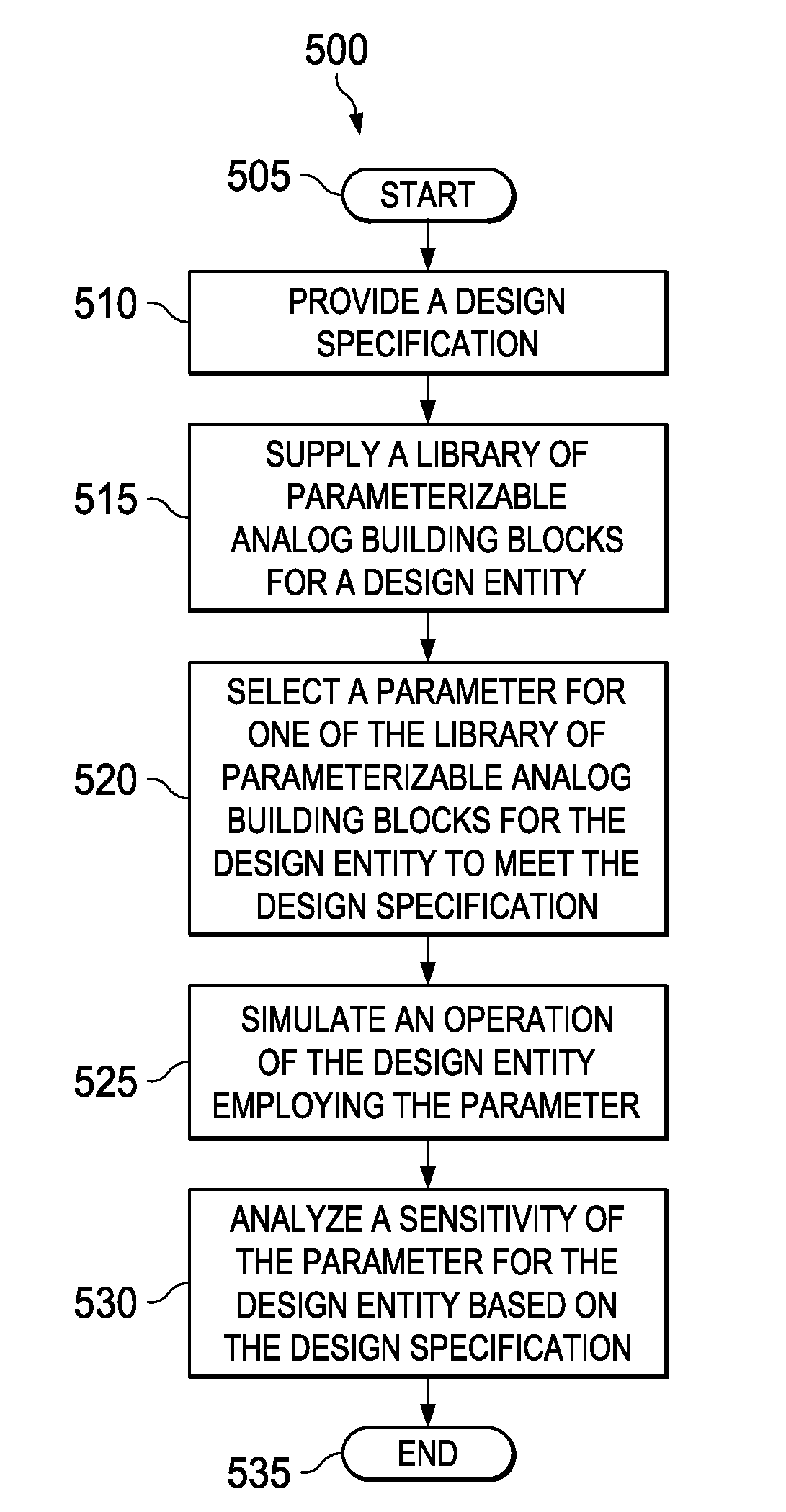

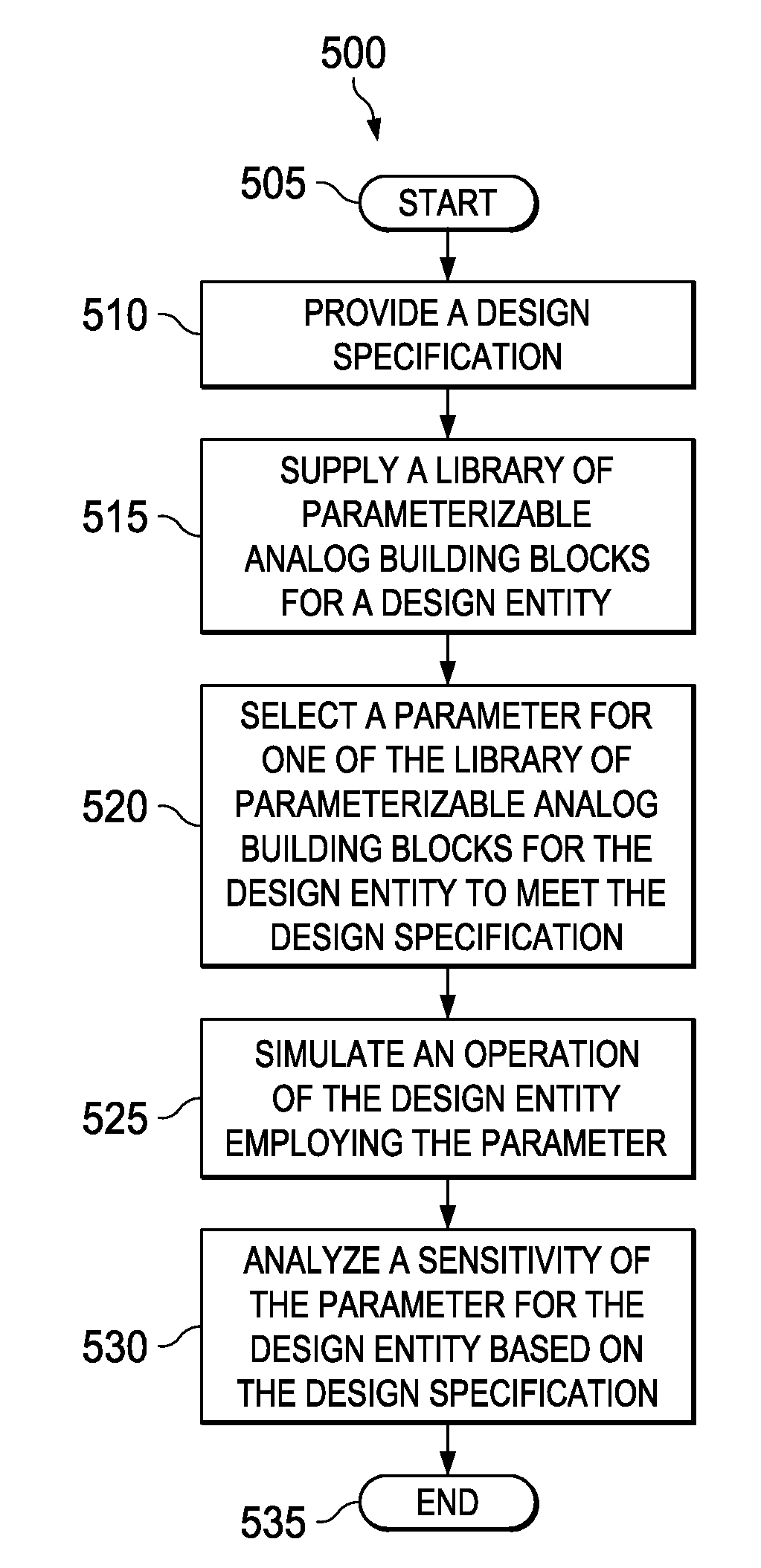

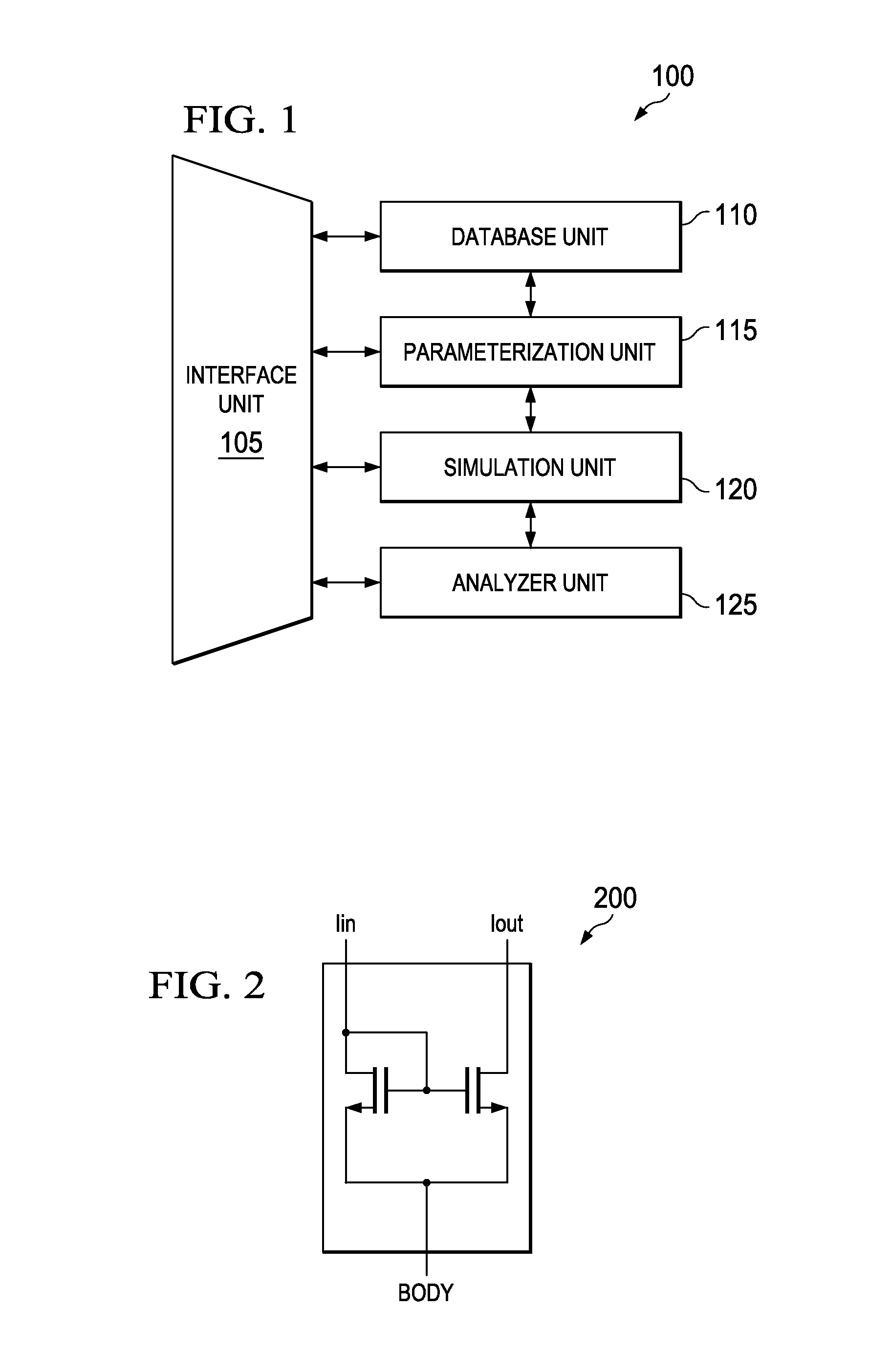

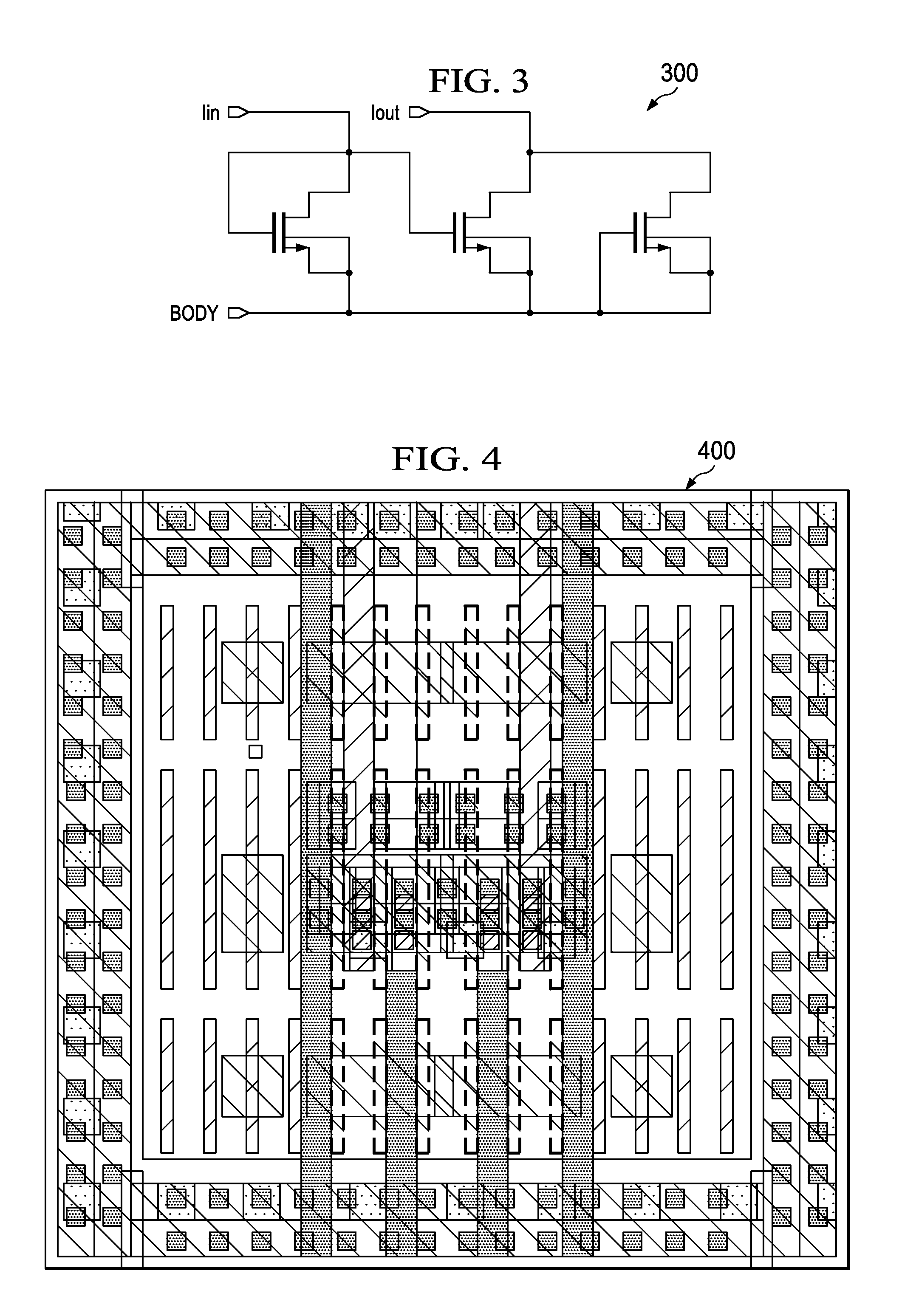

Fully parameterizable representation of a higher level design entity

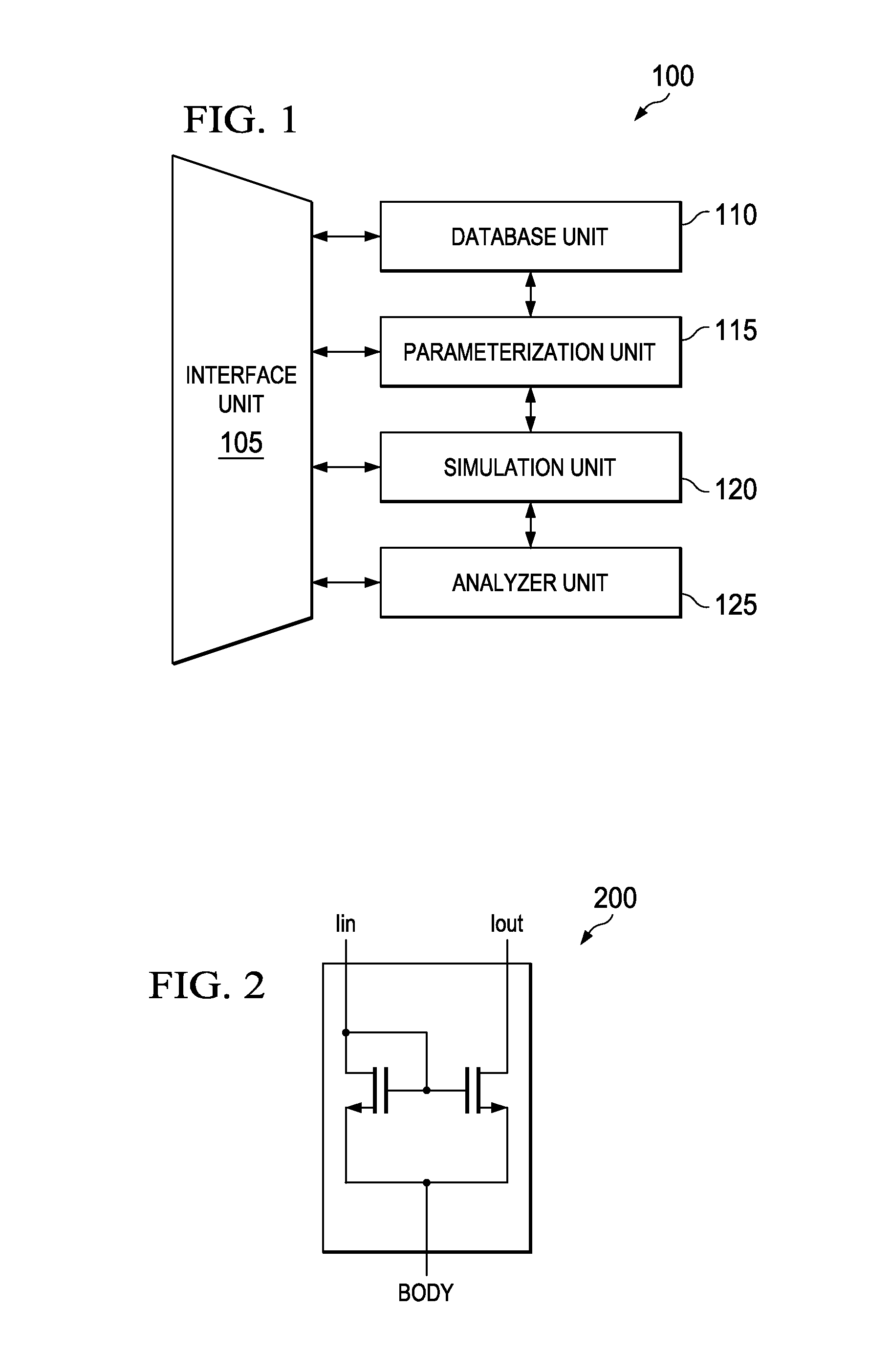

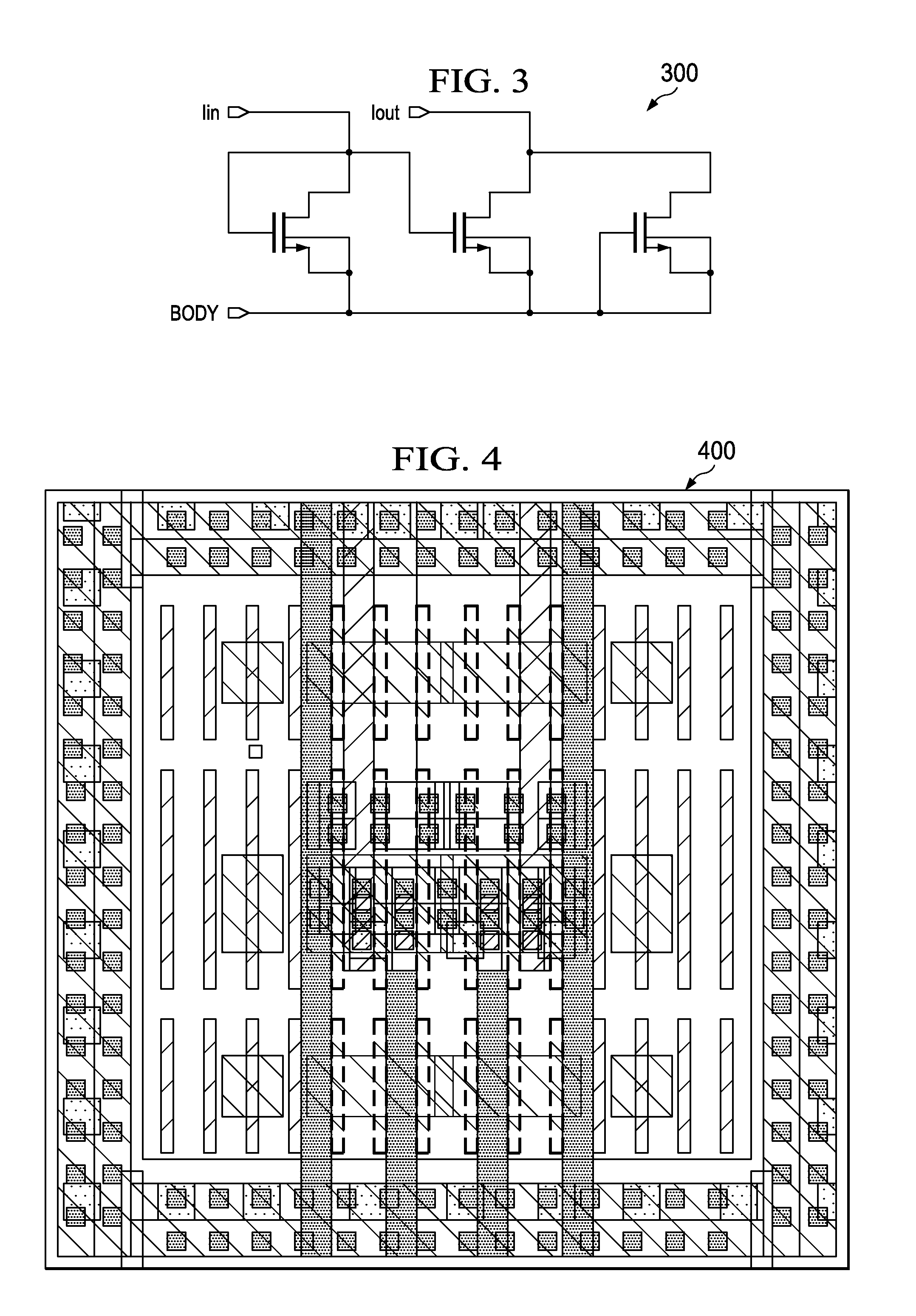

ActiveUS20120304140A1Computer programmed simultaneously with data introductionCAD circuit designEngineeringHigh-level design

A parameterizable design system is for use with semiconductor analog circuits and includes an interface unit connected to provide access to the system, a database unit connected to supply a library of parameterizable analog building blocks for a design entity, and a parameterization unit connected to select a parameter for one of the library of parameterizable analog building blocks to meet a design specification of the design entity. Additionally, the parameterizable design system may also include a simulation unit connected to simulate an operation of the design entity employing the parameter, and an analyzer unit connected to analyze a sensitivity of the parameter for the design entity based on the design specification. A method of designing a semiconductor analog circuit is also included.

Owner:BELL SEMICON LLC

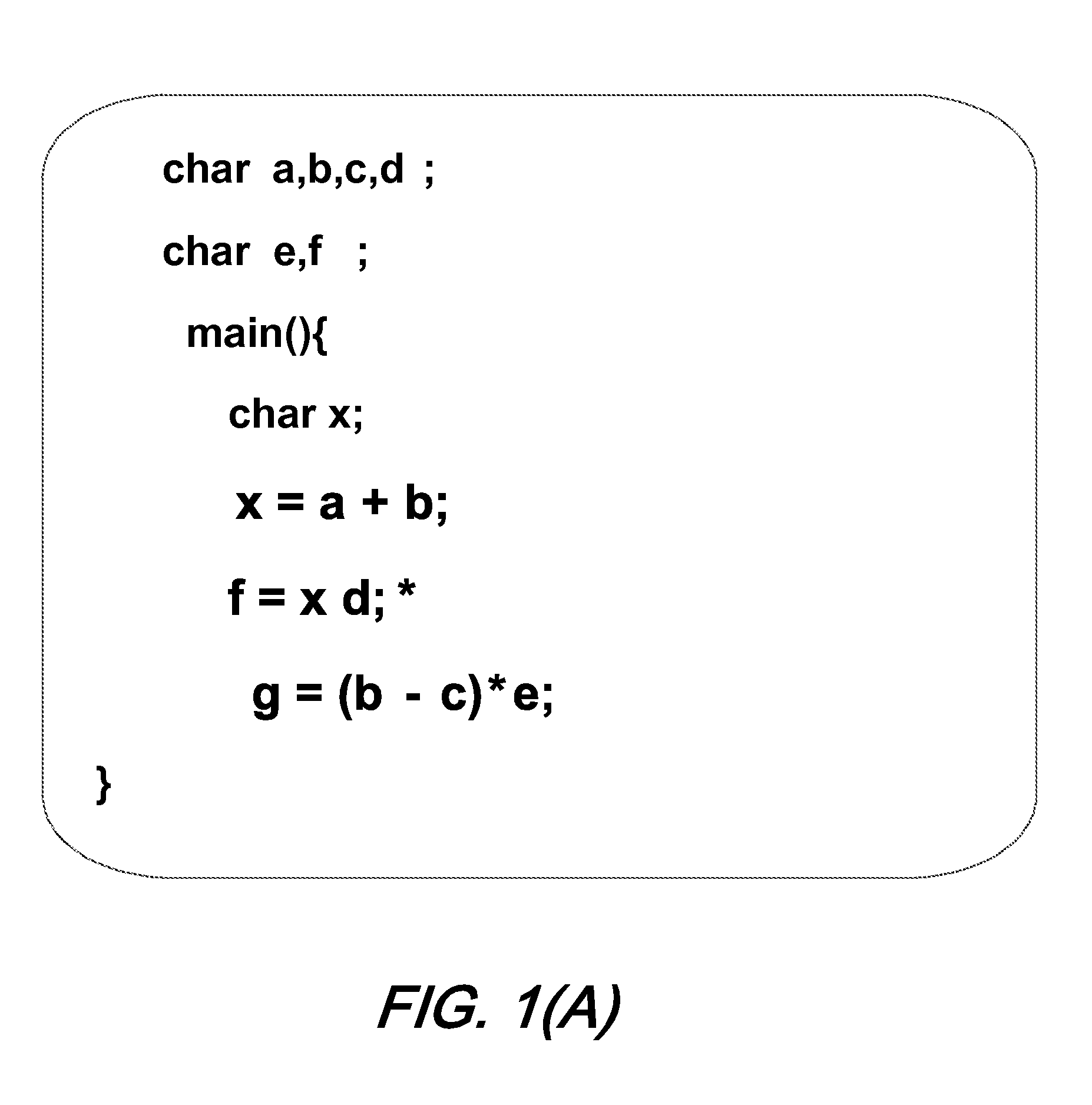

Computer implemented method of high-level synthesis for the efficient verification of computer software

InactiveUS7743352B2Use minimizedLimiting stepComputer aided designSoftware simulation/interpretation/emulationGuidelineExternal storage

Verification friendly models for SAT-based formal verification are generated from a given high-level design wherein during construction the following guidelines are enforced: 1) No re-use of functional units and registers; 2) Minimize the use of muxes and sharing; 3) Reduce the number of control steps; 4) Avoid pipelines; 5) Chose functional units from “verification friendly” library; 6) Re-use operations; 7) Perform property-preserving slicing; 8) Support “assume” and “assert” in the language specification; and 8) Use external memory modules instead of register arrays.

Owner:NEC CORP

Method and apparatus for power consumption analysis in global nets

InactiveUS20040177328A1CAD circuit designSoftware simulation/interpretation/emulationTime domainEngineering

The present invention describes a method and an apparatus for determining switching power consumption of global devices (e.g., repeaters, flops or the like) in an integrated circuit design during high-level design phase after the global routing for the integrated circuit is available. The clock cycle is divided into various timing intervals and the timing reports are generated for each cycle to determine a time- domain staggered distribution of each device's switching activity within a given timing interval. Each device's switching activity is analyzed within the given timing interval (or segment thereof). The power consumption is determined for each device that switches in the given timing interval.

Owner:ORACLE INT CORP

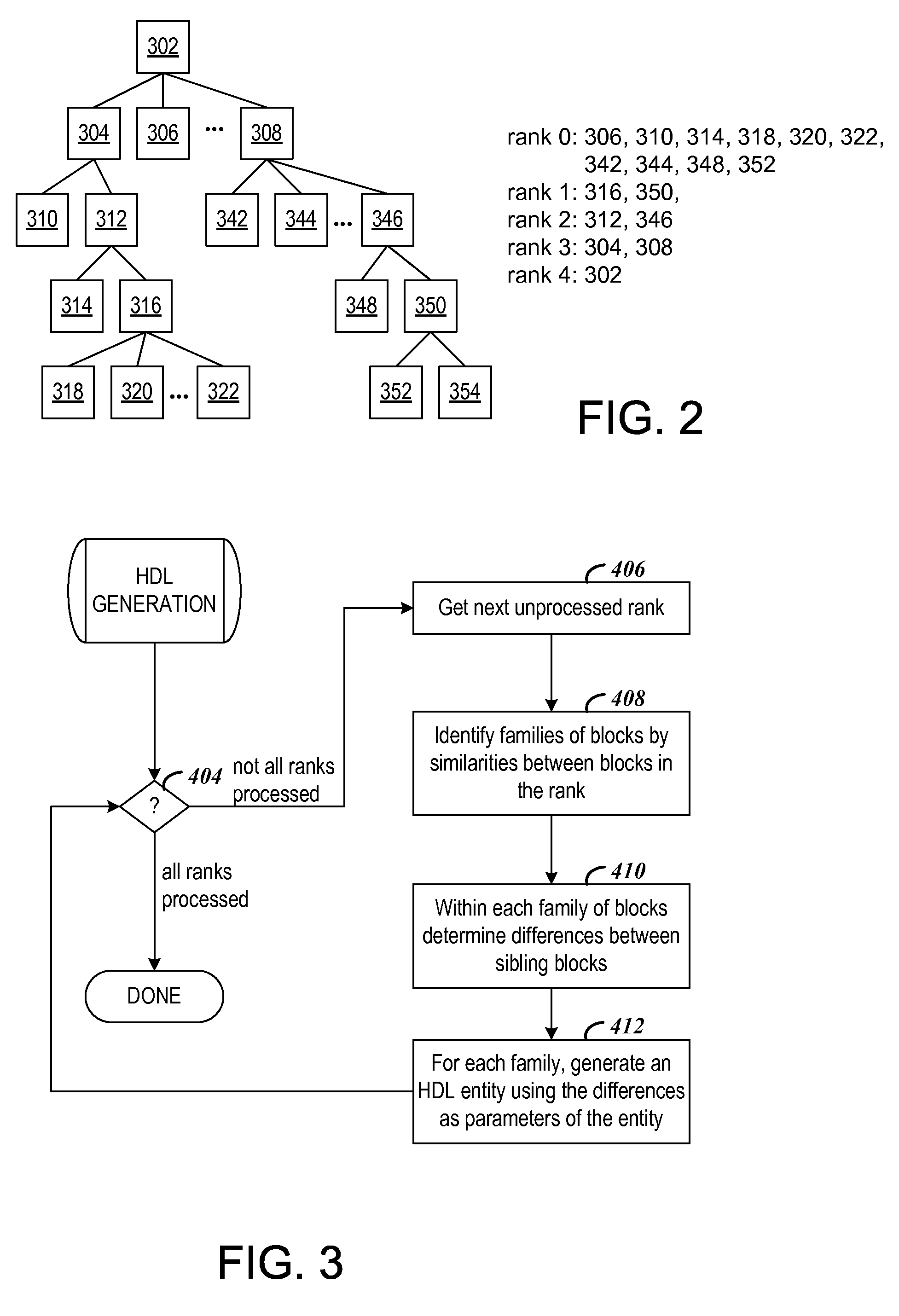

Translation of high-level circuit design blocks into hardware description language

Translation of high-level design blocks into a design specification in a hardware description language (HDL). Each block in the high-level design is assigned to a group. A set of attributes is identical between the blocks in a group. For each group of blocks, a respective set of parameters having different values on subblocks of at least two blocks in the group is determined. An HDL specification is generated for each group. The HDL specification for a group has for each parameter in the set of parameters, a parameter input.

Owner:XILINX INC

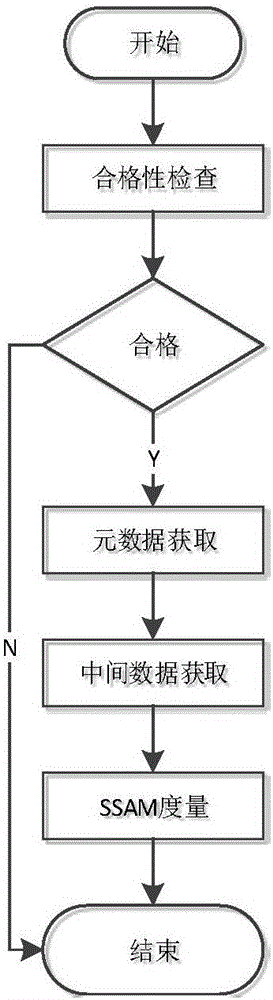

Static maturity measuring method for architecture

InactiveCN105739993AReduce maintenance costsThe measurement results are objectiveSoftware metricsSpecific program execution arrangementsSoftware EvaluationComputer module

Owner:SOUTHEAST UNIV +1

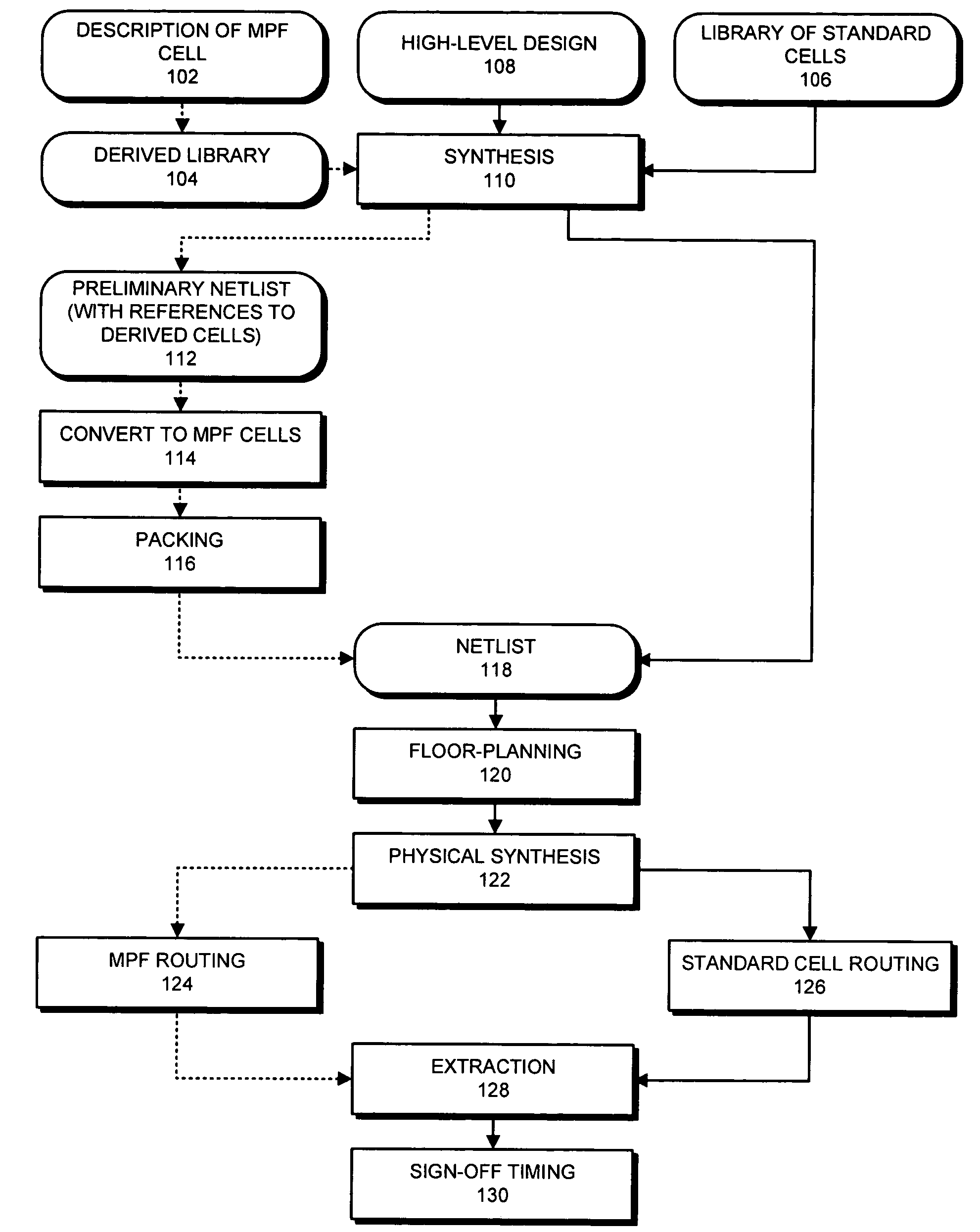

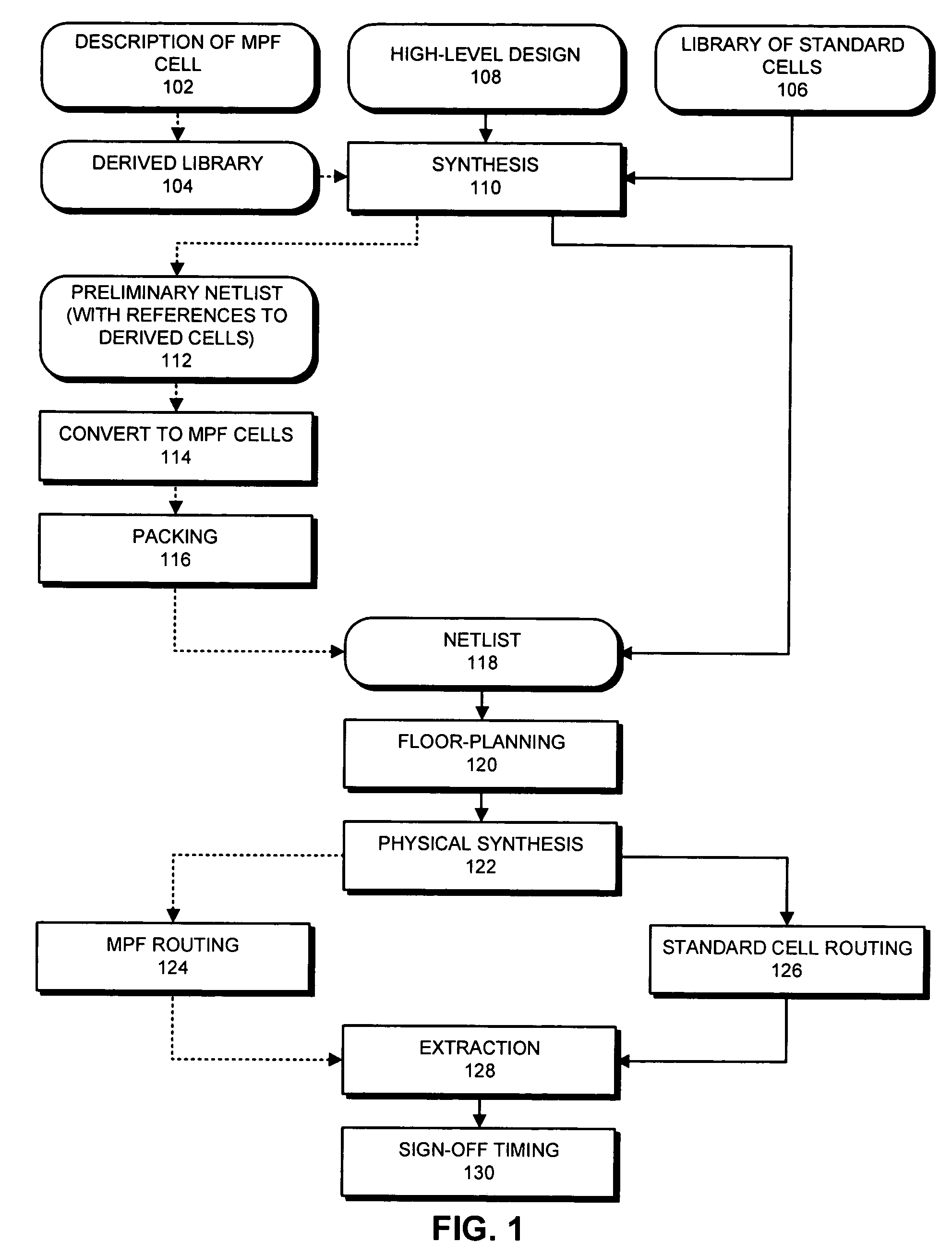

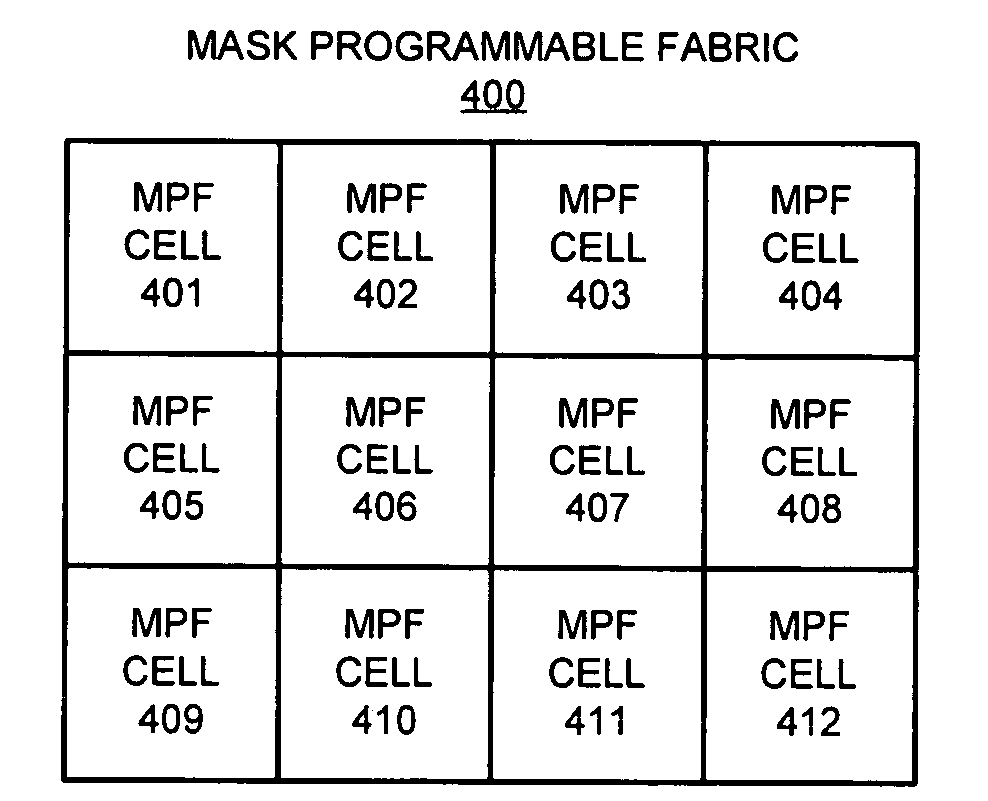

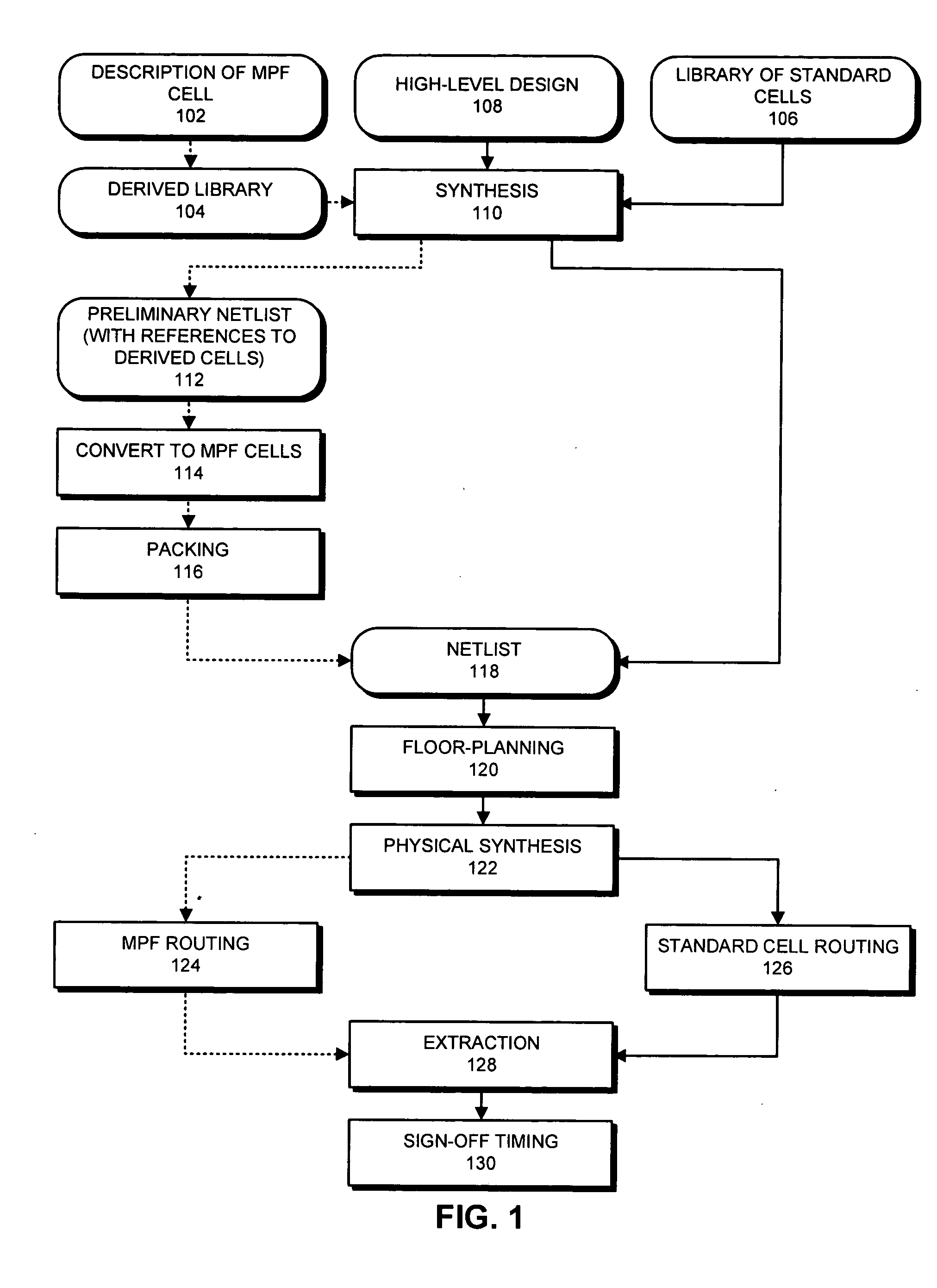

Method and apparatus for designing an integrated circuit using a mask-programmable fabric

ActiveUS20050132321A1Designing can be facilitatedCAD circuit designProgram controlProgramming constructsEngineering

One embodiment of the invention provides a system that facilitates designing an integrated circuit using a mask-programmable fabric, which contains both mask-programmable logic and a mask-programmable interconnect. During operation, the system receives a description of a mask-programmable cell, wherein instances of the mask-programmable cell are repeated to form the mask-programmable fabric. The system uses this description of the mask-programmable cell to generate a derived library containing cells that can be obtained by programming the mask-programmable cell. Next, the system receives a high-level design for the integrated circuit. The system then performs a synthesis operation on the high-level design to generate a preliminary netlist for the high-level design, wherein the preliminary netlist contains references to cells in the derived library. Finally, the system converts the preliminary netlist into a netlist that contains references to the mask-programmable cell with the logic appropriately programmed. The netlist is then placed and routed with the mask programmable constraints on the mask programmable fabric. The design, thus implemented on the programmable fabric, can be changed to accommodate logic revisions and bug fixes by changing only a few masks required for its fabrication.

Owner:SYNOPSYS INC

Translation of high-level circuit design blocks into hardware description language

Translation of high-level design blocks into a design specification in a hardware description language (HDL). Each block in the high-level design is assigned to a group. A set of attributes is identical between the blocks in a group. For each group of blocks, a respective set of parameters having different values on subblocks of at least two blocks in the group is determined. An HDL specification is generated for each group. The HDL specification for a group has for each parameter in the set of parameters, a parameter input.

Owner:XILINX INC

Fully parameterizable representation of a higher level design entity

ActiveUS8464202B2Computer programmed simultaneously with data introductionCAD circuit designEngineeringLevel design

A parameterizable design system is for use with semiconductor analog circuits and includes an interface unit connected to provide access to the system, a database unit connected to supply a library of parameterizable analog building blocks for a design entity, and a parameterization unit connected to select a parameter for one of the library of parameterizable analog building blocks to meet a design specification of the design entity. Additionally, the parameterizable design system may also include a simulation unit connected to simulate an operation of the design entity employing the parameter, and an analyzer unit connected to analyze a sensitivity of the parameter for the design entity based on the design specification. A method of designing a semiconductor analog circuit is also included.

Owner:BELL SEMICON LLC

A High-Order Tunable Bandpass Filter Based on Cross-Coupling Structure

ActiveCN106972227BImprove frequency selectivityEasy to adjustWaveguide type devicesBandpass filteringDielectric substrate

Owner:SOUTHWEST JIAOTONG UNIV

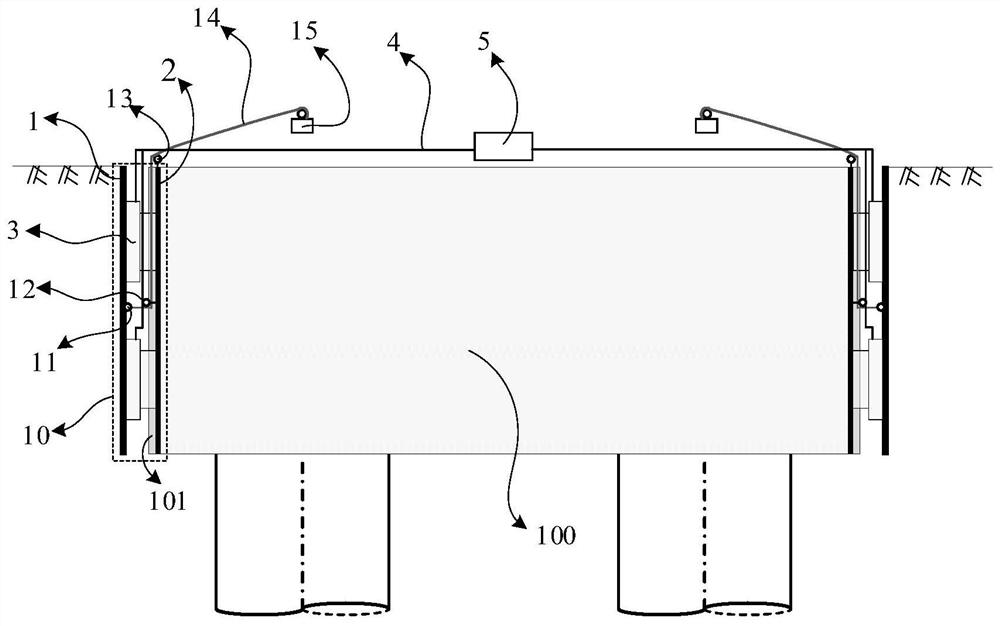

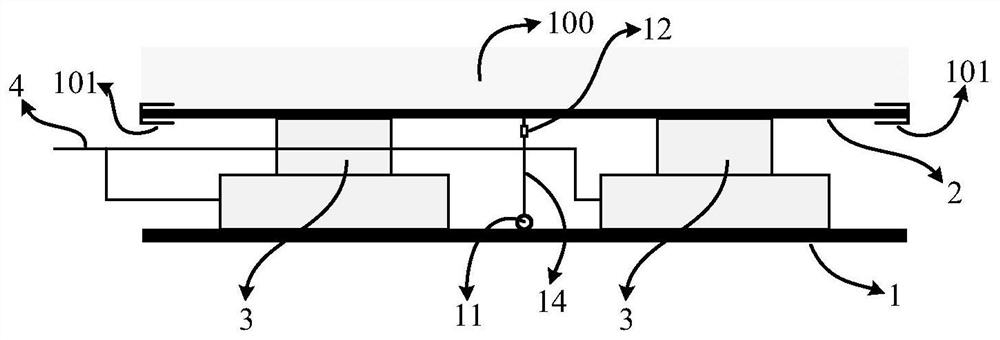

Pushing device and method for improving horizontal bearing performance of low bearing platform

ActiveCN111173020BSimple structureEasy to manufactureFoundation engineeringBridge engineeringArchitectural engineering

The invention discloses a jacking device and a method for improving the horizontal bearing performance of a low bearing platform, belonging to the technical field of bridge engineering. The jacking device can squeeze the soil of the side wall of the low cap and refill the dense crushed stone concrete, which solves the problem that the foundation soil of the side wall of the low cap is loose and cannot be in close contact with the side wall of the cap and cannot provide high-level resistance Therefore, the purpose of significantly improving the horizontal bearing capacity of low caps is realized, and the safety reserve goal of improving the pile group foundation of low caps is achieved. After the soil is compressed, the device is reset by a reset device, and the main components can be taken out from the slot, so it can be reused, thereby significantly reducing the application cost of the pushing device. It provides an additional safety reserve for the large-scale low cap pile foundation of important projects, and makes it possible to consider the role of the low cap in the design process of the pile group foundation. Security applications play an important role.

Owner:SOUTHEAST UNIV

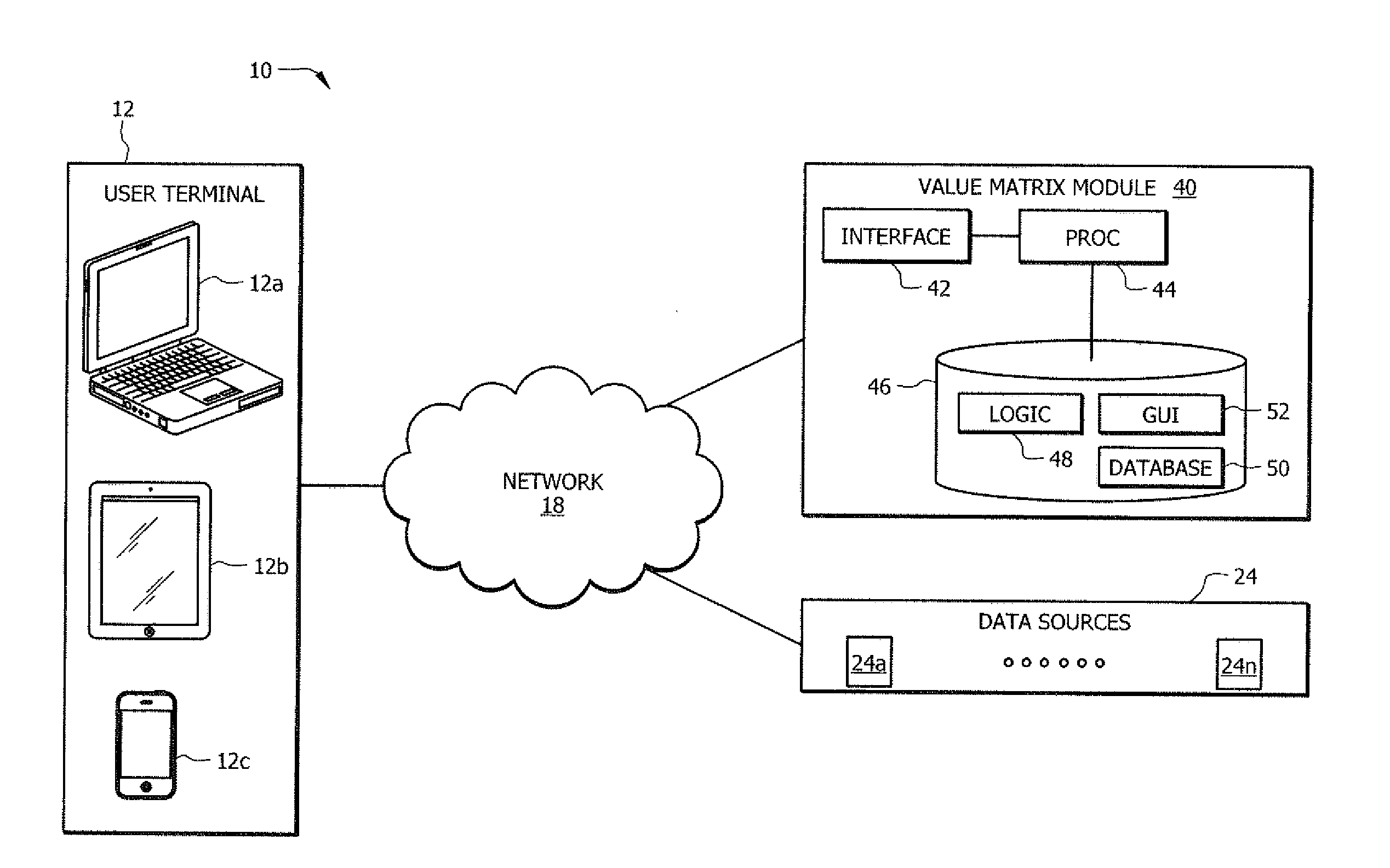

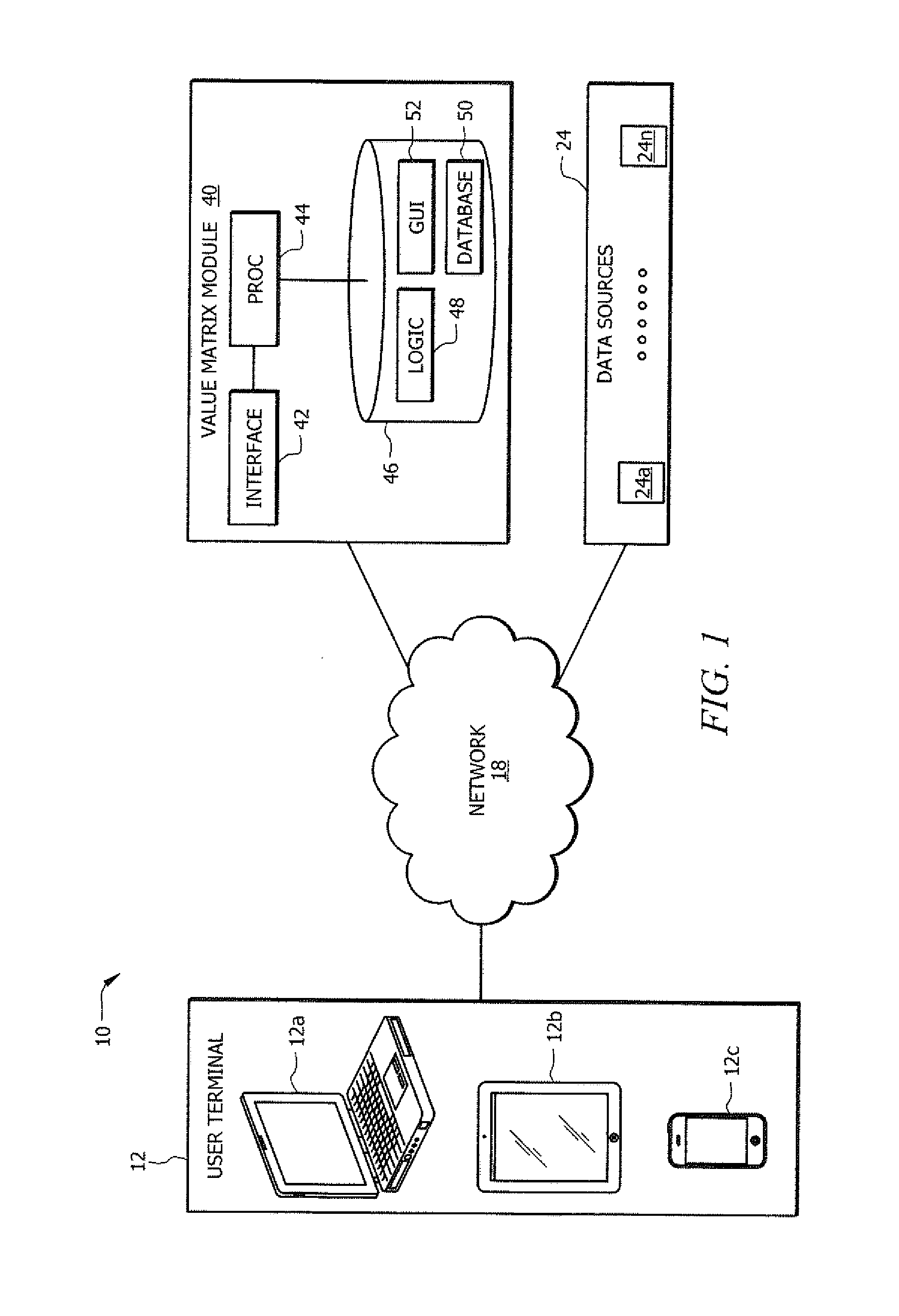

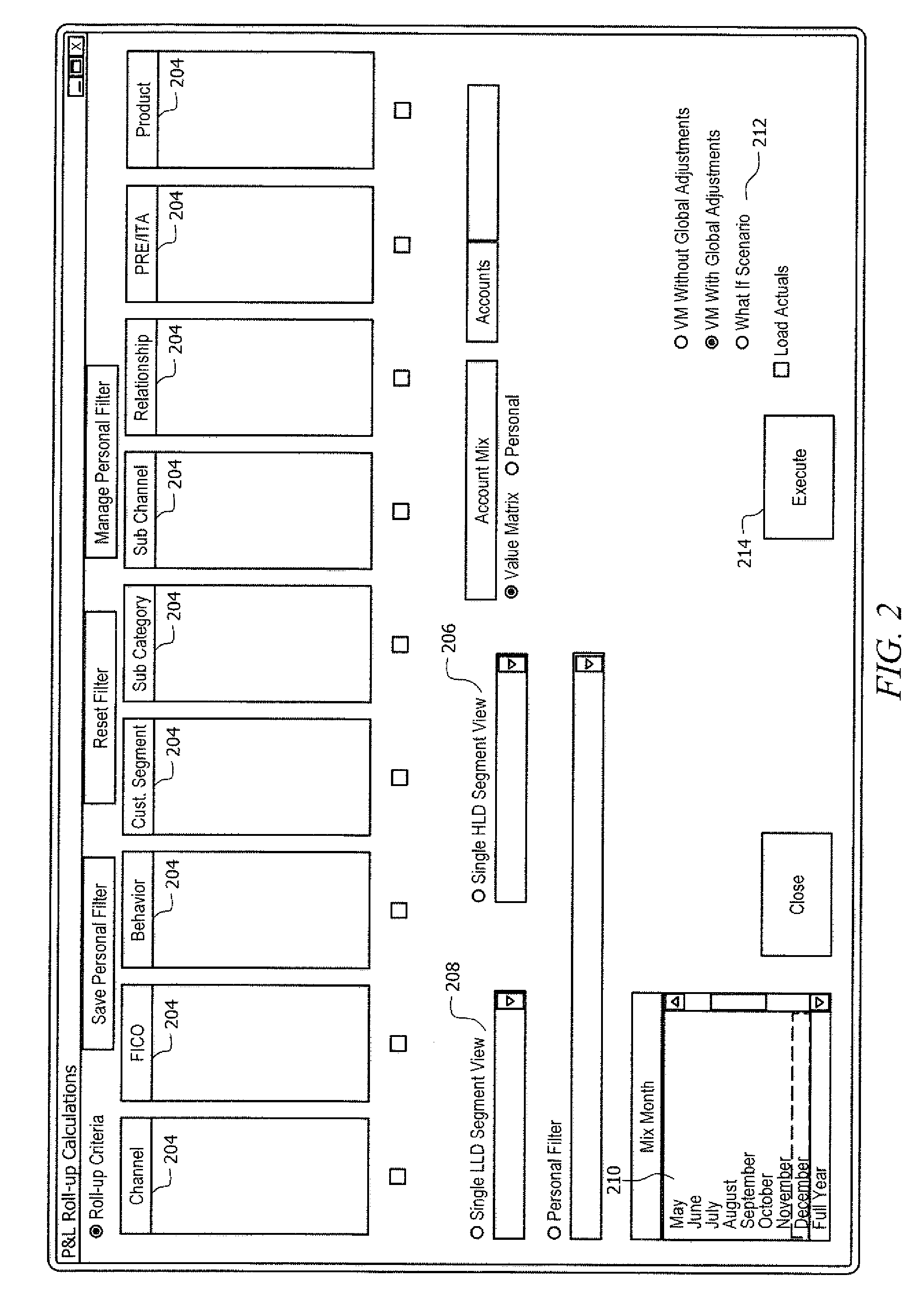

System and Method for Mapping Financial Data

InactiveUS20140244448A1Data be reduced eliminatedDisadvantages can be reduced eliminatedComplete banking machinesFinanceGraphicsGraphical user interface

Mapping financial data comprises receiving a first set of financial data from internal reporting systems. The first set of financial data is loaded into a database having high-level design segmentation. The first set of financial data is associated with a high-level segment of profitability. An input associated with the high-level segment of profitability is received in a graphical user interface. A second set of financial data is extracted from the first set of financial data according to the high-level segment of profitability received in the graphical user interface. A third set of financial data is extracted from a plurality of business units. A baseline forecast is calculated according to the second set of financial data and at least a portion of the third set of financial data. The baseline forecast is presented in the graphical user interface to determine the profitability of a new card account.

Owner:BANK OF AMERICA CORP

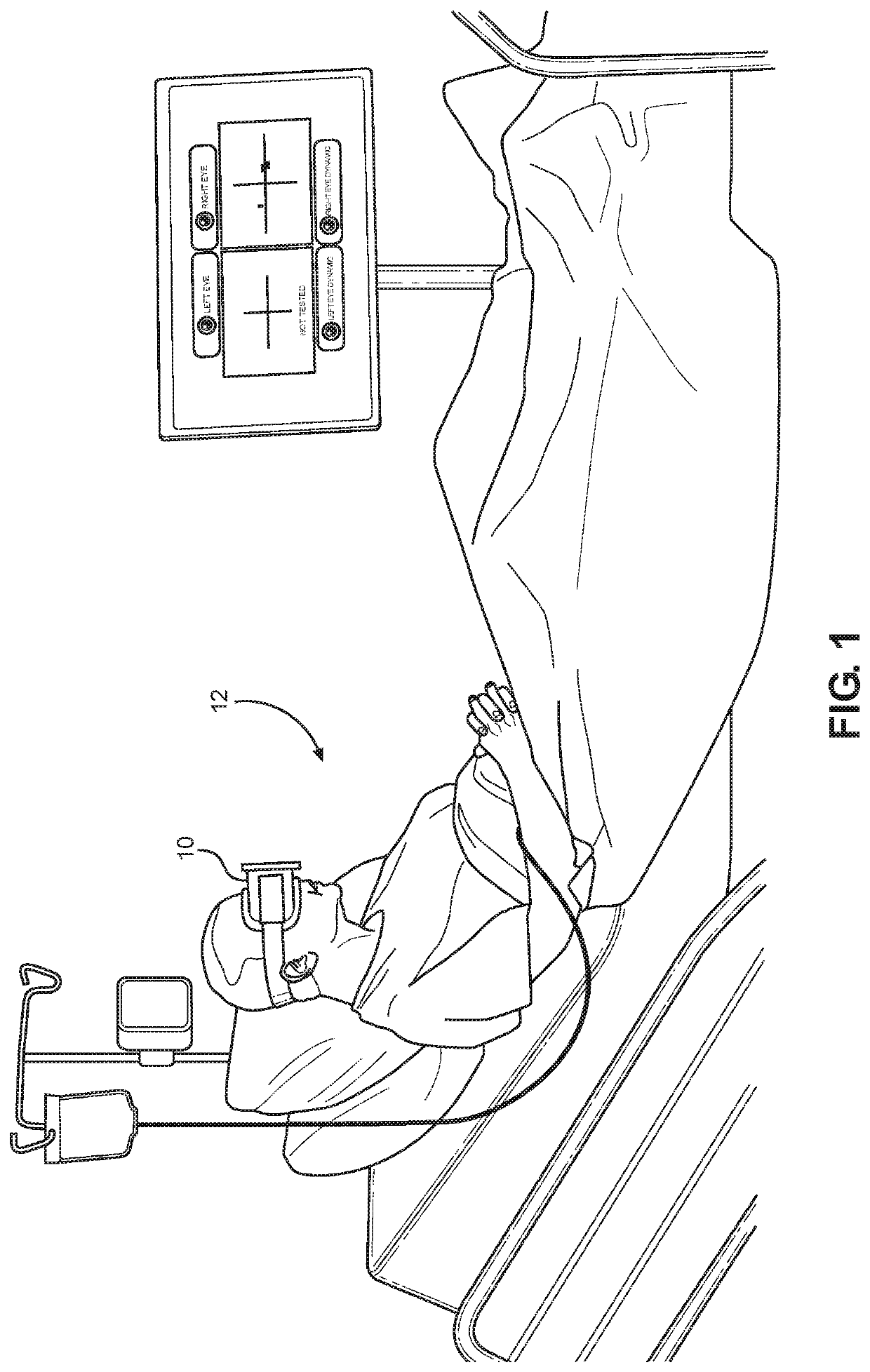

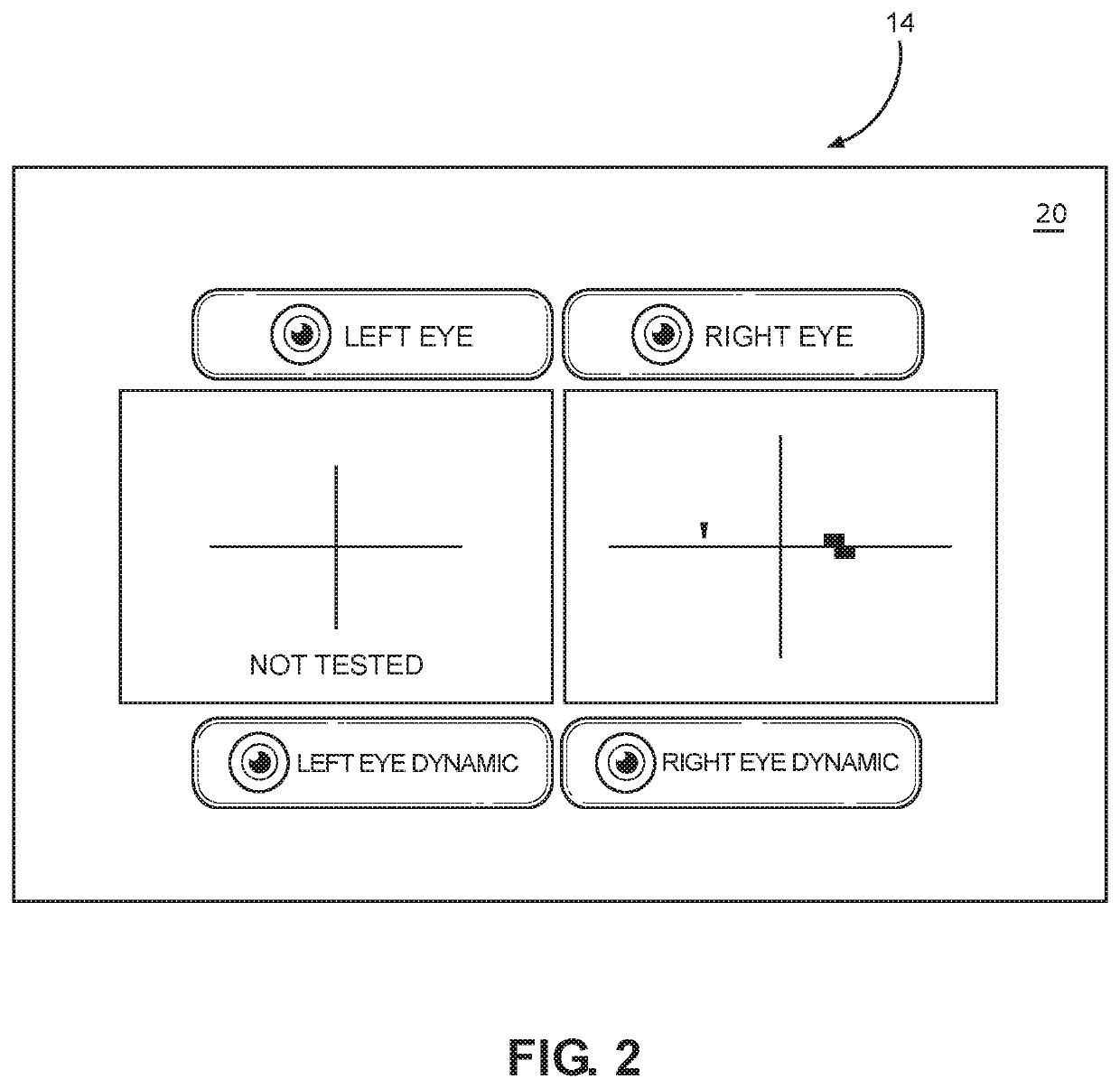

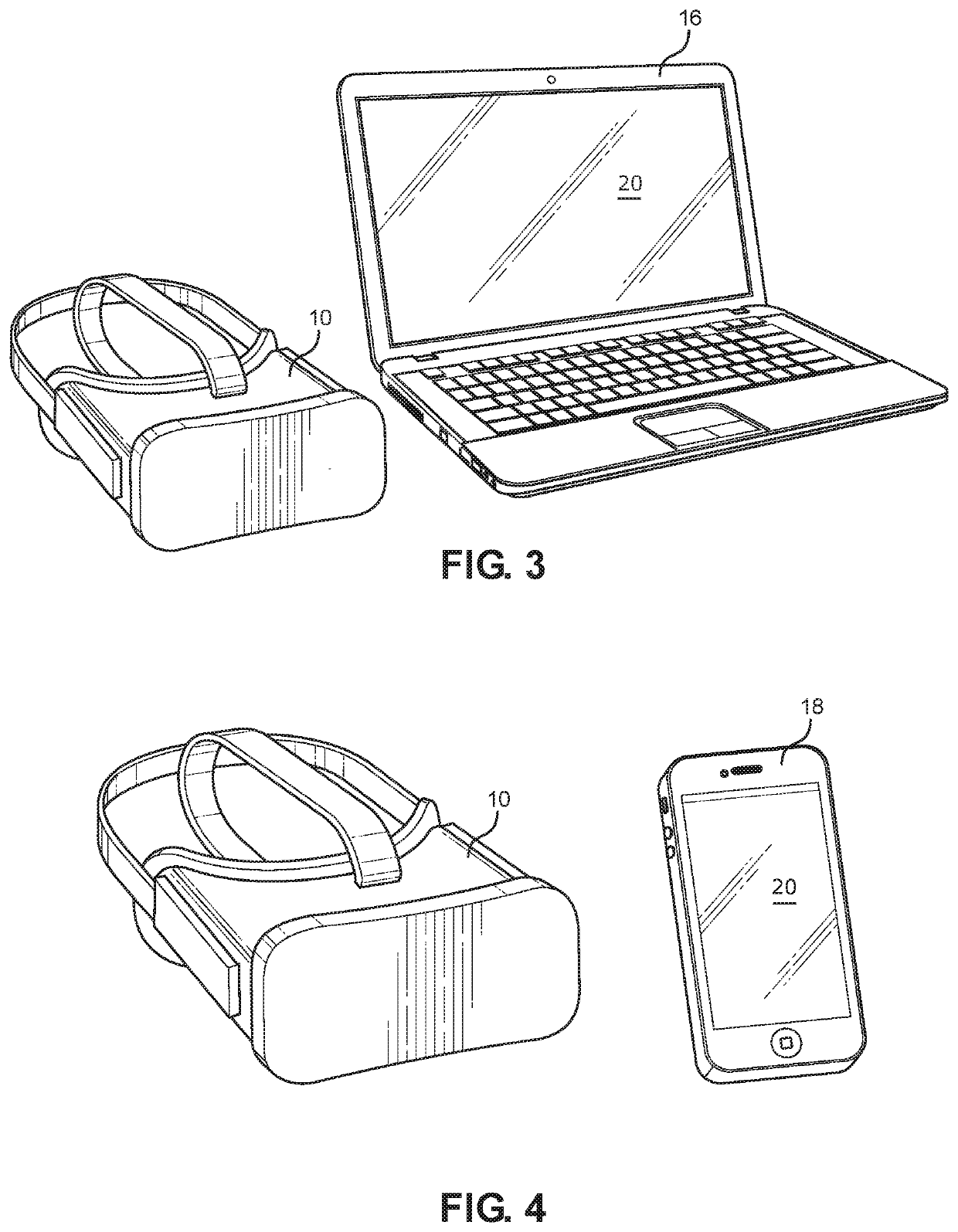

Virtual reality based visual field testing system

A visual field-testing system is provided. The visual field-testing system include a method utilizing a virtual reality output device operatively associated with a central fixation standard / static automated perimetry visual field test. The virtual reality output device is embodied in goggles providing stationary high design technology enabling a fixed axial length from the lens of each eye being tested, producing highly accurate and repeatable testing results.

Owner:LEWIS TRACEY LYNNE