Patents

Literature

44results about How to "Invention is limited" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

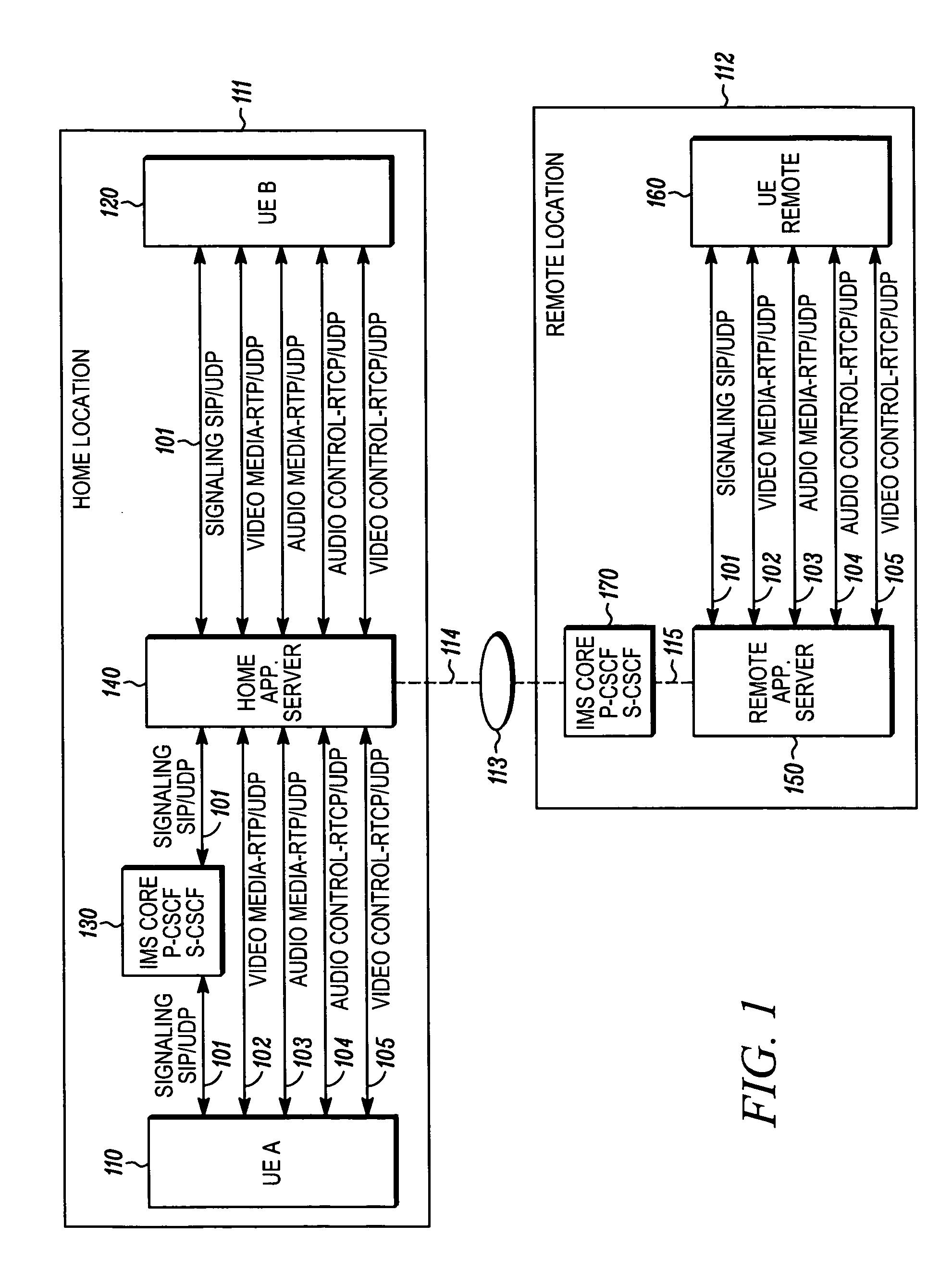

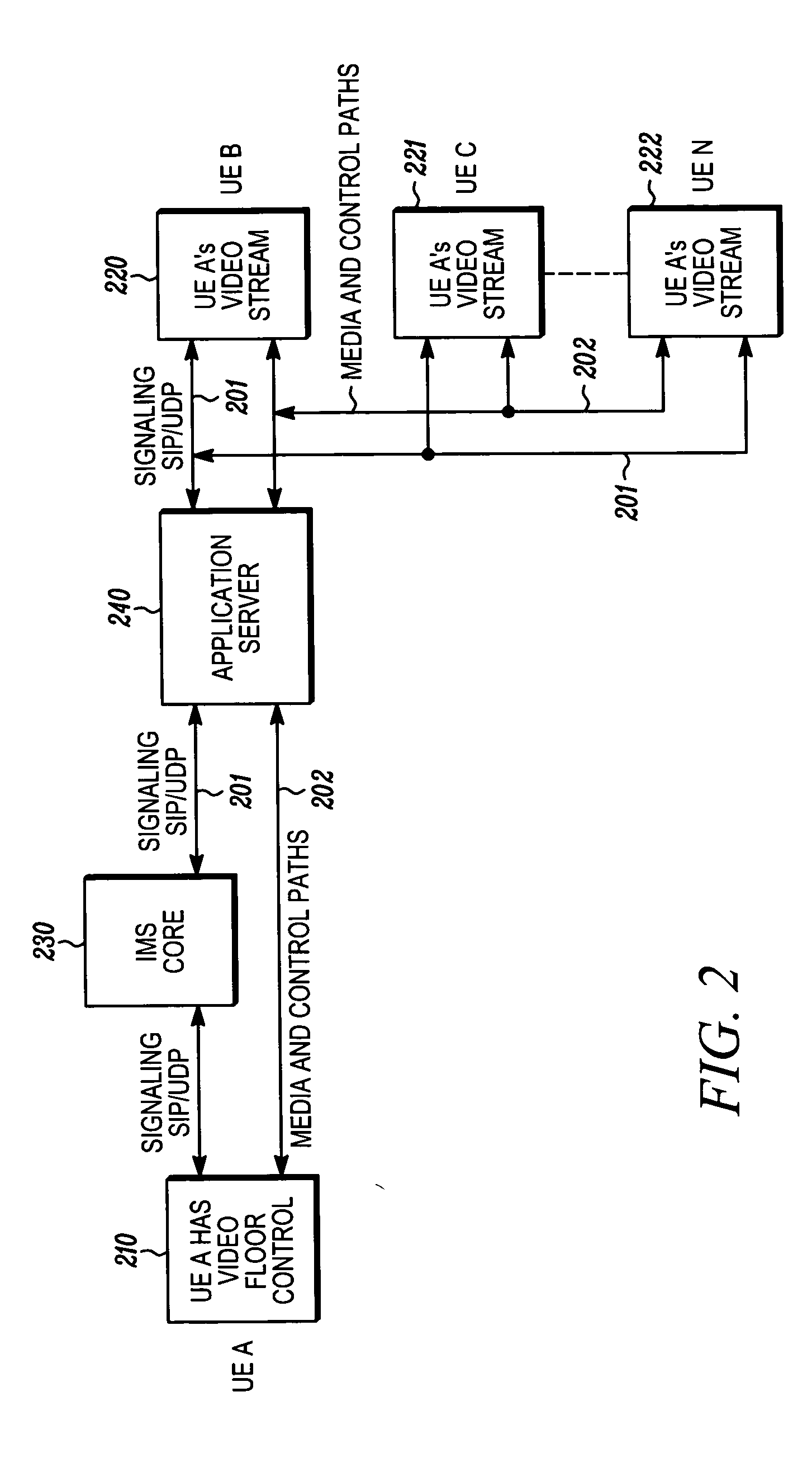

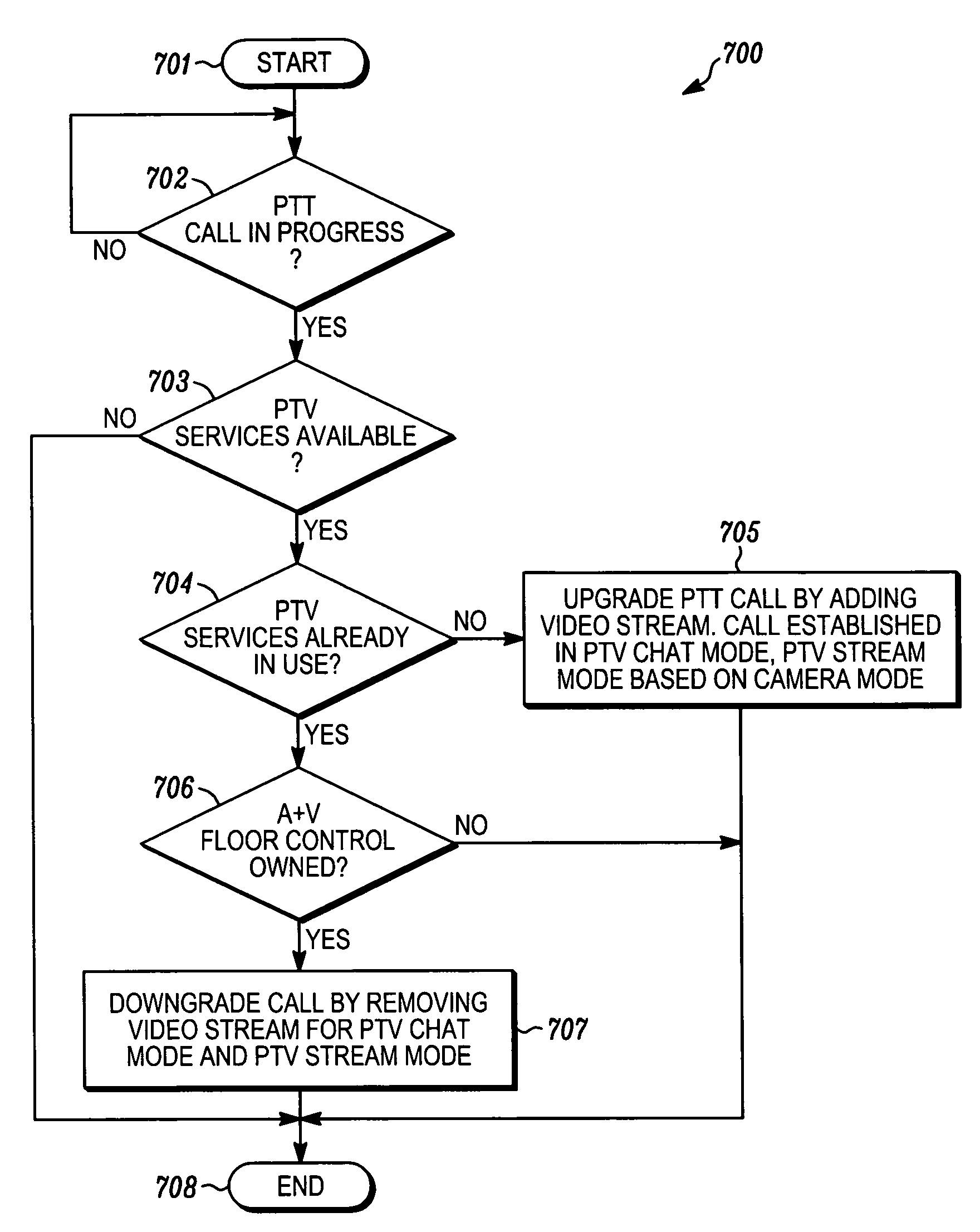

Push to video service mode selection using device settings

ActiveUS20060121924A1Improve appreciationInvention is limitedRadio transmissionTwo-way working systemsComputer networkCommunication unit

A method (600, 700) and apparatus (800) are described for selecting a Push to Video (PTV) service mode (303) allowing transmission of a video information stream (102) and a corresponding audio information stream (103) from an originating wireless communication unit (110) having floor control to a wireless target communication unit (120). Depending on a camera (420) setting, a desired PTV service mode is invoked when a PTV call is initiated by activating a PTV function.

Owner:GOOGLE TECH HLDG LLC

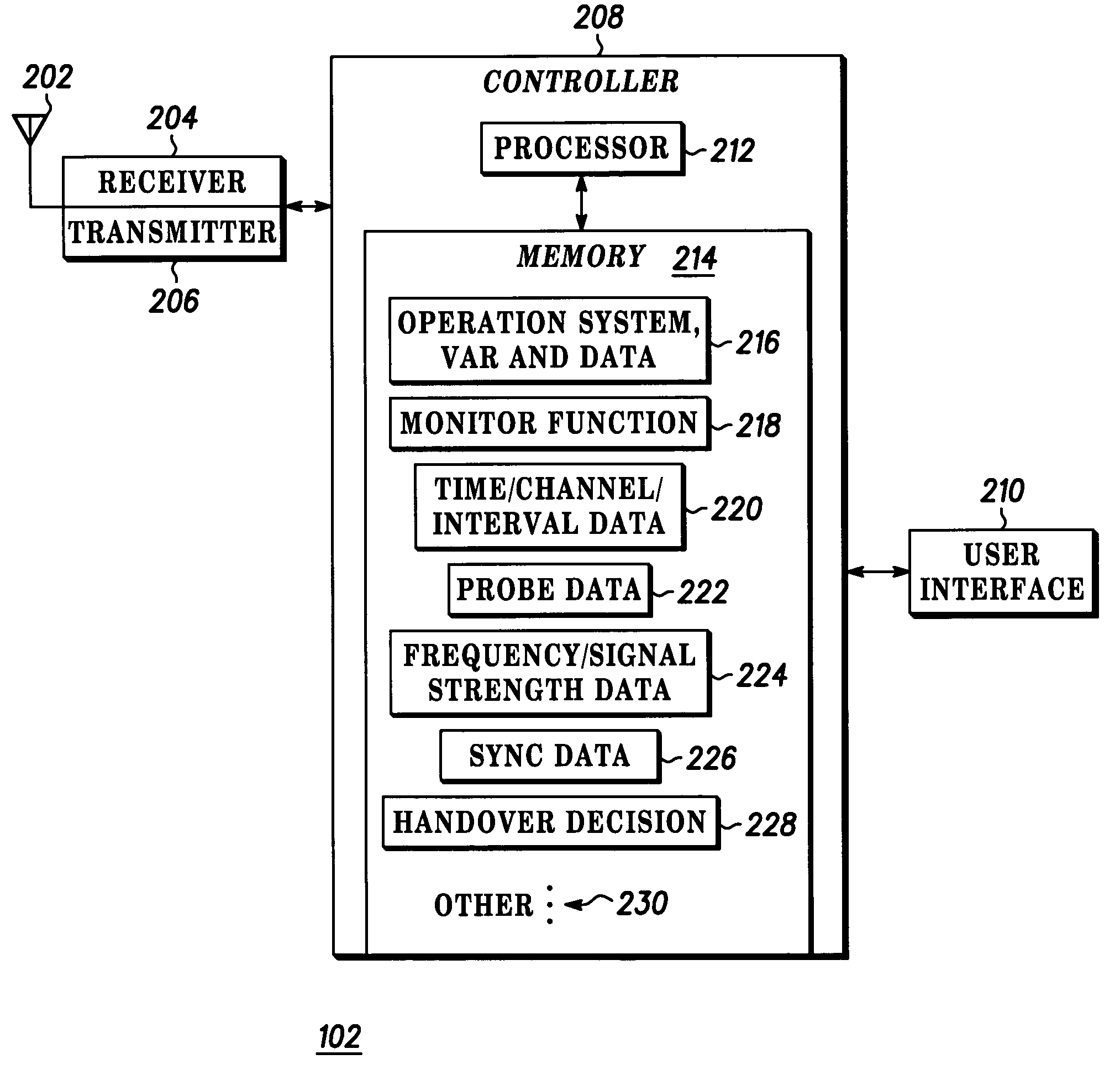

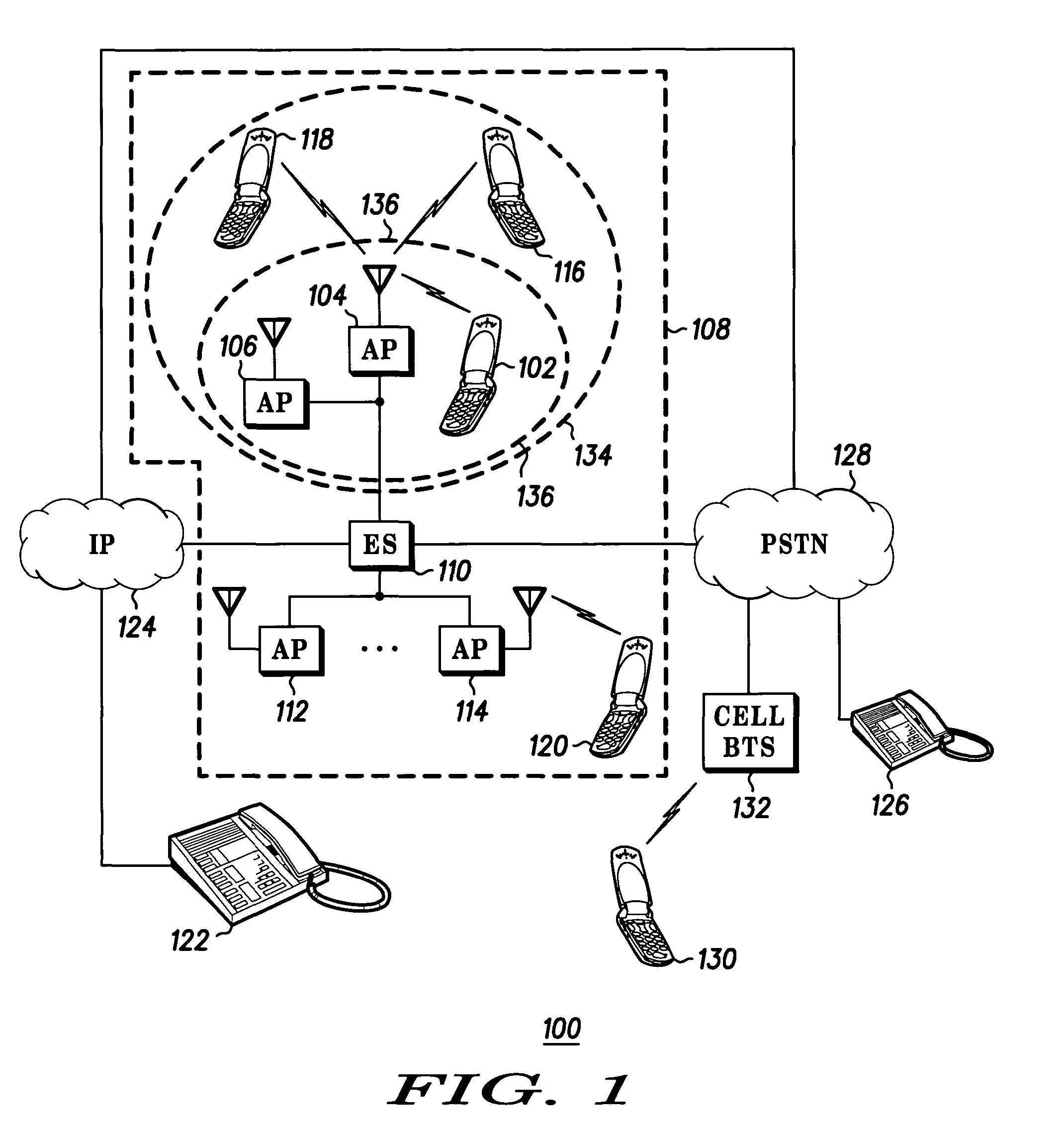

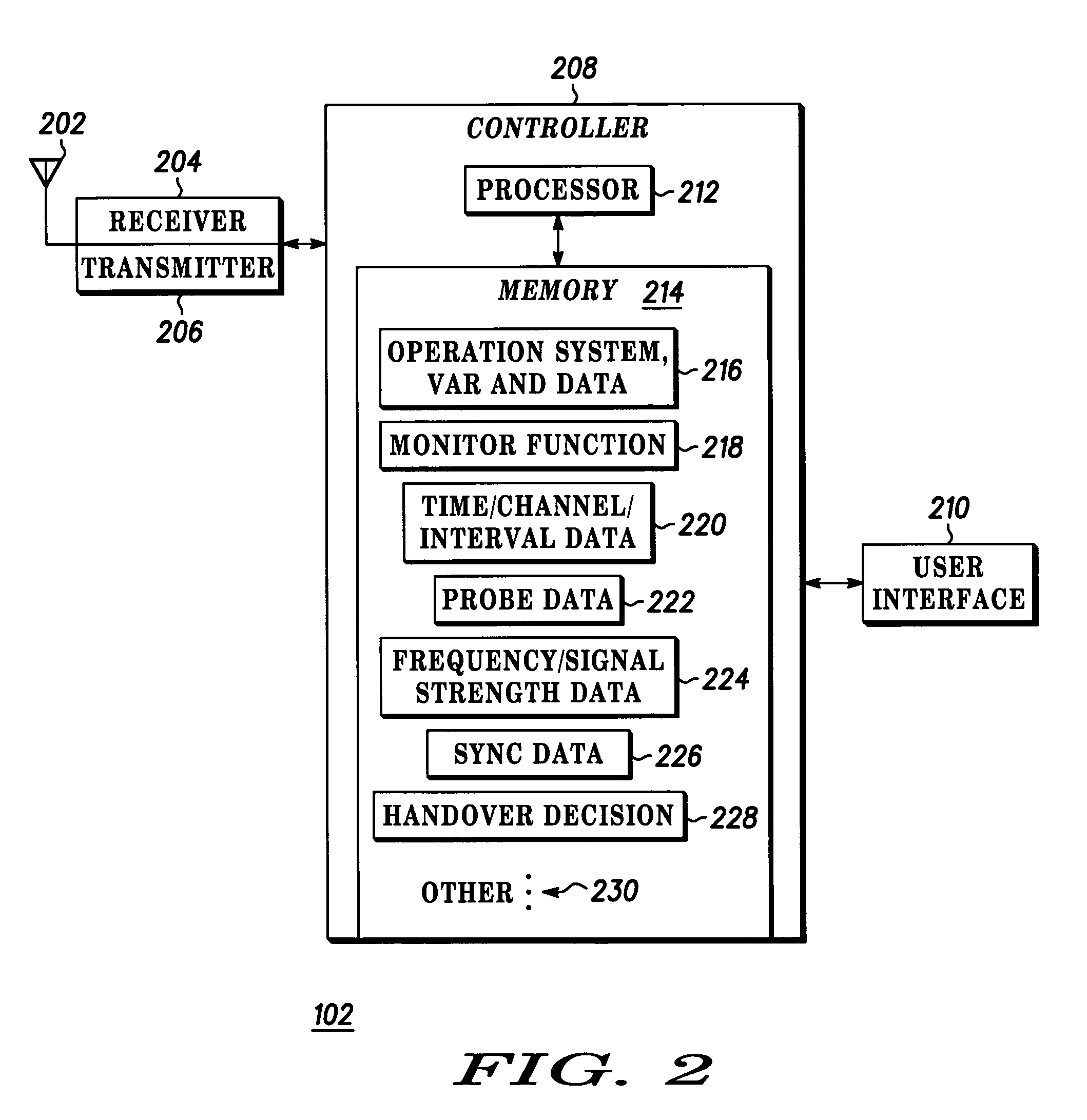

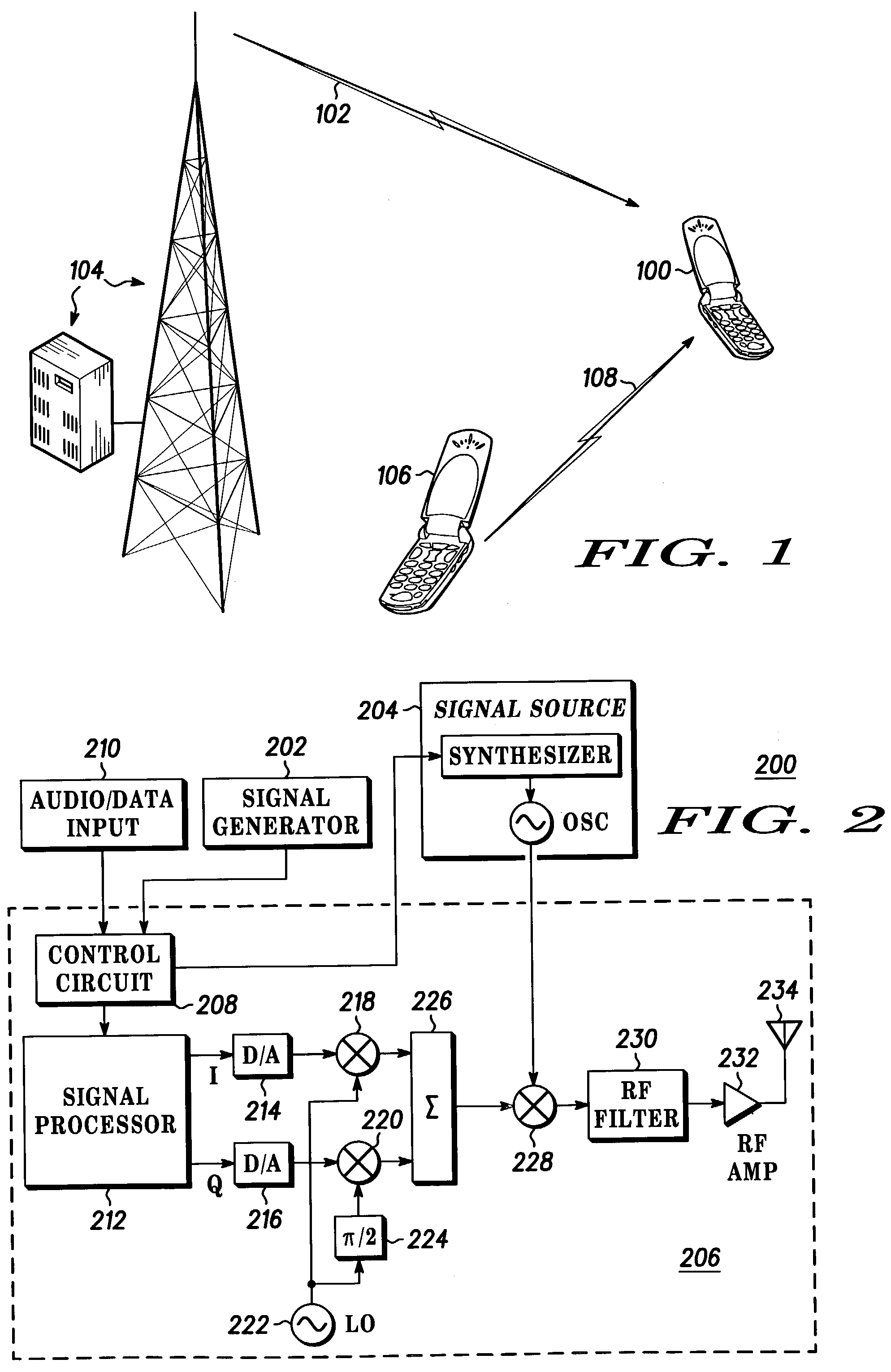

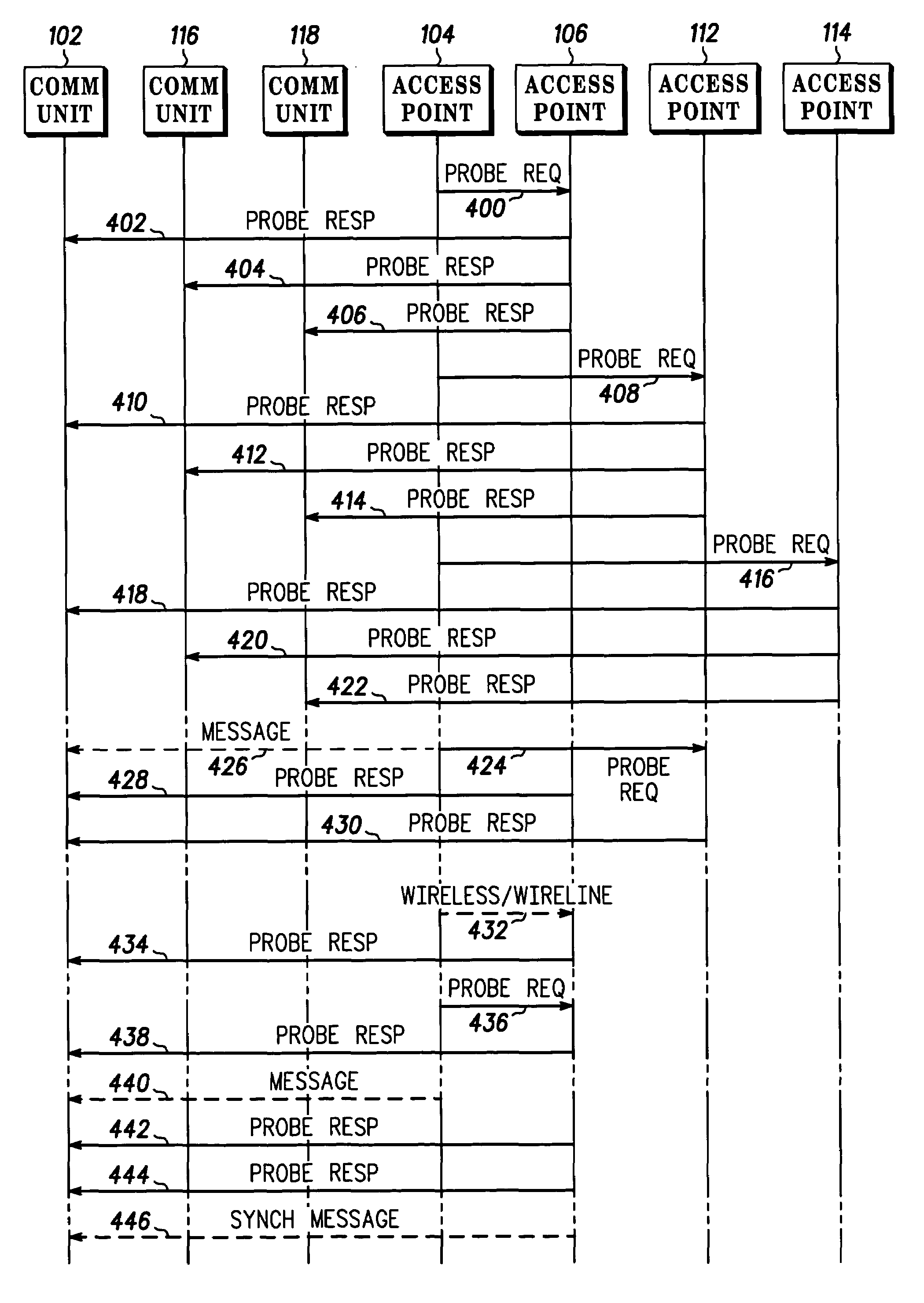

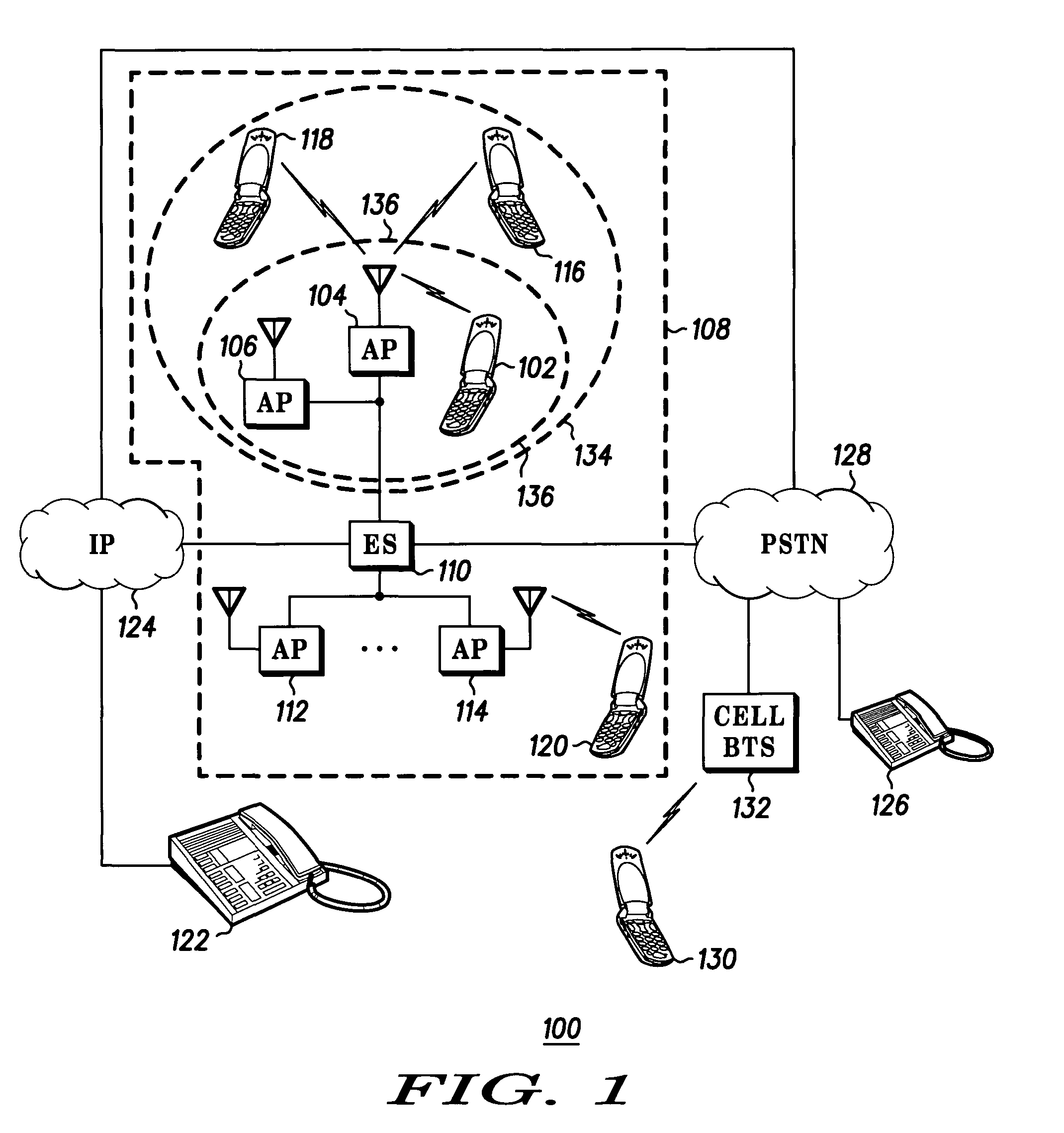

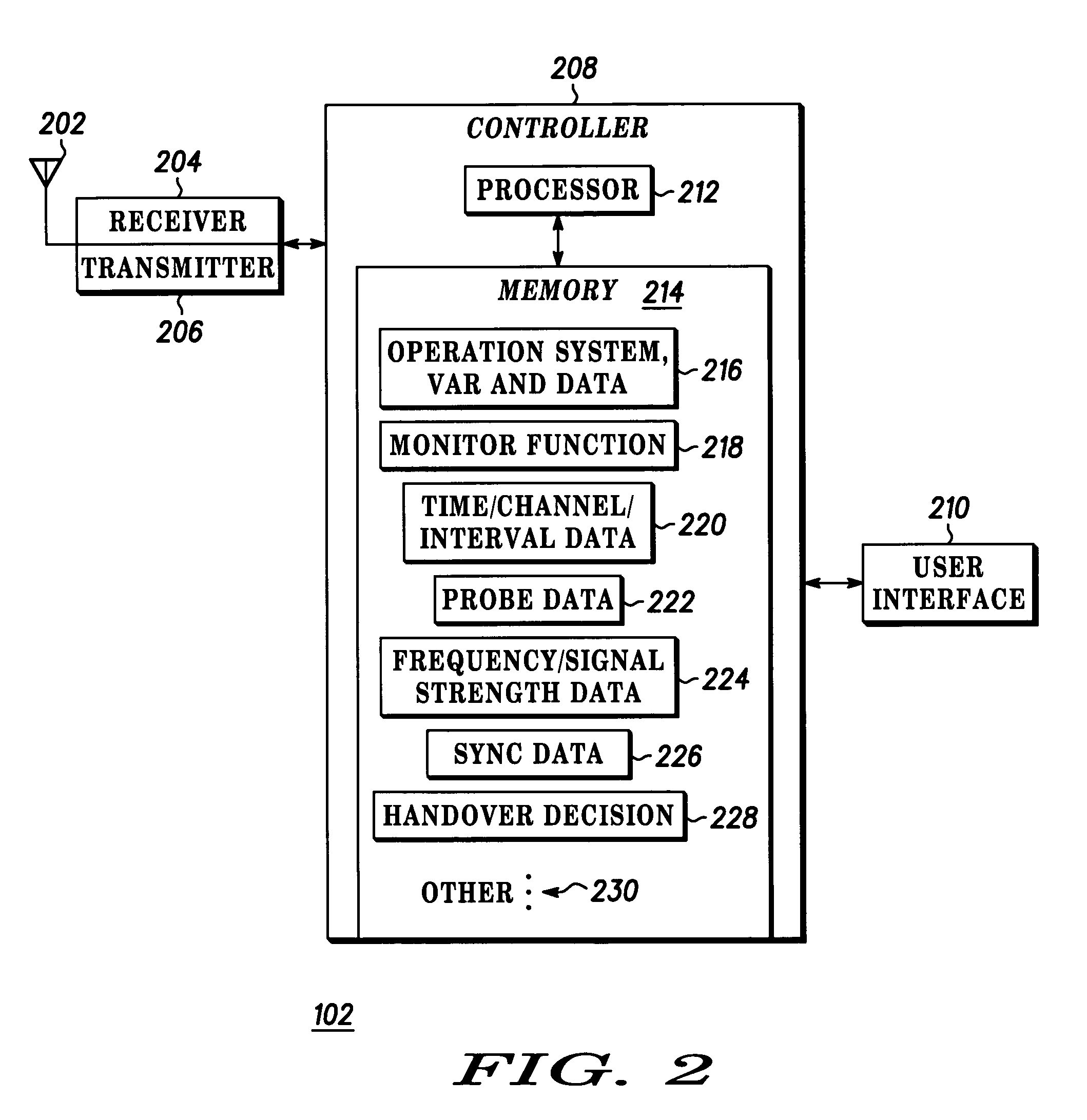

Passive probing for handover in a local area network

ActiveUS20050047371A1Improve appreciationInvention is limitedTime-division multiplexData switching by path configurationCommunication unitWireless lan

A WLAN (108) includes a first access point (104) for providing wireless service within a first coverage area, a second access point (106) for providing wireless service within a second coverage area and programmed to transmit probe responses, and a wireless communications unit (102) located within the first coverage area and operating on the wireless service of the first access point (104). The communications unit (102) is programmed to monitor, or passively probe, for the probe responses, or is instructed by the first access point (104) on when to monitor for the probe responses, transmitted by the second access point (106). By executing such passive probing, the communications unit (102) may make handover decisions for switching between the wireless service of the first access point (104) to the wireless service of the second access point (106) based on access point data included in the probe responses.

Owner:MOTOROLA SOLUTIONS INC

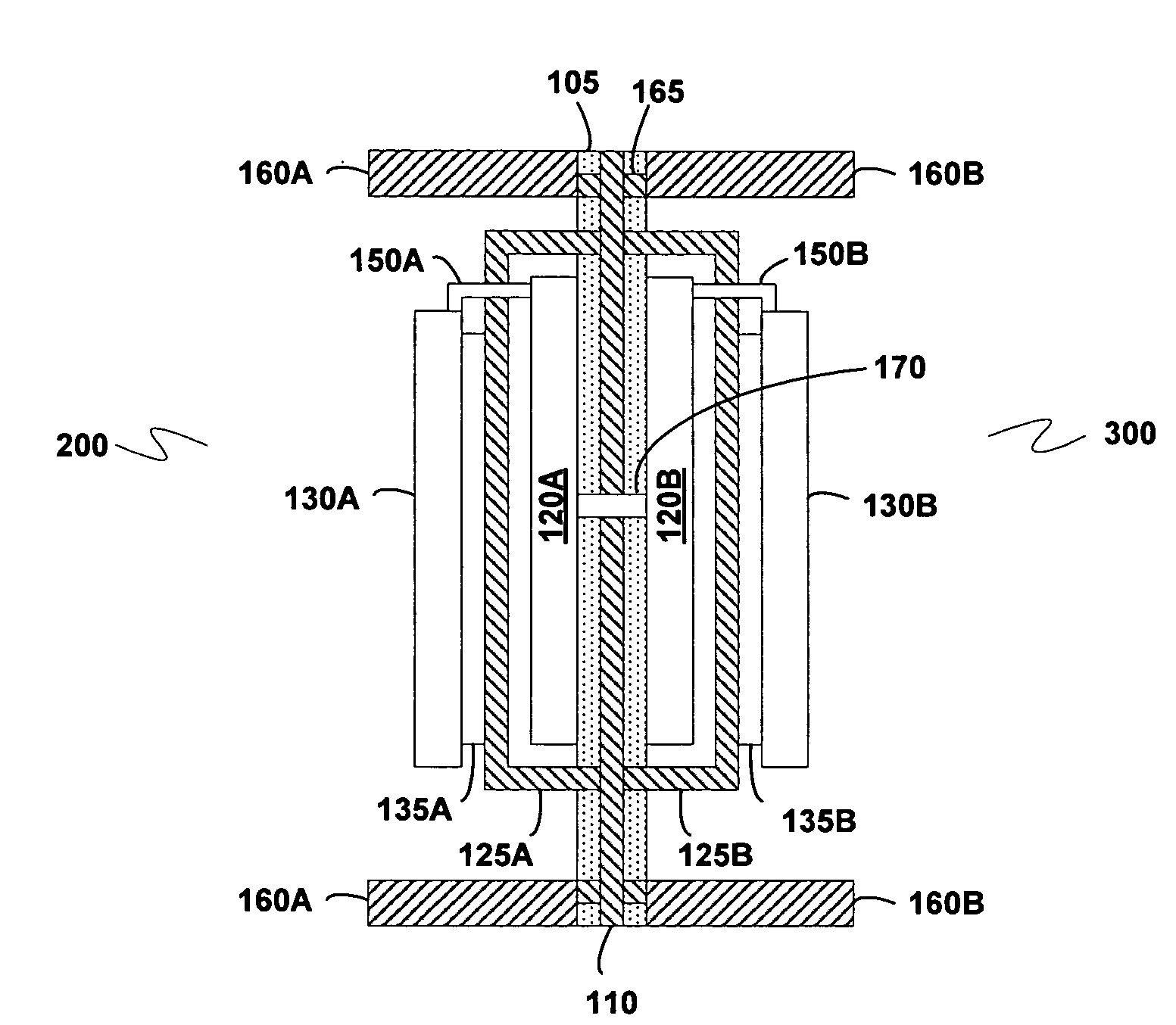

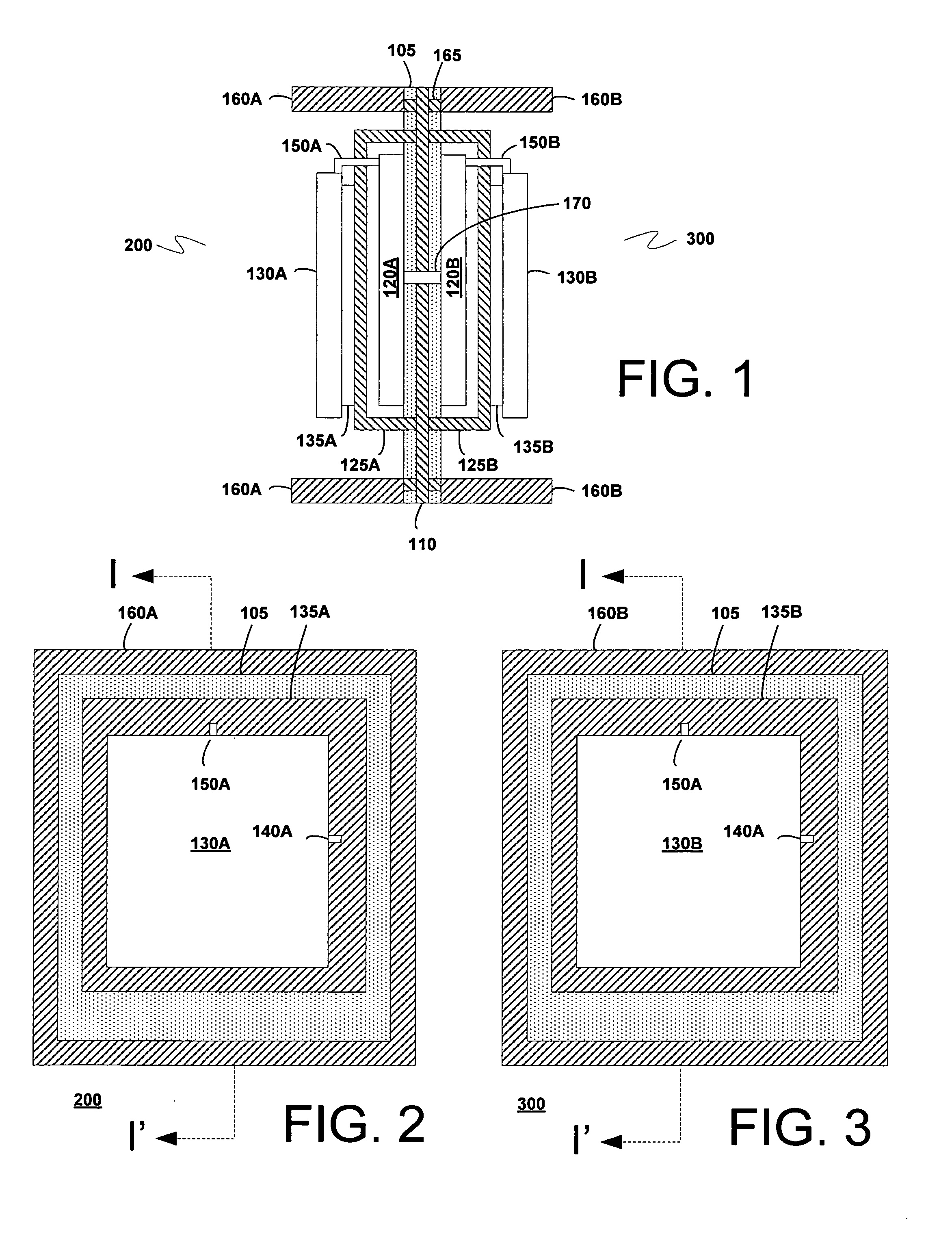

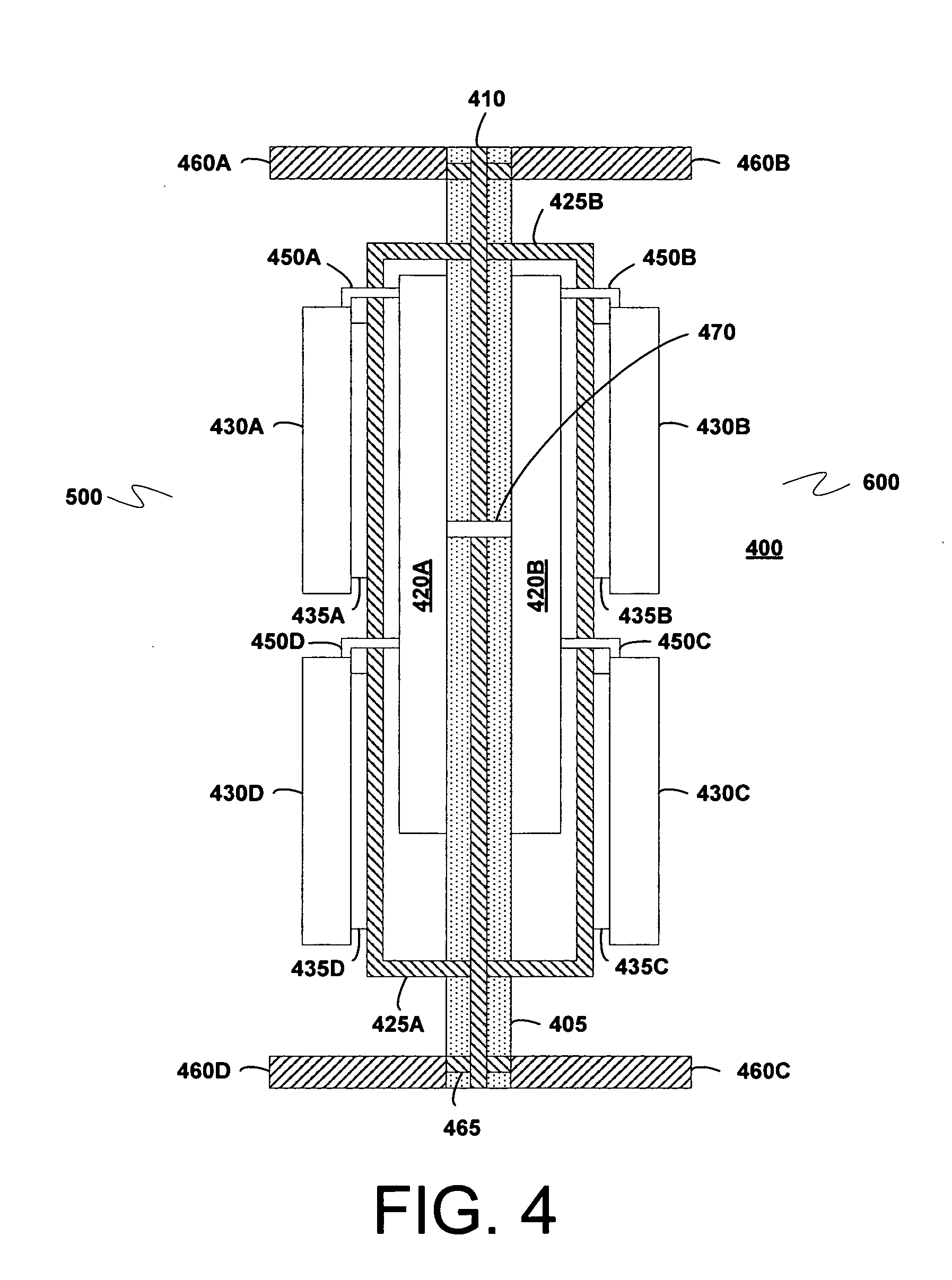

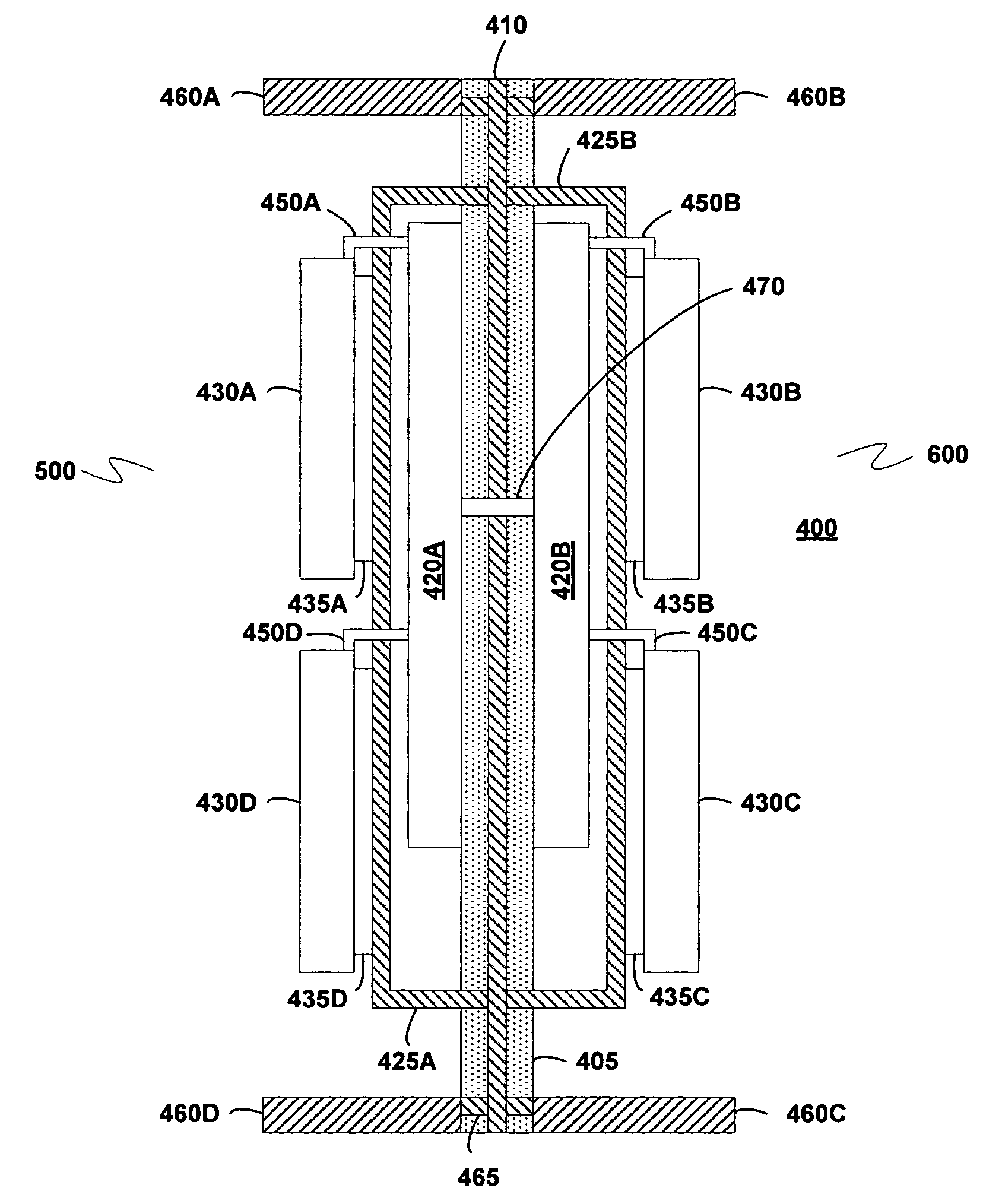

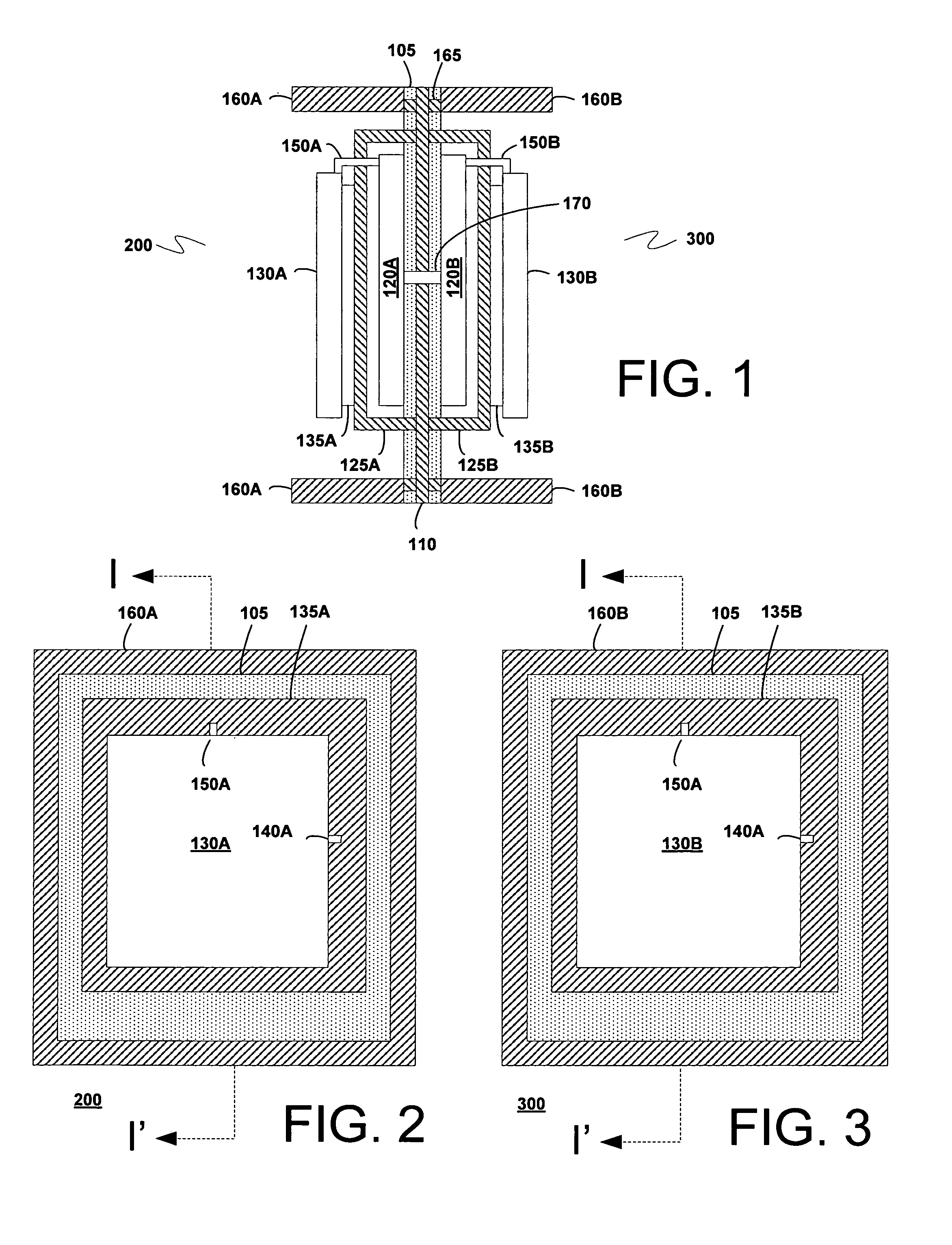

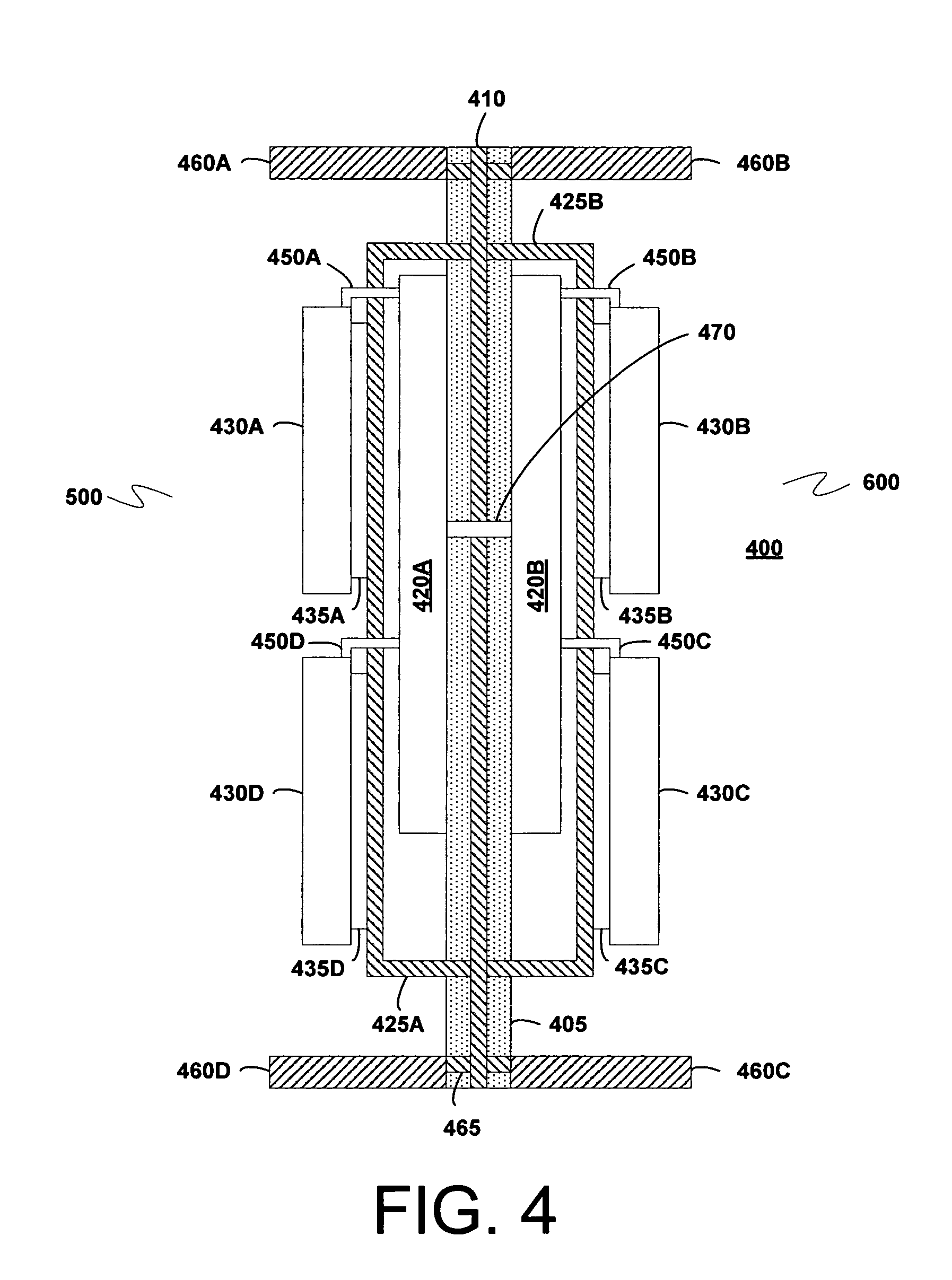

Multiple-antenna device having an isolation element

ActiveUS20080136736A1Improve appreciationInvention is limitedSimultaneous aerial operationsAntenna supports/mountingsGround planePrinted circuit board

A multiple-antenna device is provided, comprising: a printed circuit board having a ground plane configured to provide electromagnetic isolation between a first side of the printed circuit board and a second side of the printed circuit board; a first non-conductive support member formed over the first side of the printed circuit board; a second non-conductive support member formed over the second side of the printed circuit board; a first antenna formed over the first non-conductive support member; and a second antenna formed over the second non-conductive support member, wherein the first antenna is electrically connected to a first feed point on a first portion of the printed circuit board that is not connected to the ground plane, and wherein the second antenna is electrically connected to a second feed point on a second portion of the printed circuit board that is not connected to the ground plane.

Owner:QUALCOMM INC

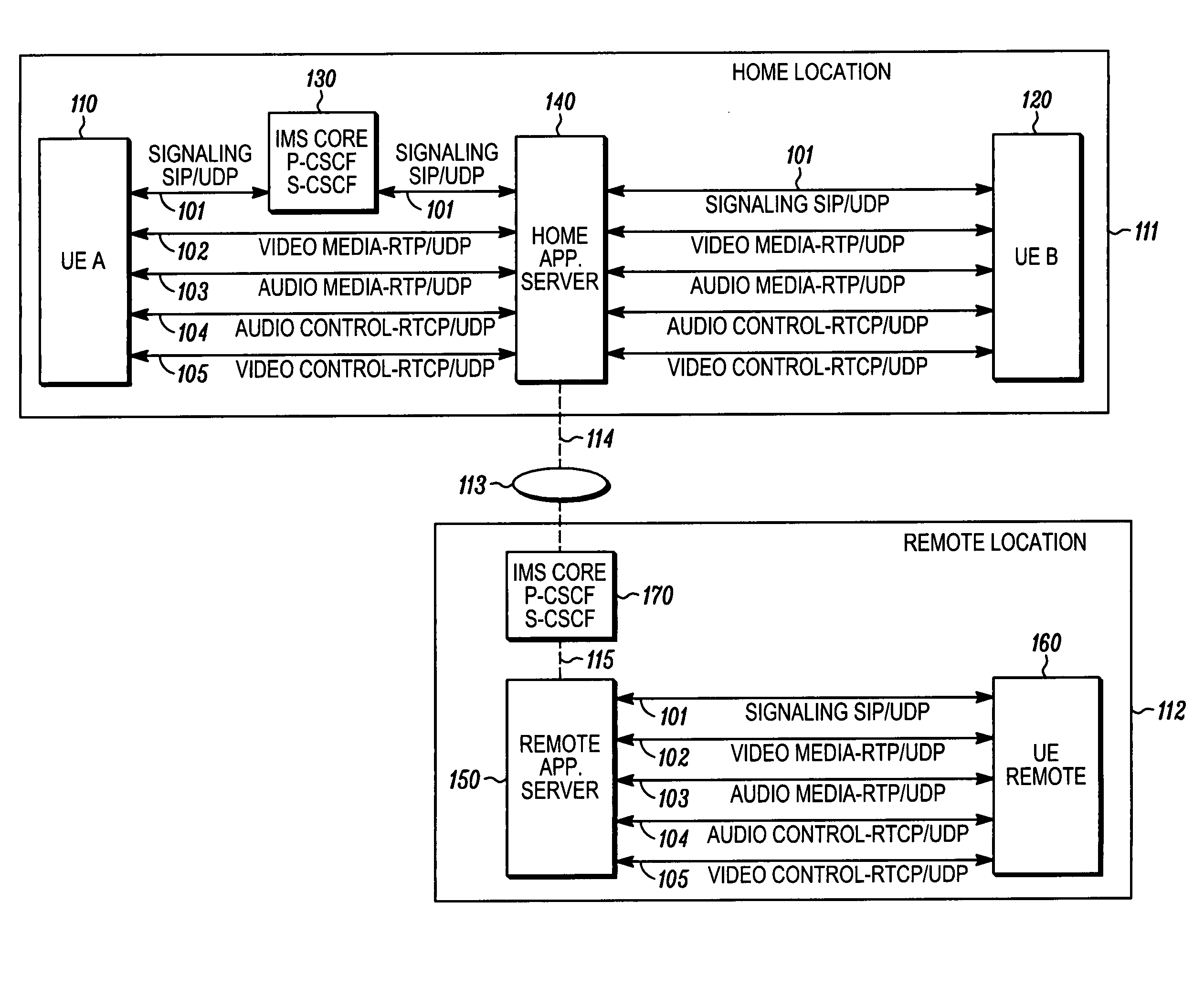

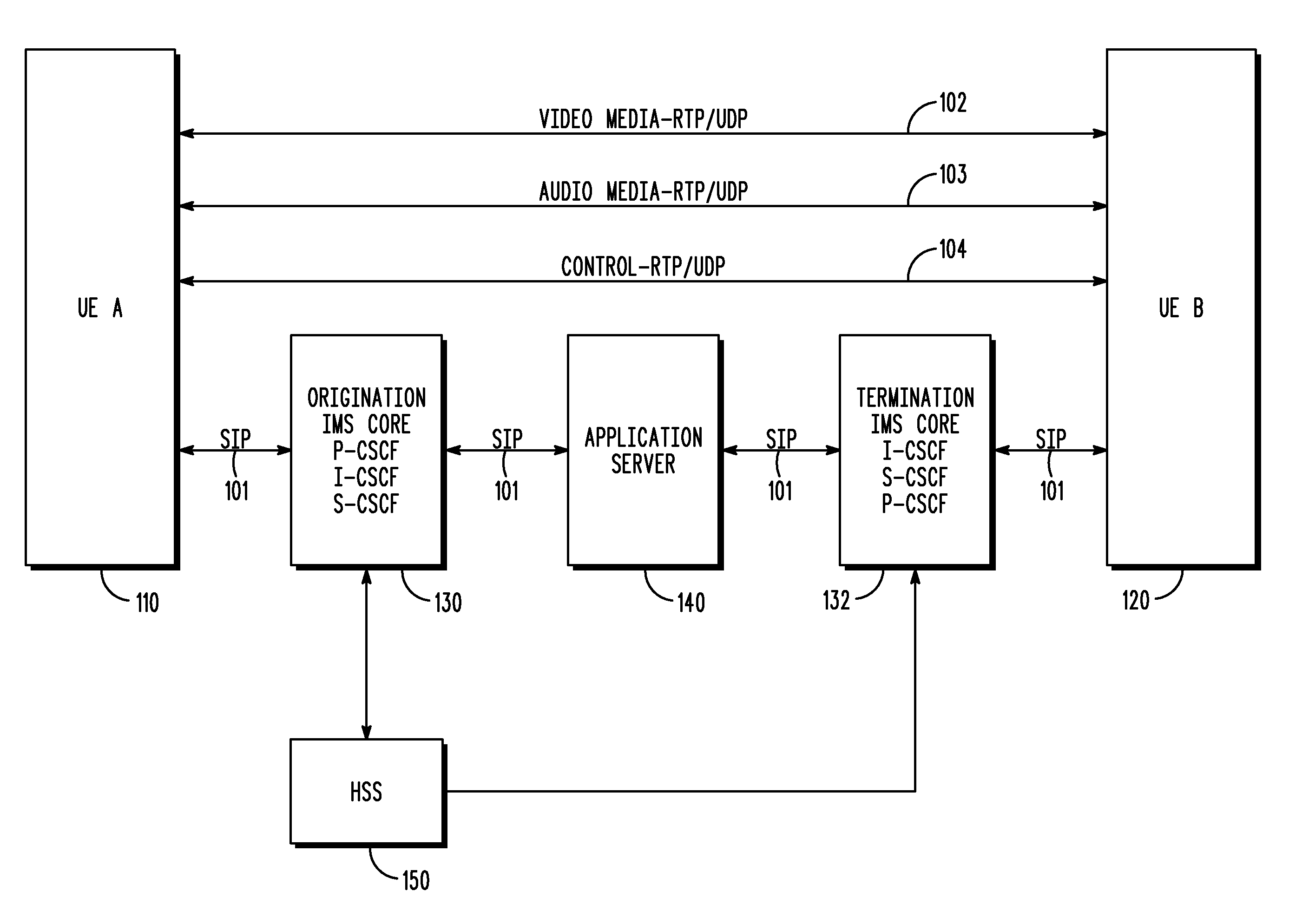

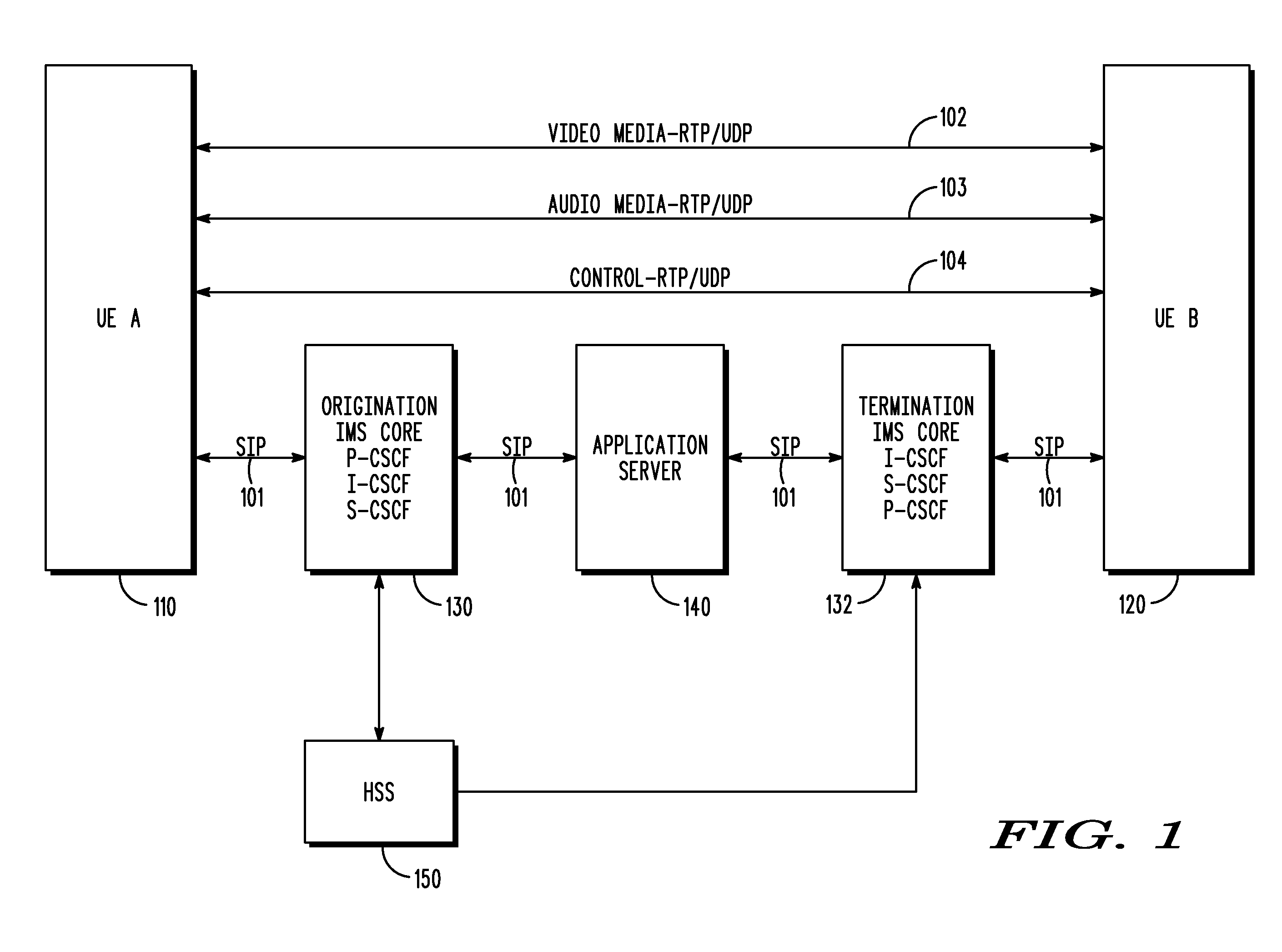

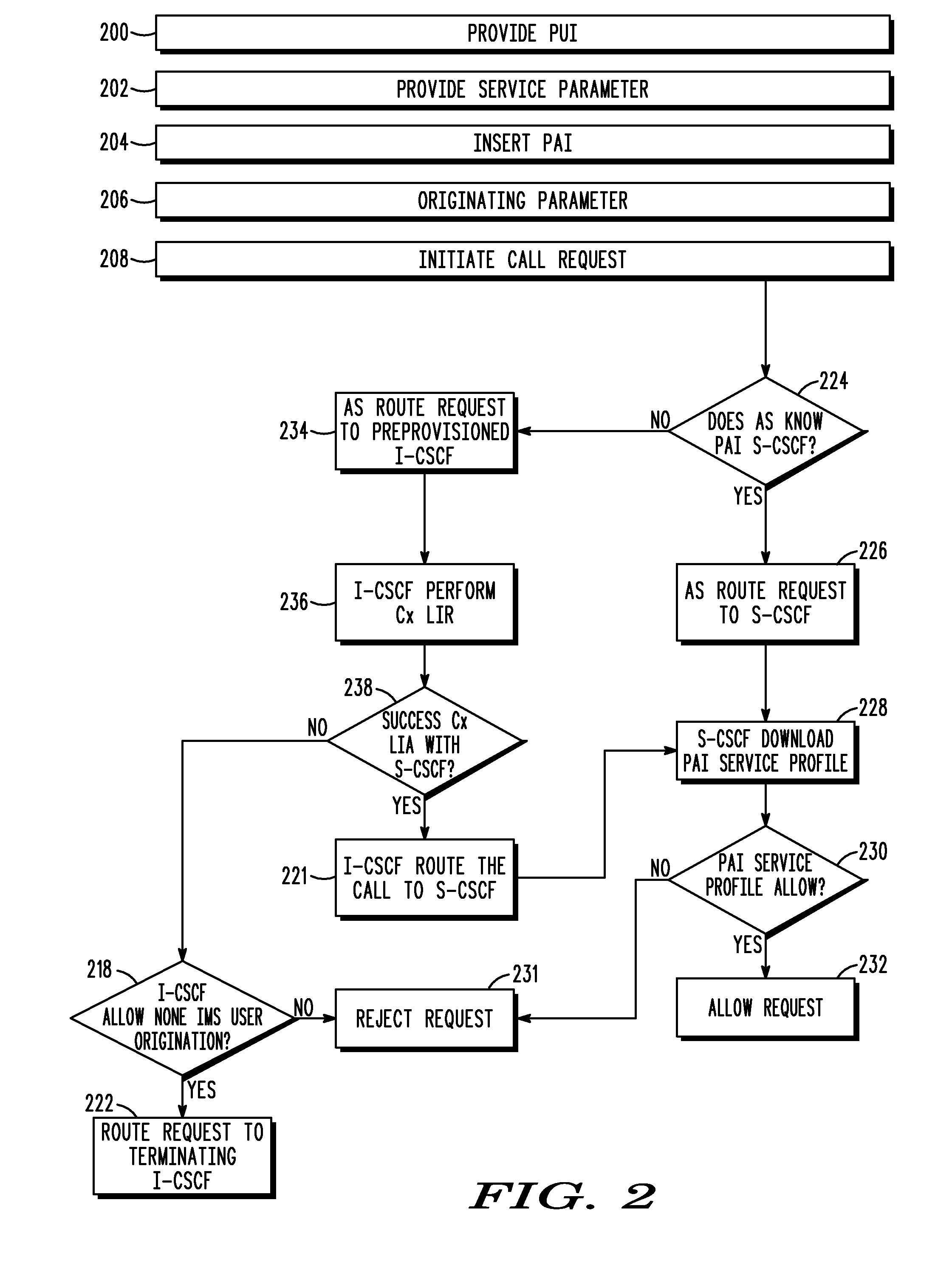

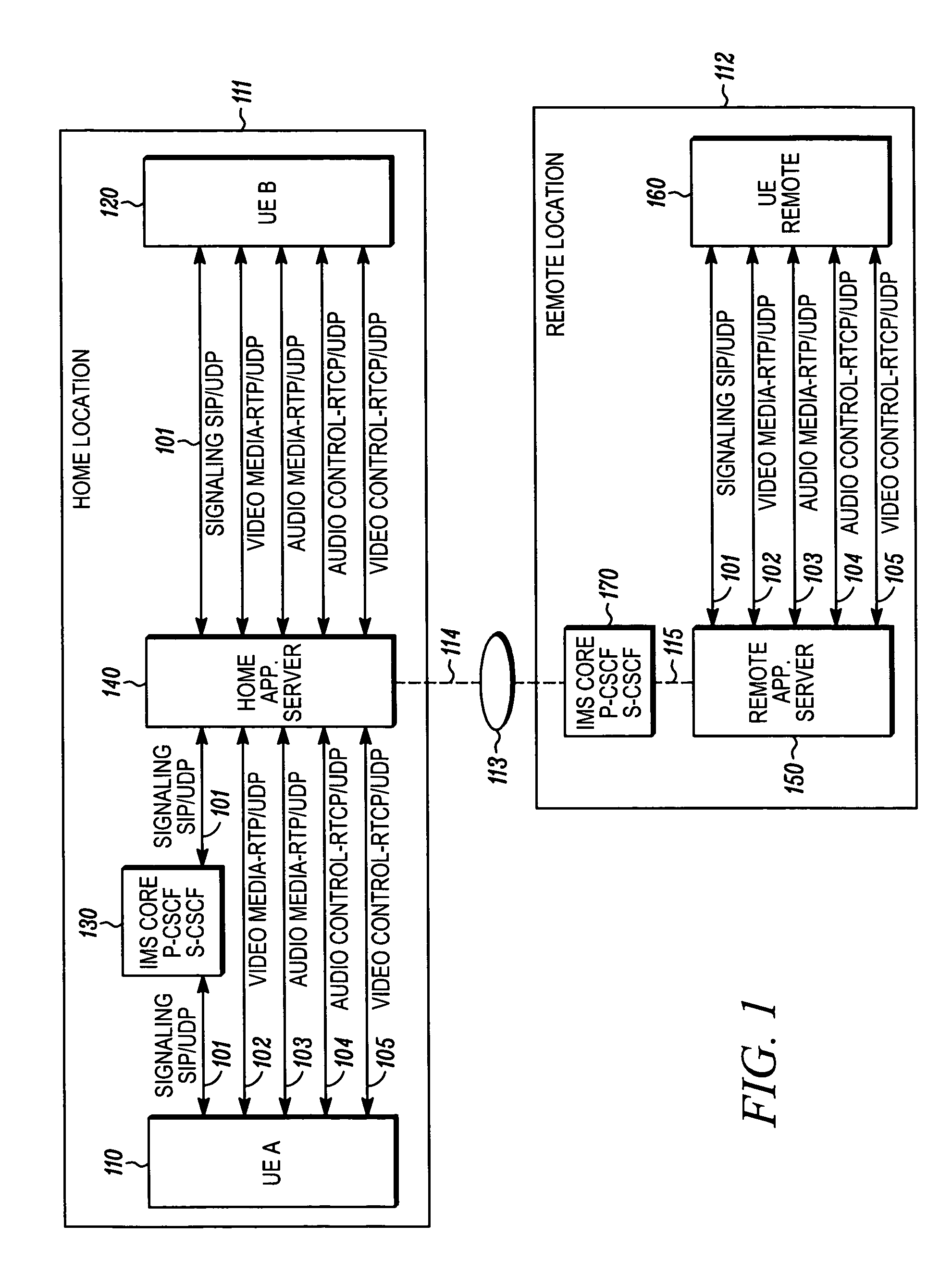

Call origination by an application server in an internet protogol multimedia core network subsystem

InactiveUS20090103518A1Improve appreciationInvention is limitedWireless network protocolsNetwork connectionsService profileTTEthernet

A system and method for call origination by an application server in an internet protocol multimedia core network subsystem includes a first step of providing a public user identity for a user. A next step includes storing a service parameter in a service profile of the user, the service parameter indicating whether to allow / disallow the application server to initiate call requests on behalf of the public user identity. If the service parameter allows the application server to initiate call requests, the system unblocks calls originated by the application server on behalf of the user. If the service parameter disallows the application server to initiate call requests, the system blocks calls originated by the application server on behalf of the user.

Owner:MOTOROLA MOBILITY LLC

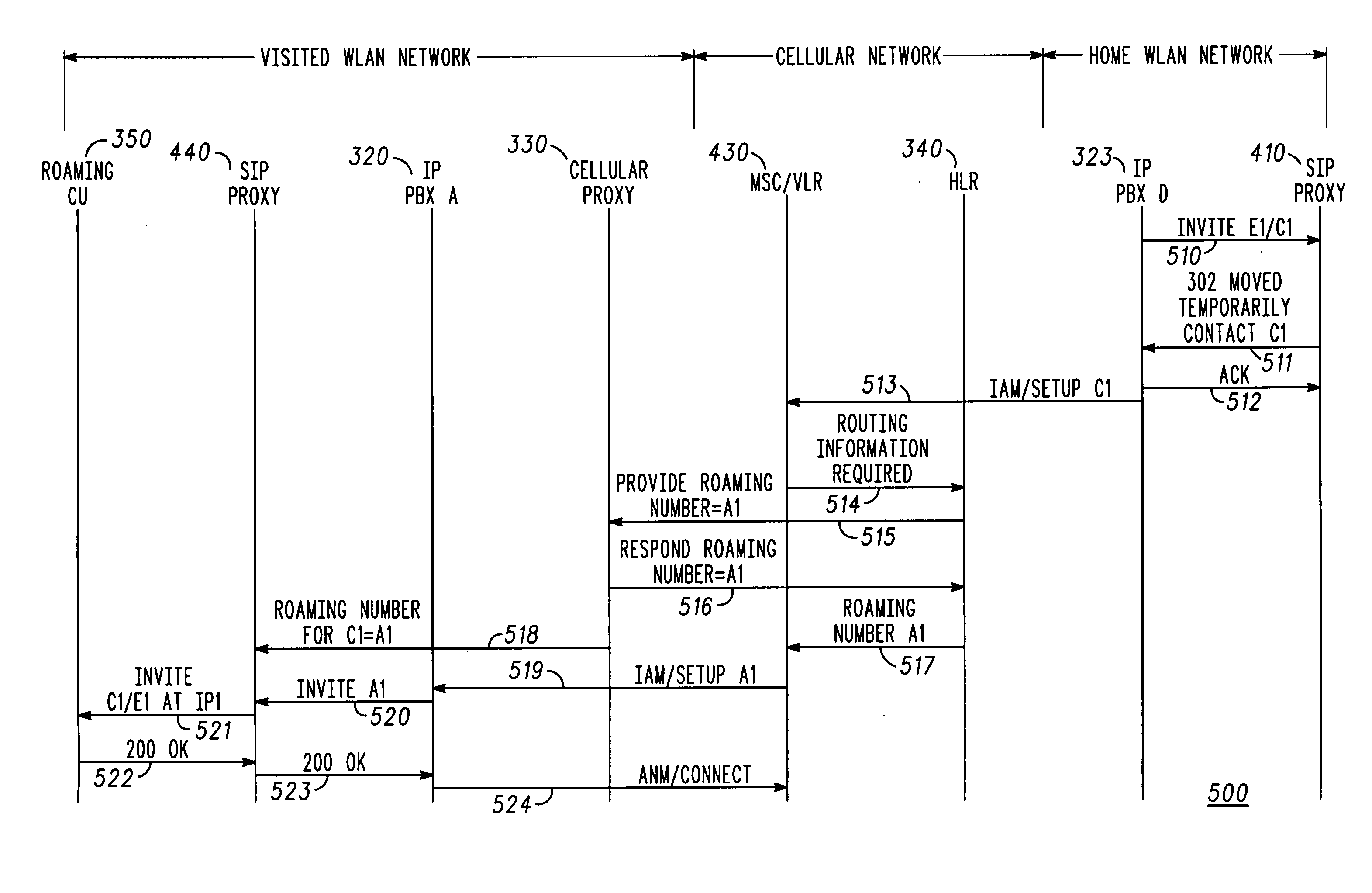

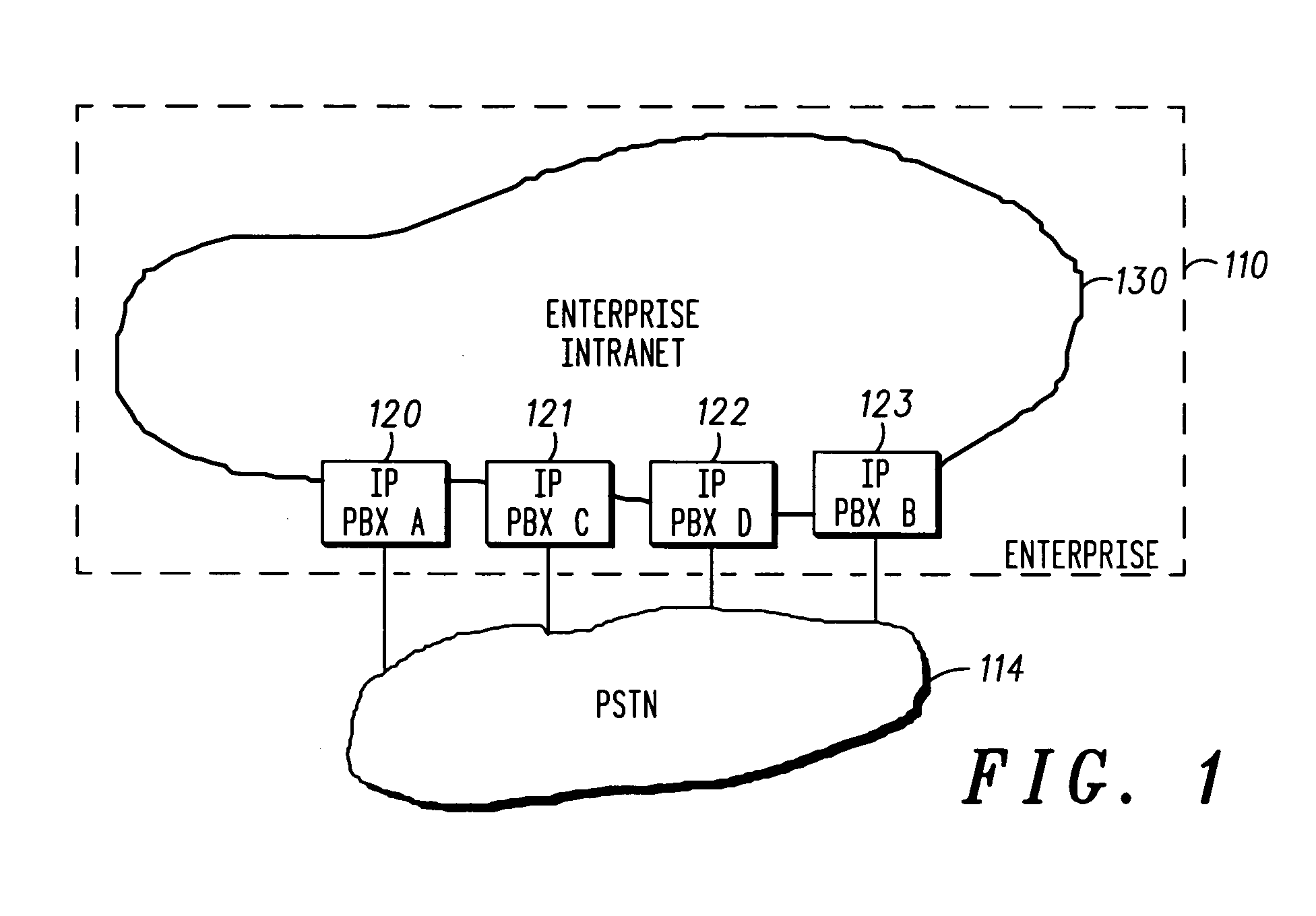

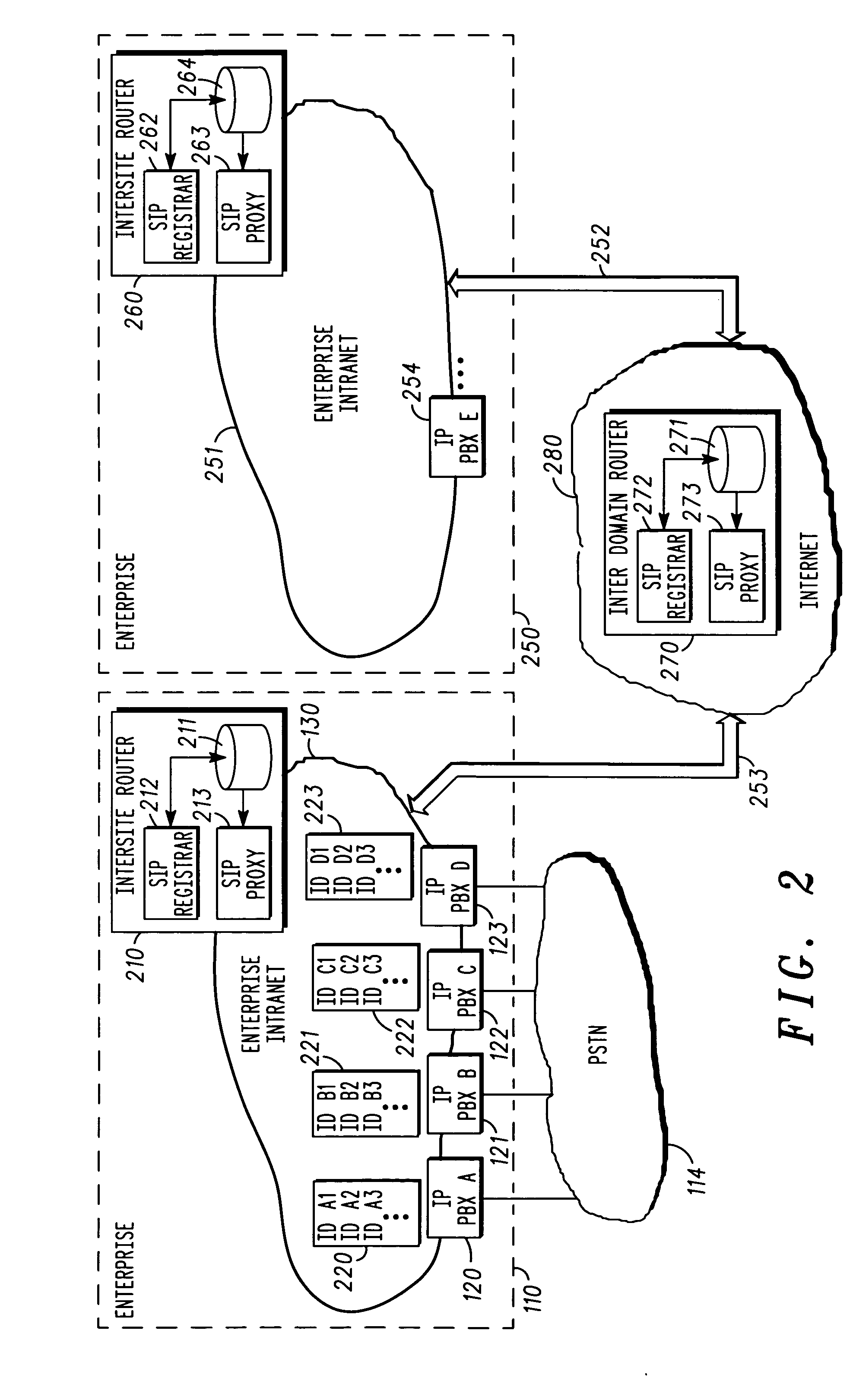

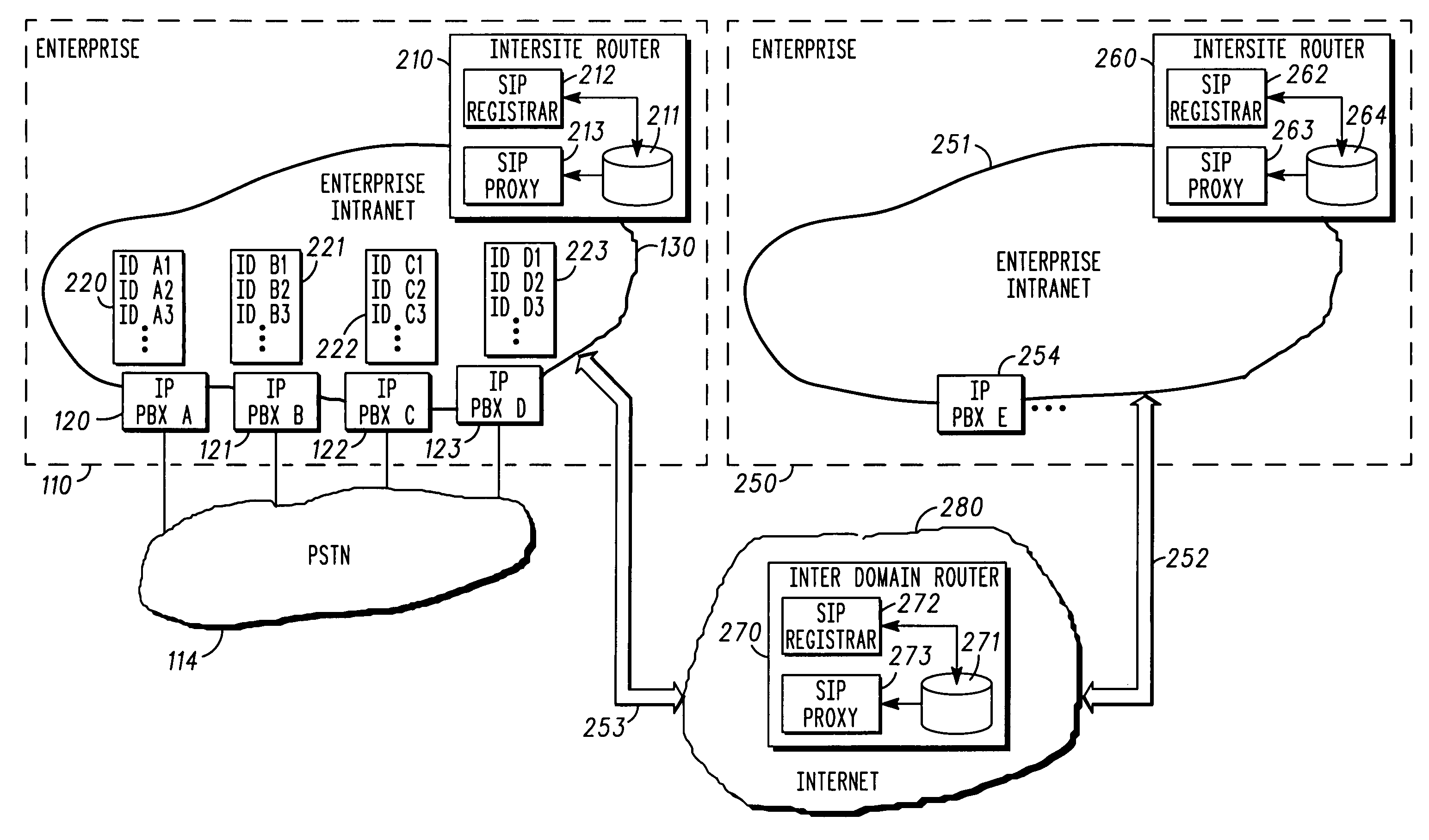

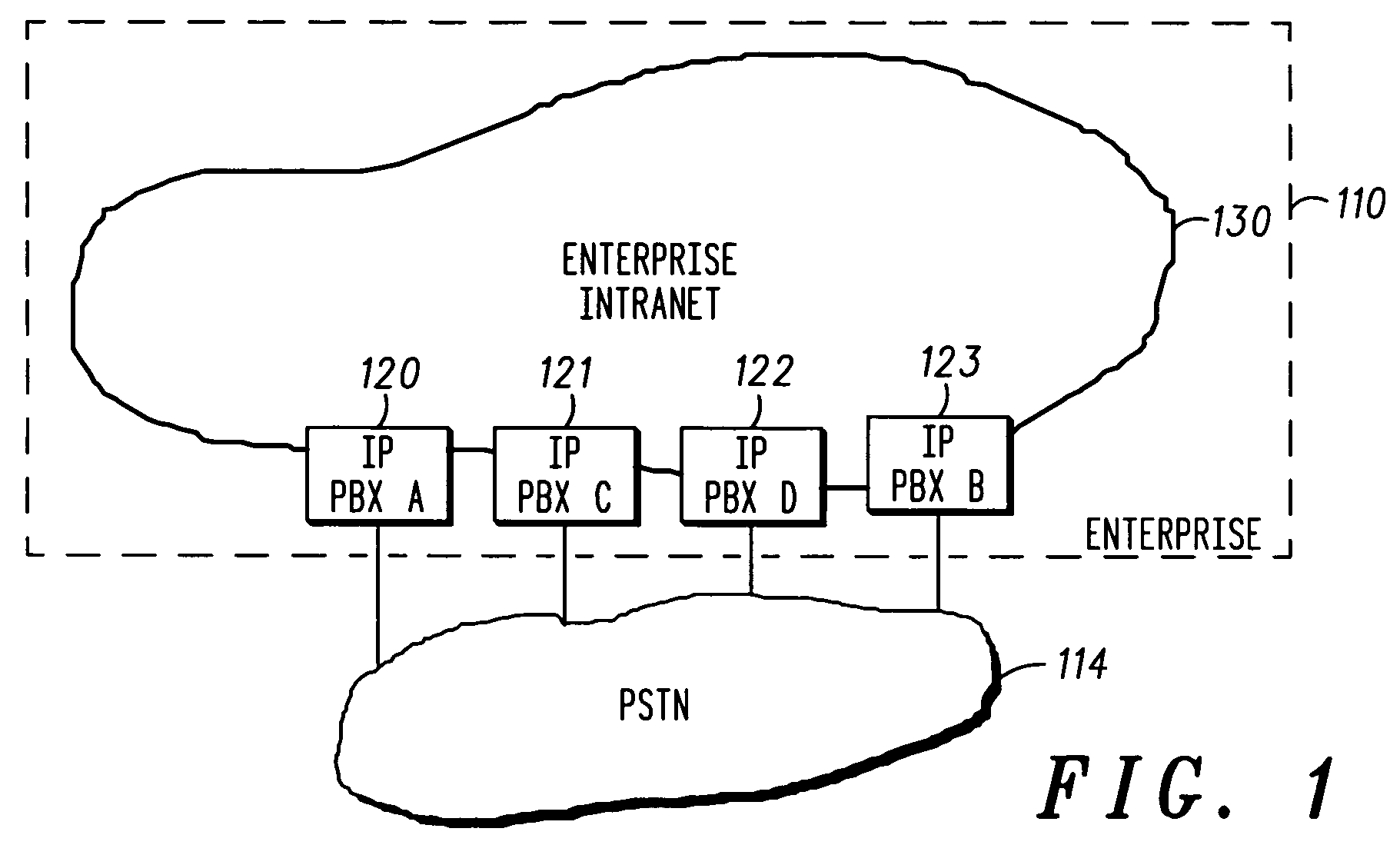

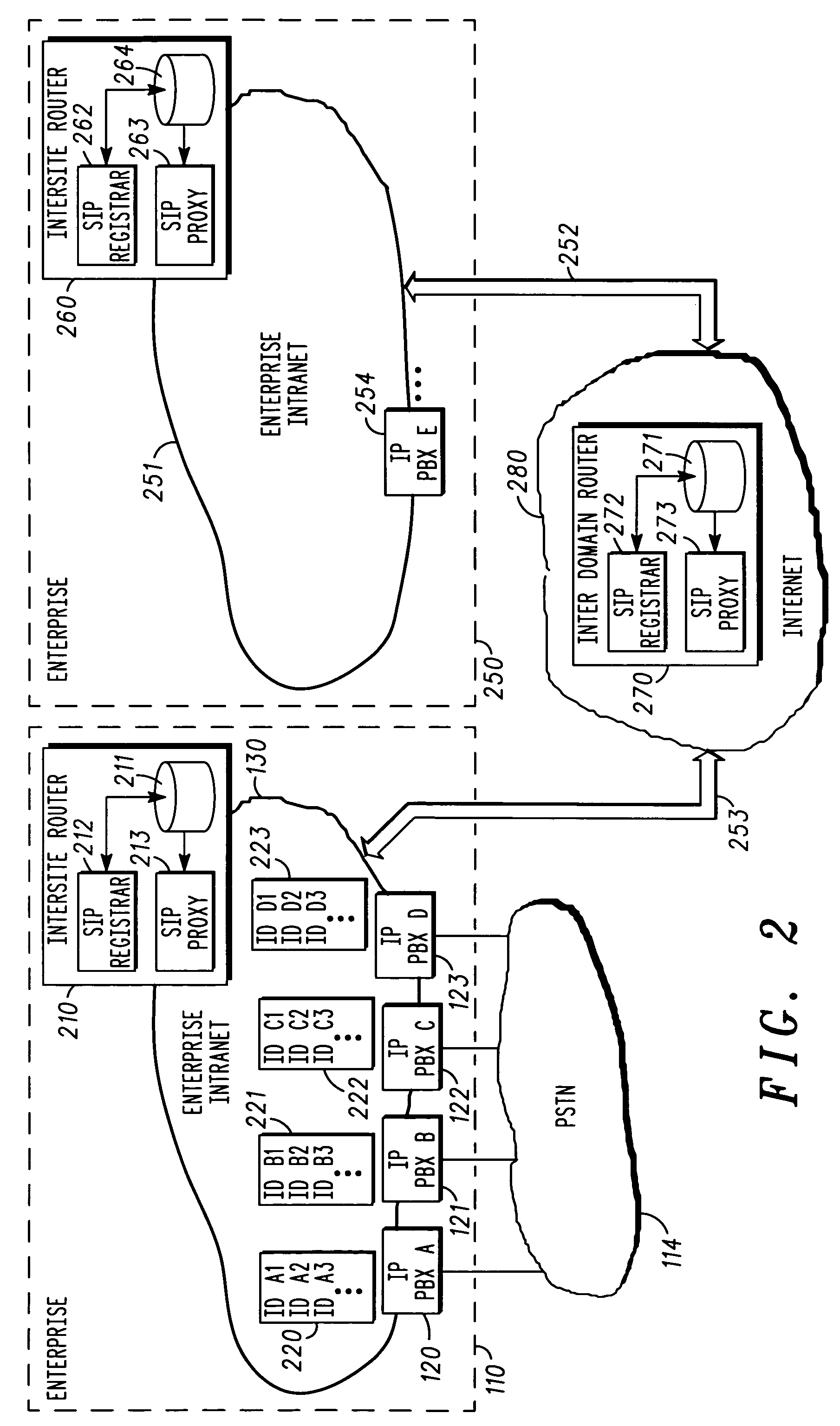

Inter-site call routing and roaming support

ActiveUS20050282543A1Improve appreciationInvention is limitedInterconnection arrangementsError preventionTelecommunicationsCommunication unit

A method (600,700) and apparatus (800) are arranged and operate for facilitating call routing between sites in an enterprise connected by a private IP network (130). A range of identifiers (220-223) served by IP PBXs (120-123) in the enterprise may be registered with a SIP registrar (212) of an inter-site router (210). Call requests to a communication unit (350) outside the home site are routed to the SIP registrar. A site identifier associated with the destination IP PBX allows the call to be completed by the SIP Proxy or the IP PBX where the call was received. When no private IP network is available, a roaming CU registers with a cellular proxy in the visited network. Calls are routed by when an HLR (340) associated with the CU obtains the roaming number from the cellular proxy (330) in the visited site. The MSC completes the call to the visited IP PBX using the roaming number and a local SIP registrar 440 forwards the call to the CU.

Owner:MOTOROLA SOLUTIONS INC

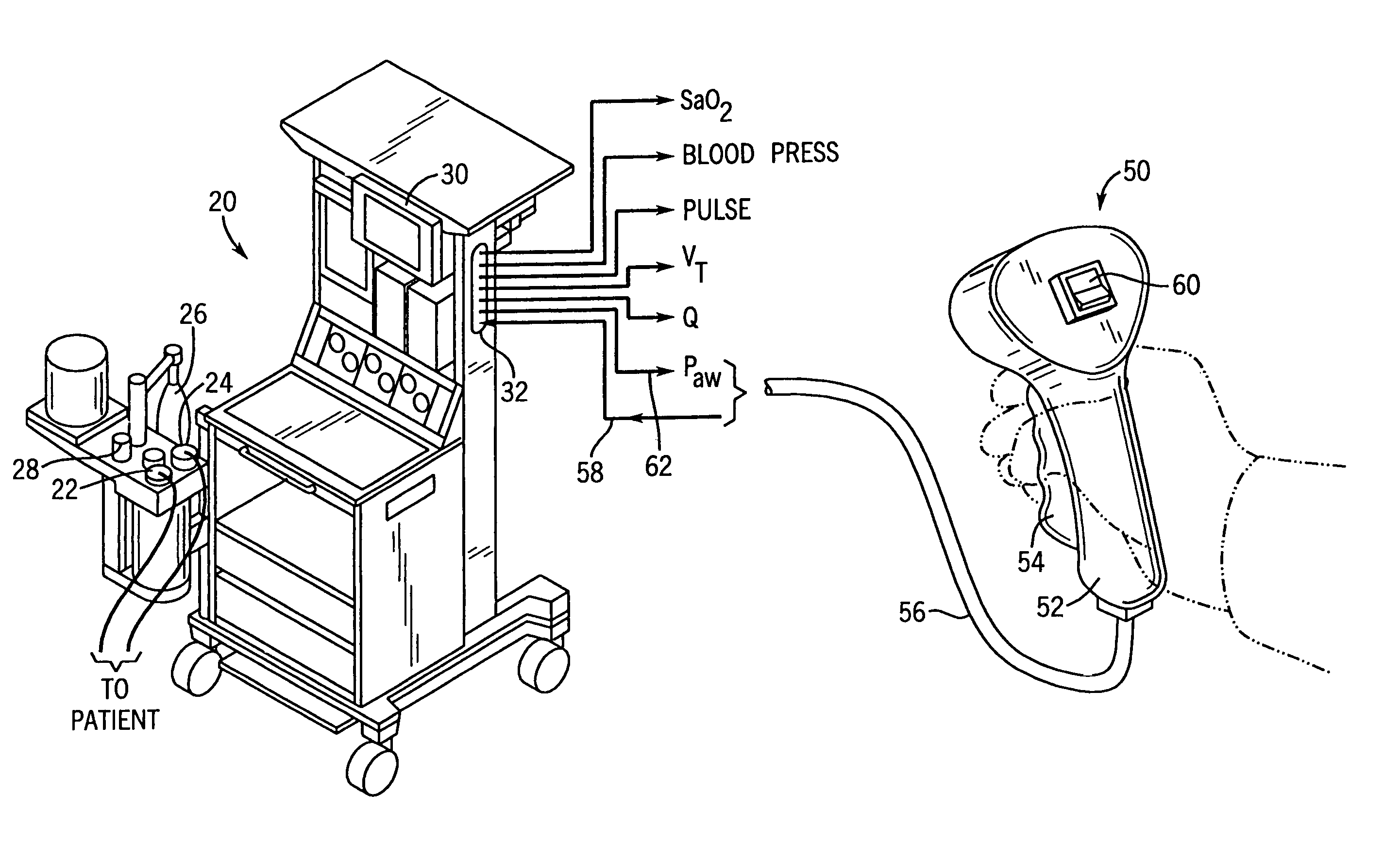

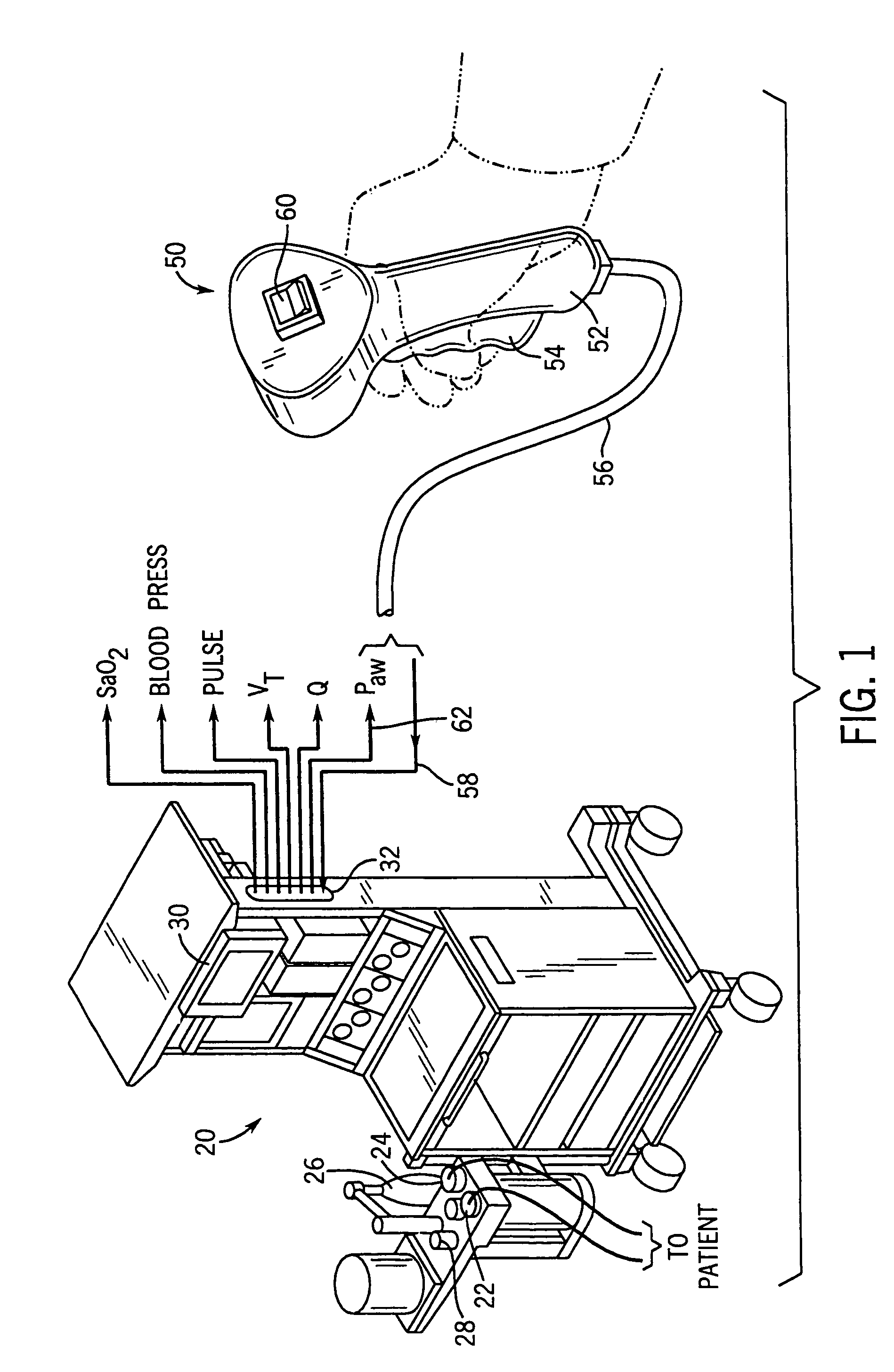

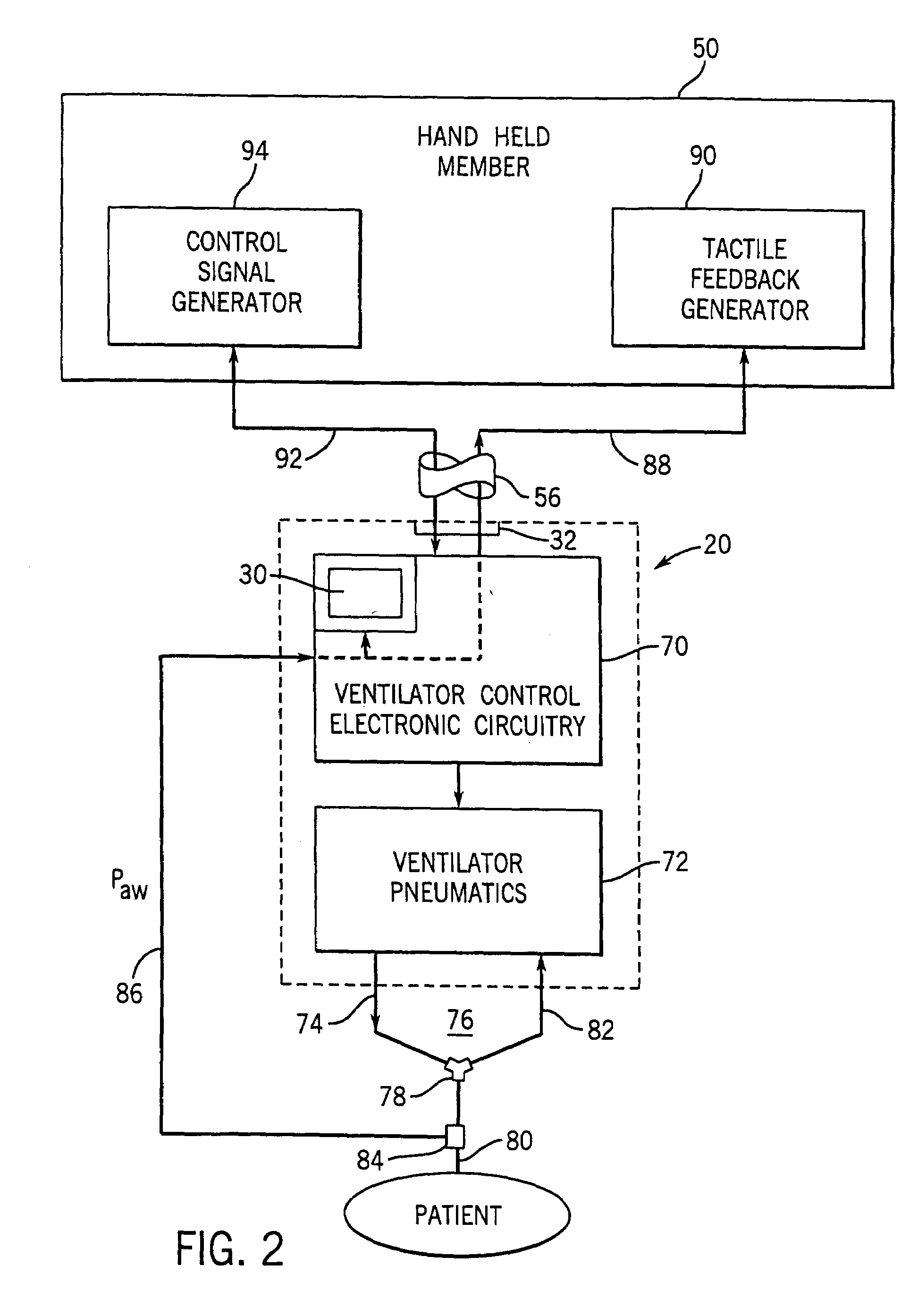

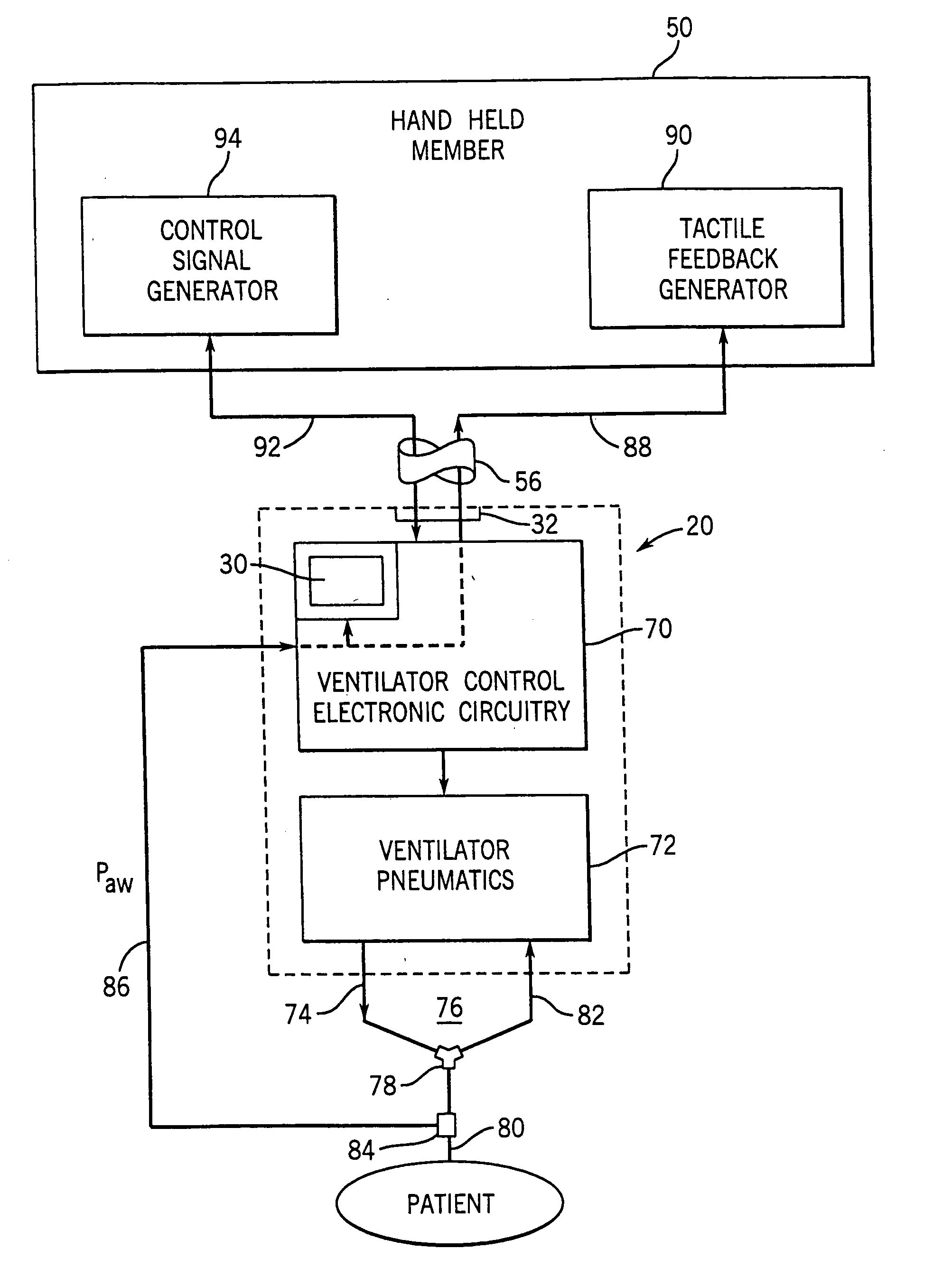

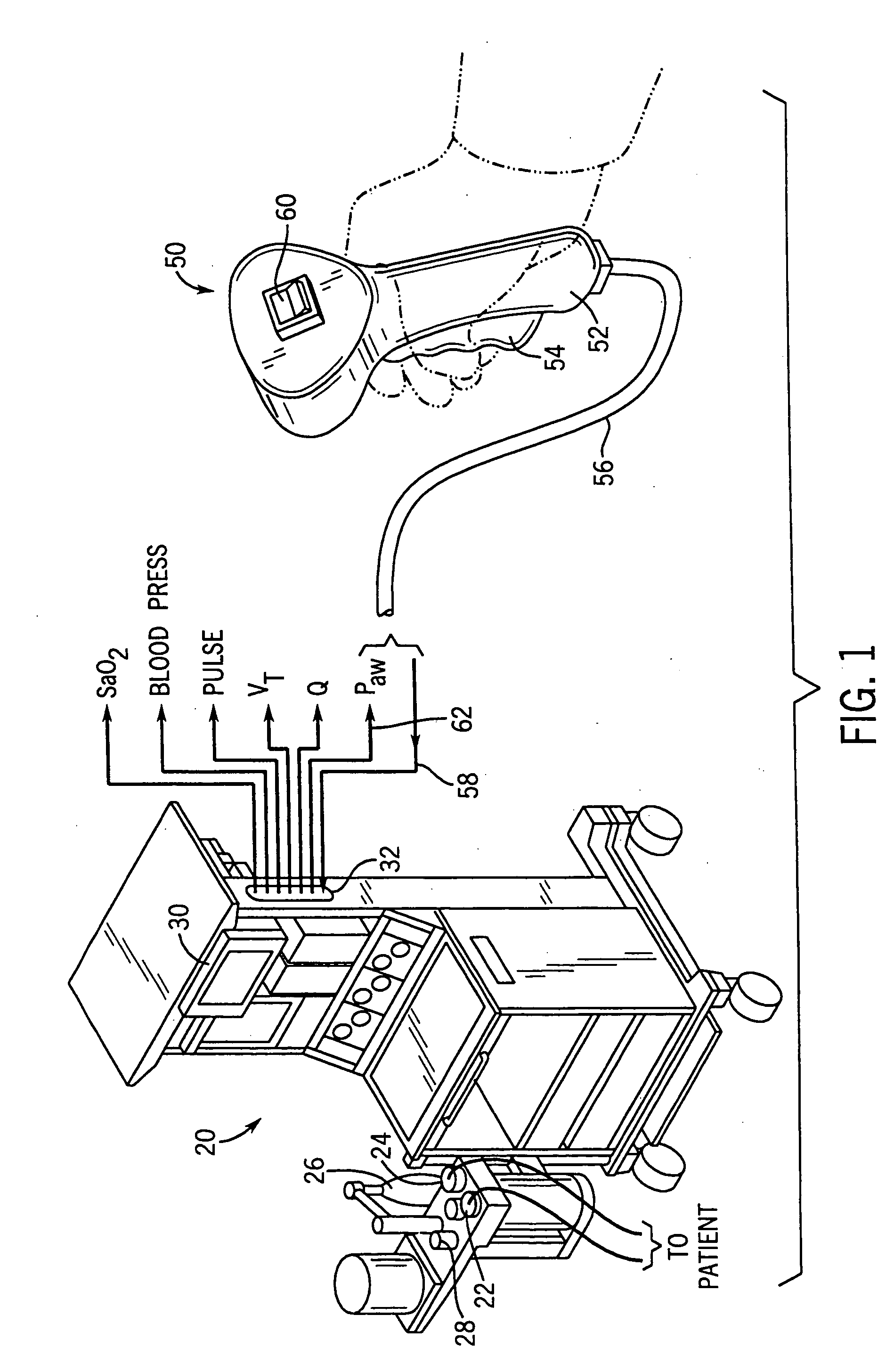

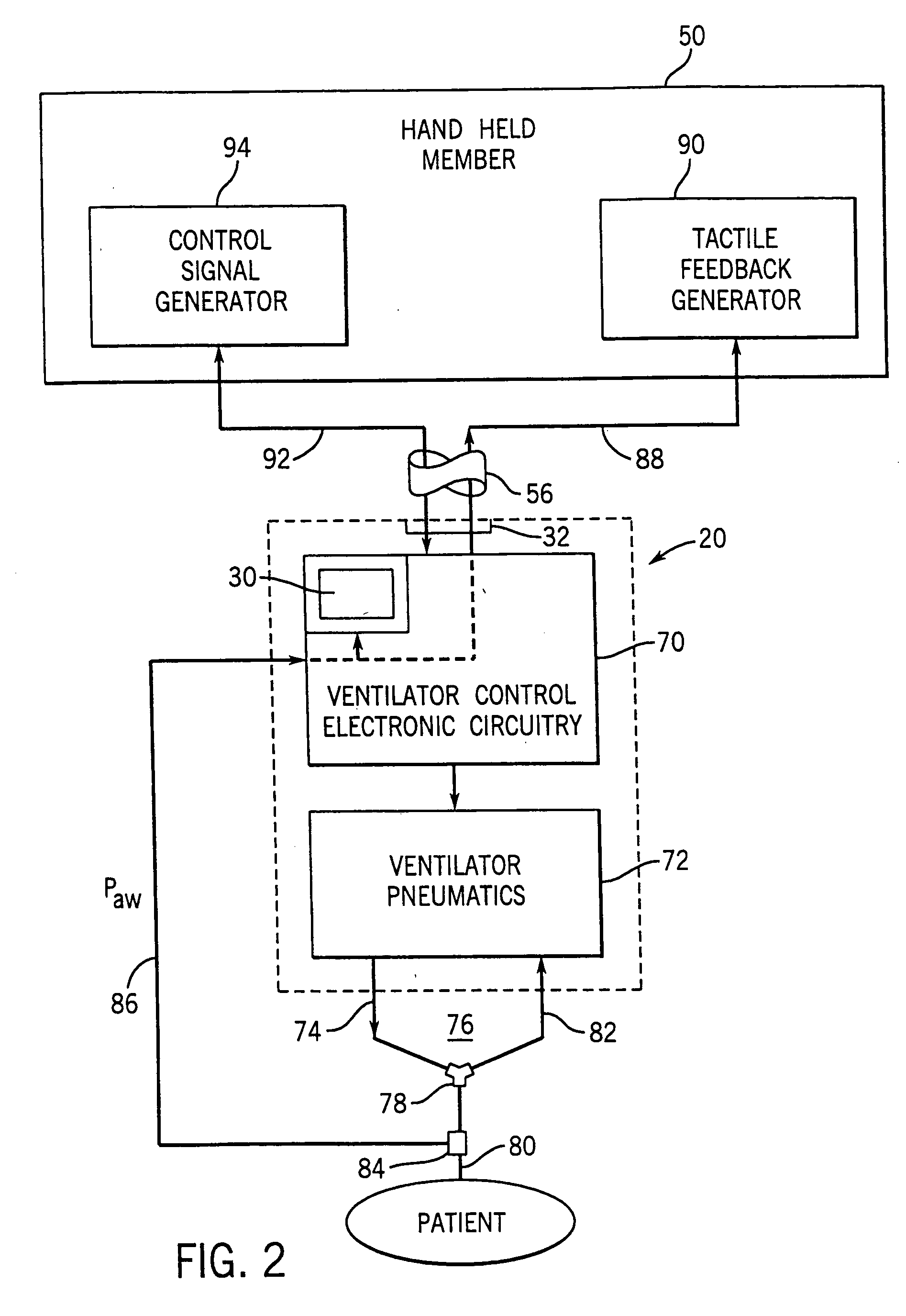

Remote control and tactile feedback system and method for medical apparatus

InactiveUS7669598B2Improve efficiencyHighly effectiveRespiratorsOperating means/releasing devices for valvesRemote controlControl signal

A system and method are for monitoring control signals provided to a medical apparatus bases upon tactile feedback from the apparatus. The system and method employ a monitoring signal indicative of a parameter relating to the apparatus or to a condition of a patient associated with the apparatus. The system includes a first feedback device in communication with the apparatus and arranged to provide tactile feedback to a first individual based upon the monitoring signal; a first controller actuatable by the first individual to provide a control signal to the apparatus for carrying a control action in the apparatus; a second feedback device in communication with the apparatus and arranged to provide tactile feedback to a second individual based upon the monitoring signal from the apparatus; and a second controller in communication with the first controller such that the control signal given by the first individual to the first controller is reflected in the second controller and communicated to the second individual. The first feedback device, first controller, second feedback device and second controller are in communication with the apparatus such that the first and second individual can be distant from the apparatus and patient and move about the apparatus and patient to a desired location.

Owner:DATEX OHMEDA

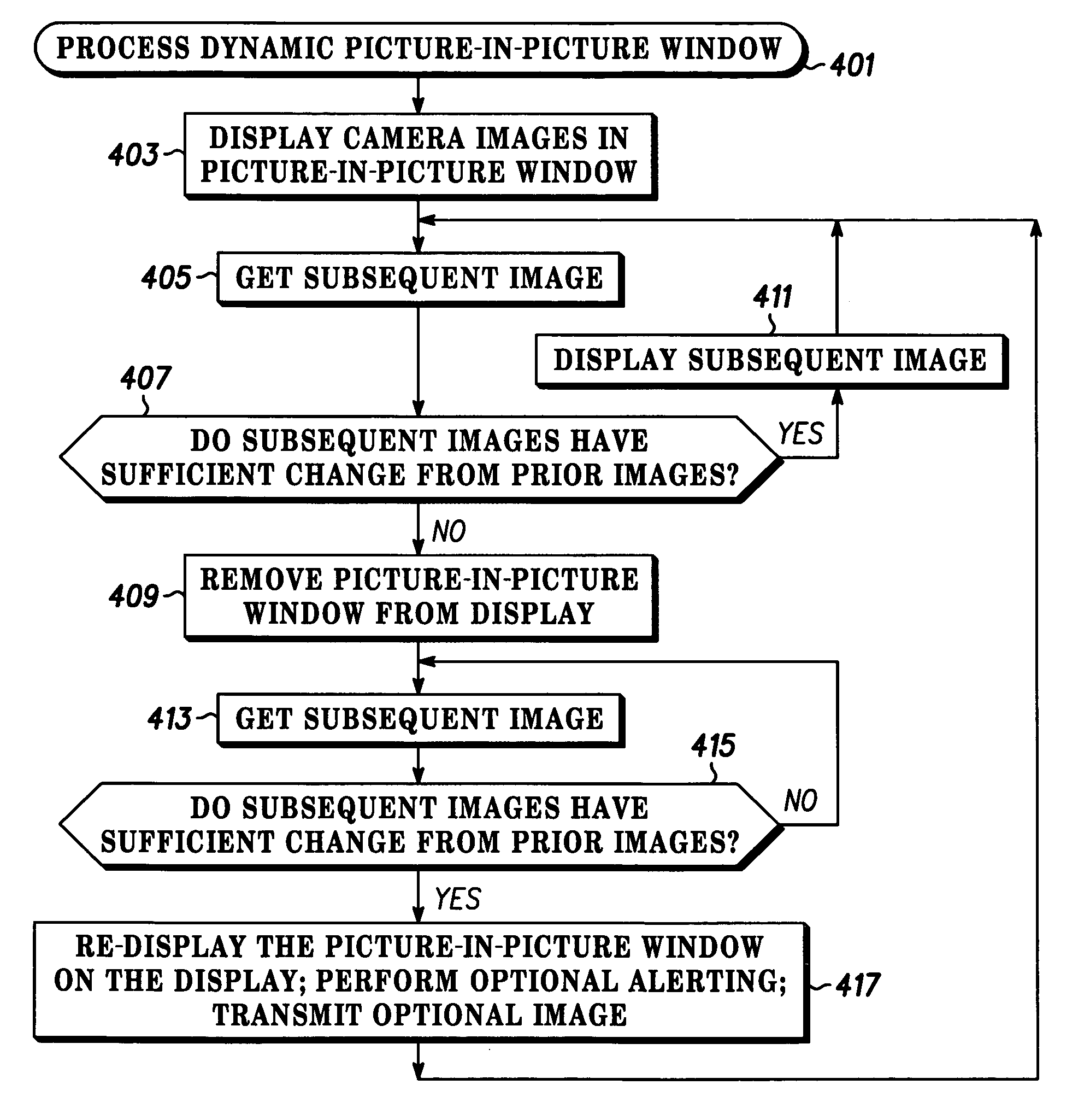

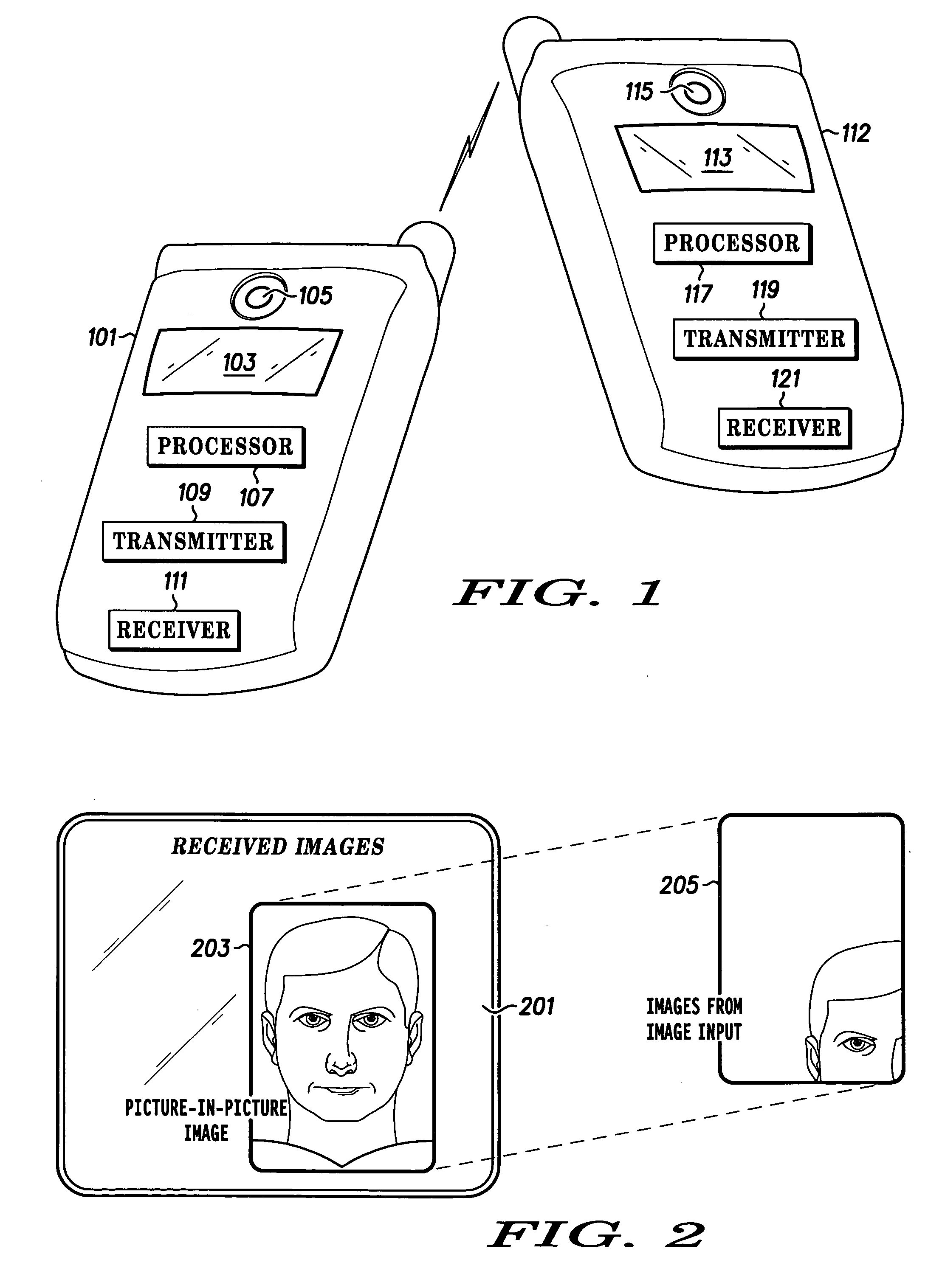

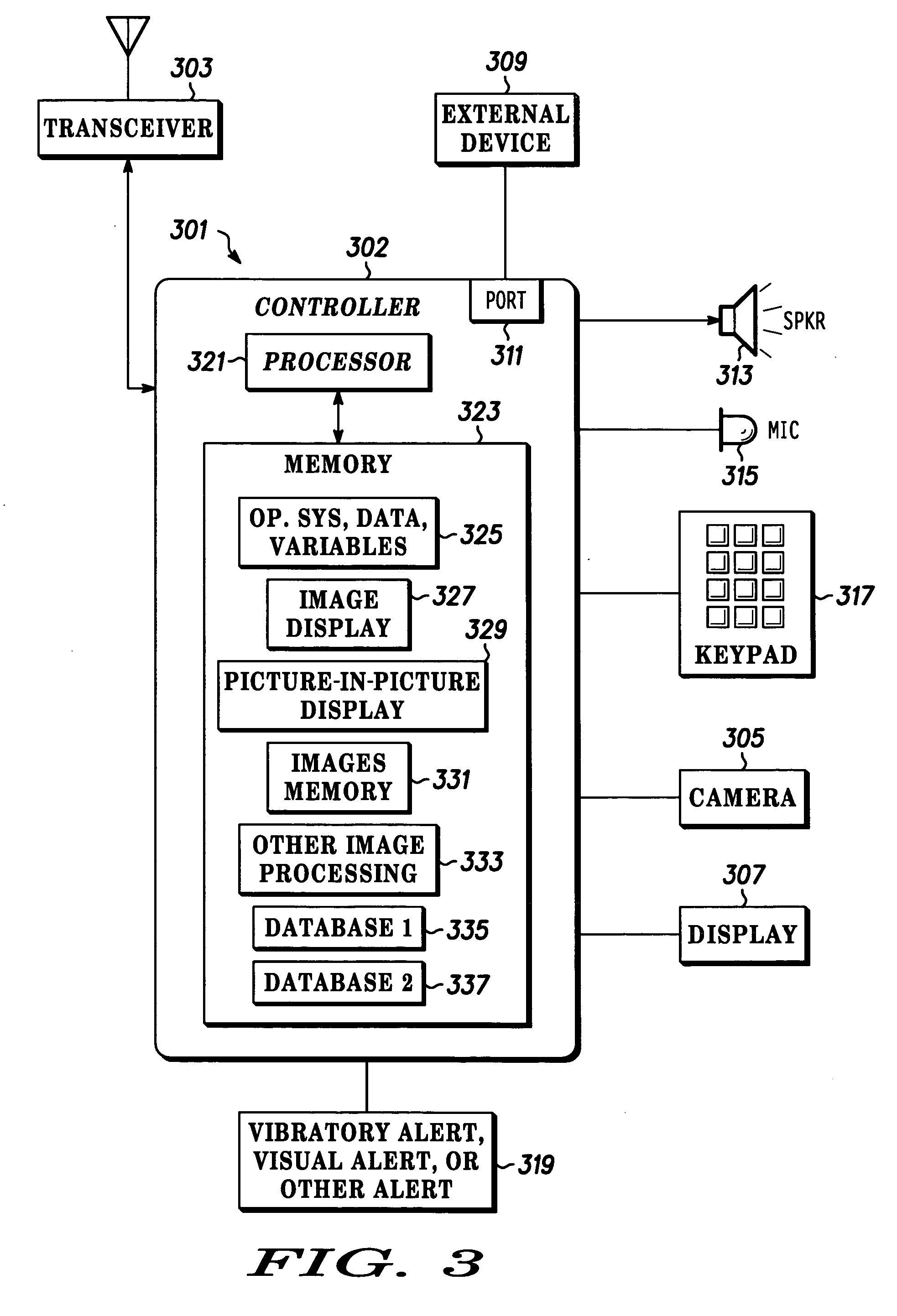

Method and system for providing a dynamic window on a display

InactiveUS20060044741A1Improve appreciationInvention is limitedInput/output for user-computer interactionTelevision system detailsDisplay deviceImage stabilization

A communication device (101) includes a display (103) screen for displaying images to a user; an image input (105) for detecting and capturing a series of images, including a prior image and subsequent images; and a processor (107). The processor (107) is configured to facilitate receiving, from the image input (105), the series of images; to facilitate displaying images received from a receiver (111) on the display (103) screen; and to facilitate determining whether the subsequent images have changed in a pre-determined manner from the prior images. A window can be provided on the display, for example to display the series of images from the image input (105). The presence or absence of the window is controlled by a determination that the subsequent images have changed in the pre-determined manner from prior images. When the images are changed, the window is deployed on the display, and when the images are stable, the window is removed from the display.

Owner:MOTOROLA INC

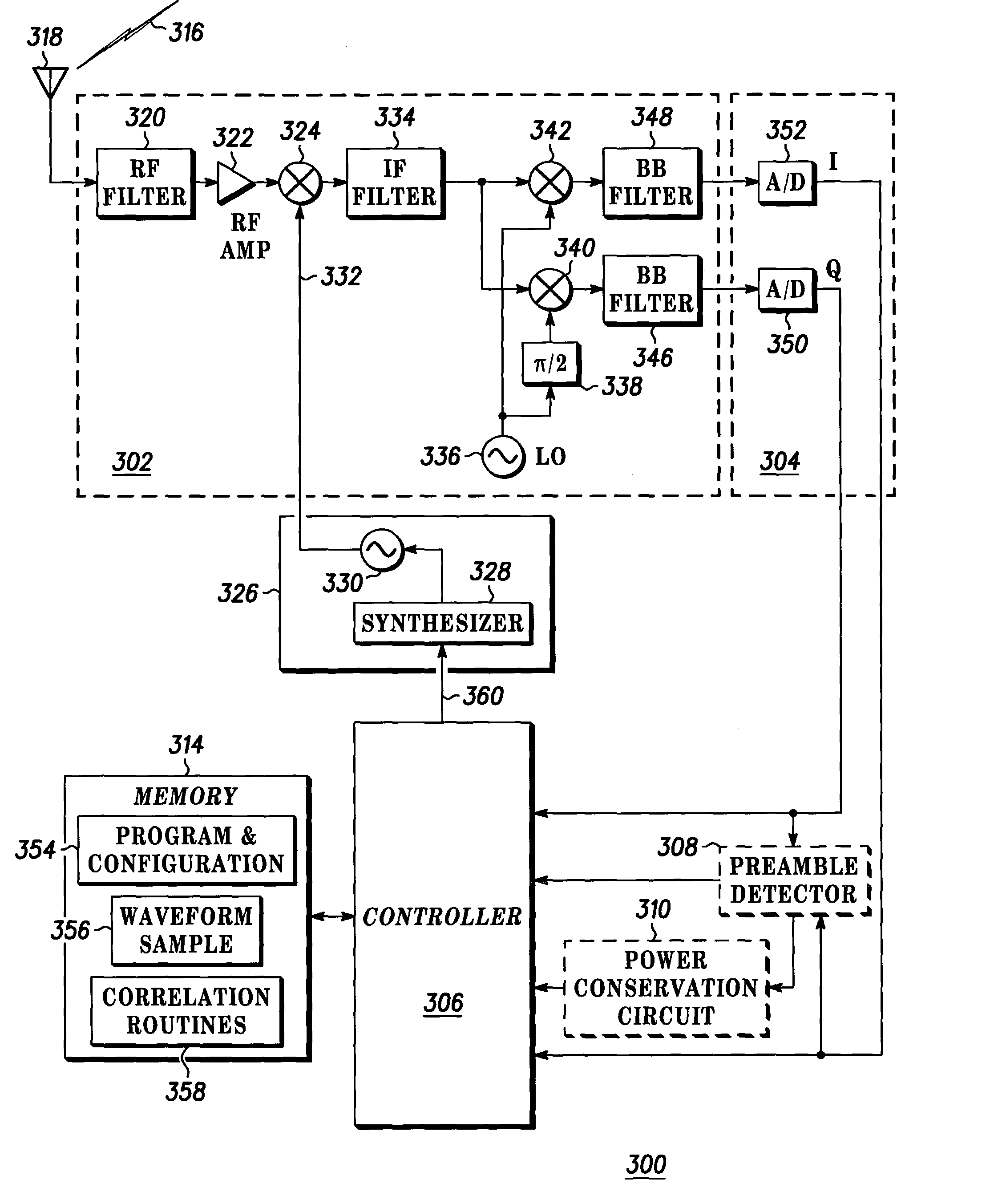

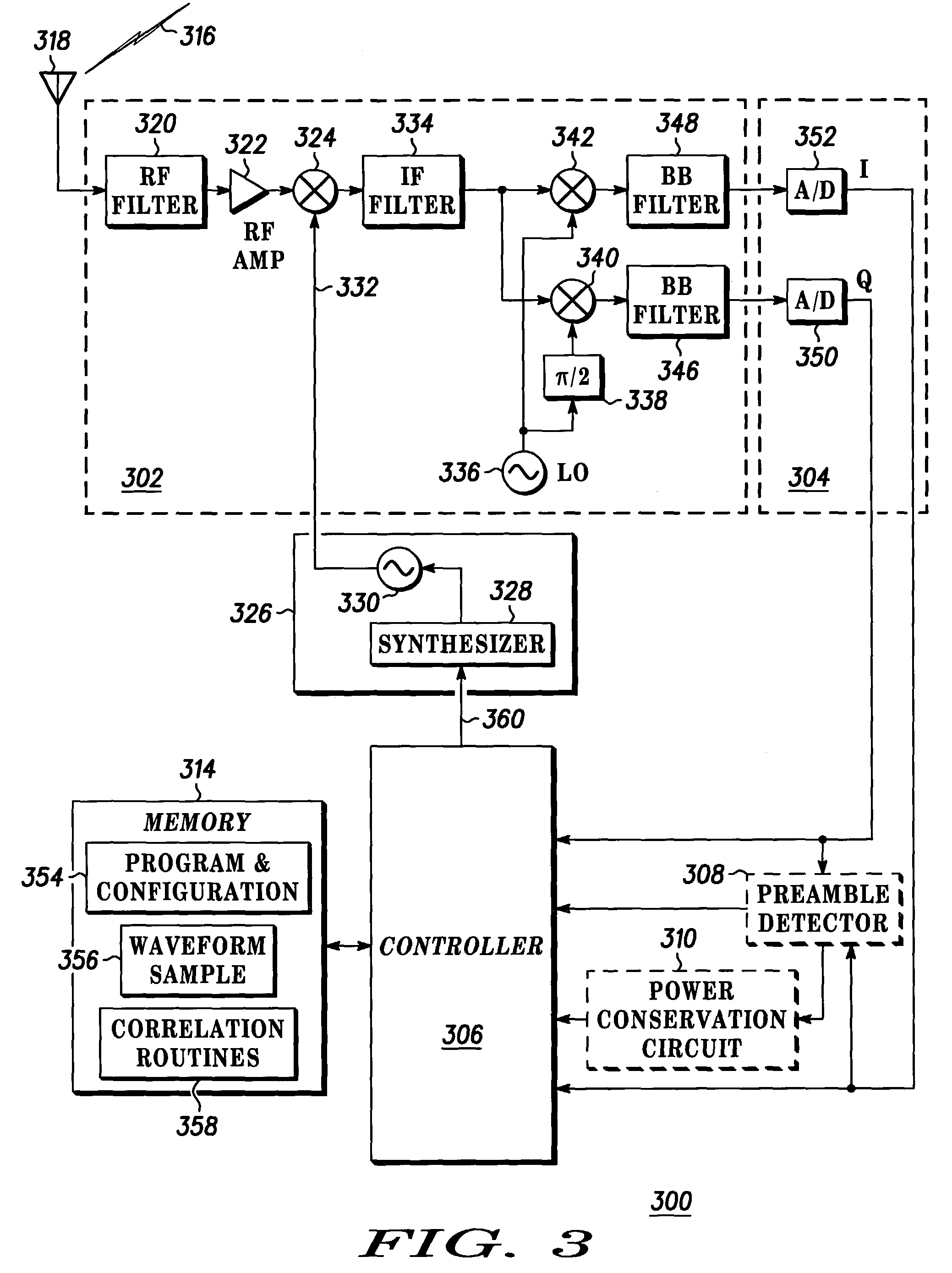

Method and wireless device employing a preamble to initiate communications

InactiveUS7106814B2Improve appreciationInvention is limitedPower managementCarrier regulationPower modeSample sequence

A wireless receiver 300 and corresponding method to detect a message identifier or preamble that has been generated and provided by a transmitter 200 uses FFTs to estimate frequency and time offset. The wireless receiver 300 scans, asynchronously and sequentially during a wakeup time, a plurality of predetermined frequencies for the message identifier or specialized preamble. A plurality of received sample sequences are collected, one received sample sequence collected at each of the plurality of predetermined frequencies. A correlation between data corresponding to the preamble and data corresponding to a received sample sequence is compared to a threshold value to determine when the preamble has been detected. The wireless receiver 300 is wakened from a low power mode when the preamble is detected.

Owner:GOOGLE TECH HLDG LLC

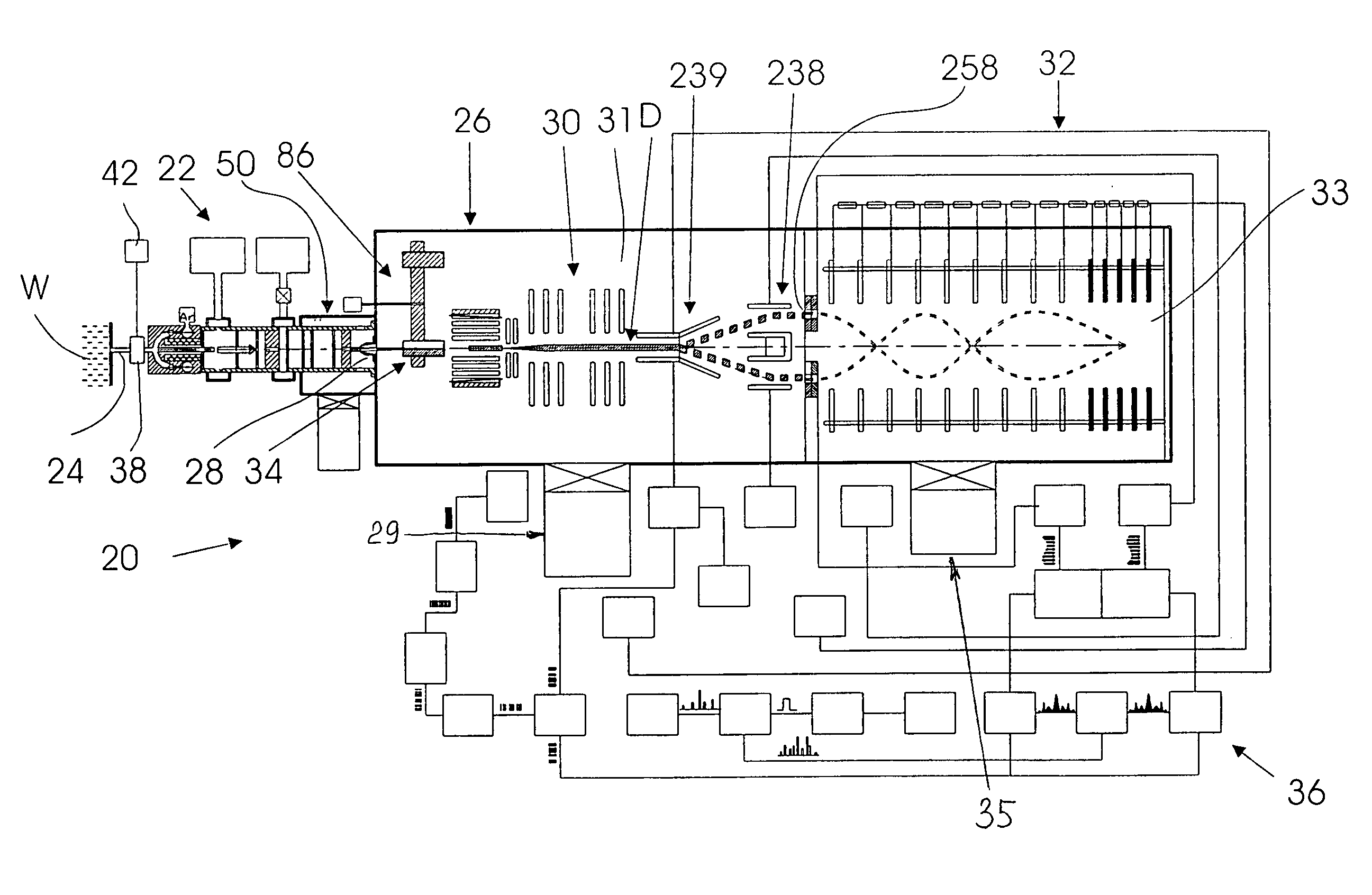

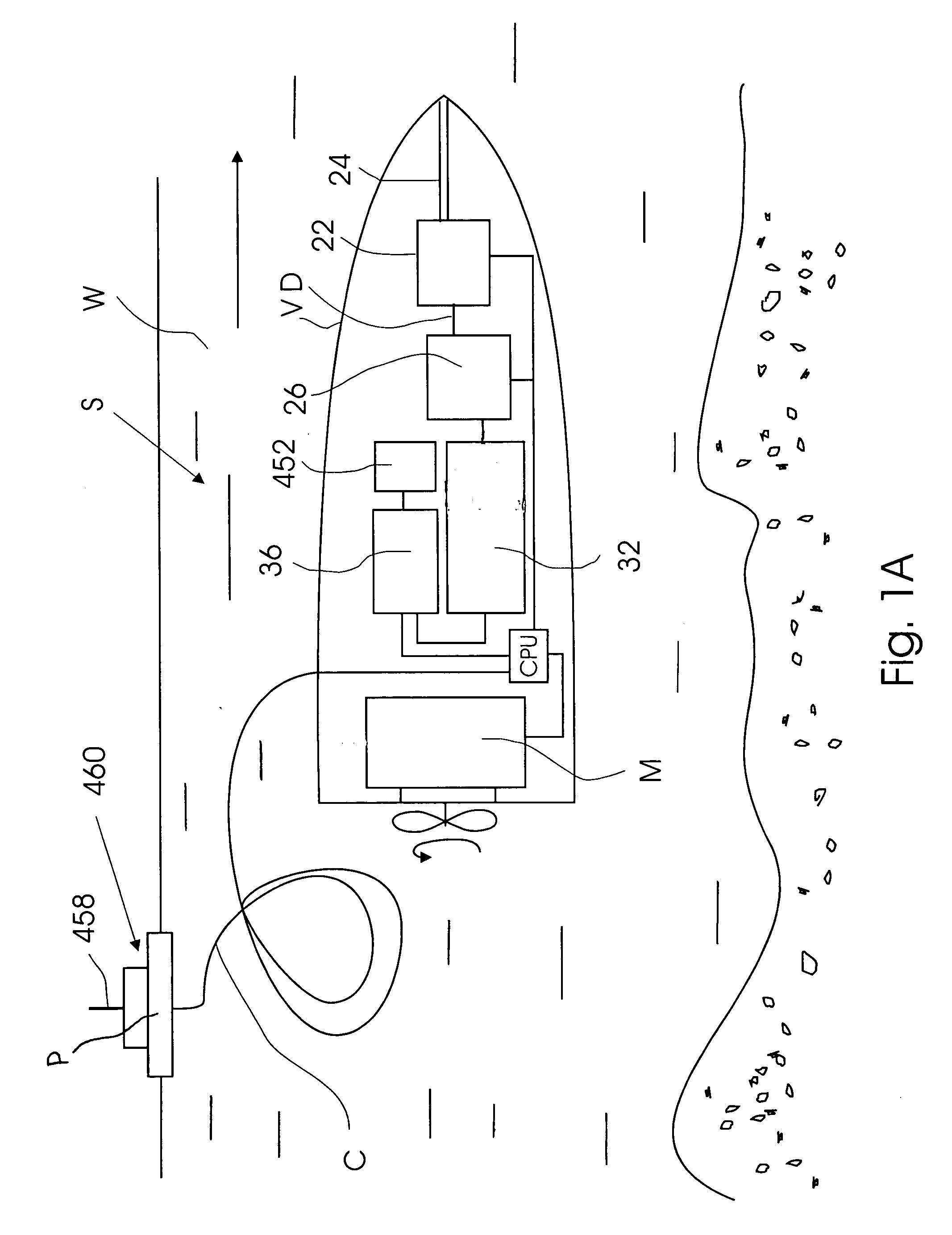

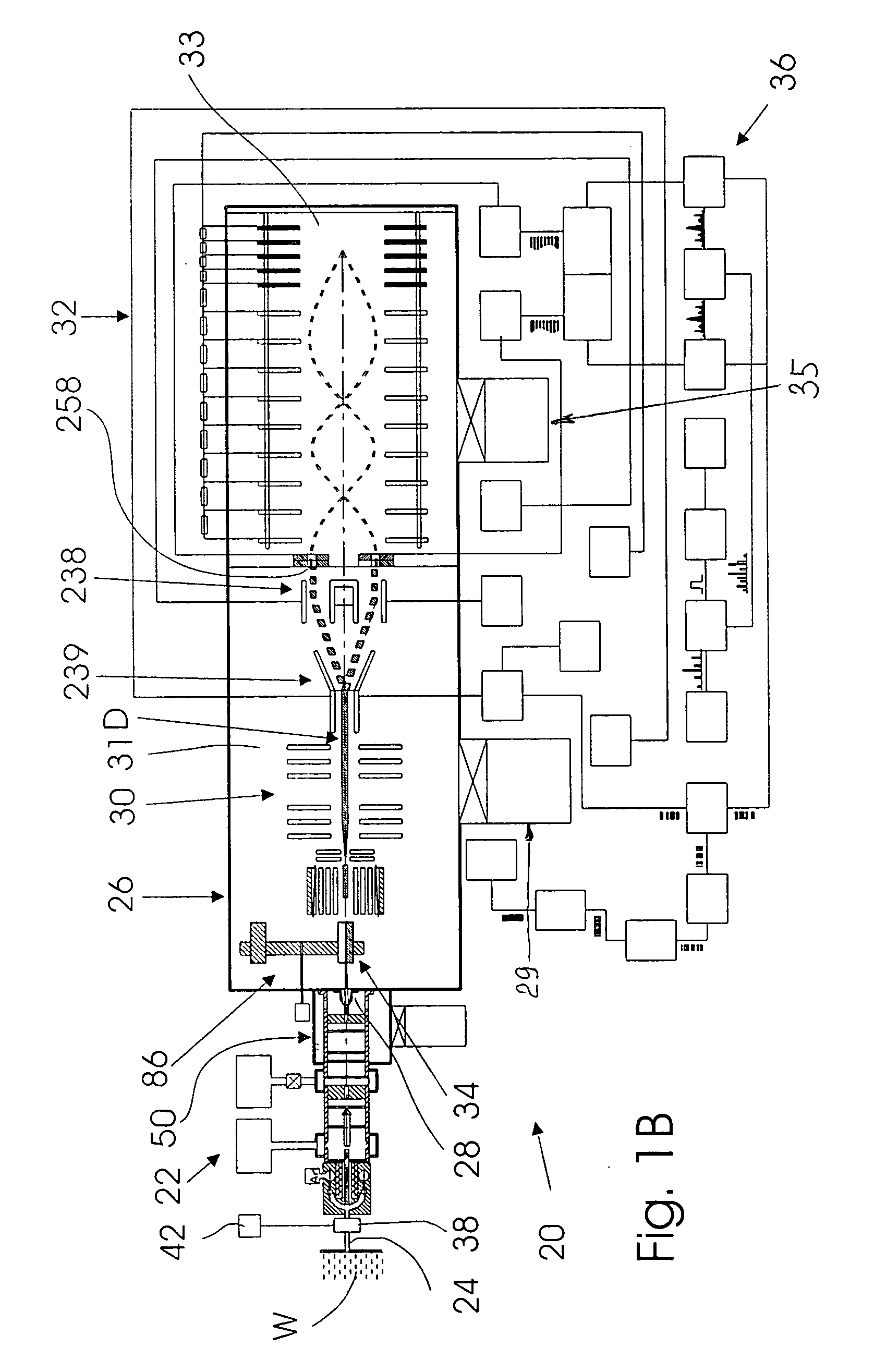

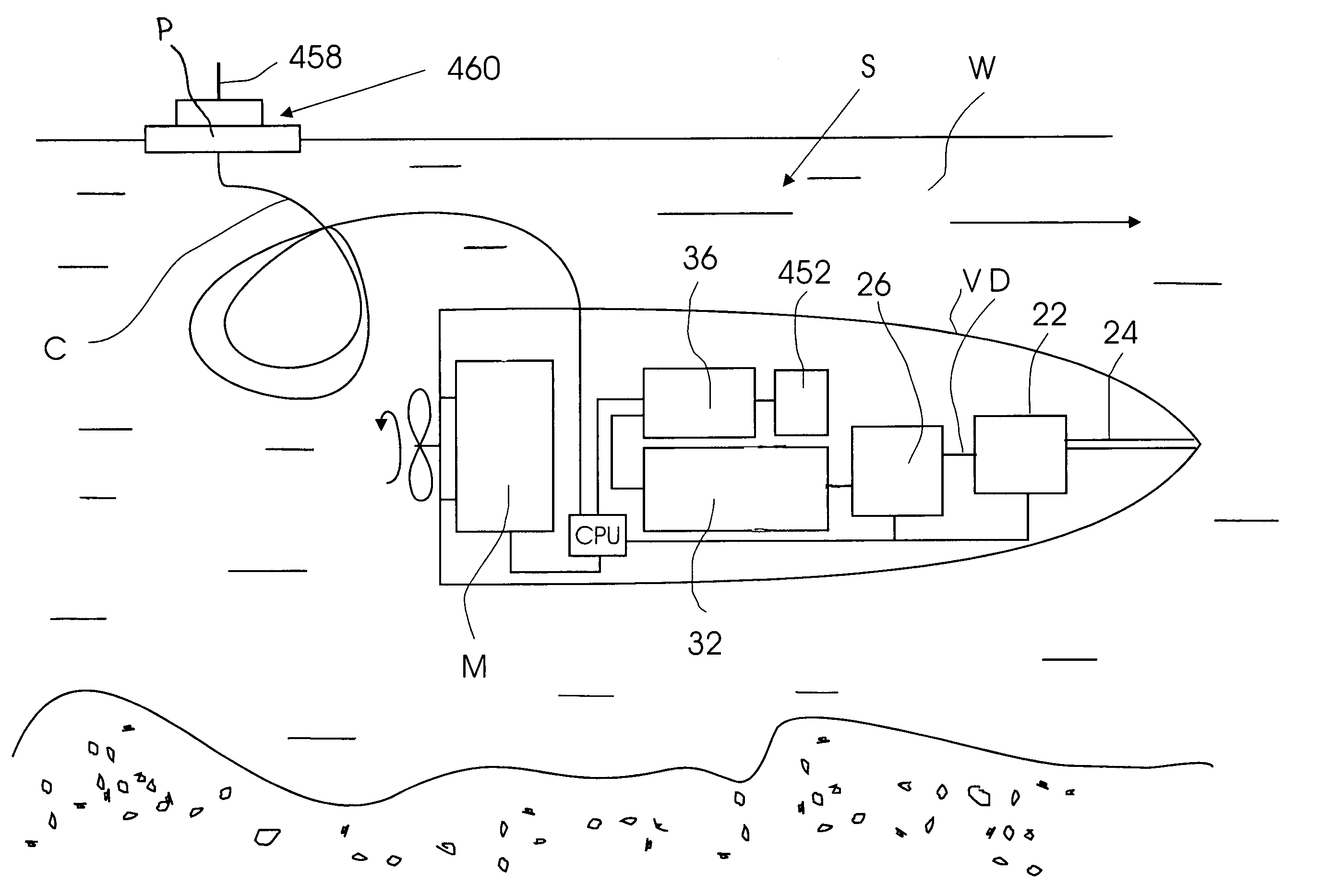

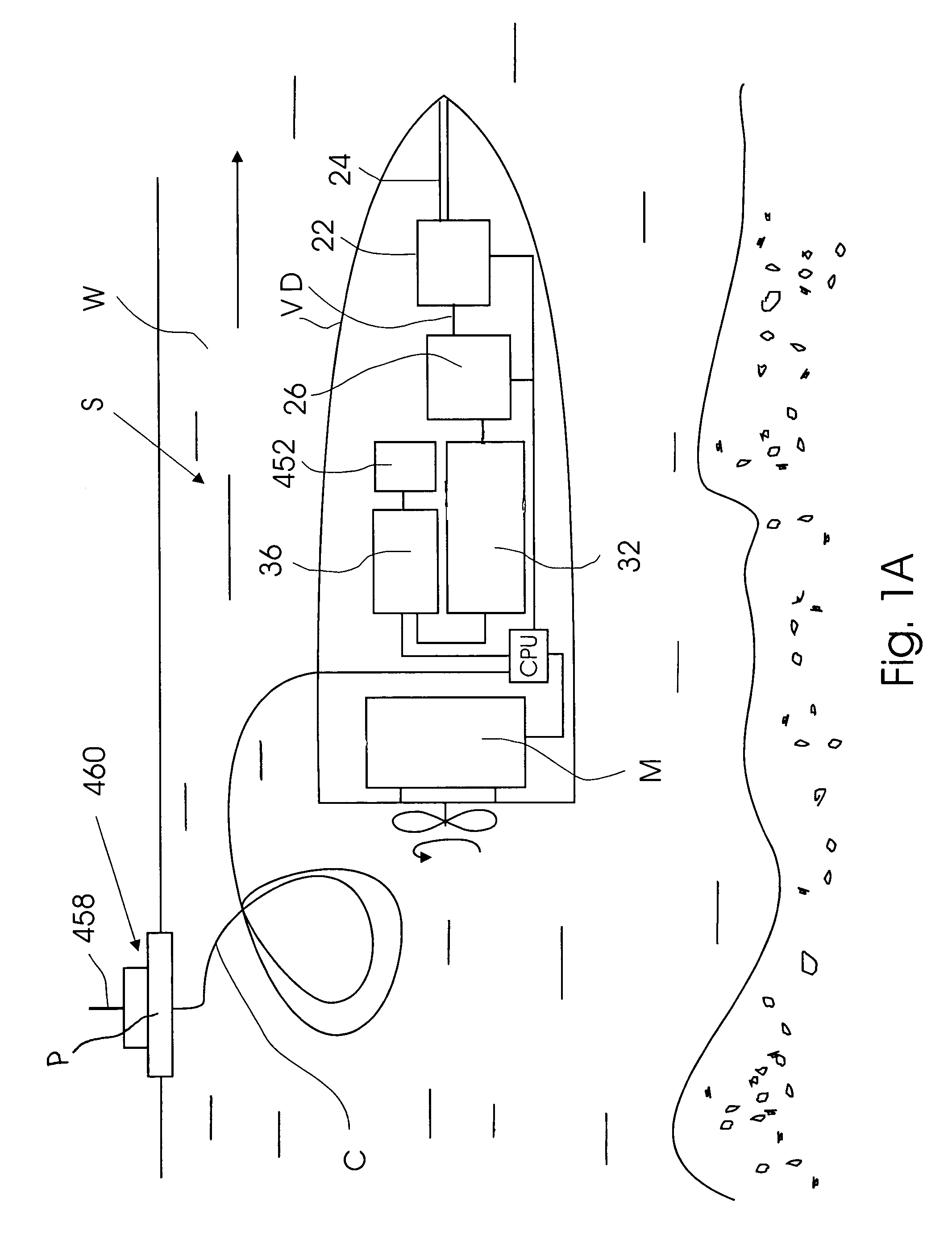

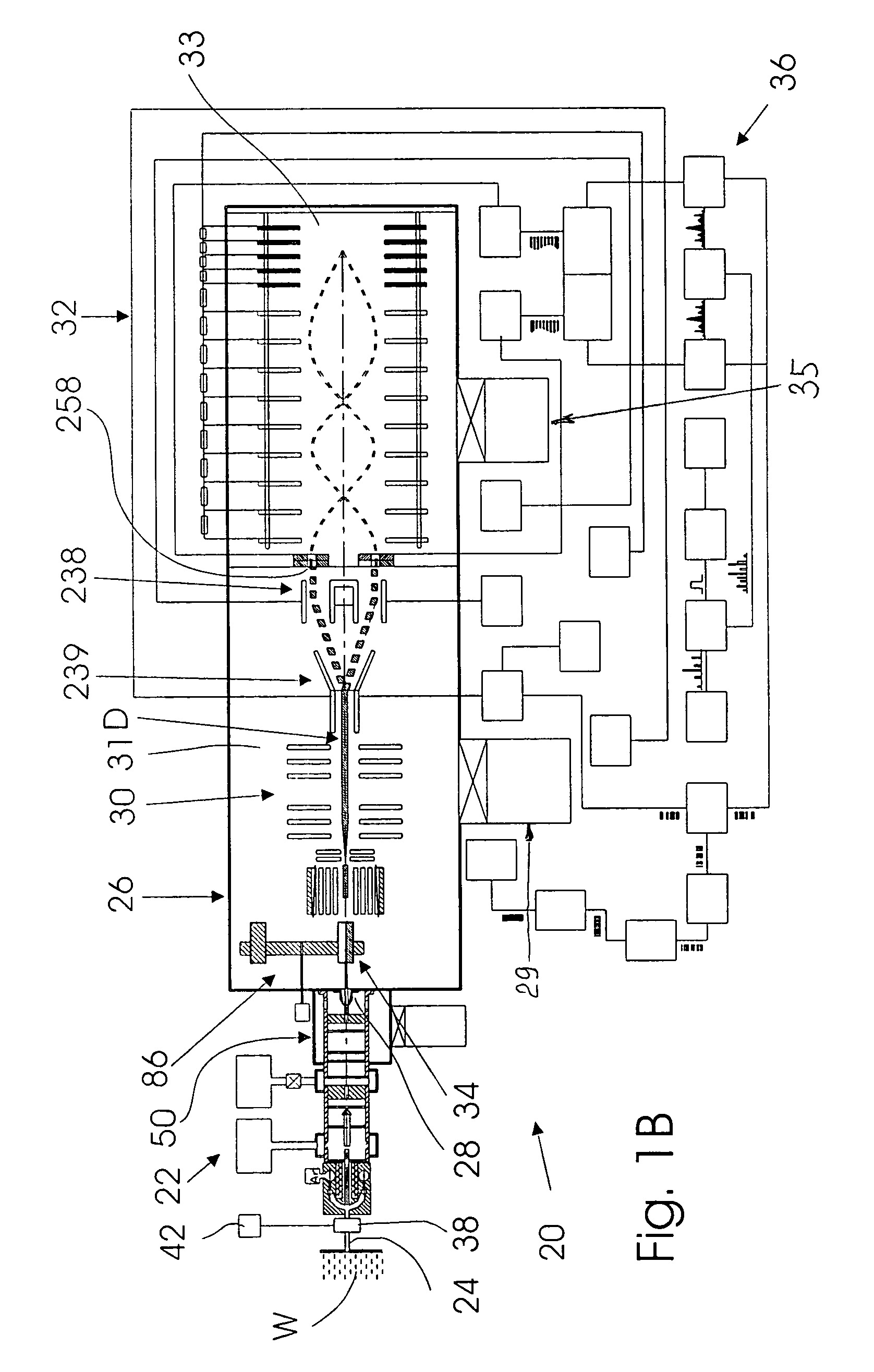

Mass spectrometry system for continuous control of environment

InactiveUS20050230614A1Continuous operationCompact structureTime-of-flight spectrometersIon sources/gunsThree levelData acquisition

A mass spectrometry system for continuous control of environment based on the use of an aerosol TOF MS that provides operation with a high duty cycle of up to 98% and can be realized in the form of a mobile unit having a data acquisition and analysis system with three levels of data correlation on the basis of constant interaction between various actuating mechanisms of the system via a central processing unit. The TOF MS is based on the use of quadrupole lenses with angular gradient of the electrostatic field. On the entrance side, the TOF MS contains an ion-optic system that is used for focusing, aligning, and time-modulating the ionized flow of particles and a deflector modulator that provides alternating deflections of the flow of particles between two positions for aligning the flow with two inlet openings into the TOF MS. As a result, two independently analyzed discrete flows of particles pass through the ion mass separation chamber of the TOF MS without interference with each other. The charged particles fly in direct and return paths along helical trajectories which extend the length of the flight time. The time of the collision and the magnitude of the collision pulse will contain information about the M / Z ratio for the particles being registered. Multiplication of a single flow of particles into a plurality of independent and spatially separated flows propagating in one chamber increases efficiency of the TOF MS and makes it possible to use it in continuous and high-duty applications with the duty cycle as high as 98%, which is unattainable with any known device of this class. The system can be mounted either on an underwater and ground vehicle, or on an aircraft.

Owner:YURI GLUKHOY

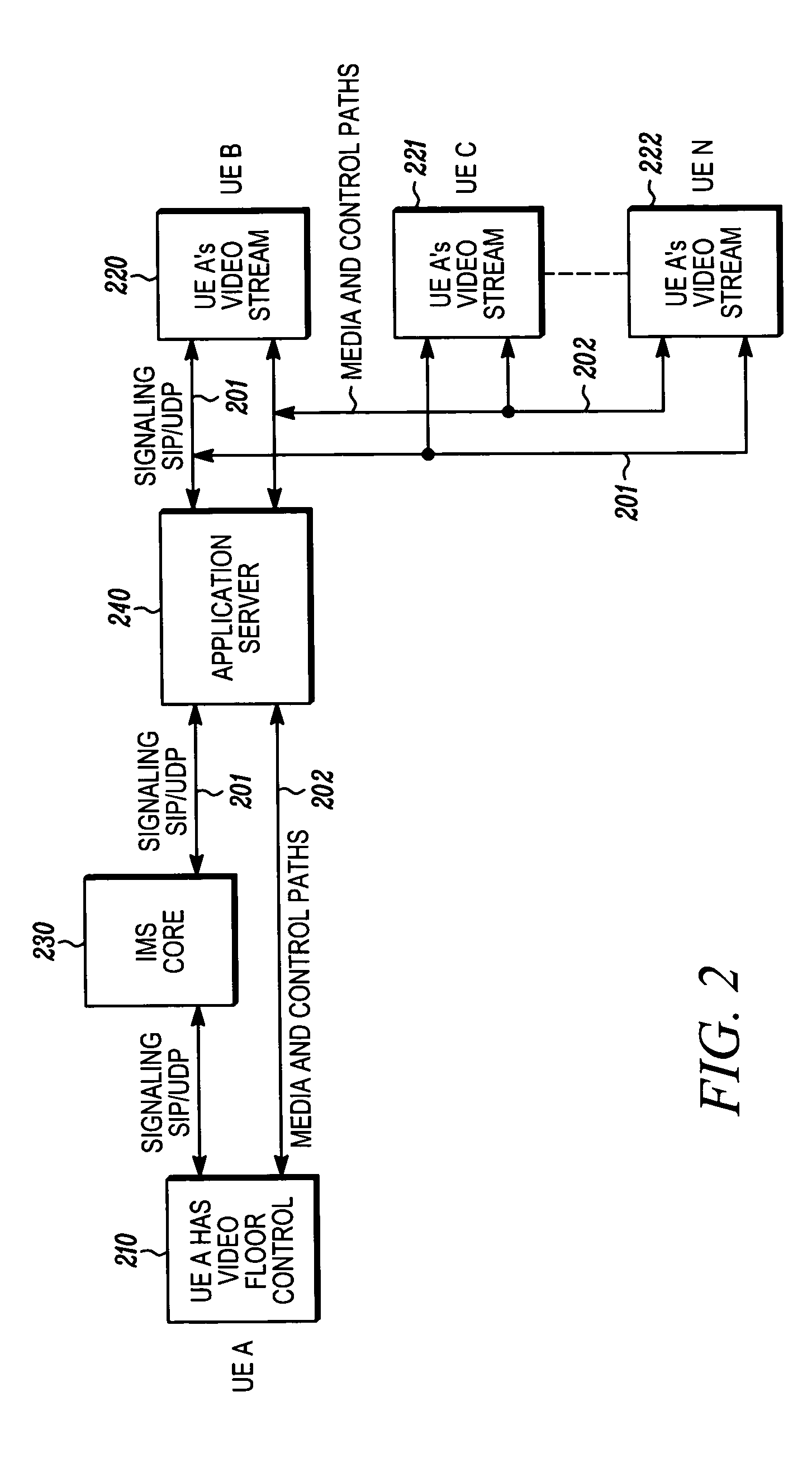

Push to video service mode selection using device settings

ActiveUS7446795B2Improve appreciationInvention is limitedRadio transmissionTwo-way working systemsCommunication unitComputer network

A method (600, 700) and apparatus (800) are described for selecting a Push to Video (PTV) service mode (303) allowing transmission of a video information stream (102) and a corresponding audio information stream (103) from an originating wireless communication unit (110) having floor control to a wireless target communication unit (120). Depending on a camera (420) setting, a desired PTV service mode is invoked when a PTV call is initiated by activating a PTV function.

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

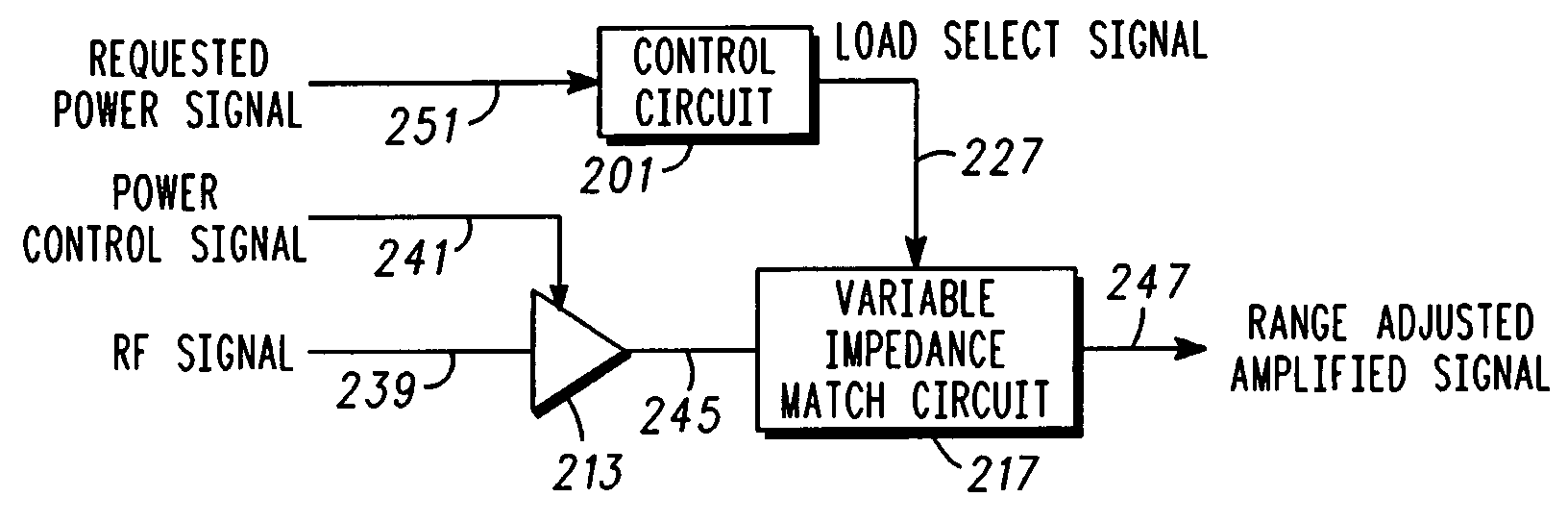

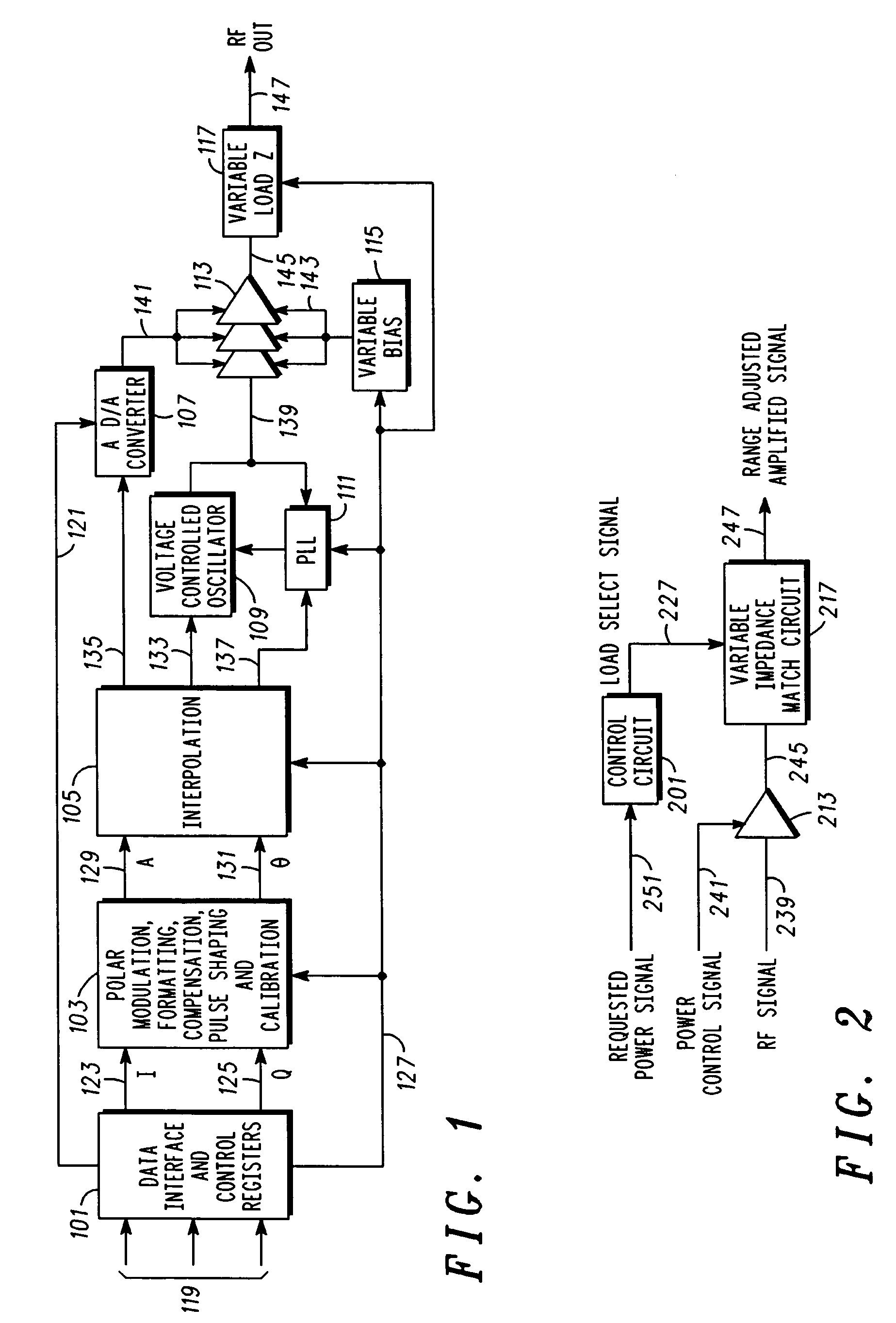

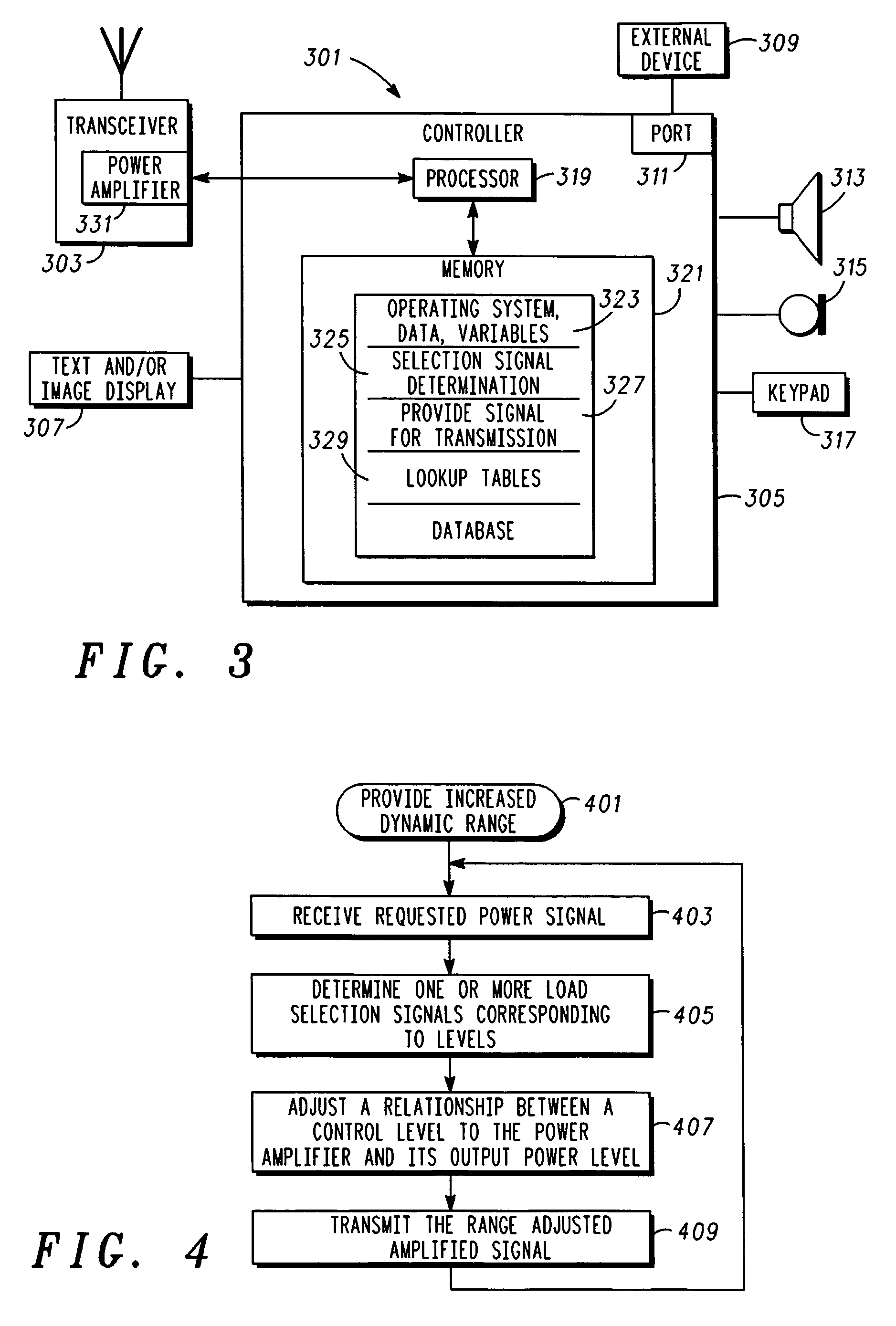

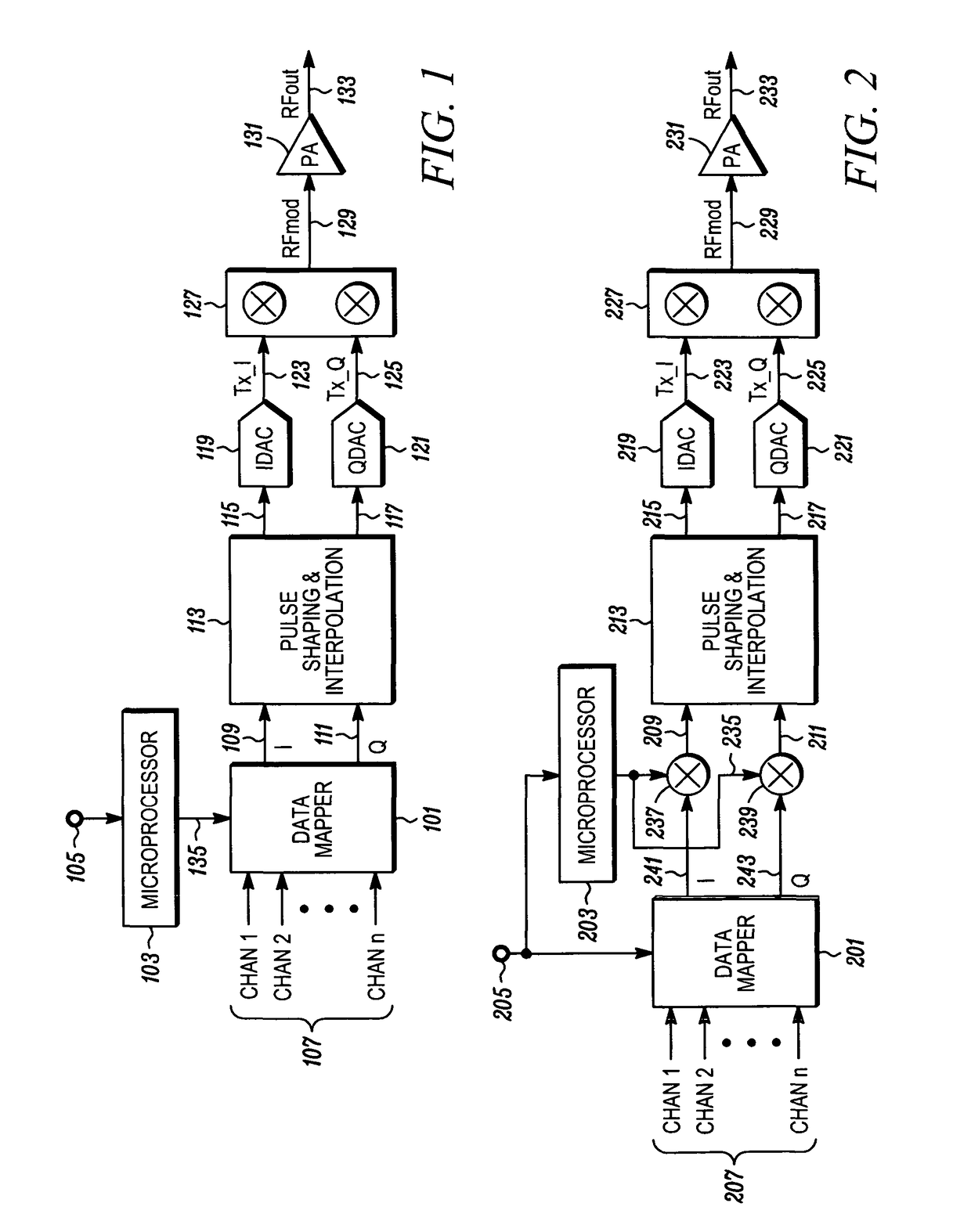

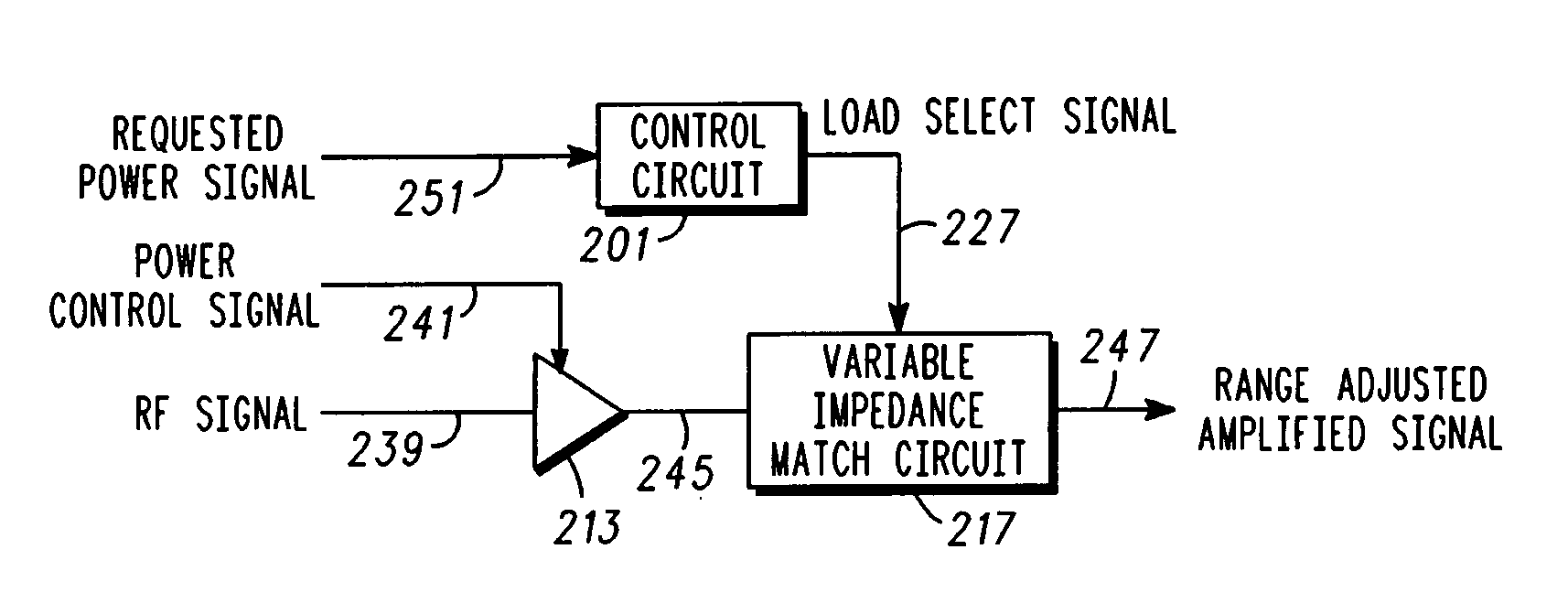

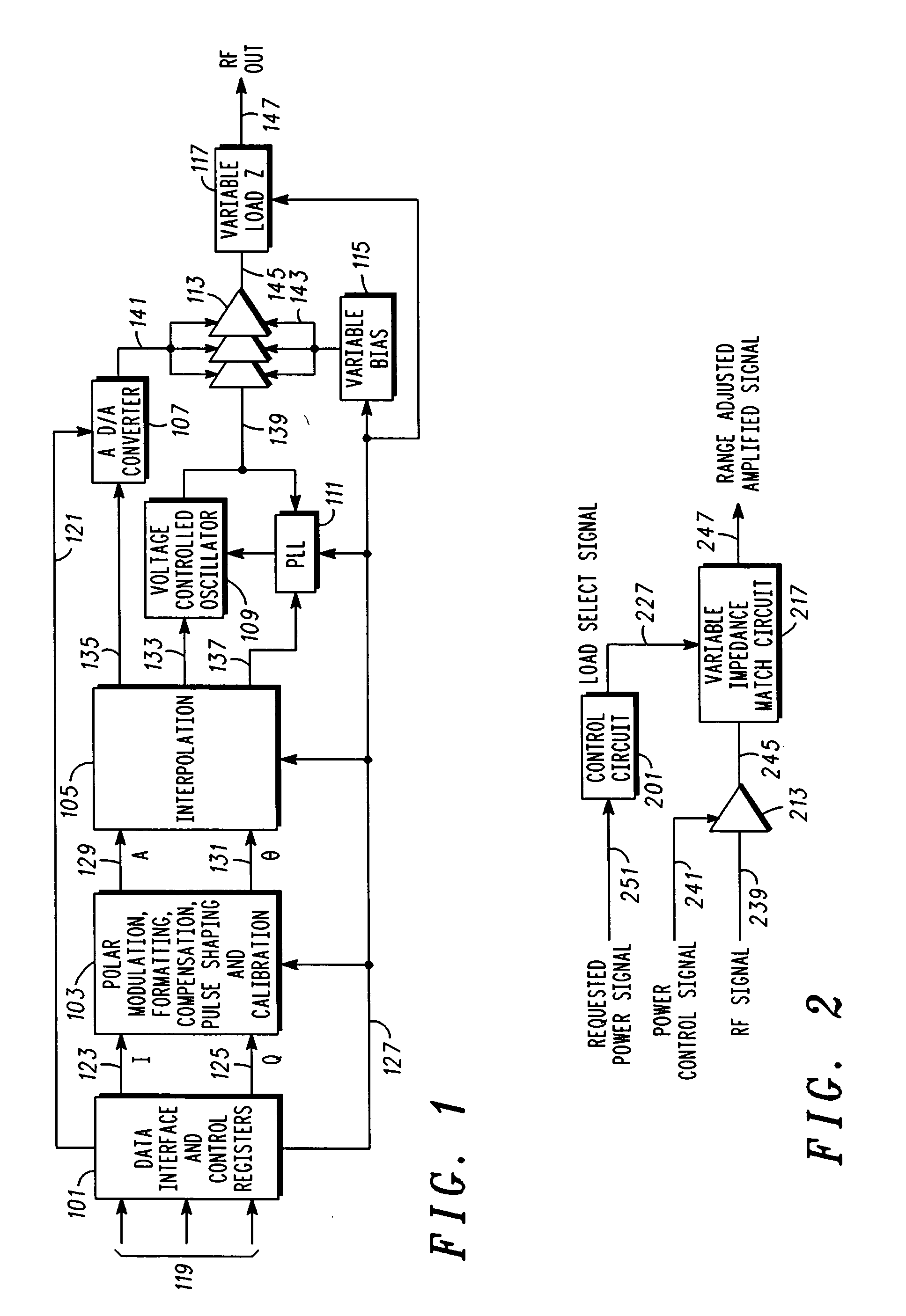

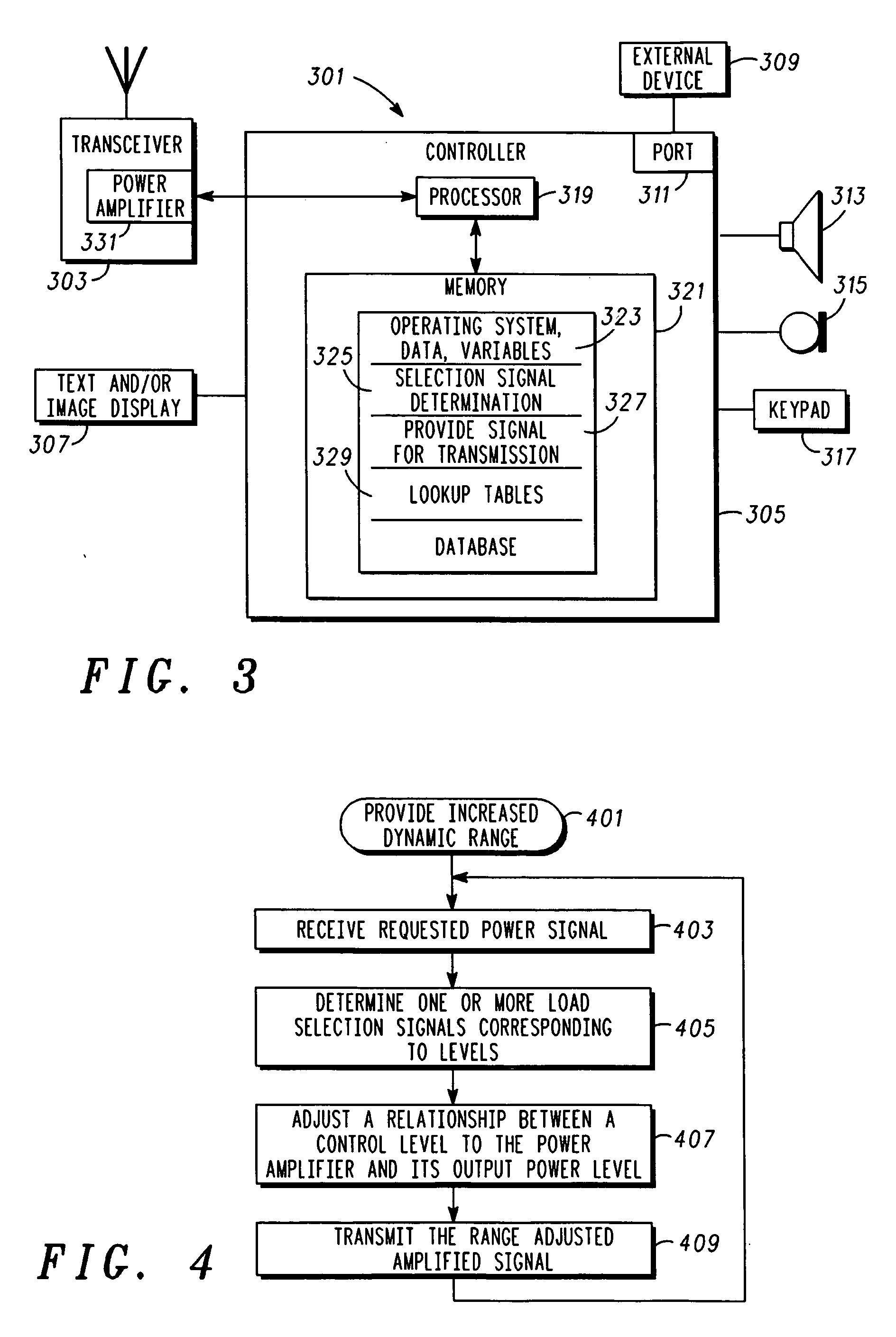

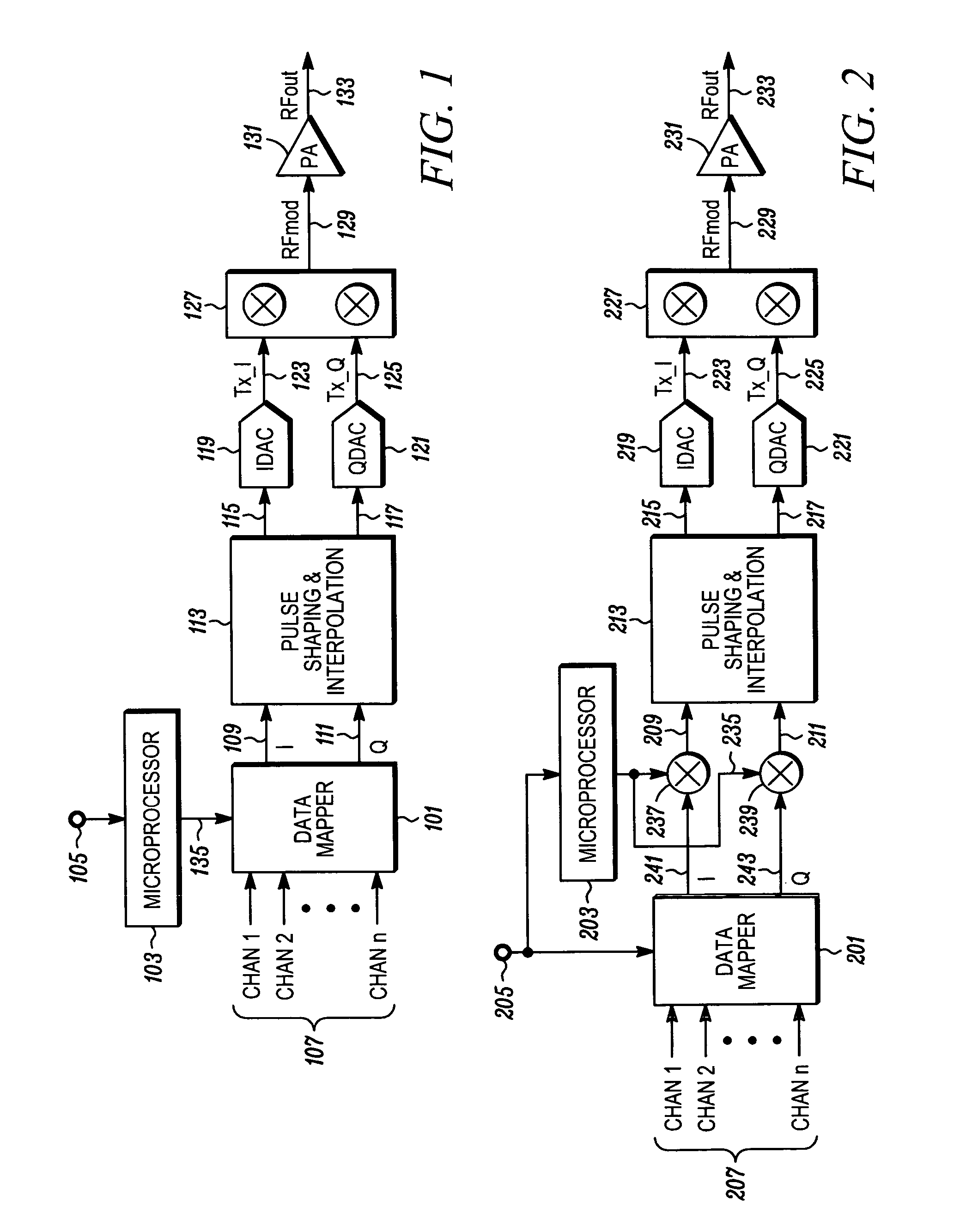

Multi-state load switched power amplifier for polar modulation transmitter

ActiveUS7183844B2Improve appreciationInvention is limitedAmplifier modifications to reduce temperature/voltage variationGain controlAudio power amplifierControl signal

A polar modulation power amplifier circuit includes a control circuit (101) to determine and provide a load selection signal (127), wherein the load selection signal (127) is determined responsive to a requested power signal (119). A power amplifier (113) is responsive to a power control signal (141), for amplifying an RF signal (139) to produce an amplified signal (145), having an output power level. A variable impedance matching circuit (117) is responsive to the load selection signal (127), to adjust a relationship between the control level and the output power level, to produce a range-adjusted amplified signal (147).

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

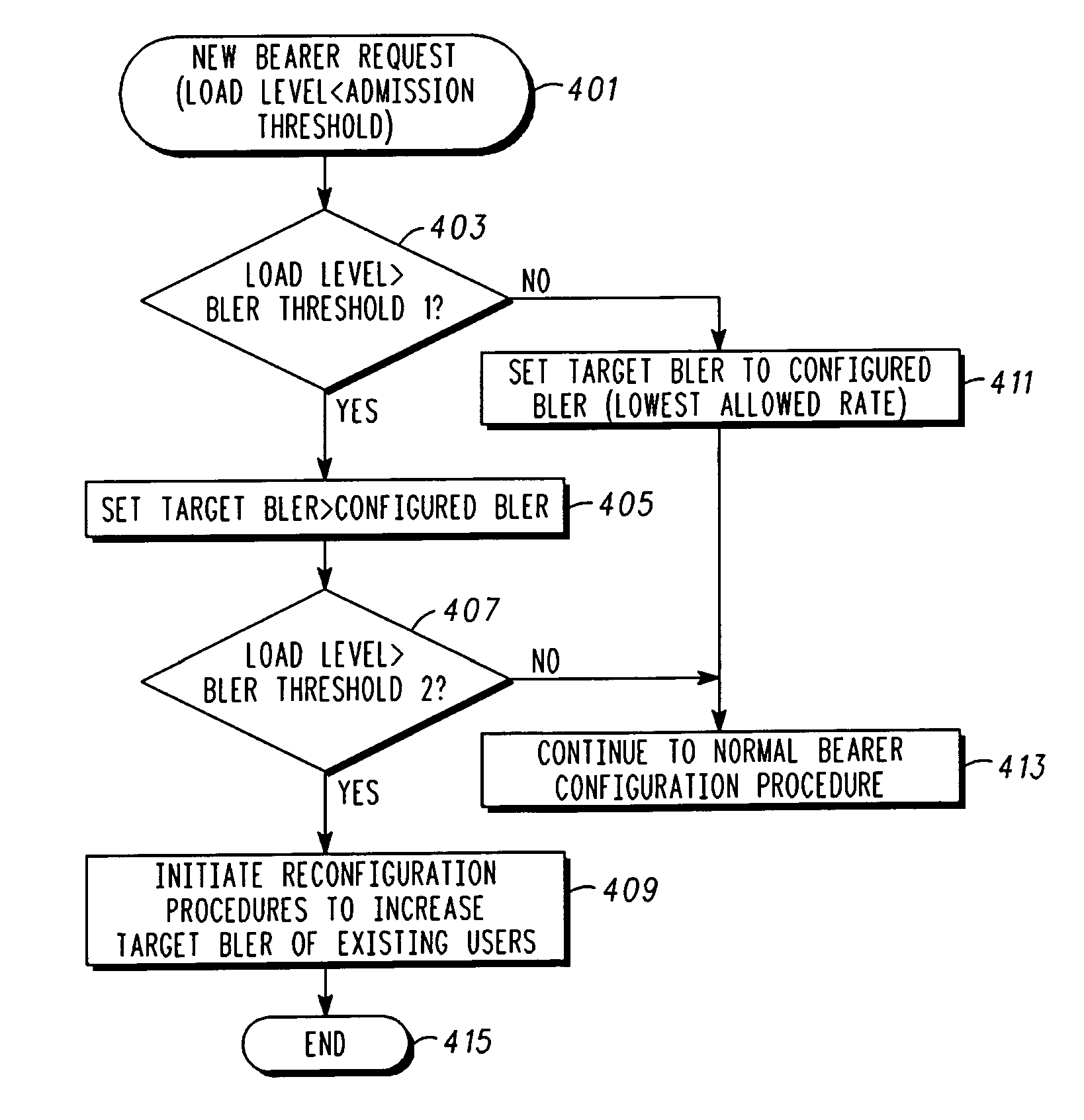

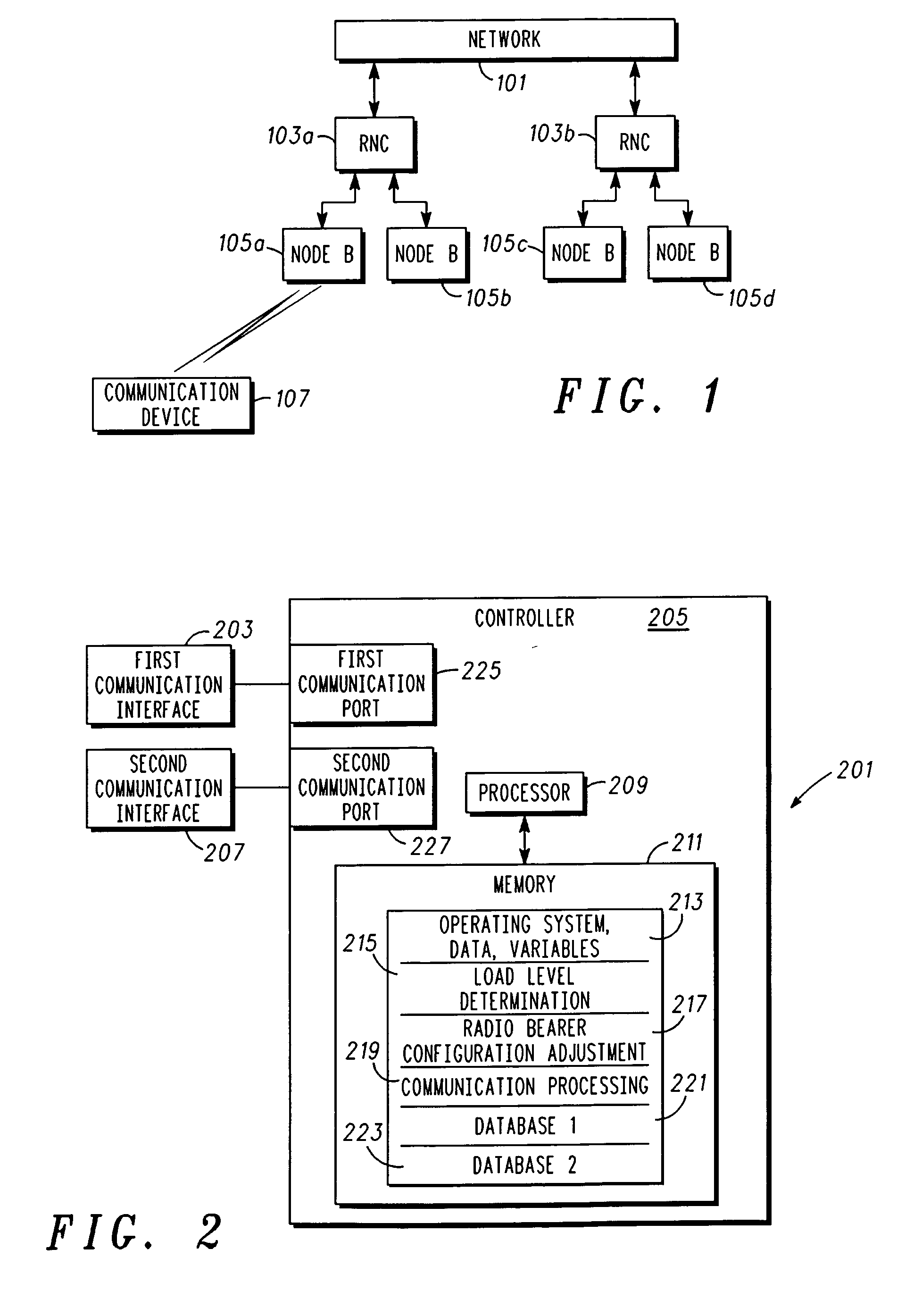

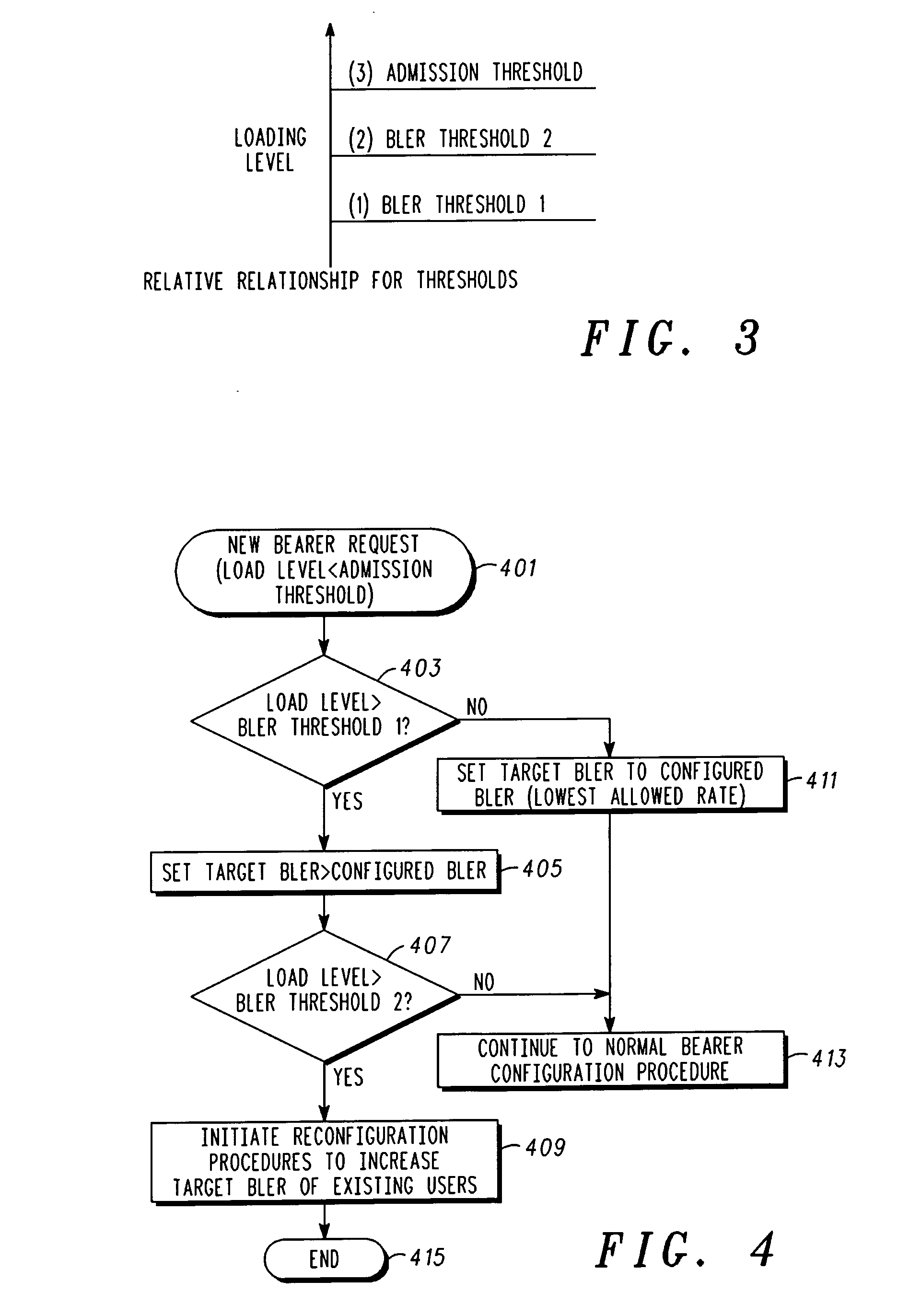

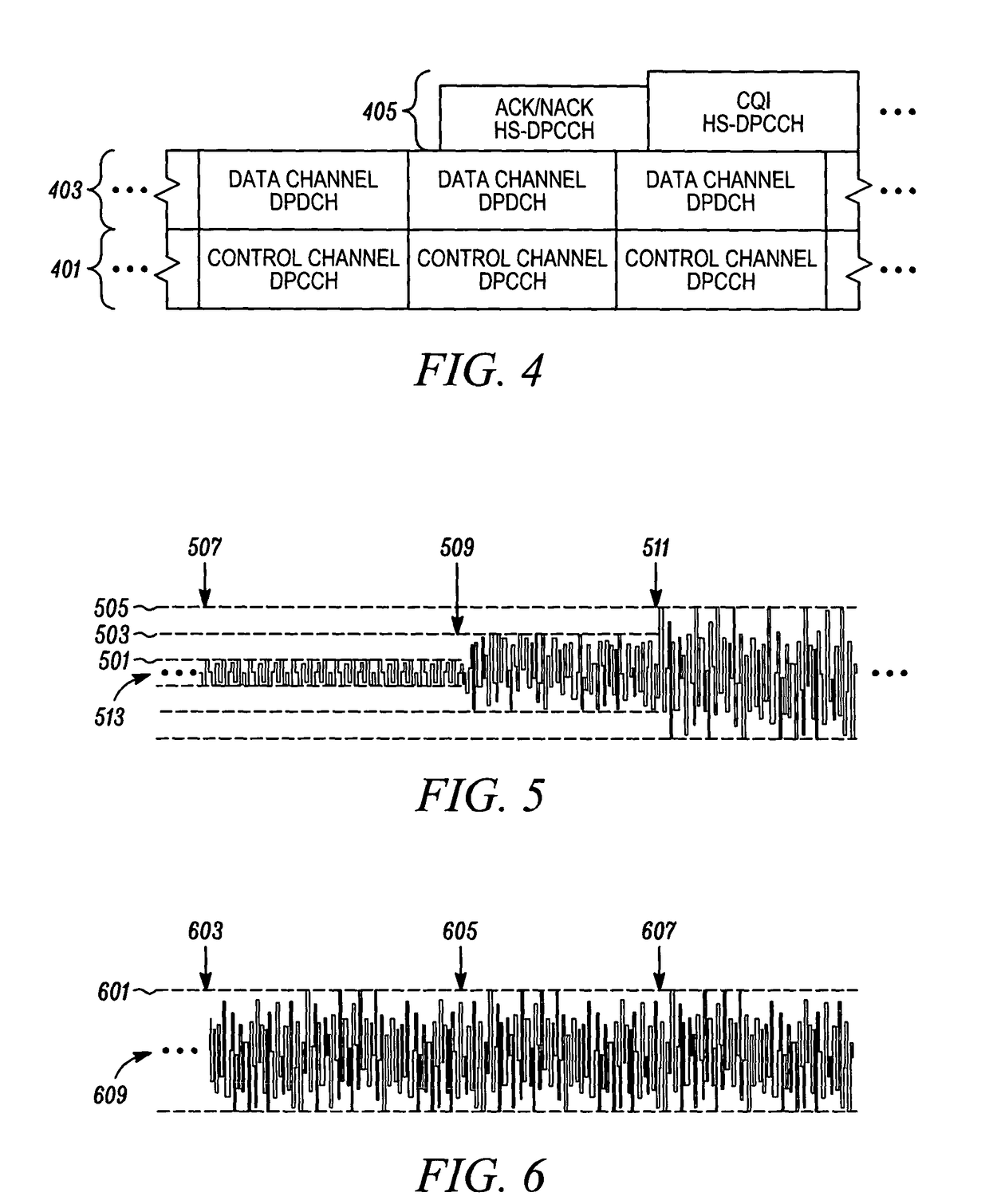

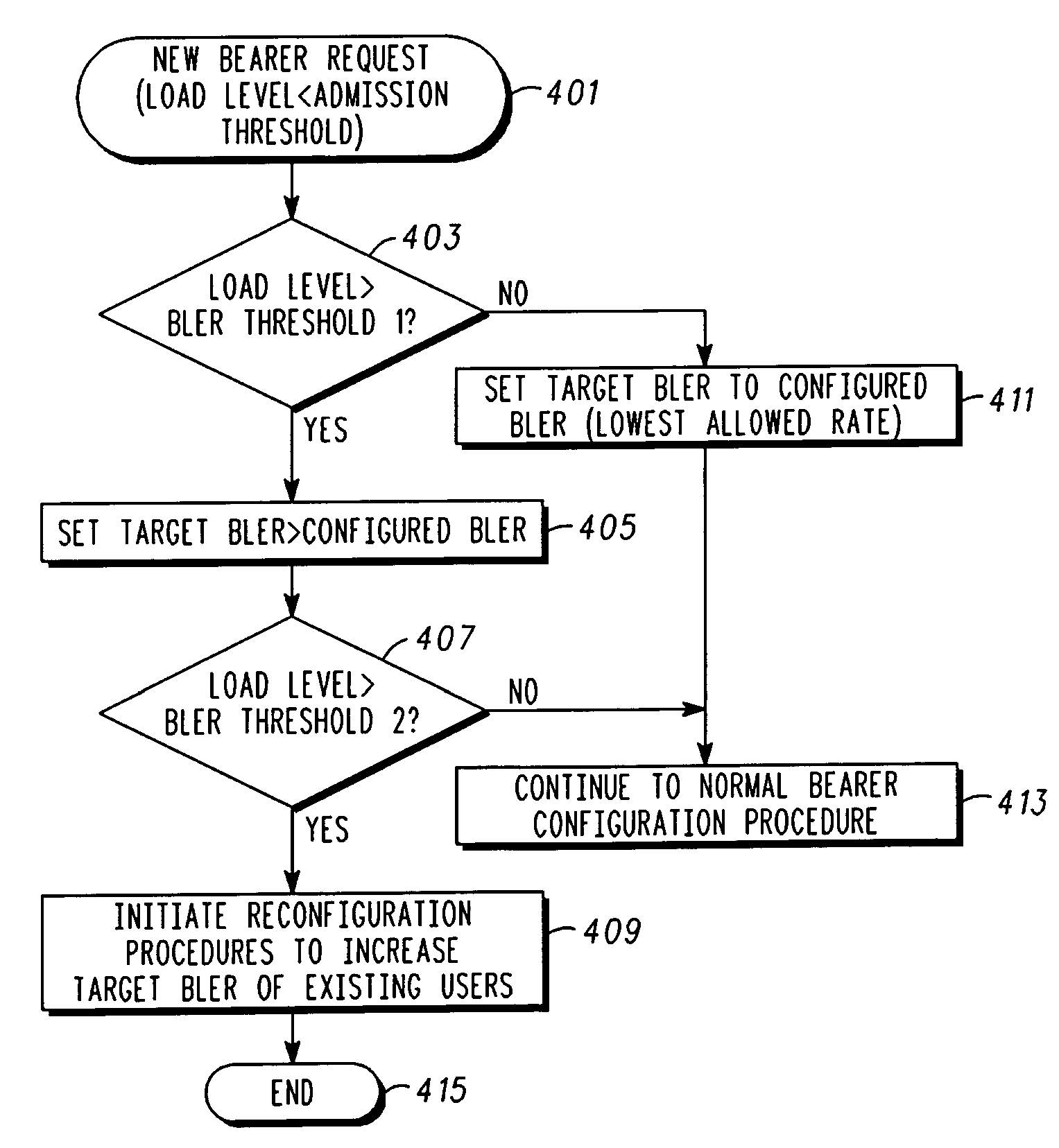

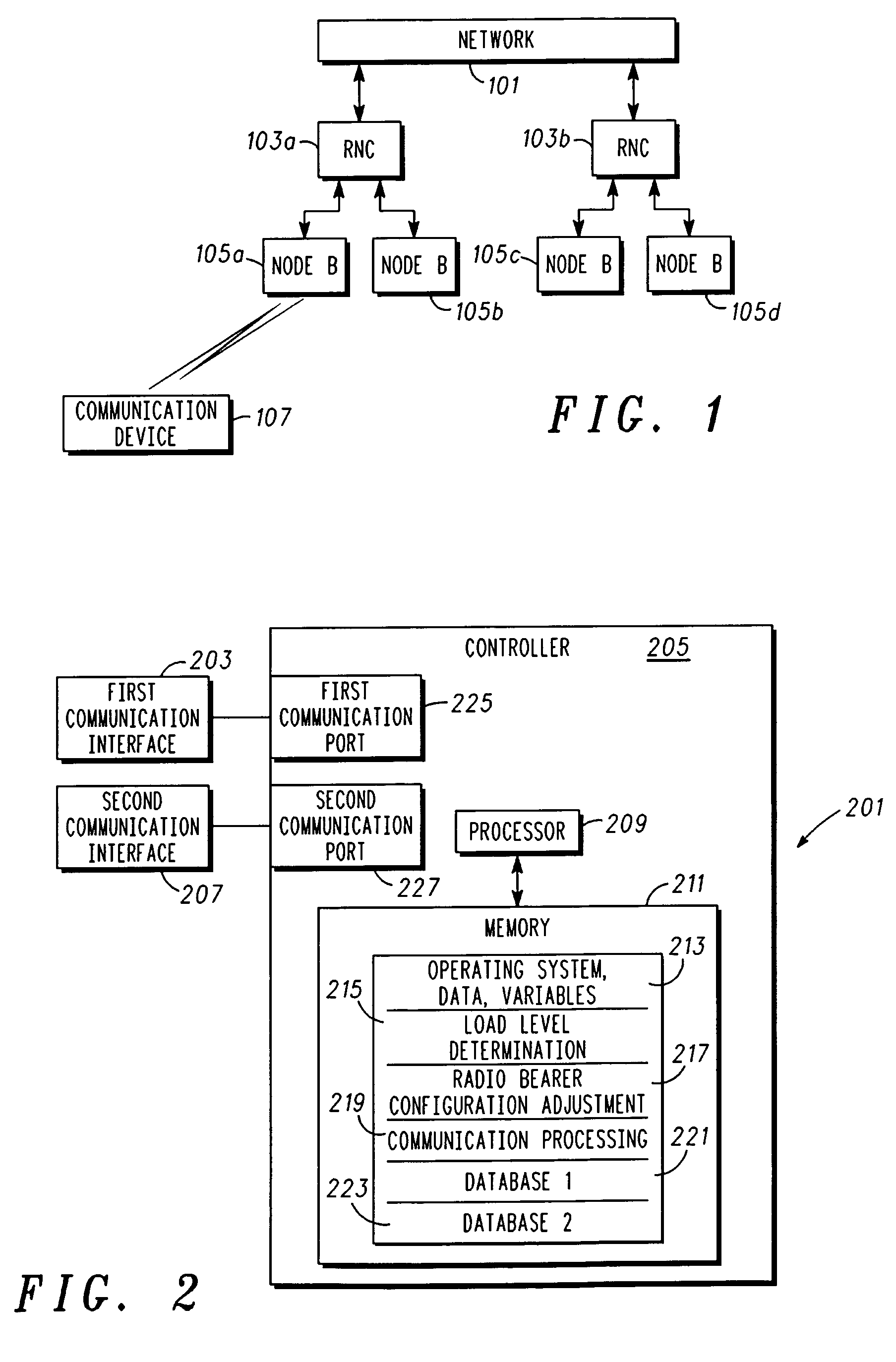

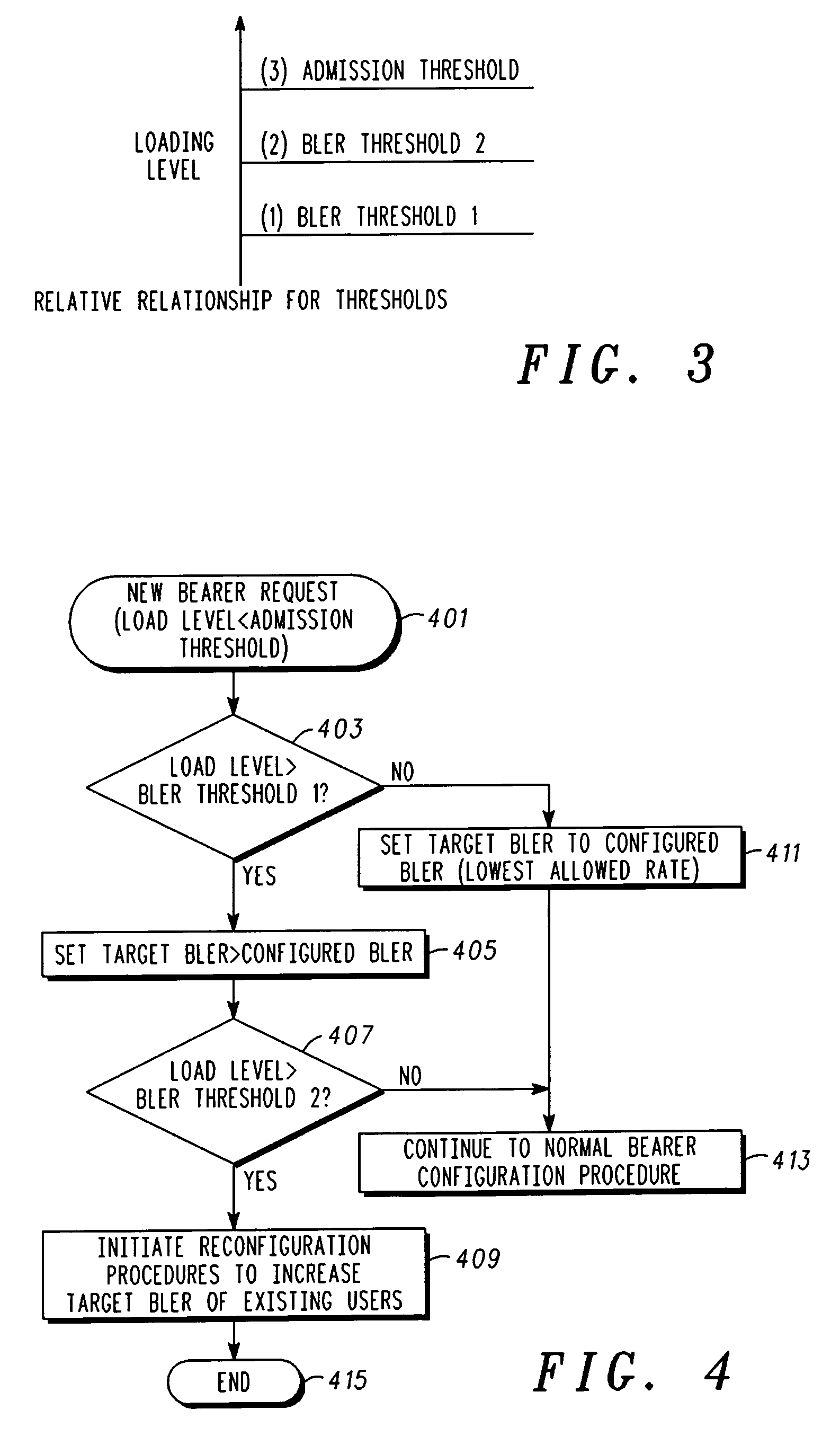

Method and system for control of capacity in a communication network

InactiveUS20060067270A1Improve appreciationInvention is limitedError preventionTransmission systemsCurrent loadControl communications

A controller (103a, 103b) provides dynamic capacity, for use in connection with a communication network (101). A processor of the controller (103a, 103b) that can be utilized in the communication network can be configured to facilitate determining whether a current load level is below a predetermined low usage, and responsive thereto, adjusts a bearer configuration to allow higher throughput per user. Further, the processor (103a, 103b) can be configured to facilitate determining whether the current load level exceeds a predetermined high usage, and responsive thereto, adjusting the bearer configuration to allow lower throughput per user.

Owner:GOOGLE TECH HLDG LLC

Remote control and tactile feedback system and method for medical apparatus

InactiveUS20050066969A1Improve efficiencyHighly effectiveRespiratorsOperating means/releasing devices for valvesRemote controlControl signal

A system and method are for monitoring control signals provided to a medical apparatus based upon tactile feedback from the apparatus. The system and method employ a monitoring signal indicative of a parameter relating to the apparatus or to a condition of a patient associated with the apparatus. The system includes a first feedback device in communication with the apparatus and arranged to provide tactile feedback to a first individual based upon the monitoring signal; a first controller actuatable by the first individual to provide a control signal to the apparatus for carrying a control action in the apparatus; a second feedback device in communication with the apparatus and arranged to provide tactile feedback to a second individual based upon the monitoring signal from the apparatus; and a second controller in communication with the first controller such that the control signal given by the first individual to the first controller is reflected in the second controller and communicated to the second individual. The first feedback device, first controller, second feedback device and second controller are in communication with the apparatus such that the first and second individuals can be distant from the apparatus and patient and move about the apparatus and patient to a desired location.

Owner:DATEX OHMEDA

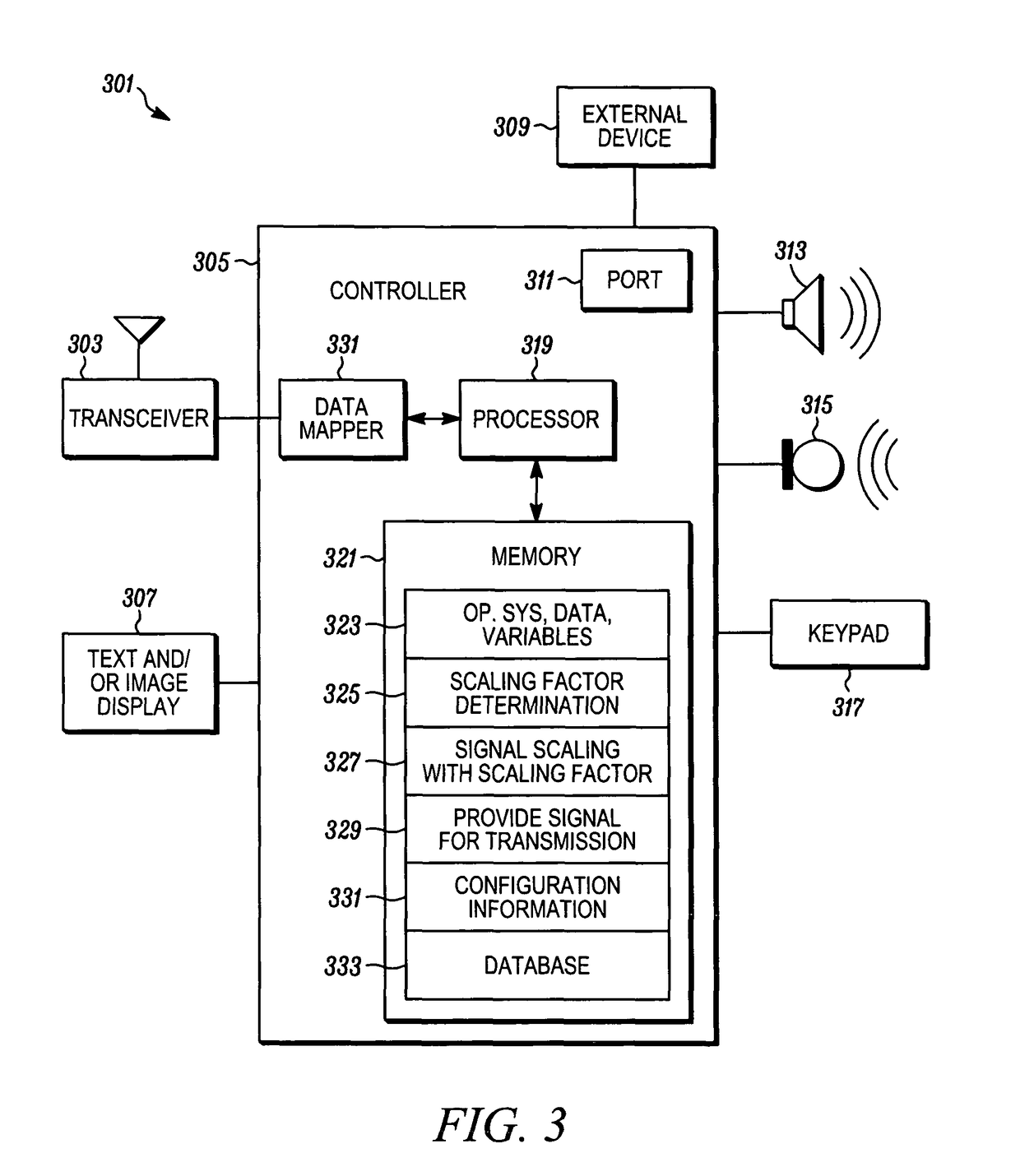

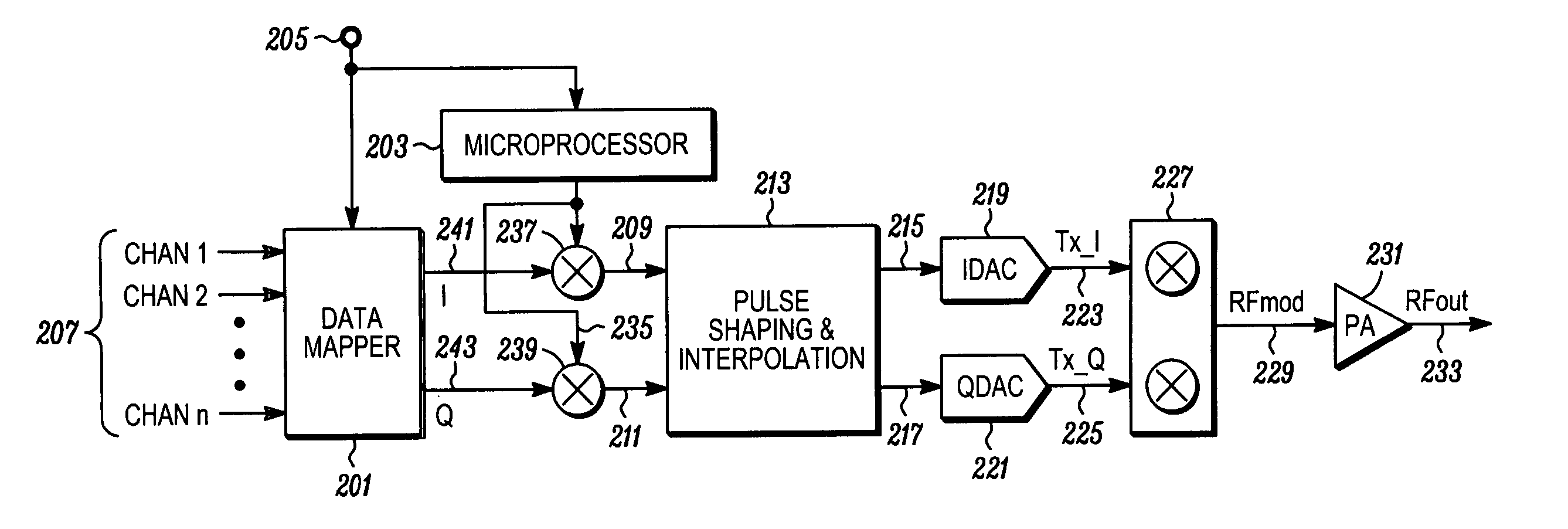

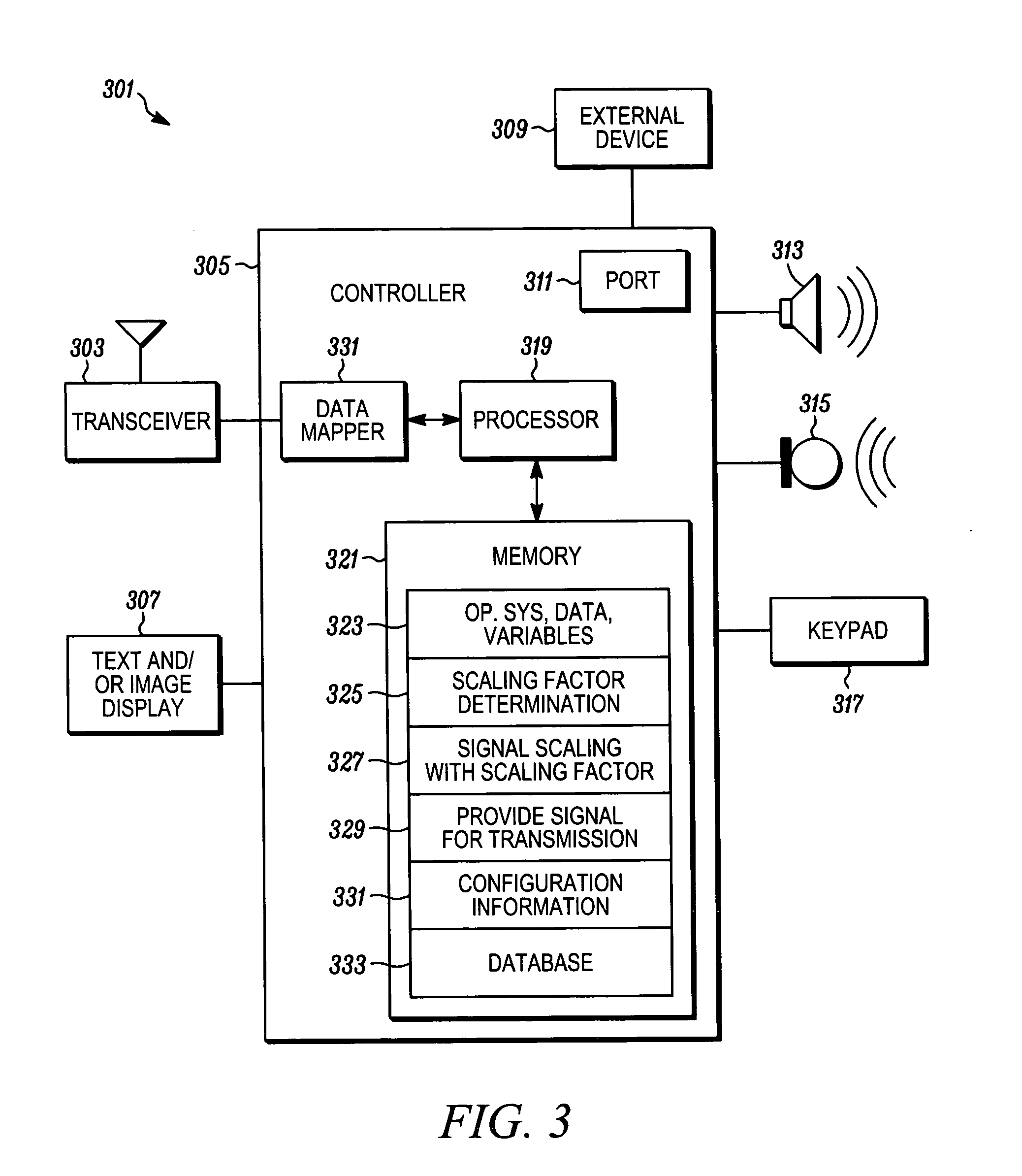

Method and system for scaling a multi-channel signal

InactiveUS7907671B2Improve appreciationInvention is limitedPower managementSecret communicationCommunication unitComputer science

A communication unit is provided having a transmitter and a processor (103). The processor (103) receives information (105) representative of a configuration of physical channels (107). The processor (103) determines a scaling factor responsive to the information (105) and facilitates scaling a signal (109, 111) provided by a combination of the channels utilizing the scaling factor. The scaled signal (109, 111) is provided to the transmitter.

Owner:GOOGLE TECH HLDG LLC

Passive probing for handover in a local area network

InactiveUS6980535B2Improve appreciationInvention is limitedTime-division multiplexData switching by path configurationCommunication unitPassive probing

A WLAN (108) includes a first access point (104) for providing wireless service within a first coverage area, a second access point (106) for providing wireless service within a second coverage area and programmed to transmit probe responses, and a wireless communications unit (102) located within the first coverage area and operating on the wireless service of the first access point (104). The communications unit (102) is programmed to monitor, or passively probe, for the probe responses, or is instructed by the first access point (104) on when to monitor for the probe responses, transmitted by the second access point (106). By executing such passive probing, the communications unit (102) may make handover decisions for switching between the wireless service of the first access point (104) to the wireless service of the second access point (106) based on access point data included in the probe responses.

Owner:MOTOROLA SOLUTIONS INC

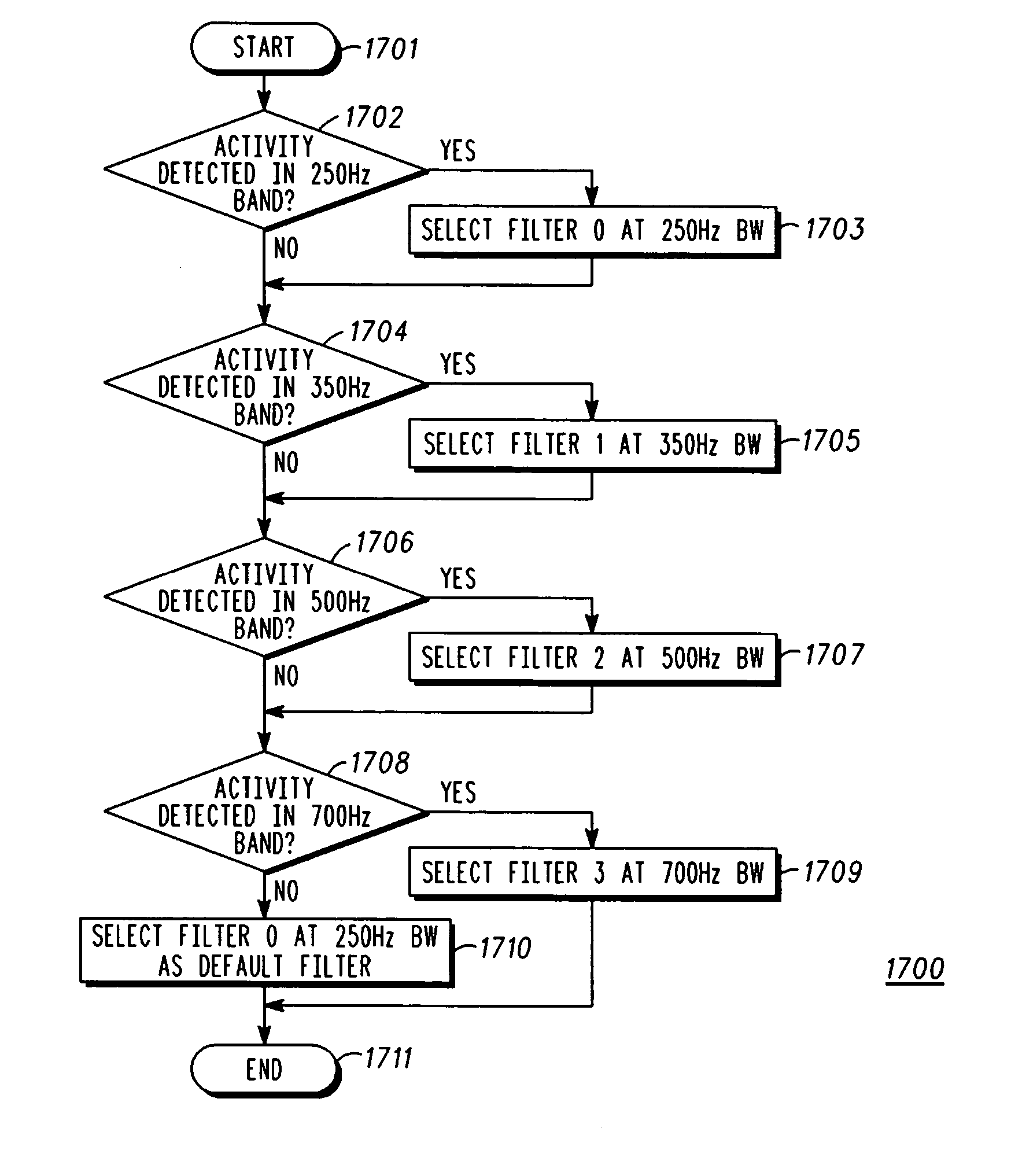

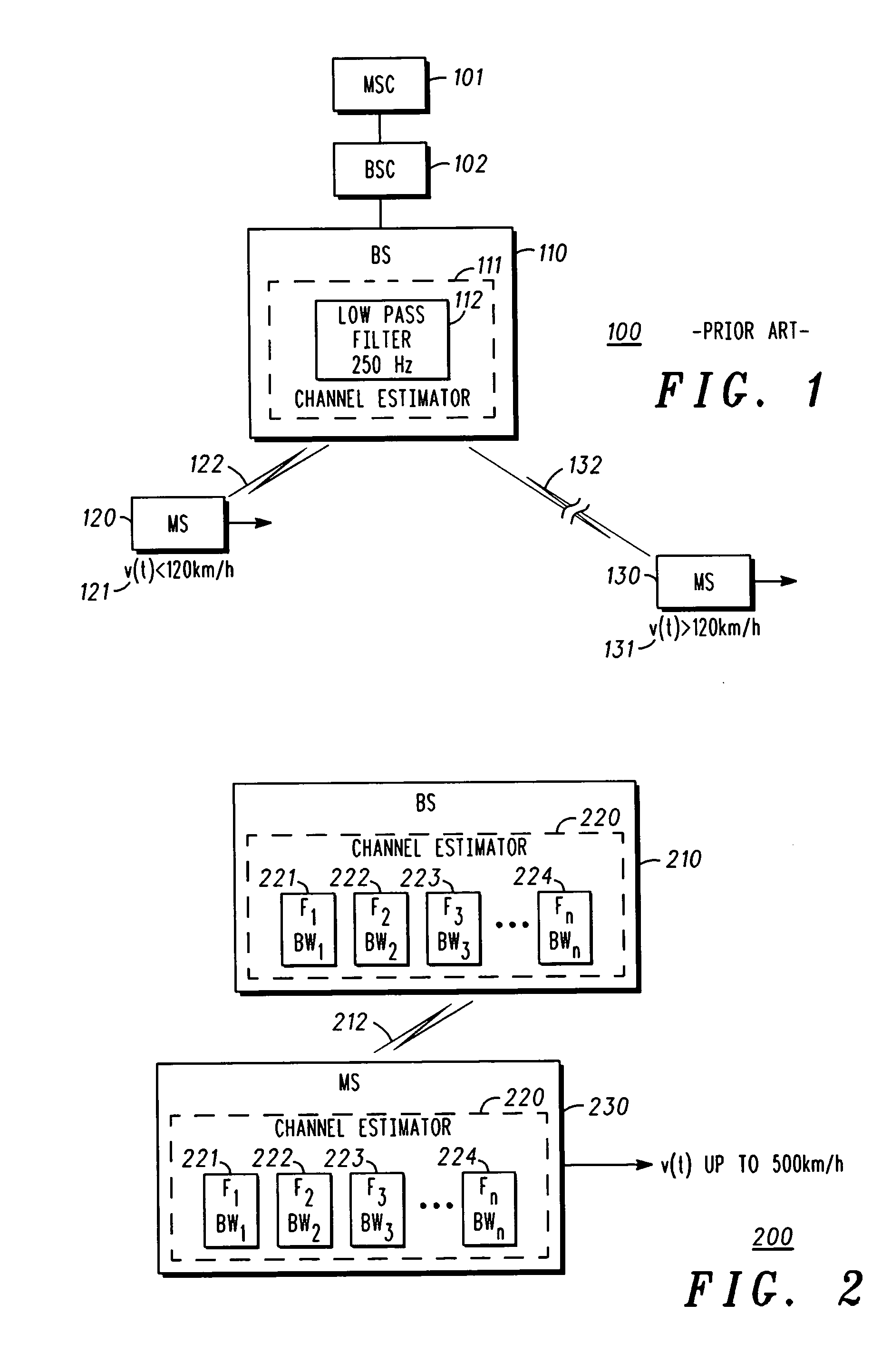

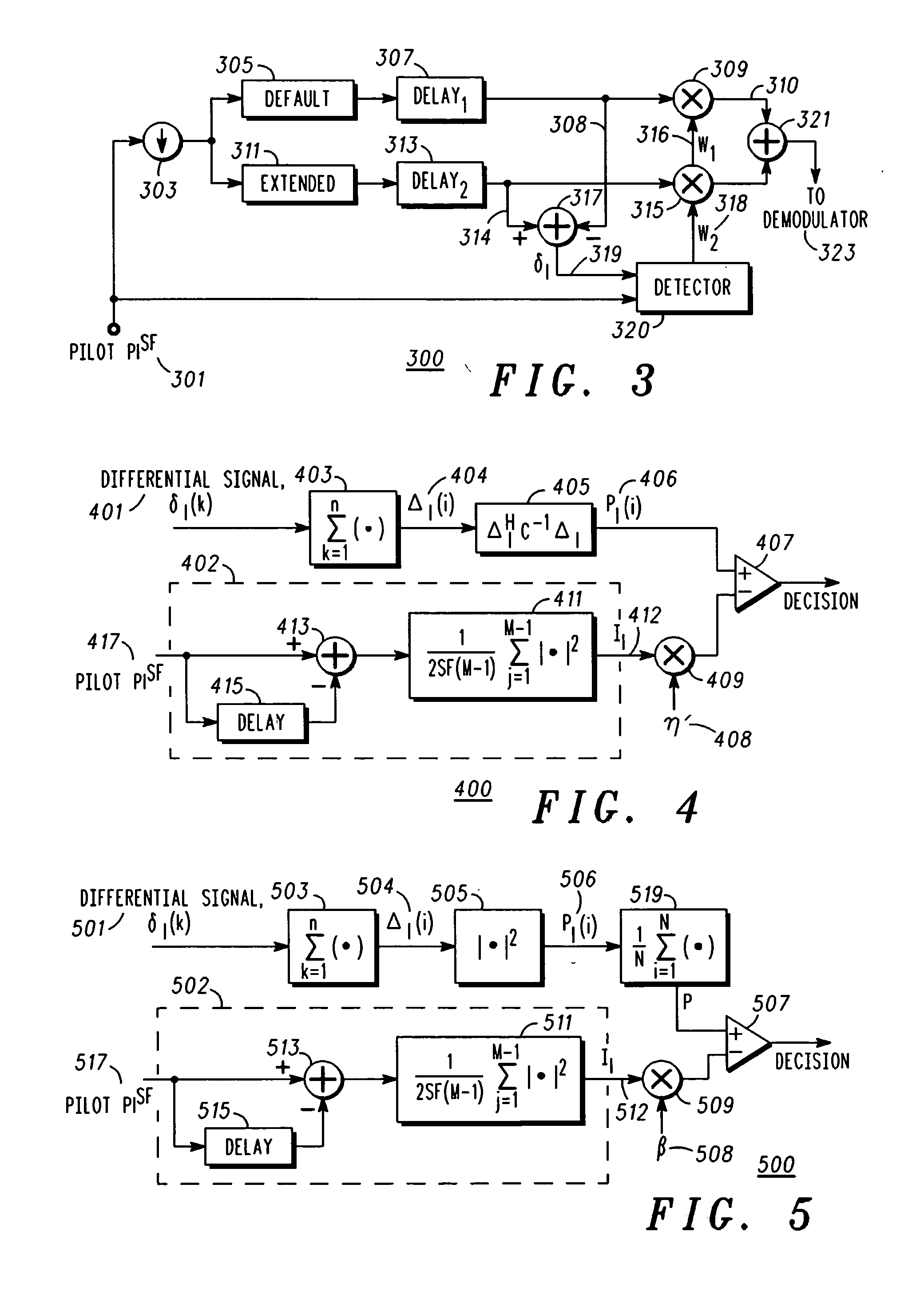

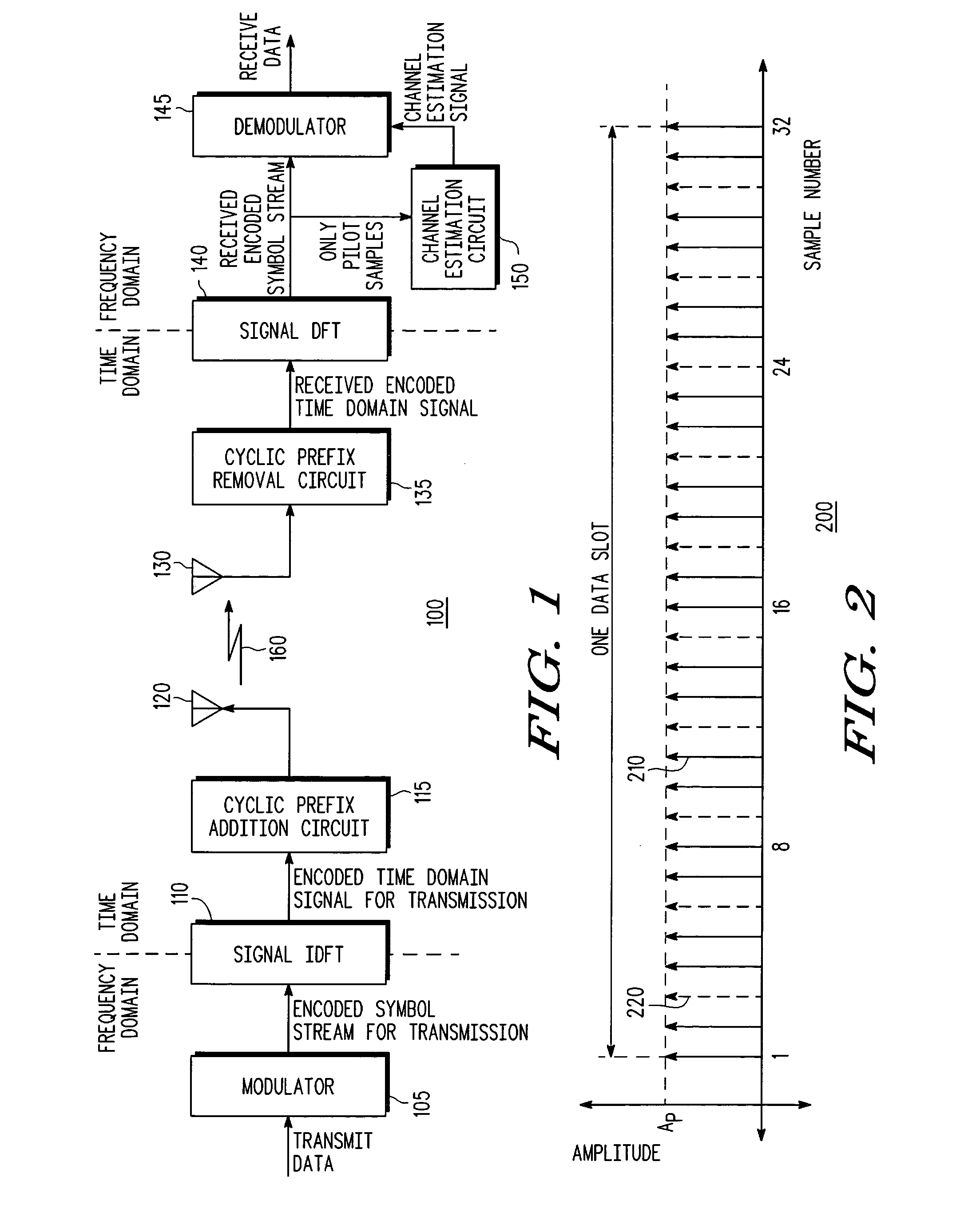

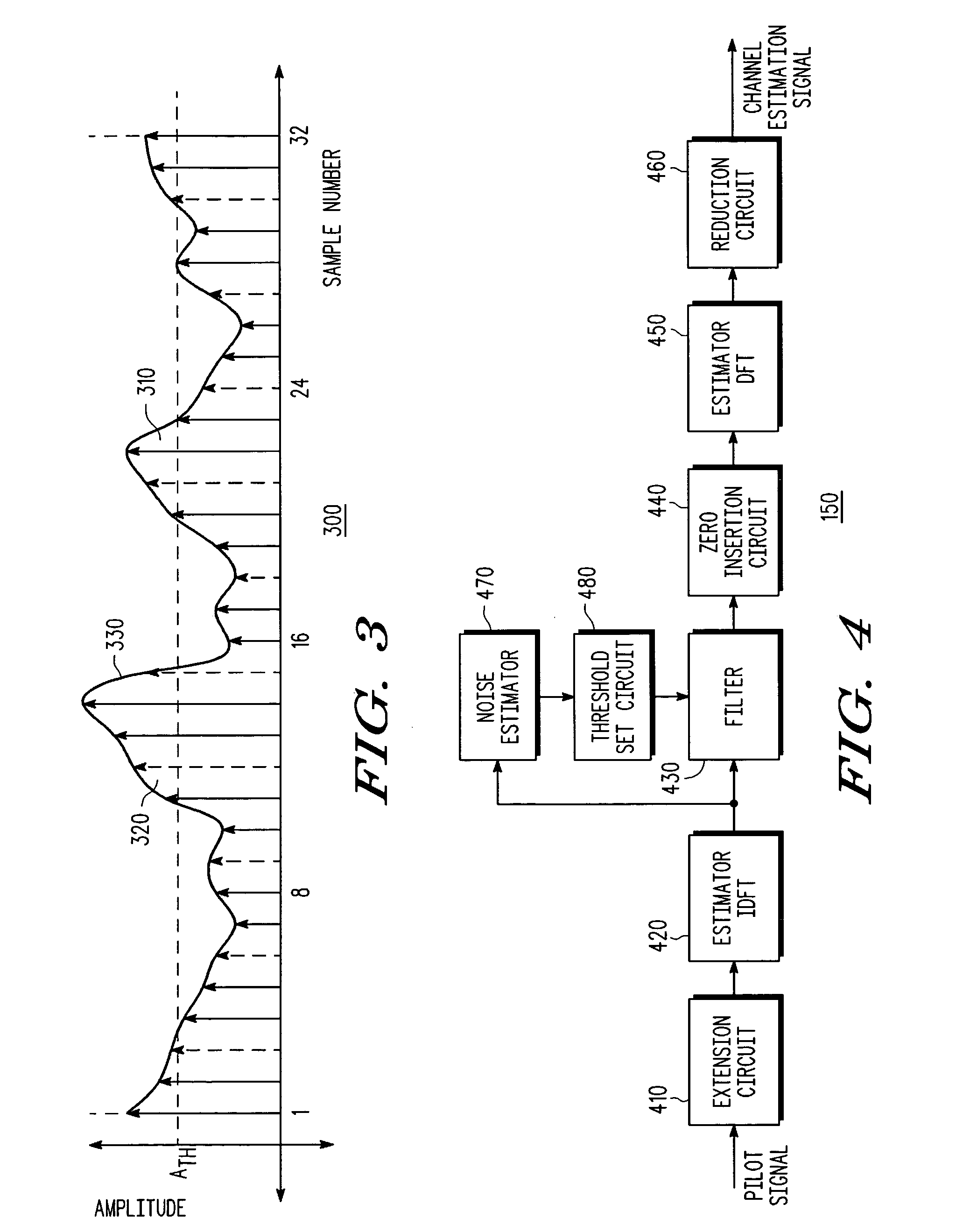

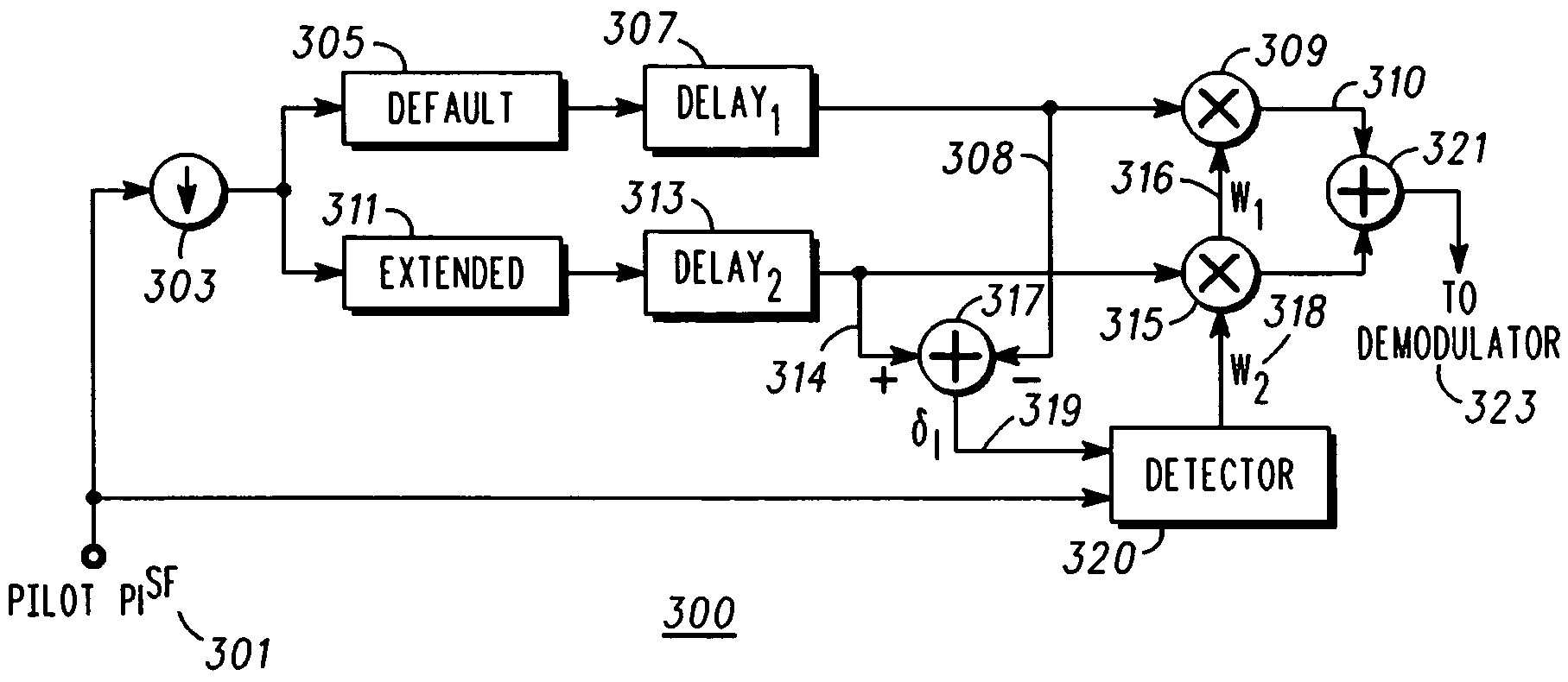

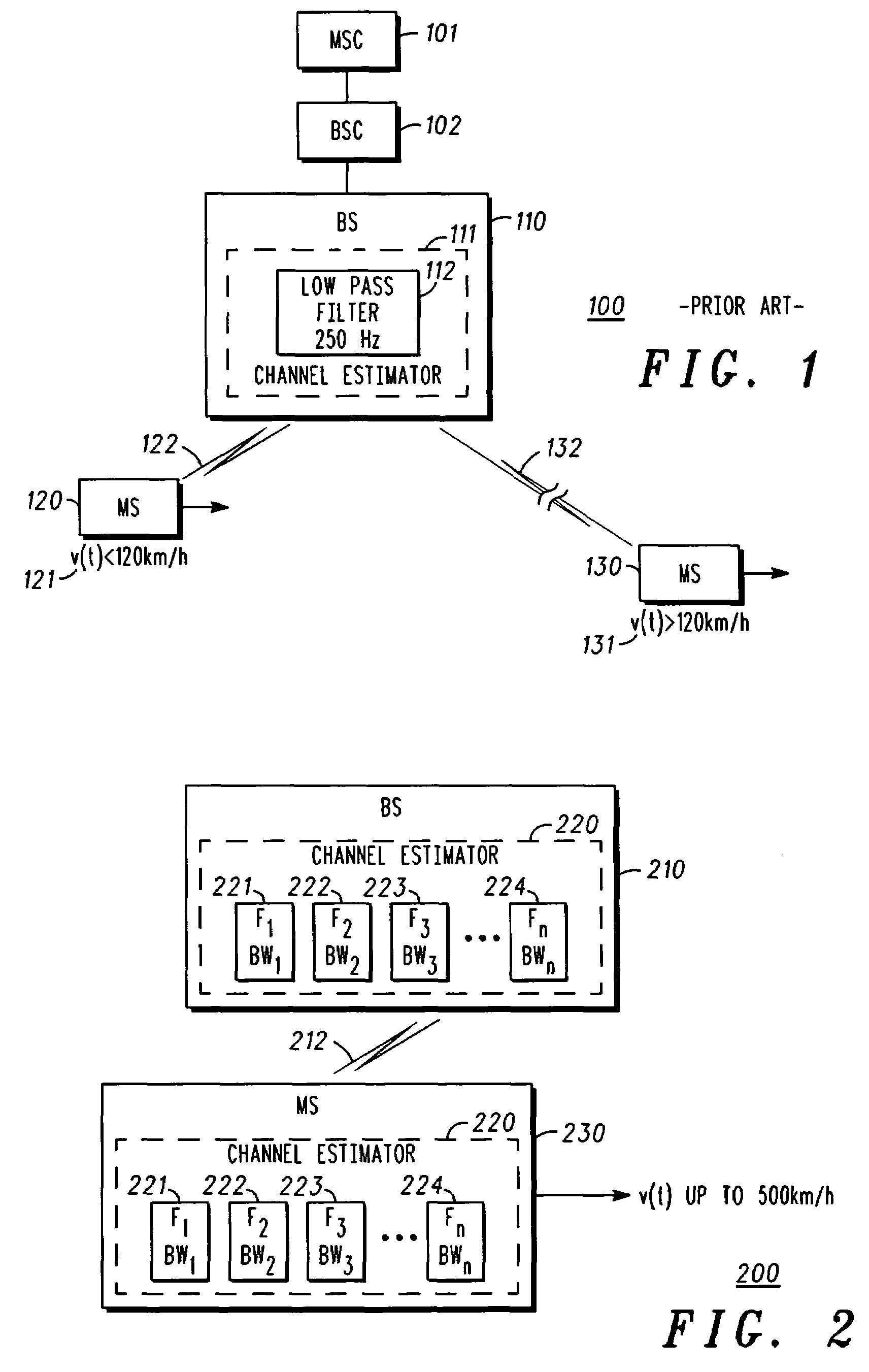

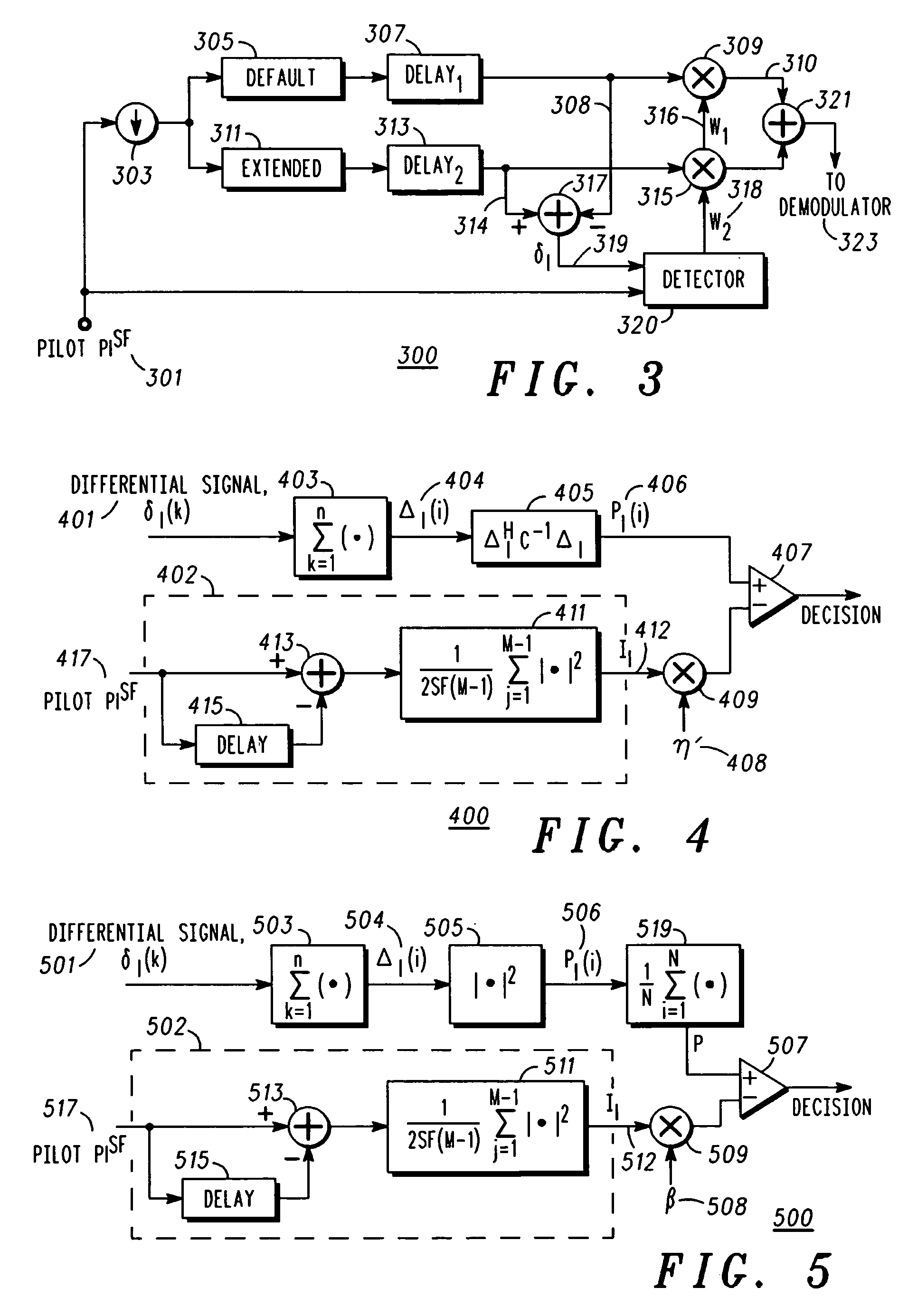

Channel estimator with extended channel bandwidth

InactiveUS20060133457A1Improve appreciationInvention is limitedChannel estimationTelecommunicationsPilot signal

A method (1700) and apparatus (1801) provide channel estimation with extended bandwidth filters. Antenna (1813) receives a signal such as a pilot signal and detects a bandwidth associated with the pilot signal in a detector (320). One of a plurality of filters (603, 605, 607, and 609) including extended bandwidth filters (311) and a default filter (305) can be selected by a selector (617). If the detector detects activity associated with a wider bandwidth, the filter associated with the wider bandwidth is selected over the presently selected filter. If no activity is detected, the default filter is selected.

Owner:MOTOROLA MOBILITY LLC

Multi-state load switched power amplifier for polar modulation transmitter

ActiveUS20060145758A1Improve appreciationInvention is limitedGain controlAmplifier modifications to reduce temperature/voltage variationEngineeringImpedance matching

A polar modulation power amplifier circuit includes a control circuit (101) to determine and provide a load selection signal (127), wherein the load selection signal (127) is determined responsive to a requested power signal (119). A power amplifier (113) is responsive to a power control signal (141), for amplifying an RF signal (139) to produce an amplified signal (145), having an output power level. A variable impedance matching circuit (117) is responsive to the load selection signal (127), to adjust a relationship between the control level and the output power level, to produce a range-adjusted amplified signal (147).

Owner:GOOGLE TECH HLDG LLC

Multiple-antenna device having an isolation element

ActiveUS7592969B2Improve appreciationInvention is limitedSimultaneous aerial operationsAntenna supports/mountingsGround planePrinted circuit board

A multiple-antenna device is provided, comprising: a printed circuit board having a ground plane configured to provide electromagnetic isolation between a first side of the printed circuit board and a second side of the printed circuit board; a first non-conductive support member formed over the first side of the printed circuit board; a second non-conductive support member formed over the second side of the printed circuit board; a first antenna formed over the first non-conductive support member; and a second antenna formed over the second non-conductive support member, wherein the first antenna is electrically connected to a first feed point on a first portion of the printed circuit board that is not connected to the ground plane, and wherein the second antenna is electrically connected to a second feed point on a second portion of the printed circuit board that is not connected to the ground plane.

Owner:QUALCOMM INC

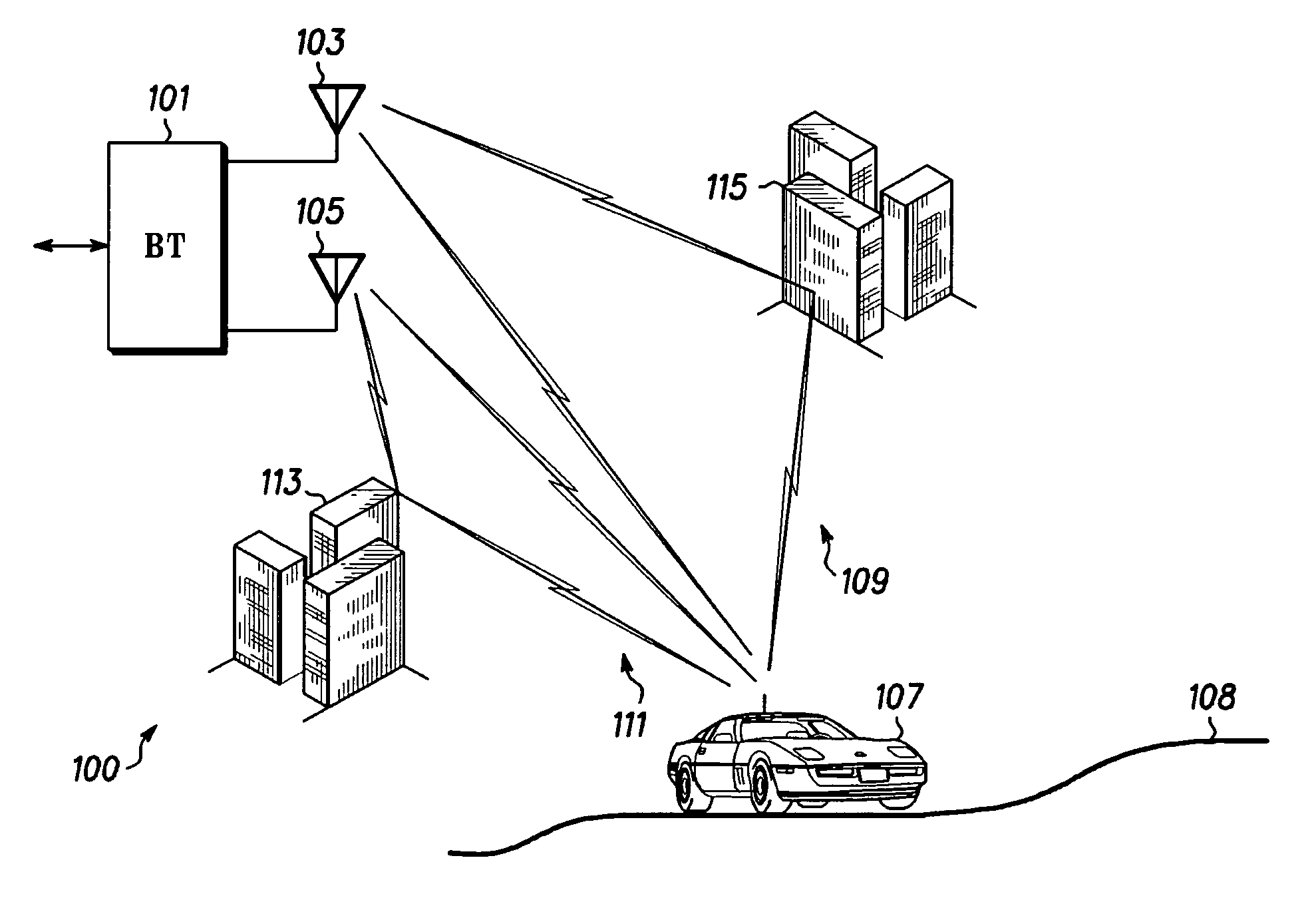

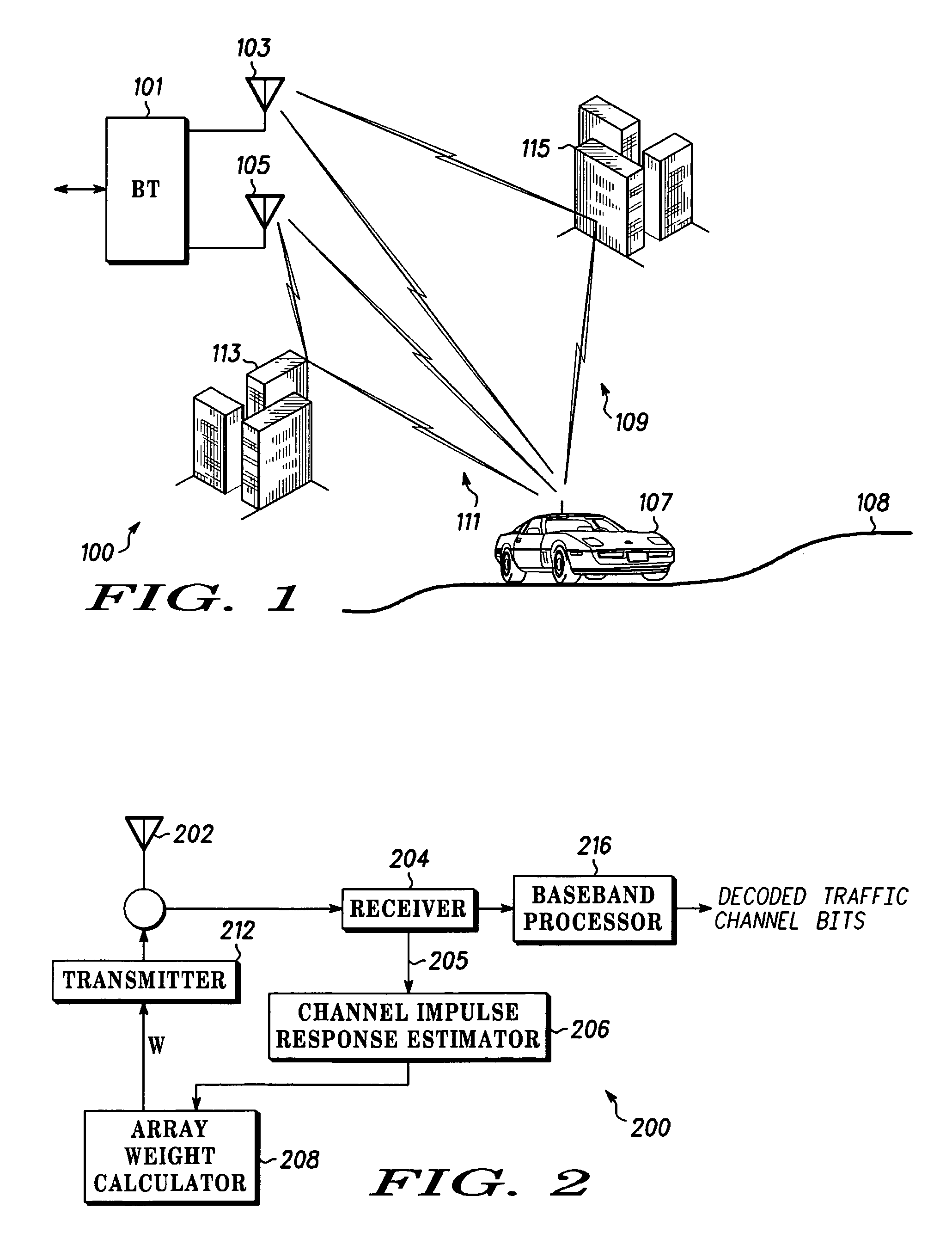

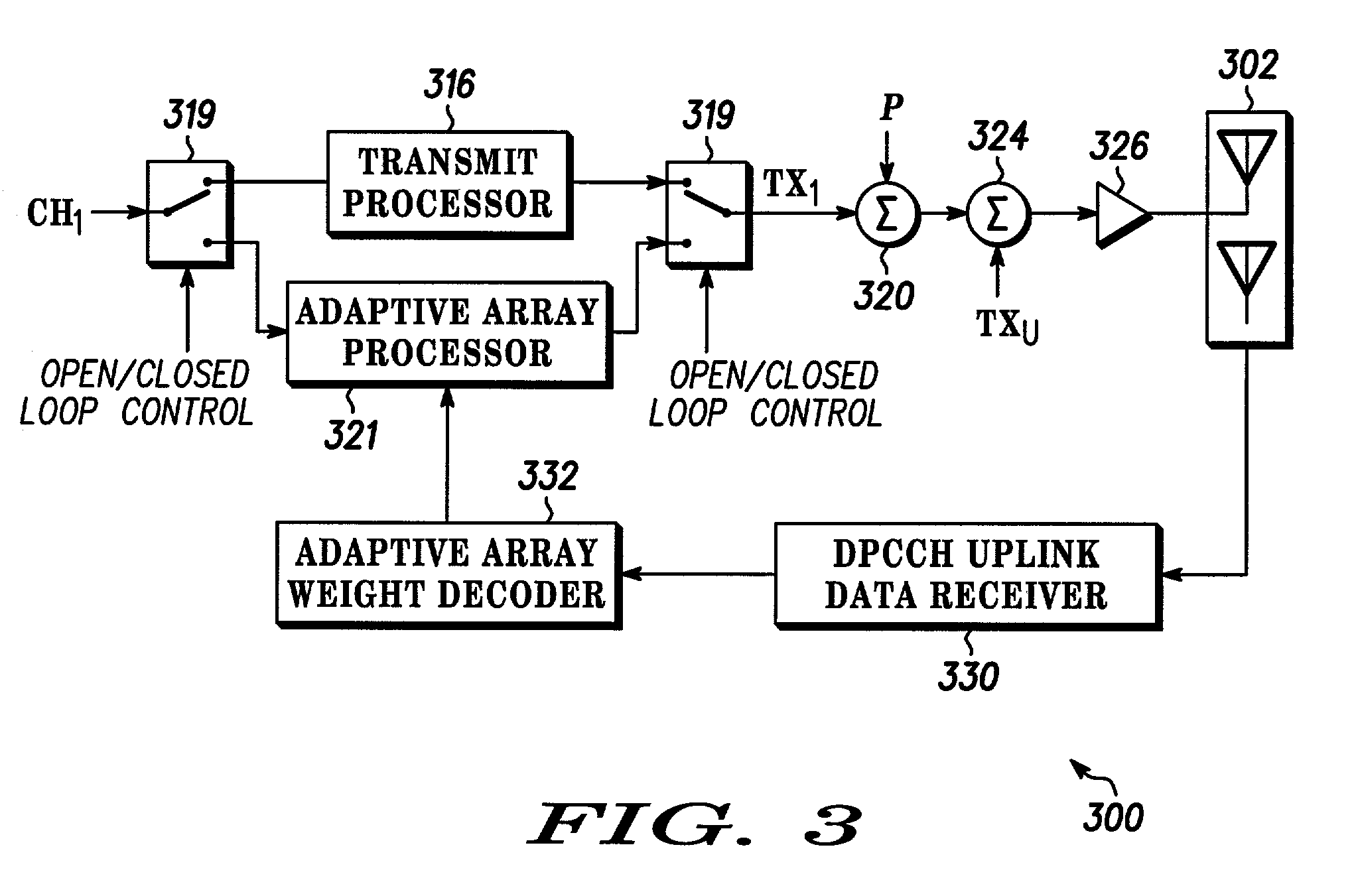

System implementing closed loop transmit diversity and method thereof

ActiveUS7010055B2Improve appreciationInvention is limitedSpatial transmit diversityFrequency-modulated carrier systemsTime segmentClosed loop

A method of and apparatus for adapting an antenna array for closed loop transmit diversity, the method comprising: receiving an adapting signal corresponding to an antenna array weighting pattern for a time period; demodulating the adapting signal to provide a symbol for the time period; determining a preferred symbol from the symbol for the time period and a previous symbol for a previous time period; and transmitting with an antenna array weighting pattern corresponding to the preferred symbol.

Owner:MOTOROLA SOLUTIONS INC

Mass spectrometry system for continuous control of environment

InactiveUS7071466B2Continuous operationCompact structureStability-of-path spectrometersTime-of-flight spectrometersThree levelData acquisition

A mass spectrometry system for continuous control of environment based on the use of an aerosol TOF MS that provides operation with a high duty cycle of up to 98% and can be realized in the form of a mobile unit having a data acquisition and analysis system with three levels of data correlation on the basis of constant interaction between various actuating mechanisms of the system via a central processing unit. The TOF MS is based on the use of quadrupole lenses with angular gradient of the electrostatic field. As a result, two independently analyzed discrete flows of particles pass through the ion mass separation chamber of the TOF MS without interference with each other. The system can be mounted either on an underwater and ground vehicle, or on an aircraft.

Owner:YURI GLUKHOY

System and method for monitoring a moving vehicle

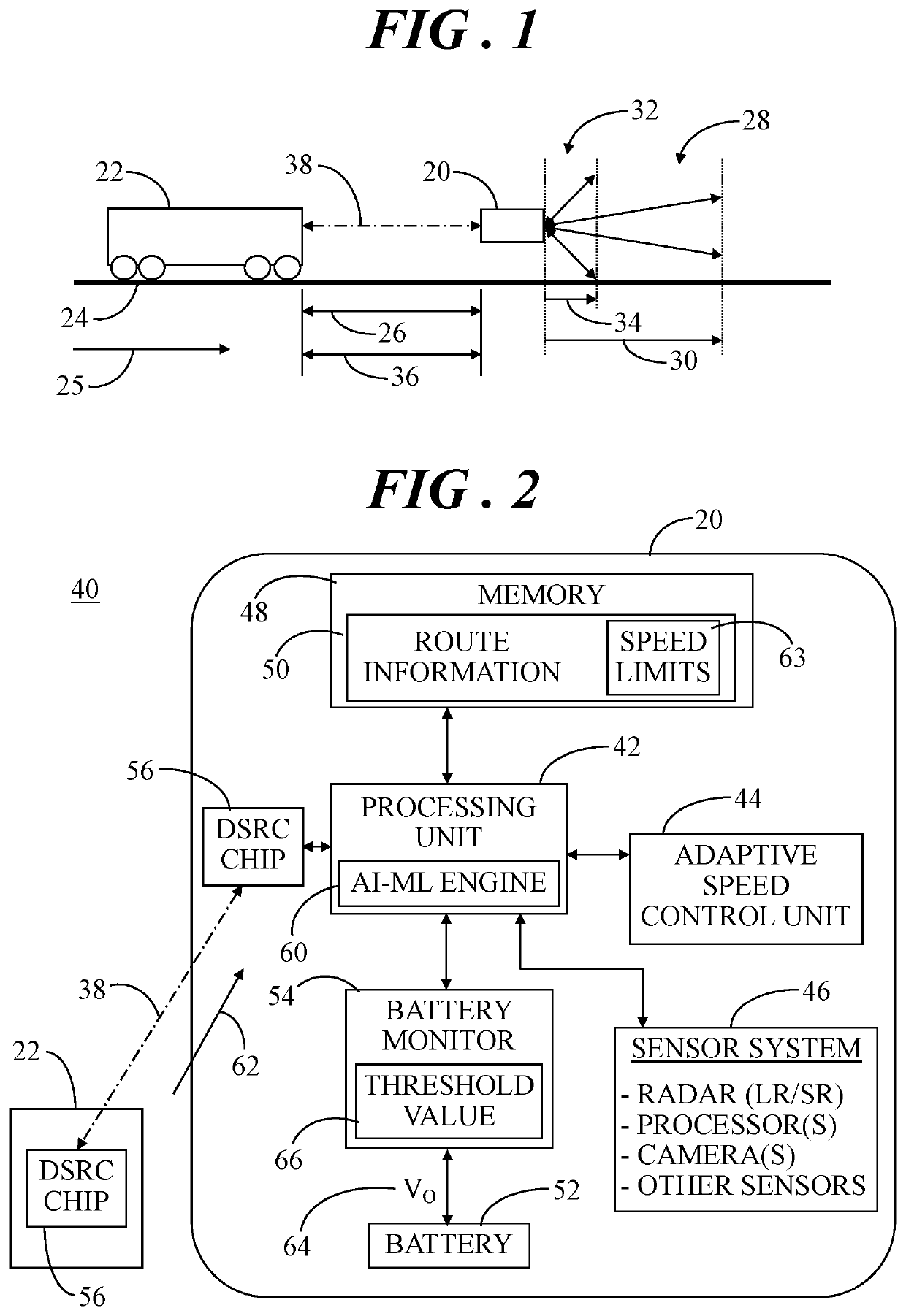

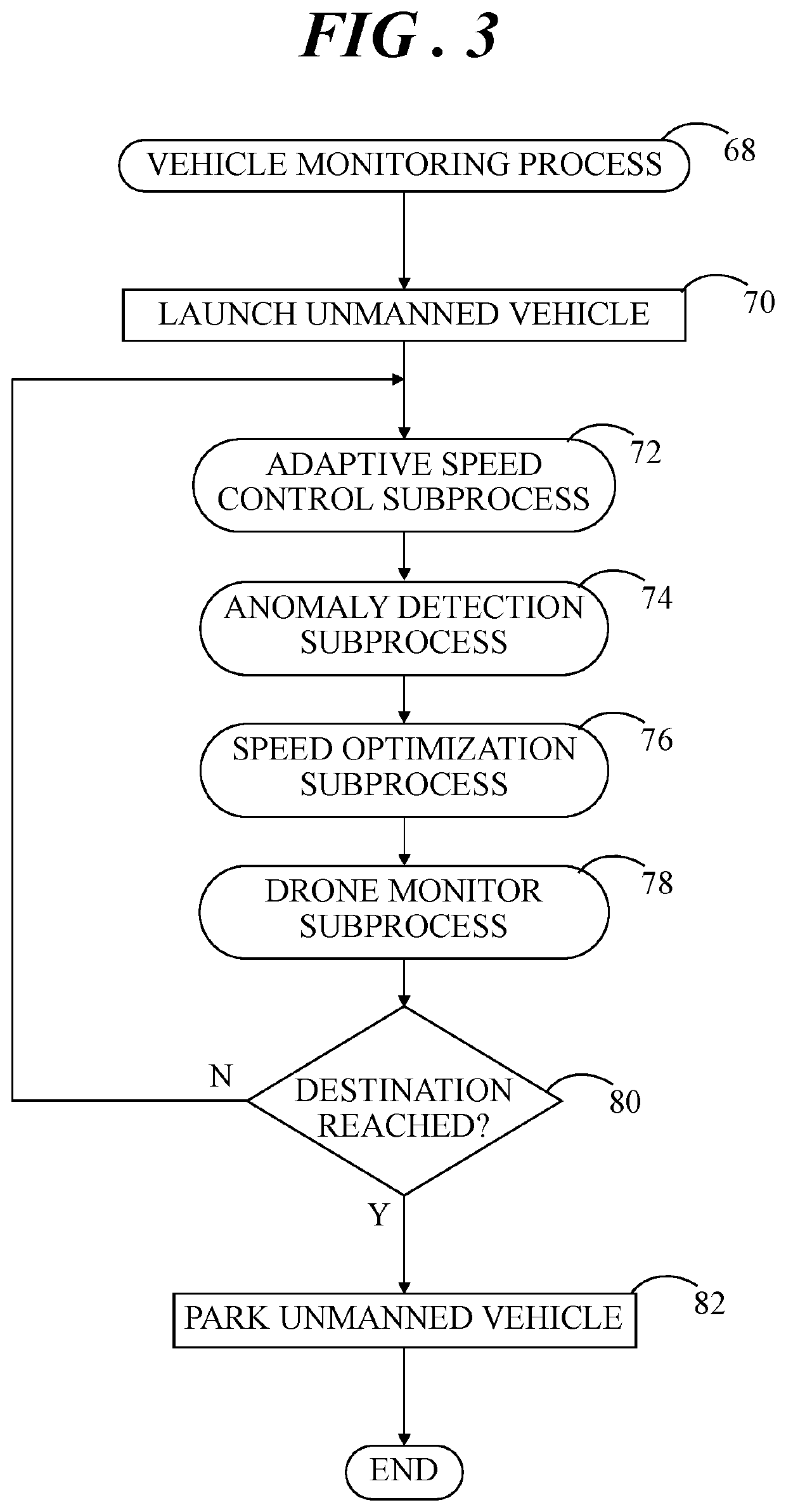

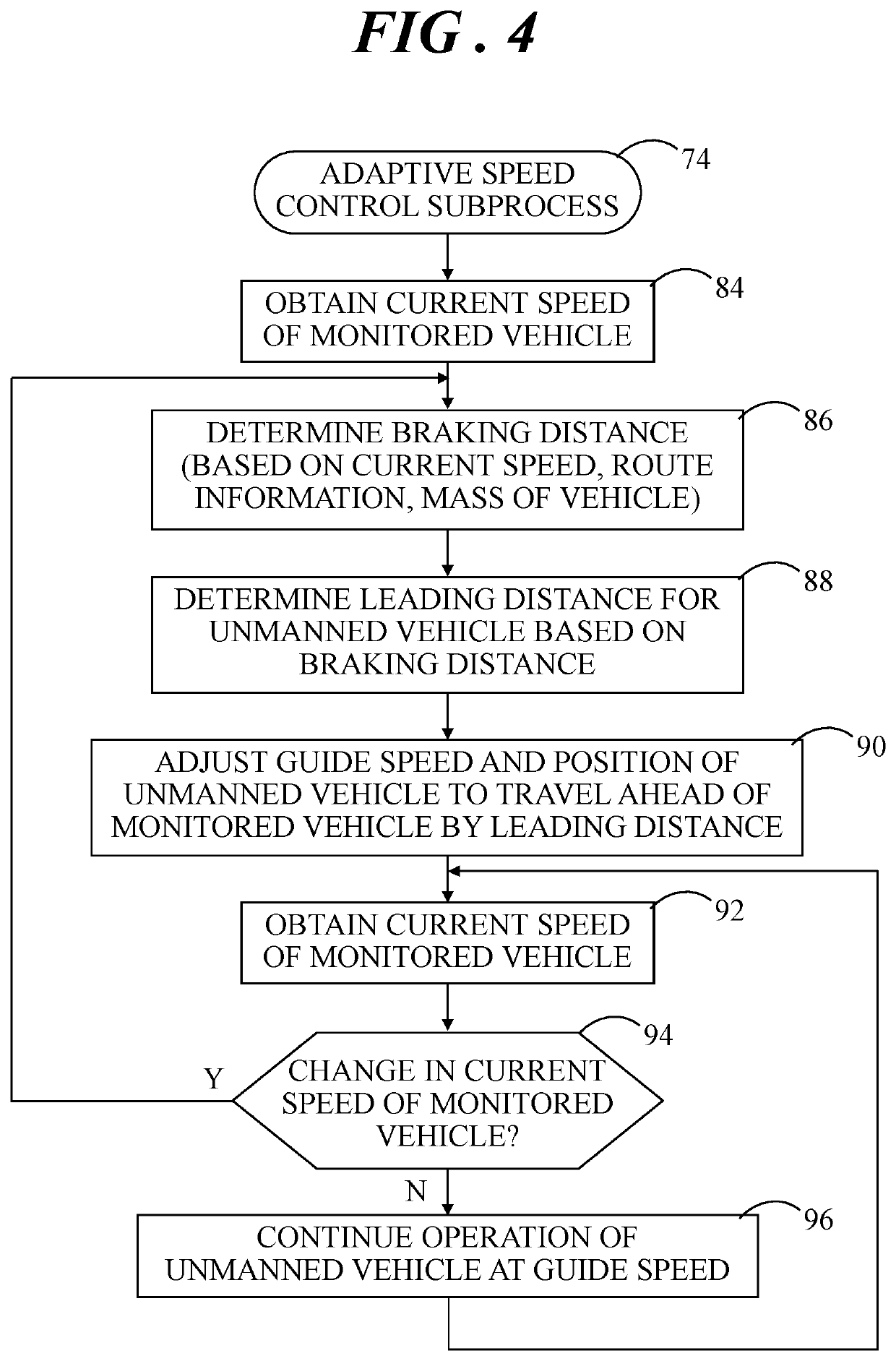

ActiveUS20210146977A1Improve appreciationInvention is limitedSignalling indicators on vehiclePropulsion by batteries/cellsTelecommunications linkUncrewed vehicle

A system includes a drone for monitoring a second vehicle moving along a route. The drone includes a processing unit, a speed control unit, a sensor system, and a communication module. The processing unit determines a braking distance for the second vehicle in response to a current speed of the second vehicle and determines a leading distance for the drone based on the braking distance. The speed control unit adjusts a guide speed and a position of the unmanned vehicle such that the drone travels ahead of the second vehicle by at least the leading distance. The sensor system detects a hazardous condition along the route ahead of the unmanned vehicle, and the communication module enables a wireless communication link between the drone and the second vehicle for notifying the second vehicle of the hazardous condition.

Owner:NXP BV

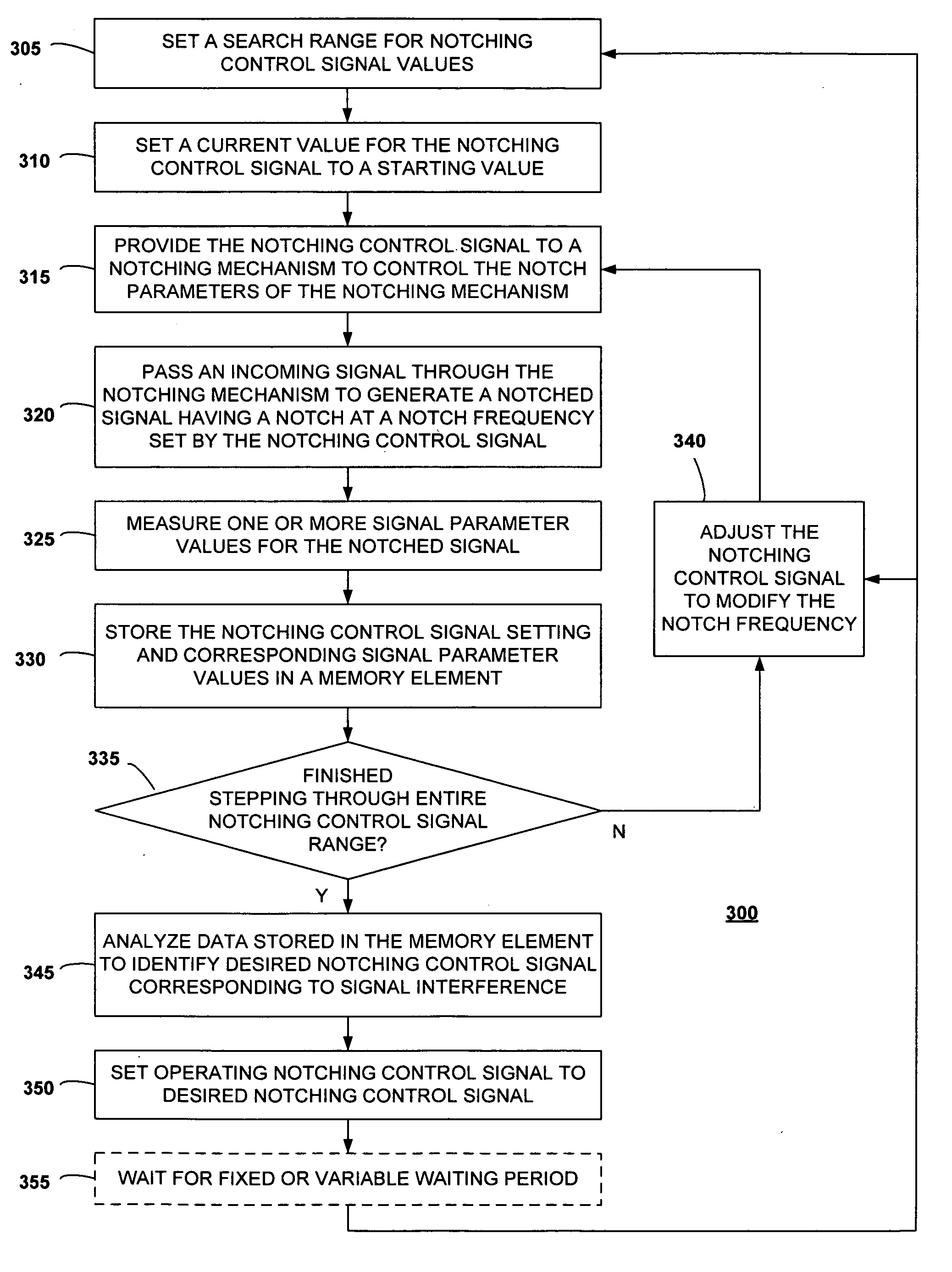

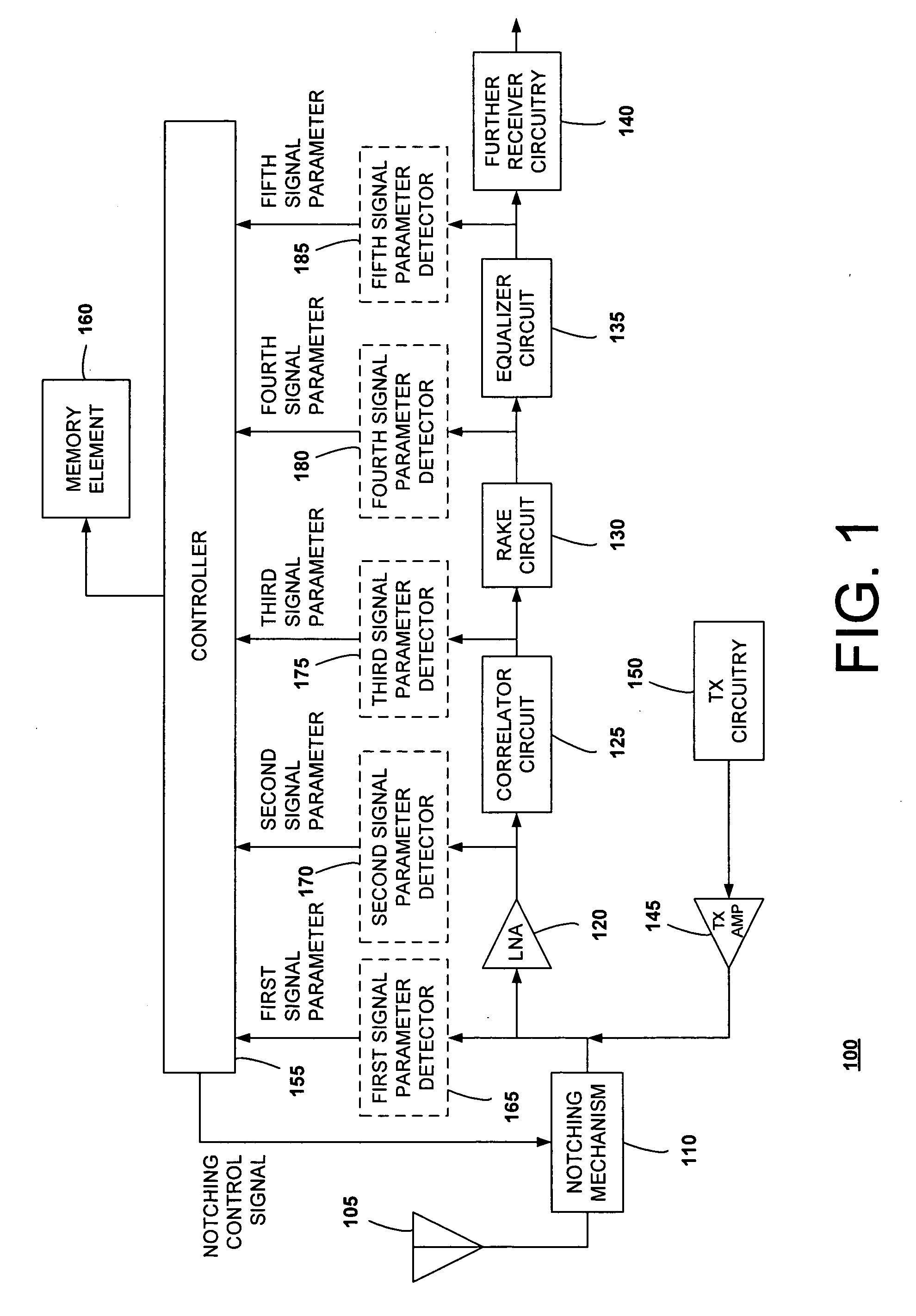

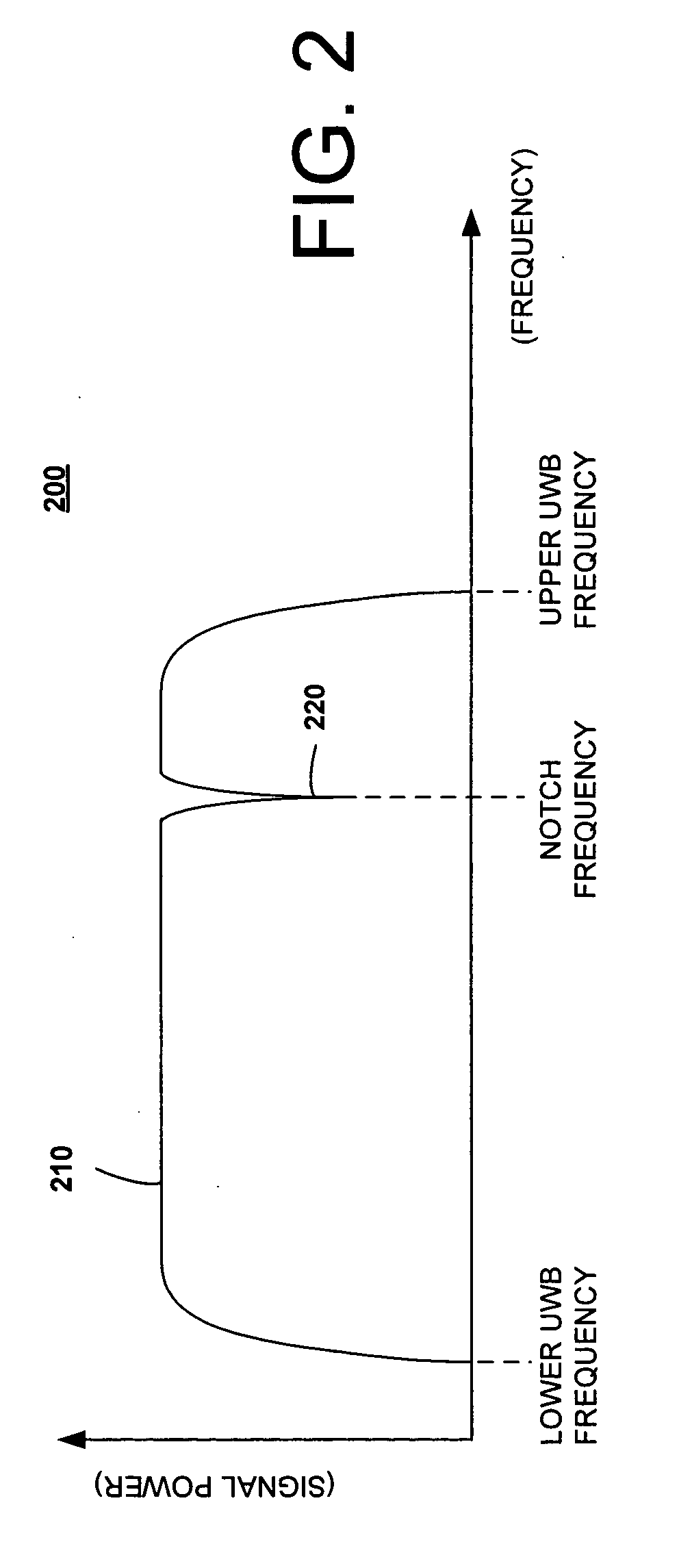

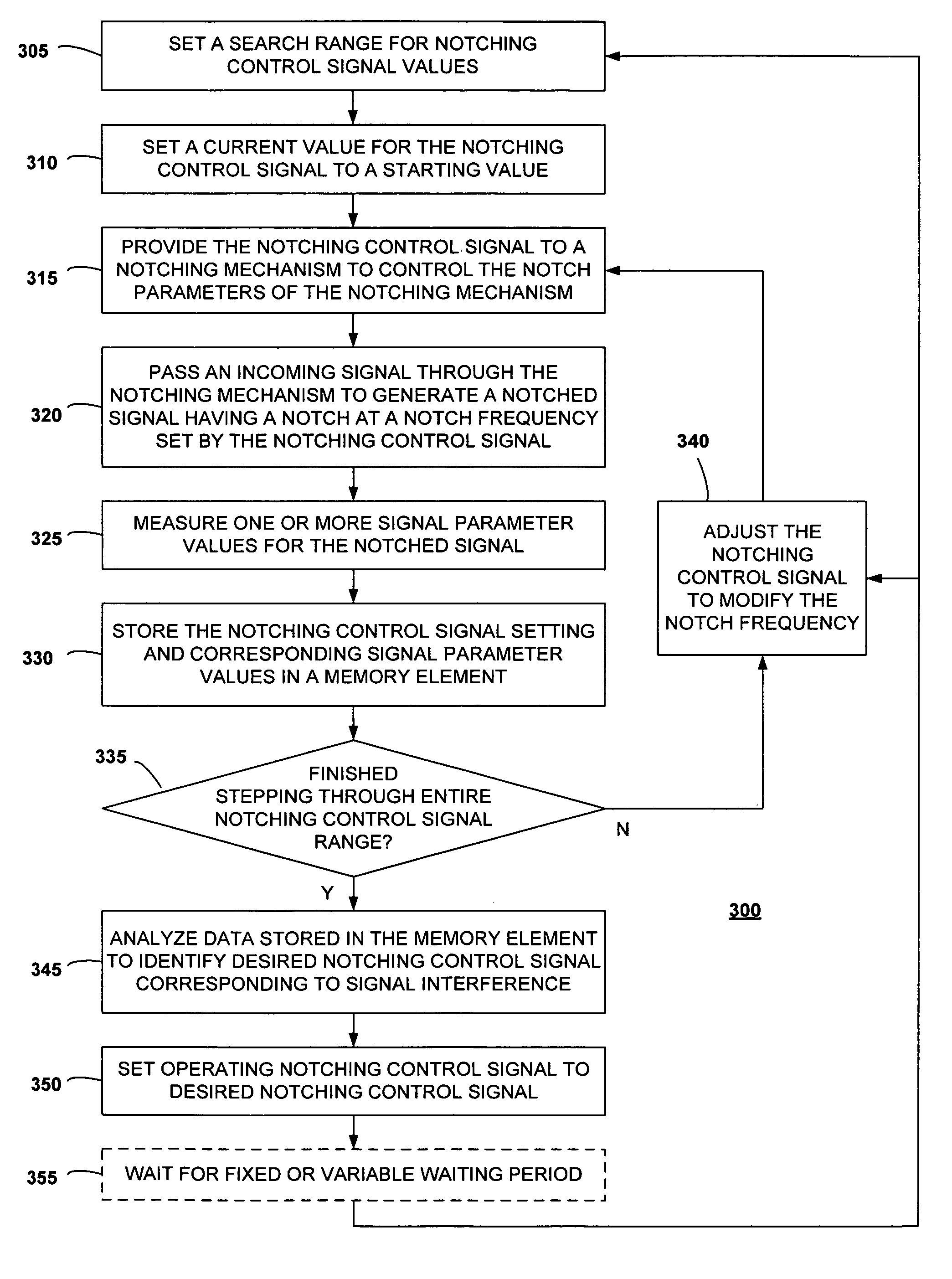

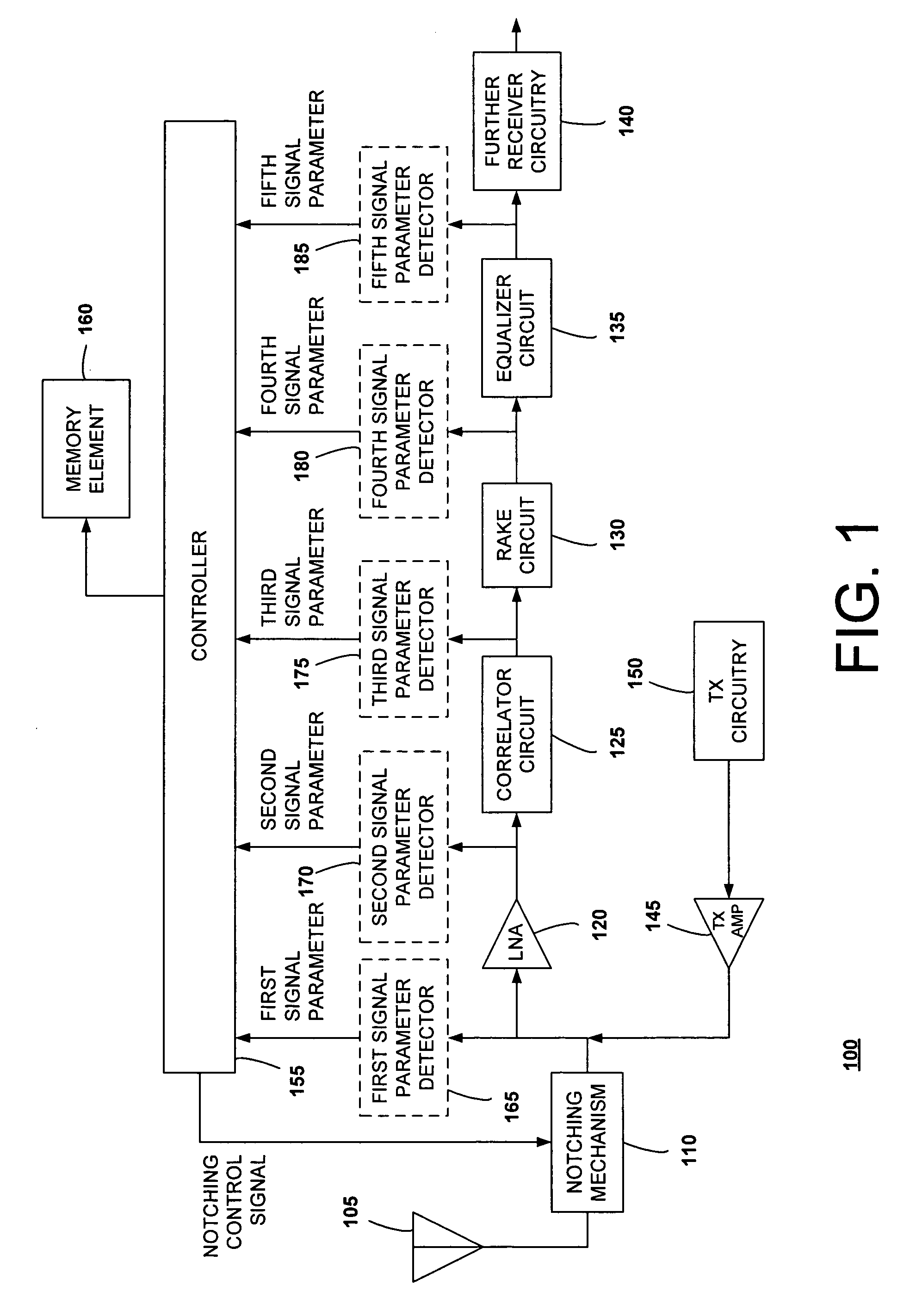

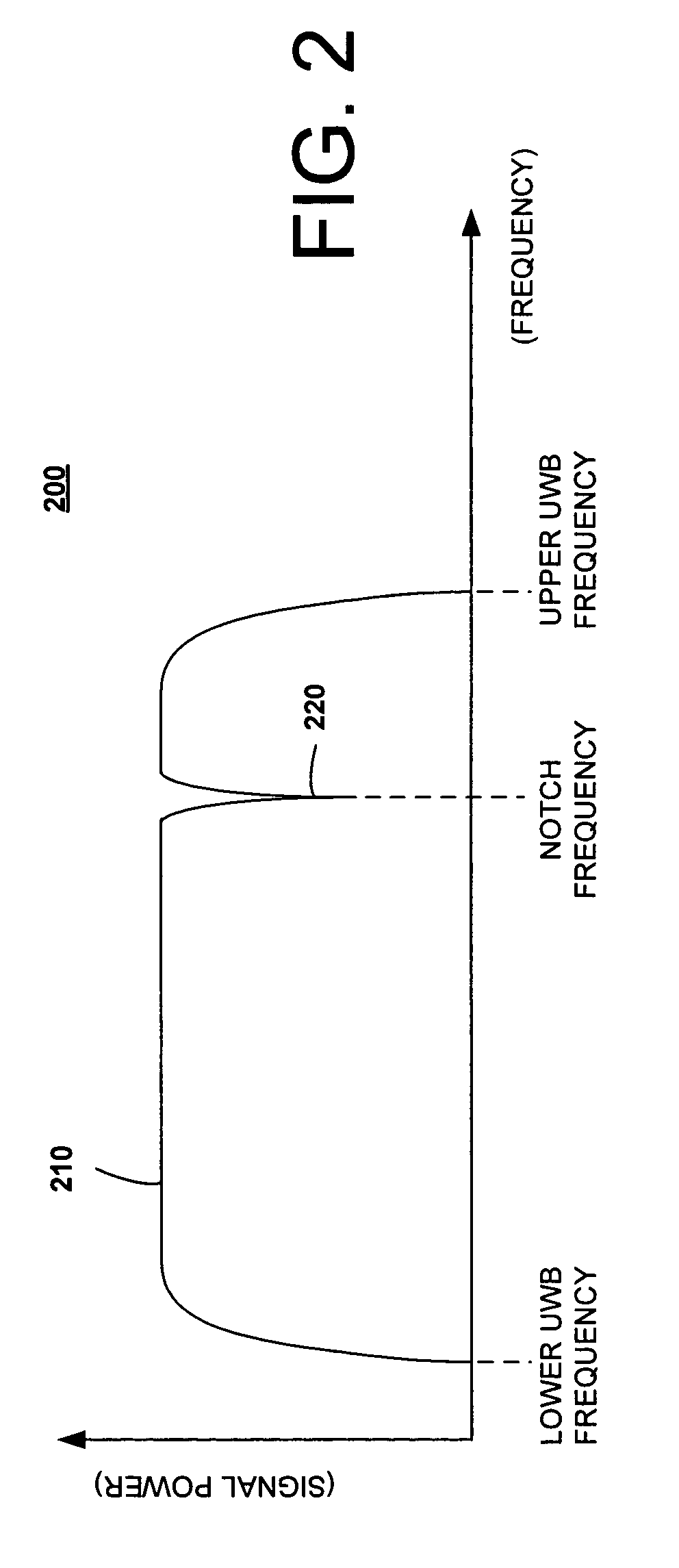

Method and system for controlling a notching mechanism

InactiveUS20070076782A1Improve appreciationInvention is limitedTransmission monitoringLine-transmission monitoring/testingControl signalEngineering

A circuit (100) is provided for notching an incoming wireless signal. The circuit comprises: a notching mechanism (110) for receiving an incoming signal and generating a notched signal having reduced power at the notch frequency (320), the notch frequency being adjustable in response to a notching control signal; a signal parameter detector (165, 170, 175, 180, 185) for detecting a signal parameter of the notched signal (325); a controller (155) for receiving the signal parameter and for generating the notching control signal (315), the controller being configured to vary the signal parameter within a notching control signal range (340); and a memory (160) for storing the signal parameter and the notching control signal received from the controller in a notching database (330). The controller is configured to analyze the notching database to determine an optimal notching control signal to achieve a desired level of signal performance (345).

Owner:NORTH STAR INNOVATIONS

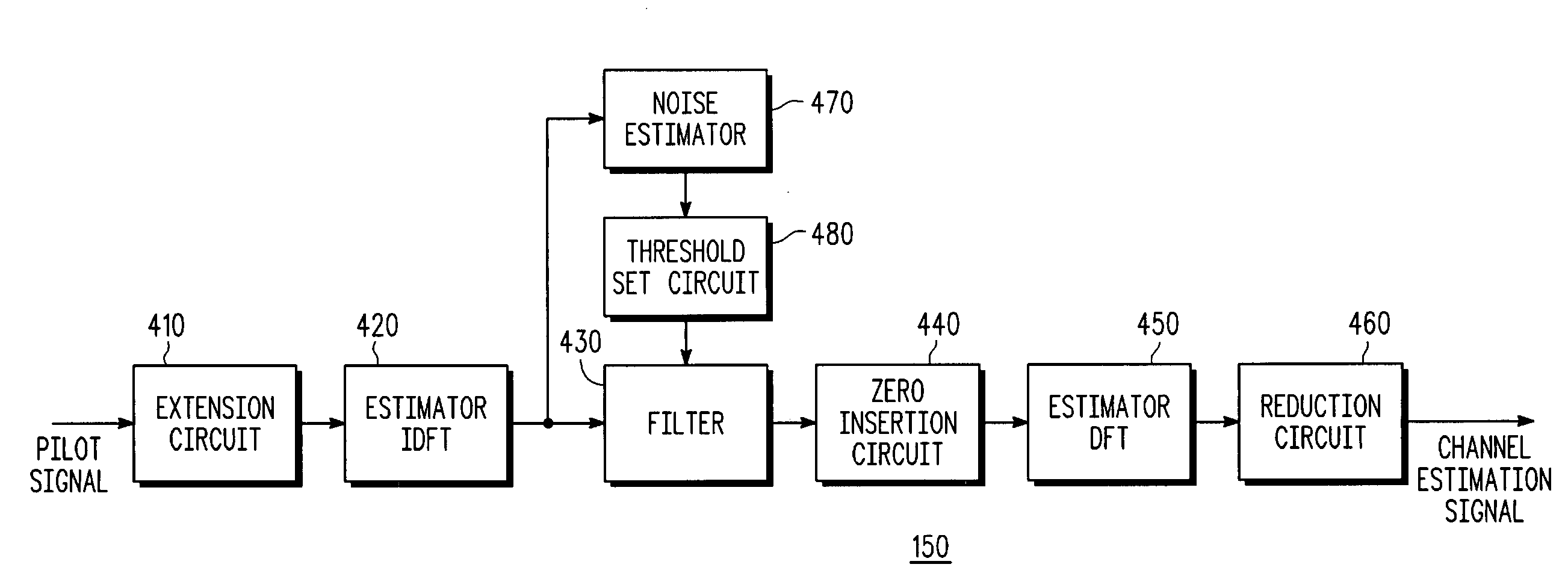

System and method for reducing edge effect

ActiveUS20080101483A1Improve appreciationInvention is limitedDiversity/multi-antenna systemsSecret communicationEdge effectsEngineering

A channel estimator (150) is provided that comprises: an extension circuit (410) configured to receive a pilot signal (510), and add front and back extension signals (620, 630) to a front and back of the pilot signal, respectively, creating a first signal (610), the front and back extension signals being extension of a first and last symbol, respectively, in the pilot signal; an IDFT circuit (420) configured to perform an IDFT function on the first signal, generating a second signal (710); a signal processing element (430, 440, 470, 480) configured to perform one or more operations on the second signal, generating a third signal (910); a DFT circuit (450) configured to perform a DFT function on the third signal, generating a fourth signal (1010); and a reduction circuit configured to cut off front and back ends of the fourth signal, generating a channel estimation signal (1110).

Owner:NXP USA INC

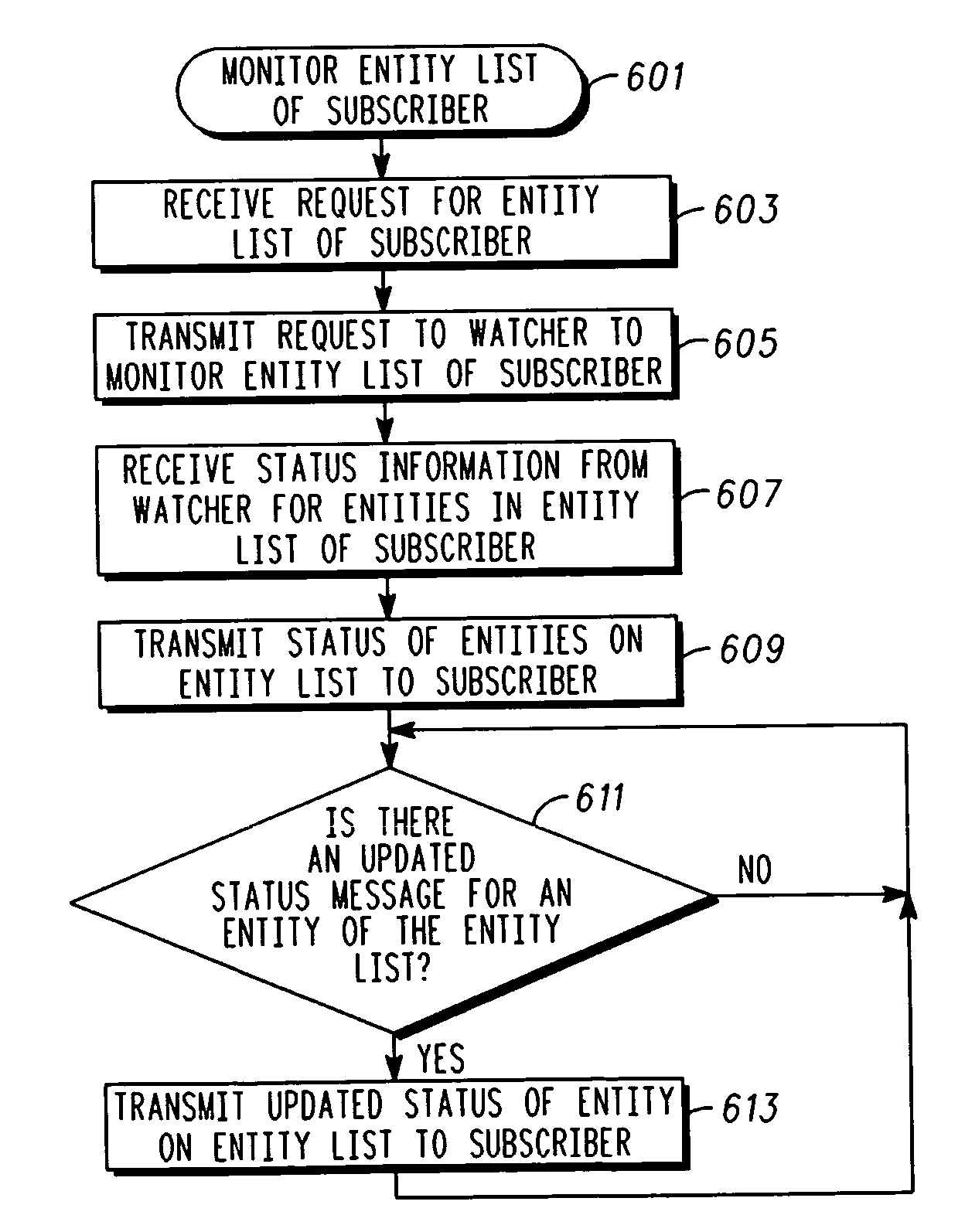

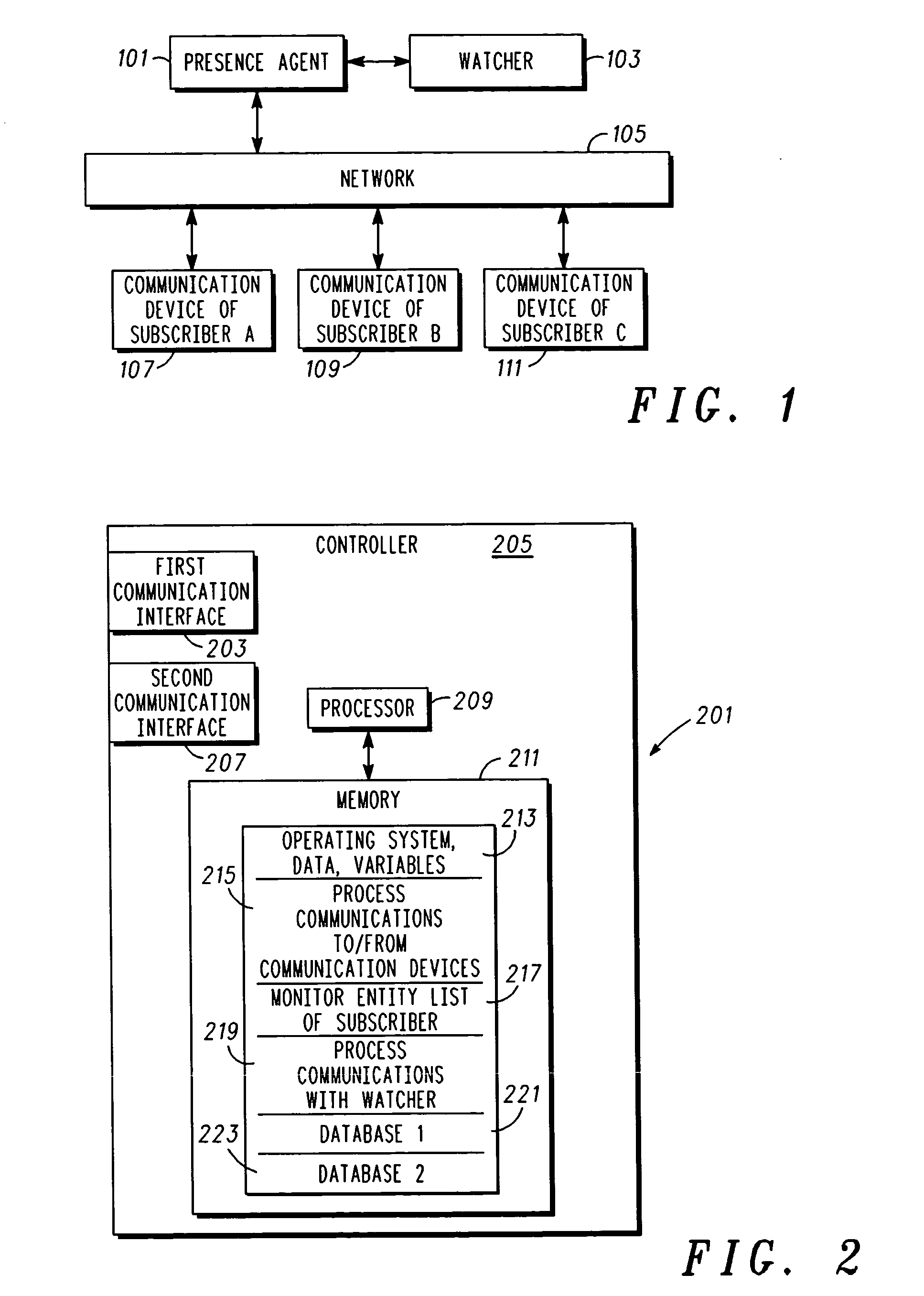

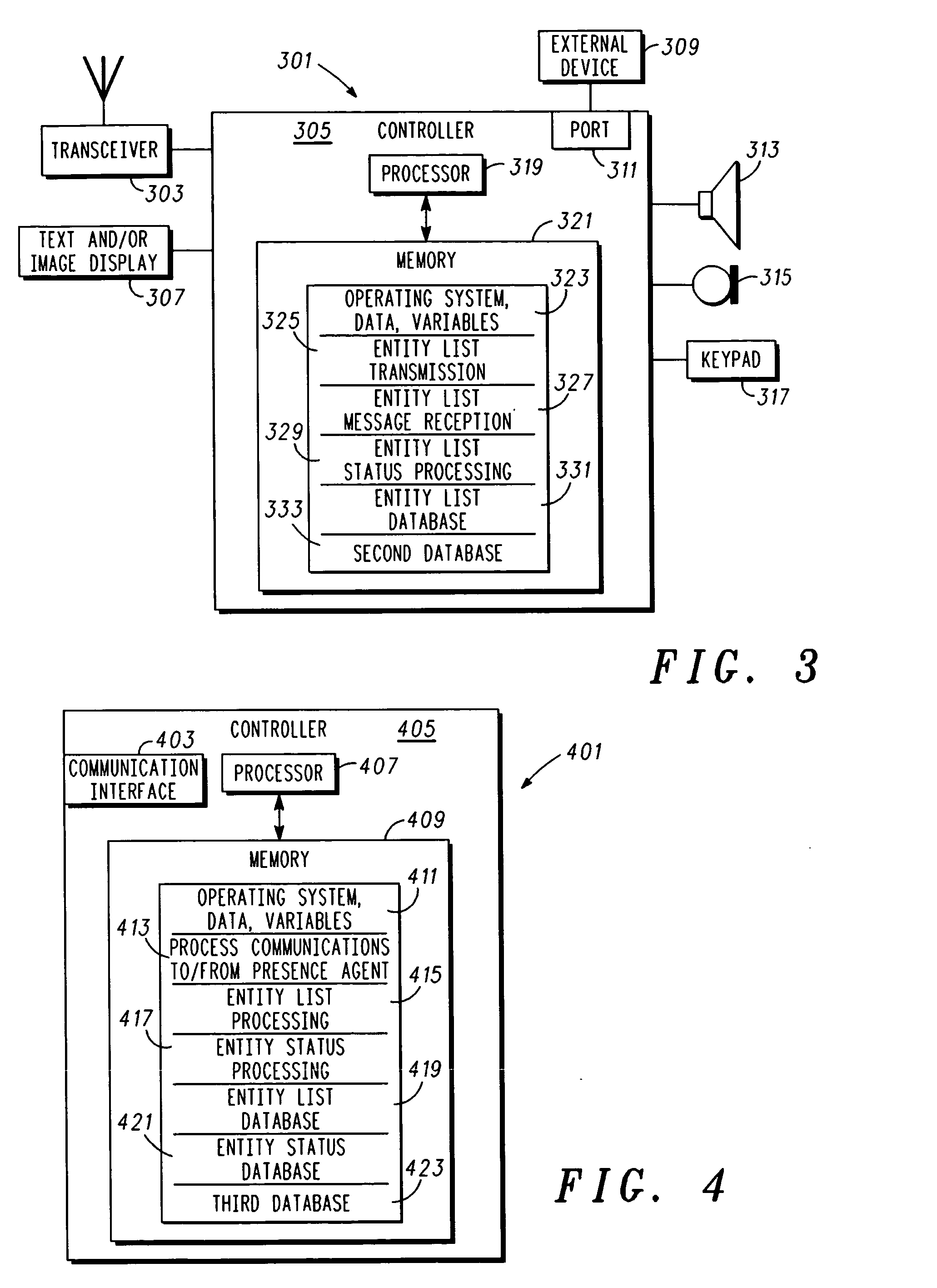

Method and system for providing entity status information in a communication network

InactiveUS20060129673A1Improve appreciationInvention is limitedMultiple digital computer combinationsTransmissionCommunication deviceReceipt

A presence agent (101) receives a message with a request for a status of one or more entities. The presence agent (101) determines the status of the entities, and transmits a message with the status of the entities. Transmitting the message includes initiating a connection to a communication device (107). A watcher (103) monitors the status of the entities, and provides updated information regarding the status to the users. The watcher (103) receives a request for a status of entities, determines the status of the entities, and transmits, in response to receipt of the request, a response indicating the status. A communication device (107) transmits a message having a request for status of entities. The communication device receives, from a connection initiated by a communication network (105), a message with a status of the entities, and processes the status of the entities, in response thereto.

Owner:GOOGLE TECH HLDG LLC

Method and system for control of capacity in a communication network

InactiveUS7414990B2Improve appreciationInvention is limitedError preventionFrequency-division multiplex detailsCurrent loadControl communications

A controller (103a, 103b) provides dynamic capacity, for use in connection with a communication network (101). A processor of the controller (103a, 103b) that can be utilized in the communication network can be configured to facilitate determining whether a current load level is below a predetermined low usage, and responsive thereto, adjusts a bearer configuration to allow higher throughput per user. Further, the processor (103a, 103b) can be configured to facilitate determining whether the current load level exceeds a predetermined high usage, and responsive thereto, adjusting the bearer configuration to allow lower throughput per user.

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

Inter-site call routing and roaming support

ActiveUS7539494B2Improve appreciationInvention is limitedInterconnection arrangementsError preventionPrivate IPCommunication unit

Owner:MOTOROLA SOLUTIONS INC

Method and system for scaling a multi-channel signal

InactiveUS20060120480A1Improve appreciationInvention is limitedPower managementSecret communicationCommunication unitComputer science

A communication unit is provided having a transmitter and a processor (103). The processor (103) receives information (105) representative of a configuration of physical channels (107). The processor (103) determines a scaling factor responsive to the information (105) and facilitates scaling a signal (109, 111) provided by a combination of the channels utilizing the scaling factor. The scaled signal (109, 111) is provided to the transmitter.

Owner:GOOGLE TECH HLDG LLC

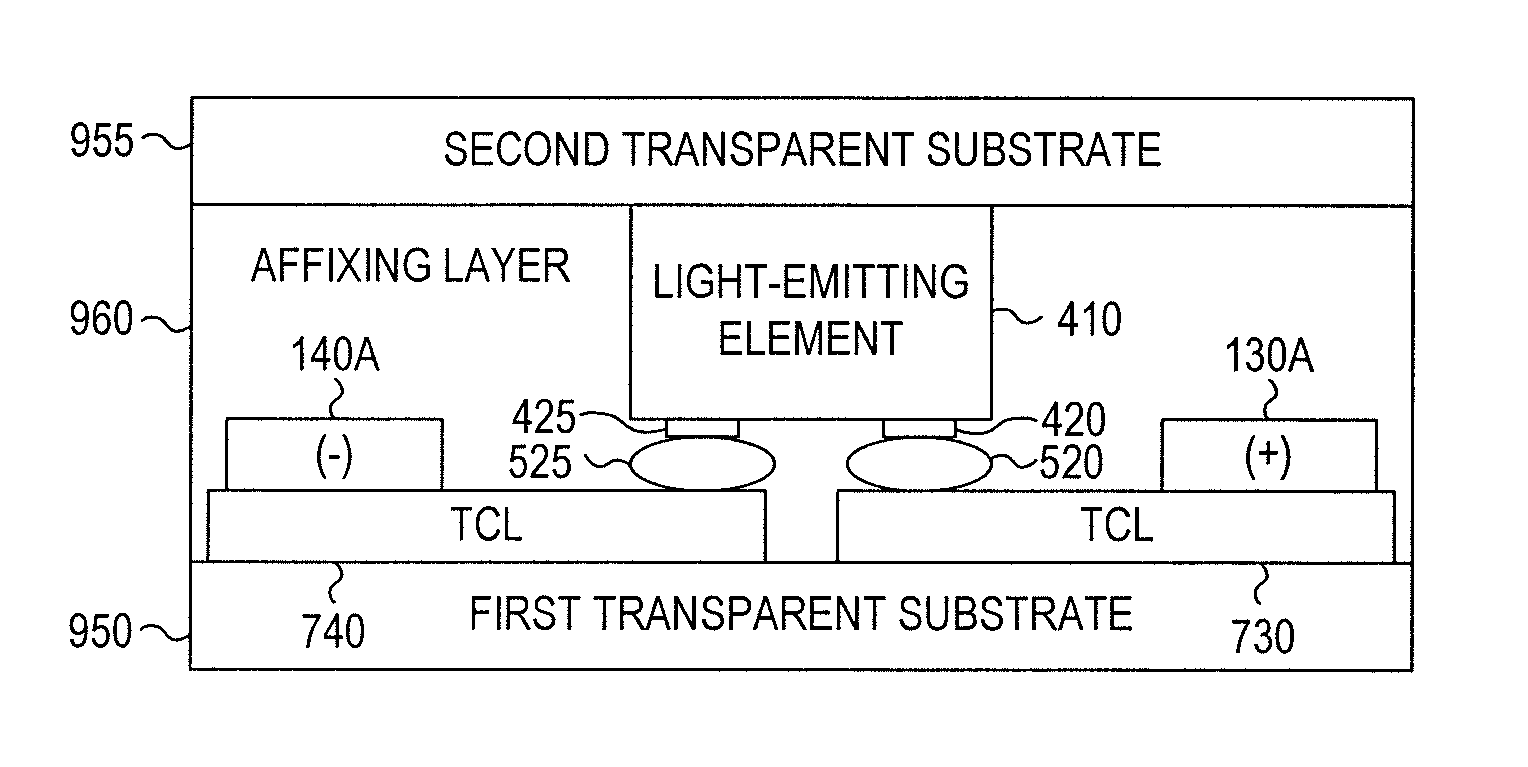

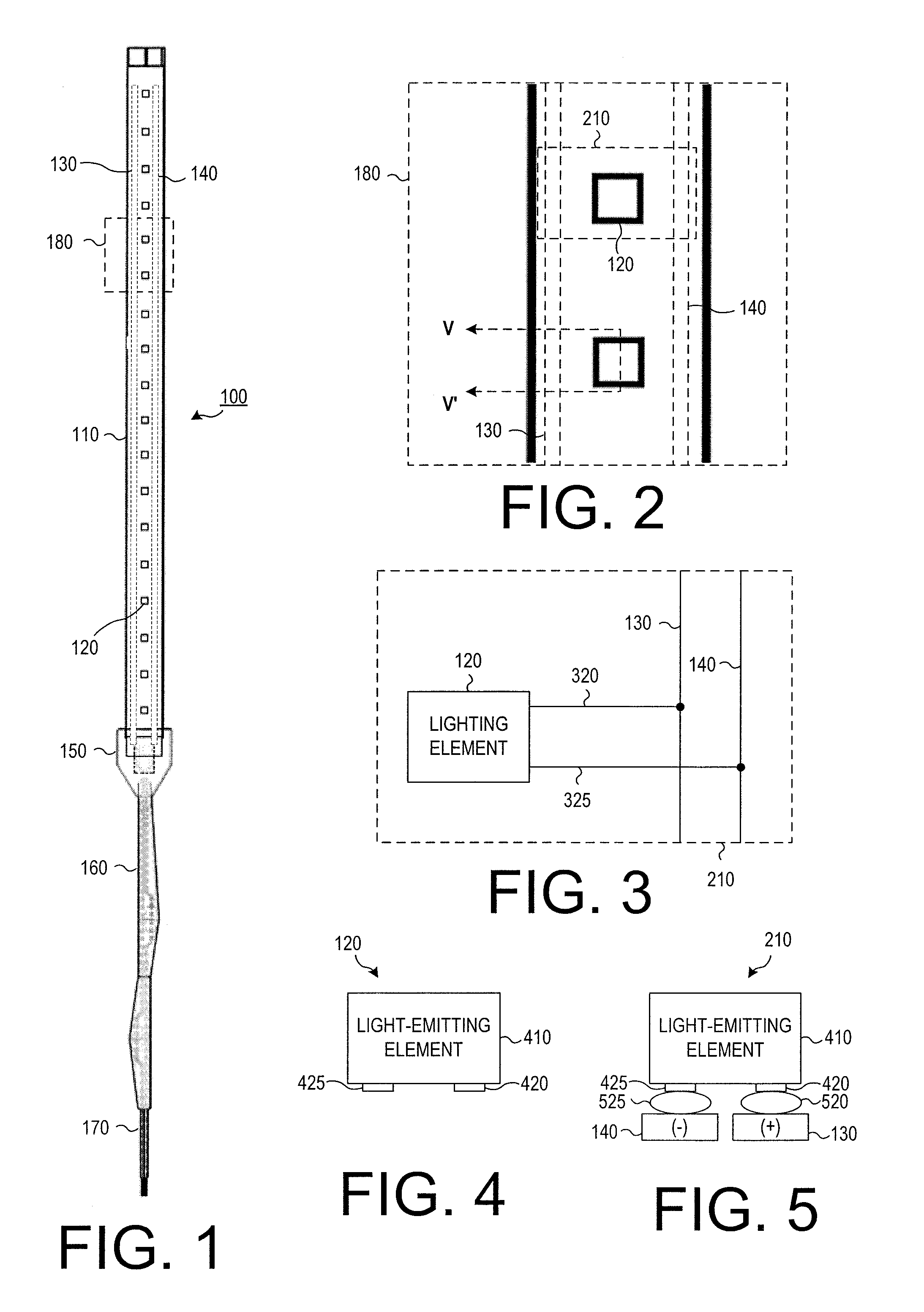

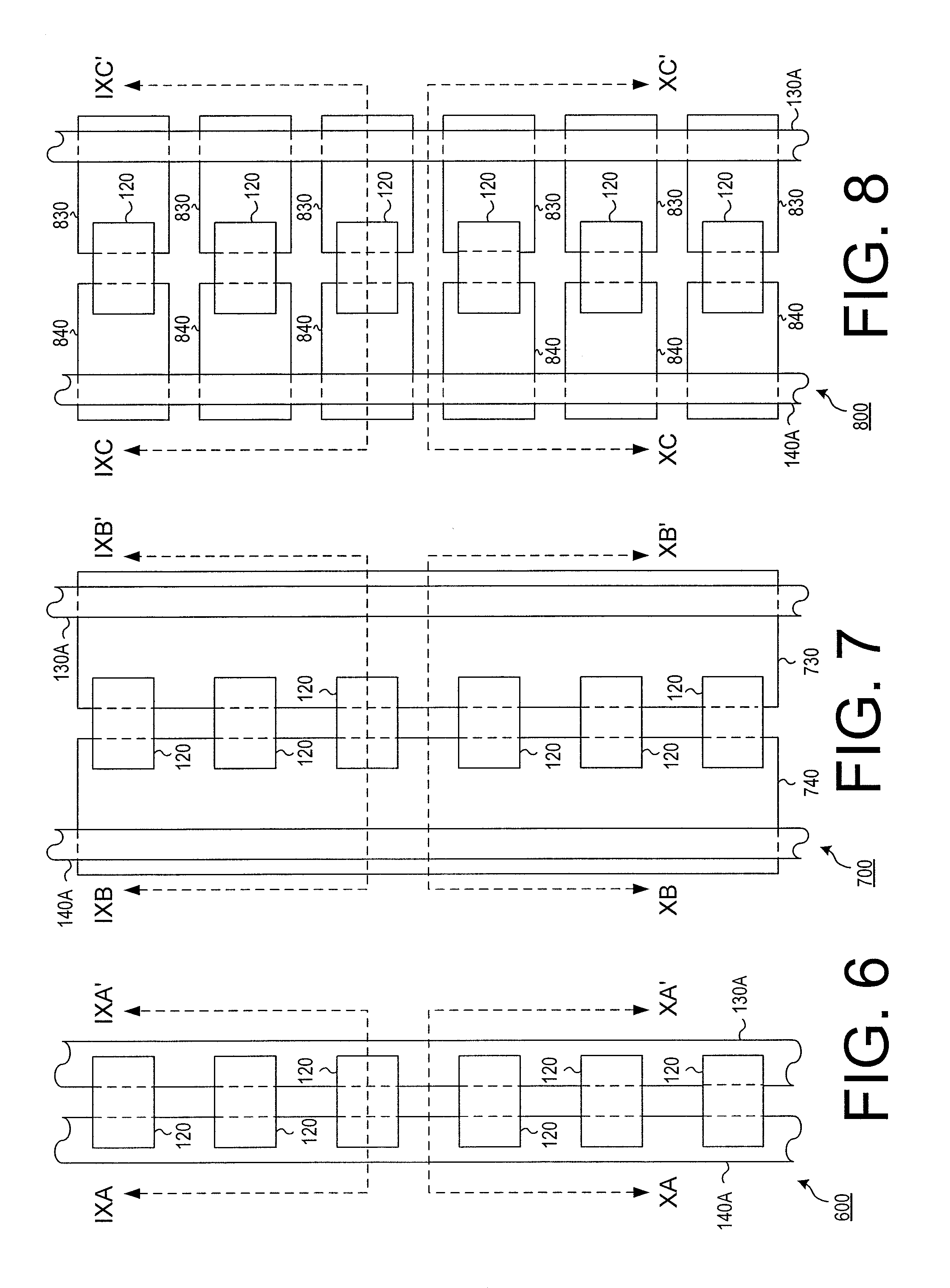

Flexible lighting device having unobtrusive conductive layers

ActiveUS9299899B2Improve appreciationInvention is limitedSolid-state devicesPrinted circuitsTransmittanceEffect light

Owner:GROTE IND

Method and system for controlling a notching mechanism

InactiveUS7502410B2Improve appreciationInvention is limitedTransmission monitoringLine-transmission monitoring/testingControl signalNotching

A circuit (100) is provided for notching an incoming wireless signal. The circuit comprises: a notching mechanism (110) for receiving an incoming signal and generating a notched signal having reduced power at the notch frequency (320), the notch frequency being adjustable in response to a notching control signal; a signal parameter detector (165, 170, 175, 180, 185) for detecting a signal parameter of the notched signal (325); a controller (155) for receiving the signal parameter and for generating the notching control signal (315), the controller being configured to vary the signal parameter within a notching control signal range (340); and a memory (160) for storing the signal parameter and the notching control signal received from the controller in a notching database (330). The controller is configured to analyze the notching database to determine an optimal notching control signal to achieve a desired level of signal performance (345).

Owner:NORTH STAR INNOVATIONS

Channel estimator with extended channel bandwidth

InactiveUS7573964B2Improve appreciationInvention is limitedChannel estimationTelecommunicationsPilot signal

Owner:MOTOROLA MOBILITY LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com