Patents

Literature

49results about How to "Reduce gate current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

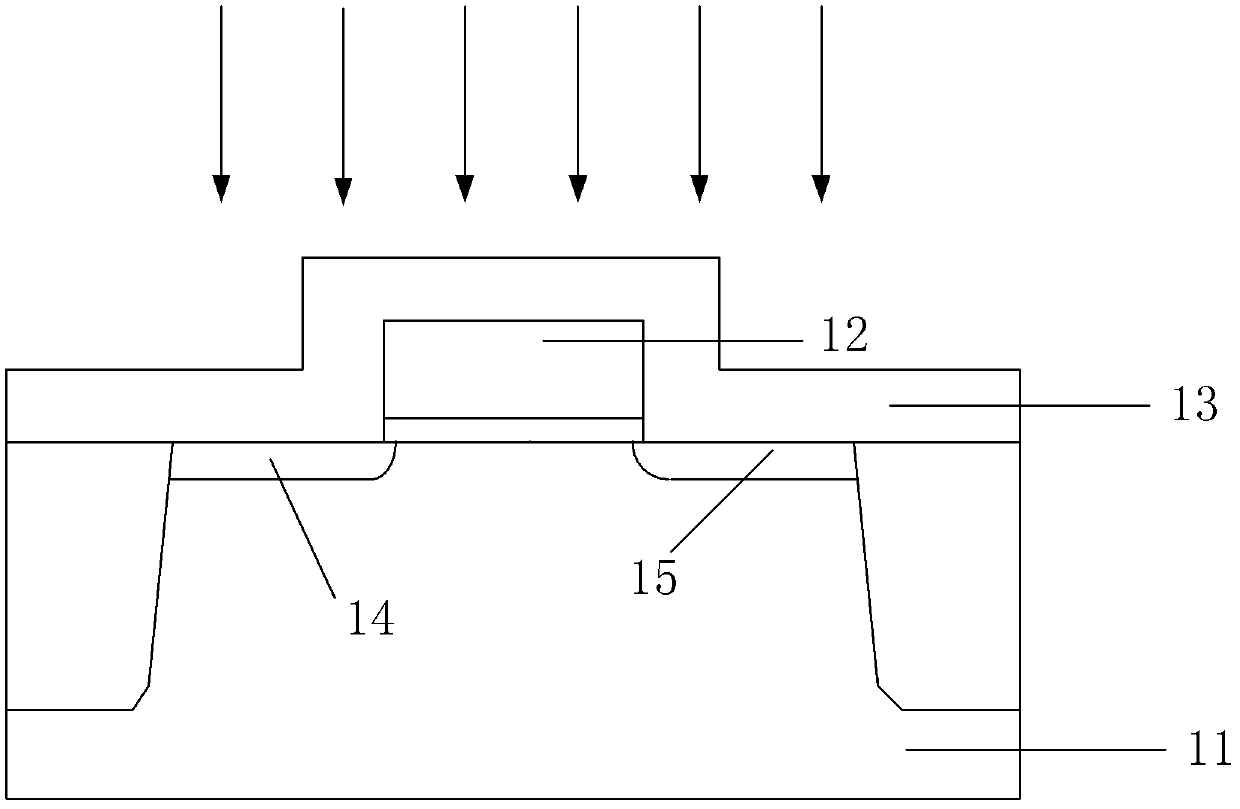

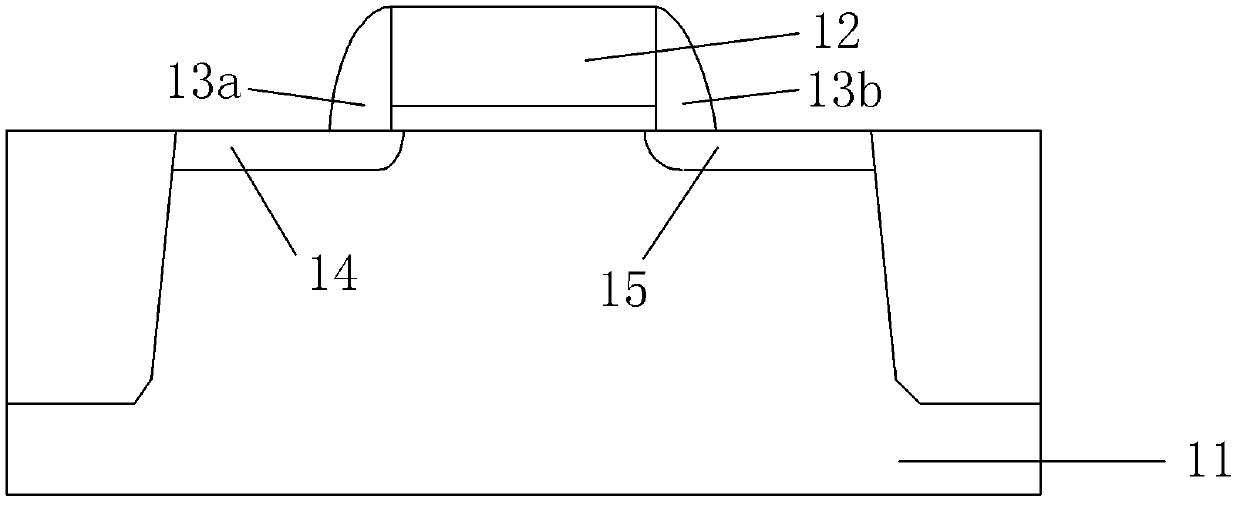

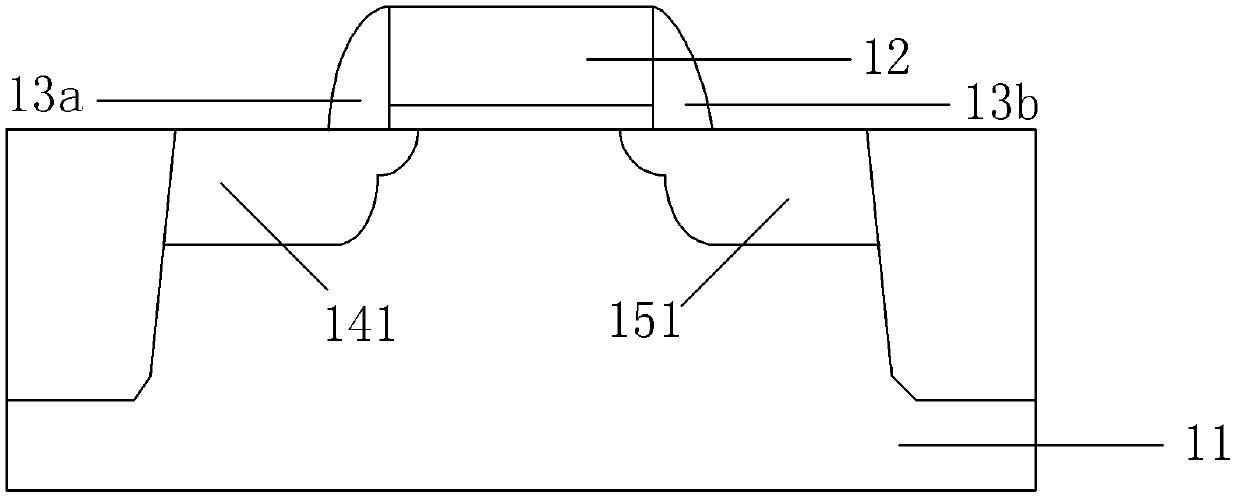

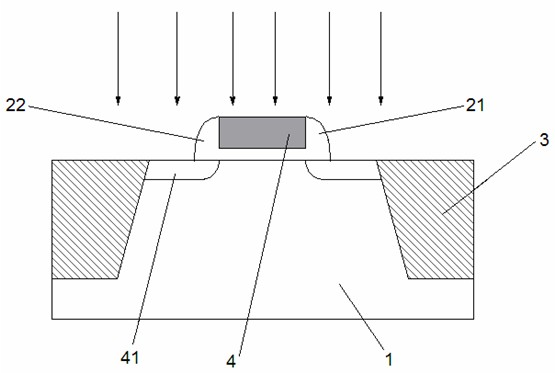

Side wall etching method for reducing heat current carrier injection damage

InactiveCN102610526ASmall section widthAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holeElectrical field strength

The invention discloses a side wall etching method for reducing heat current carrier injection damage. Ion injection is carried out on a side wall deposition layer by using neutral ions, and the ion injection direction forms an included angle with the direction vertical to a substrate and is inclined towards the source electrode direction, so the etching speed on the side wall above a source electrode region is higher than the etching speed on the side wall above a drain electrode region in the side wall etching process, after etching, the cross section width of the side wall of a source electrode is relatively reduced, and the cross section width of the side wall of a drain electrode is relatively increased. After voltage is applied on a grid electrode, the intensity of a longitudinal electric field generated at the drain terminal is weakened, so electron hole pairs are generated through the collision of current carriers accelerated by a transverse electric field, and the injection into the grid electrode can be realized by holes under the effect of the weak longitudinal electric field, so the grid current formed because of the hot current carrier injection is reduced, and the hot current carrier injection damage of a semiconductor device is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

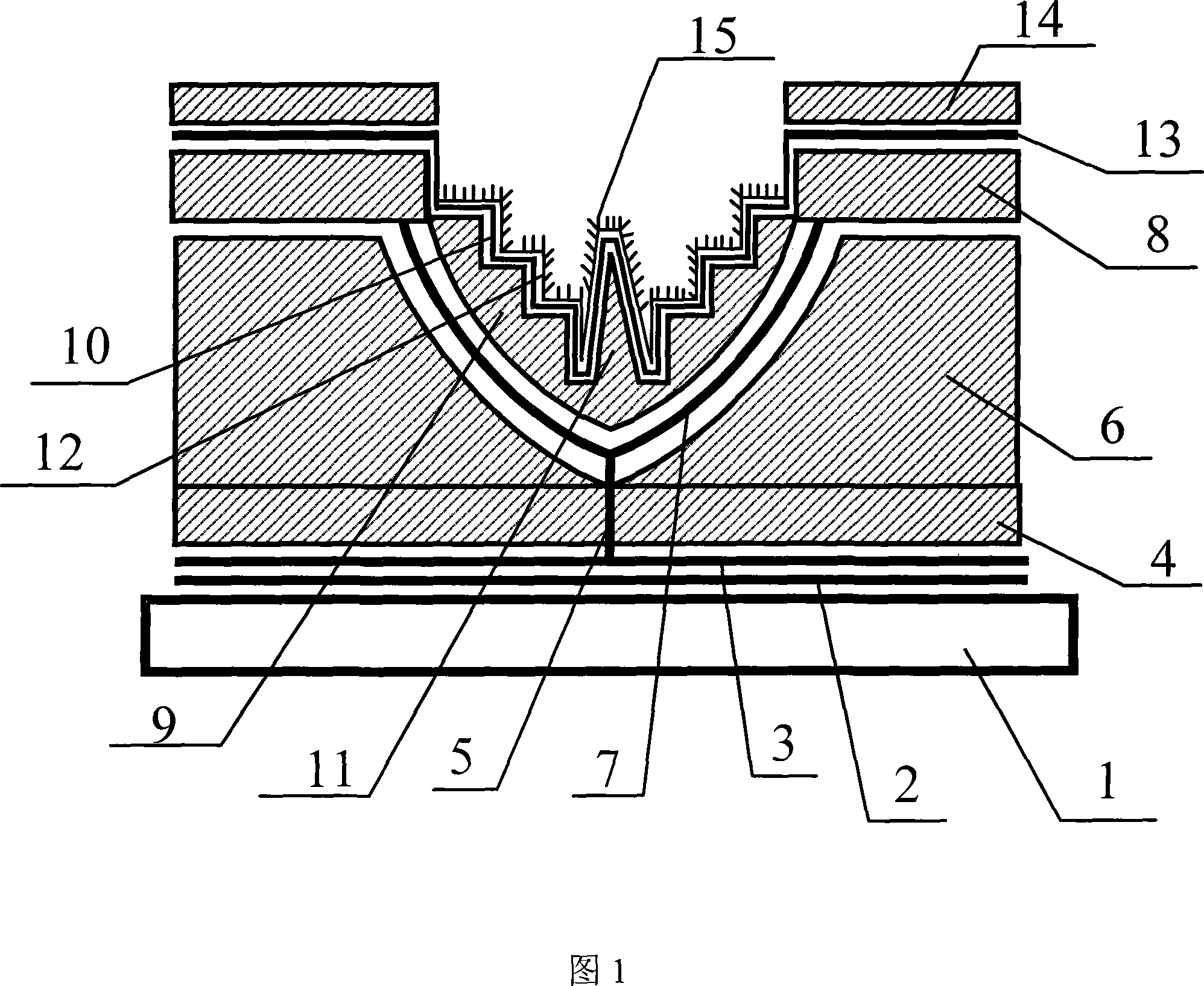

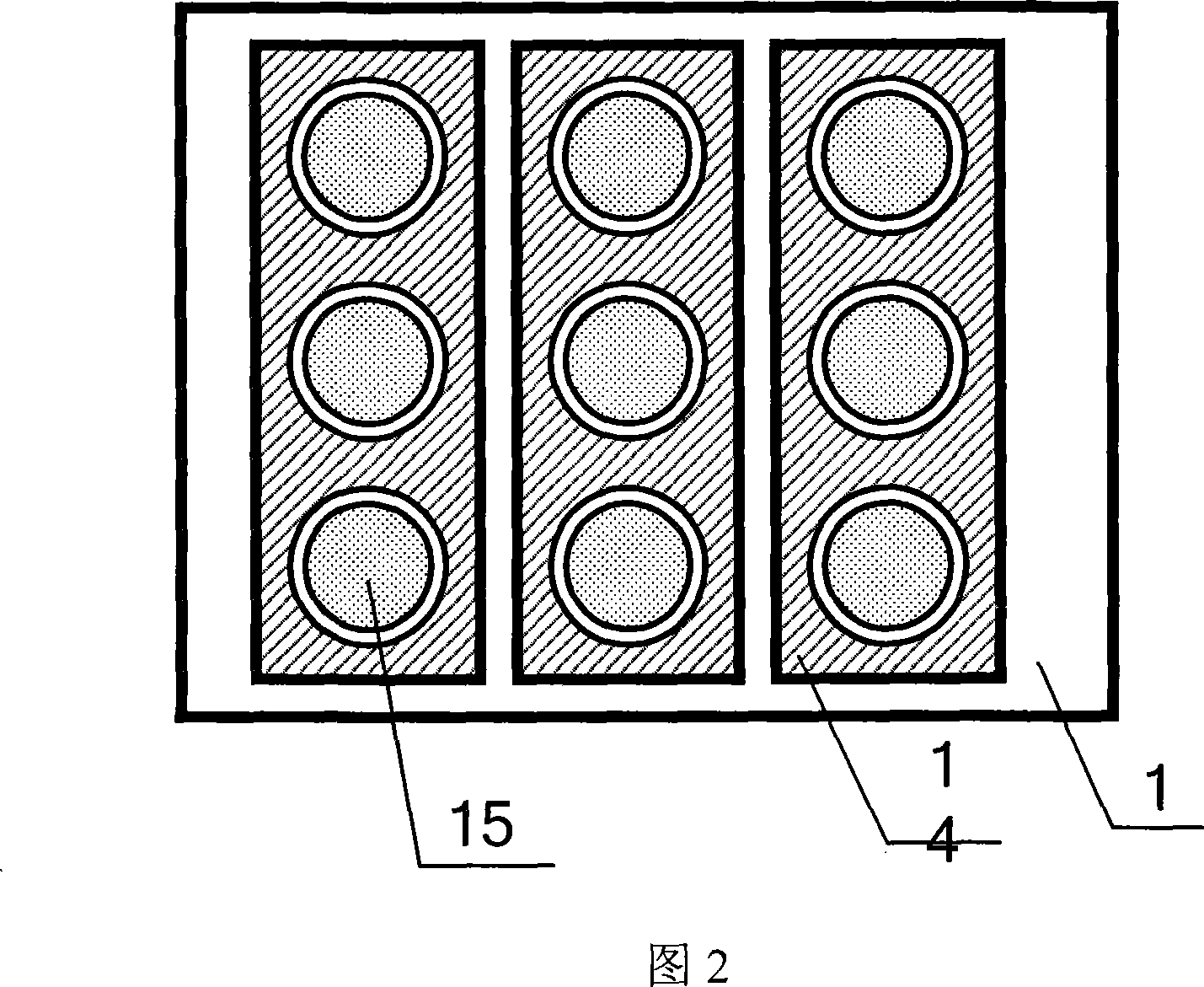

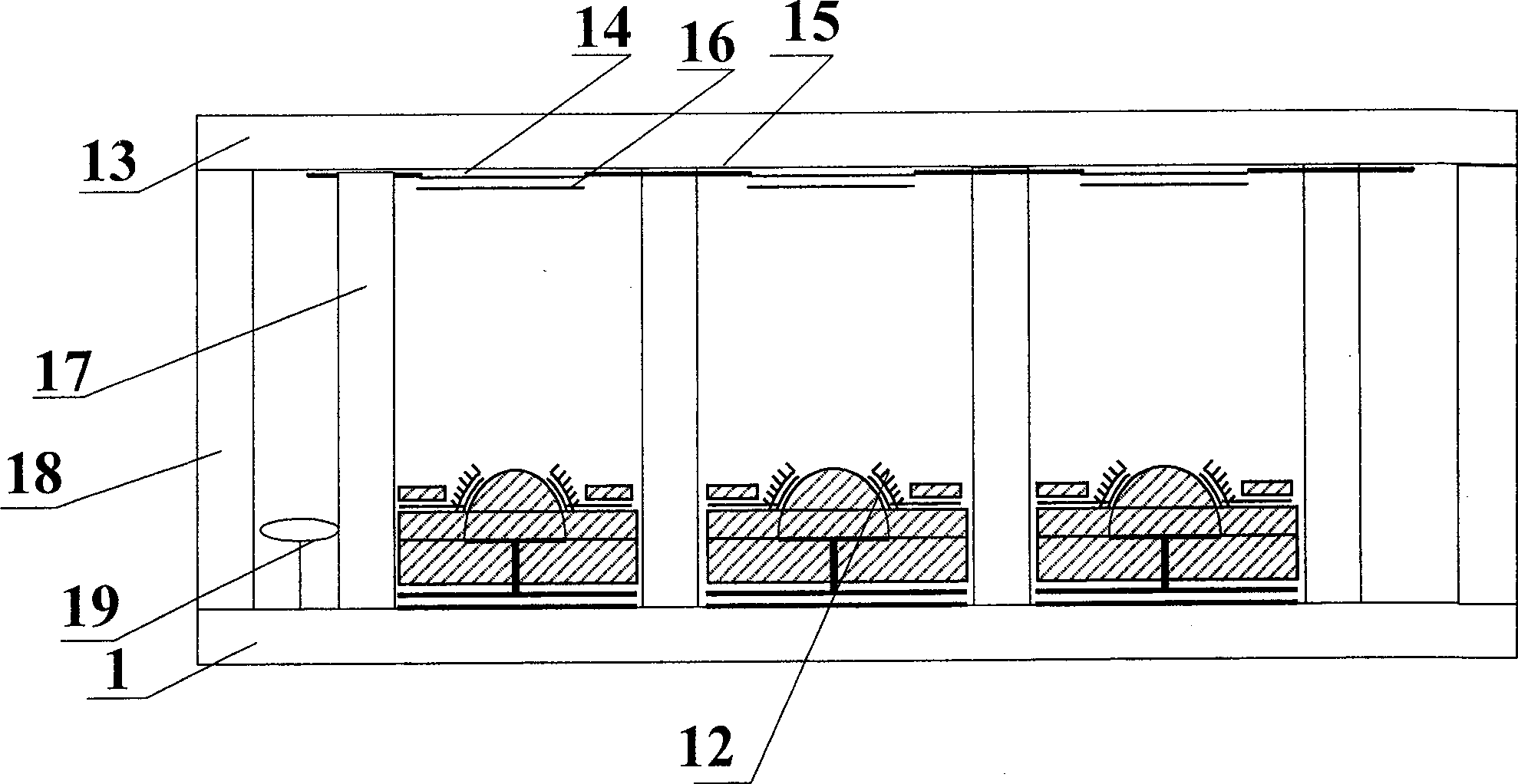

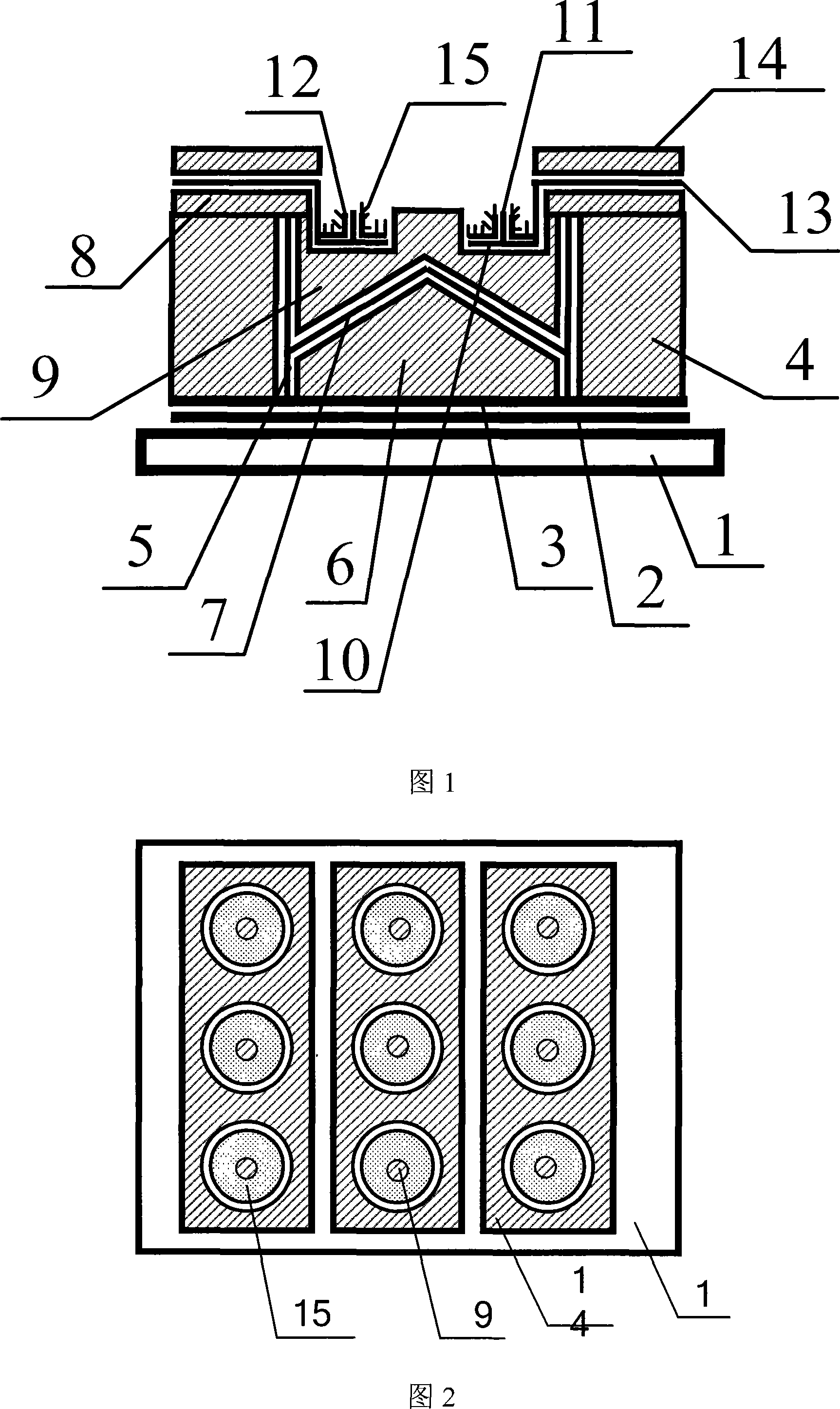

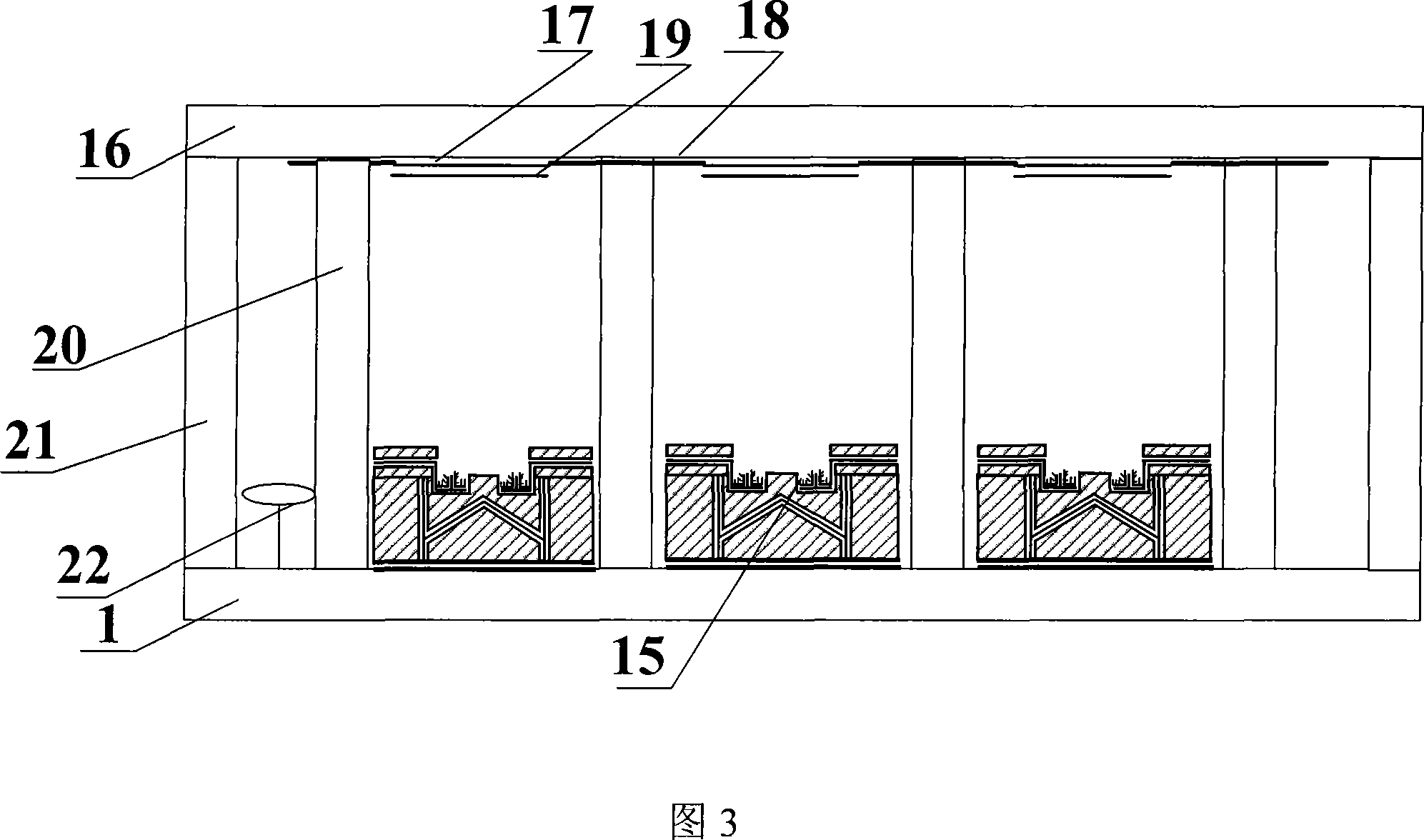

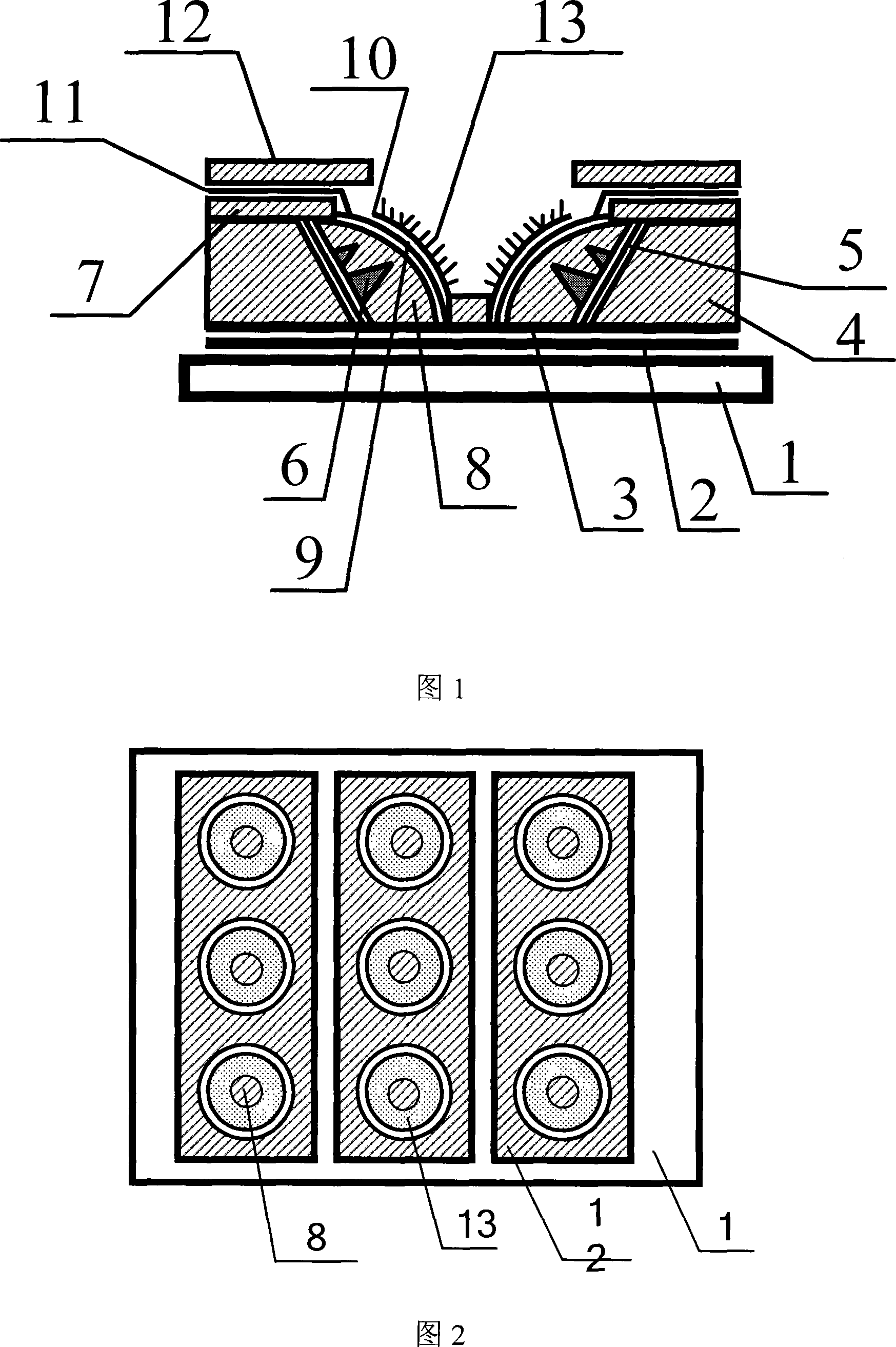

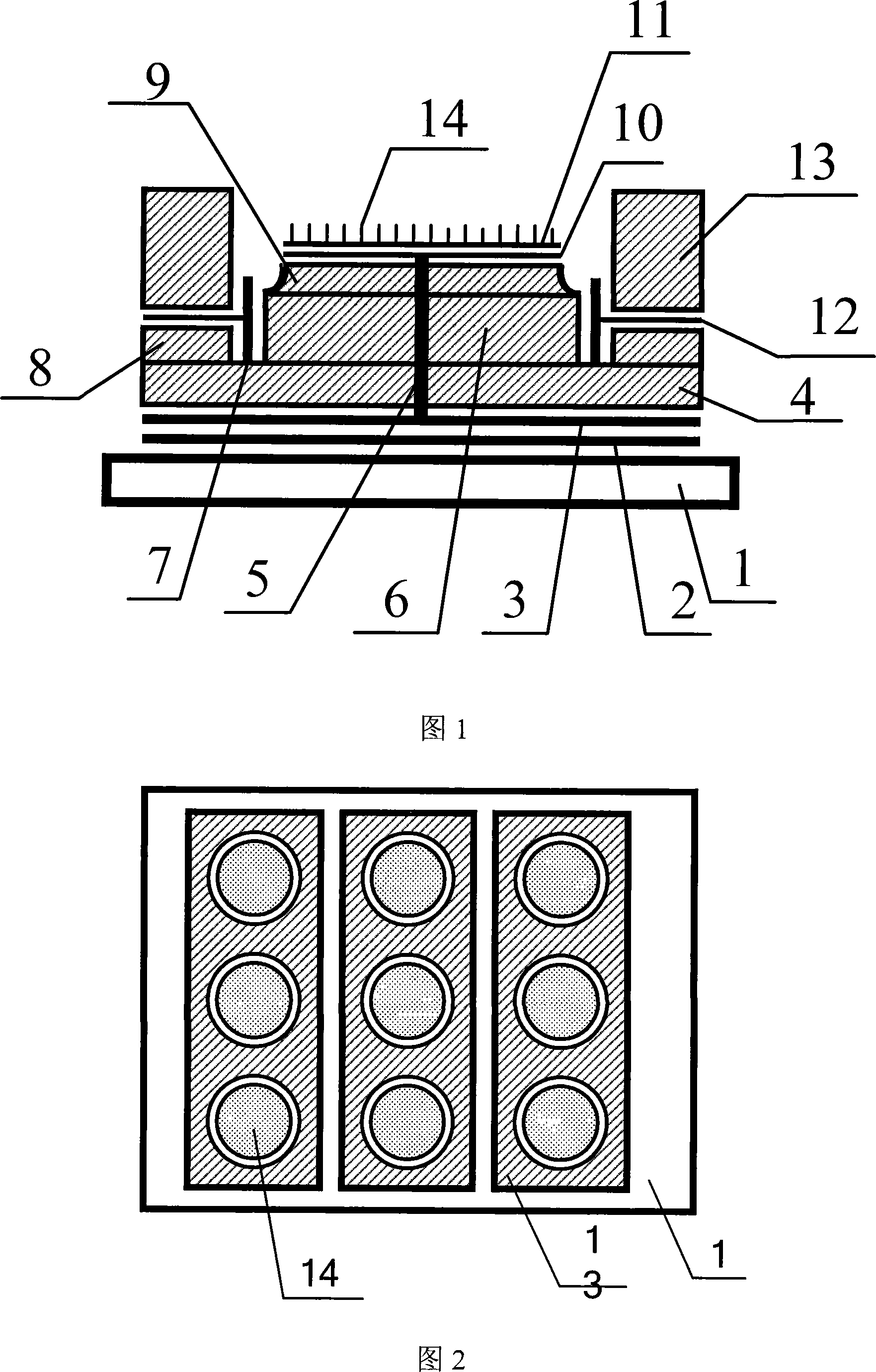

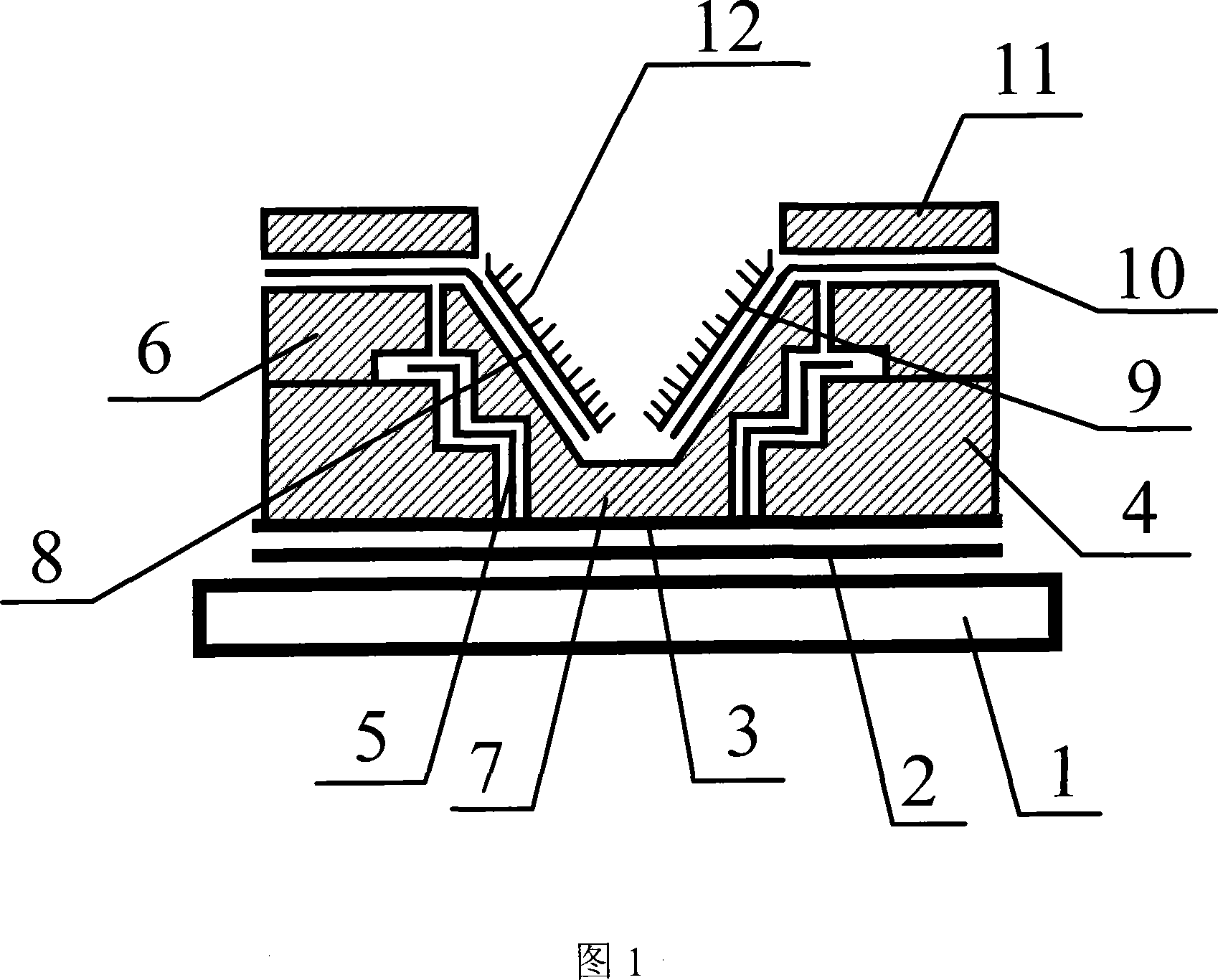

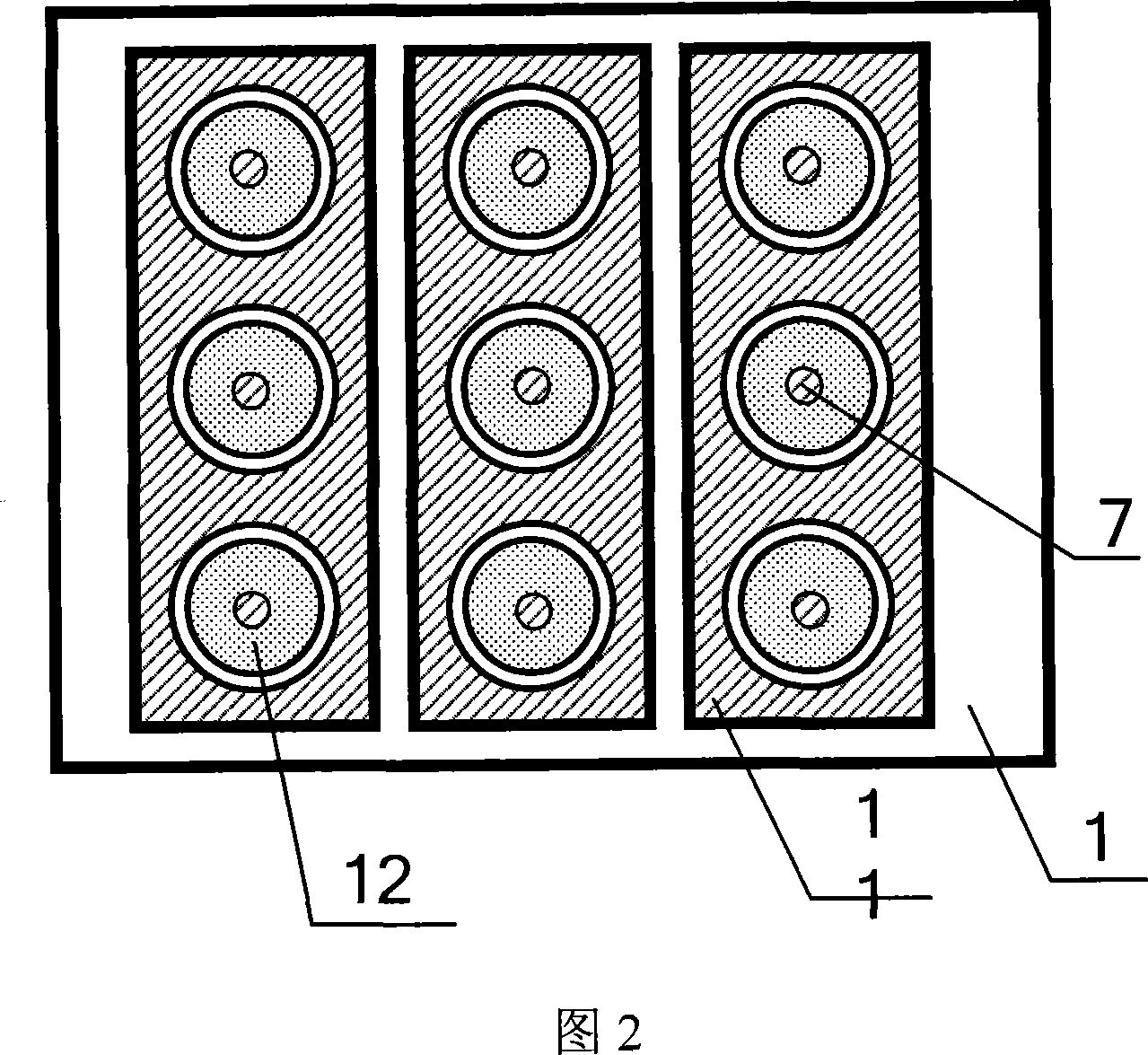

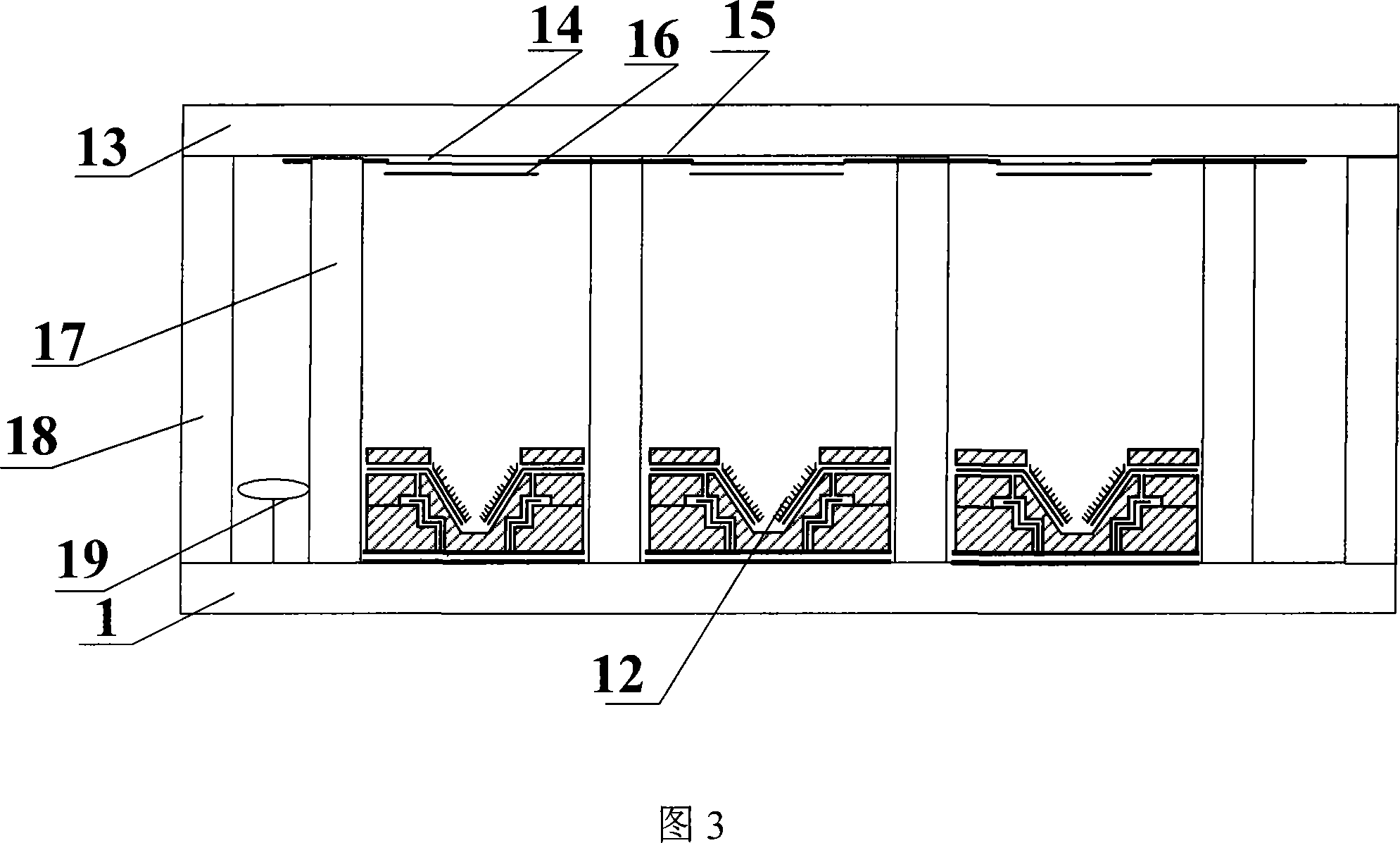

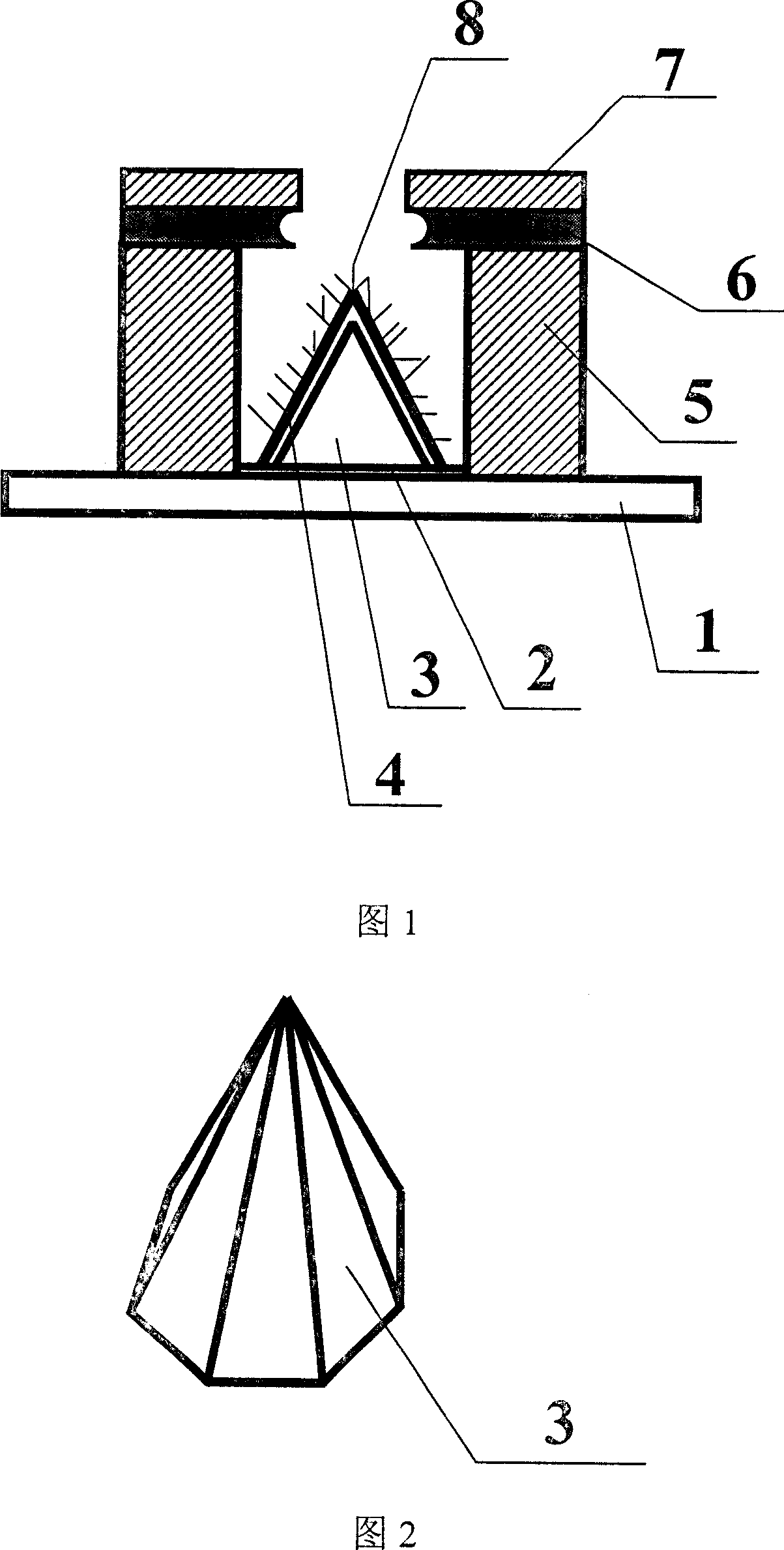

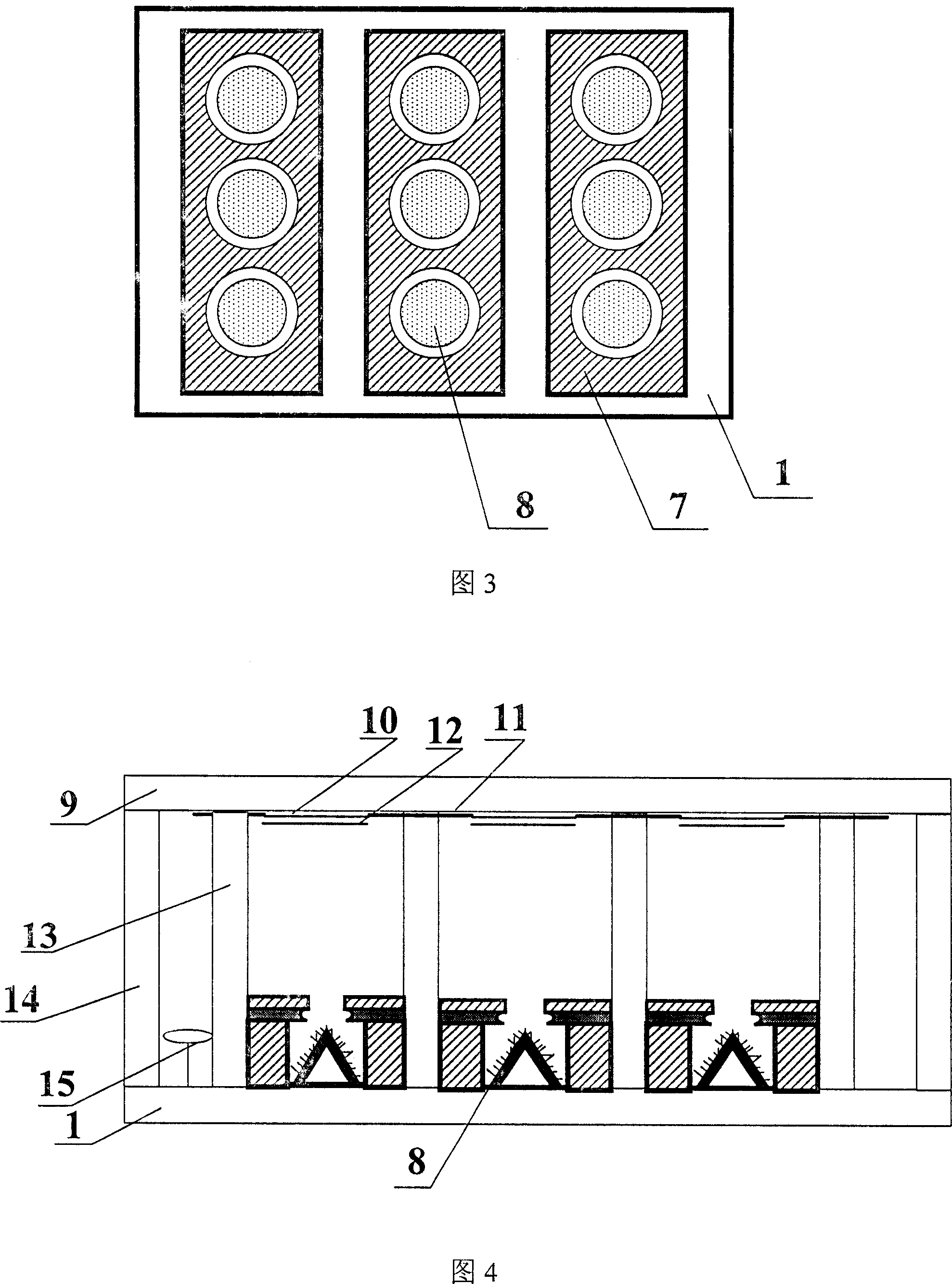

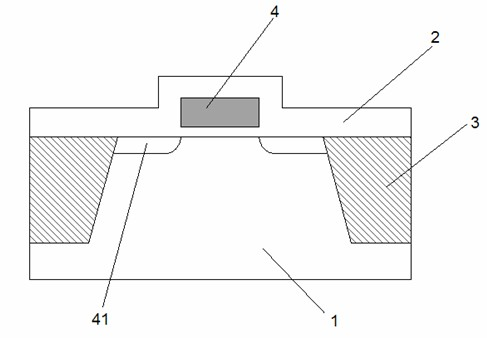

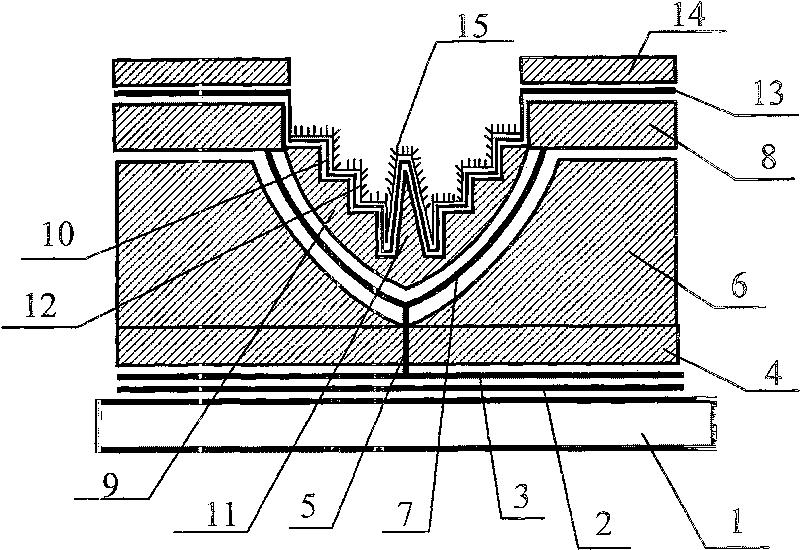

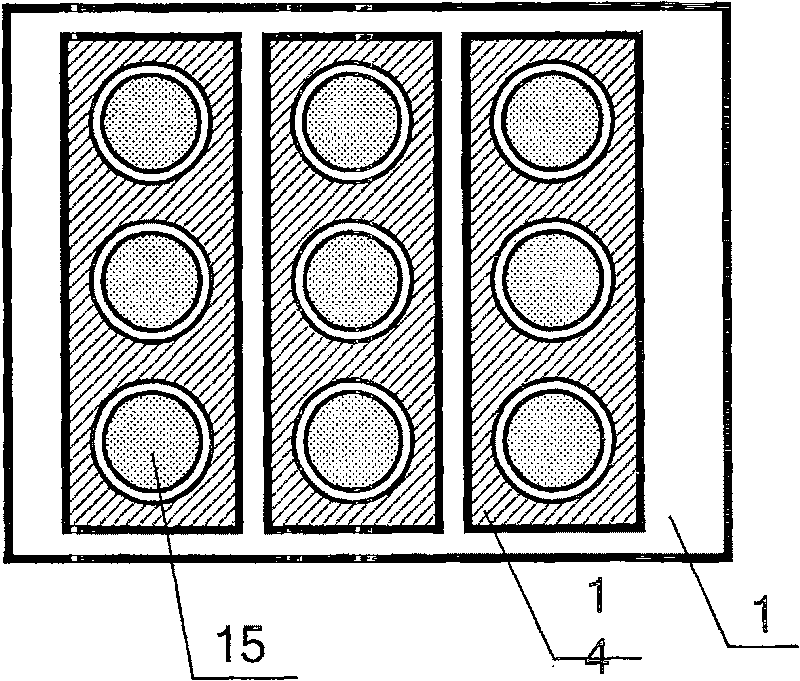

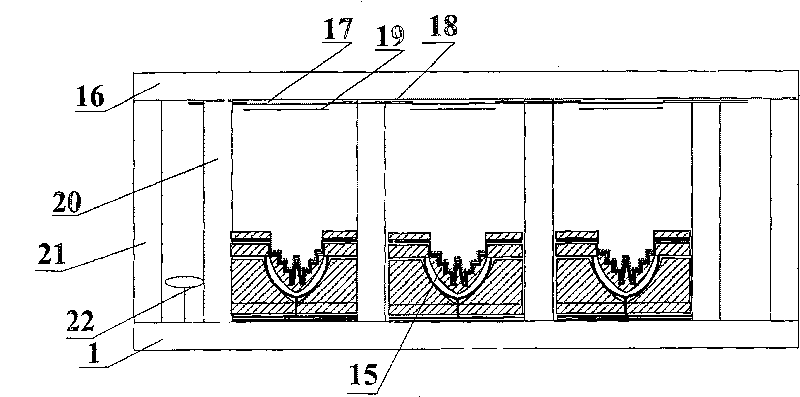

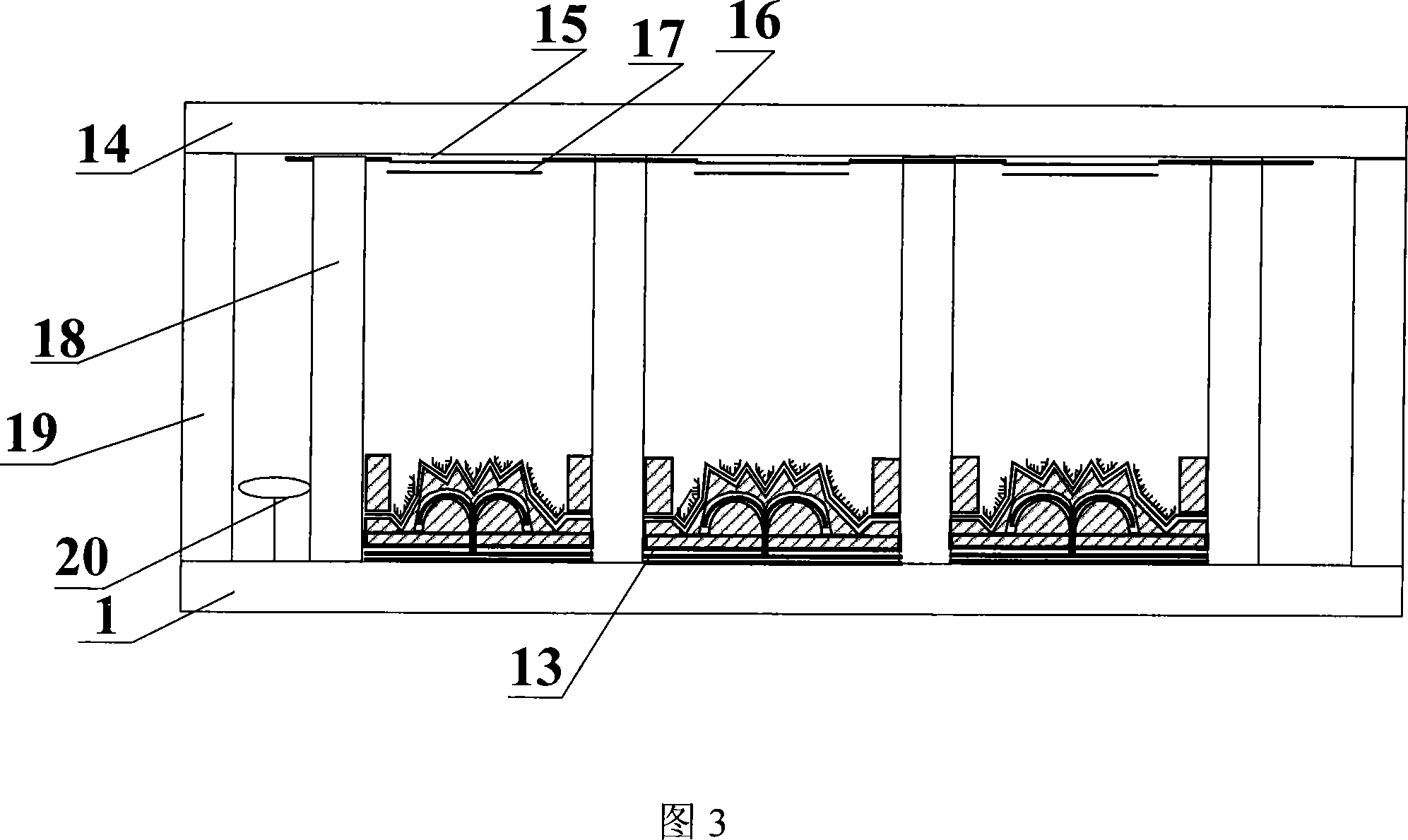

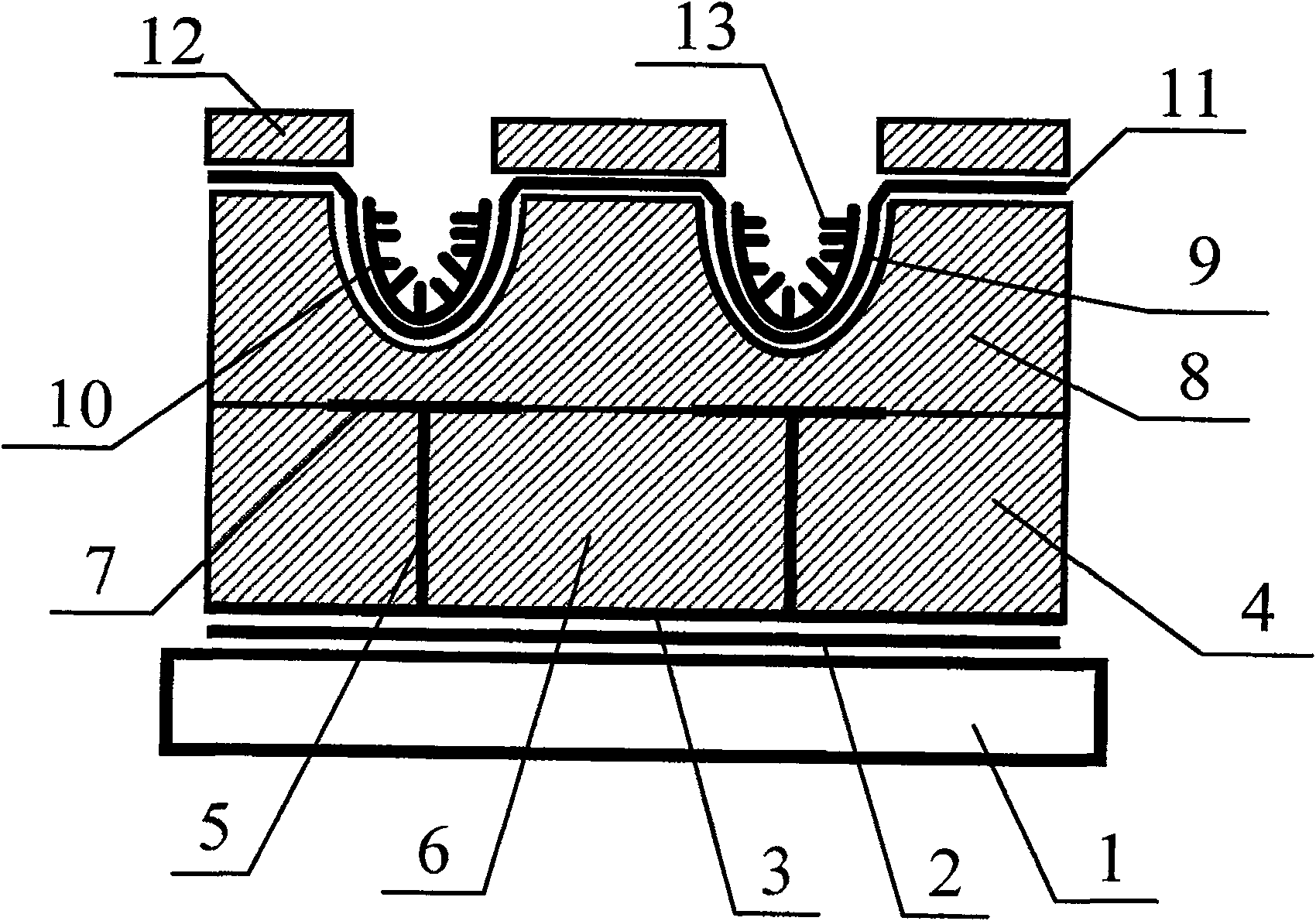

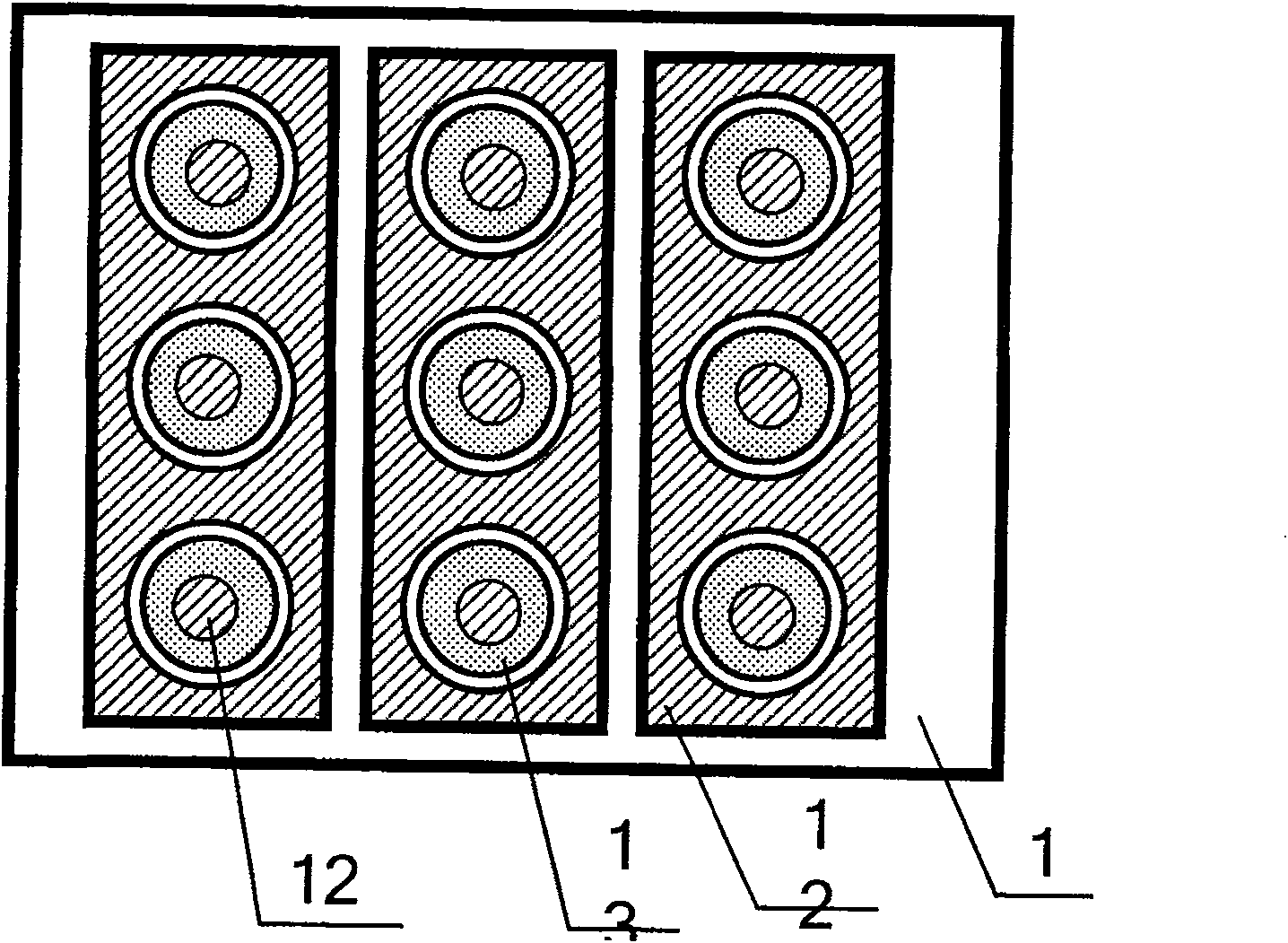

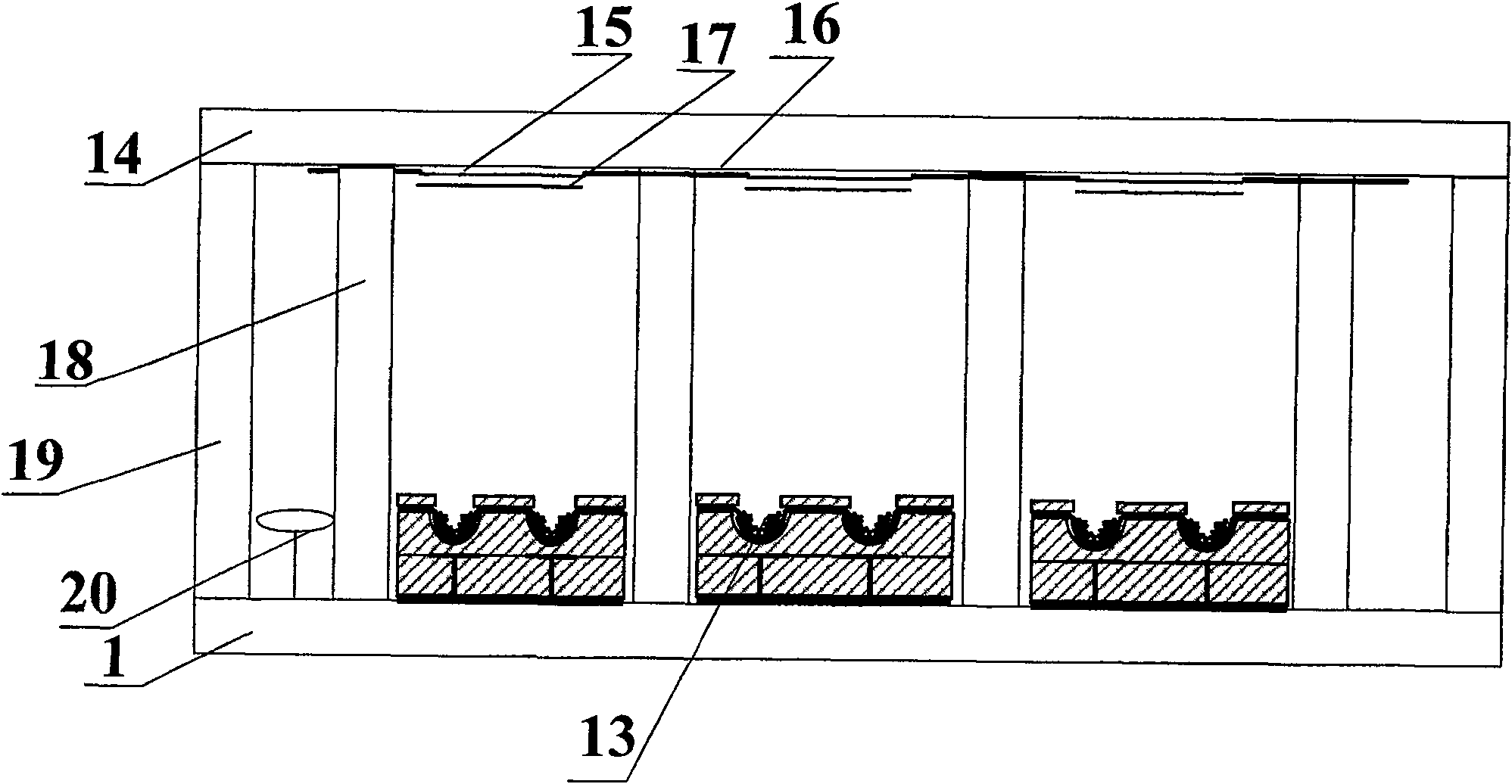

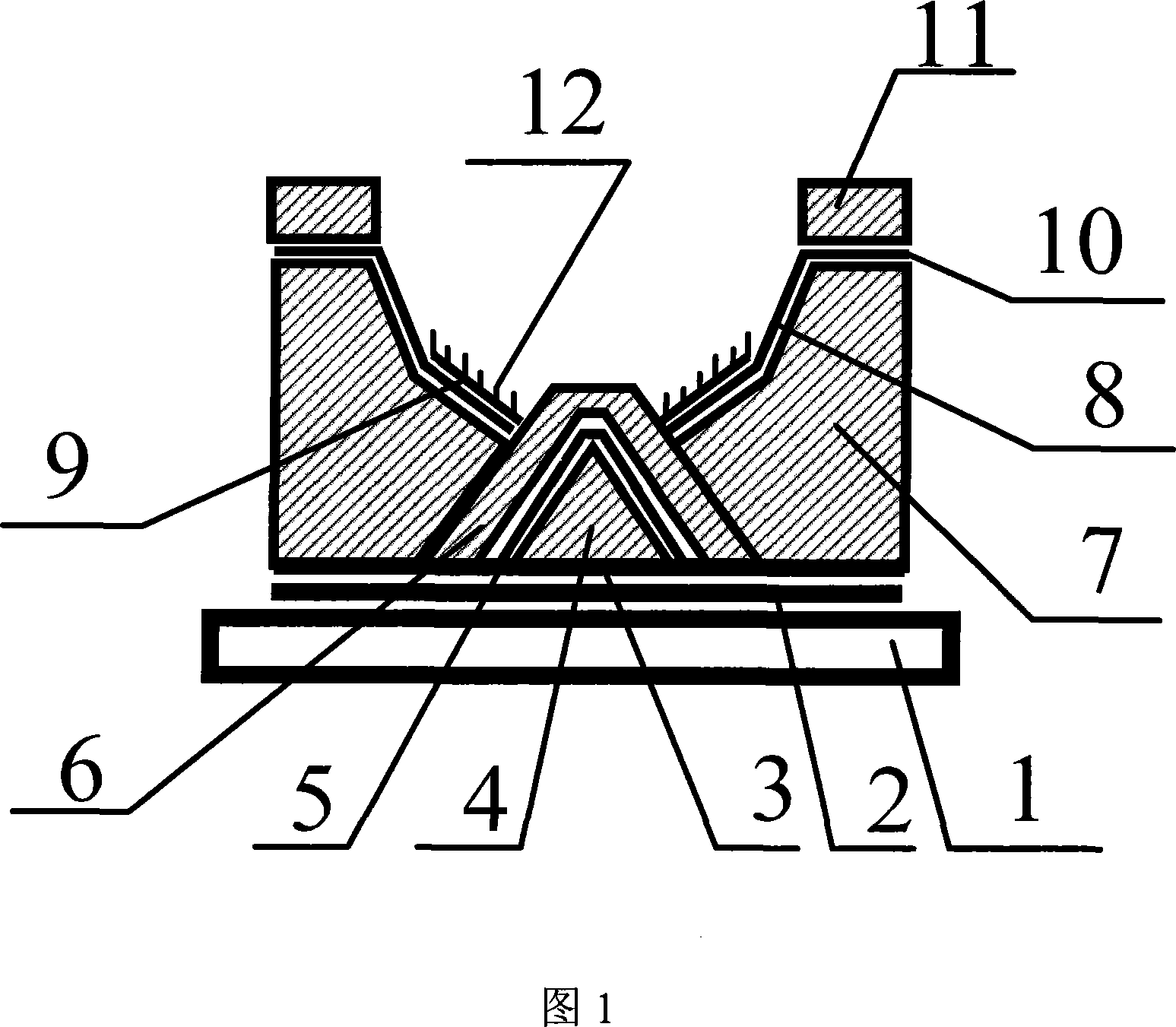

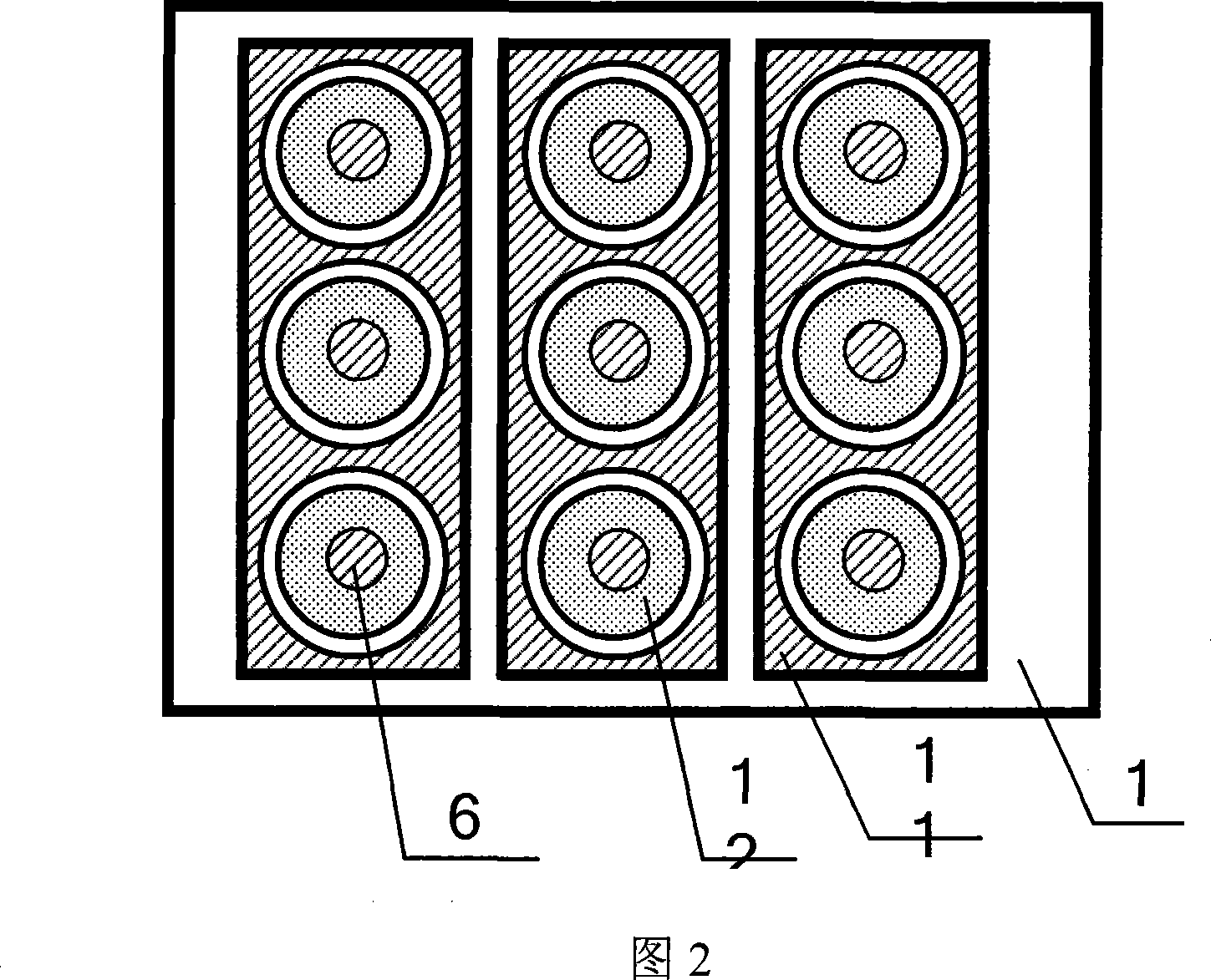

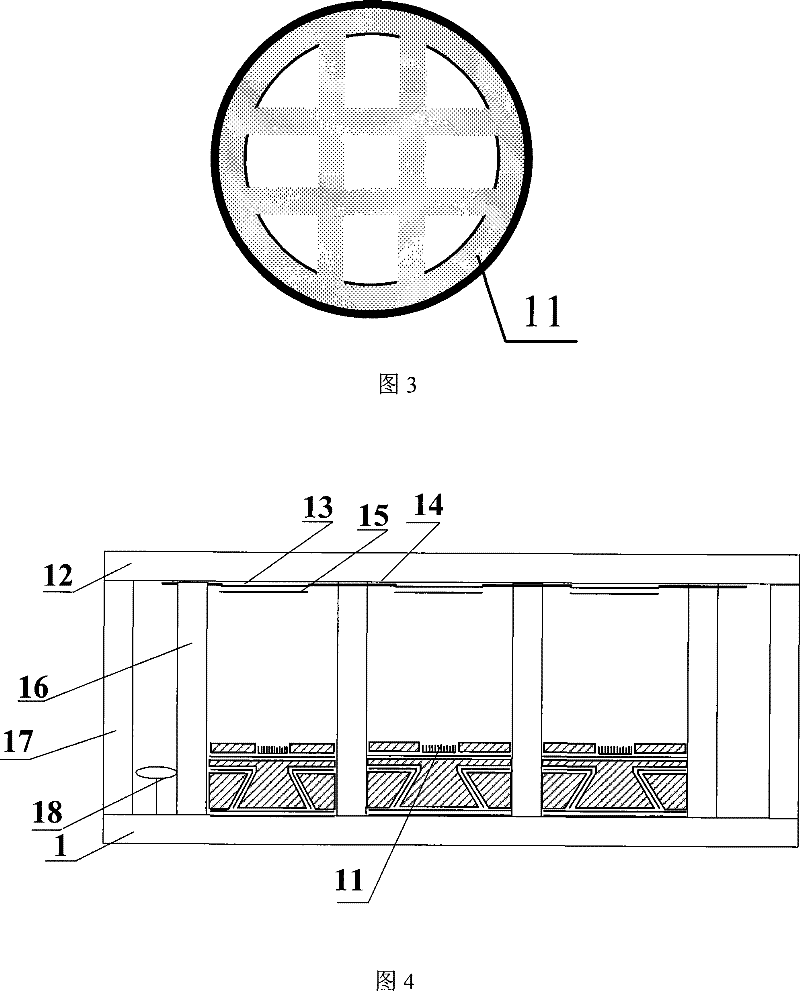

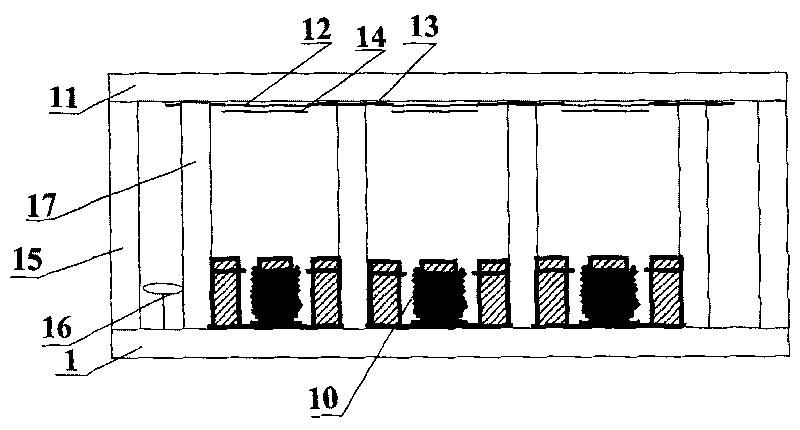

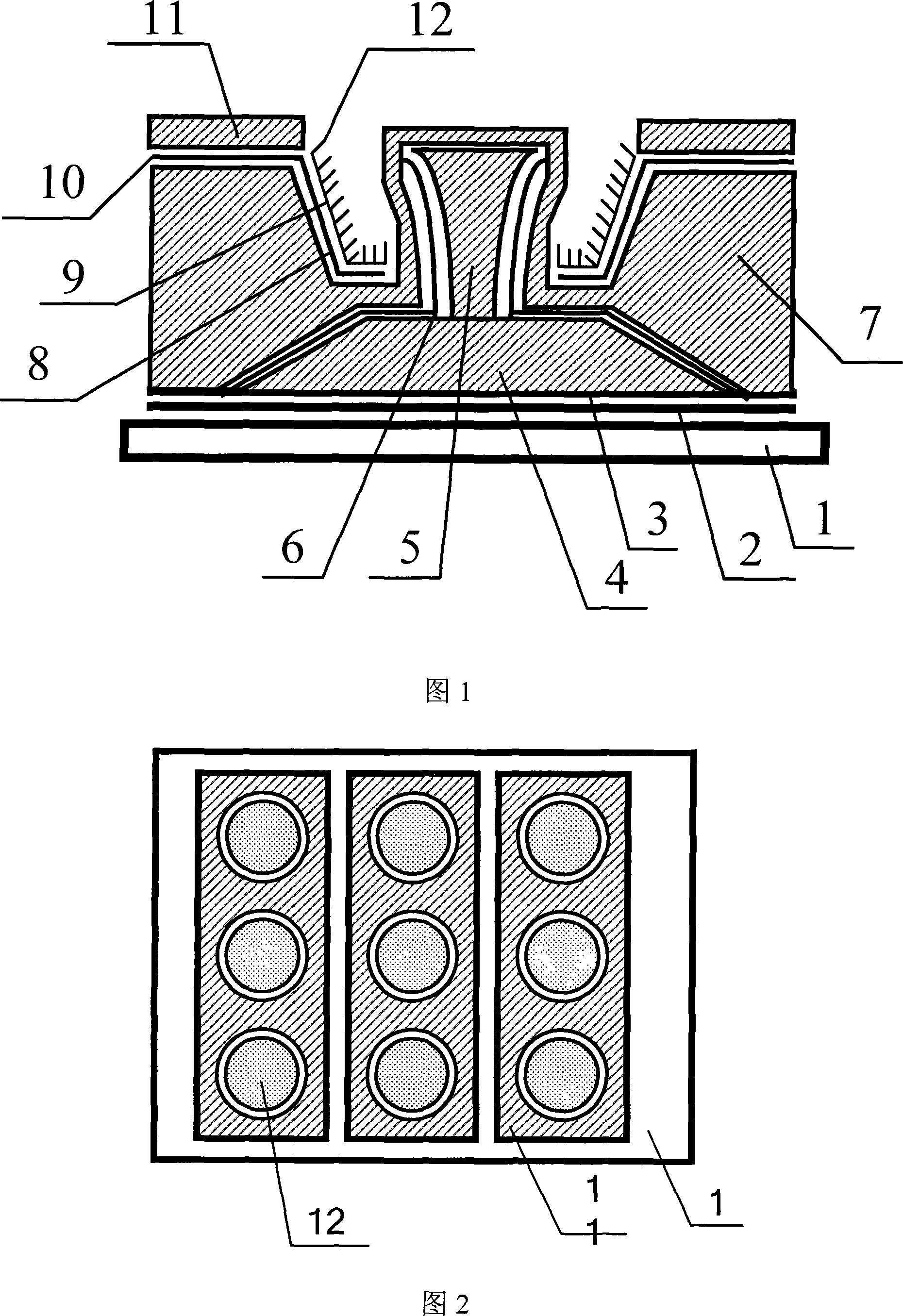

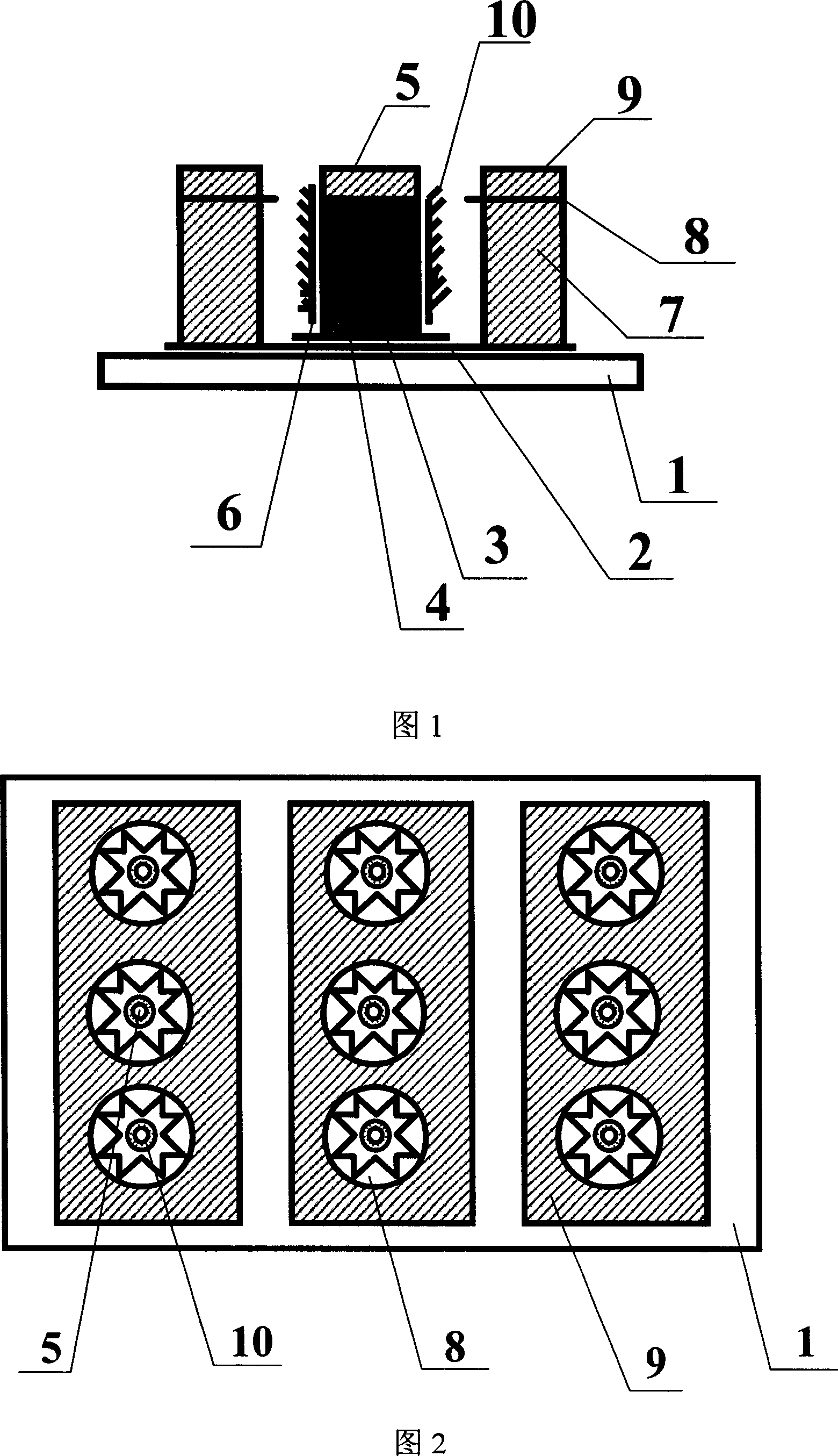

Planar display device with internal-concaved lowr-grid controlled stair cathode structure and its production

InactiveCN101075532ALaunch moreIncrease display brightnessControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

This is a flat displayer of step shape concave low grid cathode structure and its production process. It includes a sealed vacuum chamber formed by a anodic glass panel, a cathode glass panel and surrounded glass frame; on the anodic glass panel is a conducting layer coated with fluorescent; a supporting wall between the anodic and cathode panel and a getter; on the cathode glass panel are a grid down-lead layer, carbon nanotube and step shape concave low grid structure, which is capable of increasing the display quality and decreasing working voltage of the grid.

Owner:ZHONGYUAN ENGINEERING COLLEGE

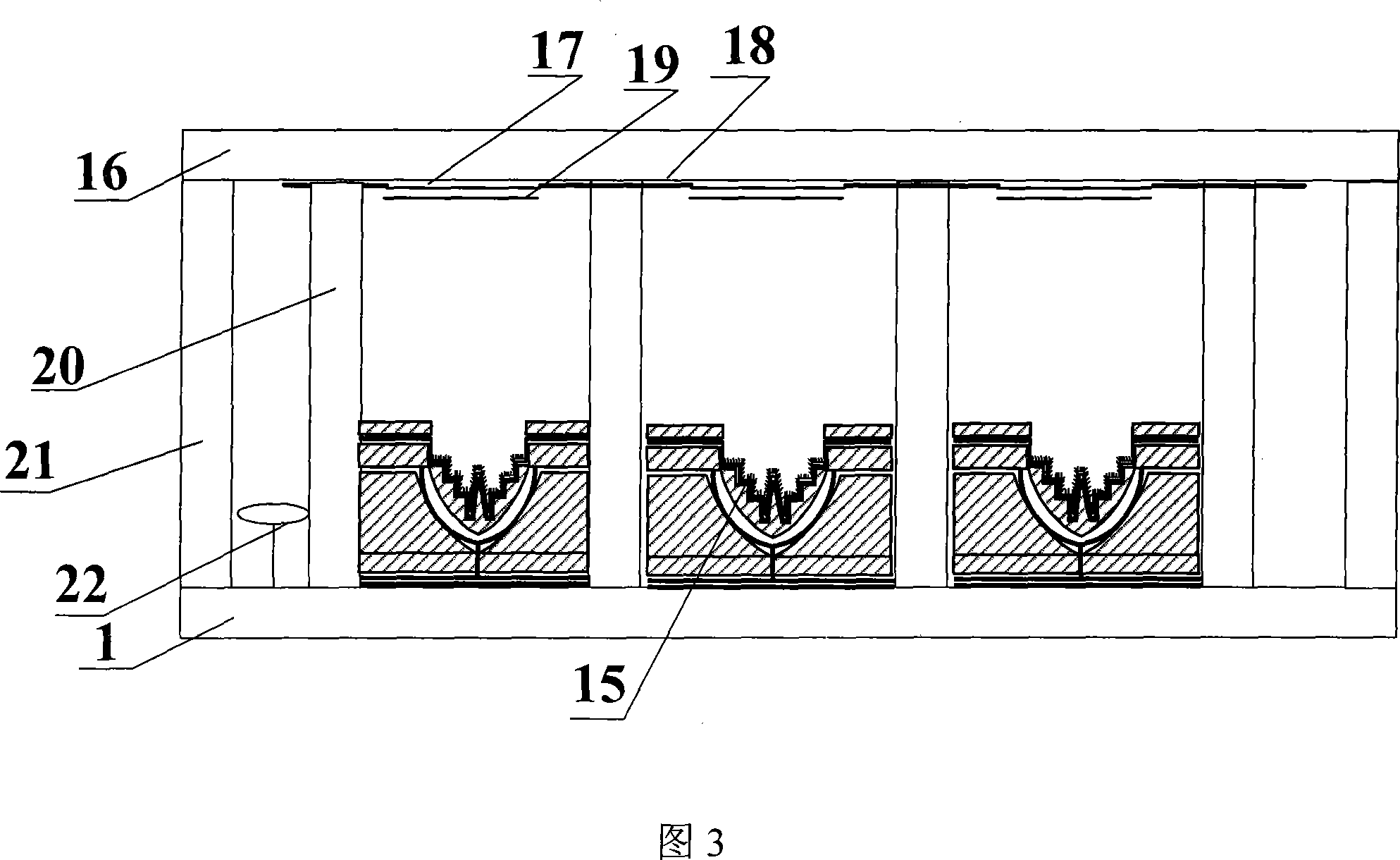

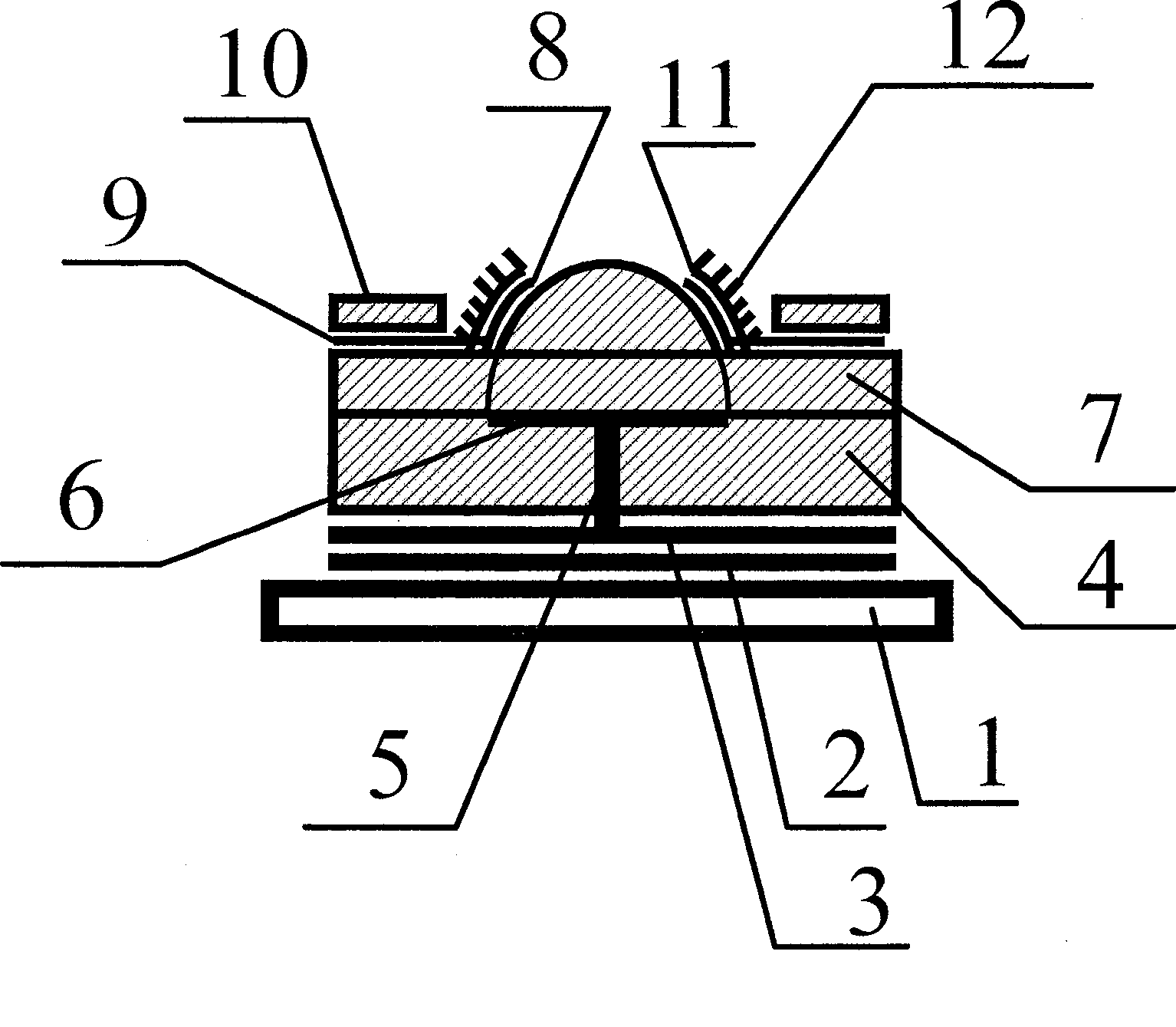

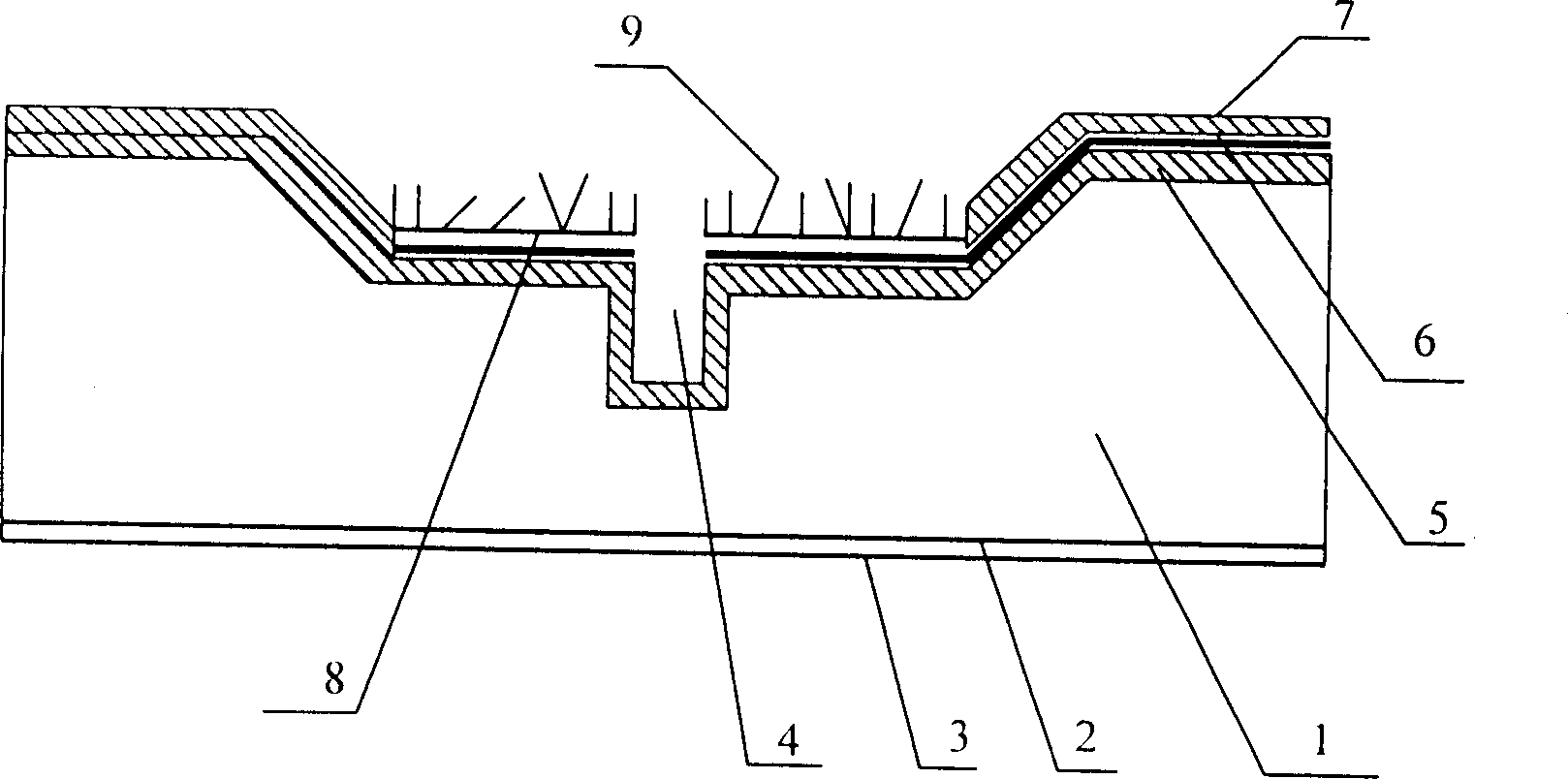

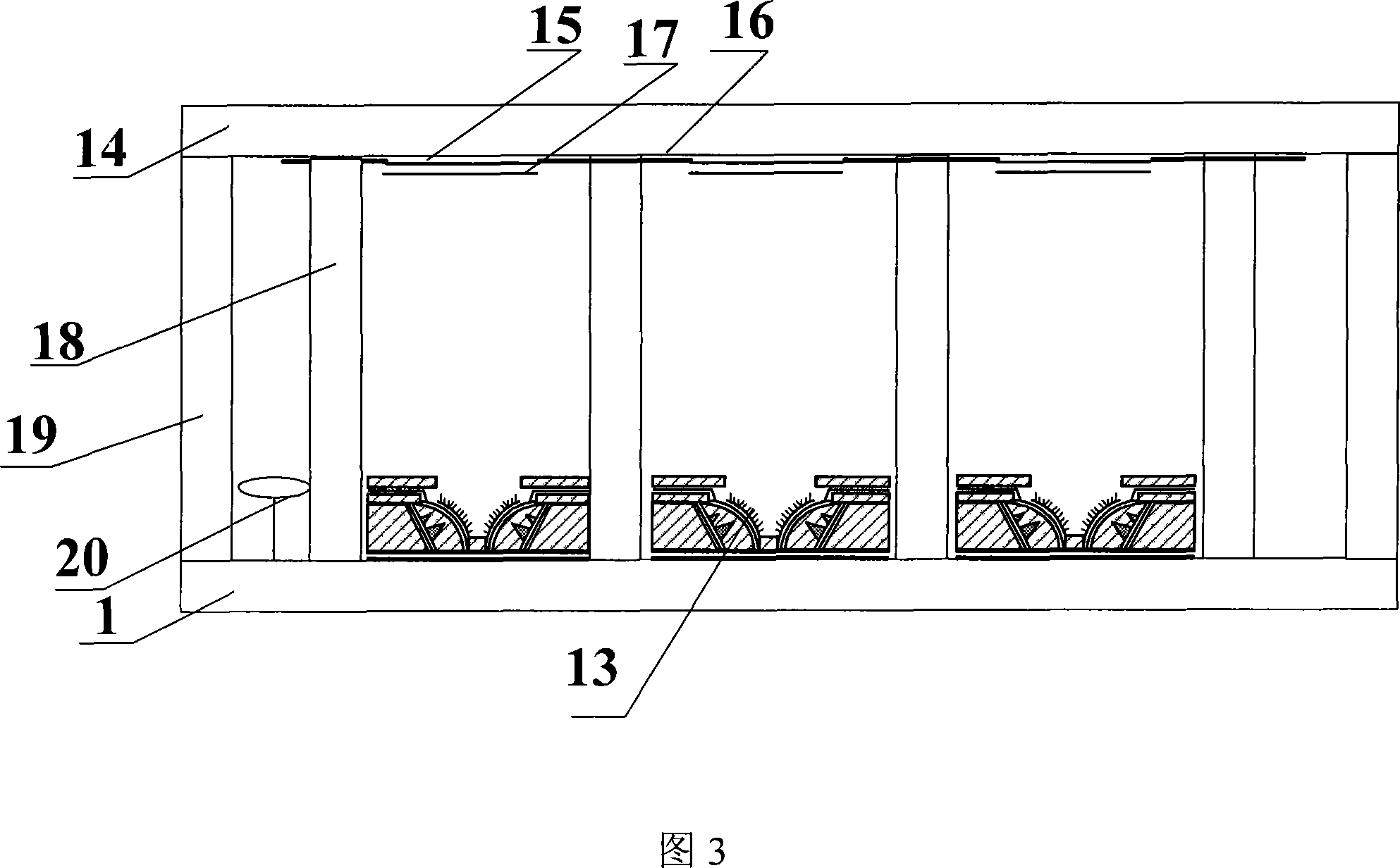

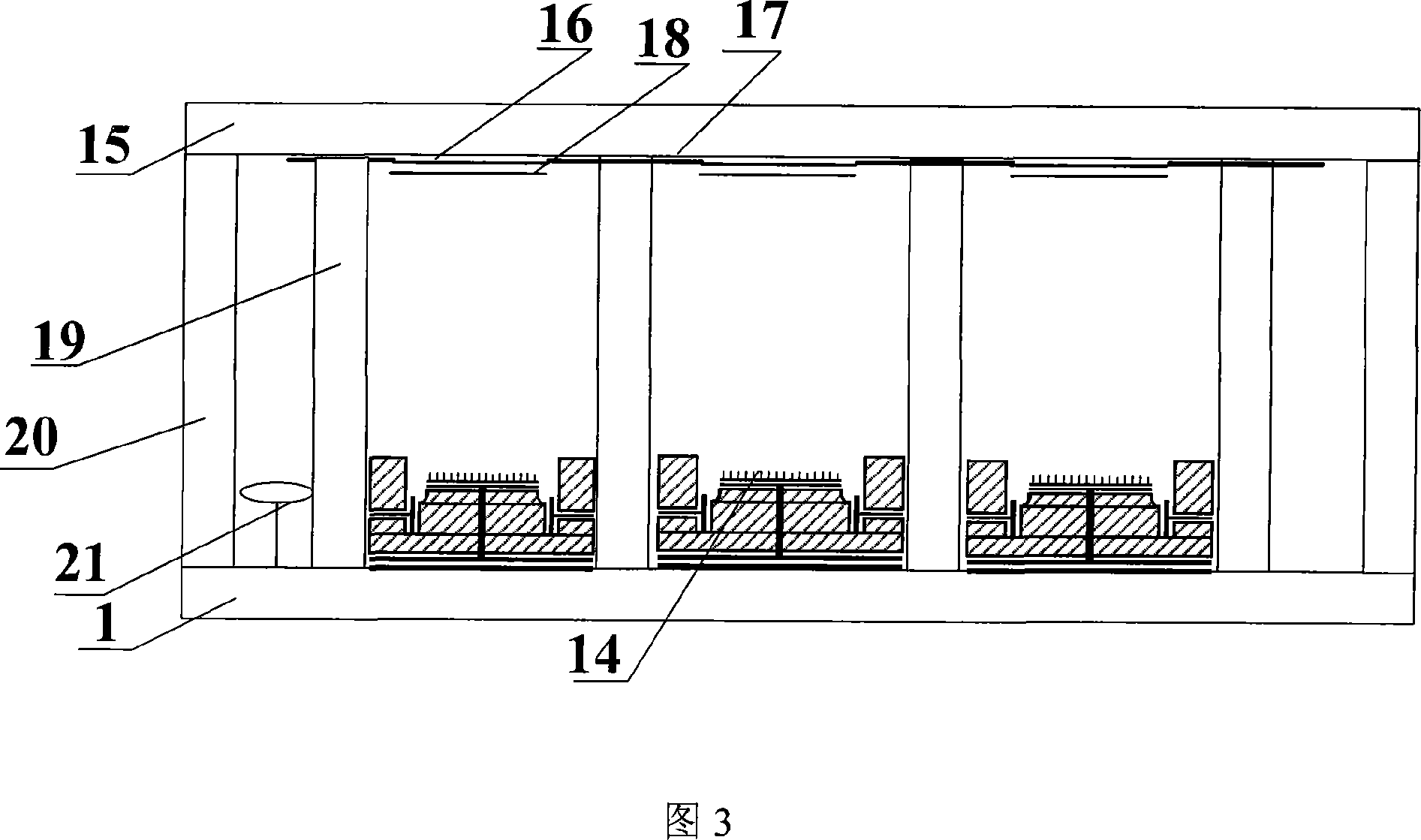

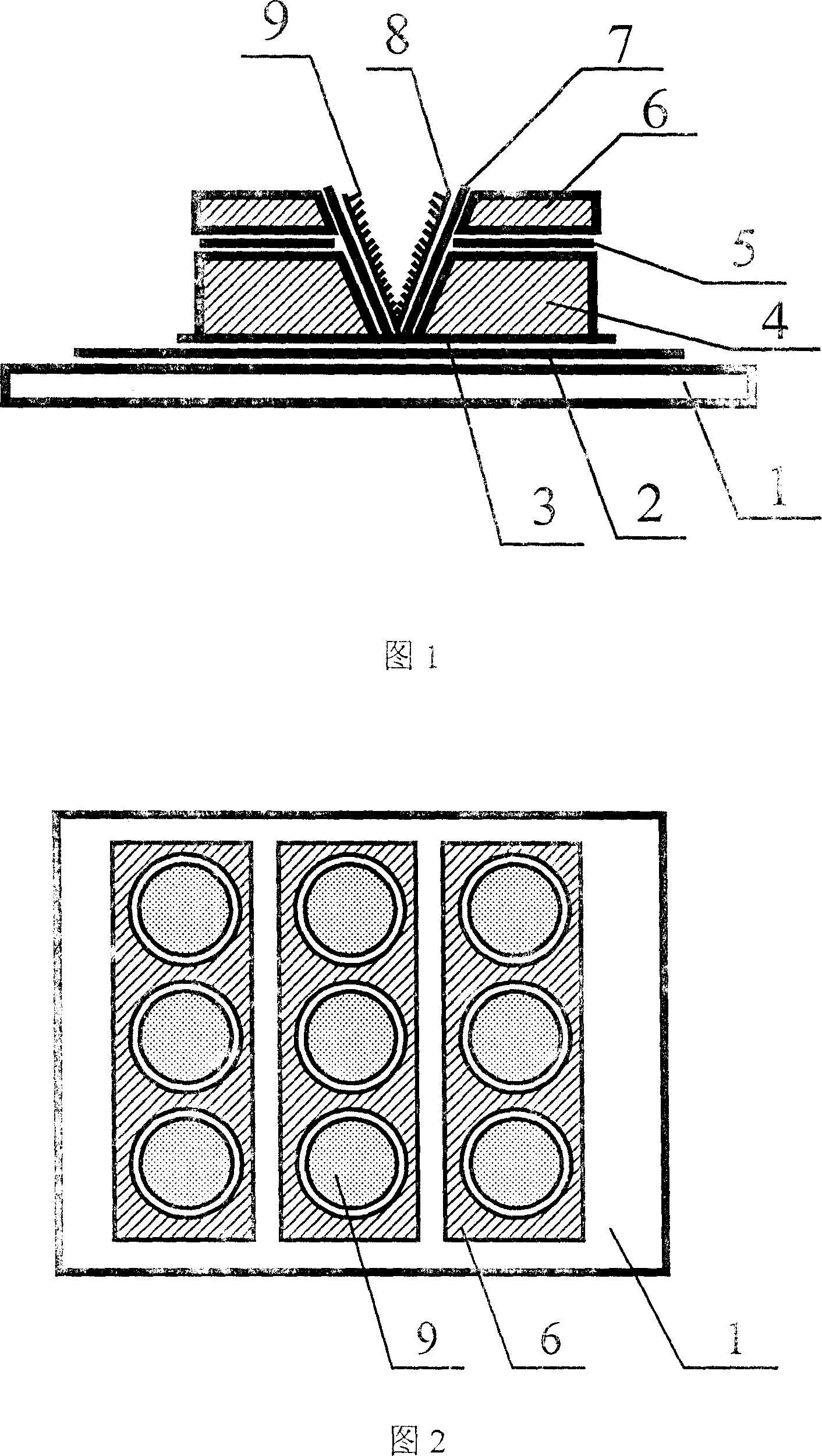

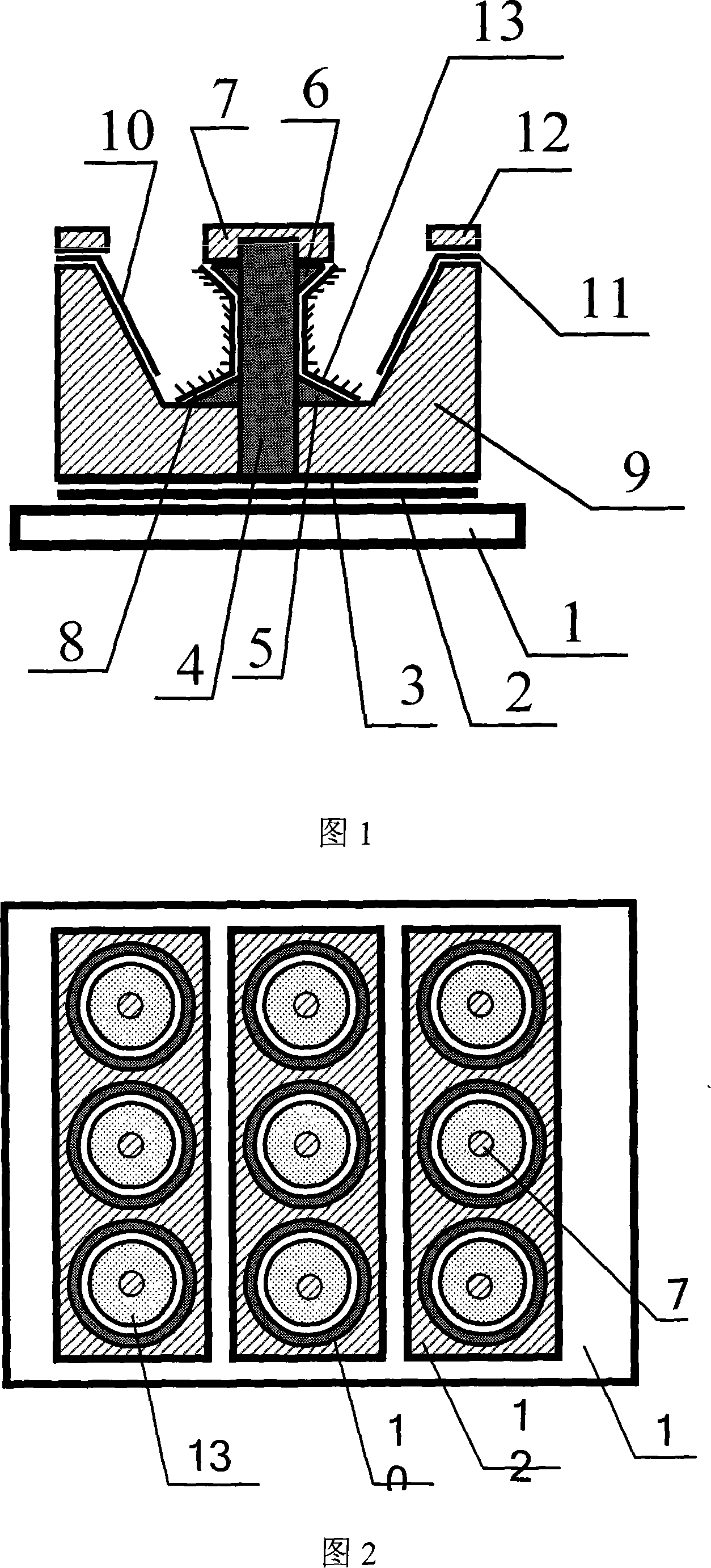

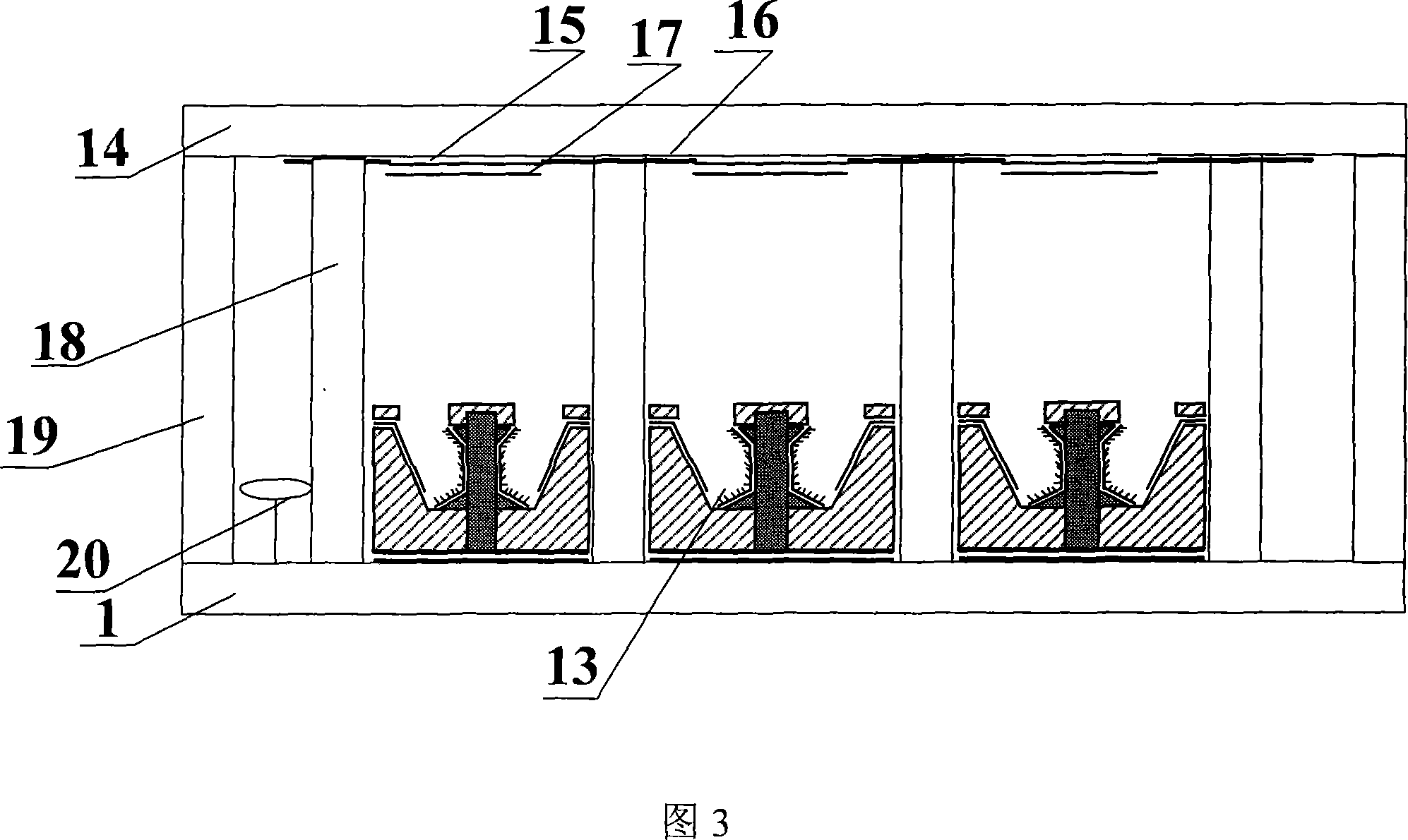

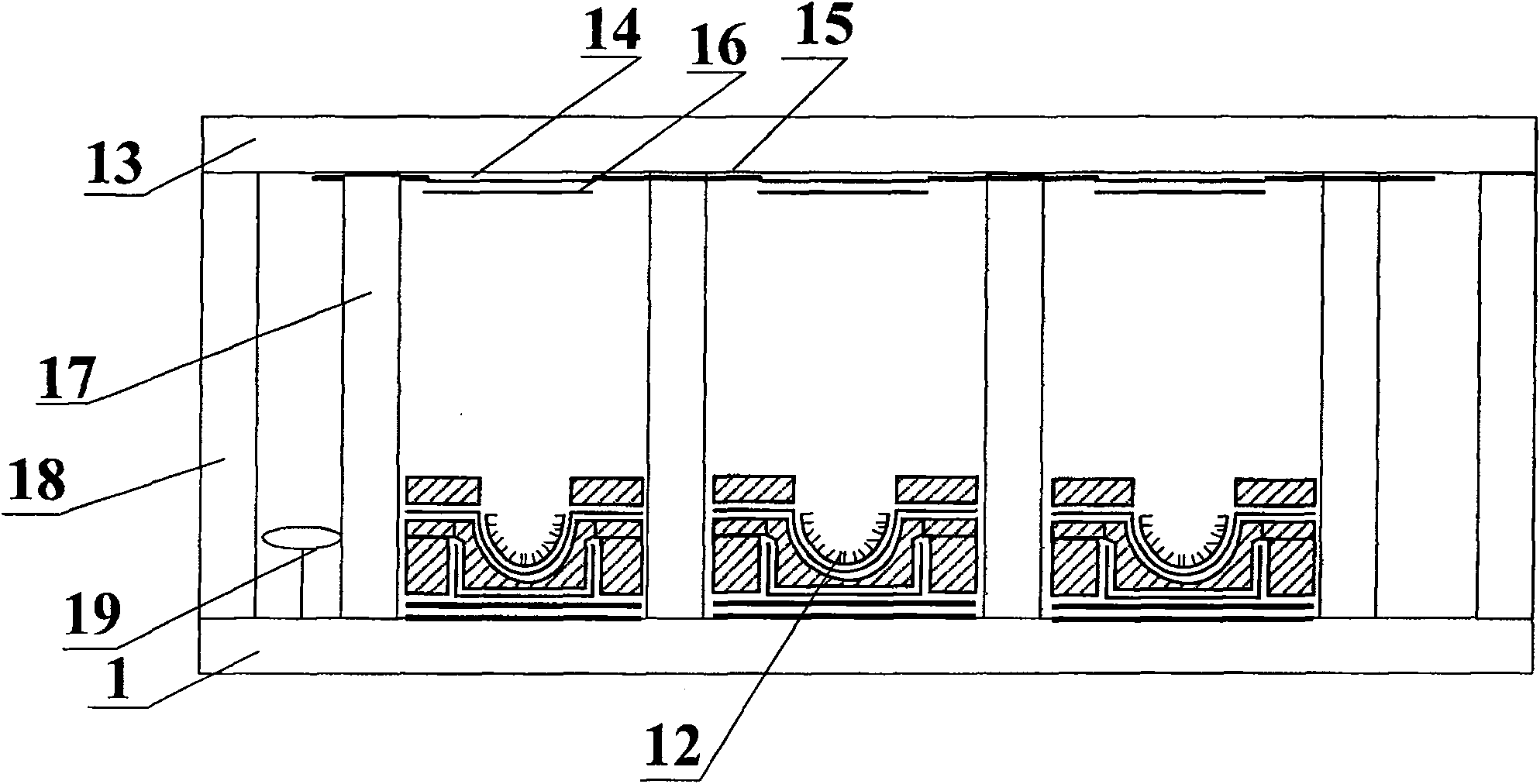

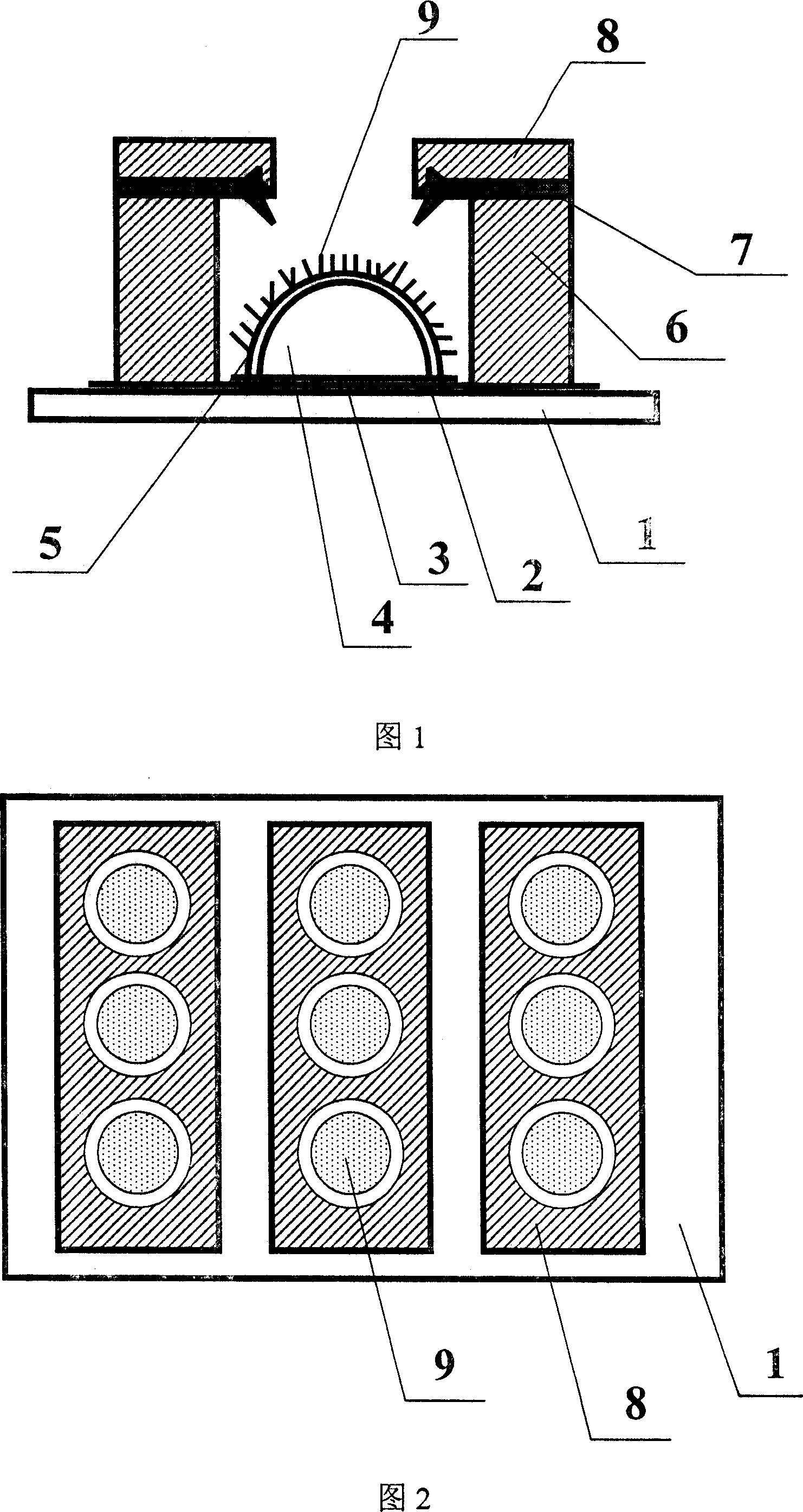

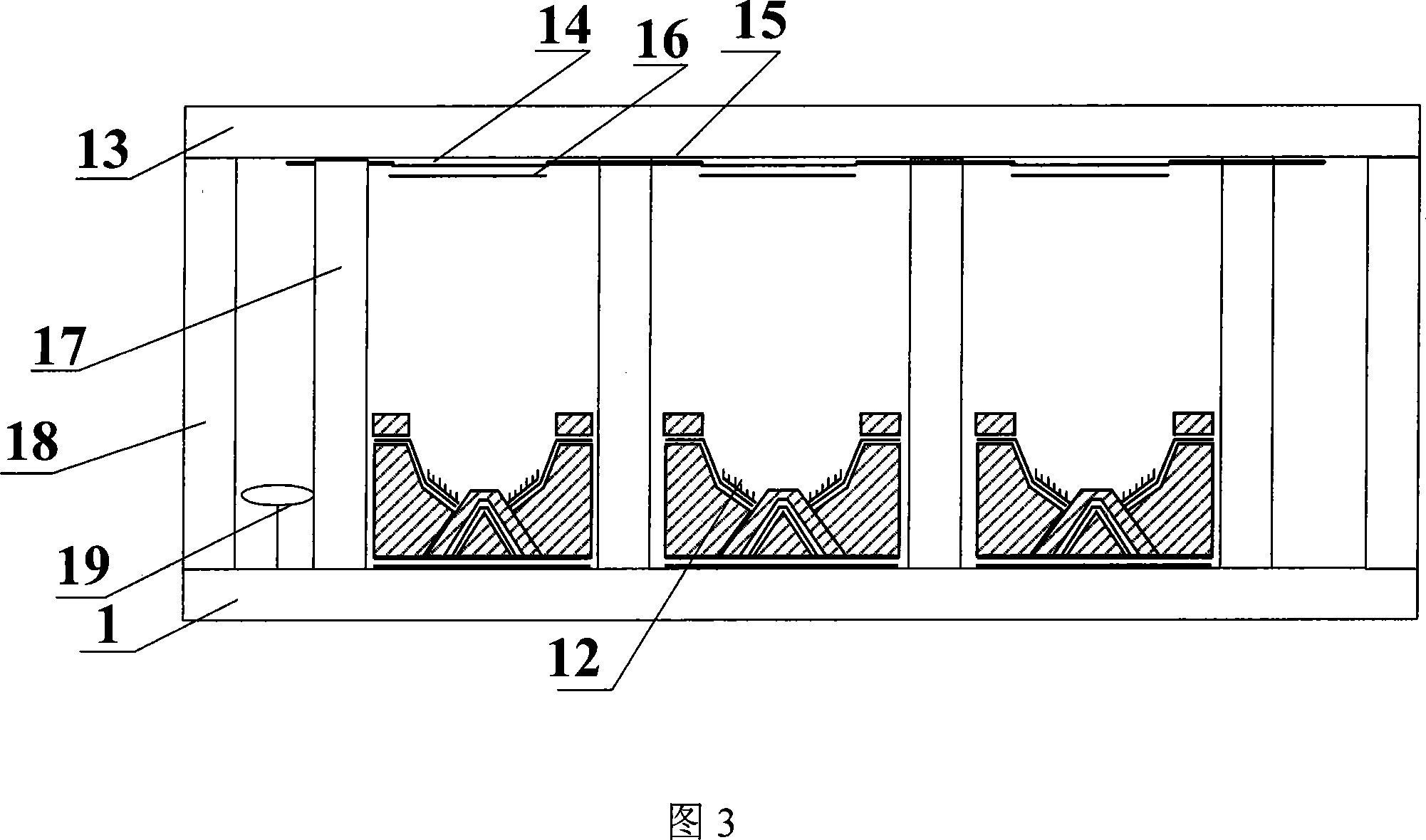

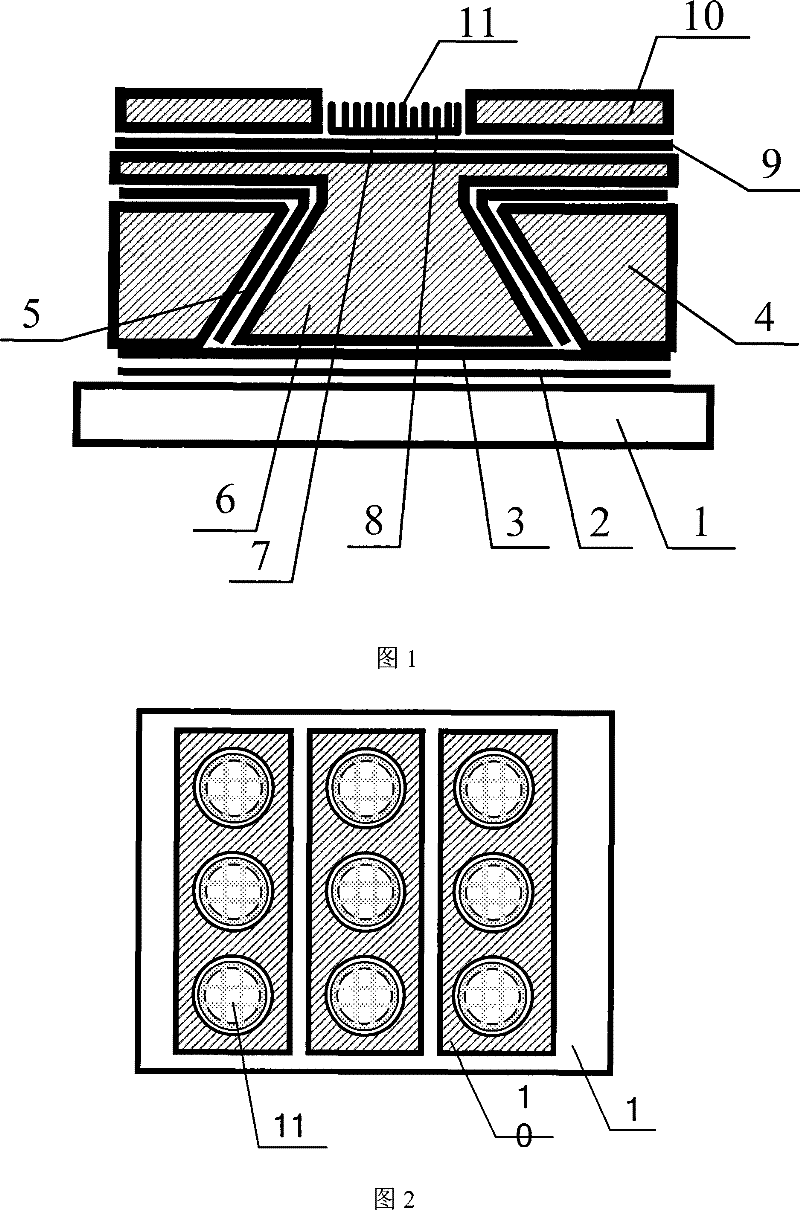

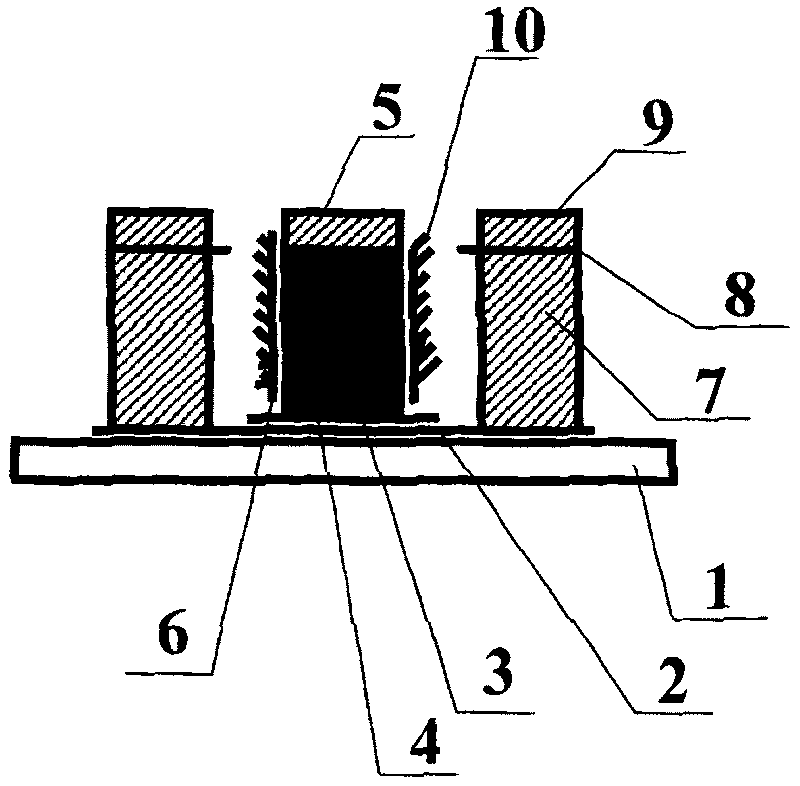

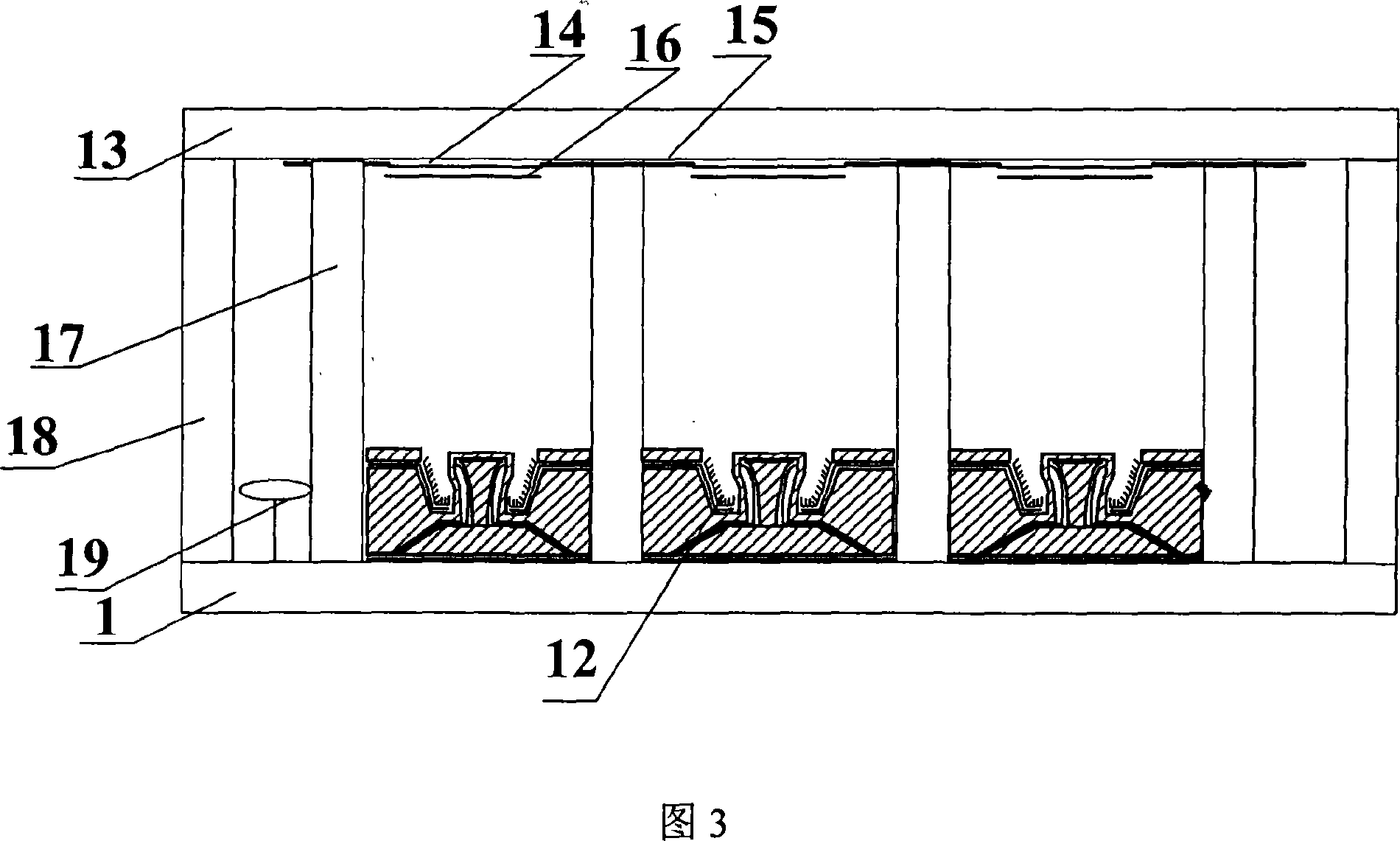

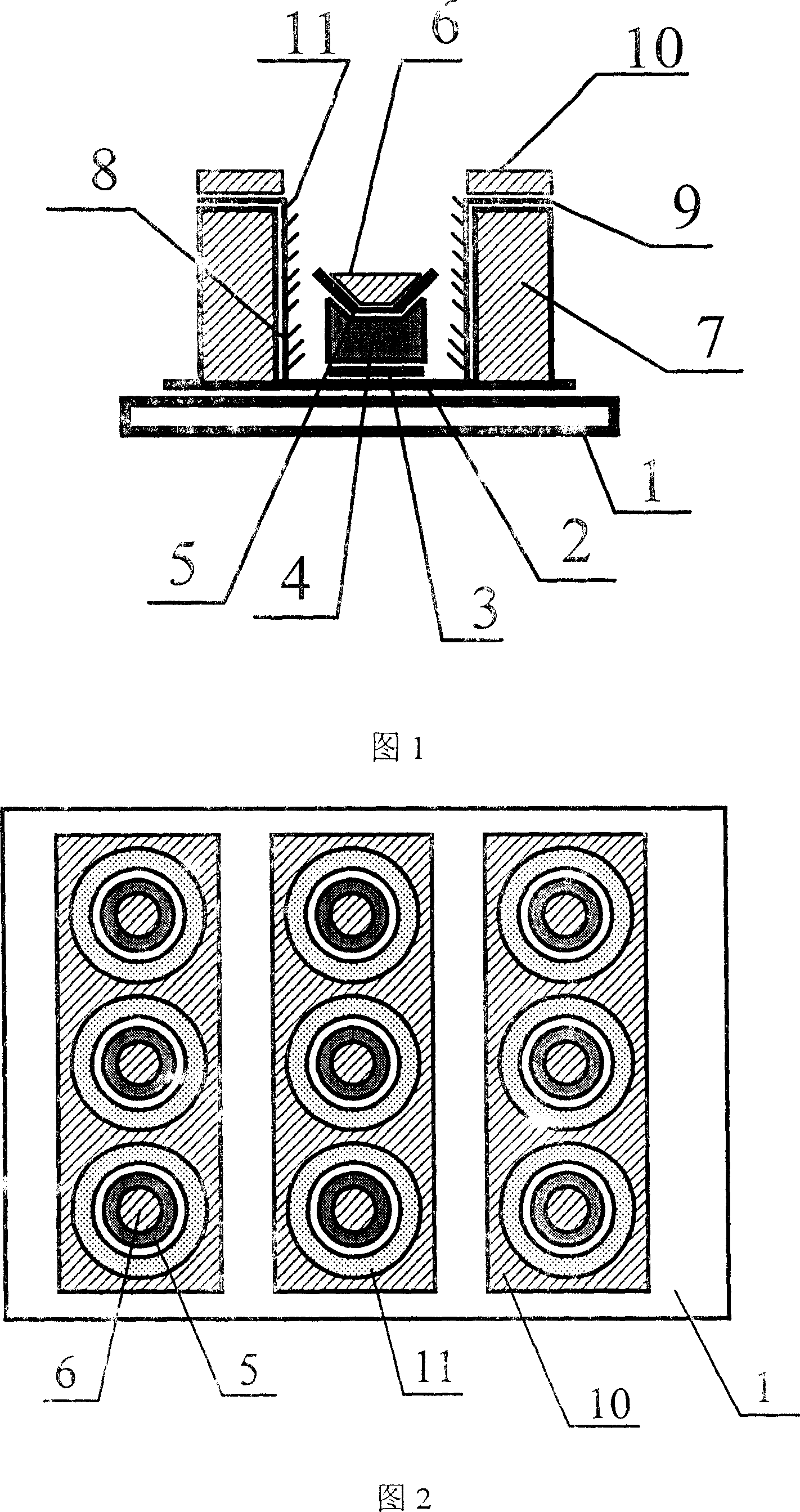

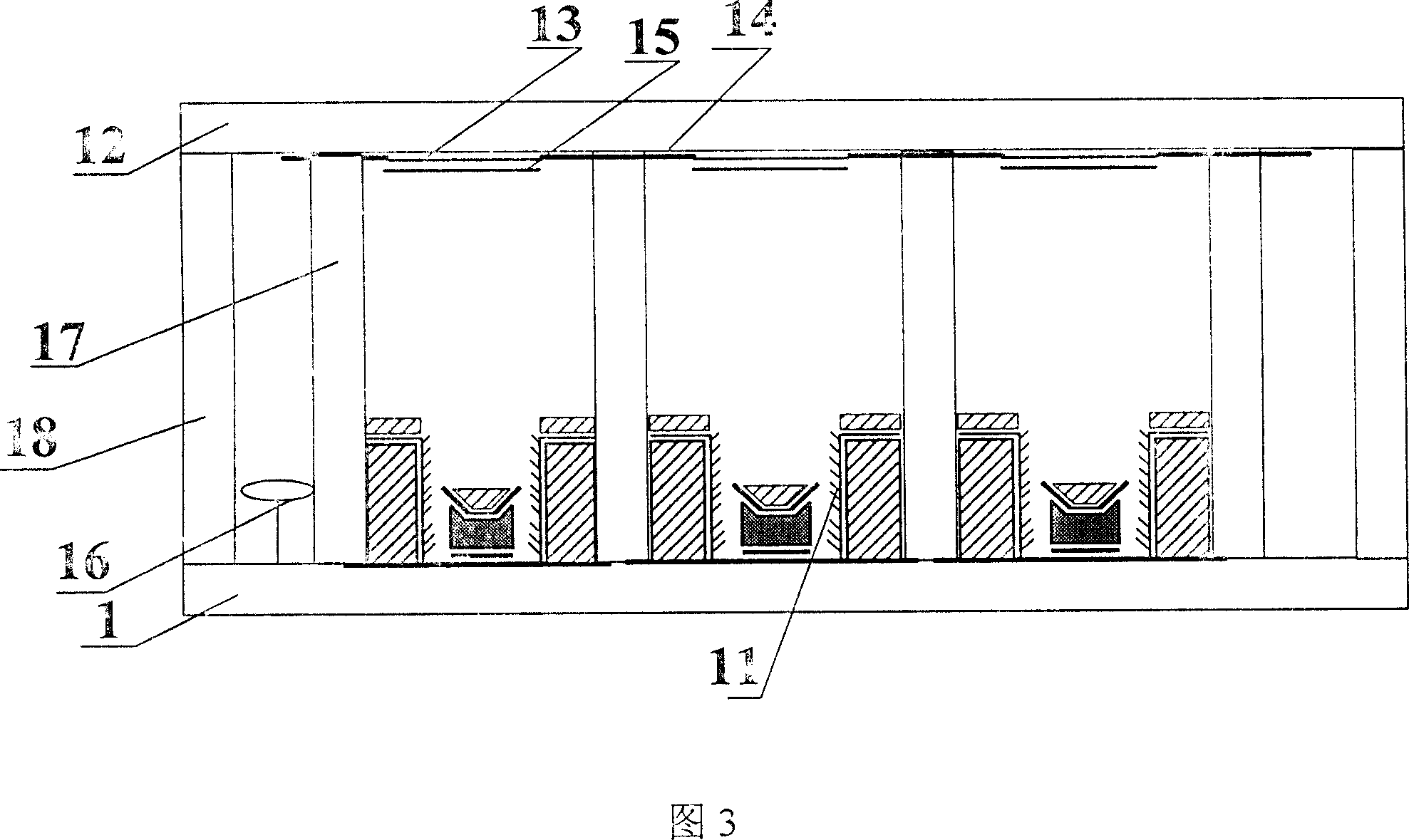

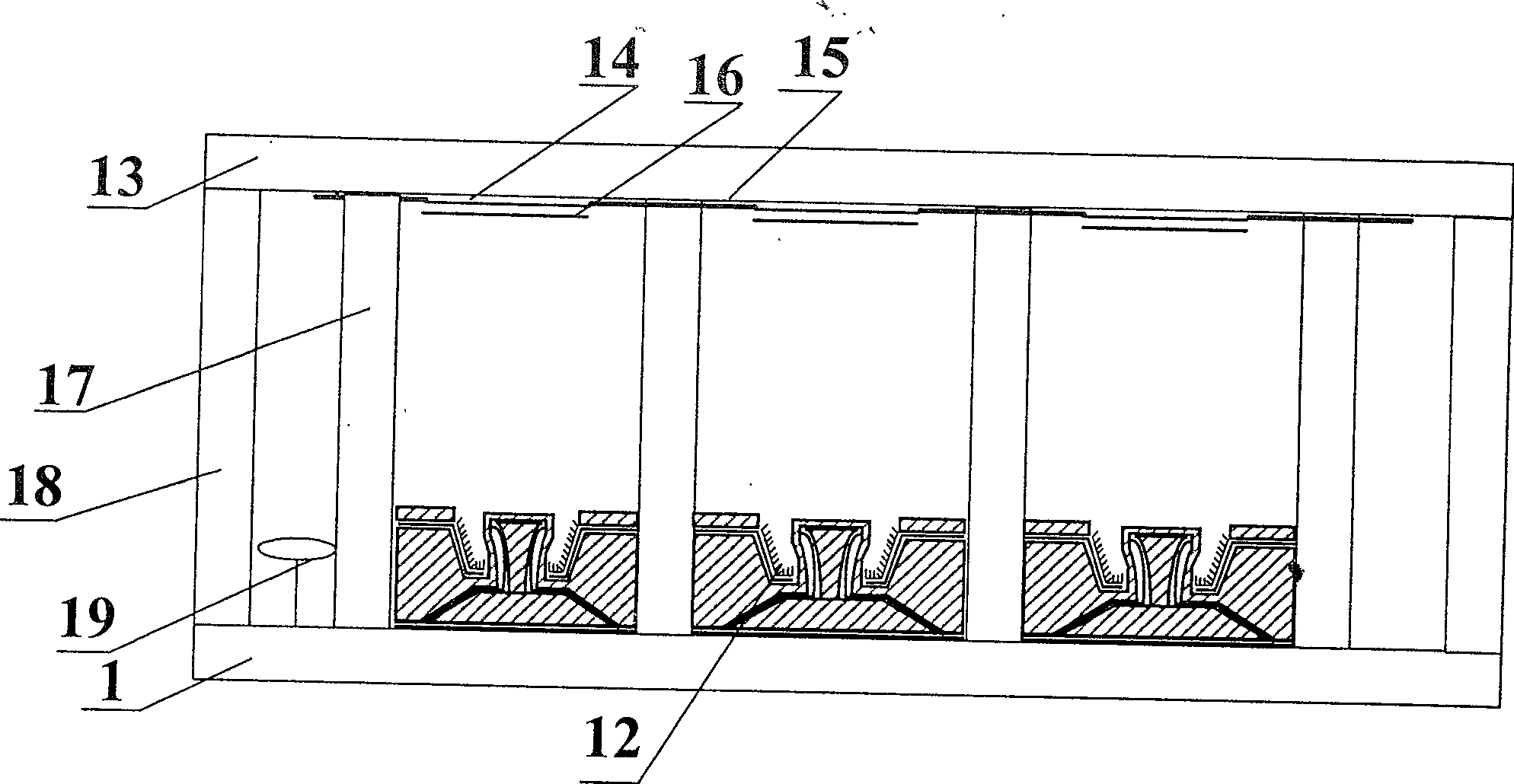

Planar display device with capped bottom-grid controlled cathode structure and its production

InactiveCN100527339CStrong control functionIncrease display brightnessControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

The invention relates to a flat panel display with hat-shaped bottom grid-controlled cathode structure and its manufacturing process, which includes a sealed vacuum chamber composed of an anode glass panel, a cathode glass panel and surrounding glass frames; layer and the phosphor layer prepared on top of the anode conductive layer; the supporting wall structure and getter accessory components between the anode glass panel and the cathode glass panel, and the grid lead layer, carbon nanotubes and cap type on the cathode glass panel Bottom-gate-controlled cathode structure; it can reduce the working voltage of the grid, improve the display brightness of the overall device, and reduce the working current of the grid. It has the advantages of stable and reliable manufacturing process, simple manufacturing process, low manufacturing cost and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

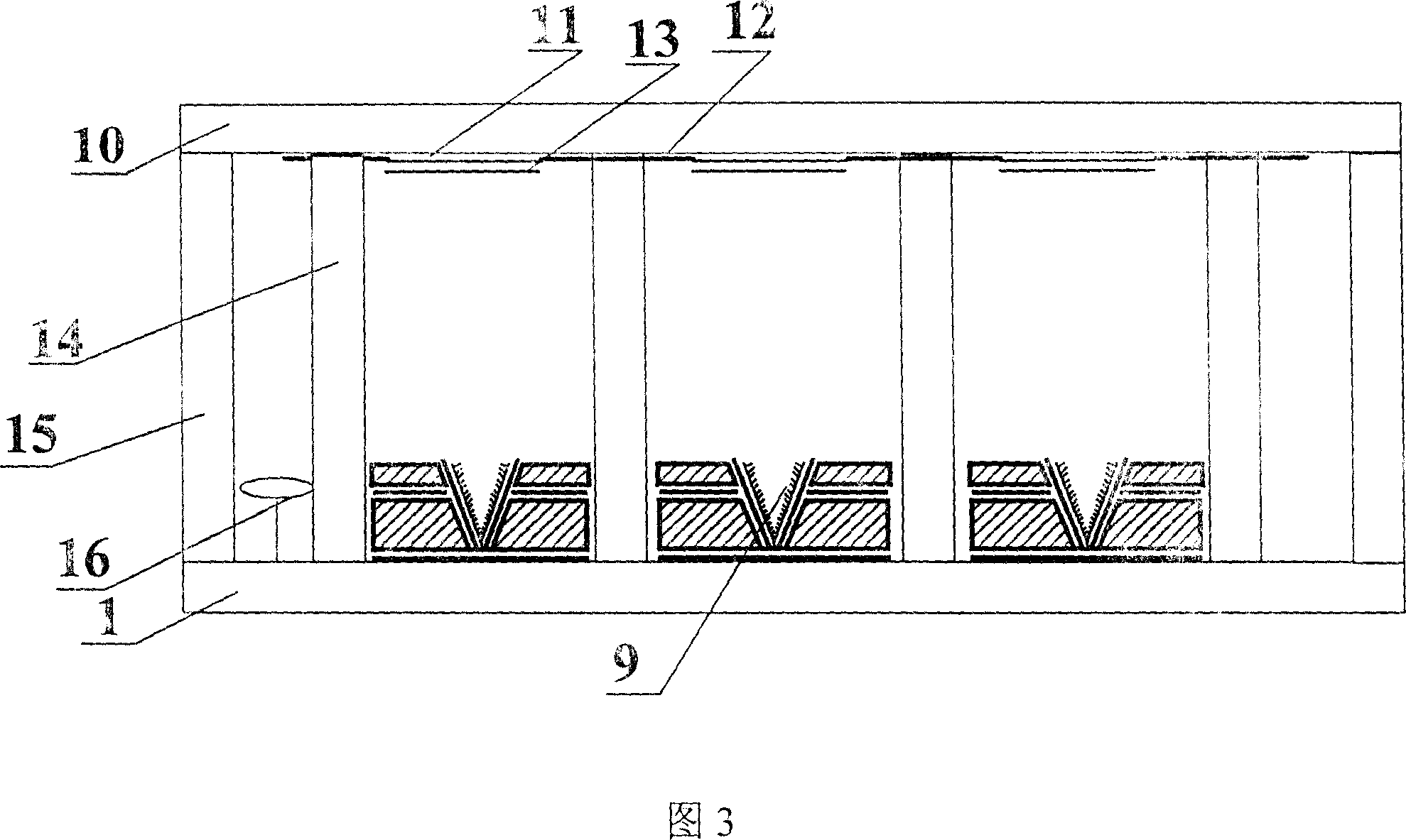

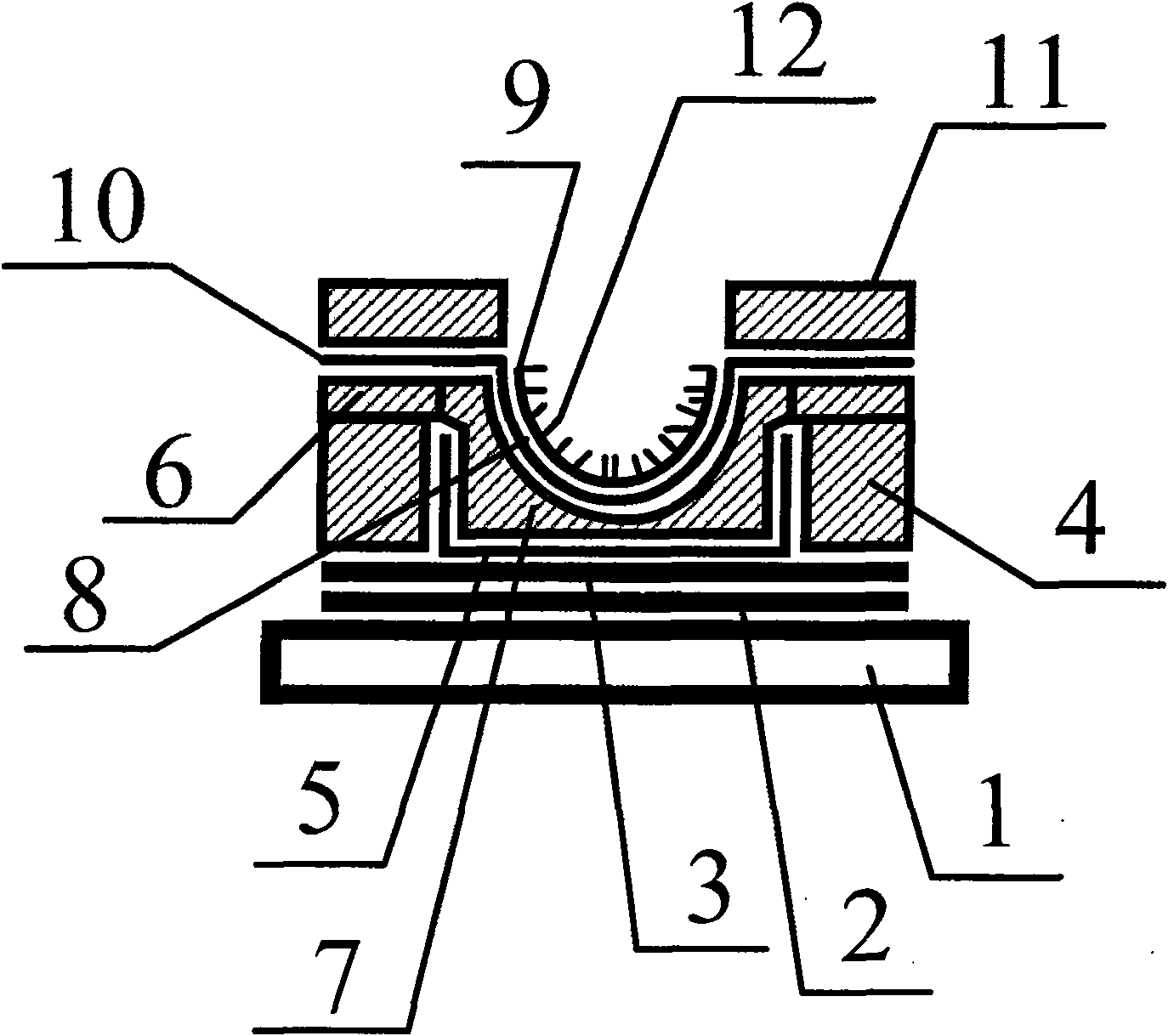

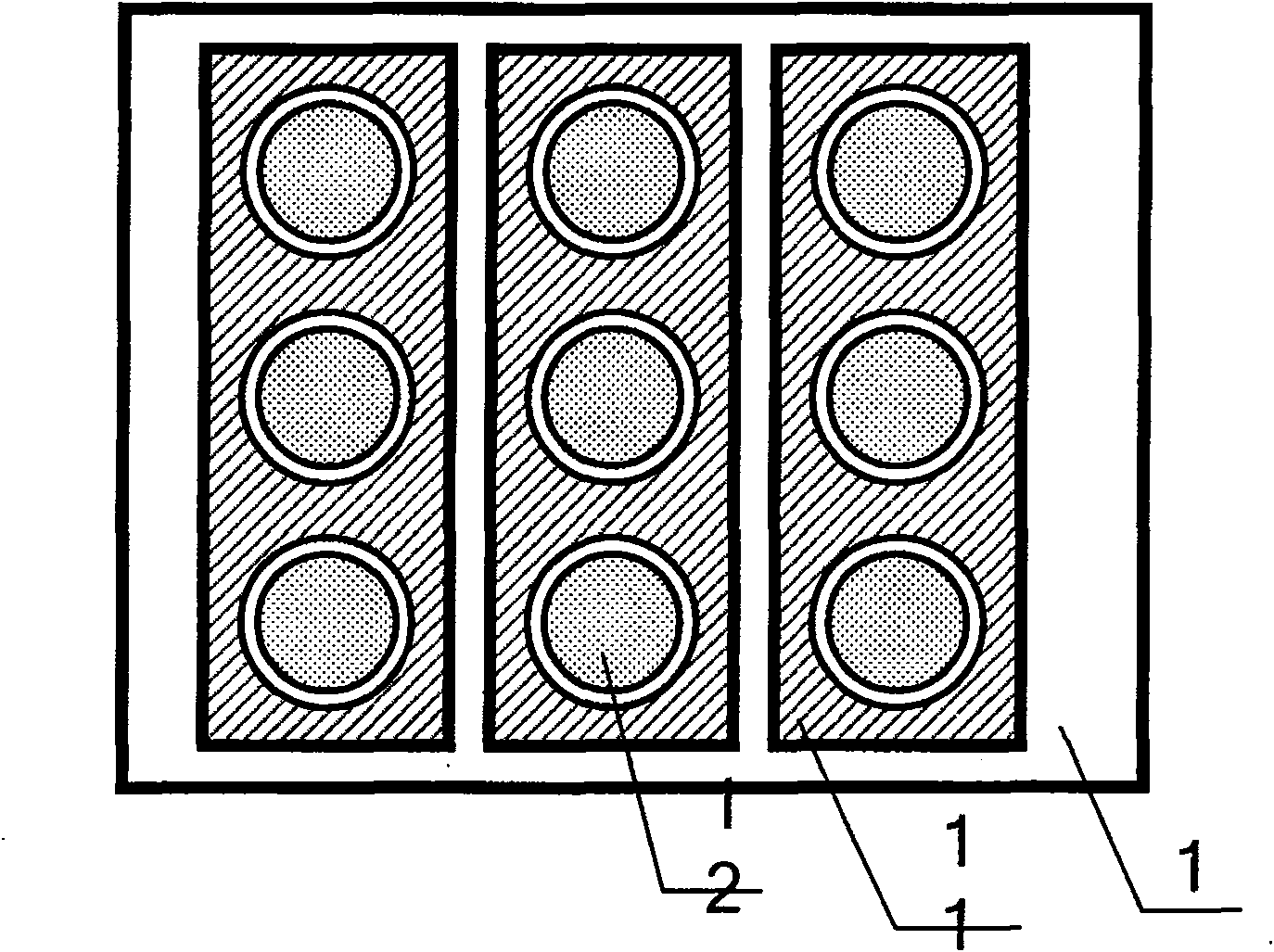

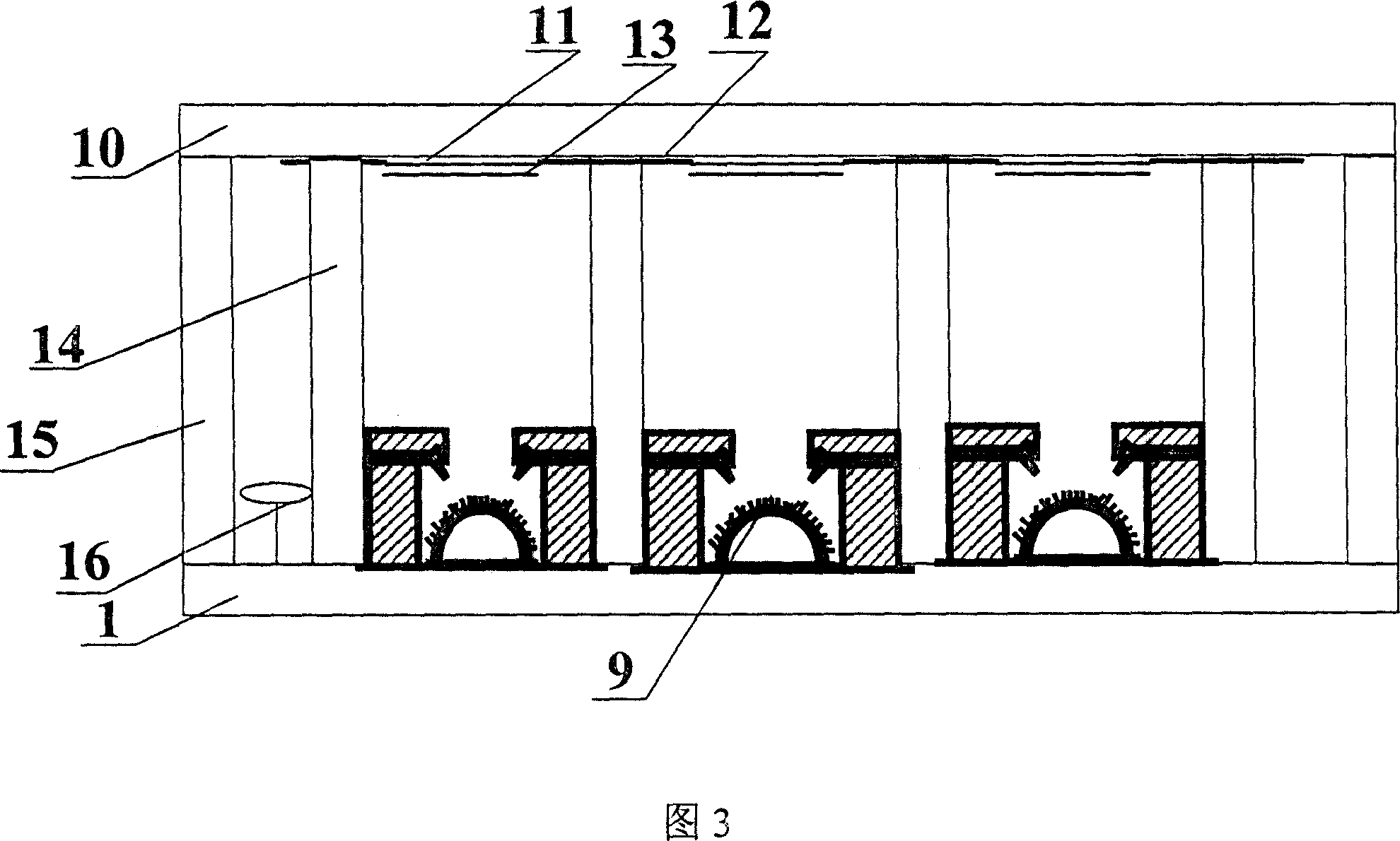

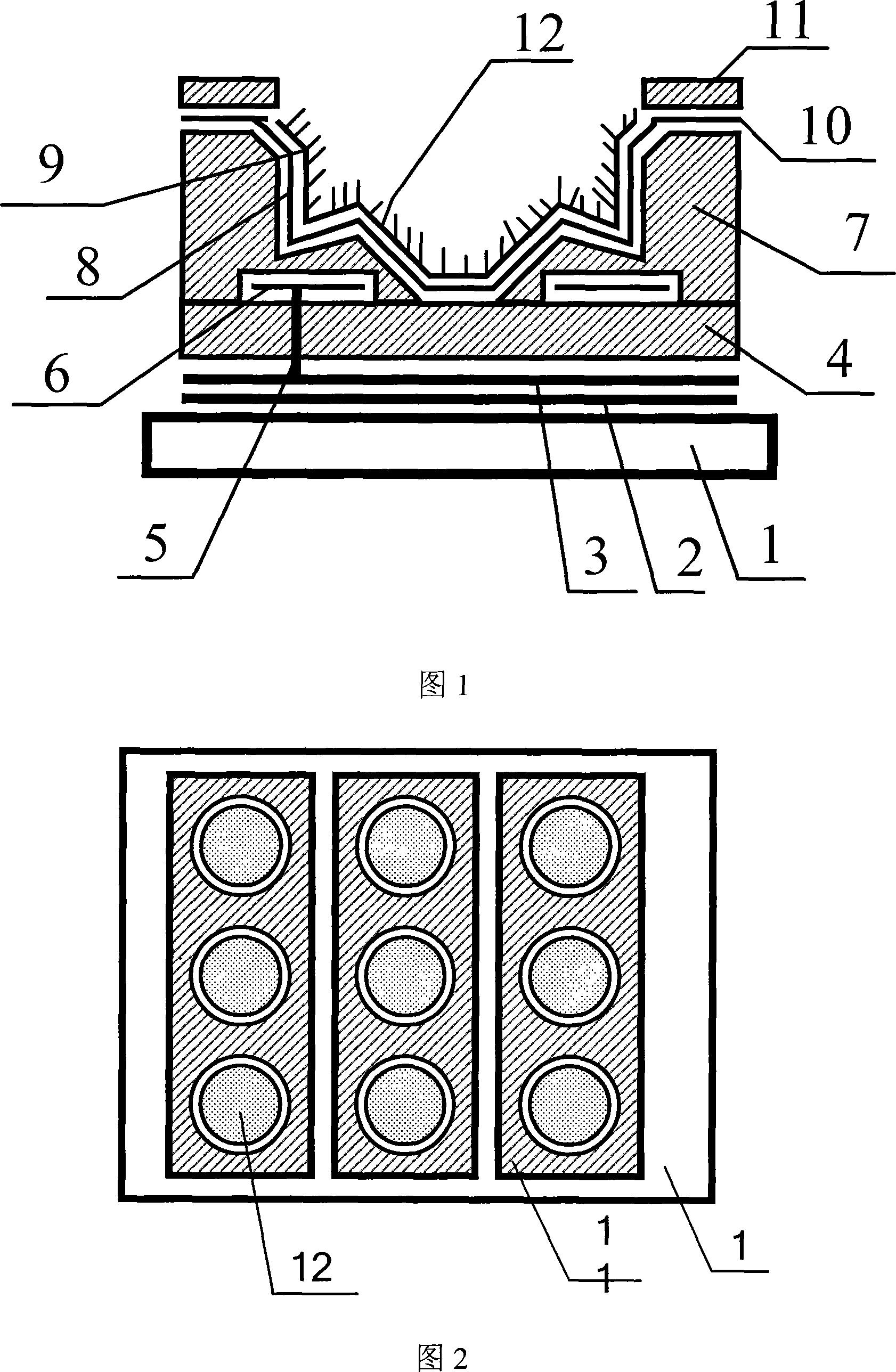

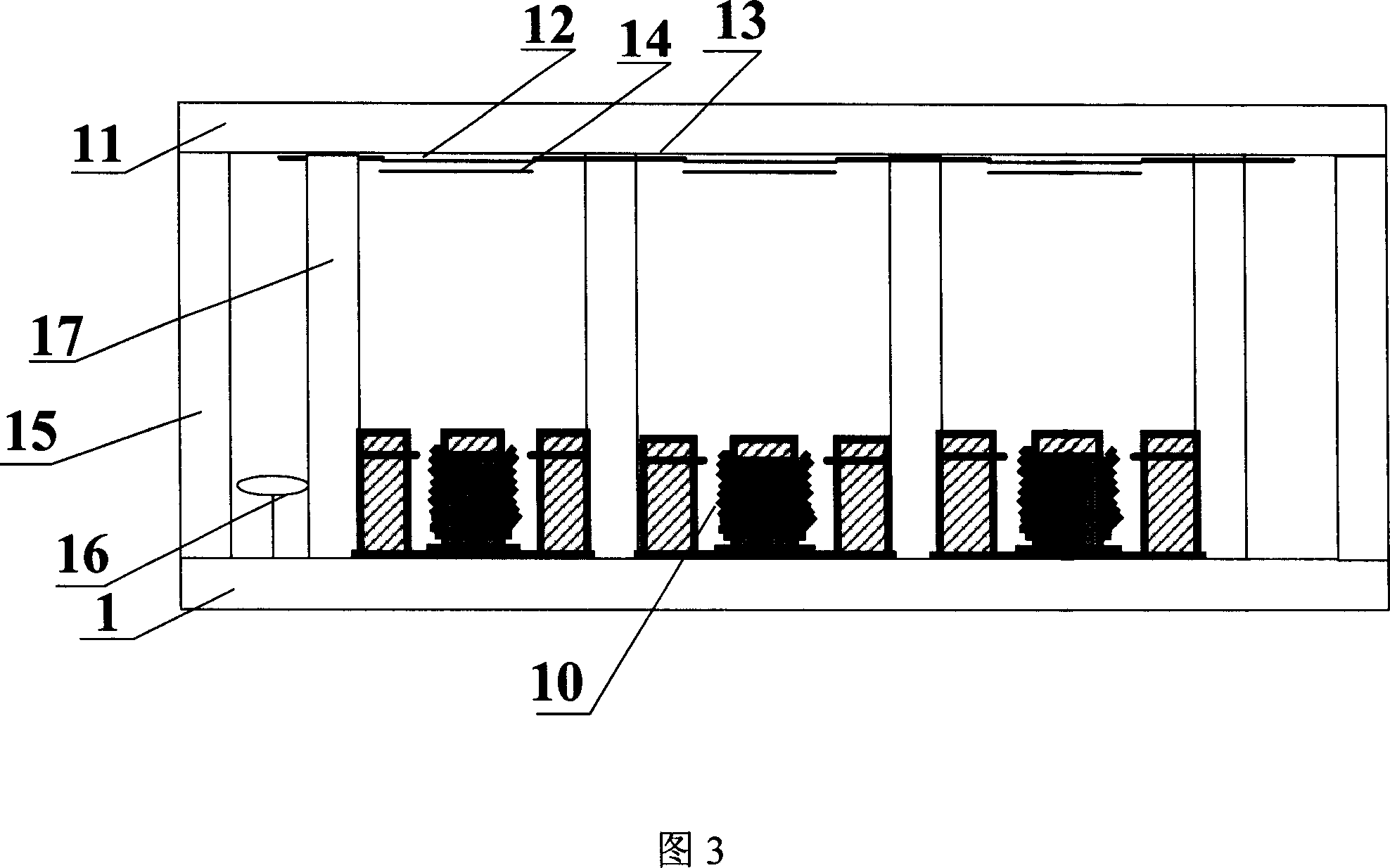

Flat panel display with integrated step type slot grid structure

InactiveCN1822297AImprove controlIncrease display brightnessControl electrodesImage/pattern display tubesPhosphorCarbon nanotube

Present invention relates to a flat-panel display having integrated echelonment trough gate structure and making technology. It contains anode panel and concave cycle glass enclose constructed sealed vacuum cavity, anode panel having photo etched anode conducting layer and phosphor powder layer anode conducting layer, growing carbon nanotube cathode, knee wall structure and getter element, cathode panel having integrated echelonment trough gate structure and reducing whole device operating voltage, at the same time highly integrating signal grid and carbon nanotube cathode, said grid having strong control action to carbon nanotube cathode electron emission. Said invention raises carbon nanotube cathode electron emission efficiency having reliable manufacturing process, simple technology, low cost, and simple structure etc advantages.

Owner:ZHONGYUAN ENGINEERING COLLEGE

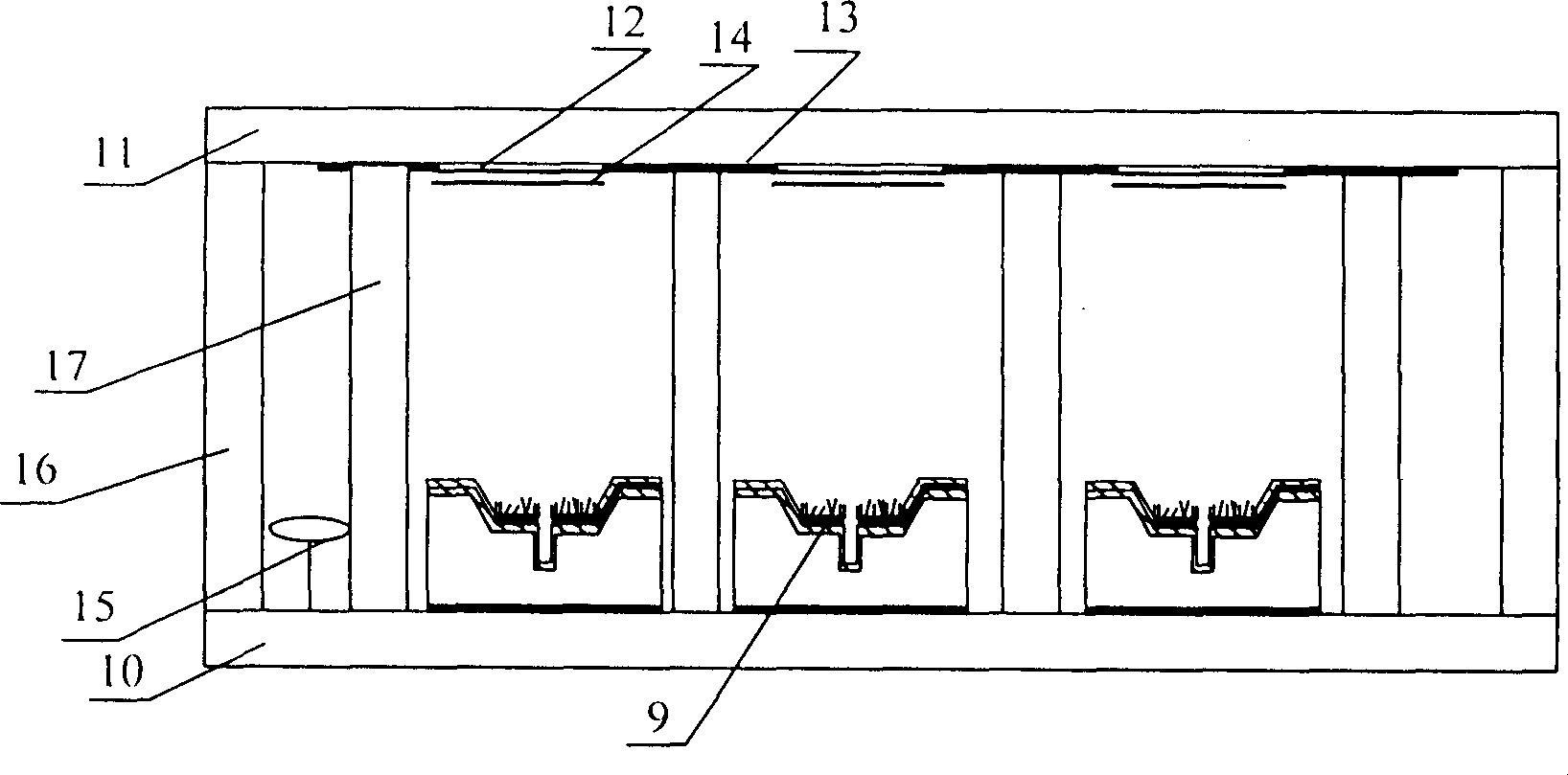

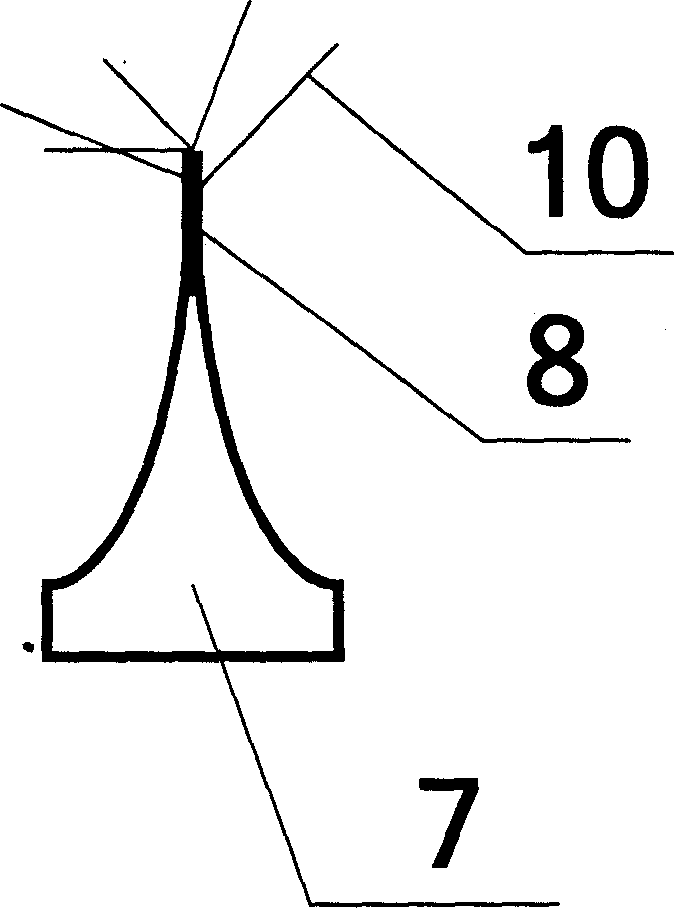

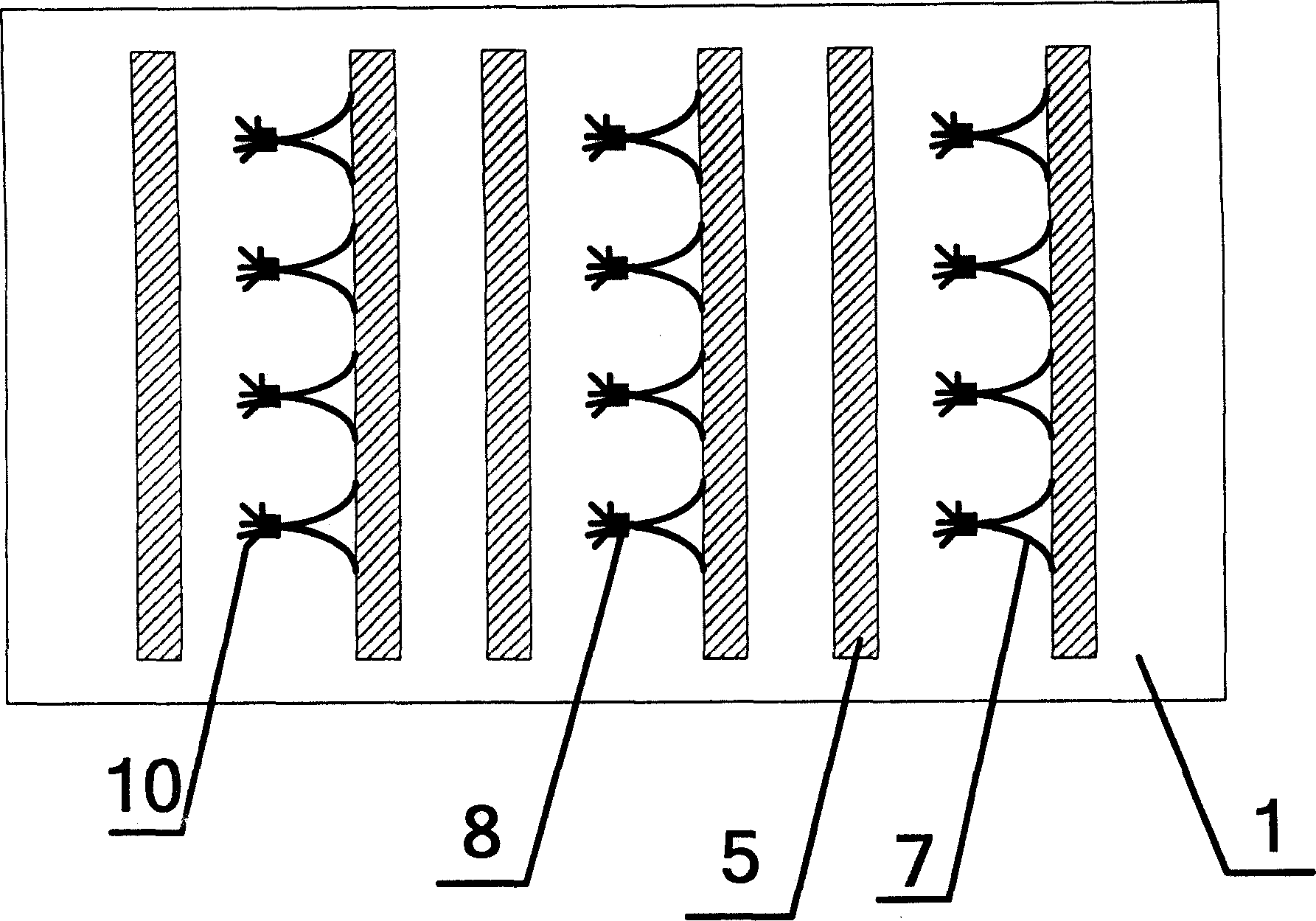

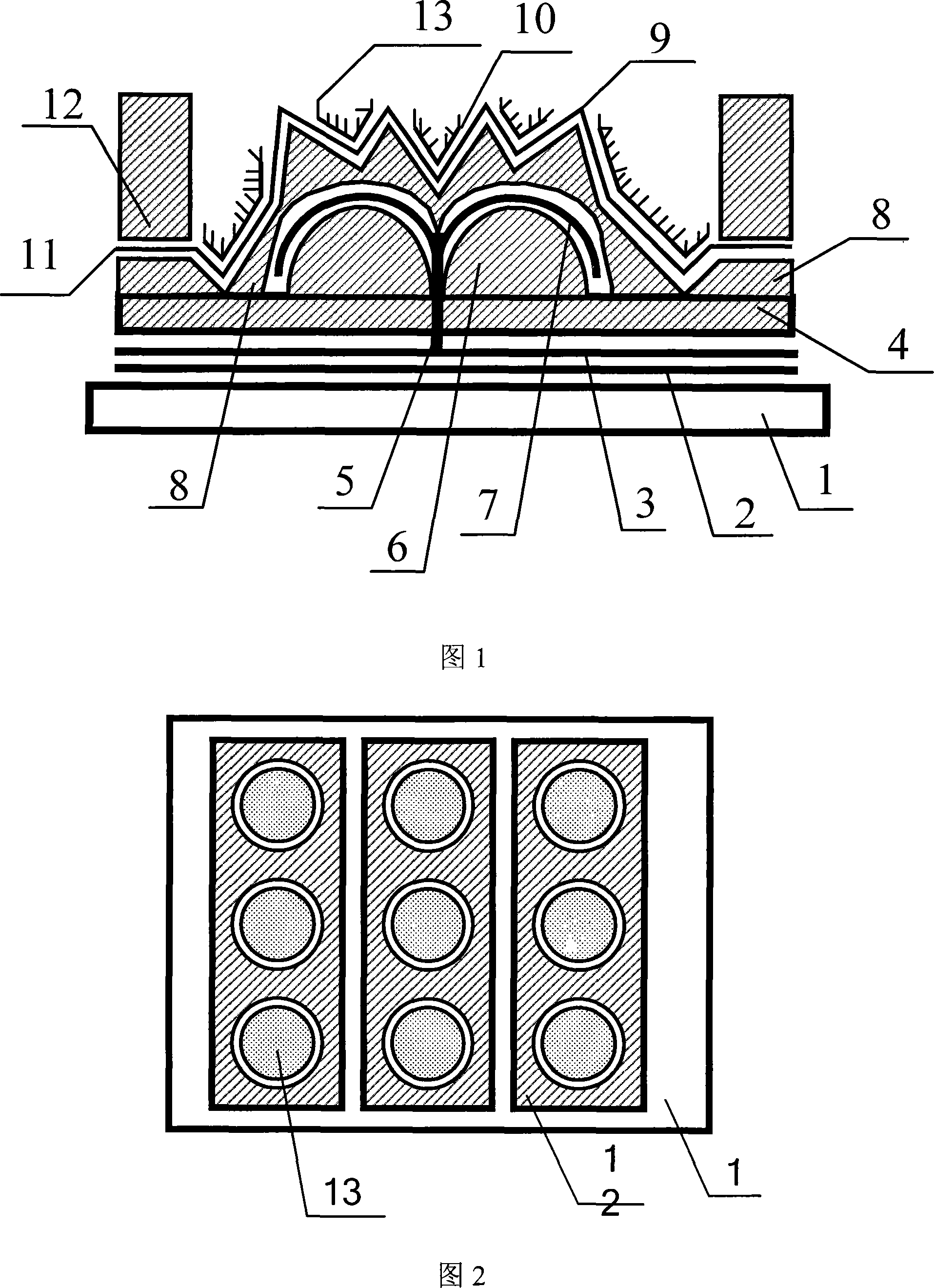

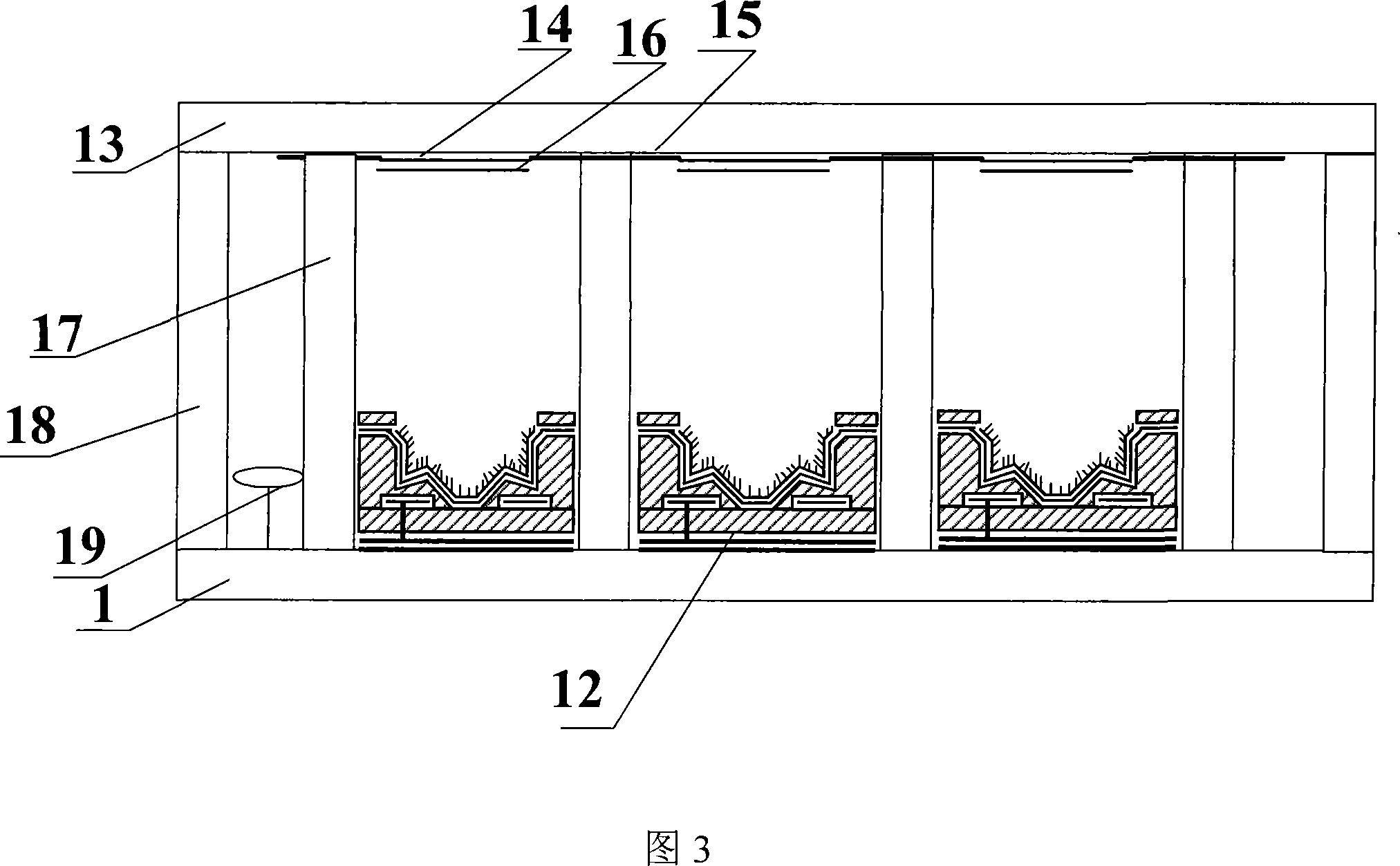

Flat-panel display device with branched side-bottom gate modulation structure and its preparing process

InactiveCN101071742AEasy to manufactureReduce manufacturing costControl electrodesImage/pattern display tubesCarbon nanotubeOptoelectronics

The invention relates to a flat-panel display of a forked side bottom grid-controlled structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and grid lead layer, carbon nanotube and forked side bottom grid-controlled structure on the cathode glass panel; and it can further increase operating current of anode and reduce operating voltage of grid structure, and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

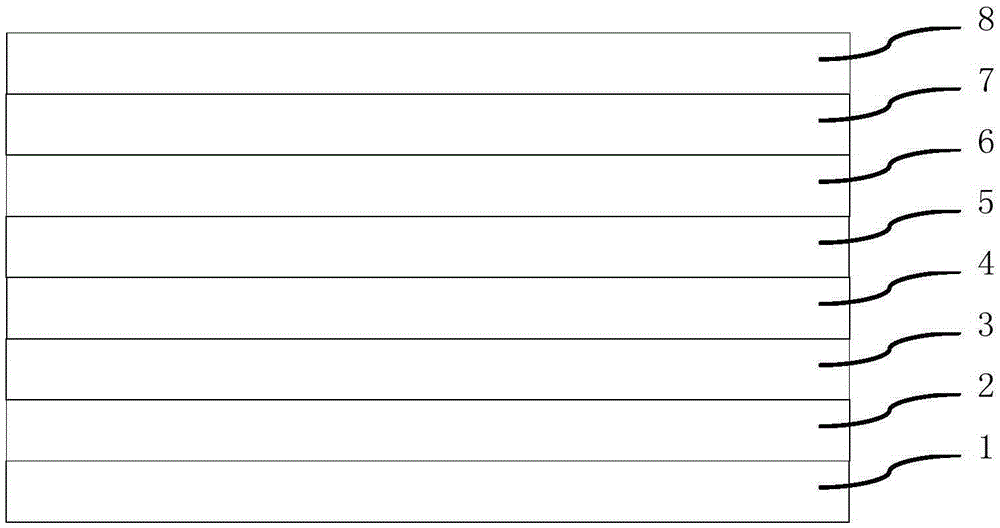

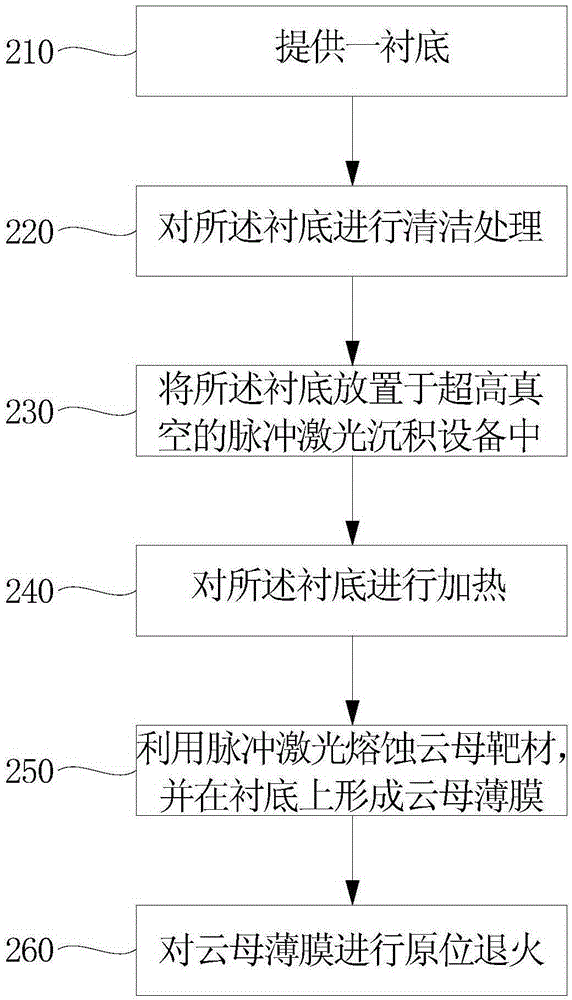

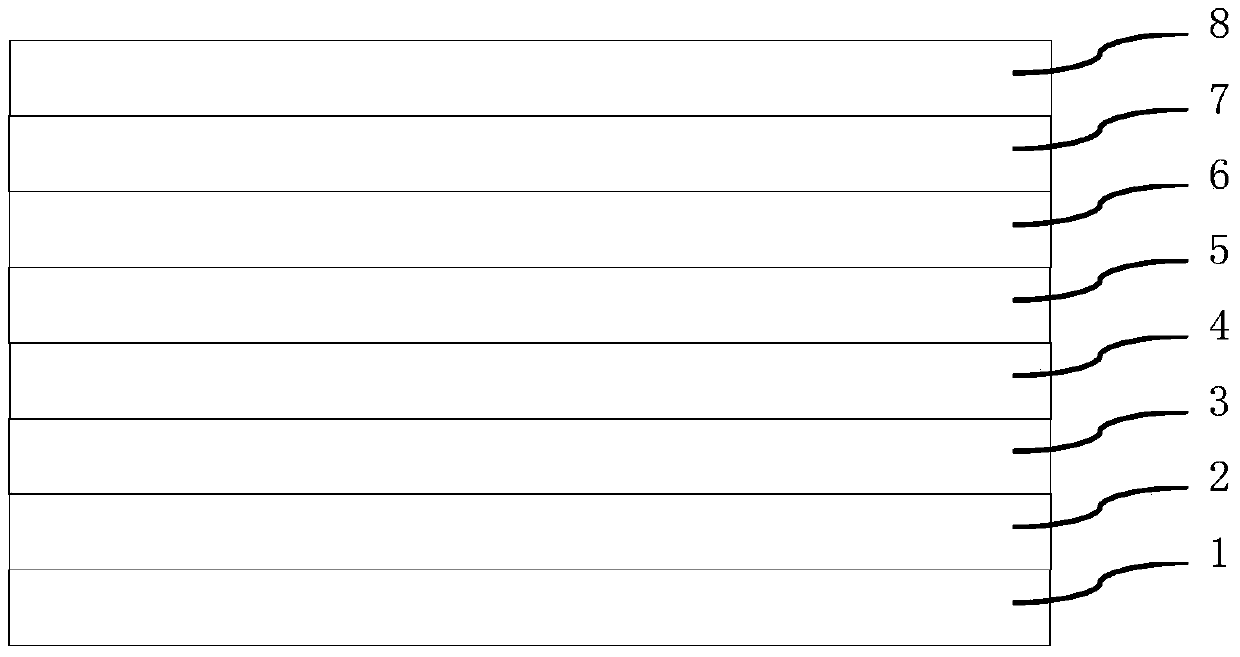

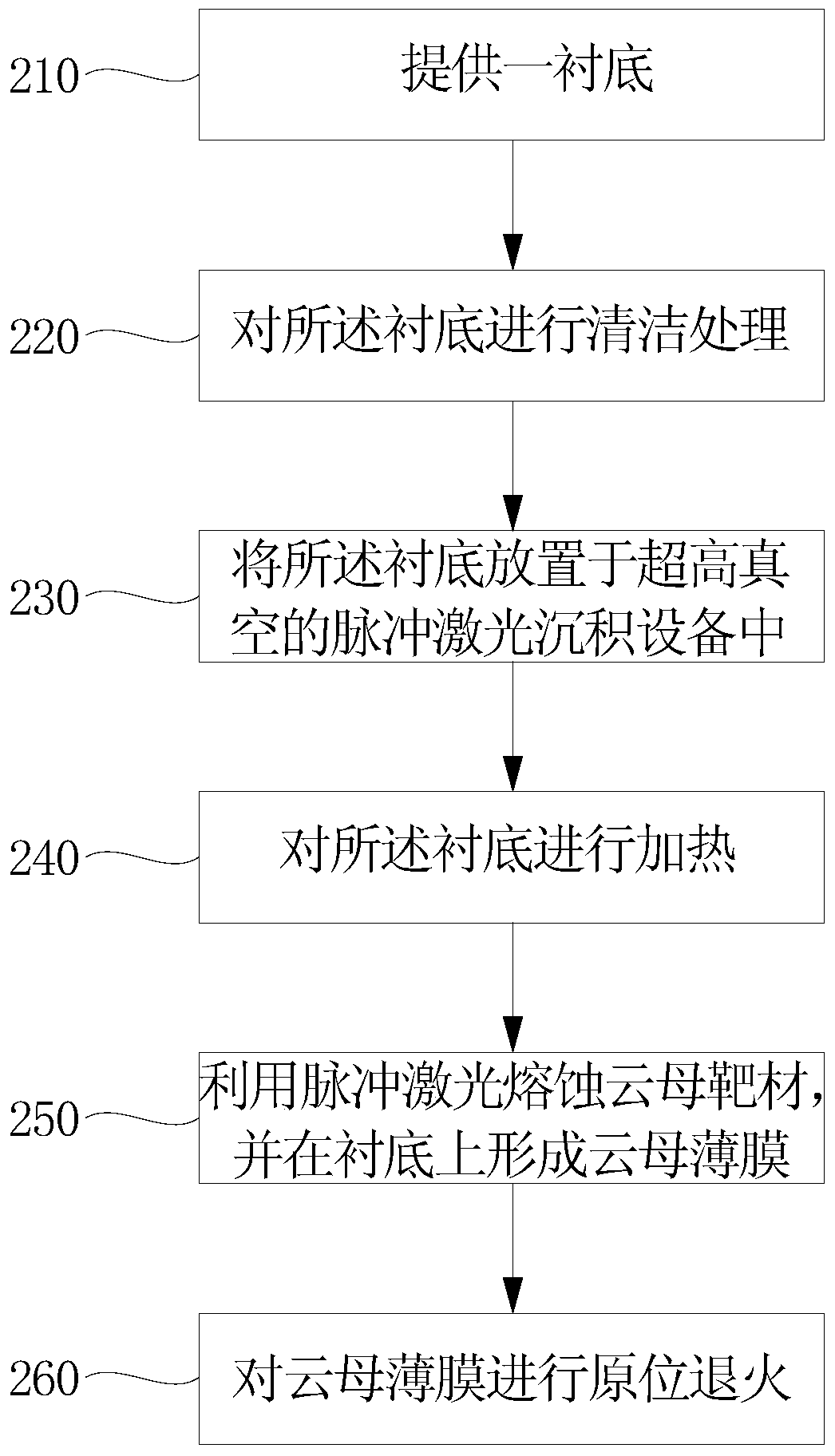

Preparation method of mica film and transistor

ActiveCN106601613AHigh carrier mobilityReduce gate currentSemiconductor/solid-state device manufacturingSemiconductor devicesMicaCharge carrier

The invention discloses a preparation method of a mica film. The method comprises that a substrate is placed in a vacuum pulse laser deposition device; and a mica target material is corroded by pulse laser so that the surface of the mica target material generates a plasma plume, and the plasma plume deposed on the substrate grows to form the uniform mica film. The invention also discloses a transistor which includes the mica film prepared by the preparation method. The mica film is introduced into the transistor and serves as a dielectric layer, and a layered 2D nano structure of mica is ultrathin, and is conducive to grid modulation of the transistor and high-density integration of the transistor in the vertical direction. In addition, the surface of the mica film is very smooth, carriers of the transistor can be avoided from influence of surface roughness and a trapping state, and the transistor can obtain a higher carrier mobility rate.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Flat-panel display device with two-sharp side gate-modulation structure and its preparing process

InactiveCN101071750AReflect control functionIncrease display brightnessControl electrodesImage/pattern display tubesDisplay deviceCarbon nanotube

The invention relates to a flat-panel display of a double-pointed side grid-controlled cathode structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and grid lead layer, carbon nanotube and double-pointed side grid-controlled cathode structure on the cathode glass panel; and it can enlarge electron emission area of carbon nanotube cathode and improve control function of grid and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with inclined-down gate-modulated flat cadhode structure and its preparing process

InactiveCN101071737AEmbodies powerful control functionsLow working voltageControl electrodesImage/pattern display tubesFluorescenceImage resolution

The invention relates to a flat-panel display of a tilted lower grid-controlled flat cathode structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; and grid lead layer, carbon nanotube and tilted lower grid-controlled flat cathode structure on the cathode glass panel; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and it can improve whole display brightness and resolution and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Planar display device with stair-shaped sided-grid controlled transmitting structure and its production

InactiveCN101075530AEmbodies powerful control functionsLow working voltageControl electrodesImage/pattern display tubesDisplay deviceCarbon nanotube

This is a flat displayer of step shape side grid cathode structure and its production process. It includes a sealed vacuum chamber formed by a anodic glass panel, a cathode glass panel and surrounded glass frame; on the anodic glass panel is a conducting layer coated with fluorescent; a supporting wall between the anodic and cathode panel and a getter; on the cathode glass panel are a grid down-lead layer, carbon nanotube and step shape side grid structure, which is capable of decreasing working voltage of the grid and increasing the control function and efficiency.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Transversing cathode emitting structural panel display device and its production technique

InactiveCN1909173AAvoid influenceHigh success rate of preparationControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

The invention relates to a plate display in transverse cathode emission structure and relative production, wherein it comprises an anode glass panel, a cathode glass panel, and a sealing vacuum chamber surrounded by four glass frames; the anode glass panel is arranged with anode conductive layer and a fluorescent powder layer is above the conductive layer; a support wall structure and a gattering additional element are between the anode glass panel and the cathode glass panel; a control grid, a carbon nanometer tube cathode and transverse cathode emission structure are arranged on the cathode glass panel; the carbon nanometer tube cathode is transverse, the grid is at the side of cathode to control the electron emission of cathode to improve the electron emission efficiency and reduce the working voltage, with lower cost and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat board display of bevel cathode side-grid controlled structure and mfg. process

InactiveCN1937155AAdd control functionIncrease display brightnessControl electrodesElectrode and associated part arrangementsPhosphorCarbon nanotube

The flat panel display includes cathode glass faceplate, anode glass faceplate, and sealed vacuum cavity surrounded by glass frame. There are cathode conductive layer, Nano carbon tubes, and side grid control structure of beveled cathode on the cathode glass faceplate. There are anode conductive layer and phosphor layers prepared on the conductive layer on anode glass faceplate. Structure of supporting wall and attached elements of getter are located between anode glass faceplate and cathode glass faceplate. The invention enhances control function of grid structure greatly, increases emission area and emission efficiency of cathode of Nano carbon tubes so as to be in favor of raising display brightness of whole apparatus further. Advantages are: stable and reliable manufacturing procedure, simple technique and structure, and low cost.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-board display of internal concave type grid-controlled array structure and mfg. process

InactiveCN1937146AReduce the chance of mutual contactIncrease display brightnessControl electrodesElectrode and associated part arrangementsImaging qualityDisplay device

The flat panel display includes cathode glass faceplate, anode glass faceplate, and sealed vacuum cavity surrounded by glass frame. There are cathode conductive layer, Nano carbon tubes, and inner concave formed structures of grid control array on the cathode glass faceplate. There are anode conductive layer and phosphor layers prepared on the conductive layer on anode glass faceplate. Structure of supporting wall and attached elements of getter are located between anode glass faceplate and cathode glass faceplate. The invention reduces working voltage of grid electrode further, enhances control function and control efficiency of grid electrode so as to be in favor of raising brightness and image quality displayed by the whole apparatus. Advantages are: stable and reliable manufacturing procedure, simple technique and structure, and low cost.

Owner:ZHONGYUAN ENGINEERING COLLEGE

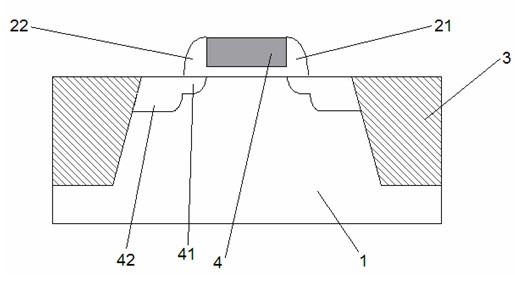

Method for reducing semiconductor device hot carrier injection damage

ActiveCN102437057AIncrease side wall widthReduced side wall widthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorElectric field

The invention provides a method for reducing the semiconductor device hot carrier injection damage. In a spacer etching process, an inclined angle introduction plasma etching method is adopted, so the spacer width of the drain end after the etching is increased, the spacer width of the source end is decreased, after the subsequent source and drain high doping injection and annealing process, the distance from doped ions of the drain end to a channel is enlarged, the distance from doped ions of the source end to the channel and a substrate is reduced, under the condition of keeping the effective channel length unchanged, and the longitudinal electric field intensity of the drain end is reduced, so the semiconductor device hot carrier injection damage is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

MOS element manufacturing method for reducing damage caused by hot carriers injection

InactiveCN102610502ASmall section widthAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a MOS element manufacturing method for reducing damage caused by hot carriers injection; a photoresist layer is formed on a lateral wall deposition layer above a drain region; a method that neutral ions process ion injection to the lateral wall deposition layer above a source region is used, thus, a cross section width of an etched source lateral wall is relatively small; and the cross section width of a drain lateral wall is relatively increased. When voltage is added to grid, the strength of a longitudinal electric field generated on the drain is weakened; therefore, holes of electronic hole pairs generated by carriers collision accelerated by a transverse electric field will be injected into the grid under the action of a relatively weak longitudinal electric field; thus, grid current formed by injecting the hot carrier is reduced; and damage of hot carriers injection of semiconductors is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

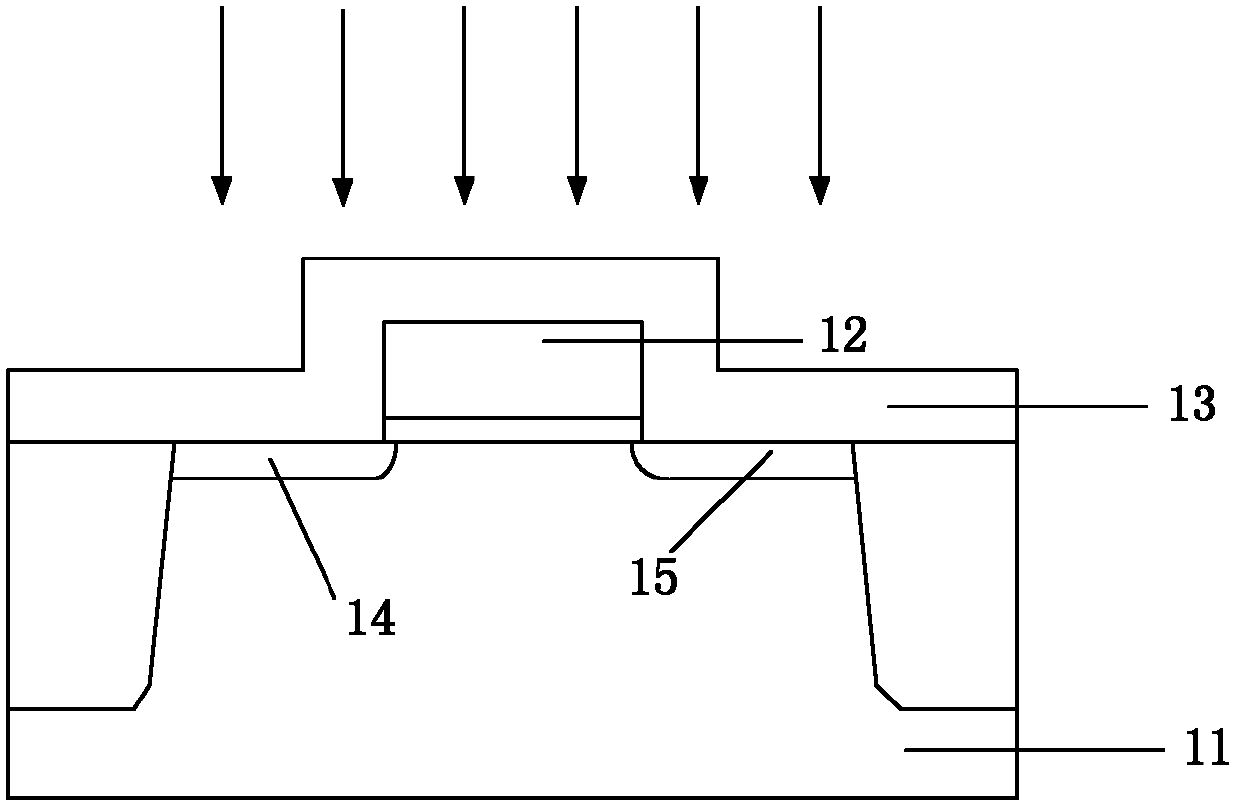

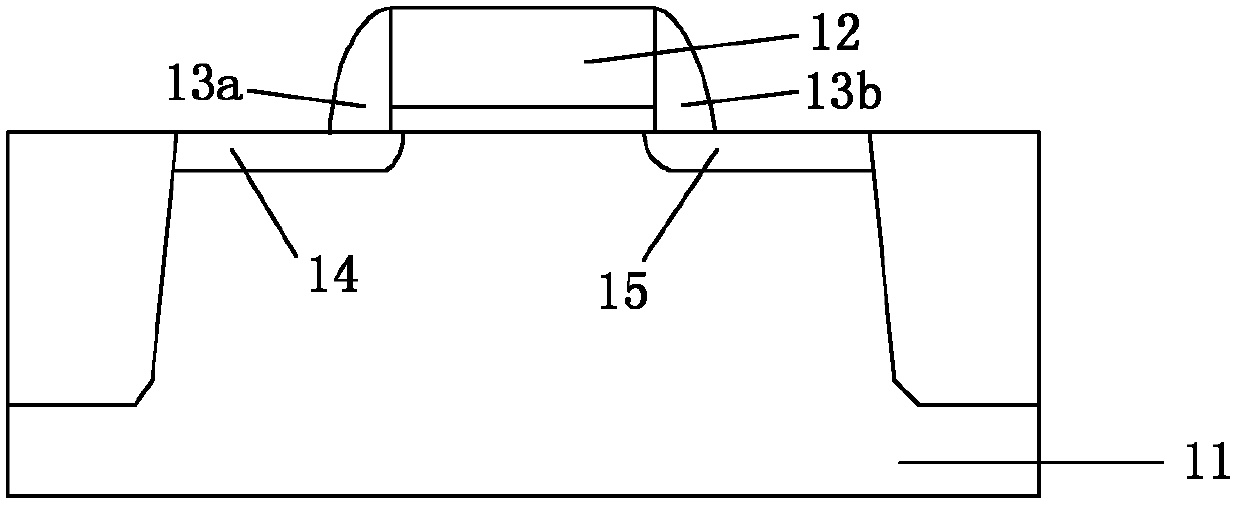

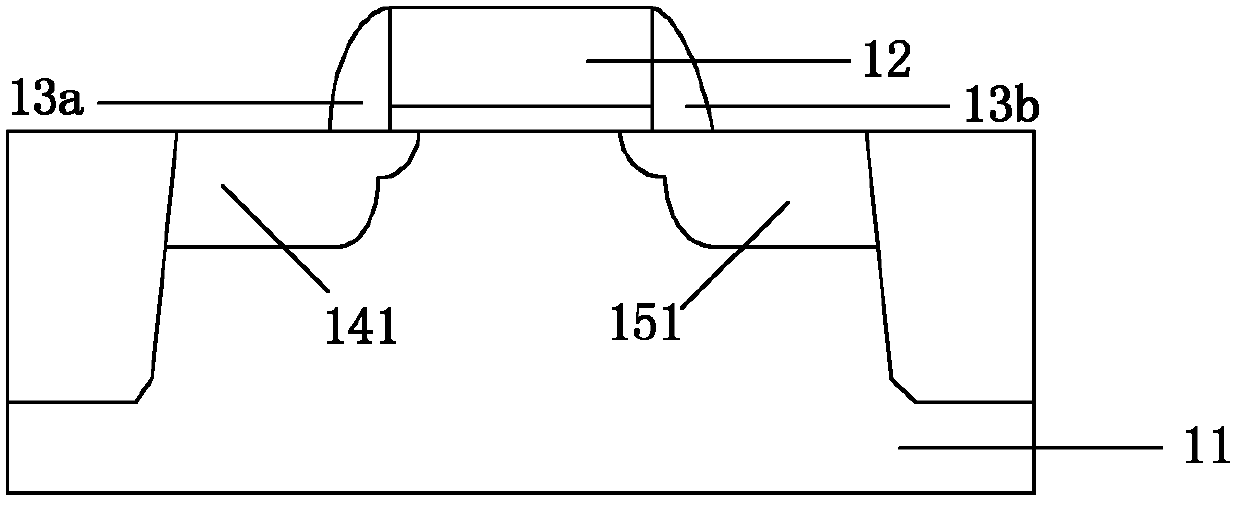

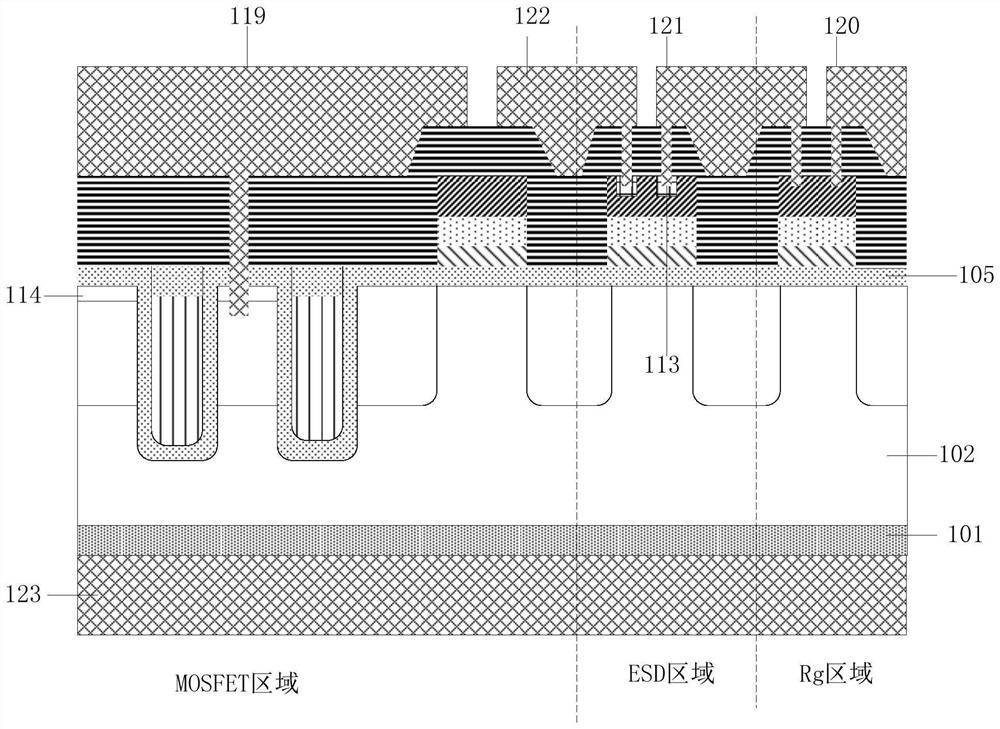

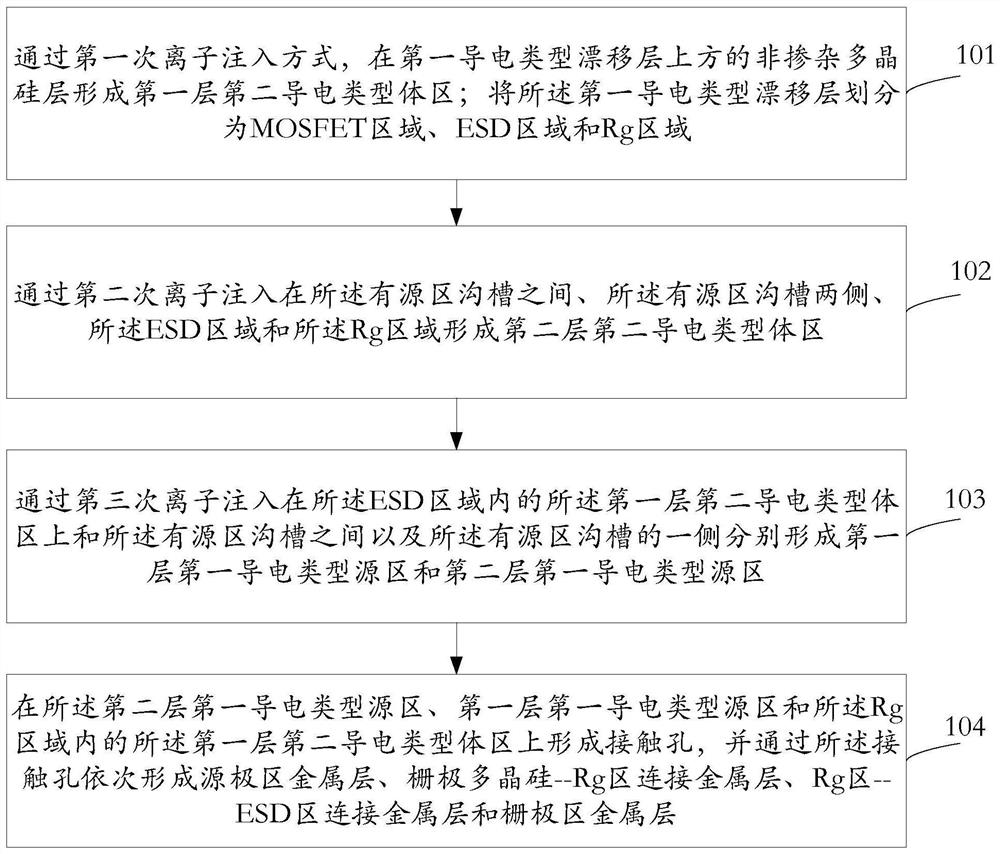

MOSFET device and preparation method thereof

PendingCN113764525APrevent breakdownReduce gate currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETField-effect transistor

The invention discloses an MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device and a preparation method, and relates to the field of semiconductor power devices. The anti-static and anti-impact capabilities of the grid electrode can be effectively enhanced, and the purpose of withstand voltage of the device is achieved by using the ESD polycrystalline silicon layer as a mask plate to block the injection of the P-type body region at the periphery. The method comprises the steps that active region grooves are formed in a first conduction type drift layer, a second layer of first conduction type source regions are arranged between the active region grooves and on one sides of the active region grooves, and the active region grooves are located in an MOSFET region; a first layer of second conductive type body region is arranged on the non-doped polycrystalline silicon layer in the MOSFET region; the non-doped polycrystalline silicon layer is arranged above the first conductive type drift layer; a first layer of second conductive type body region and a first layer of first conductive type source region are arranged on the non-doped polycrystalline silicon layer in the ESD region; a first layer of second conductive type body region is arranged on the non-doped polycrystalline silicon layer in the Rg region; and a second layer of second conductive type body region is arranged in the first conductive type drift layer.

Owner:华羿微电子股份有限公司

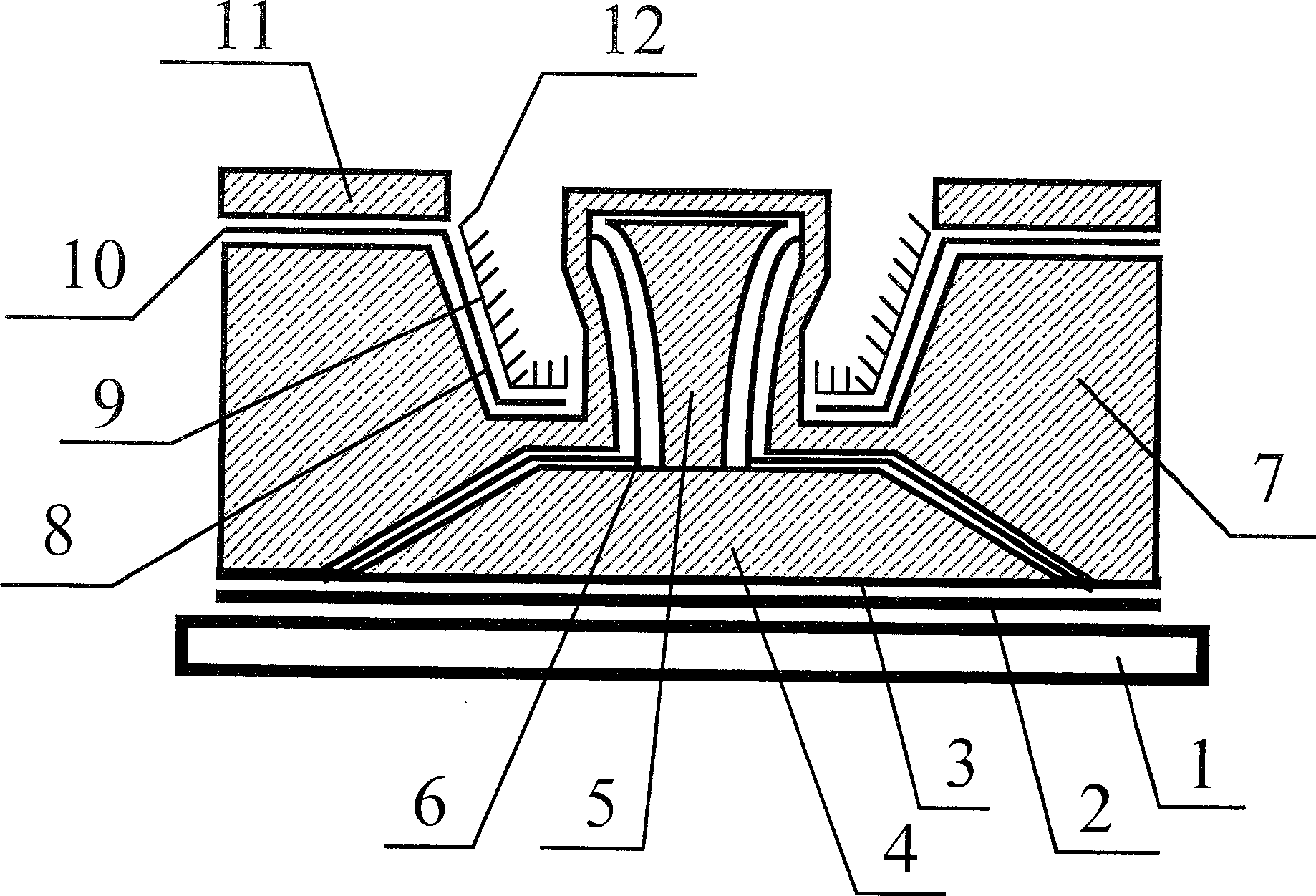

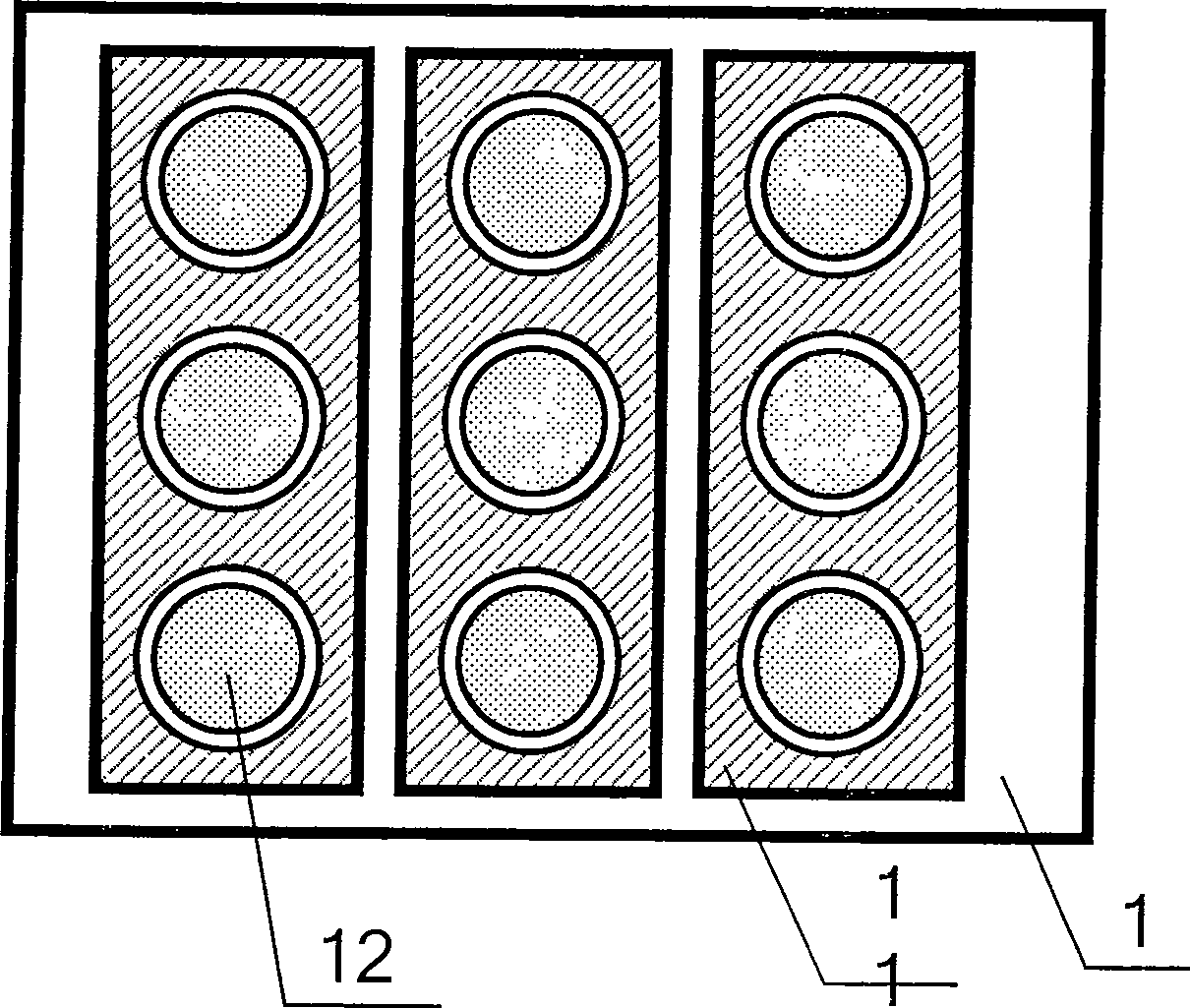

Planar display device with internal-concaved lowr-grid controlled stair cathode structure and its production

InactiveCN101075532BLaunch moreIncrease display brightnessControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

This is a flat displayer of step shape concave low grid cathode structure and its production process. It includes a sealed vacuum chamber formed by a anodic glass panel, a cathode glass panel and surrounded glass frame; on the anodic glass panel is a conducting layer coated with fluorescent; a supporting wall between the anodic and cathode panel and a getter; on the cathode glass panel are a griddown-lead layer, carbon nanotube and step shape concave low grid structure, which is capable of increasing the display quality and decreasing working voltage of the grid.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Preparation method of mica thin film and transistor

ActiveCN106601613BGood for gate modulationFacilitates high-density integrationSemiconductor/solid-state device manufacturingSemiconductor devicesNano structuringHigh density

The invention discloses a method for preparing a mica thin film, which comprises: placing a substrate in a vacuum pulsed laser deposition device; using a pulsed laser to ablate a mica target to generate a plasma plume on the surface of the mica target, the resulting The plasma plume is deposited on the substrate to form a uniform mica film. The invention also discloses a transistor, which includes the mica film prepared by the preparation method. The transistor of the present invention introduces the mica thin film as the dielectric layer, and because the layered two-dimensional nanostructure of the mica has an ultra-thin thickness, it is beneficial to gate modulation of the transistor and high-density integration of the transistor in the vertical direction. In addition, the surface of the mica film is very smooth, which makes the carriers of the transistor free from the influence of surface roughness and trap states, so that the transistor can obtain higher carrier mobility.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

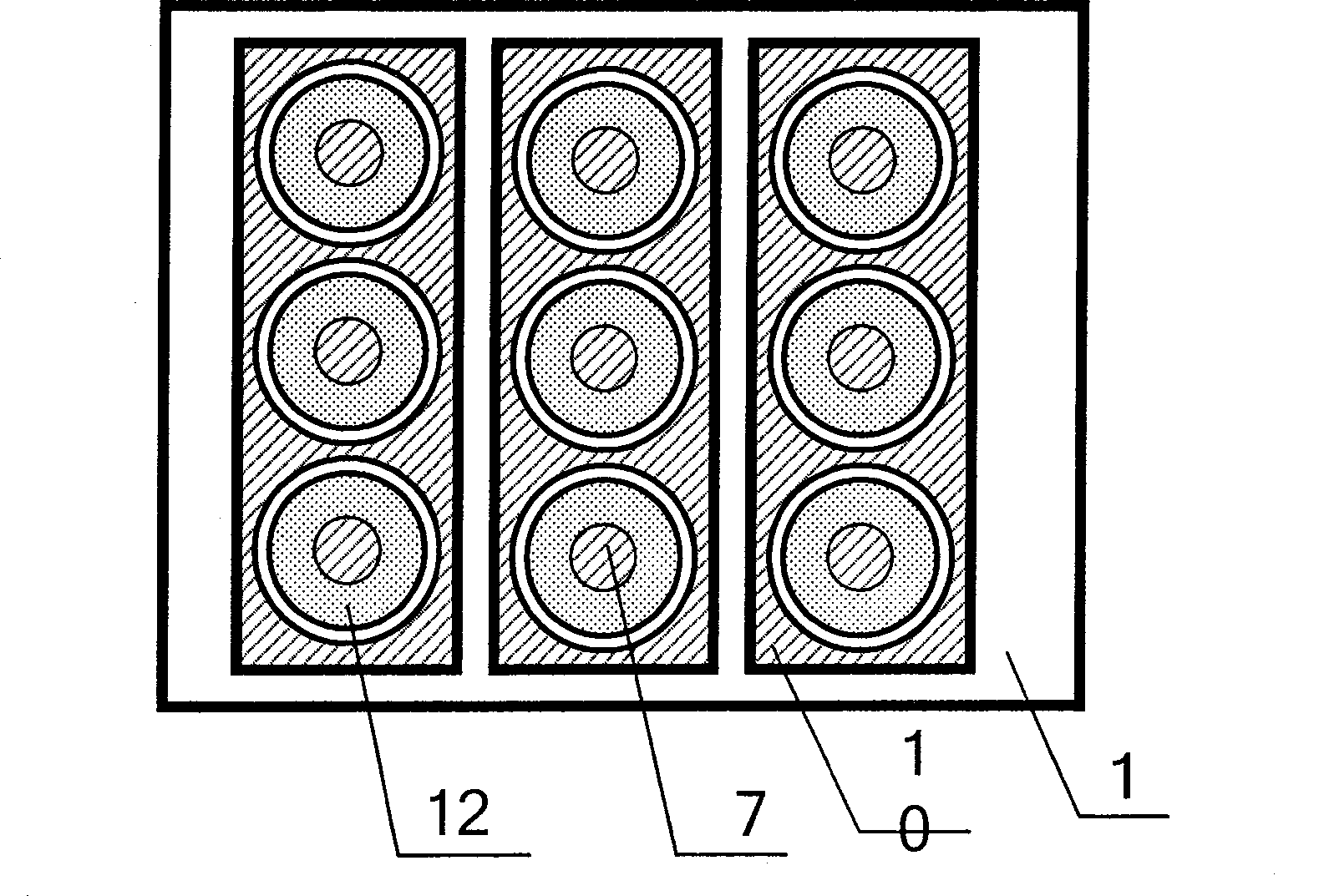

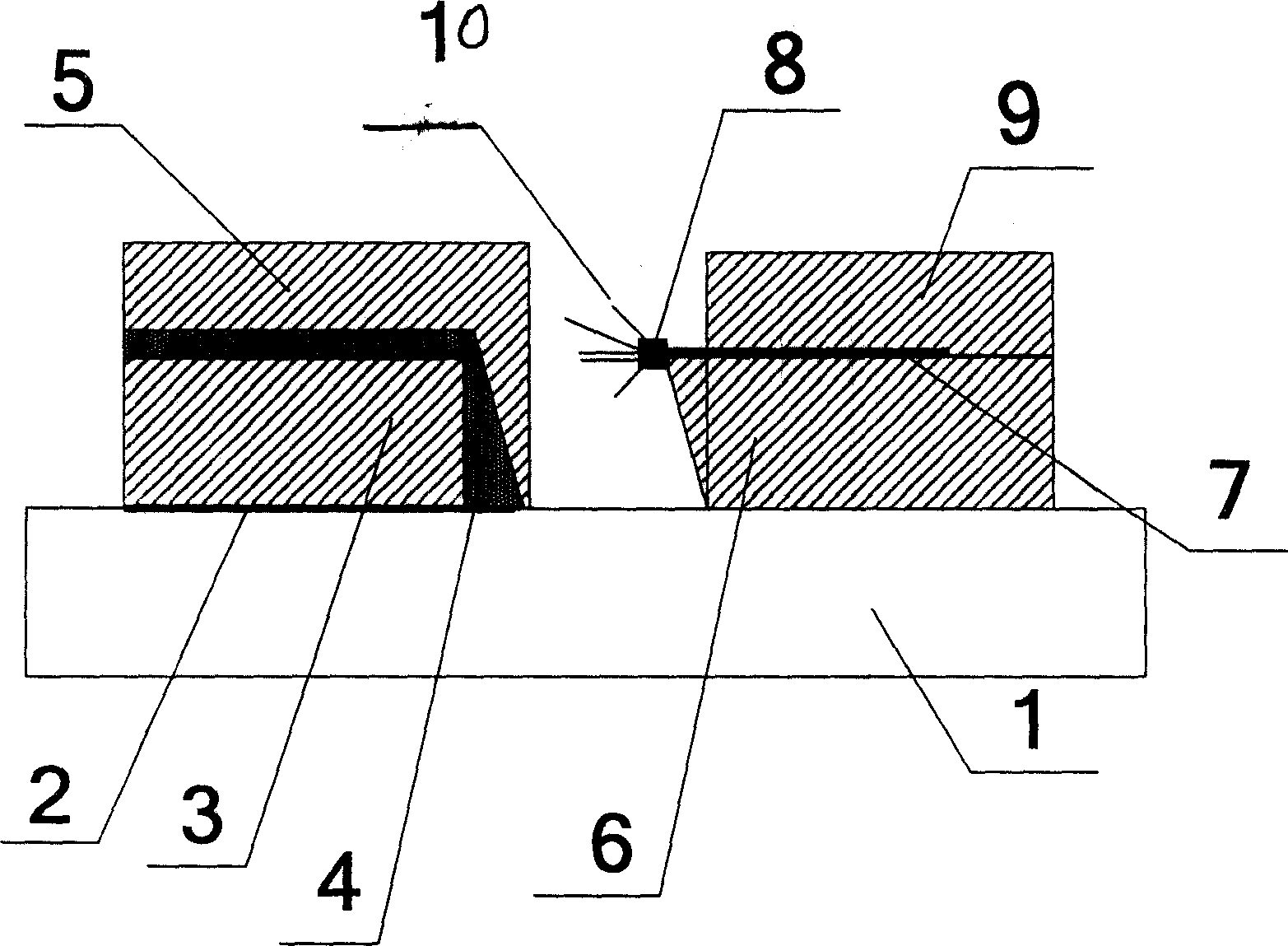

Flat-panel display device with oblique flat-gate structure and its preparing process

InactiveCN101071728AIncrease display brightnessReduce gate currentControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

The invention relates to a flat-panel display of a inclined-plane flat grid structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; cathode conducting layer, carbon nanotube and inclined-plane flat grid structure on the cathode glass panel; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel, and it can further improve control function of grid, reduce operating voltage of grid, and besides, raise electron emission efficiency and number of emitted electrons of carbon nanotube cathode, and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

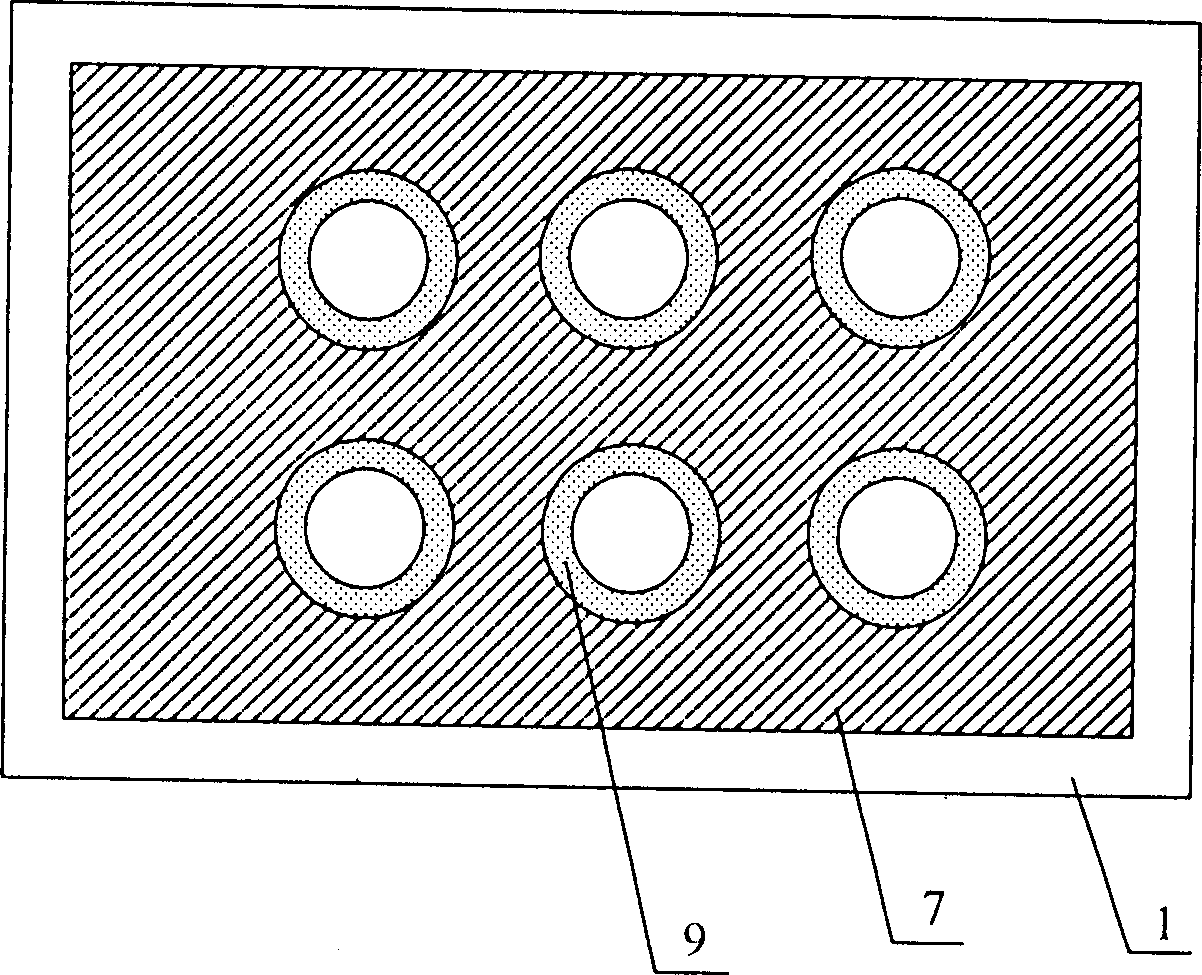

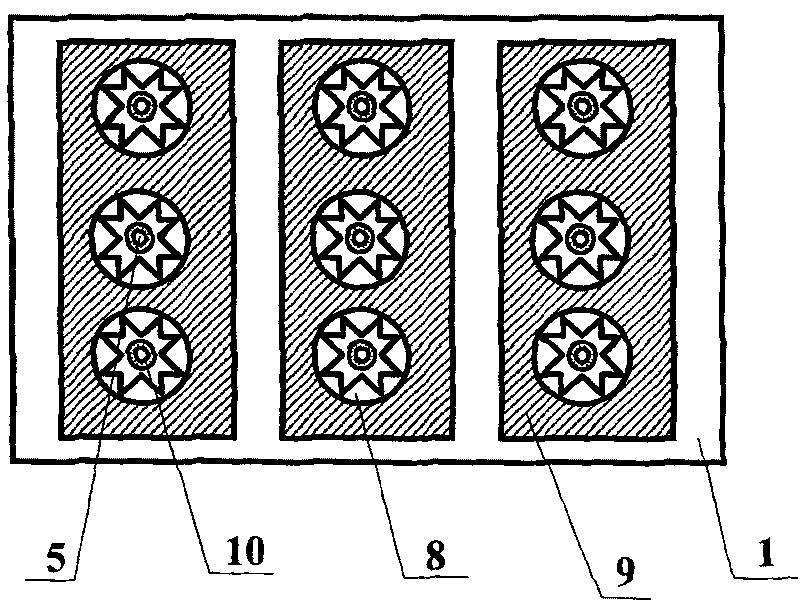

Planar display device with square opening bottom-grid controlled structure and its production

InactiveCN100561651CEmbodies powerful control functionsIncrease display brightnessControl electrodesImage/pattern display tubesDisplay deviceBottom gate

The invention relates to a flat panel display with an open square bottom grid control structure and its manufacturing process, comprising a sealed vacuum chamber composed of an anode glass panel, a cathode glass panel and surrounding glass frames; an anode conductive layer arranged on the anode glass panel And the phosphor layer prepared on the anode conductive layer; the support wall structure and getter accessory elements between the anode glass panel and the cathode glass panel, and the grid lead layer, carbon nanotubes and open squares are arranged on the cathode glass panel The bottom gate control structure can further increase the electron emission area of the carbon nanotube and reduce the working voltage of the grid structure, and has the advantages of stable and reliable manufacturing process, simple manufacturing process, low manufacturing cost and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-board display of three-tip fold-line type grid controlled array structure and mfg. process

InactiveCN1937147AAdd control functionLow working voltageControl electrodesElectrode and associated part arrangementsArray data structureImaging quality

The flat panel display includes cathode glass faceplate, anode glass faceplate, and sealed vacuum cavity surrounded by glass frame. There are cathode conductive layer, Nano carbon tubes, and polyline with three tips type structures of grid control array on the cathode glass faceplate. There are anode conductive layer and phosphor layers prepared on the conductive layer on anode glass faceplate. Structure of supporting wall and attached elements of getter are located between anode glass faceplate and cathode glass faceplate. The invention reduces working voltage of grid electrode further, decreases interval between grid electrode and cathode so as to be in favor of raising brightness and image quality displayed by the whole apparatus. Advantages are: stable and reliable manufacturing procedure, simple technique and structure, and low cost.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with internal gate-modulated multi-angle cathode structure and its preparing process

InactiveCN101071736AChanging the macroscopic surface shapeLow working voltageControl electrodesImage/pattern display tubesImaging qualityCarbon nanotube

The invention relates to a flat-panel display of an inner grid-controlled multiangular cathode structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and cathode lead layer, carbon nanotube and inner grid-controlled multiangular cathode structure on the cathode glass panel; and it can improve display brightness and image quality and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Planar display device with pallet bottom-grid controlled structure and its production

InactiveCN100561653CPowerful strong controlIncrease working currentControl electrodesImage/pattern display tubesCarbon nanotubeDisplay device

The invention relates to a flat-panel display with a tray-type bottom grid control structure and its manufacturing process, comprising a sealed vacuum chamber composed of an anode glass panel, a cathode glass panel and surrounding glass frames; an anode conductive layer arranged on the anode glass panel And the phosphor layer prepared on the anode conductive layer; the support wall structure between the anode glass panel and the cathode glass panel and the accessory components of the getter; the grid lead layer, carbon nanotubes and tray type are arranged on the cathode glass panel Bottom gate control structure; it can further increase the electron emission quantity and electron emission efficiency of the carbon nanotube cathode, improve the display brightness of the overall device, and has the advantages of stable and reliable manufacturing process, simple manufacturing process, low manufacturing cost and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Planar display device with triangular bottom-grid controlled cathode structure and its production

InactiveCN101075537ADemonstrate strong controlLow working voltageControl electrodesImage/pattern display tubesDisplay deviceFlat panel display

This is a flat displayer of triangle shape low grid cathode structure and its production process. It includes a sealed vacuum chamber formed by a anodic glass panel, a cathode glass panel and surrounded glass frame; on the anodic glass panel is a conducting layer coated with fluorescent; a supporting wall between the anodic and cathode panel and a getter; on the cathode glass panel are a grid down-lead layer, carbon nanotube and triangle shape low grid structure, which is capable of increasing the control function and efficiency of the grid, and increasing the electron ejecting area of the nanotube and display brightness.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with semi-trapezoidal tilt gate-modulated emission structure and its preparing process

InactiveCN101071743BEmbodies powerful control functionsReduce capacitive effectControl electrodesImage/pattern display tubesImaging qualityDisplay device

The invention relates to a flat-panel display of a semi-trapezoidal tilted grid-controlled emission structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and cathode lead layer, carbon nanotube and semi-trapezoidal tilted grid-controlled emission structure on the cathode glass panel; and it can further raise electron emission efficiency of carbon nanotube cathode, and improve whole image quality, and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Hackle sidegrid-controlled structure panel display and its manufacturing method

InactiveCN1971831BIncreased electron emission areaIncrease display brightnessControl electrodesElectrode and associated part arrangementsGratingFluorescence

This invention relates to one gear grating control plane display process, which comprises the following parts: cathode glass panel, cathode glass panel and circle glass frame to form sealed vacuum chamber; fluorescence layer on anode electrode layer with anode conductive layer on anode glass panel; supportive wall structure and air detrained assistant elements between anode glass panel and cathodeglass panel; control grating electrode, carbon nanometer tube cathode and emission structure on cathode glass panel.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with side gate-modulated round-top cathode type emitting structure and its preparing process

InactiveCN101071735AIncrease the launch areaImprove display image qualityImage/pattern display tubesDischarge tube/lamp detailsImaging qualityImage resolution

The invention relates to a flat-panel display of a side grid-controlled circular truncated cone surface cathode emission structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and cathode lead layer, carbon nanotube and side grid-controlled circular truncated cone surface cathode emission structure on the cathode glass panel; and it can further improve whole display brightness, image quality and resolution and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with ring-gate modulated valley cathode structure and its preparing process

InactiveCN101071741ALow working voltageIncrease the launch areaControl electrodesImage/pattern display tubesCarbon nanotubeOptoelectronics

The invention relates to a flat-panel display of an annular grid-controlled valley mouth-type cathode structure and the making process thereof, comprising: sealed vacuum cavity composed of anode glass panel, cathode glass panel, and peripheral glass frame; anode conducting layer on the anode glass panel and fluorescent powder layer prepared on the anode conducting layer; supporting wall structure and degassing agent auxiliary component between the anode glass panel and cathode glass panel; and grid lead layer, carbon nanotube and annular grid-controlled valley mouth-type cathode structure on the cathode glass panel; and it can further improve whole displayed image quality and reduce operating voltage of grid, and has advantages of stable and reliable making course, simple making process, low making cost, and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-board display of round grid side-wall emitting structure and mfg. process

InactiveCN1937152AIncrease display brightnessIncrease the launch areaControl electrodesElectrode and associated part arrangementsDisplay deviceCarbon nanotube

The flat panel display includes cathode glass faceplate, anode glass faceplate, and sealed vacuum cavity surrounded by glass frame. There are cathode conductive layer, Nano carbon tubes, and sidewall emission structure of round grid on the cathode glass faceplate. There are anode conductive layer and phosphor layers prepared on the conductive layer on anode glass faceplate. Structure of supporting wall and attached elements of getter are located between anode glass faceplate and cathode glass faceplate. The invention increases electronic field-emission area of cathode of Nano carbon tubes, electronic emission efficiency, and enhances control function of grid electrode so as to be in favor of raising display brightness of apparatus further. Advantages are: stable and reliable manufacturing procedure, simple technique and structure, and low cost.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Flat-panel display device with side gate-modulated round-top cathode type emitting structure and its preparing process

InactiveCN100527343CIncrease the launch areaImprove display image qualityImage/pattern display tubesDischarge tube/lamp detailsImaging qualityImage resolution

The invention relates to a flat-panel display with side-grid-controlled circular mesa cathode emission structure and its manufacturing process, including a sealed vacuum chamber composed of an anode glass panel, a cathode glass panel and surrounding glass frames; An anode conductive layer and a phosphor layer prepared on the anode conductive layer; a support wall structure between the anode glass panel and the cathode glass panel and an accessory component of the getter; a cathode lead layer, carbon nanotubes and The side-gate-controlled circular mesa cathode emission structure can further improve the display brightness, display image quality and resolution of the overall device; it has the advantages of stable and reliable manufacturing process, simple manufacturing process, low manufacturing cost and simple structure.

Owner:ZHONGYUAN ENGINEERING COLLEGE

Hackle sidegrid-controlled structure panel display and its manufacturing method

InactiveCN1971831AIncreased electron emission areaIncrease display brightnessControl electrodesElectrode and associated part arrangementsGratingFluorescence

This invention relates to one gear grating control plane display process, which comprises the following parts: cathode glass panel, cathode glass panel and circle glass frame to form sealed vacuum chamber; fluorescence layer on anode electrode layer with anode conductive layer on anode glass panel; supportive wall structure and air detrained assistant elements between anode glass panel and cathode glass panel; control grating electrode, carbon nanometer tube cathode and emission structure on cathode glass panel.

Owner:ZHONGYUAN ENGINEERING COLLEGE