Patents

Literature

49 results about "Sequential programming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Sequential programming means that a program operates sequentially, meaning one instruction at a time in a linear sequence, as opposed to it operating in parallel.

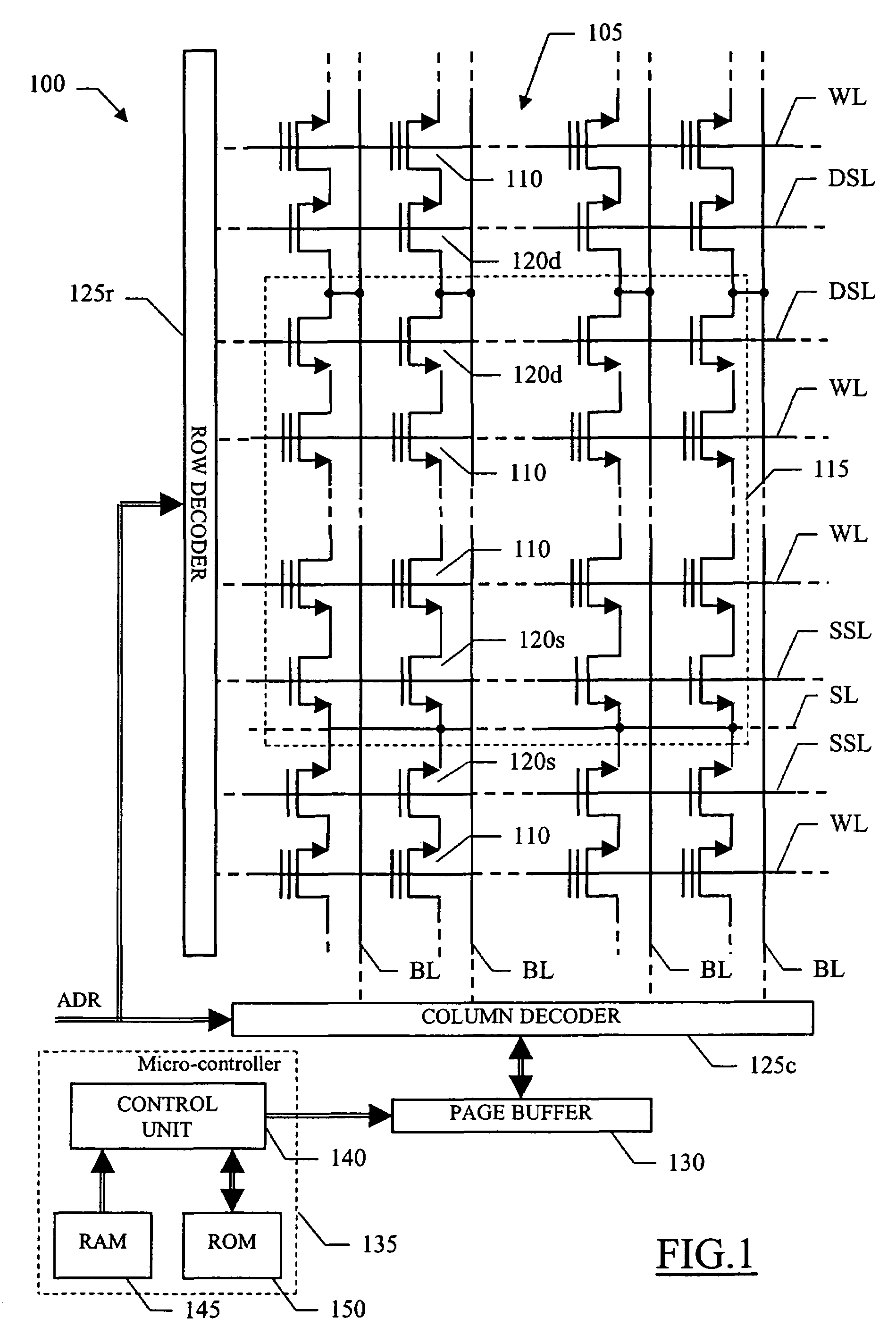

Multi-pass programming for memory with reduced data storage requirement

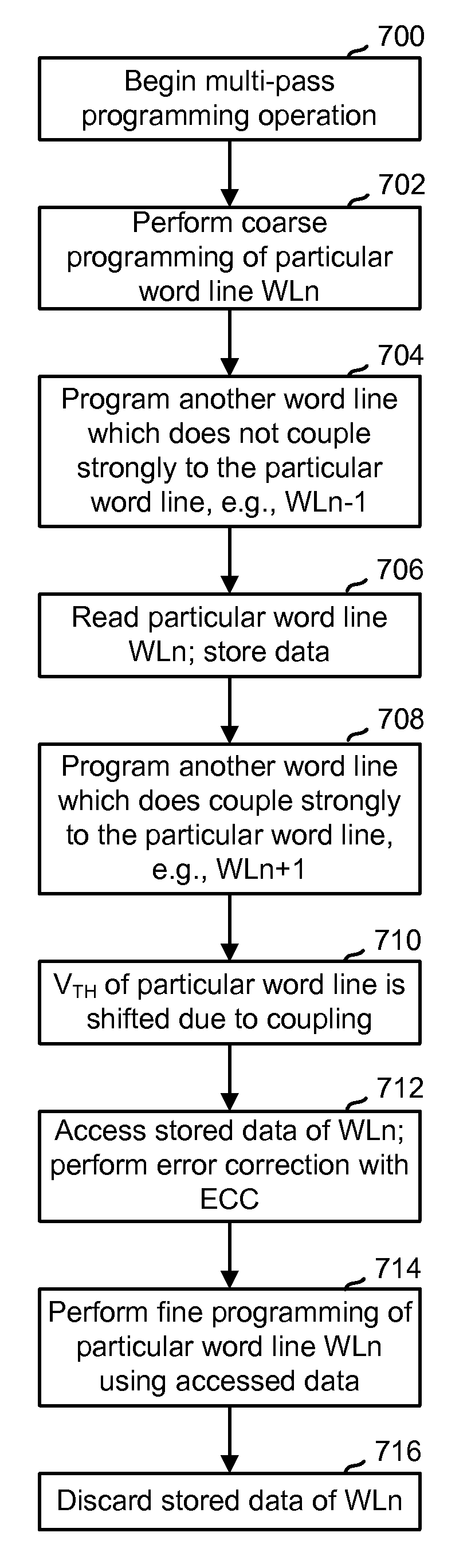

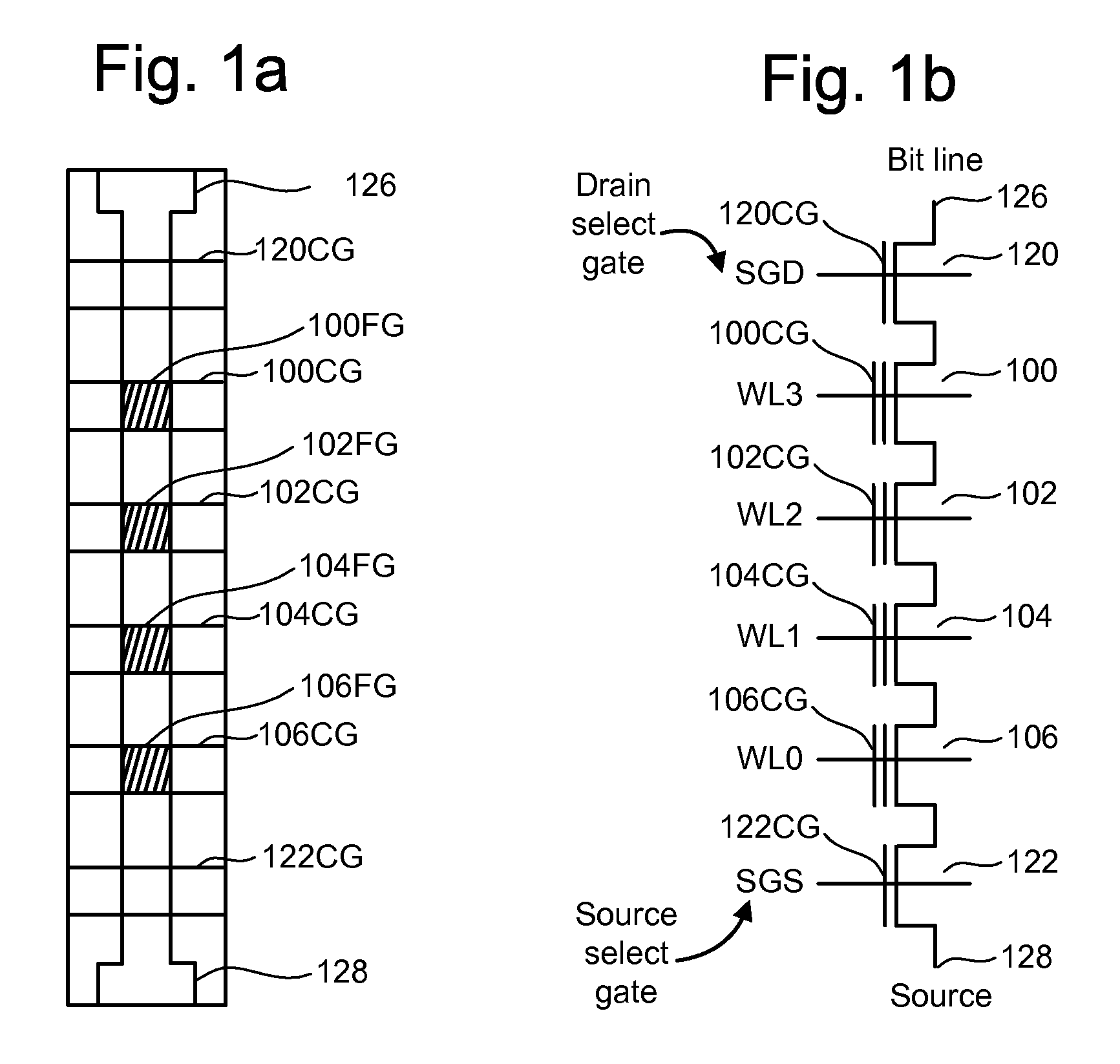

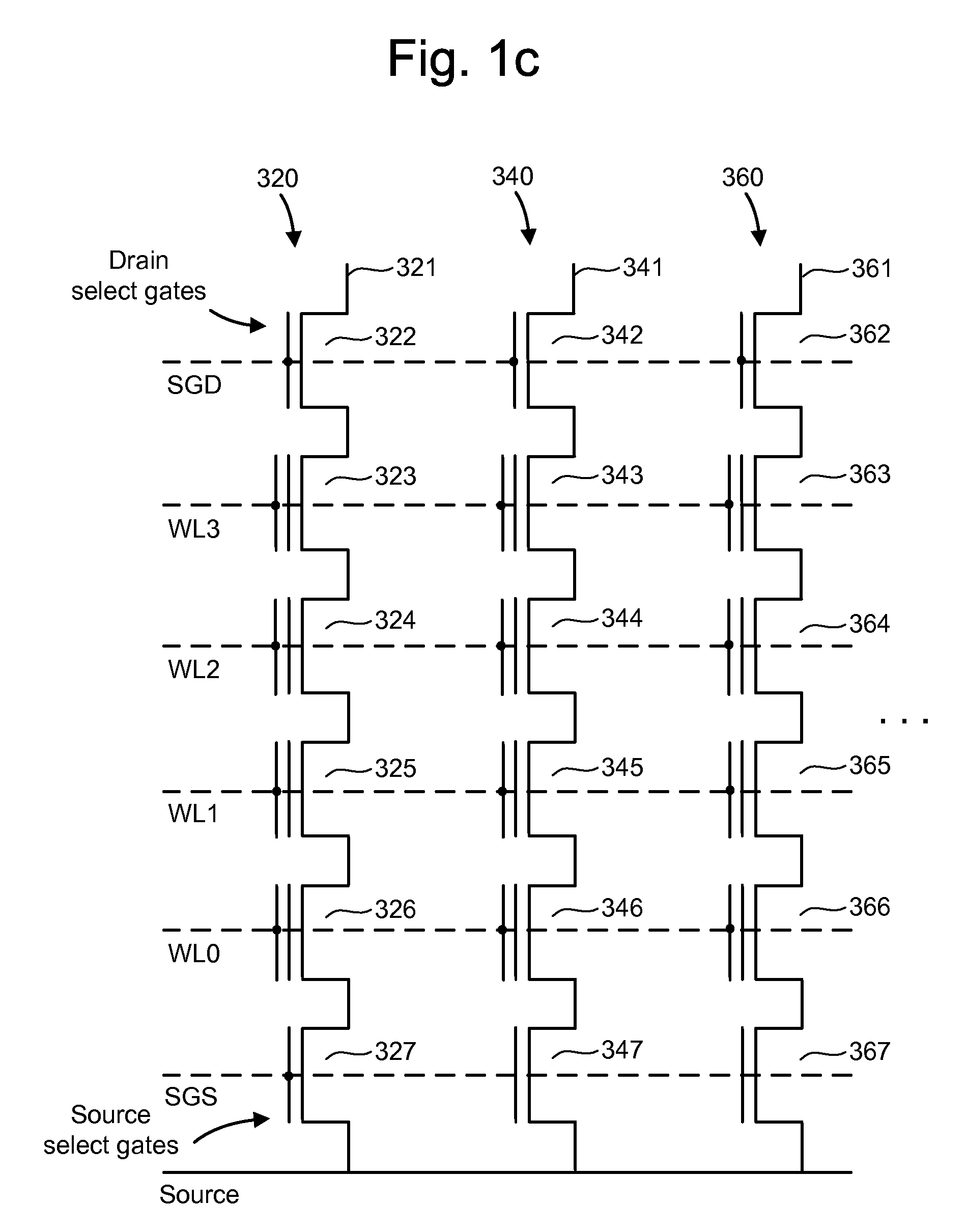

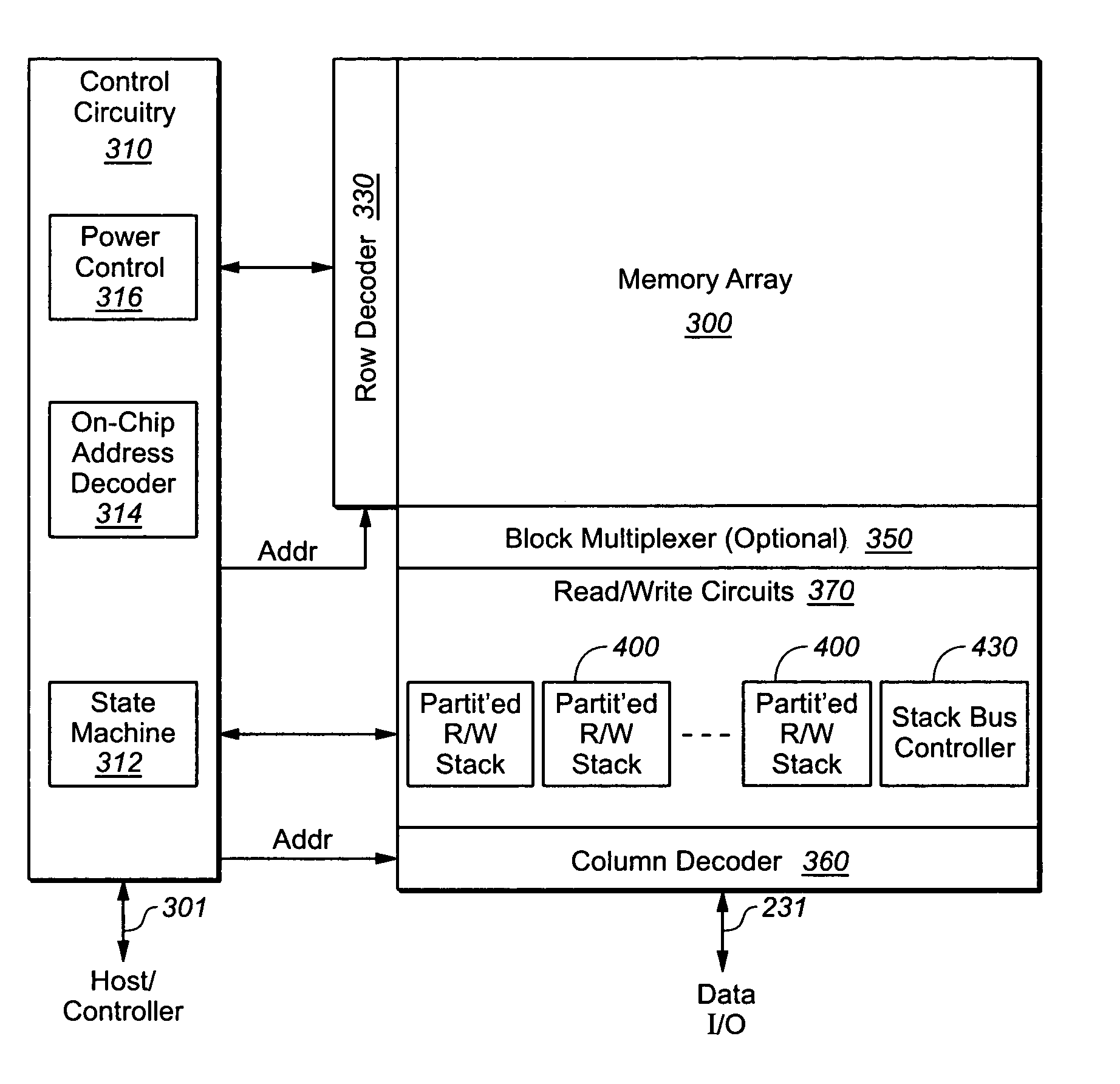

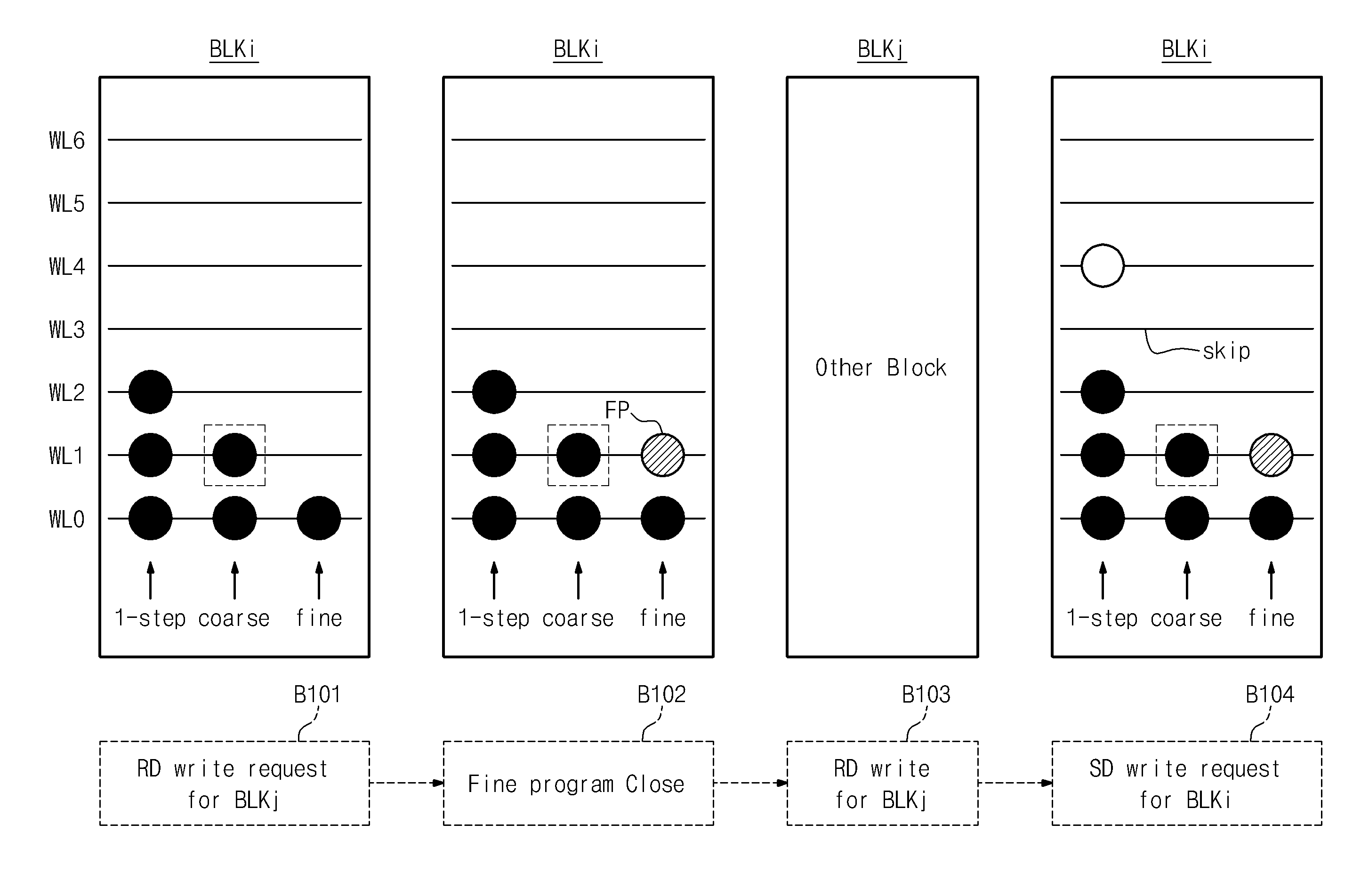

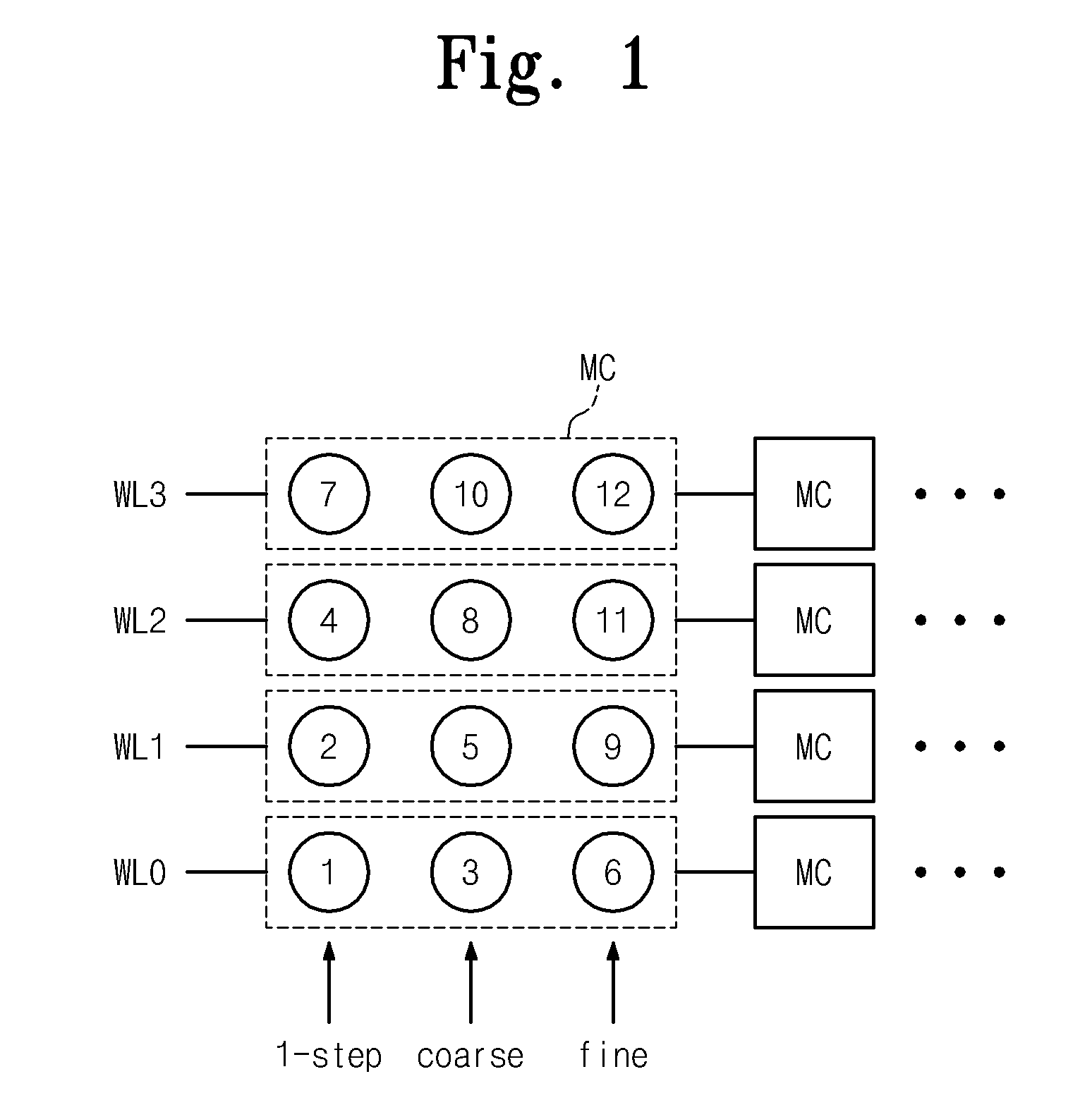

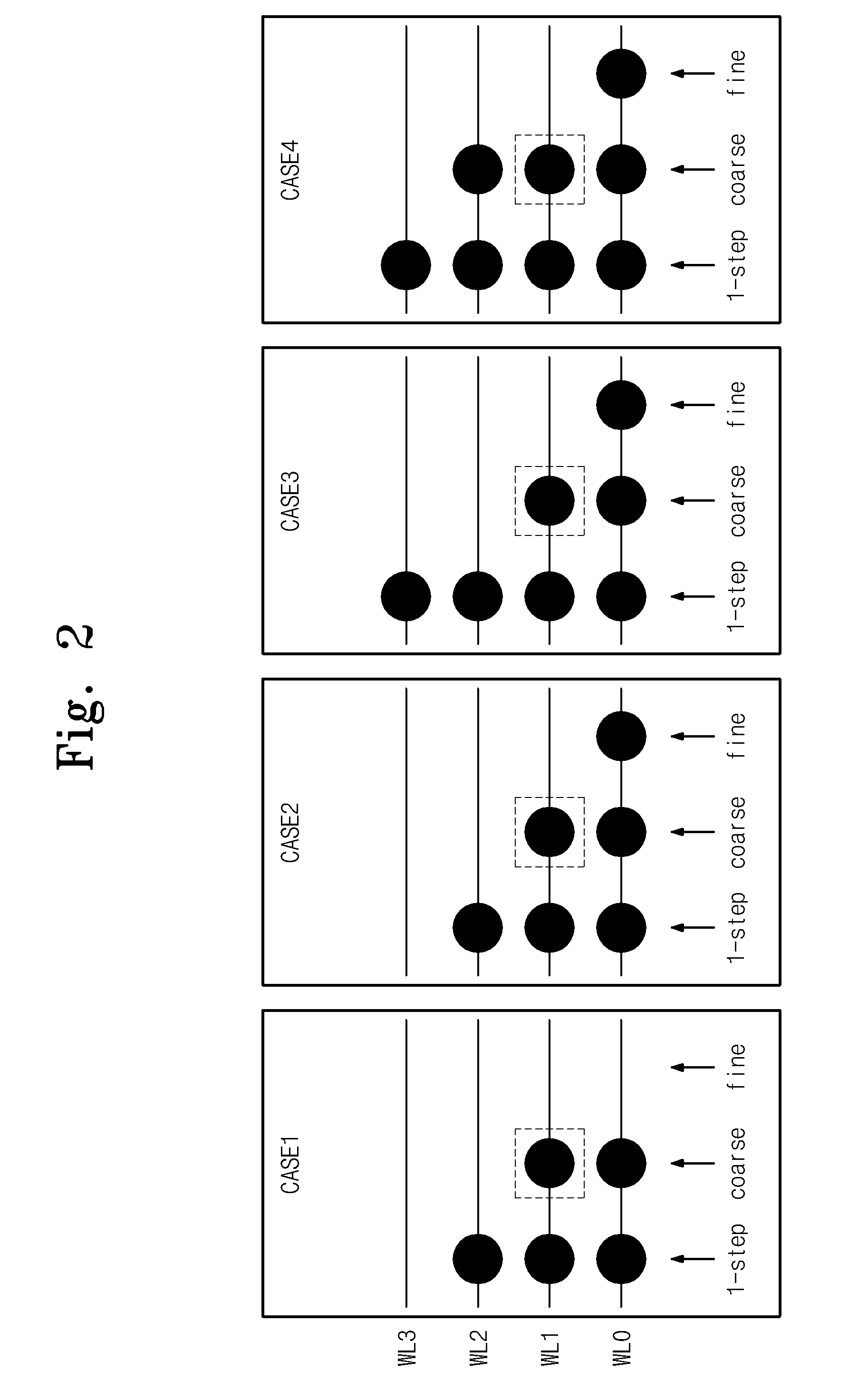

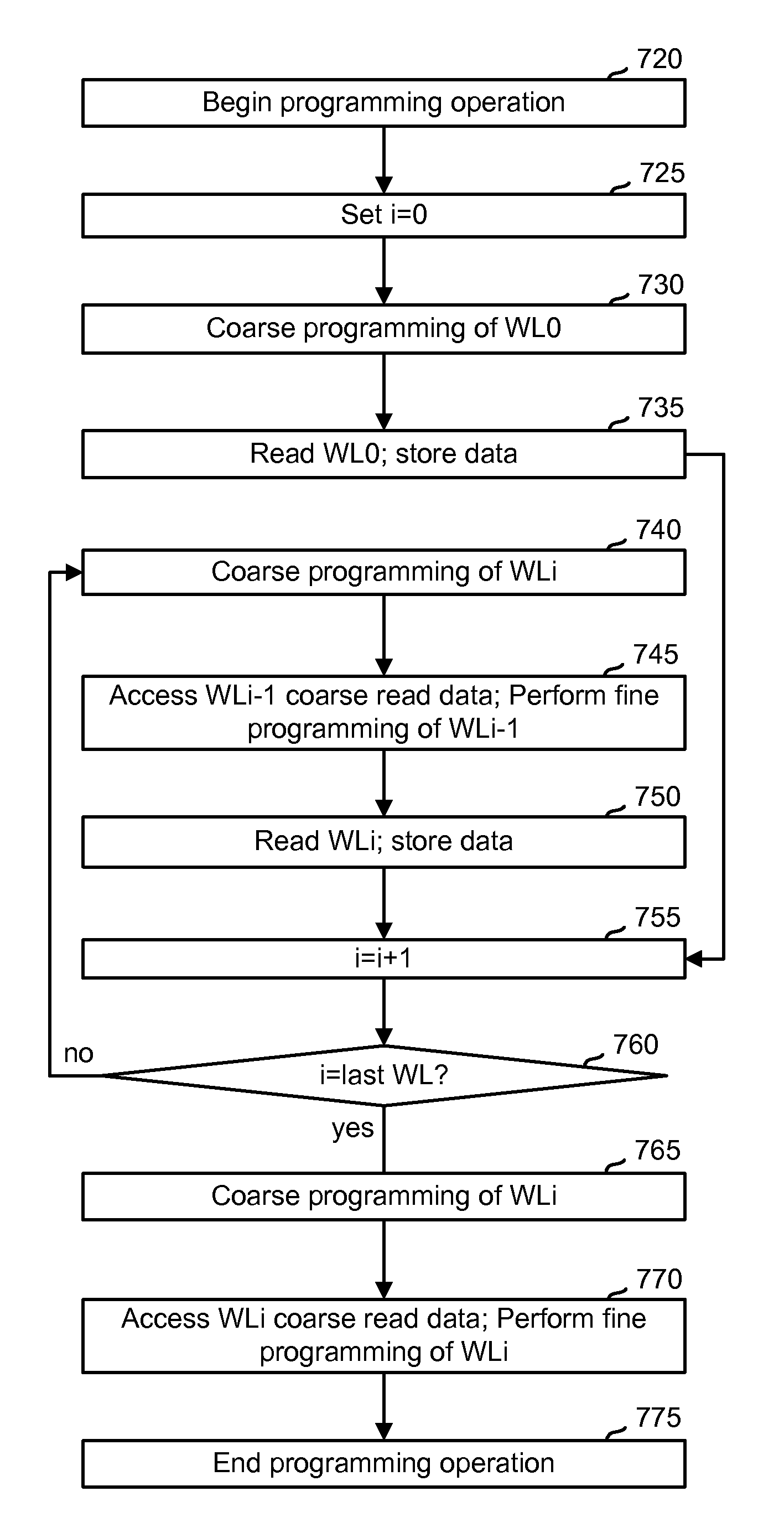

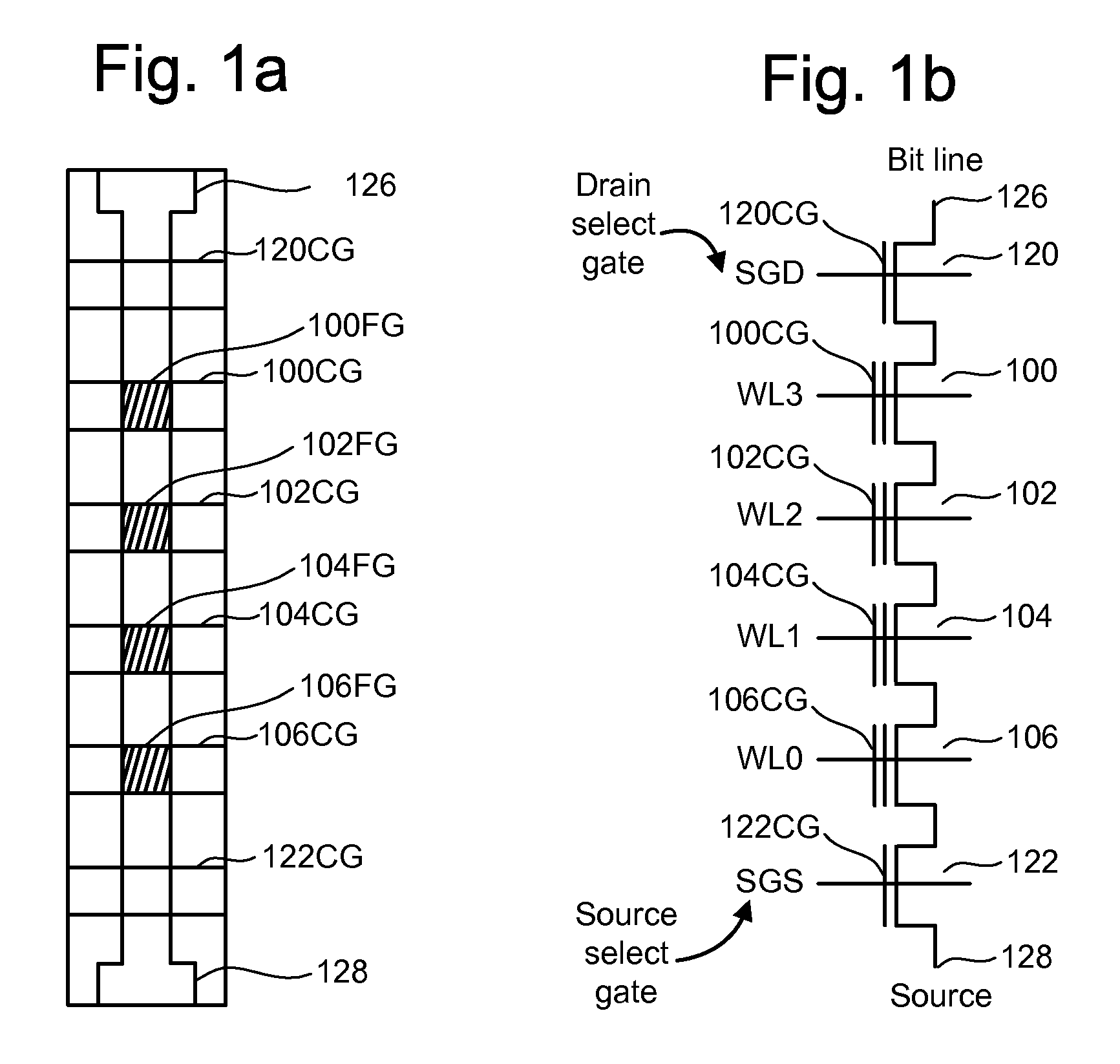

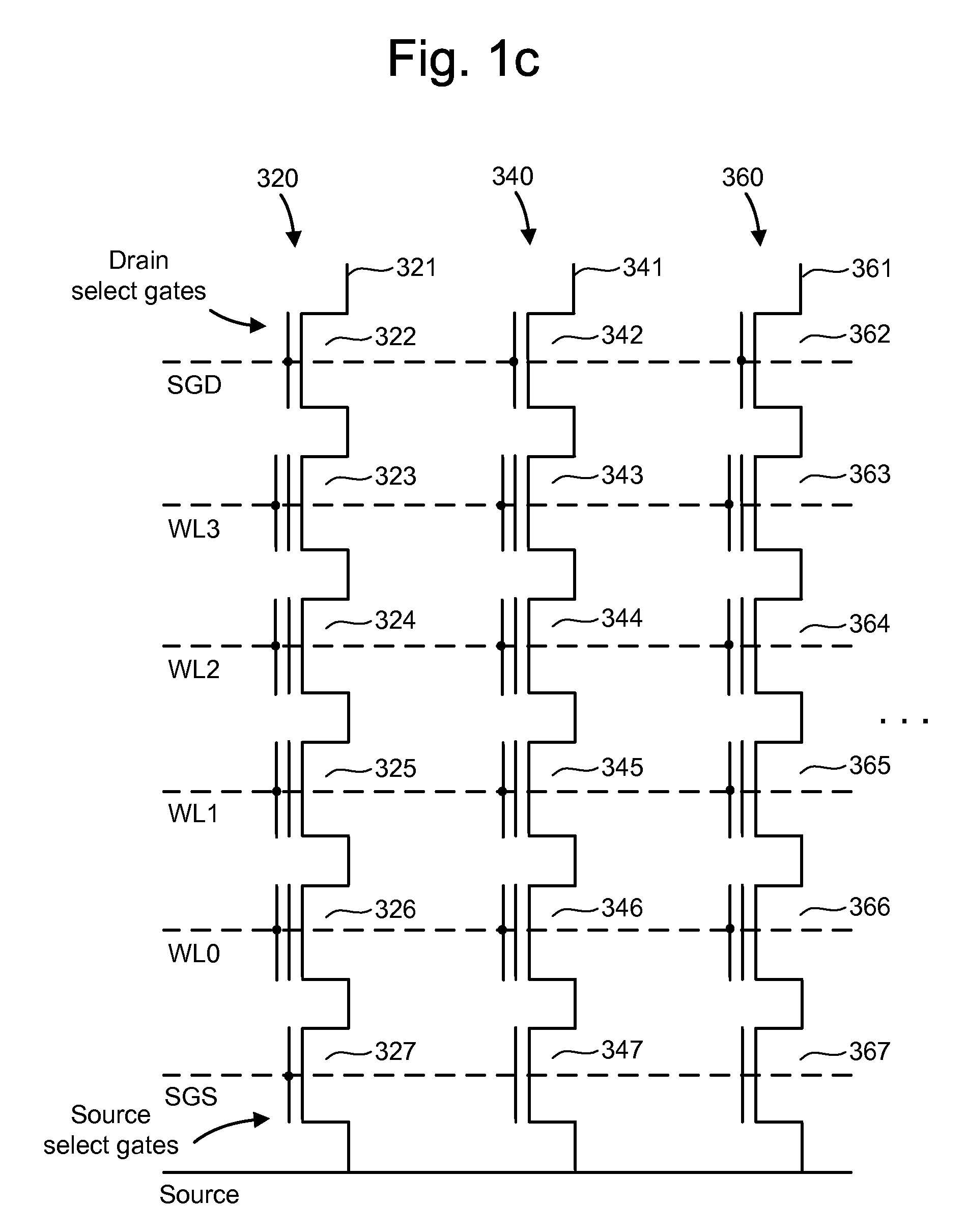

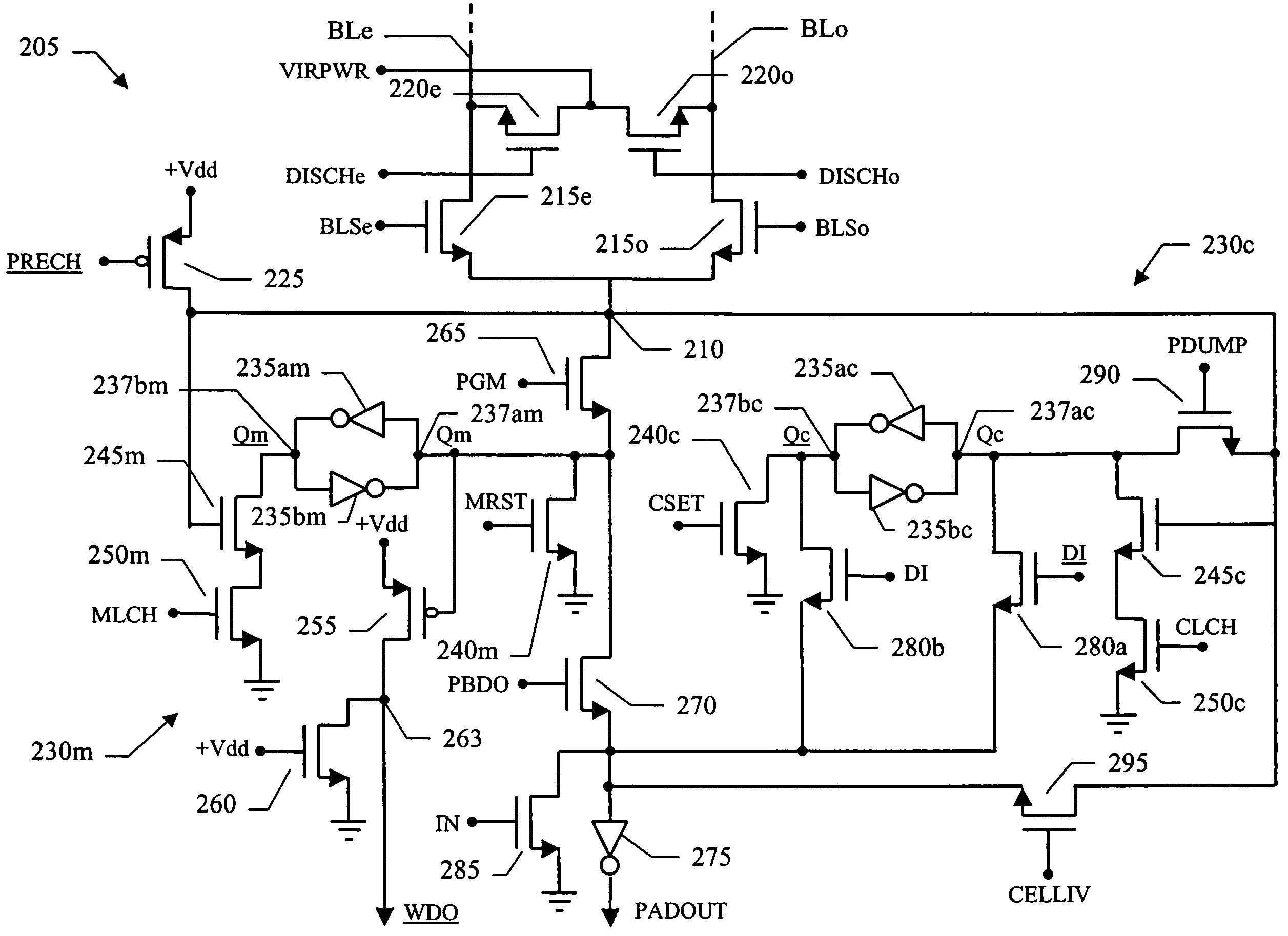

Coupling effects between adjacent floating gates in a non-volatile storage device are reduced in a multi-pass programming operation, while reducing program data storage requirements. In one approach, storage elements are programmed in an out of sequence or zigzag word line order. A particular word line is programmed with a coarse program pass, after which another word line is programmed with a fine program pass, after which the particular word line is read. The particular word line is read before another word line is programmed with a coarse program pass which causes coupling interference to storage elements of the particular word line. The read data is subsequently used to perform a fine program pass for the particular word line. This avoids the need to store program data of multiple word lines concurrently, so that storage hardware can be reduced in size along with power consumption.

Owner:SANDISK TECH LLC

Non-volatile memory and control with improved partial page program capability

Owner:SANDISK TECH LLC

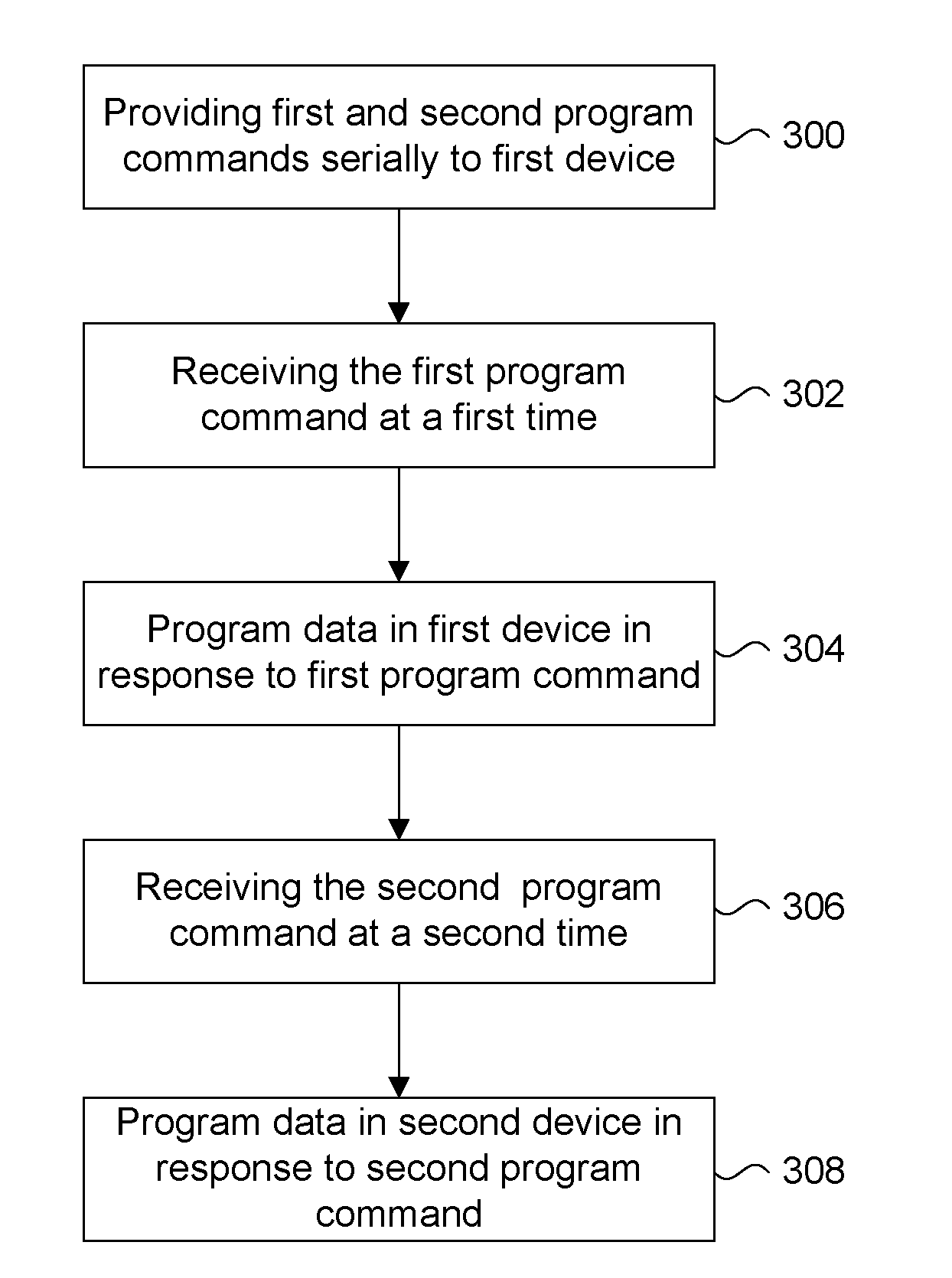

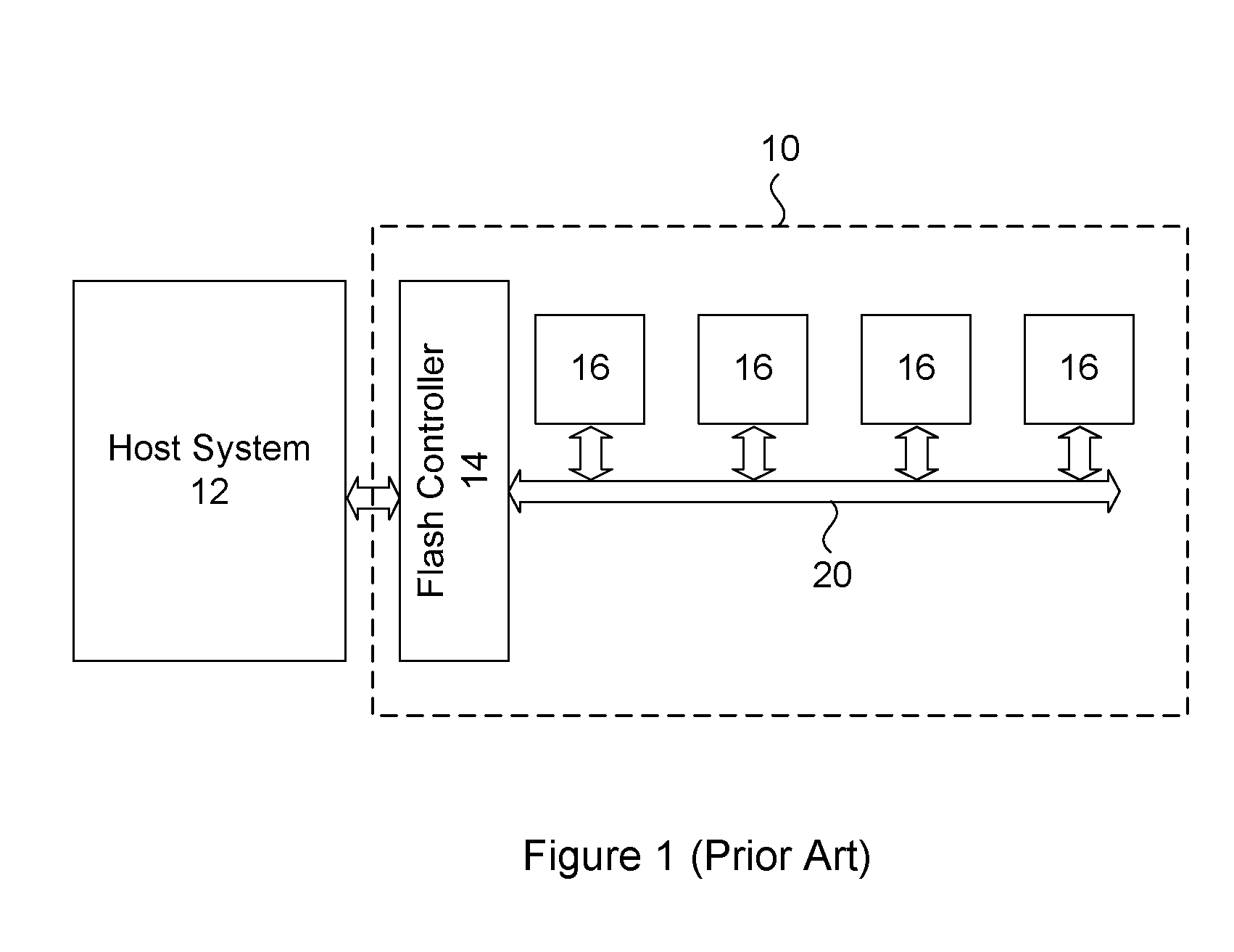

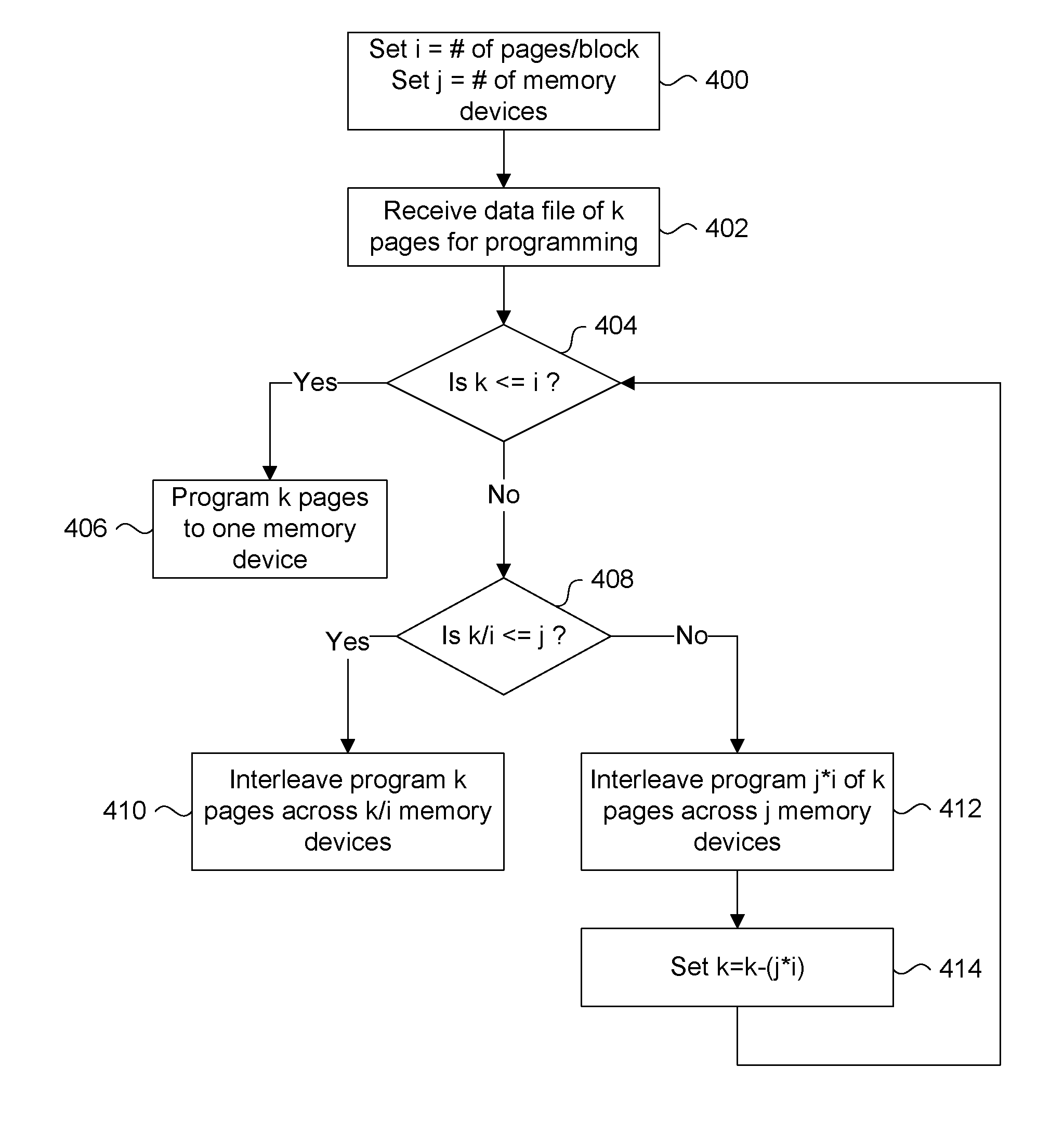

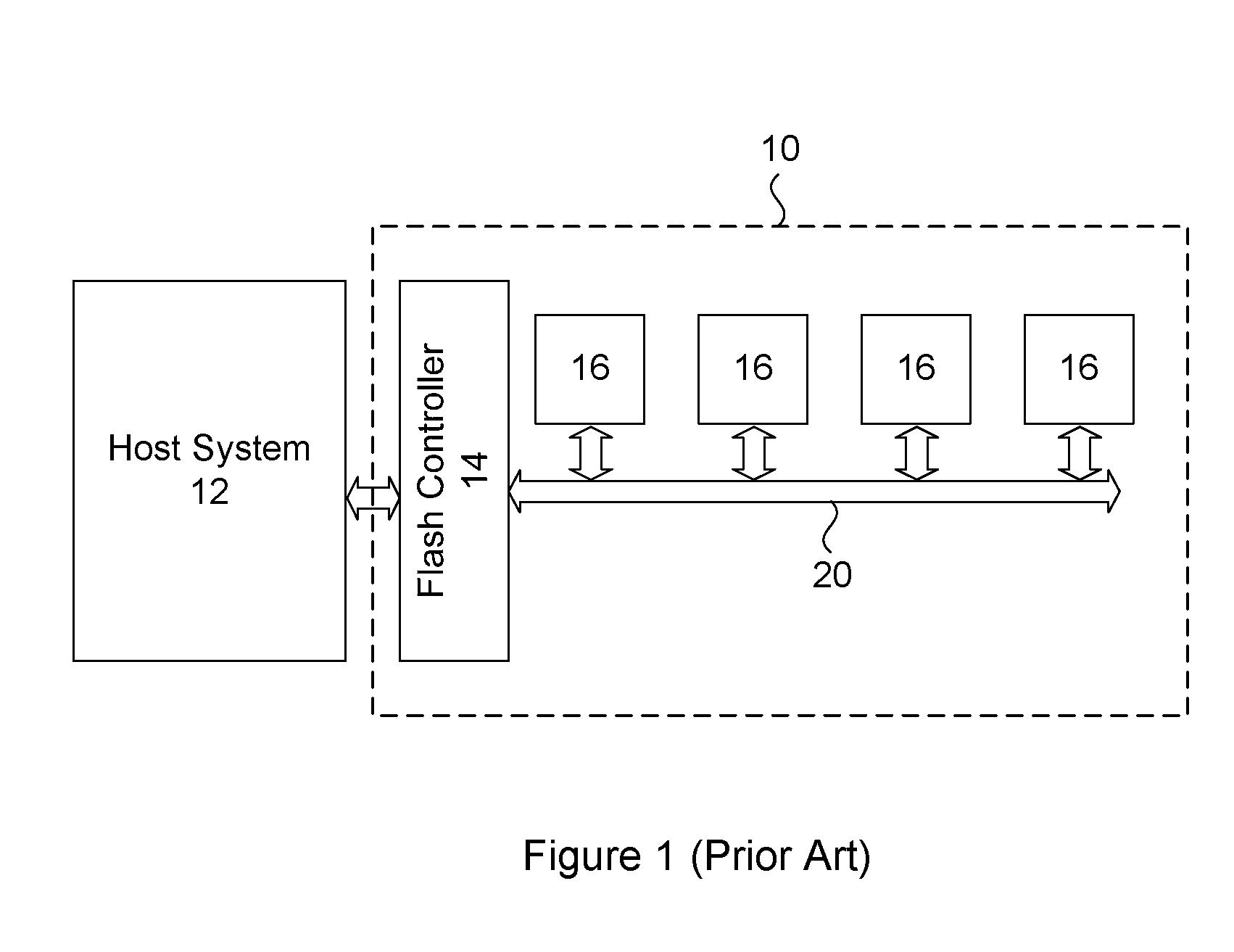

Flash memory system control scheme

ActiveUS20070233939A1Improve Flash memory system programming throughputImprove throughputMemory architecture accessing/allocationRead-only memoriesSequential programmingMemory controller

A Flash memory system architecture having serially connected Flash memory devices to achieve high speed programming of data. High speed programming of data is achieved by interleaving pages of the data to be programmed amongst the memory devices in the system, such that different pages of data are stored in different memory devices. A memory controller issues program commands for each memory device. As each memory device receives a program command, it either begins a programming operation or passes the command to the next memory device. Therefore, the memory devices in the Flash system sequentially program pages of data one after the other, thereby minimizing delay in programming each page of data into the Flash memory system. The memory controller can execute a wear leveling algorithm to maximize the endurance of each memory device, or to optimize programming performance and endurance for data of any size.

Owner:MOSAID TECH

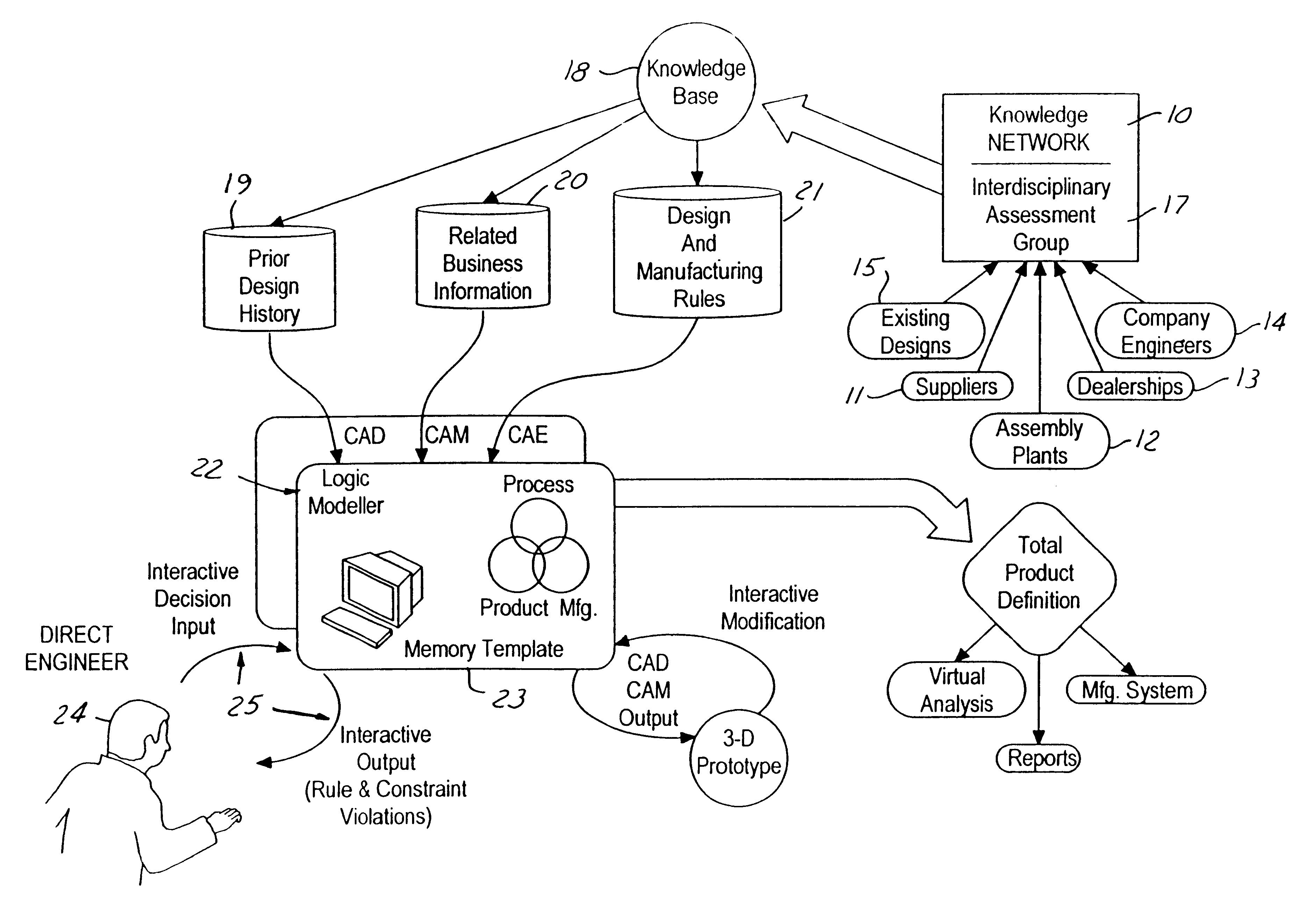

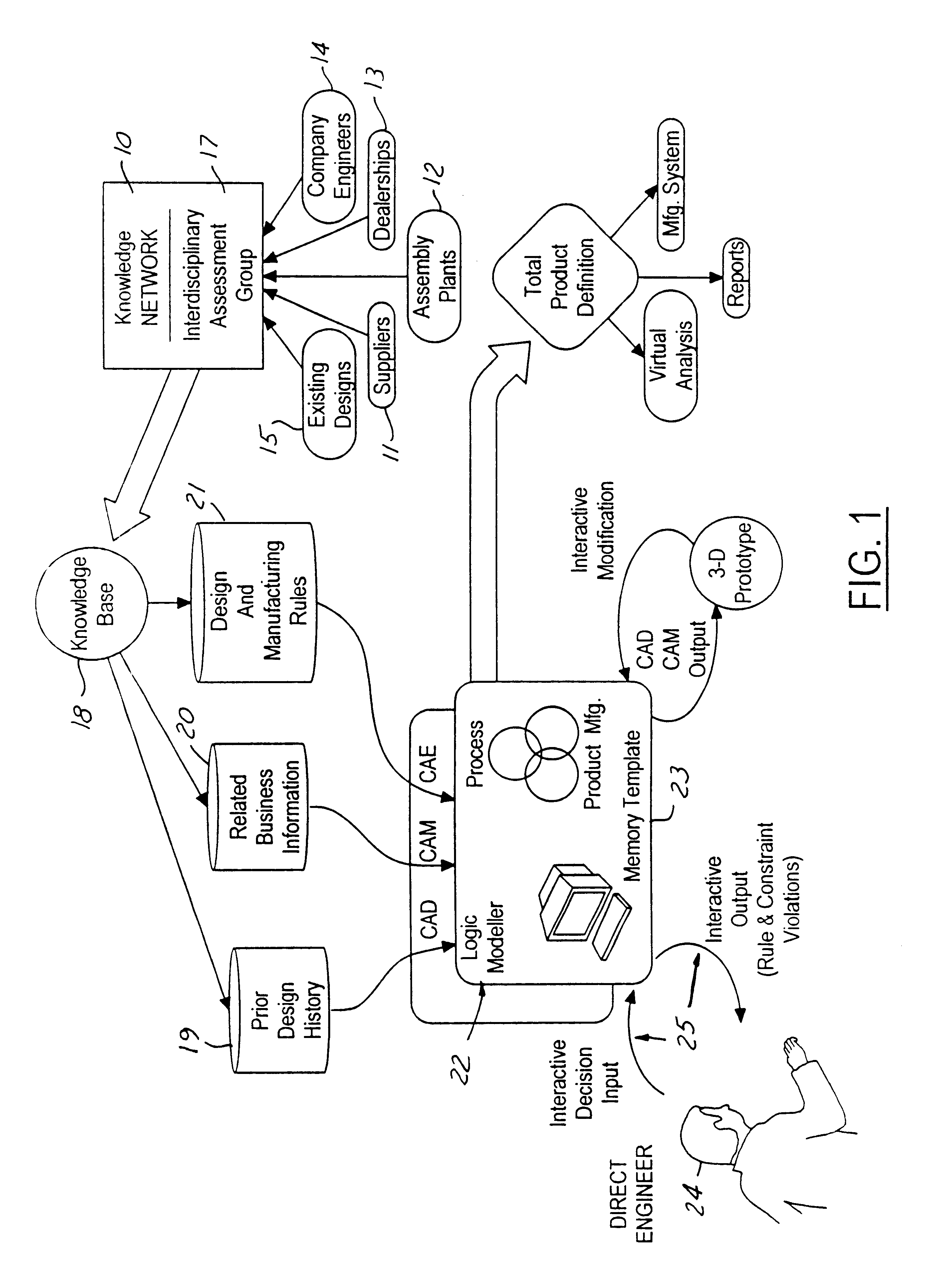

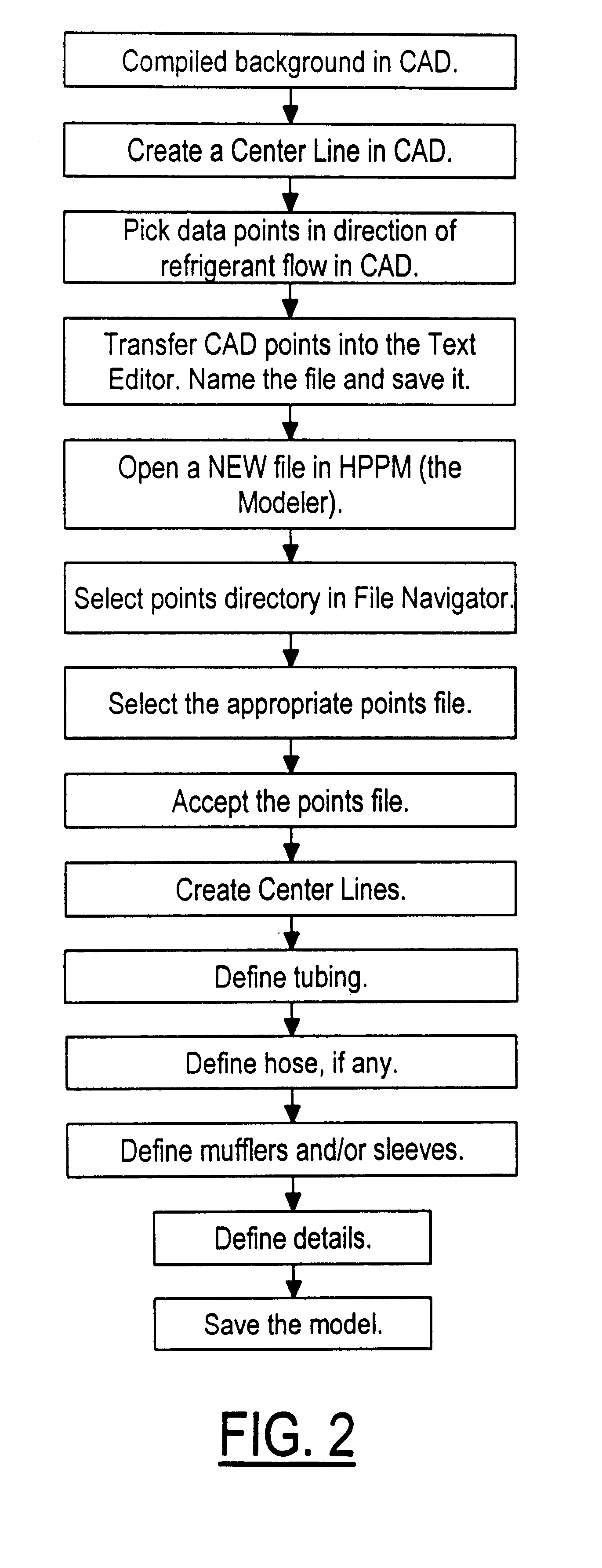

Simultaneous manufacturing and product engineering integrated with knowledge networking

InactiveUS6230066B1Analogue computers for electric apparatusComputer programmed simultaneously with data introductionSequential programmingProduct engineering

Method of simultaneously carrying out manufacturing and product engineering integrated with knowledge networking. The method comprises: (a) creating a logic modeller by (i) identifying elements of an engineering project and syntactically arranging such elements in a logic sequence based on engineering functions, (ii) ascertaining uniform meaning for such elements and engineering functions to allow for interdisciplinary communication, (iii) gathering existing knowledge pertinent to such elements and engineering functions, and encoding such gathered knowledge into terms according to uniform meanings, and (iv) programming a computer memory template with such logic sequence and with attached data bases of such encoded existing knowledge; and (b) operating said logic modeller through a direct engineer that: (i) requests review of initial input specifications of an inchoate design that results in an analysis by the modeller to indicate rule or constraint violations of the gathered knowledge, and (ii) interacts with the analysis in response to such indications to converge on acceptable or improved engineering design functions.

Owner:FORD GLOBAL TECH LLC

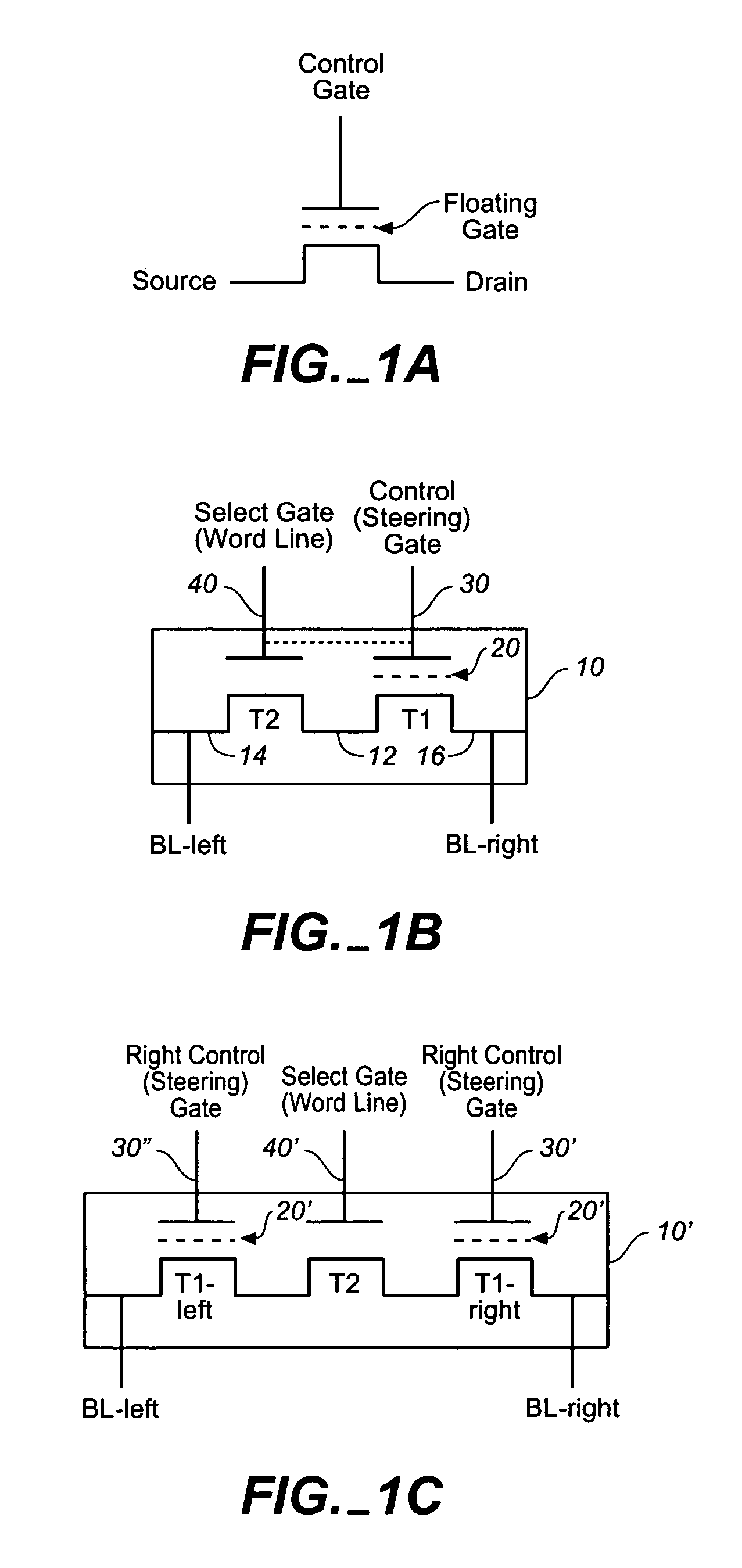

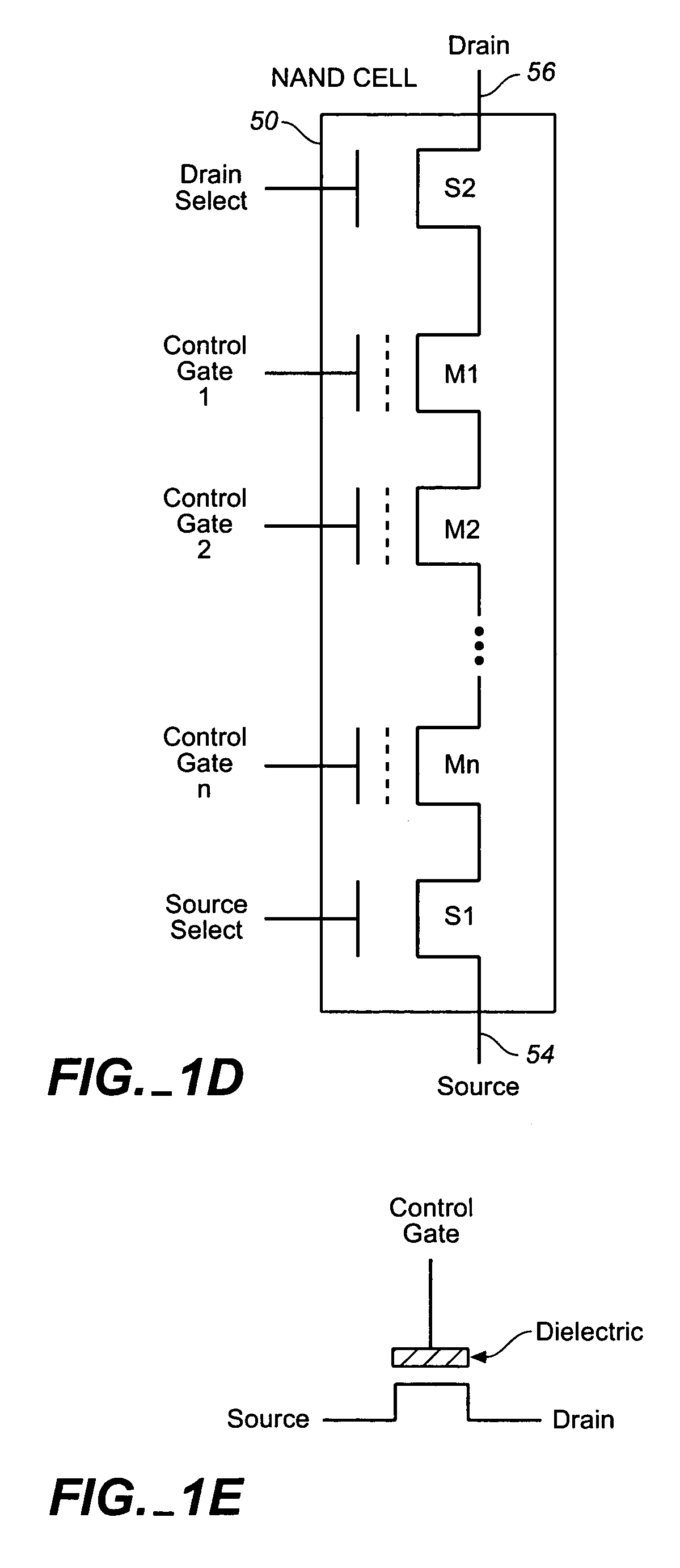

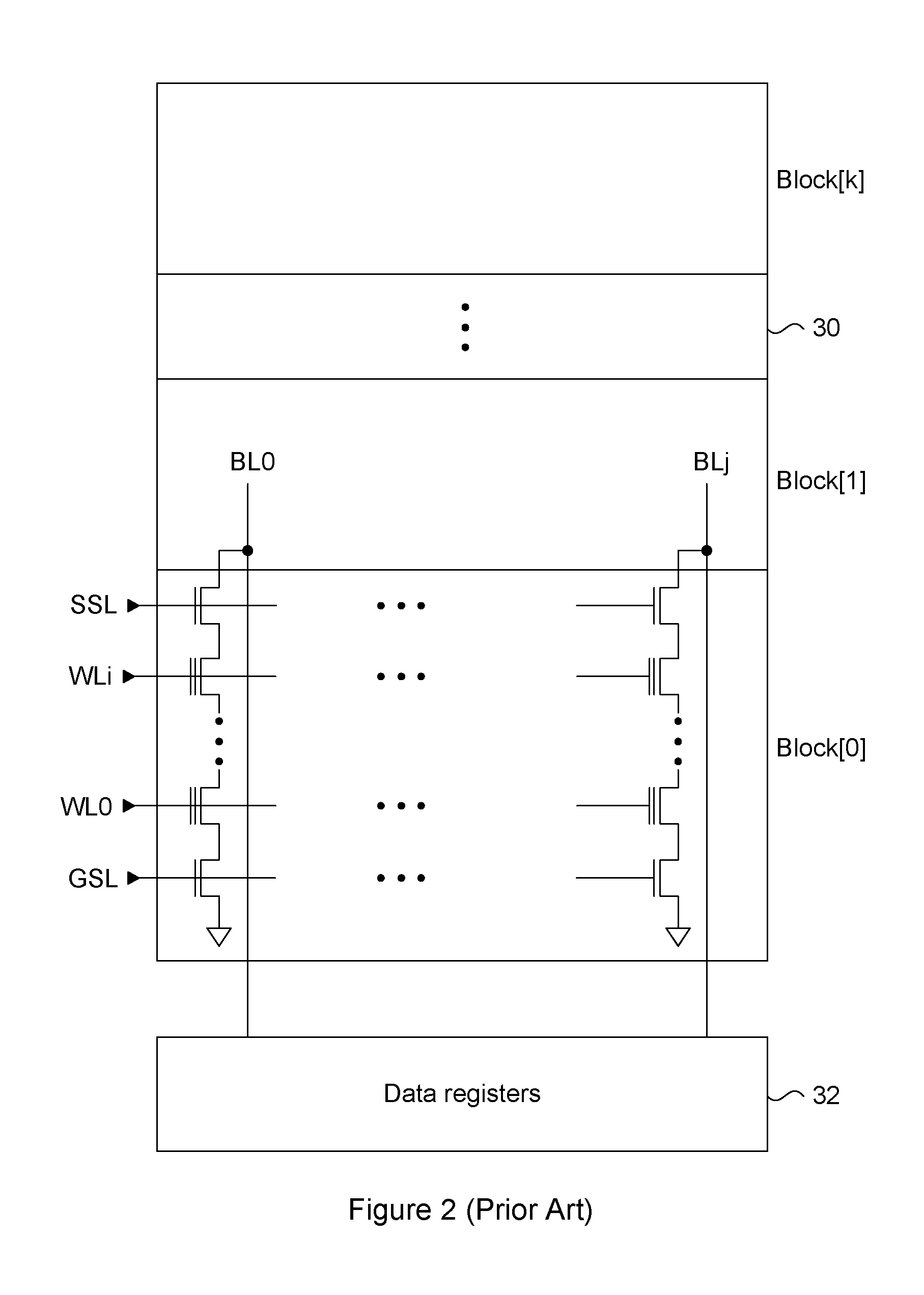

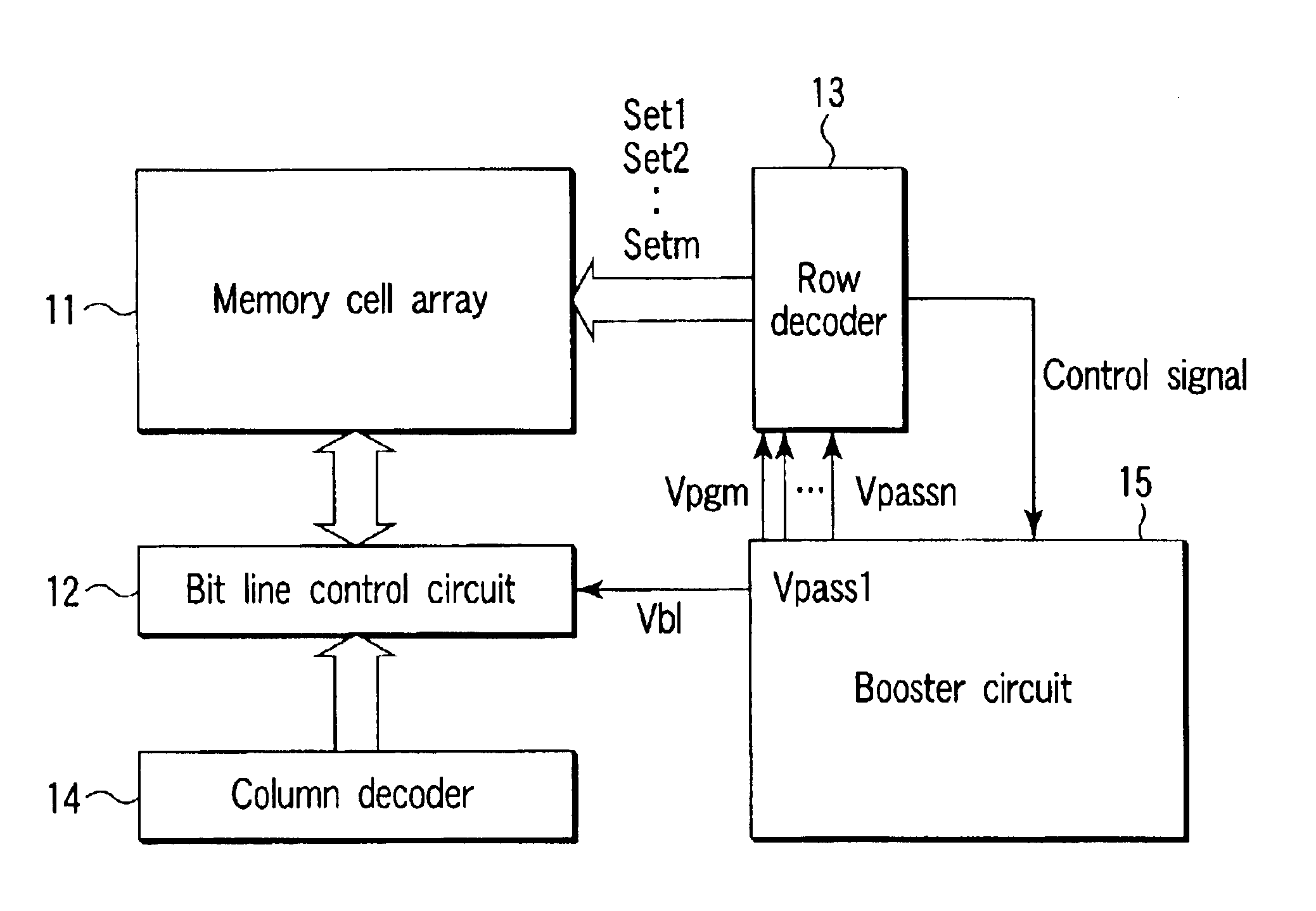

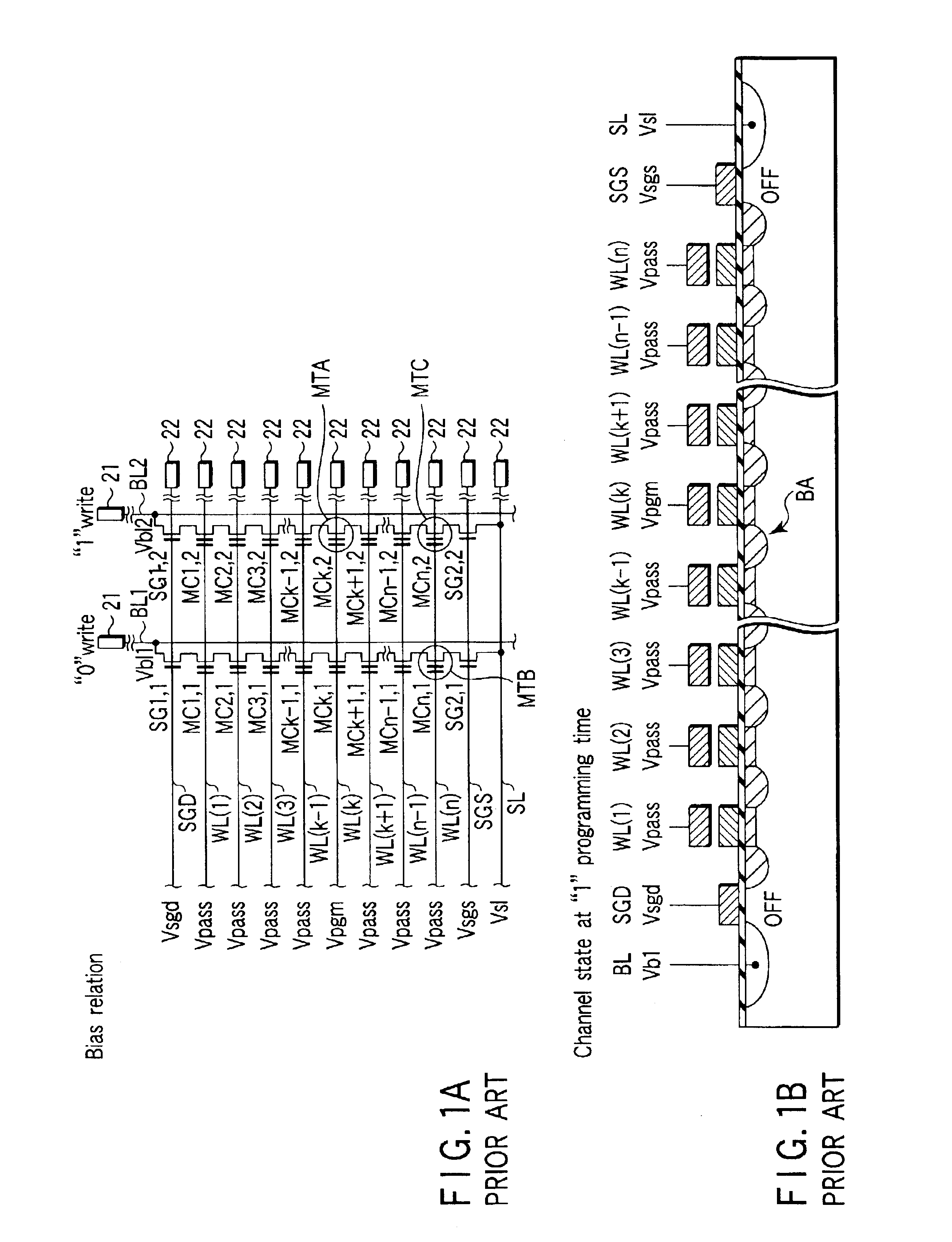

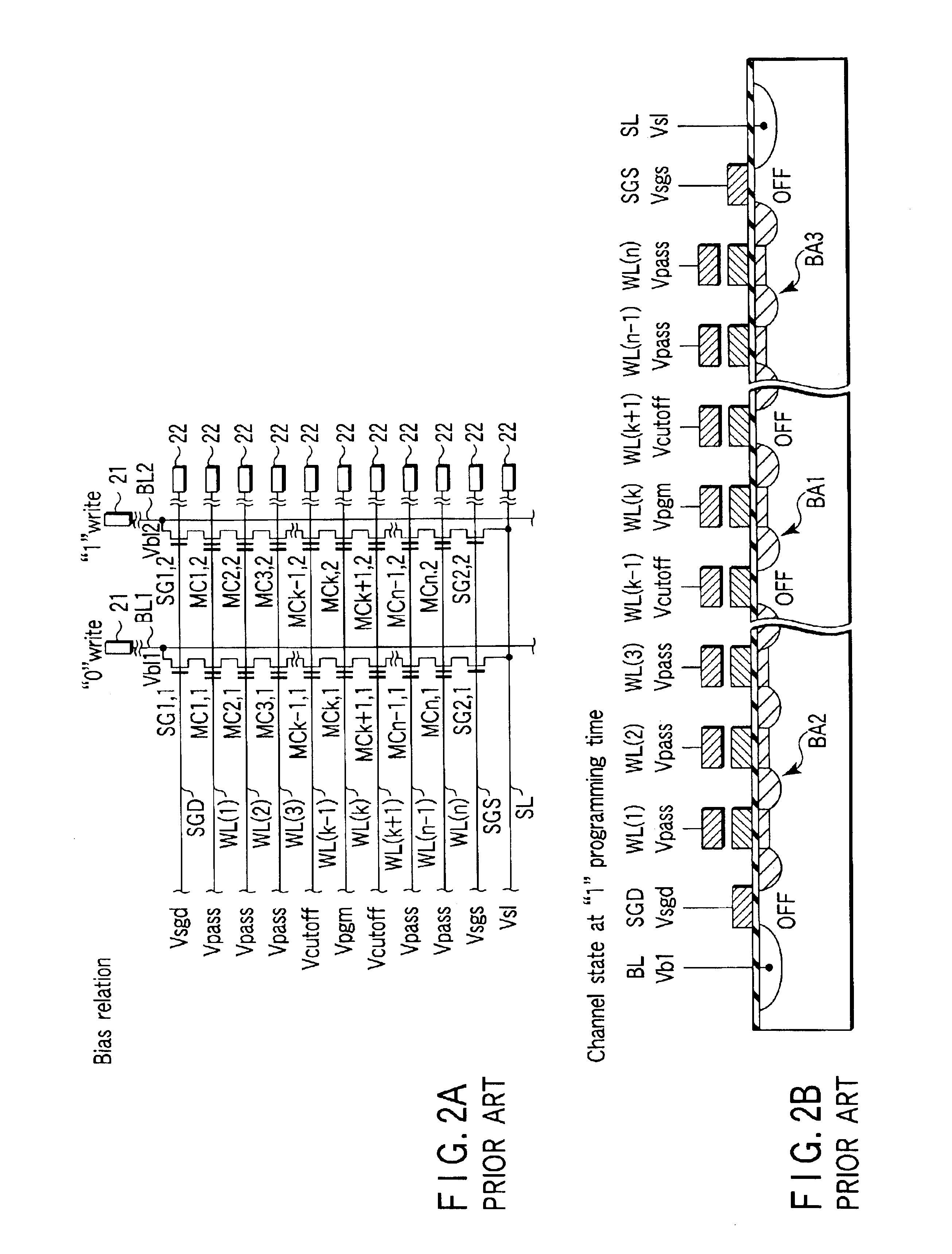

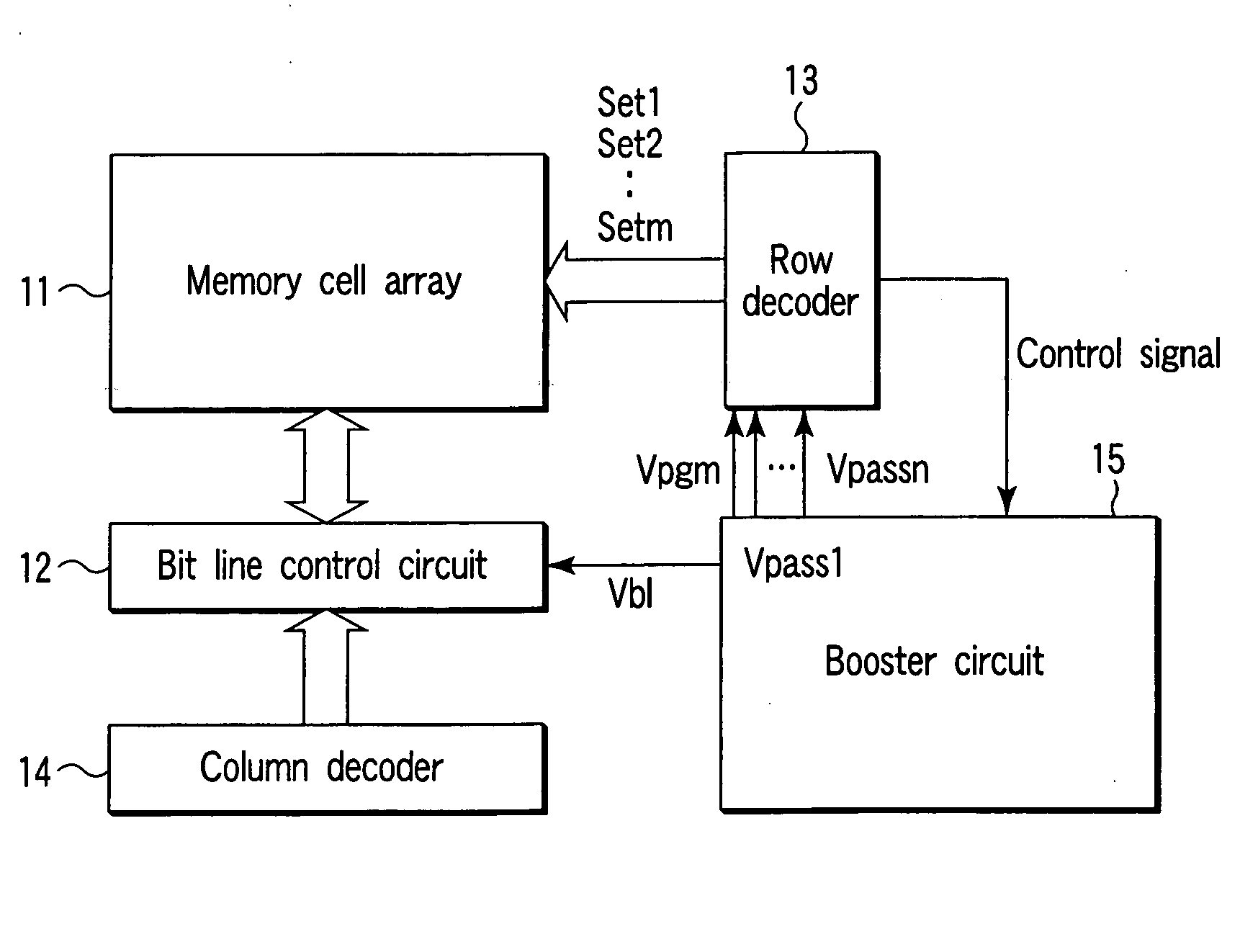

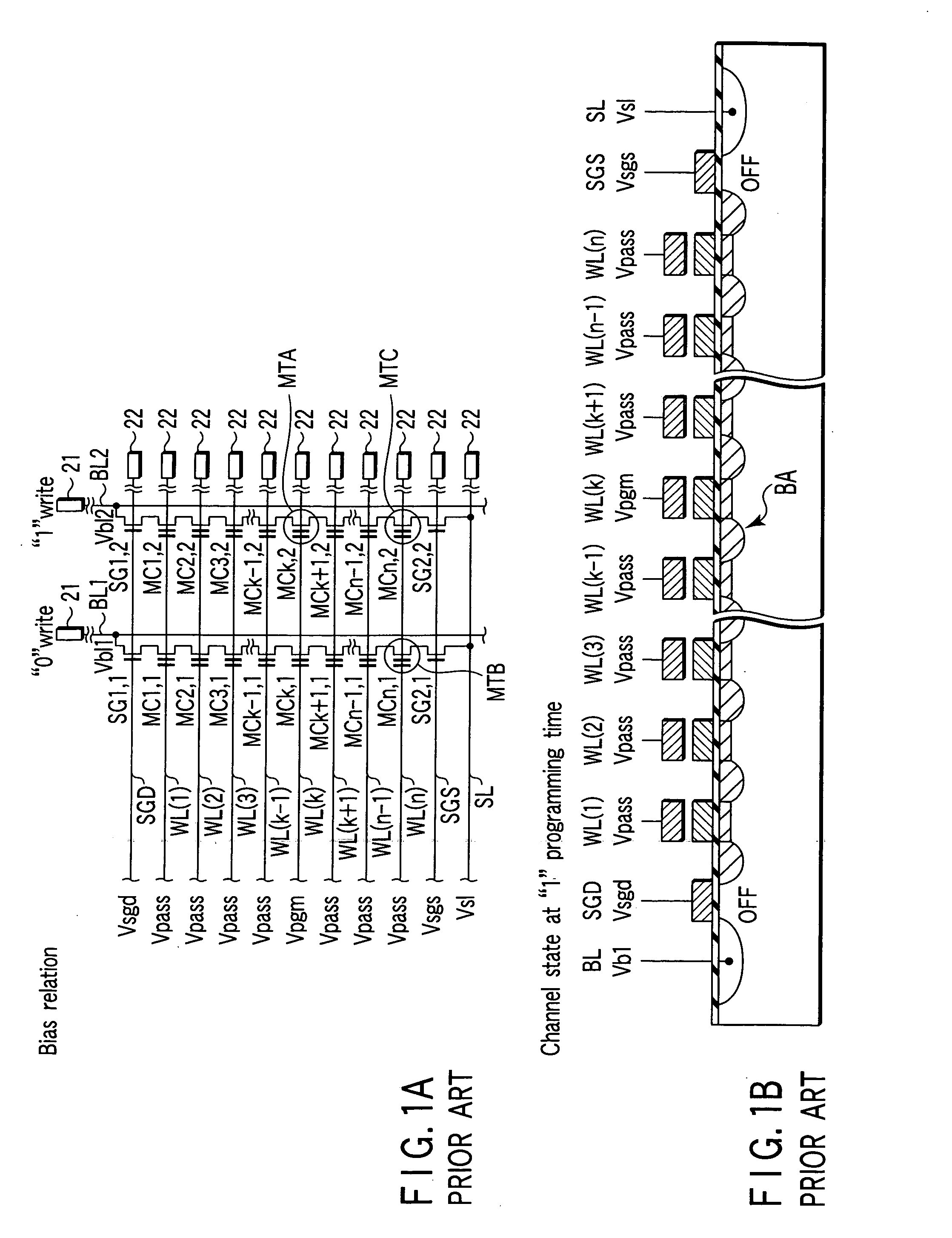

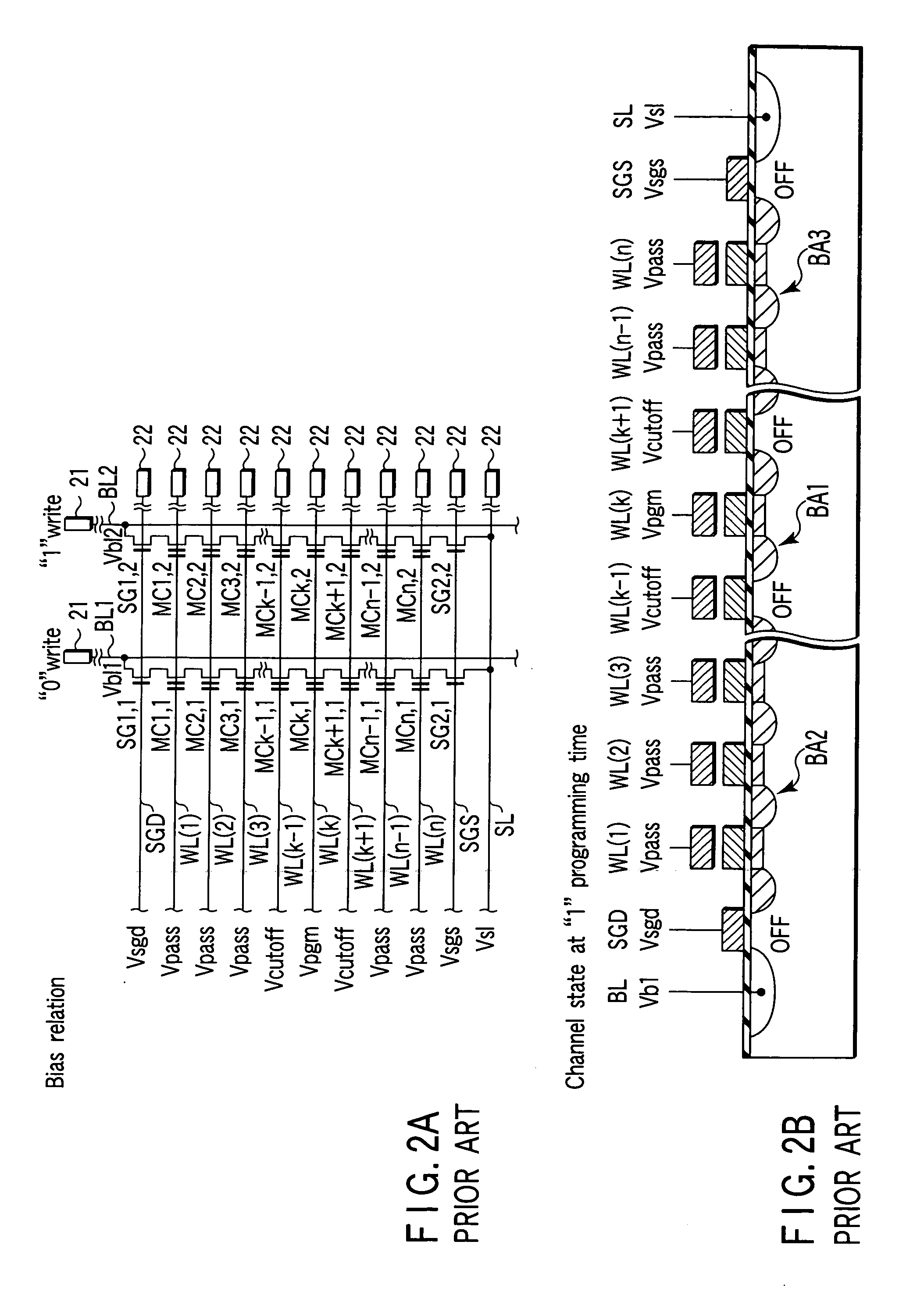

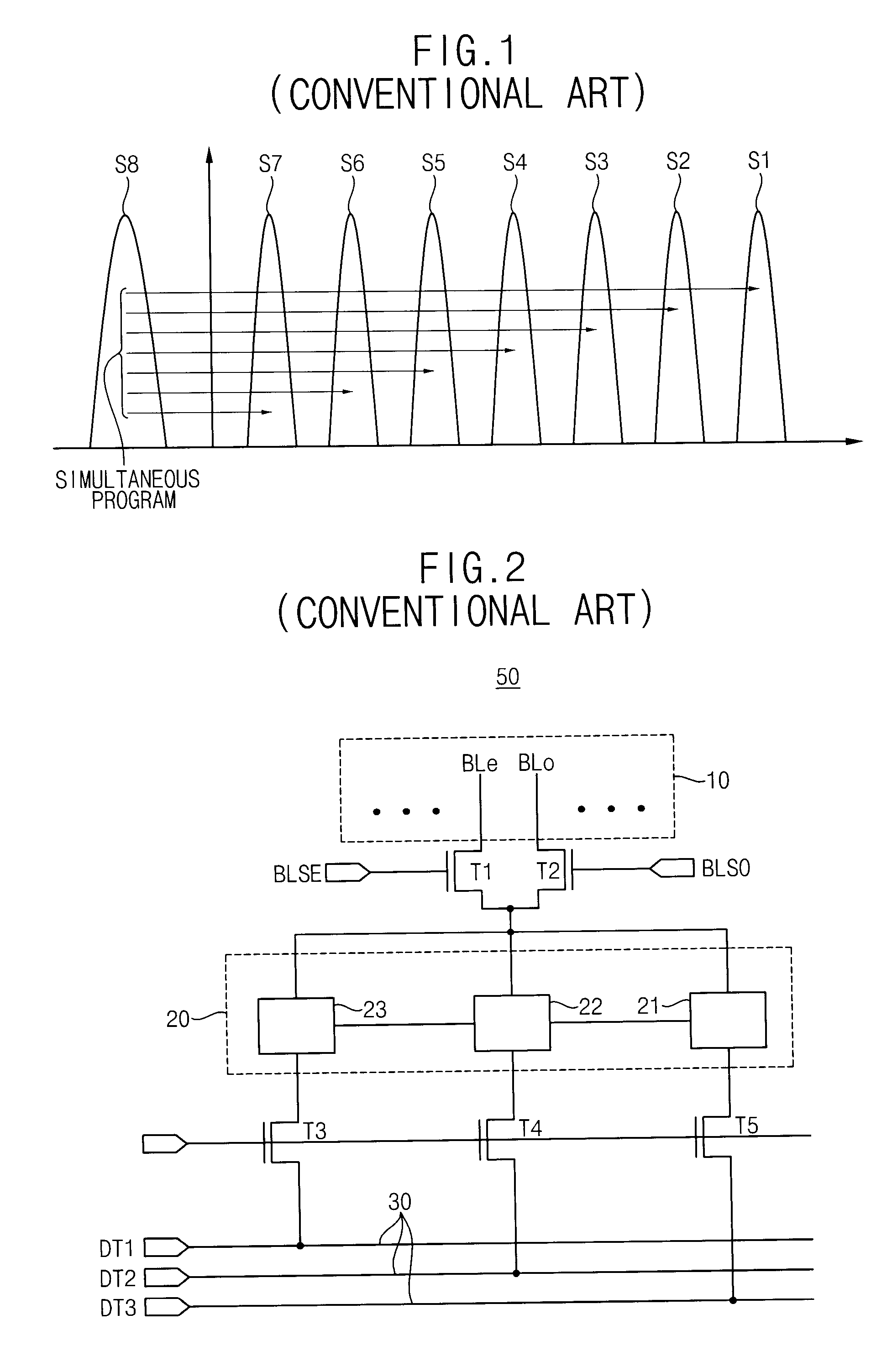

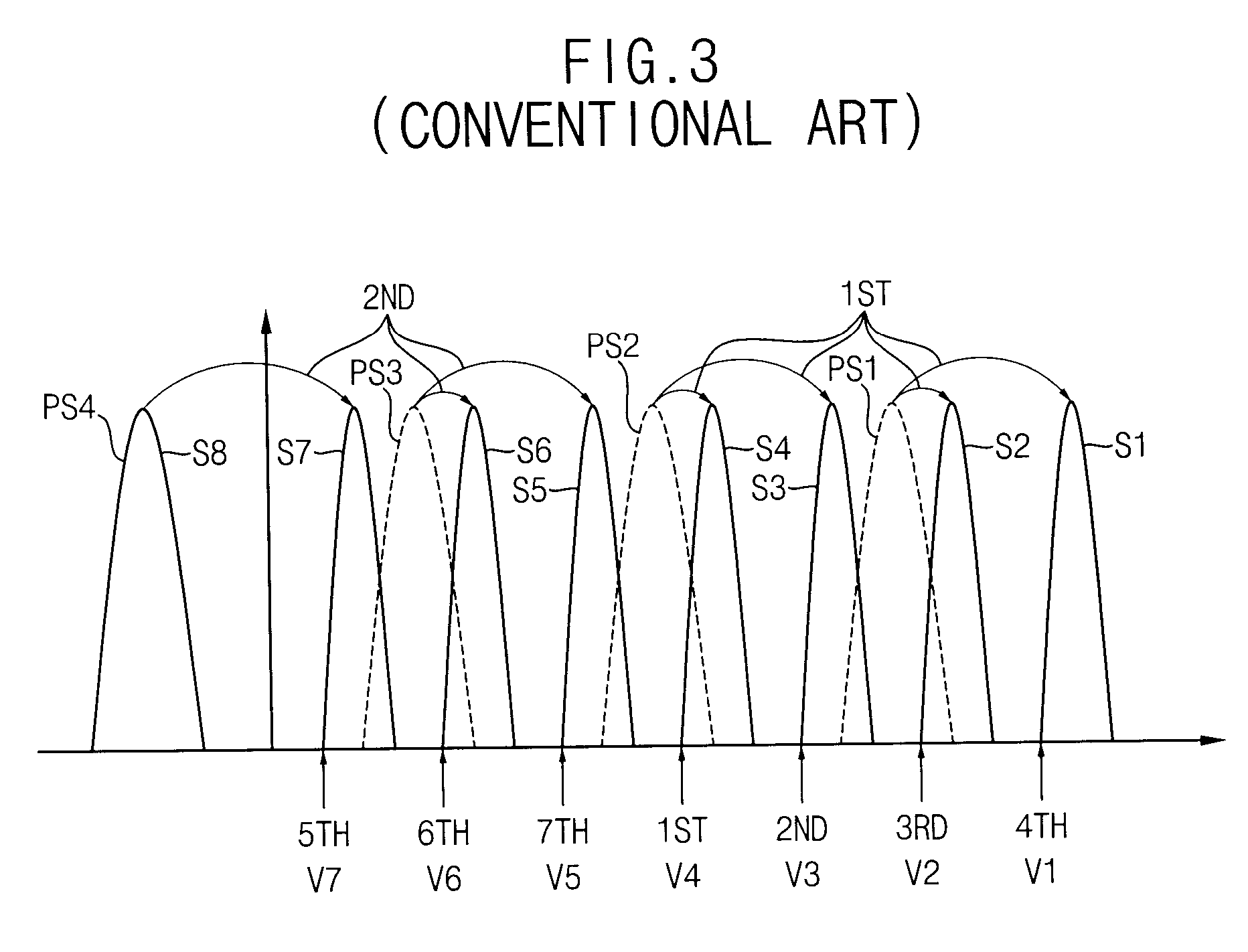

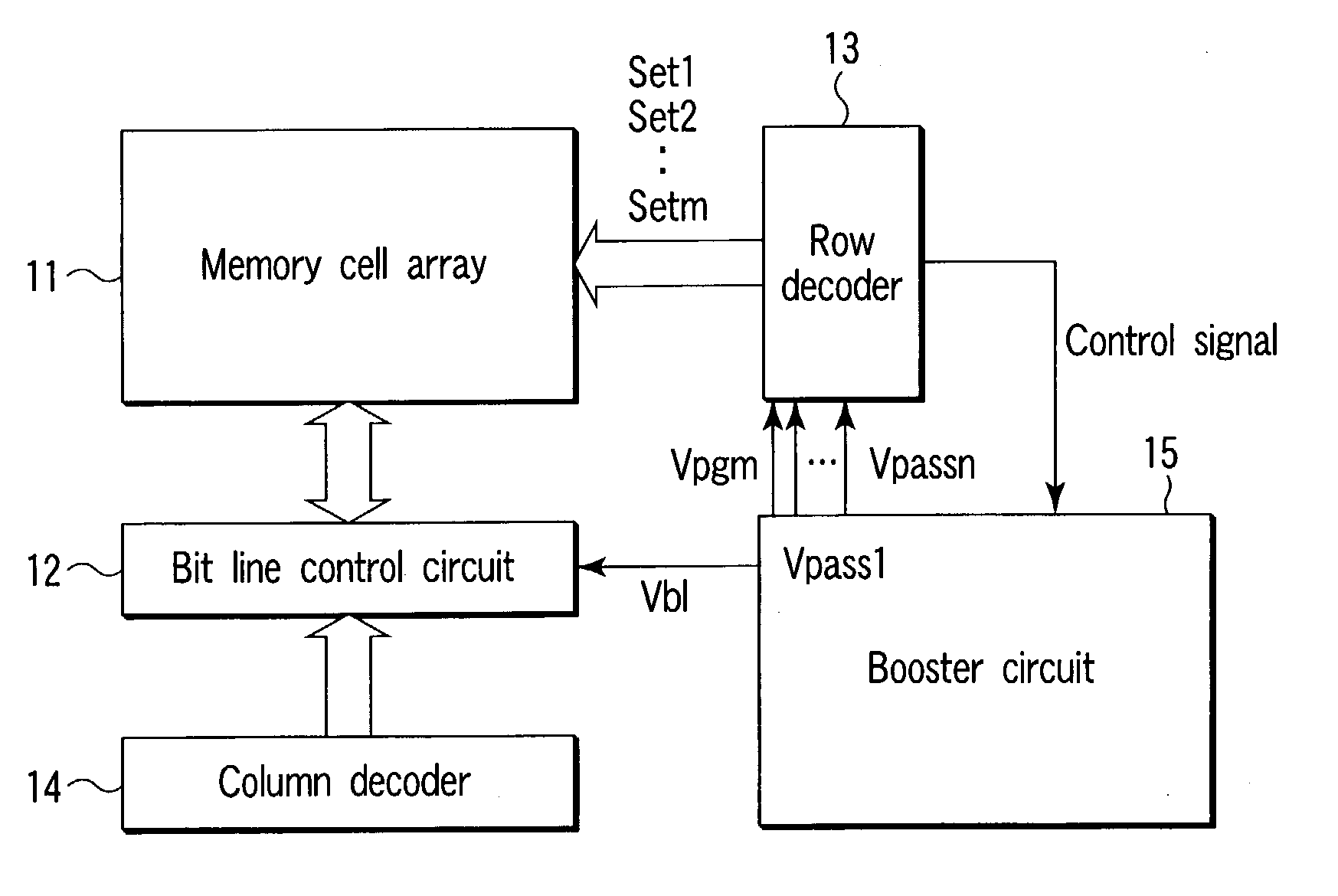

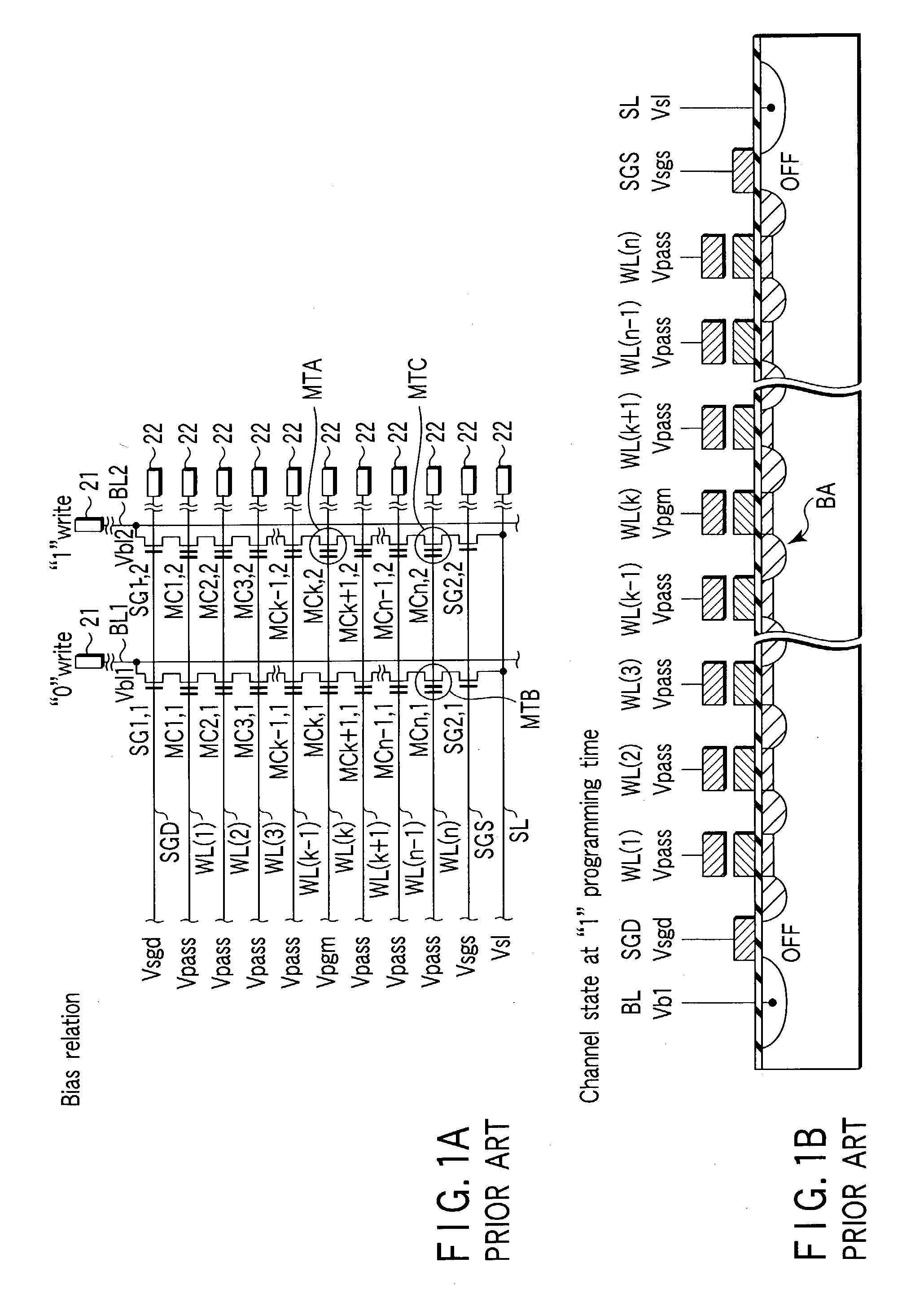

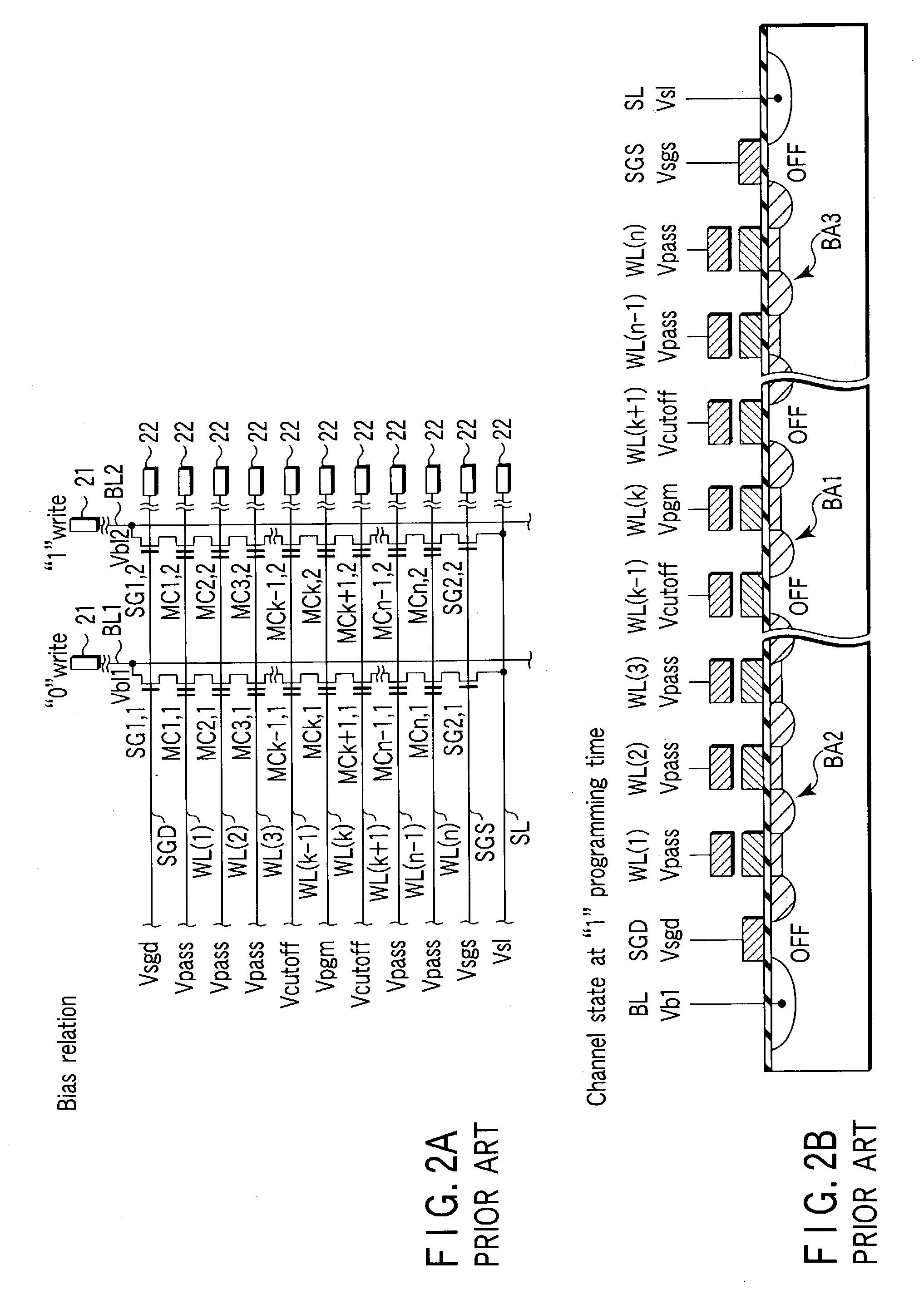

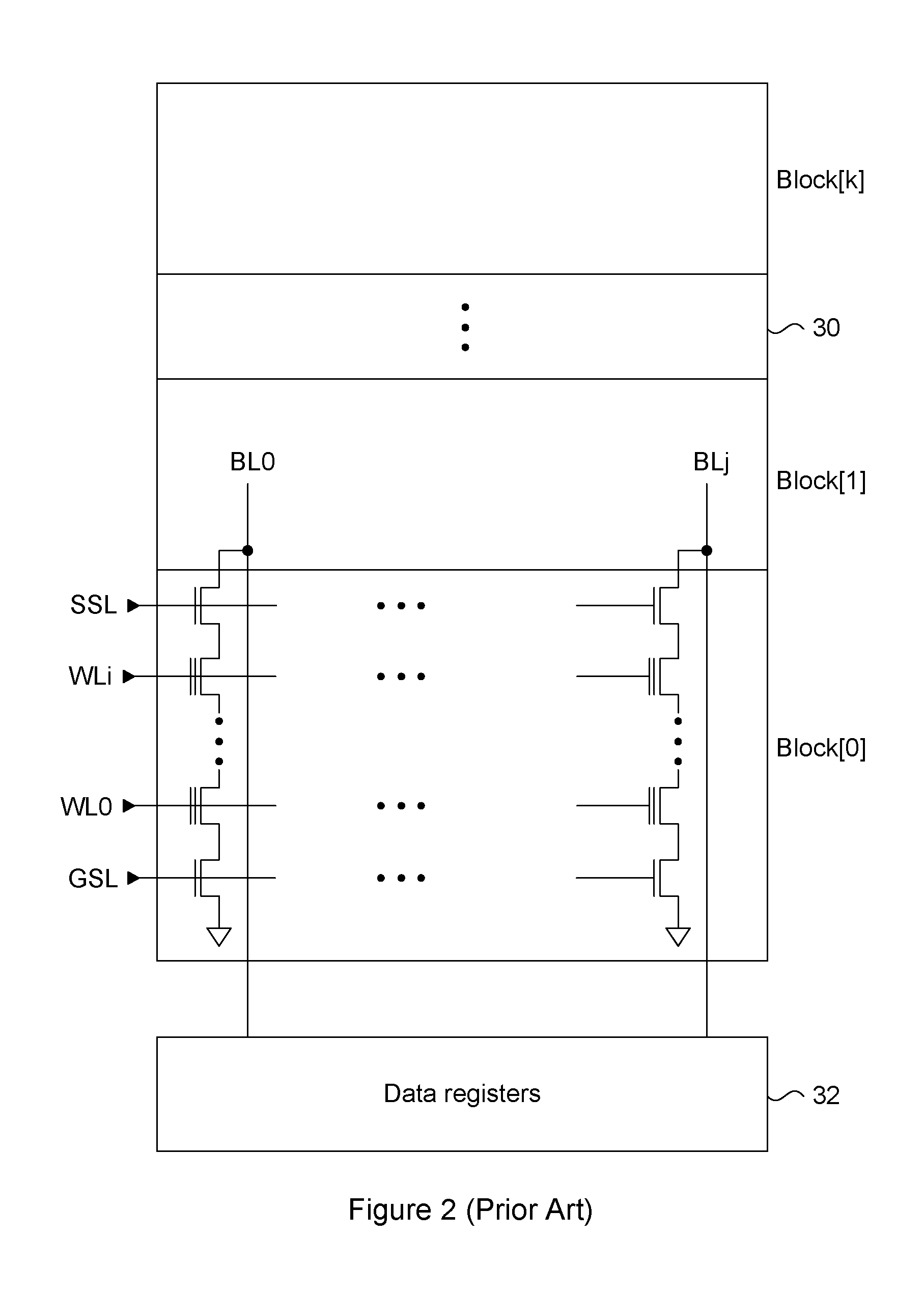

NAND type flash EEPROM in which sequential programming process is performed by using different intermediate voltages

A nonvolatile semiconductor memory device includes a NAND memory cell array, booster circuit, row decoder, bit line control circuit and column decoder. In the device, the magnitude of intermediate voltage applied to the control gates of memory transistors from the booster circuit via the row decoder is changed according to the position of a selected control gate line when data is sequentially programmed into the memory transistors in the memory cell array. Alternatively, a plurality of different intermediate voltages are applied when data is simultaneously programmed into memory transistors connected to the selected control gate line.

Owner:KIOXIA CORP

NAND type flash EEPROM in which sequential programming process is performed by using different intermediate voltages

Owner:KIOXIA CORP

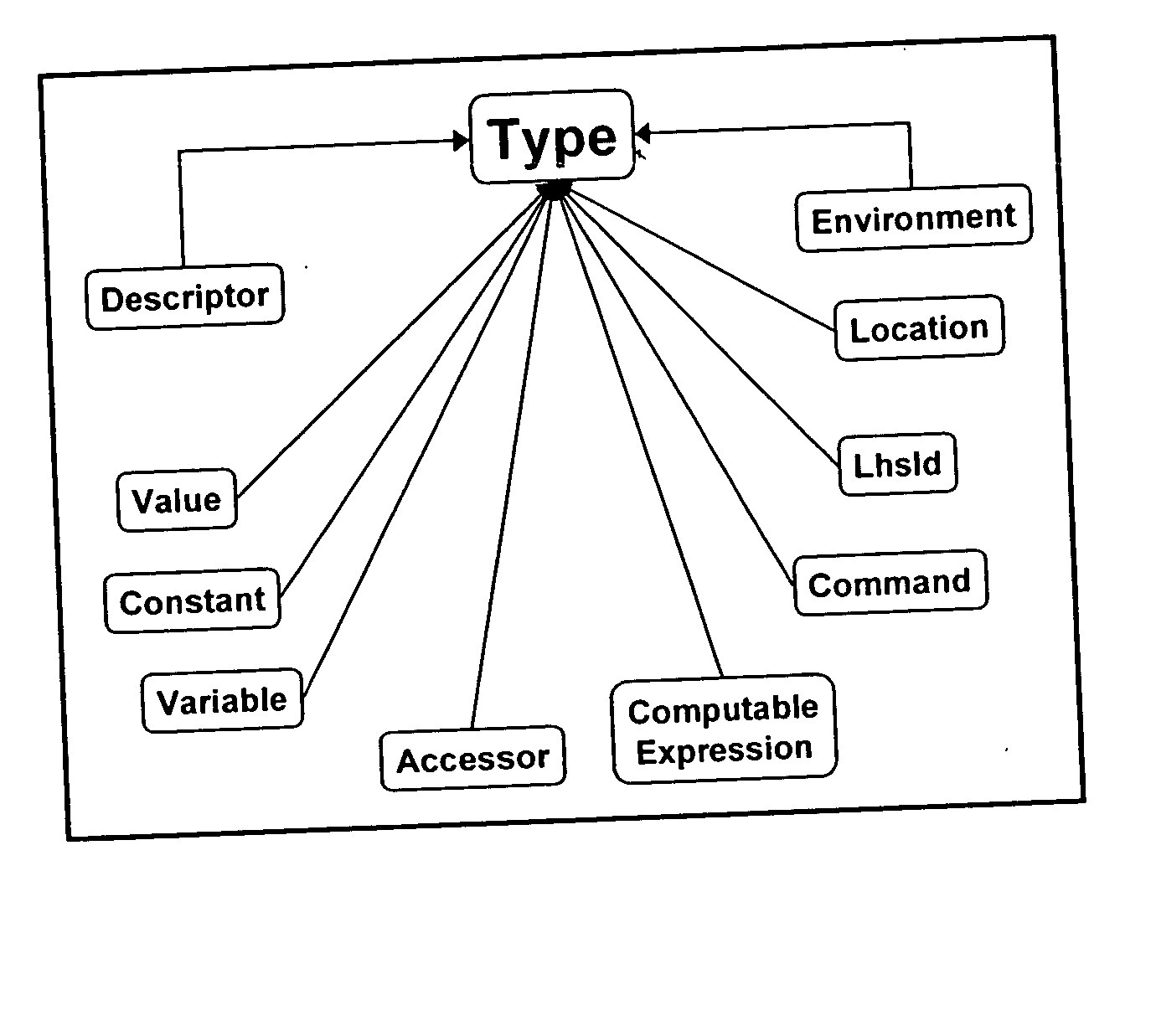

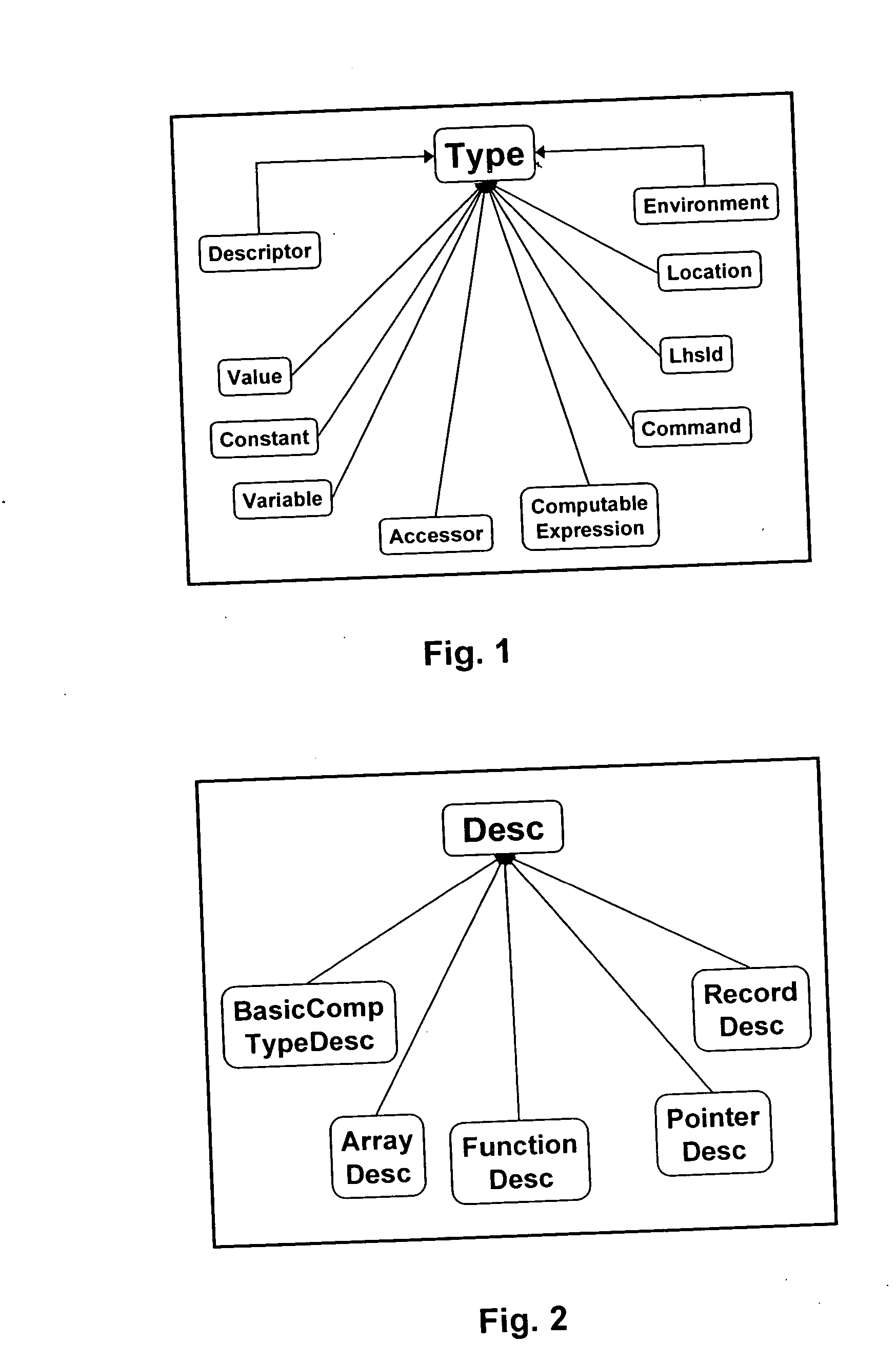

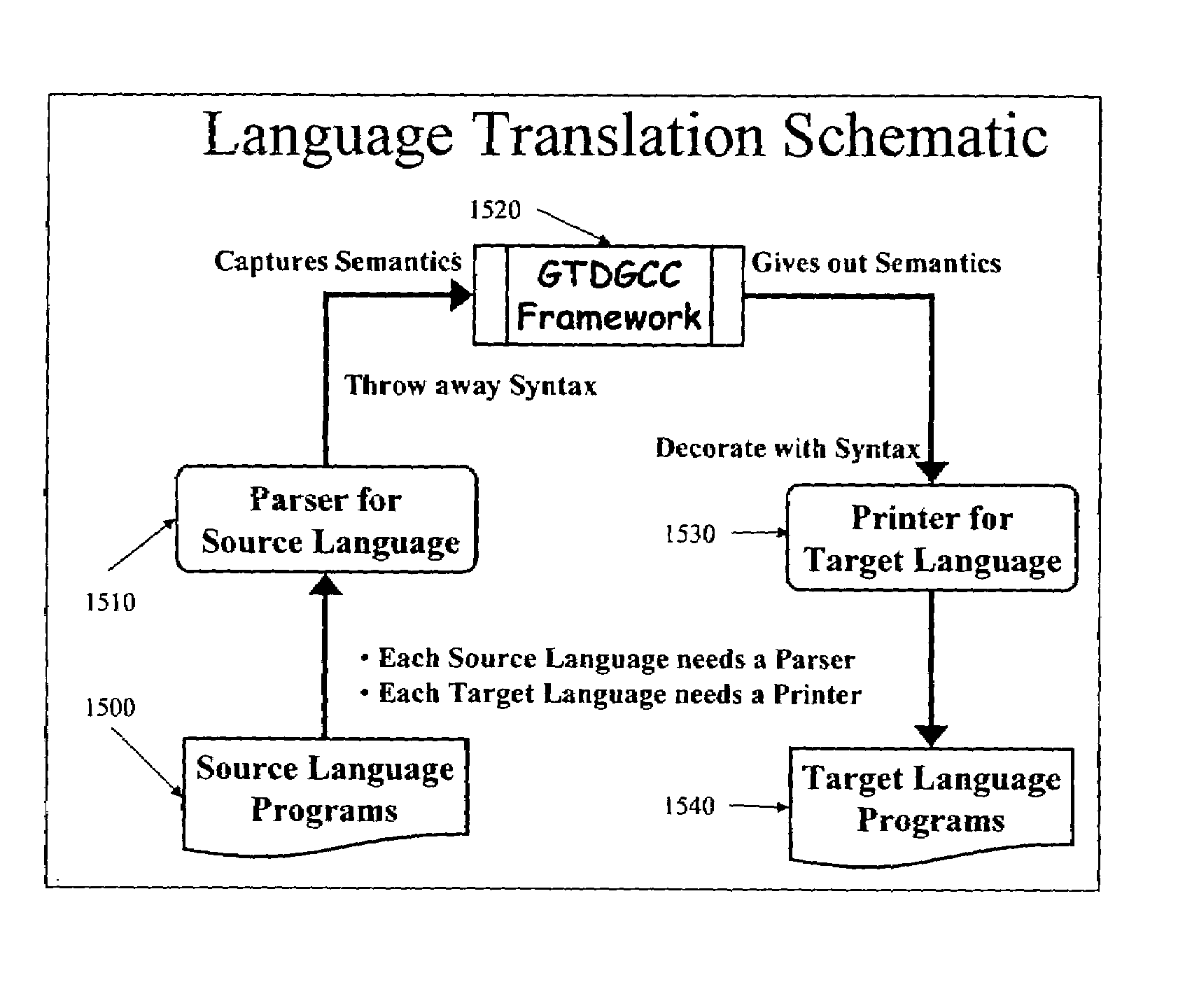

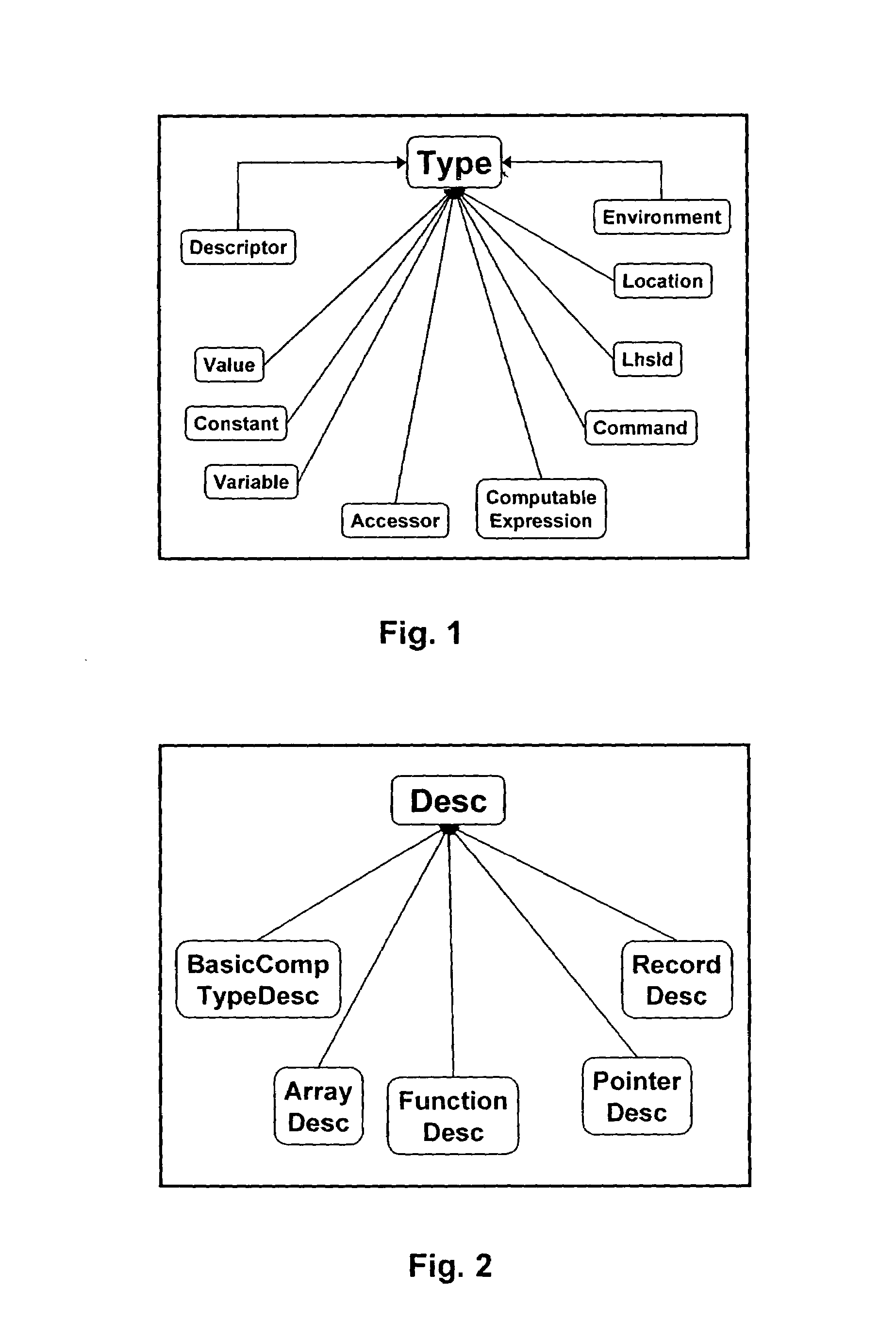

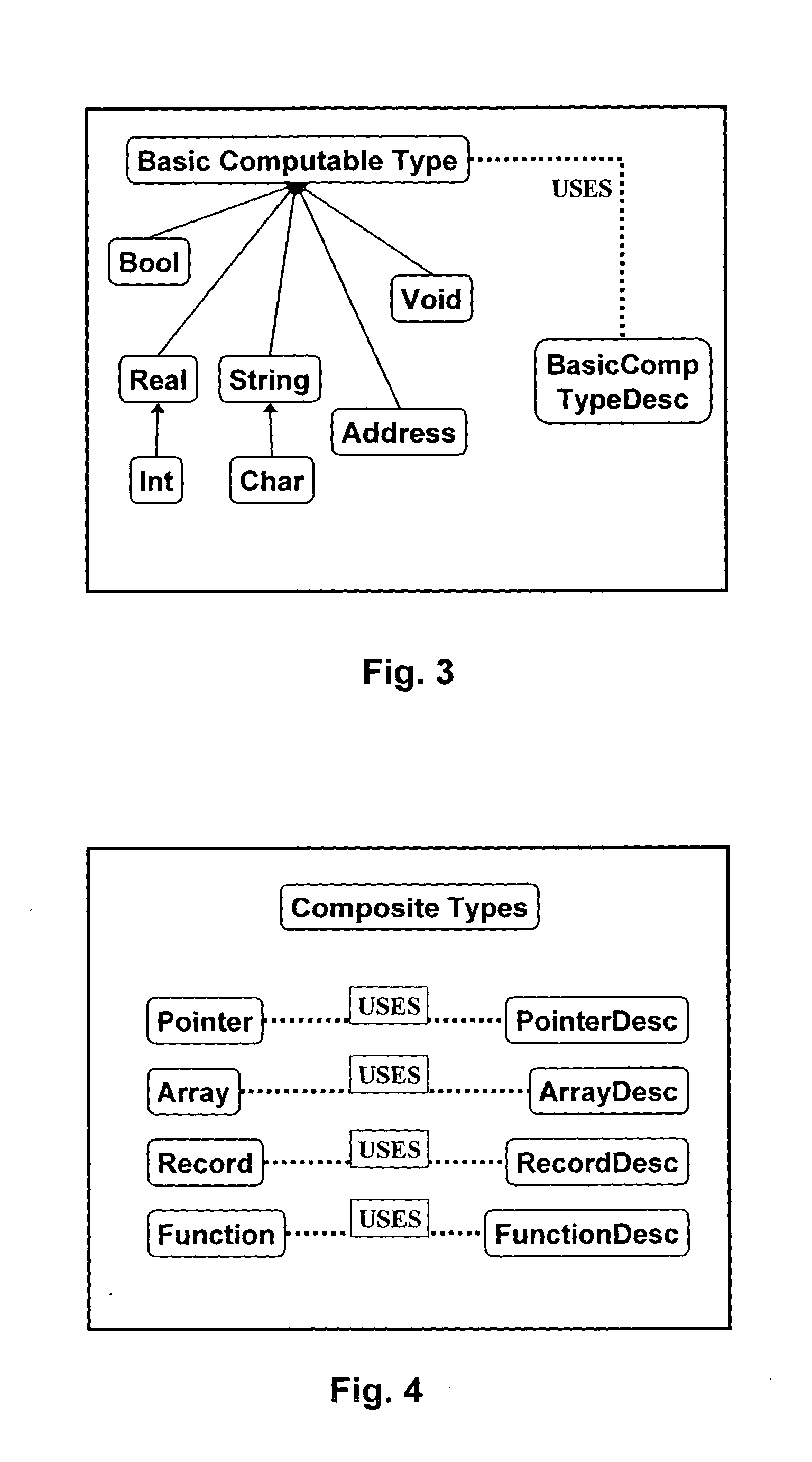

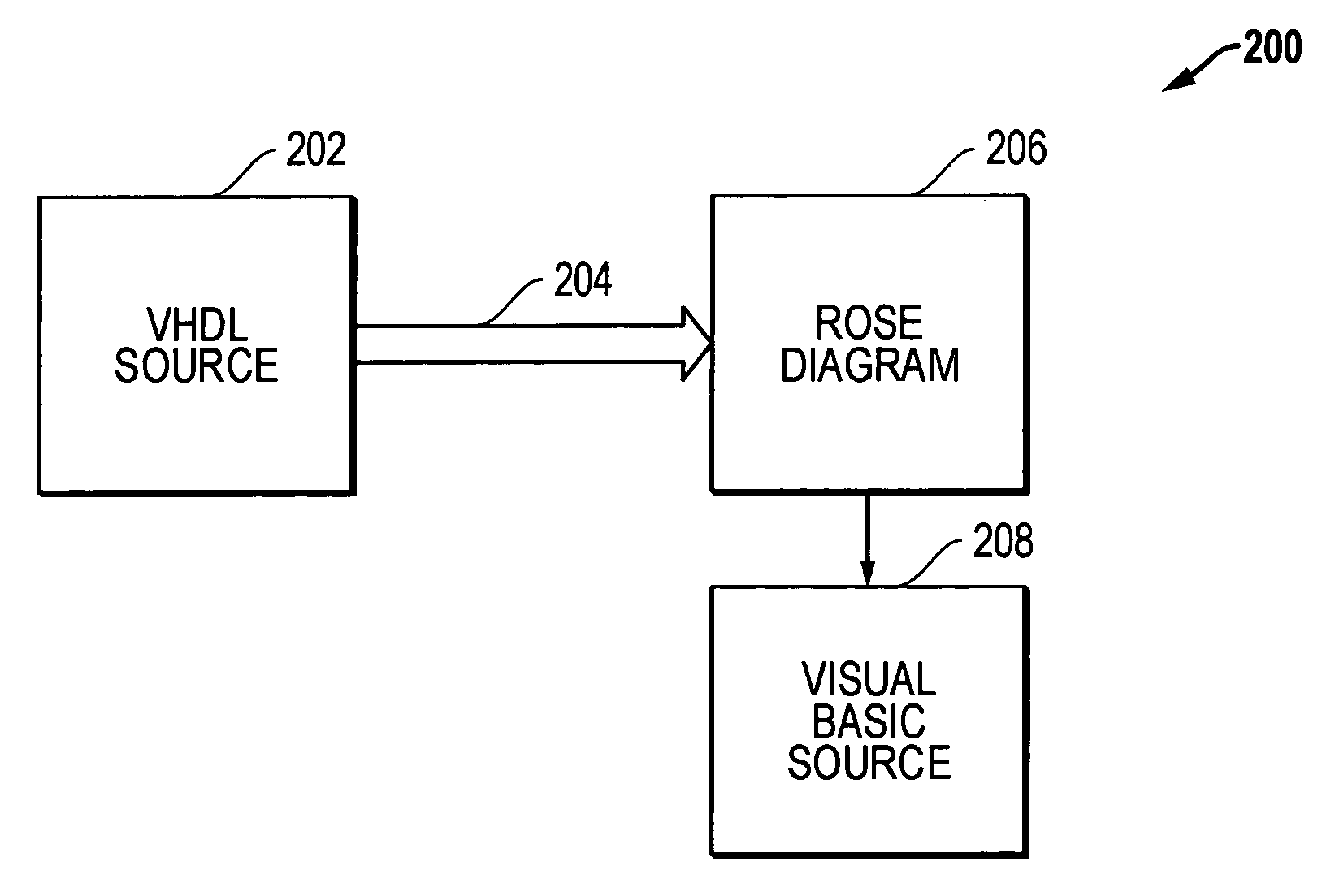

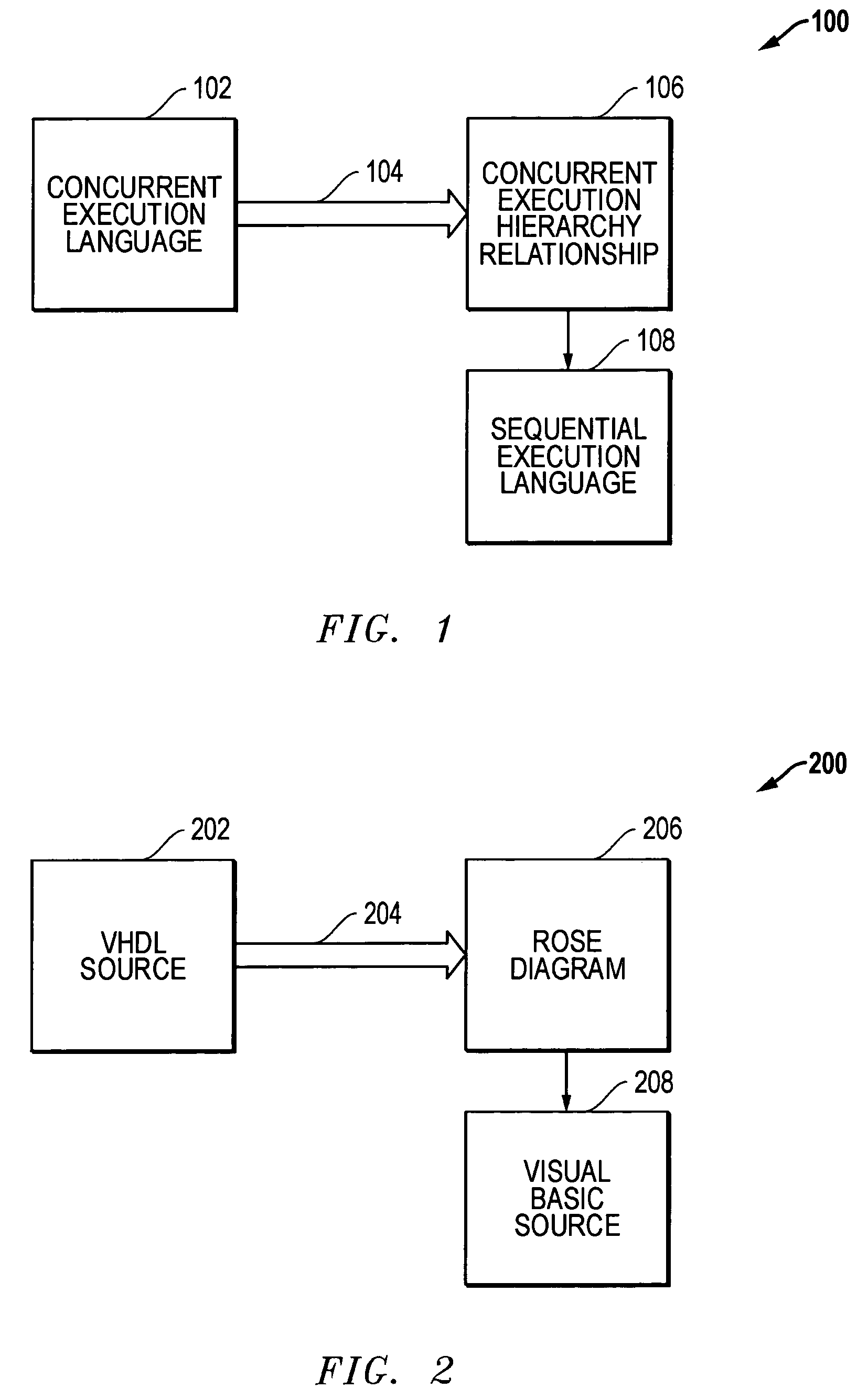

System and method of universal programming language conversion

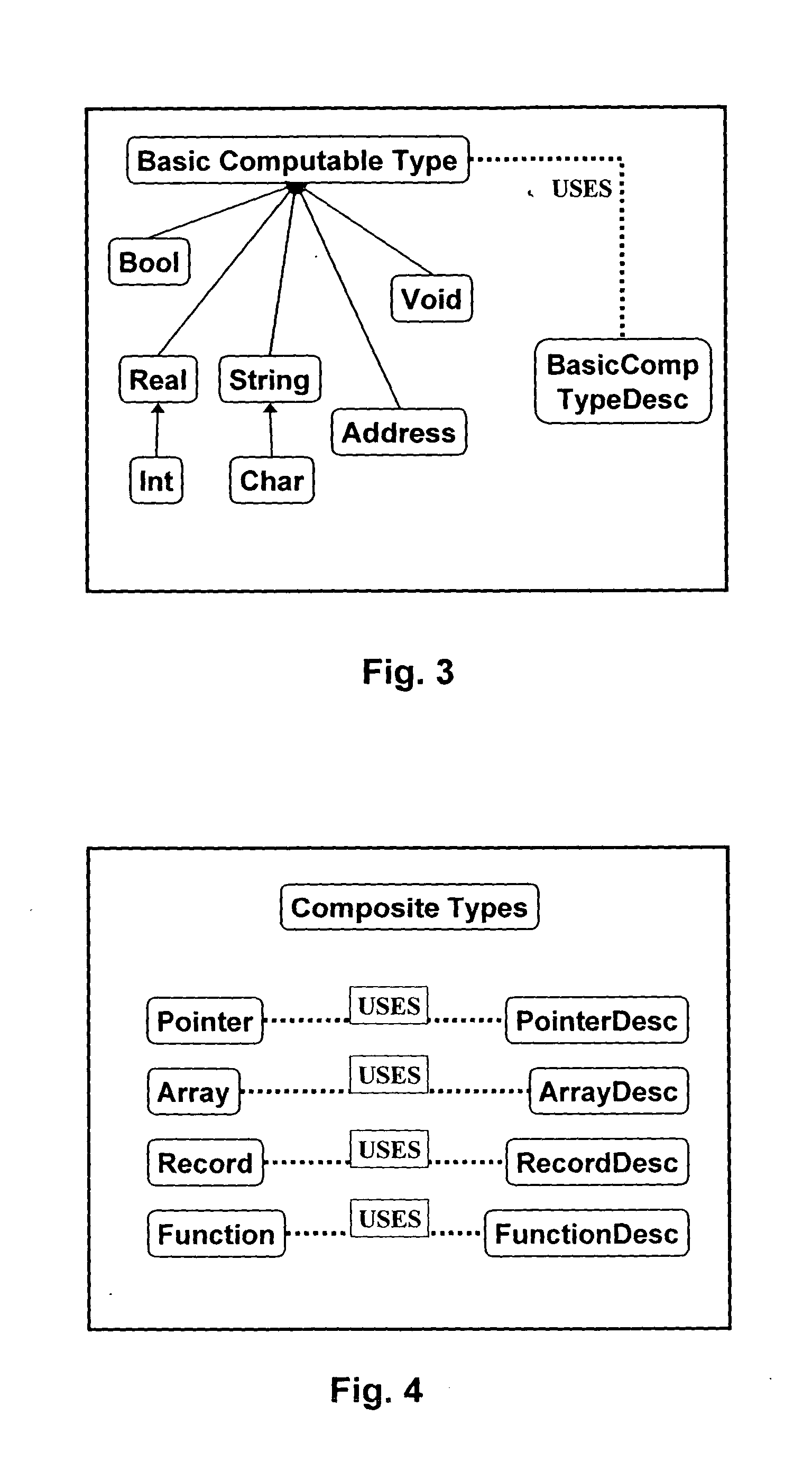

InactiveUS20050050525A1Specific program execution arrangementsMemory systemsSemantic representationGoal programming

An apparatus and method for universal programming language conversion between two different sequential programming languages, e.g., sequential procedural and sequential object oriented programming languages. In particular, conversion is between a source program in a first programming language and a target program in a second programming language. Initially, the source program in the first programming language is parsed using a parsing interface specific to the first programming language. All syntax from the parsed source program is then stripped or removed. Classes in a framework are instantiated to capture semantics of the parsed source program independent of syntax and execution model of the sequential programming languages. The classes are C++ classes representing fundamental core constructs of all sequential programming languages. A semantic representation of the parsed source program without any syntax is produced. The semantic representation is received at a printer interface specific to the second programming language and syntax of the target program in the second programming language is added. This same process can be used for either high-level conversion or compilation depending on whether the target programming language is high level or low level, respectively.

Owner:TECH MAHINDRA INDIA

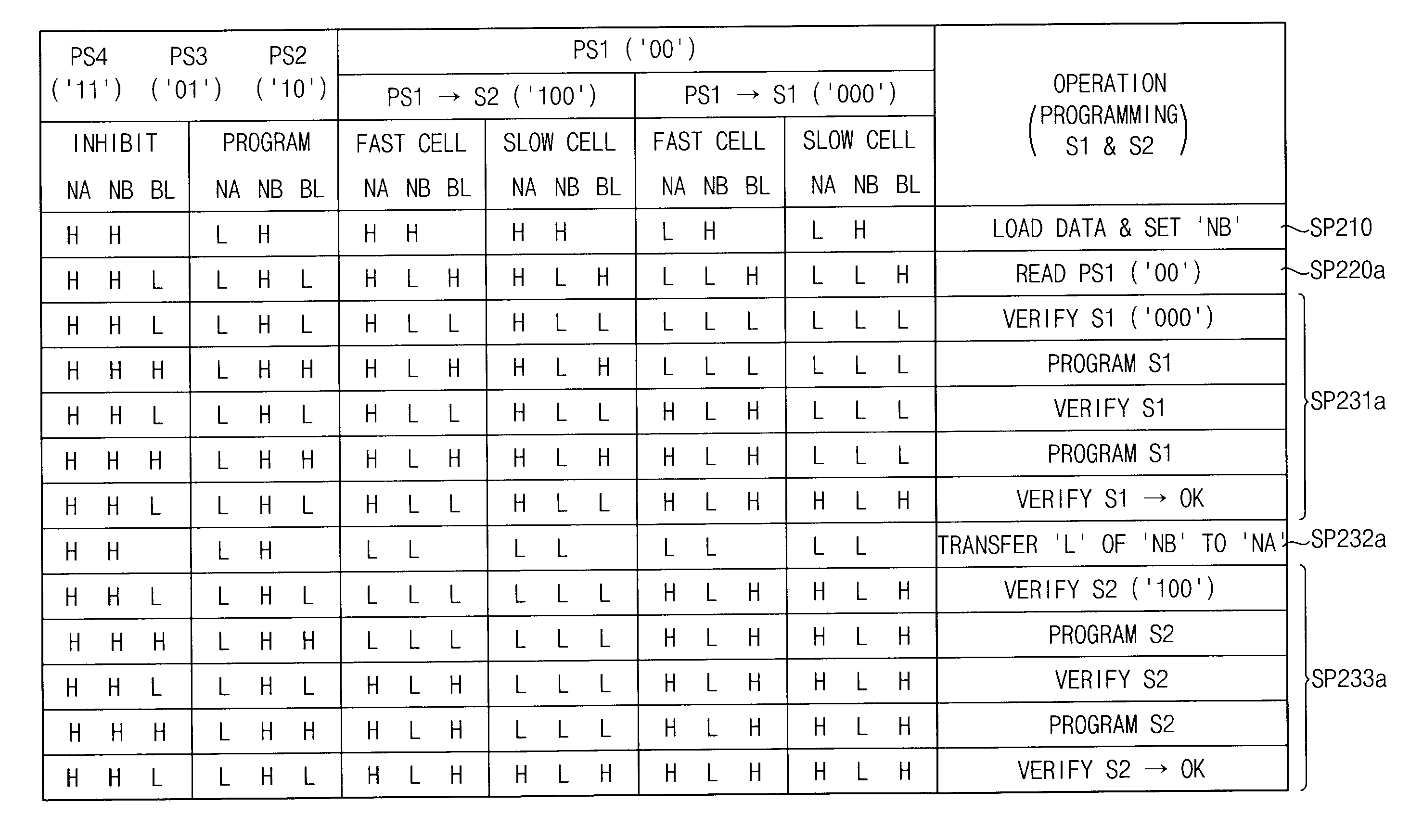

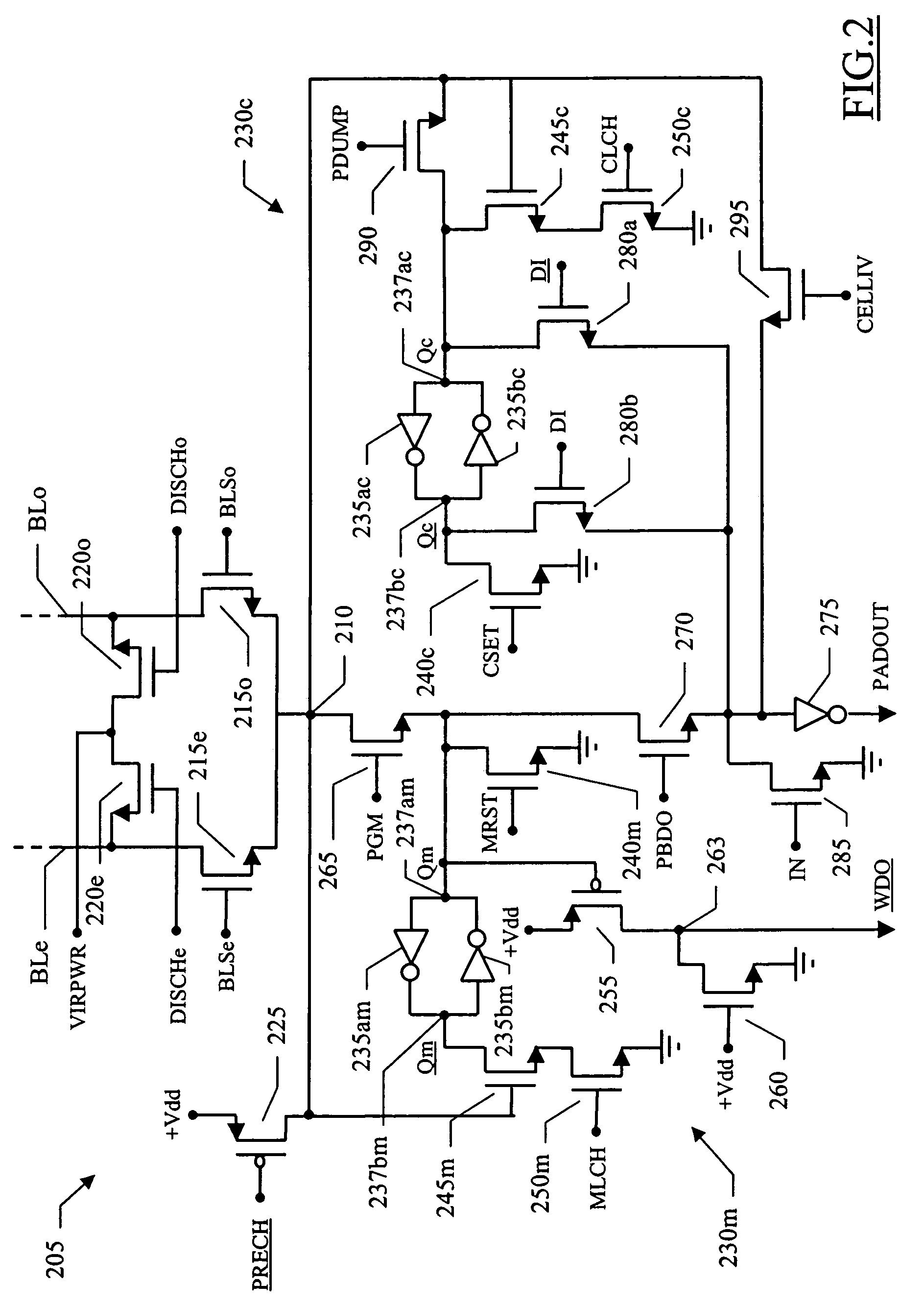

Method of programming multi-level cells and non-volatile memory device including the same

InactiveUS20080144370A1Avoid verification processShorten programming timeRead-only memoriesDigital storageSequential programmingComputer science

A non-volatile memory device has multi-level cells (MLCs), which are programmed such that one page is written in the MLCs having previous states corresponding to at least one previous page. The non-volatile memory device includes a memory cell array, a row selection circuit and a page buffer block. The memory cell array includes the MLCs commonly coupled to a selected word line and respectively coupled to bitlines. The row selection circuit applies sequentially-decreasing read voltages to the selected wordline to read the previous states of the MLCs, and sequentially-decreasing verification voltages to the selected wordline to program states of the MLCs sequentially from a state having a highest threshold voltage to a state having a lowest threshold voltage. The page buffer block loads data corresponding to the one page, and controls a bitline voltage based on each previous state and each bit of the loaded data.

Owner:SAMSUNG ELECTRONICS CO LTD

NAND type flash EEPROM in which sequential programming process is performed by using different intermediate voltages

A nonvolatile semiconductor memory device includes a NAND memory cell array, booster circuit, row decoder, bit line control circuit and column decoder. In the device, the magnitude of intermediate voltage applied to the control gates of memory transistors from the booster circuit via the row decoder is changed according to the position of a selected control gate line when data is sequentially programmed into the memory transistors in the memory cell array. Alternatively, a plurality of different intermediate voltages are applied when data is simultaneously programmed into memory transistors connected to the selected control gate line.

Owner:KIOXIA CORP

System and method of universal programming language conversion

InactiveUS7272821B2Specific program execution arrangementsMemory systemsSemantic representationSequential programming

An apparatus and method for universal programming language conversion between two different sequential programming languages, e.g., sequential procedural and sequential object oriented programming languages. In particular, conversion is between a source program in a first programming language and a target program in a second programming language. Initially, the source program in the first programming language is parsed using a parsing interface specific to the first programming language. All syntax from the parsed source program is then stripped or removed. Classes in a framework are instantiated to capture semantics of the parsed source program independent of syntax and execution model of the sequential programming languages. The classes are C++ classes representing fundamental core constructs of all sequential programming languages. A semantic representation of the parsed source program without any syntax is produced. The semantic representation is received at a printer interface specific to the second programming language and syntax of the target program in the second programming language is added. This same process can be used for either high-level conversion or compilation depending on whether the target programming language is high level or low level, respectively.

Owner:TECH MAHINDRA INDIA

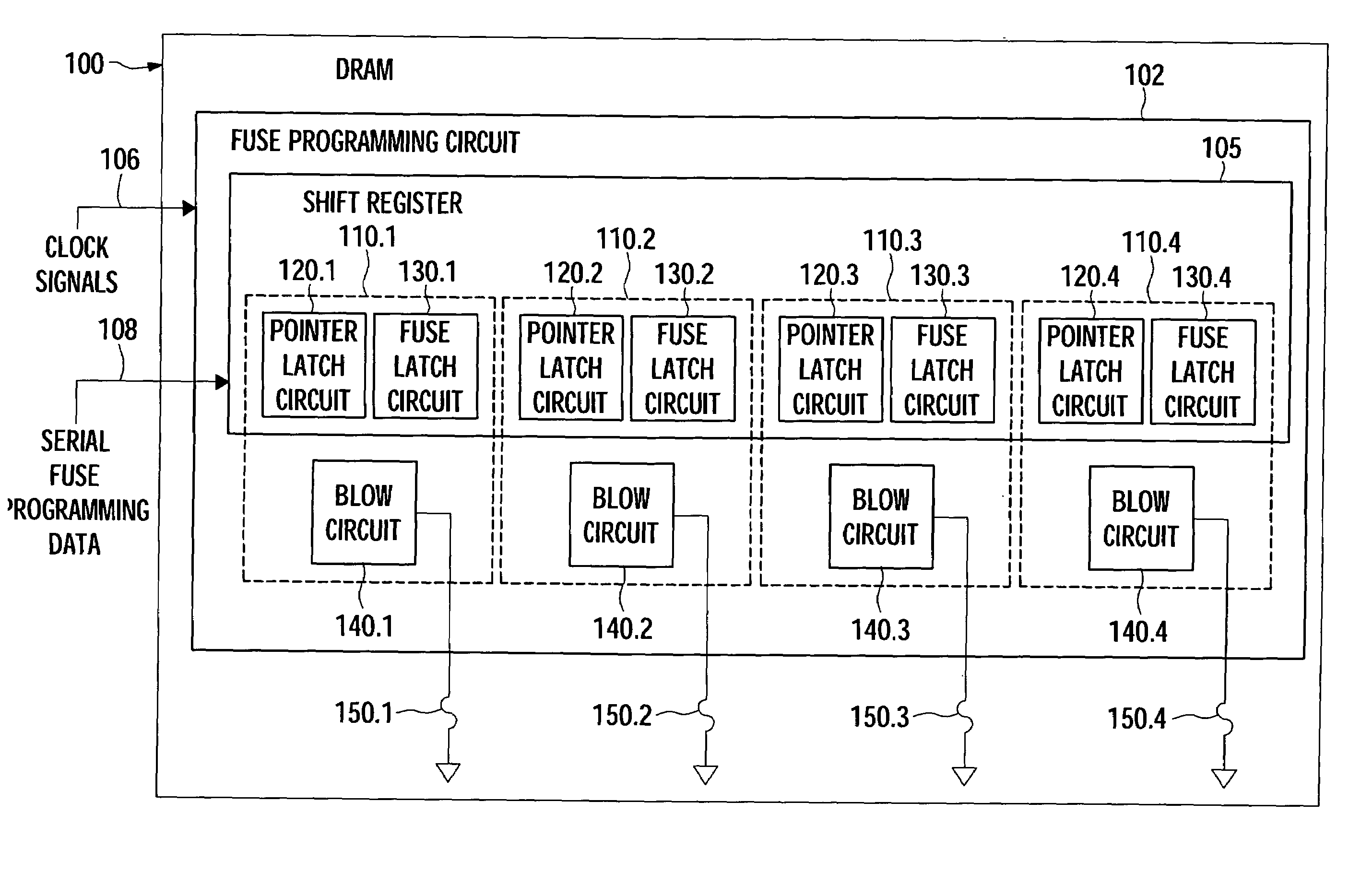

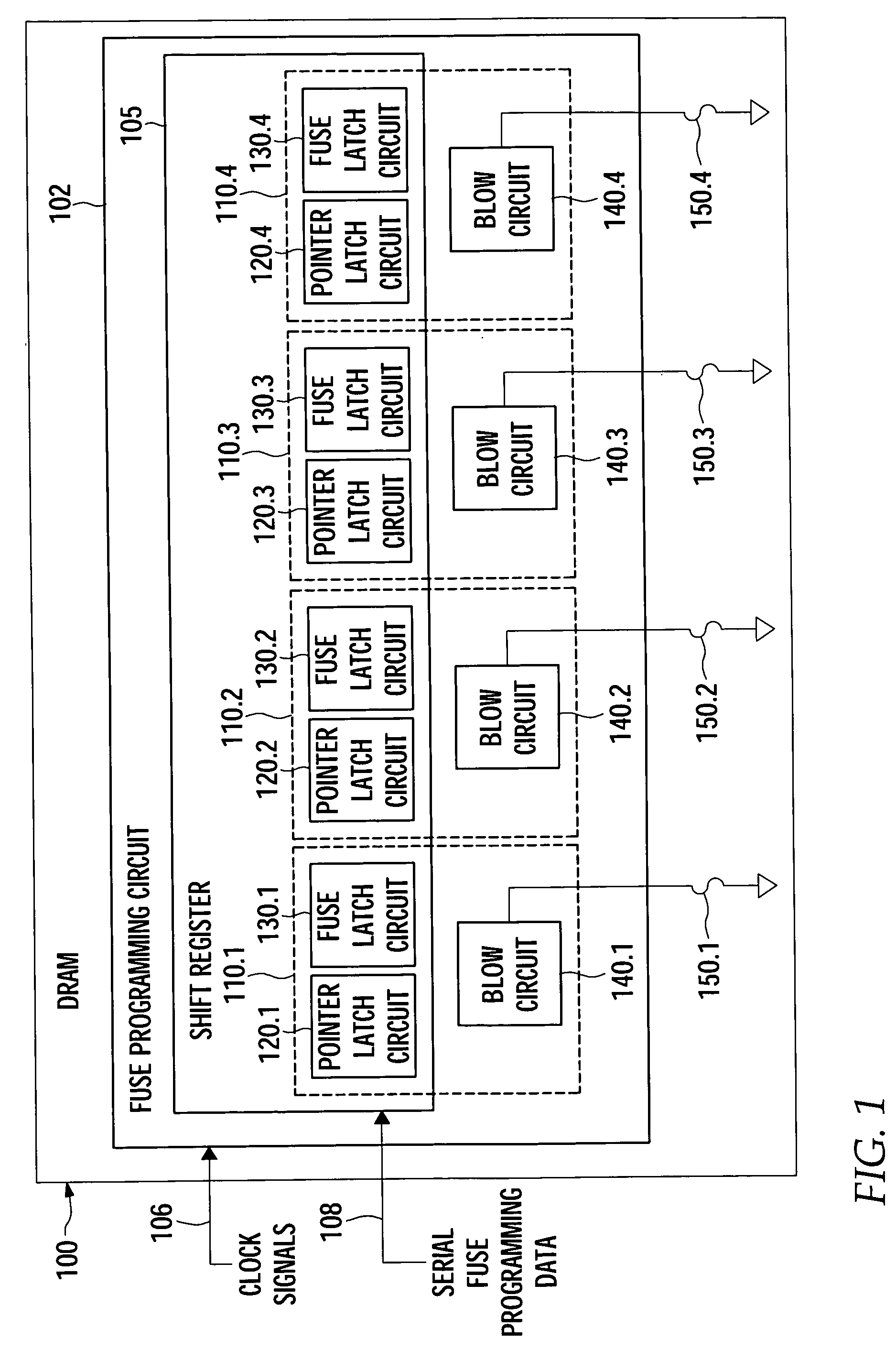

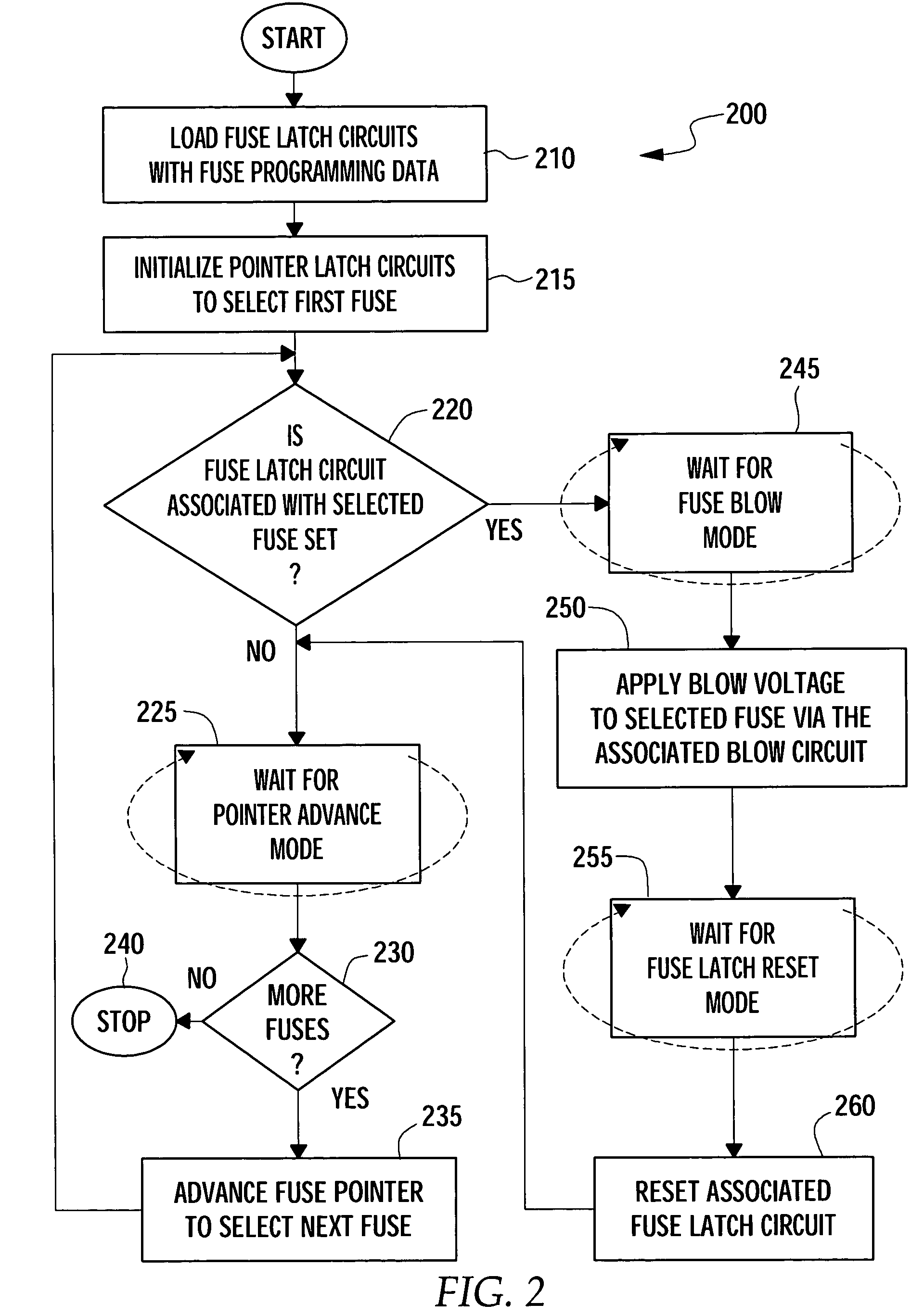

Externally clocked electrical fuse programming with asynchronous fuse selection

Embodiments are provided in which a method and an apparatus for sequentially programming electrical fuses are described. A fuse pointer is advanced to point to (i.e., select) the fuses sequentially. When the fuse pointer reaches (i.e., points to) a fuse that is not to be blown, the fuse pointer automatically and asynchronously (e.g. not synchronized to a programming clock signal) skips the fuse. On the other hand, when the fuse pointer reaches a fuse that is to be blown, the fuse pointer stops and the fuse is blown synchronously (e.g., in response to the programming clock signal). After the blow, the fuse pointer advances to the next fuse and the process described above repeats, until the last fuse is programmed. A fuse latch circuit associated with the blown fuse may be optionally reset prior to advancing the fuse pointer.

Owner:POLARIS INNOVATIONS

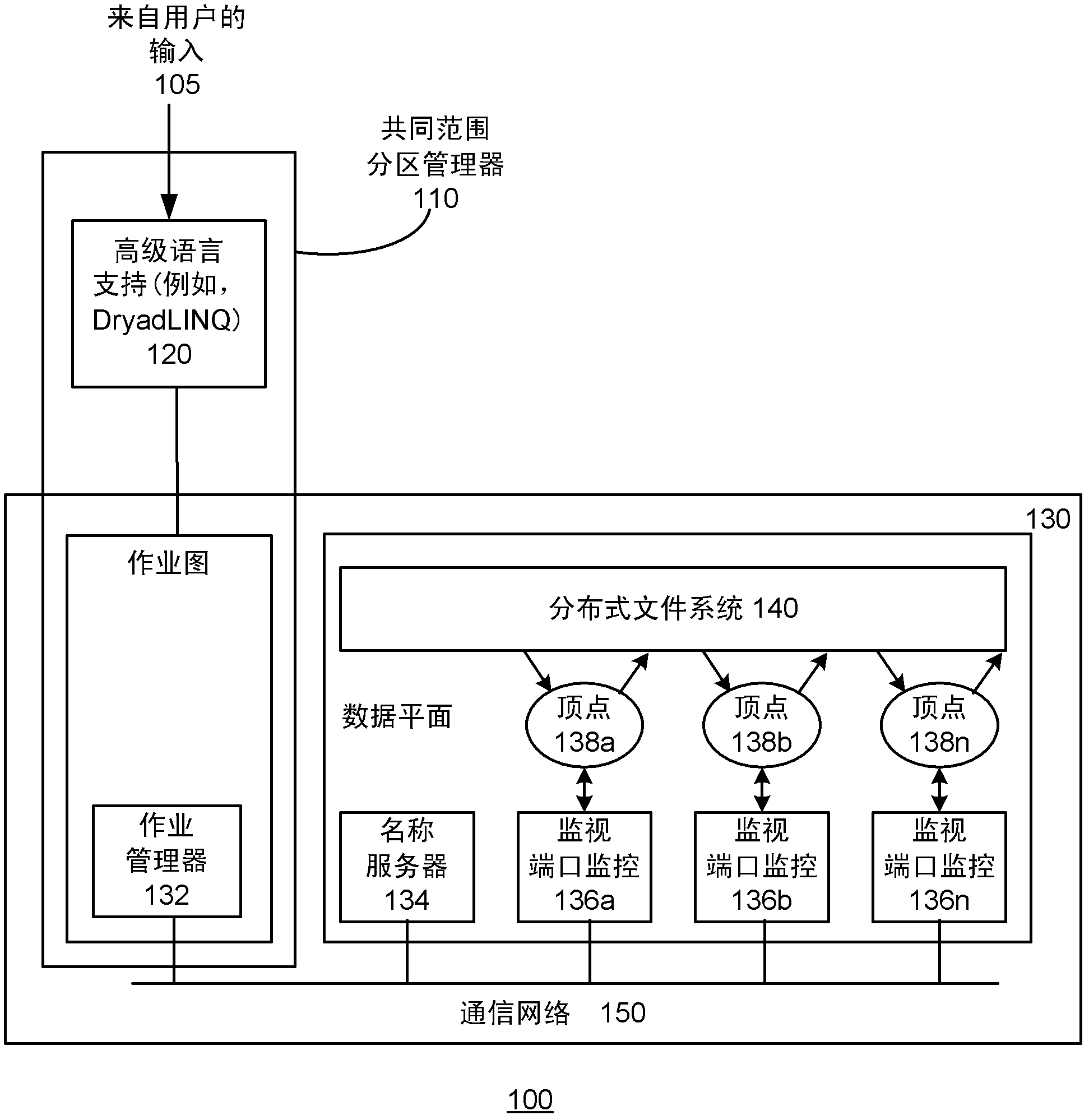

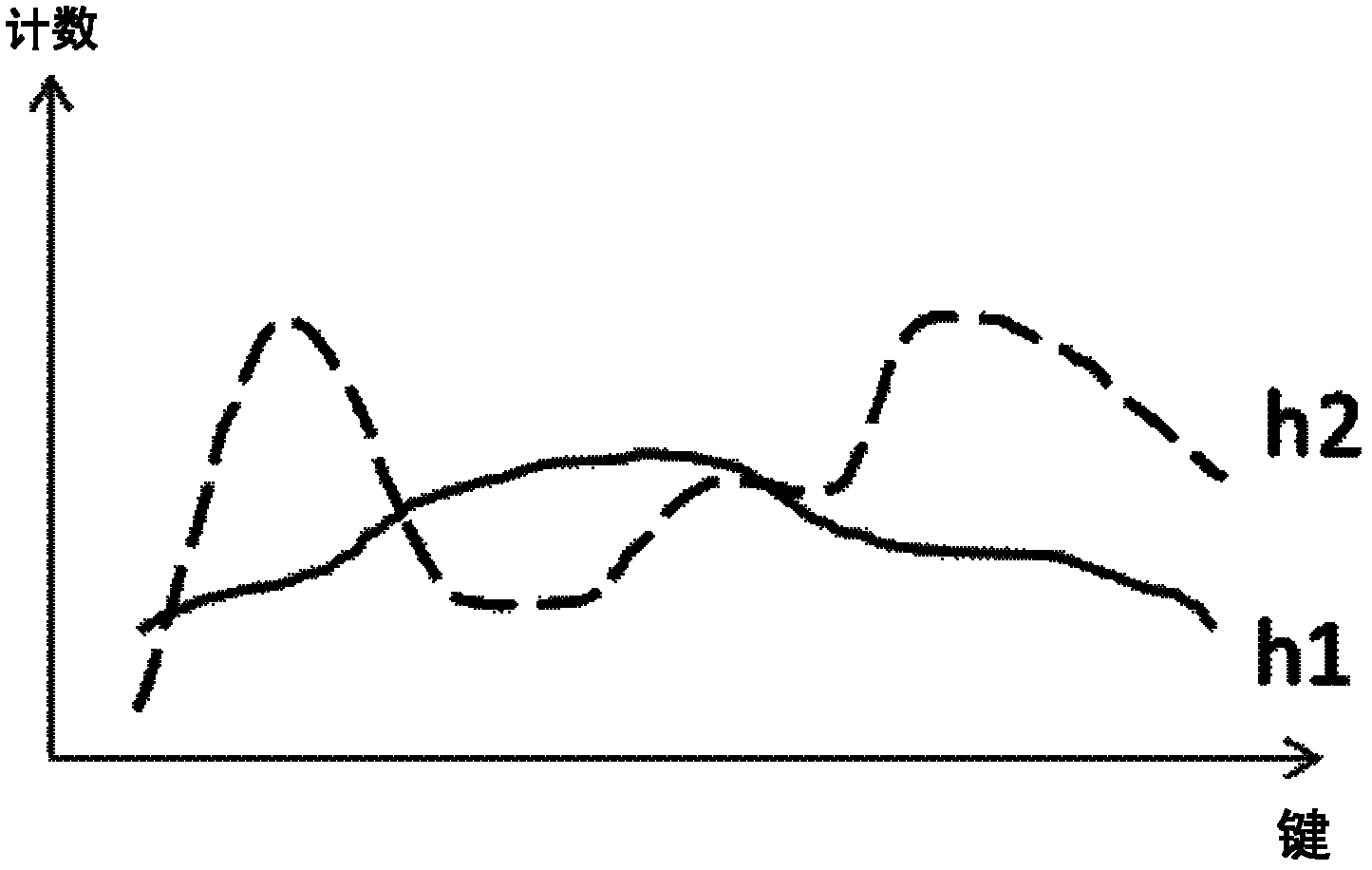

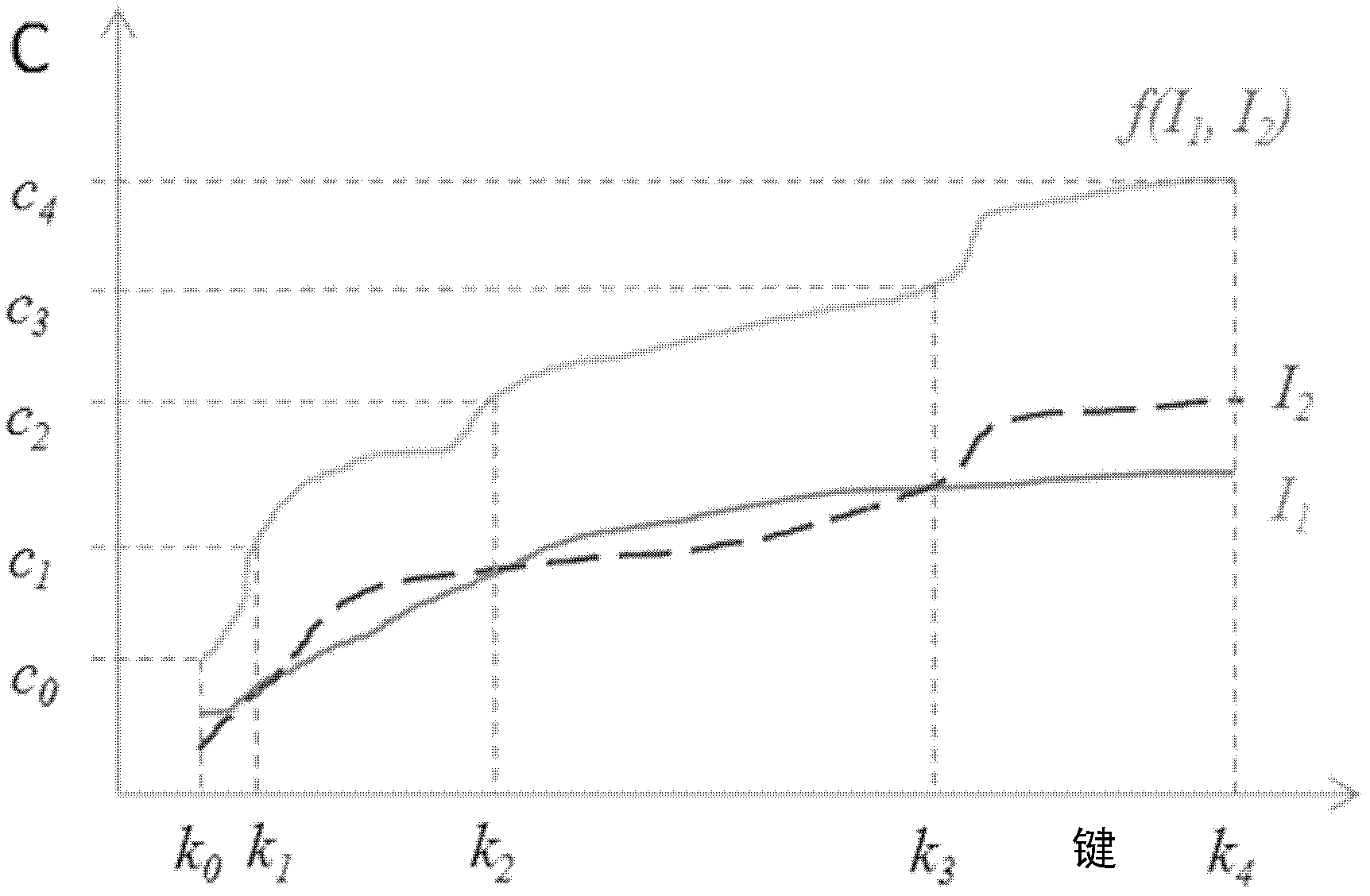

Co-range partition for query plan optimization and data-parallel programming model

The invention relates to a co-range partition for query plan optimization and data-parallel programming model. A co-range partitioning scheme that divides multiple static or dynamically generated datasets into balanced partitions using a common set of automatically computed range keys. A co-range partition manager minimizes the number of data partitioning operations for a multi-source operator (e.g., join) by applying a co-range partition on a pair of its predecessor nodes as early as possible in the execution plan graph. Thus, the amount of data being transferred is reduced. By using automatic range and co-range partition for data partitioning tasks, a programming API is enabled that abstracts explicit data partitioning from users to provide a sequential programming model for data-parallel programming in a computer cluster.

Owner:MICROSOFT TECH LICENSING LLC

Method and apparatus for managing open blocks in nonvolatile memory device

ActiveUS8526245B2Improve reliabilityInput/output to record carriersMemory adressing/allocation/relocationControl storeSequential programming

A memory system comprises a multi-bit memory device and a memory controller that controls the multi-bit memory device. The memory system determines whether a requested program operation is a random program operation or a sequential program operation. Where the requested program operation is a random program operation, the memory controller controls the multi-bit memory device to perform operations according to a fine program close policy or a fine program open policy.

Owner:SAMSUNG ELECTRONICS CO LTD

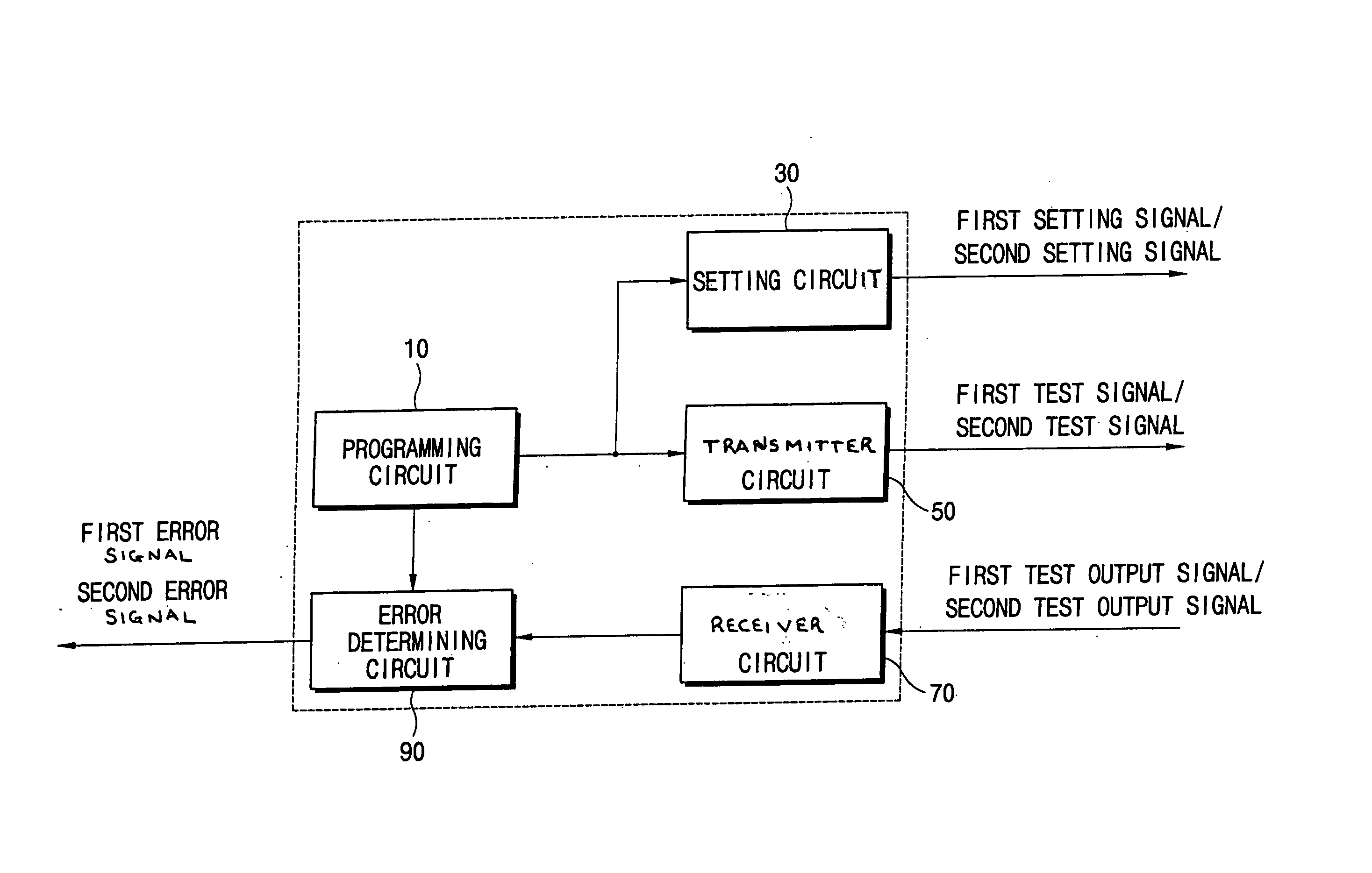

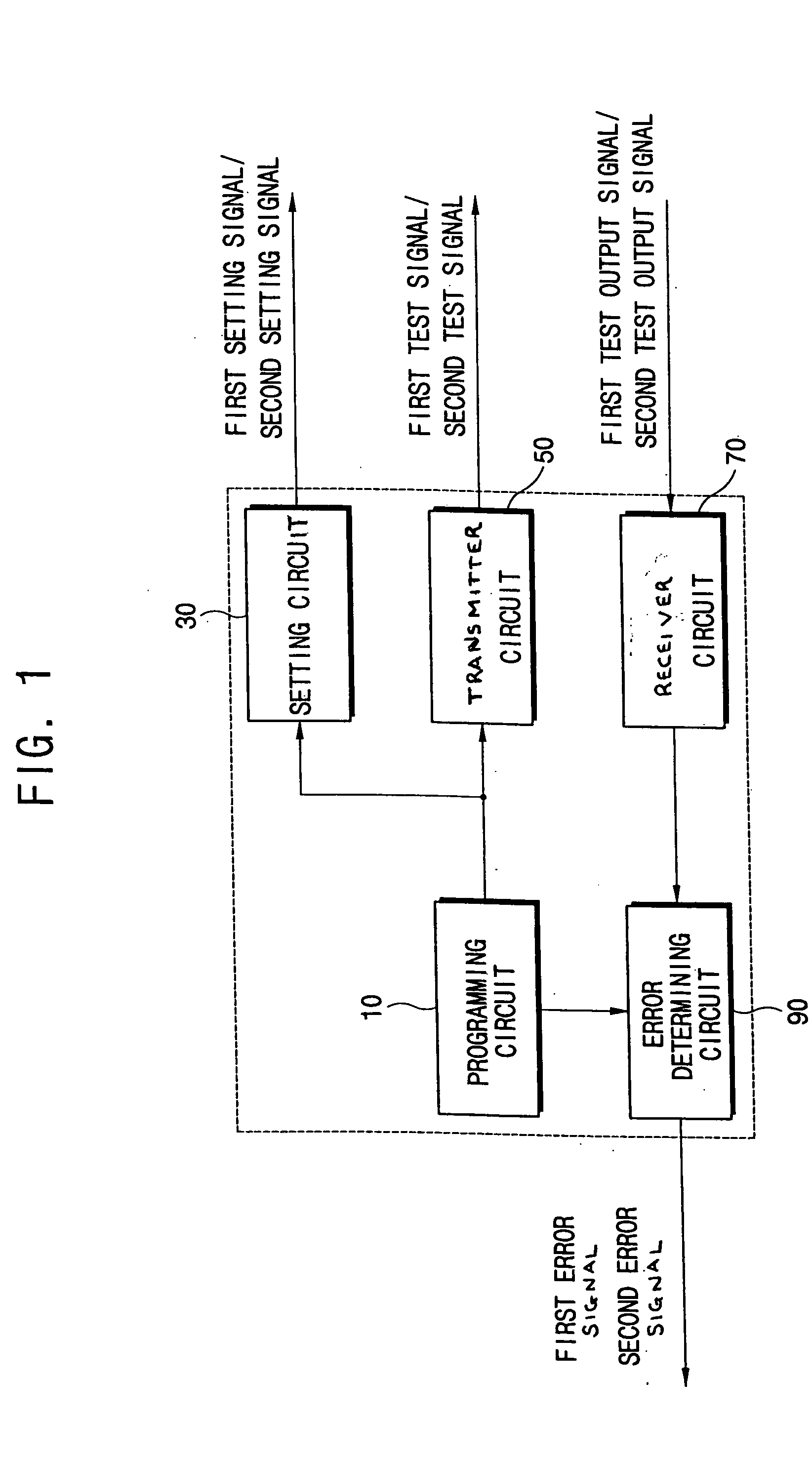

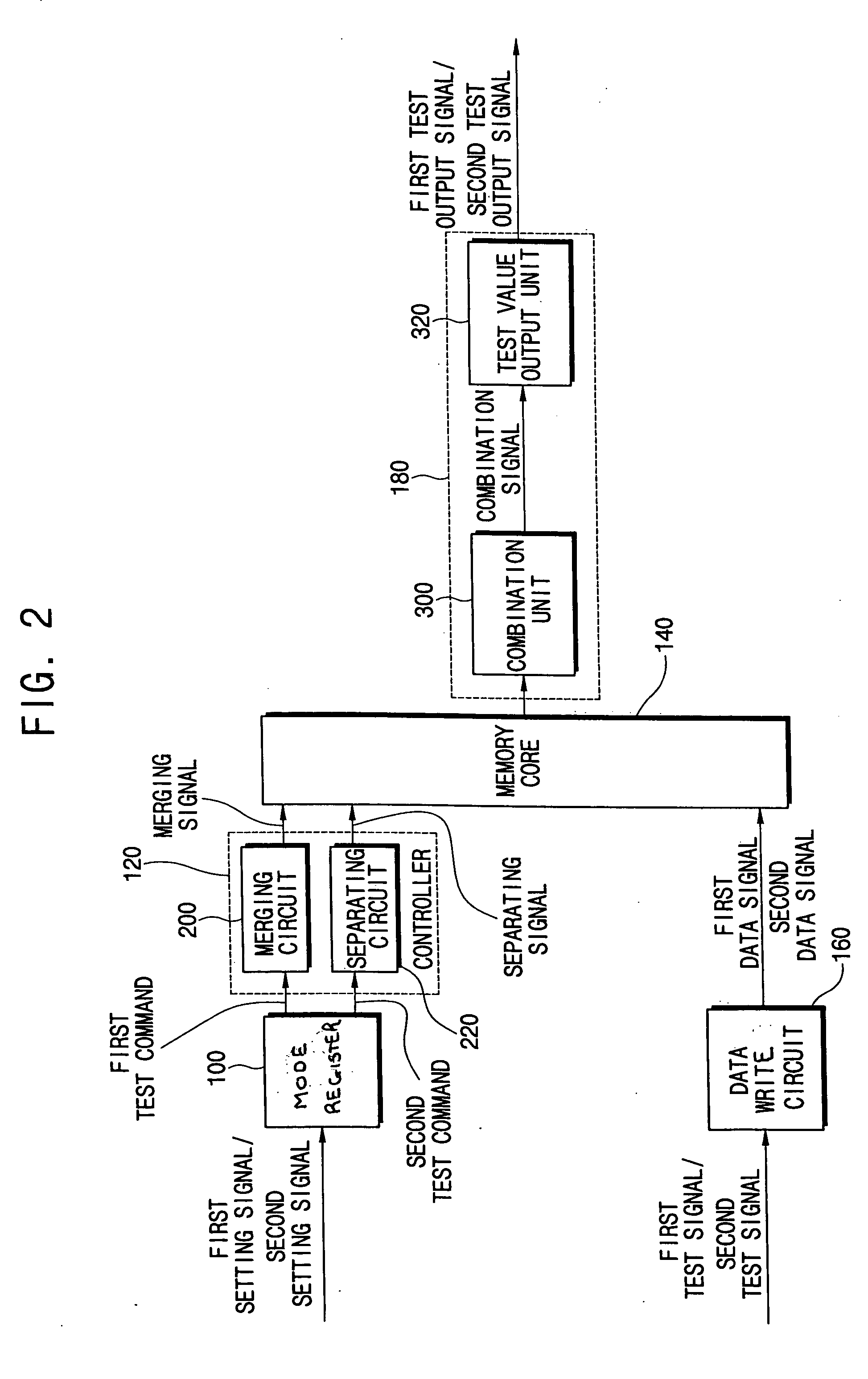

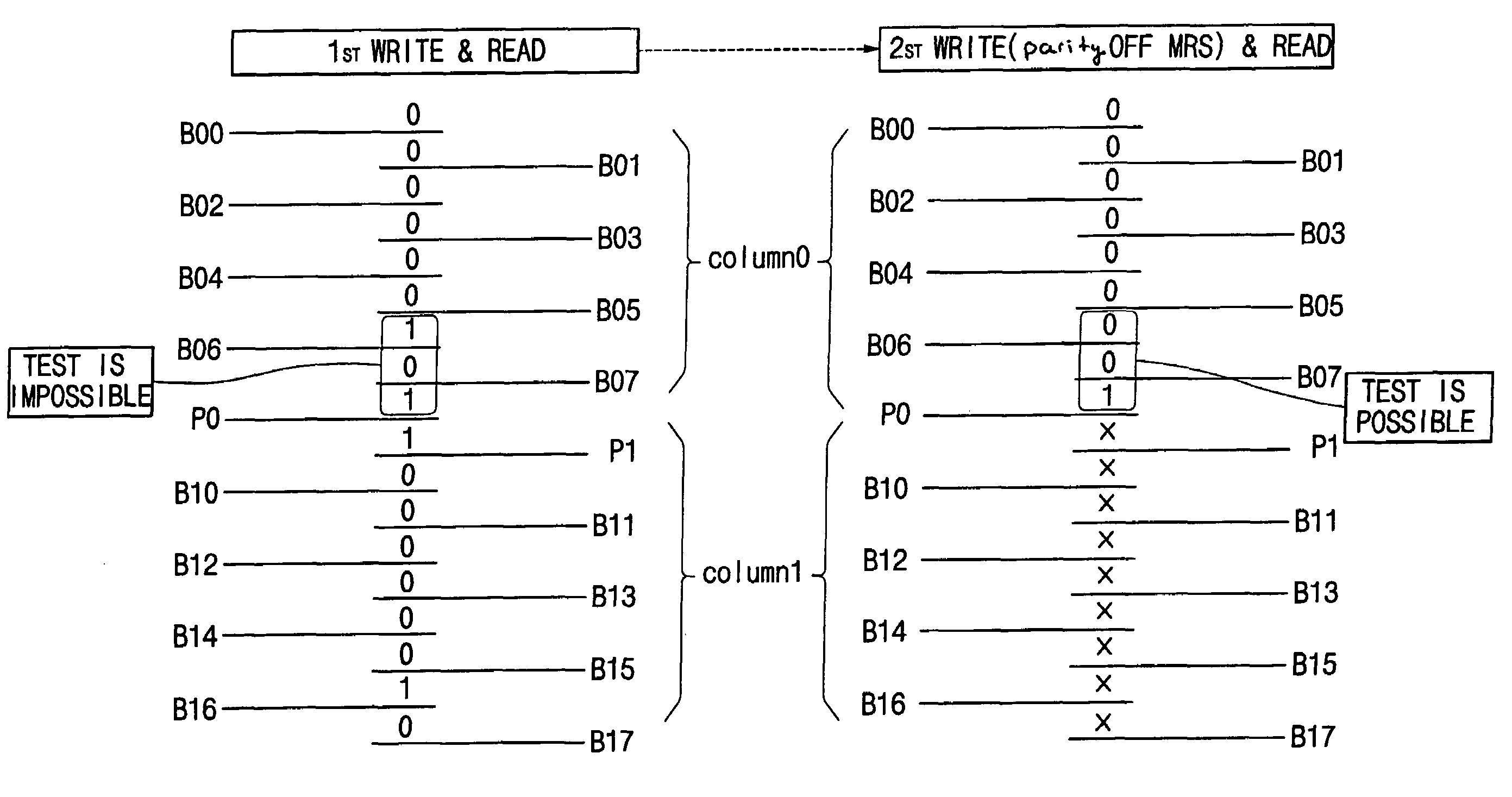

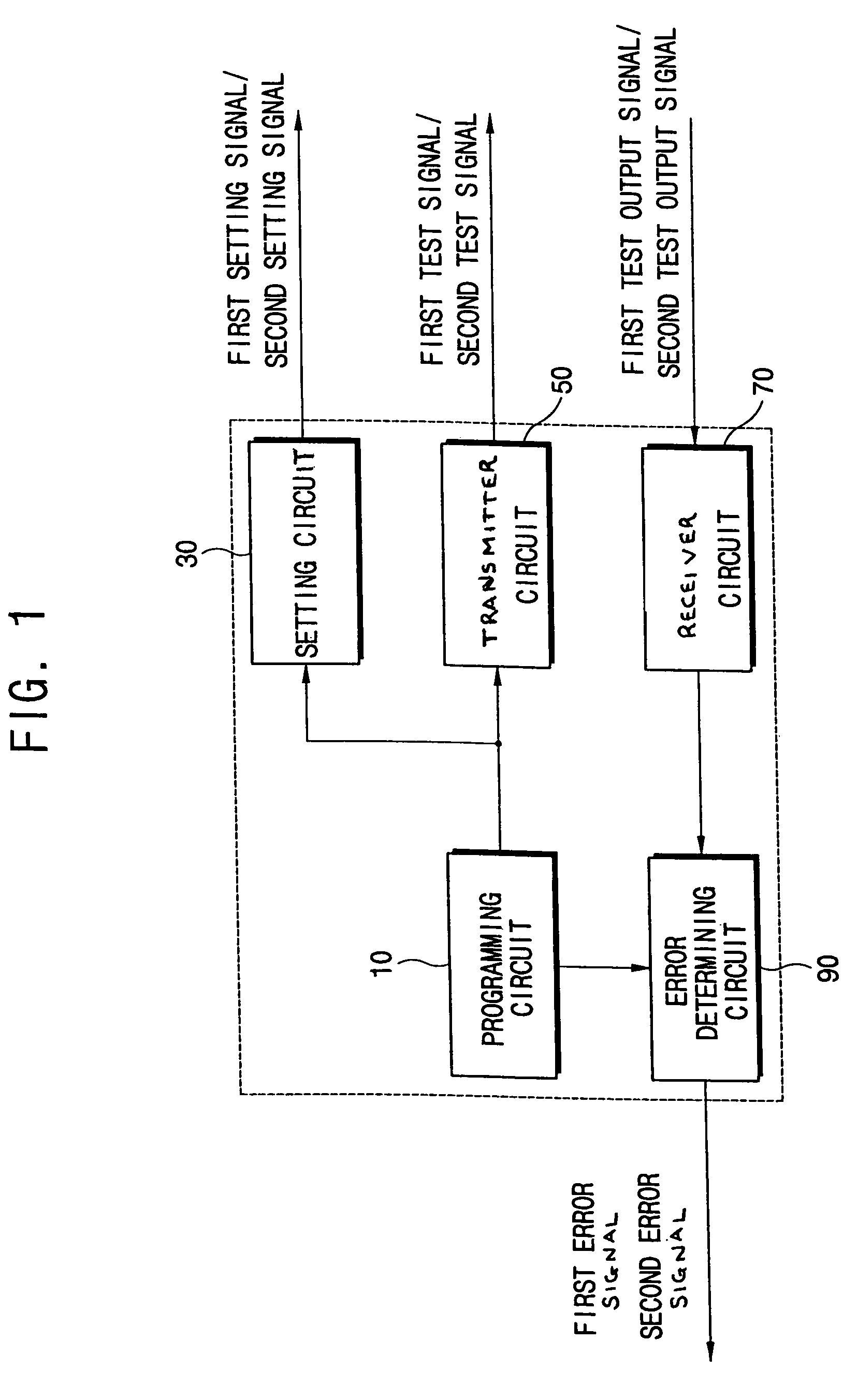

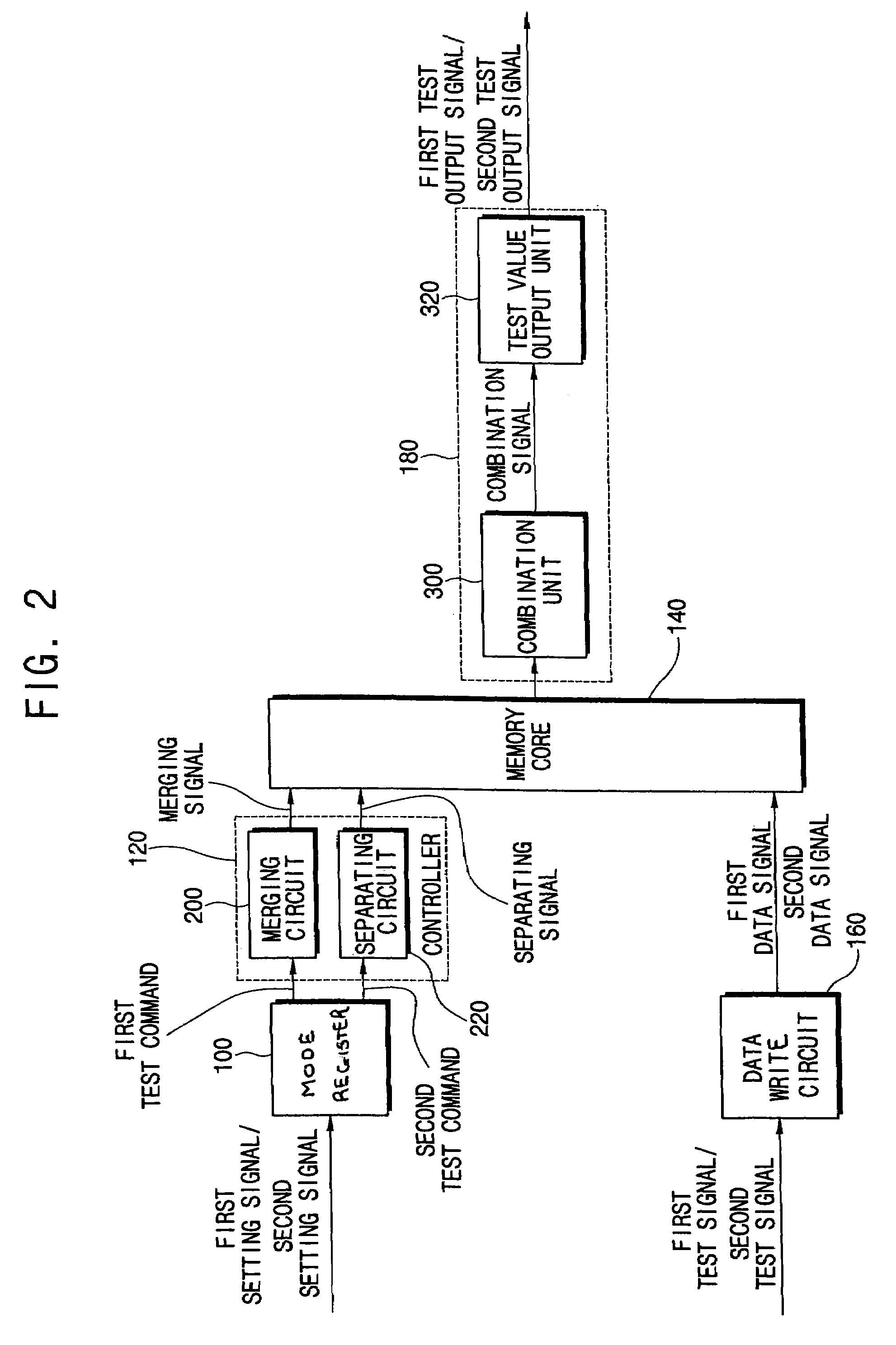

Method and apparatus for testing semiconductor memory device and related testing methods

ActiveUS20050102595A1Electronic circuit testingError detection/correctionBit lineSequential programming

A test method and apparatus for a semiconductor memory device is characterized by the sequentially programmed use of two test different modes. A first test mode tests at least signal line integrity for the semiconductor memory device by testing a merged set of bits line. The second test mode further tests at least signal line integrity after first separating the merged bits lines. Logical combination of test data derived from the first and second test modes are used to generate error detection signals. At least one bit line associated with a parity bit is preferable merged and separated in the foregoing approach.

Owner:SAMSUNG ELECTRONICS CO LTD

Flash memory system control scheme

ActiveUS7802064B2Improve throughputHigh speed wear levelingMemory architecture accessing/allocationRead-only memoriesSequential programmingMemory controller

A Flash memory system architecture having serially connected Flash memory devices to achieve high speed programming of data. High speed programming of data is achieved by interleaving pages of the data to be programmed amongst the memory devices in the system, such that different pages of data are stored in different memory devices. A memory controller issues program commands for each memory device. As each memory device receives a program command, it either begins a programming operation or passes the command to the next memory device. Therefore, the memory devices in the Flash system sequentially program pages of data one after the other, thereby minimizing delay in programming each page of data into the Flash memory system. The memory controller can execute a wear leveling algorithm to maximize the endurance of each memory device, or to optimize programming performance and endurance for data of any size.

Owner:MOSAID TECH

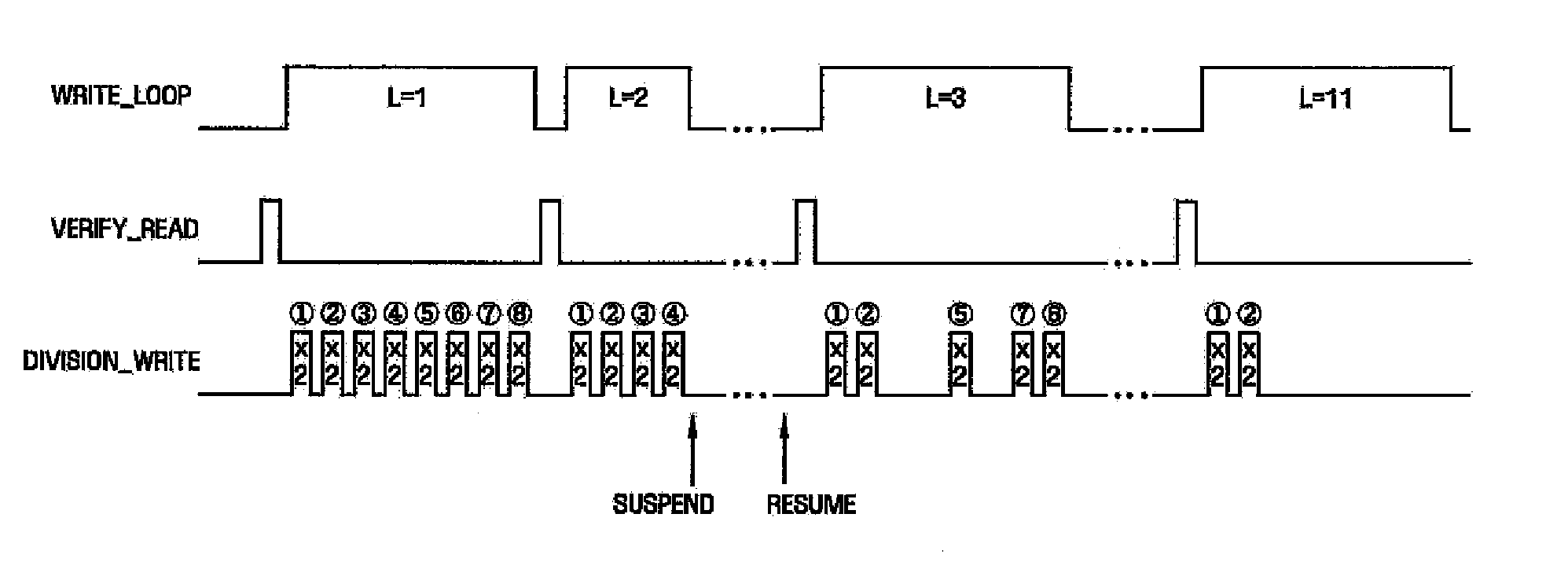

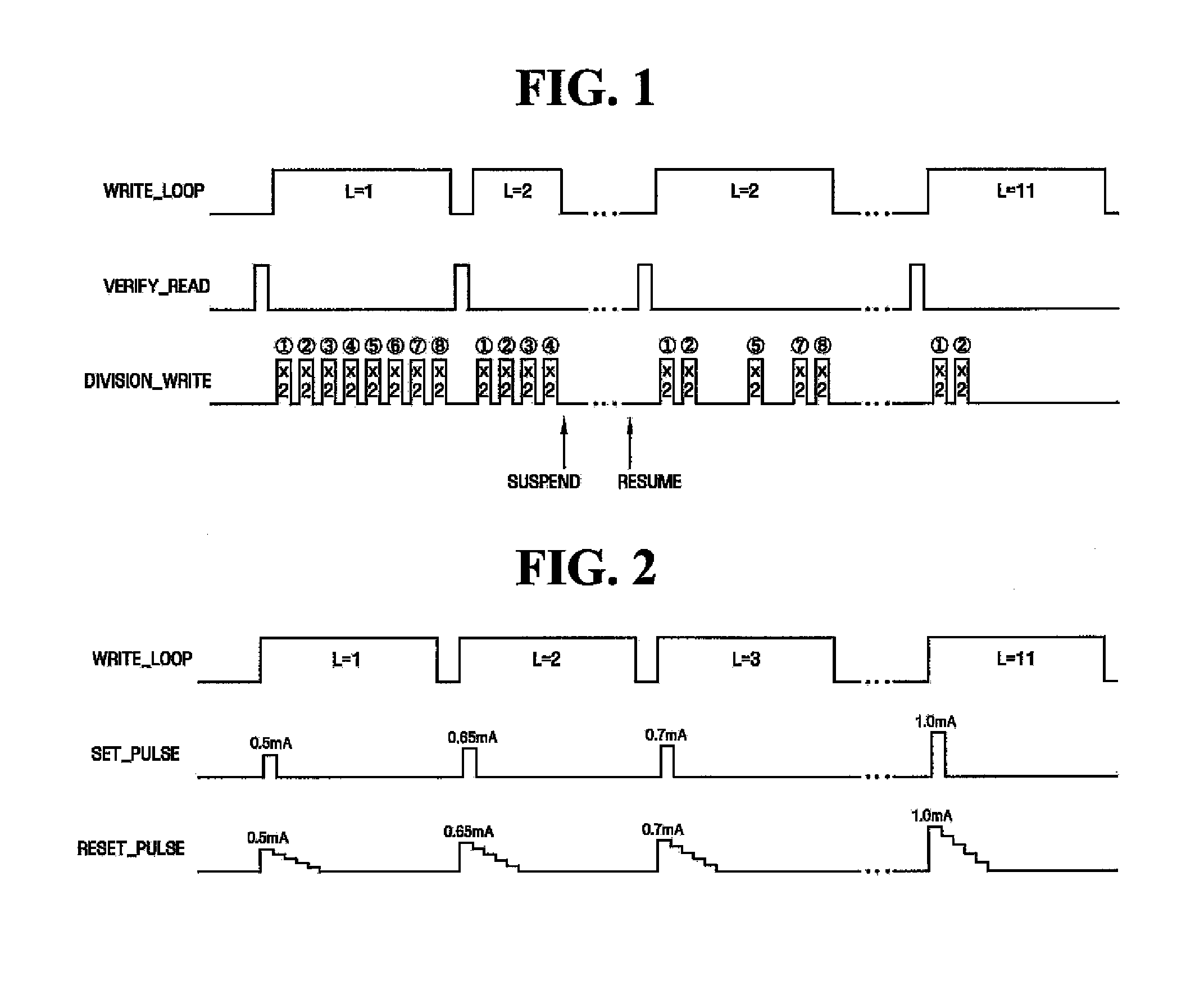

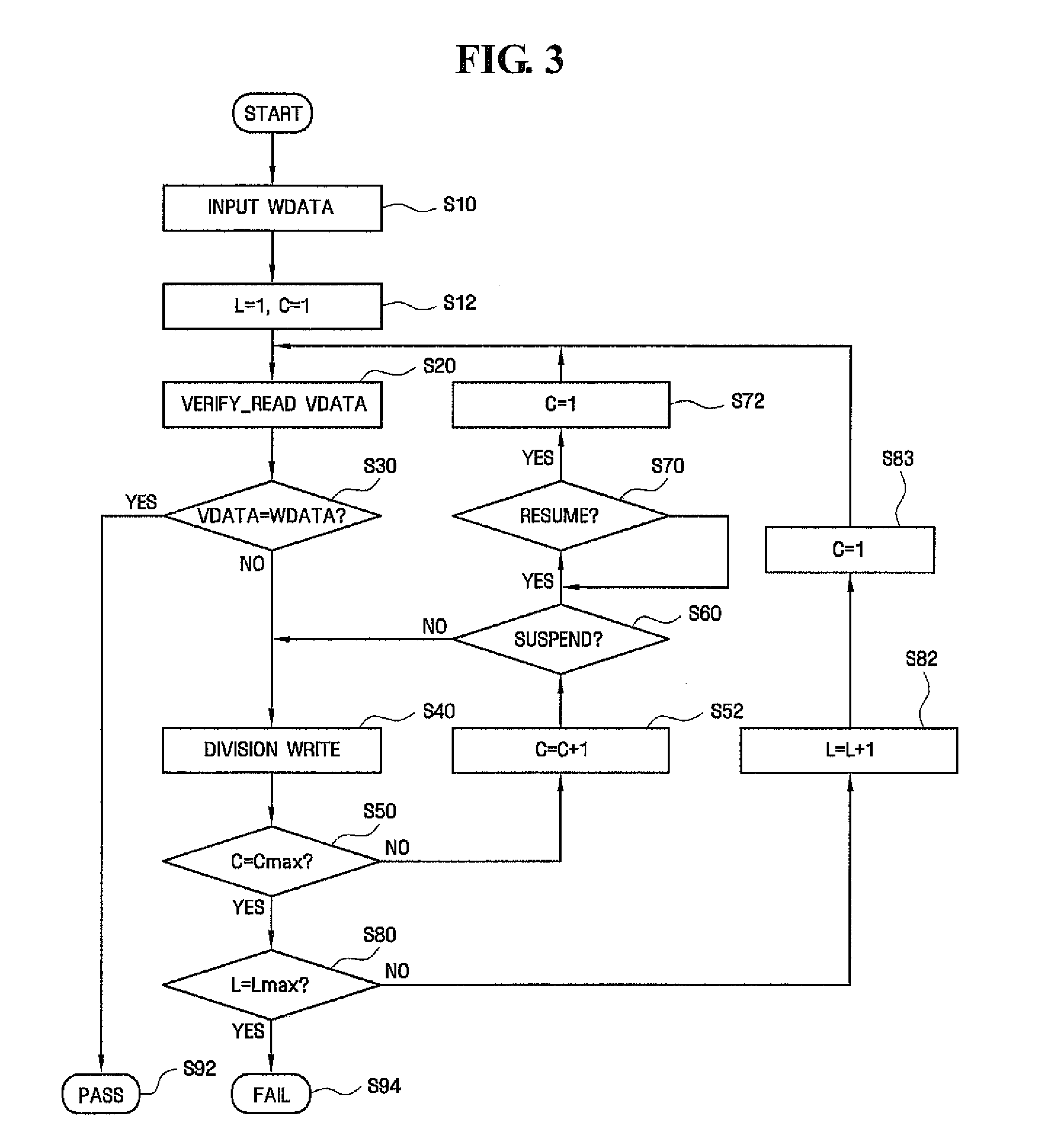

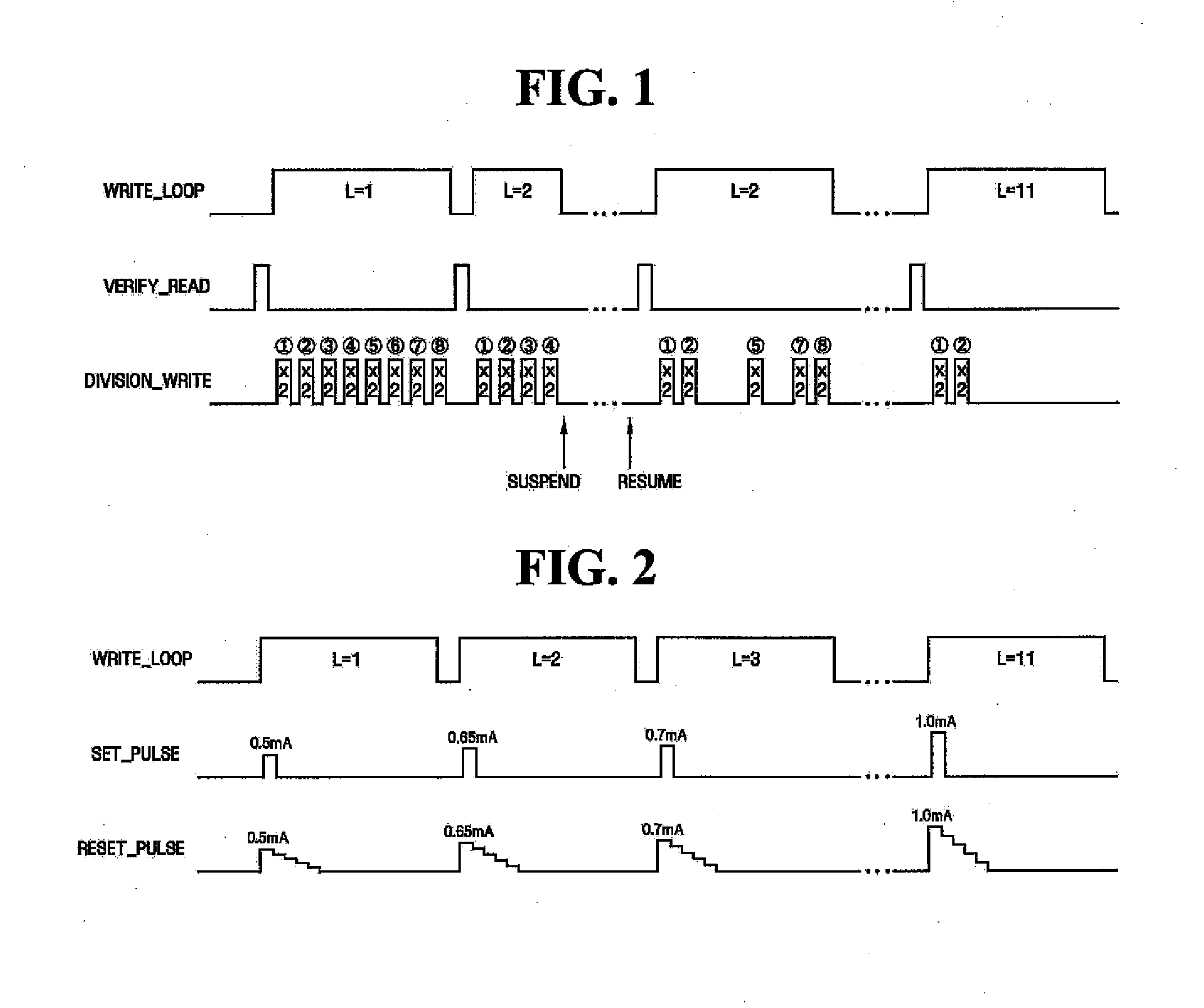

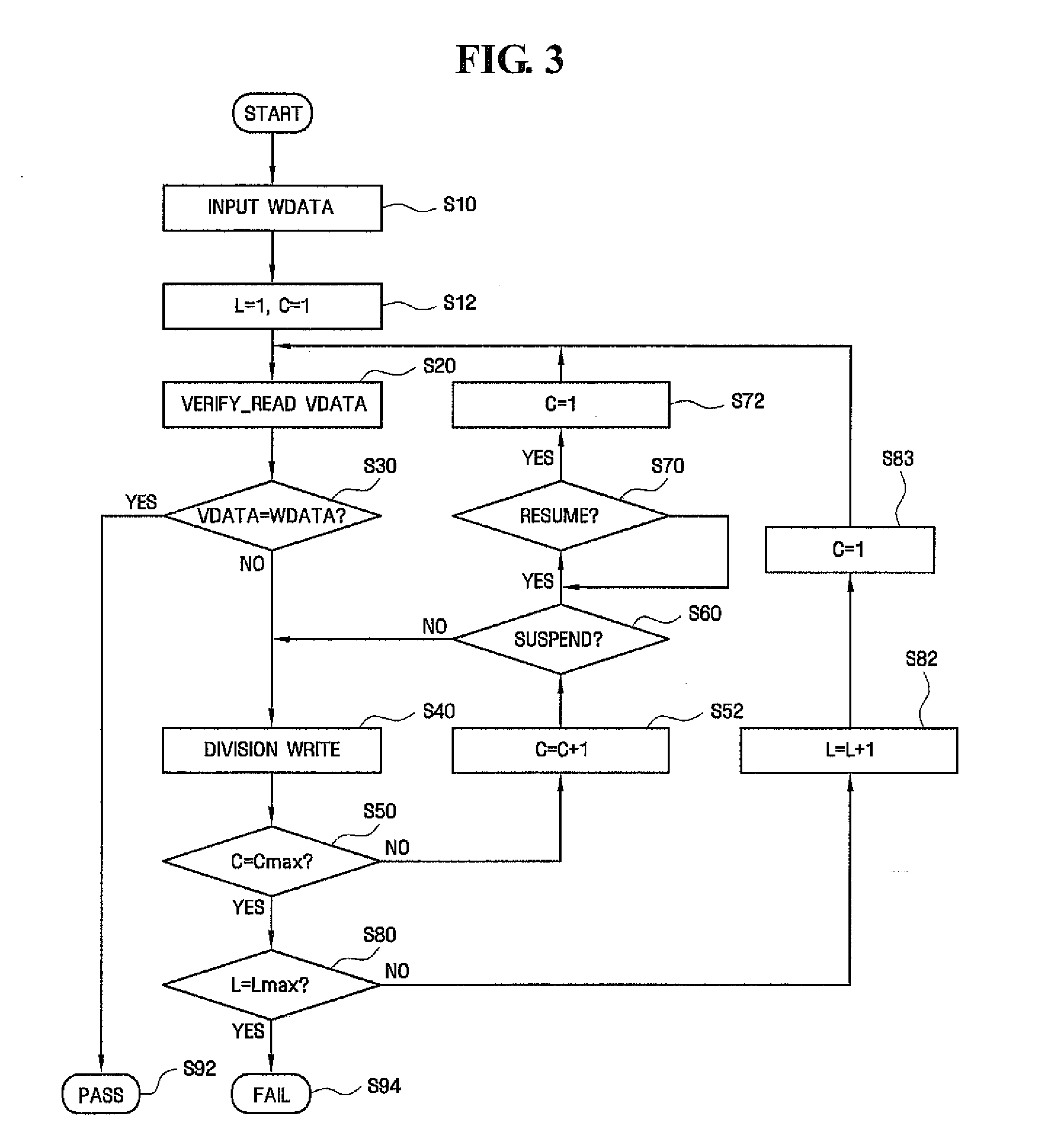

Phase change random access memory device and related methods of operation

A method of operating a phase change random access memory (PRAM) device comprises performing a program operation to store data in selected PRAM cells of the device, wherein the program operation comprises a plurality of sequential program loops. The method further comprises suspending the program operation in the middle of the program operation, and after suspending the program operation, resuming the program operation in response to a resume command.

Owner:SAMSUNG ELECTRONICS CO LTD

Multi-pass programming for memory with reduced data storage requirement

ActiveUS8130552B2Reduce impactRead-only memoriesDigital storageSequential programmingComputer science

Coupling effects between adjacent floating gates in a non-volatile storage device are reduced in a multi-pass programming operation, while reducing program data storage requirements. In one approach, storage elements are programmed in an out of sequence or zigzag word line order. A particular word line is programmed with a coarse program pass, after which another word line is programmed with a fine program pass, after which the particular word line is read. The particular word line is read before another word line is programmed with a coarse program pass which causes coupling interference to storage elements of the particular word line. The read data is subsequently used to perform a fine program pass for the particular word line. This avoids the need to store program data of multiple word lines concurrently, so that storage hardware can be reduced in size along with power consumption.

Owner:SANDISK TECH LLC

Sequential program-verify method with result buffering

ActiveUS7184310B2Shorten the lengthImprove product processing performanceRead-only memoriesDigital storageNon complianceComputer architecture

A sequential program-verify method is used in a non-volatile memory device including a plurality of memory cells each one for storing a logic value, the cells being arranged into a plurality of alignments. The method includes the steps of: writing a set of target values into a plurality of blocks of cells, the corresponding cells of each block belonging to a common alignment, verifying each block of cells in succession to assert a fault value for each alignment in response to a non-compliance of the value stored in the cell of the block belonging to the alignment with the corresponding target value, buffering the fault values, and in response to the verification of all the blocks of cells providing an indication of the alignments being defective according to the fault values.

Owner:MICRON TECH INC

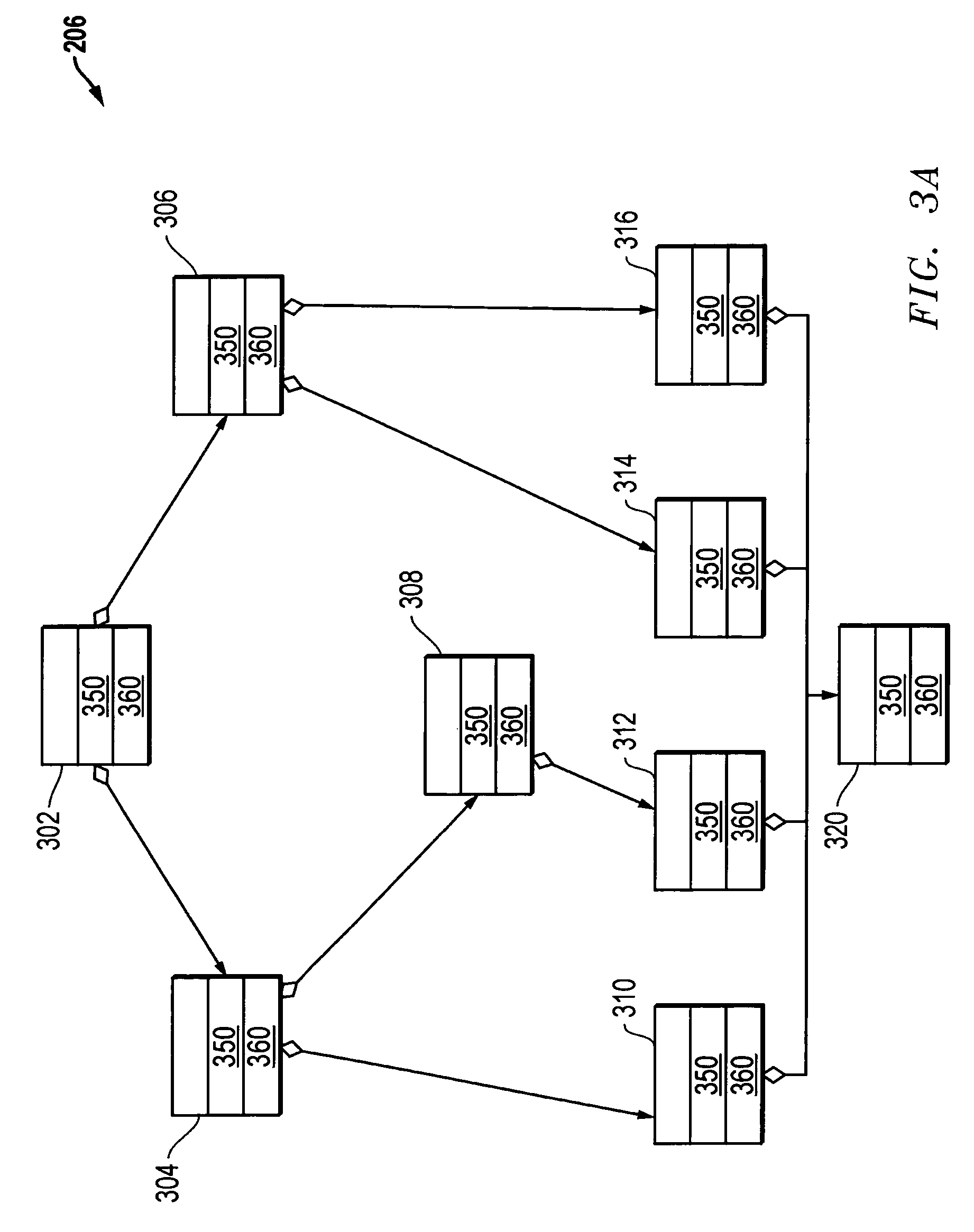

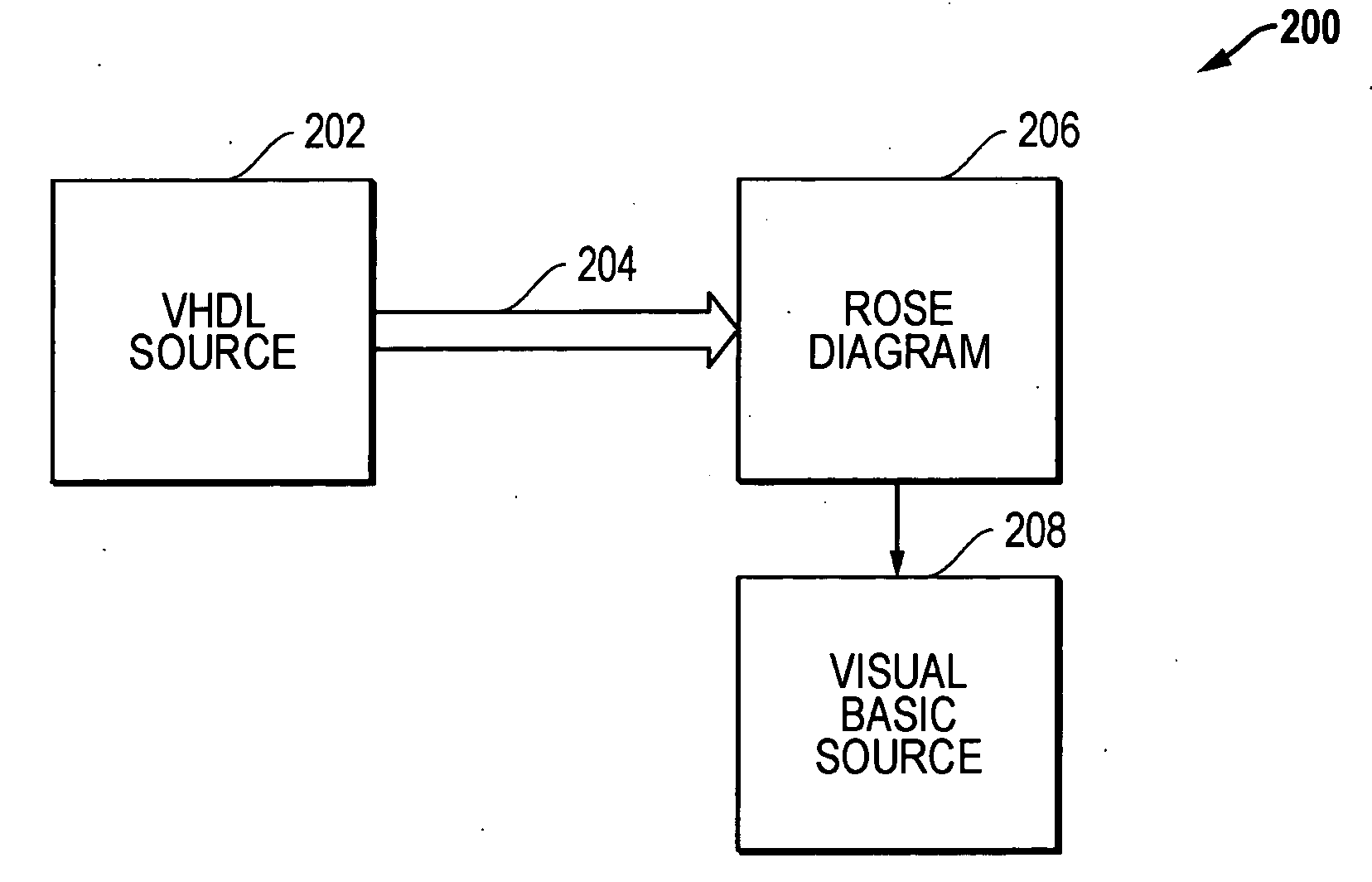

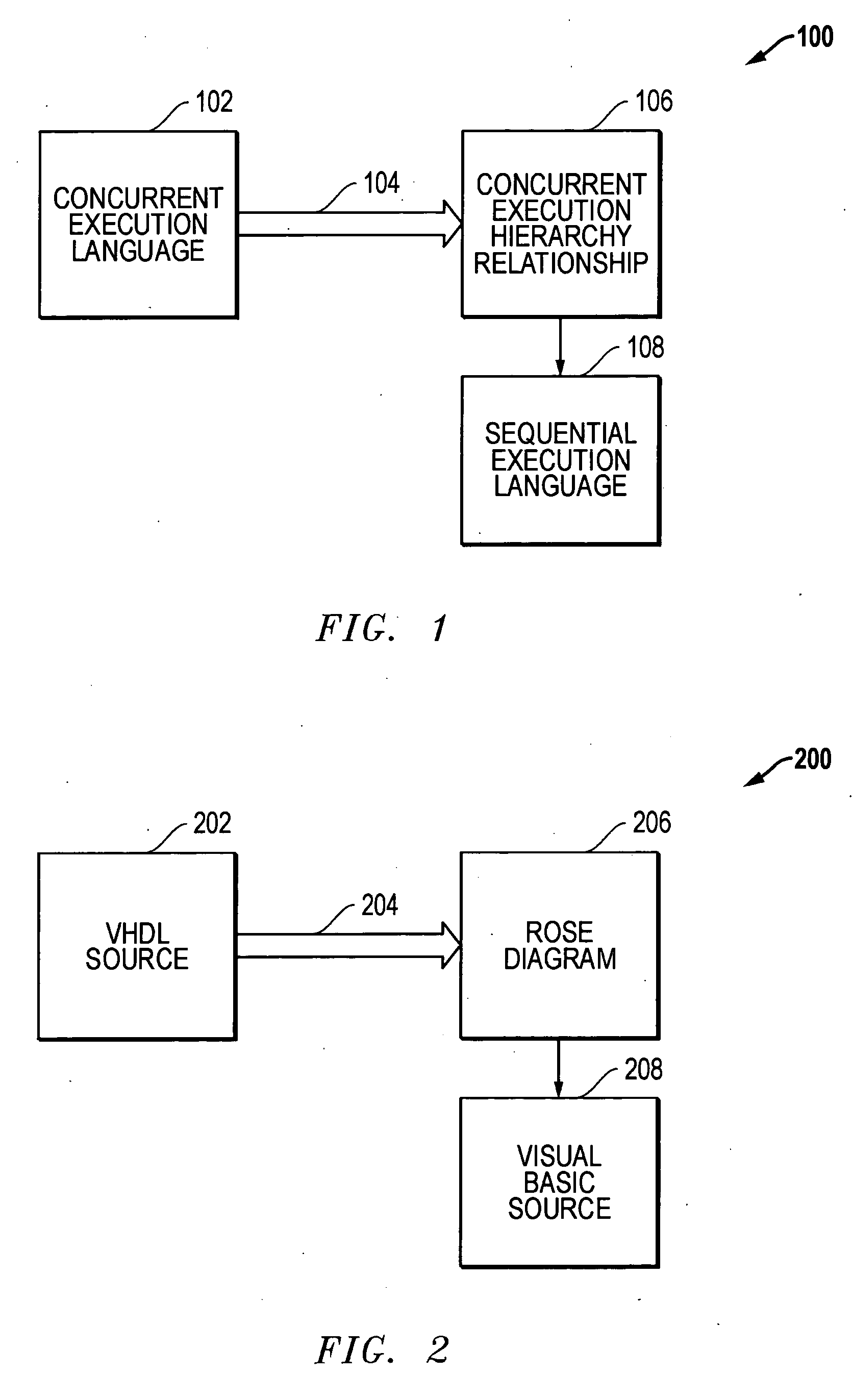

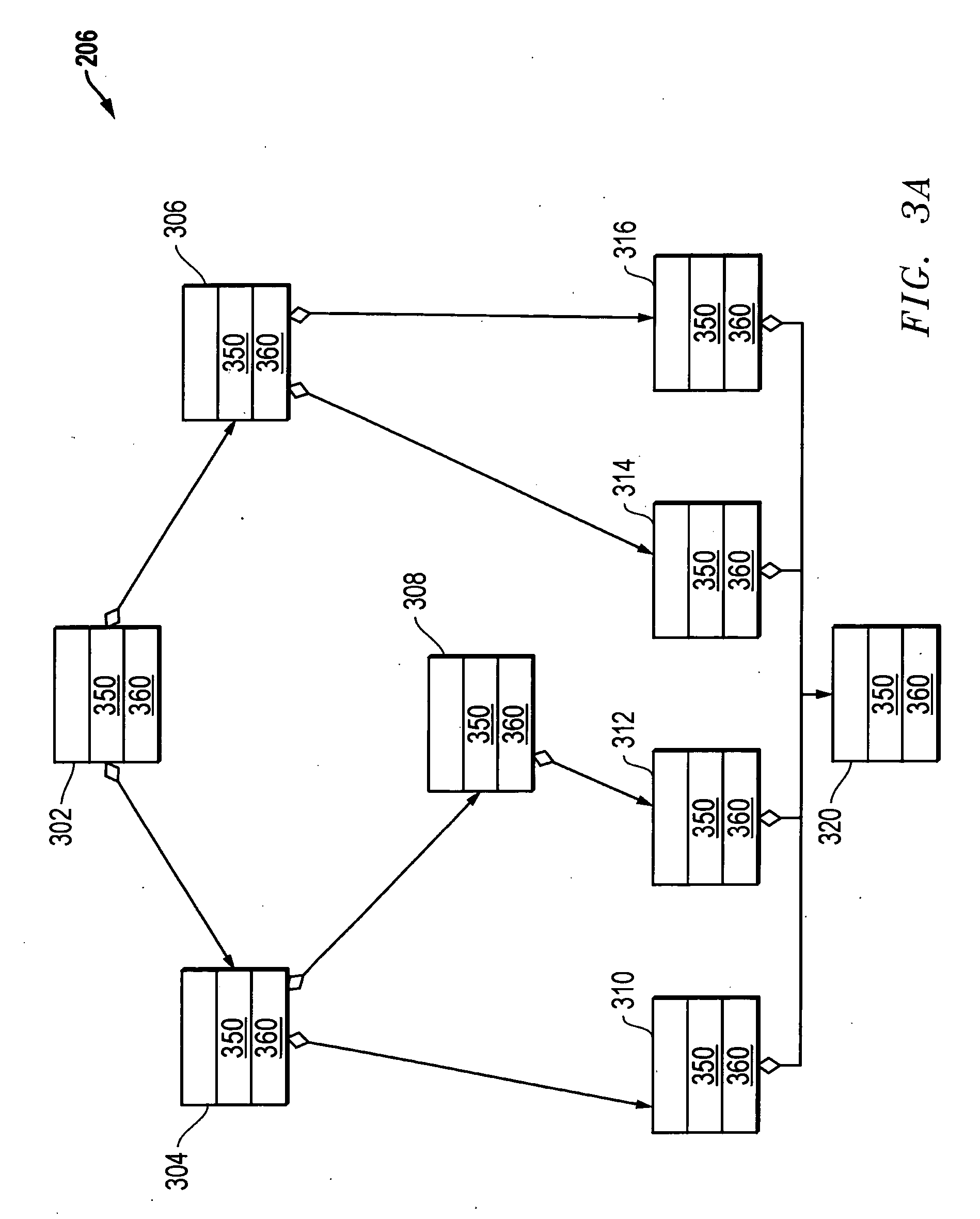

Methods and systems for modeling concurrent behavior

InactiveUS7603656B2The process is convenient and fastLengthy and time-consumingSoftware designCAD circuit designComputer architectureSequential programming

Methods and systems for modeling concurrent behavior in a sequential programming environment using sequential-execution languages to describe and model multiple different processes which are running simultaneously.

Owner:L 3 INTEGRATED SYST +1

Methods and systems for modeling concurrent behavior

InactiveUS20060161882A1The process is convenient and fastLengthy and time-consumingSoftware designCAD circuit designComputer architectureSequential programming

Methods and systems for modeling concurrent behavior in a sequential programming environment using sequential-execution languages to describe and model multiple different processes which are running simultaneously.

Owner:L 3 INTEGRATED SYST +1

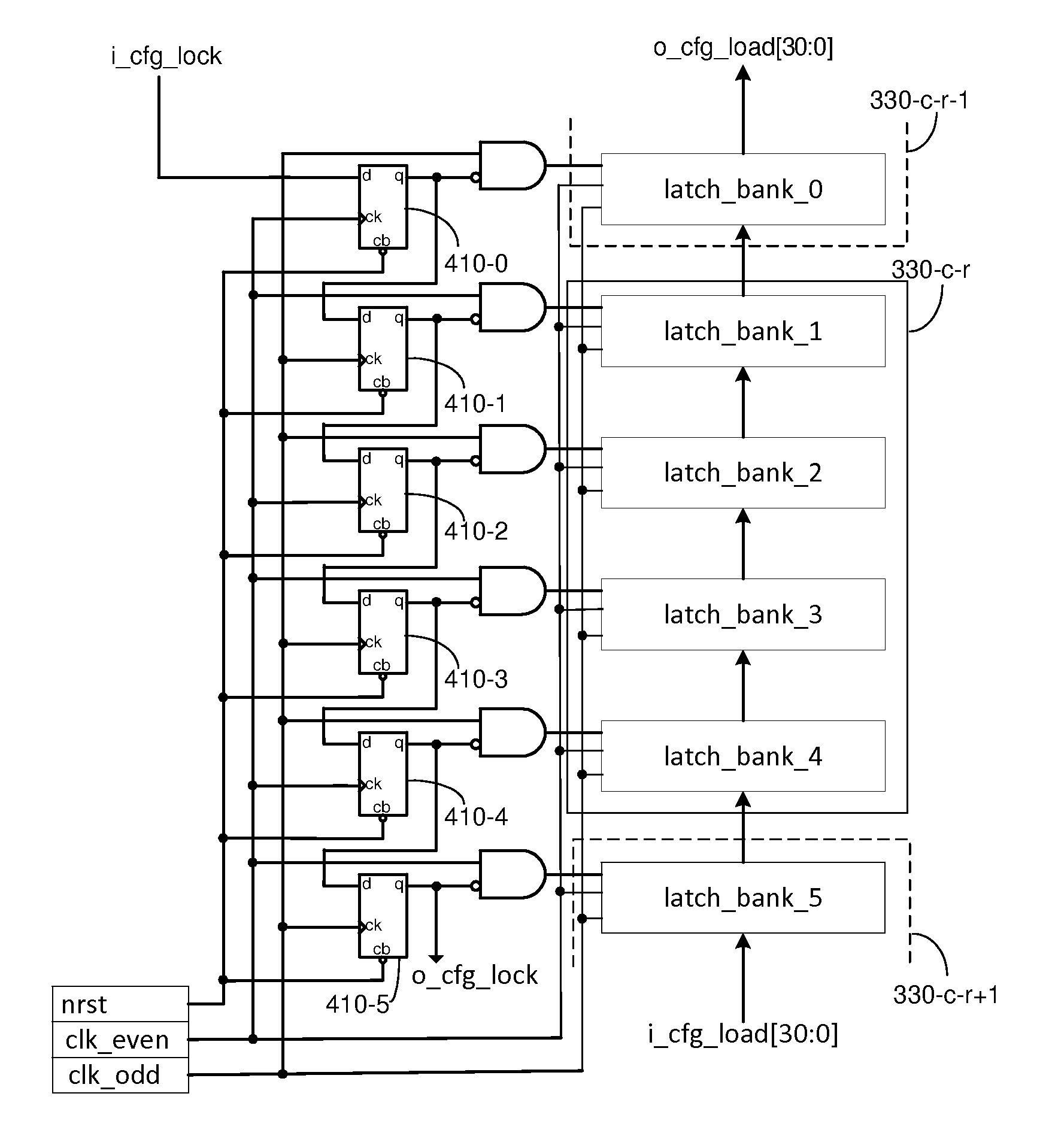

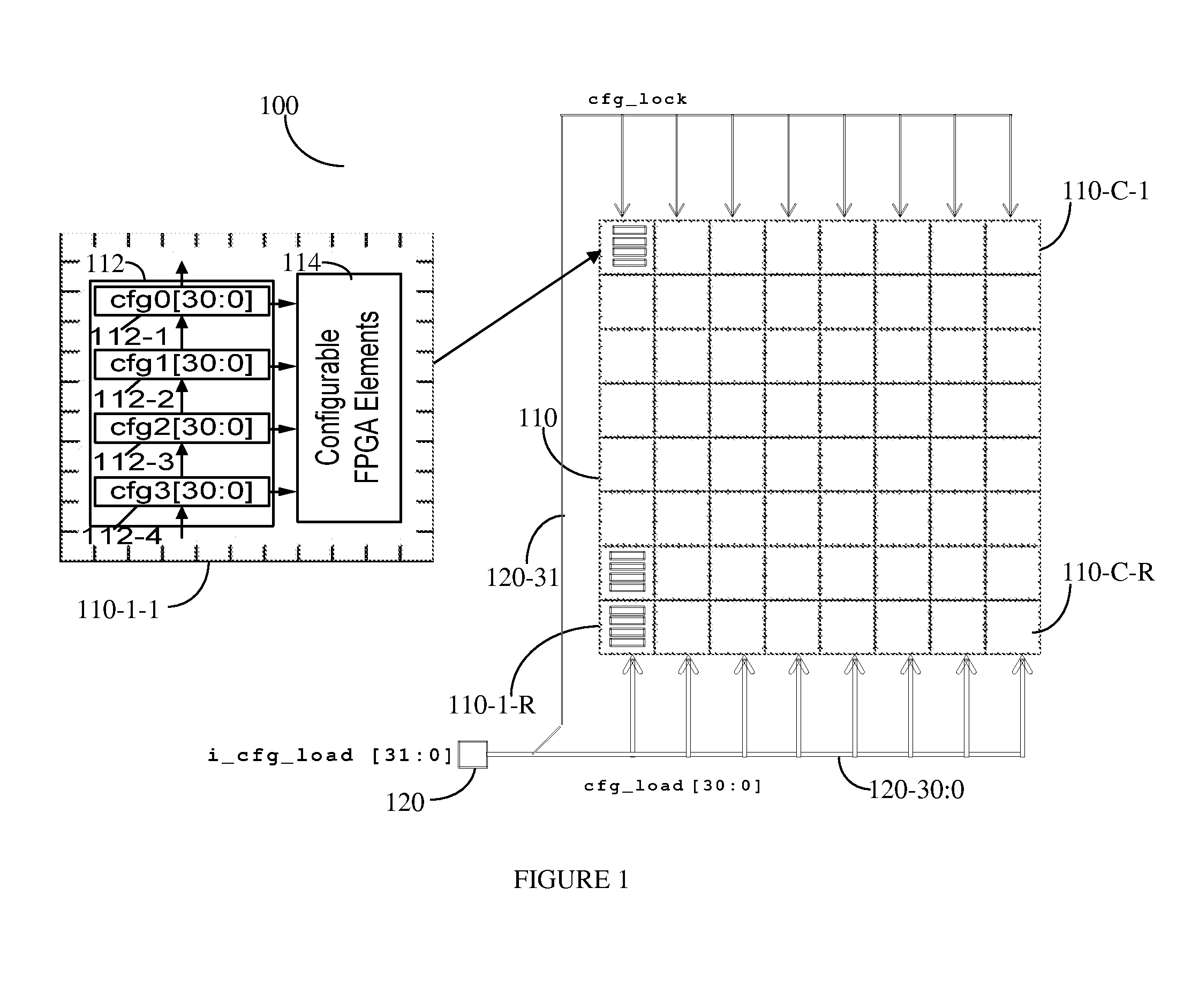

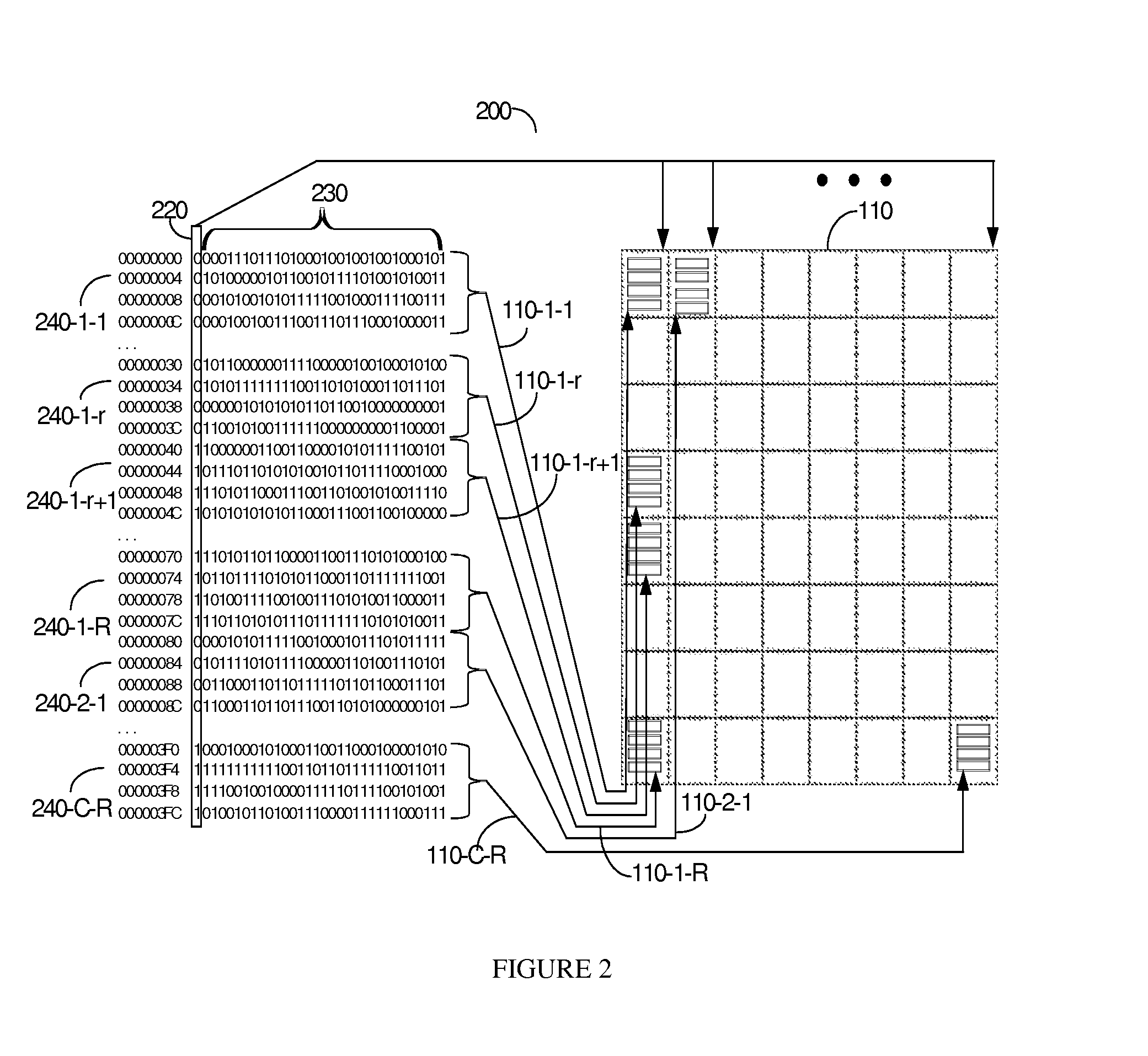

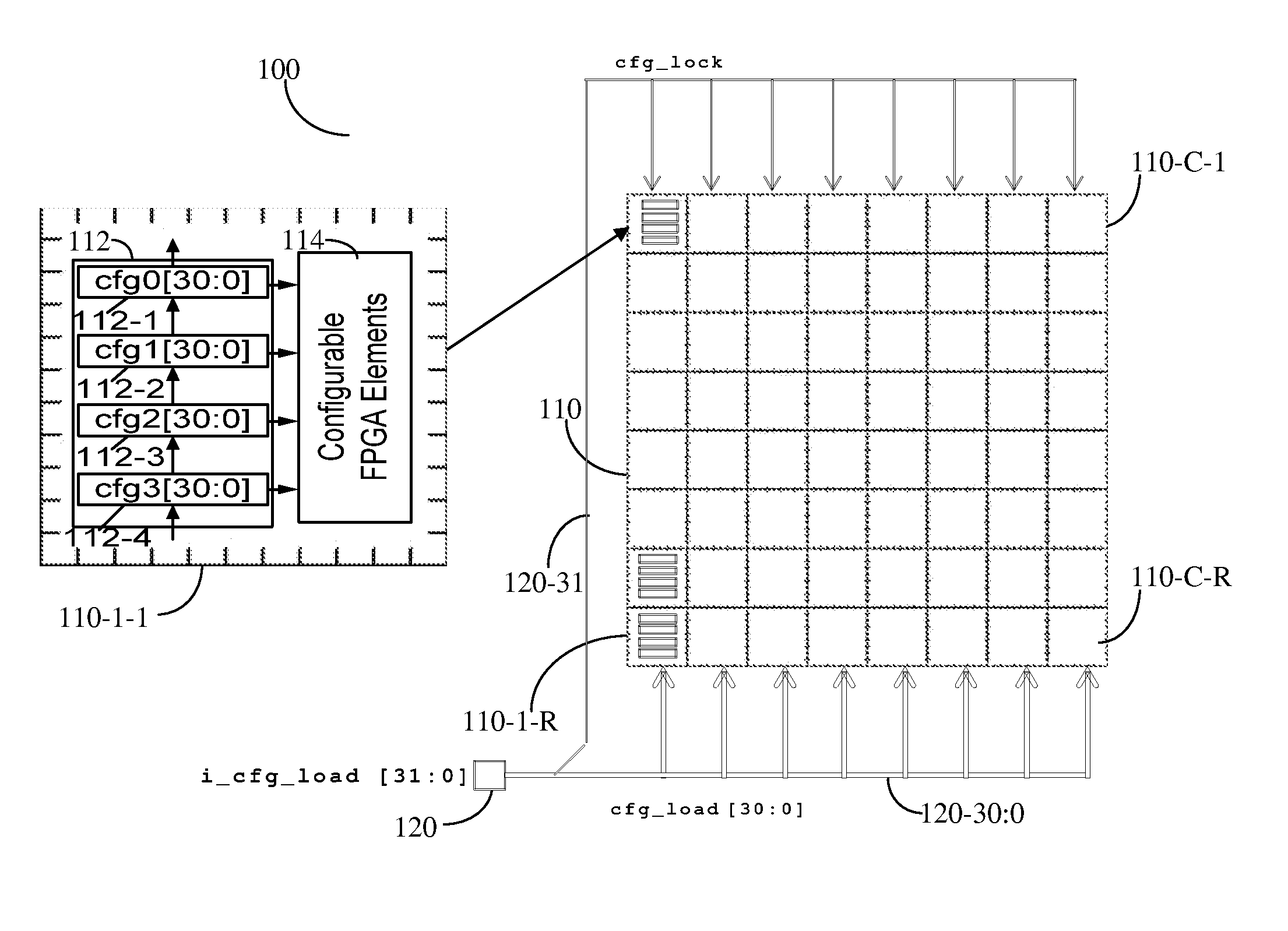

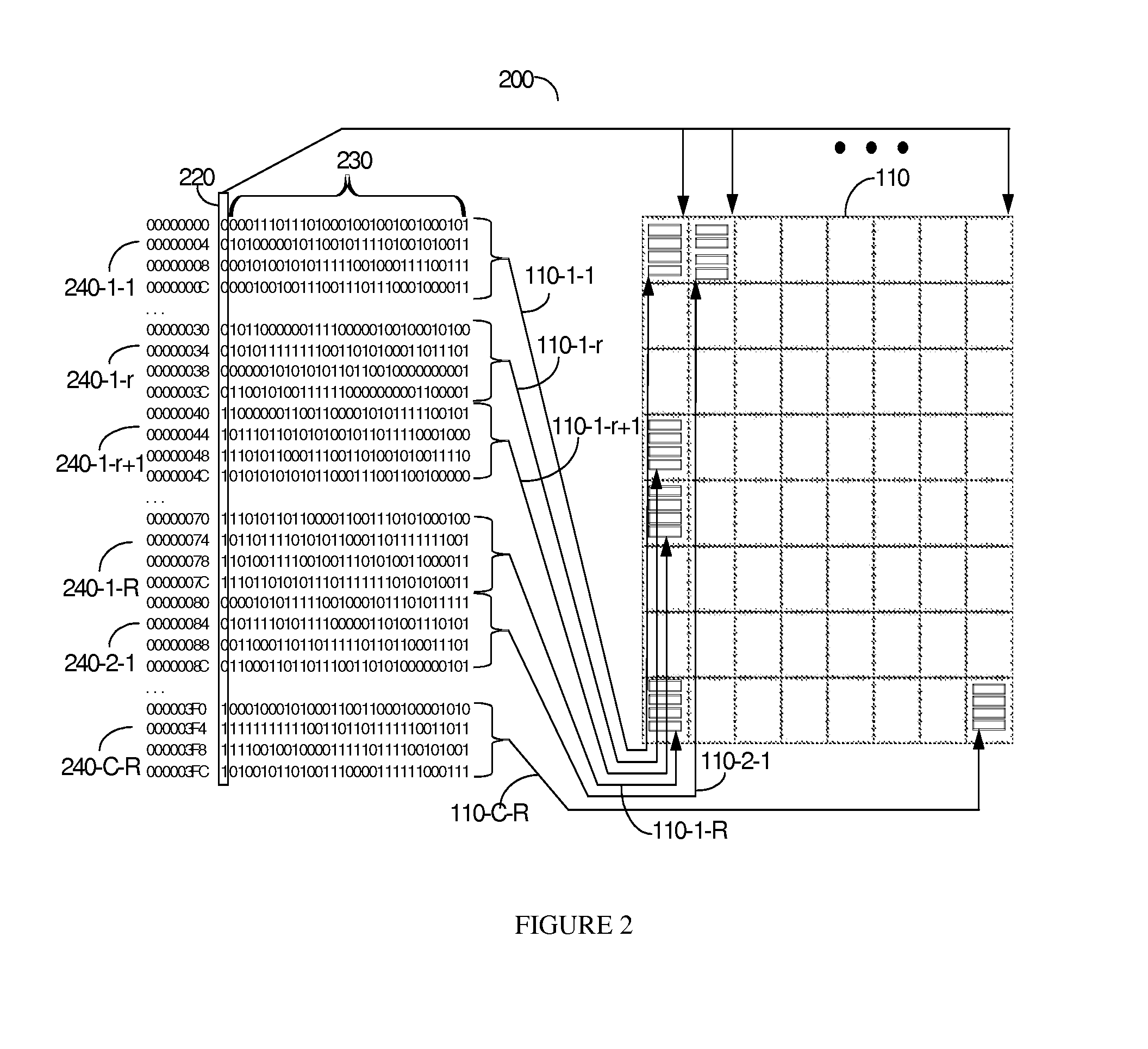

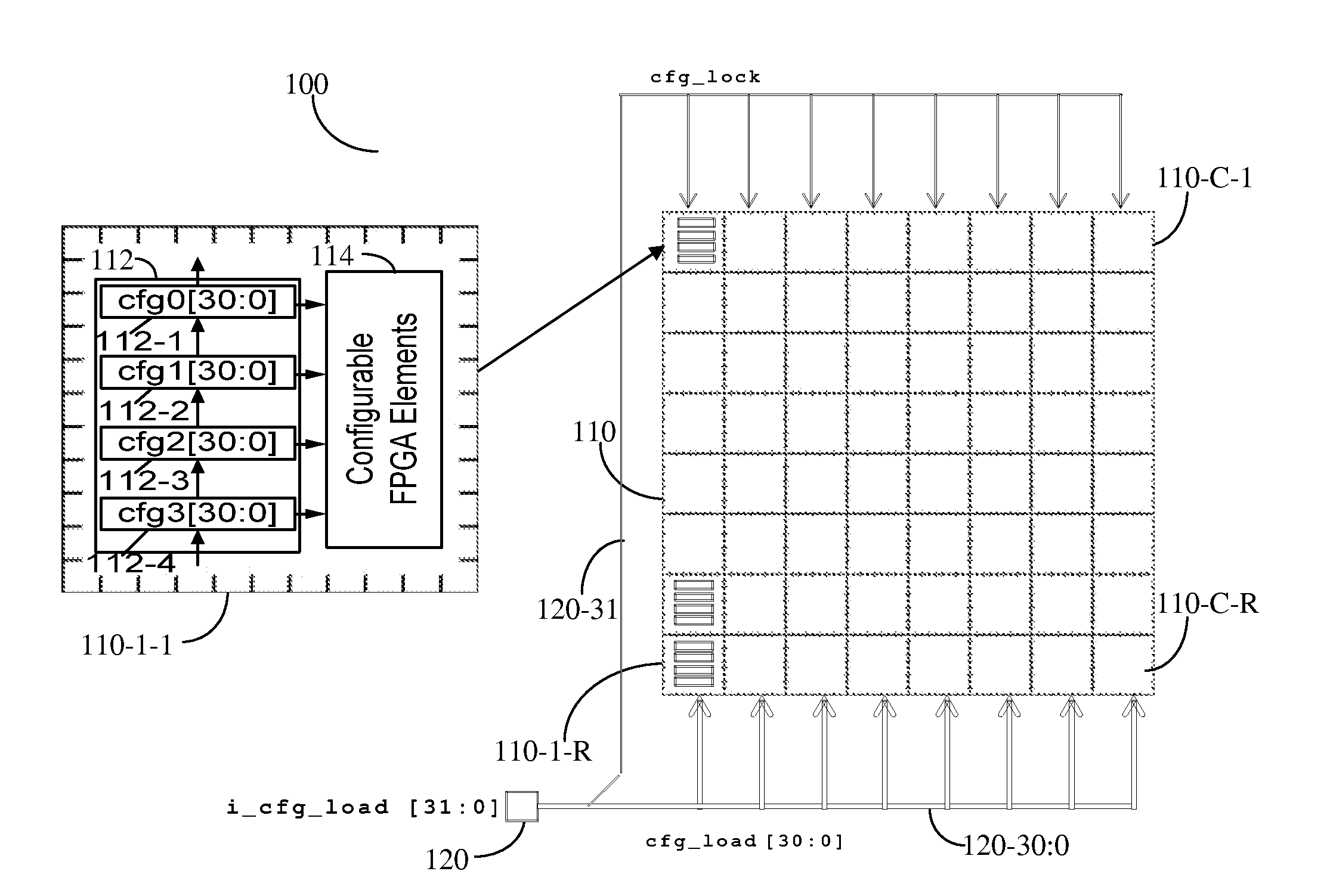

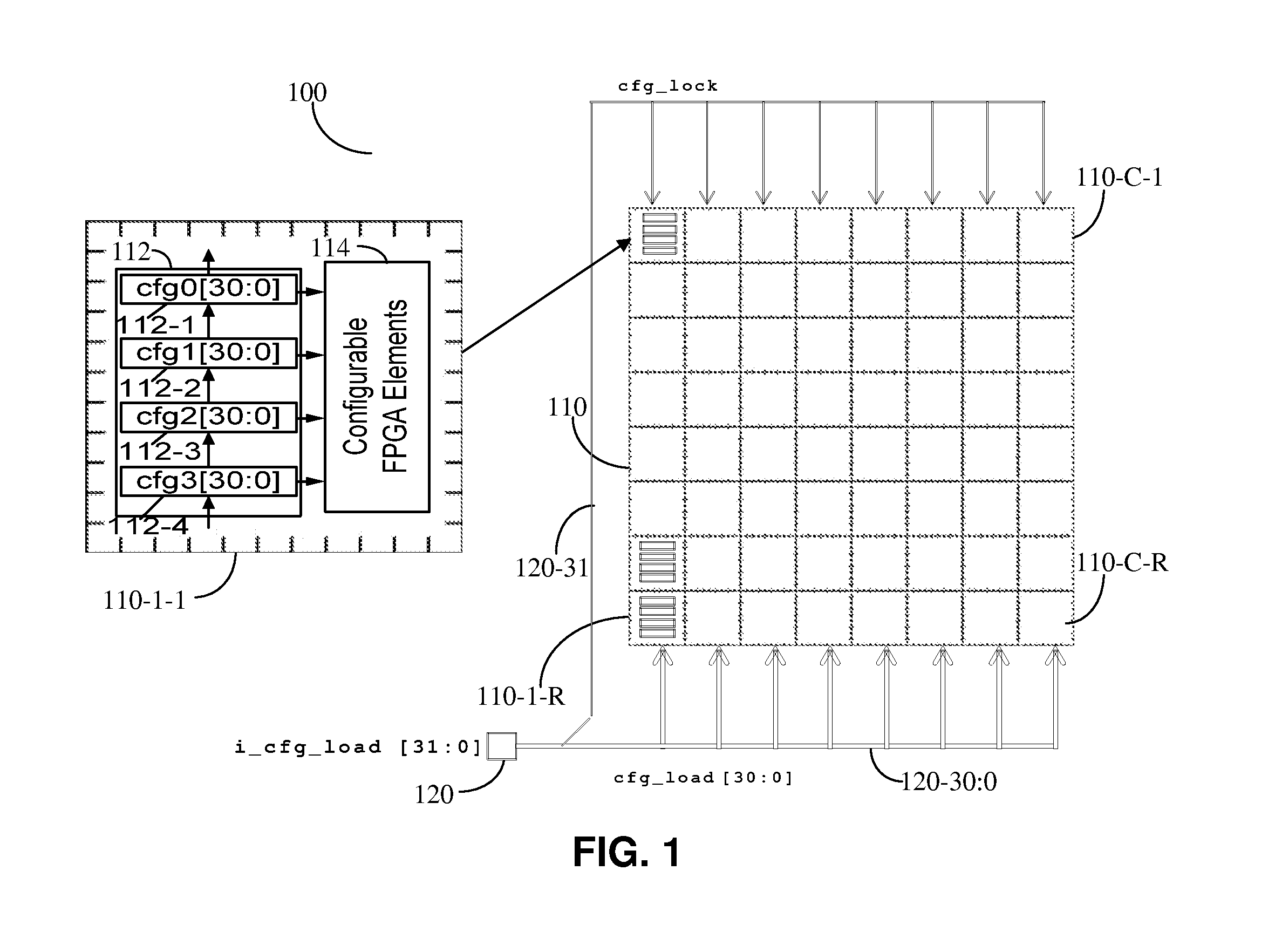

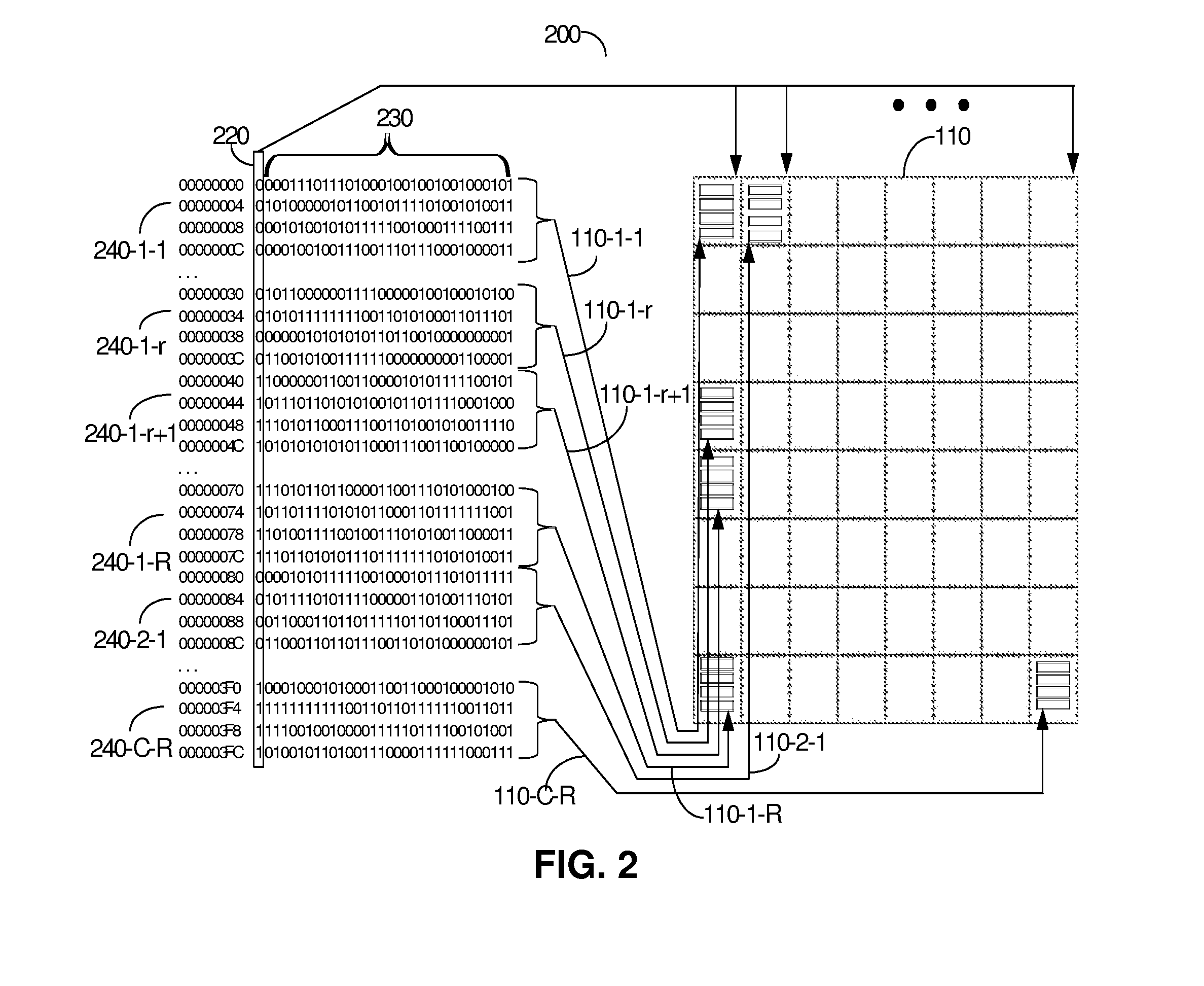

Flexible Logic Unit

ActiveUS20150091613A1Programmable logic circuit arrangementsLogic circuits using elementary logic circuit componentsField-programmable gate arraySequential programming

A flexible logic unit (FLU) is targeted to be primarily, but not exclusively, used as an embedded field programmable gate array (EFPGA). The unit is comprised of a plurality of programmable building block tiles arranged in an array of columns and rows of tiles, and programmed by downloading a bit stream, done tile by tile and column by column, using latches that are sequentially programmed and locked using a lock bit as part of the bit stream provided. A scheme of odd and even clocks prevent latch transparency and ensures that once data has arrived at its destination it is properly locked, not to be unintentionally overwritten.

Owner:SILICON MOBILITY

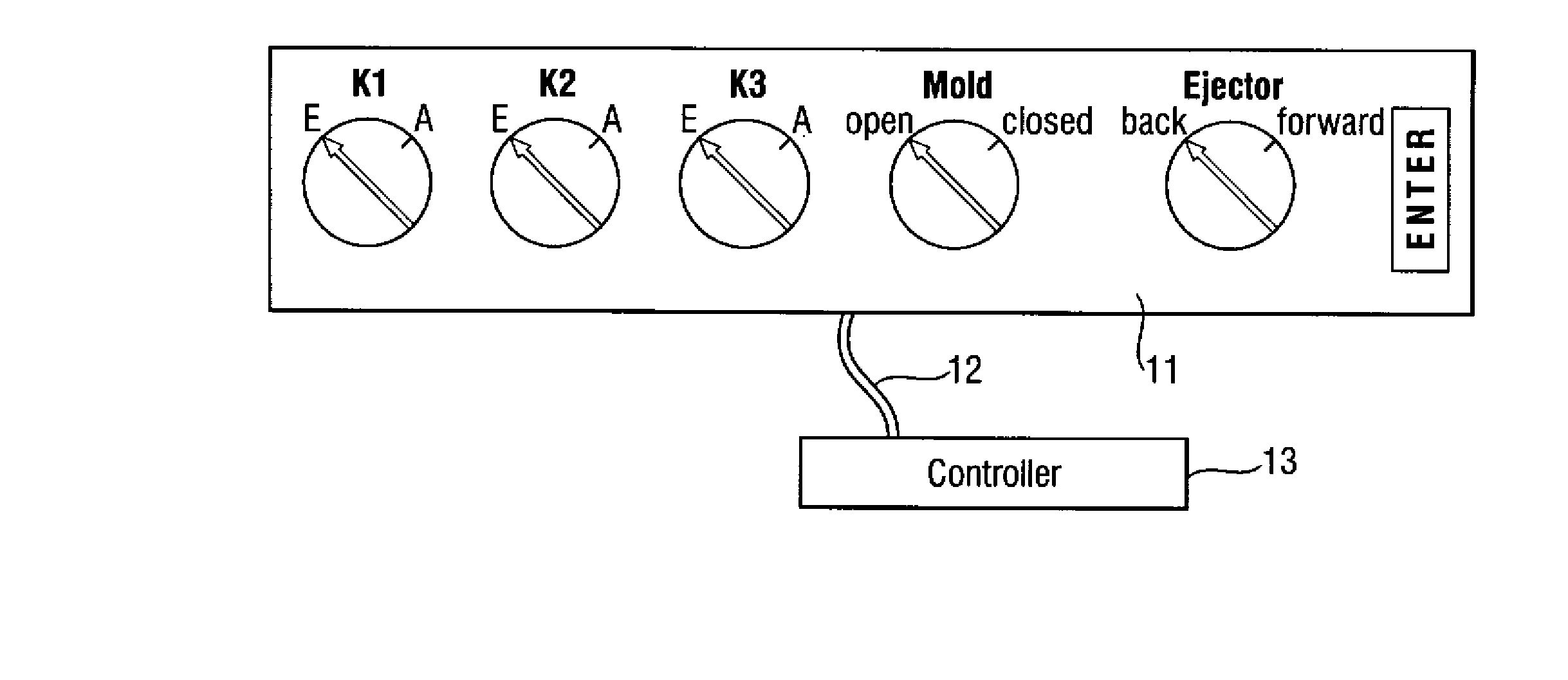

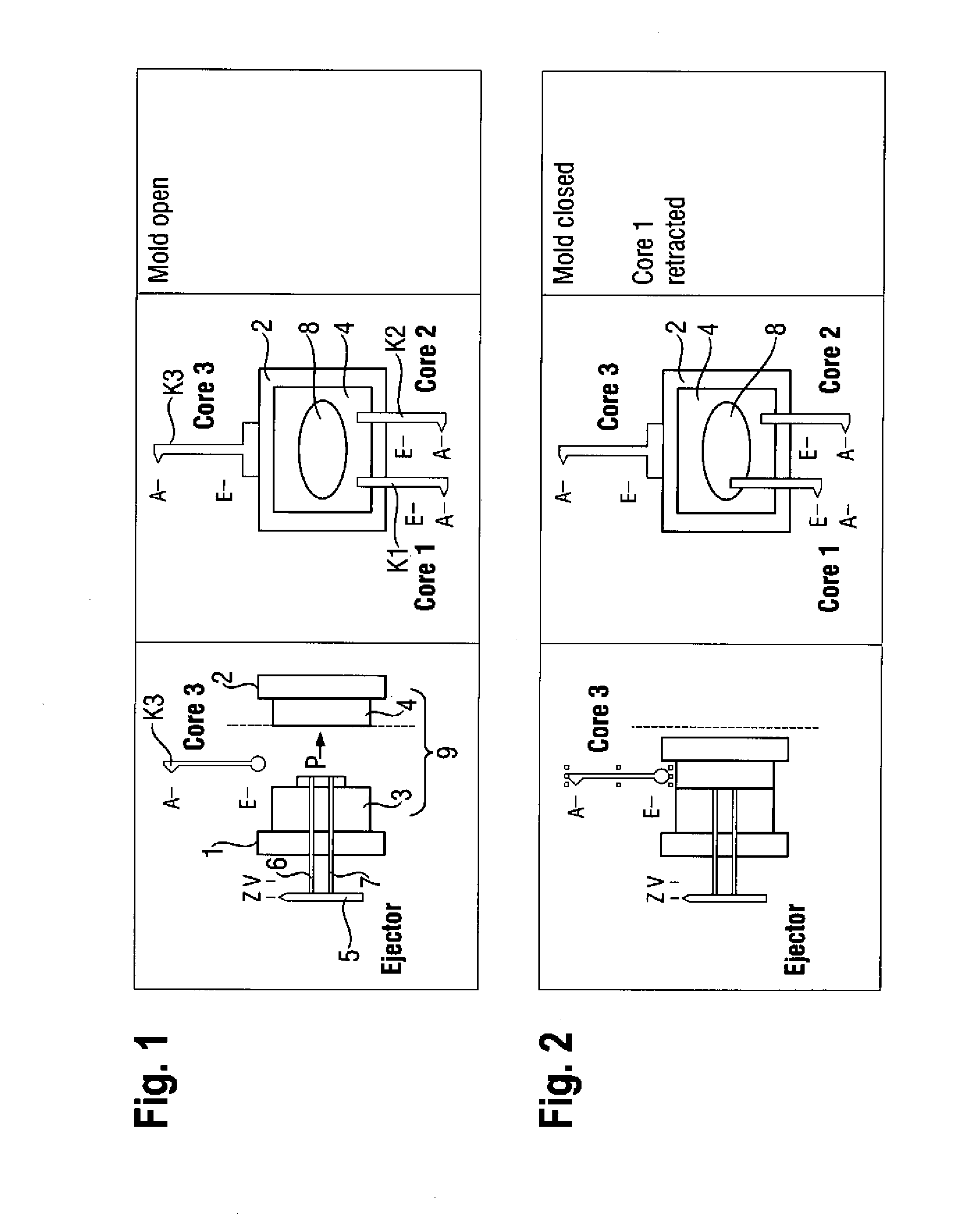

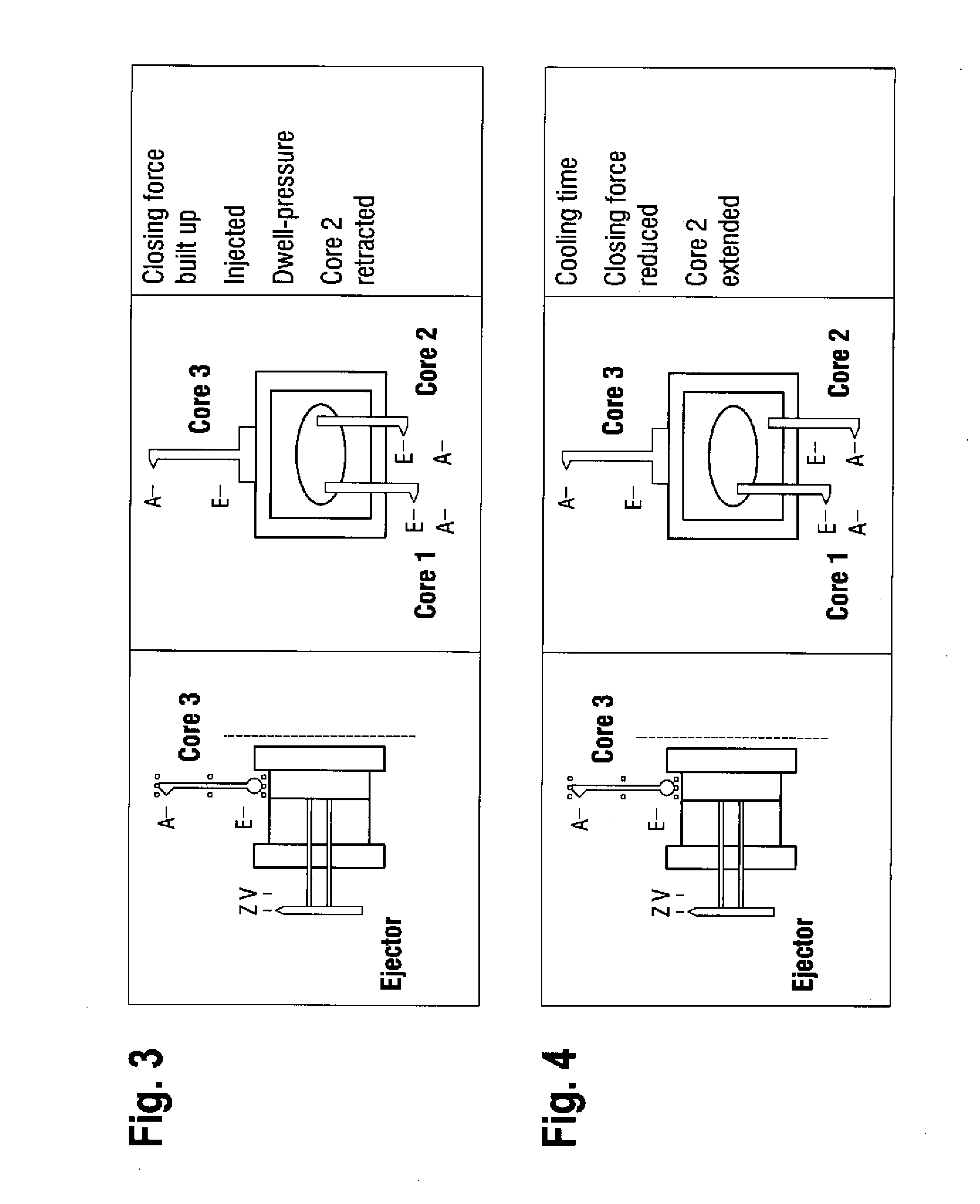

Method for sequential programming of an injection molding cycle of an injection molding machine

InactiveUS20080065261A1Avoid mistakesMinimize damageComputer controlSimulator controlSequential programmingEngineering

In a method for sequentially programming an injection molding cycle of an injection molding machine comprising one or several injection molds, the injection molding cycle is started manually step by step. The parts of the injection molding machine and / or the parts of the injection mold(s) are manually displaced into the positions or states required for the injection molding cycle in the order required for the injection molding cycle. The movement sequence (the actions and the obtained states) of the machine parts and / or the mold parts is stored in a controller.

Owner:KRAUSSMAFFEI TECH GMBH

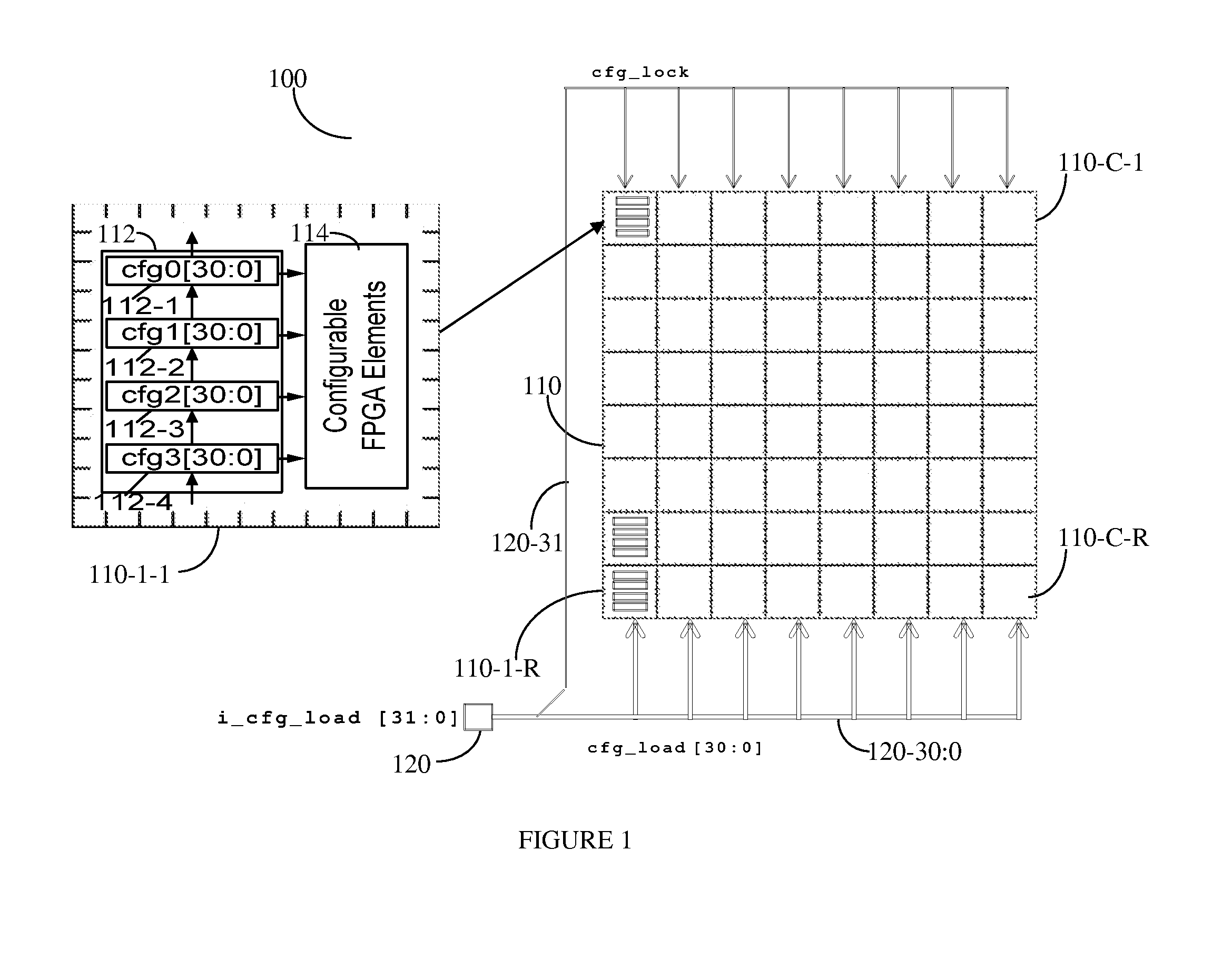

Robust Flexible Logic Unit

ActiveUS20150091614A1Logic circuits using elementary logic circuit componentsComputation using denominational number representationSequential programmingLogic cell

A robust flexible logic unit (FLU) is targeted to be primarily, but not exclusively, used as an embedded field programmable gate array (EFPGA). The unit is comprised of a plurality of programmable building block tiles arranged in an array of columns and rows of tiles, and programmed by downloading a bit stream, done tile by tile and column by column, using latches that are sequentially programmed and locked using a lock bit as part of the bit stream provided. A scheme of odd and even clocks prevent latch transparency and ensures that once data has arrived at its destination it is properly locked, not to be unintentionally overwritten. The robust FLU is further equipped with cyclic redundancy check capabilities to provide indication of faulty column configuration.

Owner:SILICON MOBILITY

Robust Flexible Logic Unit

ActiveUS20150303926A1Logic circuits using elementary logic circuit componentsComputation using denominational number representationIndependent functionLogic cell

A robust flexible logic unit (FLU) is targeted to be primarily, but not exclusively, used as an embedded field programmable gate array (EFPGA). The unit is comprised of a plurality of programmable building block tiles arranged in an array of columns and rows of tiles, and programmed tile by tile and column by column, using latches that are sequentially programmed and locked using a lock bit that is part of the bit stream provided. A scheme of odd and even clocks prevent latch transparency and ensures that loaded data is properly locked, to prevent overwrites. The robust FLU is further equipped with cyclic redundancy check capabilities to provide indication of faulty column configuration. The invention also provides for splitting the single FLU into multiple independent reconfigurable FLU sections, with independent user clock and reset, for implementing a plurality of independent functions or for establishing redundancy for critical functions.

Owner:SILICON MOBILITY

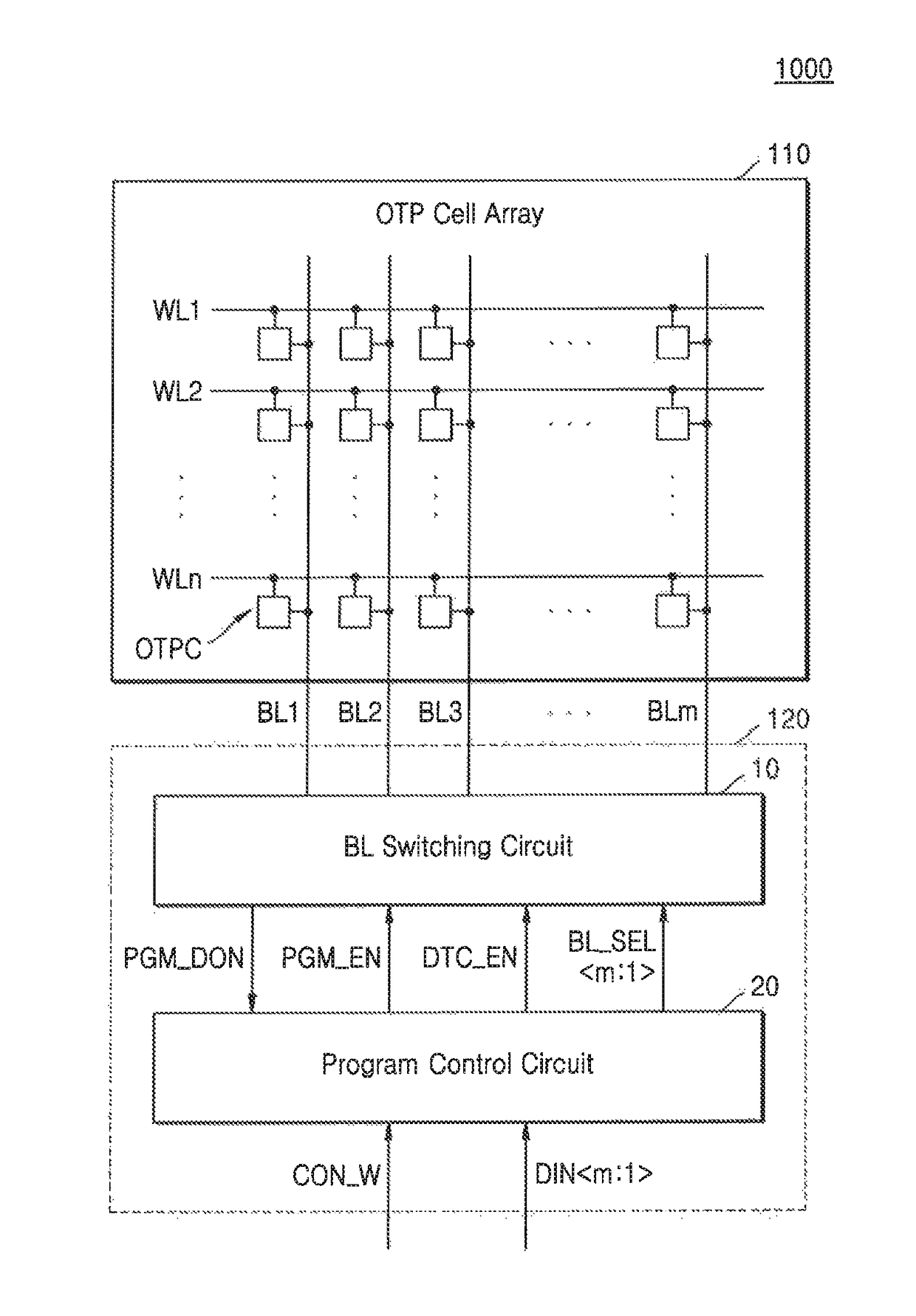

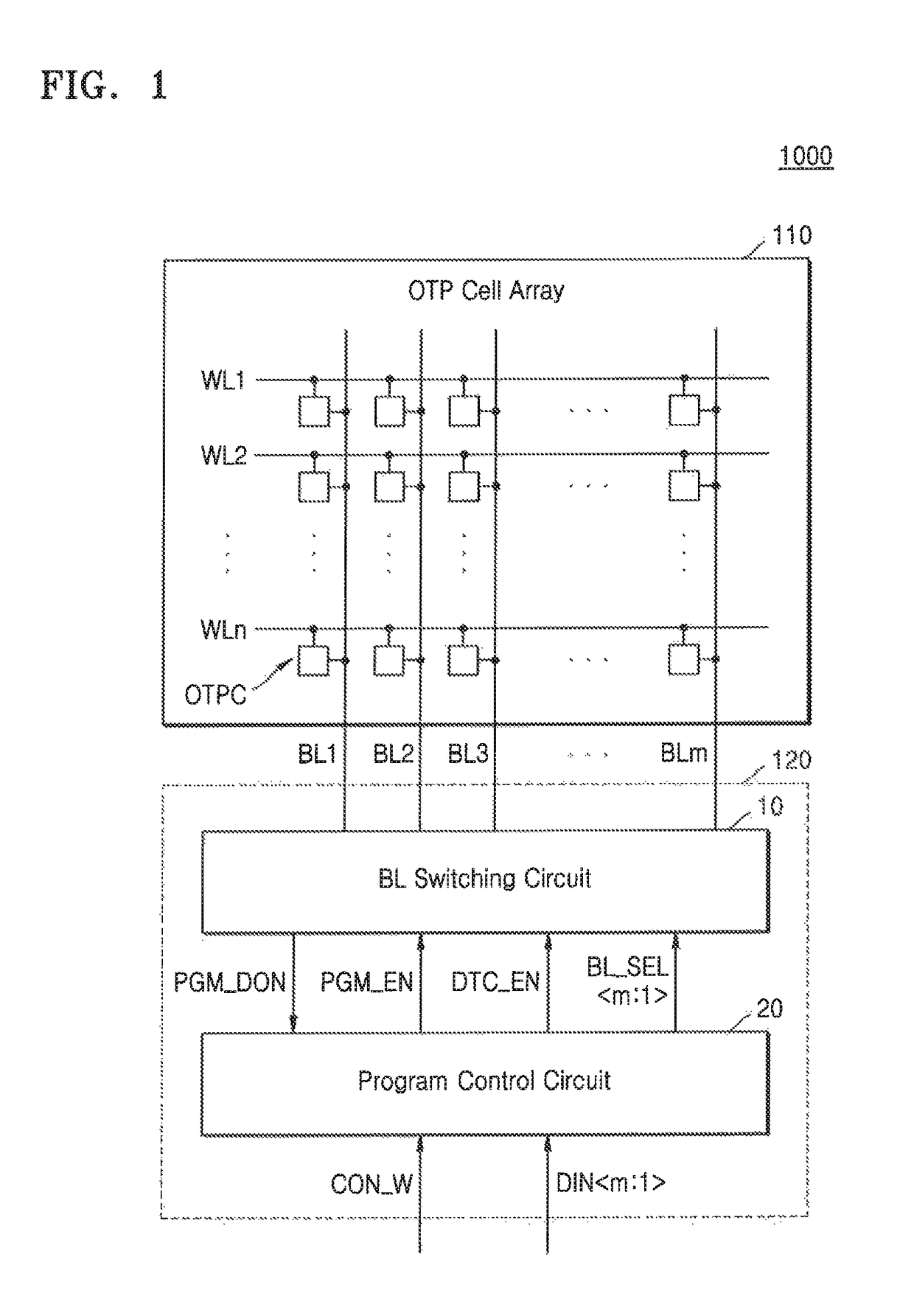

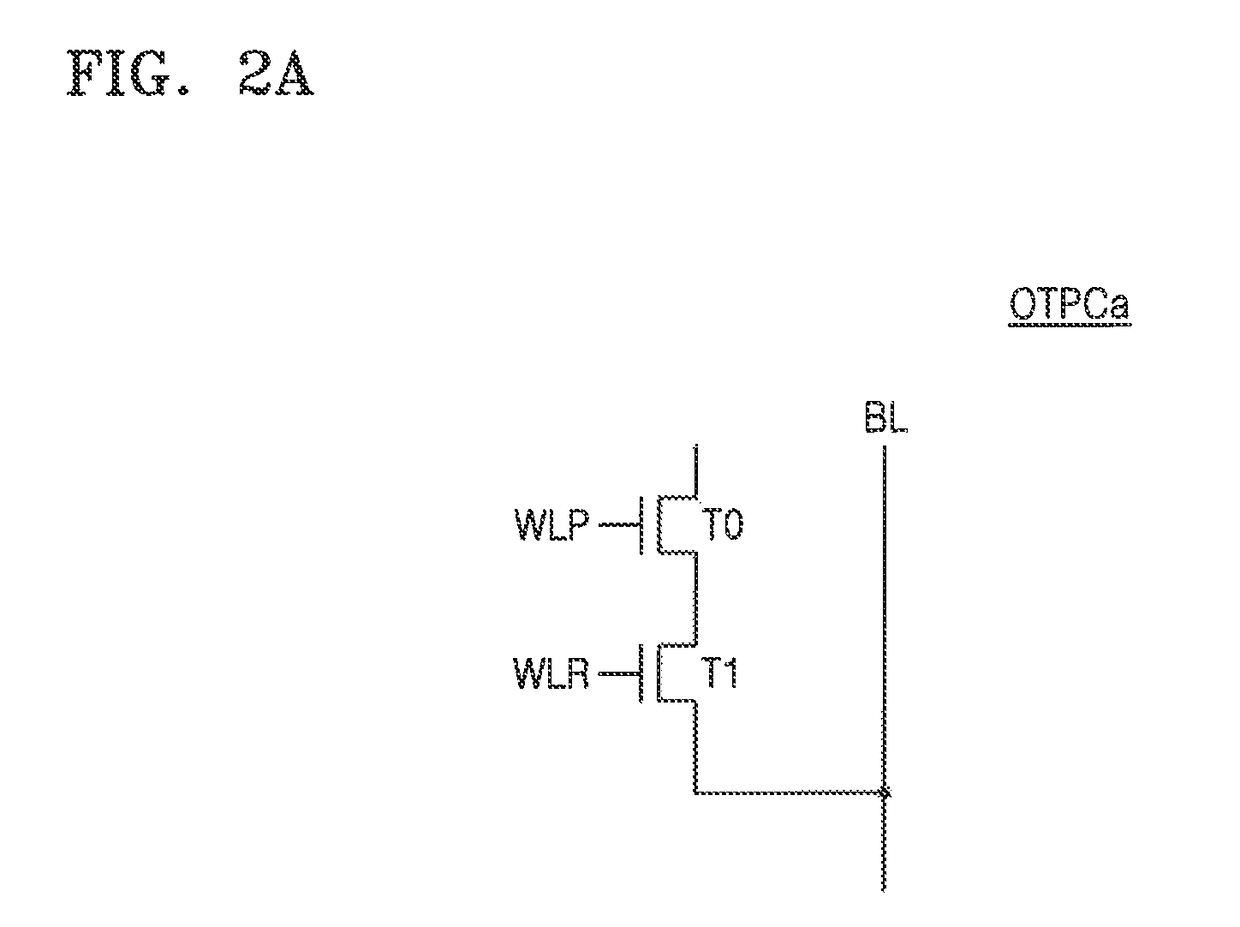

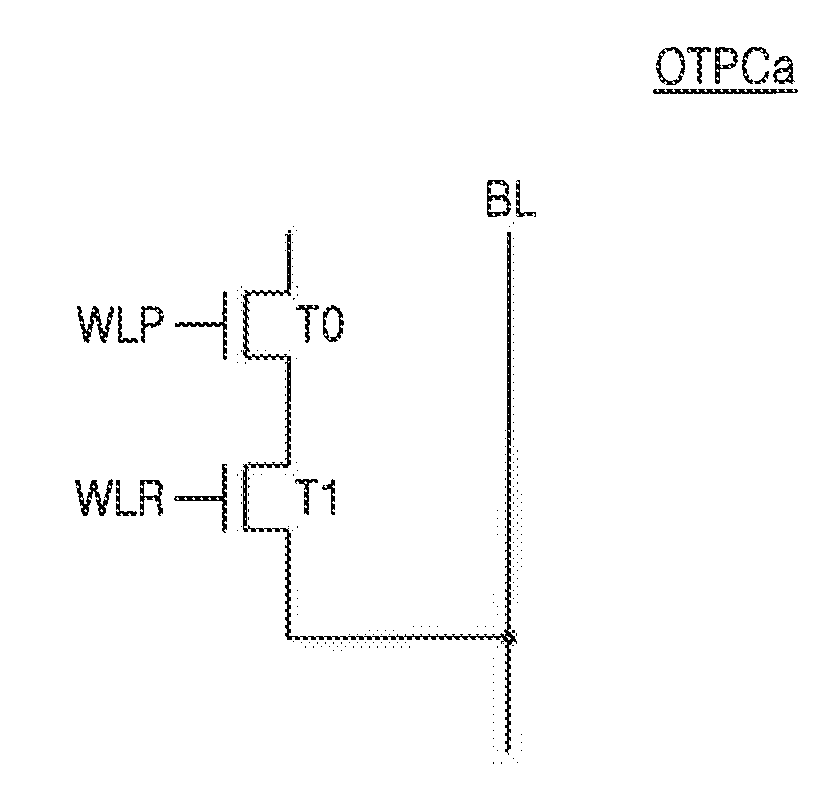

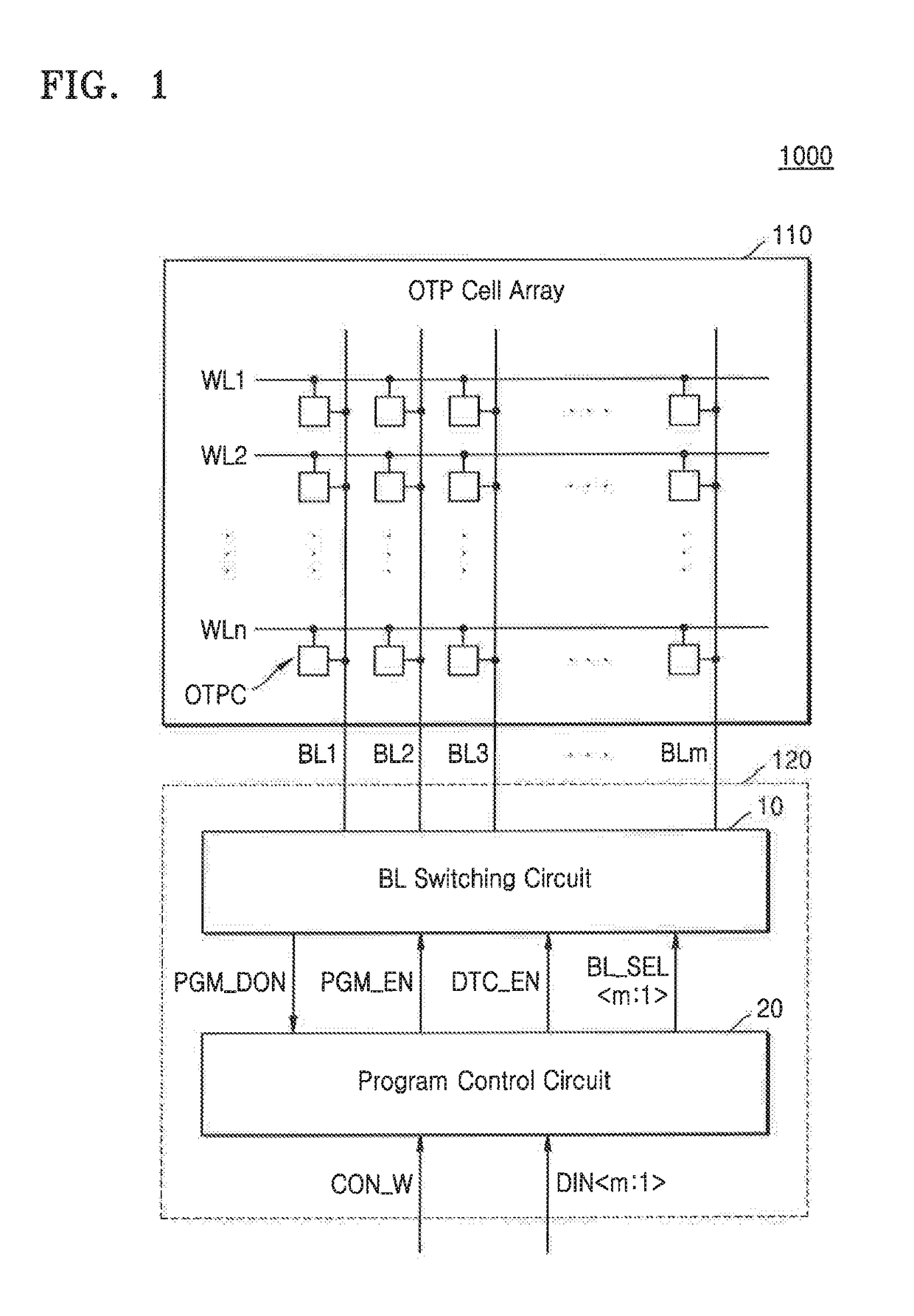

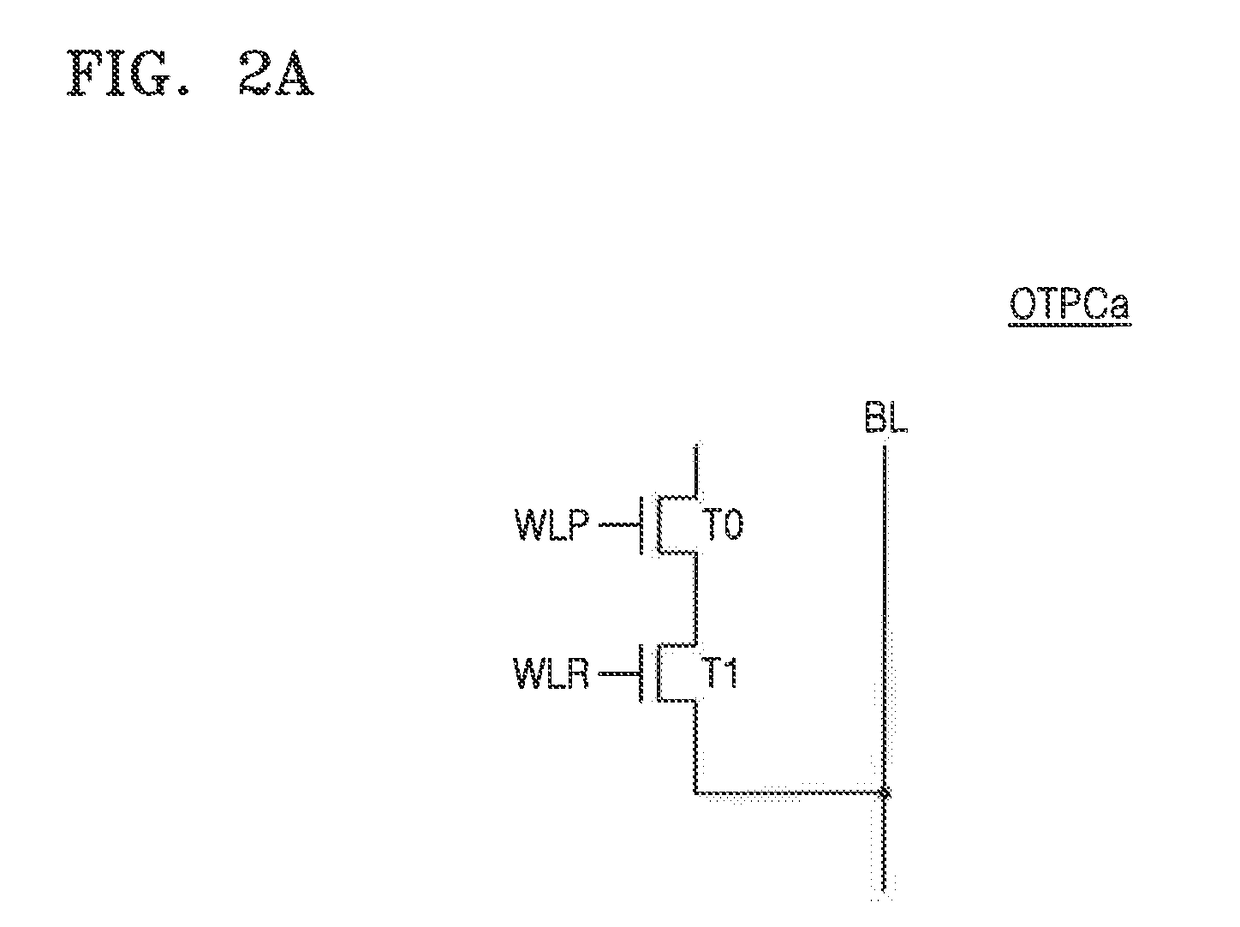

One time programmable memory and a data writing method thereof

Owner:SAMSUNG ELECTRONICS CO LTD

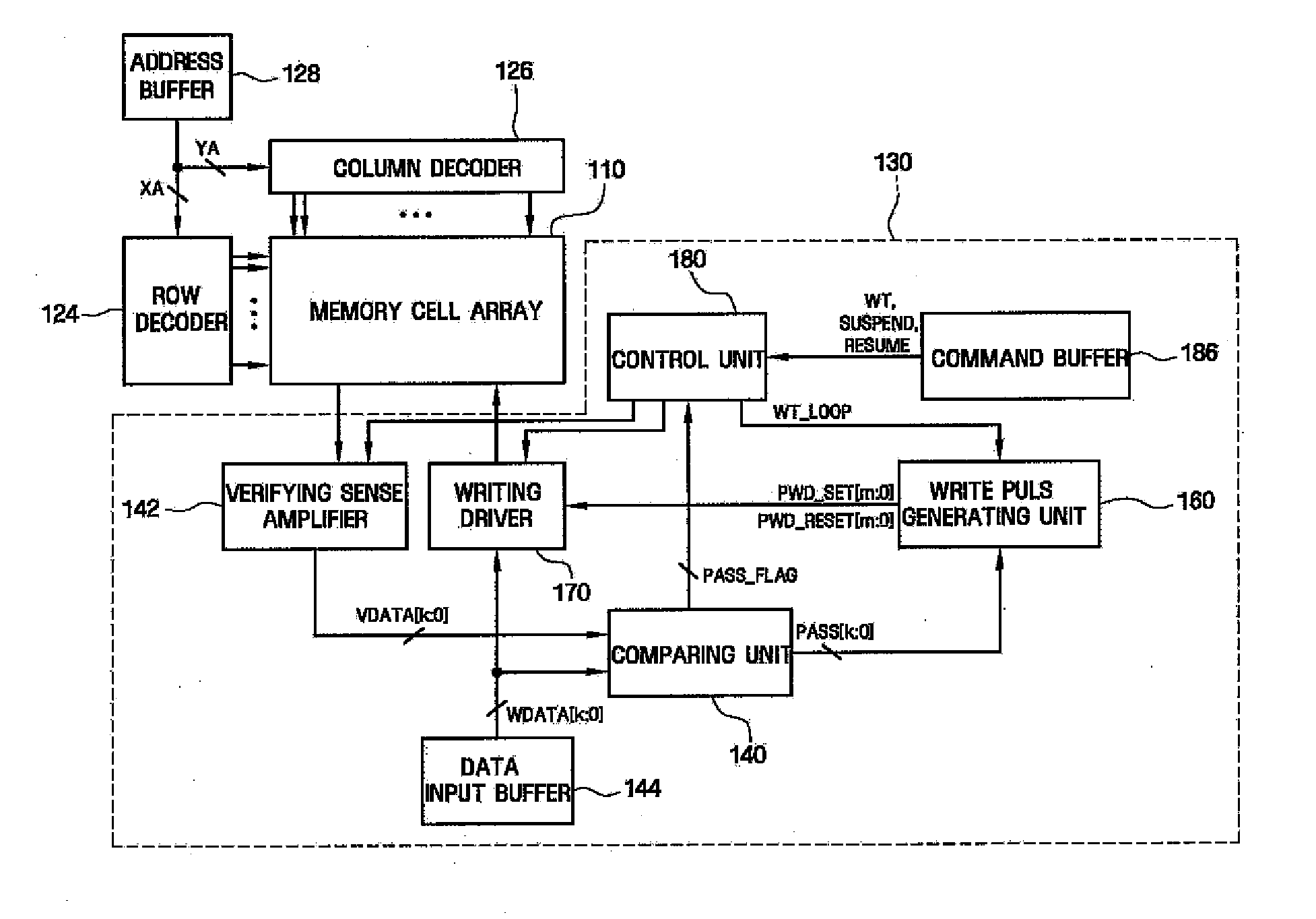

Phase change random access memory device and related methods of operation

A method of operating a phase change random access memory (PRAM) device comprises performing a program operation to store data in selected PRAM cells of the device, wherein the program operation comprises a plurality of sequential program loops. The method further comprises suspending the program operation in the middle of the program operation, and after suspending the program operation, resuming the program operation in response to a resume command.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for testing semiconductor memory device and related testing methods

Owner:SAMSUNG ELECTRONICS CO LTD

One time programmable memory and a data writing method thereof

A one time programmable (OTP) memory includes an OTP cell array including a plurality of OTP cells provided at locations where a plurality of word lines and a plurality of bit lines cross each other, and a write circuit configured to sequentially program the OTP cells by selecting the bit lines one at a time and program a selected OTP cell connected to the selected bit line, wherein the write circuit is further configured to detect a voltage level of the selected bit line and select another bit line when the detected voltage level indicates that the selected OTP cell is in a programmed state.

Owner:SAMSUNG ELECTRONICS CO LTD

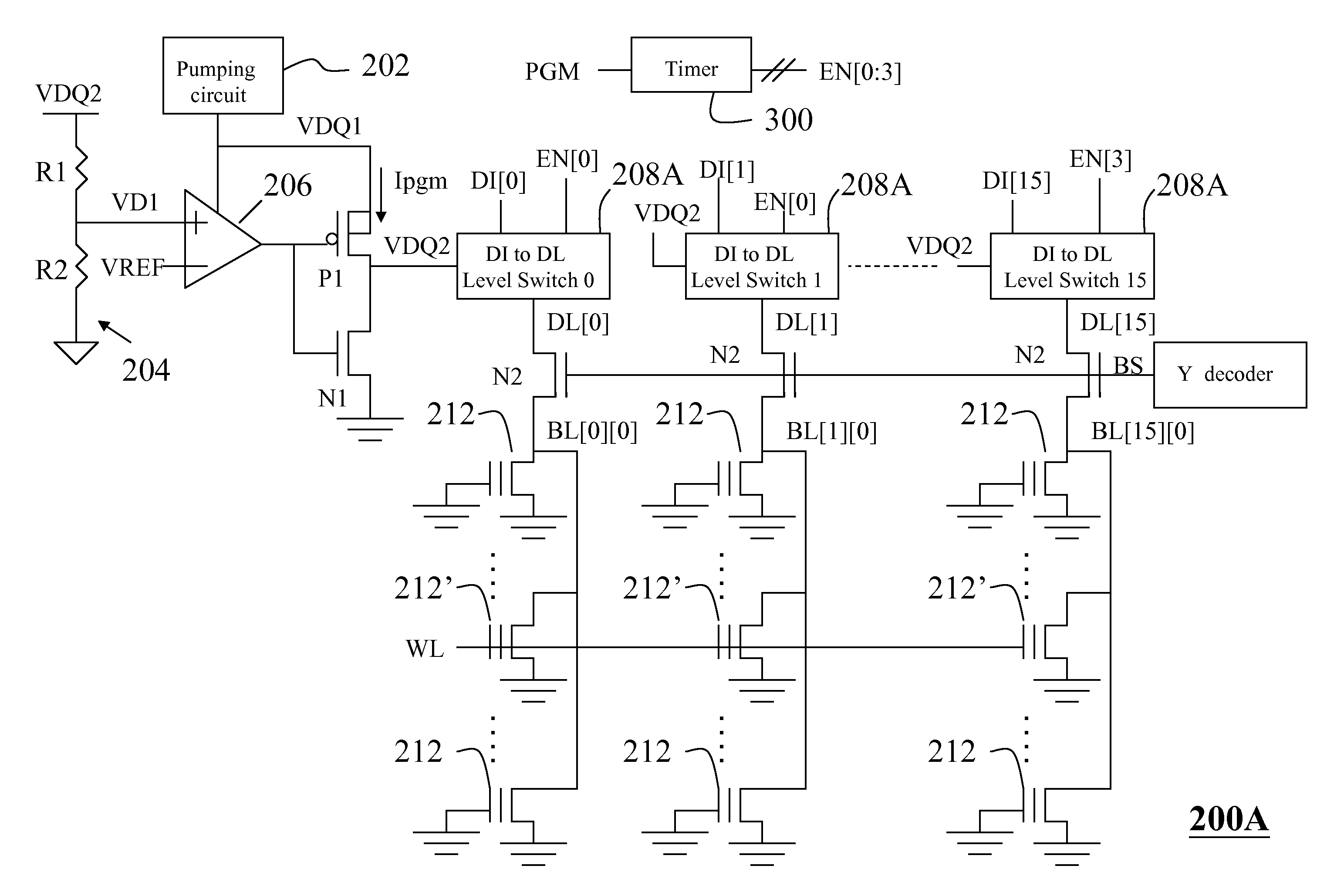

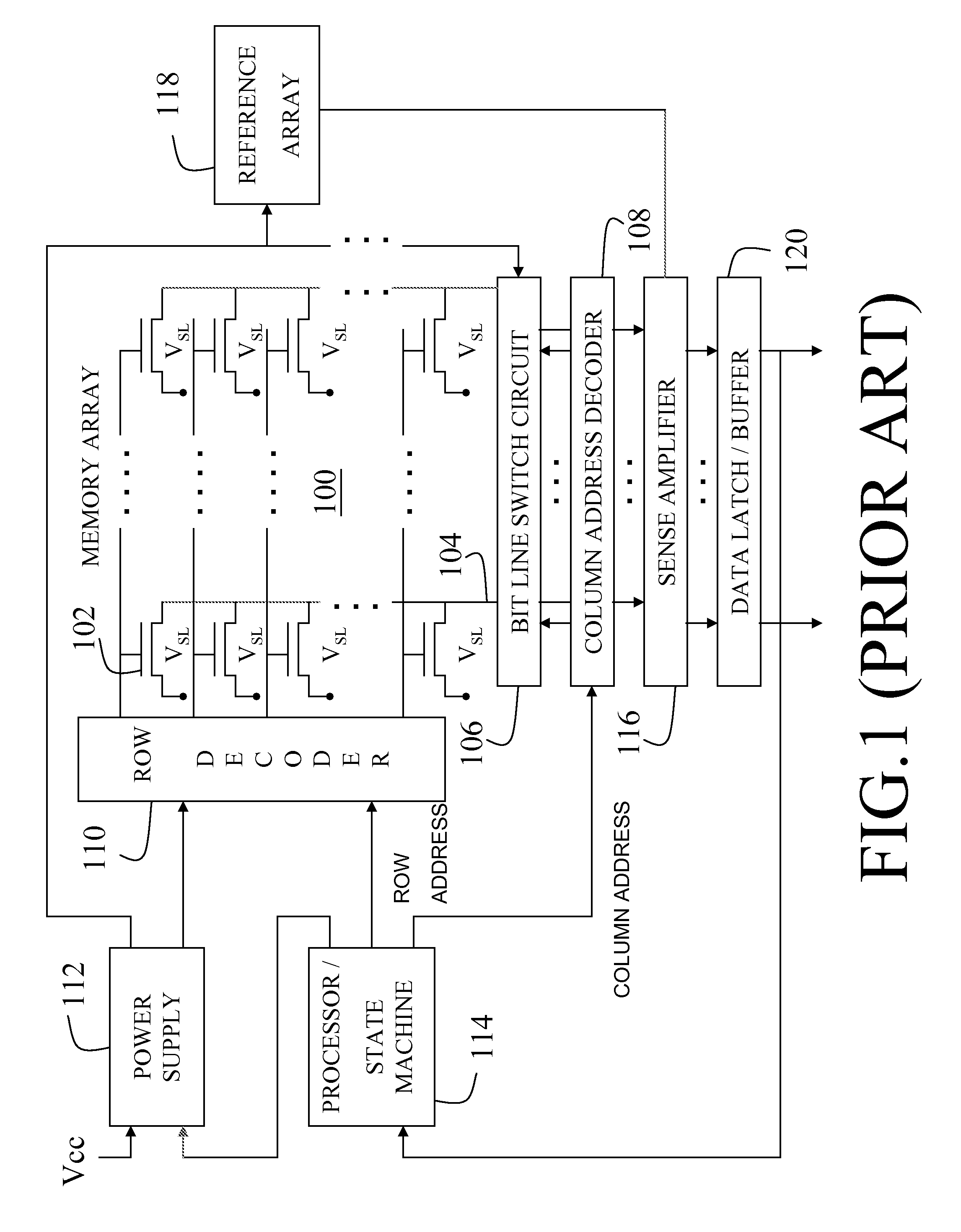

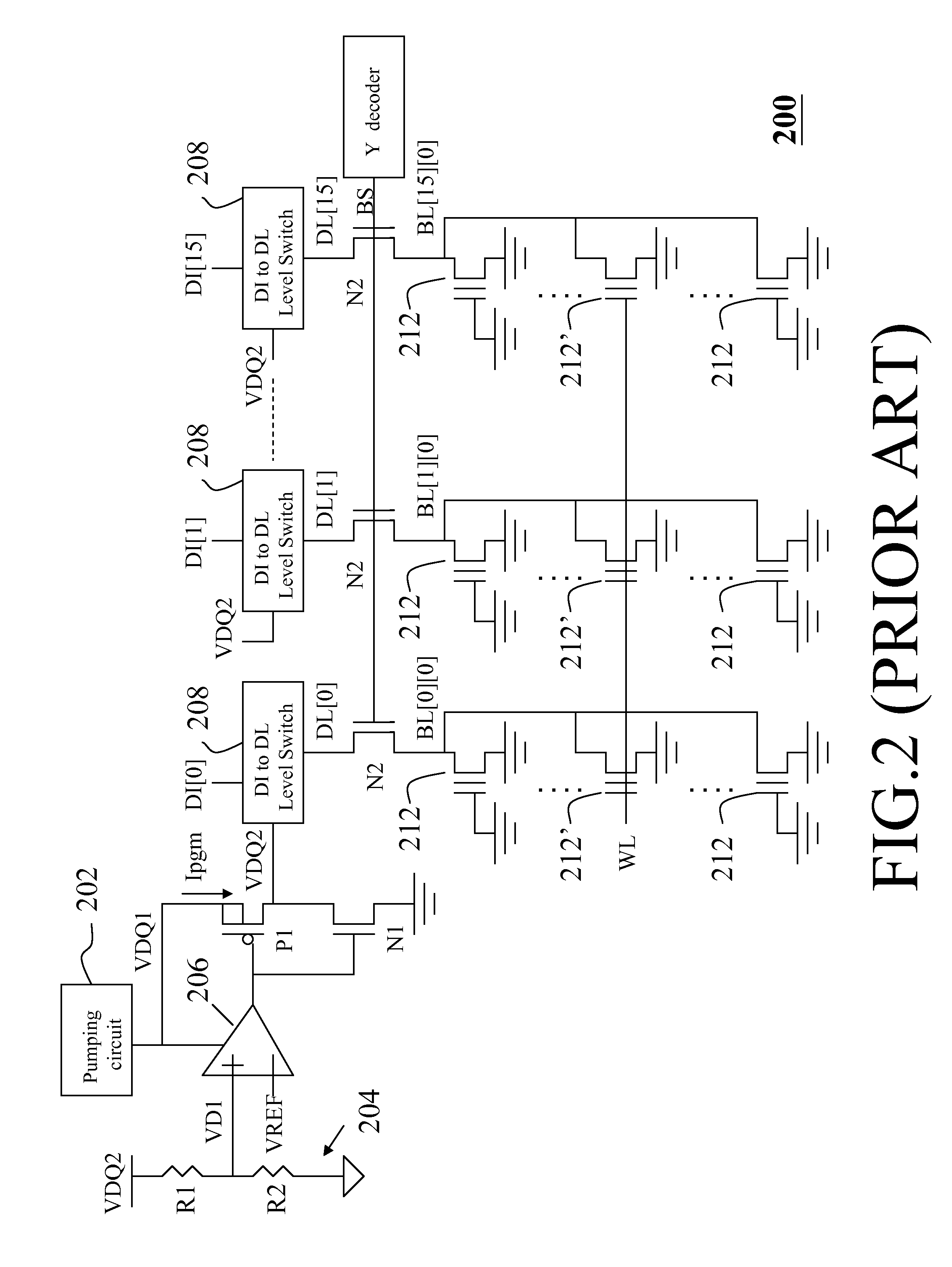

Flash memory with sequential programming

A method of programming a group of memory cells in a semiconductor memory device selecting a group of memory cells for programming, and enabling a first subgroup of memory cells from the group of memory cells for programming. After enabling the first subgroup, the programming method waits a first predetermined time period and after the first predetermined time period, enables a second subgroup of memory cells from the group of memory cells for programming while continuing to enable the first subgroup for programming.

Owner:ELITE SEMICON MEMORY TECH INC

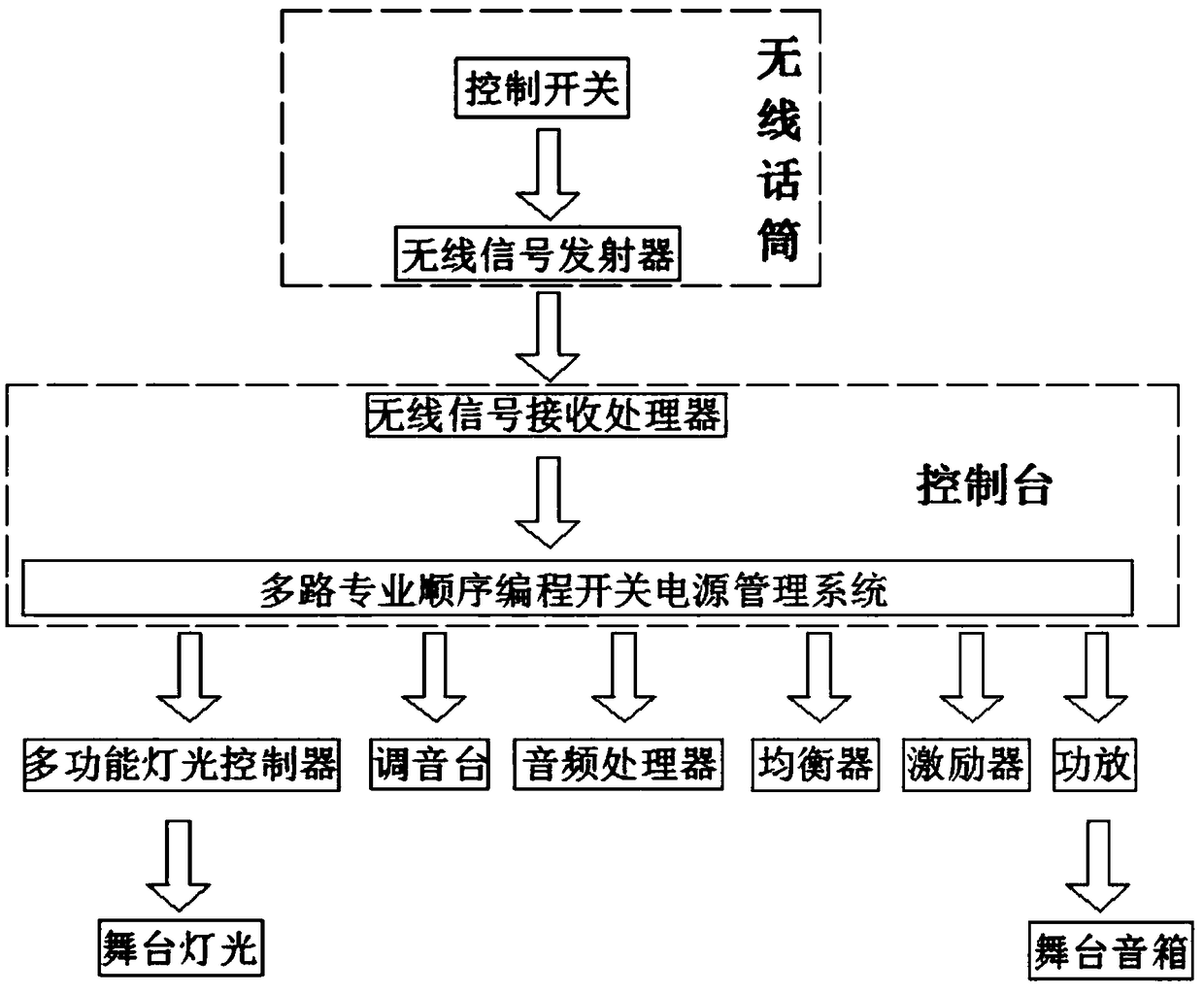

Wireless microphone remote control system

PendingCN109151666AImprove timelinessImprove display effectSignal processingMouthpiece/microphone attachmentsWireless microphoneSequential programming

The invention discloses a wireless microphone remote control system comprising a wireless microphone and a console. The wireless microphone is wirelessly connected with the console. The wireless microphone is internally provided with a wireless signal transmitter and a control switch. The control switch is connected with the signal transmitter through the circuit. The console is provided with a wireless signal receiving processor and a multi-channel professional sequential programming switching power supply management system. The wireless signal receiving processor is connected with the multi-channel professional sequential programming switching power supply management system through the line. The multi-channel professional sequential programming switching power supply management system isrespectively connected with the power switching line of a multi-functional light controller, a sound console, an audio processor, an equalizer and a power amplifier and controls the switching state of the multi-functional light controller, the sound console, the audio processor, the equalizer and the power amplifier. The microphone holder is enabled to turn on the control switch at any time according to the use demand of the stage so that the electronic product turn-on signal can be transmitted to the console in time through the wireless signal transmitter and the turn-on timeliness of the electronic product can be enhanced.

Owner:苏健荣