Patents

Literature

49 results about "Execute in place" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, execute in place (XIP) is a method of executing programs directly from long term storage rather than copying it into RAM. It is an extension of using shared memory to reduce the total amount of memory required.

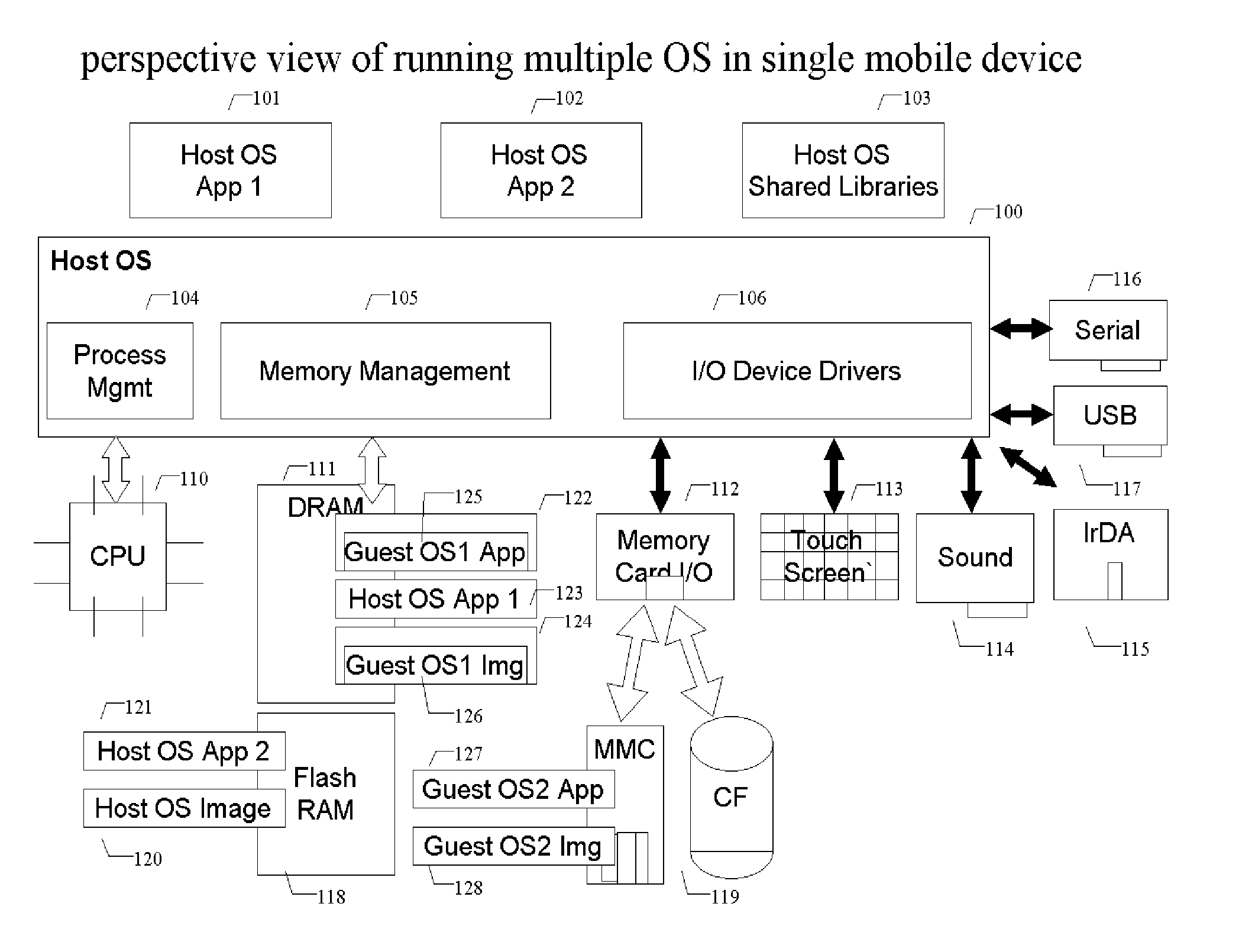

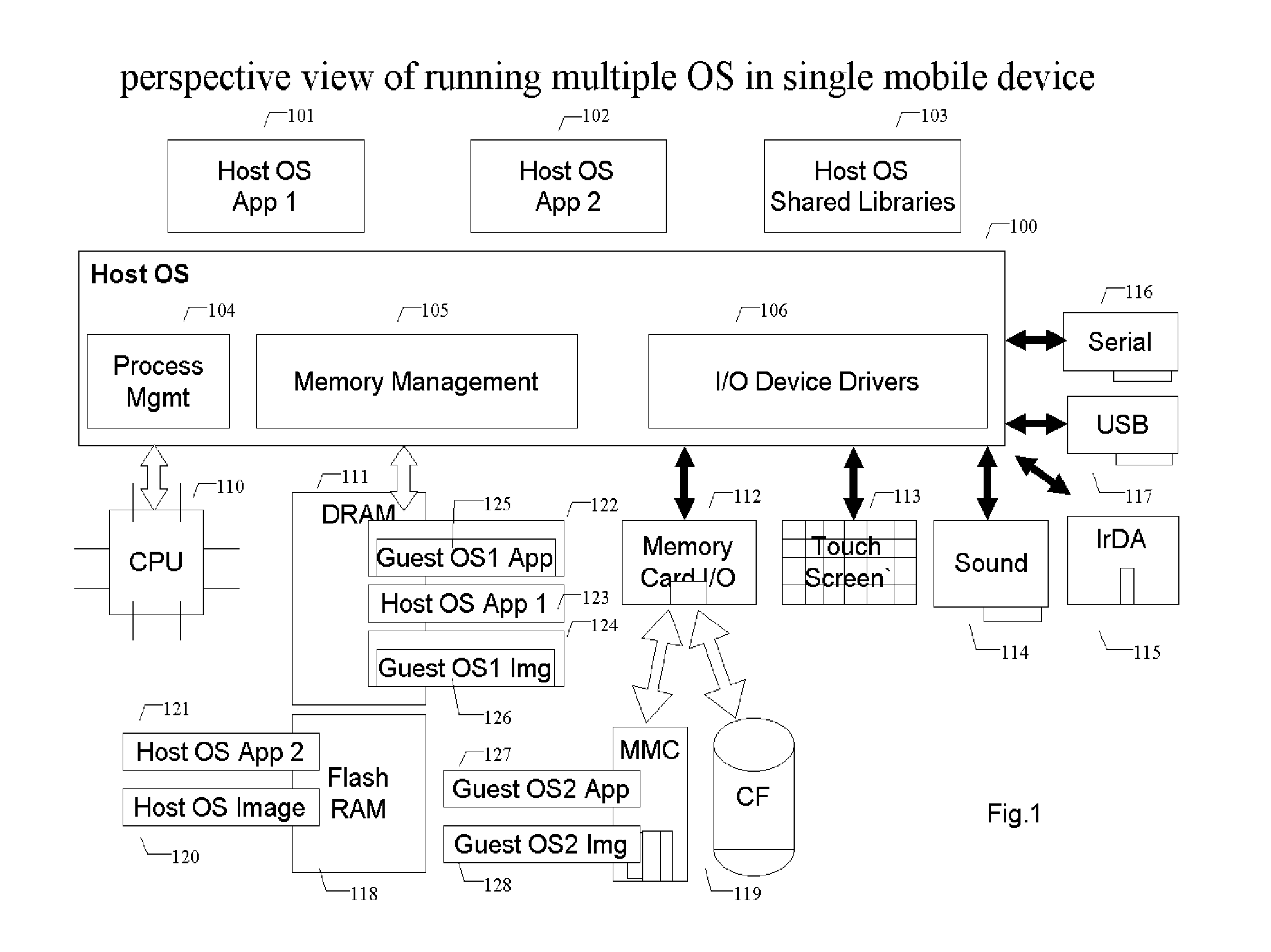

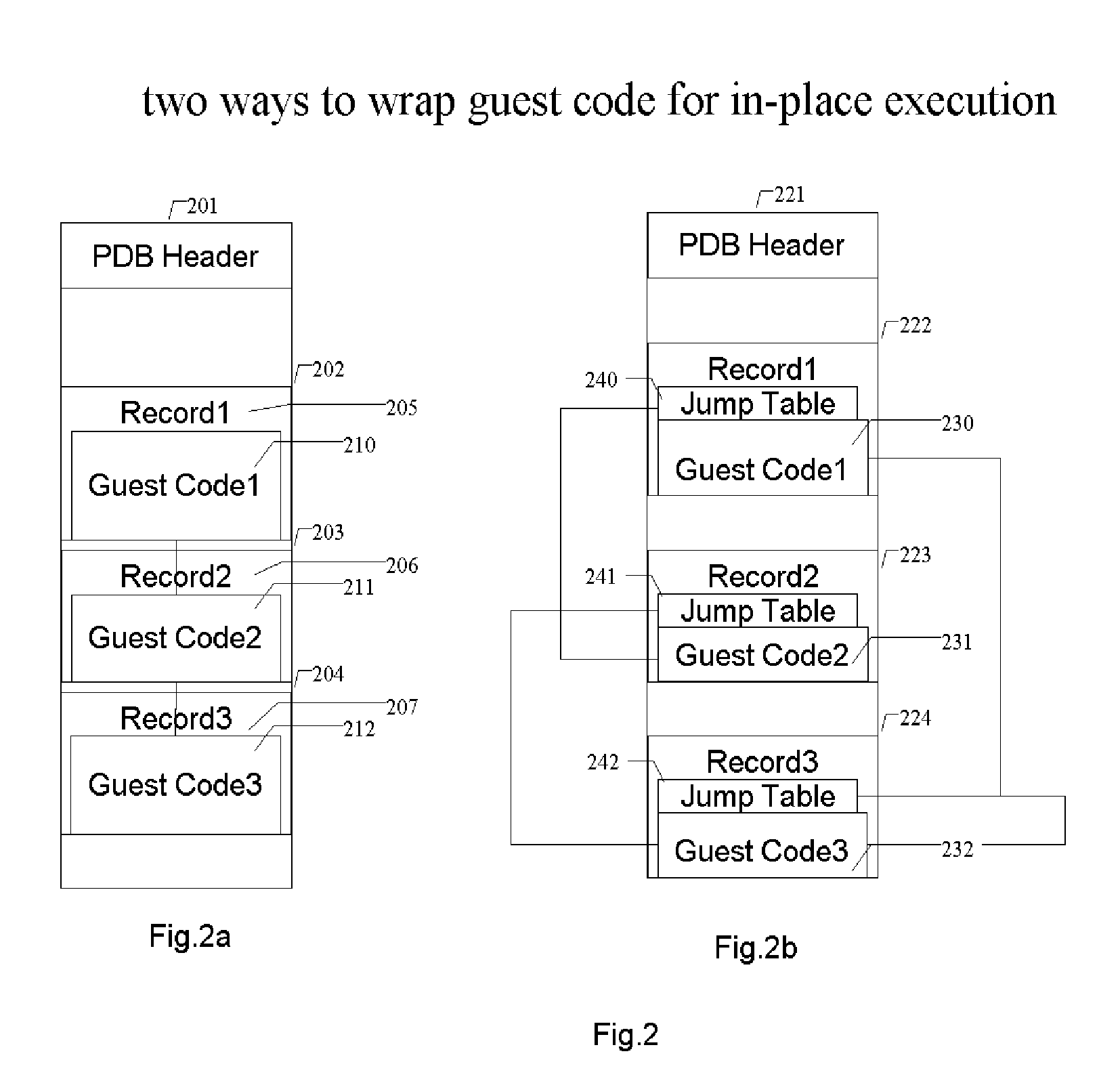

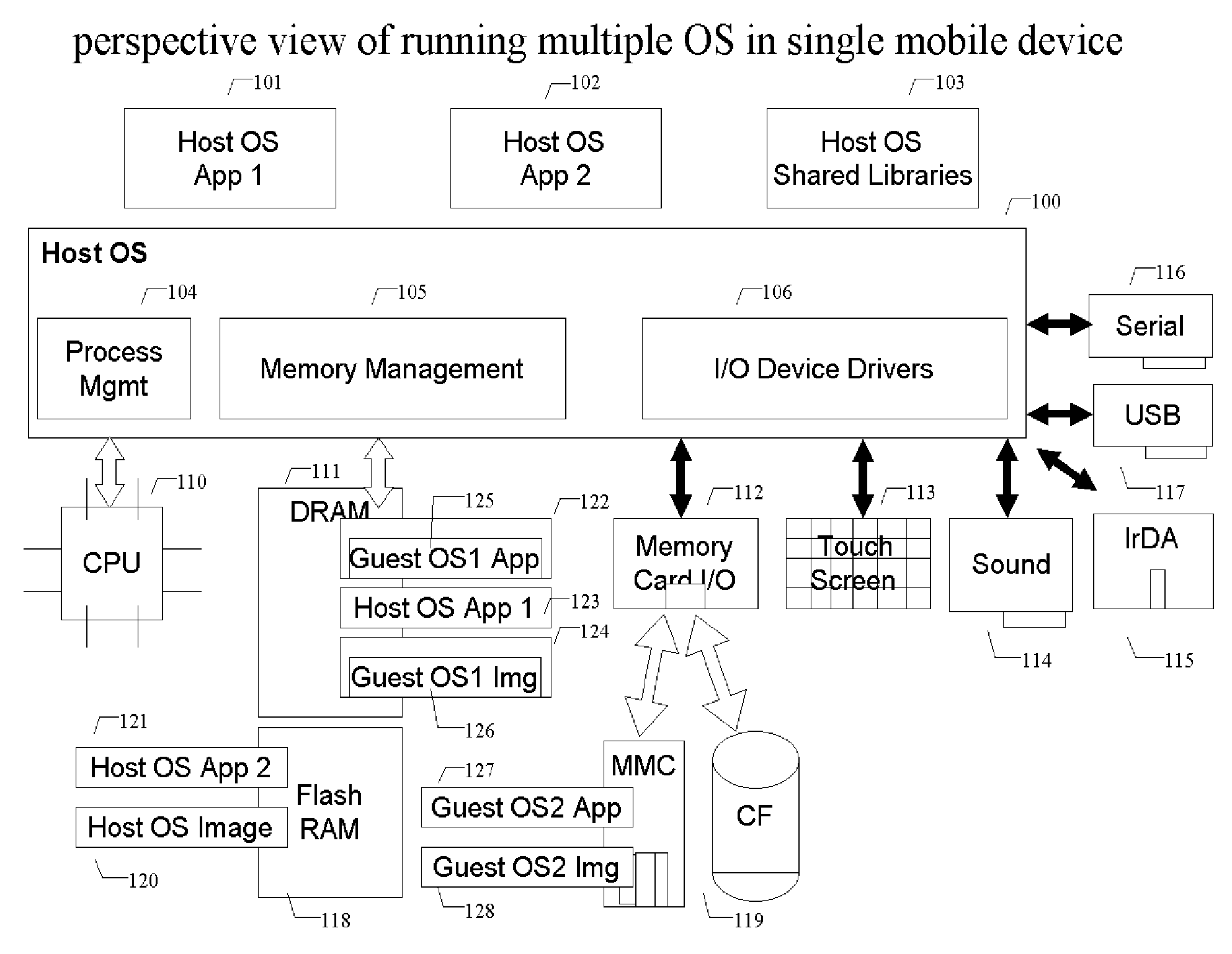

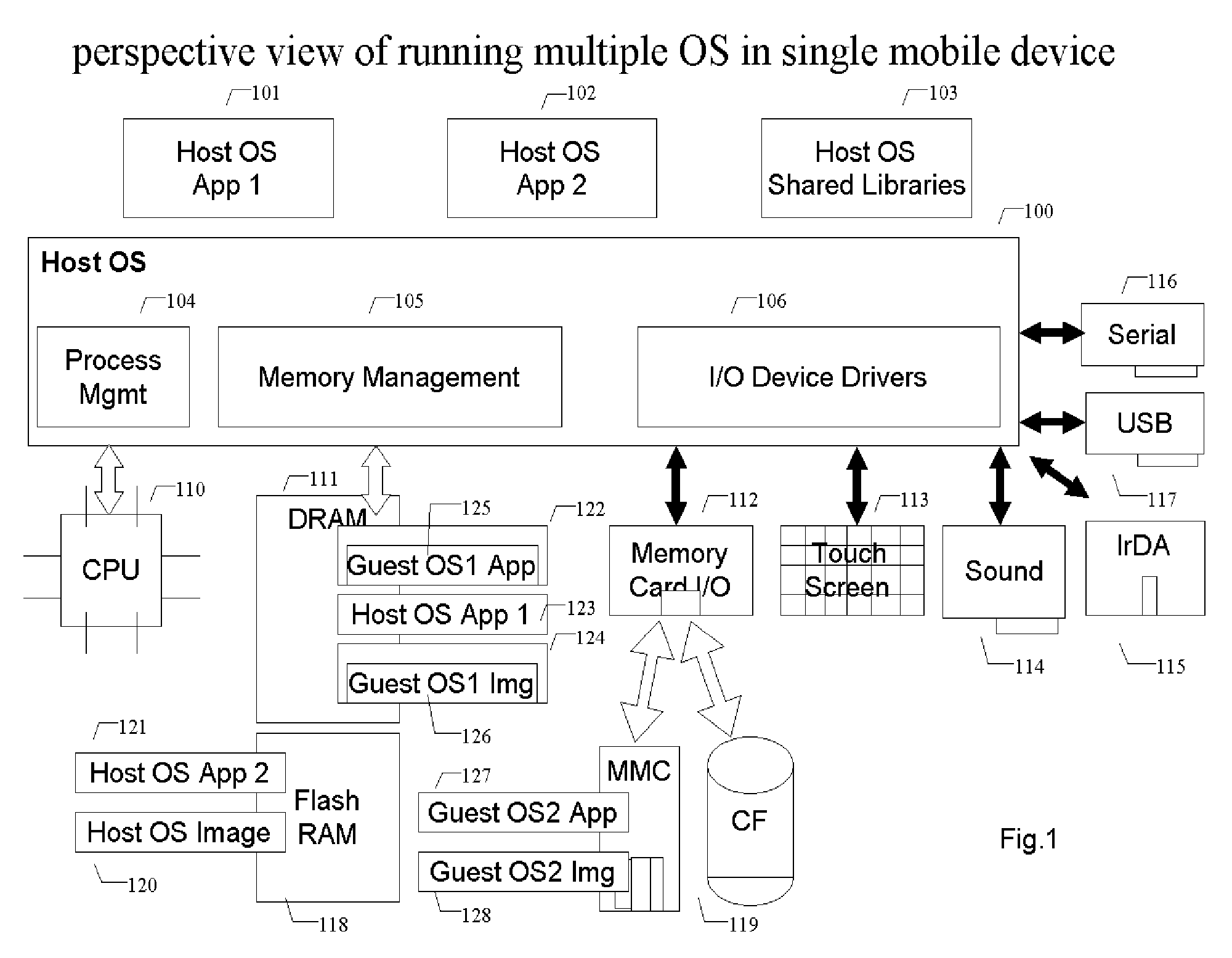

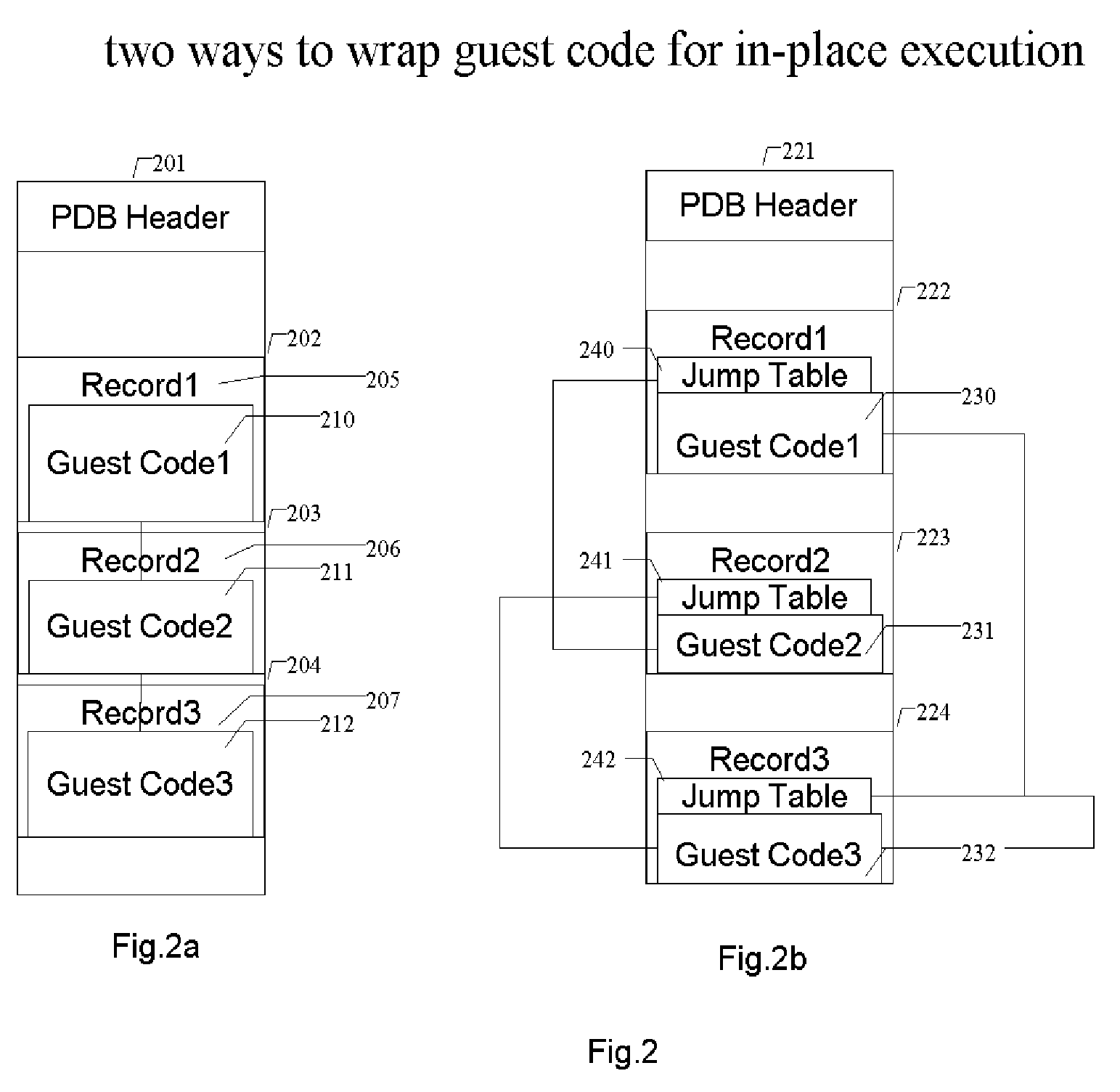

Methods and systems for running multiple operating systems in a single mobile device

ActiveUS20060010314A1Reduce memory usageError detection/correctionDigital computer detailsOperational systemEngineering

Methods and systems for running multiple operating systems in a single embedded or mobile device (include PDA, cellular phone and other devices) are disclosed. The invention allows a mobile device that normally can only run a single operating system to run another operating system while preserving the state and data of the original operating system. Guest OS is packaged into special format recognizable by the host OS that still can be executed in place by the system. The Methods include: •Change the memory protection bits for the original OS; •Fake a reduced physical memory space for guest OS; •Use special memory device driver to claim memories of host OS; •Backup whole image of the current OS and data to external memory card.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

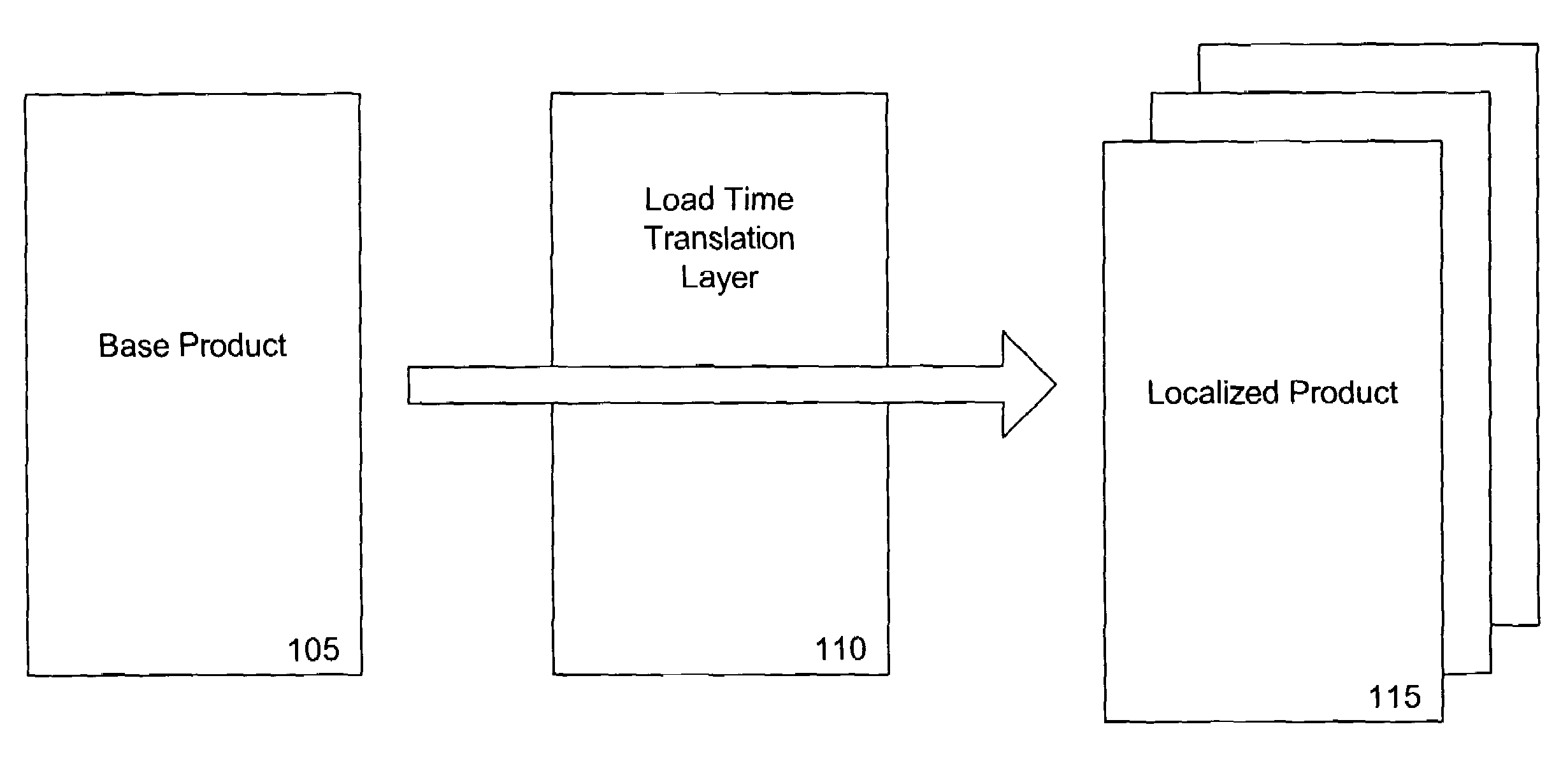

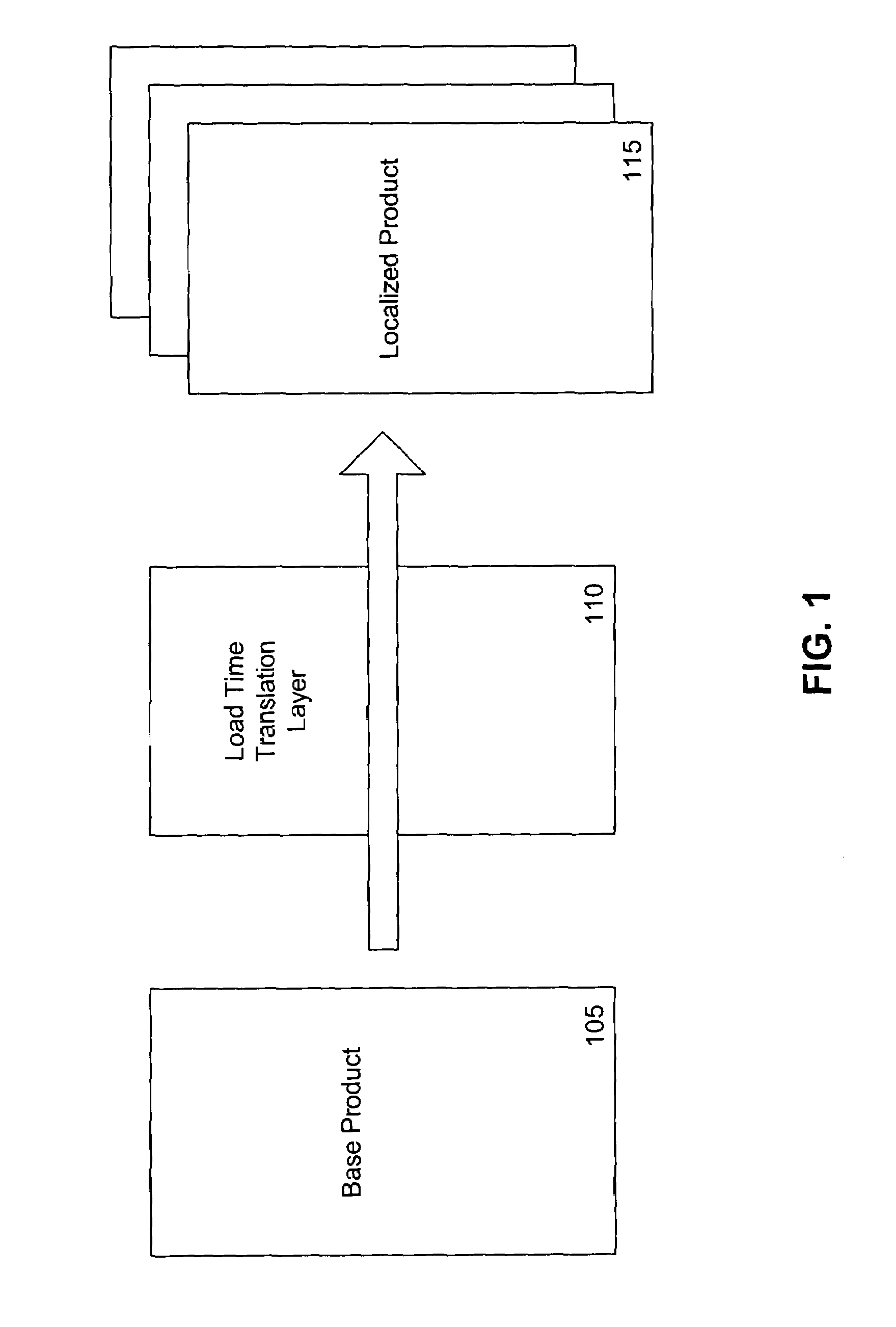

Methods and systems for external localization

Embodiments of the present invention relate to methods, systems and computer-readable media for external localization of a software product. This external localization comprises loading a base product having one or more calls to an operating system to load language specific data. A language specific localized product is generated, during loading of the base product, by converting the base product to a localized product using and at least one language map containing language specific data. The localized product is then executed in place of the base product.

Owner:MICROSOFT TECH LICENSING LLC

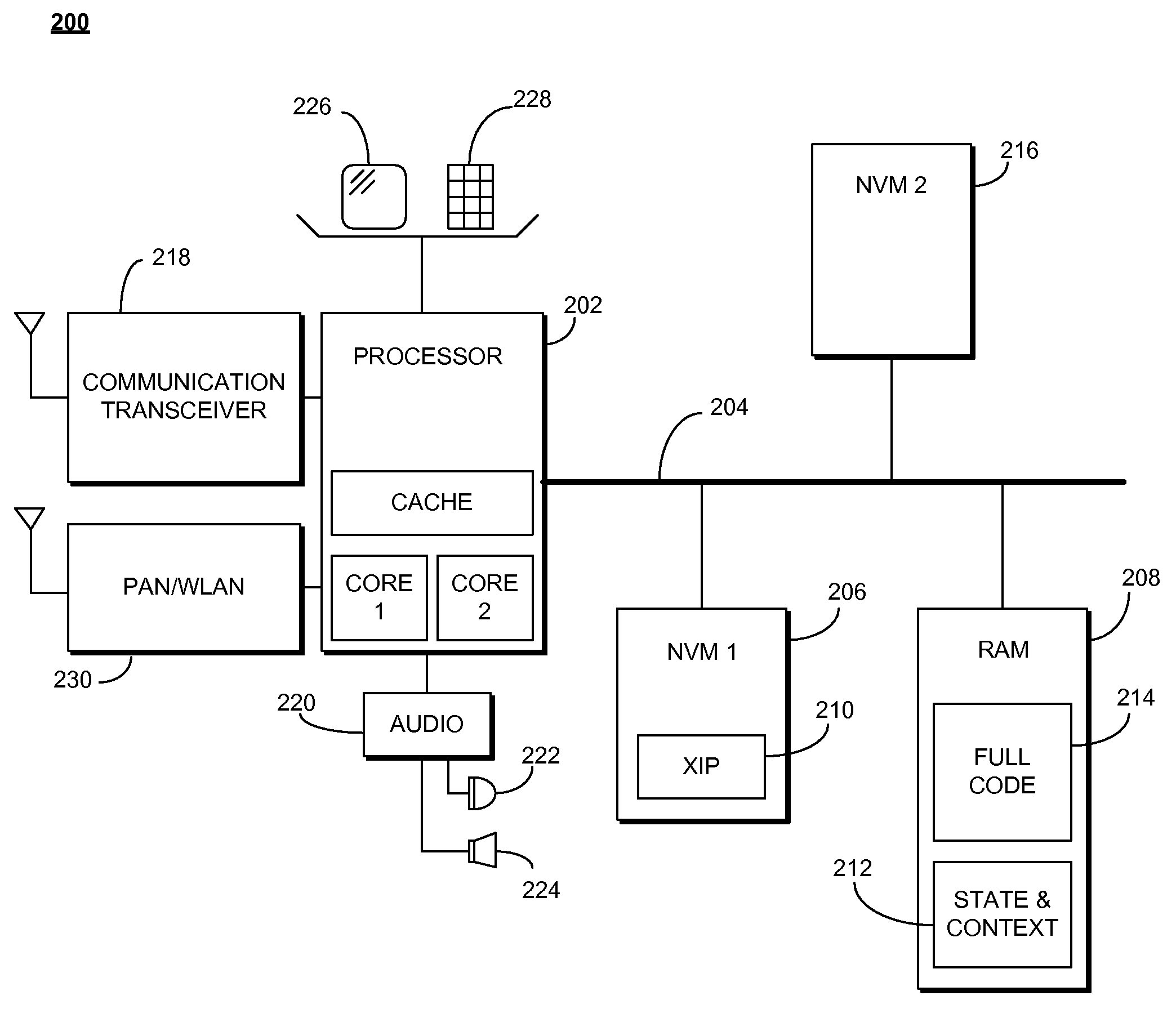

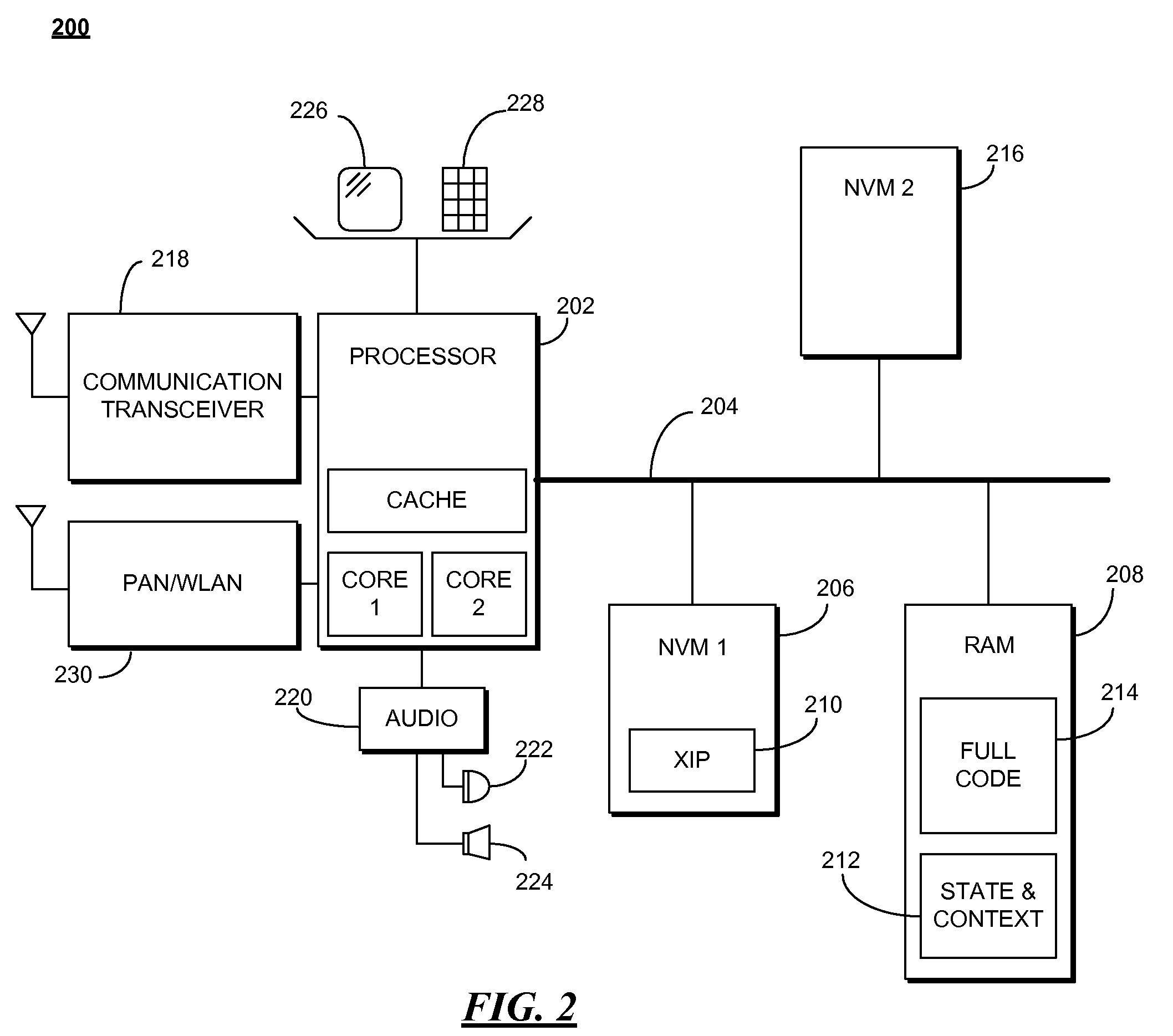

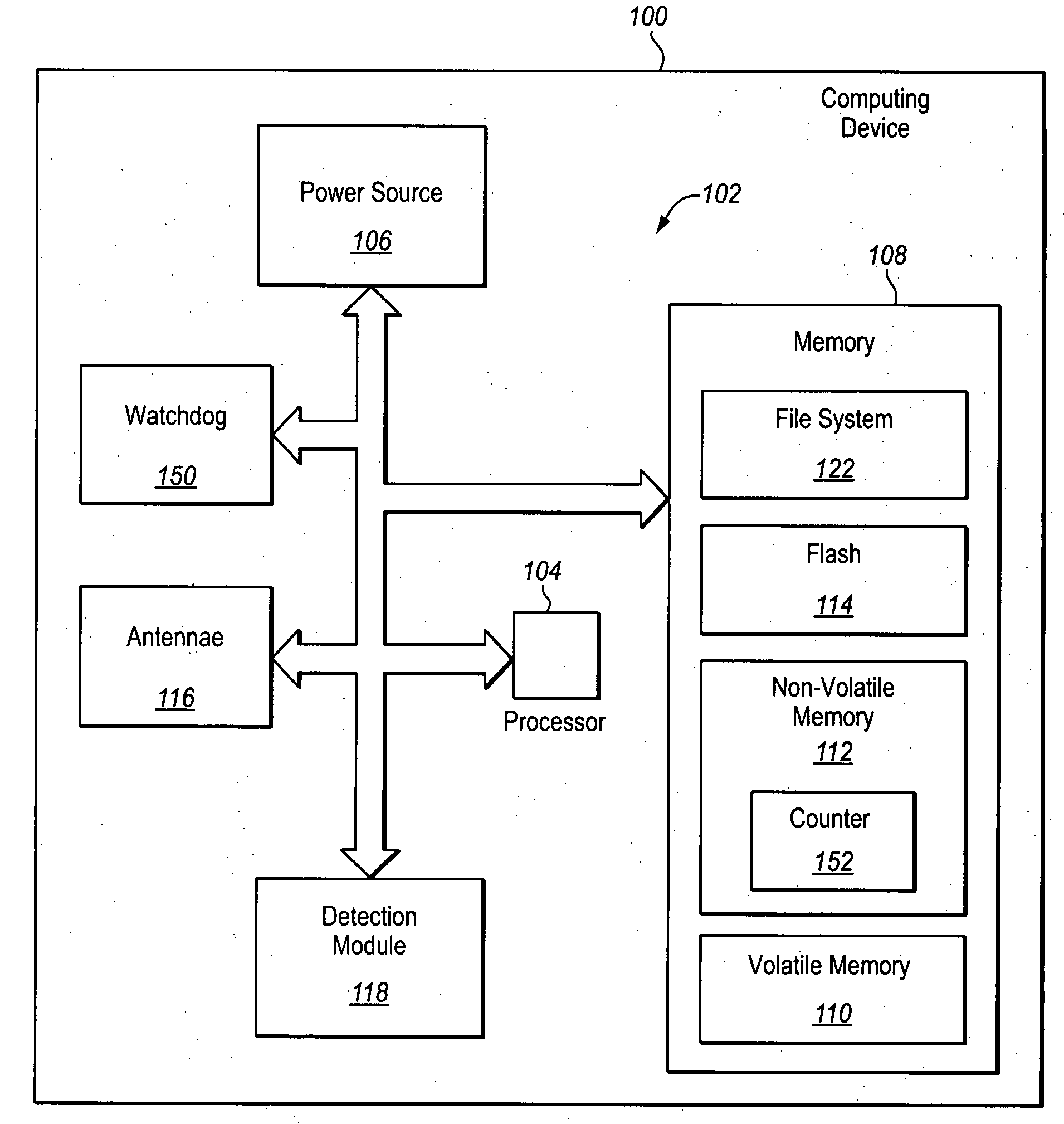

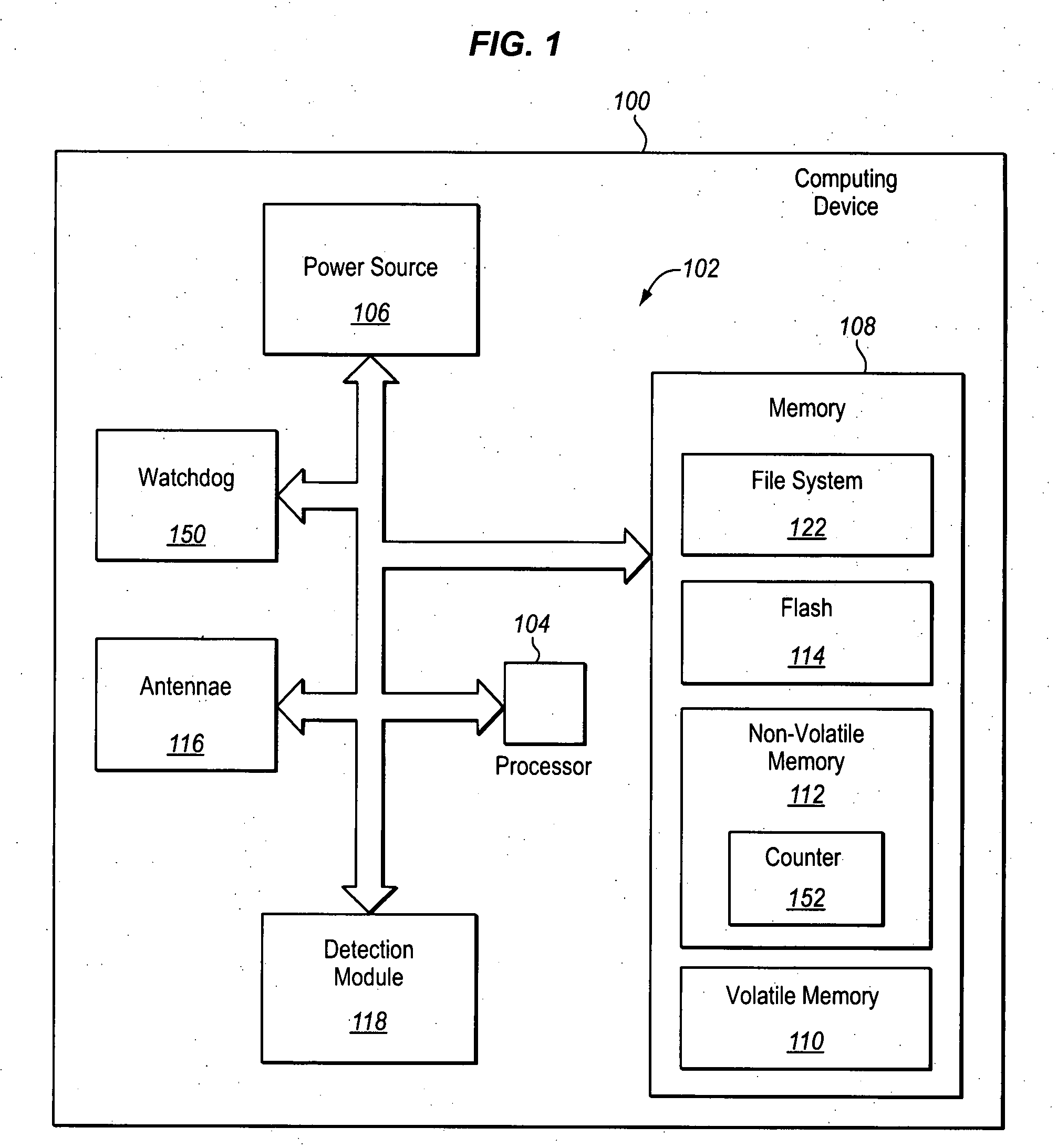

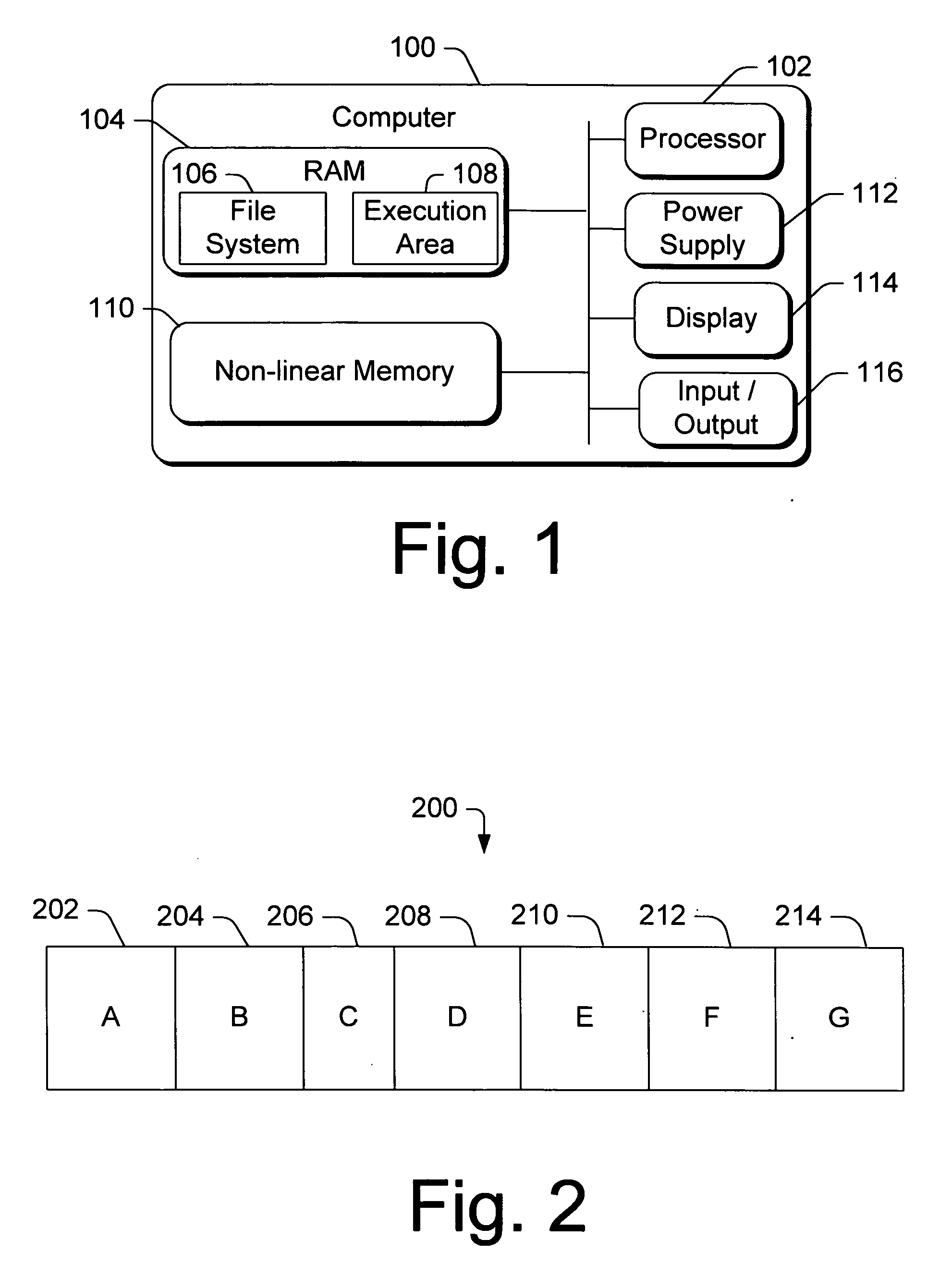

Method and apparatus for fast booting a portable computing device allowing for immediate operation

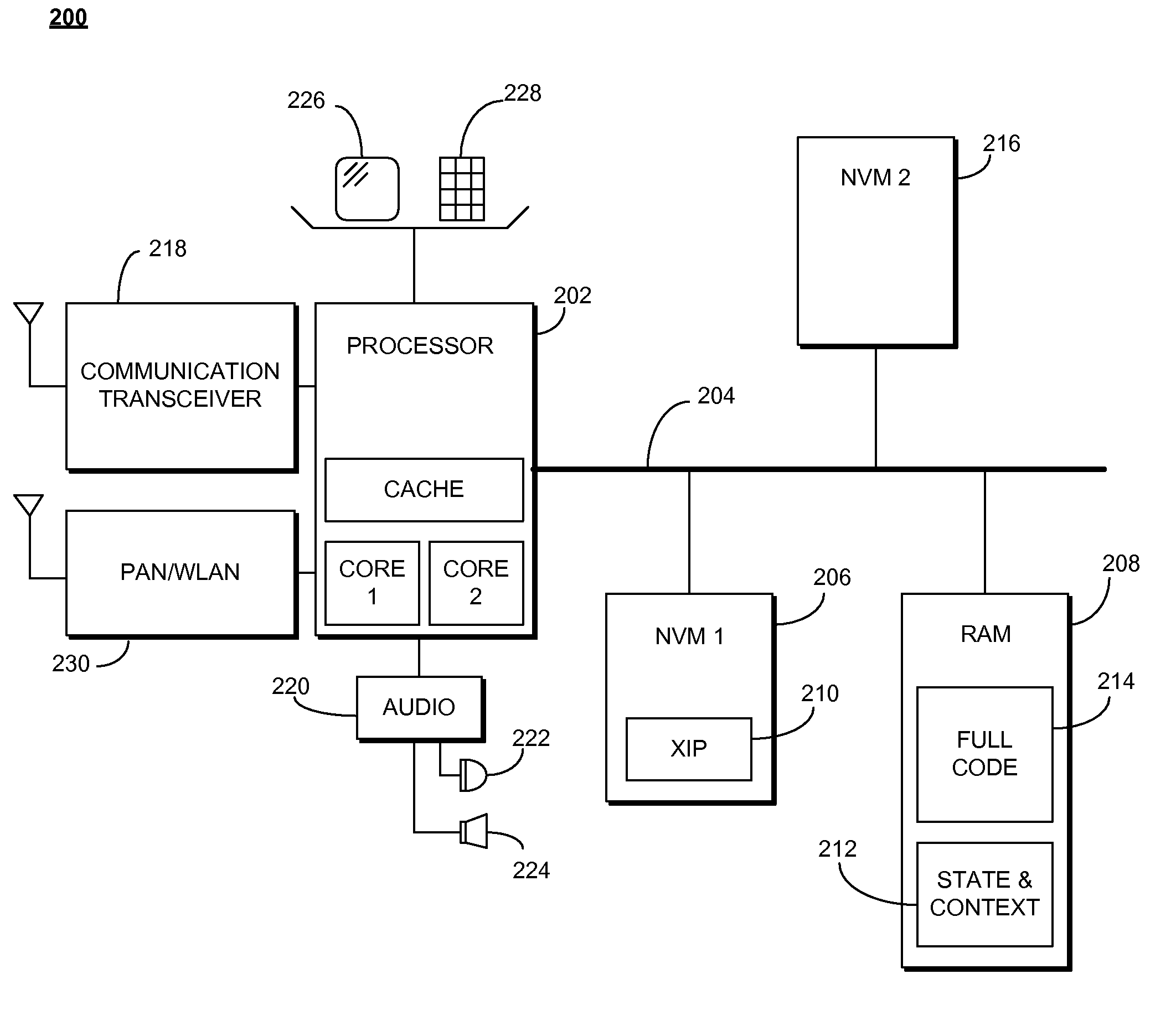

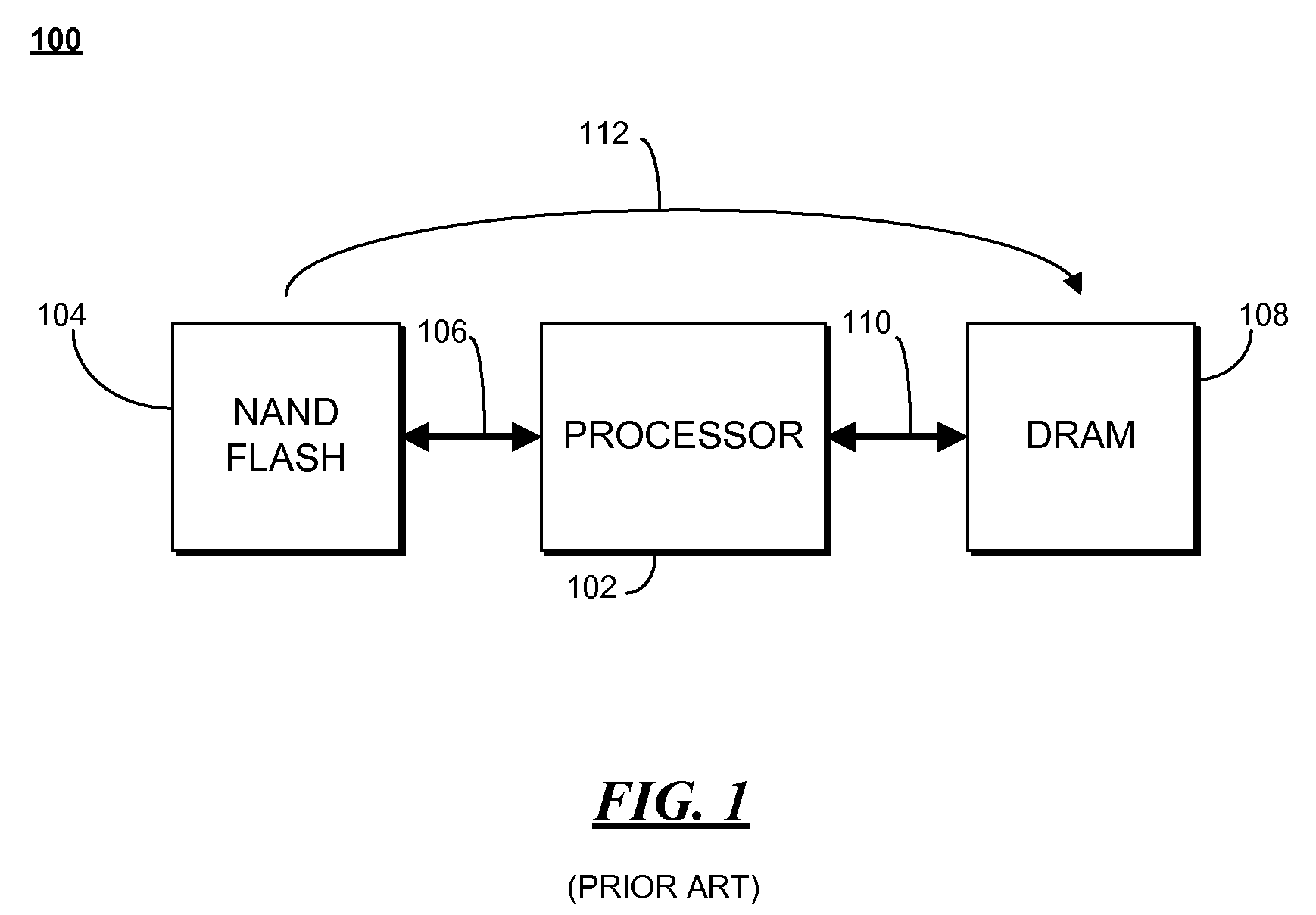

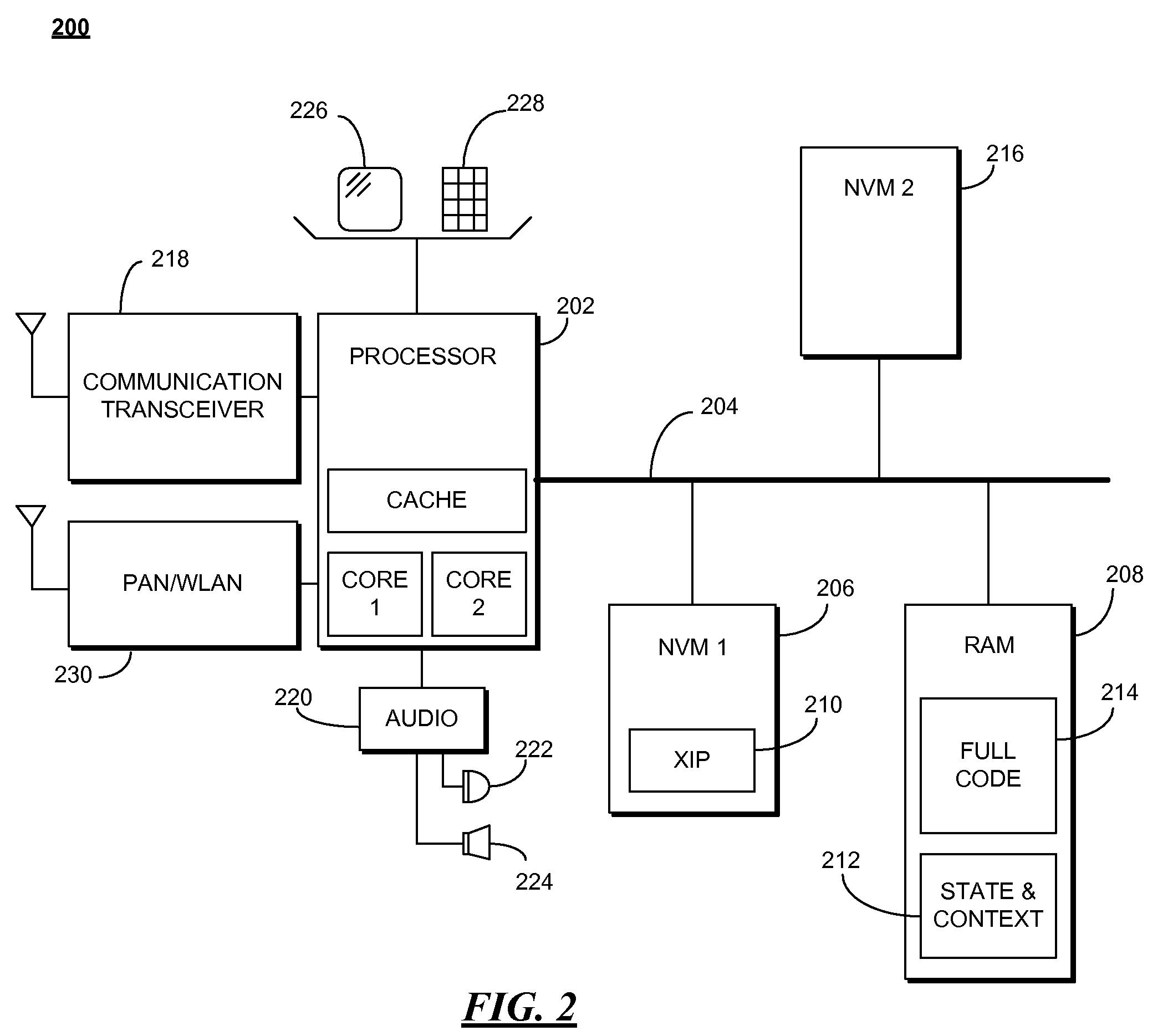

InactiveUS20100058045A1Memory adressing/allocation/relocationDigital computer detailsUser interfaceVolatile memory

The present invention discloses a portable computing device (200) including a processor (202), non-volatile memory (206), and a volatile memory (208). An execute in place (XIP) kernel (210) stored in the non-volatile memory is executed immediately upon powering up the device. As the XIP kernel is executed, the processor maintain state and context information (212) in the volatile memory. The XIP kernel includes user interface and application segments, along the user to perform some functions immediately upon powering up the device. While executing the XIP kernel and full code instantiation (214) is loaded into the volatile memory. The full code instantiation includes identical code as is in the XIP kernel, in addition to other code. Once loaded, execution is switched (412) from the XIP kernel to the full code instantiation, providing full functionality of the device.

Owner:WIRELESS SILICON GROUP

Methods and systems for running multiple operating systems in a single mobile device

ActiveUS7424601B2Reduce memory usageError detection/correctionDigital computer detailsExternal storageOperational system

Methods and systems for running multiple operating systems in a single embedded or mobile device (include PDA, cellular phone and other devices) are disclosed. The invention allows a mobile device that normally can only run a single operating system to run another operating system while preserving the state and data of the original operating system. Guest OS is packaged into special format recognizable by the host OS that still can be executed in place by the system. The Methods include: Change the memory protection bits for the original OS; Fake a reduced physical memory space for guest OS; Use special memory device driver to claim memories of host OS; Backup whole image of the current OS and data to external memory card.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Method and apparatus for fast booting a portable computing device allowing for immediate operation

The present invention discloses a portable computing device (200) including a processor (202), non-volatile memory (206), and a volatile memory (208). An execute in place (XIP) kernel (210) stored in the non-volatile memory is executed immediately upon powering up the device. As the XIP kernel is executed, the processor maintain state and context information (212) in the volatile memory. The XIP kernel includes user interface and application segments, allow the user to perform some functions immediately upon powering up the device. While executing the XIP kernel and full code instantiation (214) is loaded into the volatile memory. The full code instantiation includes identical code as is in the XIP kernel, in addition to other code. Once loaded, execution is switched (412) from the XIP kernel to the full code instantiation, providing full functionality of the device.

Owner:WIRELESS SILICON GROUP

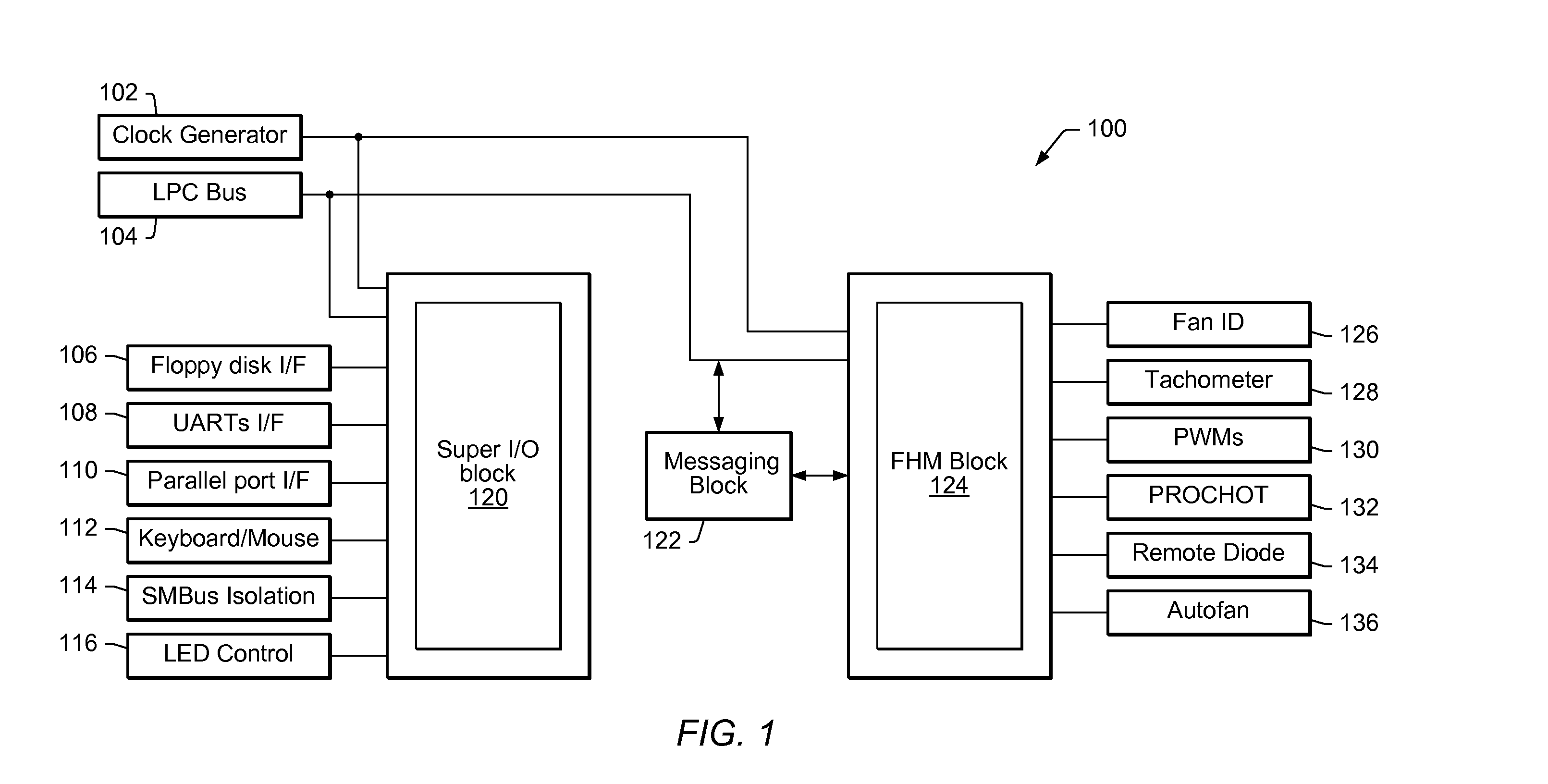

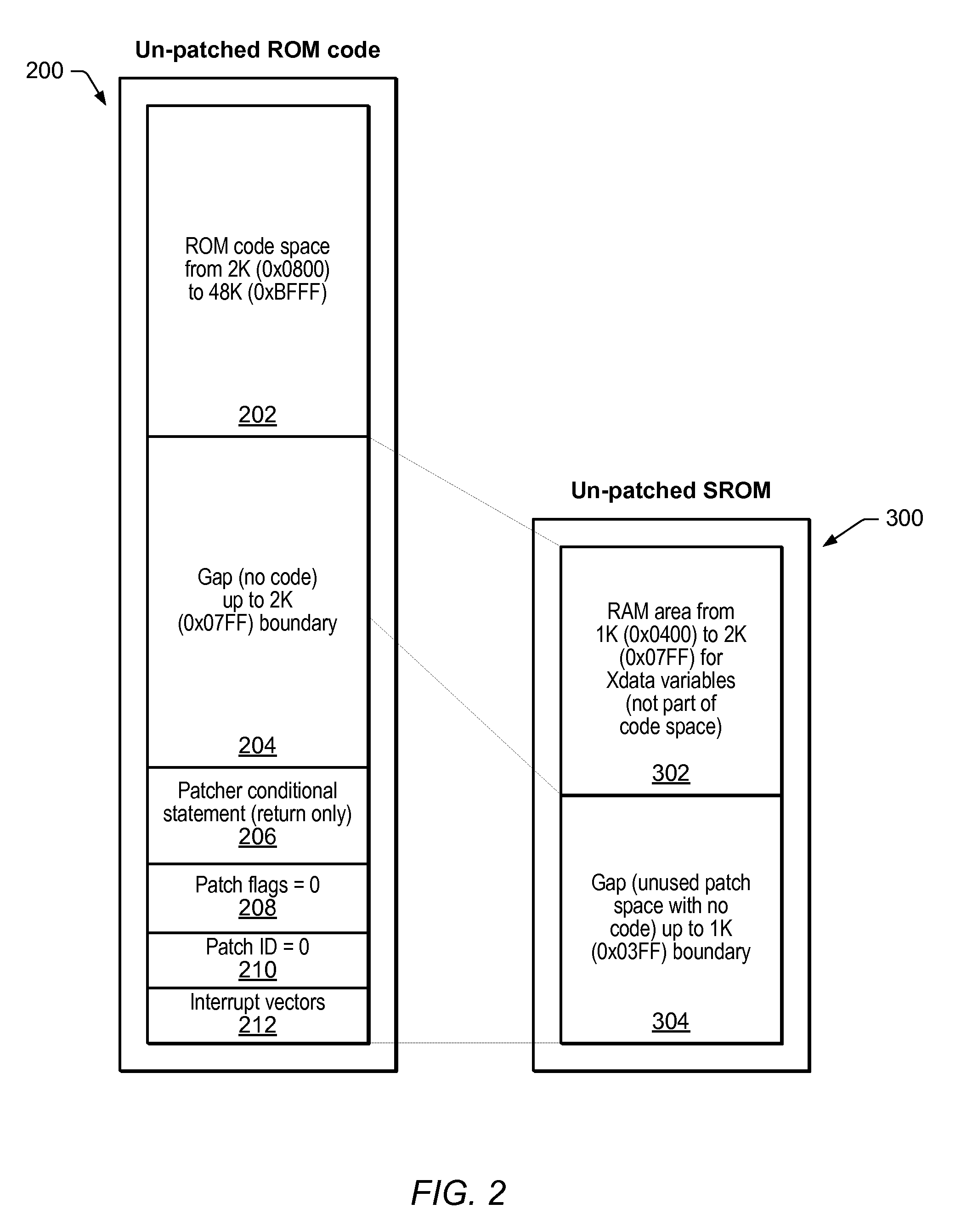

Firmware ROM Patch Method

Owner:MICROCHIP TECH INC

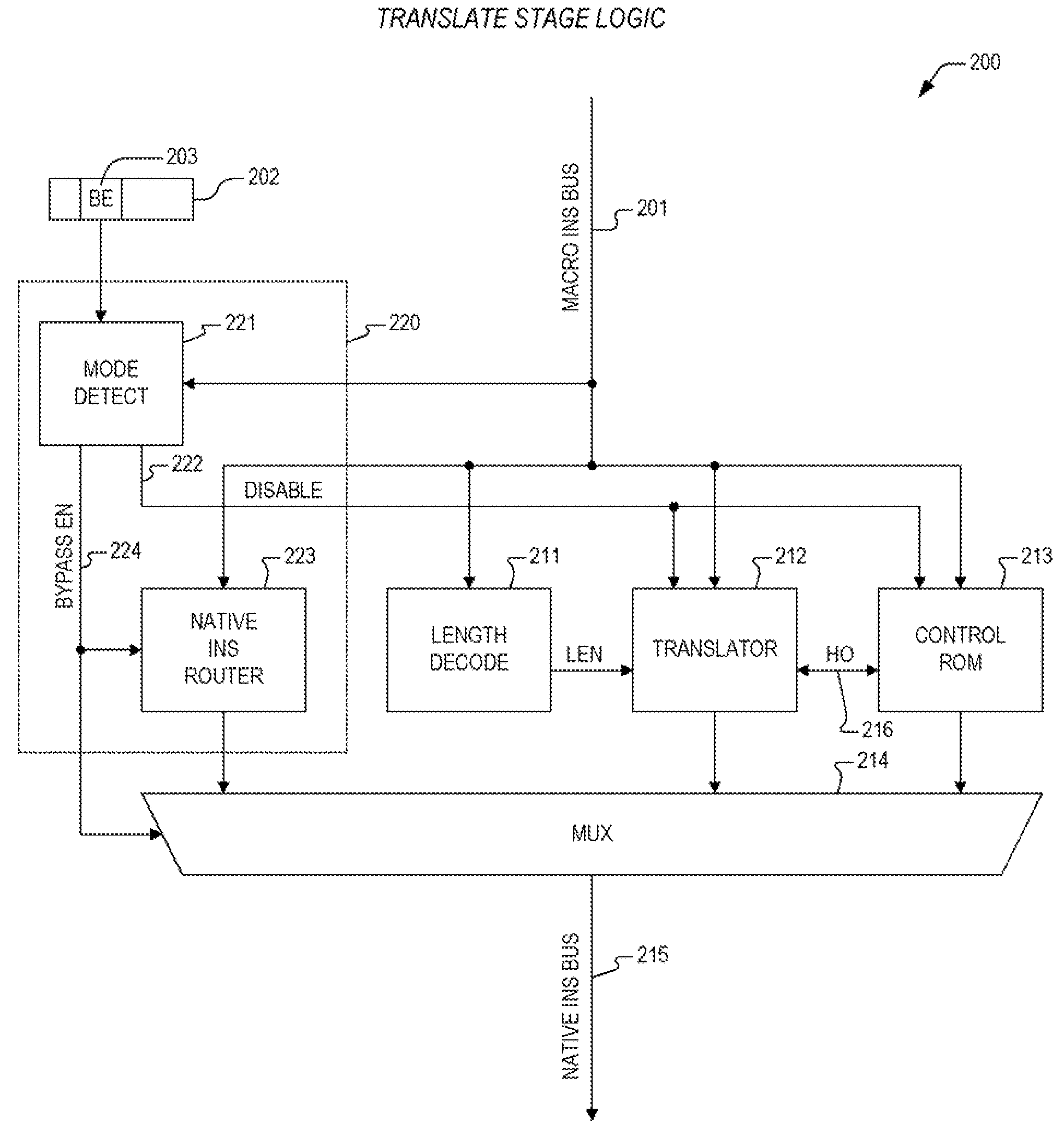

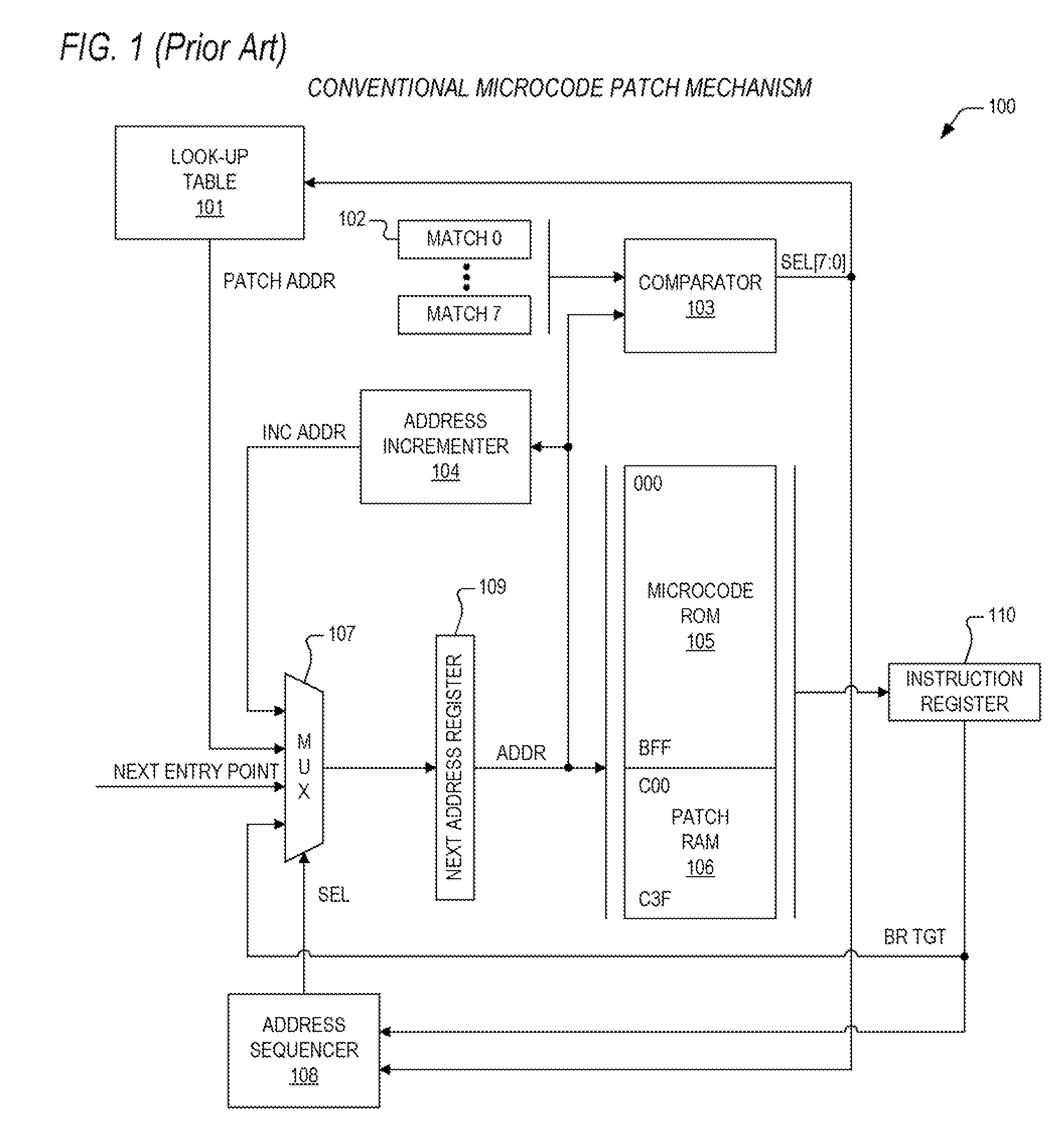

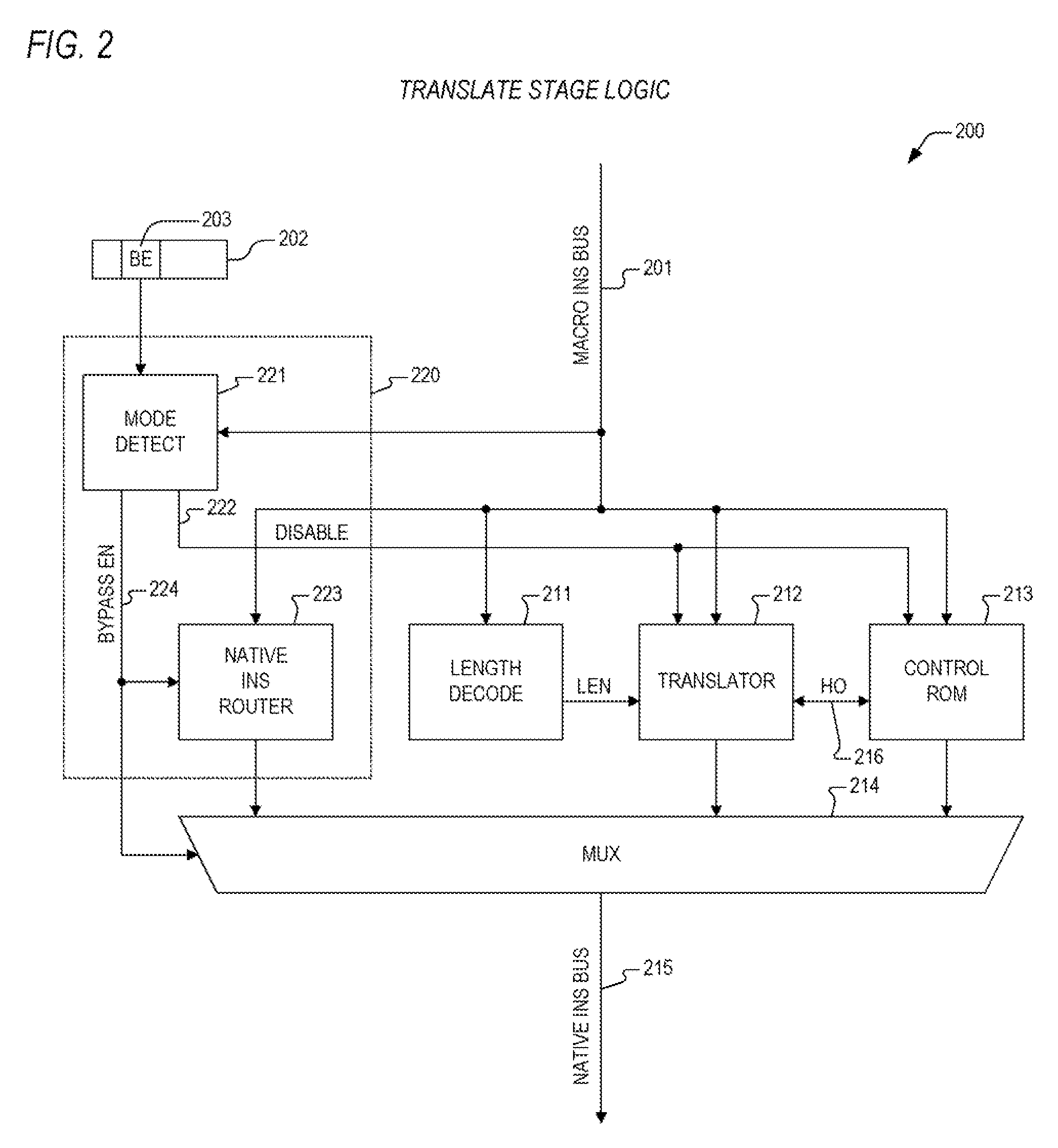

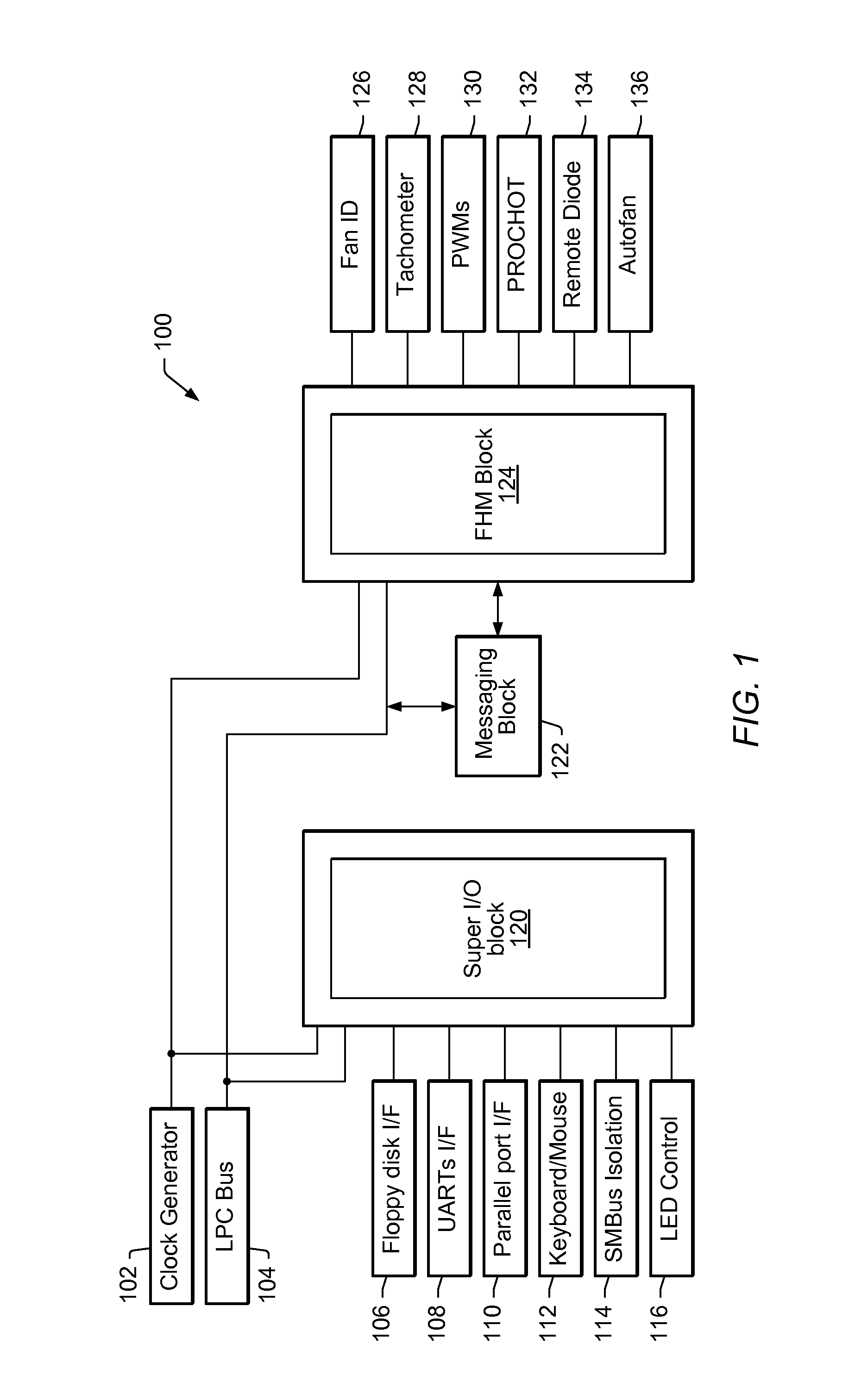

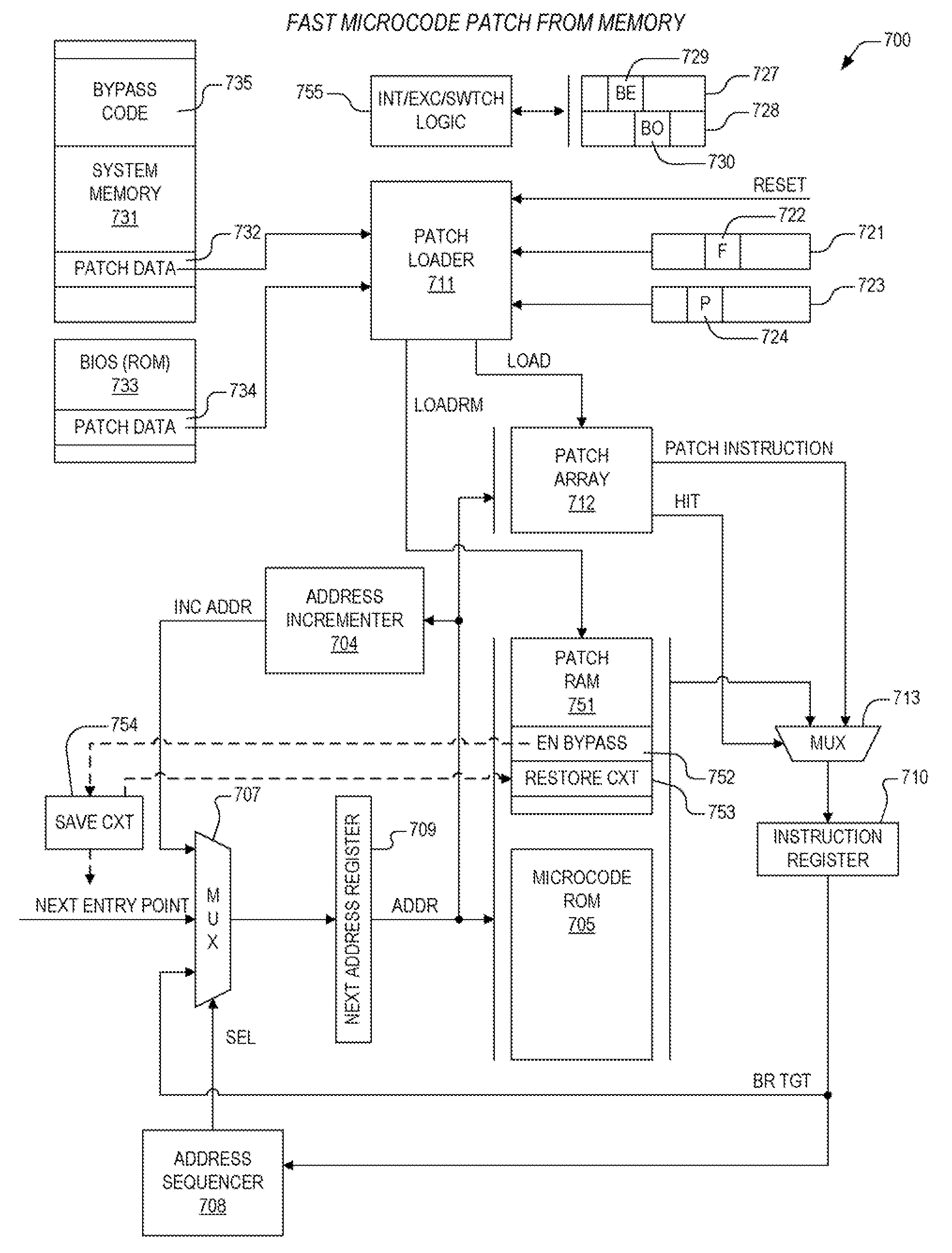

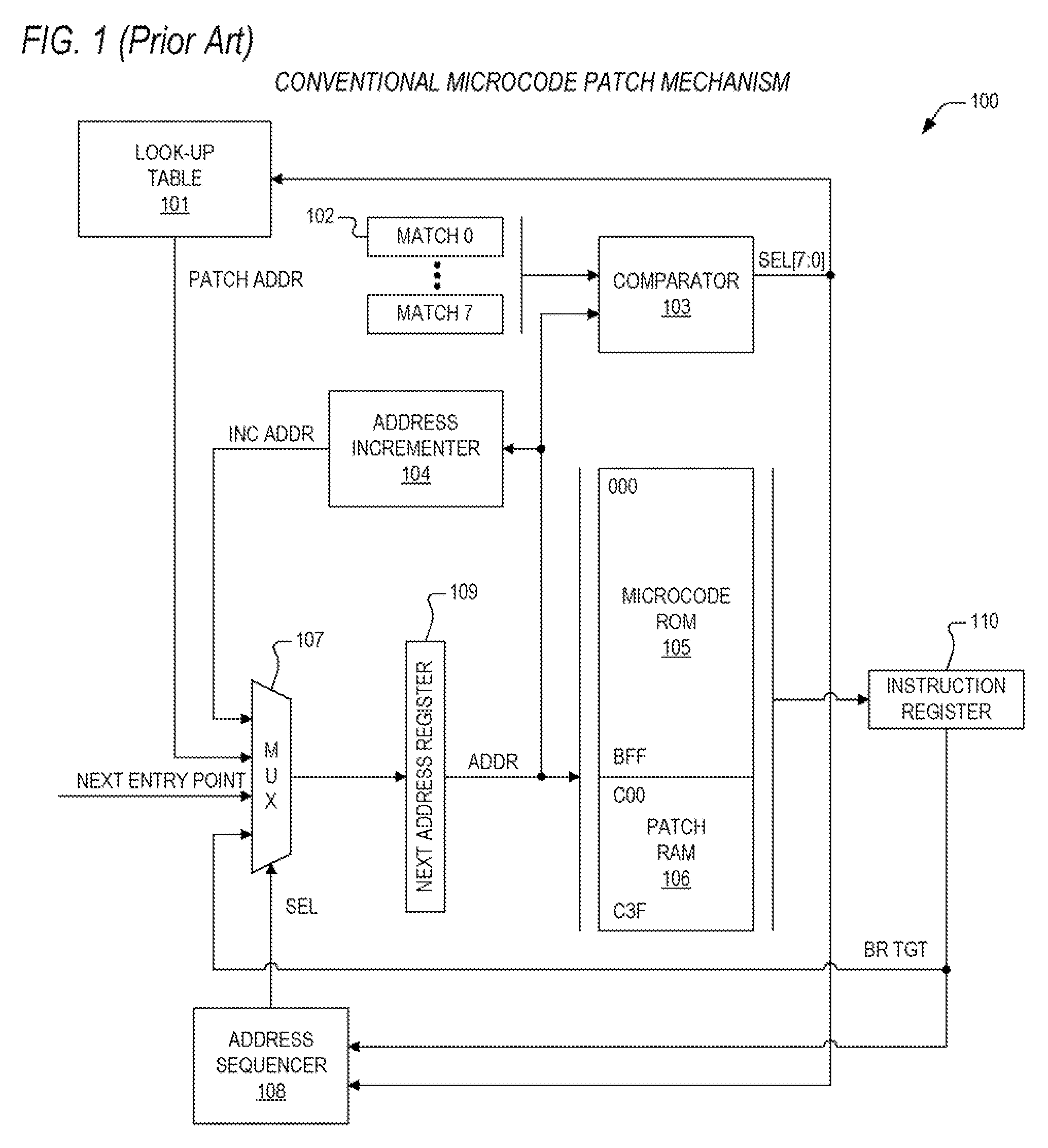

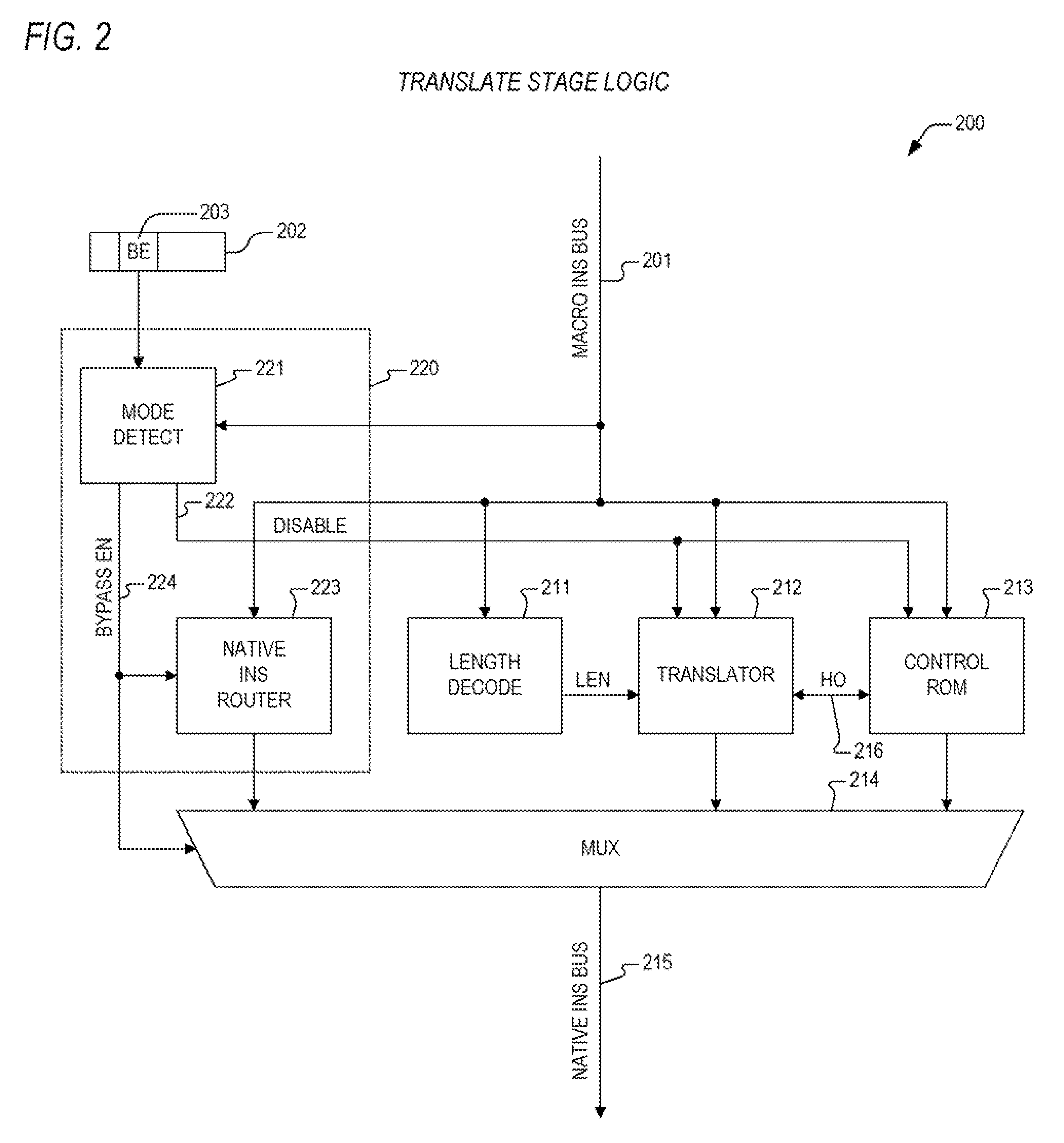

Apparatus and method for fast one-to-many microcode patch

A microcode patch apparatus including a patch array, a mux, and a RAM. The patch array receives a microcode ROM address and determines that the microcode ROM address matches one of a plurality of entries within the patch array. The patch array outputs a corresponding branch instruction and asserts a hit signal. The branch instruction prescribes a microcode branch target address. The mux receives the branch instruction from the patch array and a micro instruction corresponding to the microcode ROM address from a microcode ROM. The mux provides the micro instruction or the corresponding branch instruction to an instruction register based upon the state of the hit signal. The RAM stores a plurality of patch instructions that are to be executed in place of the micro instruction. The first one of the plurality of patch instructions is stored at a location in the RAM corresponding to the microcode branch target address.

Owner:VIA TECH INC

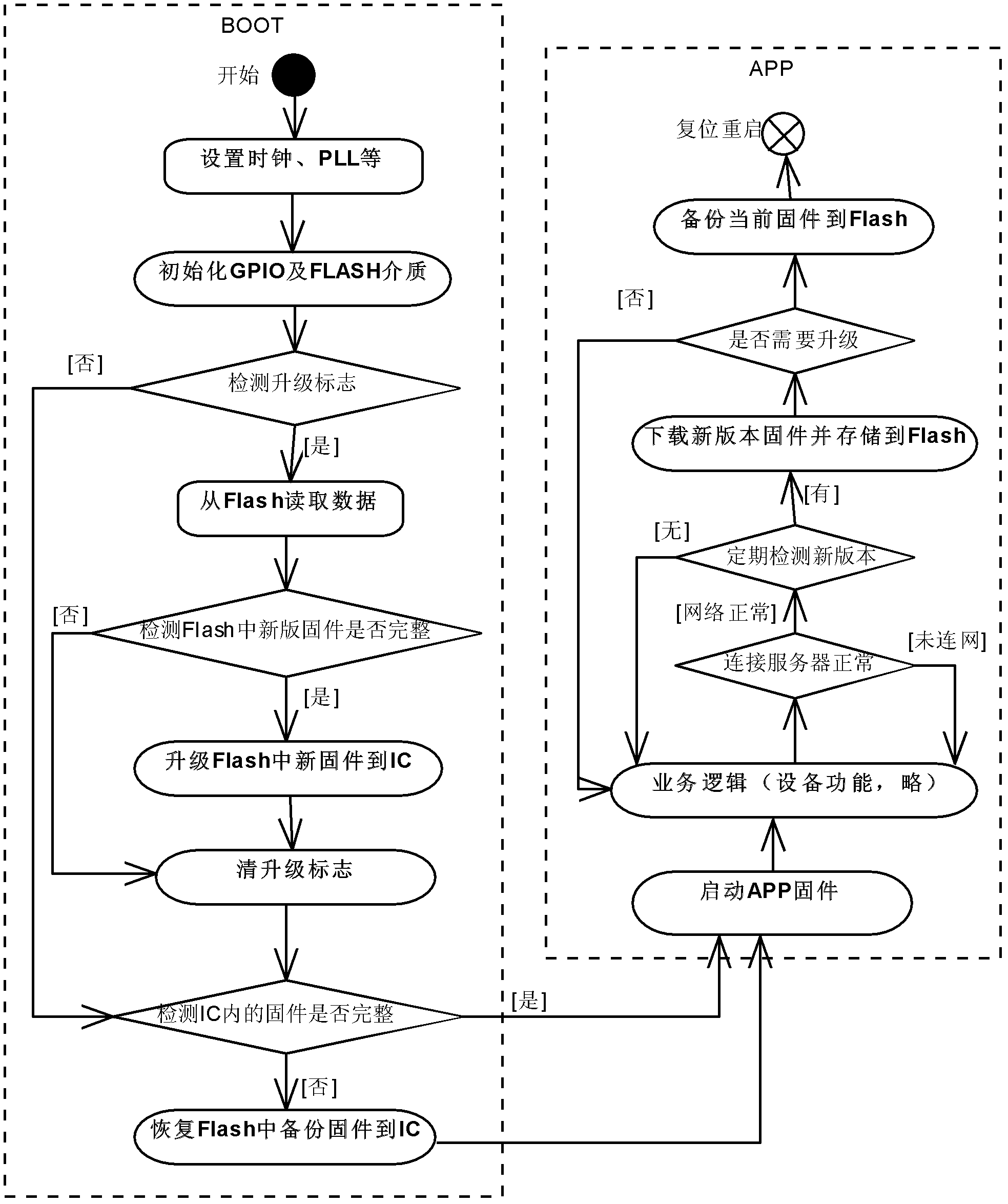

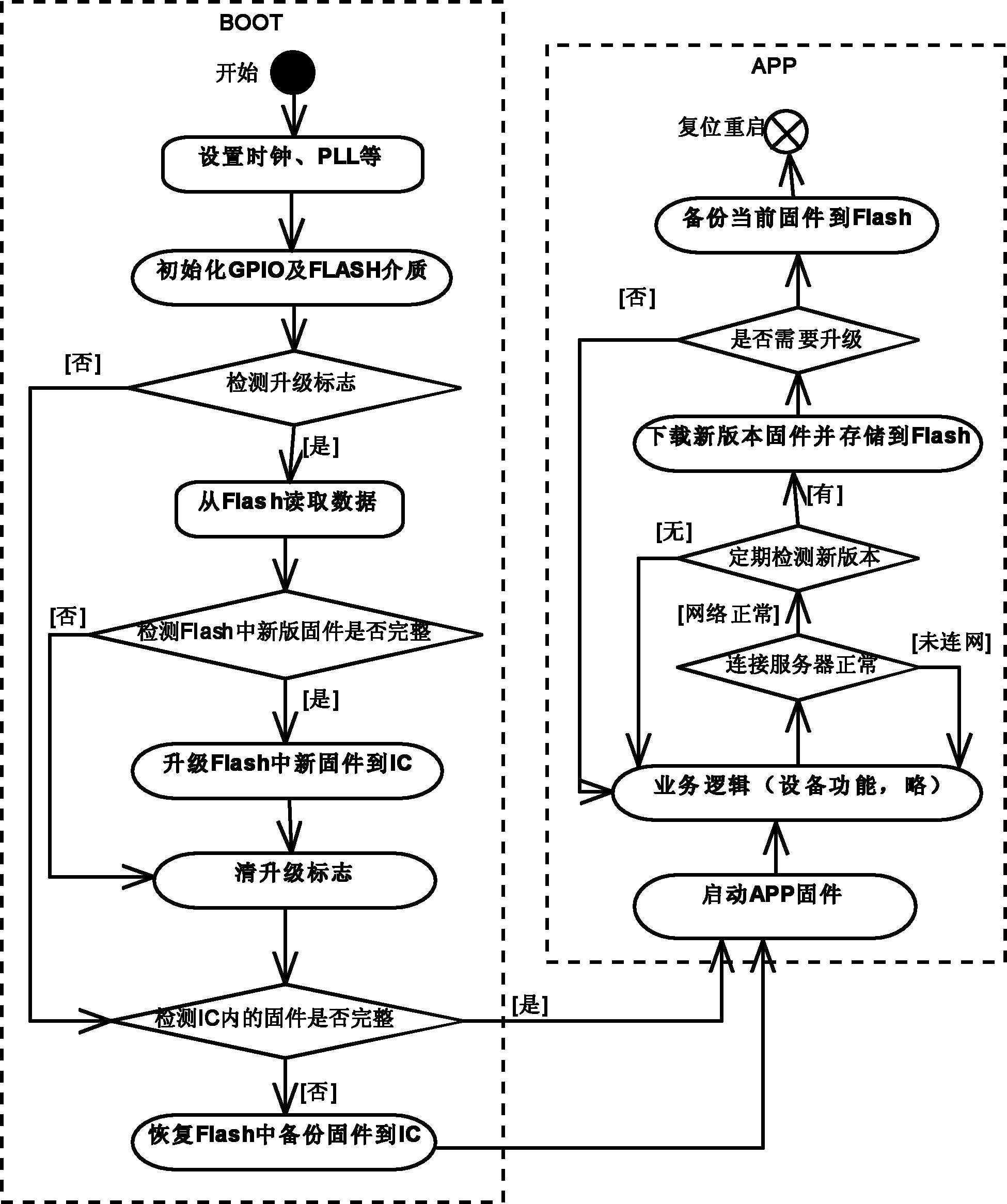

Method for remotely reliably upgrading XIP (execute in place) chip software

InactiveCN102662706ALow costSimplified function definitionProgram loading/initiatingGeneral Packet Radio ServiceFunction definition

The invention discloses a method for remotely reliably upgrading XIP (execute in place) chip software. The method aims to upgrade products designed on the basis of an XIP chip and provided with a GPRS (general packet radio service) or 3G (third generation) network or a WIFI (wireless fidelity) module. When upgrading firmware of the products, the firmware can be upgraded directly remotely through the network, and upgrading failure caused by power outage or other factors during upgrading can be avoided, and reliable upgrading can be guaranteed. Meanwhile, by the method, BOOT function definition is simplified, and downloading the firmware from a server in the BOOT area is omitted. The method can remotely reliably upgrade the XIP chip, and cost for field upgrading by operators can be evidently reduced, and the problem that the firmware cannot be reset caused by power outage during upgrading is avoided.

Owner:XIAN UNISTRONG NAVIGATION TECH CO LTD

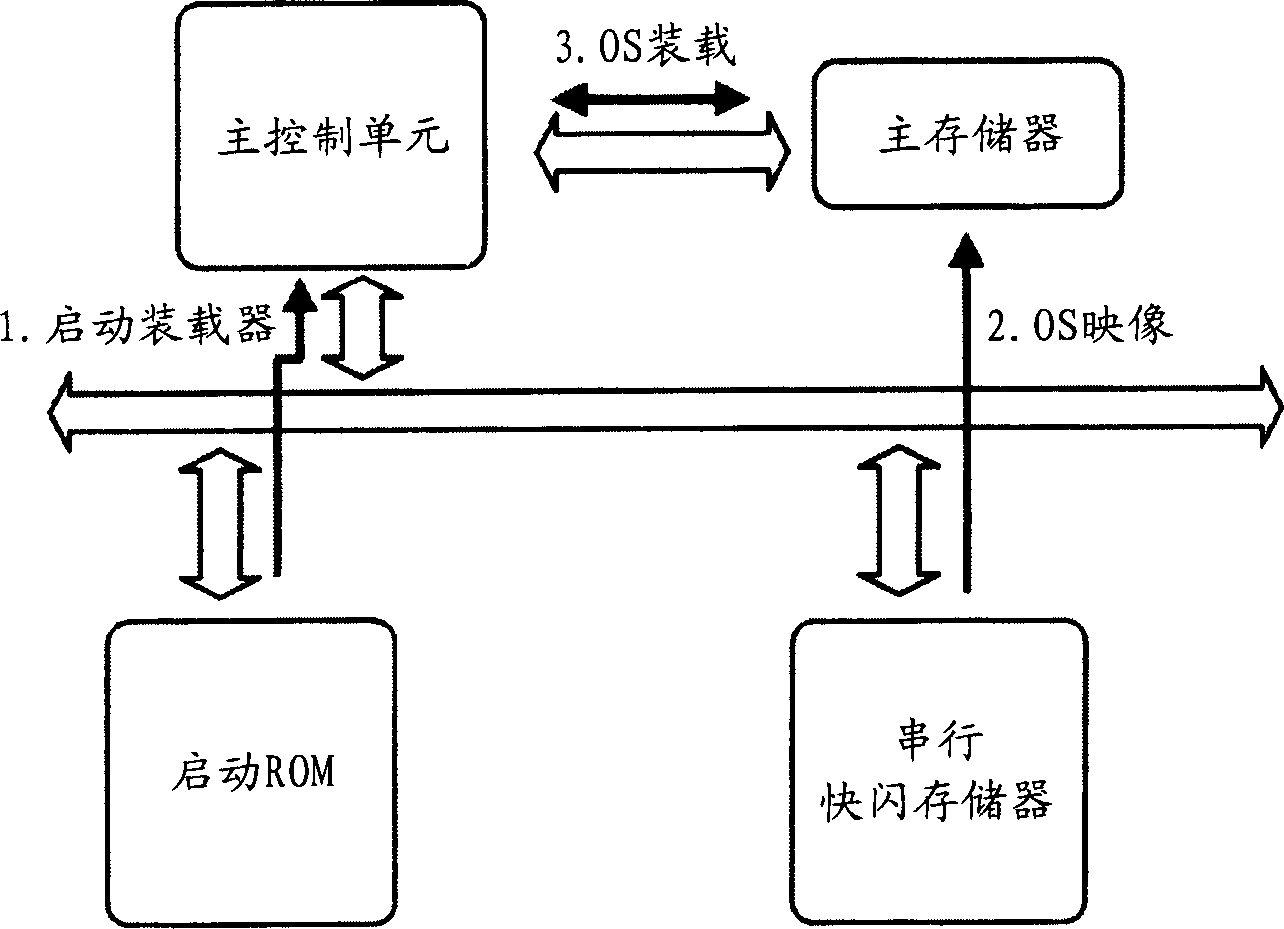

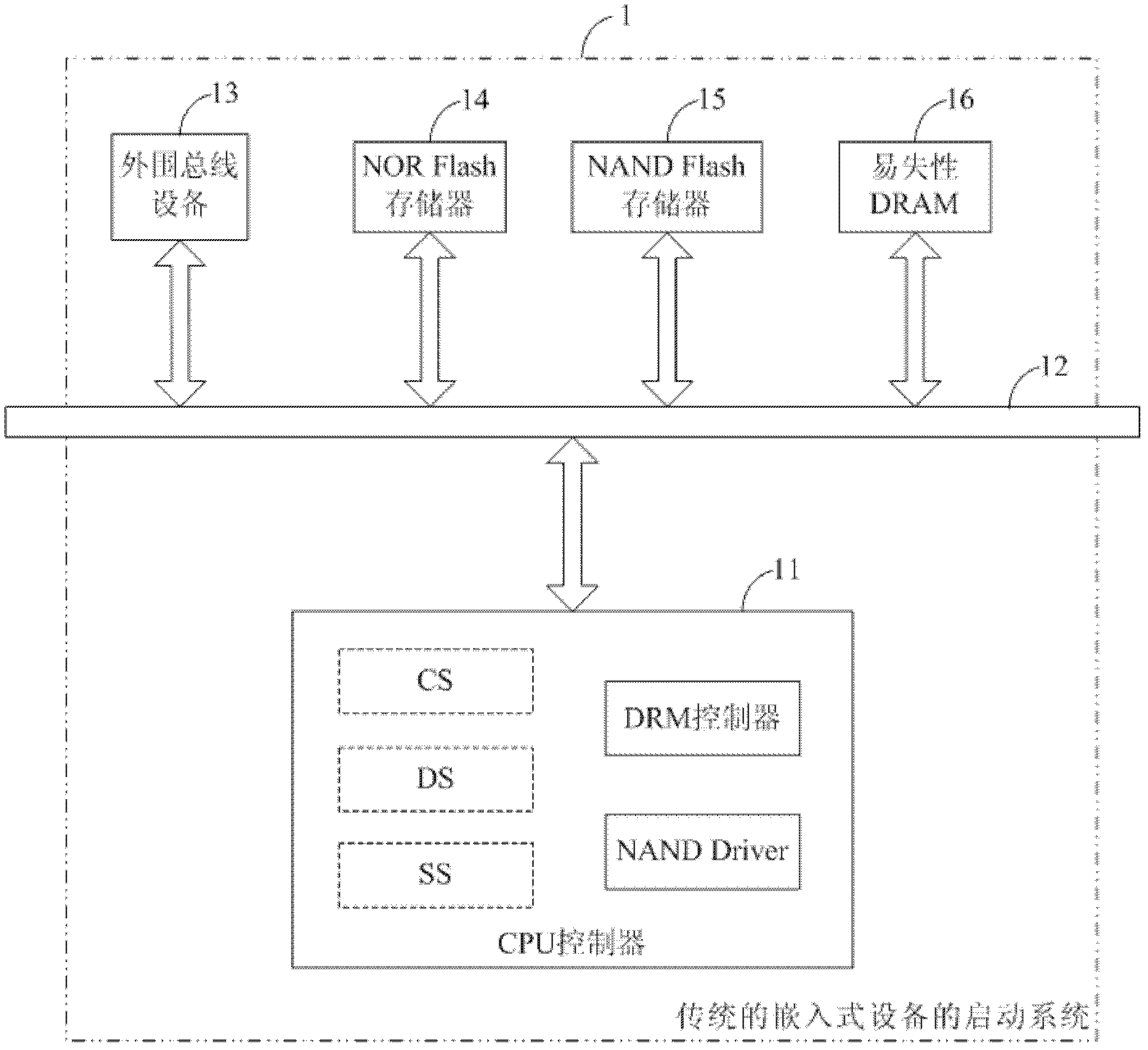

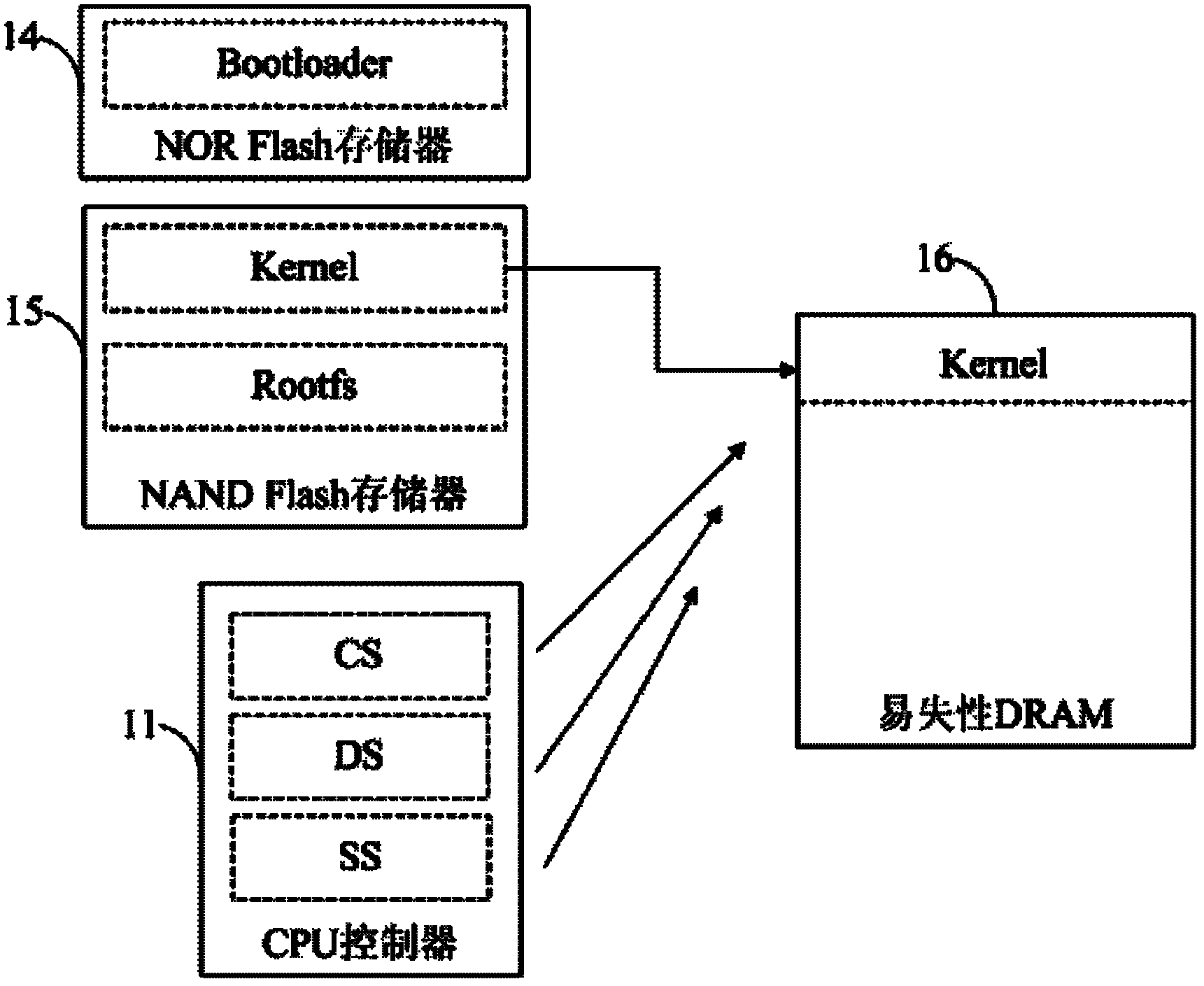

System capable of realizing bootload, bootload control device and method

ActiveCN102135891AImprove reliabilityImplement backup startupProgram loading/initiatingRedundant operation error correctionRandom access memoryBooting

The invention discloses a system capable of realizing bootload, a bootload control device and a bootload control method. A bootloader is stored in a first non-volatile memory device which does not support execute in place (XIP) and has an automatic reading characteristic; a first part of codes capable of being automatic read of the bootloader are backed up in a second non-volatile memory device, and a second residual part of codes of the bootloader are backed up in the first non-volatile memory device; a logic chip reads the backup of the first part of codes to a built-in random access memory(RAM), and switches connection between the boot chip selection output of a central processing unit (CPU) and the chip selection input of the first non-volatile memory device and the connection between the boot chip selection output of the CPU and the chip selection input of the built-in RAM for the CPU to acquire the first part of codes from the first non-volatile memory device or acquire the backup of the first part of codes from the built-in RAM; and the logic chip also can provide the second part of codes or the position information of any backup of the second part of codes in the first non-volatile memory device for the CPU, thereby realizing the backup boot of the second part of codes.

Owner:NEW H3C TECH CO LTD

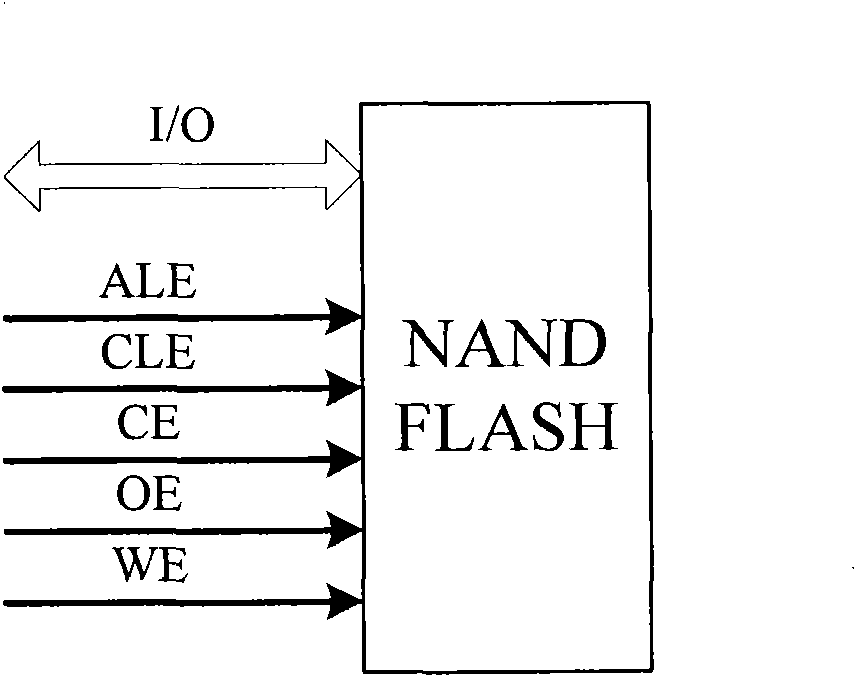

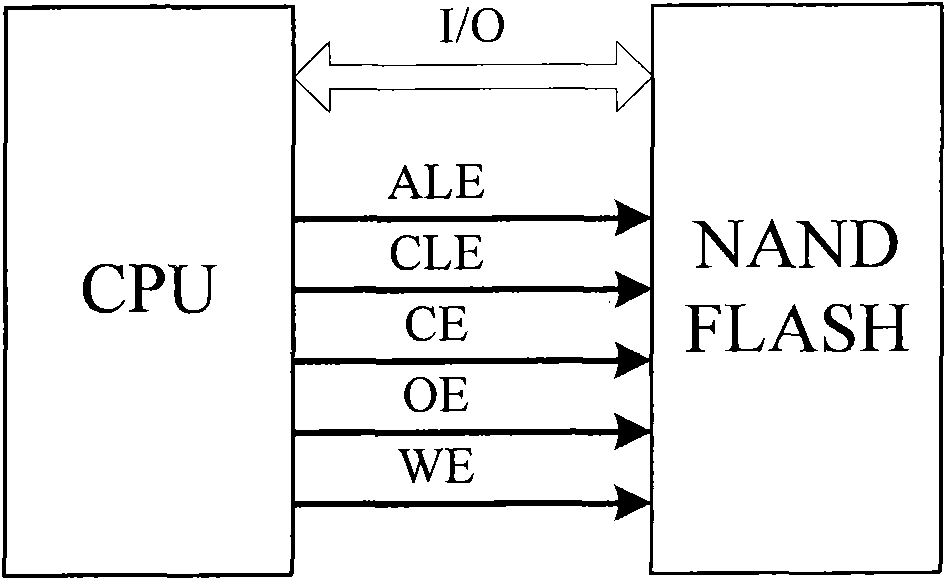

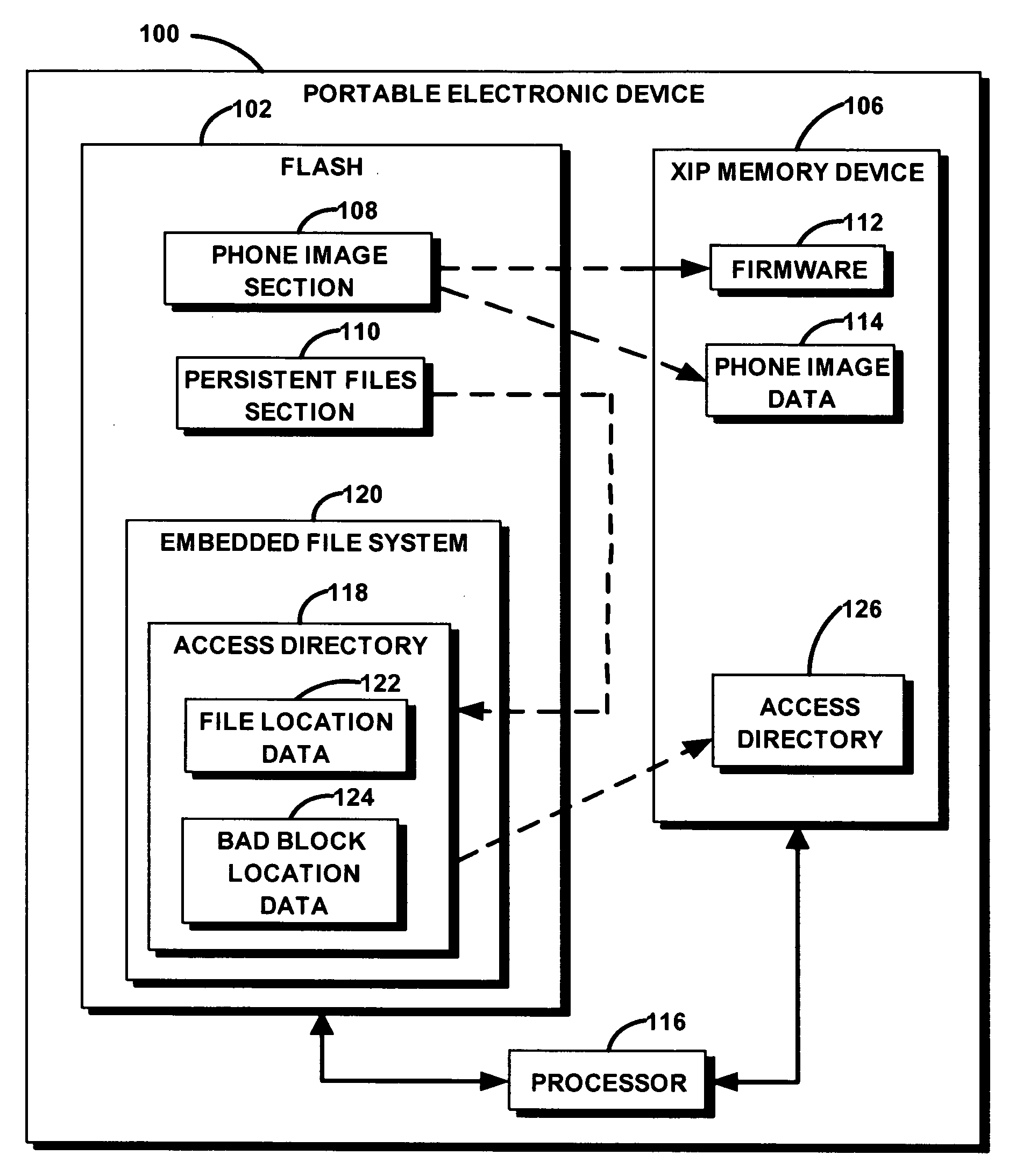

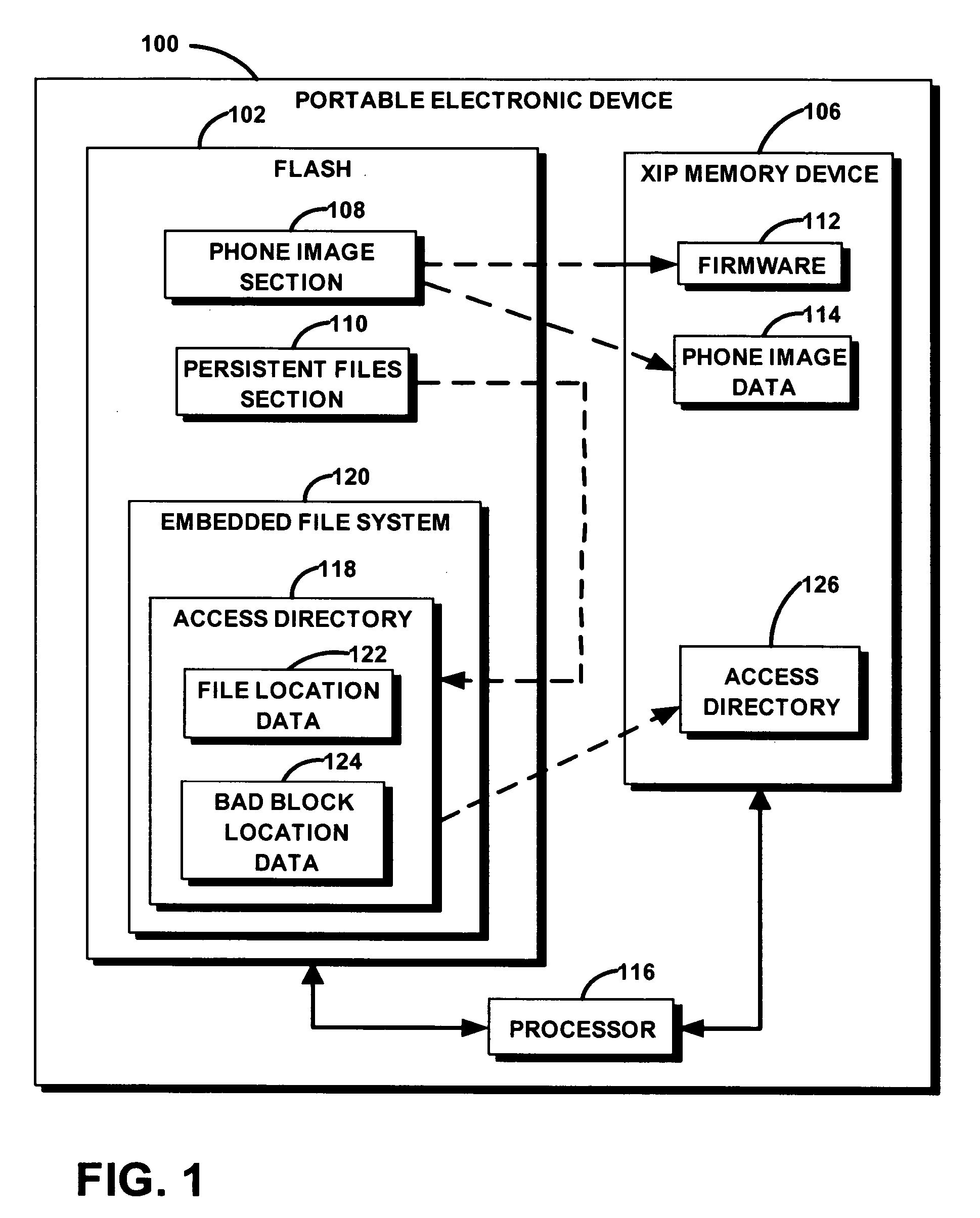

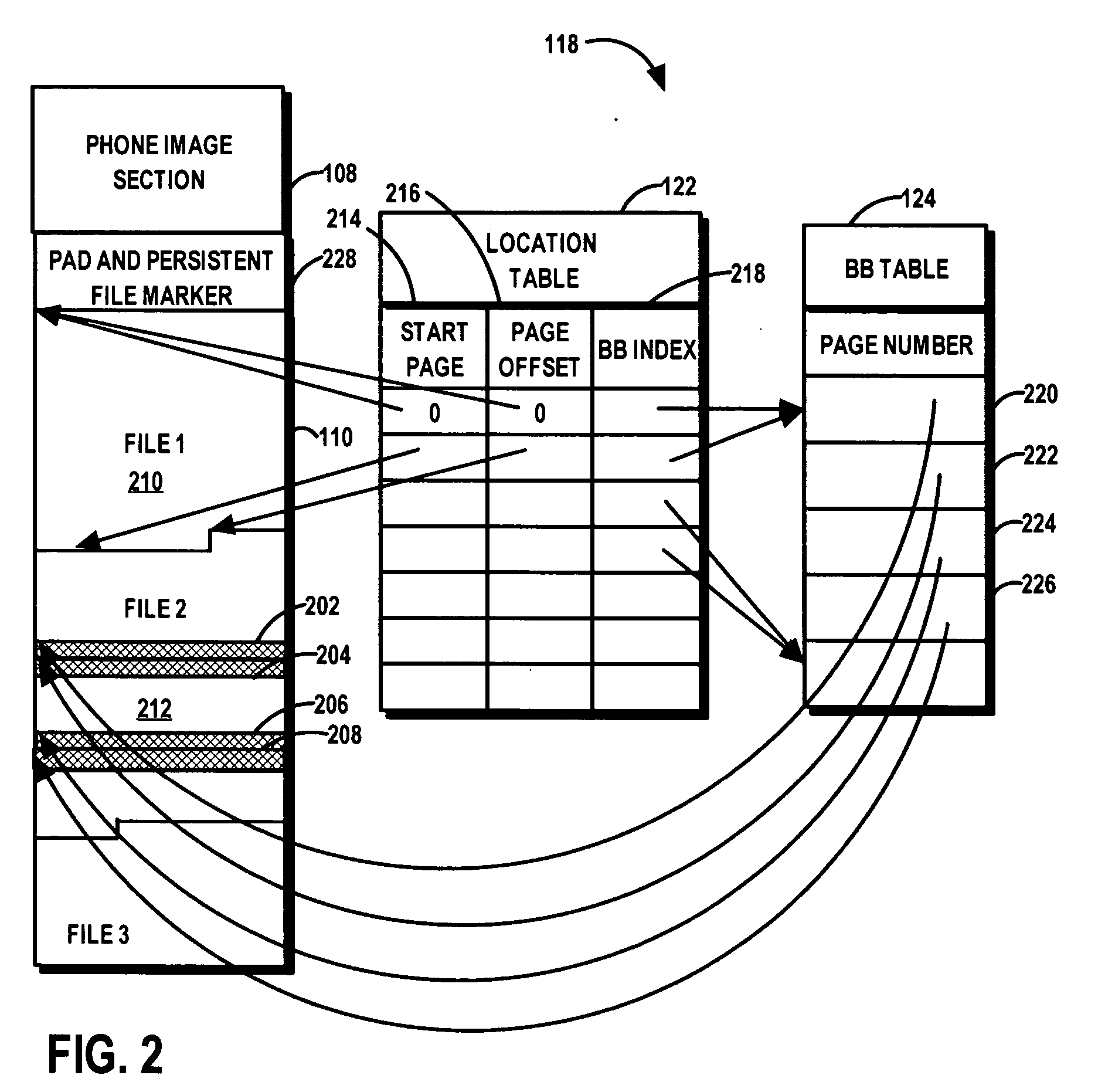

Apparatus, system, and method for accessing persistent files in non-execute-in-place flash memory

InactiveUS20070014136A1Reduce manufacturing costRequired size is minimizedElectronic circuit testingDigital storageApplication softwareElectronic equipment

Persistent files stored in non-XIP flash memory are accessed during operation of an electronic device. During execution of application code on the device, the persistent files are accessed using an access directory such as a look-up table. The access directory provides information that allows an application or other software code running on the processor of the device to locate and access a persistent file within a non-XIP flash memory device where the non-XIP flash memory device may include bad blocks. During creation of the access directory, locations of the bad blocks in the device are identified and recorded. Files are accessed from the non-XIP flash memory device by reading from file start locations identified in the access directory while accounting for bad blocks identified in the bad block data of the access directory.

Owner:KYOCERA CORP

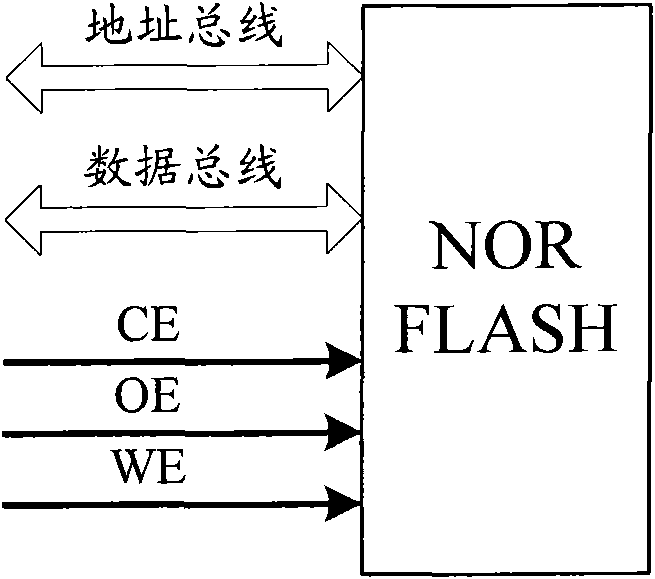

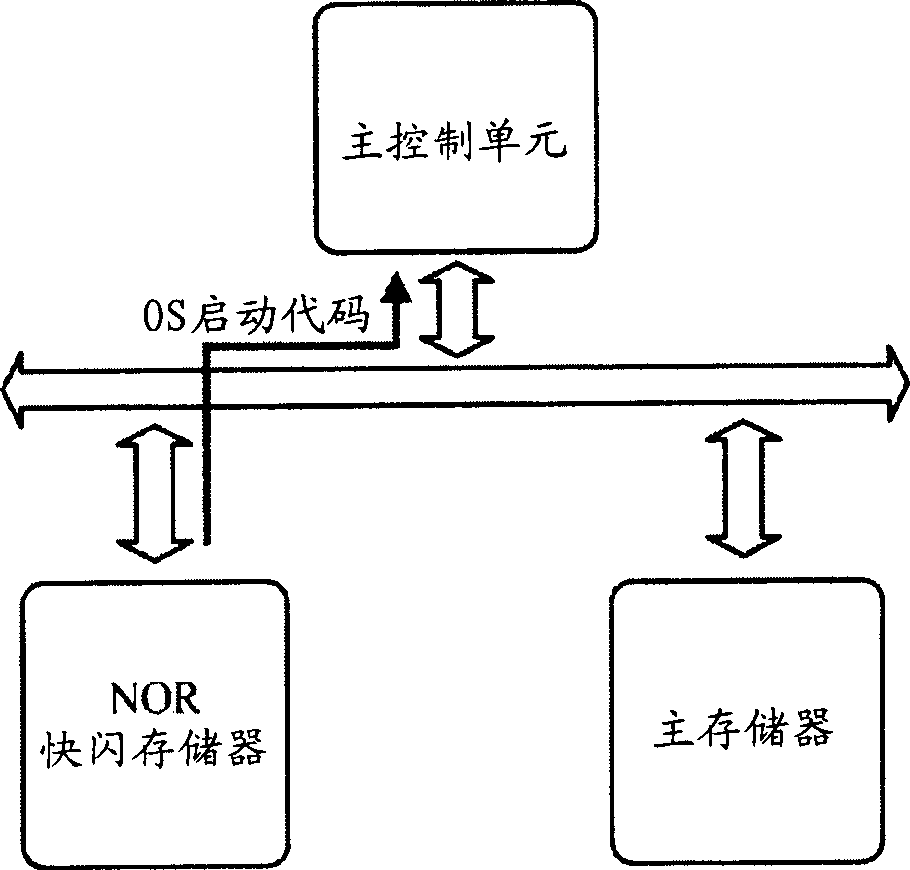

Device and method for controllintg proper execution in serial flash memory and corresponding chip

InactiveCN1517884AMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressControl unit

The invention is for controlling execute-in-place in a serial flash memory and a flash memory chip using the same, enabling a serial flash controller with predetermined amount of storage to access the serial flash, to read an entire page to which required data belong, and to transmit the desired data to a main control unit or to execute the data. The apparatus includes a cache module for accessing a designated memory address of the serial flash in response to a command received from a main control unit, and reading or writing data required by the main control unit; a serial flash controller with a boot loader for allowing system booting to be performed by reading boot codes written on the serial flash, and storing the boot codes in a buffer and immediately transmitting the boot codes to the main control unit when the main control unit requires the boot codes.

Owner:SAMSUNG ELECTRONICS CO LTD

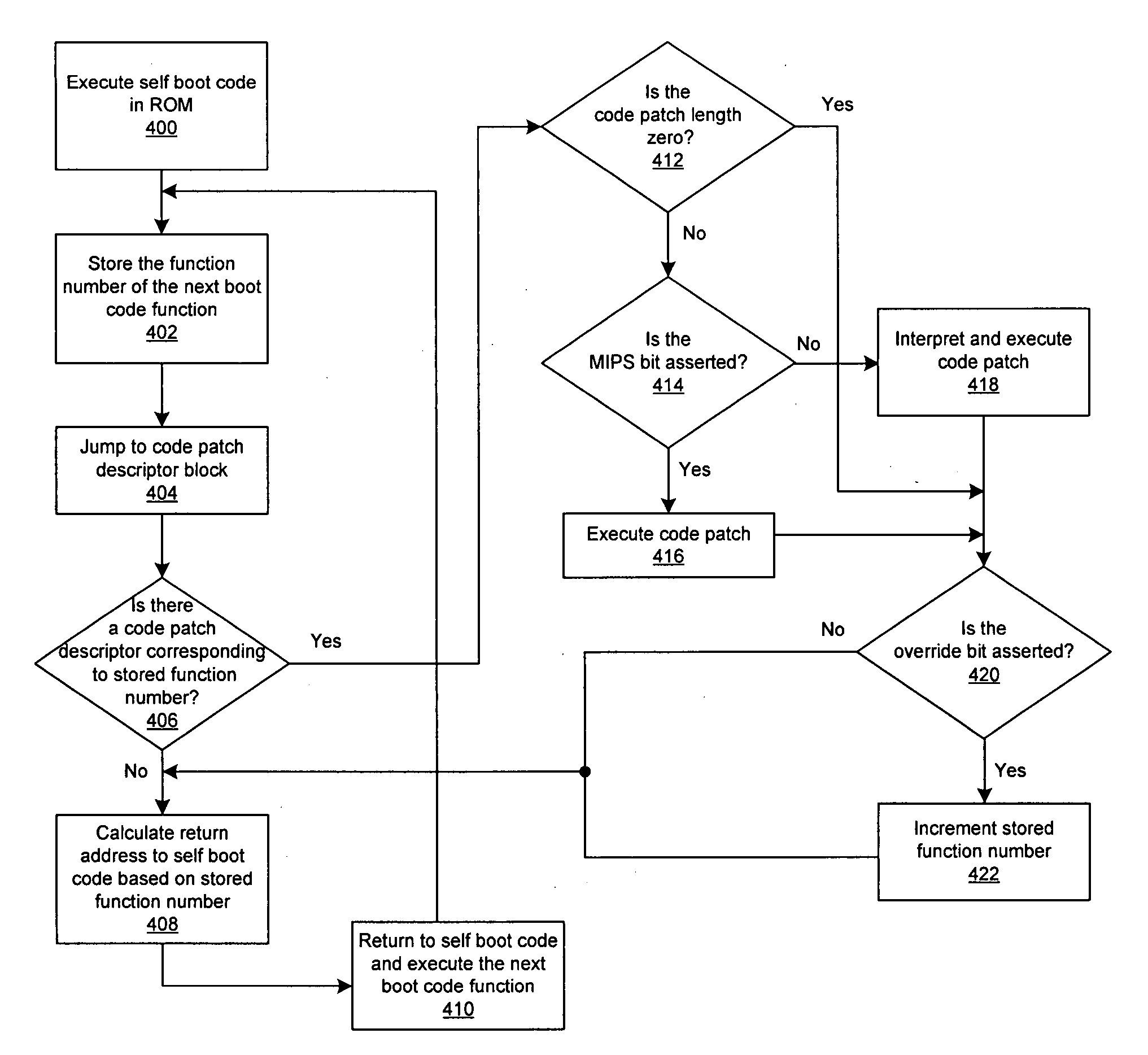

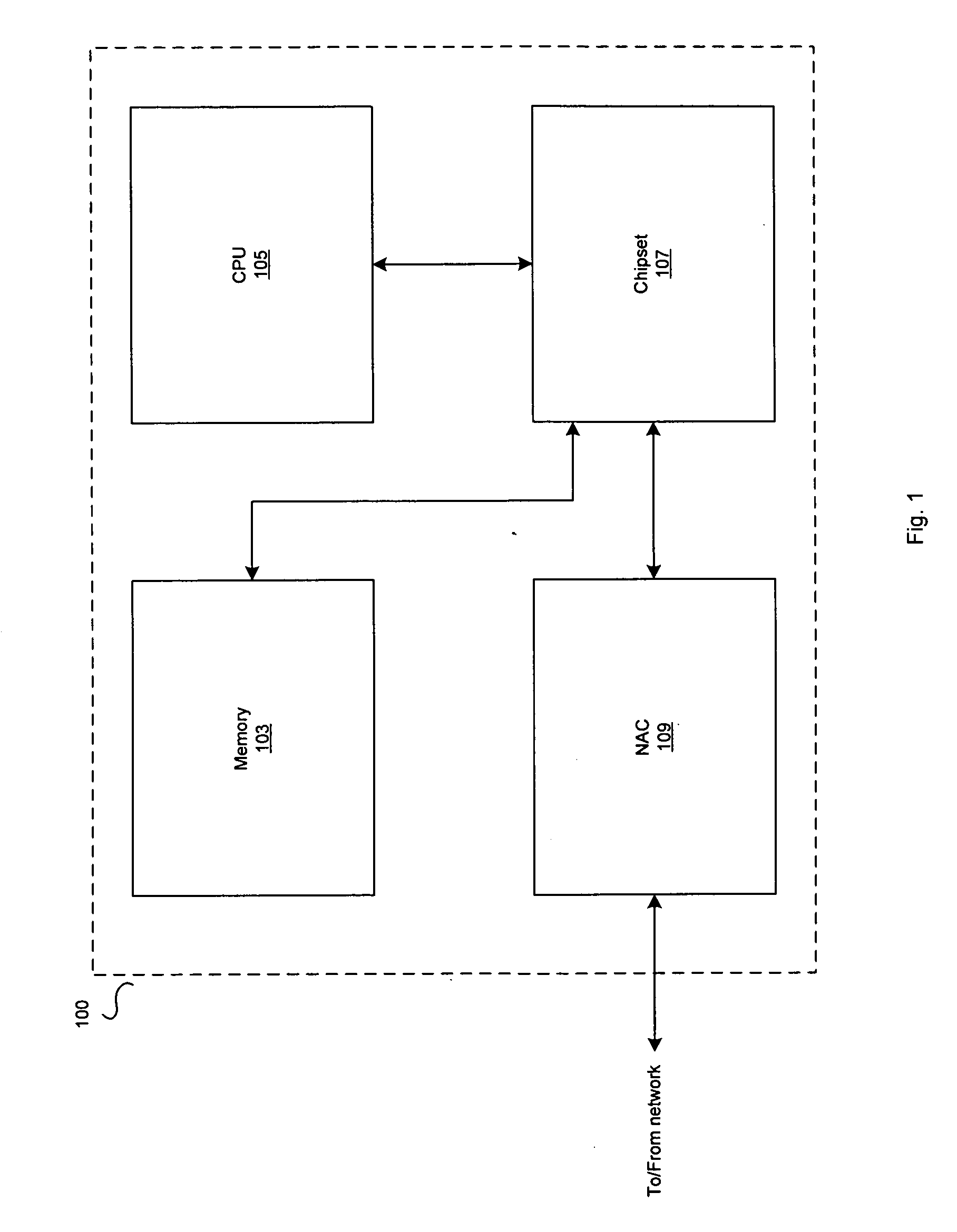

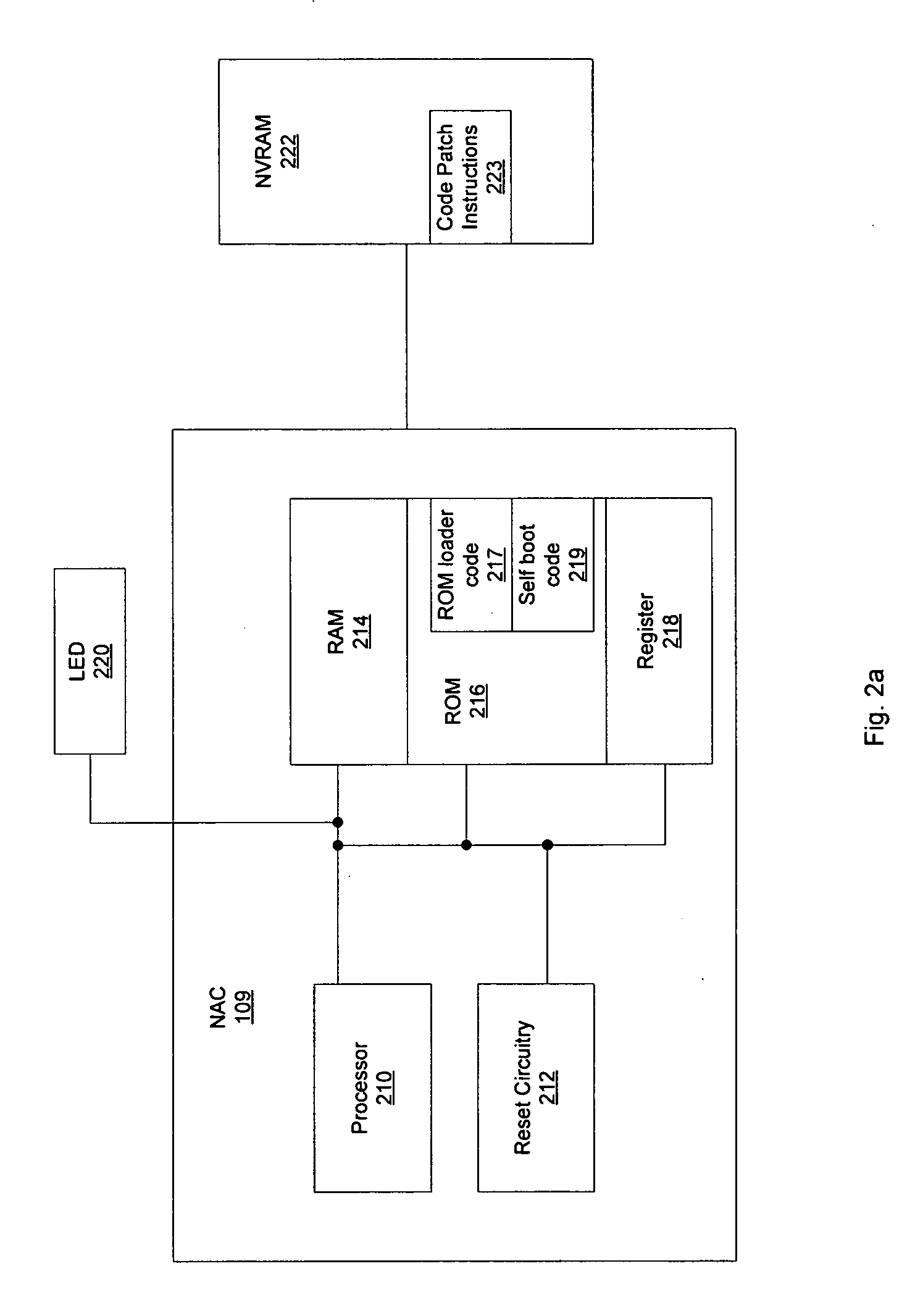

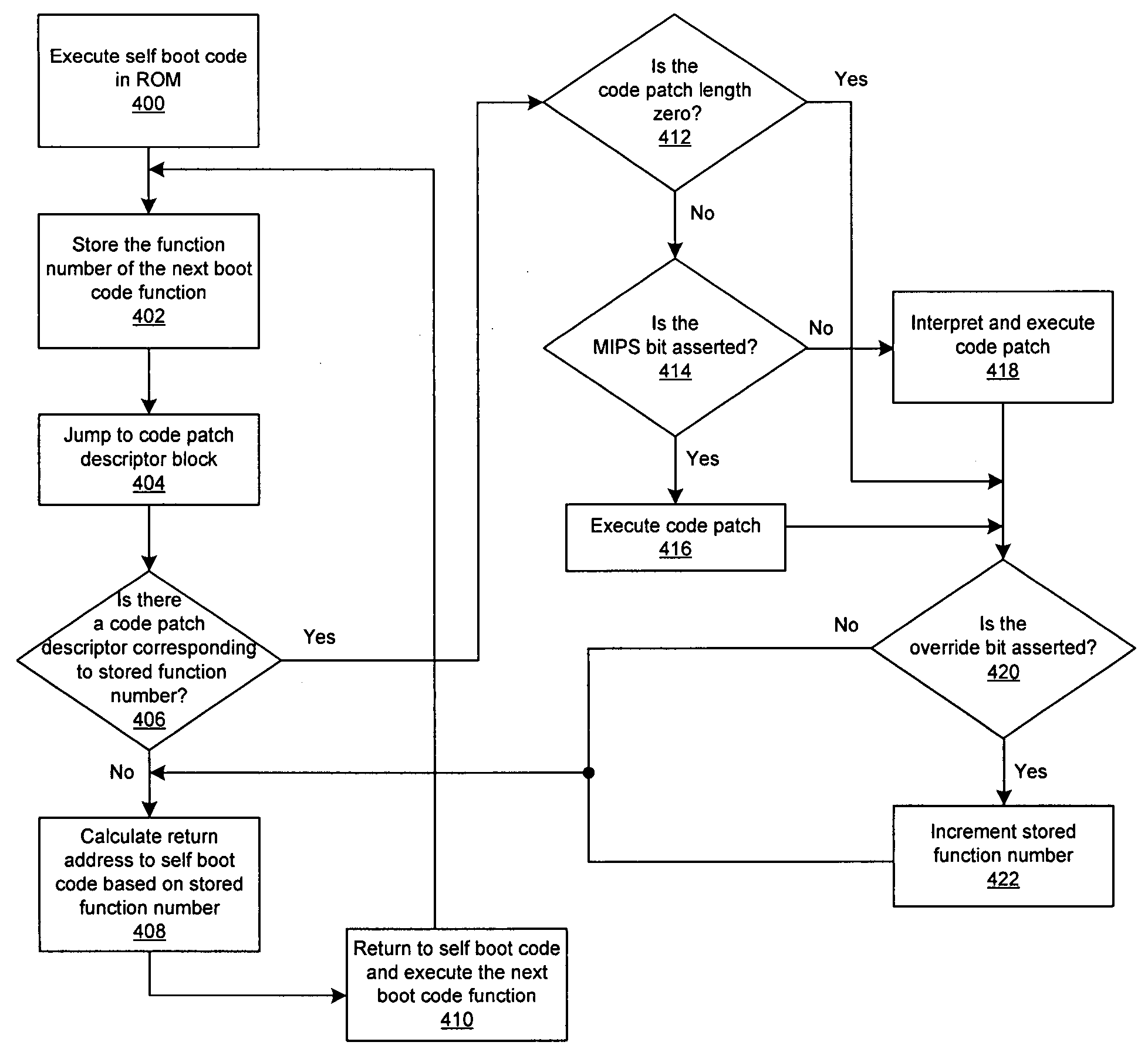

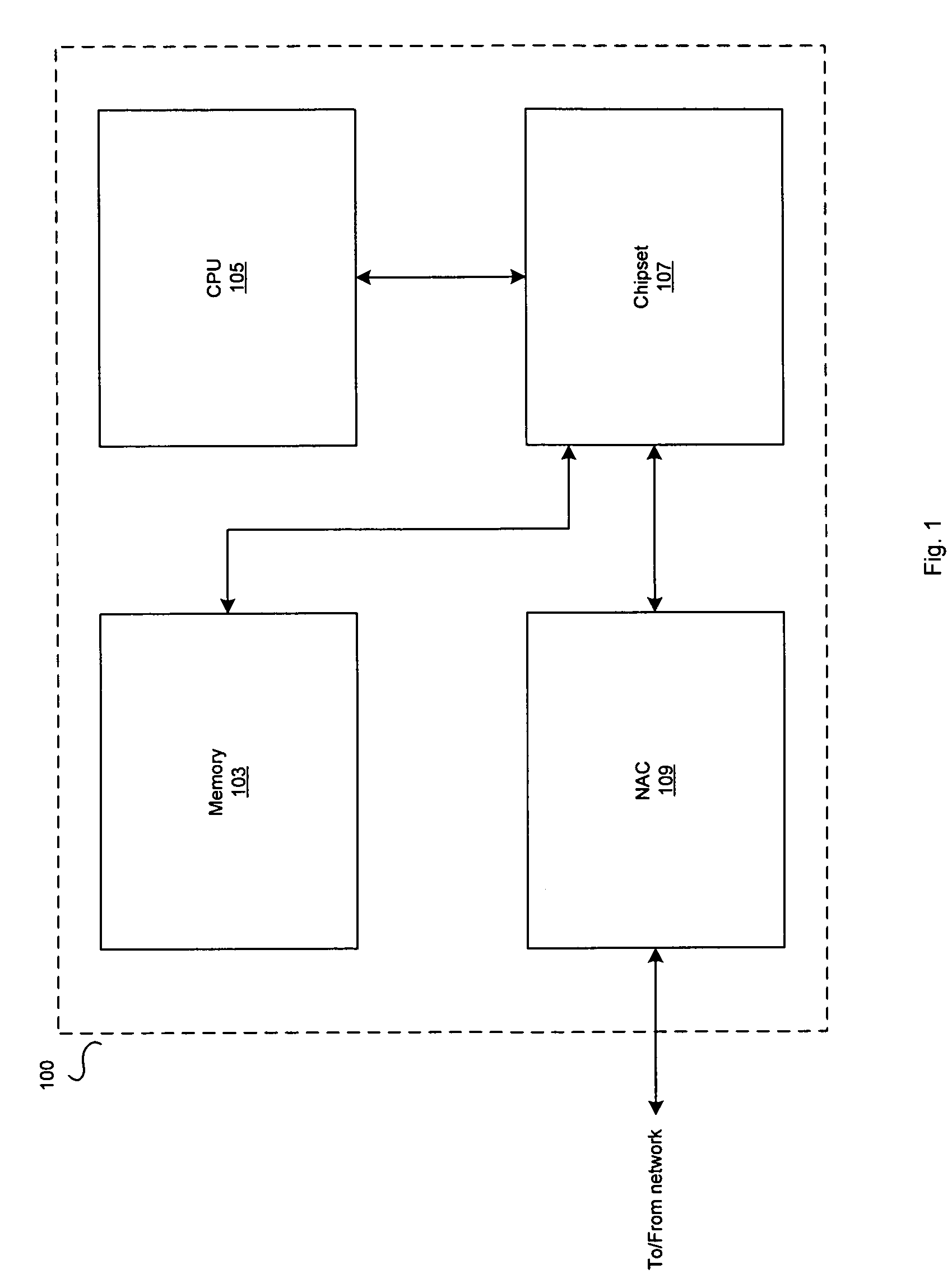

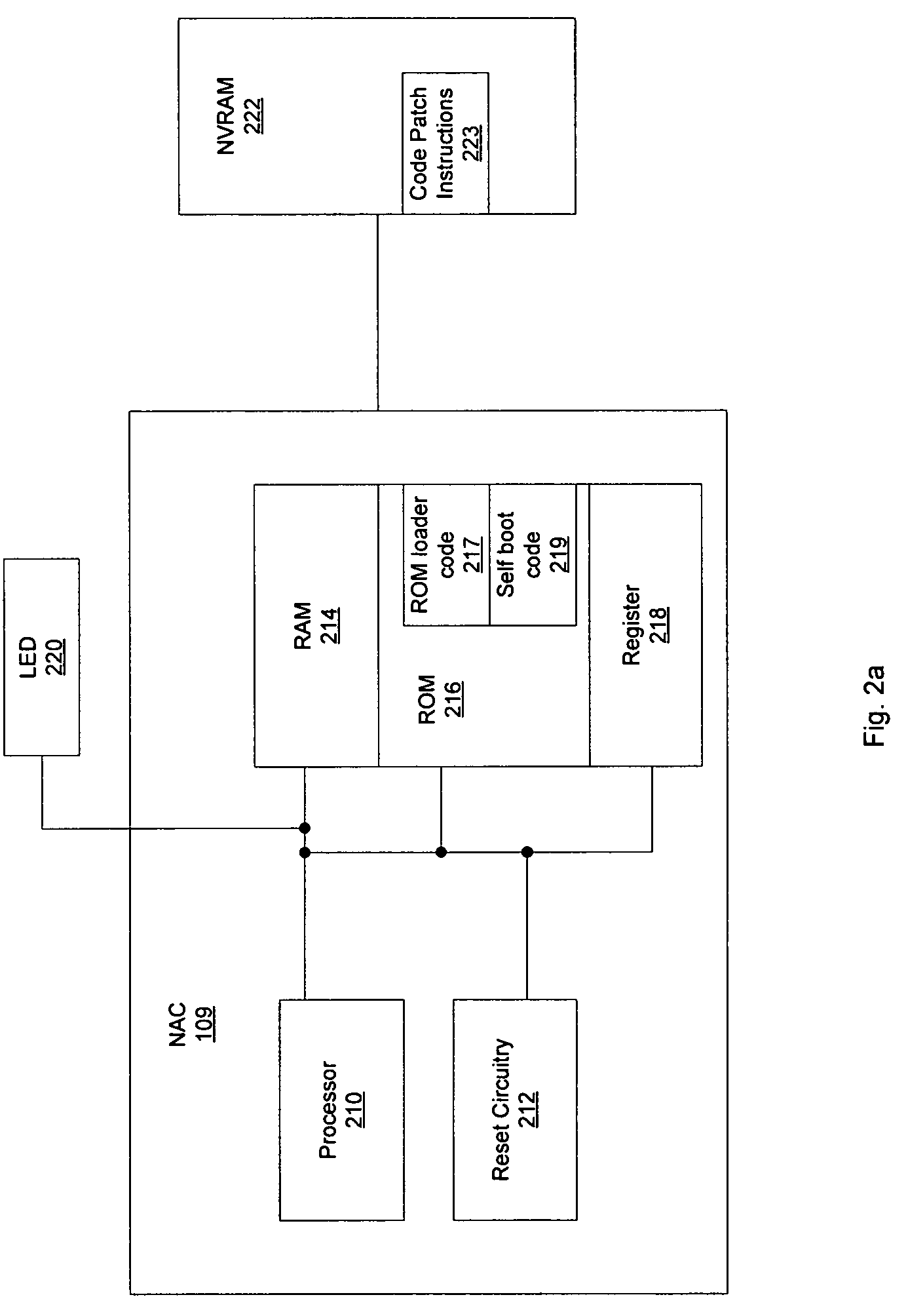

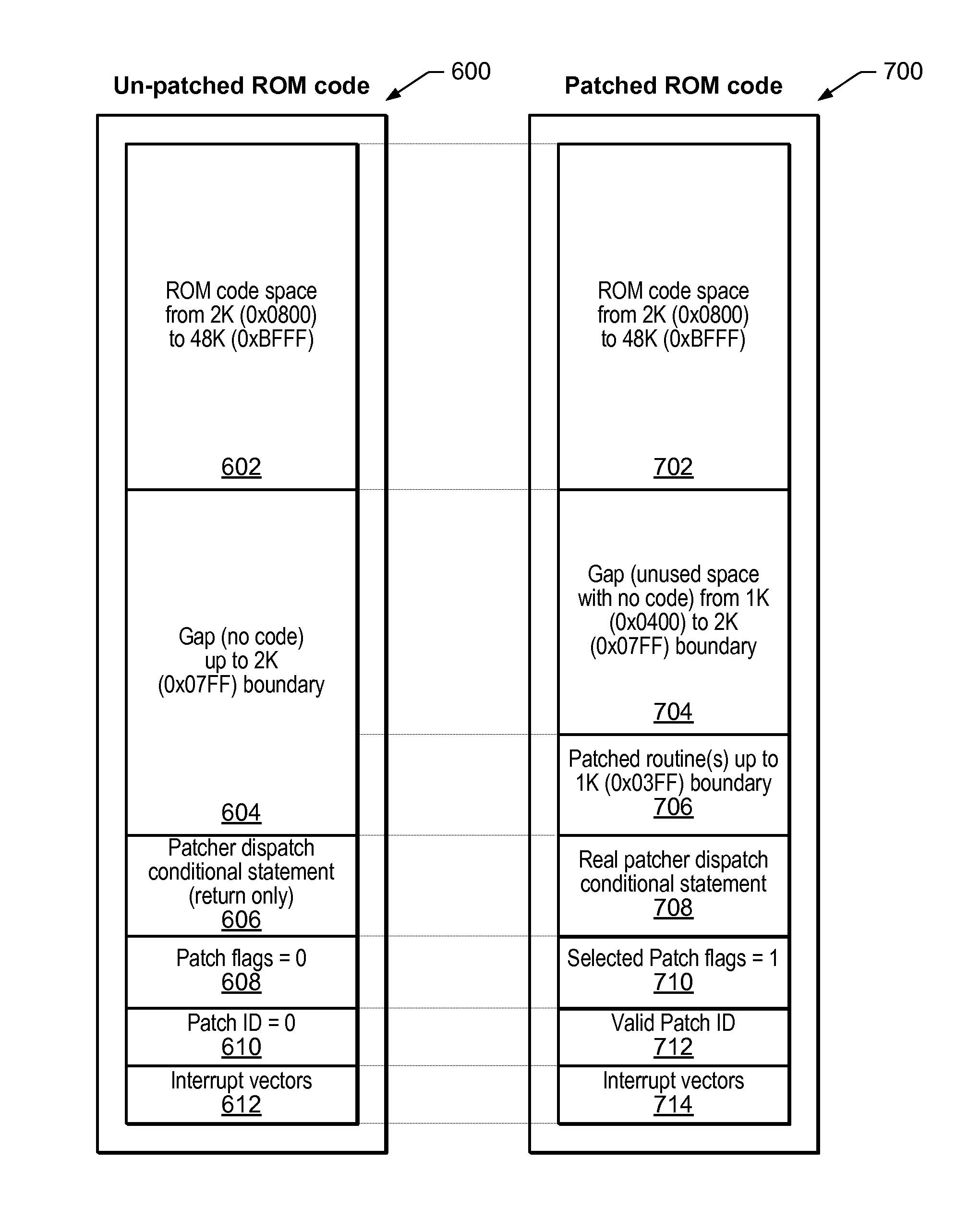

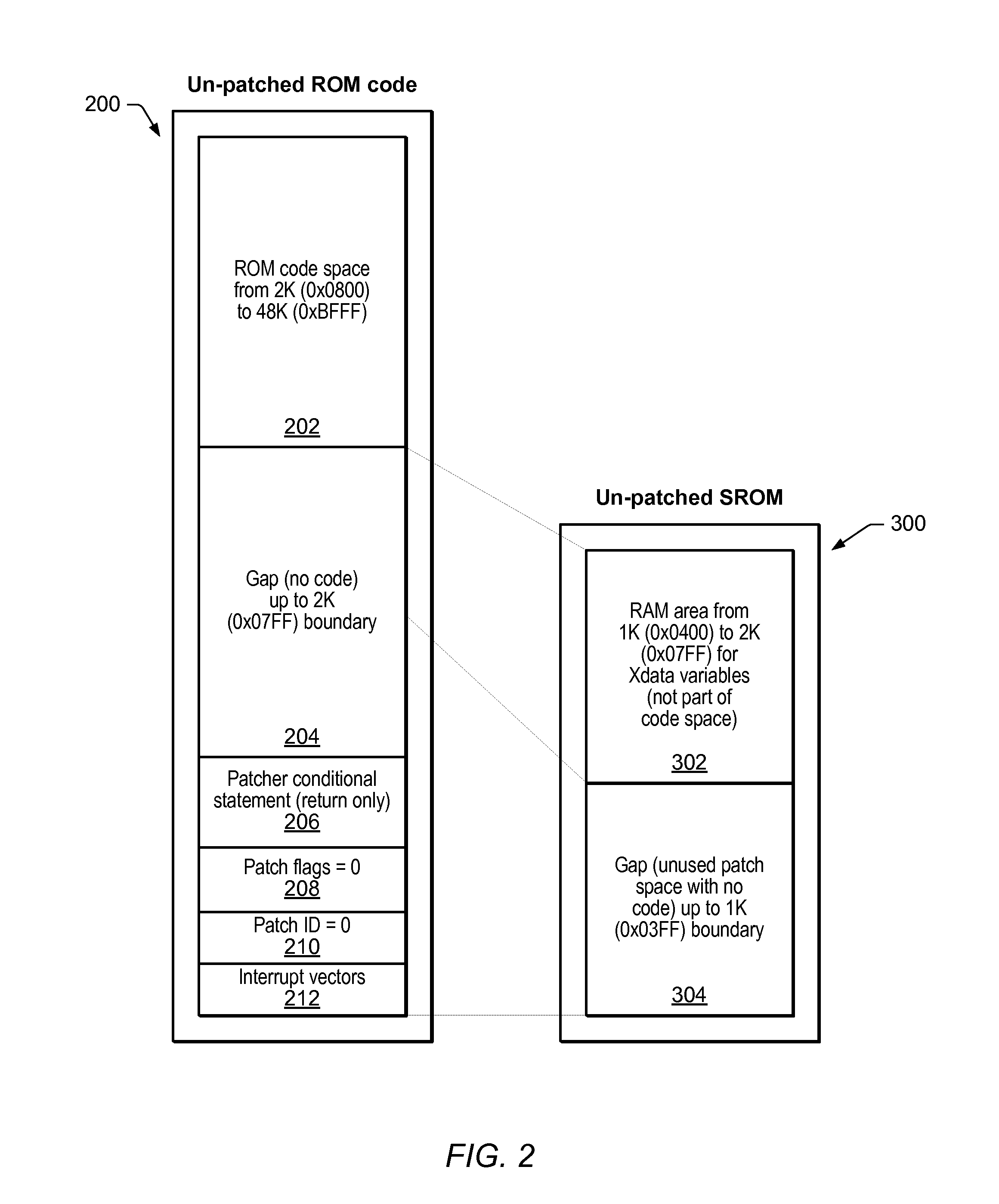

Method and system for modifying operation of ROM based boot code

Certain embodiments for modifying operation of ROM based boot code may include modifying a bootup sequence for boot code resident in a ROM within a network adapter chip (NAC). The bootup sequence may be modified during booting of the NAC using code patches in memory external to the NAC. The boot code may comprise ROM loader code and / or self-boot code in the ROM within the NAC. Execution of the self-boot code may comprise execution of code patches. The code patches may comprise initialization code patches and service code patches. The code patches may be executed in place of functions in the self-boot code or in addition to the functions in the self-boot code. Additionally, the code patches may be configured such that a function in the self-boot code may be effectively deleted where no corresponding code patch may be executed in place of the function.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

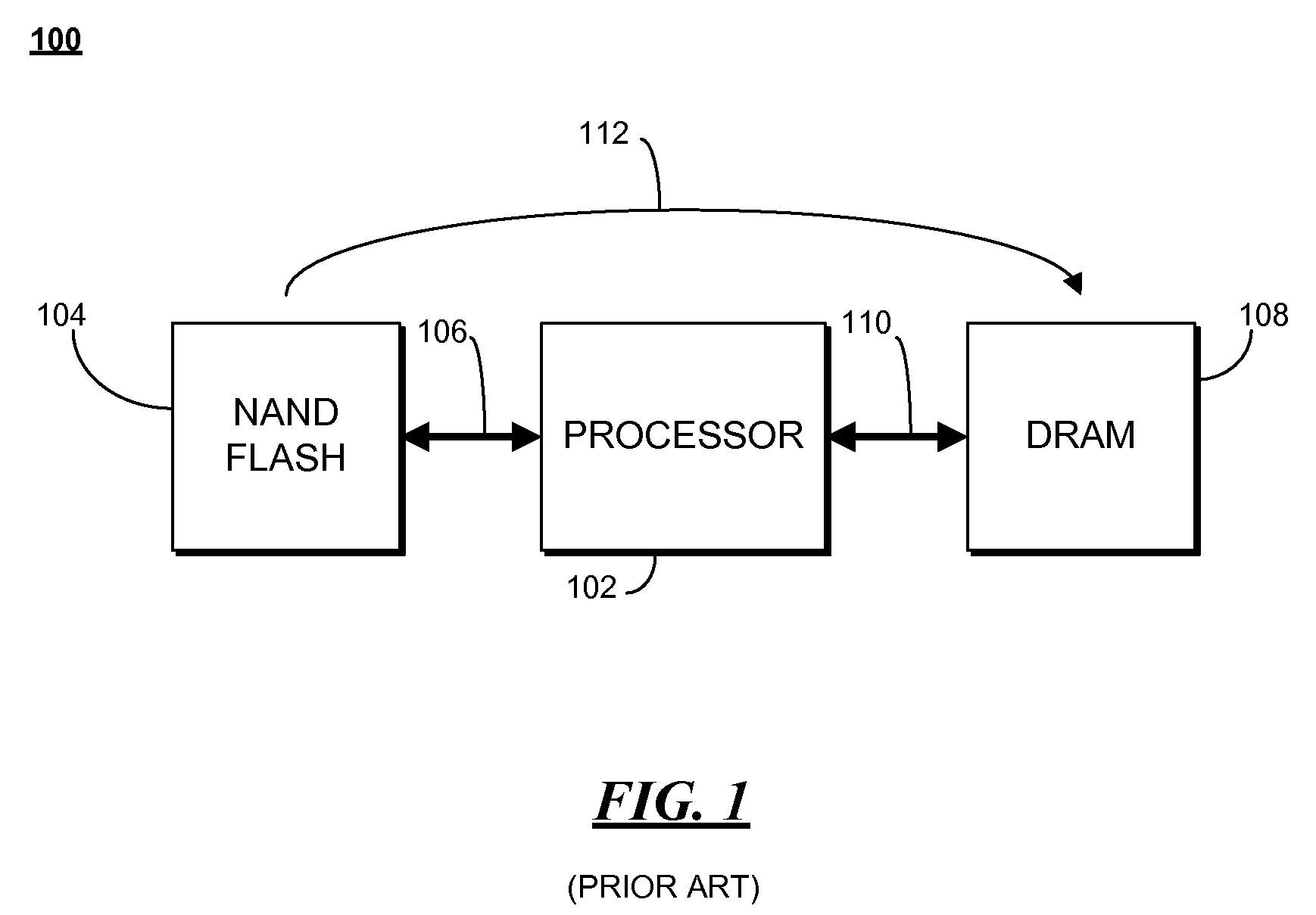

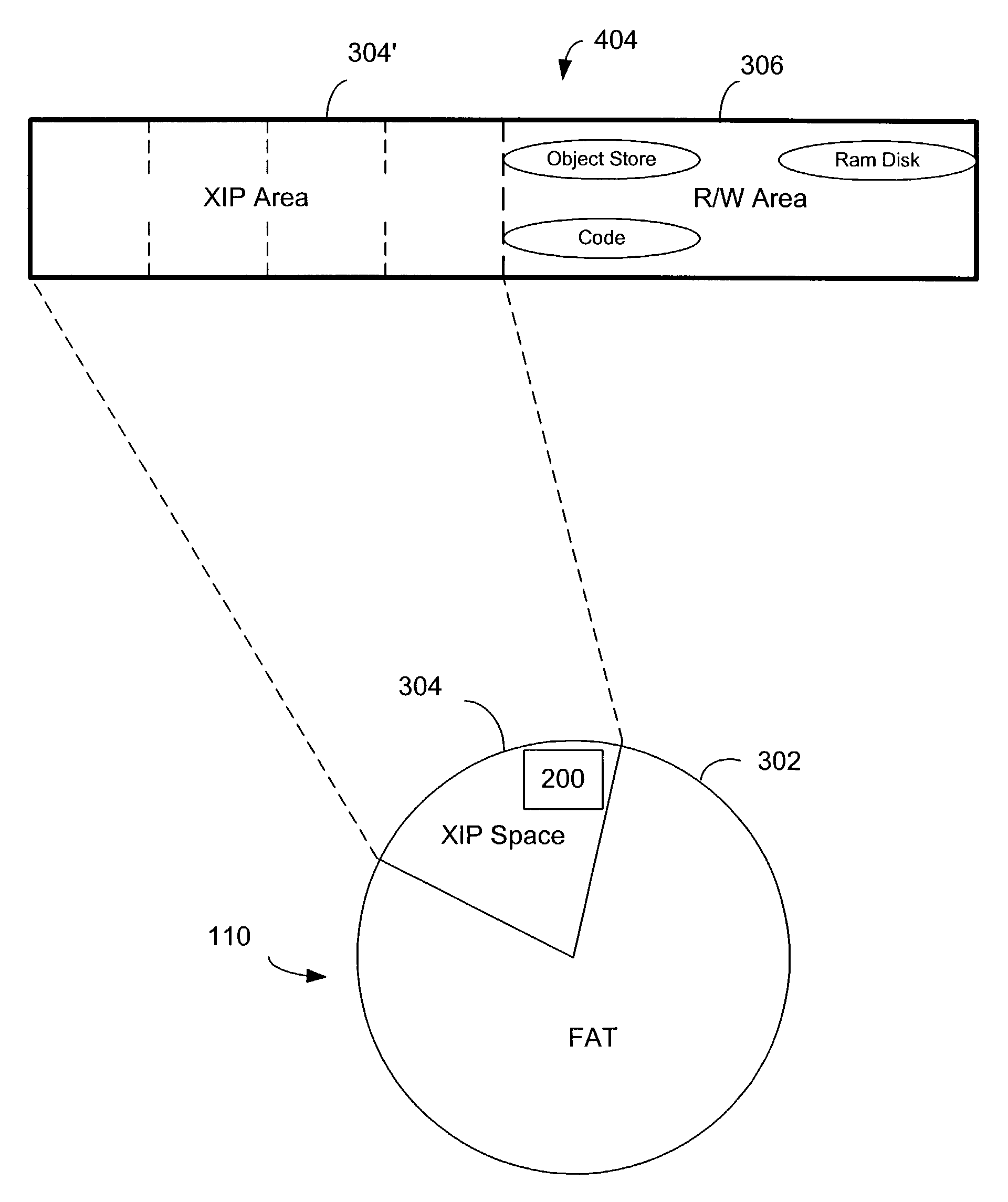

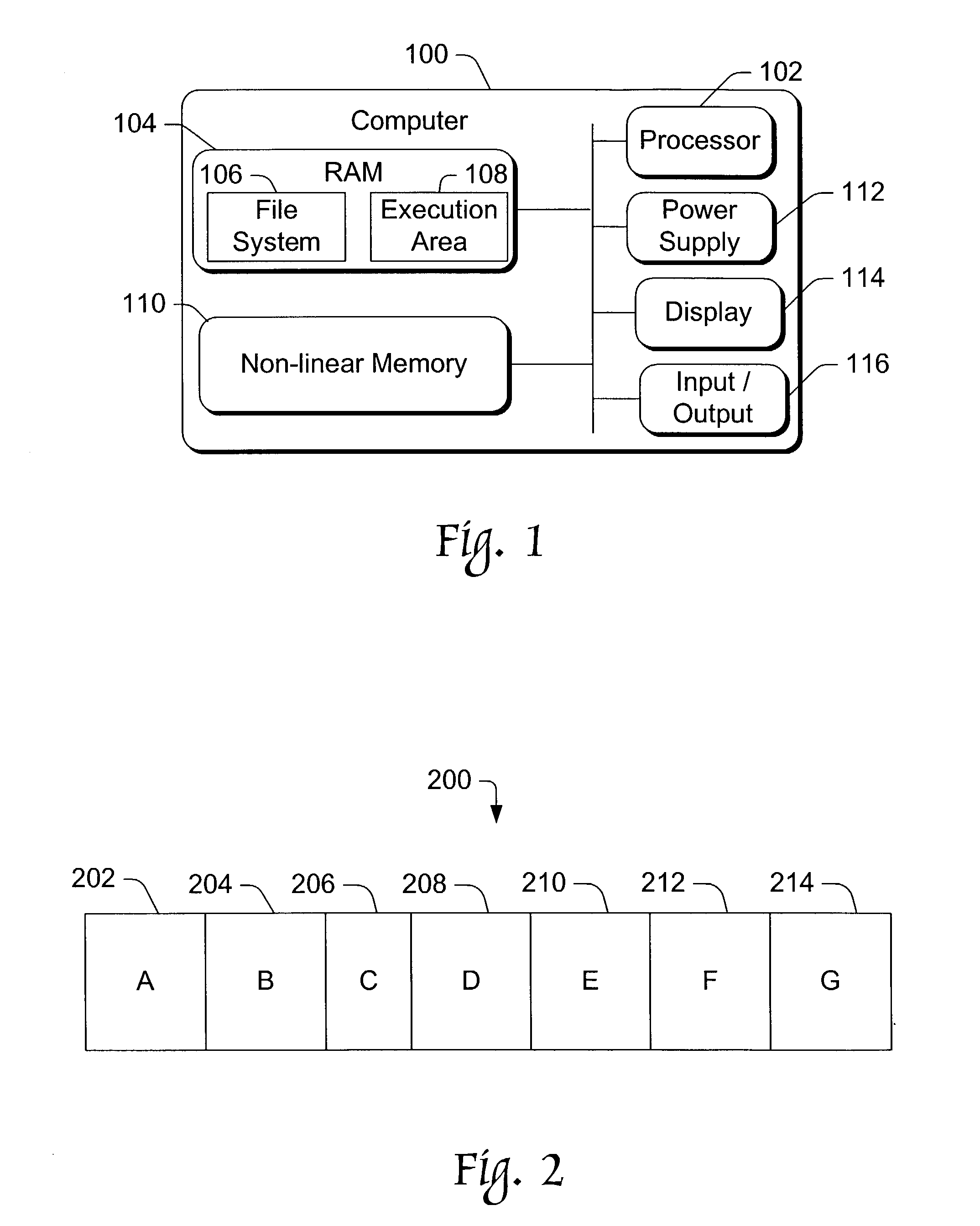

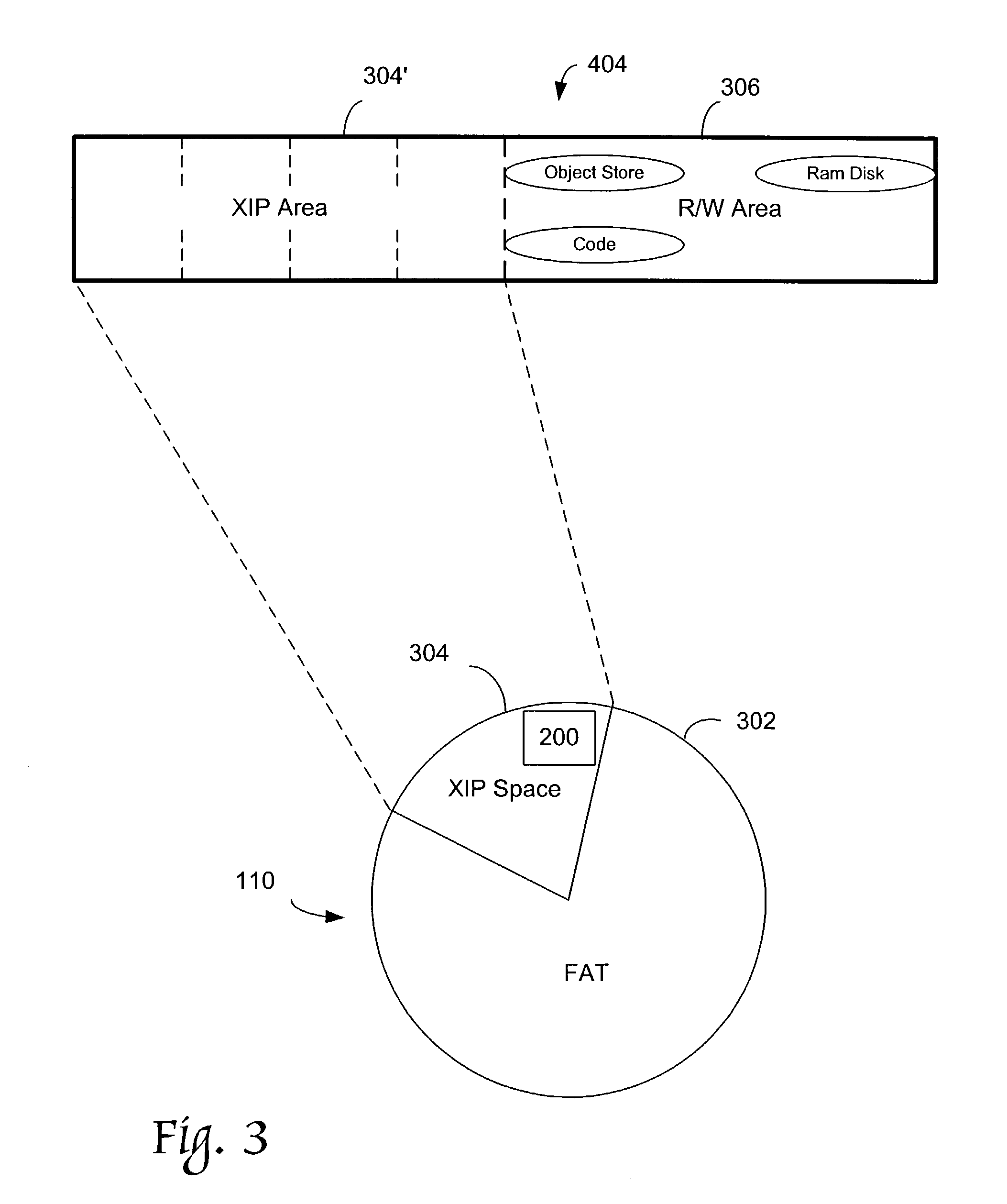

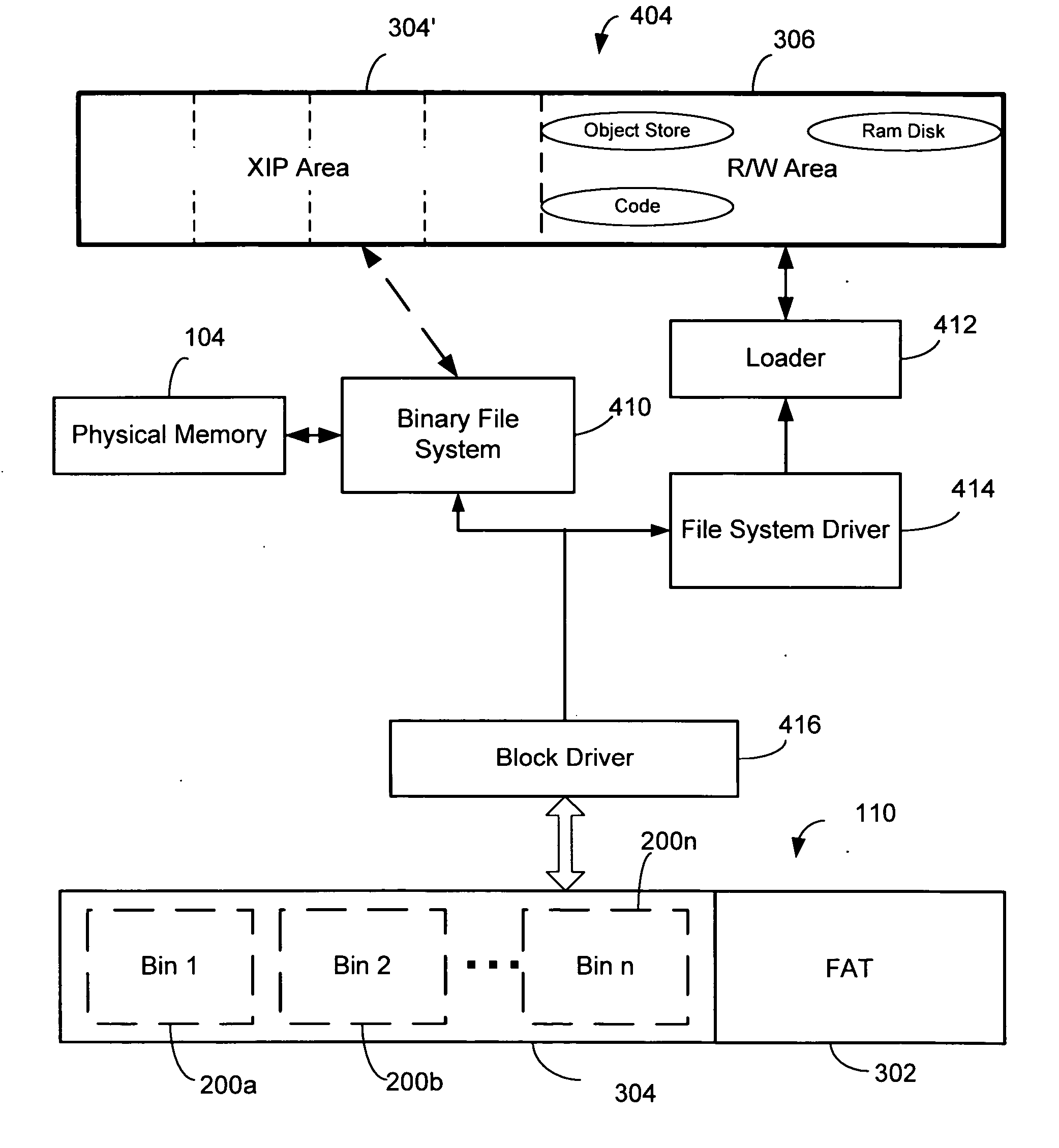

Executing binary images from non-linear storage systems

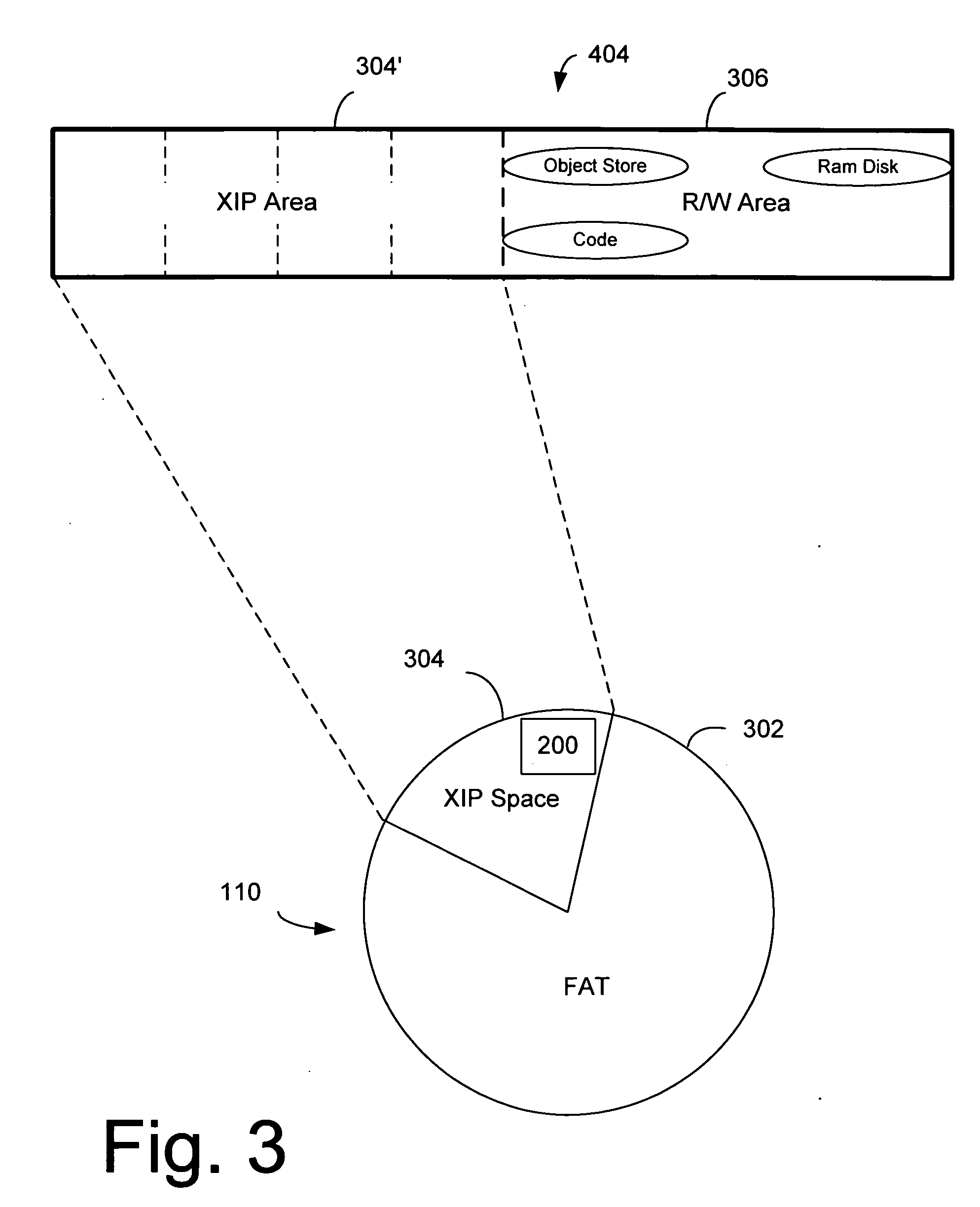

InactiveUS6988163B2Less and less working RAMRead-only memoriesDigital storageOperational systemFile system

A system that determines where a particular XIP component is stored on a non-linearly addressable storage medium and loads the component into RAM for execution, providing the ability to demand page specific components at will from storage media, frees up working RAM on memory constrained devices. A Binary File System uses a generic block driver component that loads the XIP code from a block based storage medium. Features of the file system include the ability to load pre-“fixed up” components from a block based device. The invention thus allows an operating system to load code that was previously Executed In Place (XIP) from a block-oriented device.

Owner:MICROSOFT TECH LICENSING LLC

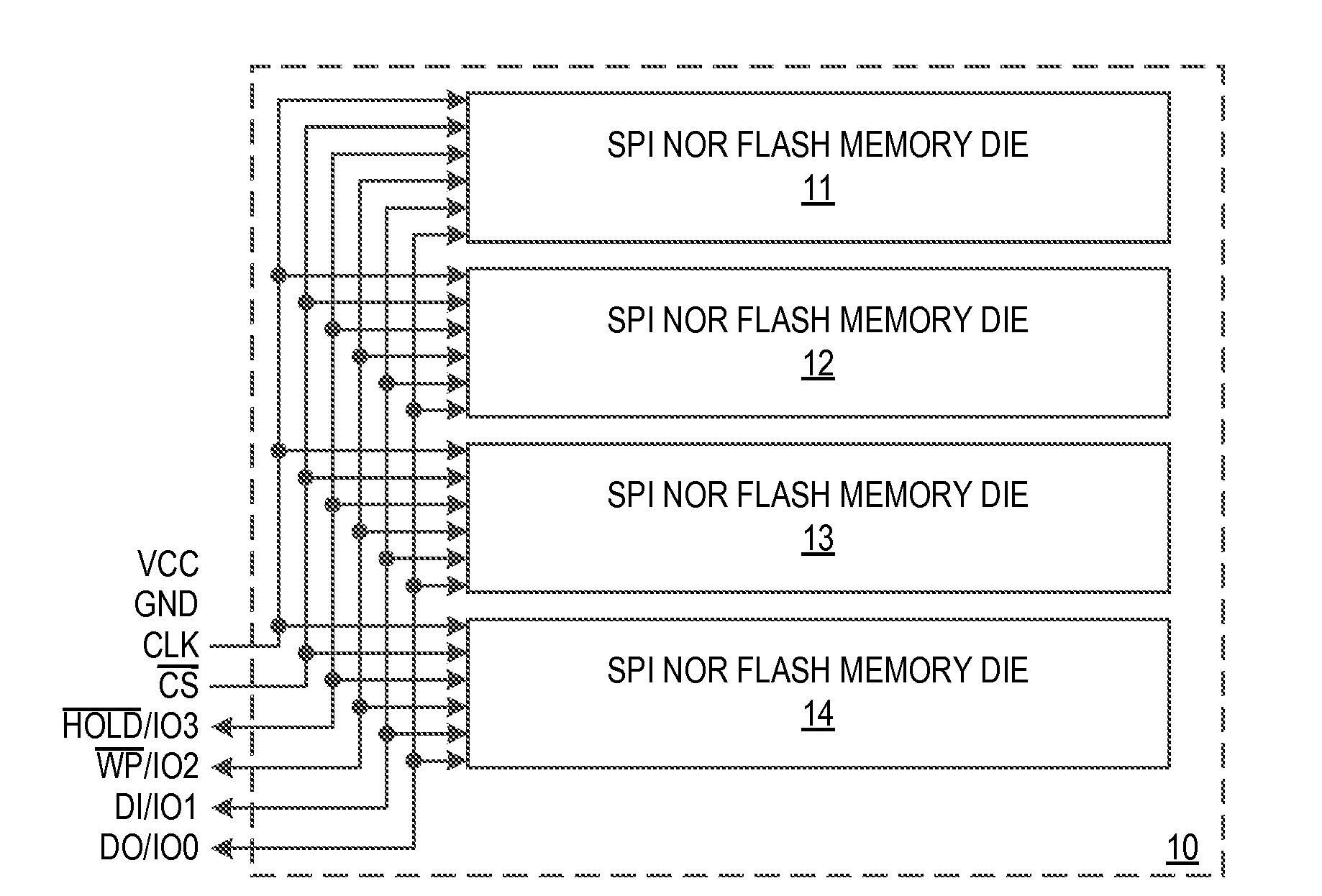

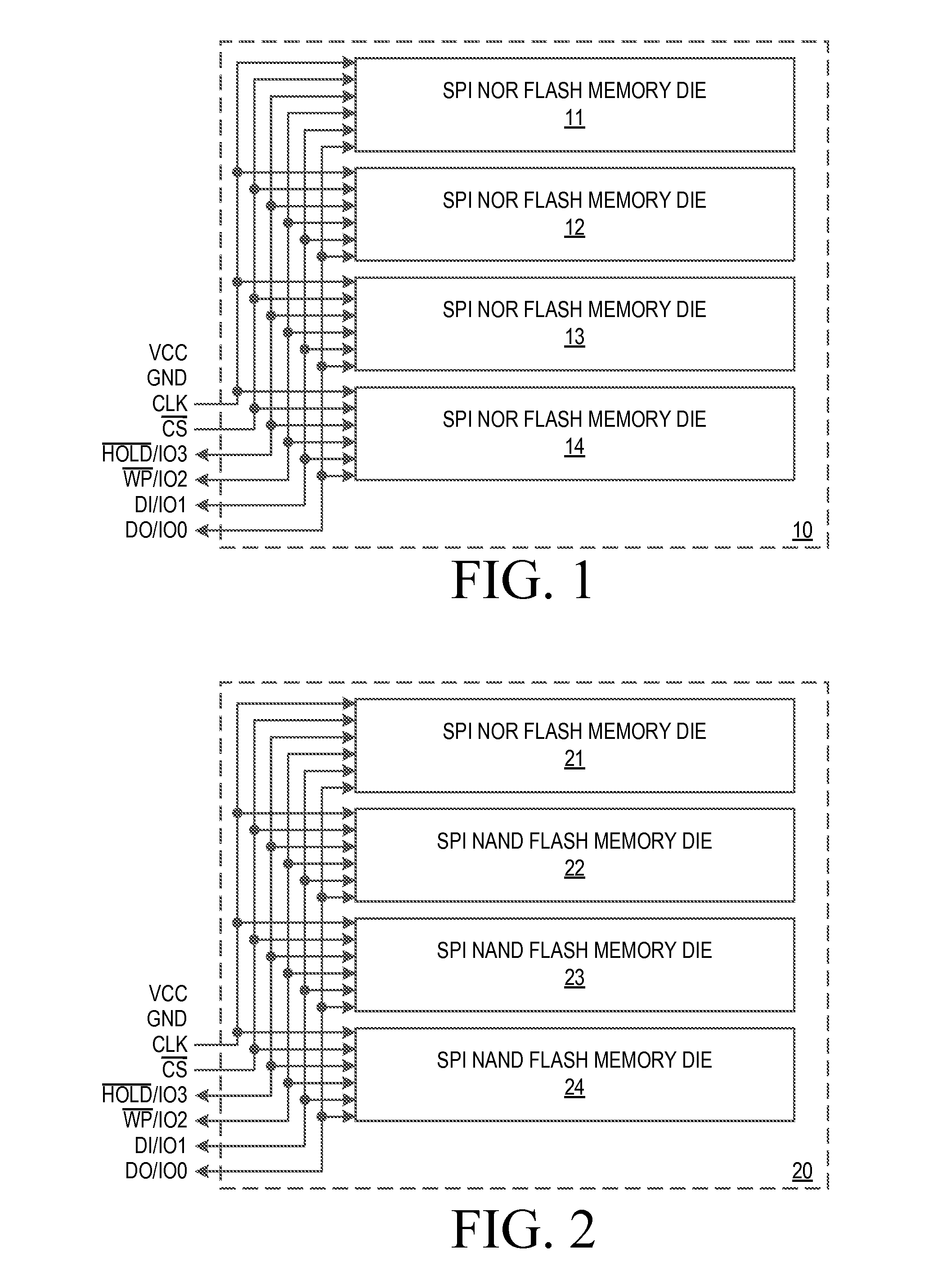

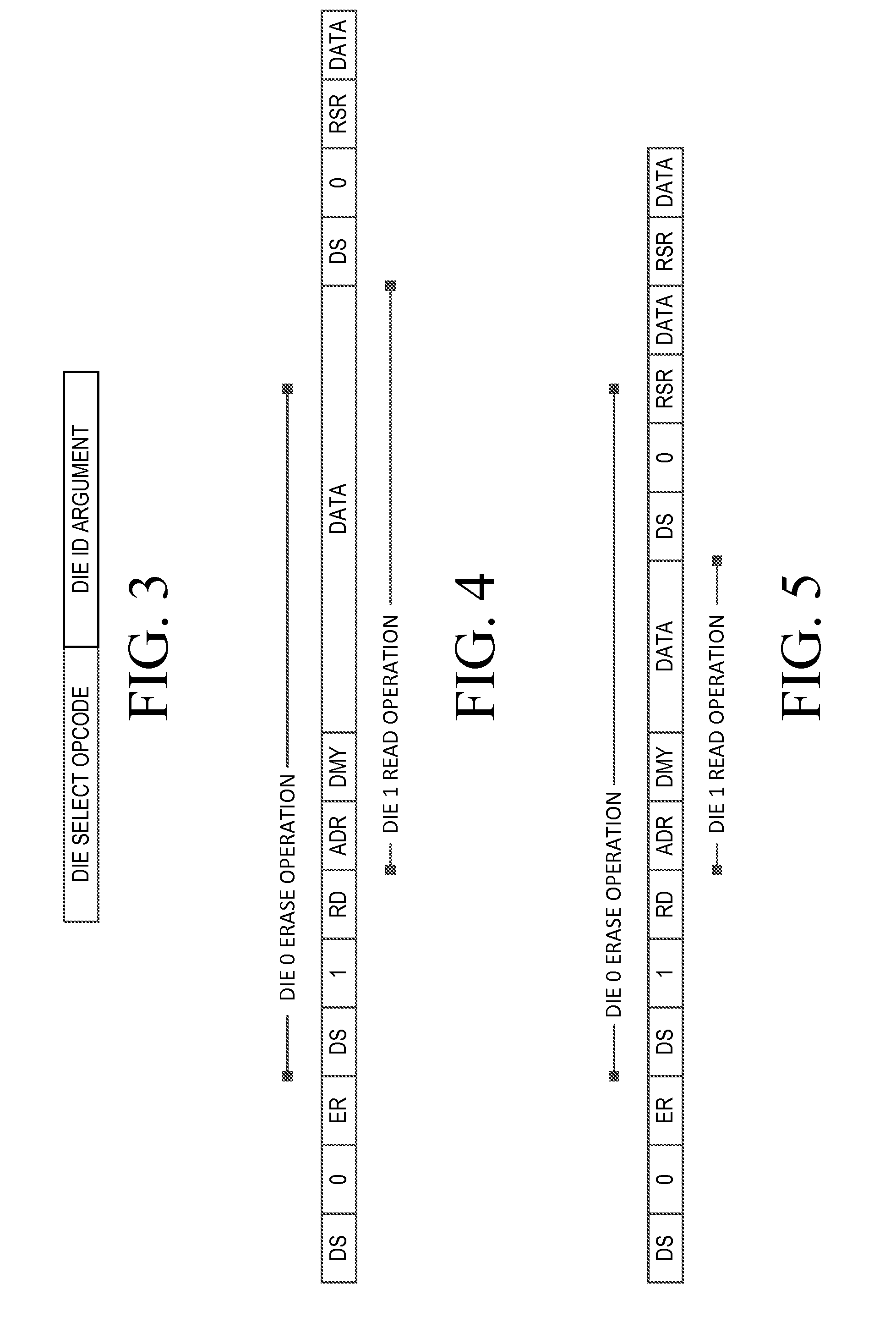

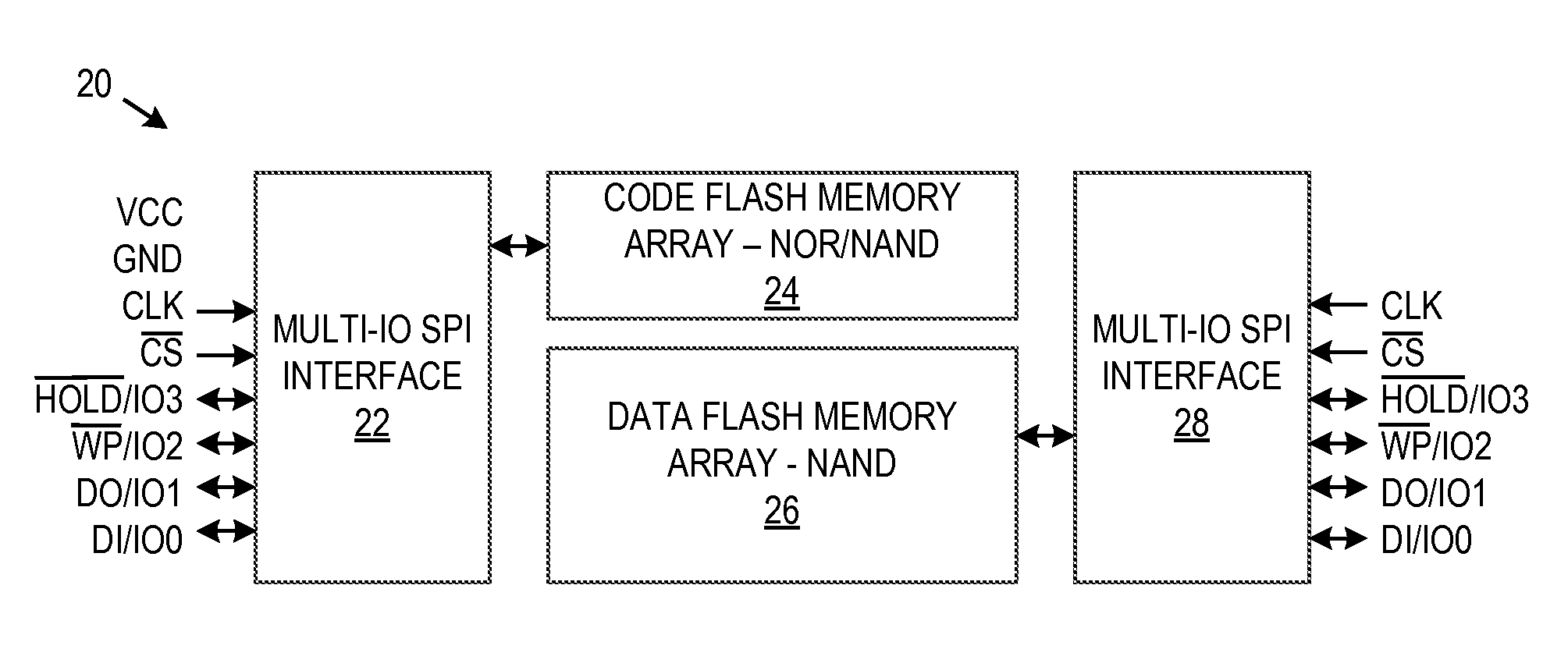

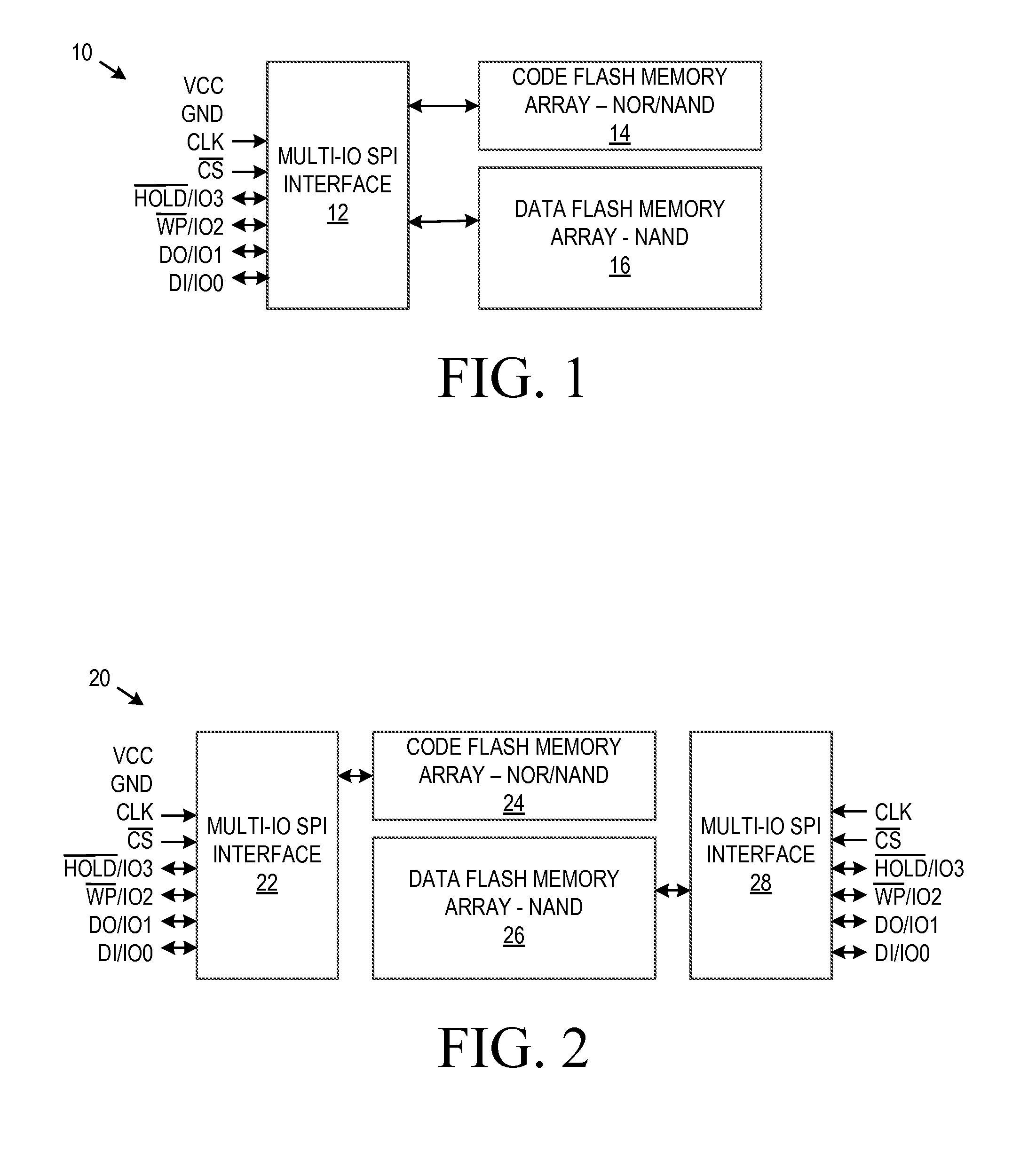

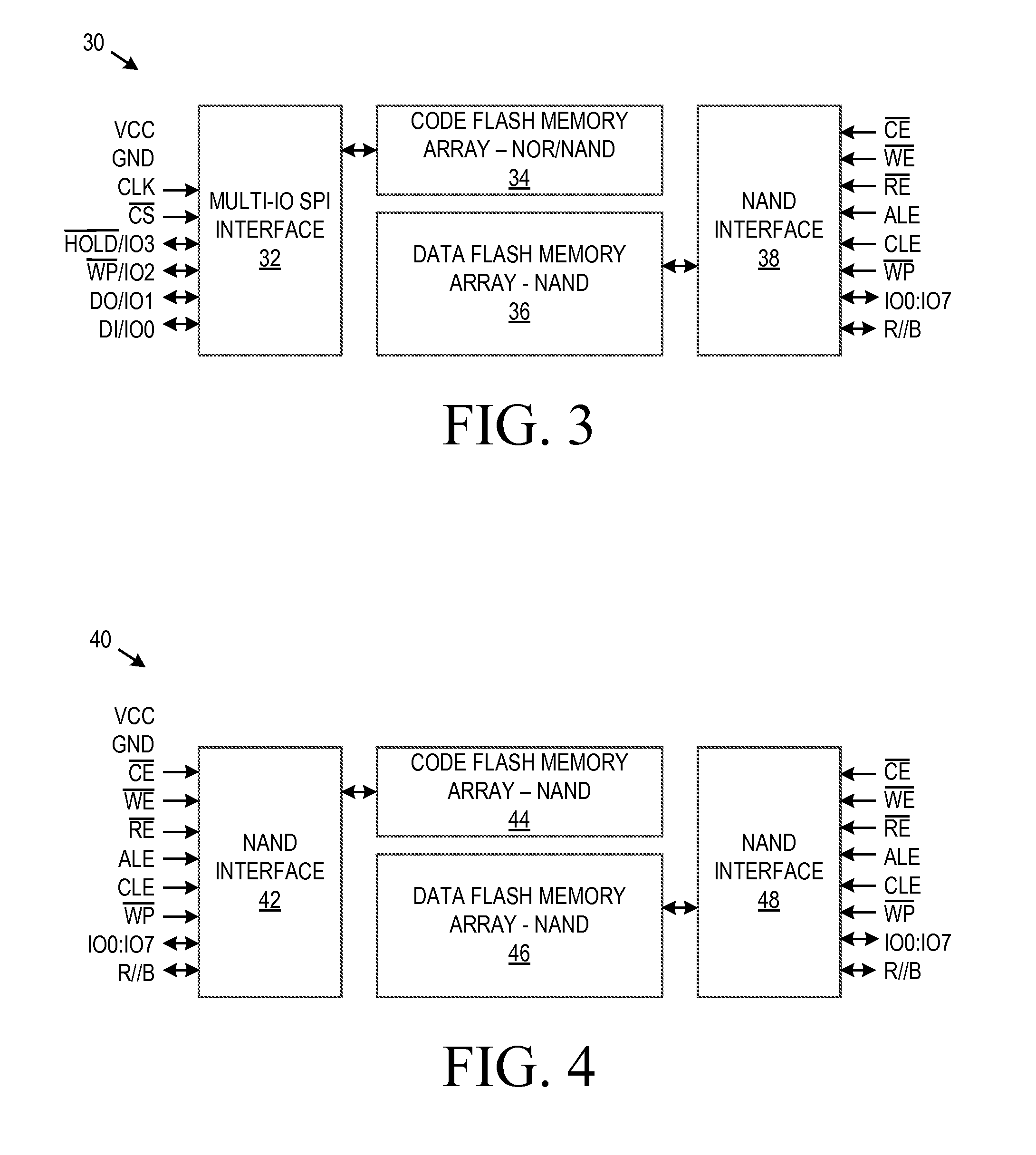

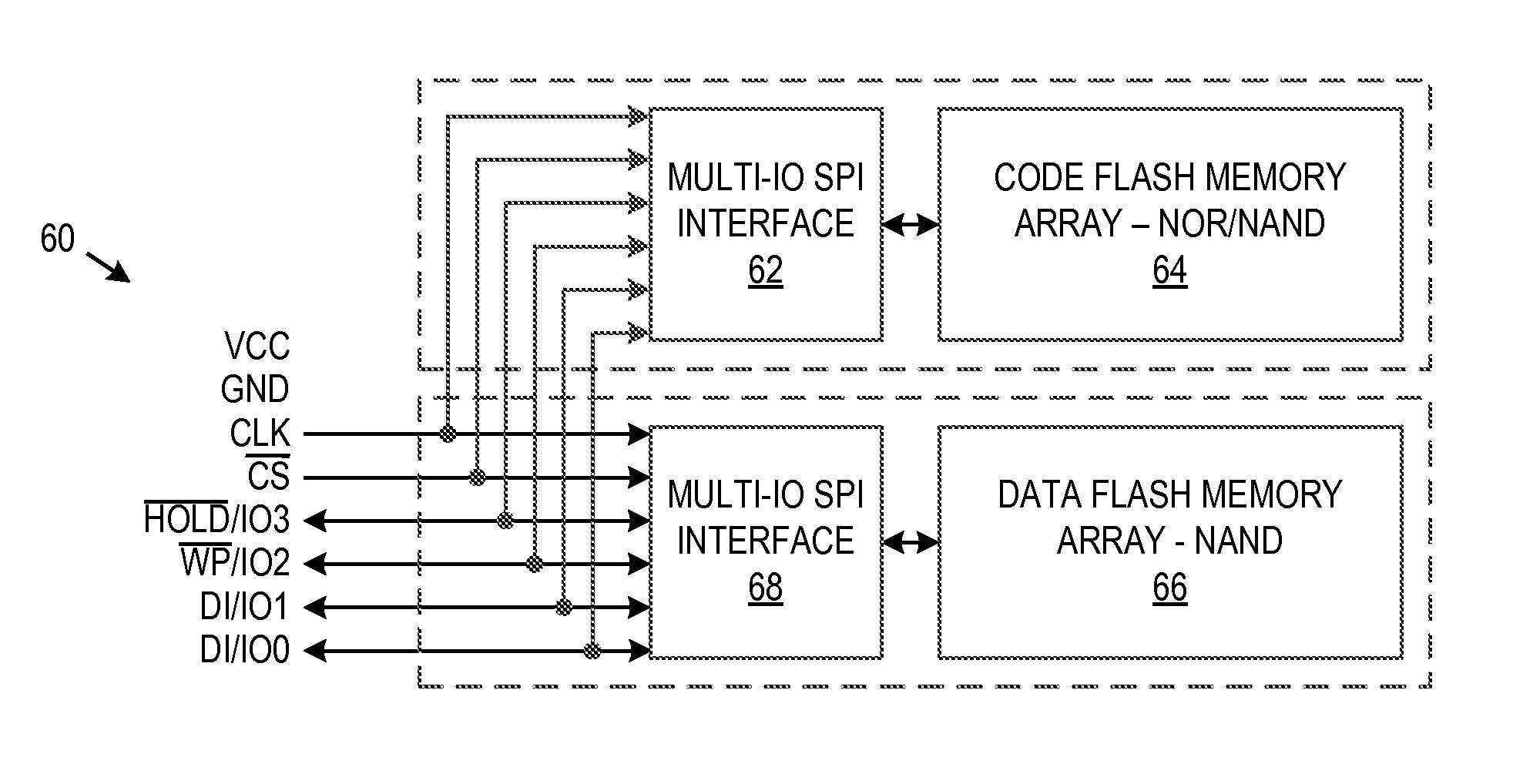

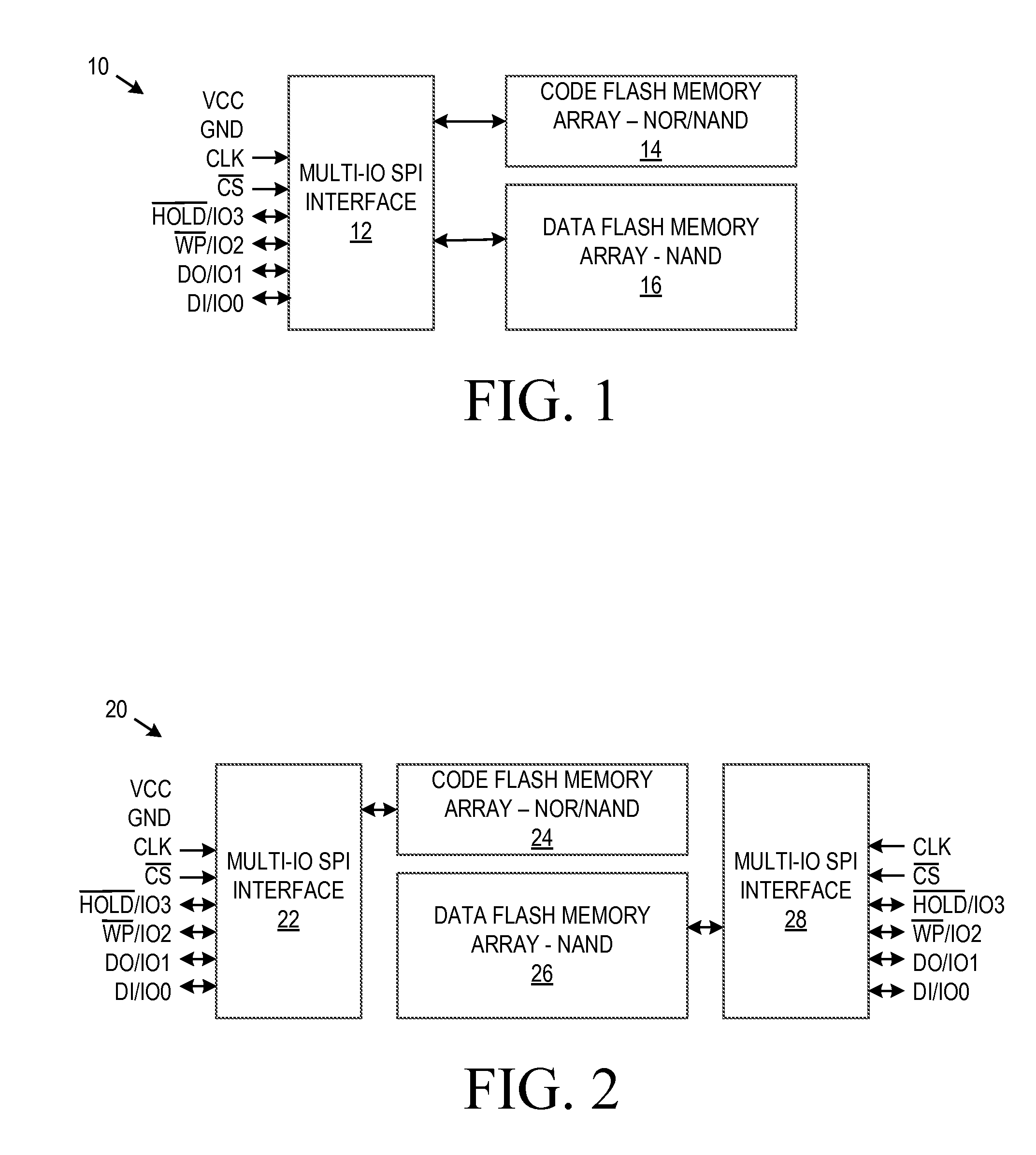

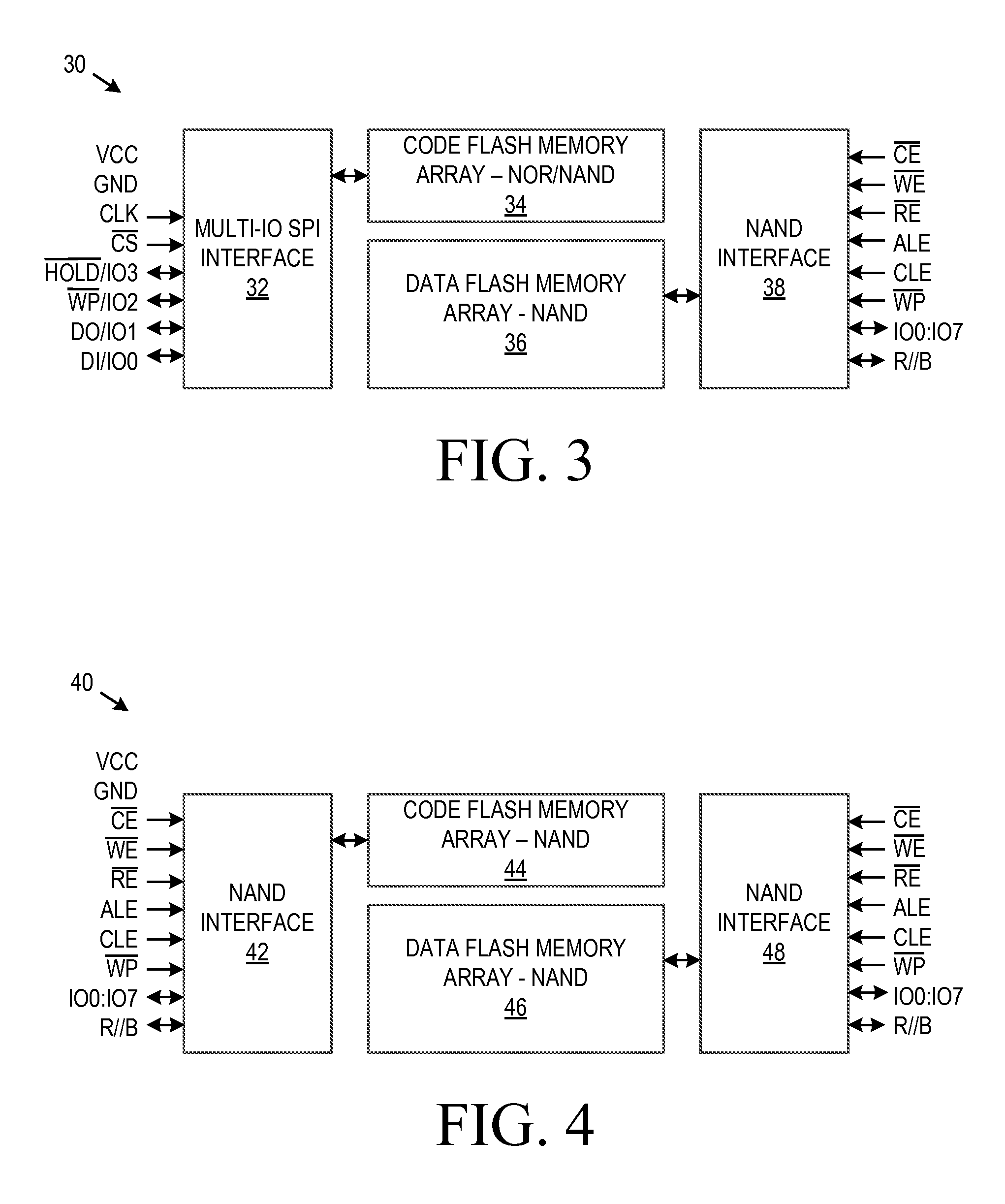

Stacked Die Flash Memory Device With Serial Peripheral Interface

Any number of Serial Peripheral Interface (“SPI”) flash memory die may be stacked and packaged using any desired multi-chip packaging technique to realize any one or combination of various capabilities such as low per-bit cost, high density storage, code shadowing to RAM, and fast random access for “execute in place” applications, while preserving the advantages of the SPI interface. During device manufacture, each of the stacked die is assigned a unique identifier or “Die ID” relative to the other stacked die in the package. During normal operations, the unique Die IDs are used by a Die Select instruction to enable one of the stacked die to respond to subsequent instructions on the SPI interface, while disabling the other stacked die in the package from responding to subsequent instructions but for certain “Universal” instructions which include the Die Select instruction. Concurrent operations by the stacked die are supported.

Owner:WINBOND ELECTRONICS CORP

Flash Memory for Code and Data Storage

ActiveUS20120084491A1Easy and economical to incorporateLarge capacityMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingData memory

A flash memory for code and data storage includes a code memory array having fast read access and suitability for execute in place, a data memory array having the characteristics of low bit cost and high density storage, and a suitable interface to provide access to both the code and data. The code memory array may be a NOR array or a performance-enhanced NAND array. The memory may be implemented in a single chip package or multi-chip package solution.

Owner:WINBOND ELECTRONICS CORP

Method and system for modifying operation of ROM based boot code of a network adapter chip

Certain embodiments for modifying operation of ROM based boot code may include modifying a bootup sequence for boot code resident in a ROM within a network adapter chip (NAC). The bootup sequence may be modified during booting of the NAC using code patches in memory external to the NAC. The boot code may comprise ROM loader code and / or self-boot code in the ROM within the NAC. Execution of the self-boot code may comprise execution of code patches. The code patches may comprise initialization code patches and service code patches. The code patches may be executed in place of functions in the self-boot code or in addition to the functions in the self-boot code. Additionally, the code patches may be configured such that a function in the self-boot code may be effectively deleted where no corresponding code patch may be executed in place of the function.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

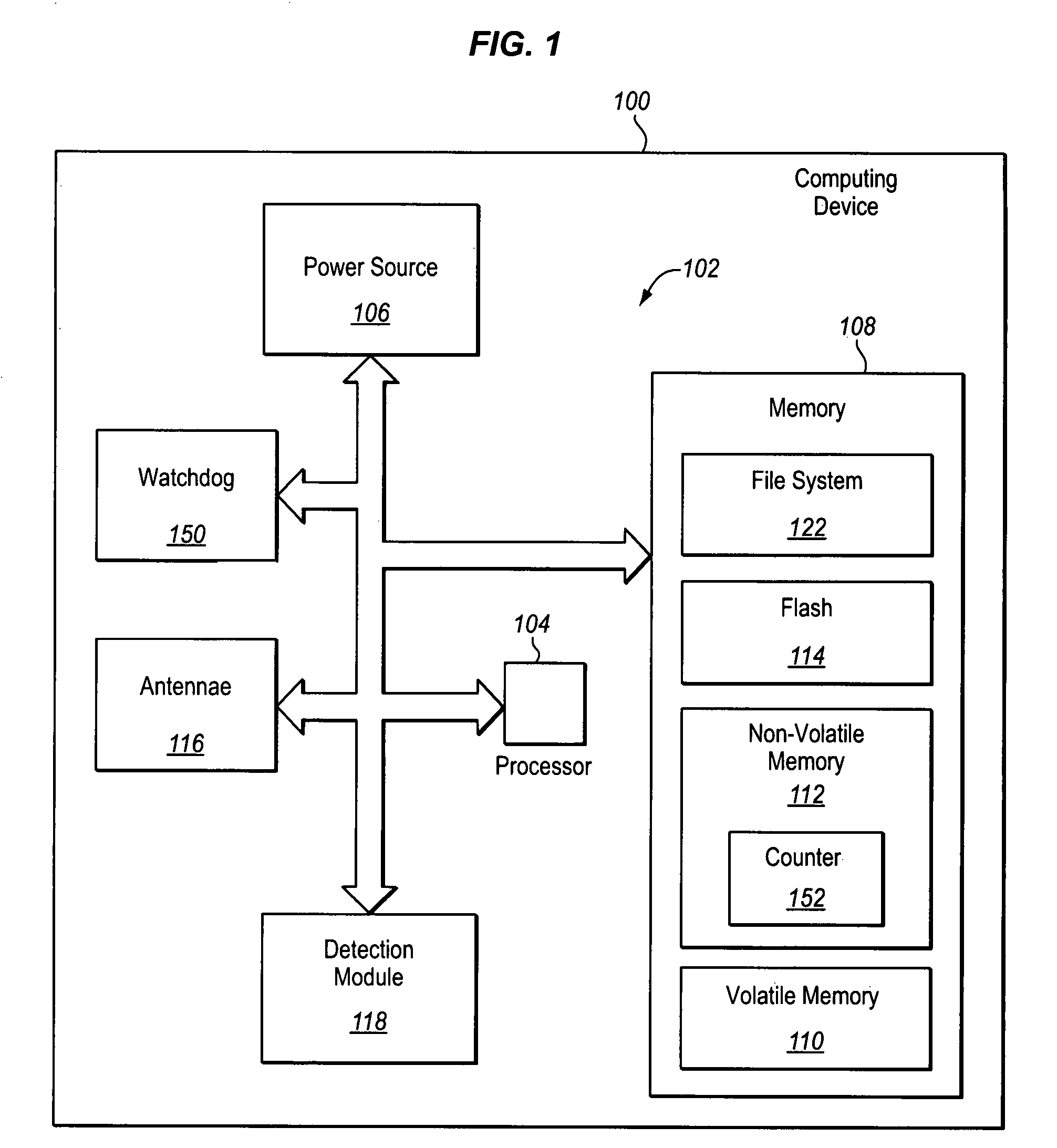

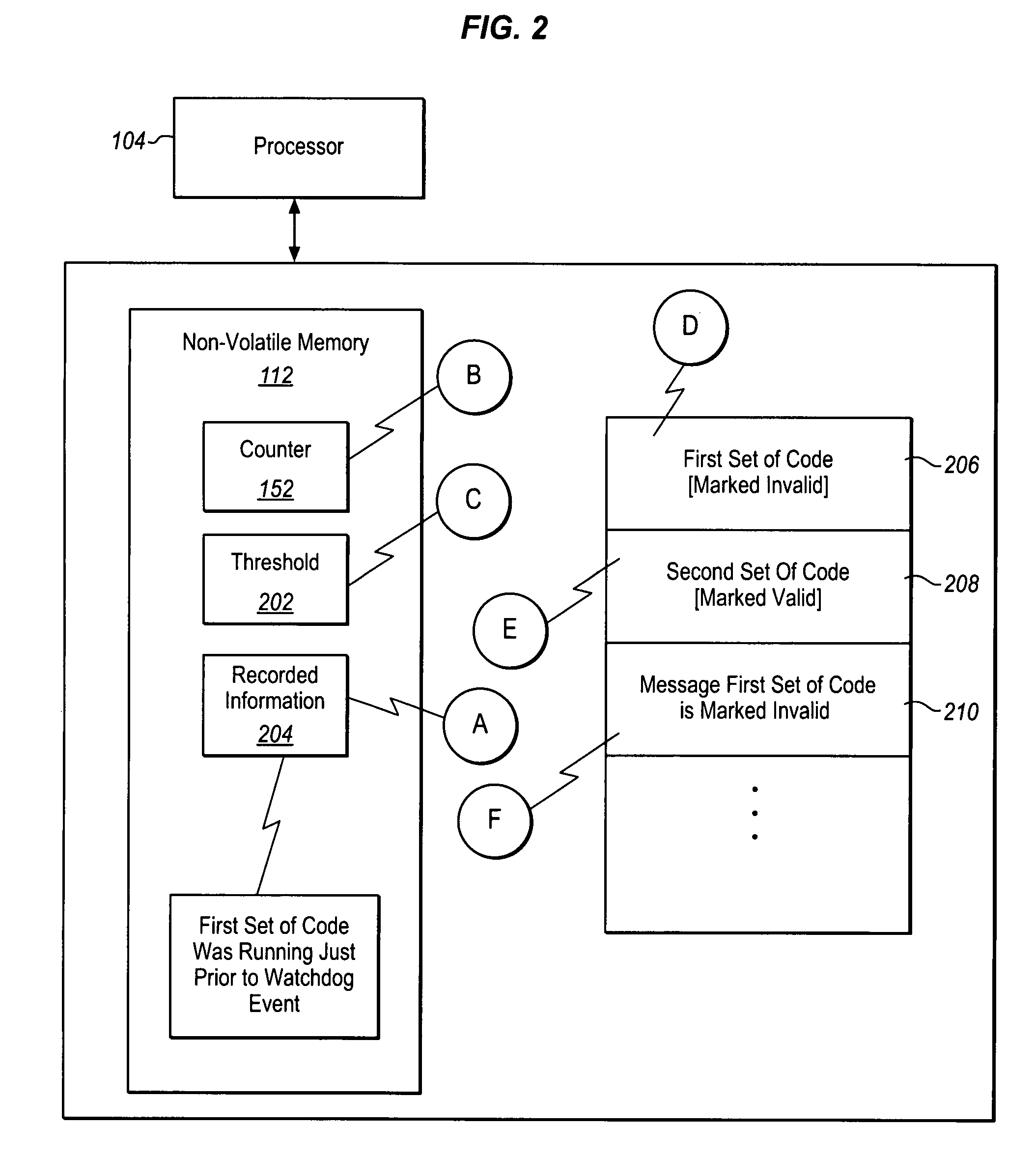

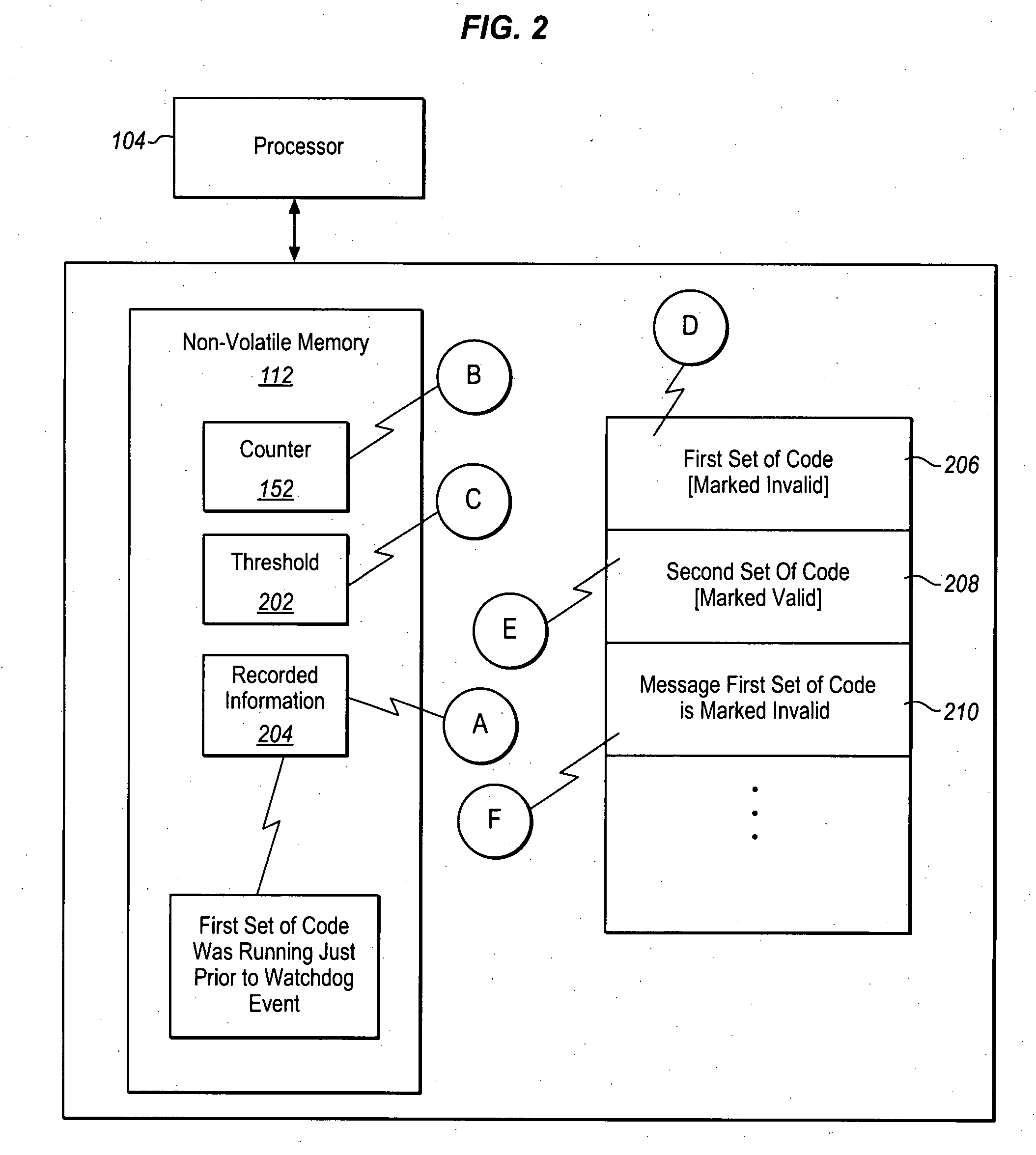

Adjusting threshold for software error reset attempts to be commensurate with reserve power

InactiveUS7814368B2Volume/mass flow measurementDigital computer detailsSoftware errorParallel computing

Owner:G2 MICROSYST

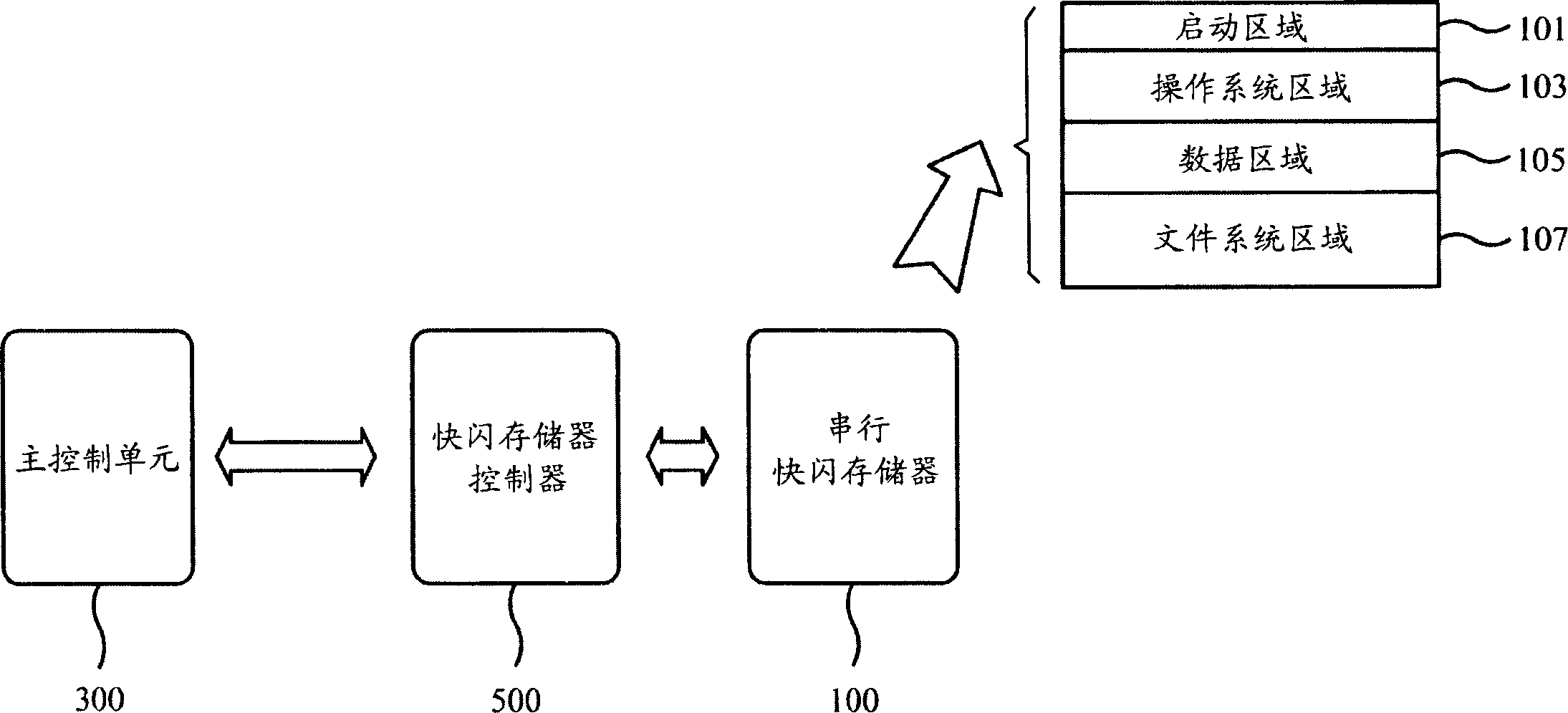

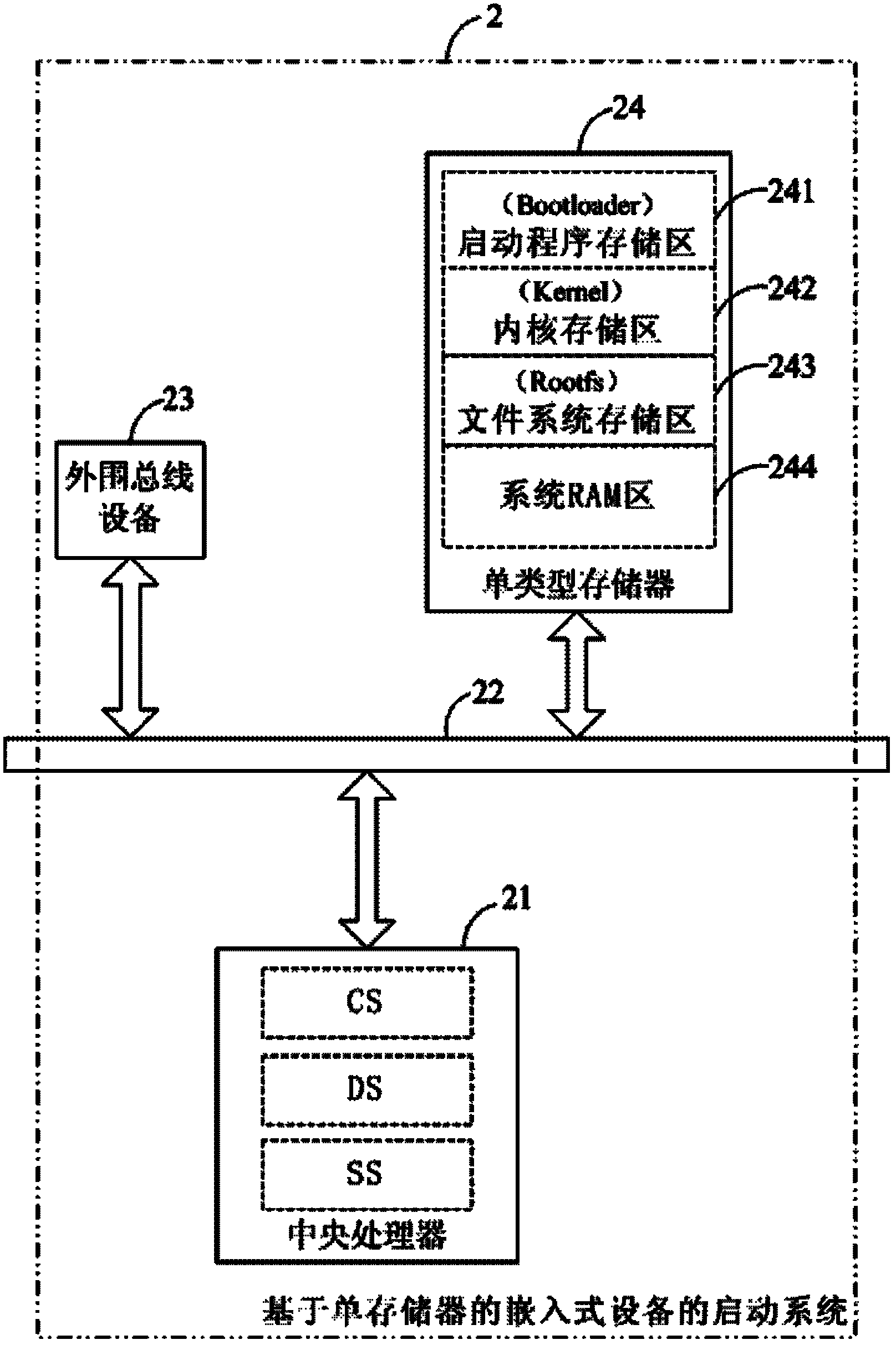

Starting system for embedded equipment on basis of single storage

ActiveCN102866896AAchieve sharingGuaranteed uptimeProgram loading/initiatingFile systemRandom access memory

The invention provides a starting system for embedded equipment on the basis of a single storage, which at least comprises a central processor, a system bus, peripheral bus equipment and a single-type storage, wherein the single-type storage is connected with the central processor by the system bus; the single-type storage is divided into a start program storage region, a kernel storage region, a file system storage region and a system RAM (Random Access Memory) region to ensure the embedded equipment to execute the start operation in two conventional and XIP (eXecute In Place) start modes, so that the sharing of a storage space can be implemented; the size of each storage region can be regulated as required; the starting system is convenient to implement software upgrading and high efficiency operation of the embedded equipment; and meanwhile, a CPU (Central Processing Unit) interface can be simplified, the number of I / O (Input / Output) pins is saved and a CPU without a DRAM (Dynamic Random Access Memory) controller even can be used in a plurality of pieces of applications so as to fulfill the aim of saving the cost.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Firmware ROM patch method

ActiveUS9348730B2Software testing/debuggingSpecific program execution arrangementsAssembly languageComputer science

Owner:MICROCHIP TECH INC

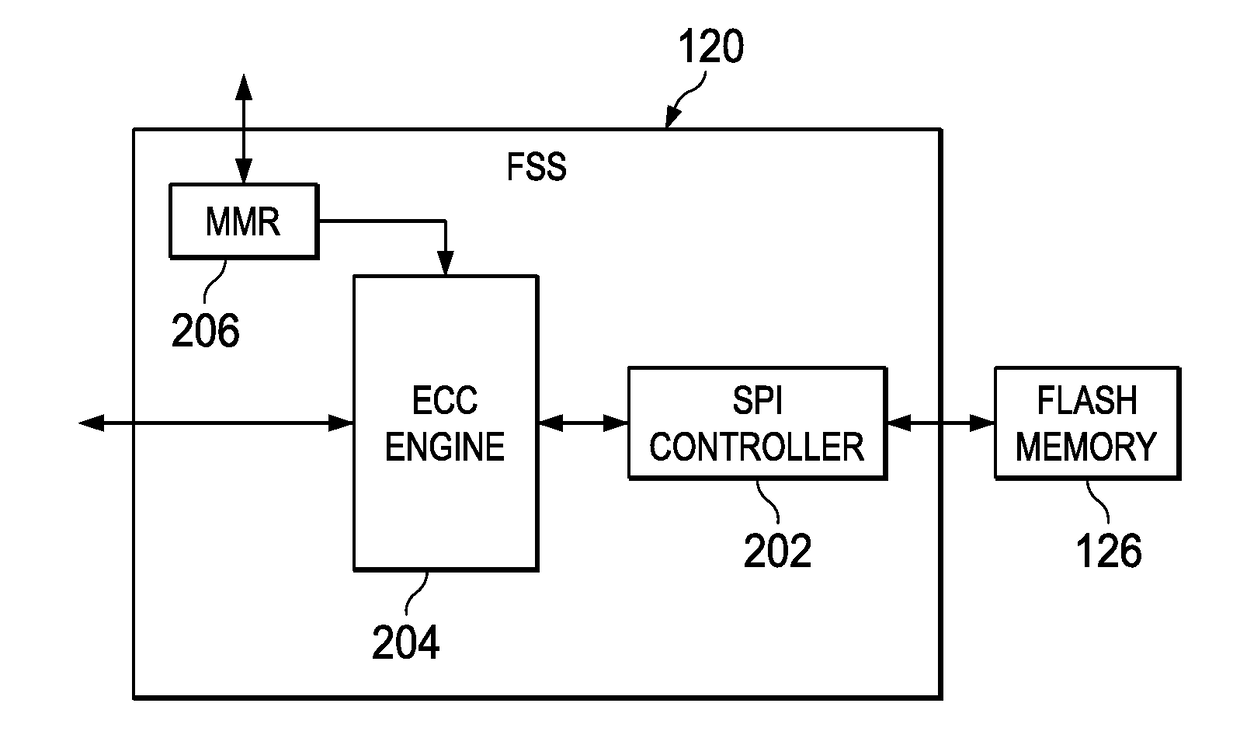

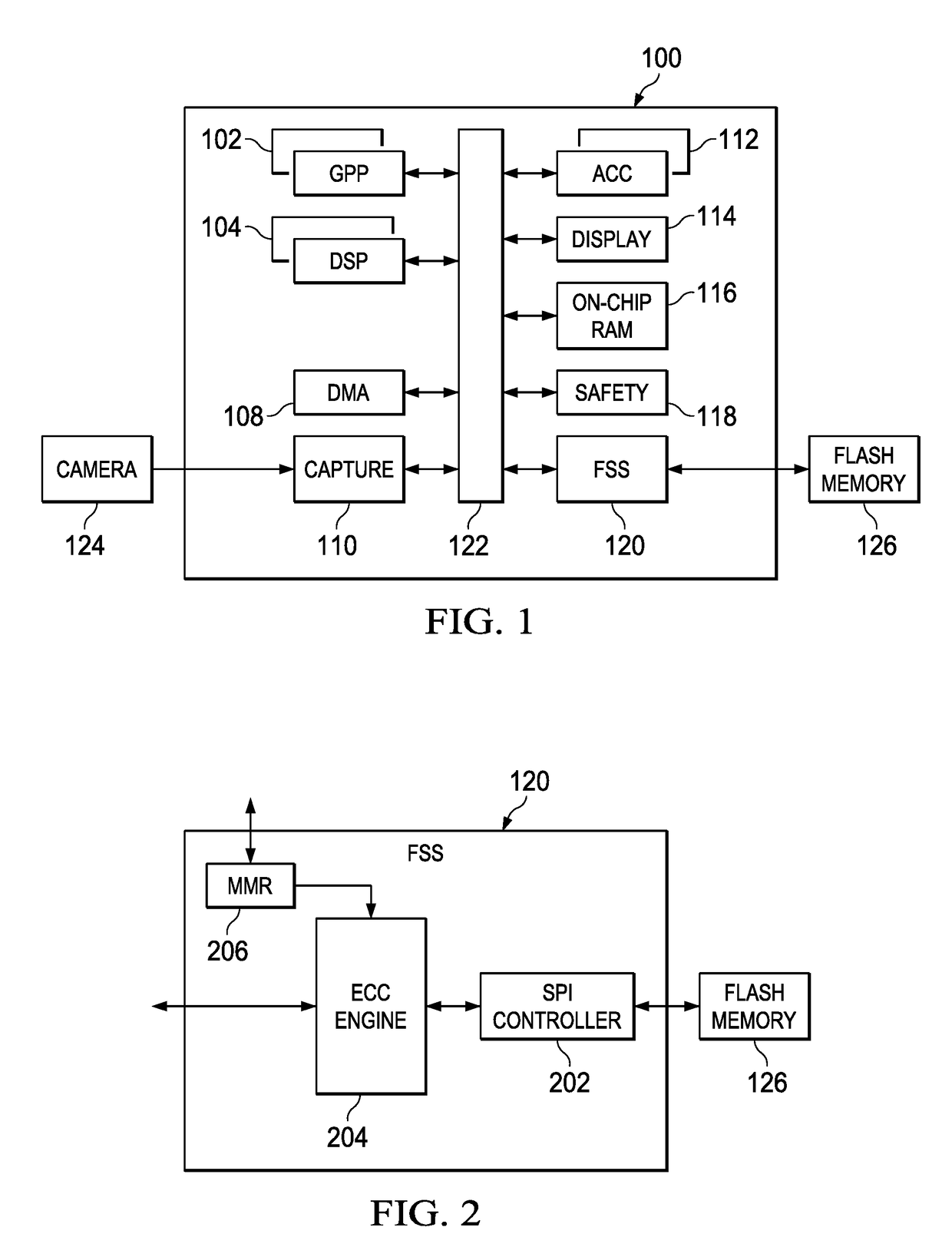

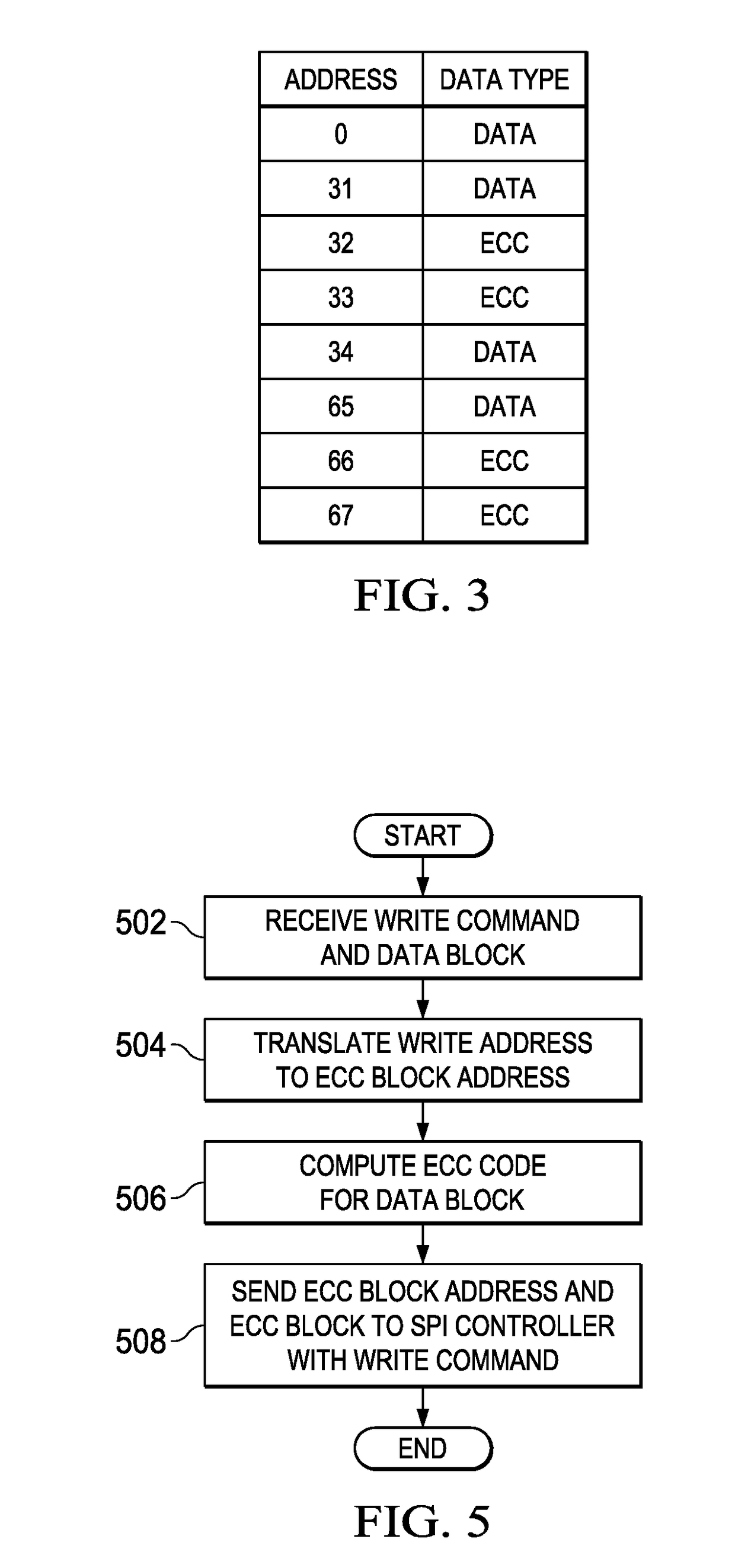

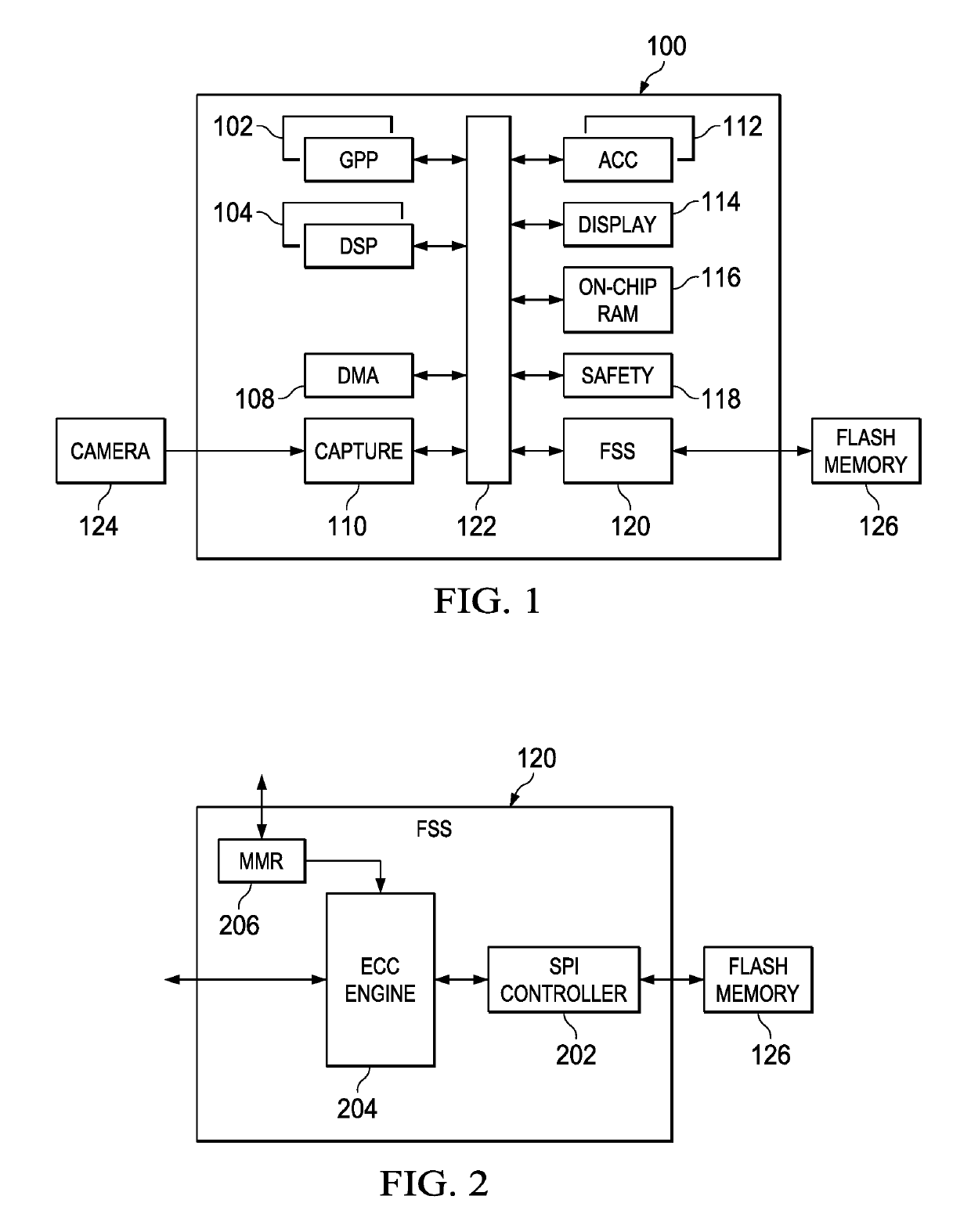

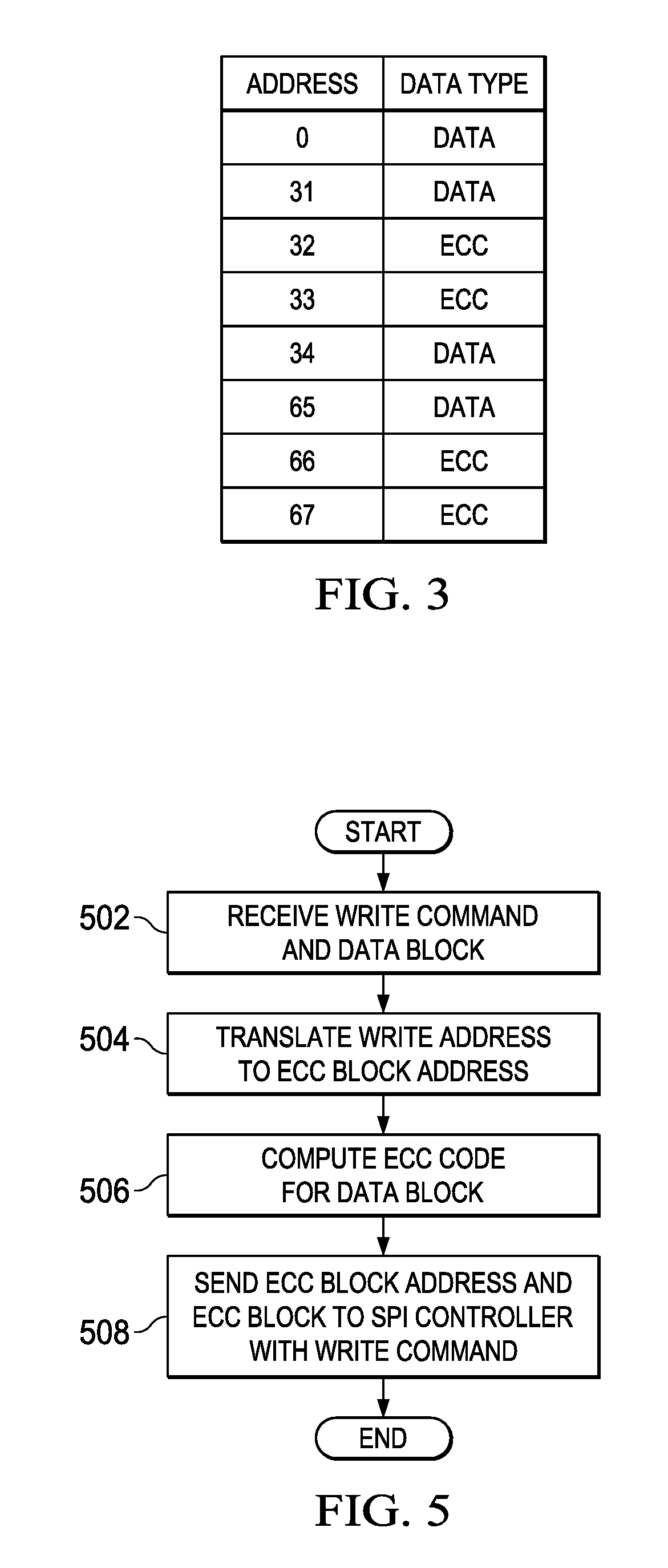

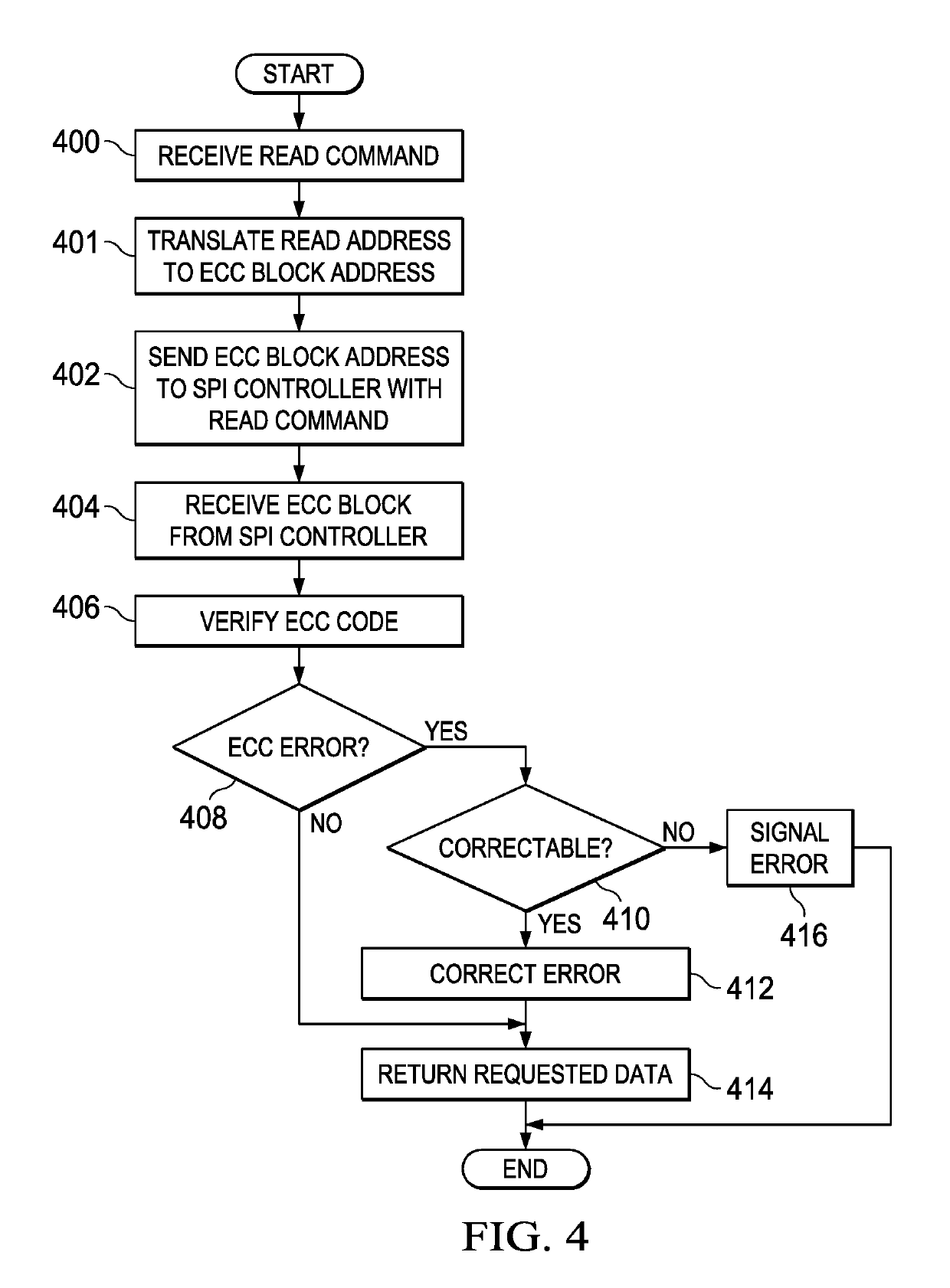

Safe Execution in Place (XIP) From Flash Memory

ActiveUS20180293129A1Read-only memoriesRedundant data error correctionComputer scienceError correcting

A device is provided that includes a processor, a flash memory configured to store error correcting code (ECC) blocks for execution in place (XIP) processing by the processor, wherein an ECC block includes a data block and an ECC code for the data block, a flash interface controller coupled to the flash memory, and an error correcting code (ECC) engine coupled between the processor and the flash interface controller, wherein the ECC engine is configured to receive a read command for the flash memory from the processor, to translate a read address to an ECC block address, to read the ECC block at the ECC block address from the flash memory via the flash interface controller, and to verify the ECC code in the read ECC block.

Owner:TEXAS INSTR INC

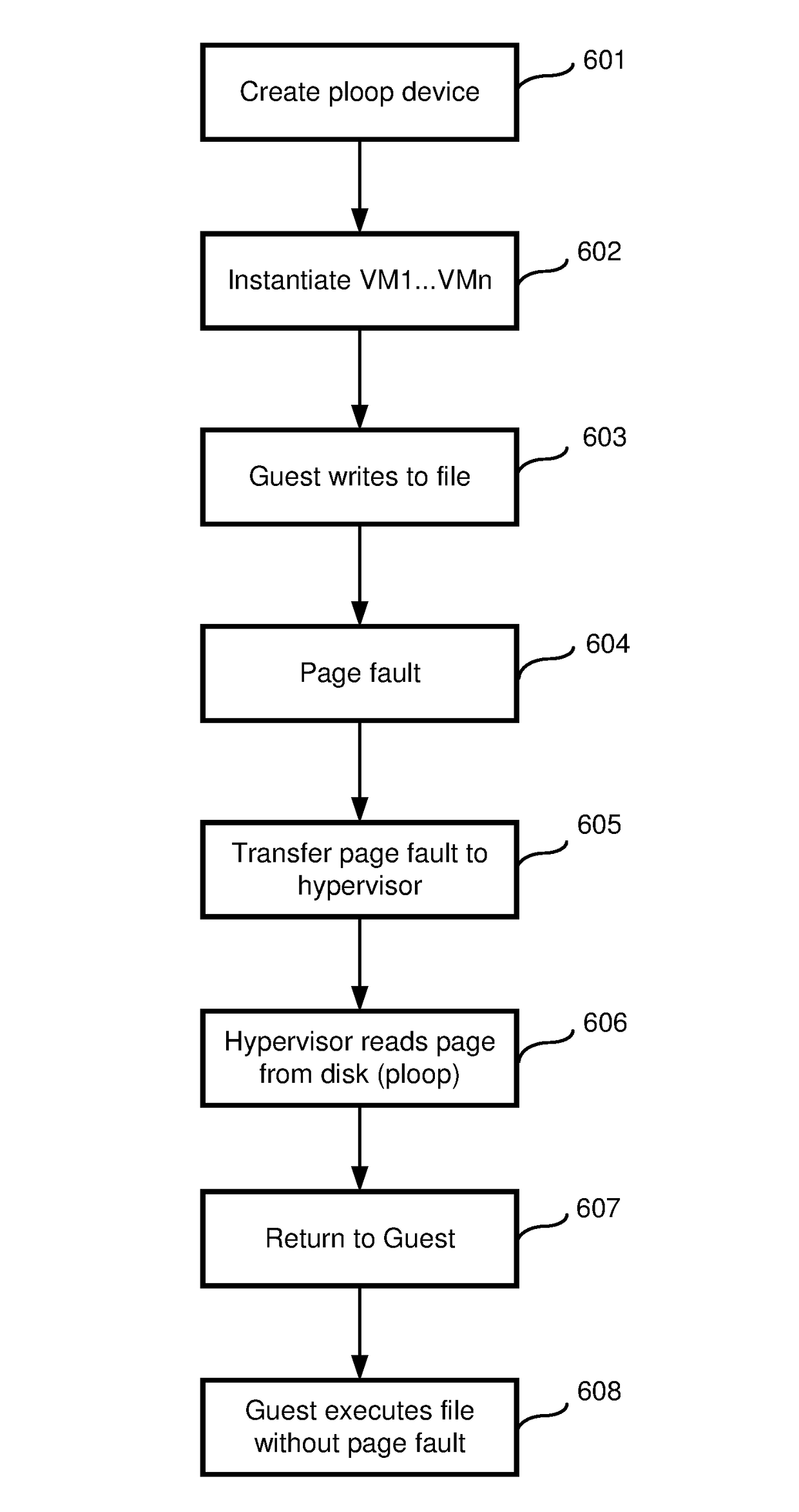

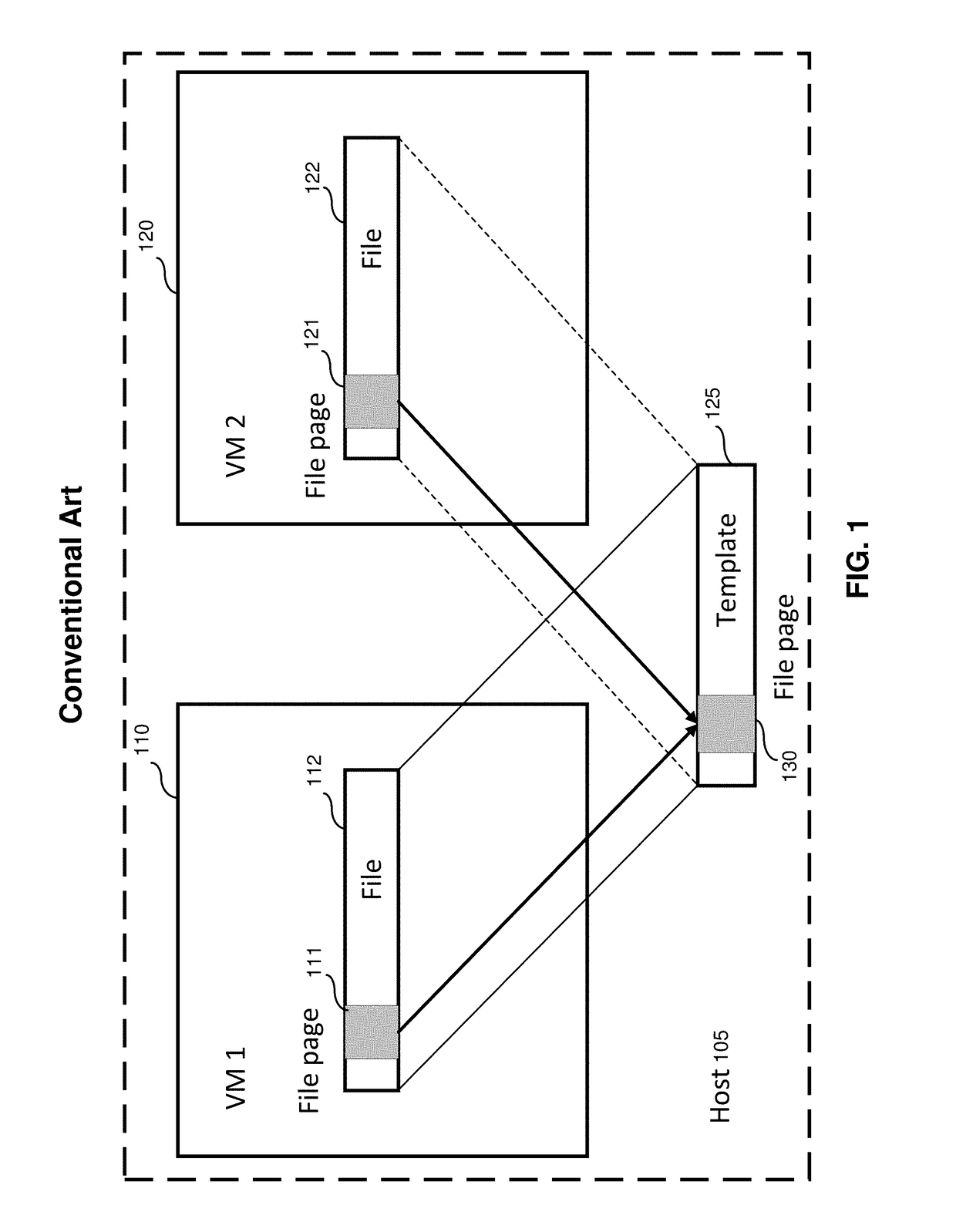

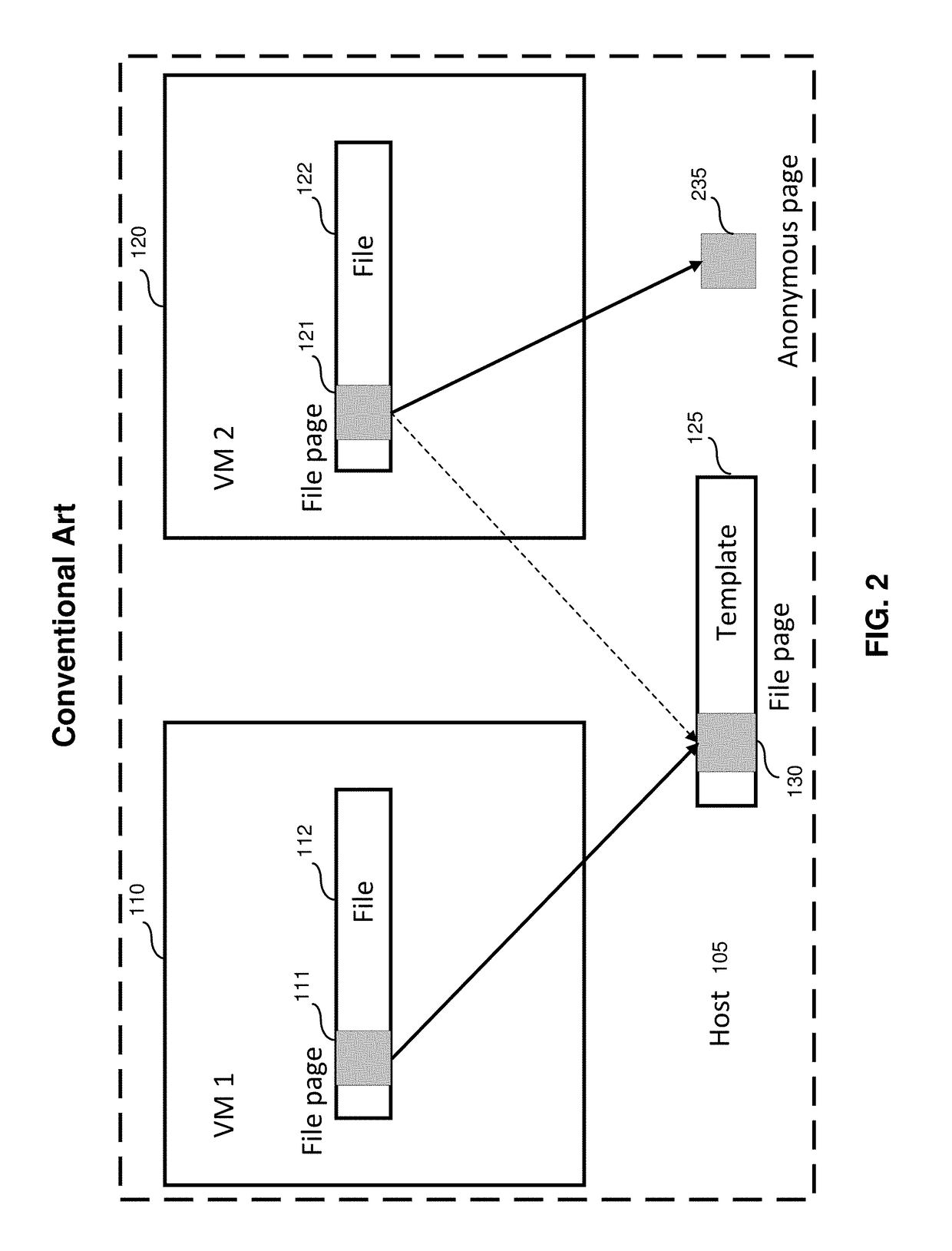

Memory management and sharing host OS files for Virtual Machines using execution-in-place

ActiveUS10037334B1Input/output to record carriersDigital data information retrievalOperational systemVirtual machine

A system for memory management for Virtual Machines (VMs), including a host computer system running a host operating system (OS); at least two Virtual Machines (VMs) running on the host computer system, wherein each of the VMs has a Guest OS supporting a guest file system with execution-in-place that allows code execution without an intermediate buffer cache; a hypervisor configured to control the VMs; and a thin provisioning block device configured to store shared pages and formed of at least one delta file. The hypervisor is configured to receive a page fault, and to read the shared pages from the thin provisioning block device. The Guest OS executes the file that is stored on the thin provisioning block device.

Owner:VIRTUOZZO INT GMBH

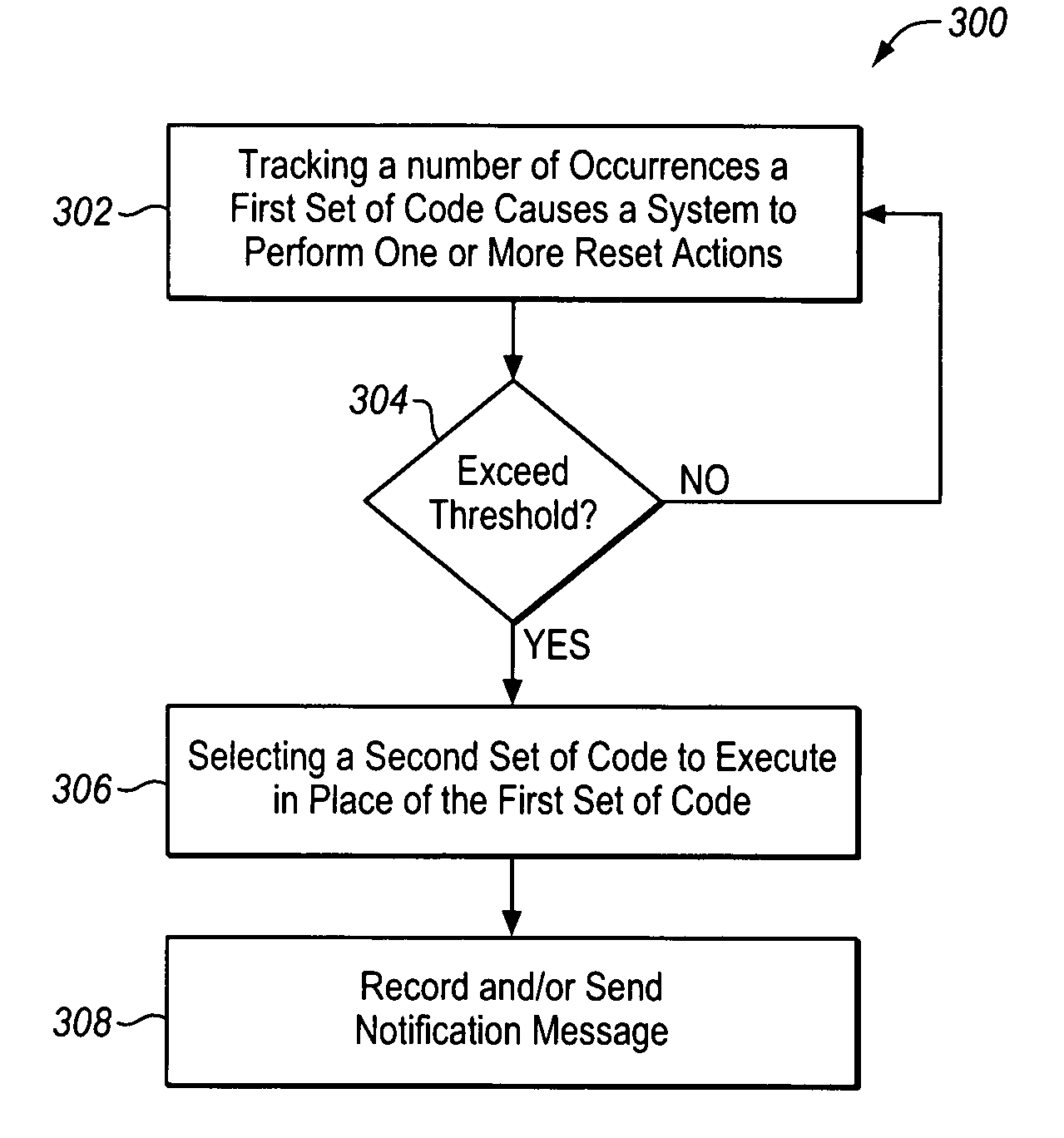

Reducing power consumption in response to software errors

InactiveUS20080155323A1Reduce power consumptionVolume/mass flow measurementDigital computer detailsParallel computingSoftware error

Power consumption that occurs in response to software errors may be reduced. In one example a system tracks a number of occurrences a first set of code causes a system to perform one or more reset actions, determines whether the number of occurrences exceeds a threshold, and selects a second set of code to execute in place of the first set of code, if the quantity exceeds the threshold.

Owner:G2 MICROSYST

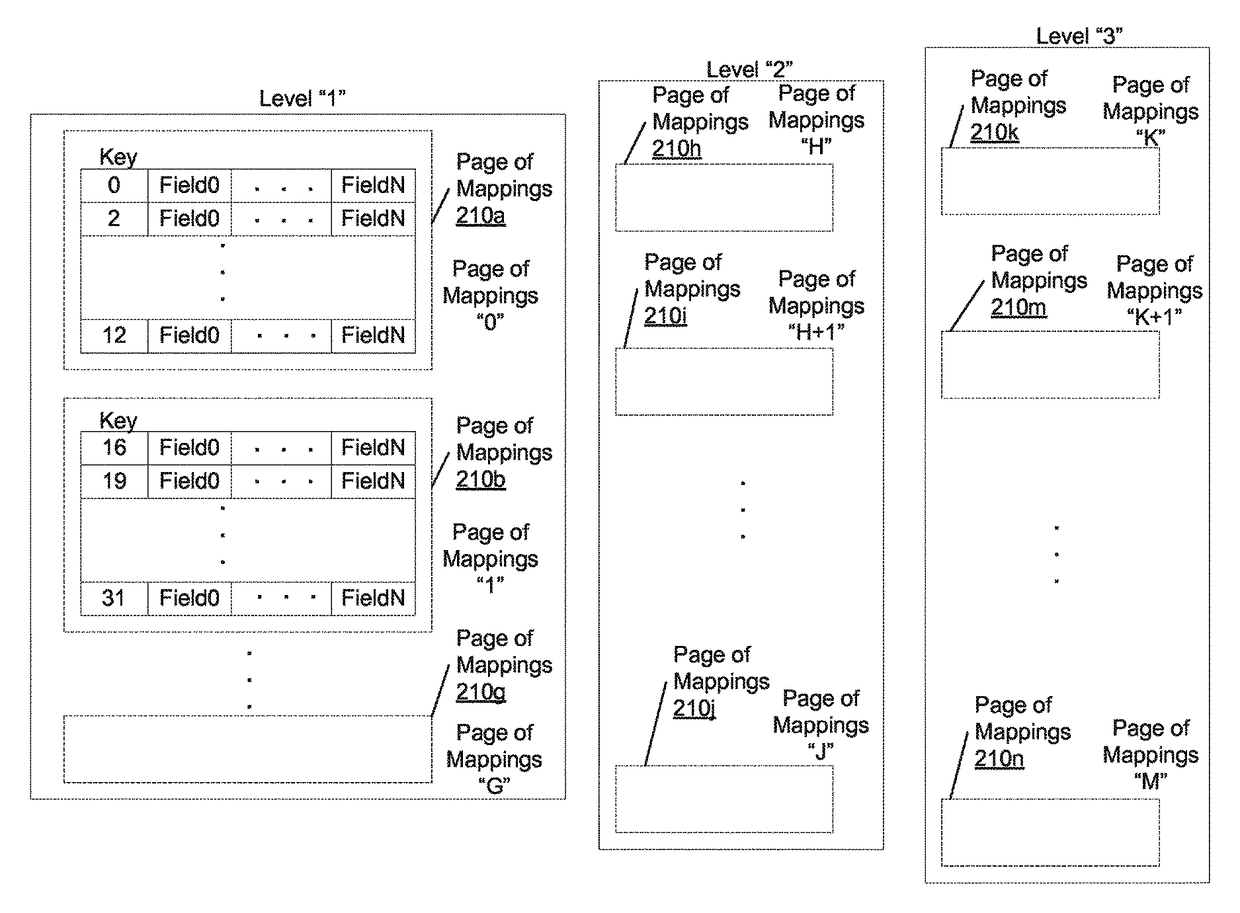

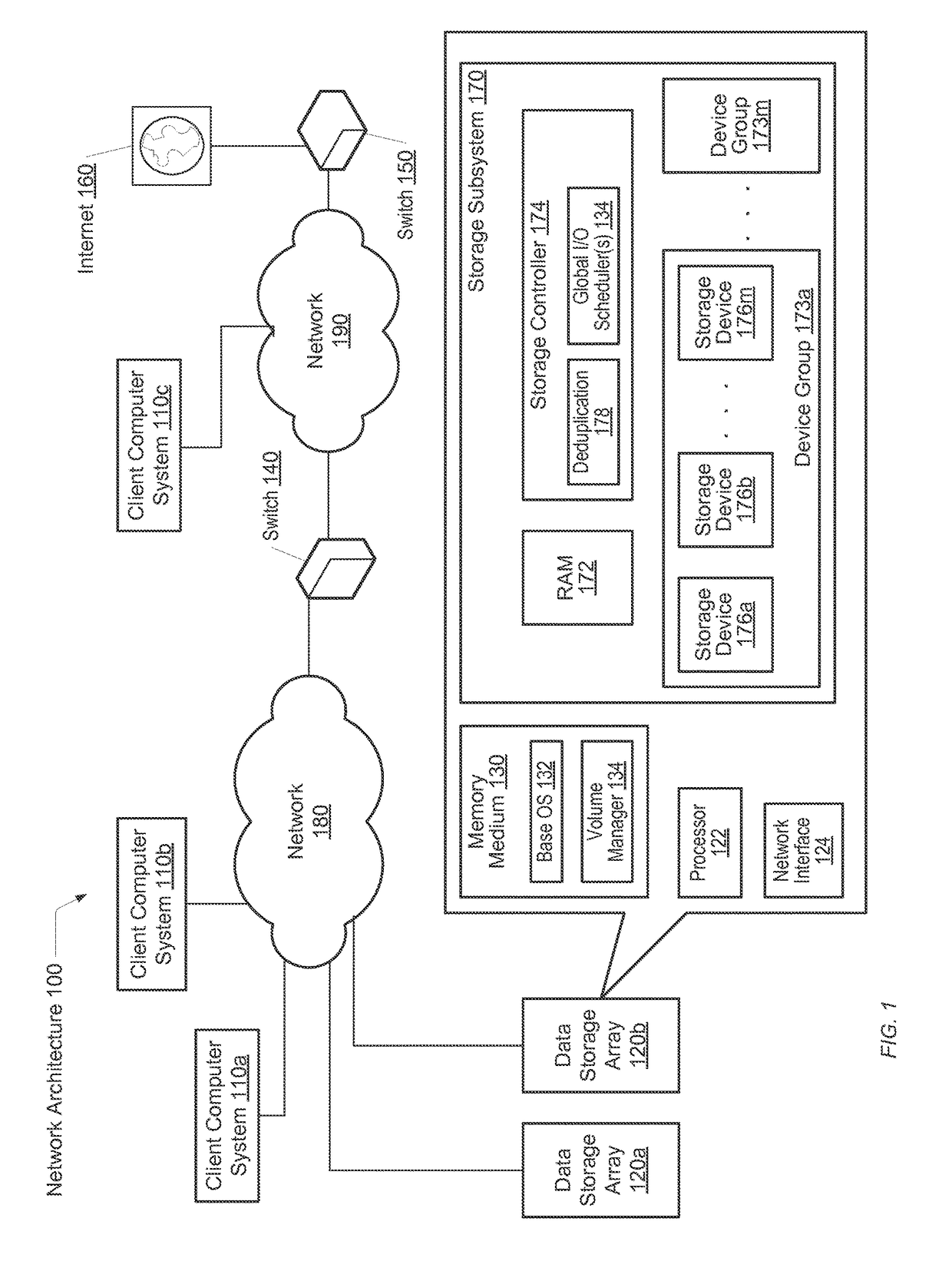

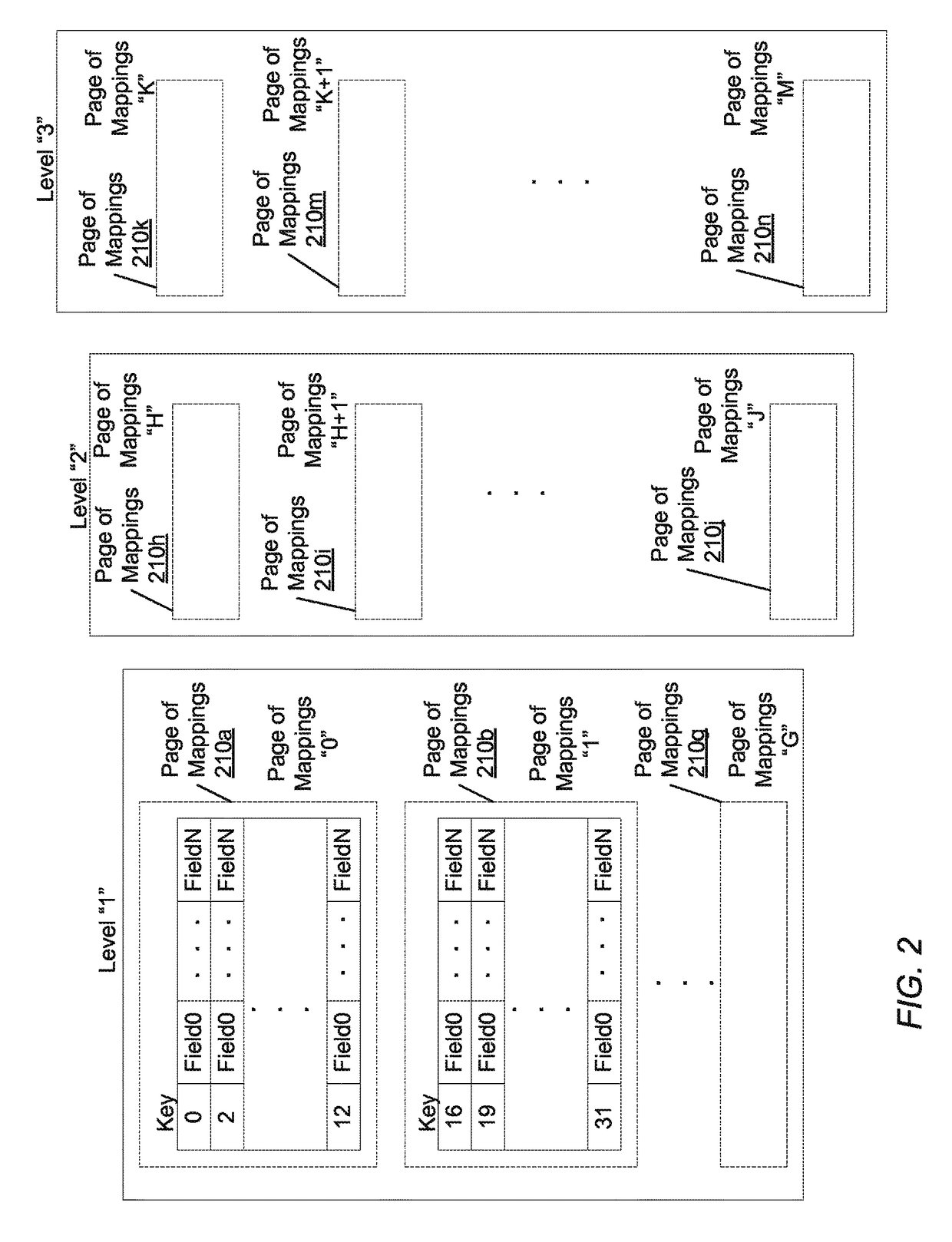

Metadata rewrite and flatten optimization

InactiveUS9727485B1Effective maintenanceMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageControl store

A system and method for efficiently maintaining metadata stored among a plurality of solid-state storage devices. A data storage subsystem supports multiple mapping tables. Records within a mapping table are arranged in multiple levels. Each level stores at least pairs of a key value and a physical pointer value. The levels are sorted by time. New records are inserted in a created new highest (youngest) level. No edits are performed in-place. A data storage controller determines both a cost of searching a given table exceeds a threshold and an amount of memory used to flatten levels exceeds a threshold. In response, the controller incrementally flattens selected levels within the table based on key ranges. After flattening the records in the selected levels within the key range, the records may be removed from the selected levels. The process repeats with another different key range.

Owner:PURE STORAGE

A Combined Motion Control System of Marine Hydraulic Steering Gear

InactiveCN102275632AEasy to controlQuick and accurate controlSteering ruddersControl signalGear wheel

The invention discloses a combined motion control system of a marine hydraulic steering gear. The combined motion control system of the marine hydraulic steering gear is characterized in that it includes a transmitter, a receiver, a steering gear circuit, a servo motor, a reduction gear set, an actuator and a feedback resistor; the control signal sent by the transmitter is controlled by The receiver receives and separates the control signals of different channels, and then transmits them to the steering gear circuit. The steering gear circuit drives the action of the servo motor according to the signal. At the same time, the action of the steering gear motor is decelerated by the reduction gear set to drive the actuator and the feedback resistor. , Feedback the angle signal to the circuit for judgment, when the execution is in place, the circuit sends a signal to stop the rotation of the motor. The combined motion control system of the marine hydraulic steering gear of the present invention has simple structure and ingenious design, and is a precision mechanism integrating electromechanical. The marine hydraulic steering gear is convenient, rapid and accurate to control, providing a good guarantee for safe driving.

Owner:史震

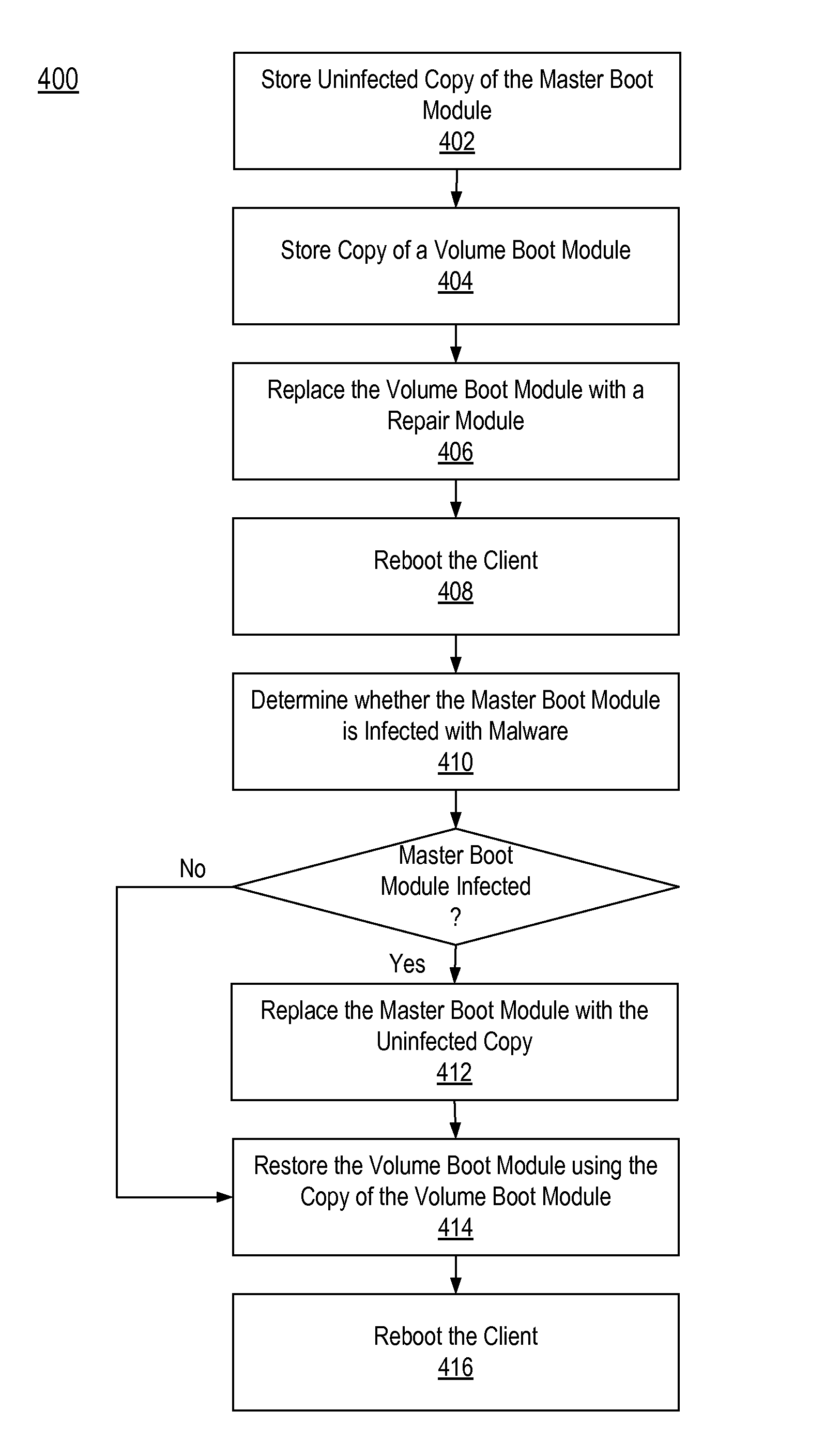

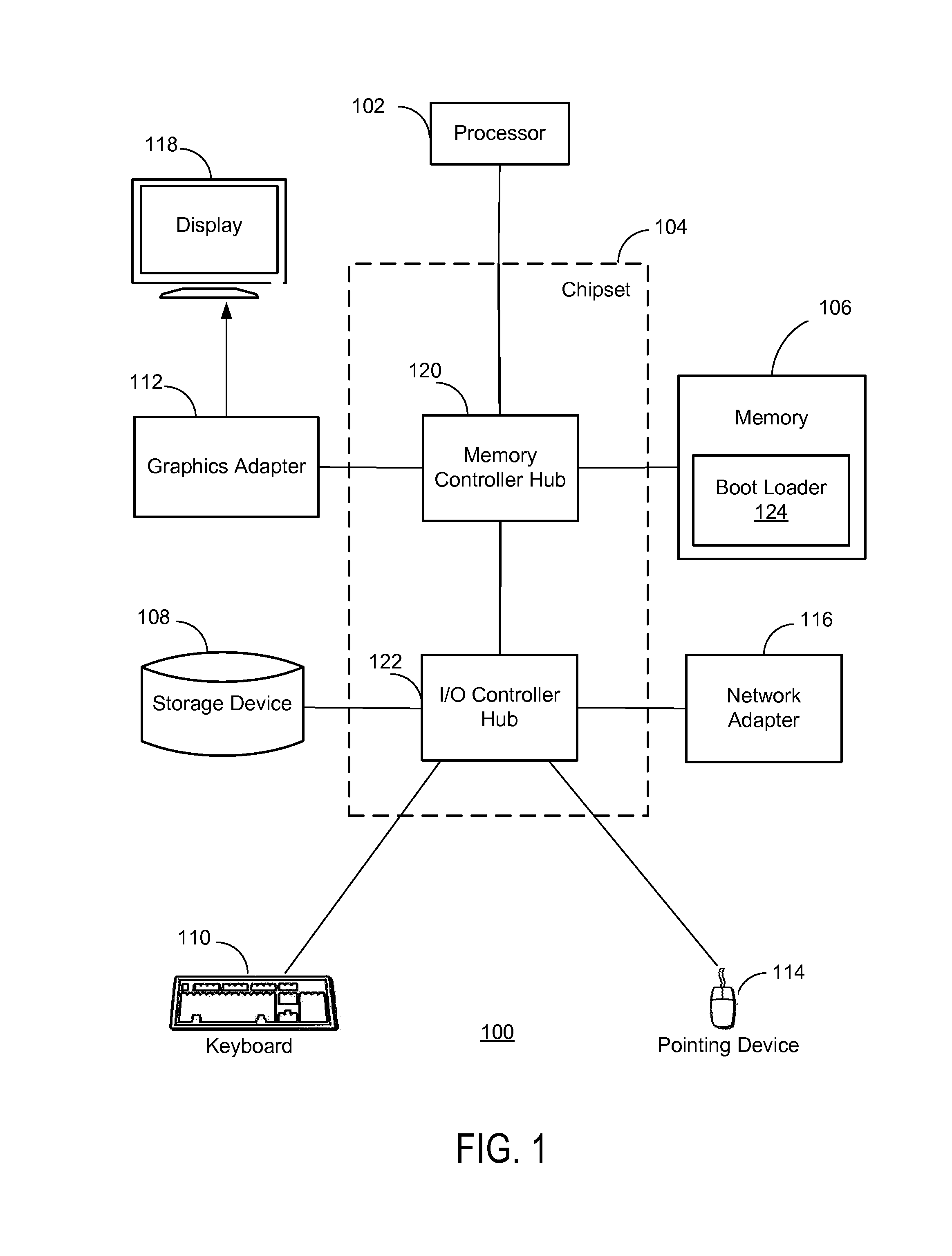

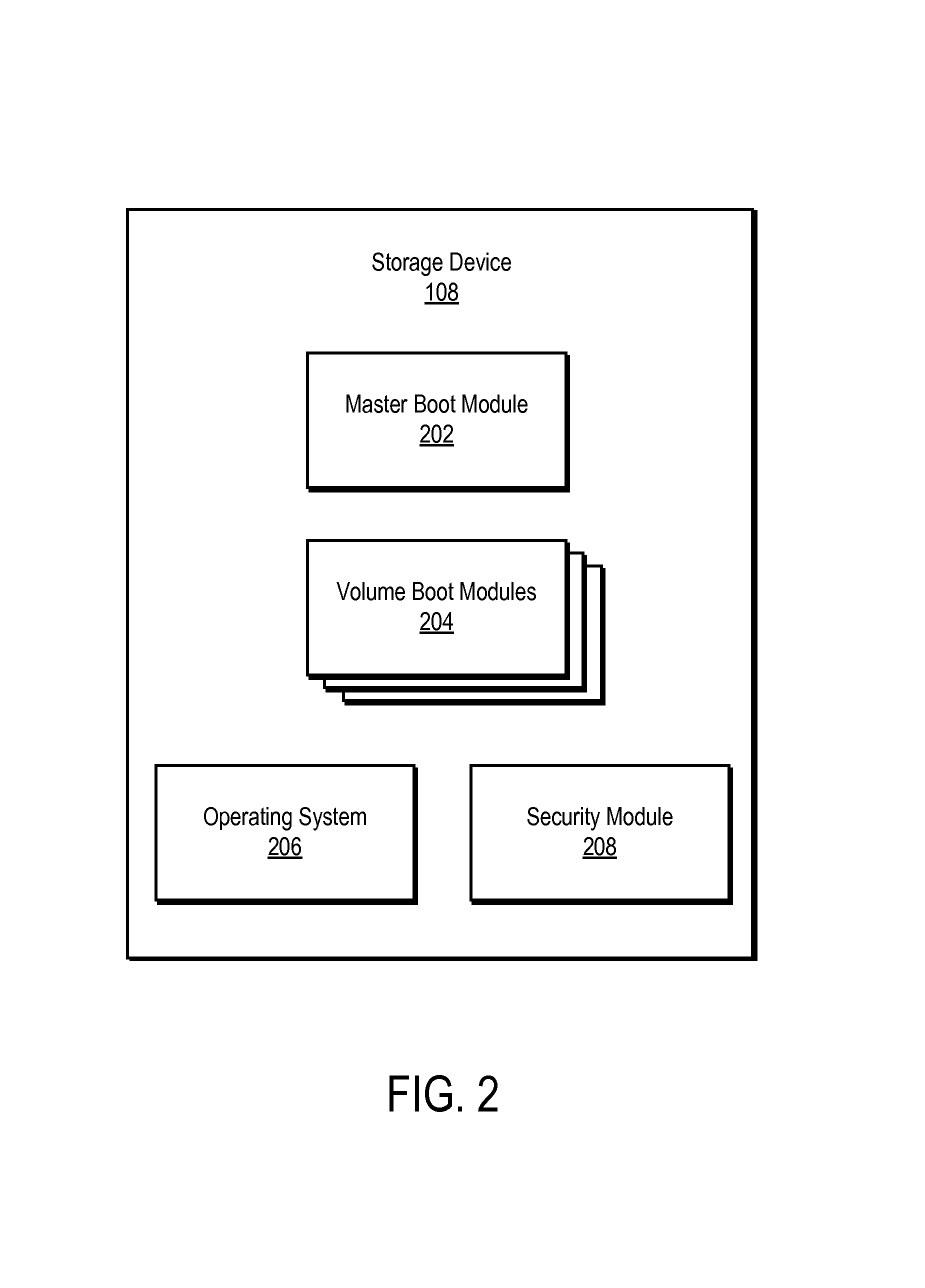

Detecting and repairing master boot record infections

Security is provided for a client by replacing a volume boot module adapted to execute during a boot process of the client with a repair module. The client is booted to start the boot process and to execute a master boot module. The repair module is executed in place of the volume boot module. The repair module determines whether the master boot module is infected with malware. If the master boot module is infected, the repair module repairs the malware infection by disabling and / or removing the malware.

Owner:CA TECH INC

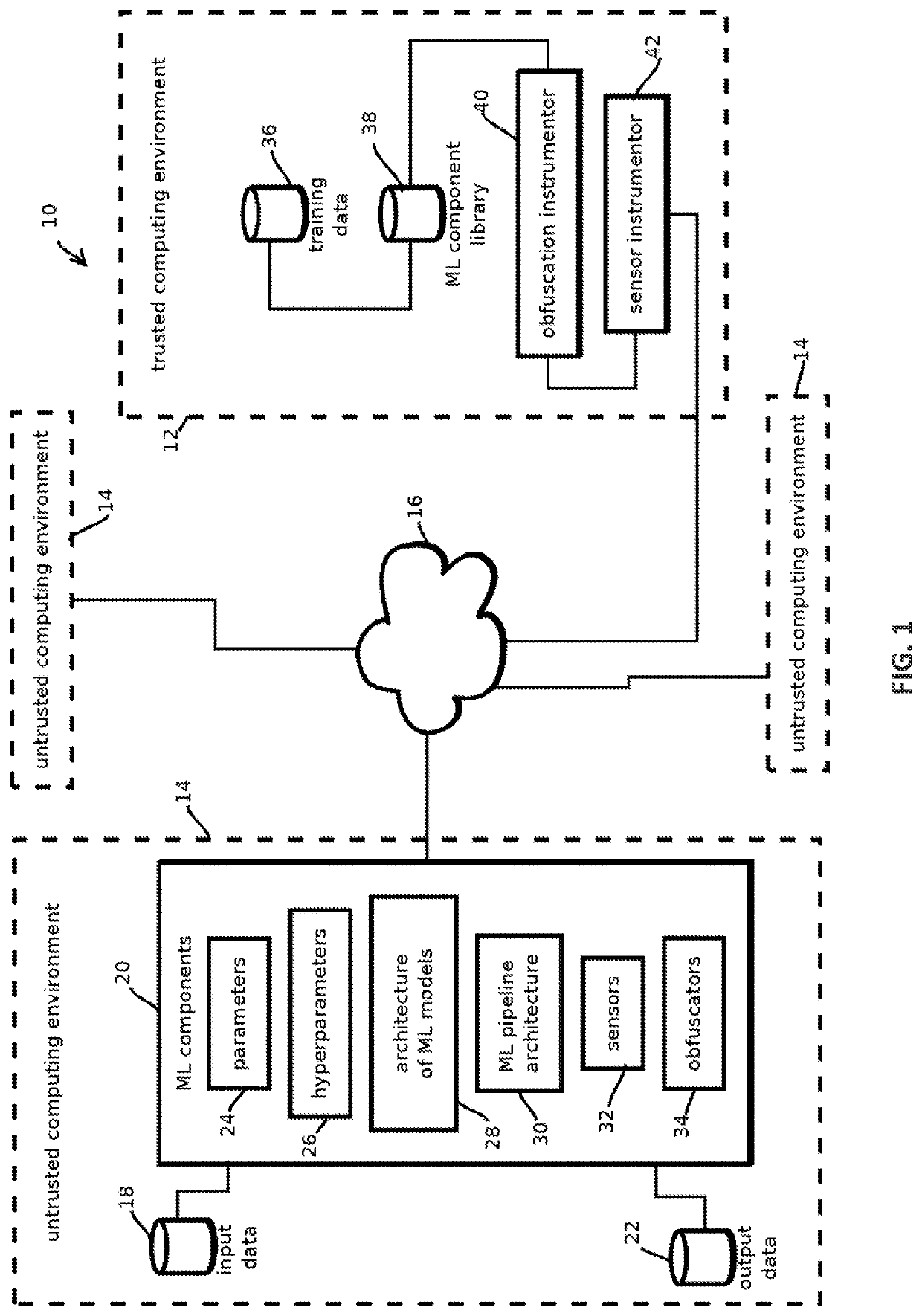

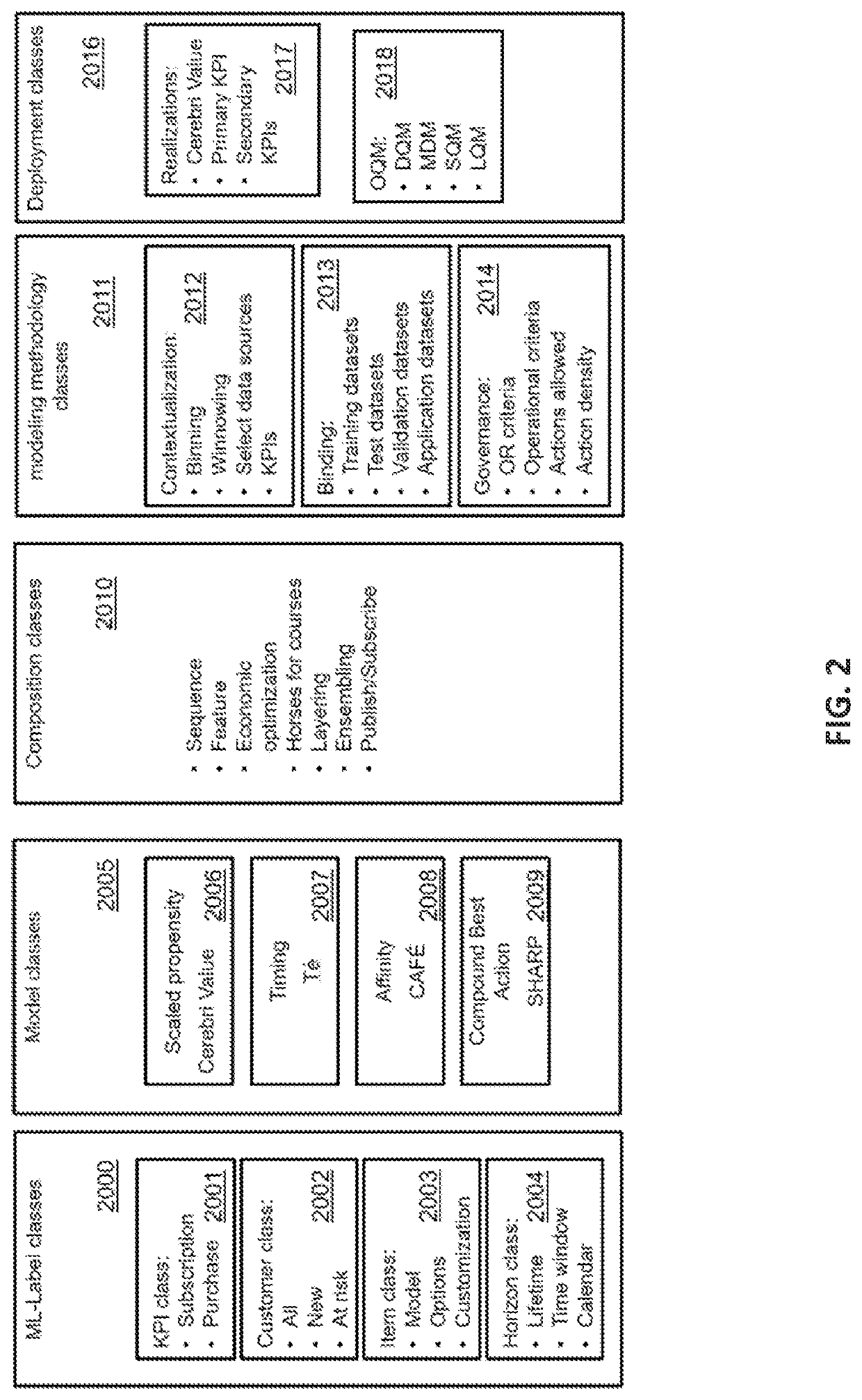

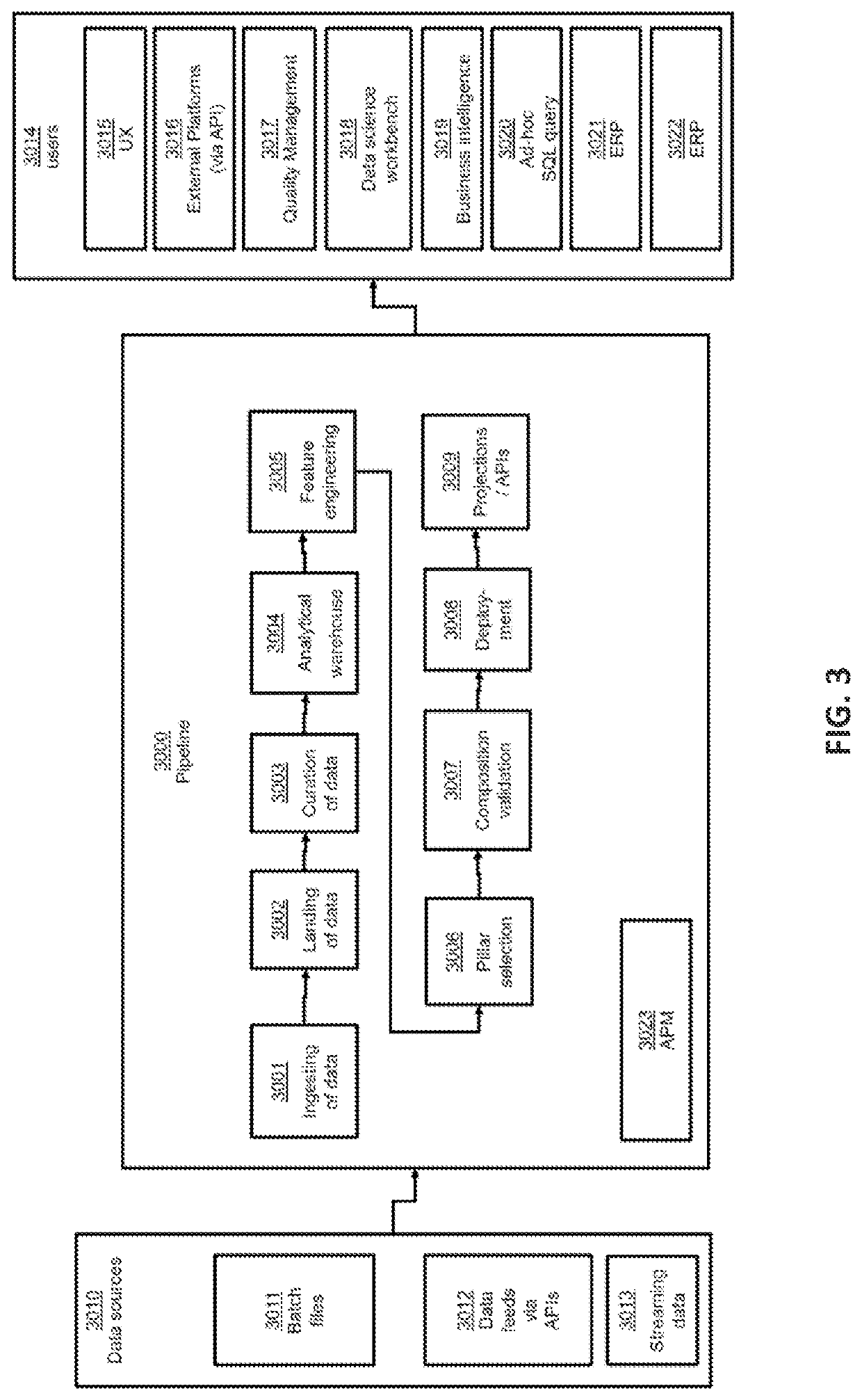

Auditable secure reverse engineering proof machine learning pipeline and methods

PendingUS20210342490A1Mathematical modelsInternal/peripheral component protectionExecute in placeTheoretical computer science

Provided is a process including: searching code of a machine-learning pipeline to find a first and a second object code sequences performing similar tasks; modifying the code of the machine learning pipeline by inserting a third object code sequence into the code of the machine learning pipeline, the third code sequence being operable to pass control to the first object code sequence; inserting a branch at the end of the first code sequence, the branch being operable to: pass control, upon detection of a first predefined condition, to an instruction following the first object code sequence, and to pass control, upon detection of a second predefined condition, to an instruction following the third object code sequence; and wherein the third code sequence is executed in place of the second object sequence without affecting completion of the tasks.

Owner:CEREBRI AI INC

System and method for executing binary images

InactiveUS20060101194A1Less and less working RAMProgram loading/initiatingMemory systemsComputer hardwareOperational system

Owner:MICROSOFT TECH LICENSING LLC

Flash memory for code and data storage

ActiveUS9021182B2Memory architecture accessing/allocationMemory adressing/allocation/relocationHigh densityParallel computing

A flash memory for code and data storage includes a code memory array having fast read access and suitability for execute in place, a data memory array having the characteristics of low bit cost and high density storage, and a suitable interface to provide access to both the code and data. The code memory array may be a NOR array or a performance-enhanced NAND array. The memory may be implemented in a single chip package or multi-chip package solution.

Owner:WINBOND ELECTRONICS CORP

Safe execution in place (XIP) from flash memory

A device is provided that includes a processor, a flash memory configured to store error correcting code (ECC) blocks for execution in place (XIP) processing by the processor, wherein an ECC block includes a data block and an ECC code for the data block, a flash interface controller coupled to the flash memory, and an error correcting code (ECC) engine coupled between the processor and the flash interface controller, wherein the ECC engine is configured to receive a read command for the flash memory from the processor, to translate a read address to an ECC block address, to read the ECC block at the ECC block address from the flash memory via the flash interface controller, and to verify the ECC code in the read ECC block.

Owner:TEXAS INSTR INC

Apparatus and method for fast microcode patch from memory

InactiveUS20090031109A1Runtime instruction translationGeneral purpose stored program computerPatch arrayOperating system

A microcode patch apparatus including a patch array, a mux, and a RAM. The patch array receives a microcode ROM address and determines that the microcode ROM address matches one of a plurality of entries within the patch array. The patch array outputs a corresponding branch instruction and asserts a hit signal. The branch instruction prescribes a microcode branch target address. The mux receives the branch instruction from the patch array and a micro instruction corresponding to the microcode ROM address from a microcode ROM. The mux provides the micro instruction or the corresponding branch instruction to an instruction register based upon the state of the hit signal. The RAM stores a plurality of patch instructions that are to be executed in place of the micro instruction. The first one of the plurality of patch instructions is stored at a location in the RAM corresponding to the microcode branch target address.

Owner:VIA TECH INC