Patents

Literature

56 results about "FOUNDATION fieldbus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Foundation Fieldbus (styled Foundation Fieldbus) is an all-digital, serial, two-way communications system that serves as the base-level network in a plant or factory automation environment. It is an open architecture, developed and administered by FieldComm Group.

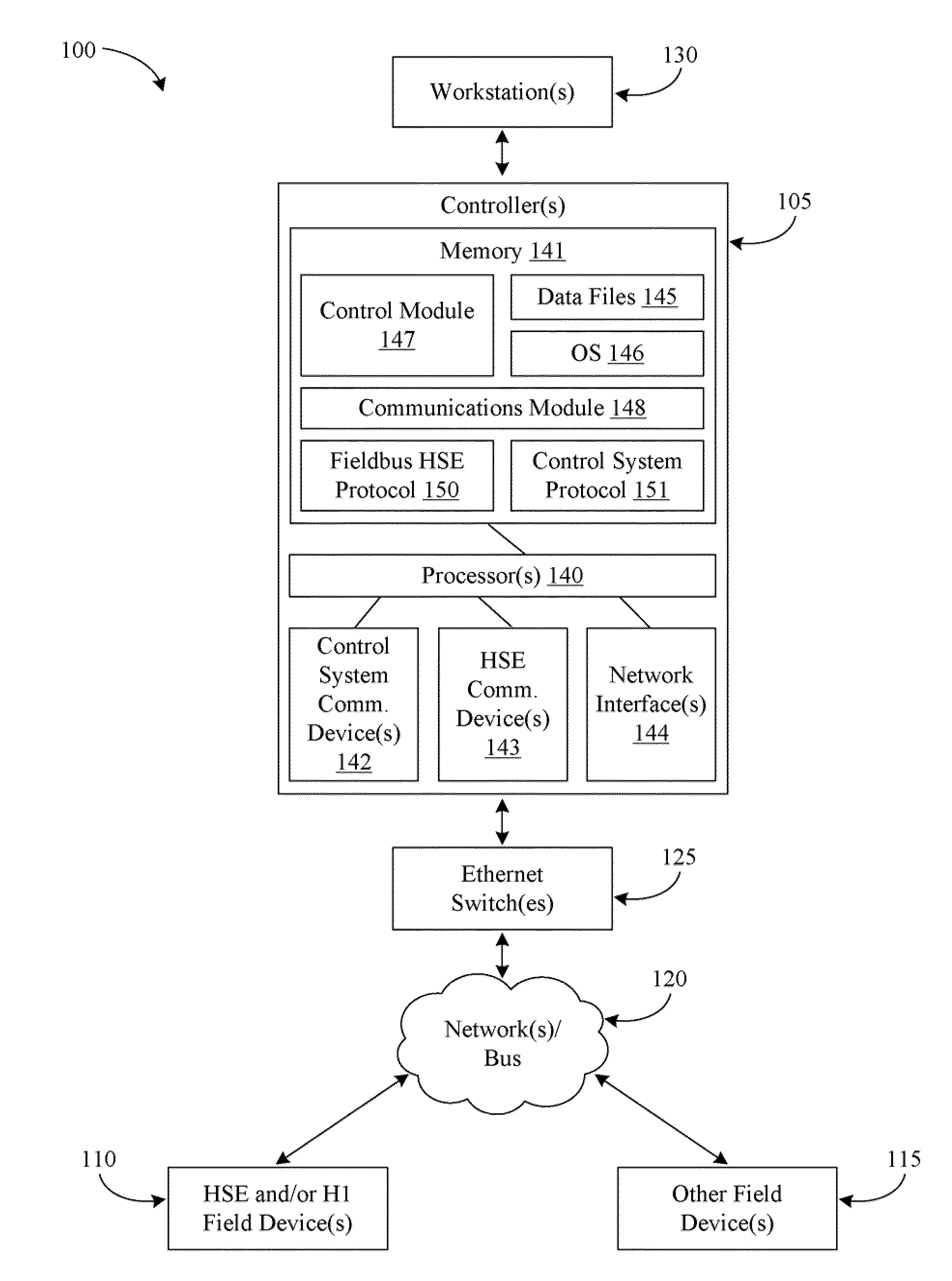

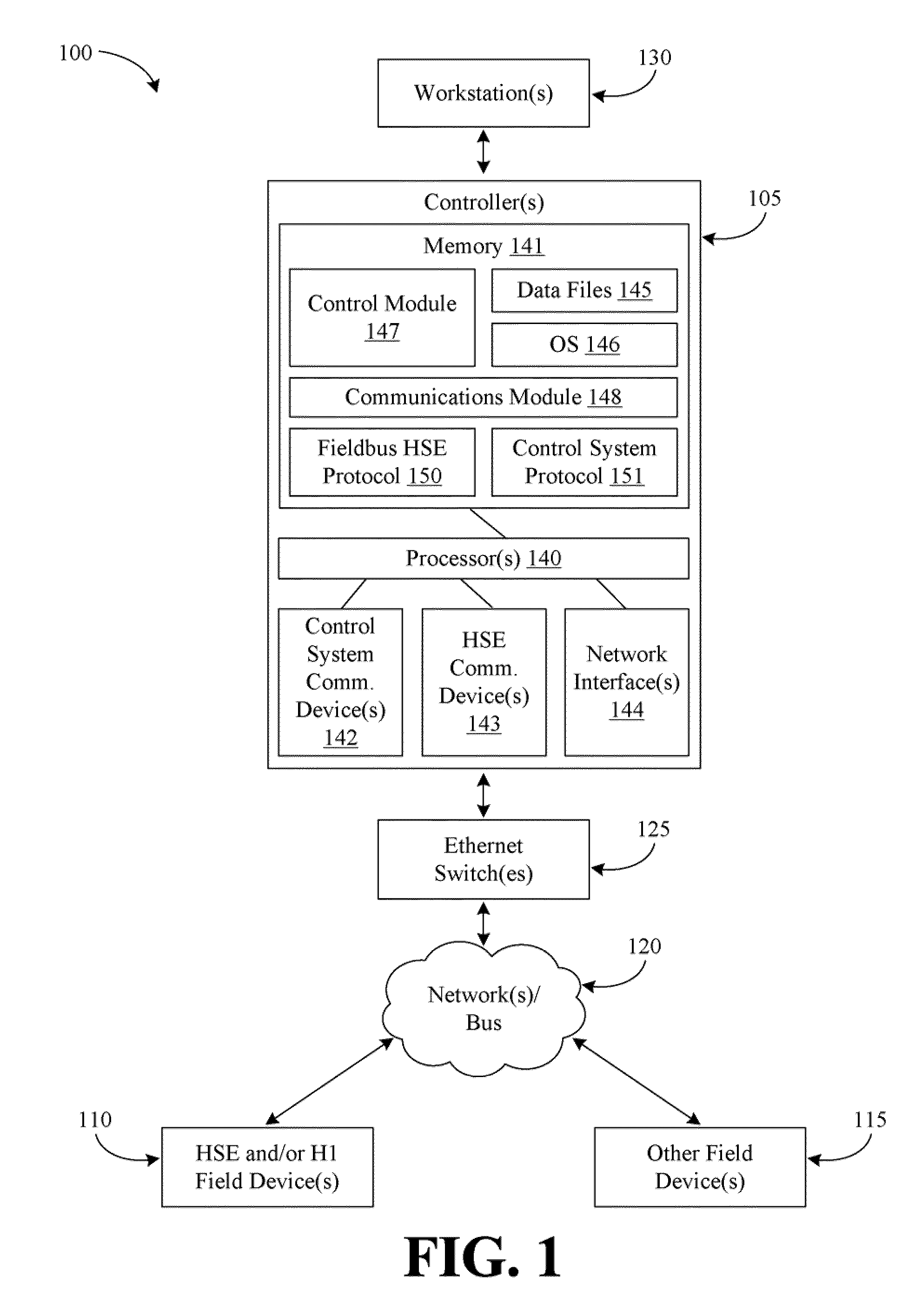

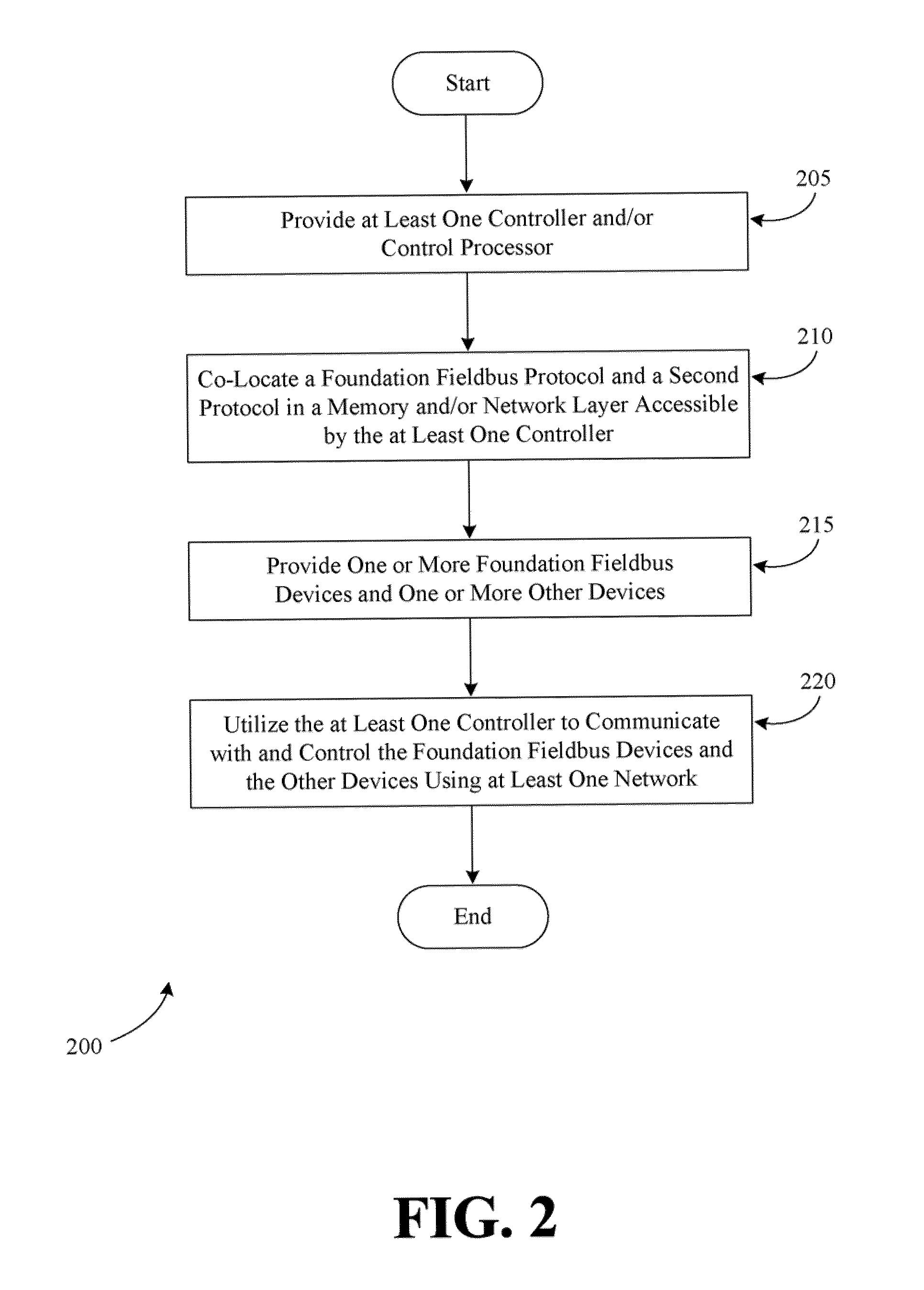

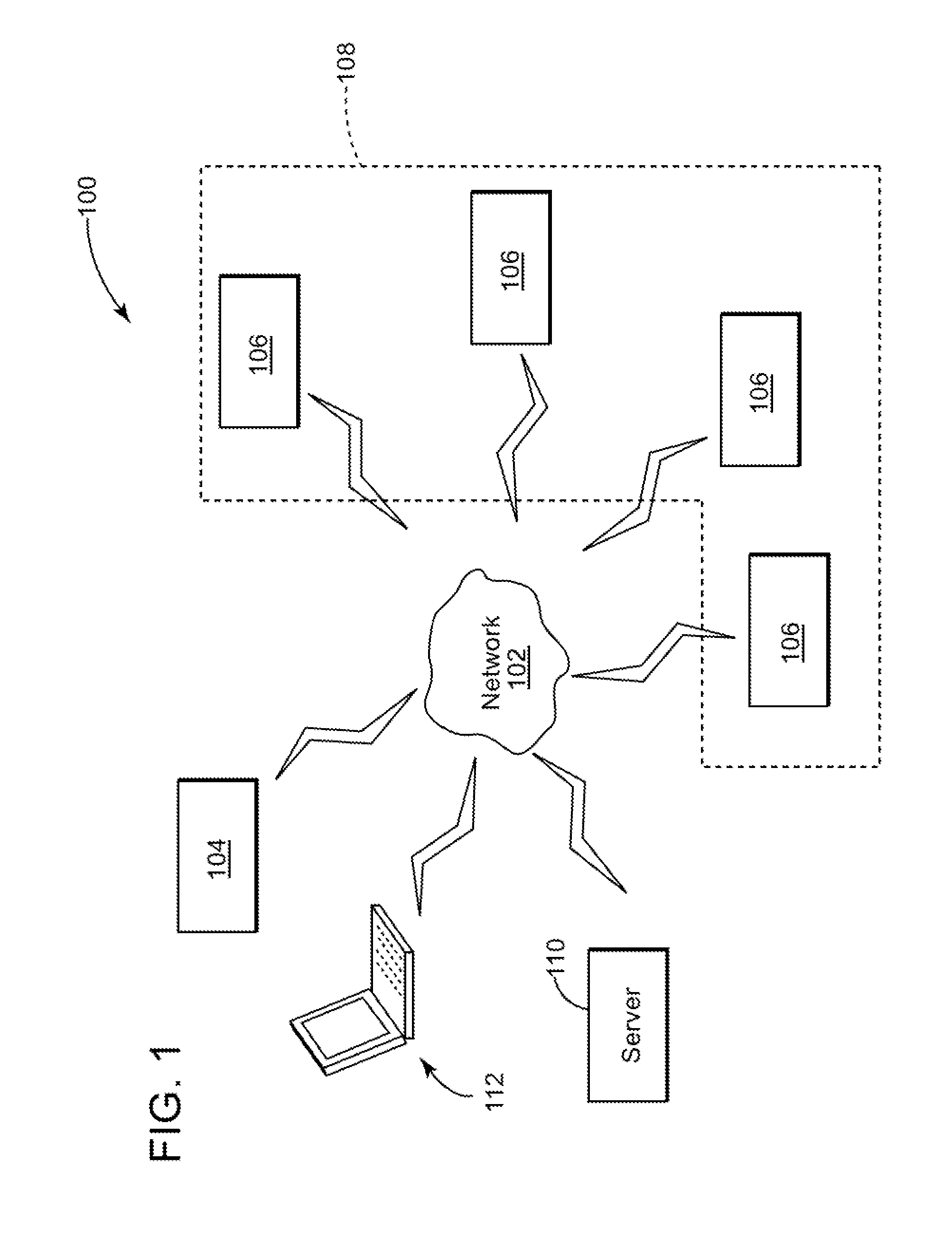

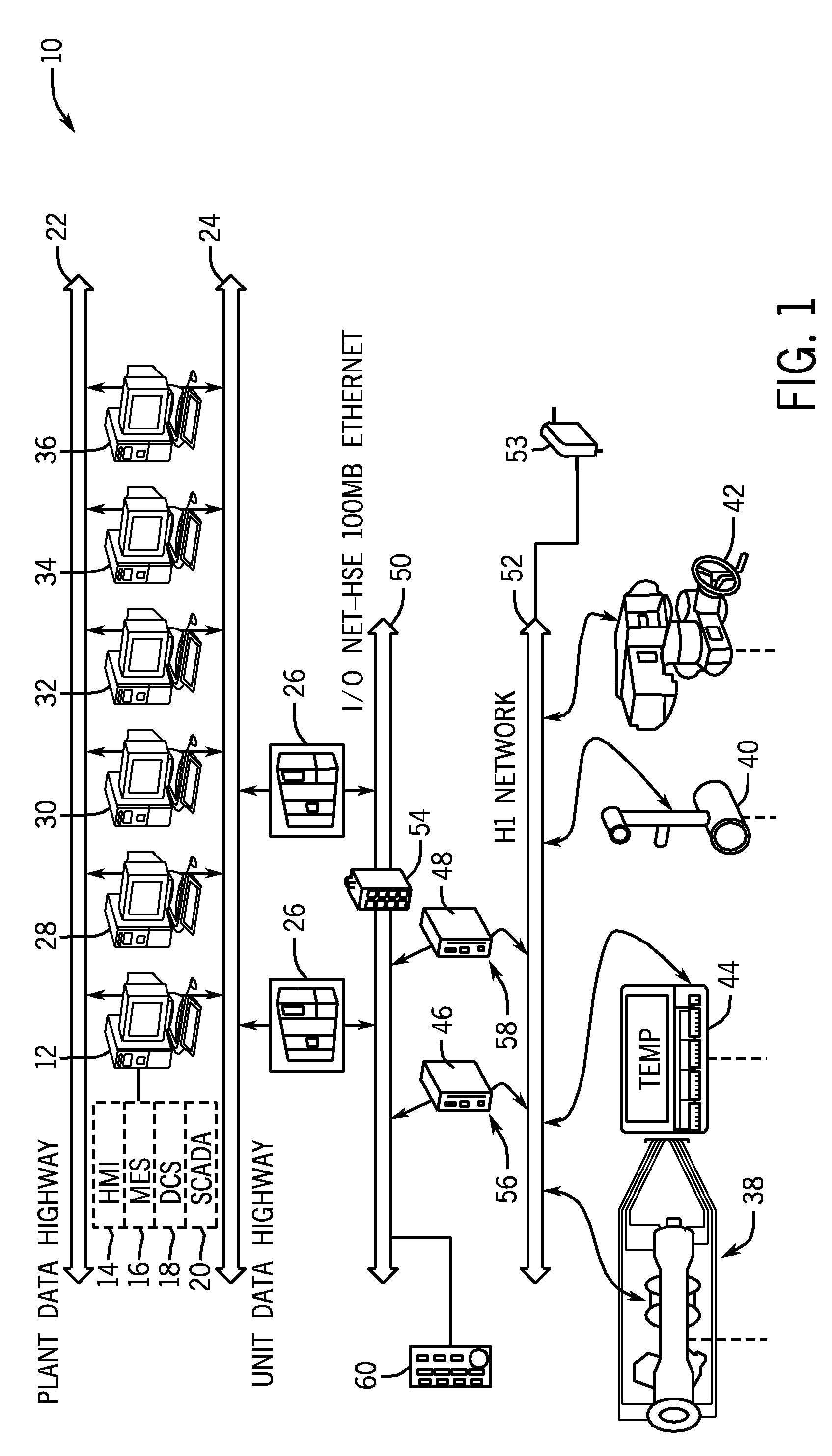

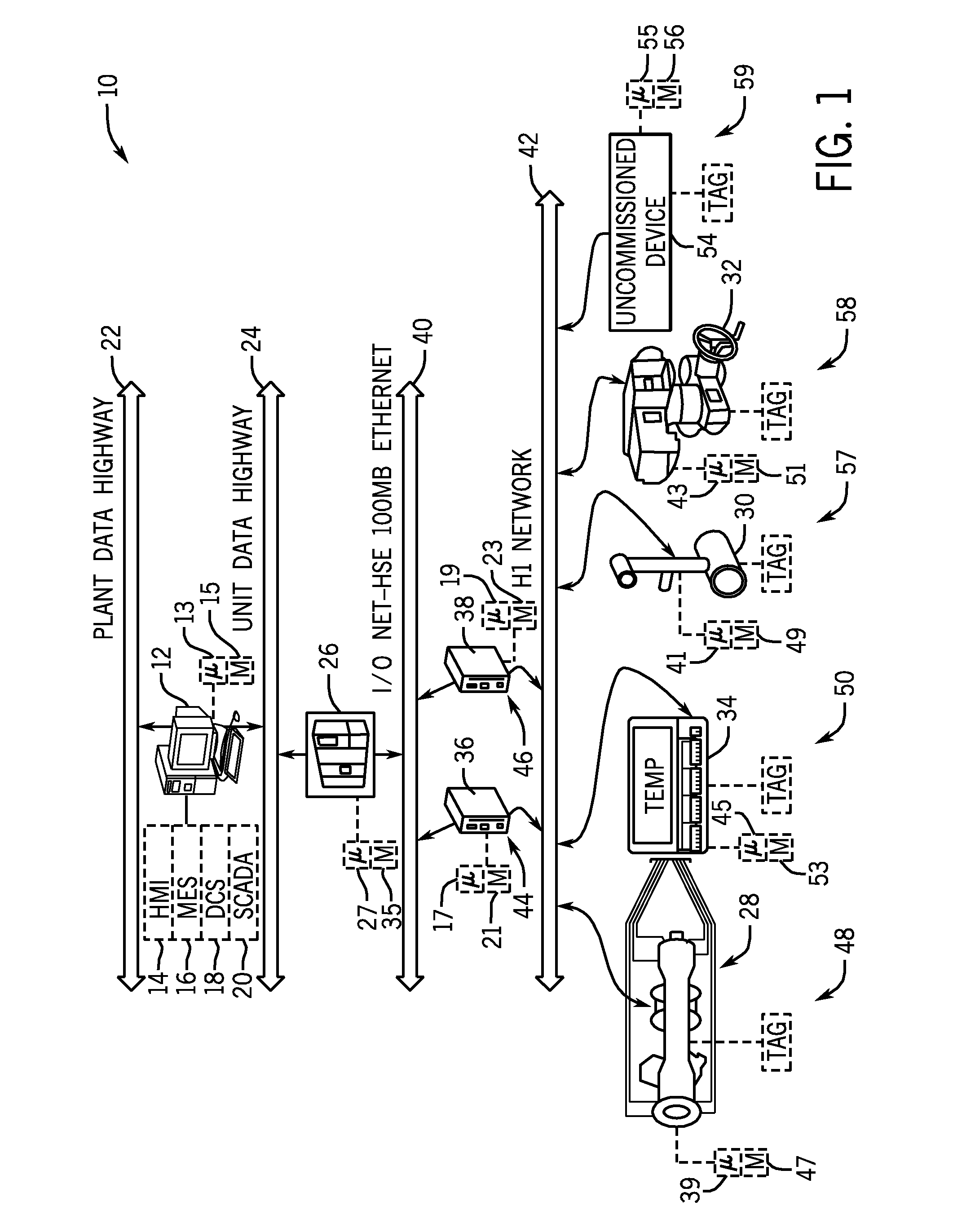

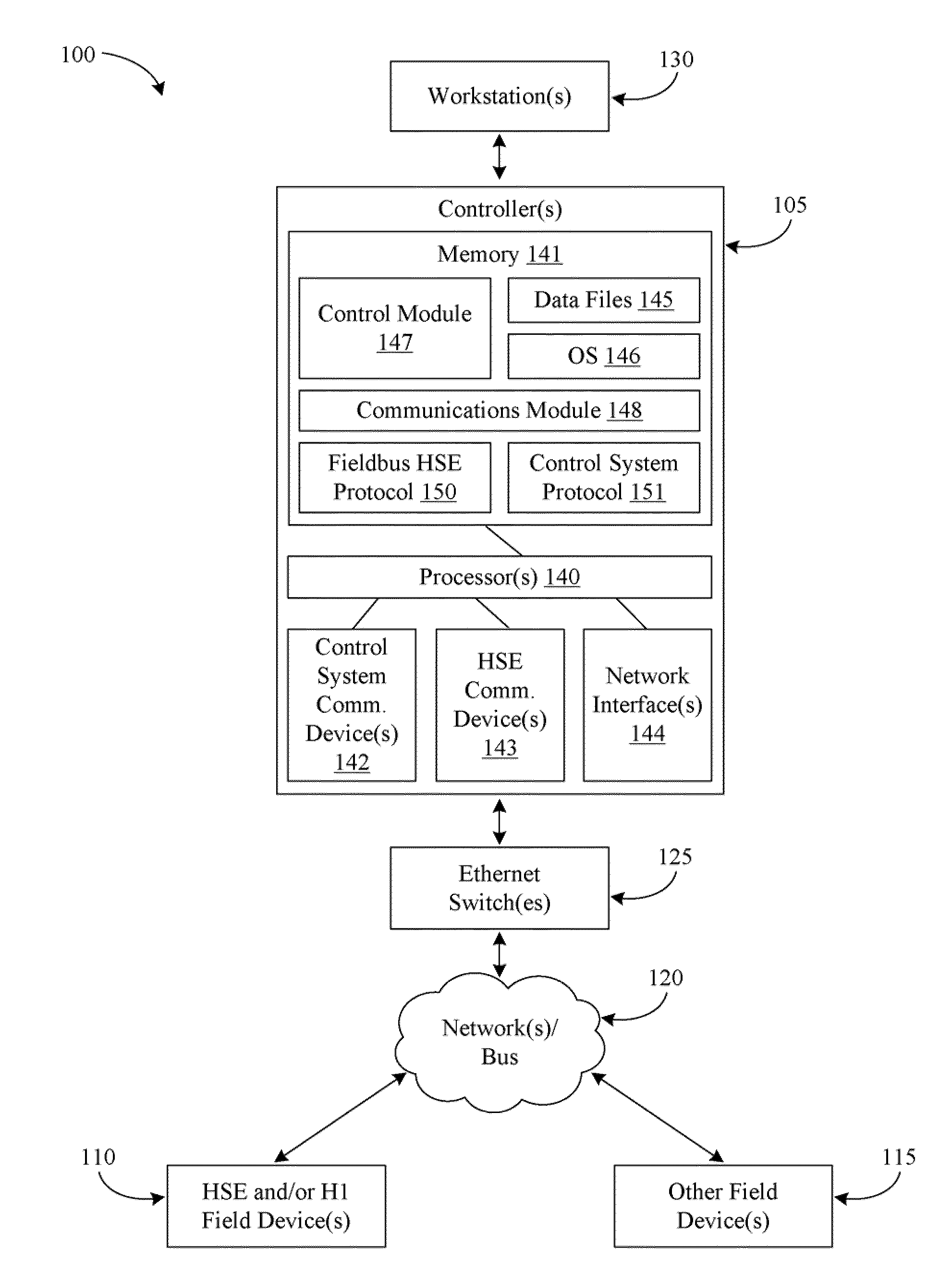

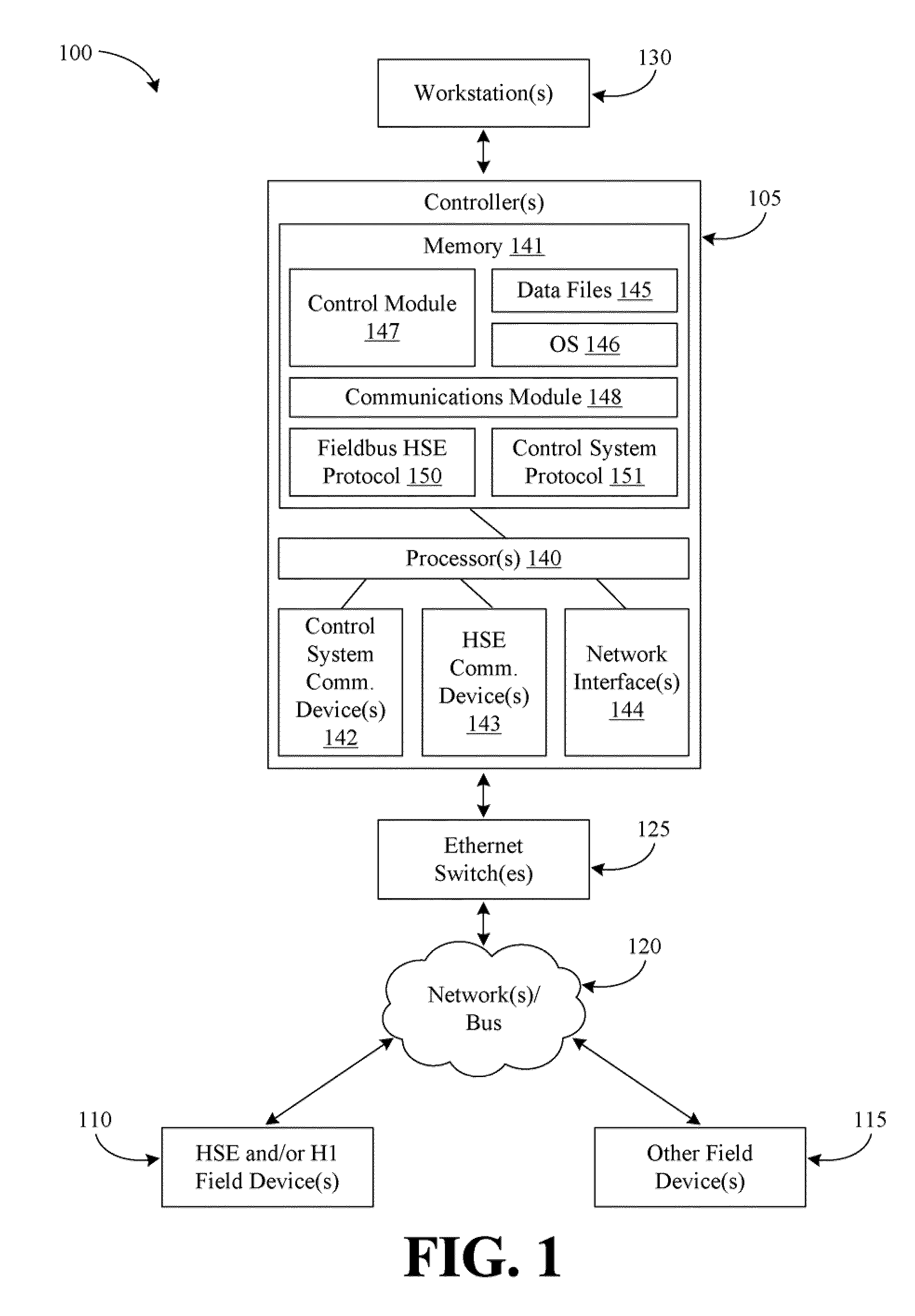

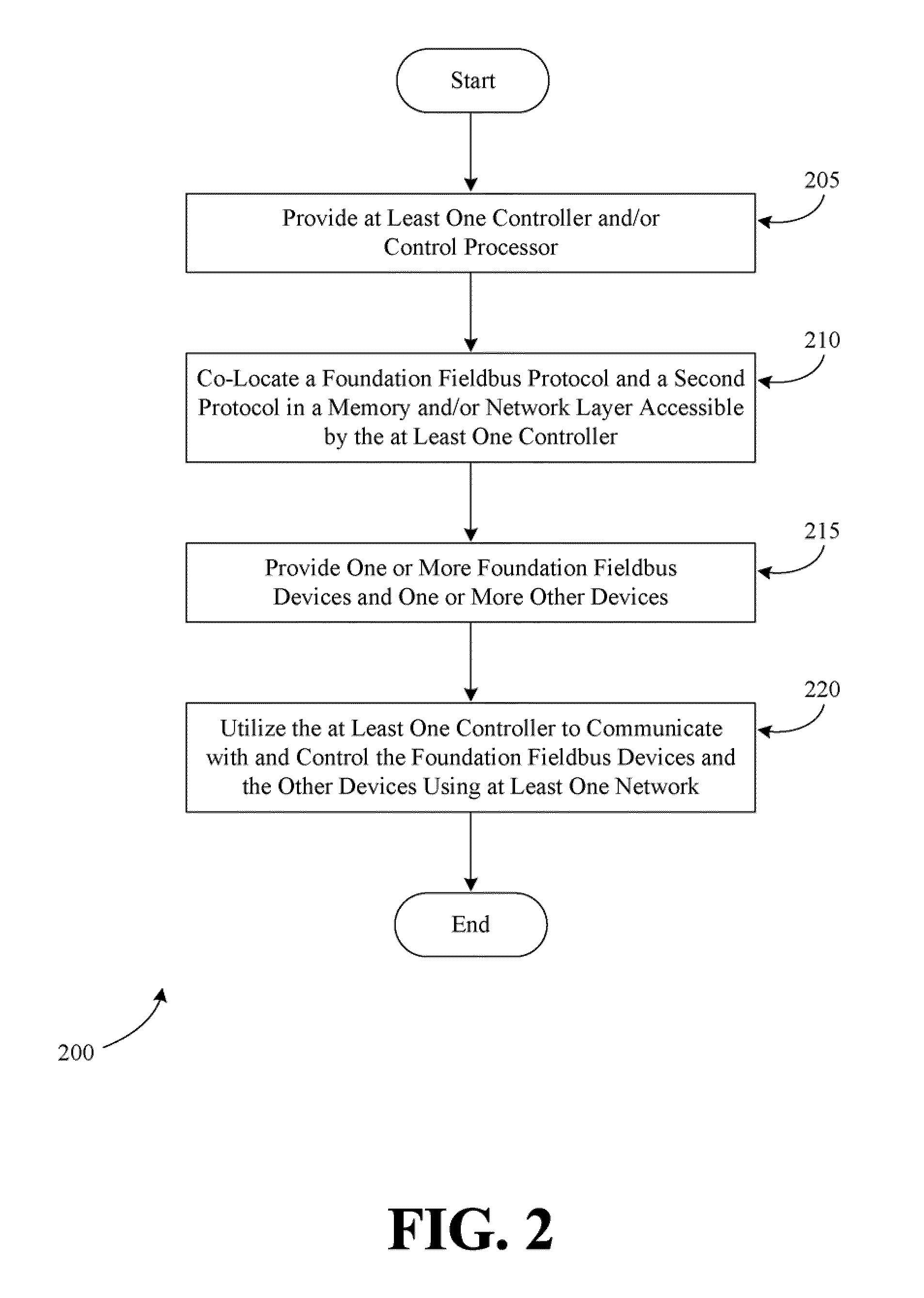

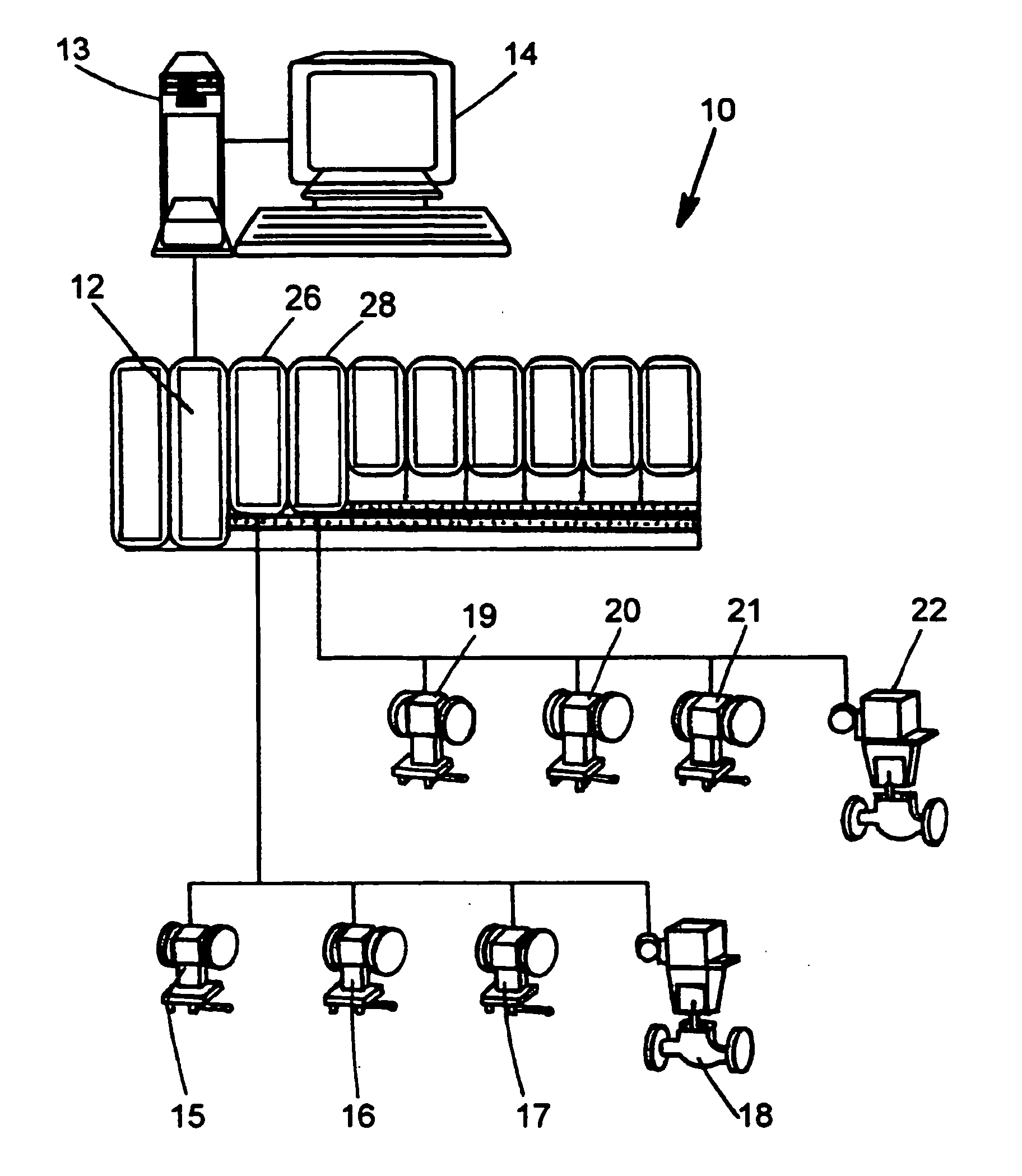

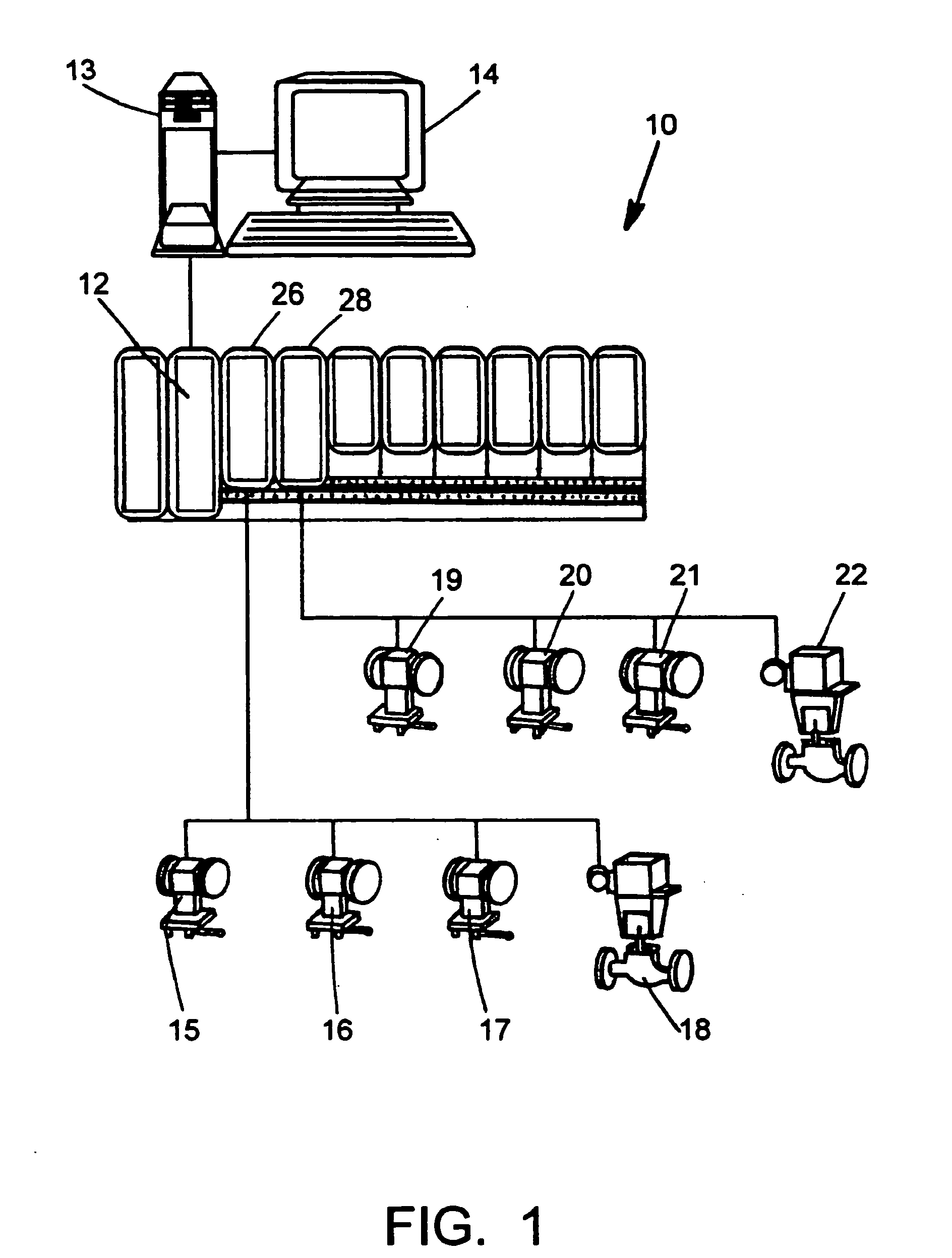

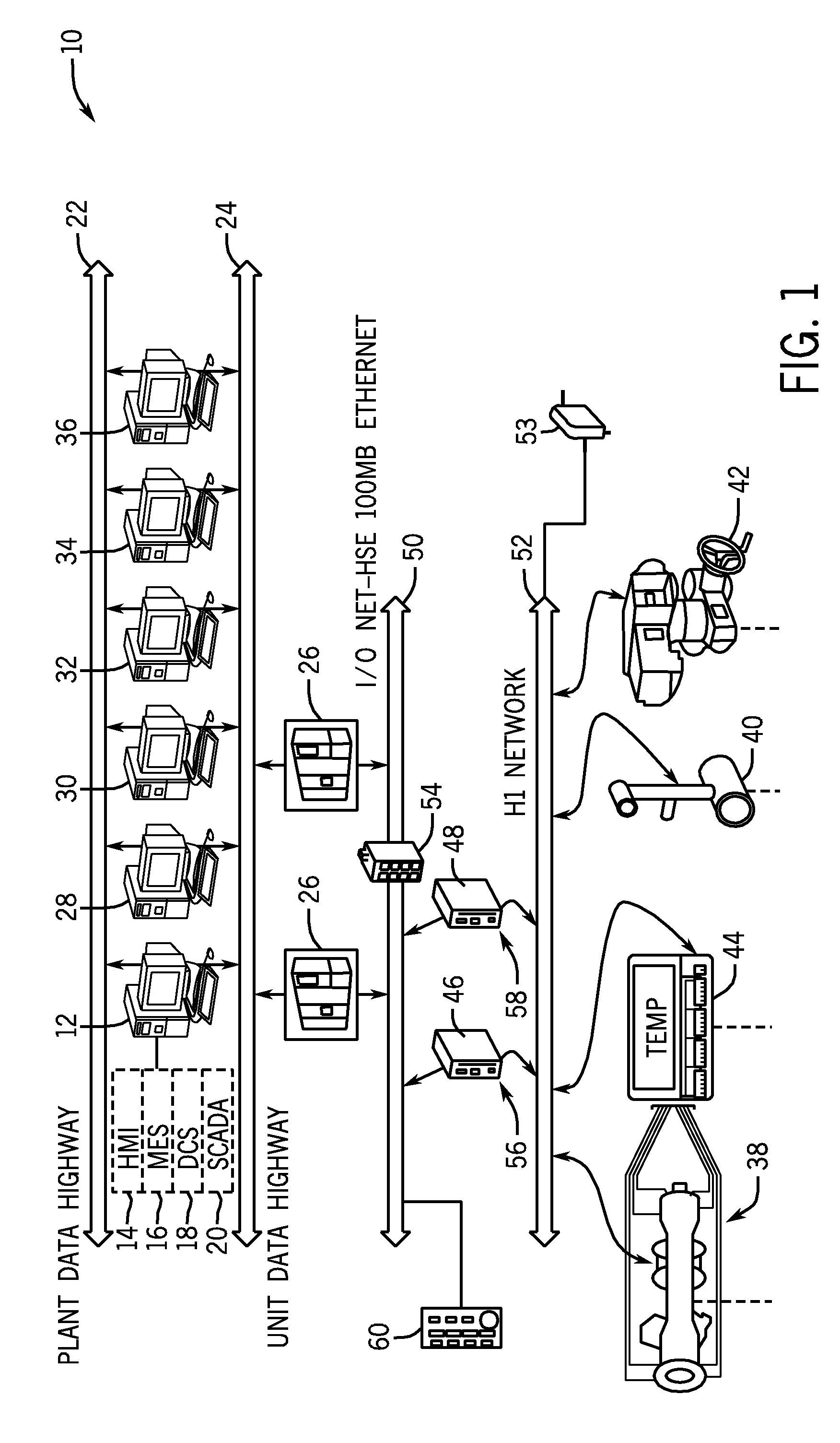

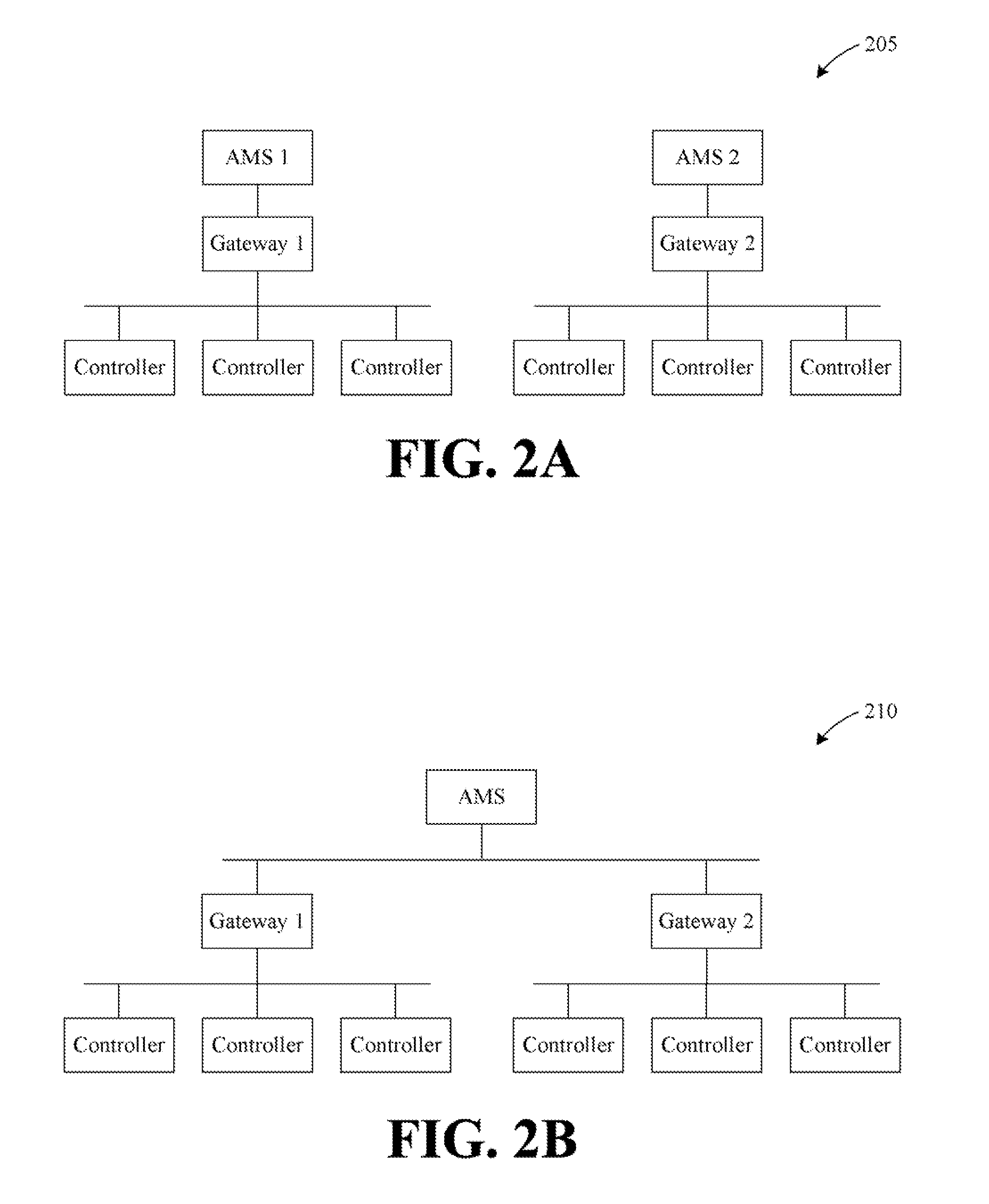

Control systems and methods of providing the same

ActiveUS8315718B2Facilitate communicationProgramme controlSafety arrangmentsControl systemComputer science

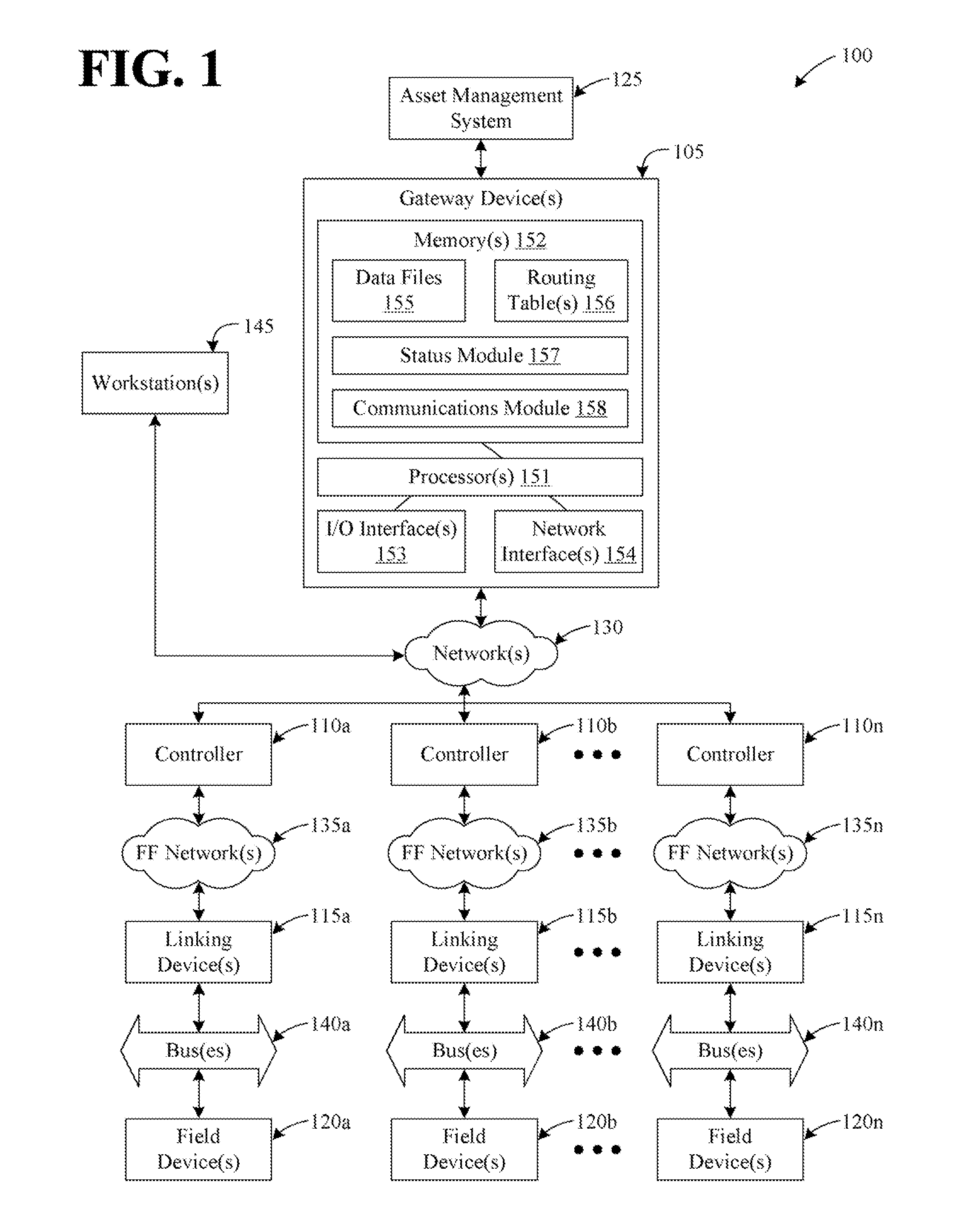

Control systems and methods for controlling certain systems, devices, and apparatus are described. A control system may include a memory and at least one processor. The memory may be operable to store both a Foundation Fieldbus protocol that facilitates communication with one or more Foundation Fieldbus devices and a second protocol that facilitates communication with one or more control devices. The at least one processor may be operable to access both the Foundation Fieldbus protocol and the second protocol, and to control the one or more Foundation Fieldbus devices and the one or more control devices. A network may facilitate communications between the at least one processor and both the one or more Foundation Fieldbus devices using the Foundation Fieldbus protocol and the one or more control devices using the second protocol.

Owner:GE INFRASTRUCTURE TECH INT LLC

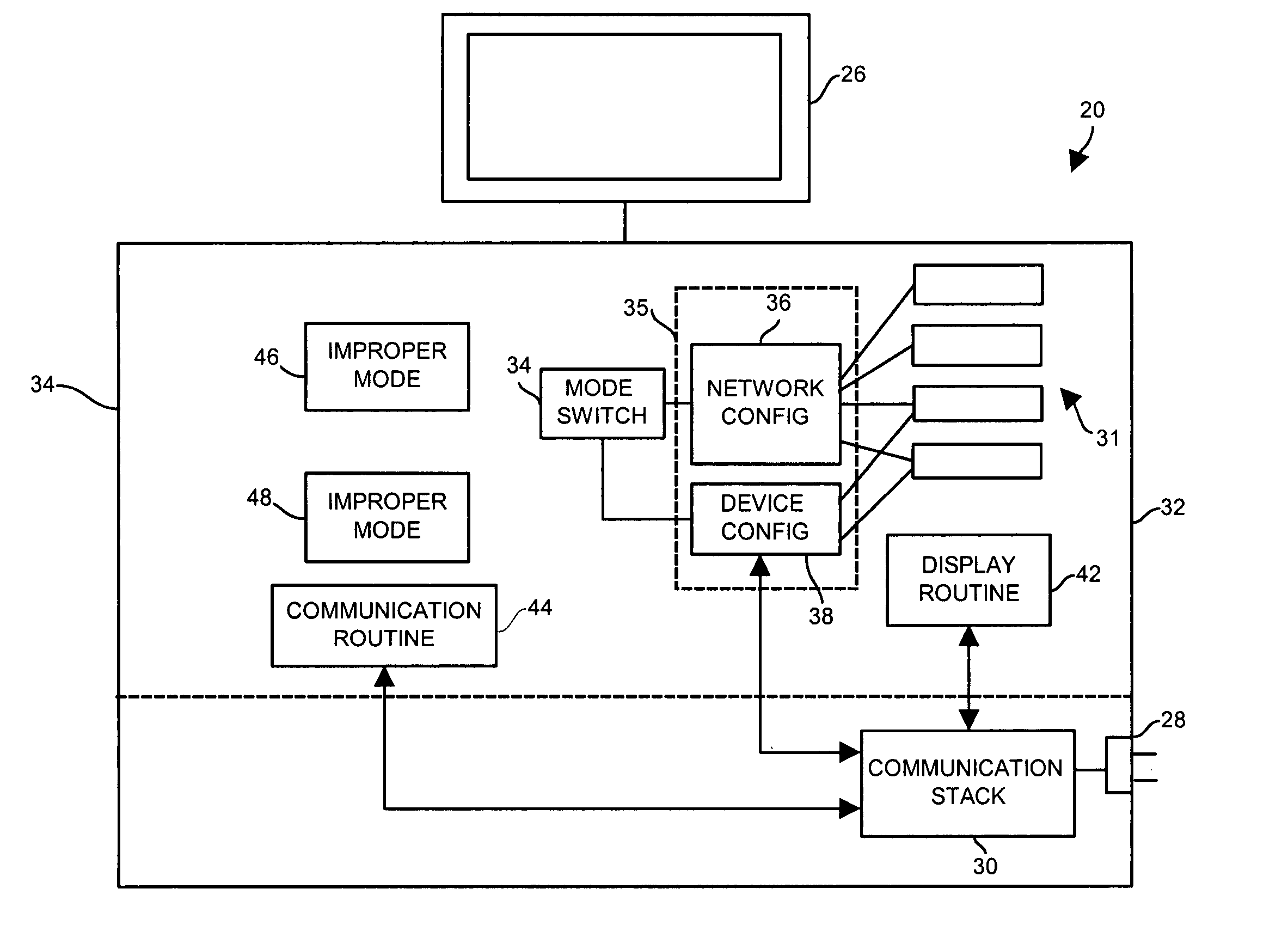

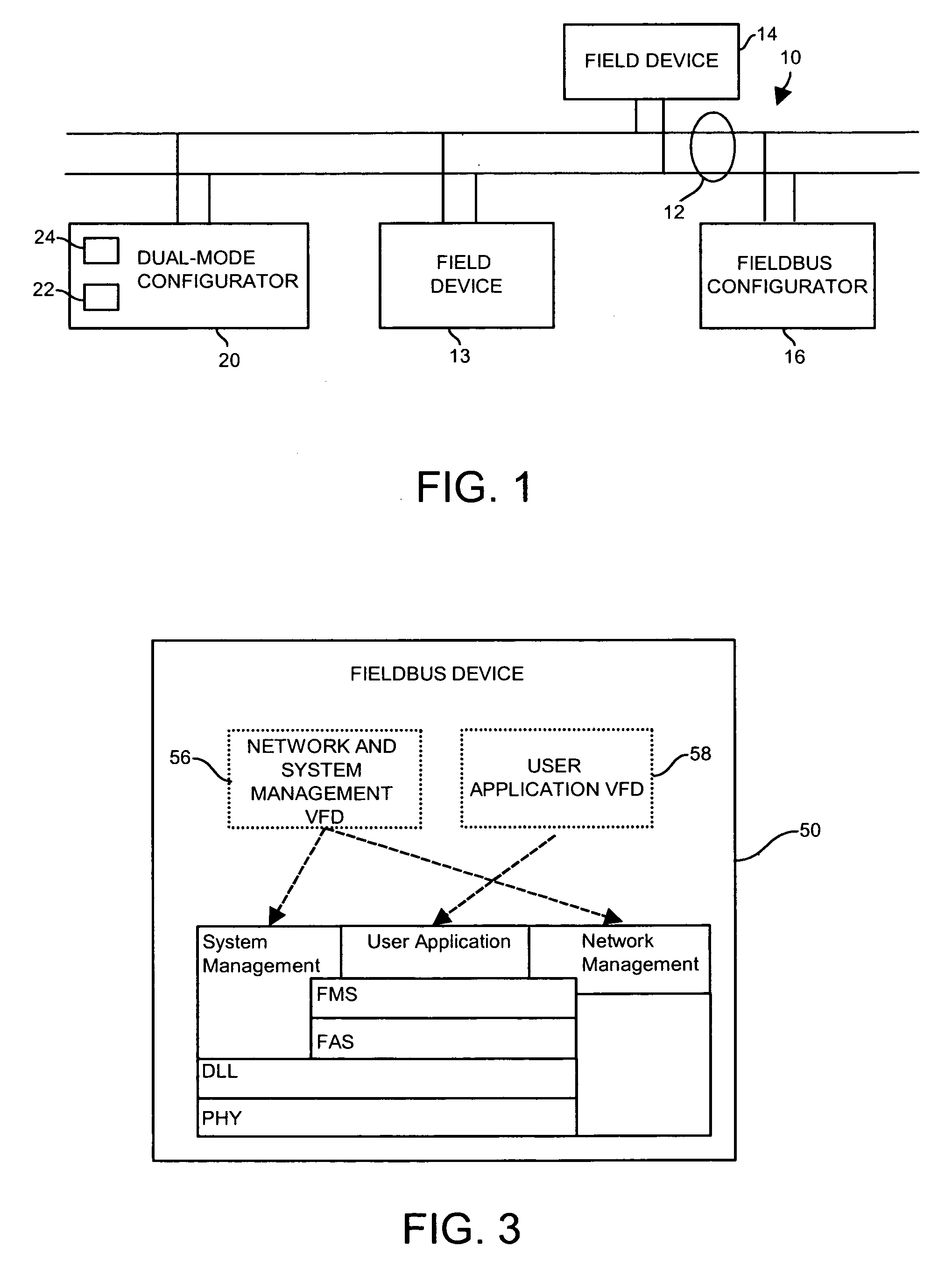

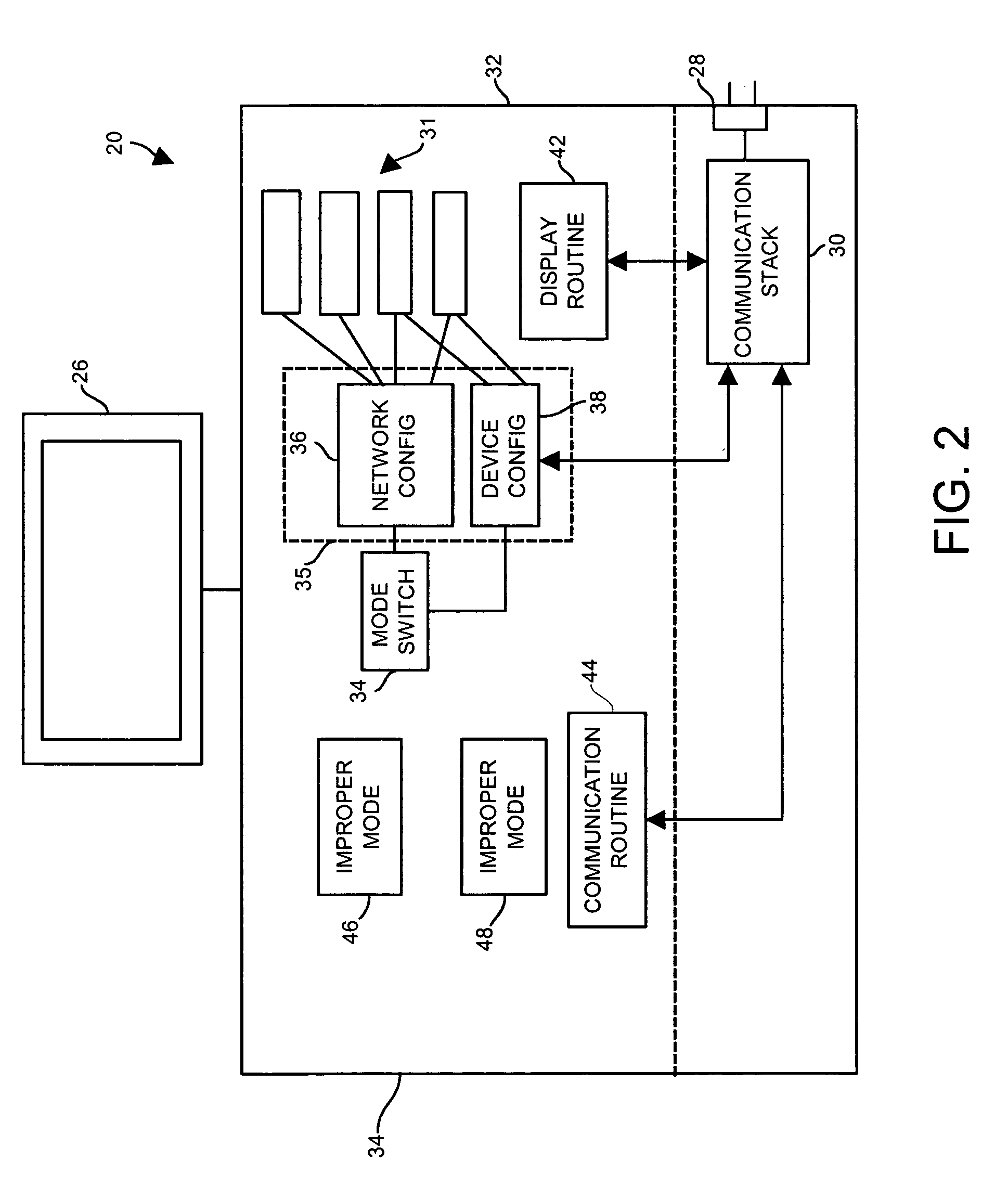

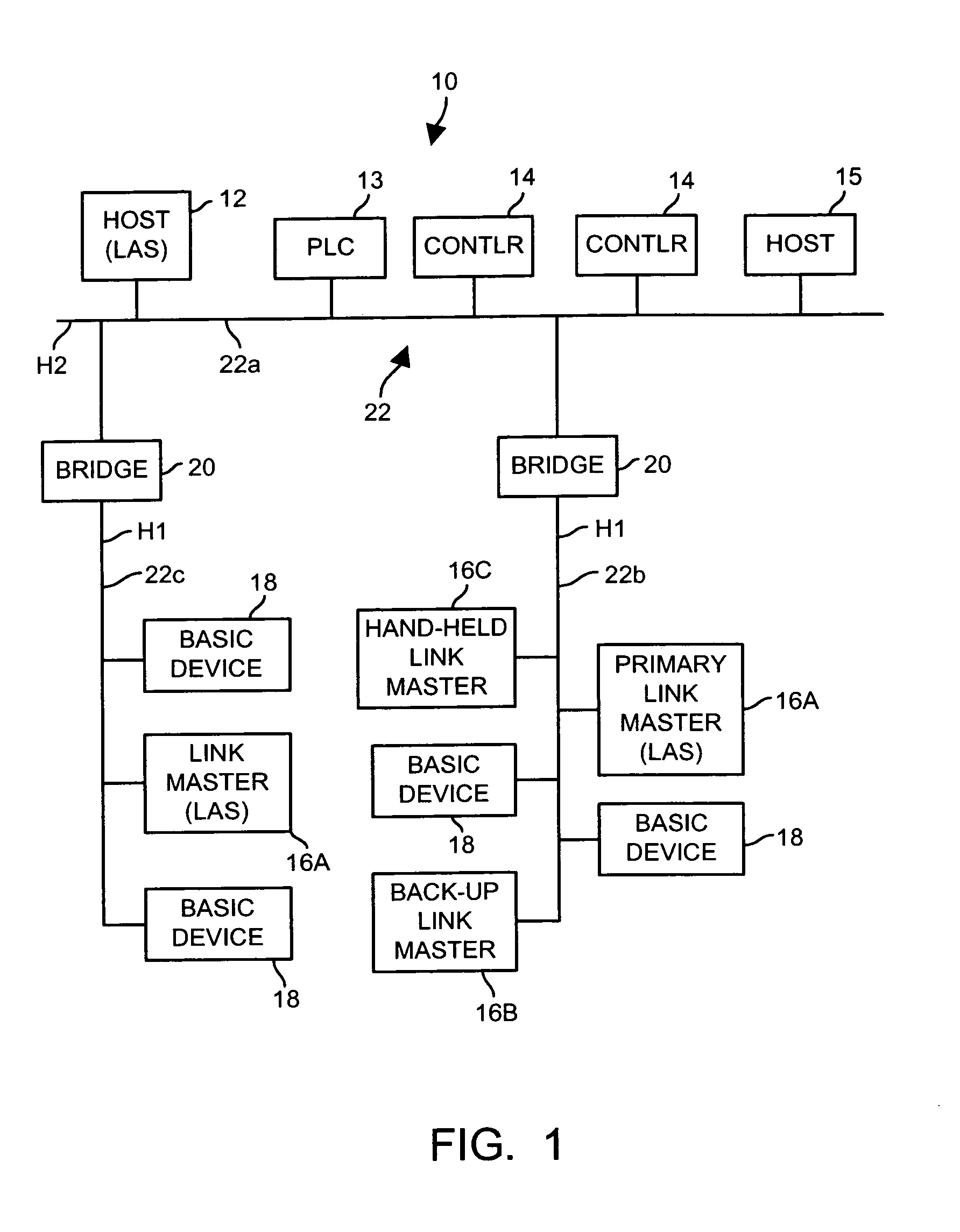

Two-mode foundation fieldbus device configurator

A dual mode configurator operates in an off-line mode to configure Fieldbus devices and / or segments in a typical manner and operates in an on-line mode to reconfigure or set certain parameters of a device when the device is connected to a segment controlled by a different host, without interfering with the on-line operation of the segment. The dual mode configurator can be used to configure an entire segment by configuring both network settings and device settings and, alternatively, can be used to configure device settings without effecting or interfering with the on-line system configuration information such as the network settings of a segment when, for example, a different host device or configuration device is connected to the segment to implement process control activities or to make segment changes.

Owner:FISHER-ROSEMOUNT SYST INC

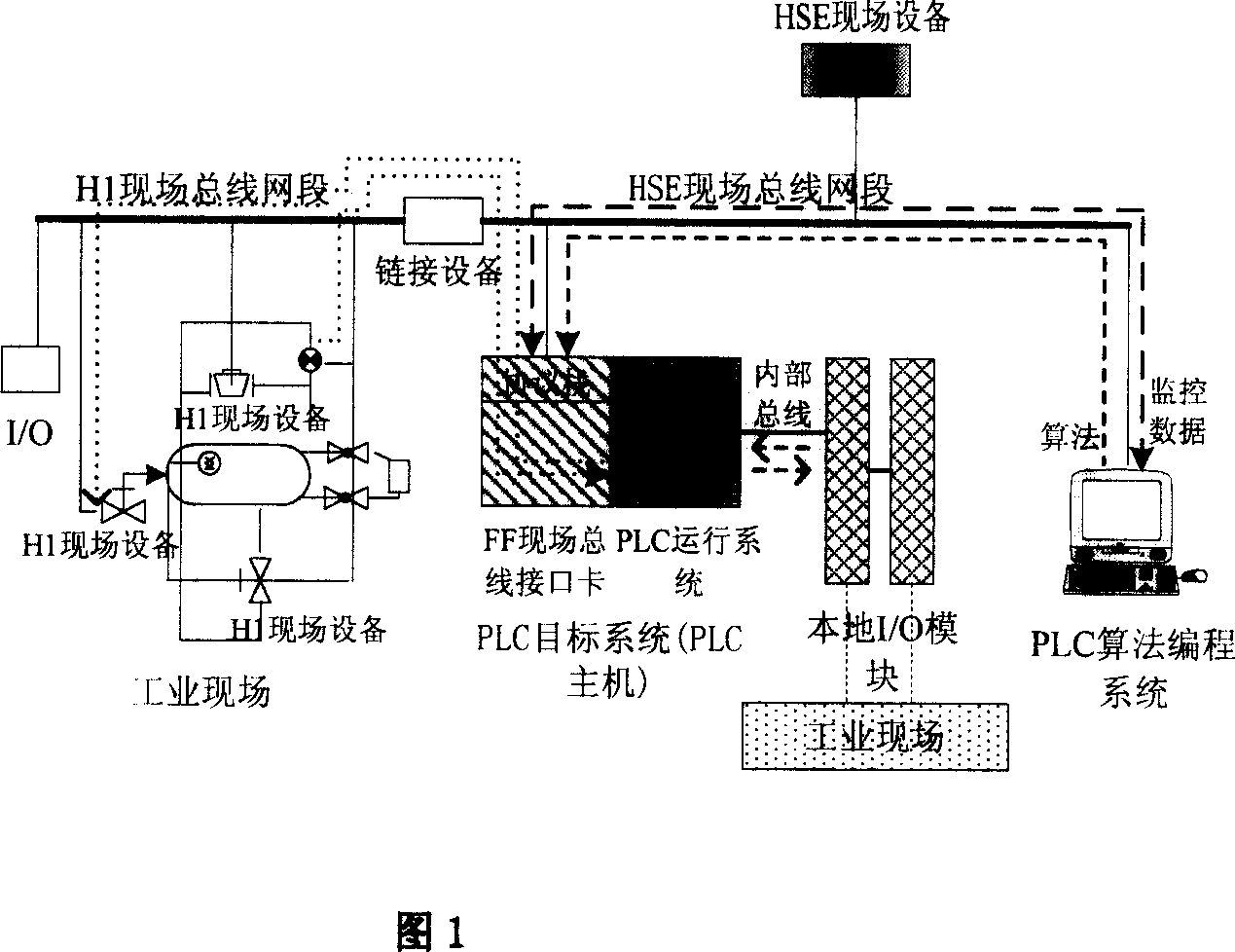

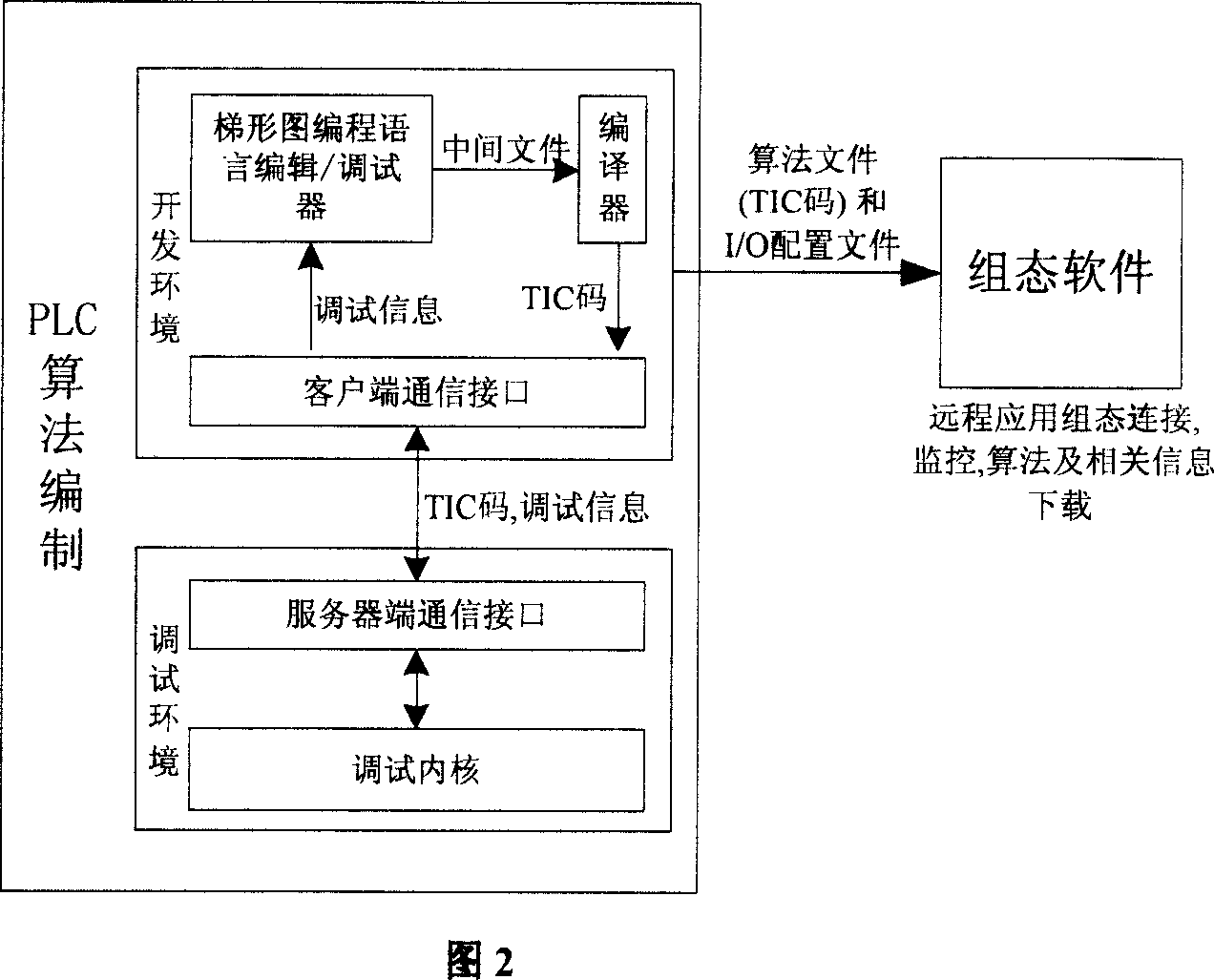

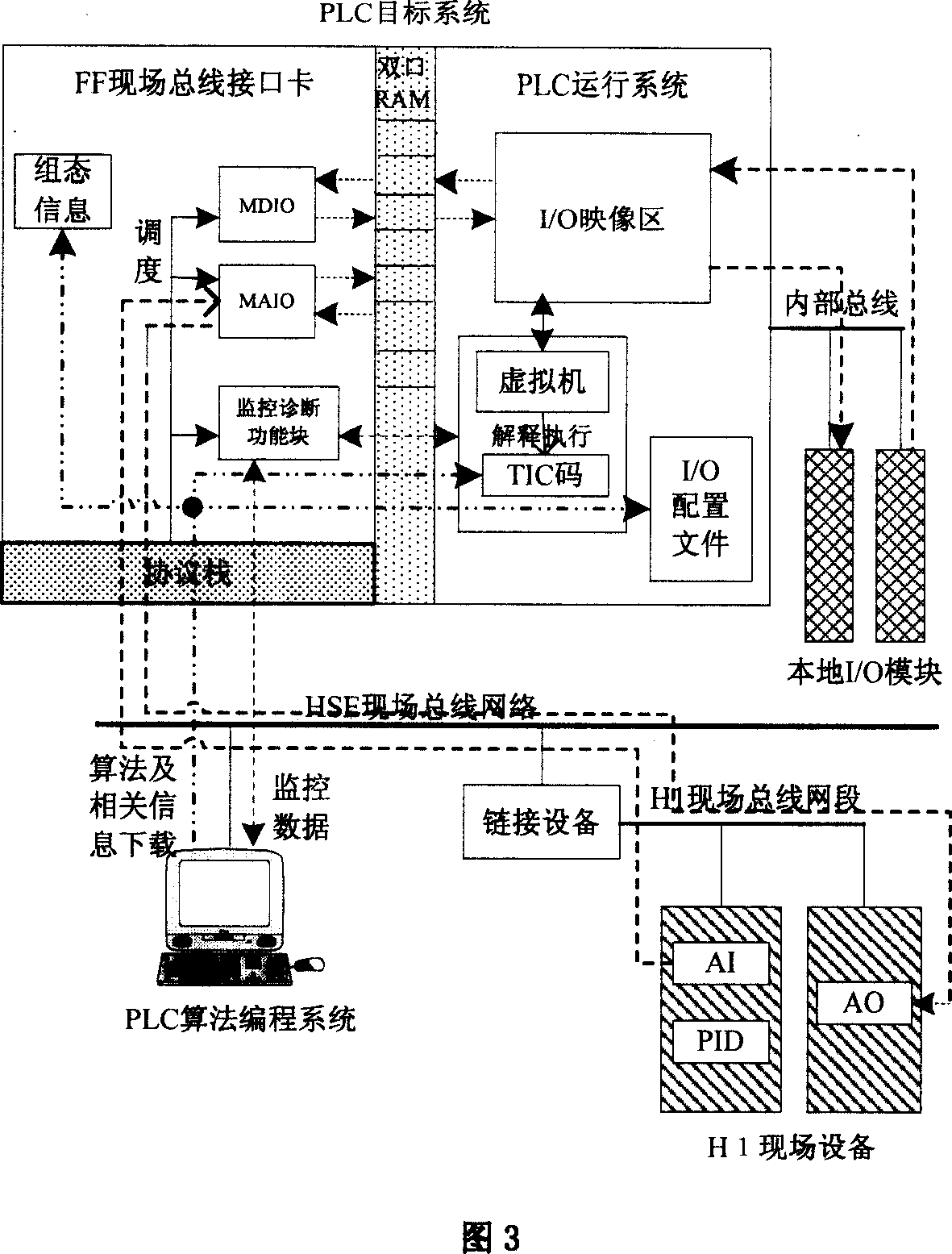

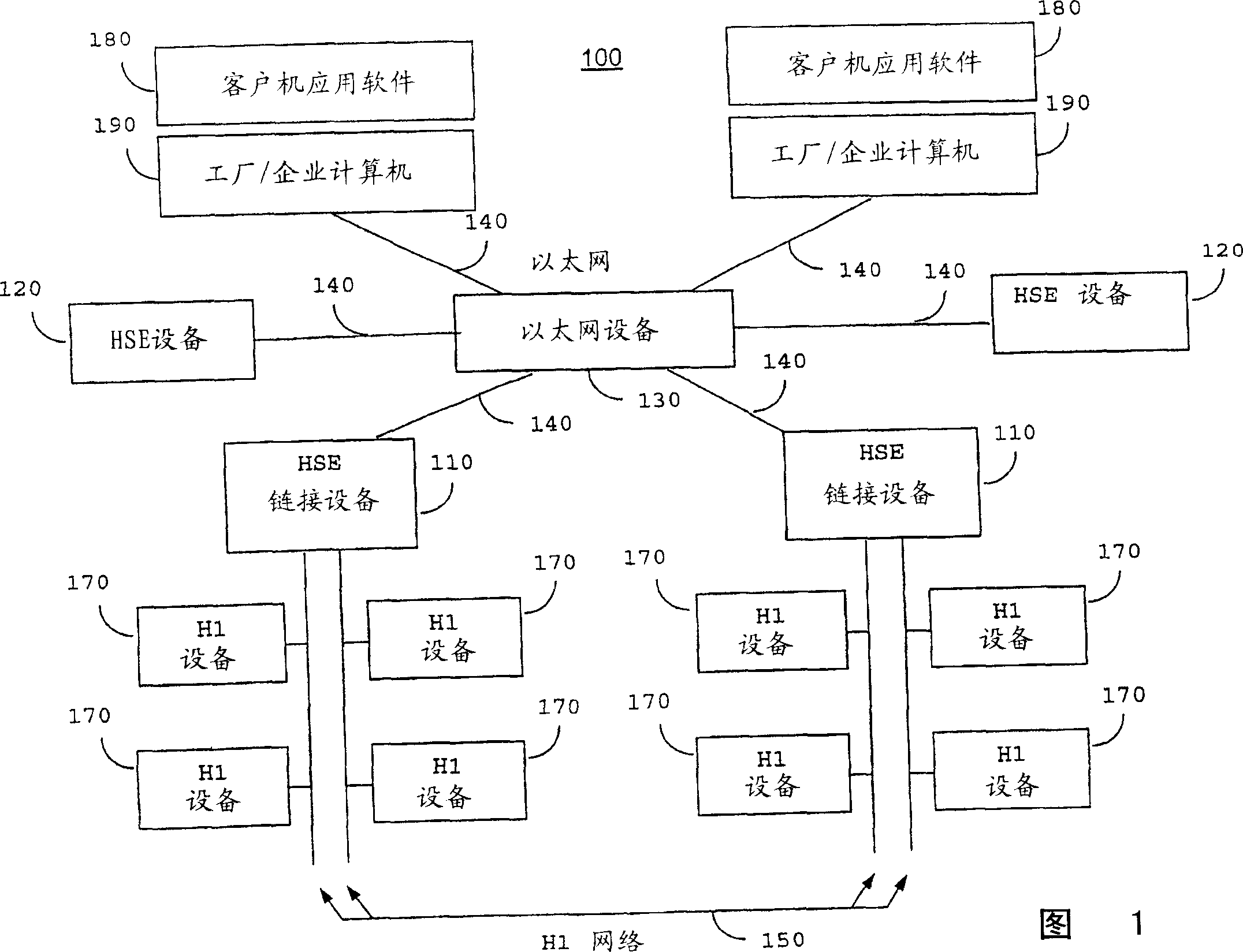

High-speed Ethernet programmable controller system based on fund conference bus in site

InactiveCN1920712ASolve the problem of seamless integration on FF HSE busSupplementary processing capacityData switching networksTotal factory controlBus interfaceEmbedded controller

The invention relates to a programmable controller based on on-site high-speed Ethernet of foundation, wherein it uses PLC target system with two embedded controllers, as FF on-site bus interface card and PLC operator; the FF on-site bus interface card has the flexible function block for inputting / outputting function as multi-path analogue input / output function block and multi-path digit input / output function block, to be used as the remote data interface of PLC; the PLC is seamlessly integrated on the FF HSE bus; and it uses detecting diagnosis function block to detect the PLC operation by superior machine; and the PLC algorism programming system of superior machine via FF on-site bus interfaces card can download algorism (TIC code) and I / O distribution document. The invention can realize single-machine on-site control, and interact with FF on-site device as remove control.

Owner:MICROCYBER CORP

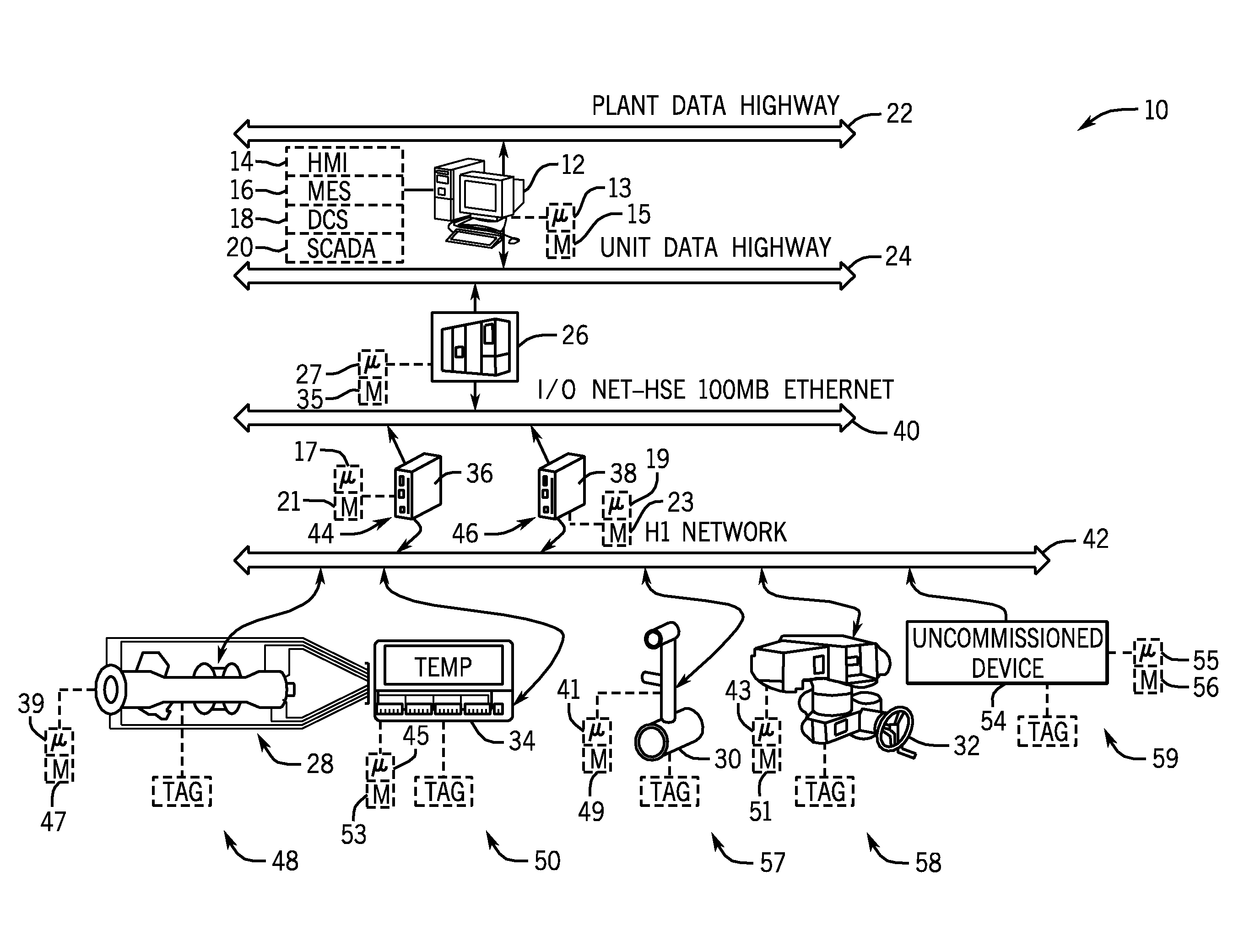

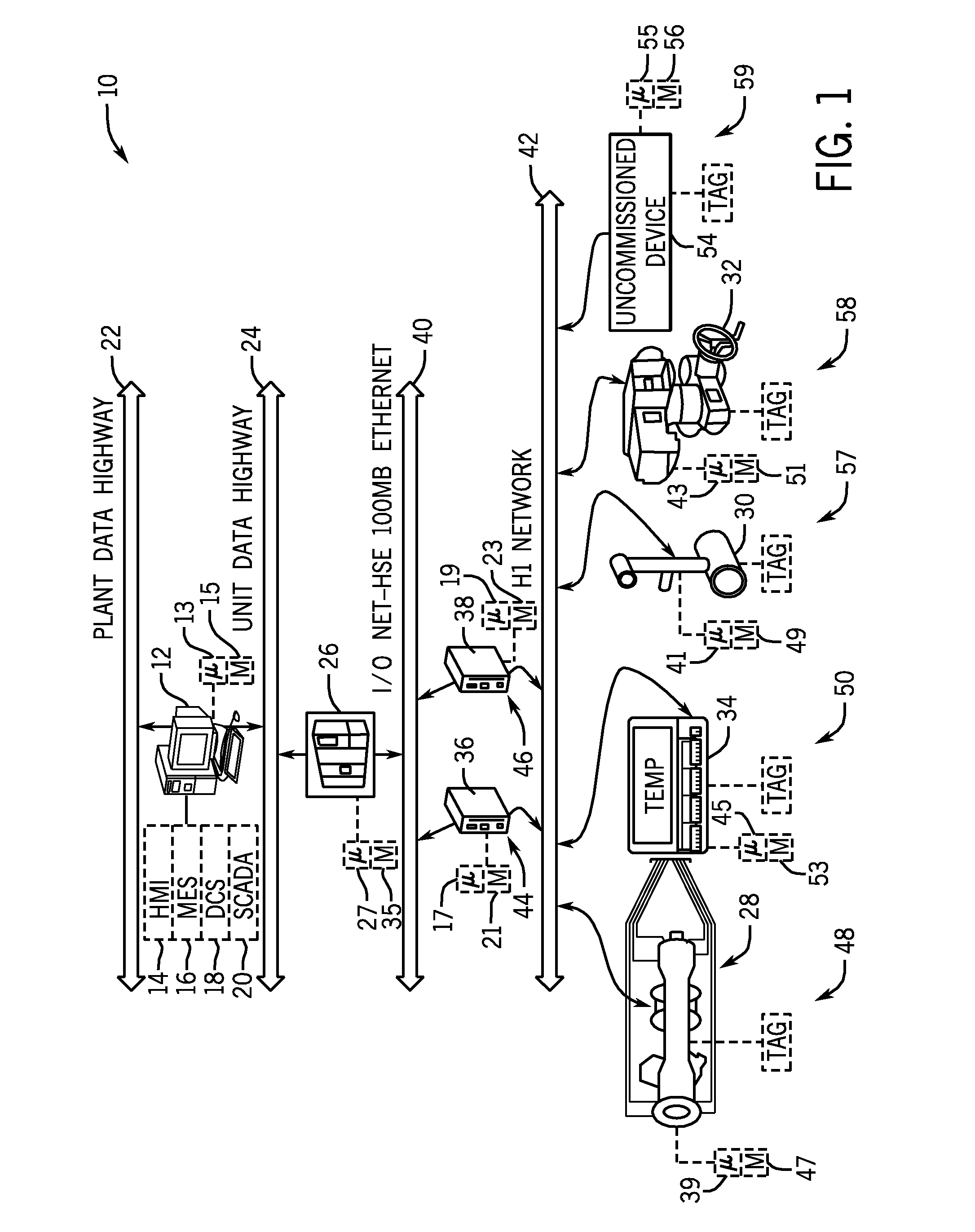

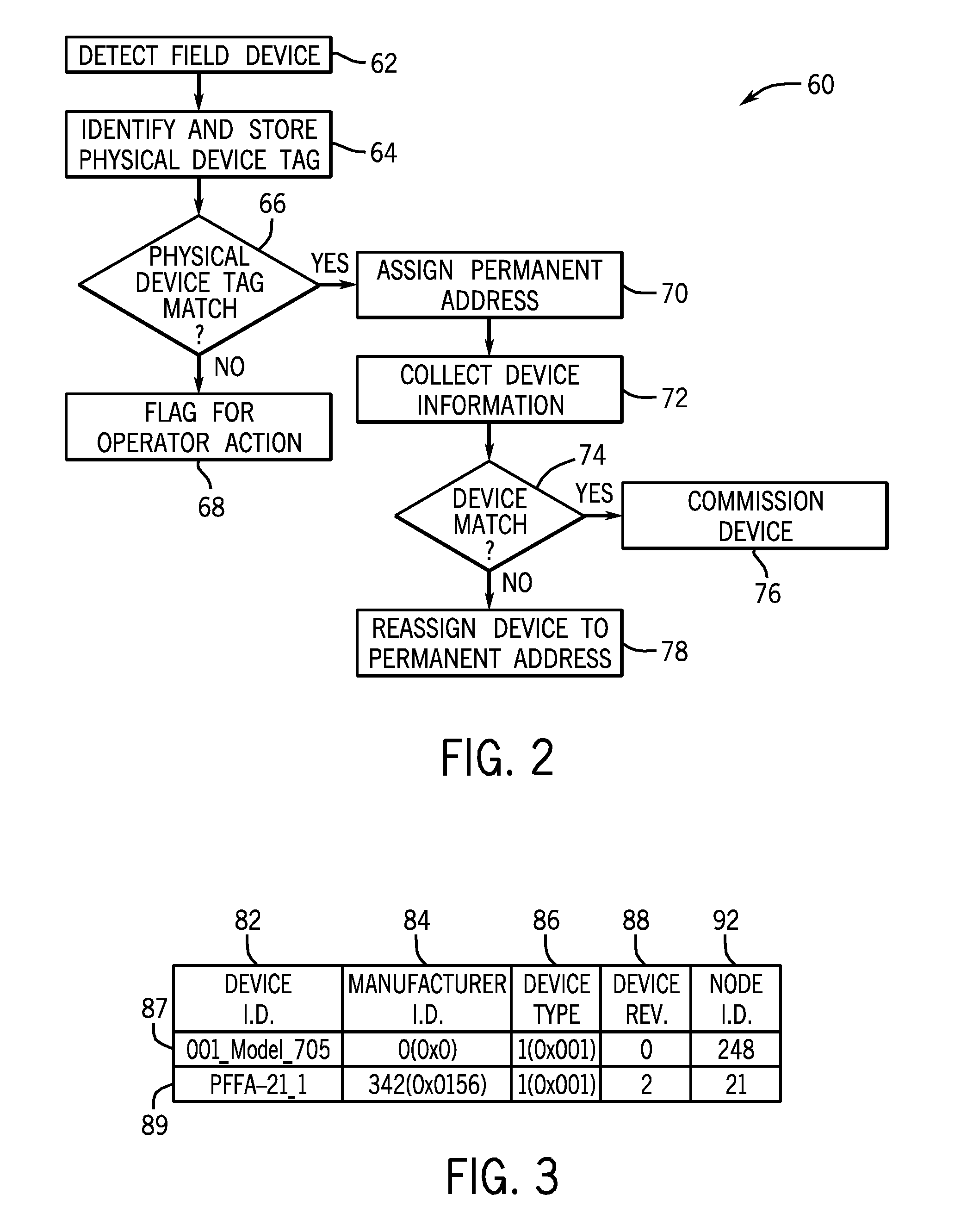

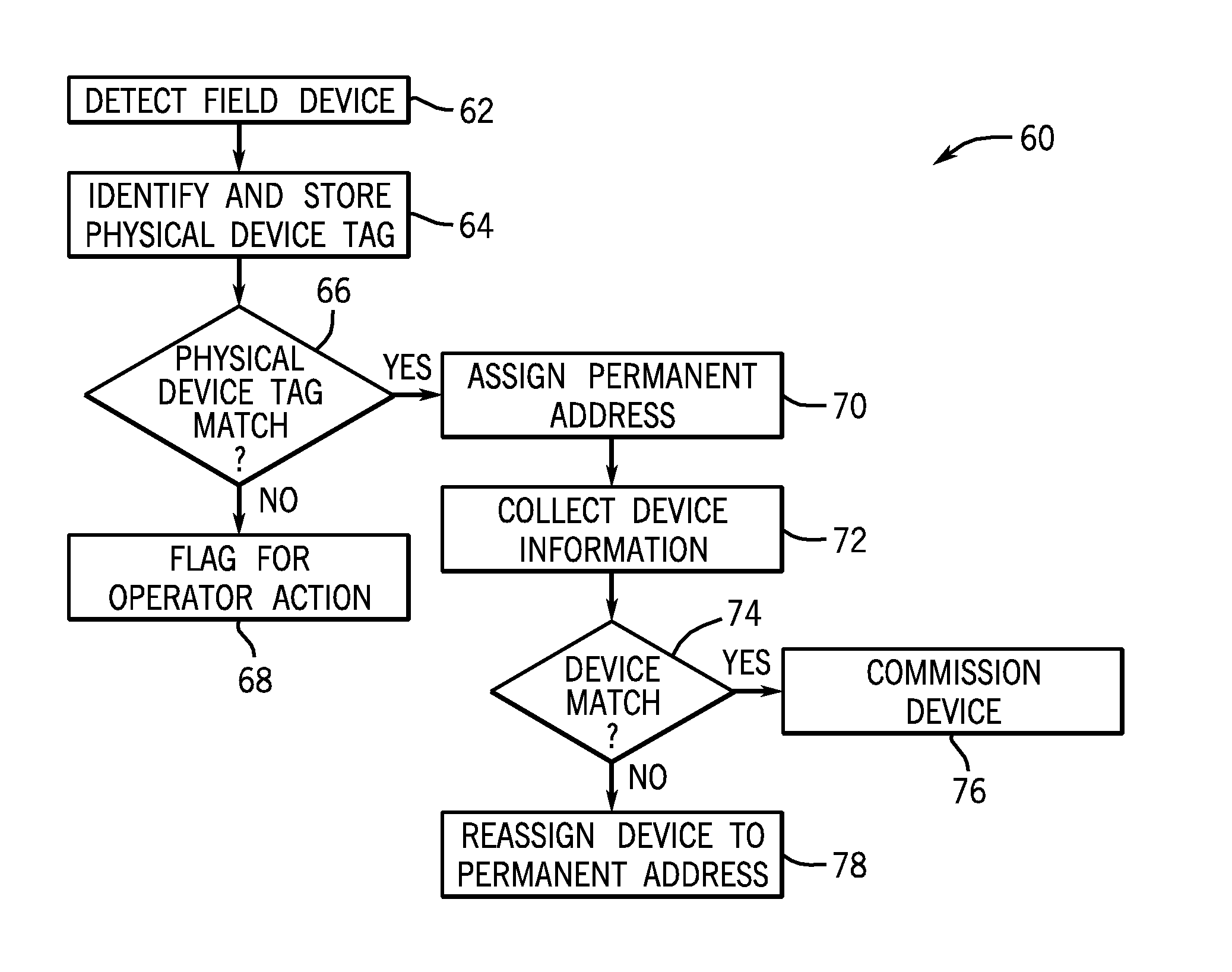

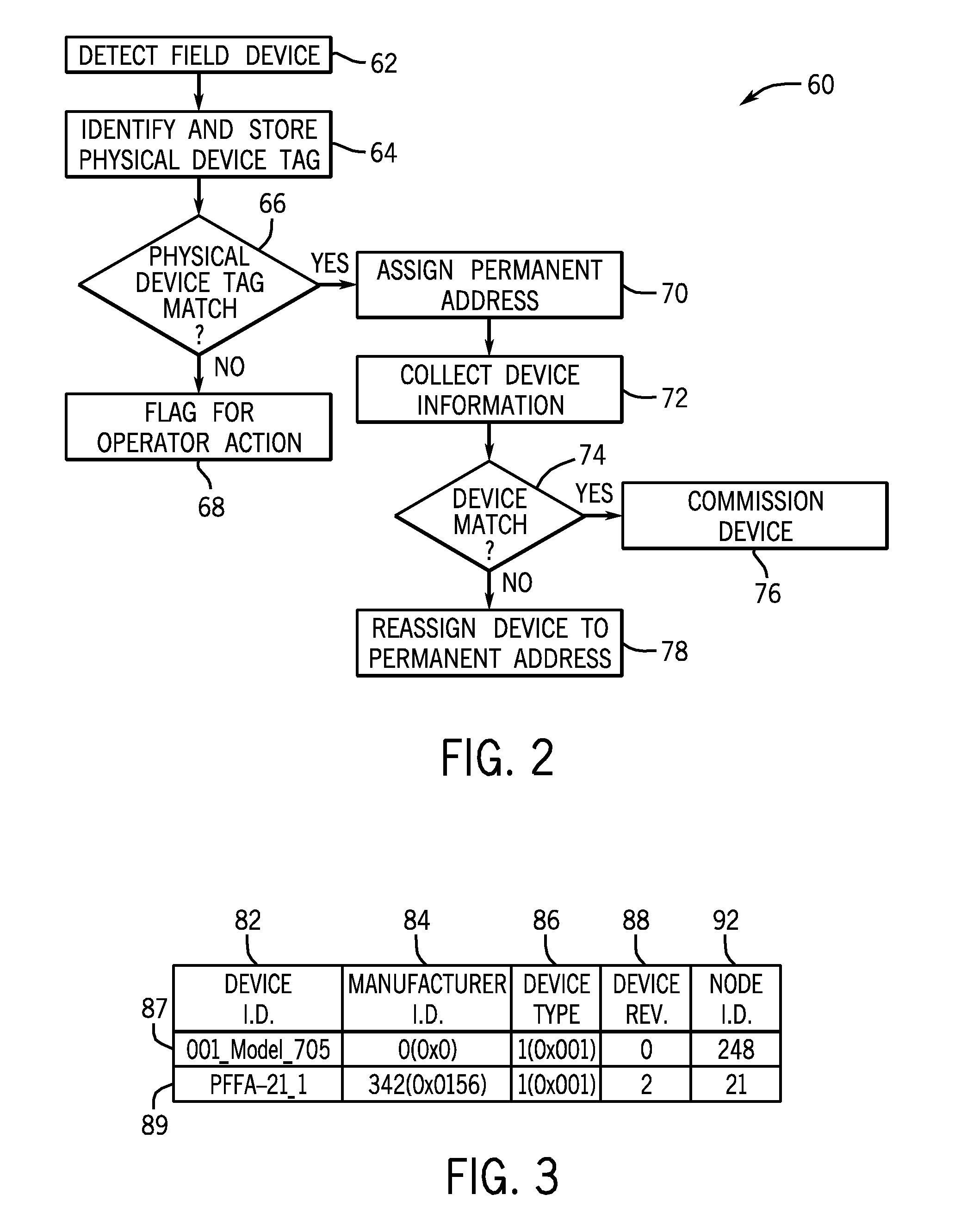

Automatic foundation fieldbus device commissioning

ActiveUS20130282931A1Home automation networksInput/output processes for data processingComputer networkActive mode

A device includes an interface configured to receive an indication of a second device on a network, and a processor configured to determine if the indication is one of an expected set of indications and generate a permanent node address for assignment to the second device if the indication is one of an expected set of indications. The permanent node address places the second device into an active mode as a permanent node addressed device. The processor is further configured to receive at least one device parameter from the permanent node addressed device, determine if the at least one device parameter matches an expected device parameter for the permanent node addressed device, and generate a second permanent node address for assignment to the device if the at least one device parameter matches the expected device parameter for the permanent node addressed device.

Owner:GENERAL ELECTRIC CO

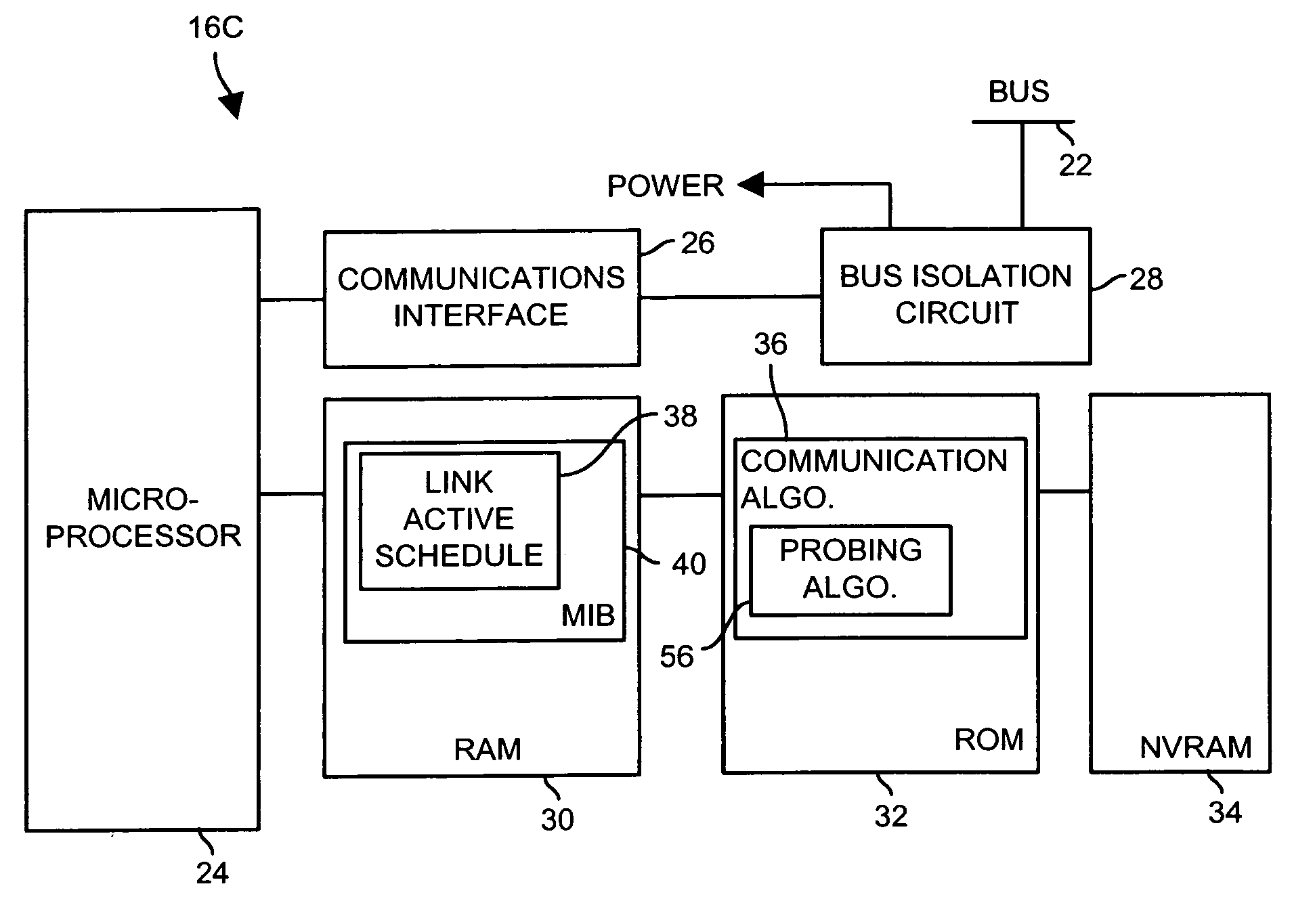

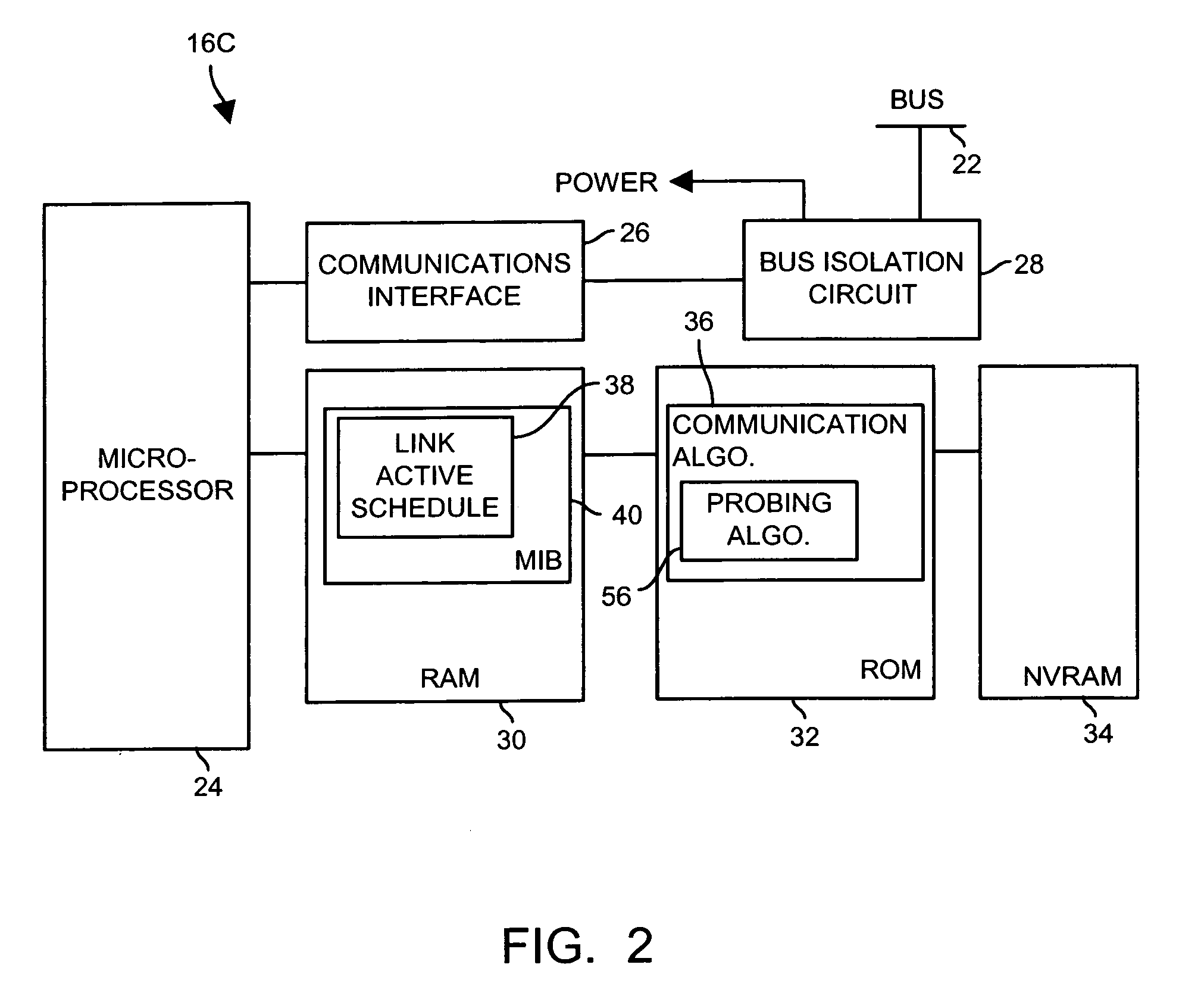

Probing algorithm for foundation fieldbus protocol

InactiveUS6944681B1Line-transmission monitoring/testingInput/output processes for data processingControl systemHand held

A hand-held communication control device which, when coupled to a process control system communication bus, controls communication occurring on the bus using a communication schedule that dictates when each of the devices coupled to the bus will be permitted to communicate on the bus. The hand-held communication control device further uses a probing algorithm to detect devices, including other communication control devices, that are coupled to the bus. The probing algorithm causes the hand-held communication control device to select an address from one of a set of three address lists to which a probe node message is then transmitted to detect the presence of a device at that address. One of the address lists is reserved for communication control devices and uses only a limited number of maximum possible addresses. The probe addresses are selected from each of the three address lists in a sequential manner and from among the three address lists in an alternating manner so that, when the communication control device takes control of a bus formerly controlled by another communication control device, the hand-held communication control device detects the presence of the other communication control device and relinquishes control of the bus to the other communication control device in a timely manner.

Owner:FISHER-ROSEMOUNT SYST INC

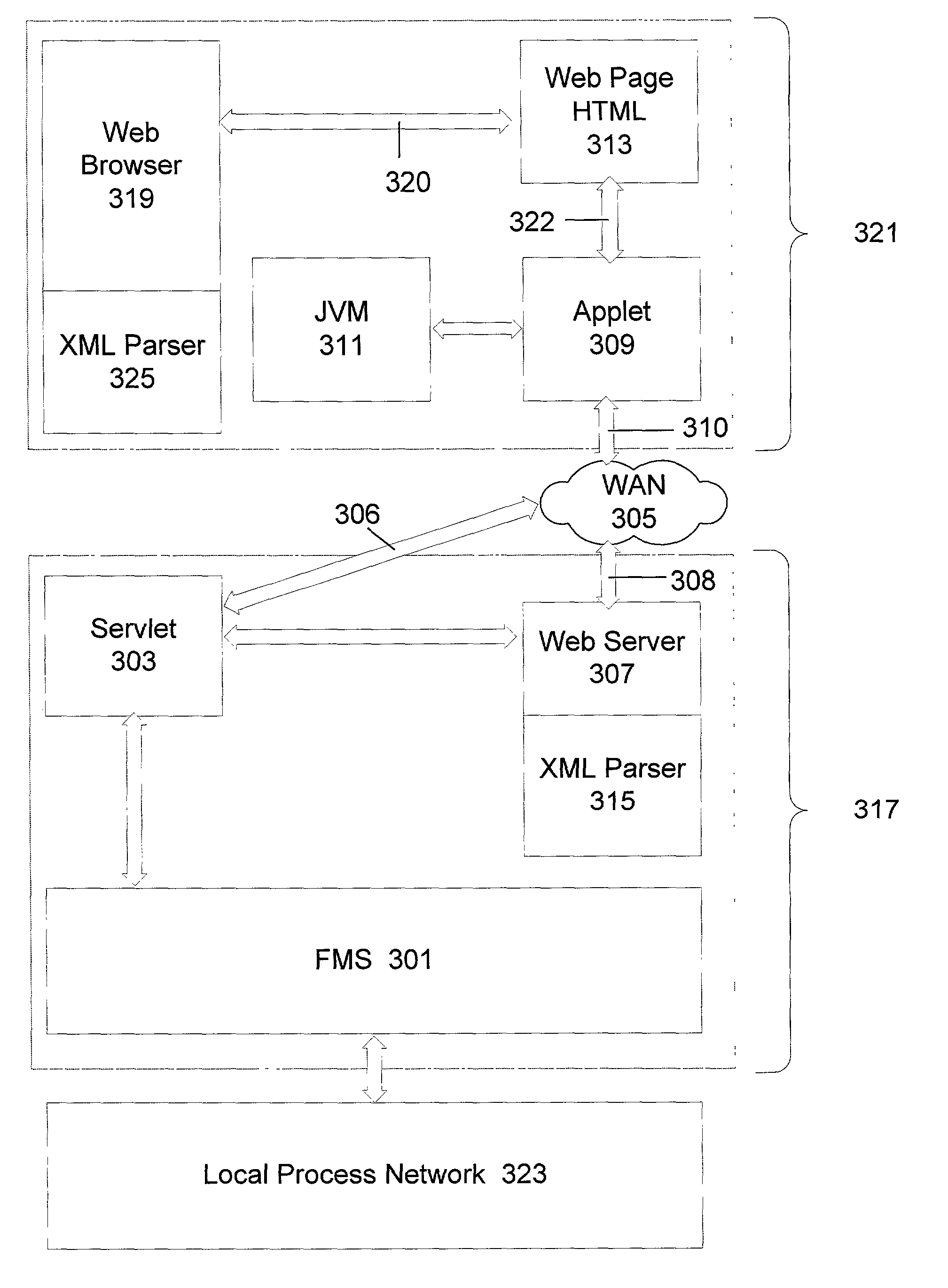

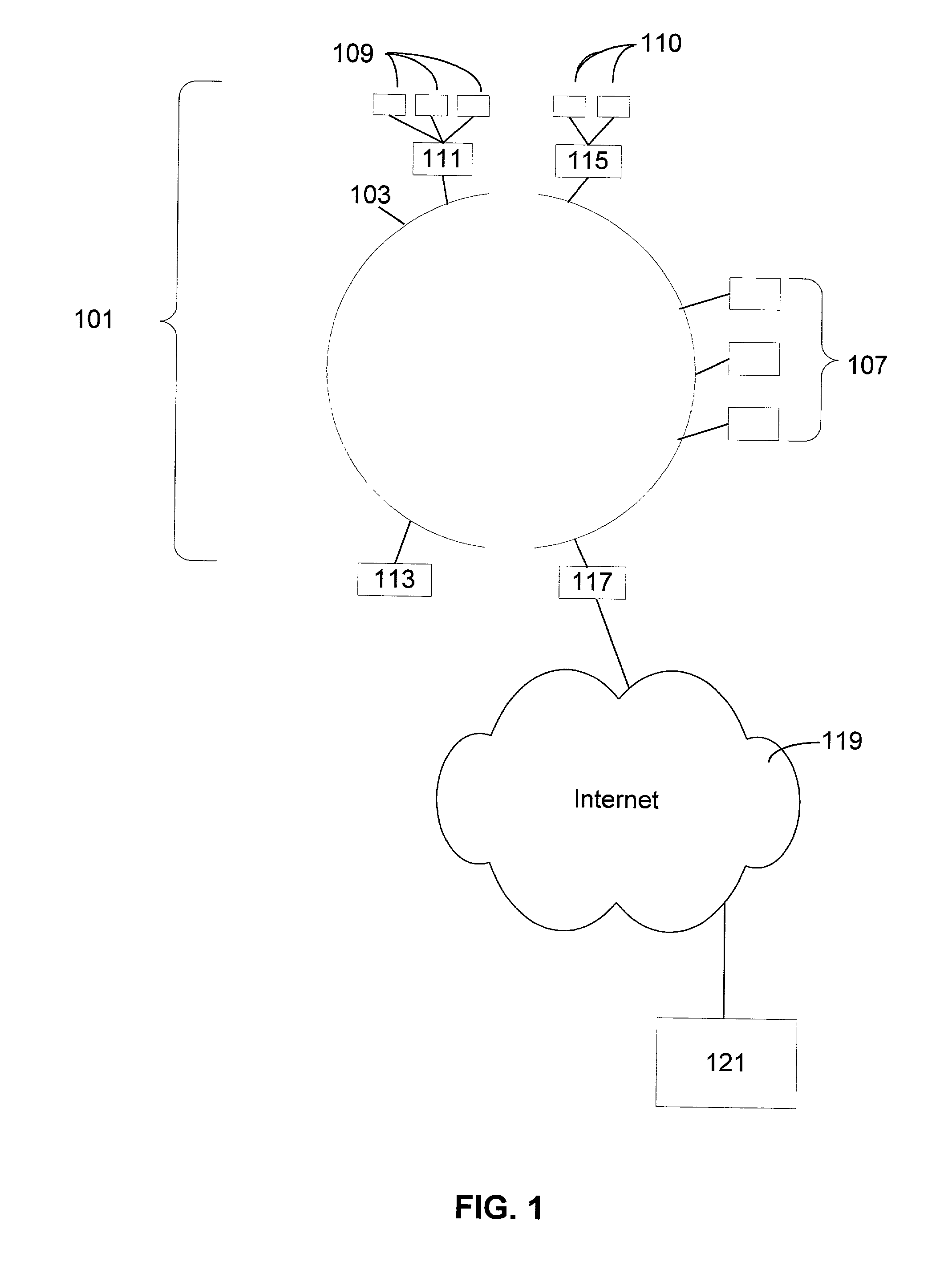

Remote fieldbus messaging via Internet applet/servlet pairs

A system and method for remote monitoring and control of a Foundation Fieldbus process network utilizes an applet / servlet pair, the applet residing on a remote node on a wide area network such as the Internet, the servlet residing on a node communicably linked to the wide area network and to the process network. The servlet is operative to collect data via the FMS layer from one or more process devices such as field devices residing on the process network and to have translated the collected data and to transmit the translated data via the wide area network to the applet residing on the remote node. The information is displayed to the user by an appropriate interface such as the graphical interface of a browser running on the remote node. The user may initiate communications by instantiating the applet via a hyperlink in a web page or otherwise, and may input and receive information via the browser's graphical interface.

Owner:SCHNEIDER ELECTRIC SOFTWARE LLC

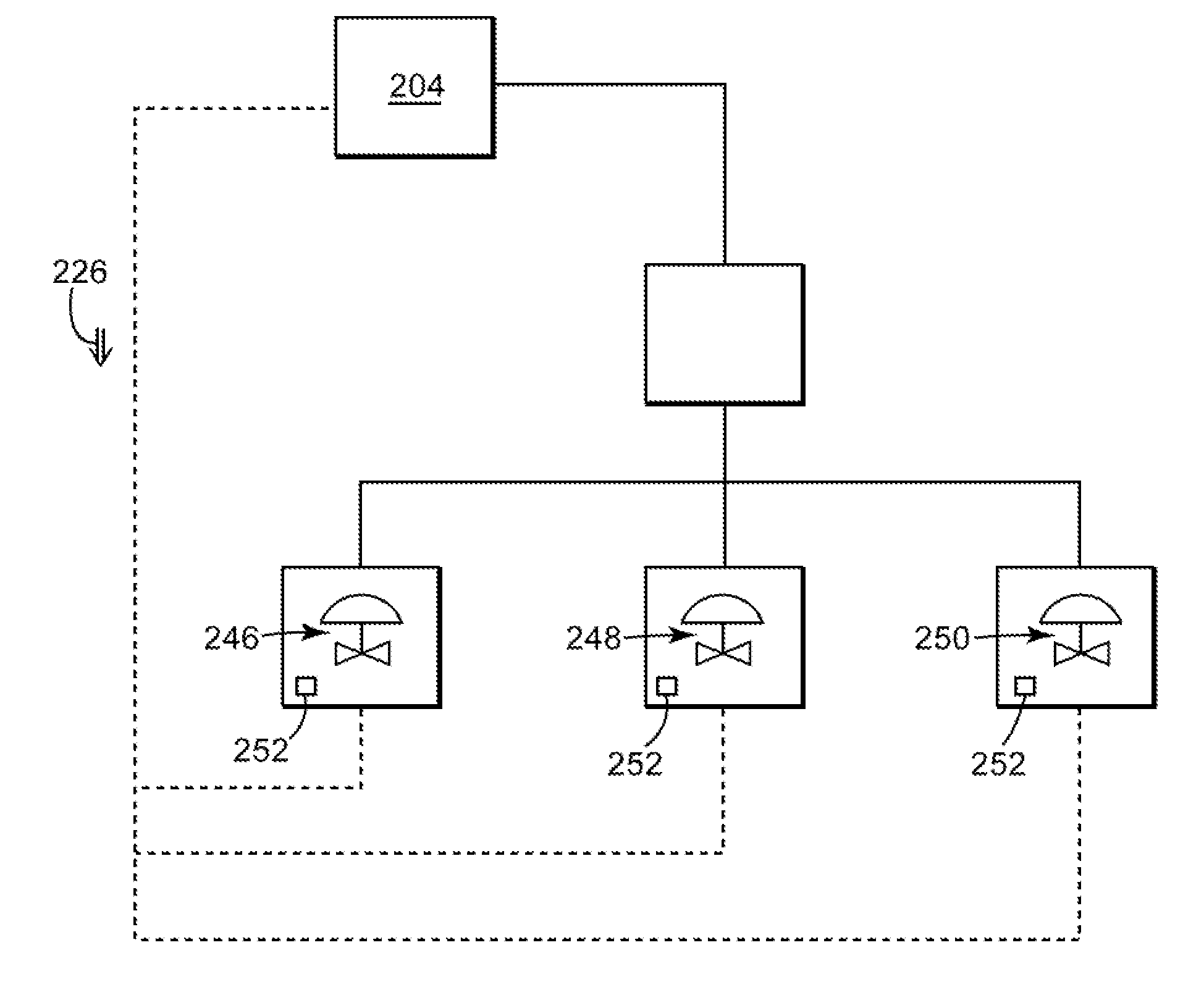

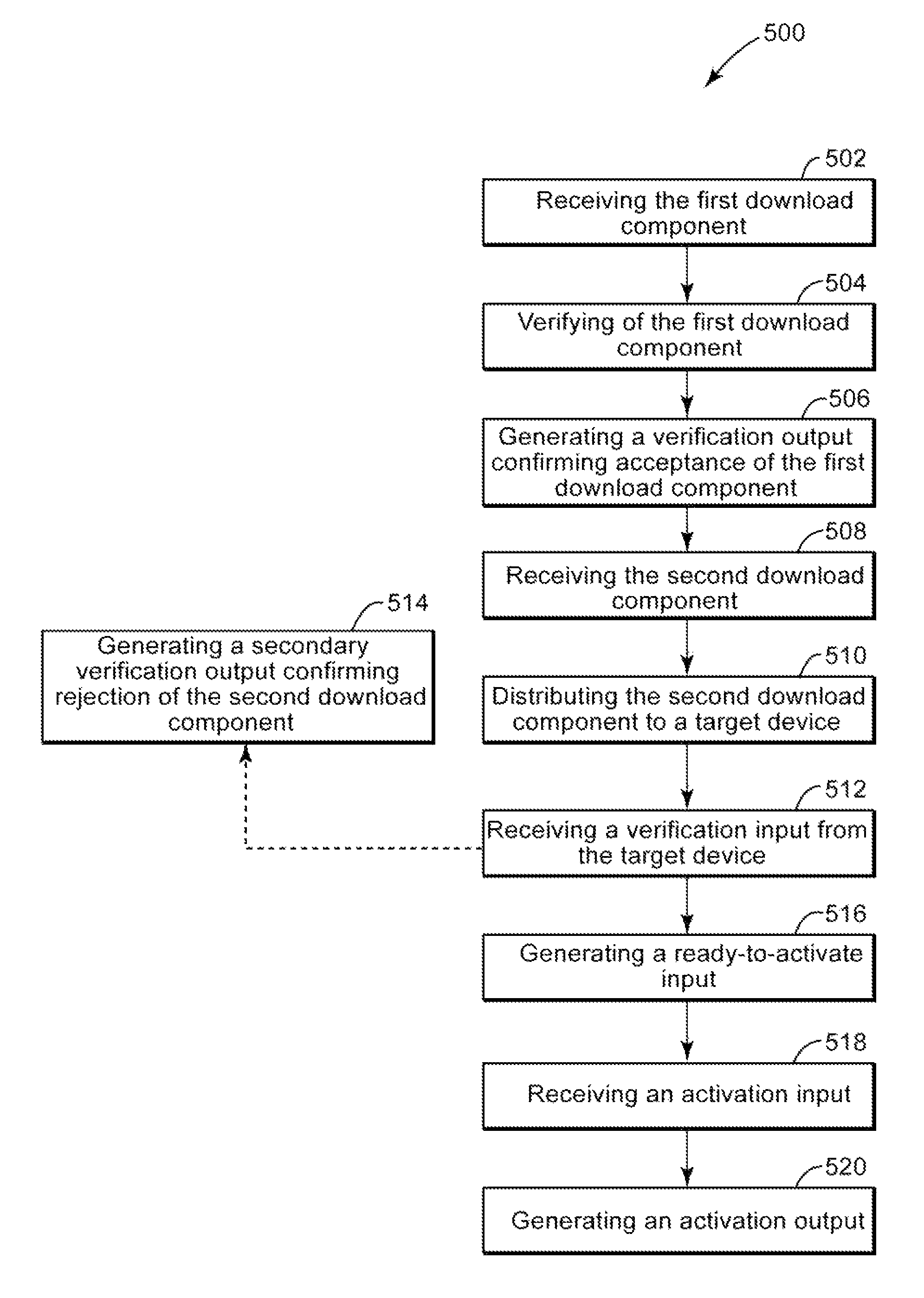

System and method for updating firmware across devices in a process facility

ActiveUS20150052512A1Easy to optimizeProgram loading/initiatingMemory systemsOperating instructionFOUNDATION fieldbus

Embodiments of a system and method to update firmware across multiple devices in a process facility using a single domain of a FOUNDATION Fieldbus protocol. In one embodiment, the system has a receiving device that couples with a pair of target devices, e.g., a first target device and a second target device. The receiving device includes operating instructions that can process an input and generate an output. The input comprises data comprising a first firmware component and a second firmware component for, respectively, the first target device and the second target device. The receiving device can direct the firmware component to the appropriate target device; generating a first output and a second output that distribute the firmware components to complete the upgrade process.

Owner:DRESSER LLC

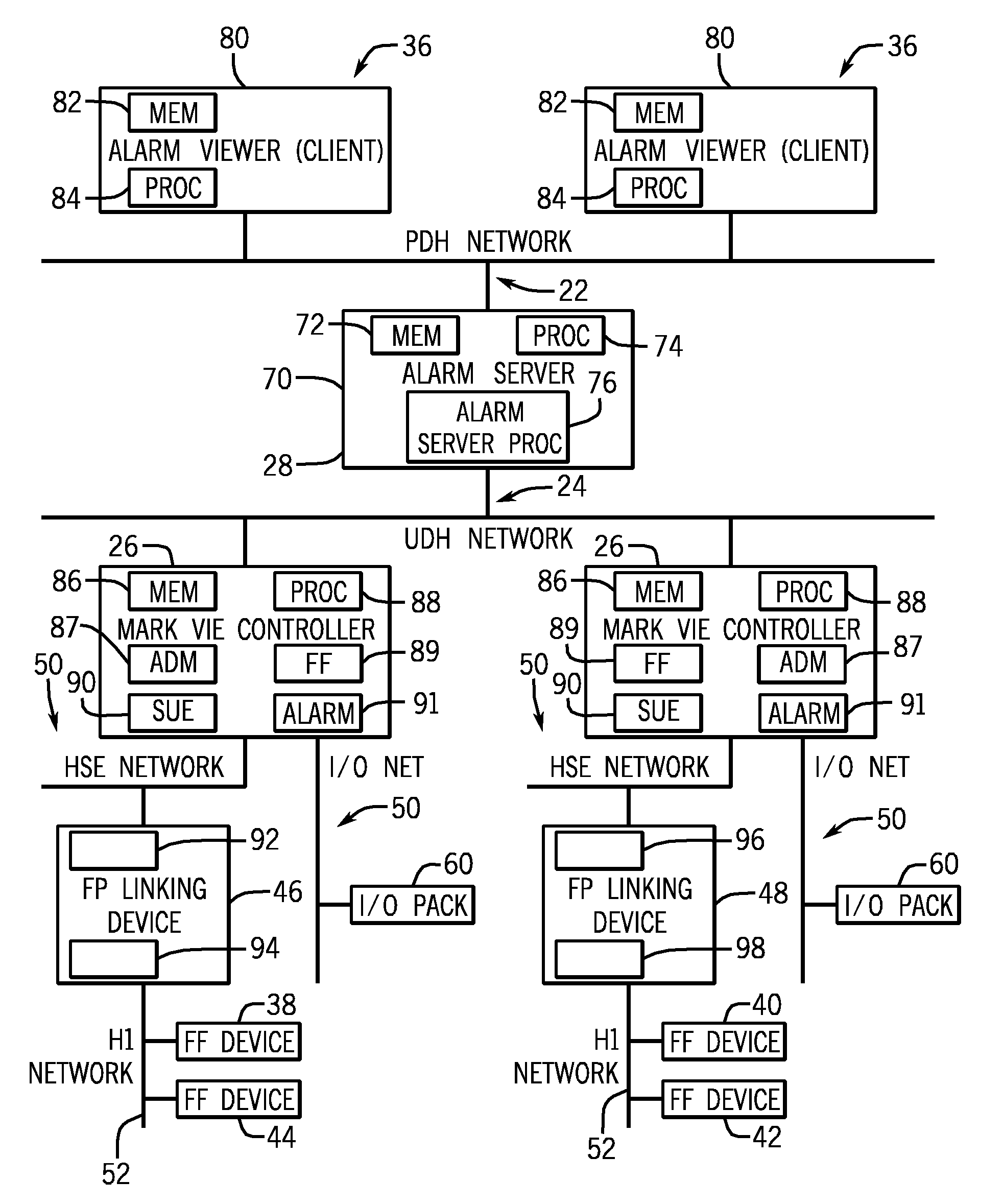

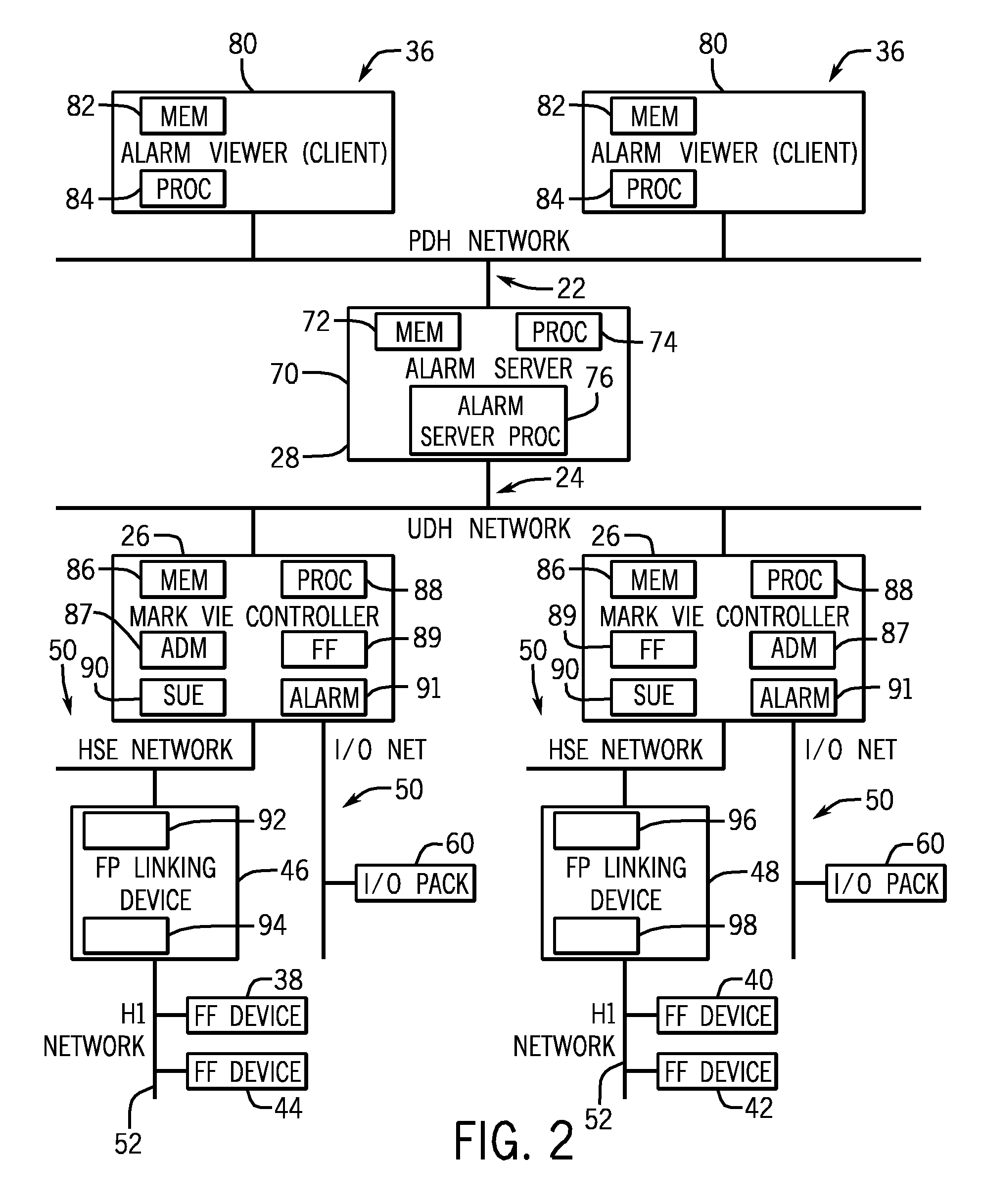

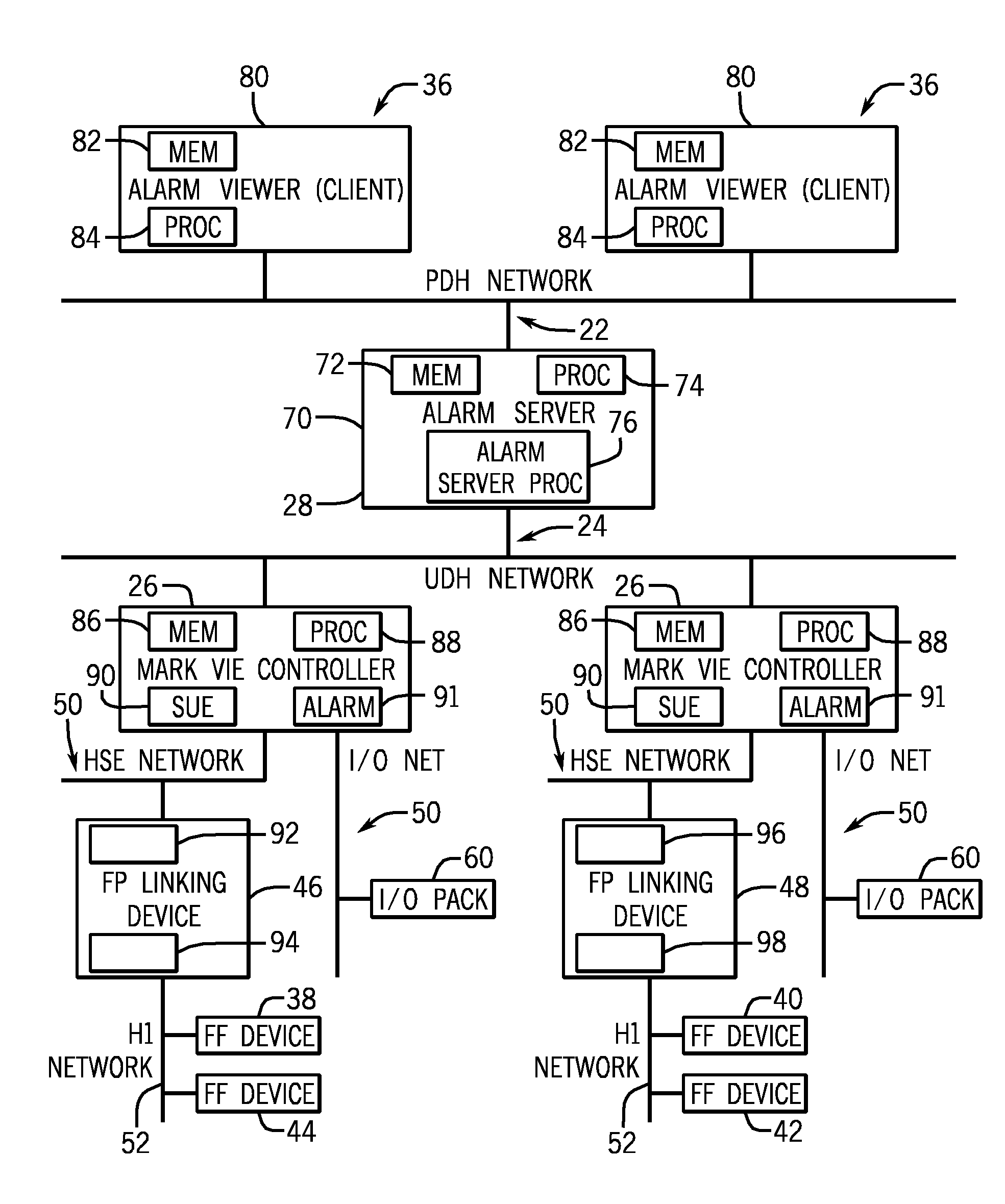

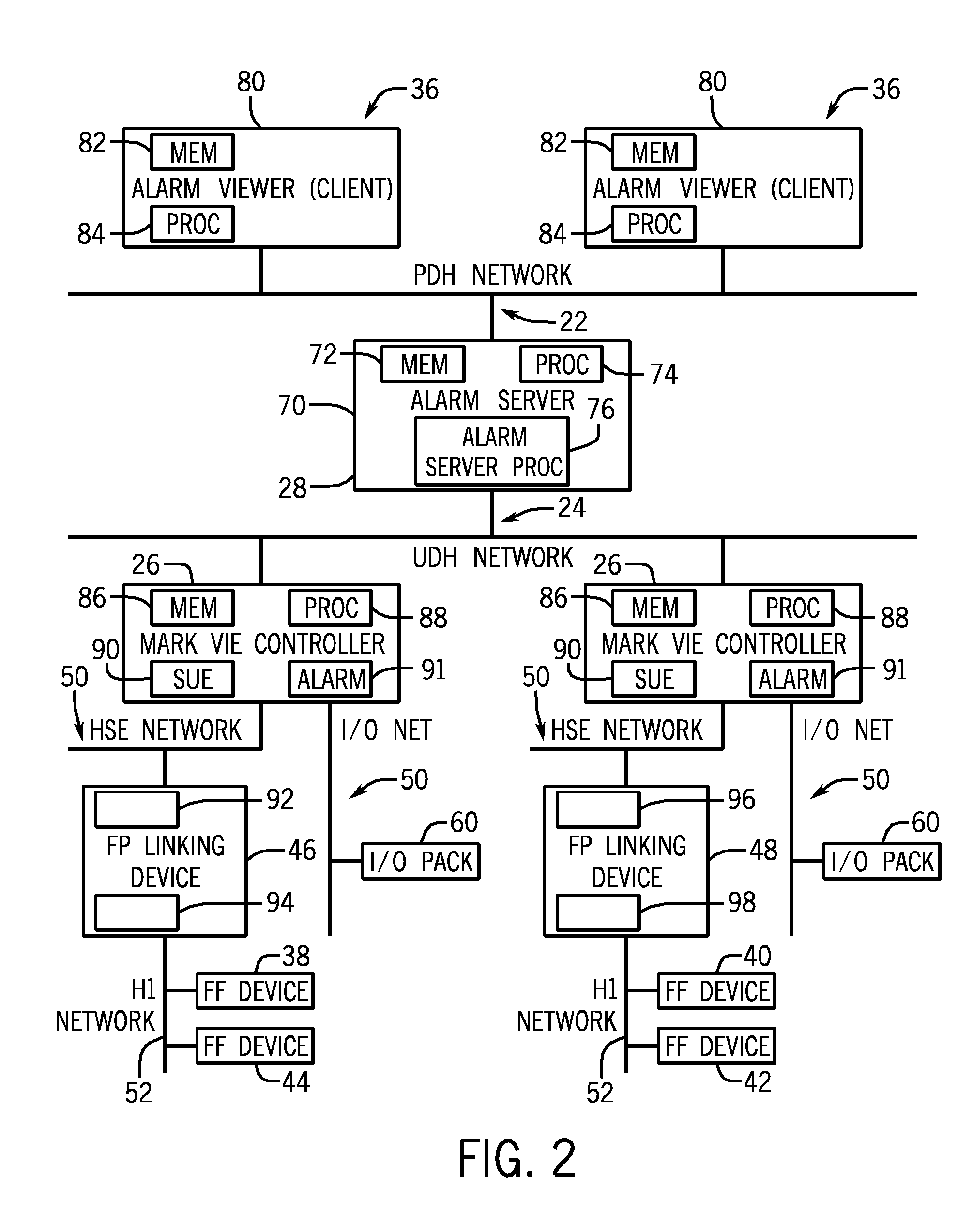

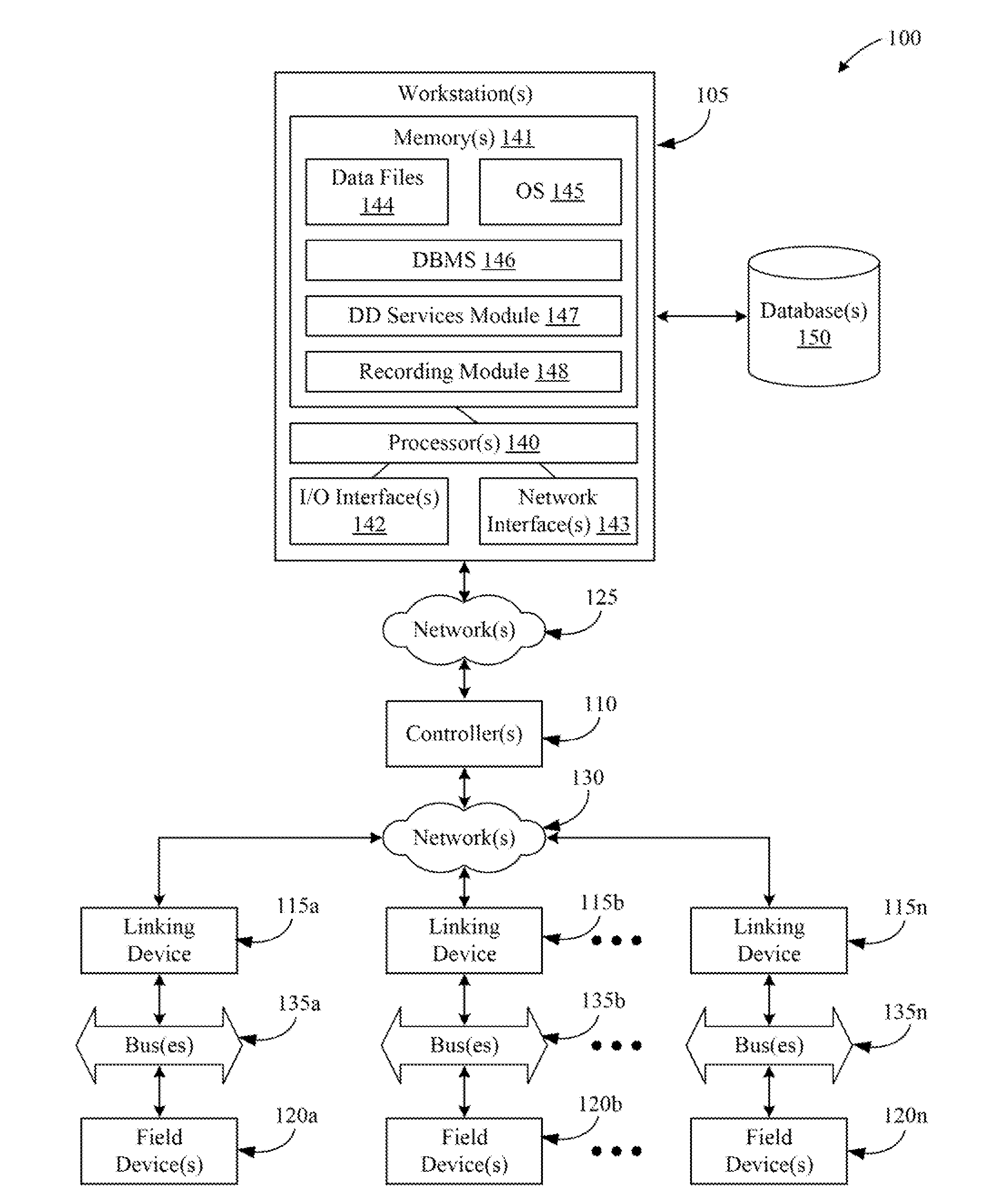

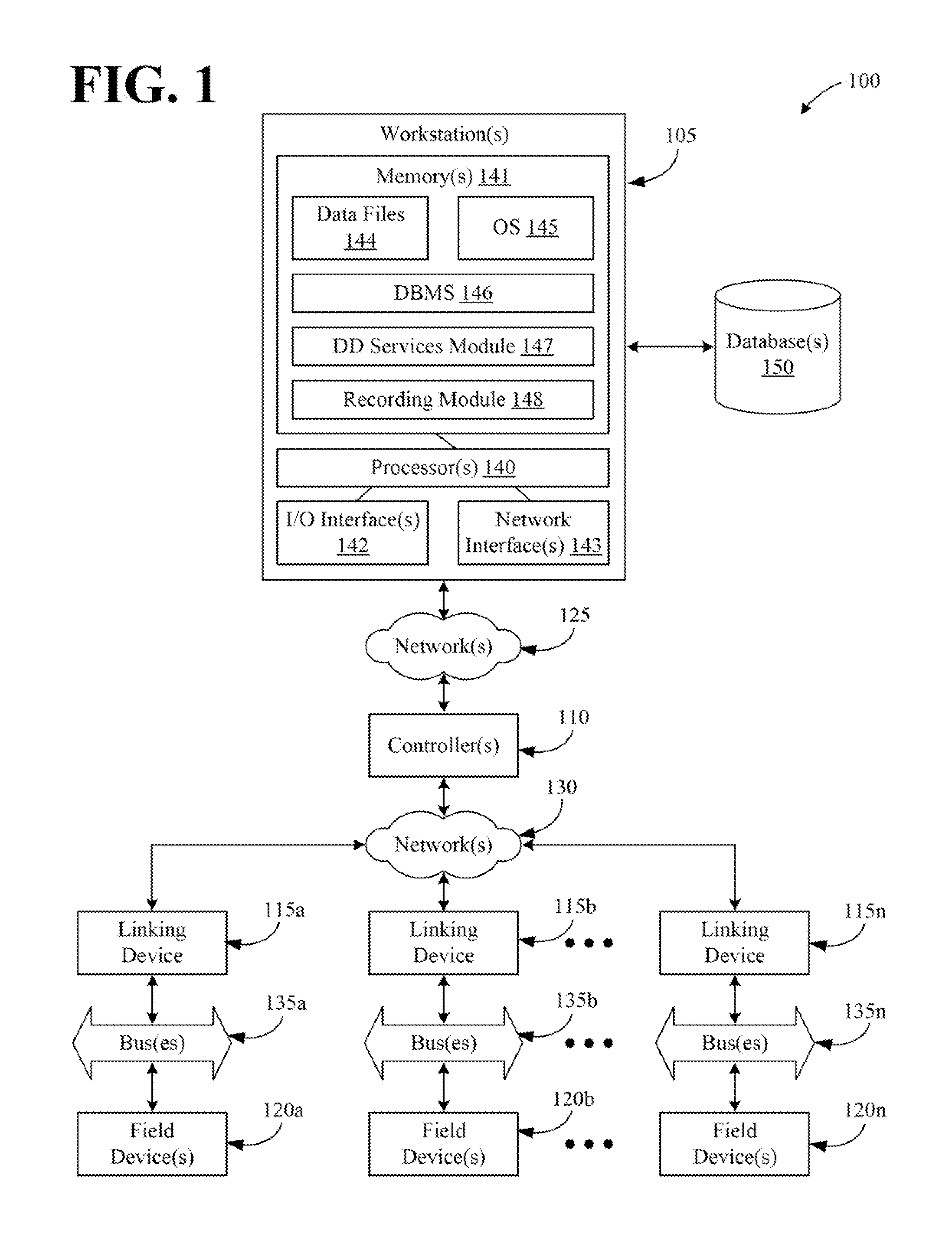

Systems and methods for third-party foundation fieldbus information

An industrial process control system is provided that includes one or more fieldbus devices configured to communicate alarm or alert information representative of alarms and alerts using a first format. The industrial process control system also includes a linking device connected to the one or more fieldbus devices that is configured to publish the alarm or alert information from the fieldbus devices to one or more computers of the industrial process control system. A controller is also included that is configured to receive the alarm or alert information from the linking device. The controller is configured to interpret the alarm or alert information and create a list of the alarms and alerts in a second format interpretable by an alarm server of the industrial process control system, wherein the alarm server cannot interpret the first format.

Owner:GENERAL ELECTRIC CO

Automatic foundation fieldbus device commissioning

ActiveUS8745281B2Home automation networksInput/output processes for data processingComputer networkFOUNDATION fieldbus

A device includes an interface configured to receive an indication of a second device on a network, and a processor configured to determine if the indication is one of an expected set of indications and generate a permanent node address for assignment to the second device if the indication is one of an expected set of indications. The permanent node address places the second device into an active mode as a permanent node addressed device. The processor is further configured to receive at least one device parameter from the permanent node addressed device, determine if the at least one device parameter matches an expected device parameter for the permanent node addressed device, and generate a second permanent node address for assignment to the device if the at least one device parameter matches the expected device parameter for the permanent node addressed device.

Owner:GE INFRASTRUCTURE TECH INT LLC

Control systems and methods of providing the same

ActiveUS20110082570A1Facilitate communicationProgramme controlSafety arrangmentsControl systemComputer science

Control systems and methods for controlling certain systems, devices, and apparatus are described. A control system may include a memory and at least one processor. The memory may be operable to store both a Foundation Fieldbus protocol that facilitates communication with one or more Foundation Fieldbus devices and a second protocol that facilitates communication with one or more control devices. The at least one processor may be operable to access both the Foundation Fieldbus protocol and the second protocol, and to control the one or more Foundation Fieldbus devices and the one or more control devices. A network may facilitate communications between the at least one processor and both the one or more Foundation Fieldbus devices using the Foundation Fieldbus protocol and the one or more control devices using the second protocol.

Owner:GENERAL ELECTRIC CO

Fieldbus process communications using error correction

ActiveUS20060259159A1Solve the slow data transmission speedLow signal levelError detection/correctionCode conversionComputer hardwareCombined use

A method of communicating over an H1 Fieldbus network is provided. The communication over the H1 Fieldbus network employs an advanced form of error correction. In one embodiment, the advanced form of error correction utilizes low-density parity check codes; while in another embodiment, the advanced error correction employs turbo codes. The use of the advanced error correction with the H1 foundation Fieldbus network allows for higher data transmission speeds than 31.25 kbps and / or lower signaling levels than used currently.

Owner:FISHER-ROSEMOUNT SYST INC +1

Systems and methods for foundation fieldbus alerts

ActiveUS20120310382A1Reduce complexityLow costProgramme controlSafety arrangmentsMobile communication systemsInformation processor

An industrial process control system is provided. The industrial control system includes an alarm server with a processor configured to receive device information representative of field device information extracted from a device definition file. The processor is further configured to translate the device information into a first format interpretable by a global system for mobile communications (OPC AE) server and provide the device information in the first format to the OPC AE server.

Owner:GENERAL ELECTRIC CO

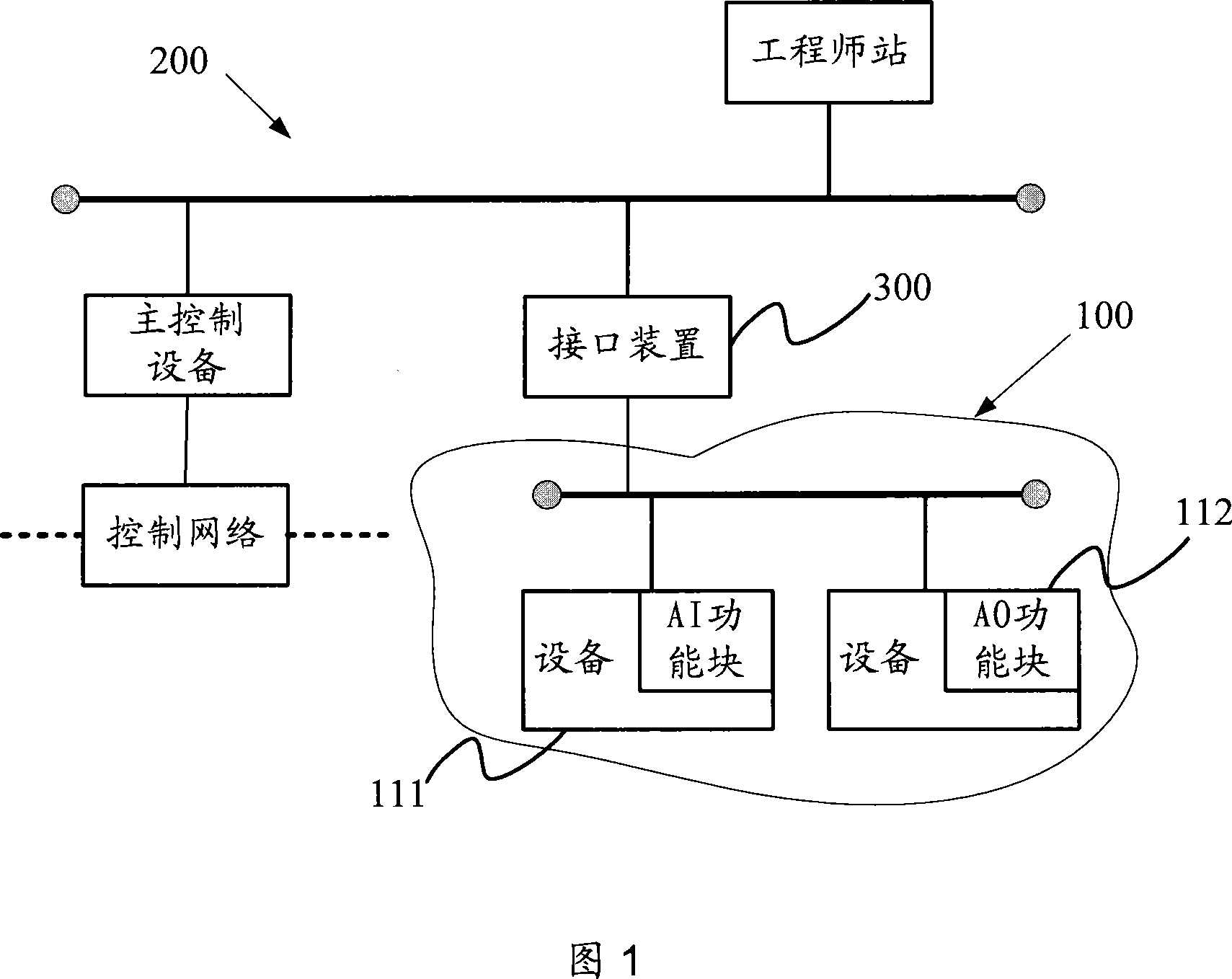

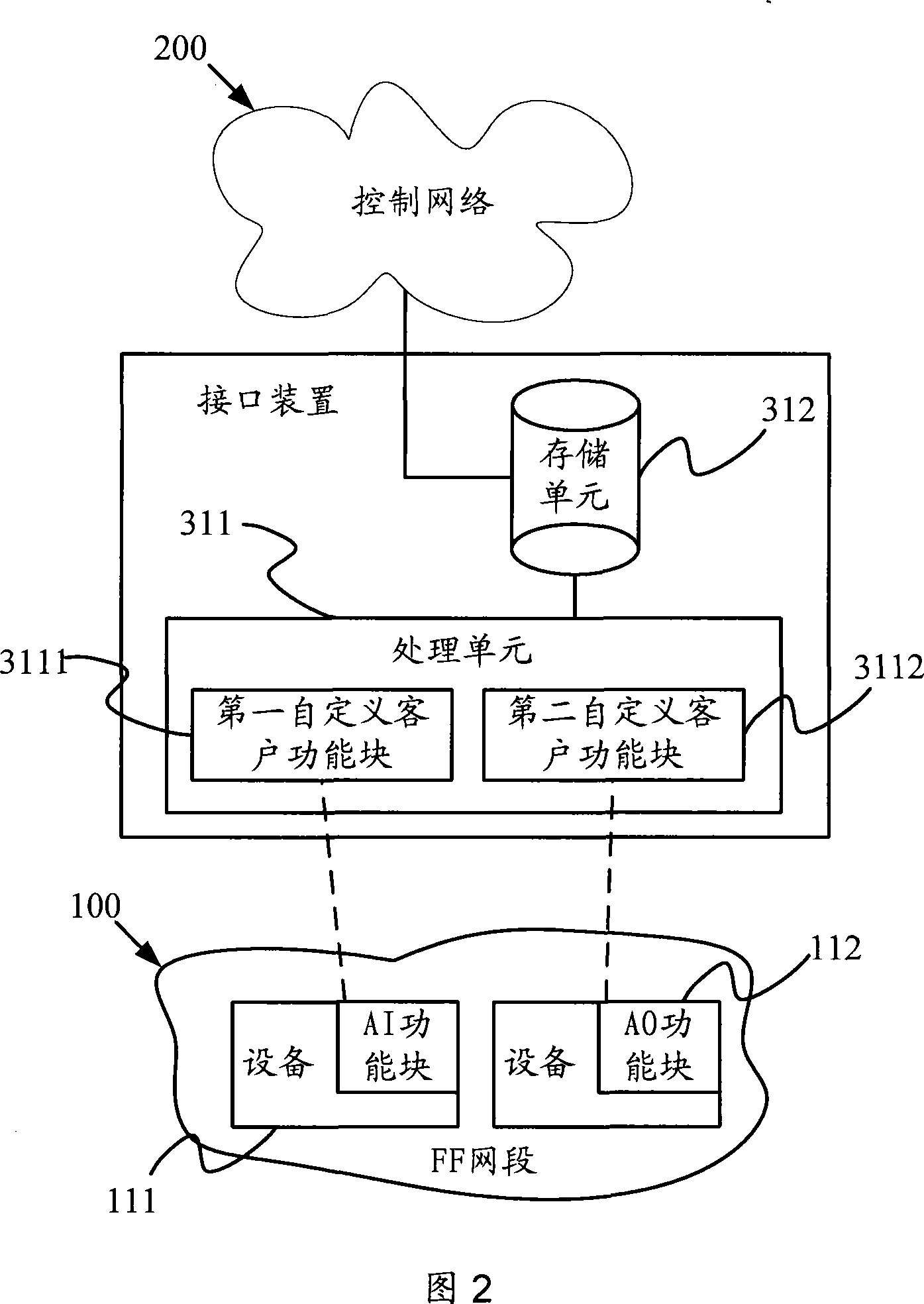

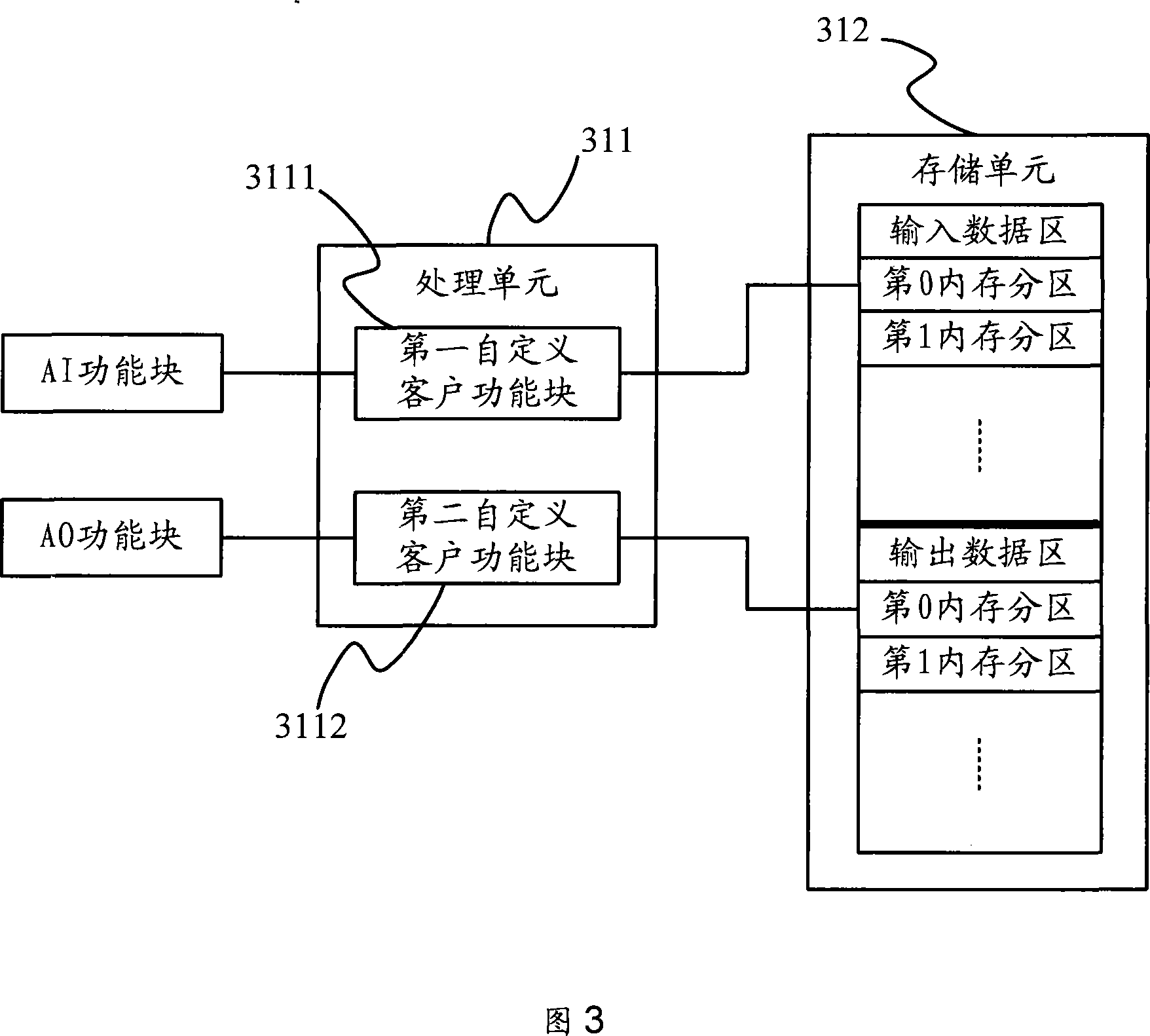

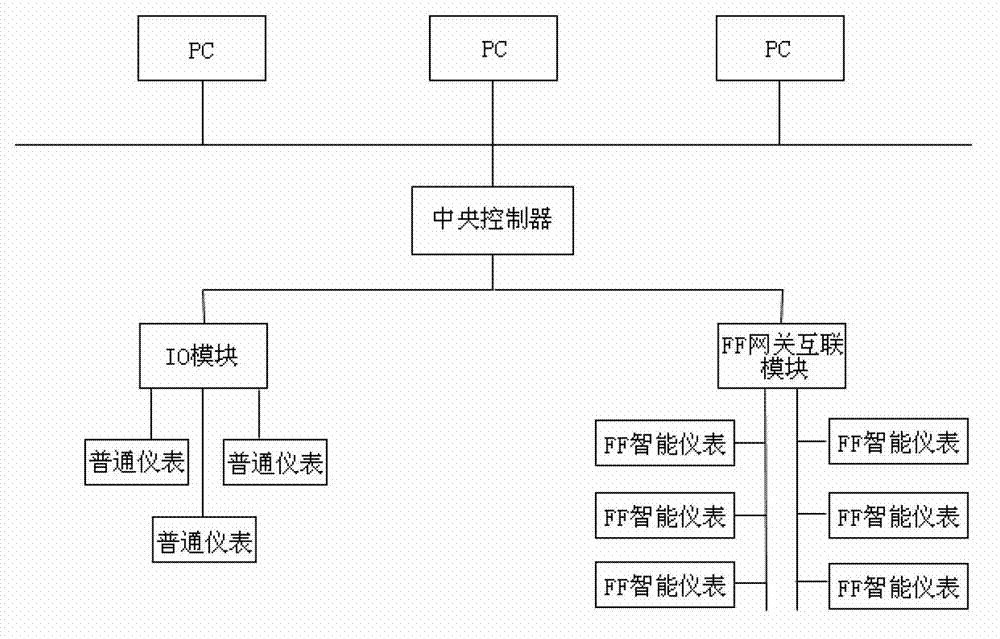

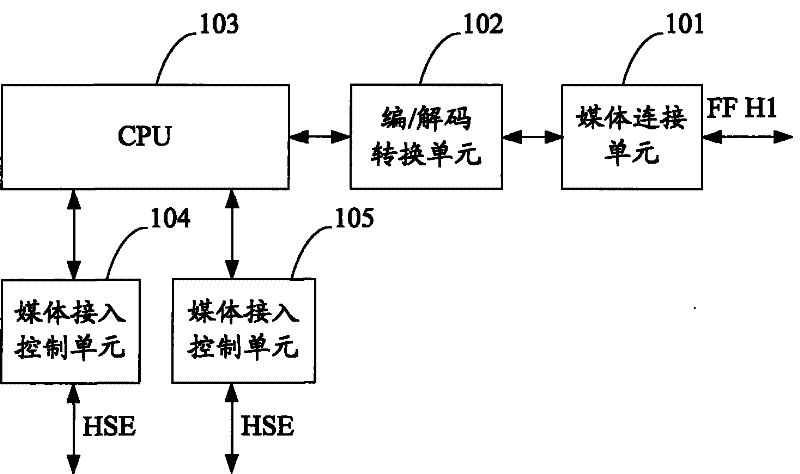

Control system including FF protocol H1 network segment and interface arrangement and communication method

InactiveCN101159650ATake advantage ofAvoid wastingTotal factory controlProgramme total factory controlControl systemDistributed computing

The invention discloses a control system comprising foundation fieldbus (FF) protocol H1 field-level network. The control system comprises a plurality of FF protocol H1-field network for supporting the FF protocol; a control network for supporting other protocols; and further an interface device for connecting the FF protocol H1 field-level network and the control network, acquiring on-site parameters and information of equipments in the FF protocol H1 field-level network, converting to the information that can be identified by the control network, and providing to the control network; wherein the control network calculates, converts the calculation results to FF protocol information and provides to the equipments in the FF protocol H1 field-level network. The invention discloses an interface device and a communication method at the same time. The invention realizes the information interchange between the equipments in the FF protocol H1 field-level network and the control network through the interface device, and realizes the control of the conventional control network to the equipments in the FF protocol H1 field-level network, so as to take full advantages of and expand the function of the conventional control network, and avoid wasting of resources.

Owner:SUPCON GRP +1

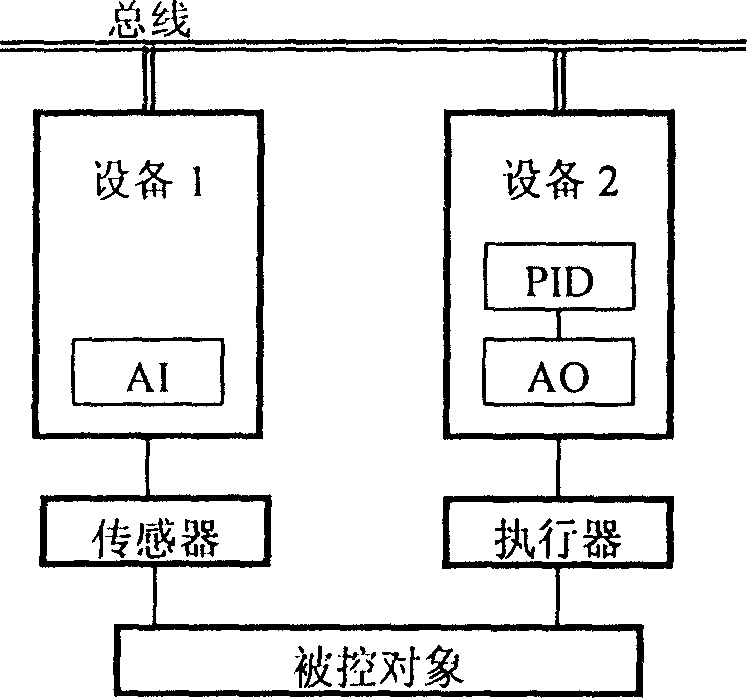

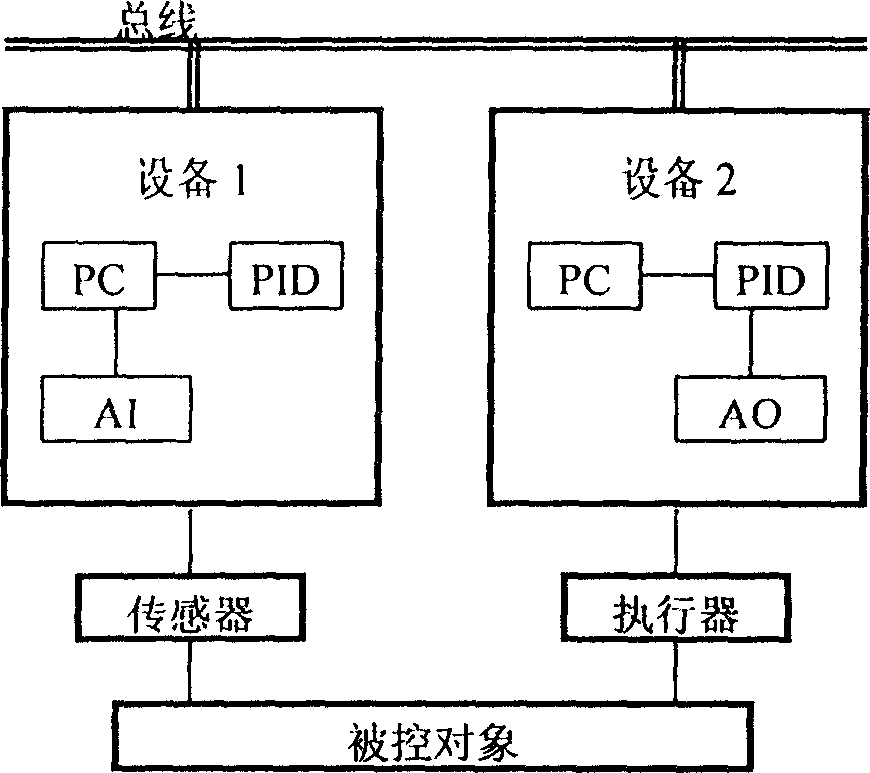

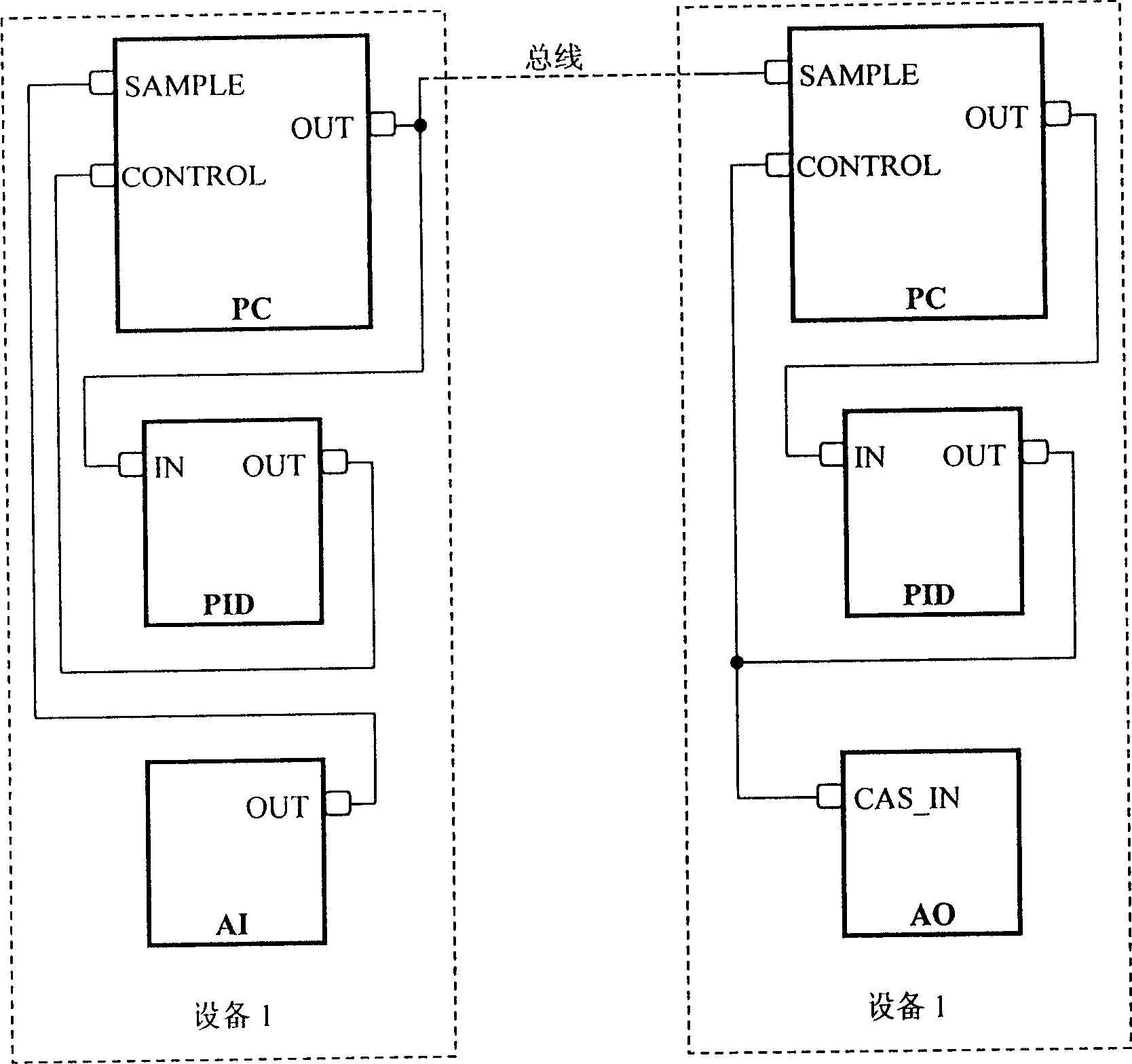

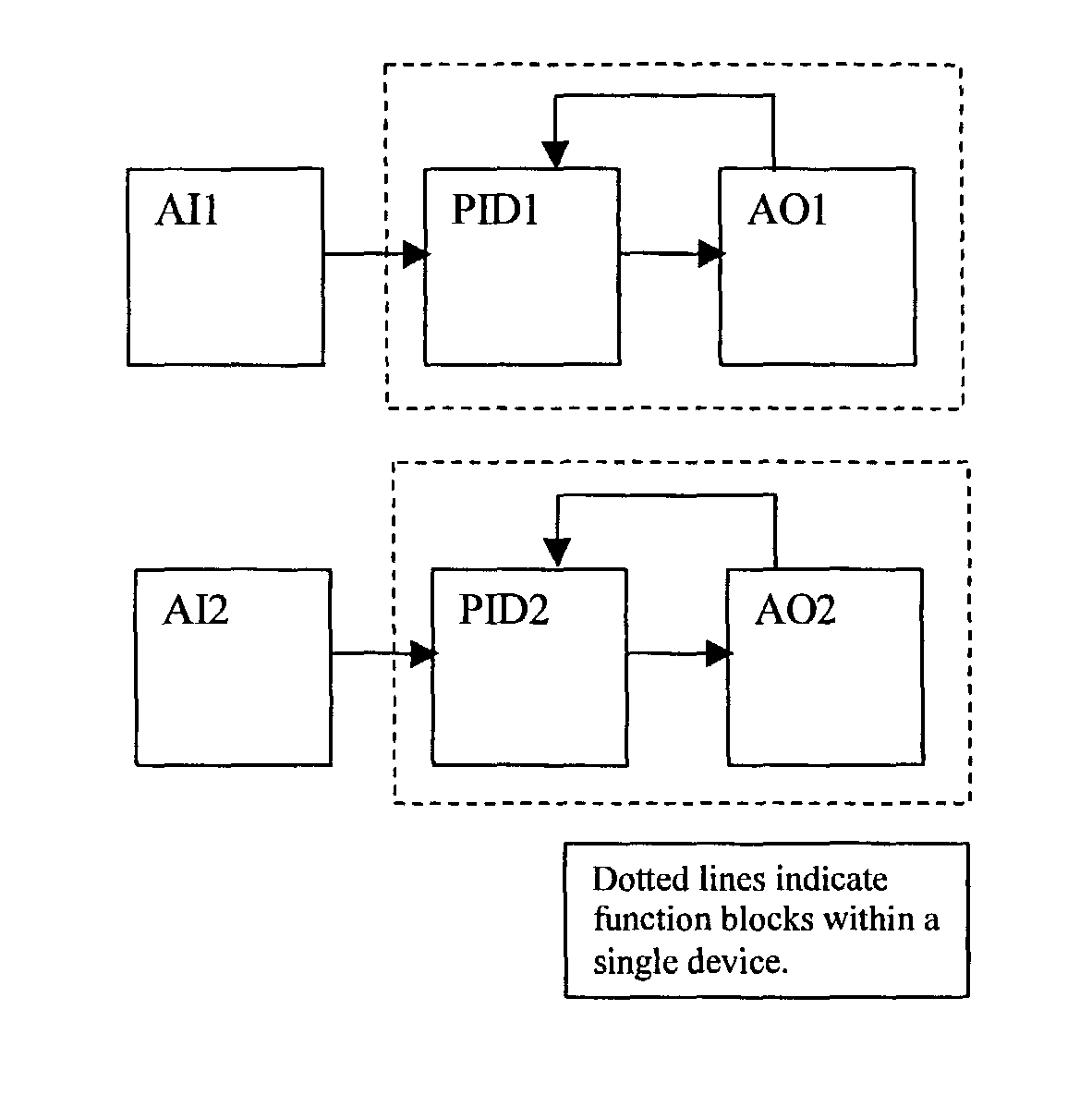

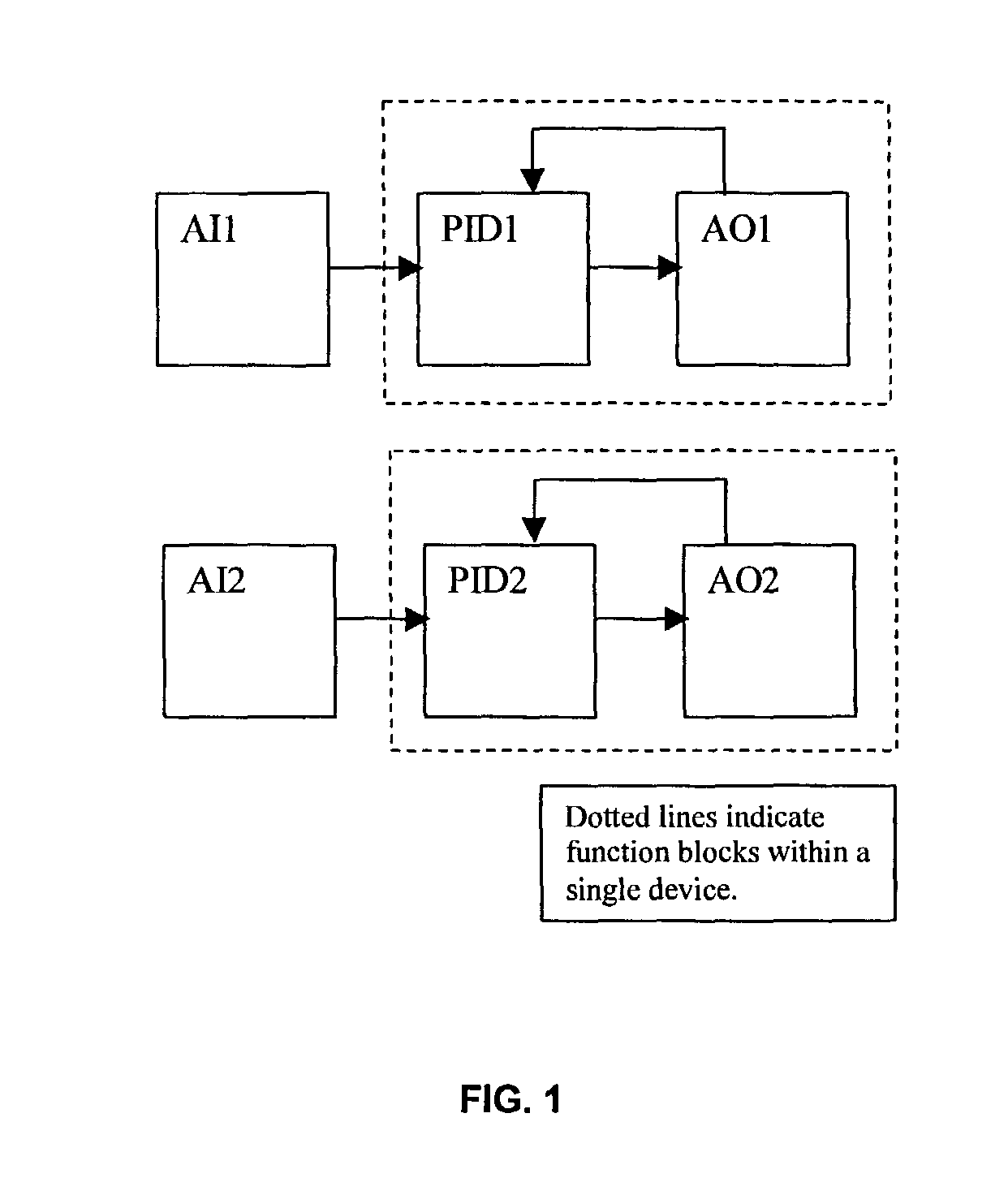

Control structure for reducing bus communication rate used for foundation in-situ bus

InactiveCN1549065AReduce communication burdenImprove real-time performanceAdaptive controlPredictive functionControl system

The control structure includes two pieces of equipment. The first equipment includes one analog amount input module connected to the sensor; and the second equipment includes control module, analog amount output module connected to the executor. The first equipment has one increased prediction control module and one control module with the same parameters as that in the second equipment; and the second equipment has also one increased prediction control module the same as that in the first equipment. Universal configuration software is used in configuring the parameter connection of the modules in the first equipment and the second equipment. The present invention reduces the bus network communication load to raise the real-time property and determinacy of bus network in data communication. The present invention also warns the error sampling data, acting as the second sensor to raise the stability of the control system.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

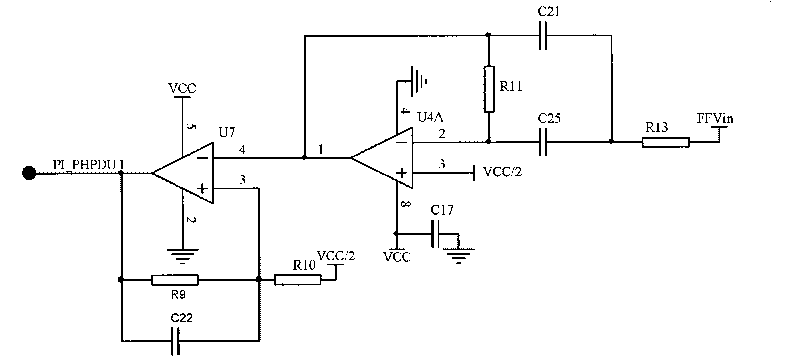

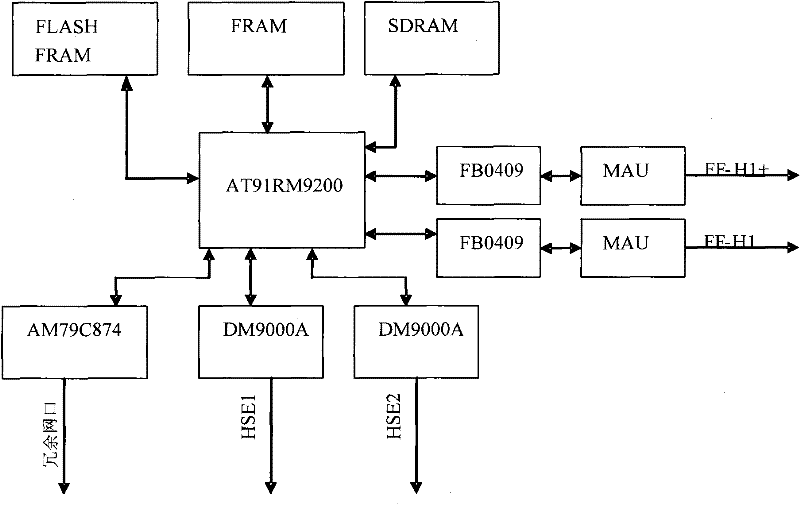

Fieldbus communication card

ActiveCN101729339AReduce power consumptionFlexible interfaceData switching by path configurationTotal factory controlAutomatic controlControl circuit

The invention relates to the field of automatic control, and in particular discloses a fieldbus communication card, which is used for coding and decoding fieldbus data based on an FBC0409 fieldbus controller. The fieldbus communication card also comprises a fieldbus signal filter circuit for receiving bus signals, a bus voltage signal modulation circuit for converting coded digital signals into voltage signals corresponding to the waveform of the bus signals, a master control circuit communicated with the fieldbus communication controller and other peripheral equipment, and a bus power supply / current modulation circuit. The fieldbus communication card solves the problem that Foundation Fieldbus and PROFIBUS PA fieldbus communication cards cannot be developed currently at home, gets rid of dependence on imported fieldbus instruments, and has the characteristics of running two fieldbus protocols of Foundation Fieldbus and Profibus PA based on the same hardware, having low cost and the like.

Owner:MICROCYBER CORP

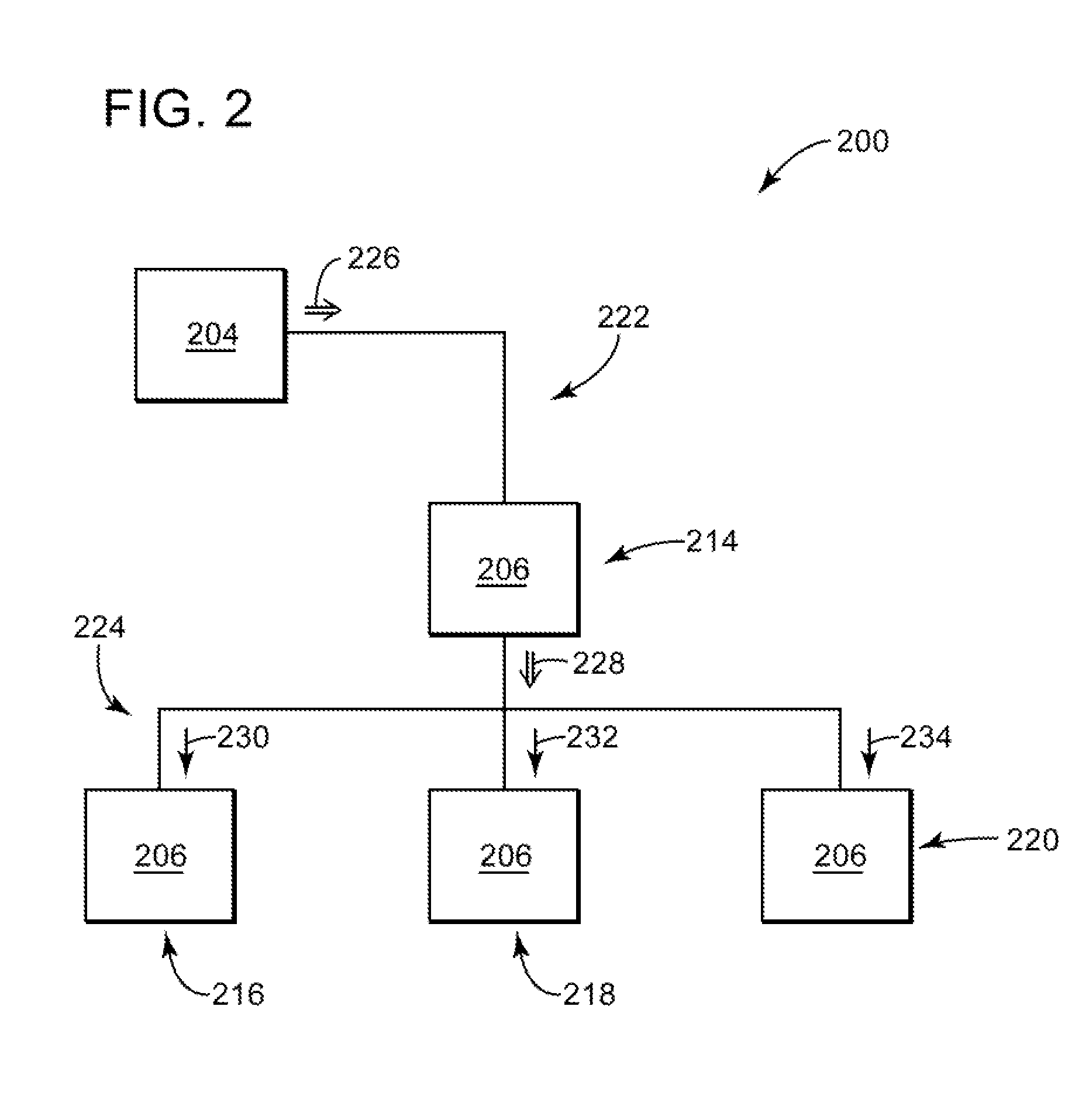

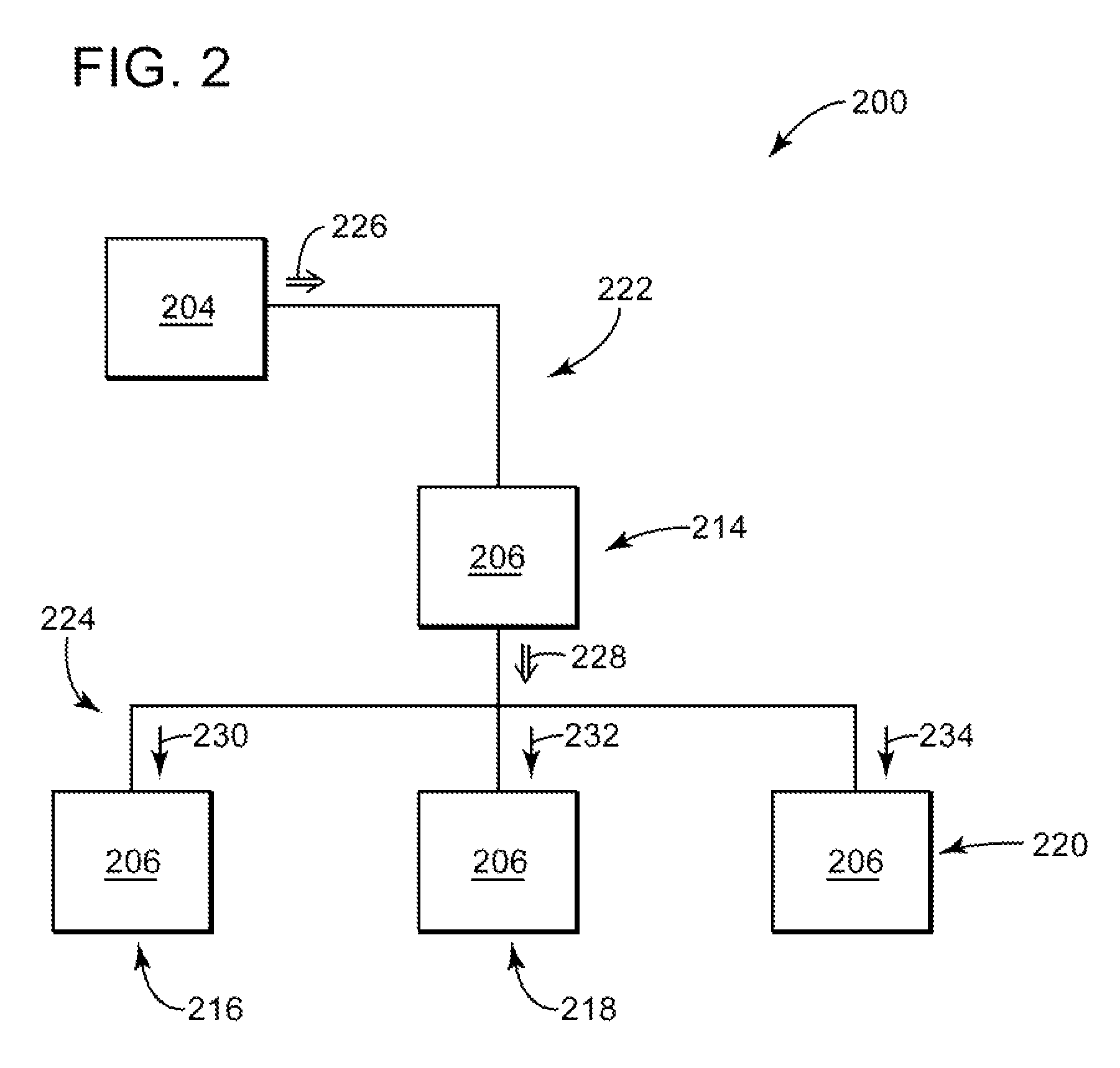

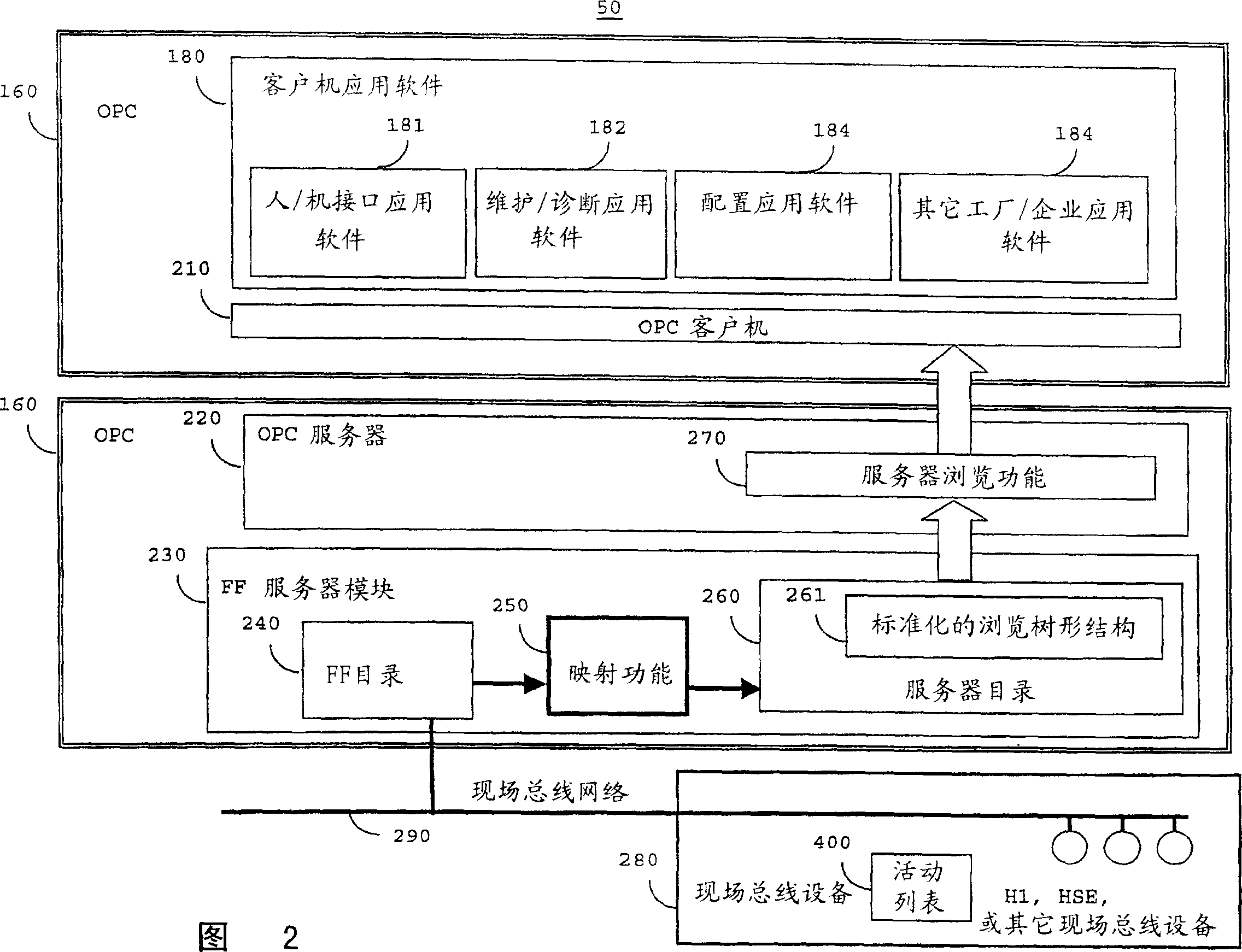

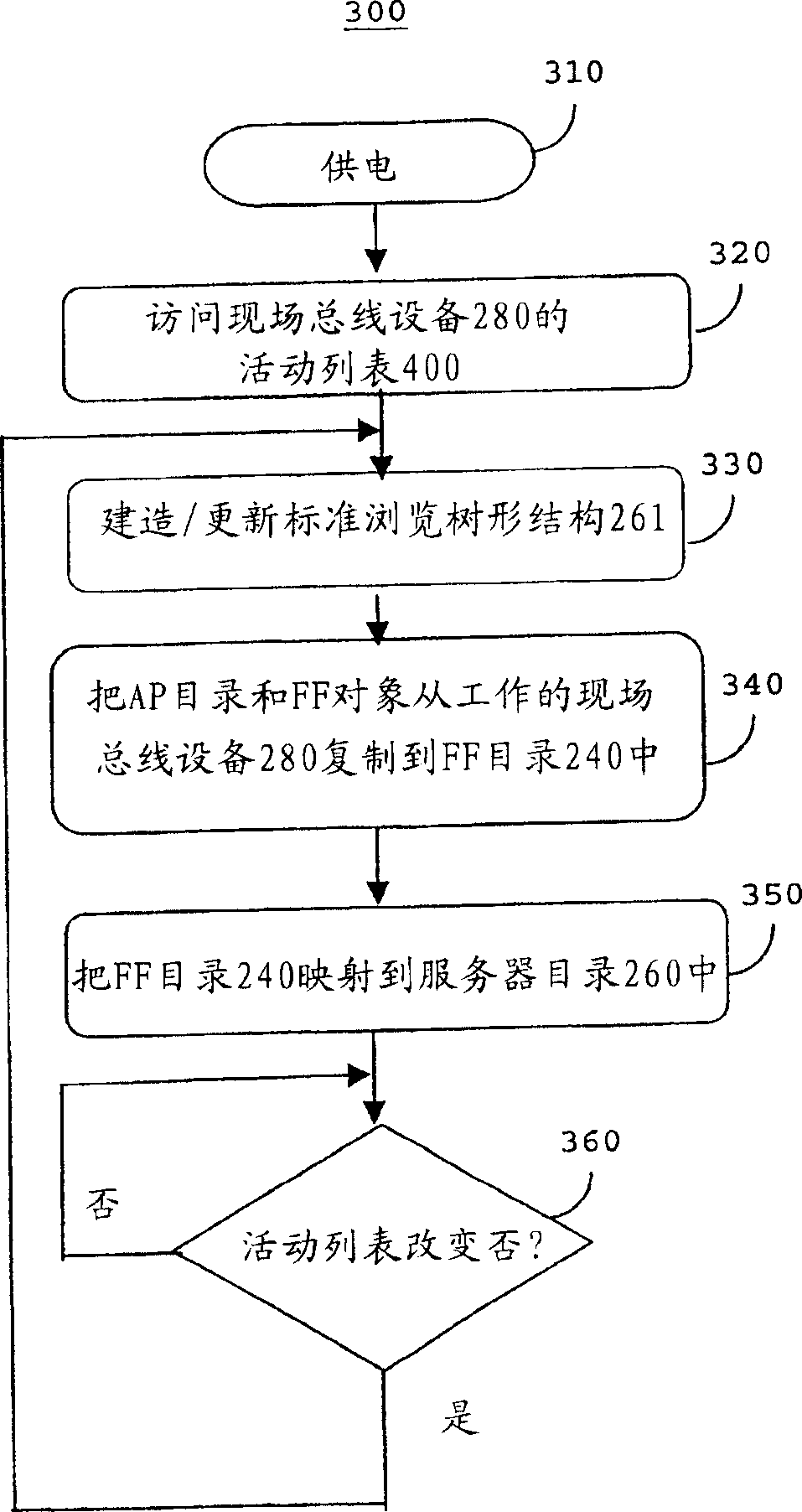

Foundation fieldbus server providing device information using a live-list-based dynamic directory

A new and improved control system architecture with a single server interface for application software that eliminates manual intervention by providing online, immediate access to information needed for plant / enterprise optimization, operation, configuration, maintenance and diagnostic application software. The control system architecture provides a method of dynamically creating a server directory to enable automatic access in an integrated control system. The method includes accessing a live list of fieldbus devices, building / updating a browse tree structure, the browse tree structure defining a branch and leaf node organization and naming for and data from the fieldbus devices, copying AP directories and FF objects from active fieldbus devices into a FF directory and mapping the FF Directory into the server directory.

Owner:FIELDBUS FOUND

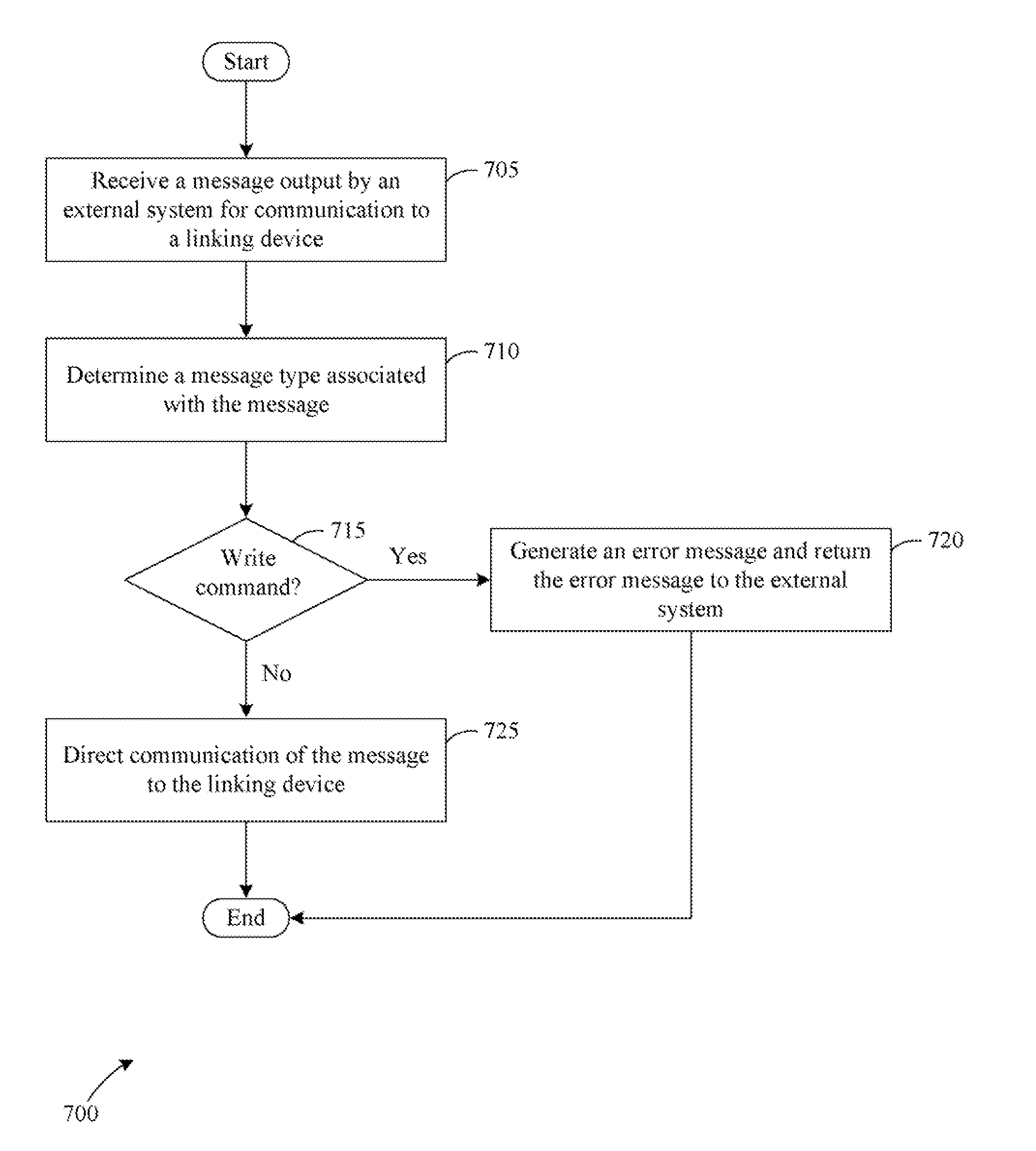

Systems and methods for write protecting foundation fieldbus linking devices

Systems and methods for write protecting Foundation Fieldbus linking devices are described. A message output by an external system for communication to a Foundation Fieldbus linking device may be received by a gateway device. The linking device may be identified by a virtual address included in the received message. The gateway device may determine whether the message includes a command to write data to the linking device or a Foundation Fieldbus device connected to the linking device. If it is determined that the message does not include a command to write data, then the gateway device may direct communication of the message to the linking device. If, however, it is determined that the message includes a command to write data, the gateway device may generate an exception for preventing the requested write operation.

Owner:GENERAL ELECTRIC CO

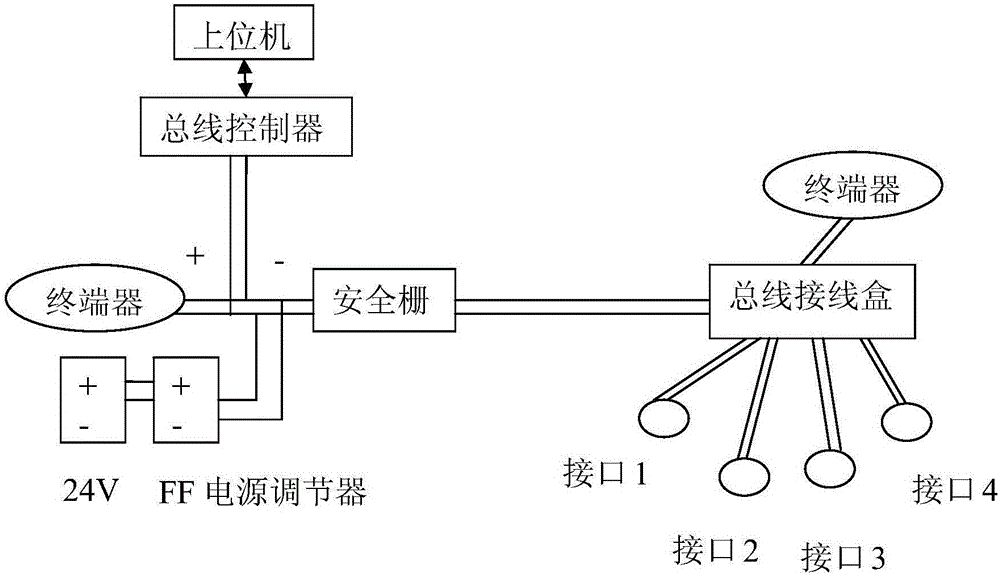

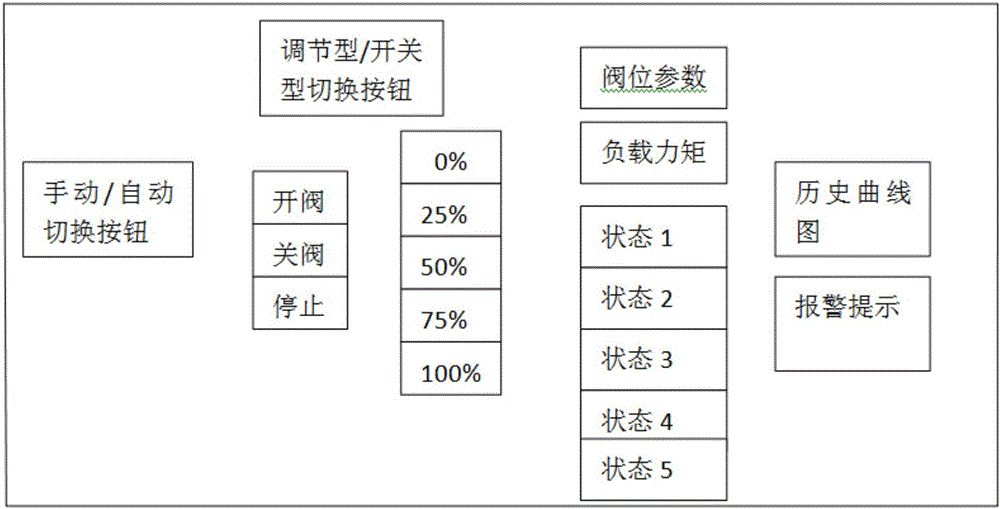

Full-digital remote automatic test system for electric actuating mechanism

InactiveCN105841749AImplement remote testingCompact structureMeasurement devicesTest efficiencyGrating

The invention relates to a full-digital remote automatic test system for an electric actuating mechanism. The system comprises a Foundation Fieldbus, a bus power supply which supplies power and a bus controller cooperating with the Foundation Fieldbus; and the bus power supply, a guard grating and the bus controller are connected with the Foundation Fieldbus, the bus controller is connected with a host computer, and the Foundation Fieldbus is further connected with bus interfaces for testing the Foundation Fieldbus type electric actuating mechanism. The full-digital remote automatic test system is compact in structure, high in automatic degree and safe and reliable, can test the electric actuating mechanism remotely, and improves the test efficiency.

Owner:WUXI LAIPUER TECH CO LTD

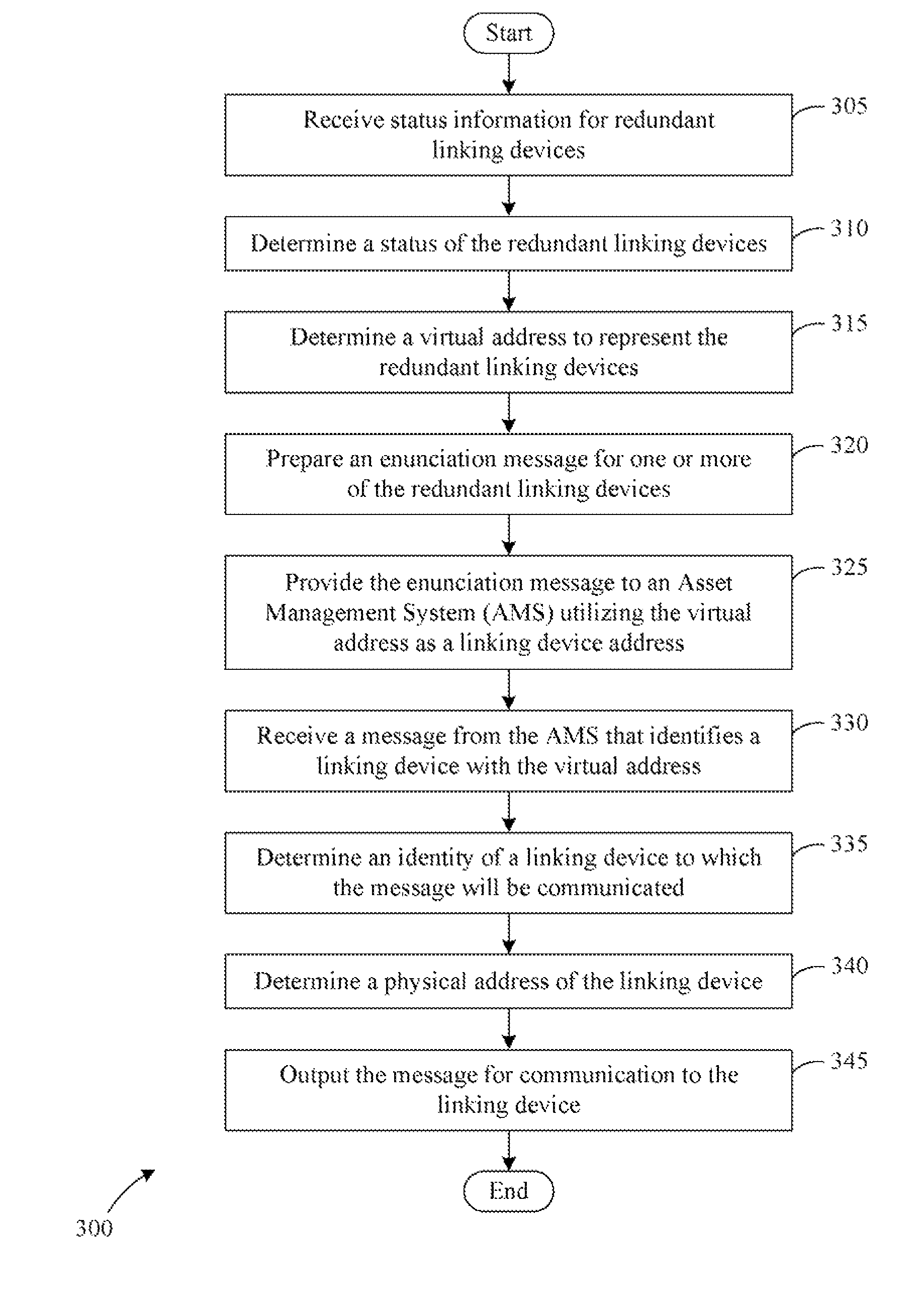

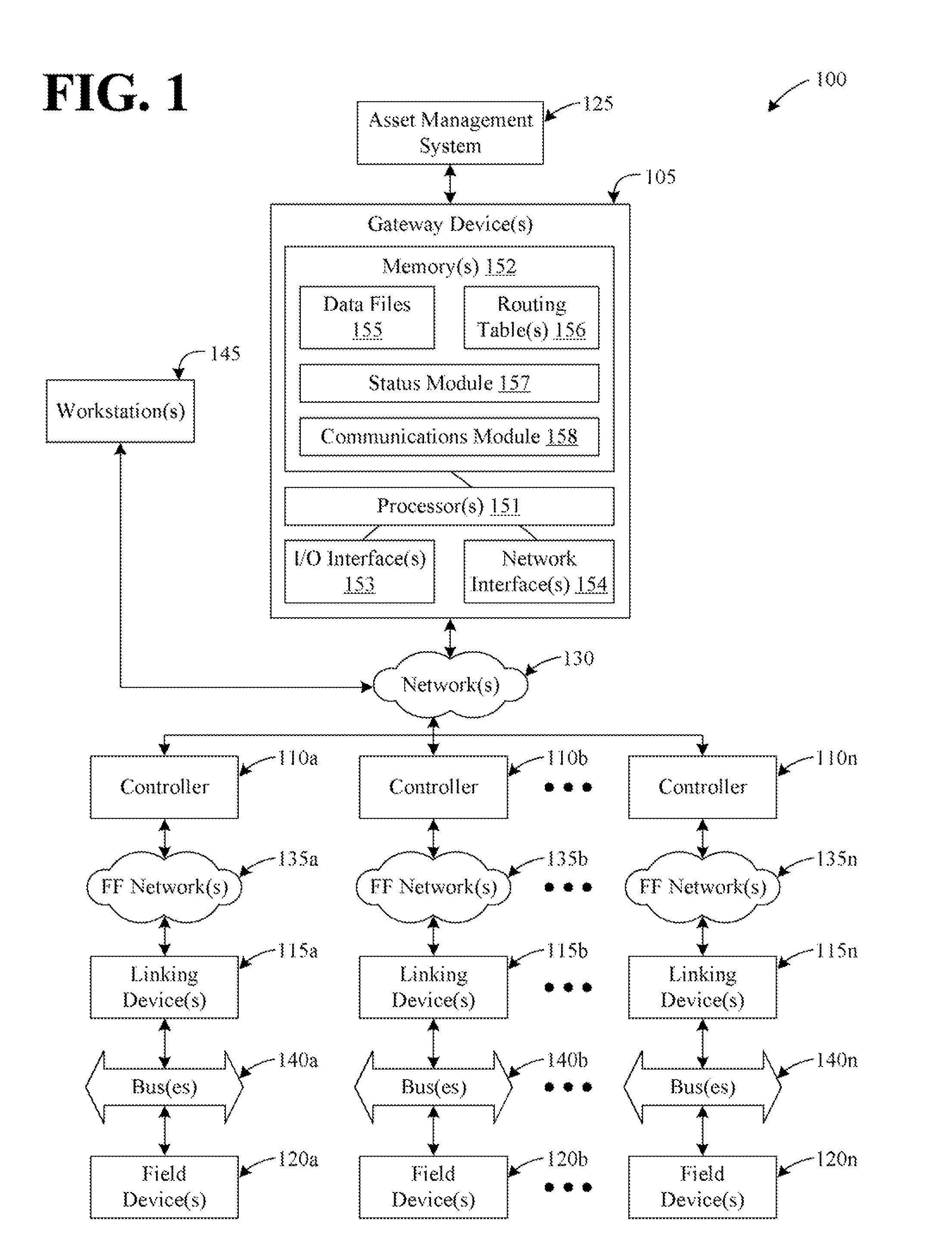

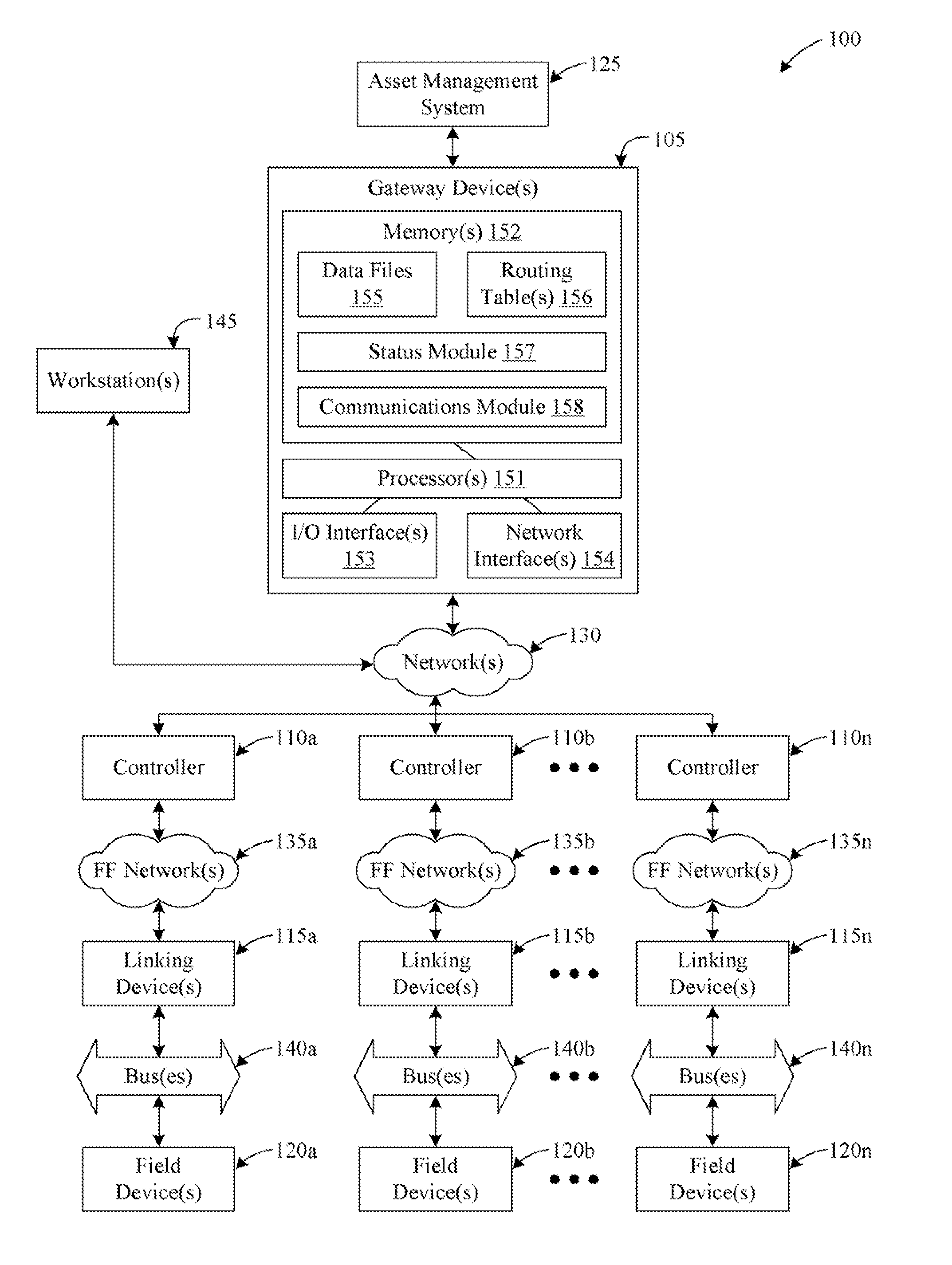

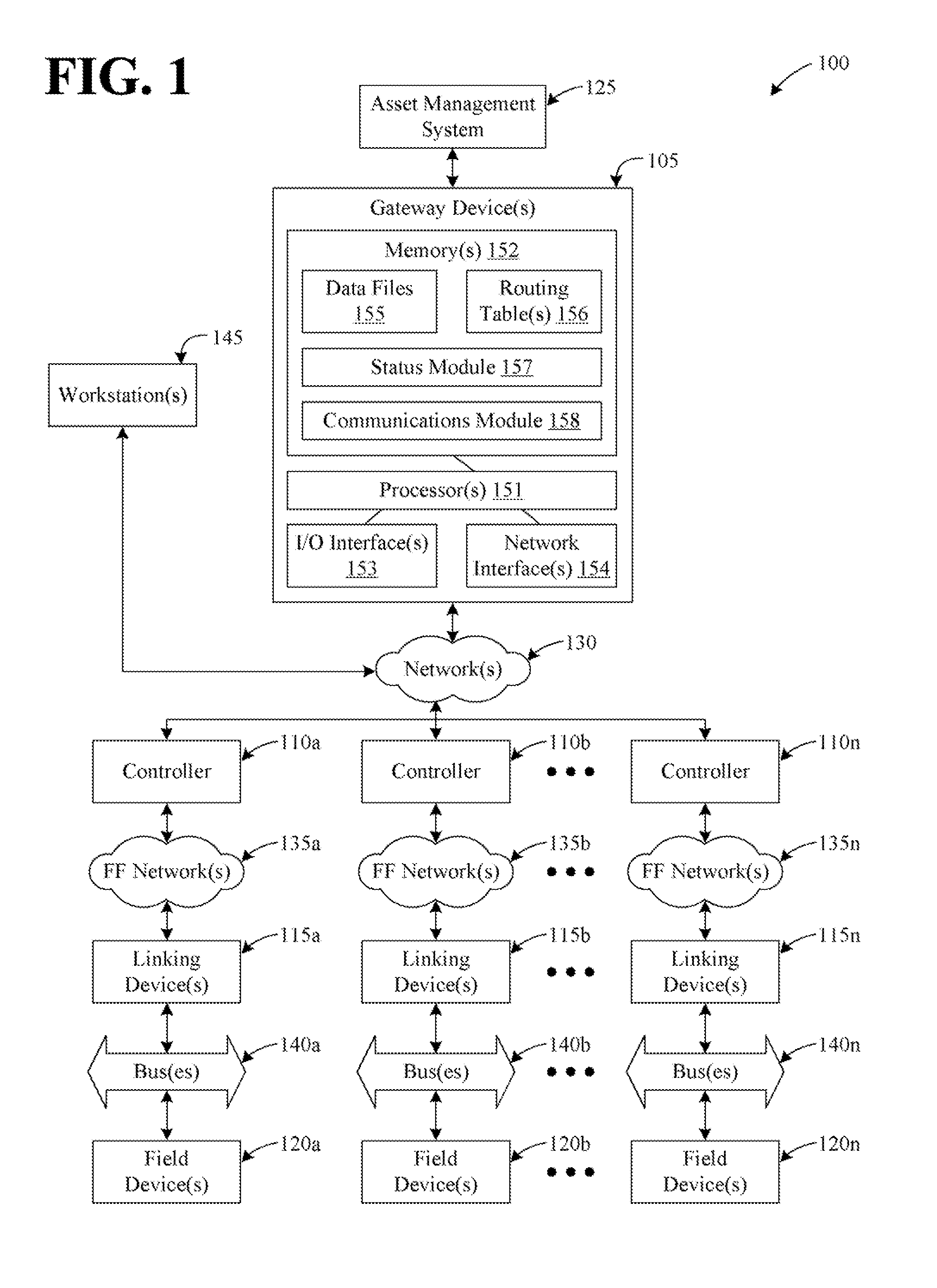

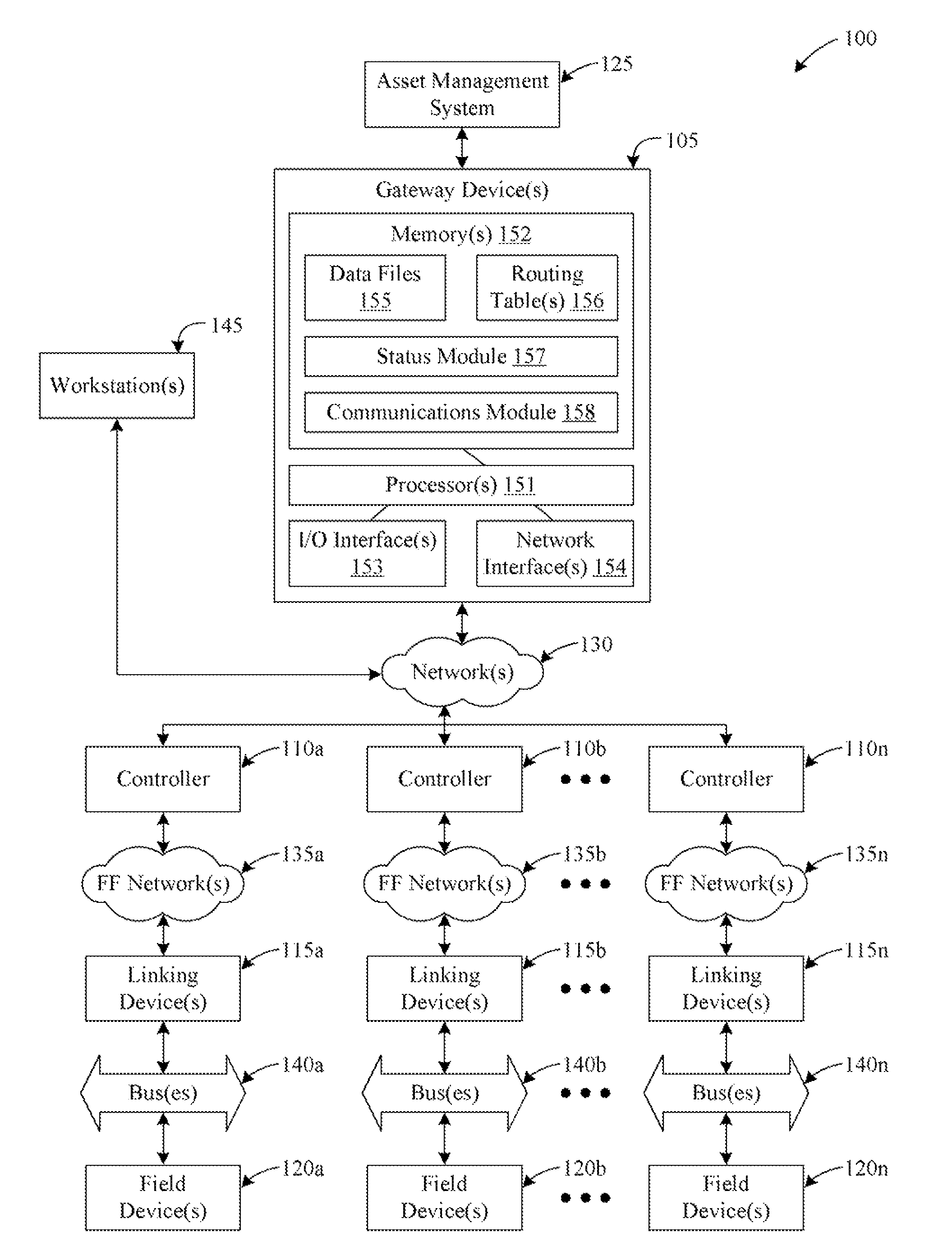

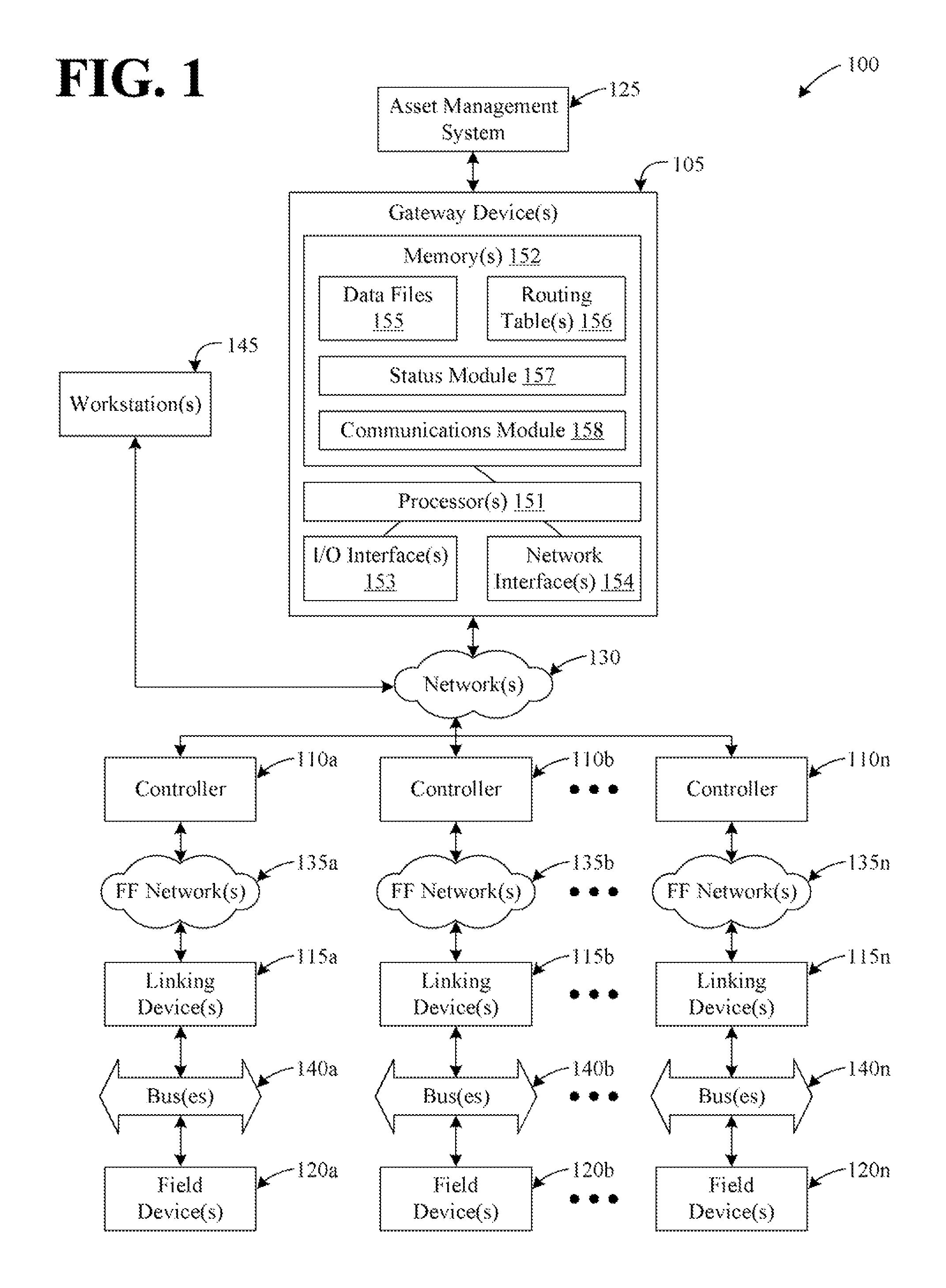

Systems and methods for facilitating communication with foundation fieldbus linking devices

ActiveUS8868732B2Facilitate communicationDigital computer detailsNetwork connectionsEthernetField bus

Owner:GE INFRASTRUCTURE TECH INT LLC

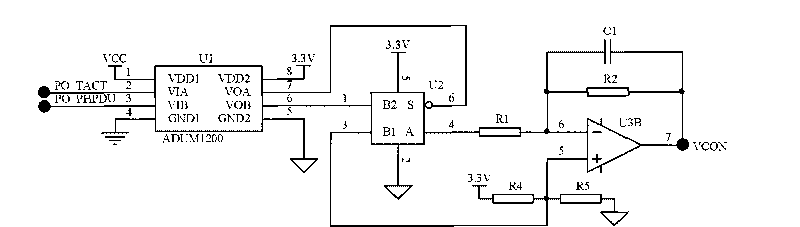

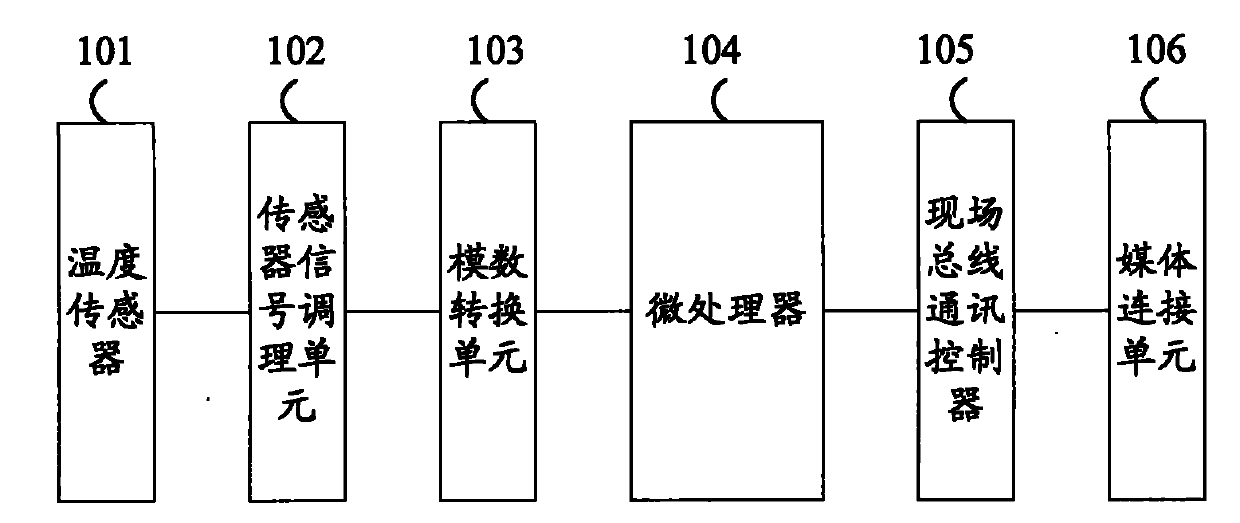

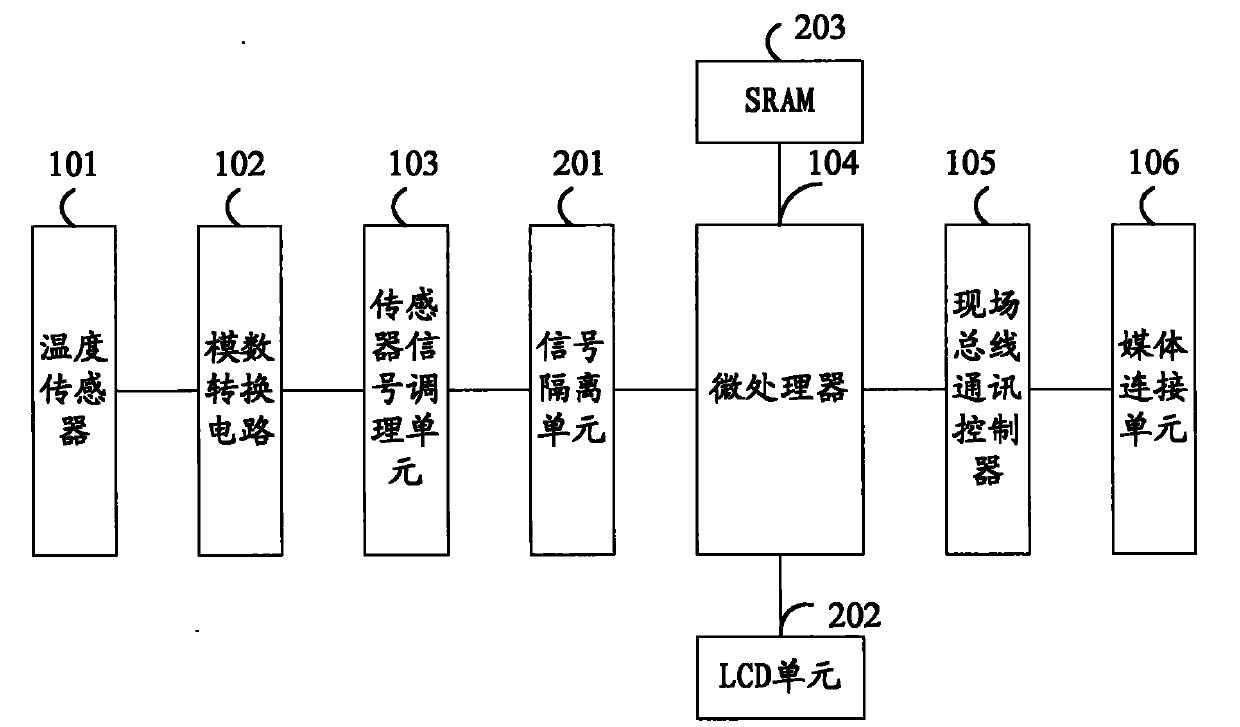

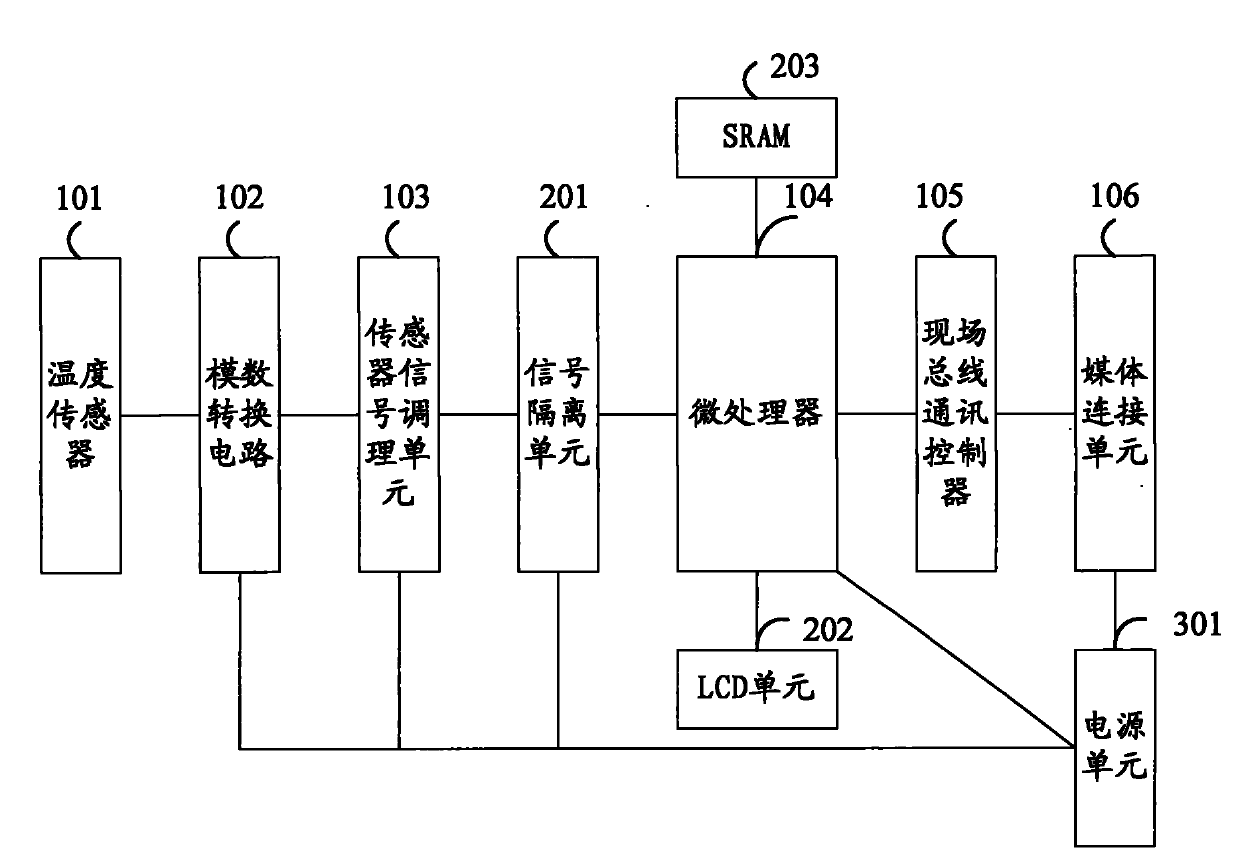

Foundation field bus (FF) H1 temperature measuring device

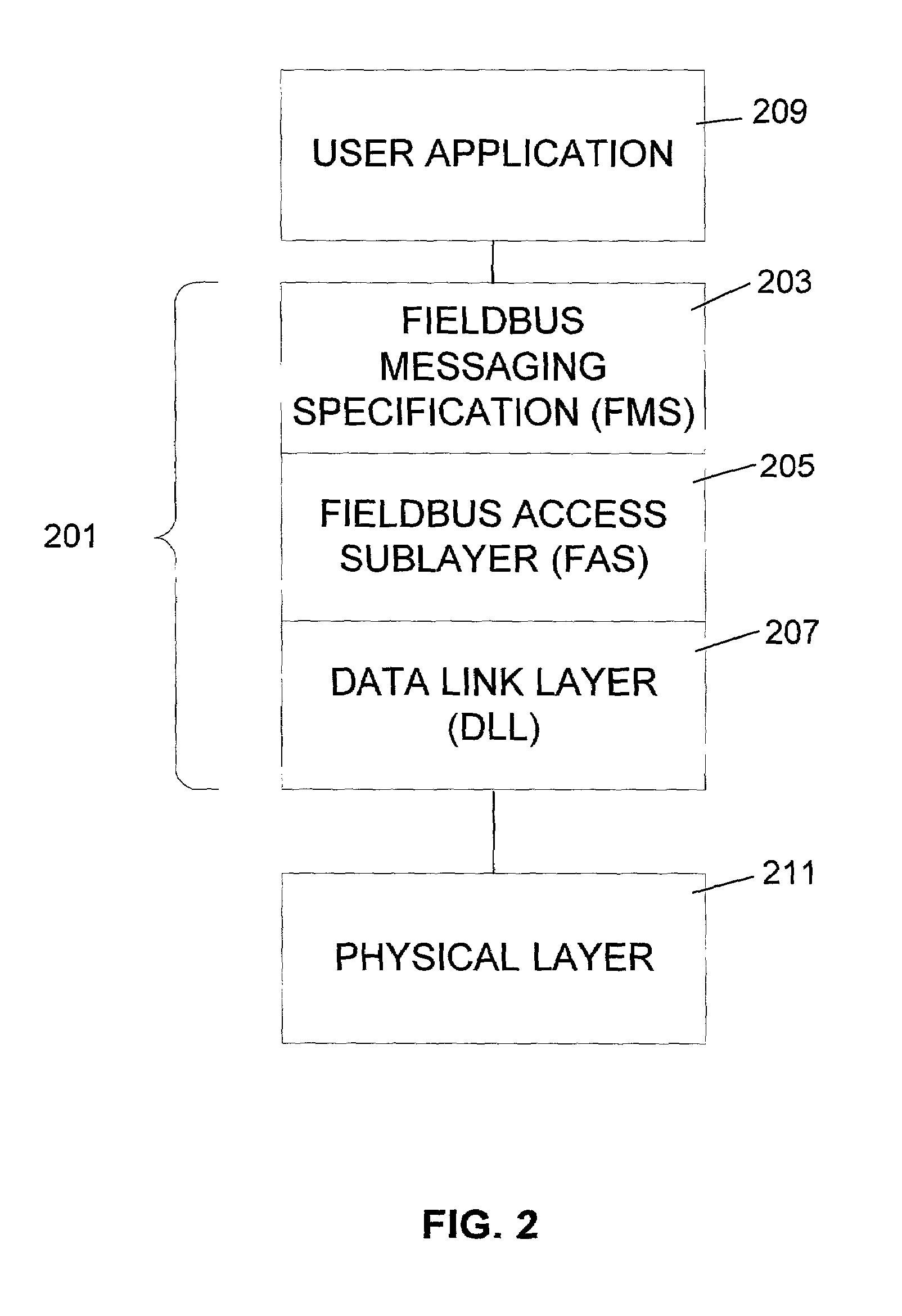

InactiveCN102087144AAccurate measurementImprove anti-interference abilityThermometer detailsElectric signal transmission systemsEngineeringData link layer

The invention provides a foundation fieldbus (FF) H1 temperature measuring device. The device comprises a temperature sensor, a sensor signal regulating unit, an analog-to-digital conversion unit, a microprocessor, a field bus communication controller and a media connecting unit, wherein the temperature sensor collects temperature of point testing equipment; the sensor signal regulating unit performs signal amplification and filter processing on the temperature collected by the temperature sensor, and transmits the processed signal to the analog-to-digital conversion unit; the analog-to-digital conversion unit performs analog-to-digital conversion on the signal transmitted by the sensor signal regulating unit, and transmits the converted digital signal to the microprocessor; the microprocessor performs linear processing and temperature compensation on the digital signal, and transmits the processed signal to the field bus communication controller; the field bus communication controller converts the signal transmitted by the microprocessor into FF H1 data link layer data, and transmits the data to the media connecting unit; and the media connecting unit converts the data link layer data into physical layer data, and transmits the physical layer data to the FF H1. The device performs transmission by adopting the digital signal, and has strong interference resistance, so the measured temperature is more accurate.

Owner:BEIJING HUAKONG TECH

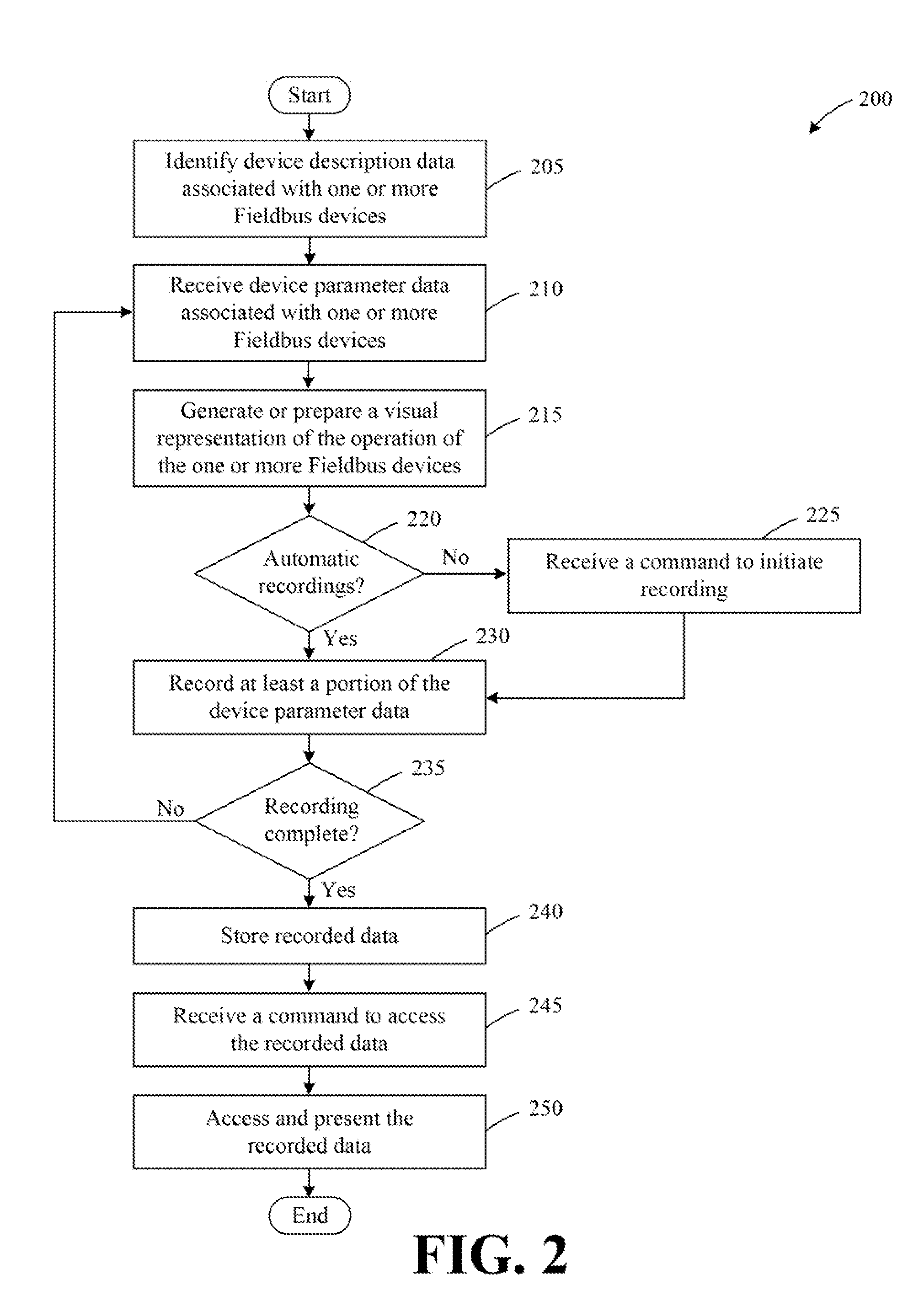

Systems and methods for recording data associated with the operation of foundation fieldbus devices

ActiveUS20130124670A1Programme controlMultiple digital computer combinationsEmbedded systemFOUNDATION fieldbus

Systems and methods are provided for recording data associated with the operation of Foundation Fieldbus devices. Device parameter data associated with one or more Foundation Fieldbus devices may be received by a device comprising one or more computers. A visual representation of the operation of the one or more Foundation Fieldbus devices may be generated by the device receiving the device parameter data. The device may then record at least a portion of the device parameter data received to generate the visual representation.

Owner:GENERAL ELECTRIC CO

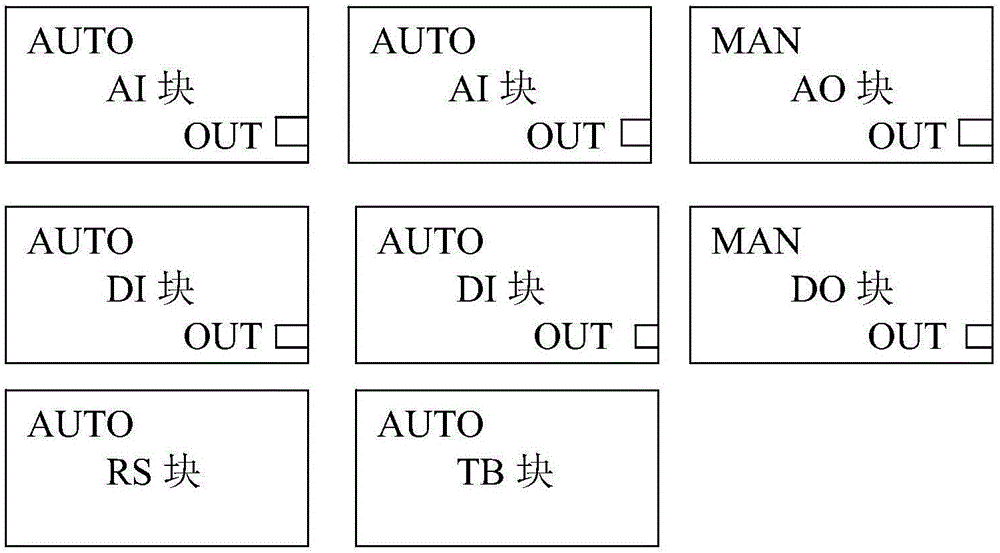

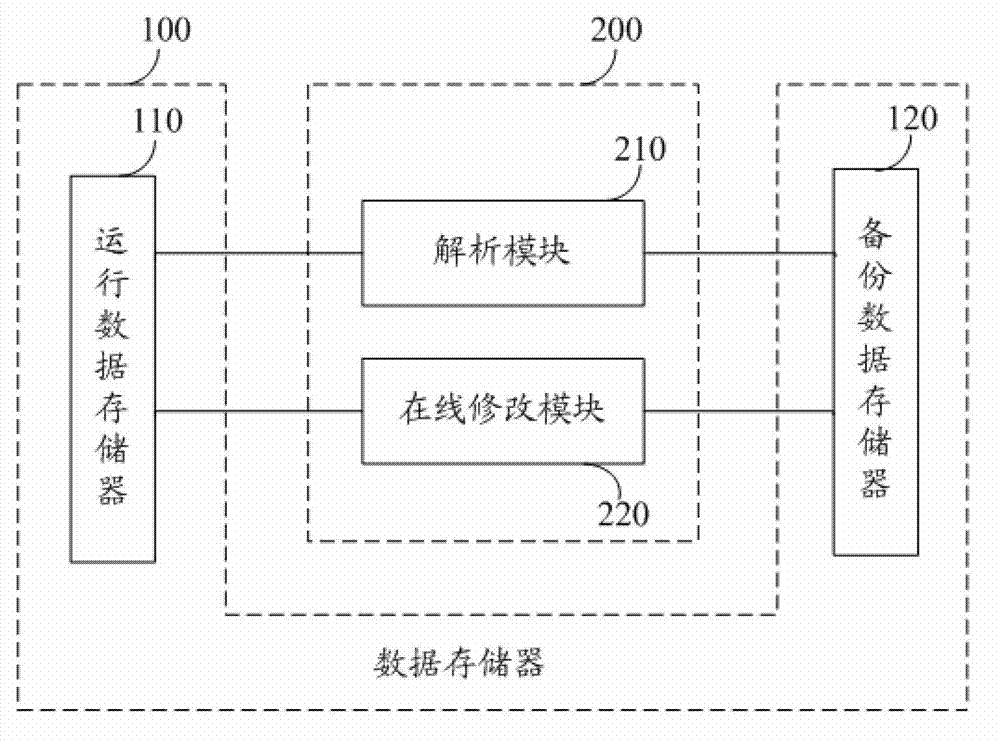

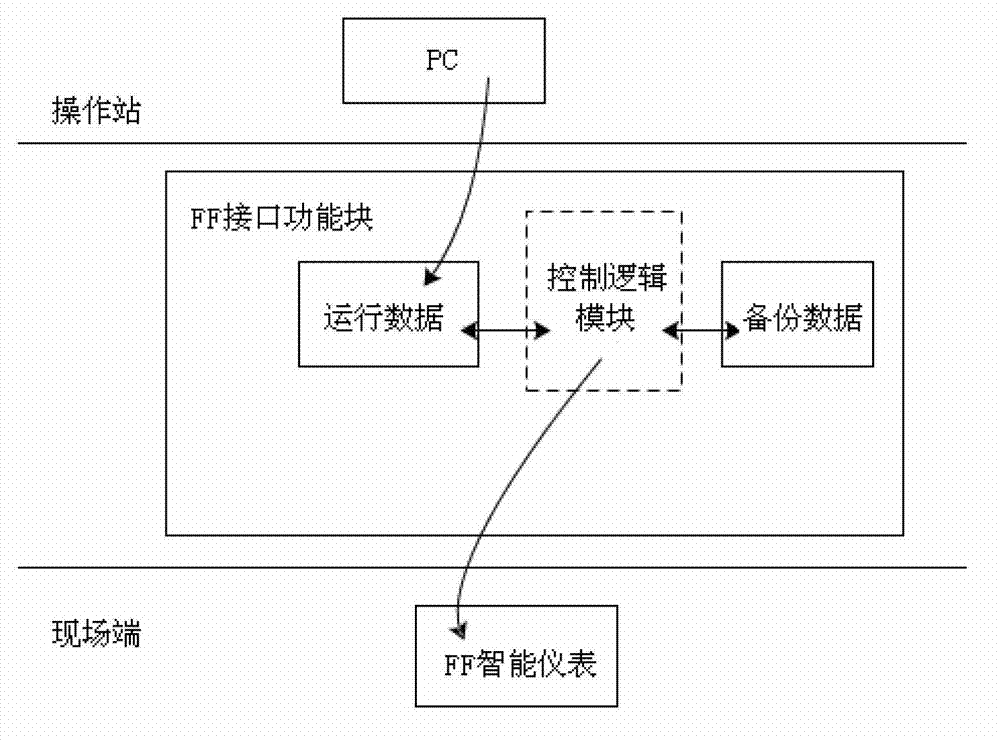

Functional block with FF (foundation fieldbus) interface

ActiveCN102854862AReduce loadProgramme total factory controlDistributed control systemComputer module

The invention discloses a functional block with an FF (foundation fieldbus) interface. The functional block comprises a data storage and a control logic module. The data storage comprises an operational data storage which opens for the external upper layer module of DCS (distributed control system). By real-time monitoring and online modifying data in the operational data storage, the external upper layer module of the DCS monitors in real time and modifies online the data of an instrument functional block. The control logic module only modifies the data of the instrument functional block when data content in the operational data storage changes, namely, modification is performed when data in the instrument functional block needs to be modified, and accordingly network load is lowered. By the functional block with the FF interface, the DCS is can control an FF device. The functional block can be built in a central control unit of the DCS. Mixing control of the DCS and the FF device can be achieved by building control schemes between the central control unit and the lower field instruments by the aid of the external upper layer module of the DCS, functions such as real-time monitoring, online modifying, warning and browsing can be performed by the DCS to the instrument functional block.

Owner:ZHEJIANG SUPCON TECH

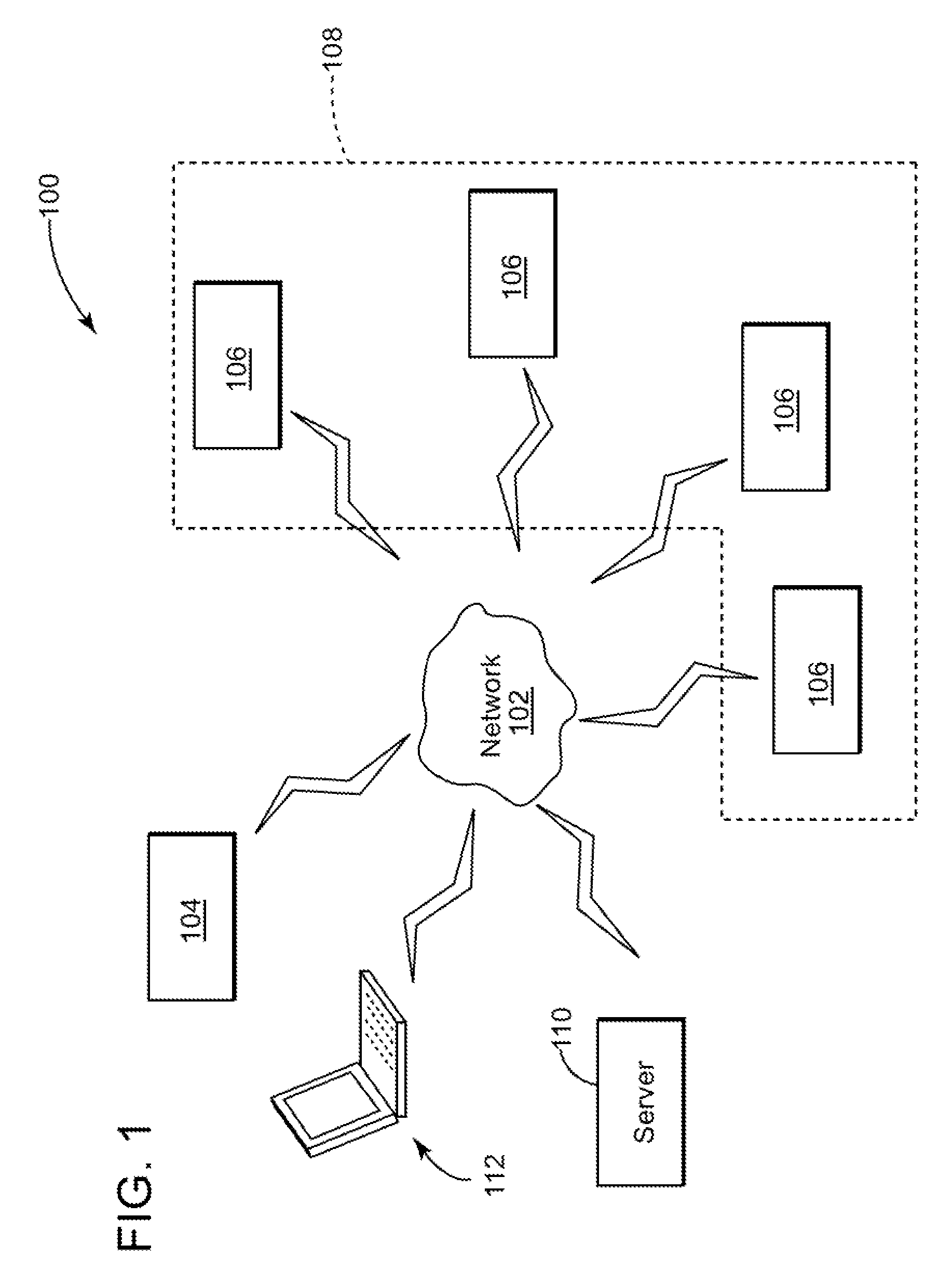

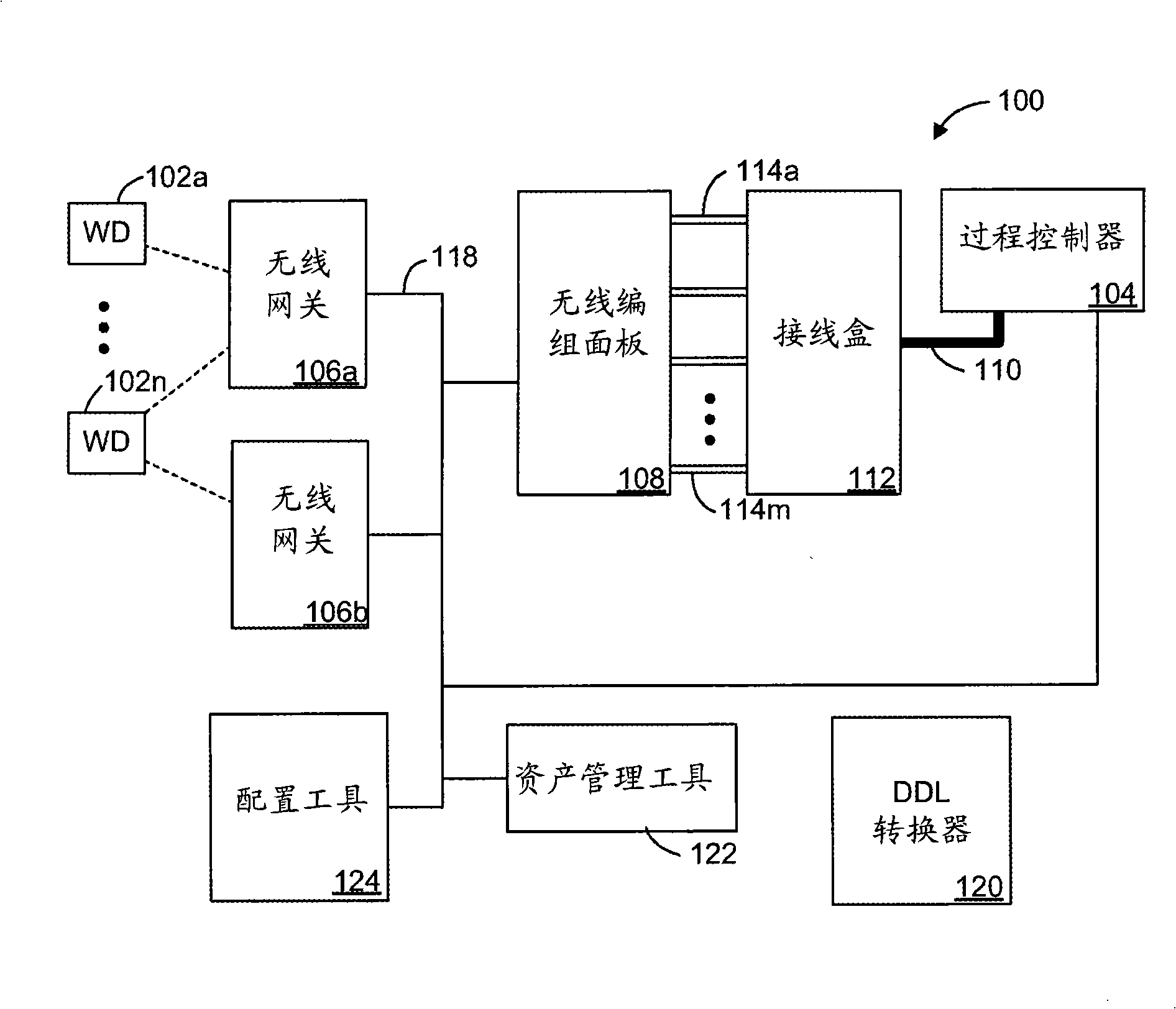

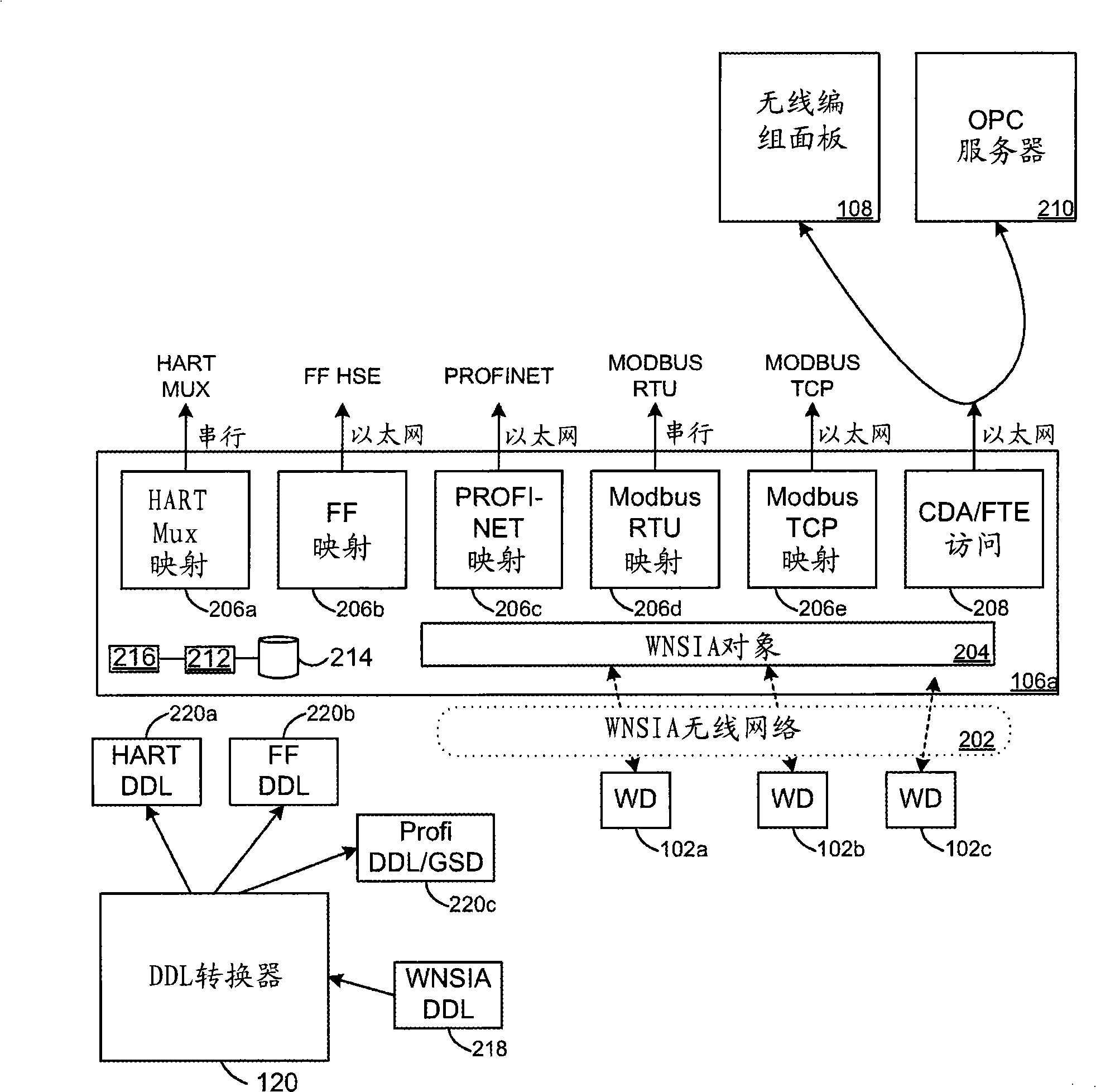

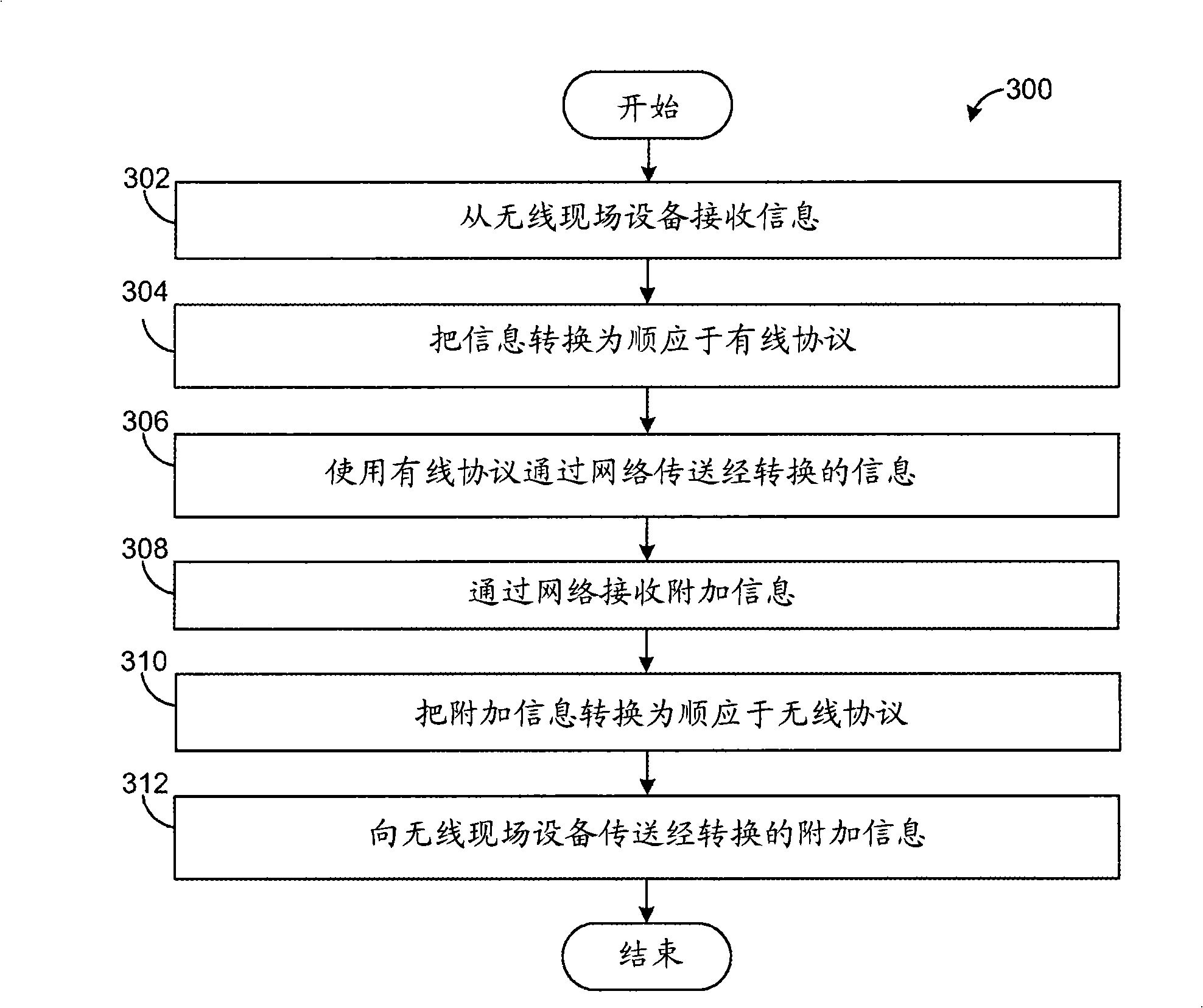

Method for integrating wireless field devices in a process control system with a wired protocol

An apparatus is provided for facilitating integration of a wireless field device (such as a wireless sensor or actuator) and a wired protocol that is used in a process control system. The apparatus supports a wireless field device protocol for communicating with the wireless field device. The apparatus also supports a wired field device protocol for communicating with other components of the process control system over a network. The apparatus could map a wireless application model associated with the wireless field device protocol to a wired application model associated with the wired field device protocol. The apparatus could actually support multiple mappings from the wireless application model to wired application models associated with multiple wired field device protocols. As particular examples, the wired field device protocol(s) could include the HART, Foundation Fieldbus, Profibus, and / or Modbus protocols. The network could represent an Ethernet network or a serial network.

Owner:HONEYWELL INT INC

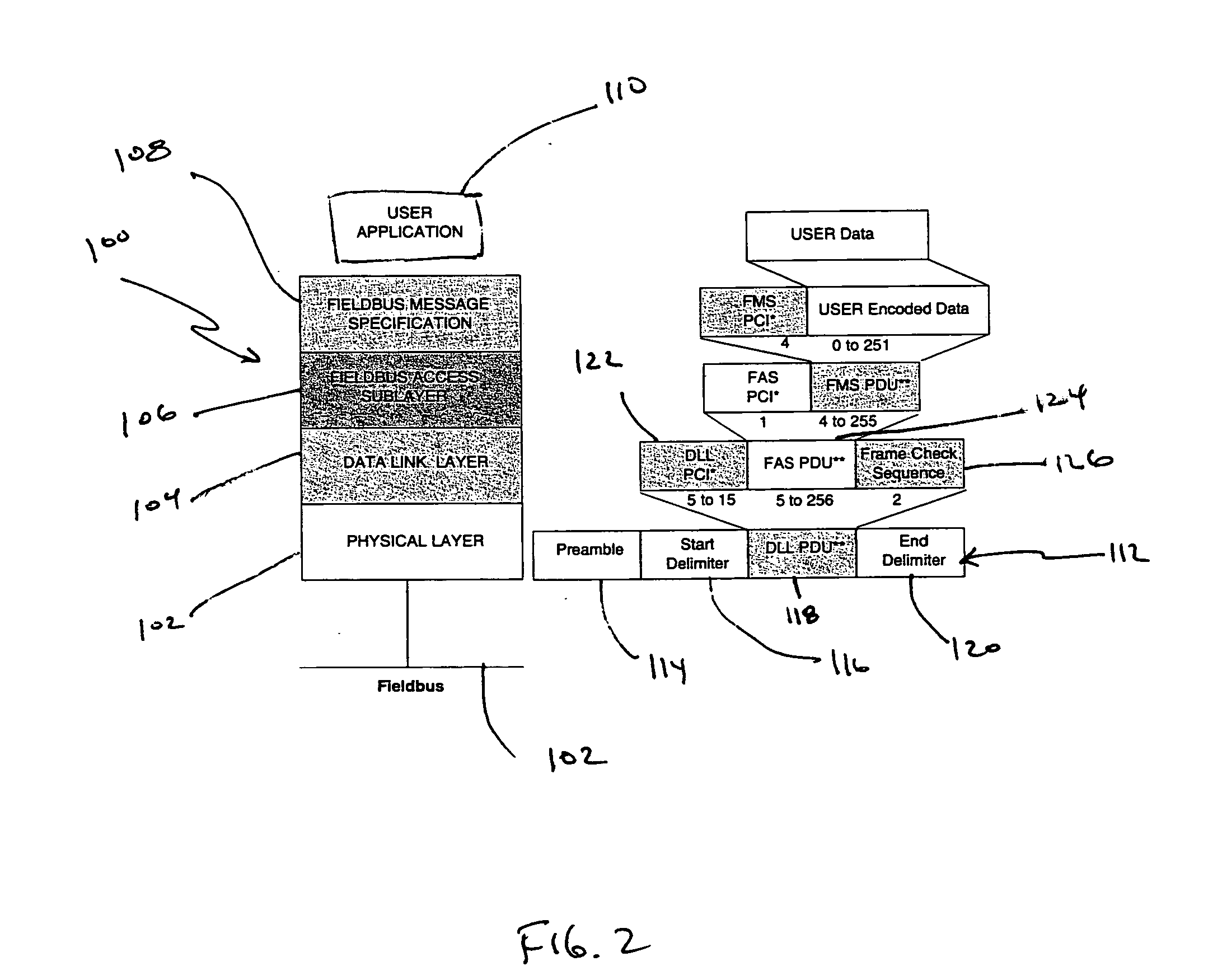

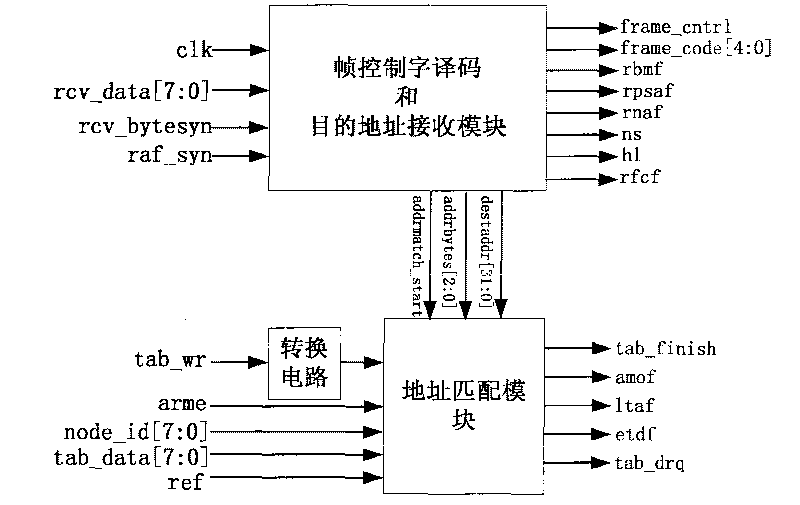

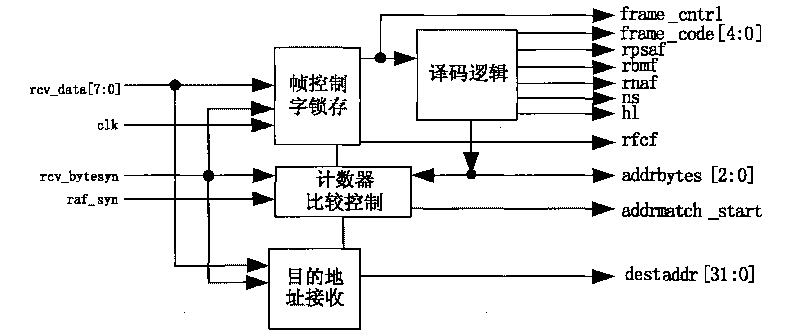

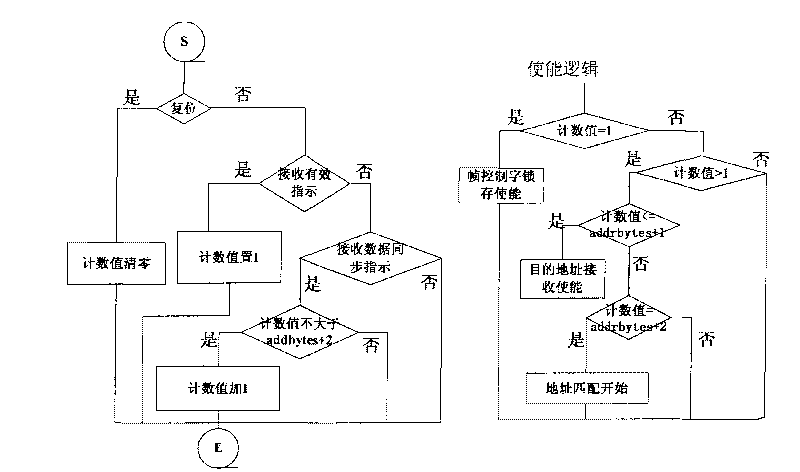

FF (foundation field) bus frame type recognizer

The invention relates to a FF (foundation field) bus frame type recognizer arranged in a data link layer of a FF field bus. The FF bus frame type recognizer comprises a frame controlled word coding and target address receiving module, an address matching module, and a conversion circuit, wherein the frame controlled word coding and target address receiving module is used for generating frame control information, an address matching result and relevant parameters of a protocol data unit of the data link layer based on data signals received from the field bus and sending the frame control information, the address matching result and the relevant parameters of the protocol data unit of the data link layer to an upper processing unit of the data link layer; the address matching module is used for carrying out address matching processing on received address table data in the data link layer and an address data available indicating signal received through the conversion circuit and outputting to the upper processing unit of the data link layer; and the conversion circuit is used for carrying out timing adjustment on the address data available indicating signal and sending the adjusted address data available indicating signal to the address matching module. The invention can extract the type information of a DLPDU (data link protocol data unit), can identify the long address or the short address of the DLPDU, can extract the address information of the DLPDU, and can be implemented in various modes of FPGA (field programmable gate array), CPLD (complex programmable logic device), IP (internet protocol) and the like.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

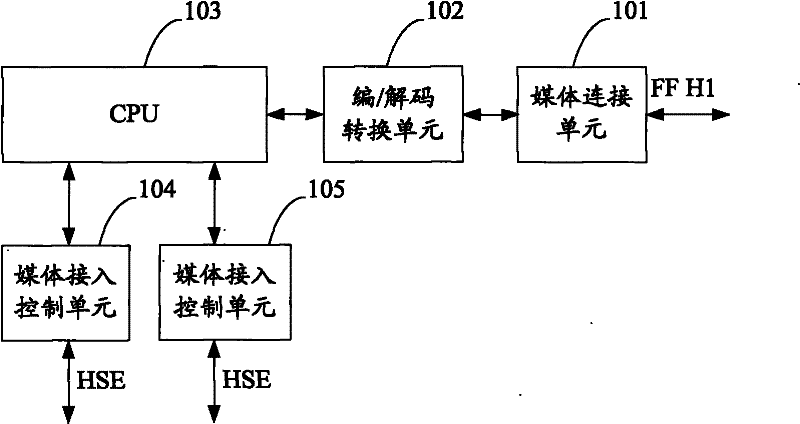

A FOUNDATION fieldbus gateway

The present invention relates to the technical field of the Foundation Fieldbus, and discloses a Foundation Fieldbus gateway, comprising: a media connection unit connected in sequence, an encoding / decoding conversion unit, a CPU, and two mutually thermally redundant modules connected to the CPU. The backup media access control unit; the media connection unit has an FF H1 interface; the media access control unit has an adaptive rate HSE interface. The invention can effectively improve the performance of the gateway and the reliability of data transmission.

Owner:BEIJING HUAKONG TECH

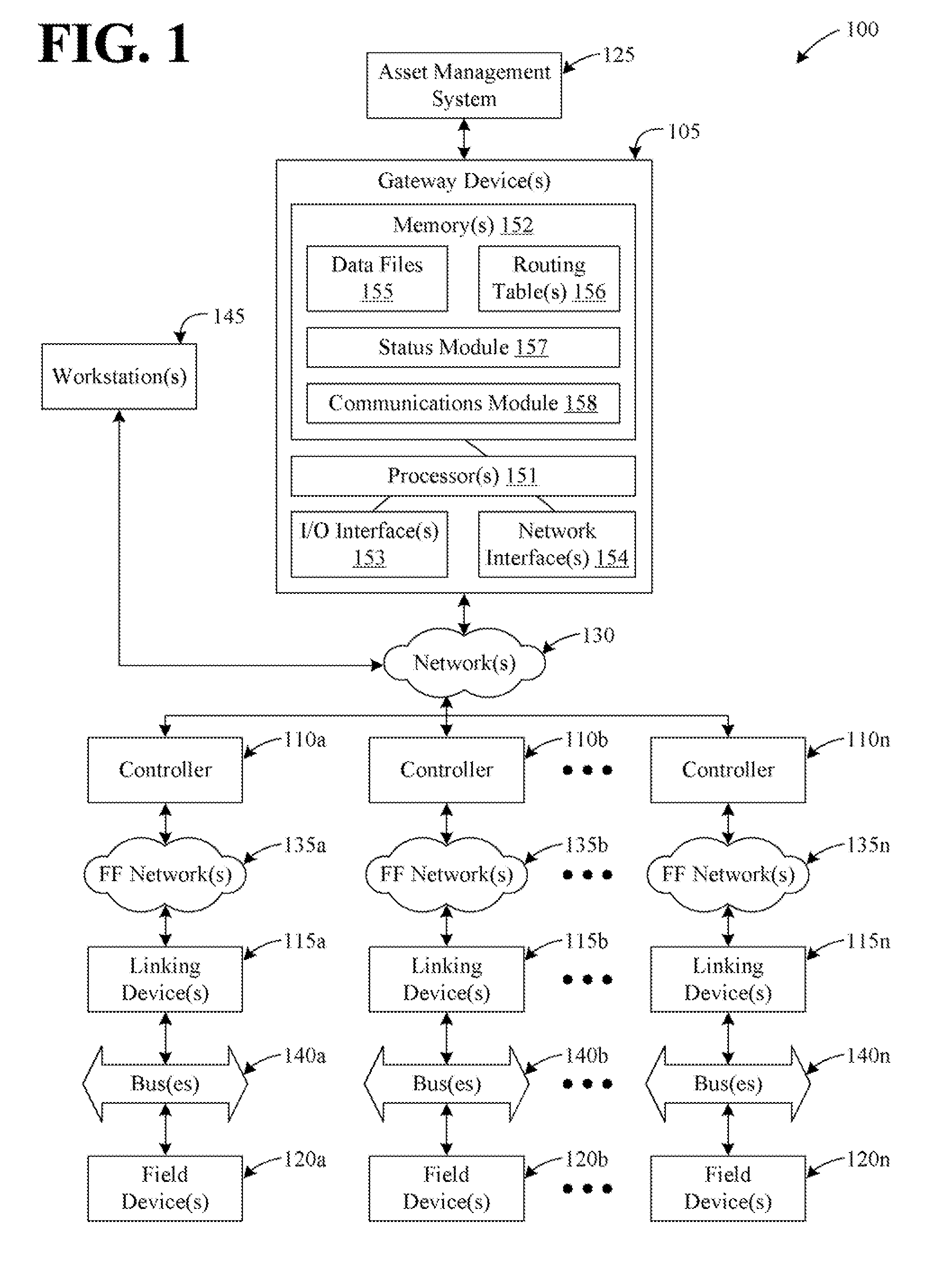

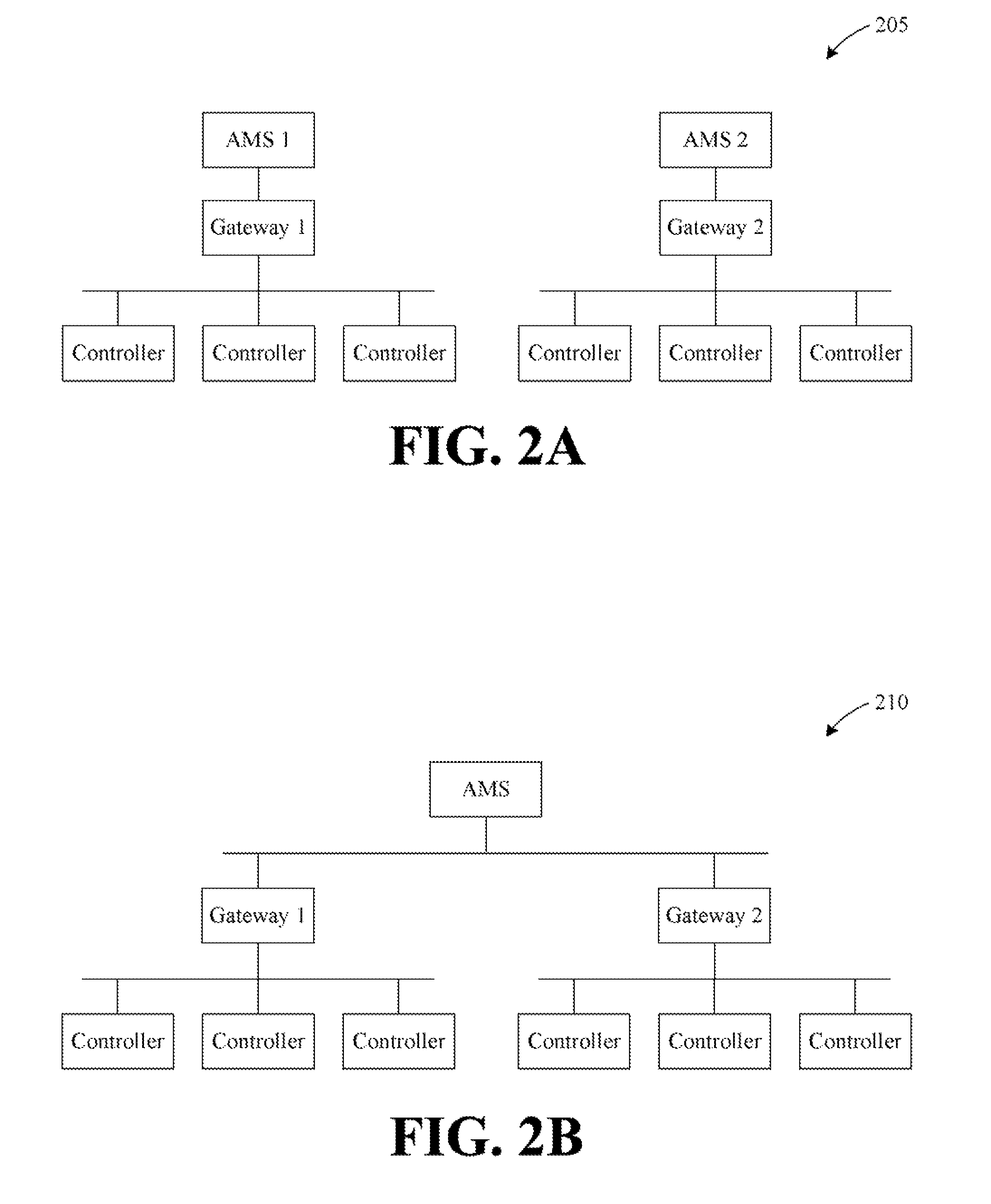

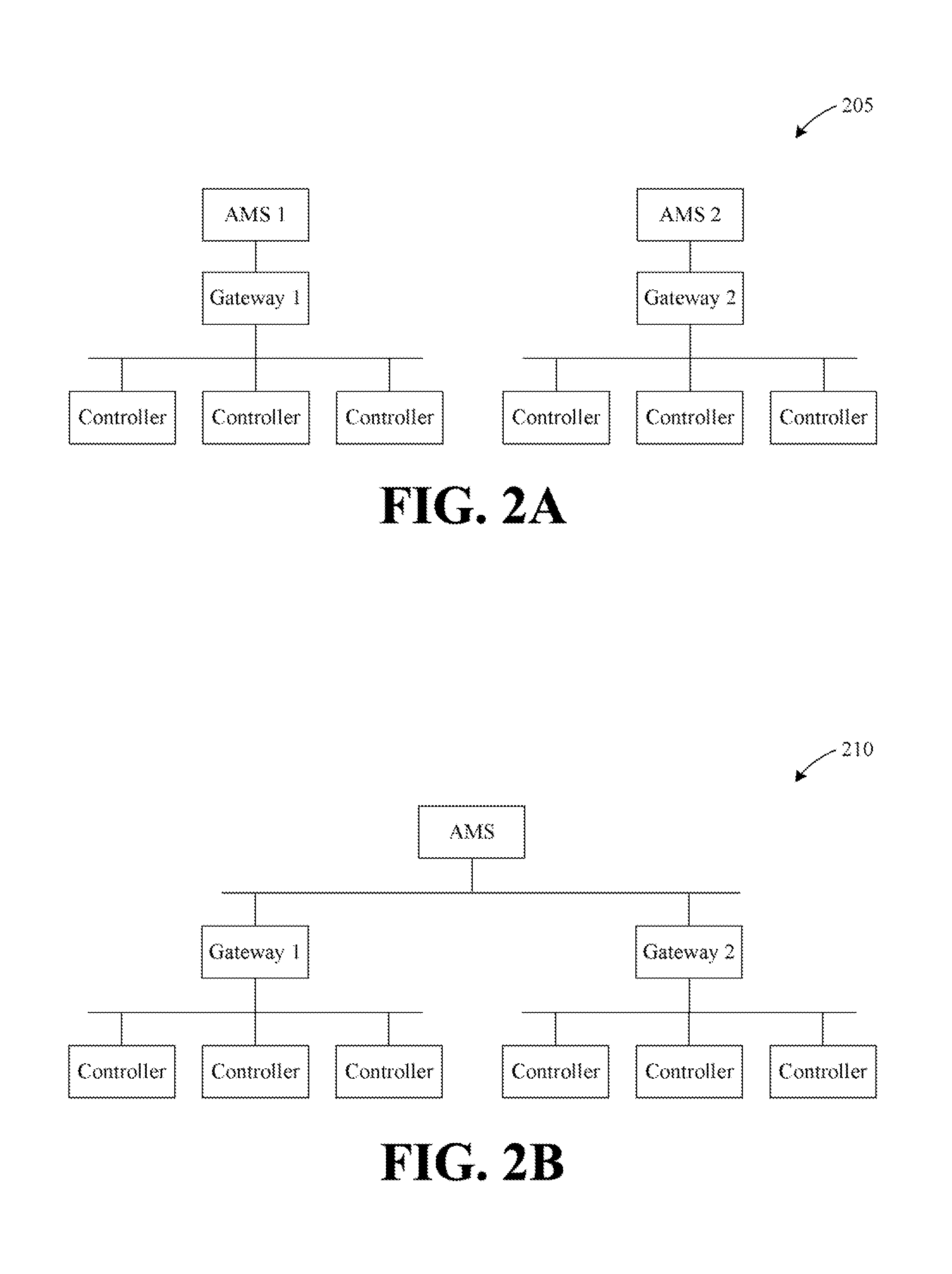

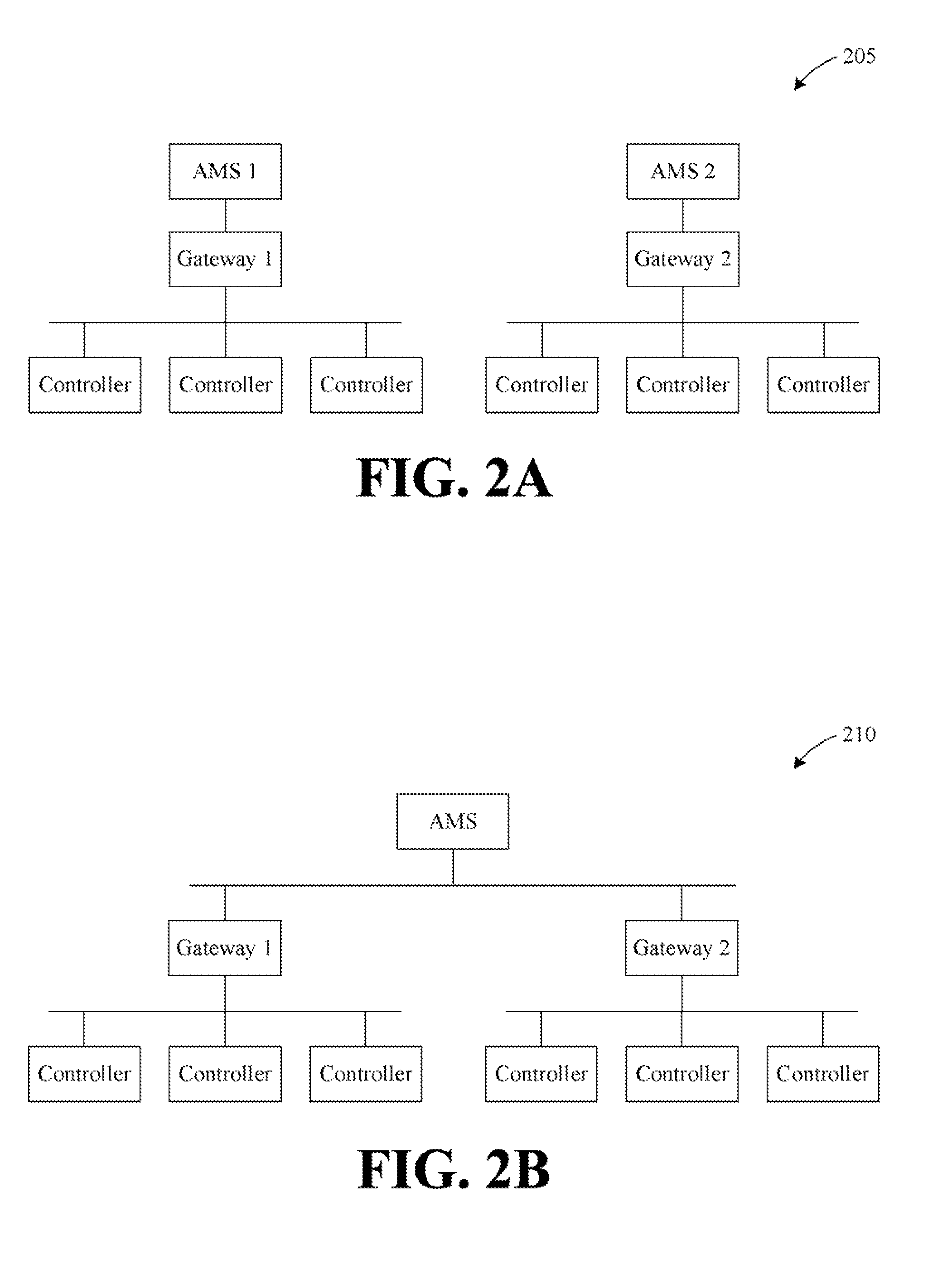

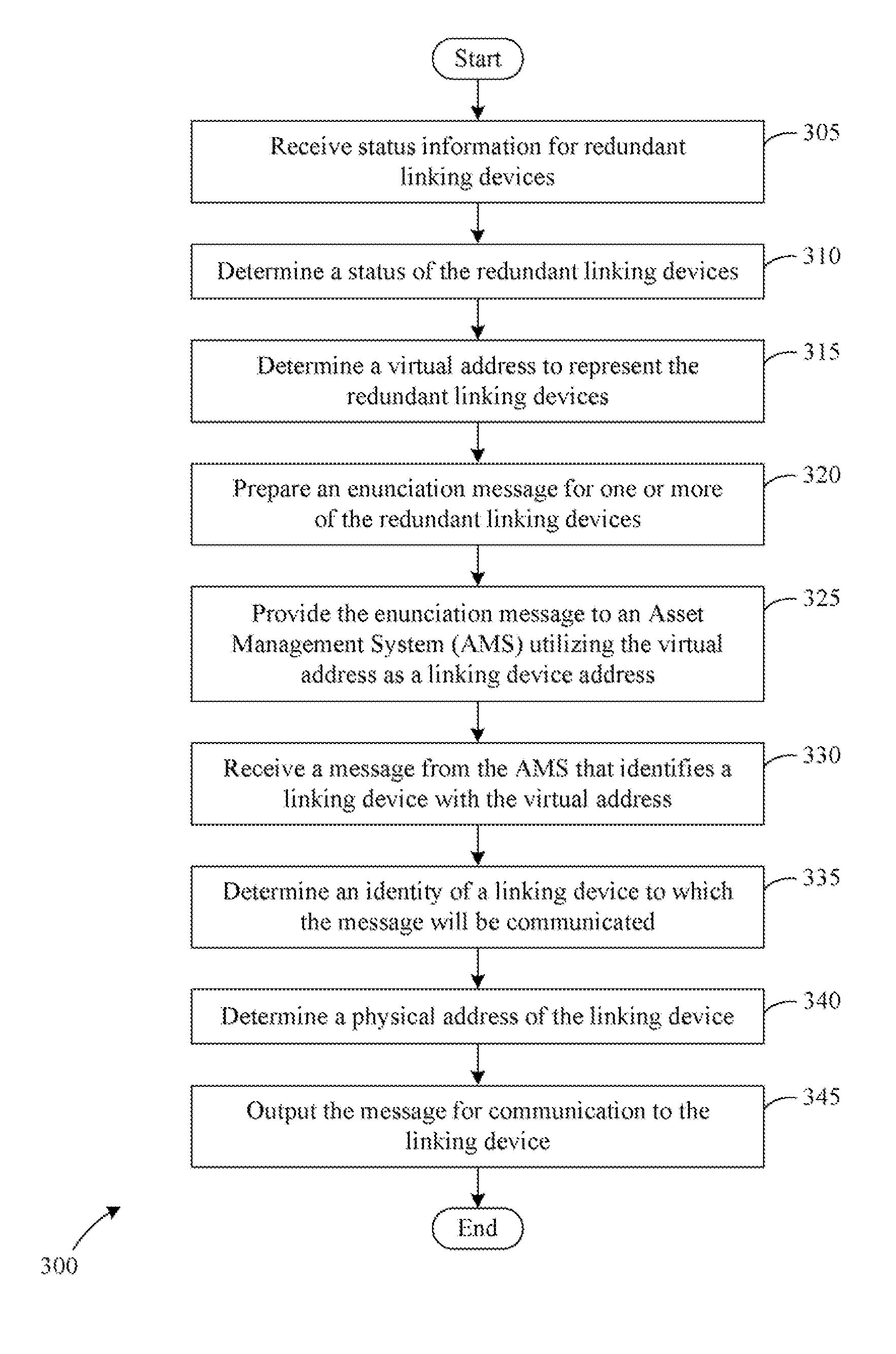

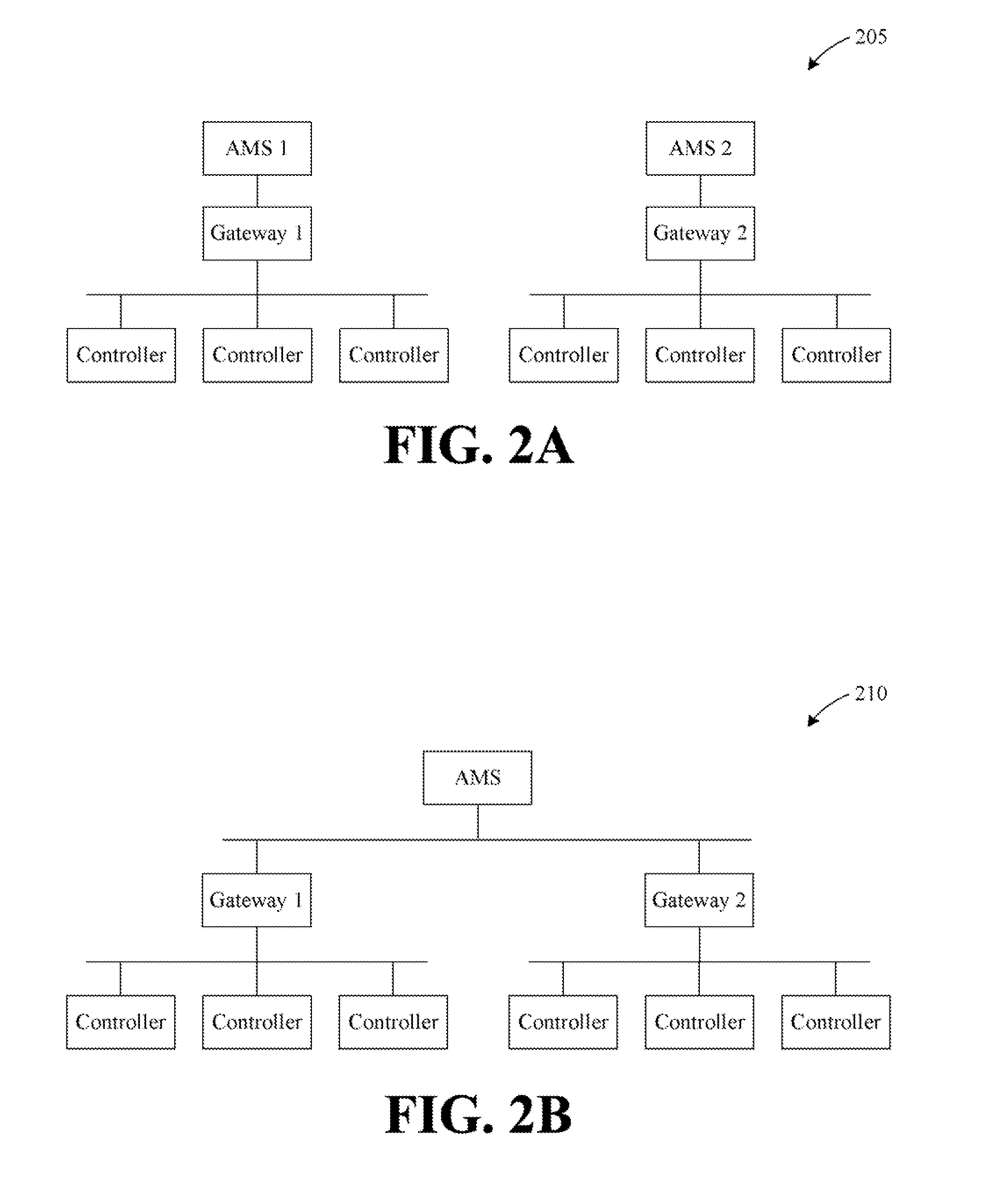

Systems and methods for facilitating communication with foundation fieldbus linking devices

InactiveUS20120310387A1Facilitate communicationComputer controlSimulator controlComputer networkFacilitated communication

Systems and methods for facilitating communication with Foundation Fieldbus linking devices are described. A plurality of Foundation Fieldbus linking devices may be identified by a gateway device that includes one or more computers. A single virtual address representative of the plurality of linking devices may be determined by the gateway device. Communications between the plurality of linking devices and an external system may the be facilitated by the gateway device, and the virtual address may be utilized to represent the plurality of linking devices to the external system.

Owner:GENERAL ELECTRIC CO

Systems and methods for identifying foundation fieldbus linking devices

Systems and methods for identifying Foundation Fieldbus linking devices are described. A Foundation Fieldbus linking device may be identified by a gateway device that includes one or more computers. An operational status for the identified linking device may be determined by the gateway device. A virtual address representative of the identified linking device may be determined by the gateway device. A message associated with operation of the identified linking device may be provided by the gateway device to an external system, and the virtual address may be utilized to represent the linking device.

Owner:GE INFRASTRUCTURE TECH INT LLC

Systems and methods for identifying foundation fieldbus linking devices

Systems and methods for identifying Foundation Fieldbus linking devices are described. A pair of redundant Foundation Fieldbus linking devices may be identified by a gateway device that includes one or more computers. A single virtual address representative of the pair of redundant linking devices may then be determined by the gateway device, and information associated with operation of at least one of the pair of redundant linking devices may be provided by the gateway device to an external system. During the provision of information to the external system, the virtual address may be utilized to represent the at least one linking device.

Owner:GENERAL ELECTRIC CO

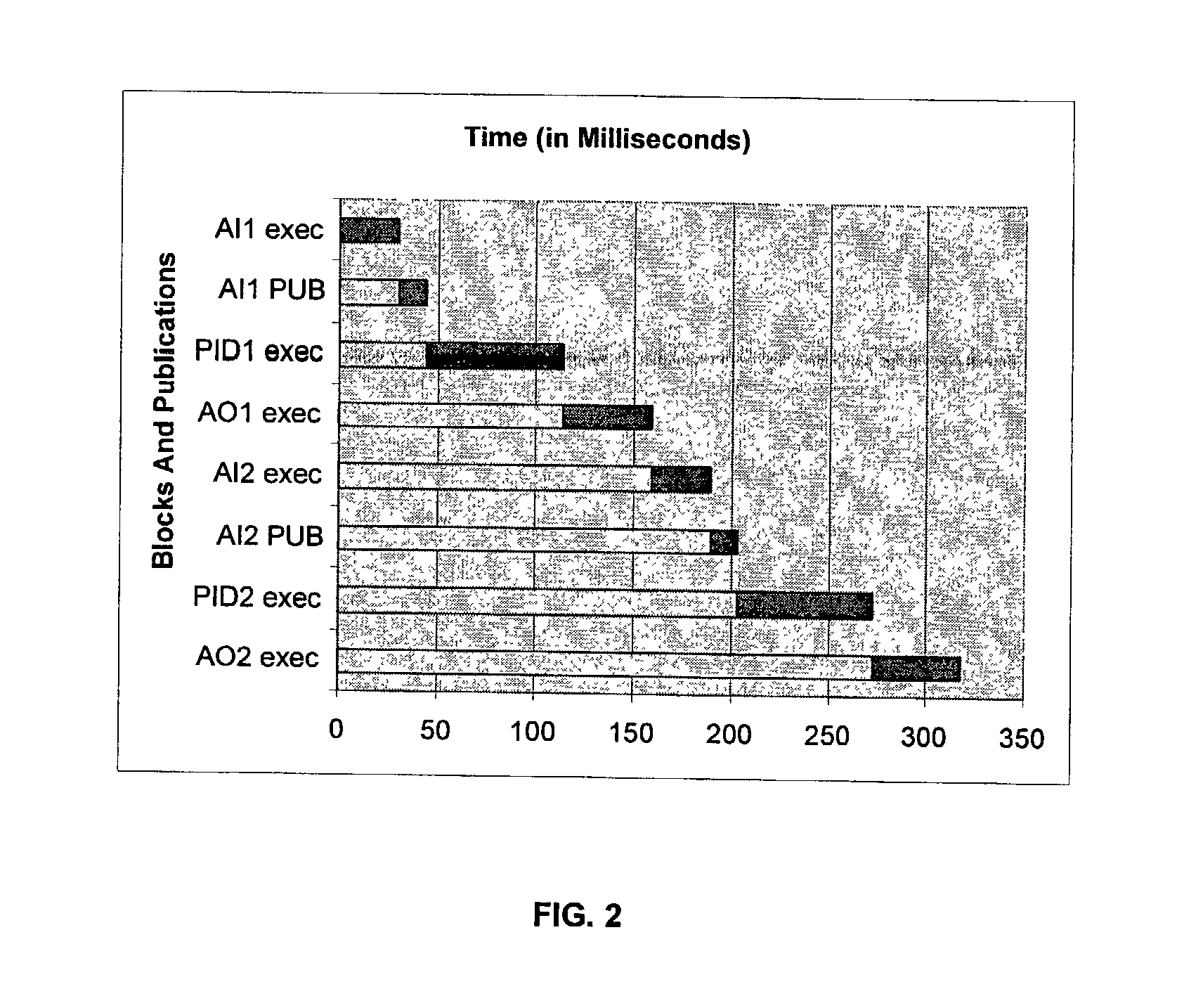

Method for optimizing a link schedule

InactiveUS20040081162A1Overcome disadvantagesImprove disadvantagesComputer controlSimulator controlDistributed computingPriority scheduling

A method for improving a link schedule used in a communications network is disclosed. While the method applies generally to networks that operate on a scheduled communications basis, it is described in the context of a Foundation FIELDBUS. The method includes: scheduling sequences and their associated publications according to their relative priority, per application; minimizing delays between certain function blocks, and between certain function blocks and publications; and grouping certain publications. Accordingly, advantages such as latency reduction, schedule length reduction, and improved communications capacity are gained.

Owner:HONEYWELL INT INC