Patents

Literature

64 results about "Decoding latency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The decoding latency is denoted by l and is defined as the overall latency minus the encoding time and the channel delay. We measure time in terms of information bits.

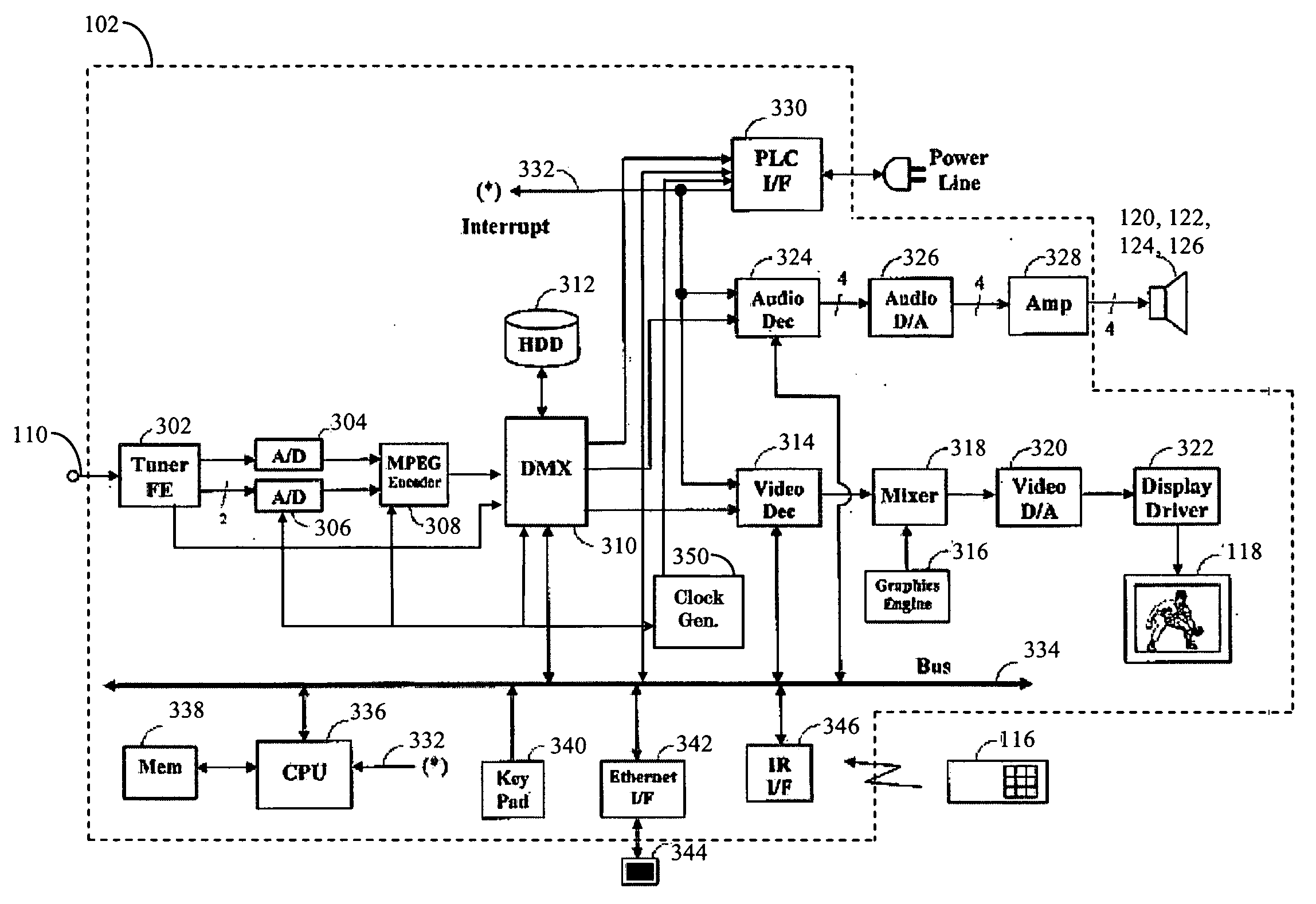

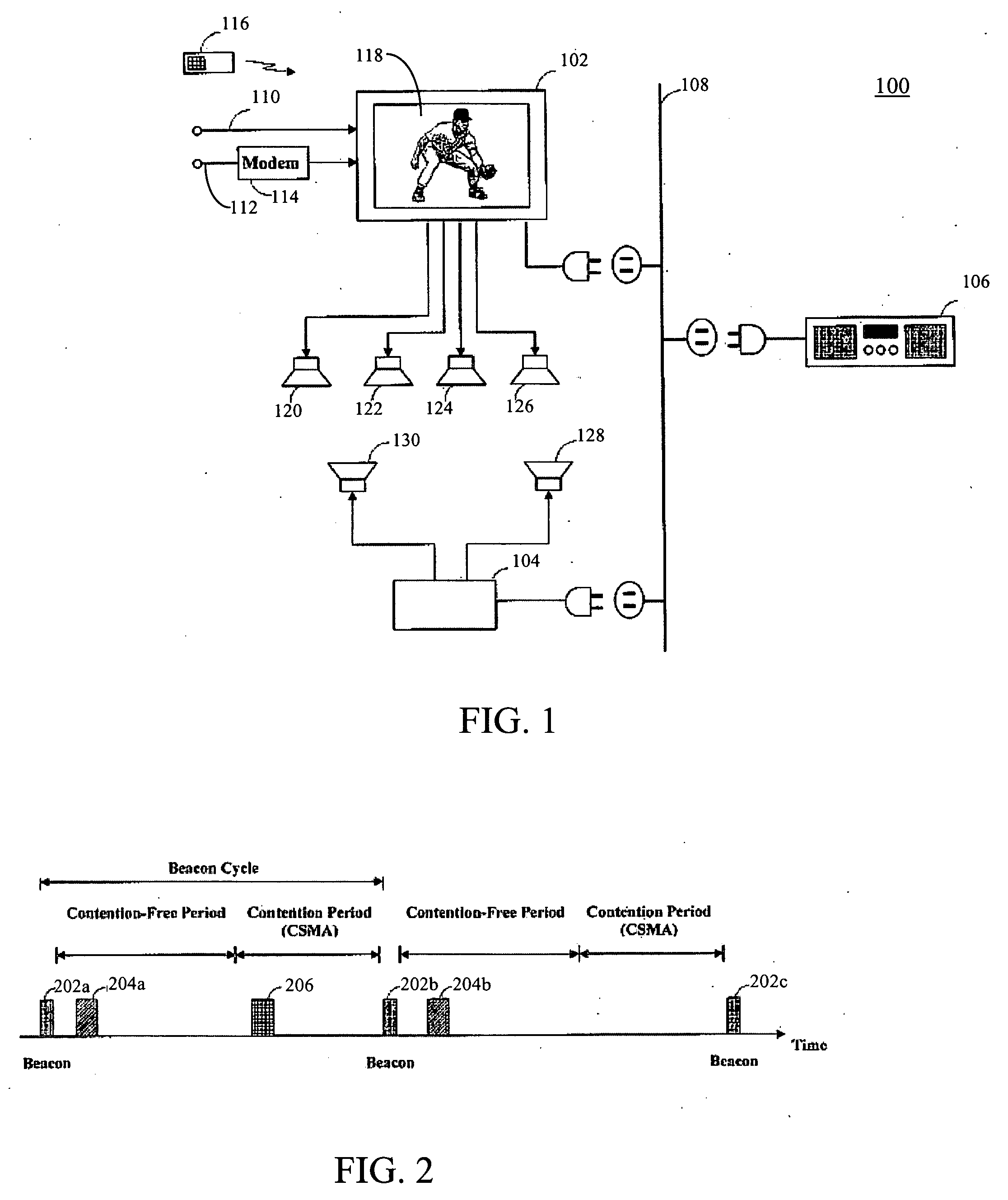

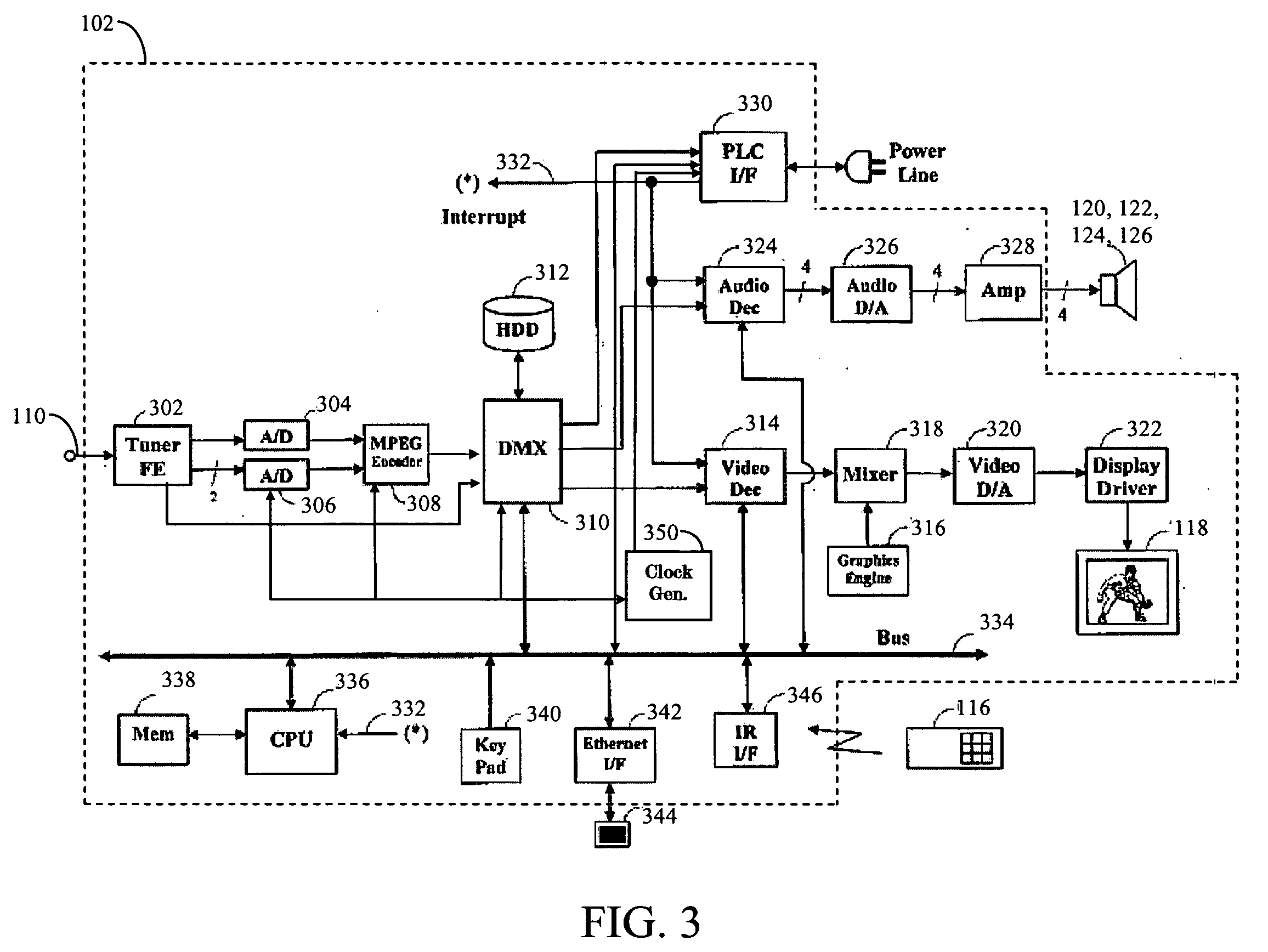

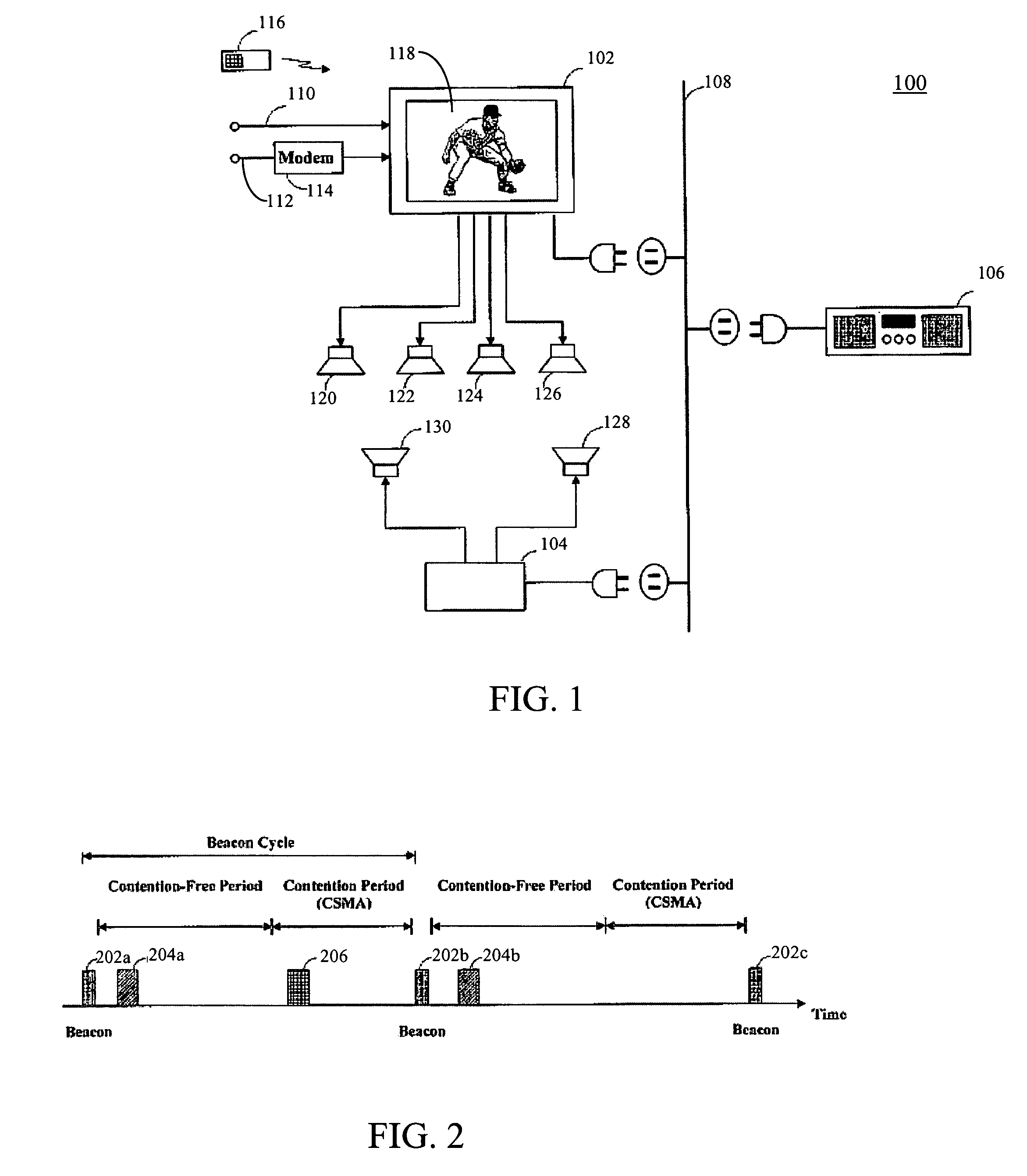

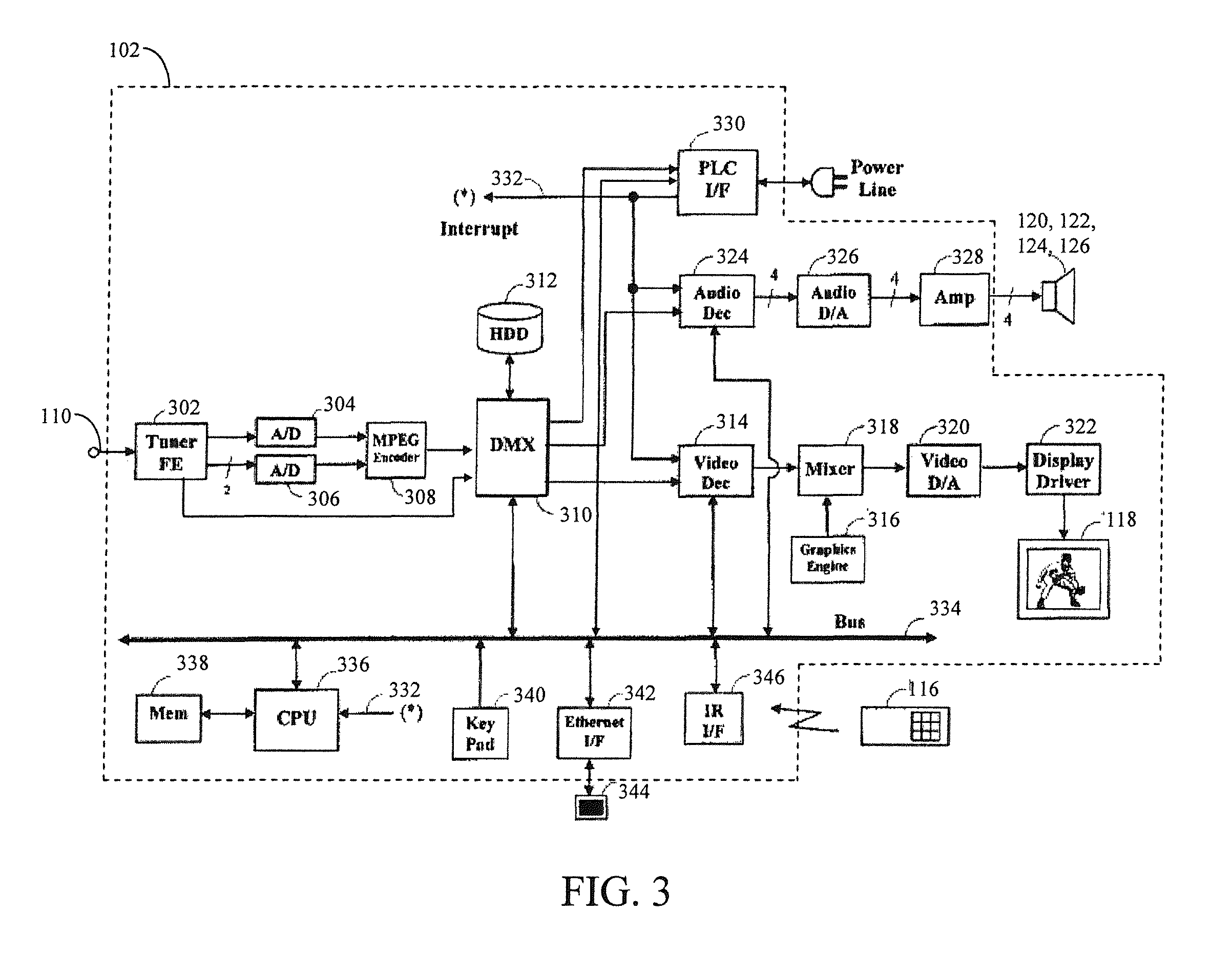

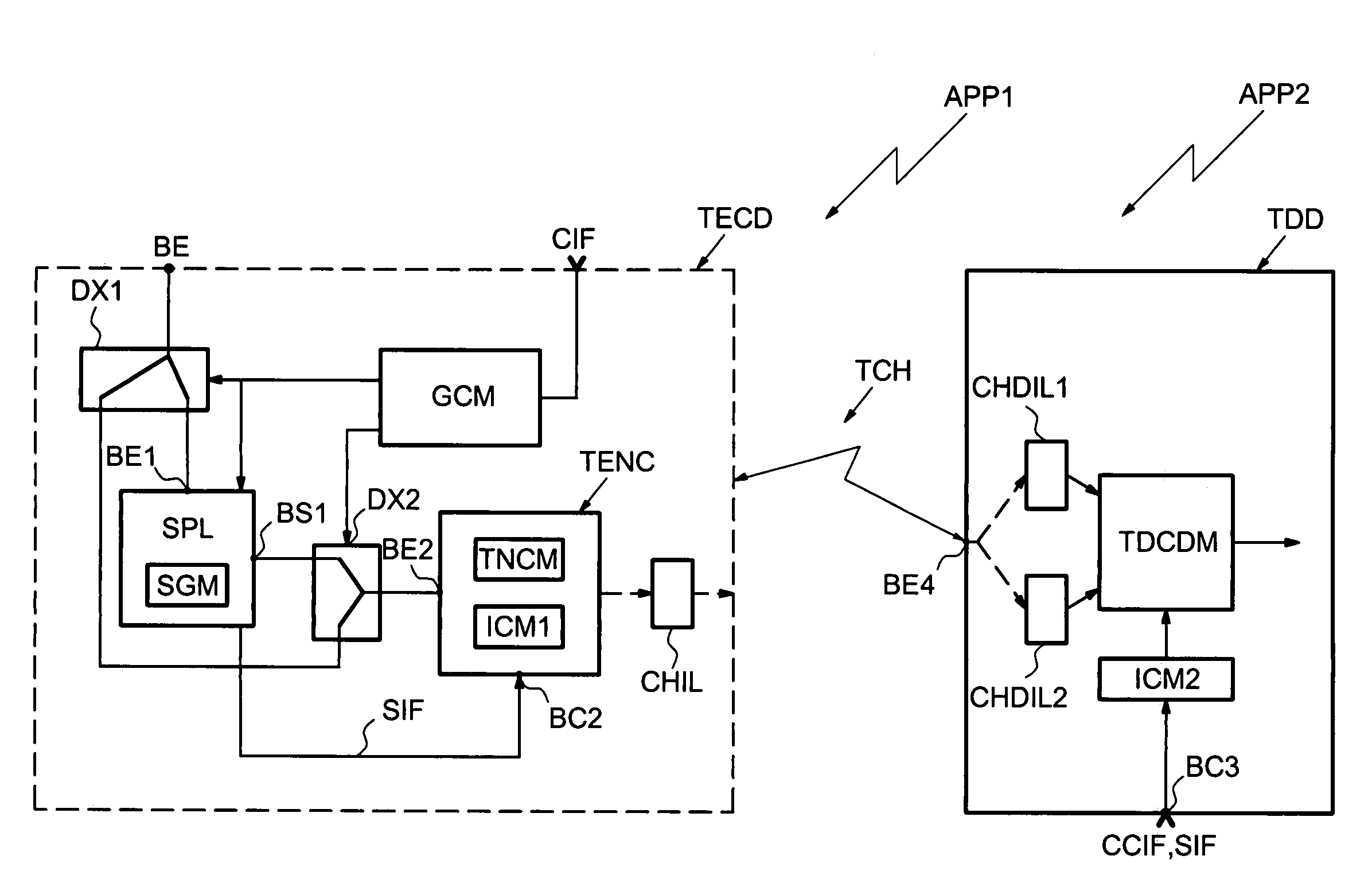

Synchronized audio/video decoding for network devices

InactiveUS20060233203A1Time-division multiplexSynchronisation signal speed/phase controlTimestampClock rate

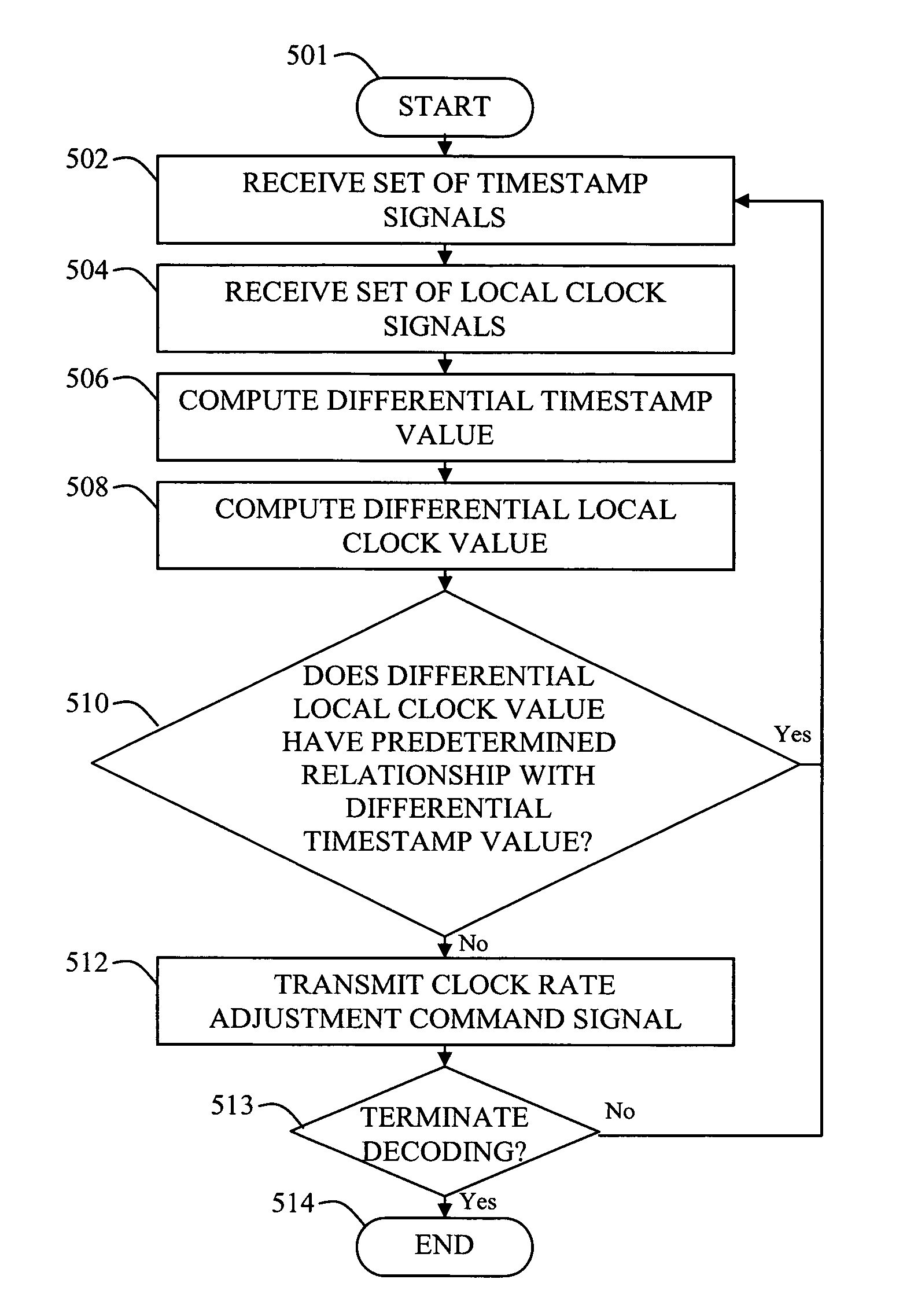

A method of synchronizing decoders within a network to a server includes receiving a set of timestamps and local clock signals upon receiving the beacon interrupt signal, computing differential timestamp and local clock values based on values of timestamp and local clock signals, respectively, within the sets of timestamp and local clock signals, determining whether the differential local clock value has a predetermined relationship with the differential timestamp value, and transmitting a clock rate adjustment command signal to the decoder when differential local clock value does not have the predetermined relationship with the differential timestamp value. The clock rate adjustment command signal adjusts the local system time clock of the decoder such that a subsequent differential clock value will have the predetermined relationship with the differential timestamp value. When this method is performed for each decoder within the network, the decoders are substantially synchronized and the decoding delay can be kept below humanly perceptible levels.

Owner:SONY CORP +1

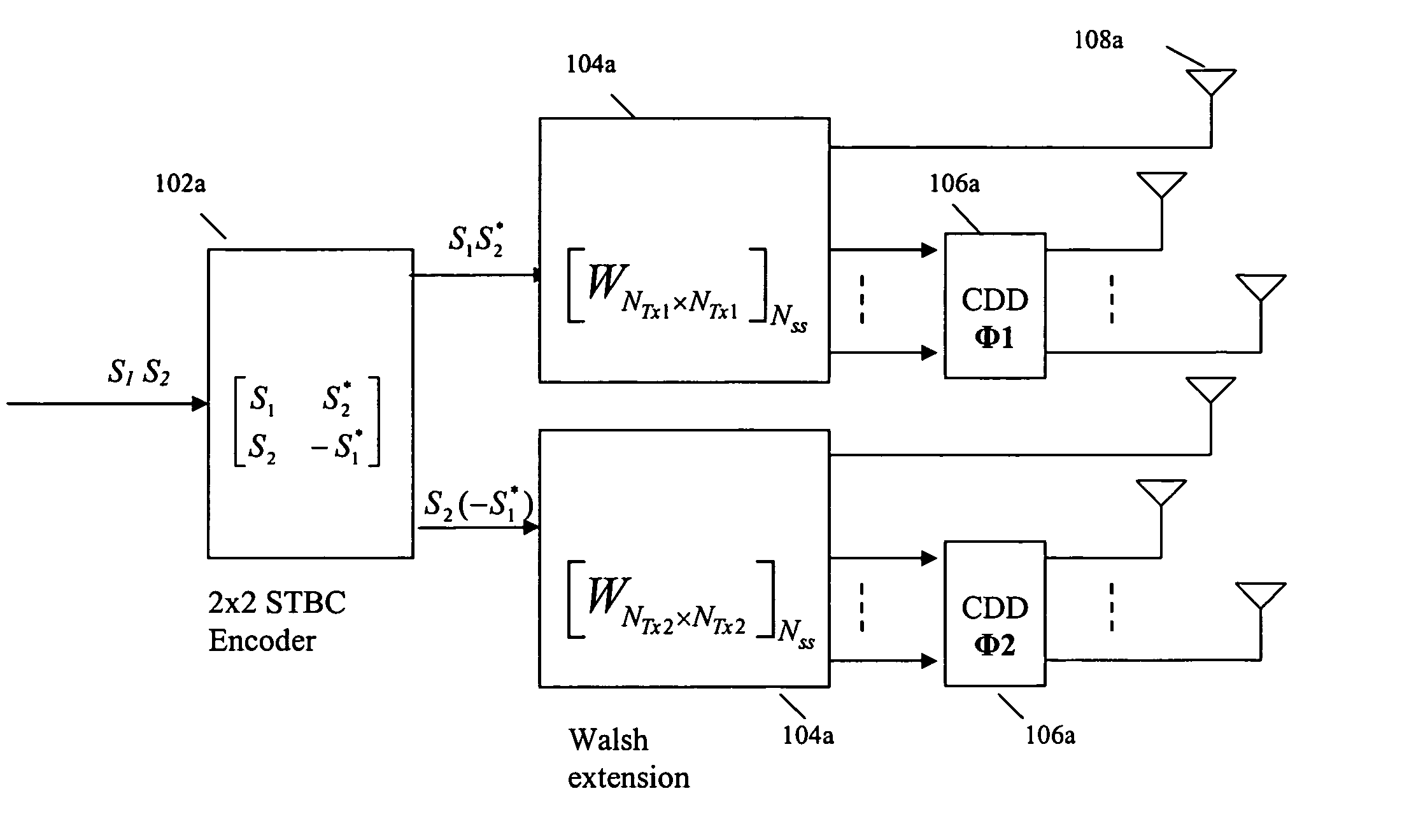

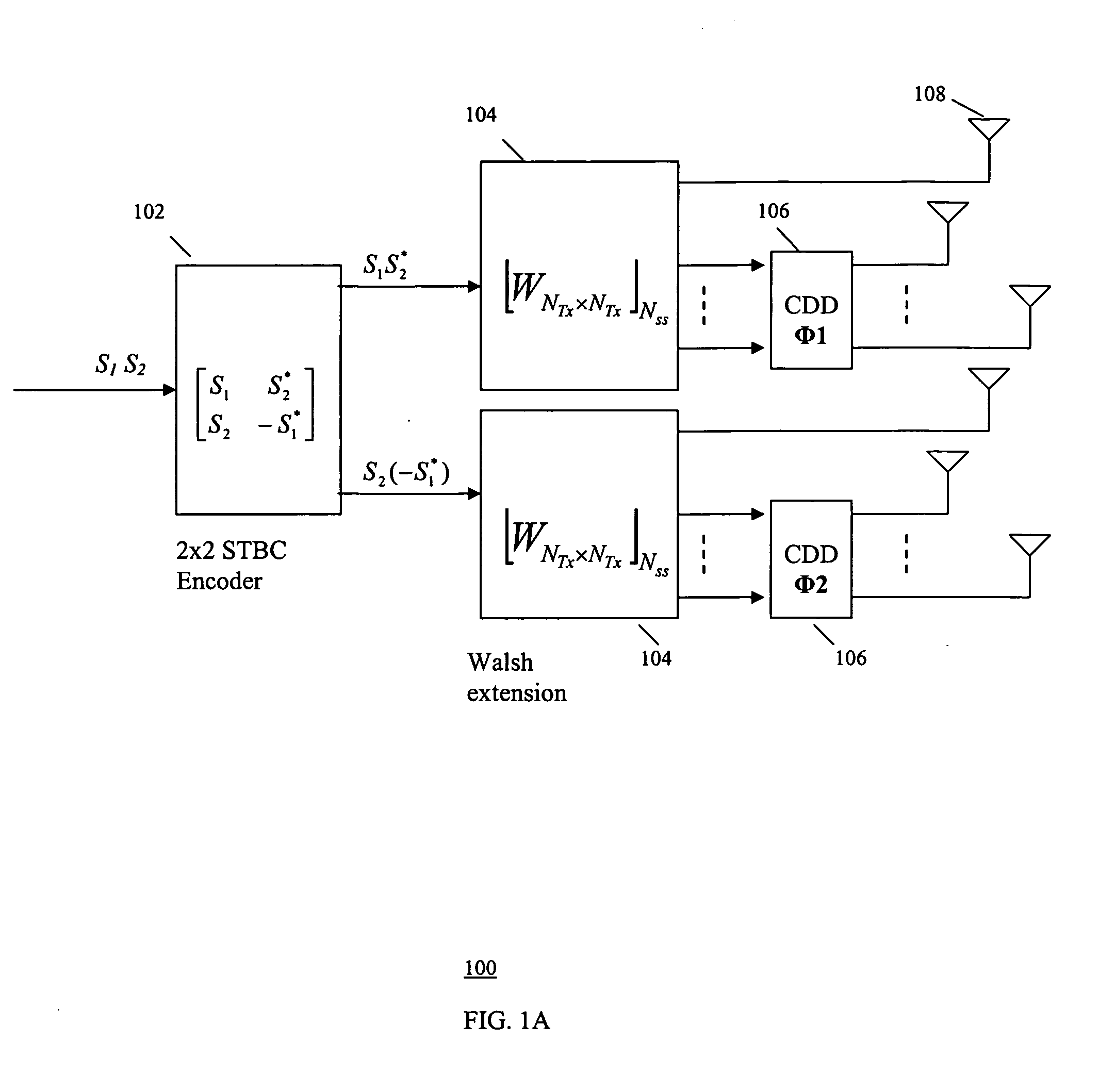

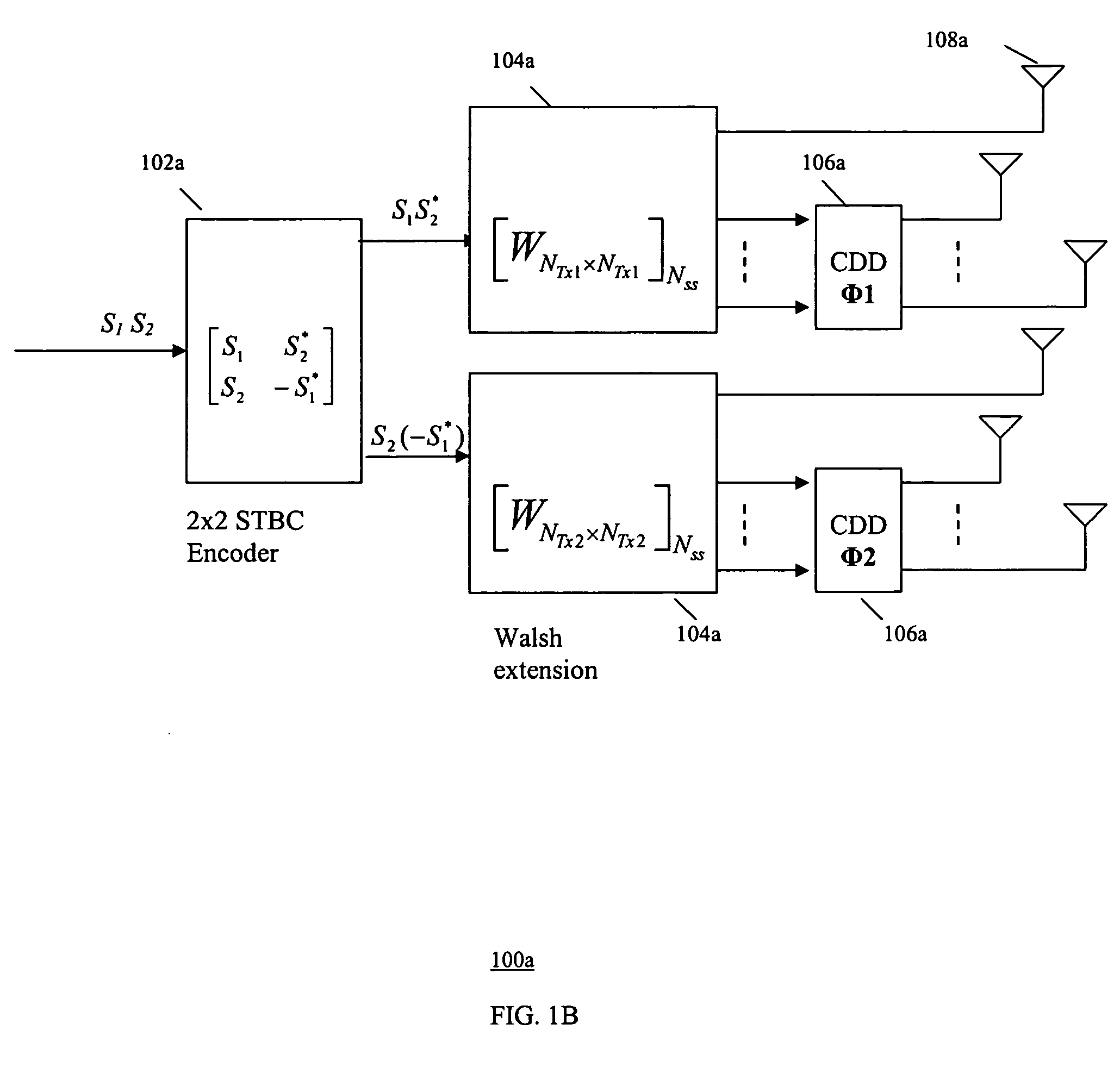

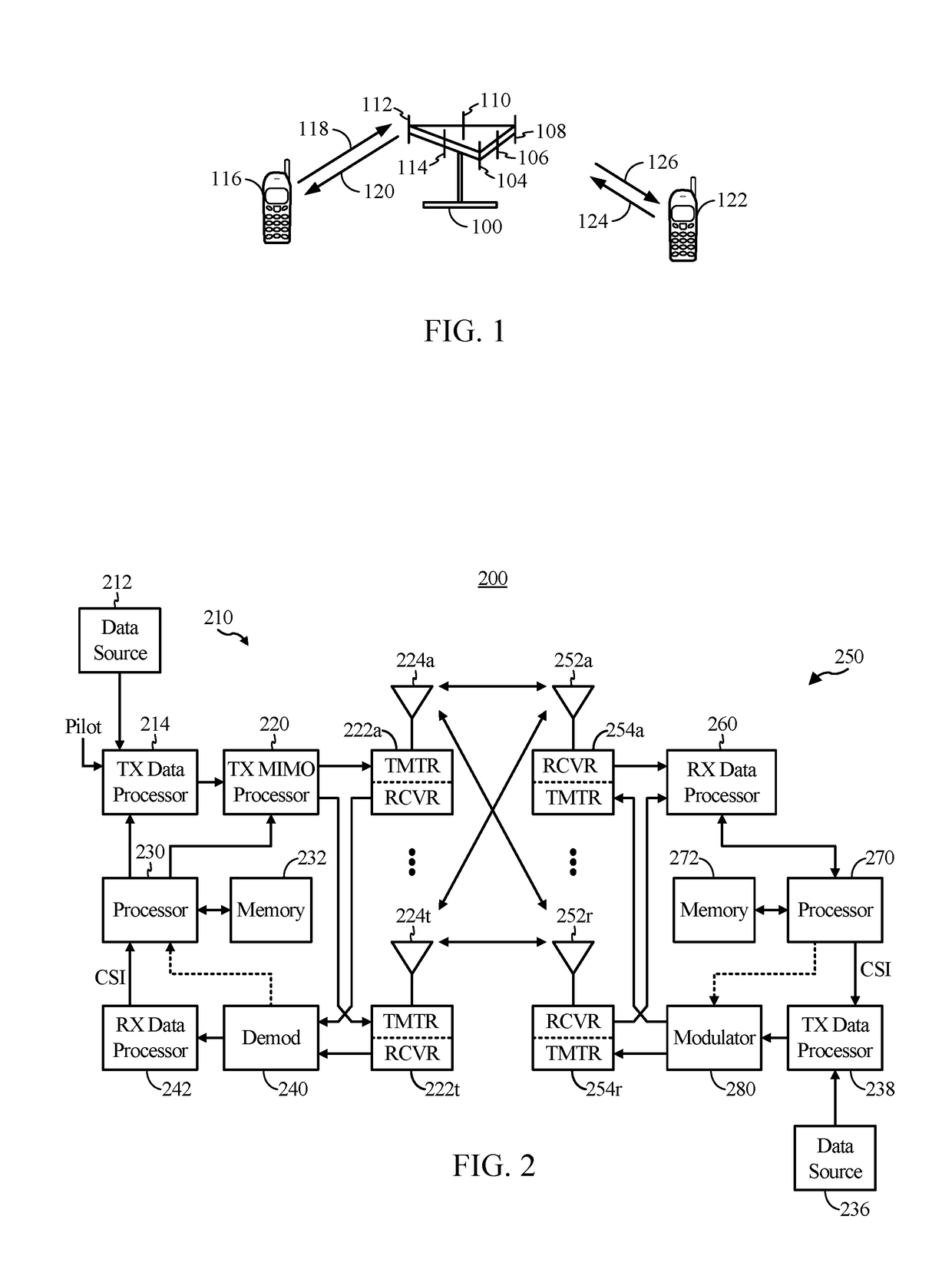

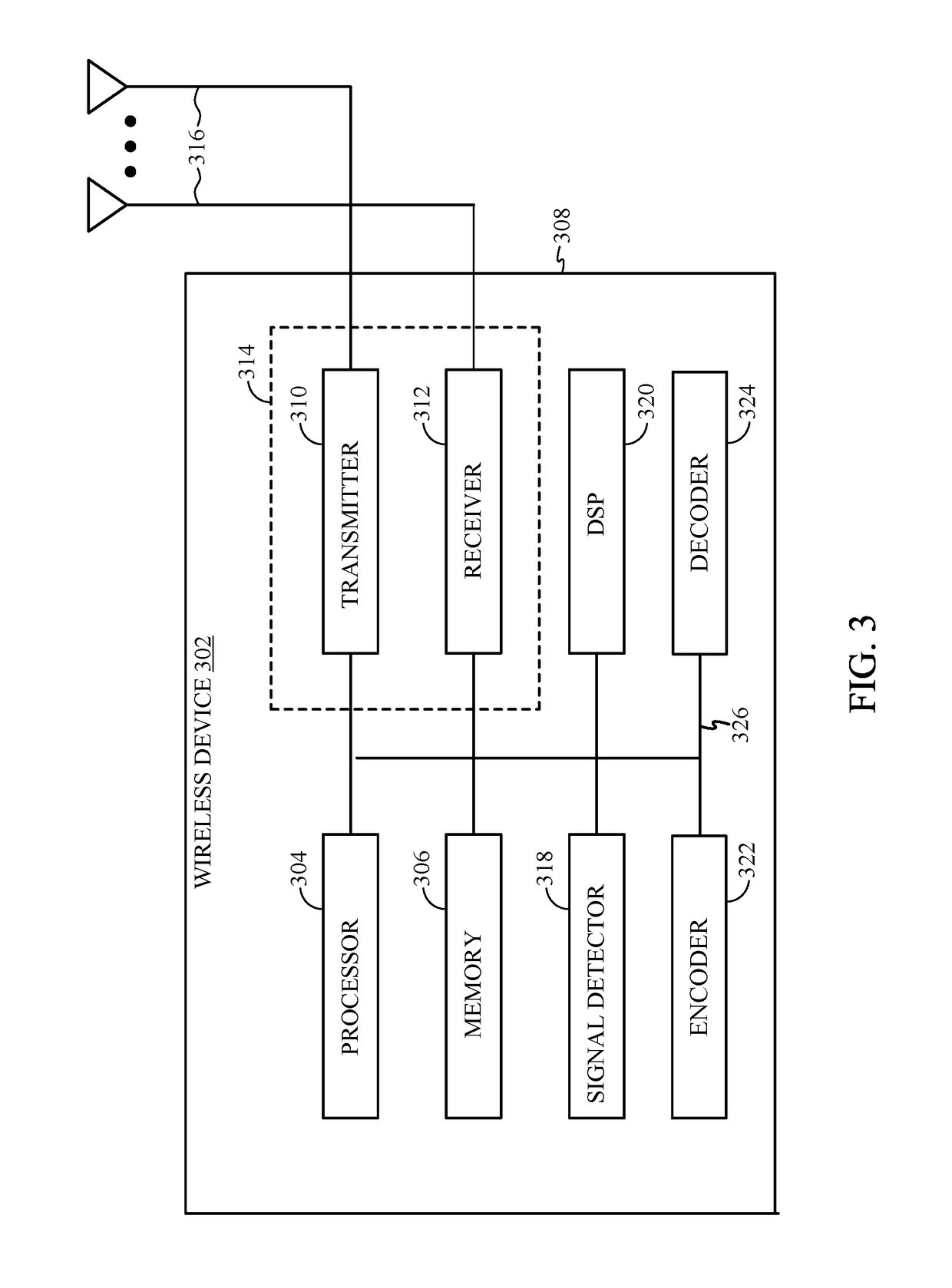

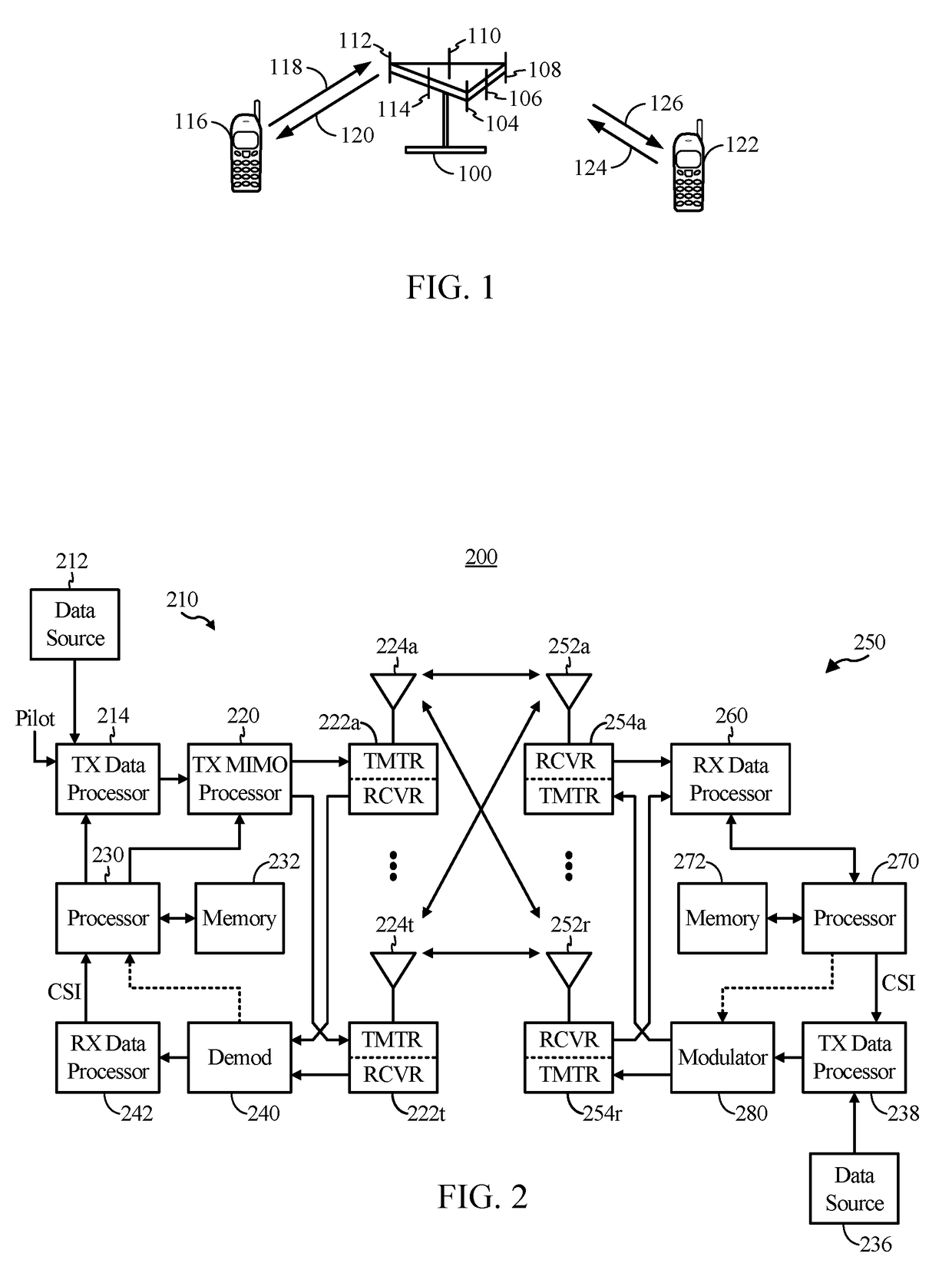

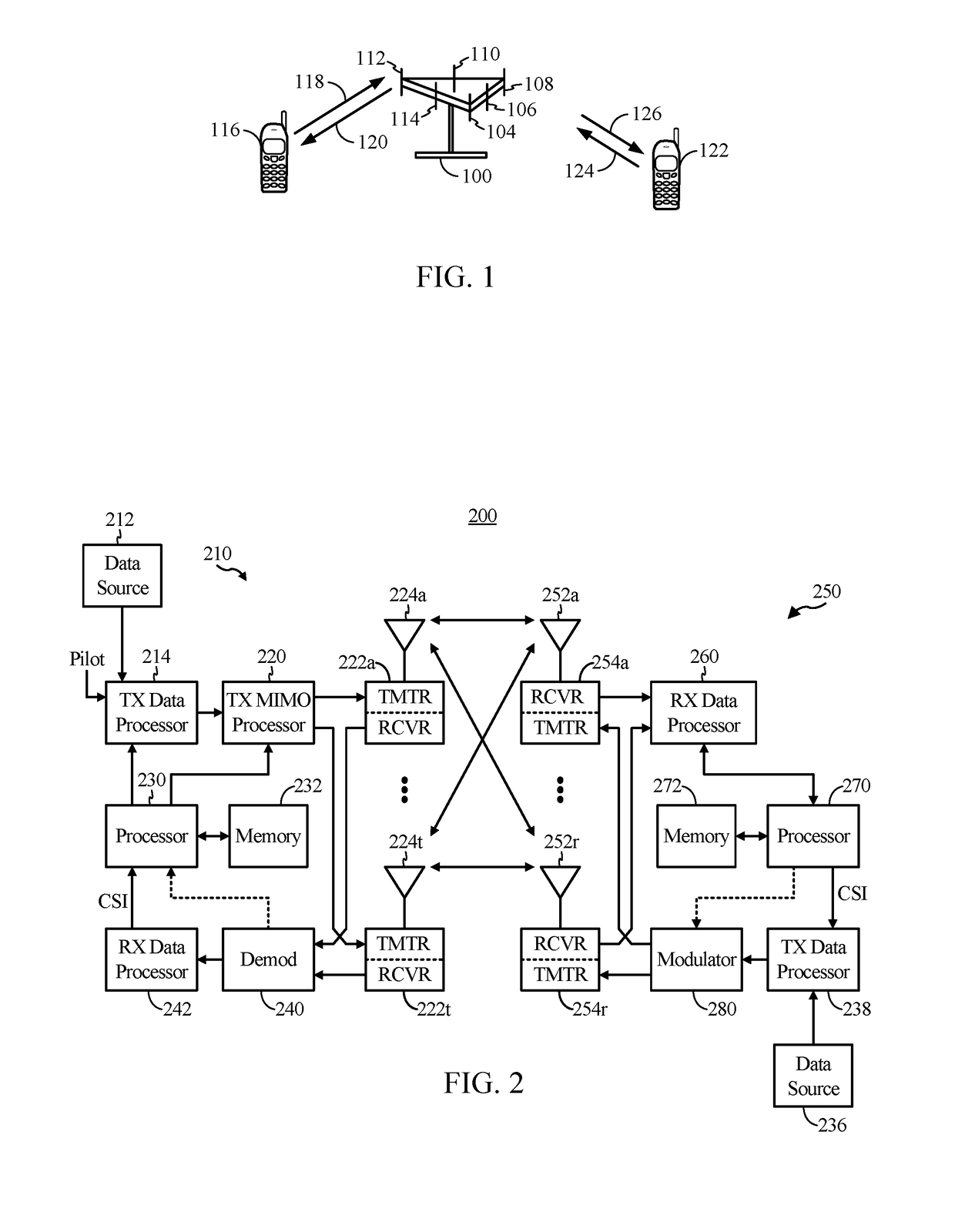

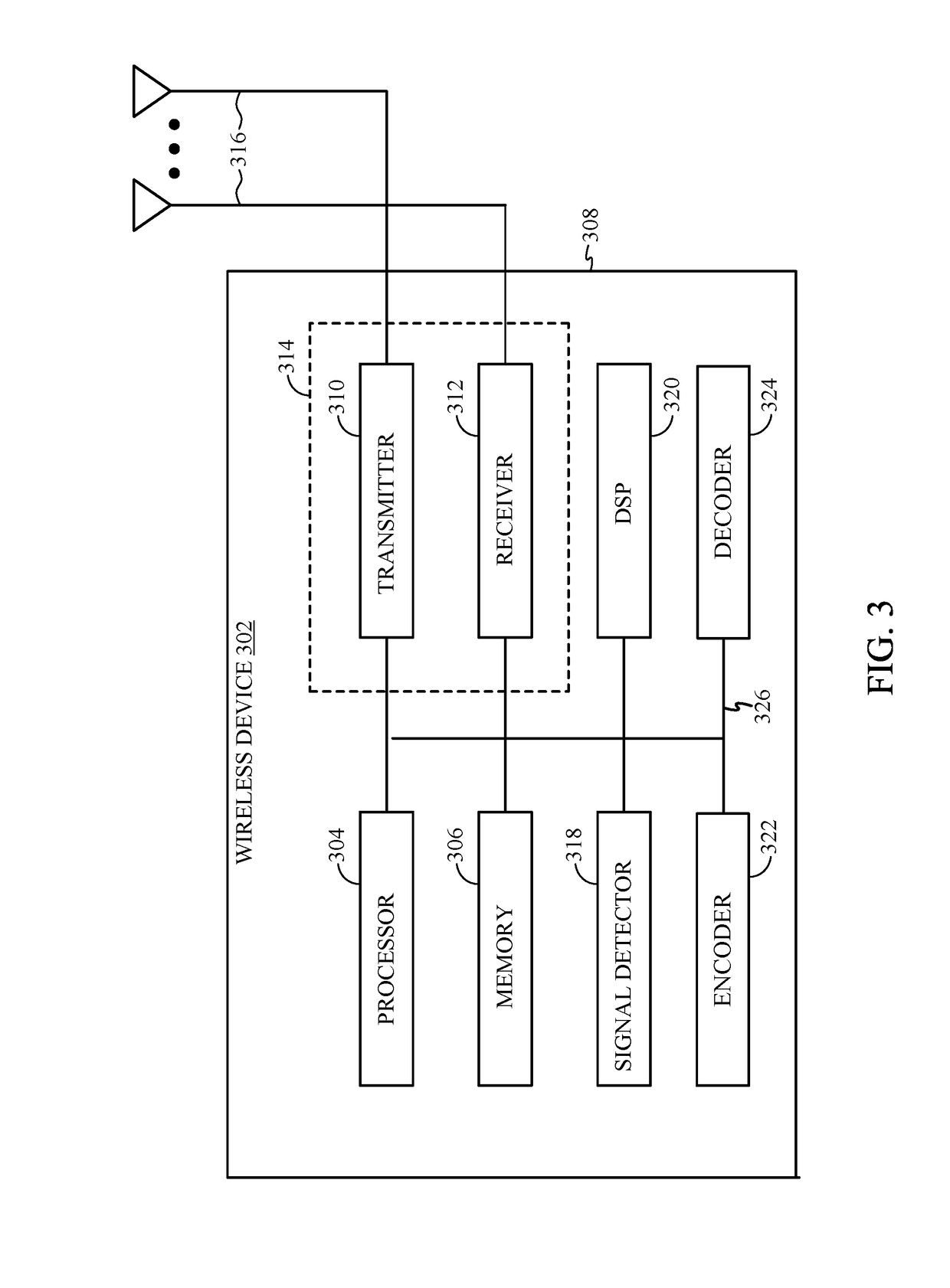

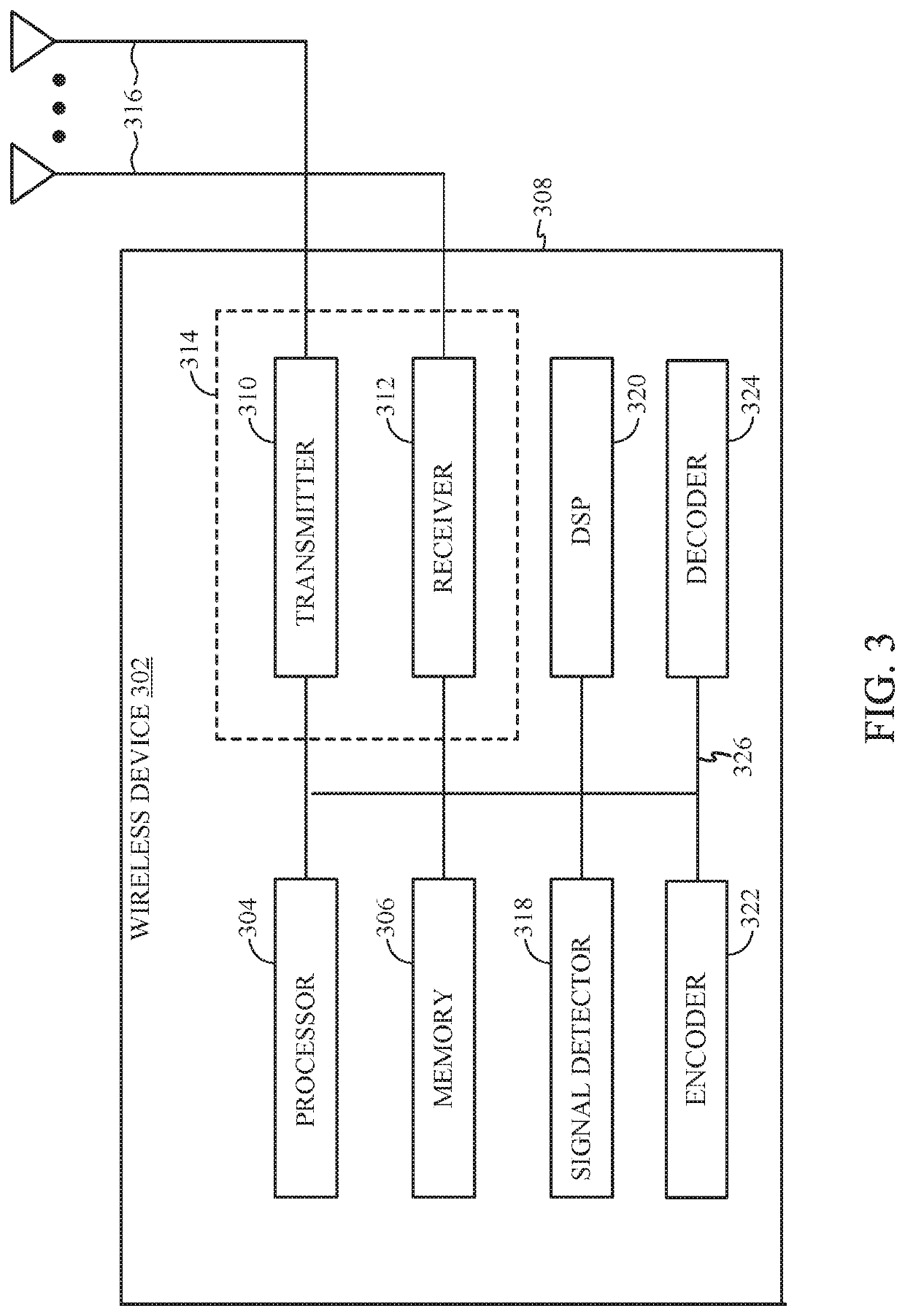

Extension of space-time block code for transmission with more than two transmit antennas

InactiveUS20070147543A1Increase diversity gainError preventionModulated-carrier systemsTelecommunicationsWireless transmission

An STBC encoding extension method for more than two transmit antennas, which provides higher diversity gains while keeping the same coding / decoding latency as in the two-transmit-antenna case of conventional STBC encoding. A N×2 STBC encoder is constructed from a 2×2 STBC encoder, wherein the N×2 STBC encoder is suitable for transmission with higher numbers of transmit antennas including wireless transmission systems with N×1 antenna configurations where N>2.

Owner:SAMSUNG ELECTRONICS CO LTD

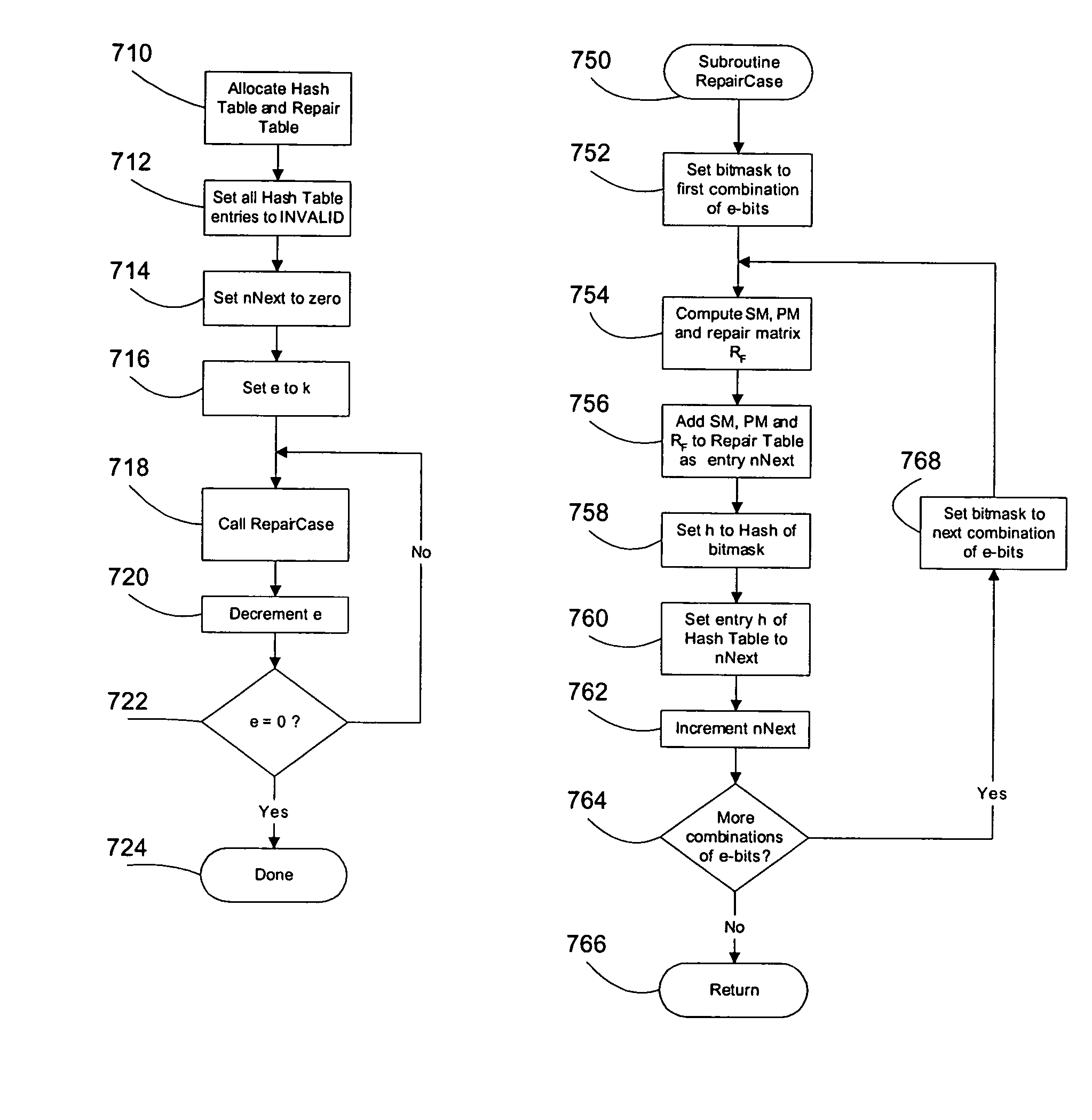

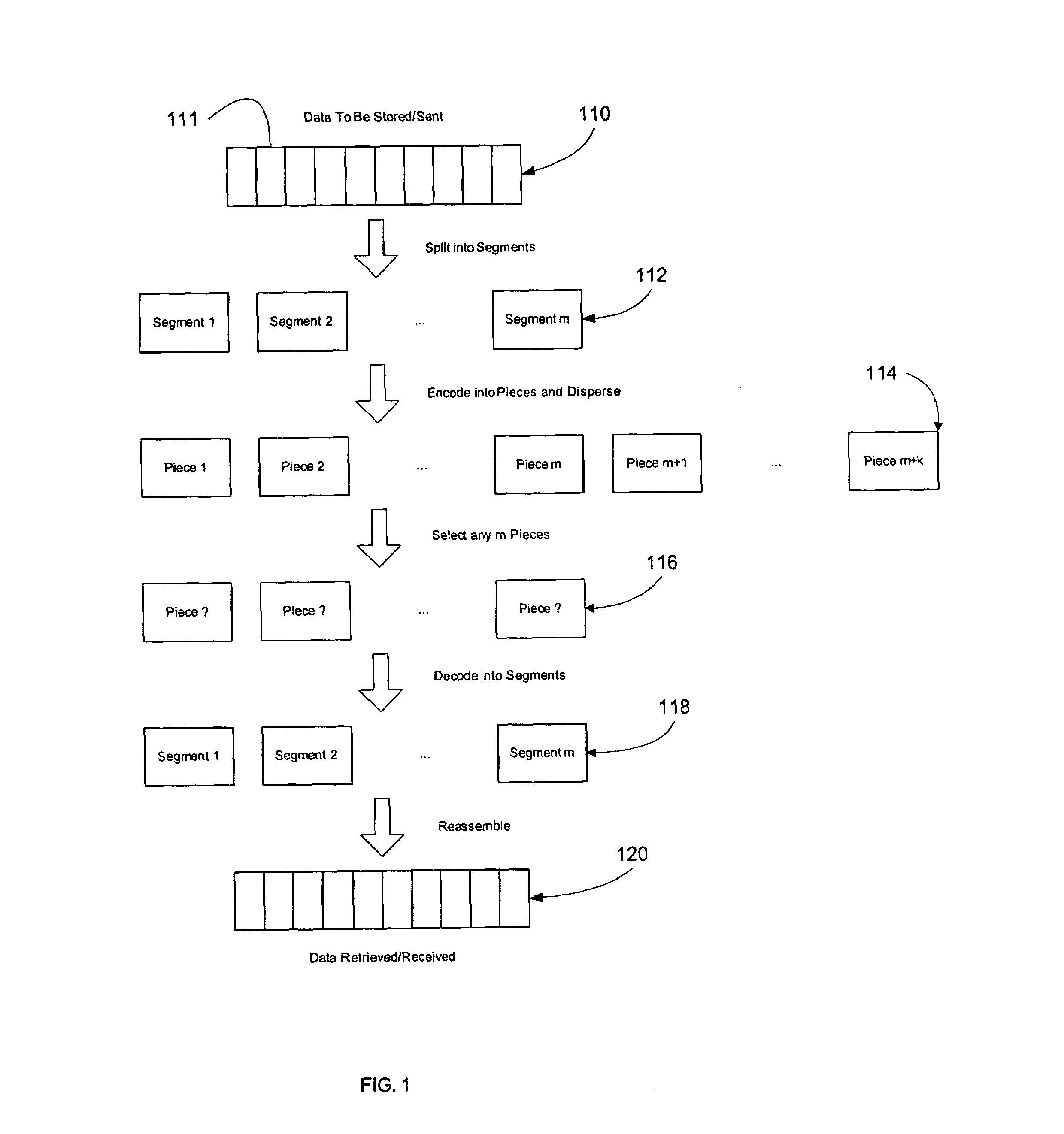

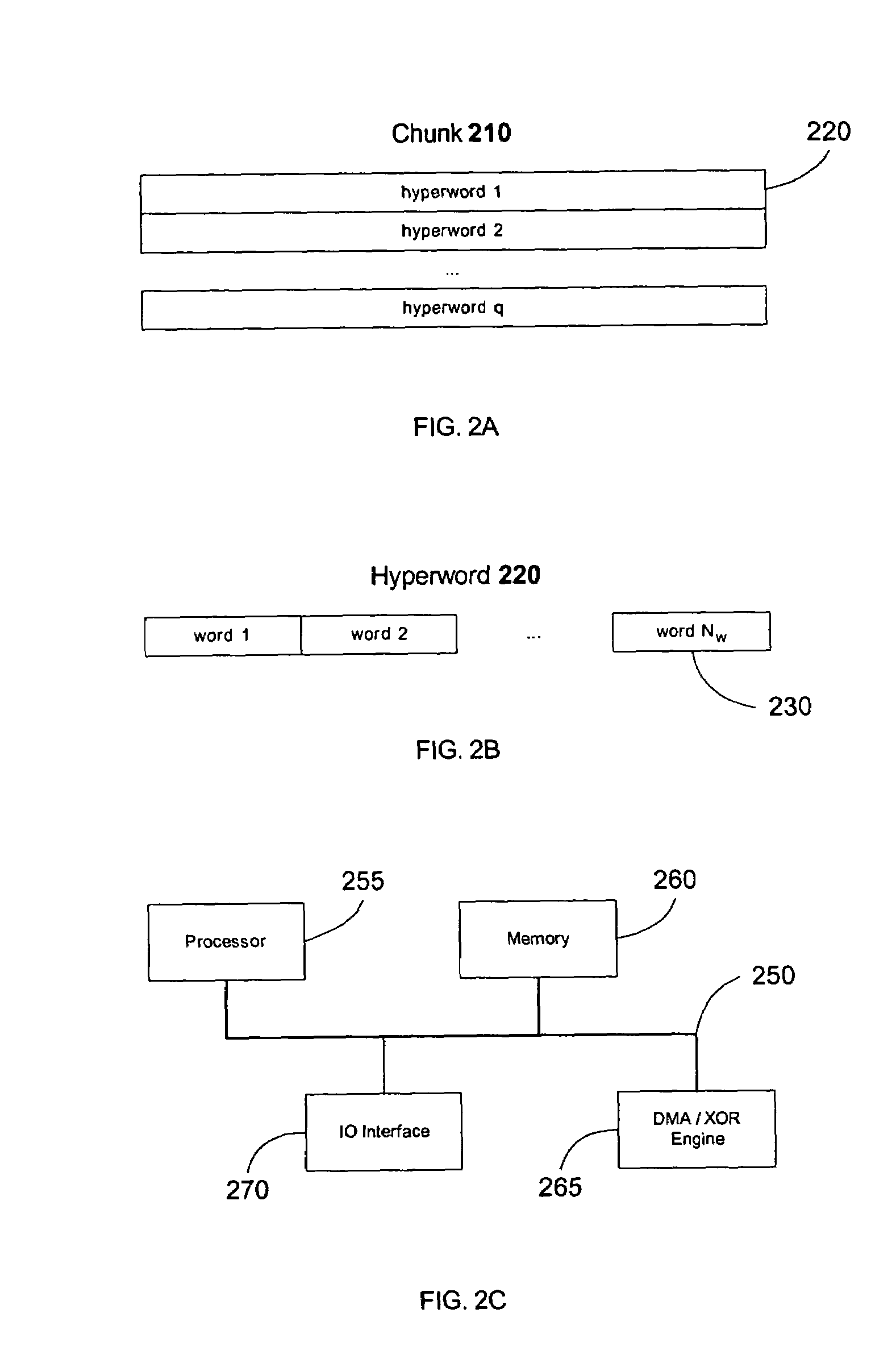

Efficient method for the reconstruction of digital information

InactiveUS7472334B1Improve decoding performanceImprove encoding performanceCode conversionCoding detailsLinear codingTheoretical computer science

Improved method of encoding and repairing data for reliable storage and transmission using erasure codes, which is efficient enough for implementation in software as well as hardware. A systematic linear coding matrix over GF(2q) is used which combines parity for fast correction of single erasures with the capability of correcting k erasures. Finite field operations involving the coding and repair matrices are redefined to consist of bitwise XOR operations on words of arbitrary length. The elements of the matrix are selected to reduce the number of XOR operations needed and buffers are aligned for optimal processor cache efficiency. Decode latency is reduced by pre-calculating repair matrices, storing them in a hashed table and looking them up using a bit mask identifying the erasures to be repaired.

Owner:SCOTT THOMAS P +1

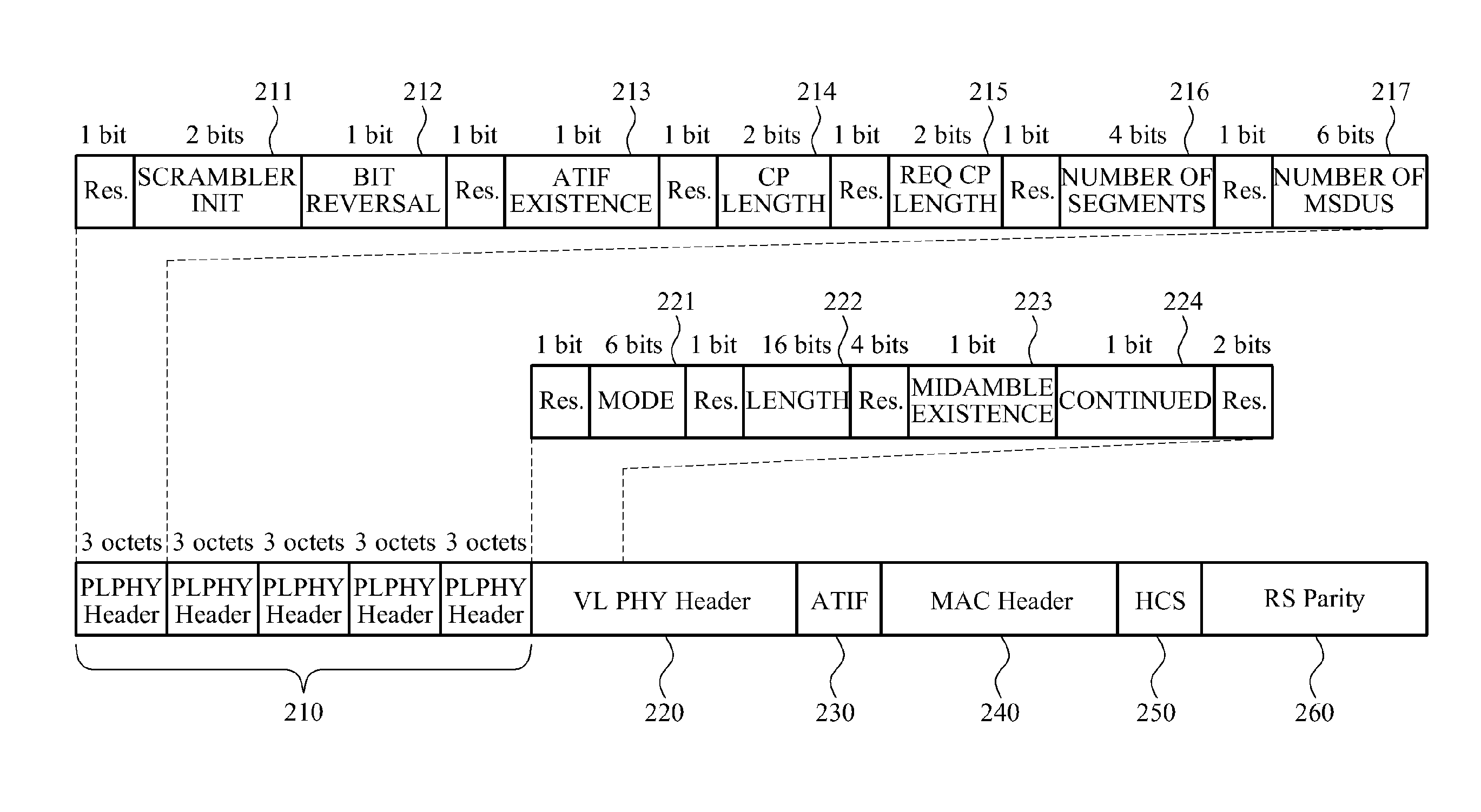

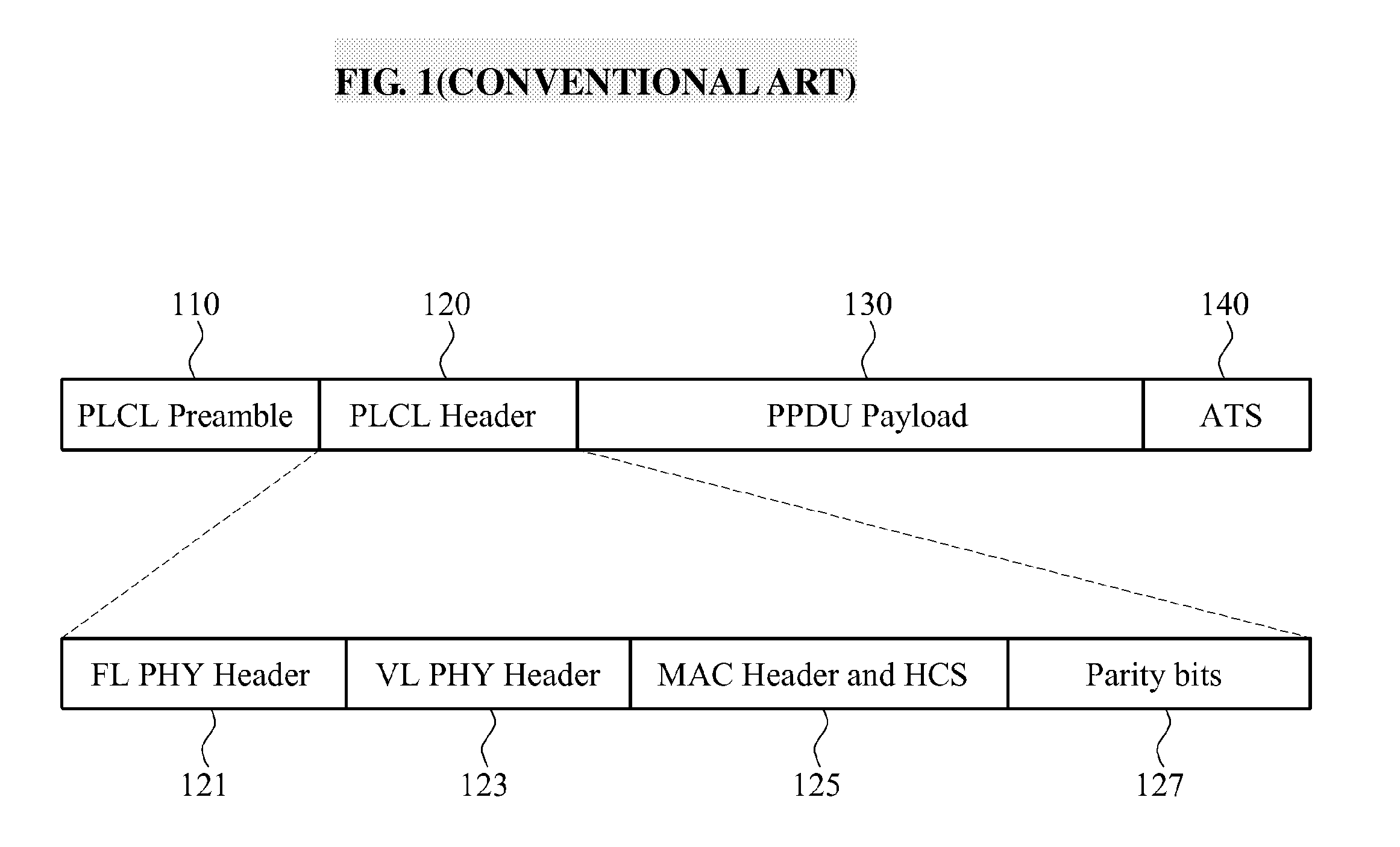

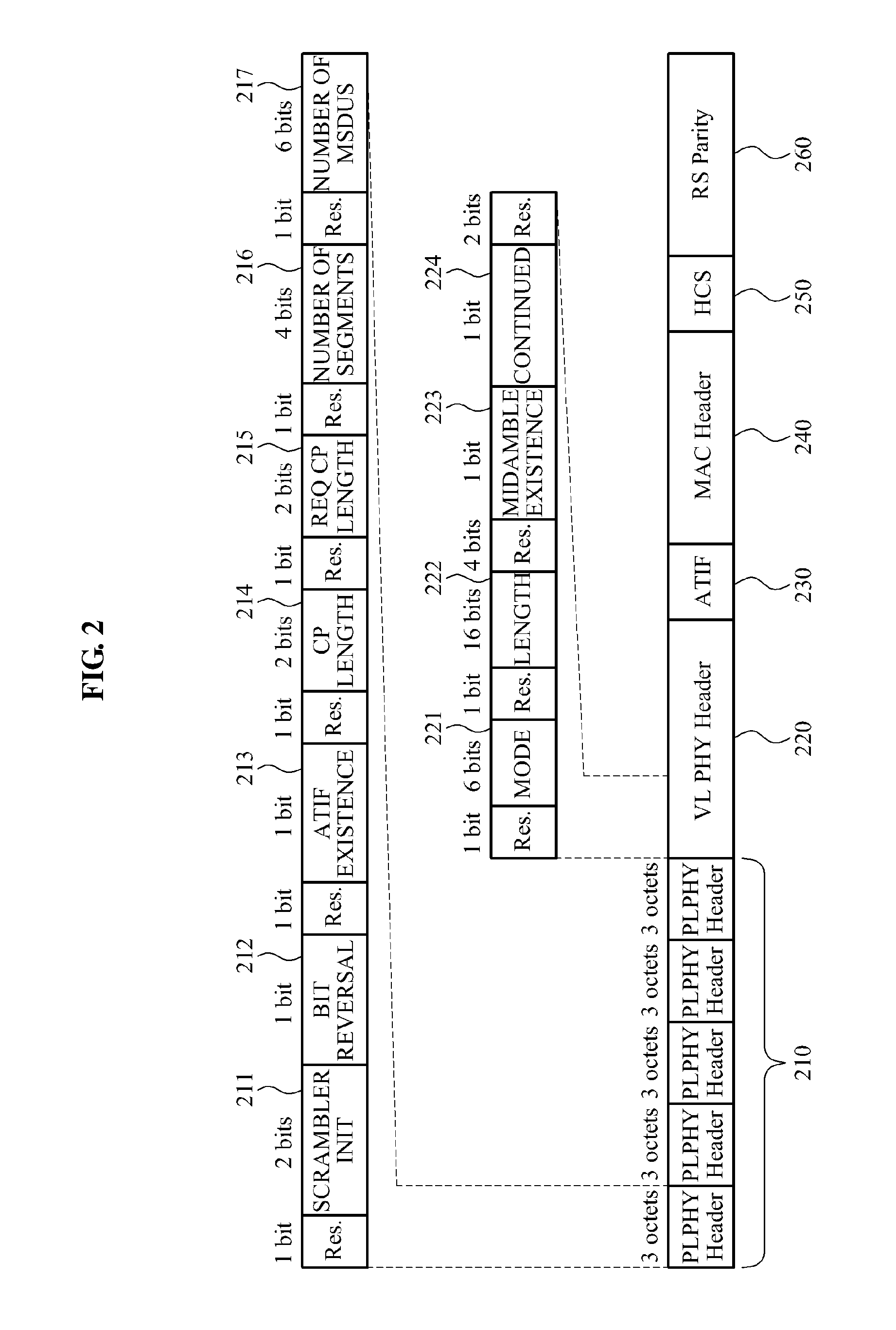

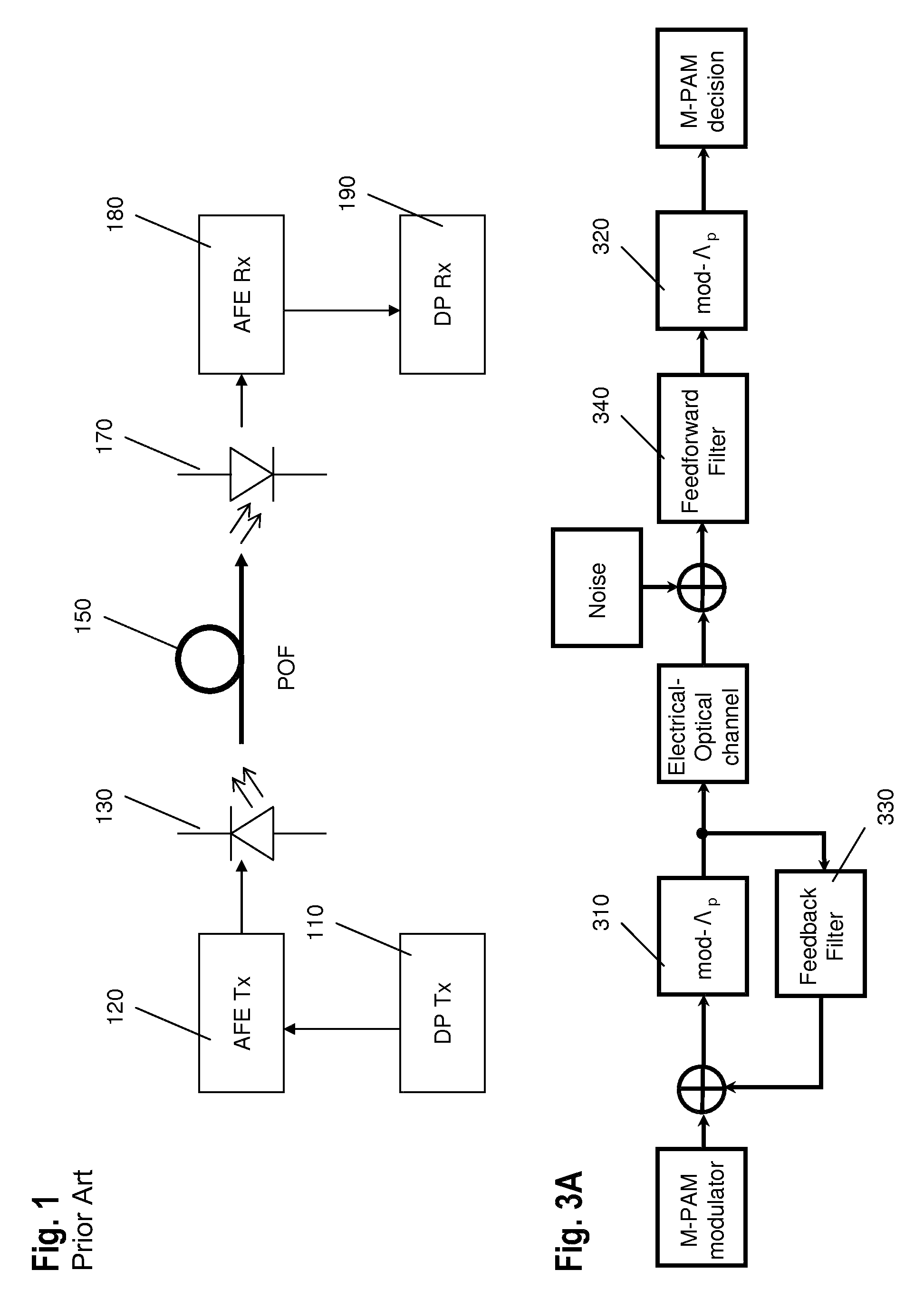

Transmission/reception apparatus and method for frame including protocol version in ultra wideband system

InactiveUS20110044271A1Network traffic/resource managementWireless commuication servicesUltra-widebandComputer hardware

Provided is a transmission / reception apparatus and method for transmitting a frame in an ultra wideband radio communication system, which may enable a protocol version to be included in a fixed-length physical layer protocol (PHY) header so that interaction between systems using different protocol versions may be realized, and may enable information about a modulation and coding scheme to be included in a variable-length PHY header to thereby overcome a decoding delay problem occurring due to a Reed Solomon code.

Owner:ELECTRONICS & TELECOMM RES INST

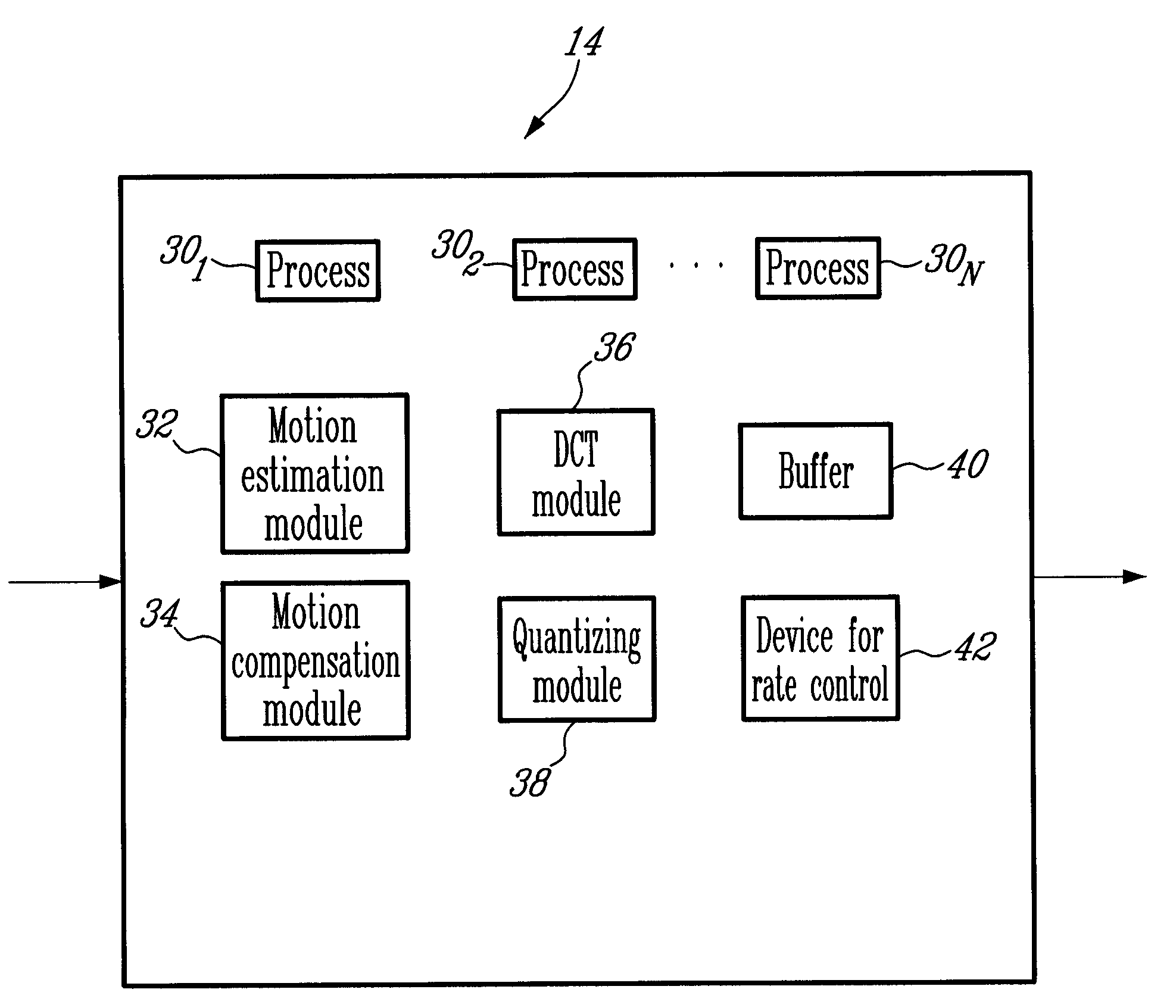

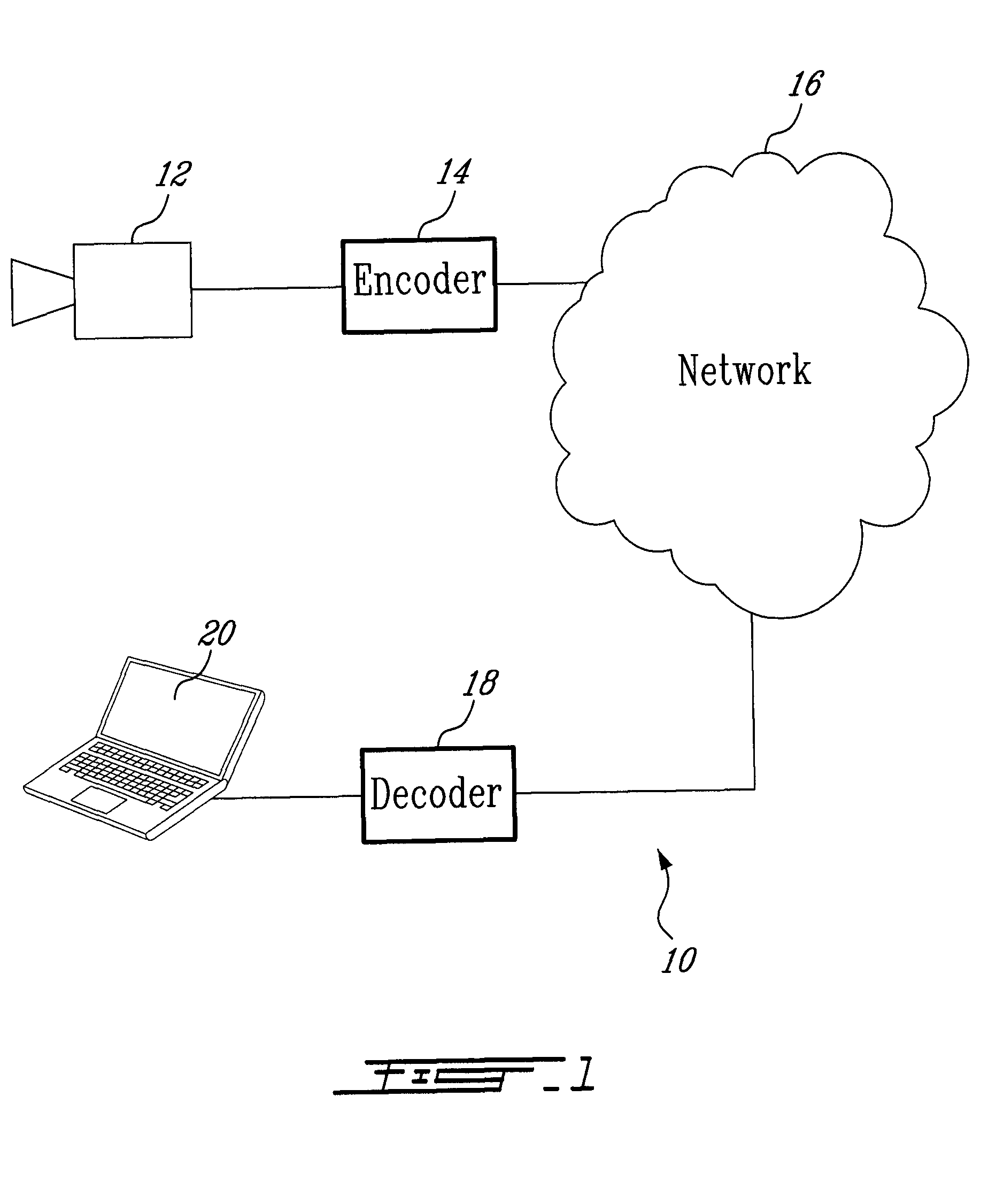

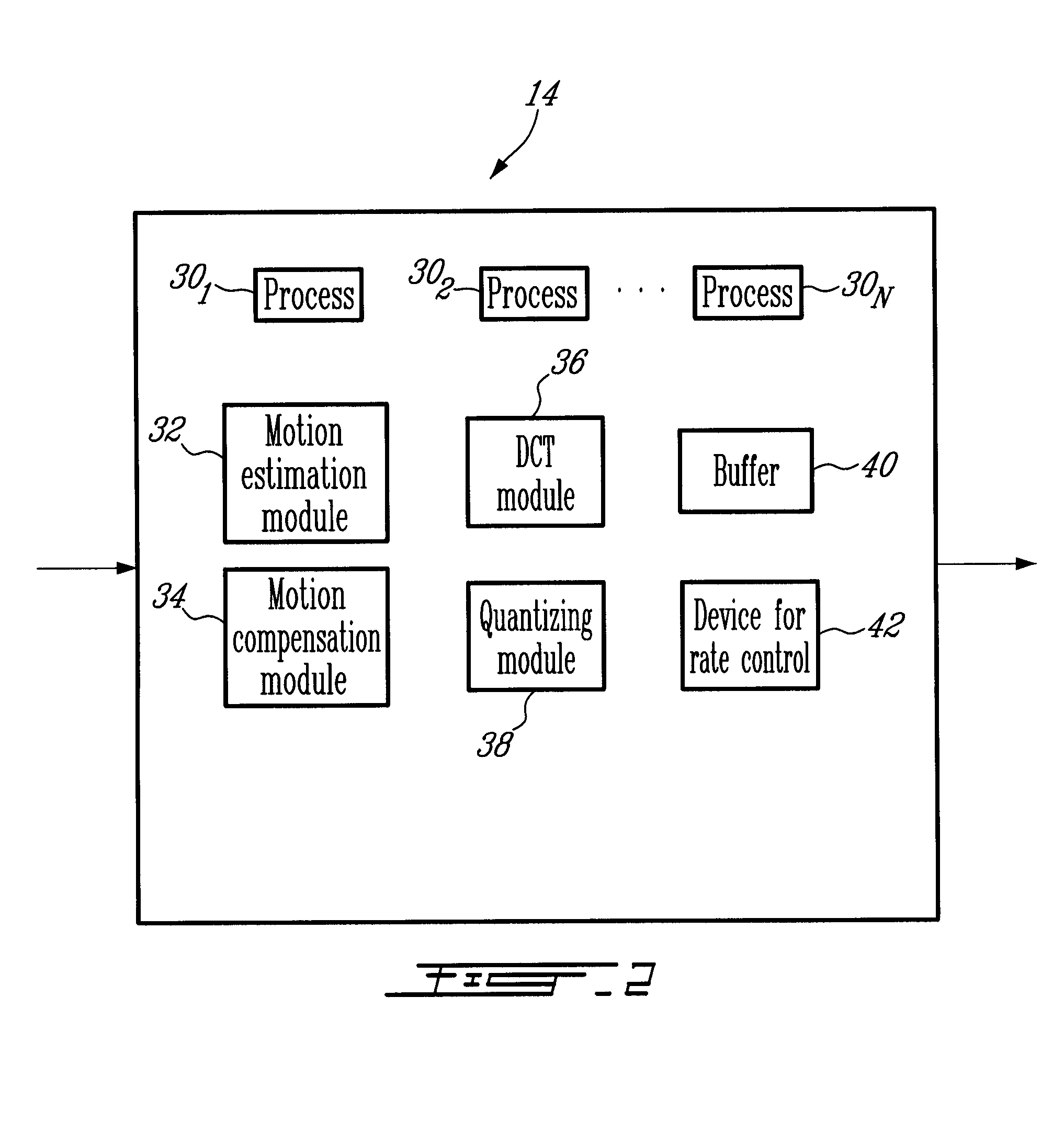

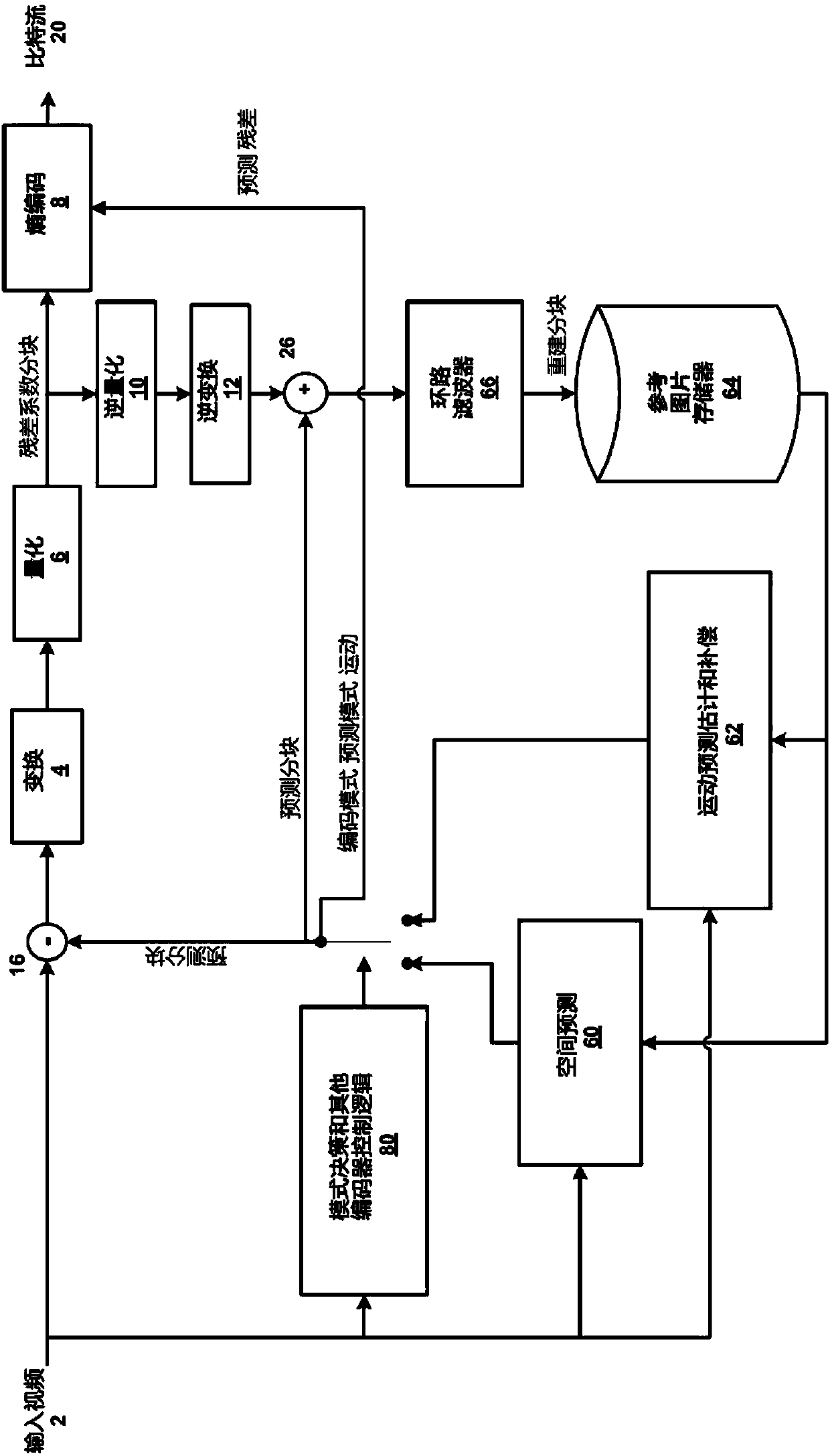

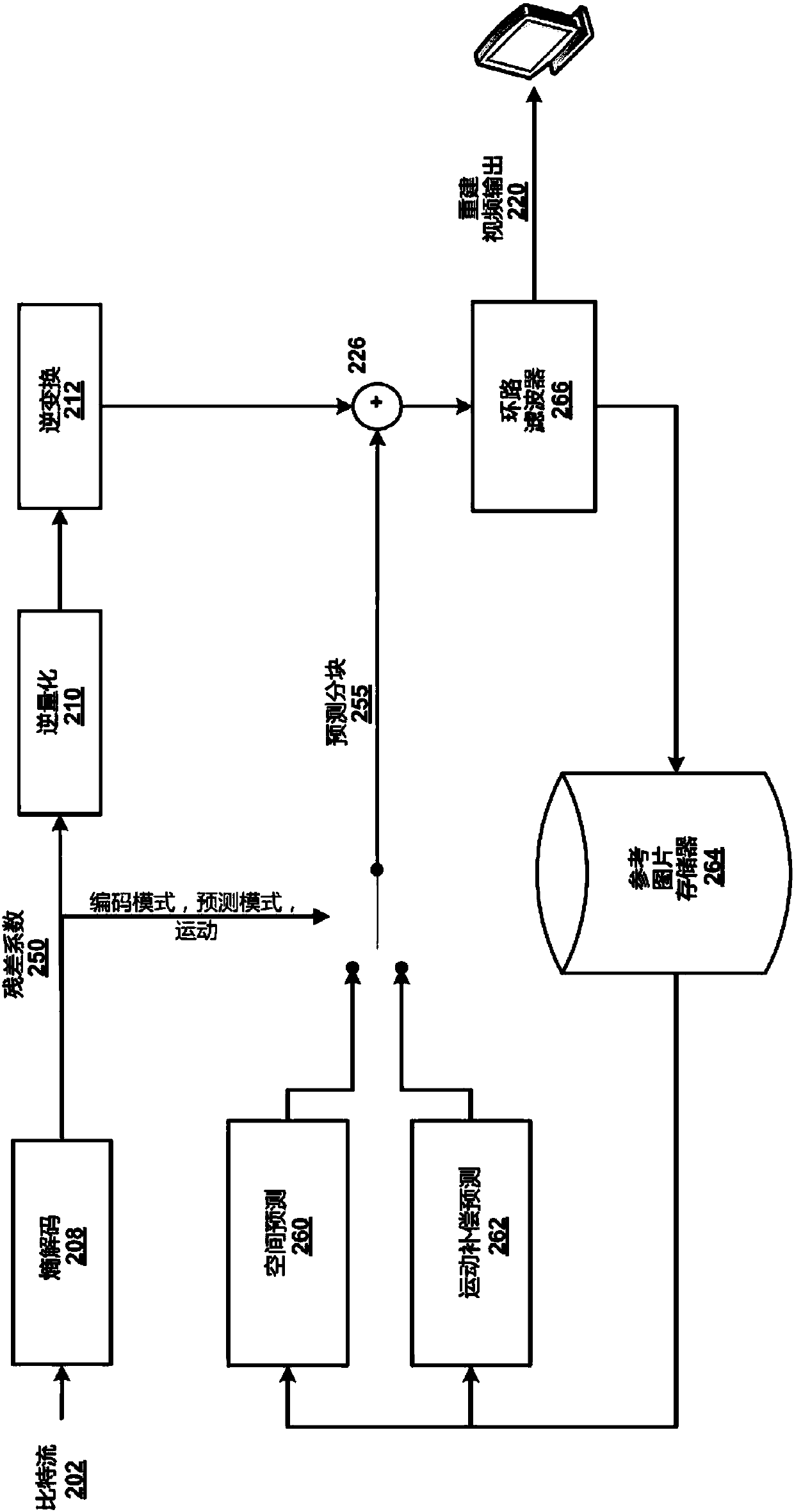

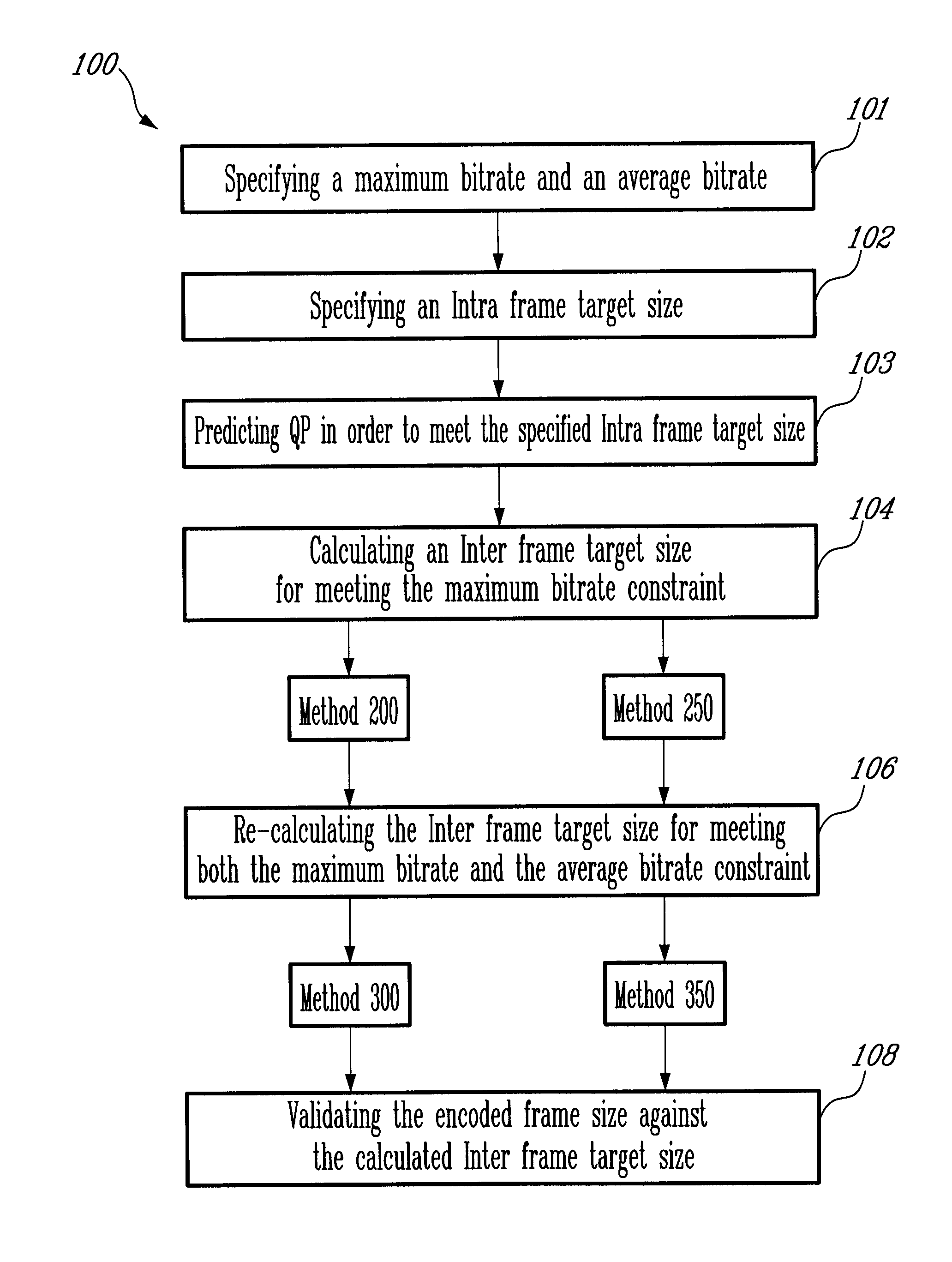

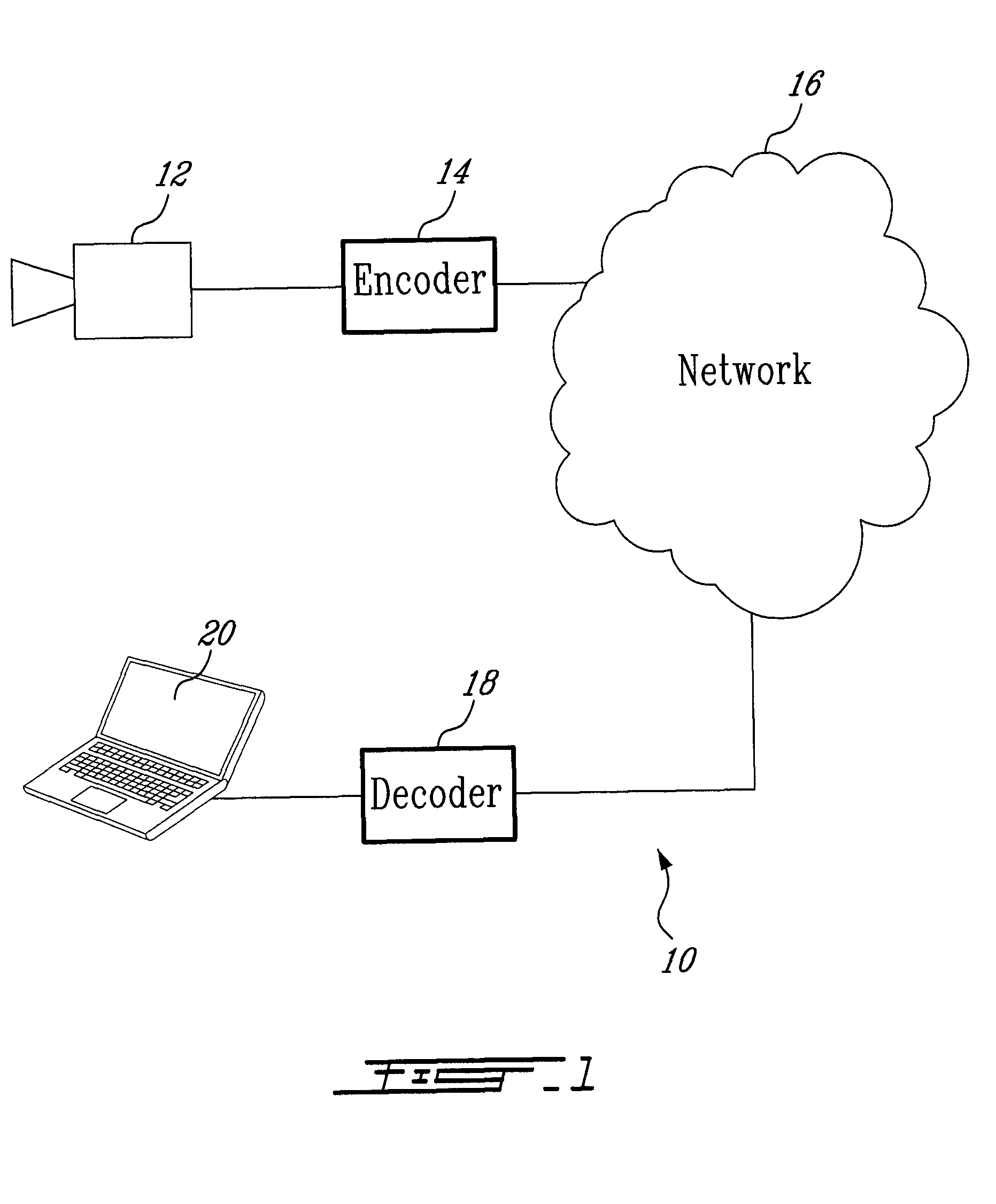

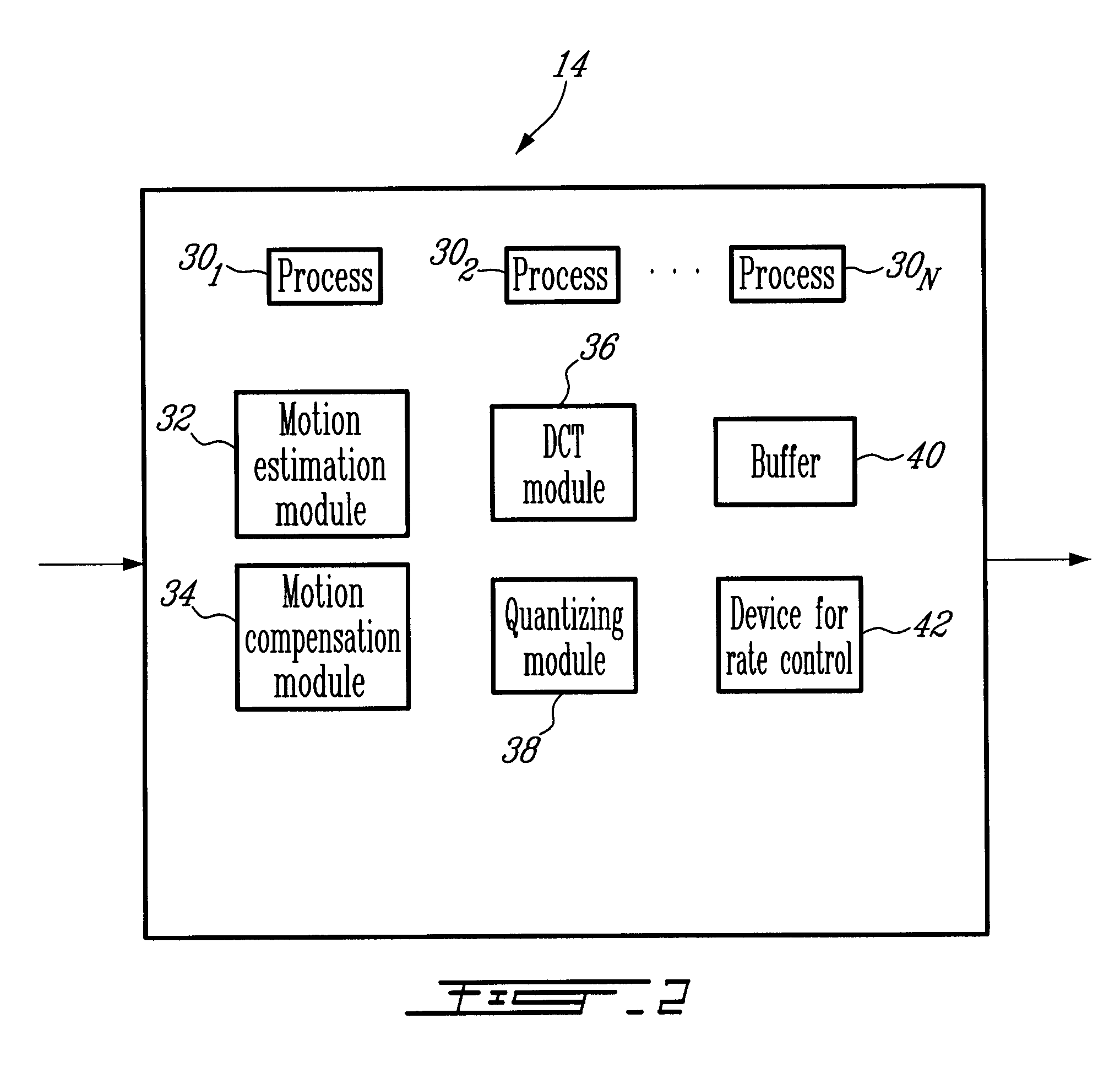

Video Rate Control for Video Coding Standards

ActiveUS20100080292A1Quality improvementColor television with pulse code modulationColor television with bandwidth reductionVideo rateVideo encoding

A method and device for improving rate controlling in video coding of sequences including a series of Inter frames separated by Intra frames, when a decoding delay is considered, comprise for each Inter frame of the series: computing a target frame size, computing a maximum buffer level related to a position of each Inter frame relative to a previous Intra frame and an upcoming Intra frame, and optimizing a transmission buffer level in response to the computed target frame size and the computed maximum buffer level.

Owner:MASIMO CORP

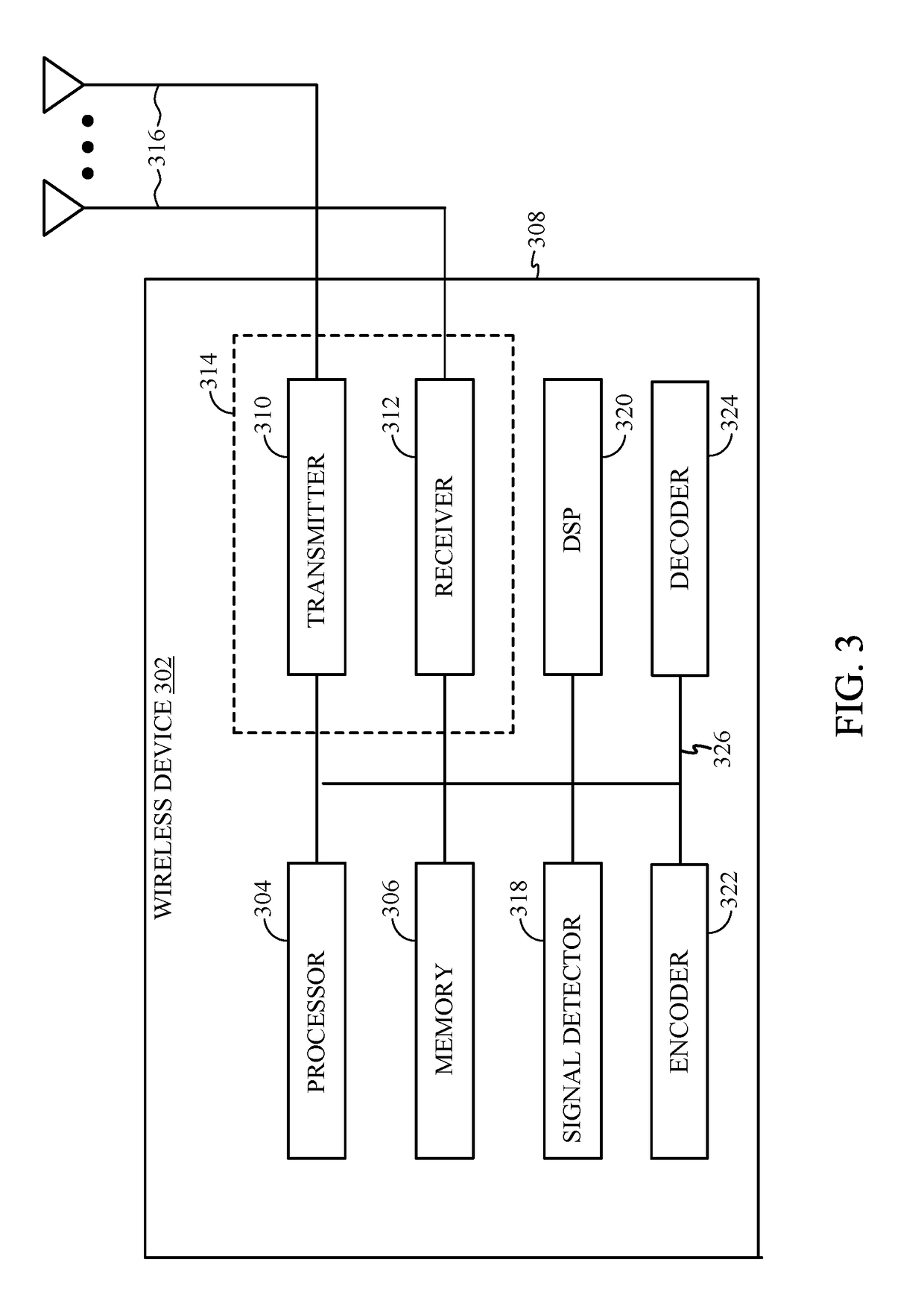

Generalized polar code construction

InactiveUS20170353267A1Error preventionError correction/detection using linear codesComputer hardwareComputer science

Certain aspects of the present disclosure relate to techniques and apparatus for improving decoding latency and performance of Polar codes. An exemplary method generally includes generating a codeword by encoding information bits using a first code of length K to obtain bits for transmission via K channels, wherein the first code comprises a polar code, further encoding the bits in each of the K channels using a second code of length M, and transmitting the codeword.

Owner:QUALCOMM INC

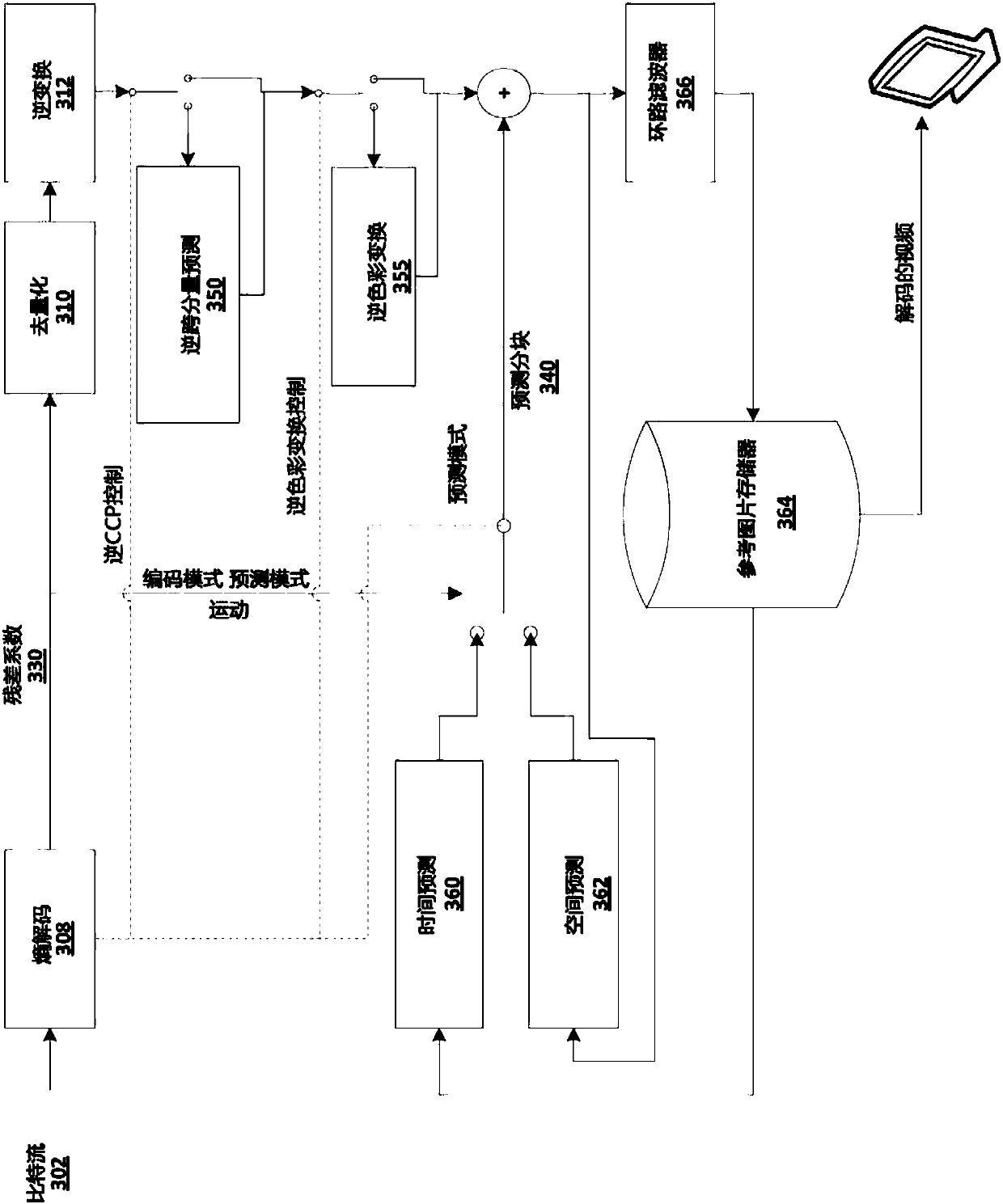

Inter-component de-correlation for video coding

Cross-component prediction (CCP) and adaptive color transform (ACT) may be performed concurrently in a video coding system. CCP and ACT may be enabled / disabled at the same level (e.g. at the transform unit level) via an indicator signaled in the bitstream such as the ACT enable indicator for the CU. Inverse CCP and ACT may be operated at the same level (e.g. at the transform unit level). Prediction residuals may be converted to original color space without waiting for reconstruction of luma and chroma residuals of an entire prediction unit or coding unit. CCP and ACT transforms may be combined into one process to reduce encoding / decoding latency. Differences in dynamic ranges of color components may be compensated by variable dynamic range adjustments. Differences in bit depths between luma and chroma components may be compensated by selectively disabling the ACT coding tool, scaling a component output of the CCP, adjusting a quantization parameters (QPs) and / or shifting a component output of an inverse transform of the video coding system.

Owner:VID SCALE INC

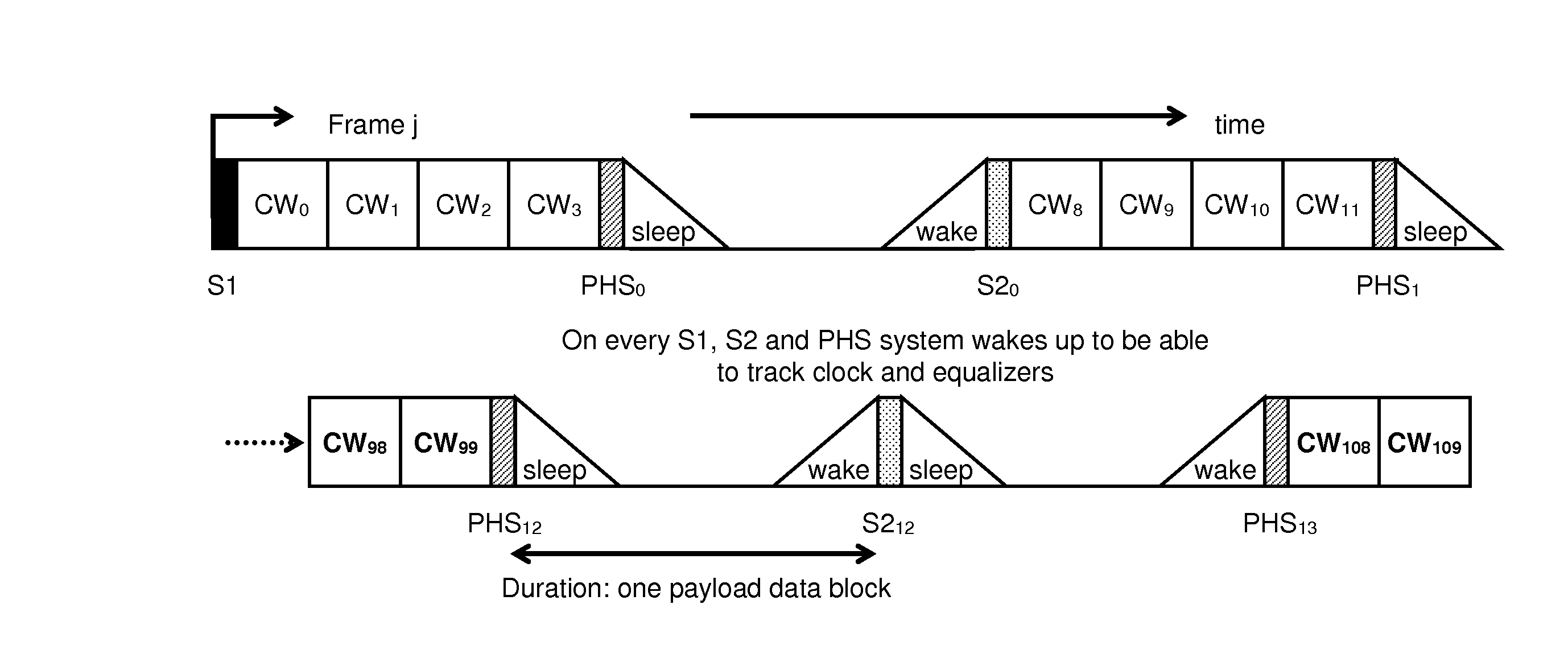

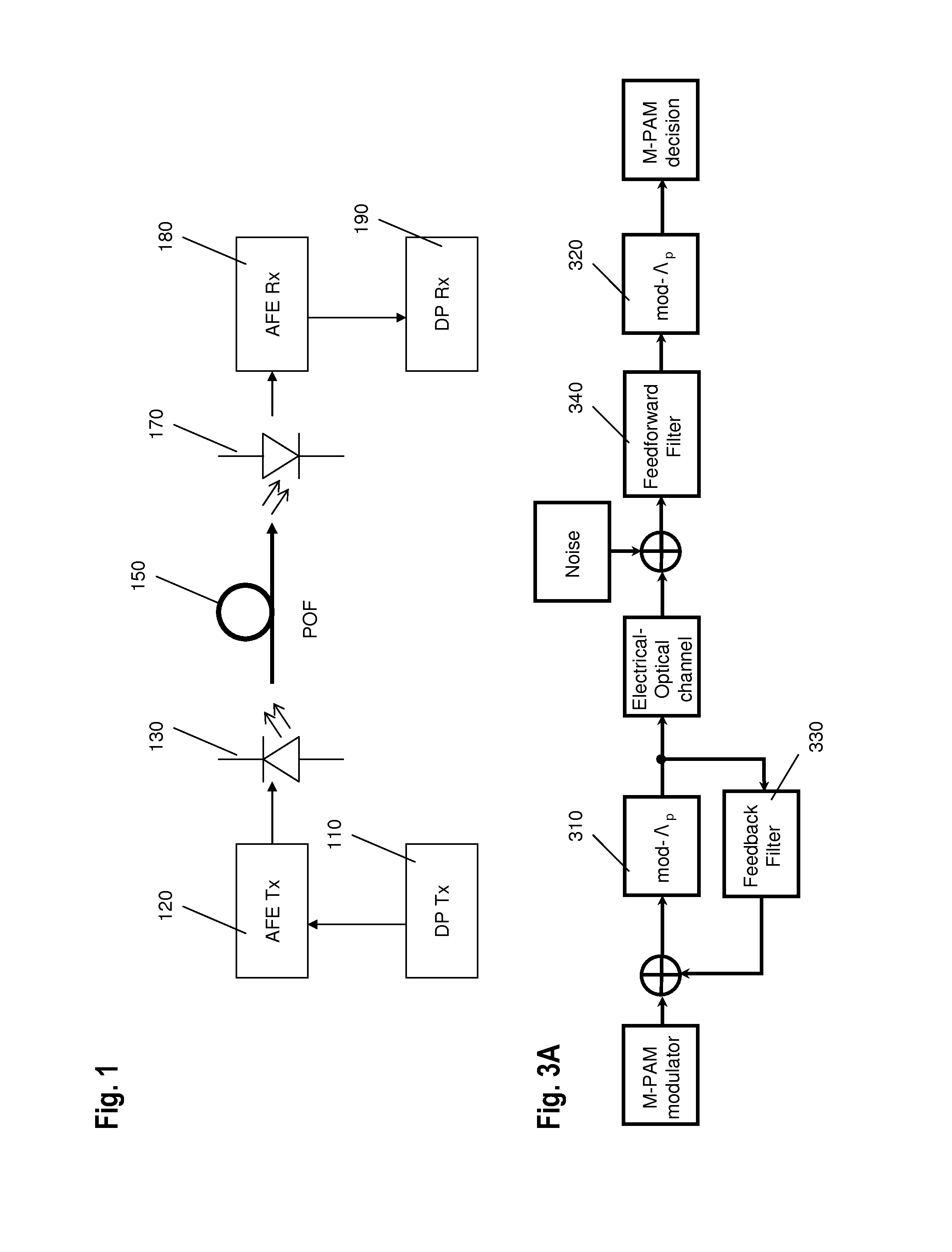

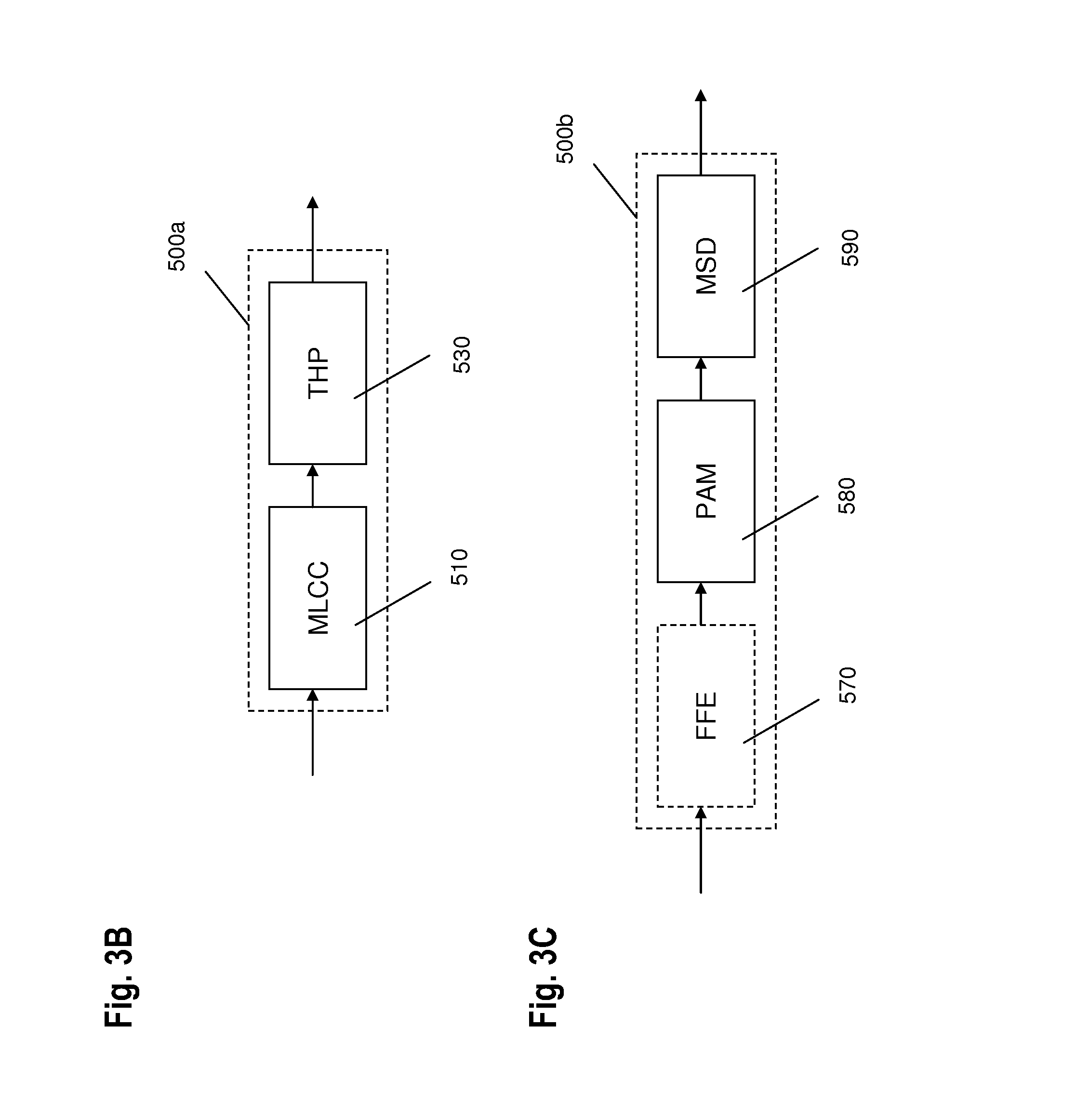

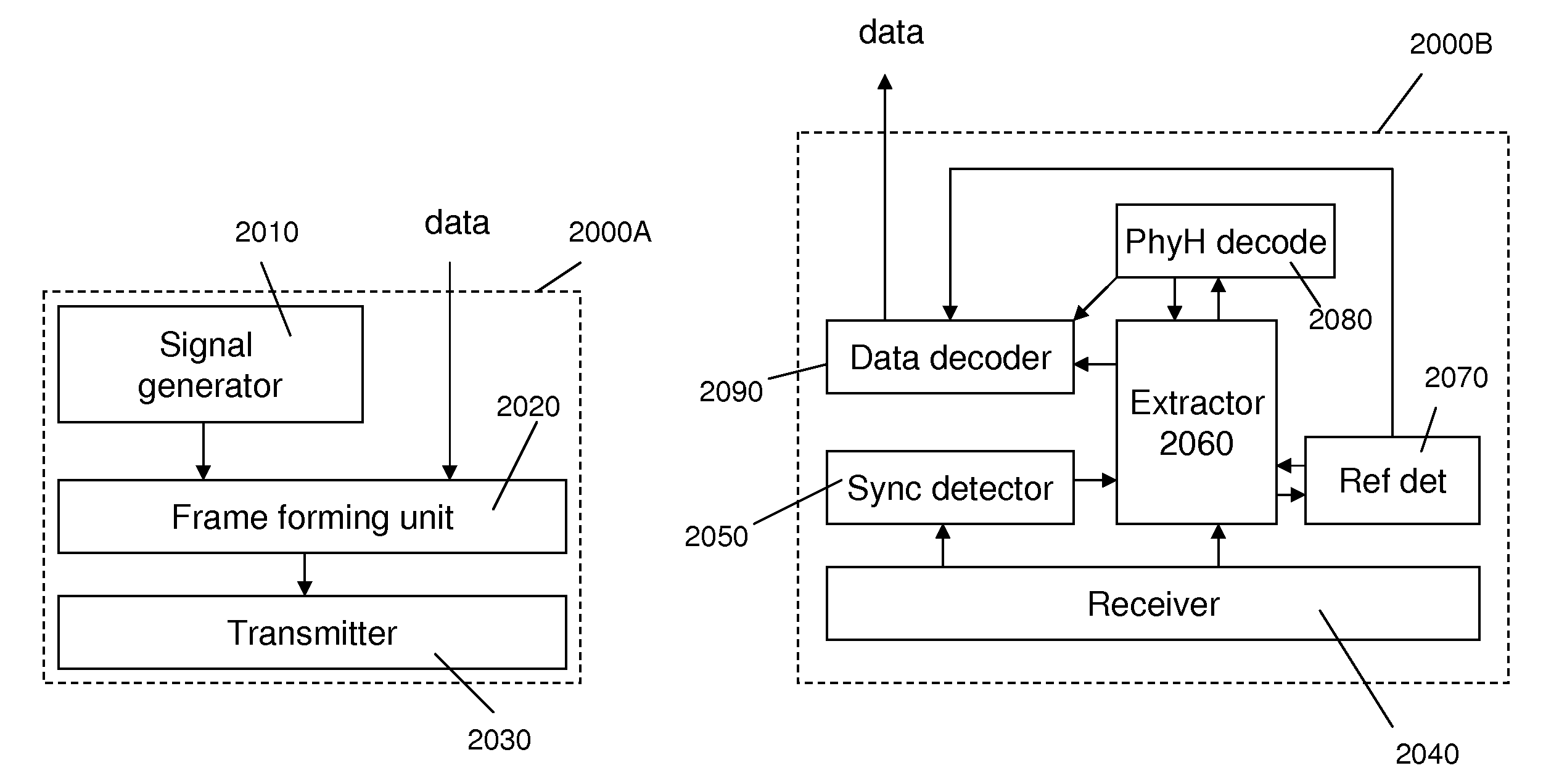

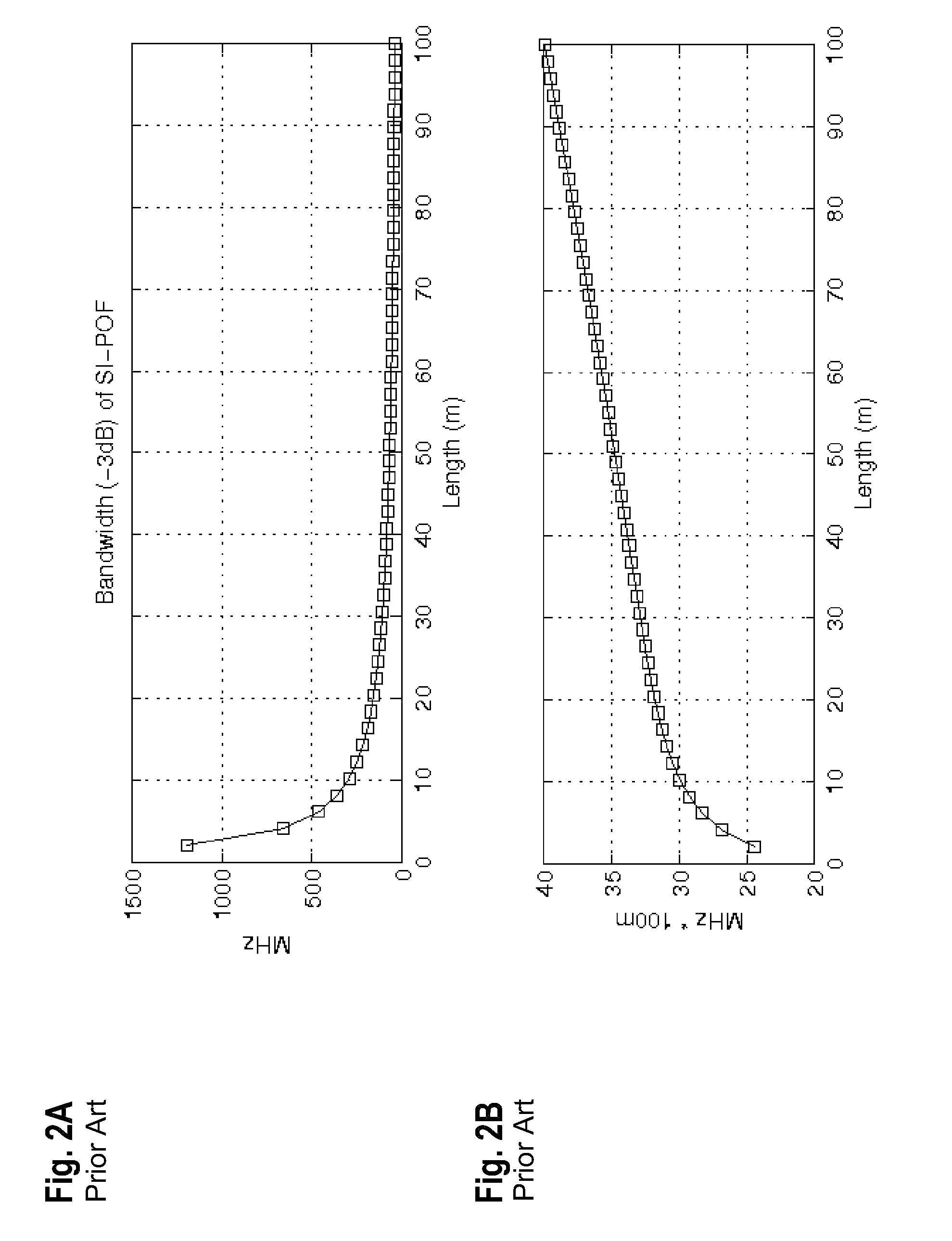

Frame Structure For Adaptive Data Communications Over A Plastic Optical Fibre

ActiveUS20130330082A1Efficient communication frame structureTime-division optical multiplex systemsFibre transmissionControl dataPlastic optical fiber

The present invention relates to transmission and reception of data over a plastic optical fibre. In particular, the present invention provides for transmission and reception over the plastic optical fibre a particularly suitable frame structure. The frame structure includes a synchronization sequence and portions of user data alternating with alternating reference signal portions and control data portions. The length of the user data portions may be equal, the length of the synchronization sequence and the control data and reference signal portions may also be equal. The distances between the synchronization sequence and the reference signal portions and the control data portions are advantageously equal. The alternating of data and additional information avoids data decoding latency while maintaining the rate necessary for the additional information.

Owner:KNOWLEDGE DEV FOR POF SL

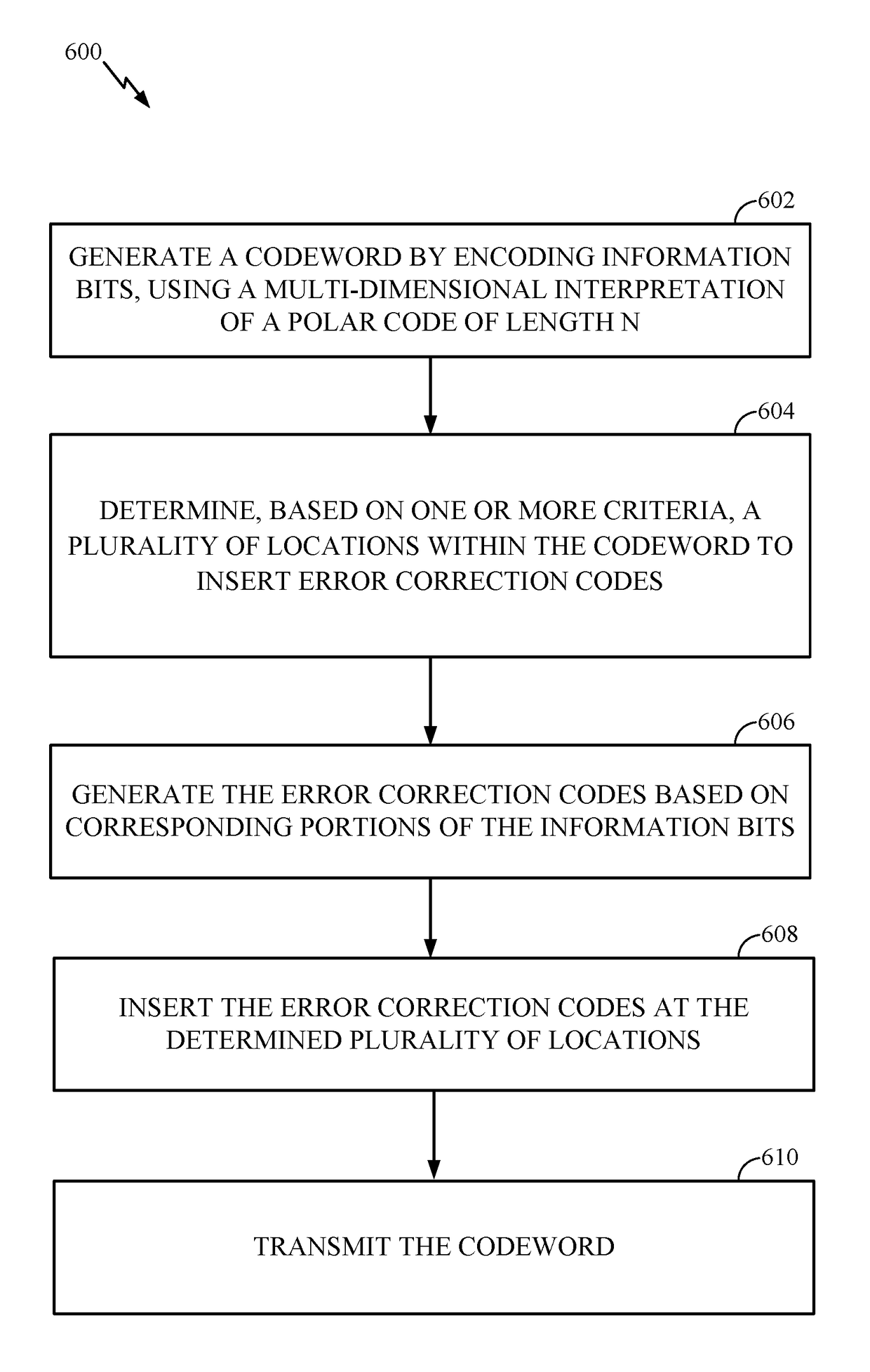

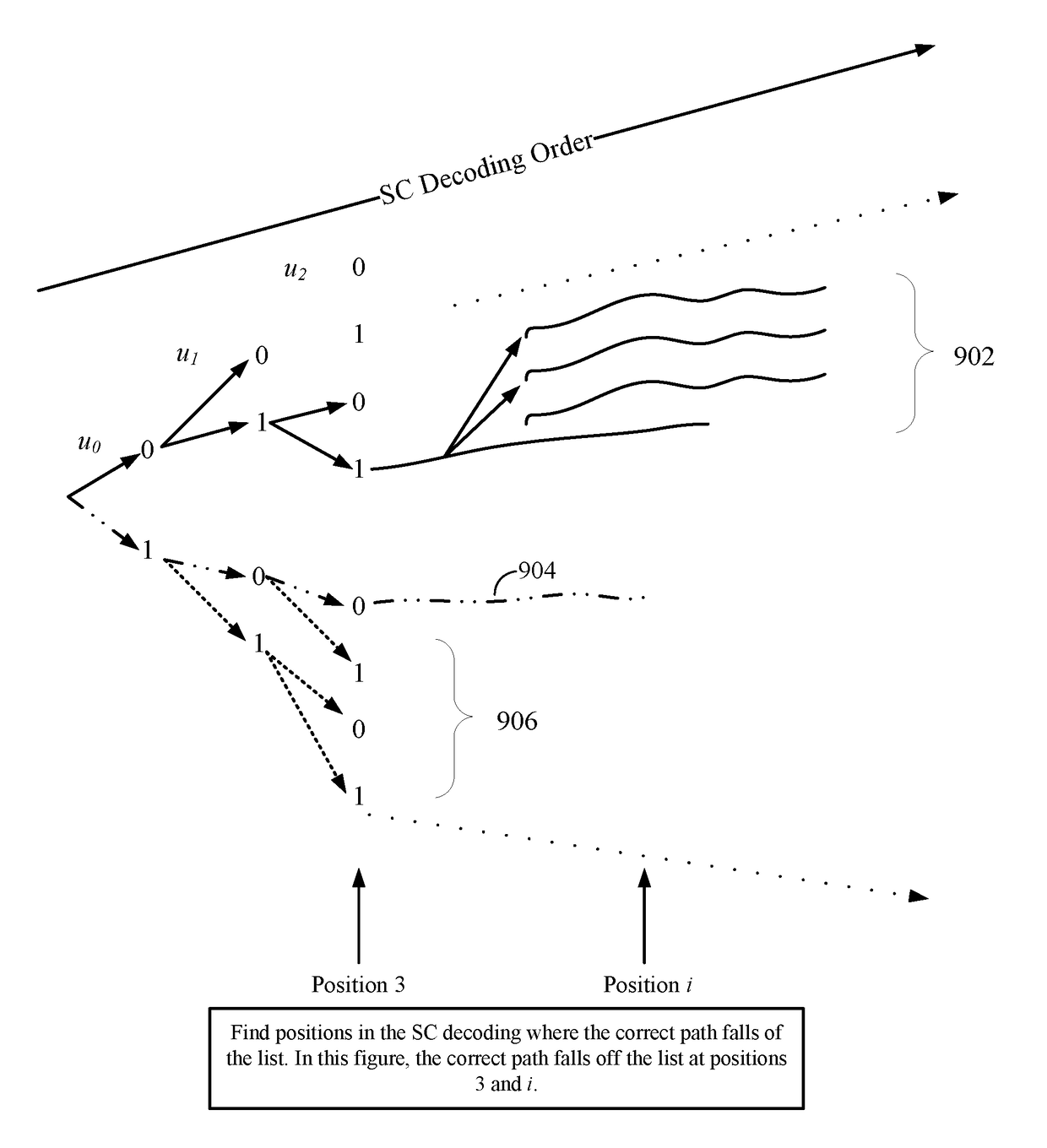

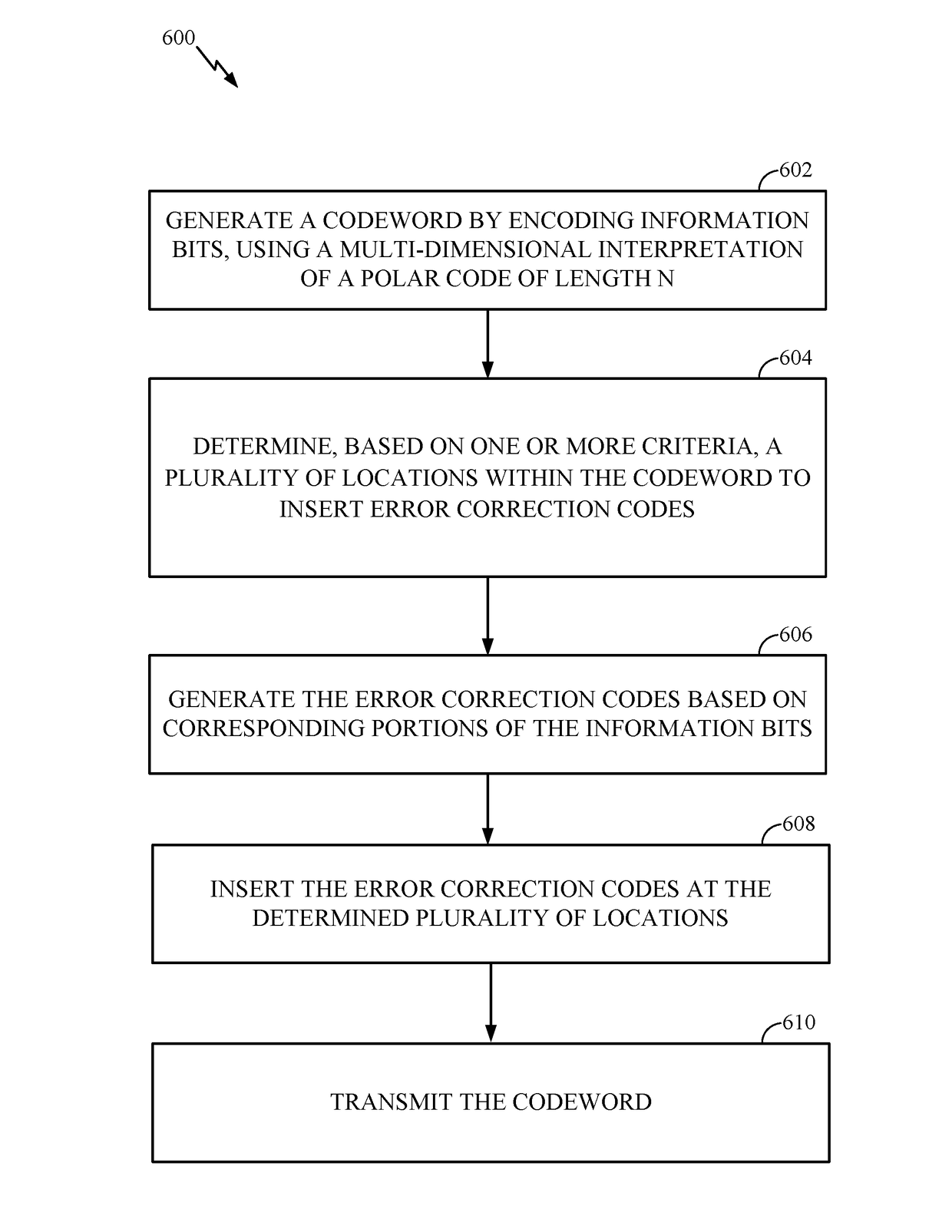

Enhanced polar code constructions by strategic placement of CRC bits

Certain aspects of the present disclosure relate to techniques and apparatus for improving decoding latency and performance of Polar codes. An exemplary method generally includes generating a codeword by encoding information bits, using a multi-dimensional interpretation of a polar code of length N, determining, based on one or more criteria, a plurality of locations within the codeword to insert error correction codes generating the error correction codes based on corresponding portions of the information bits, inserting the error correction codes at the determined plurality of locations, and transmitting the codeword. Other aspects, embodiments, and features are also claimed and described.

Owner:QUALCOMM INC

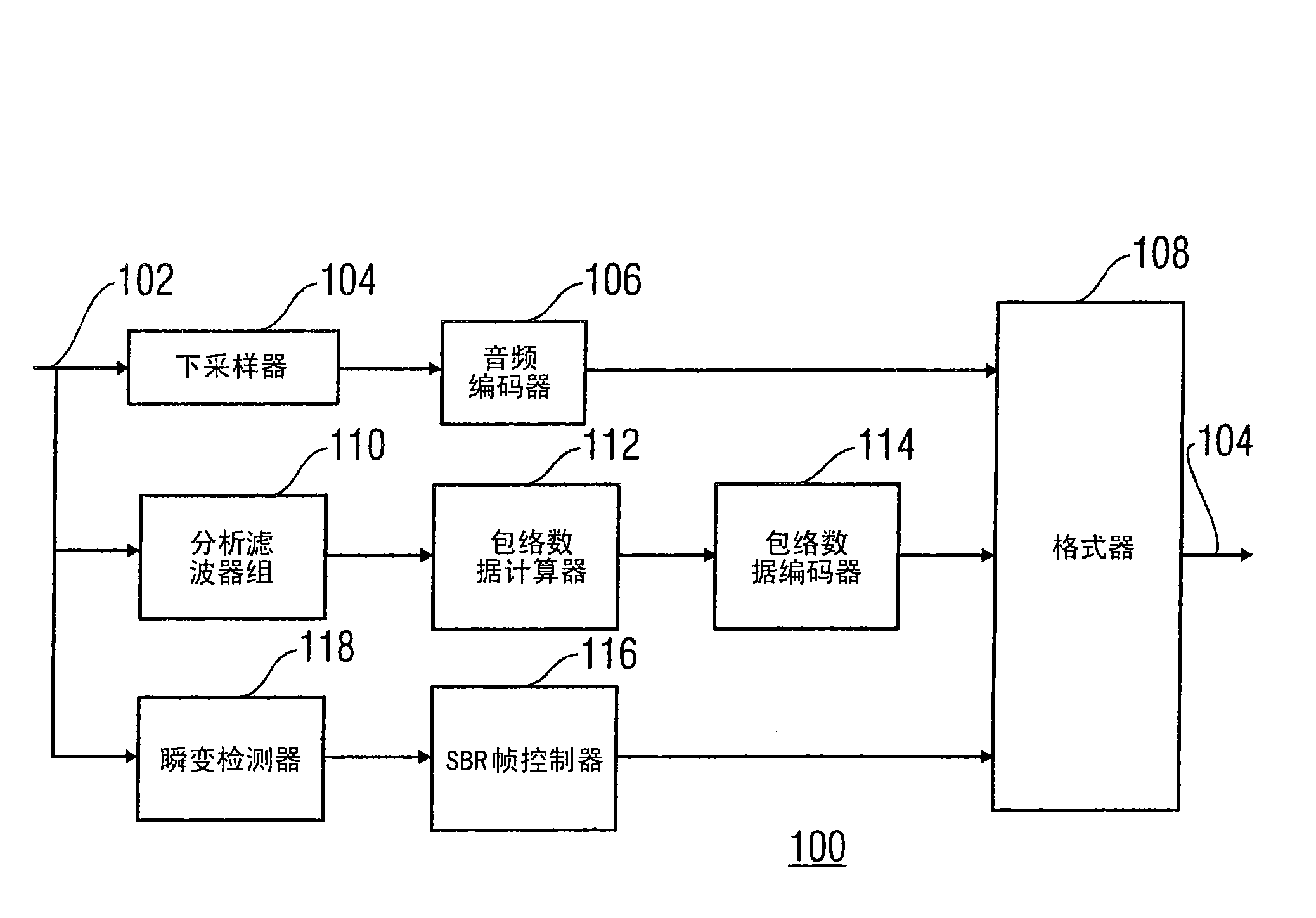

Coding of an information signal

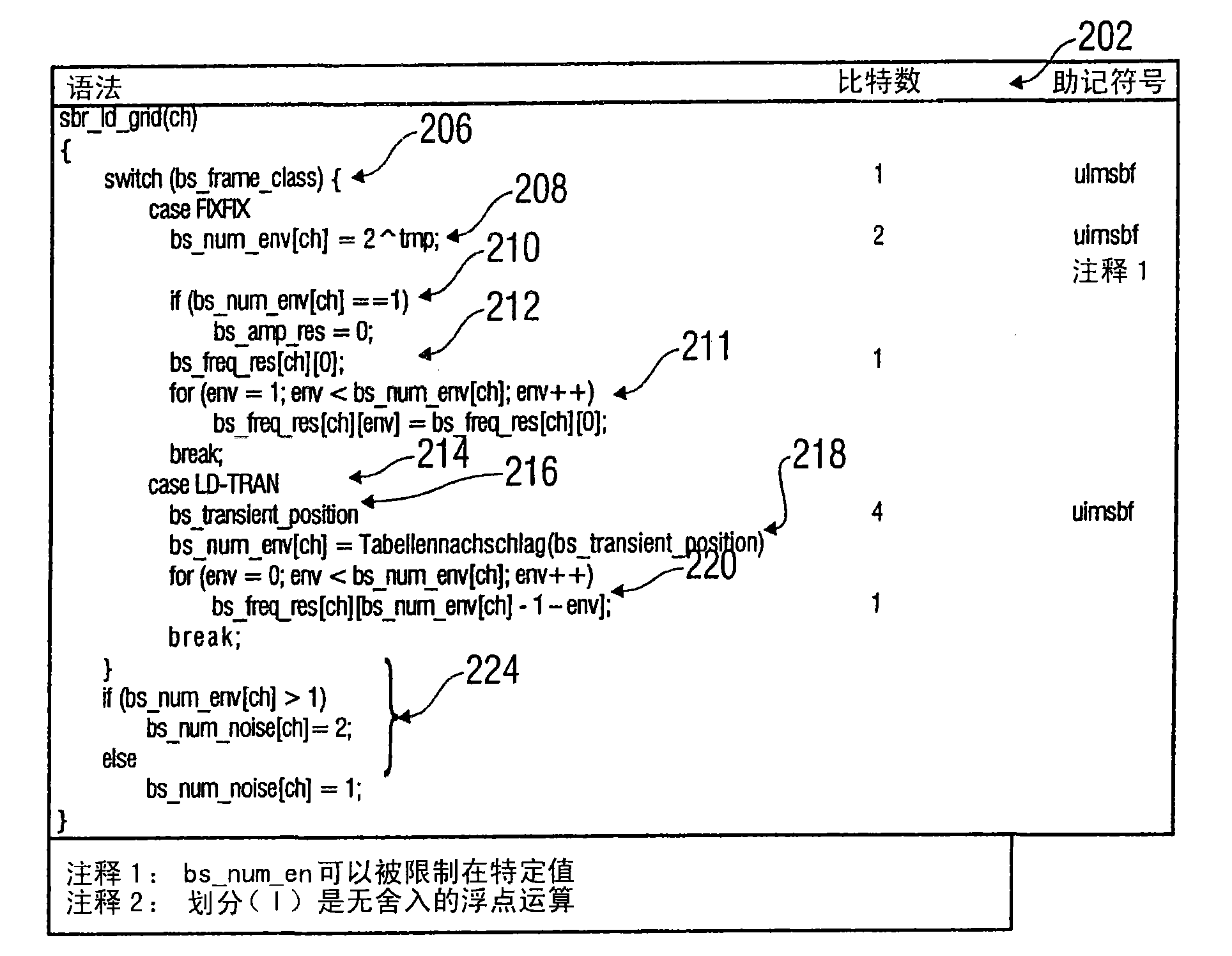

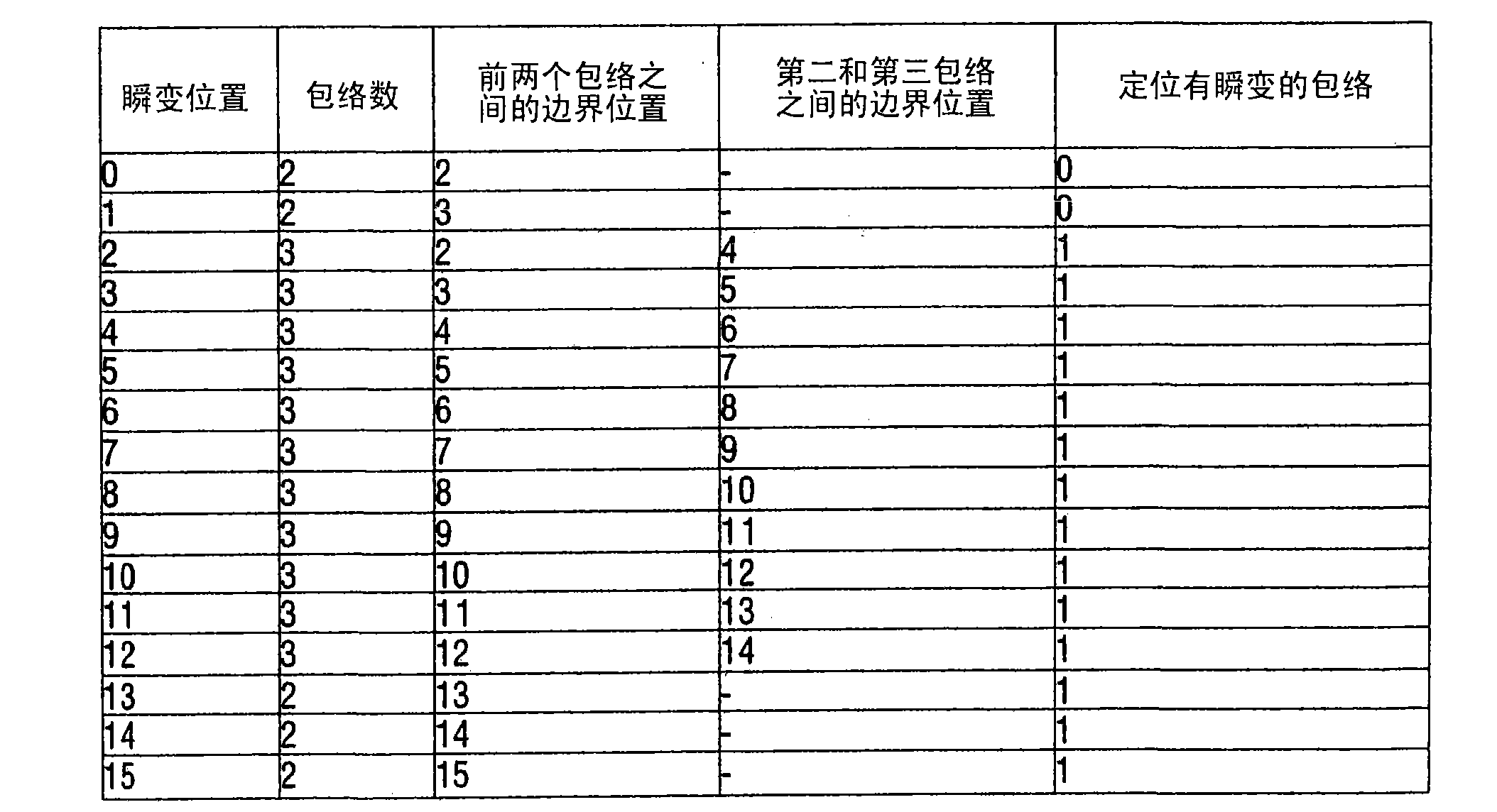

ActiveCN101529503AResolve transientsFix/or pre-echo issueSpeech analysisCode conversionSyntaxComputer science

The problem of transients can be addressed satisfactorily and a further decoding delay can be reduced for this if use is made of a new SBR frame class in which the frame limits (902a, 902b) are not shifted, that is to say the grid limits are still synchronized with the frame limits (902a, 902b), but in which a statement of the transient position is also used as a syntax element in order to be used, within the frames of this new frame class, to determine the grid limits within these frames at the coder and / or decoder end.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

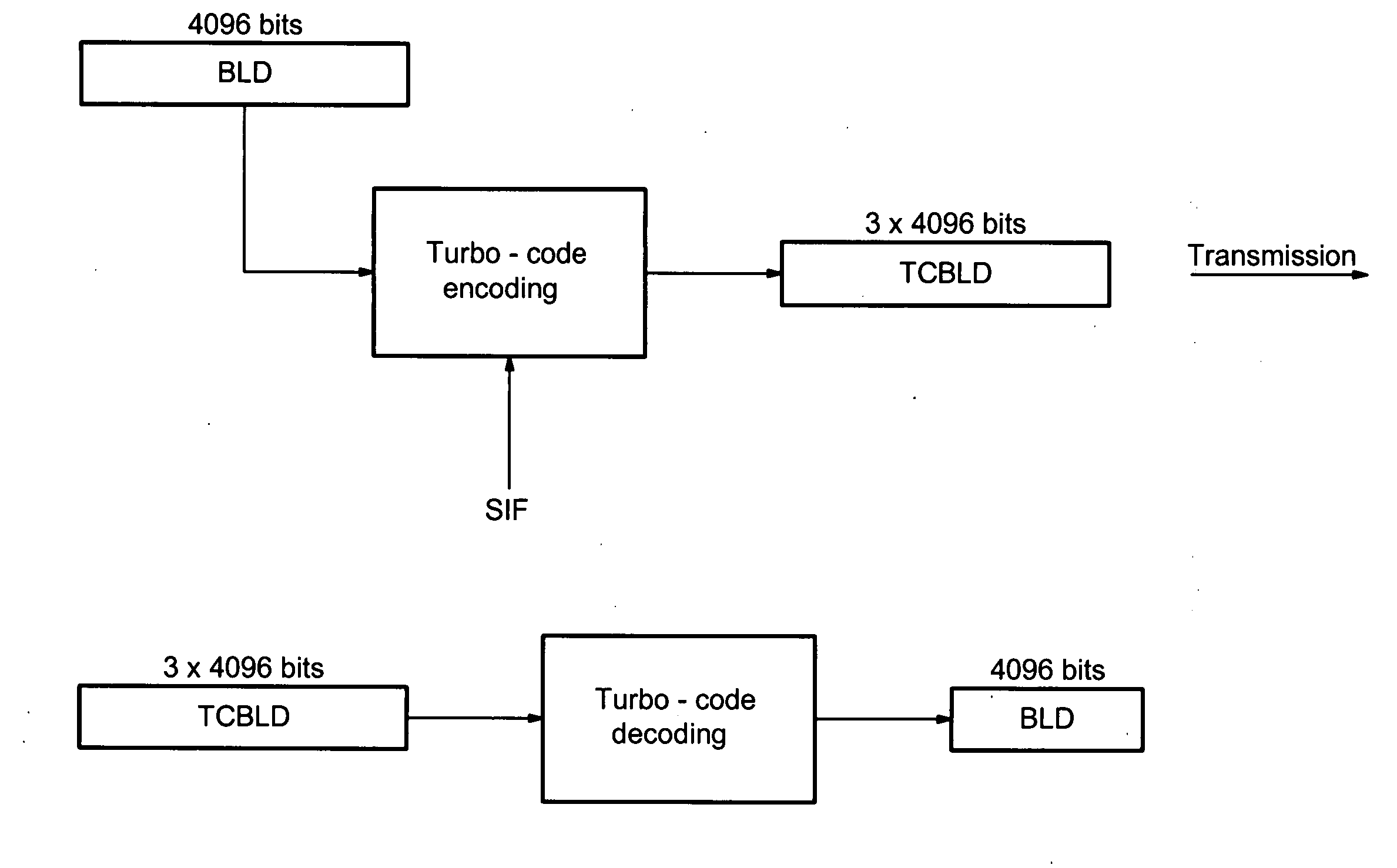

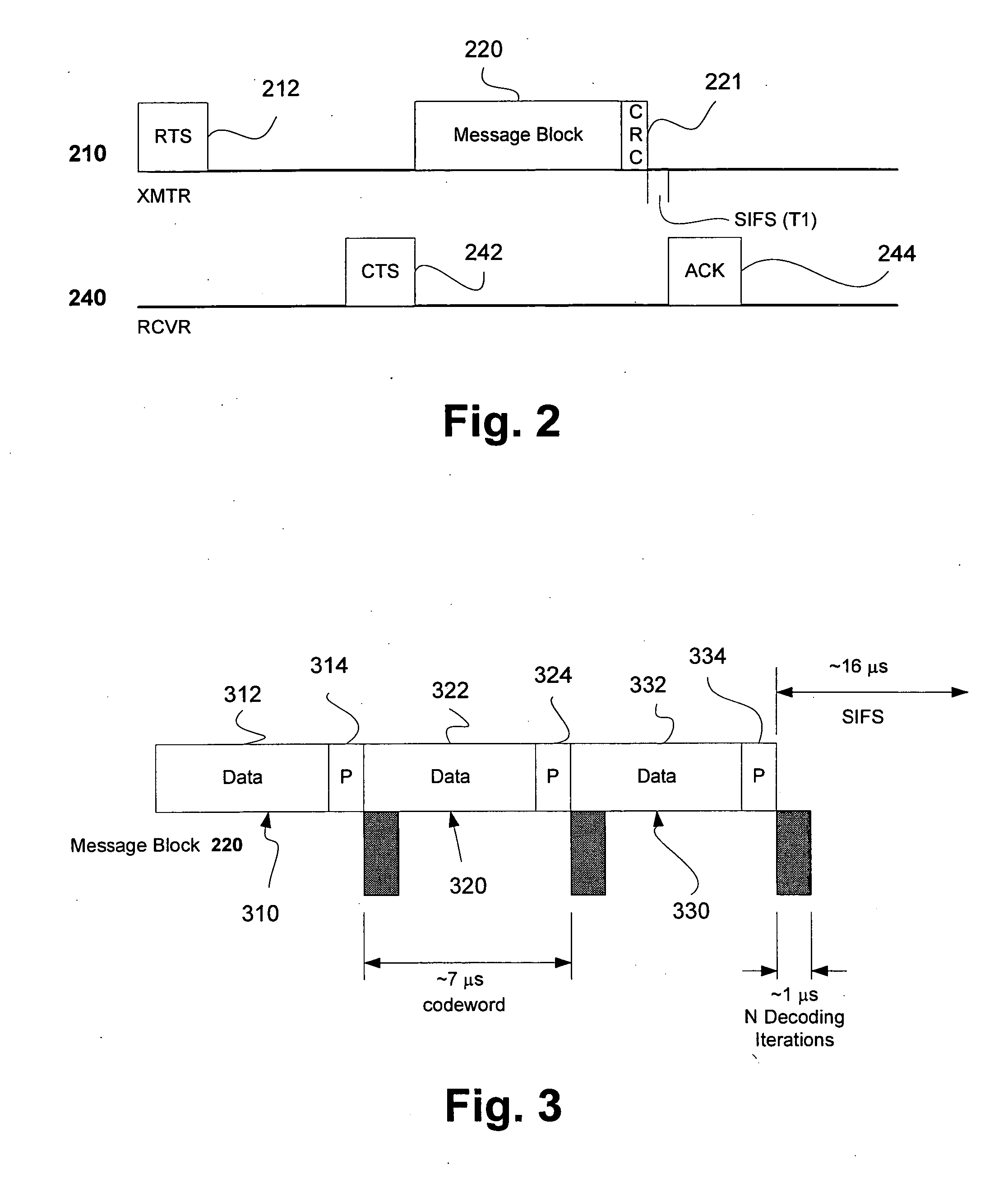

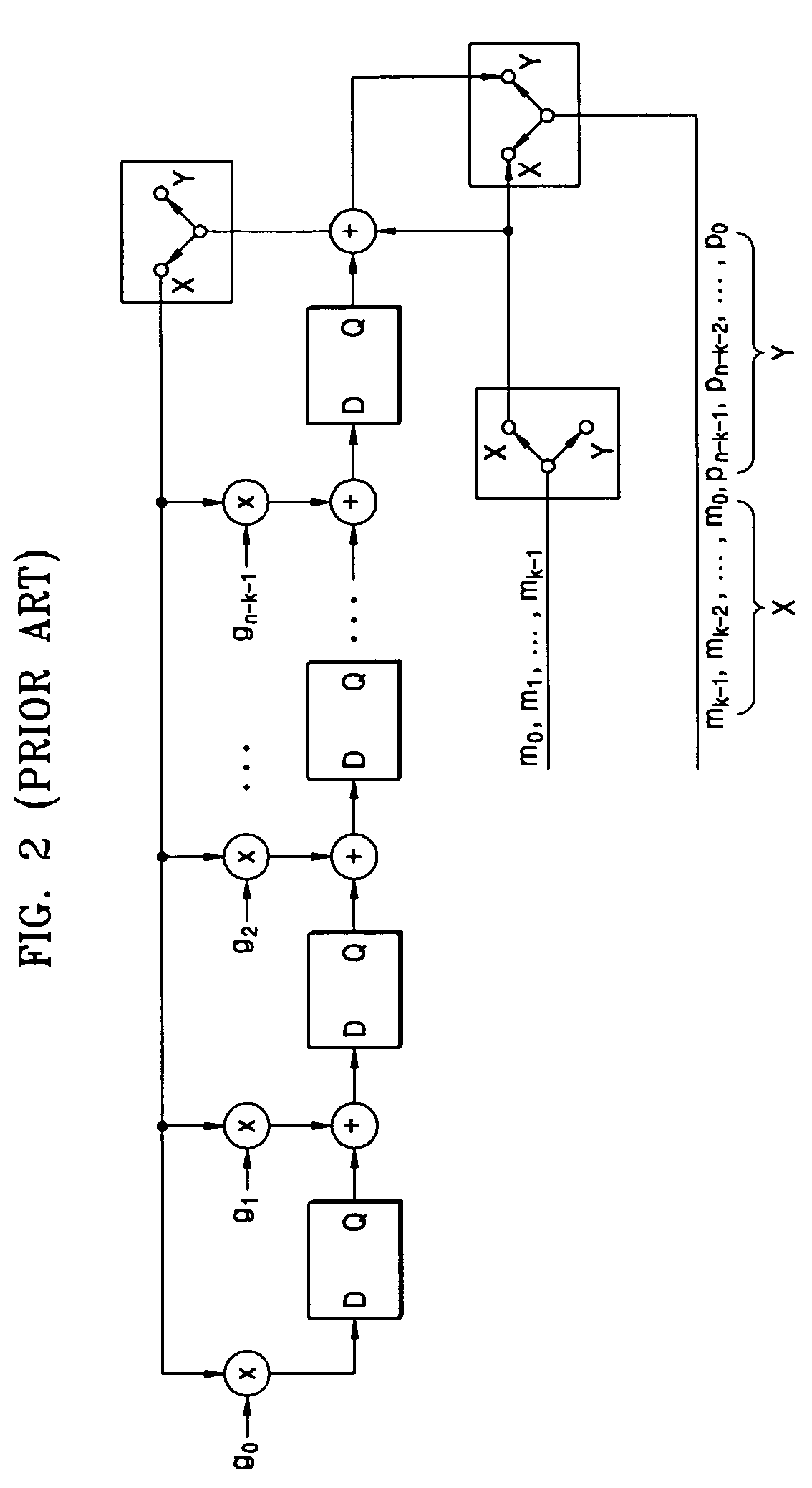

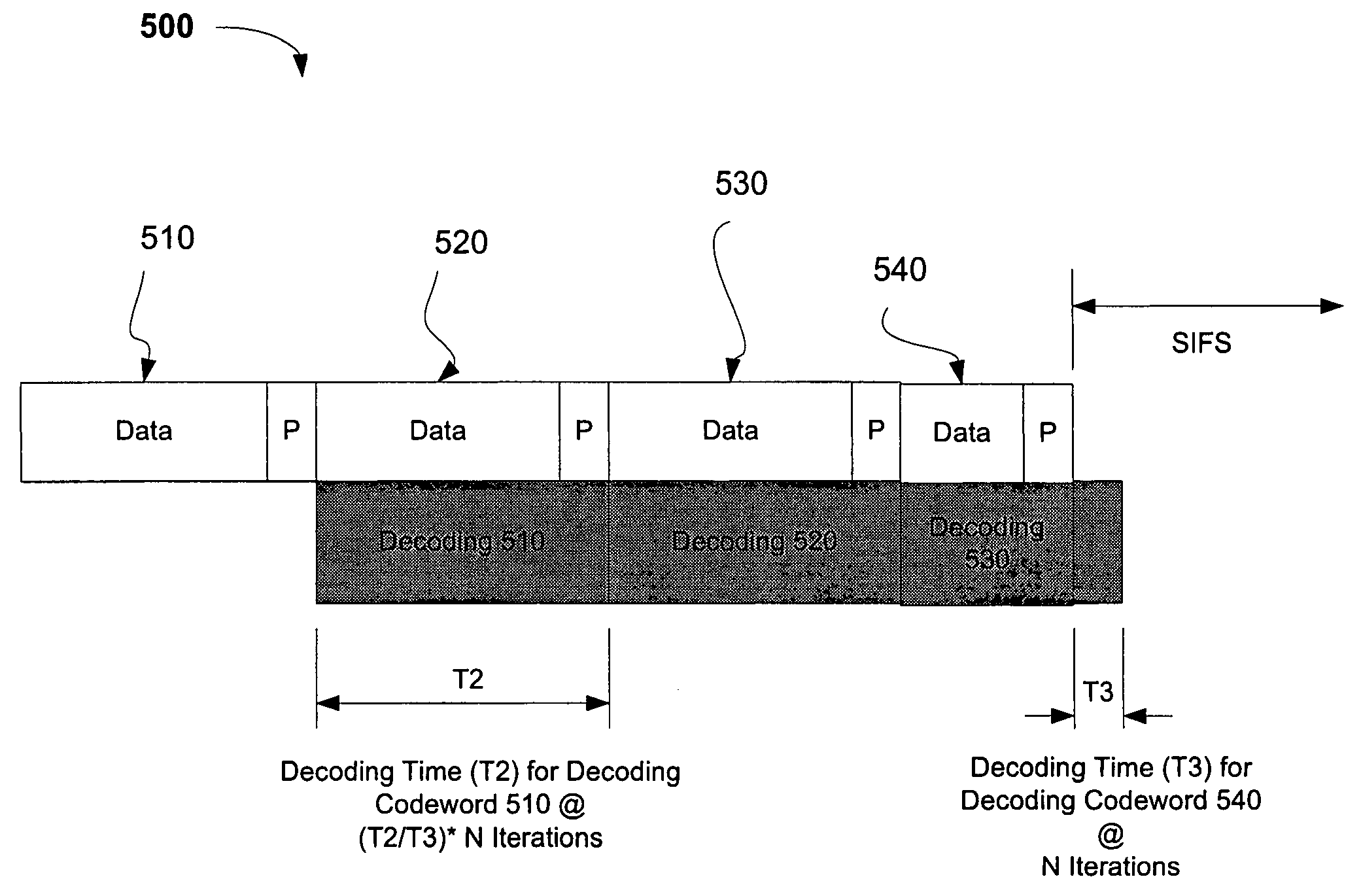

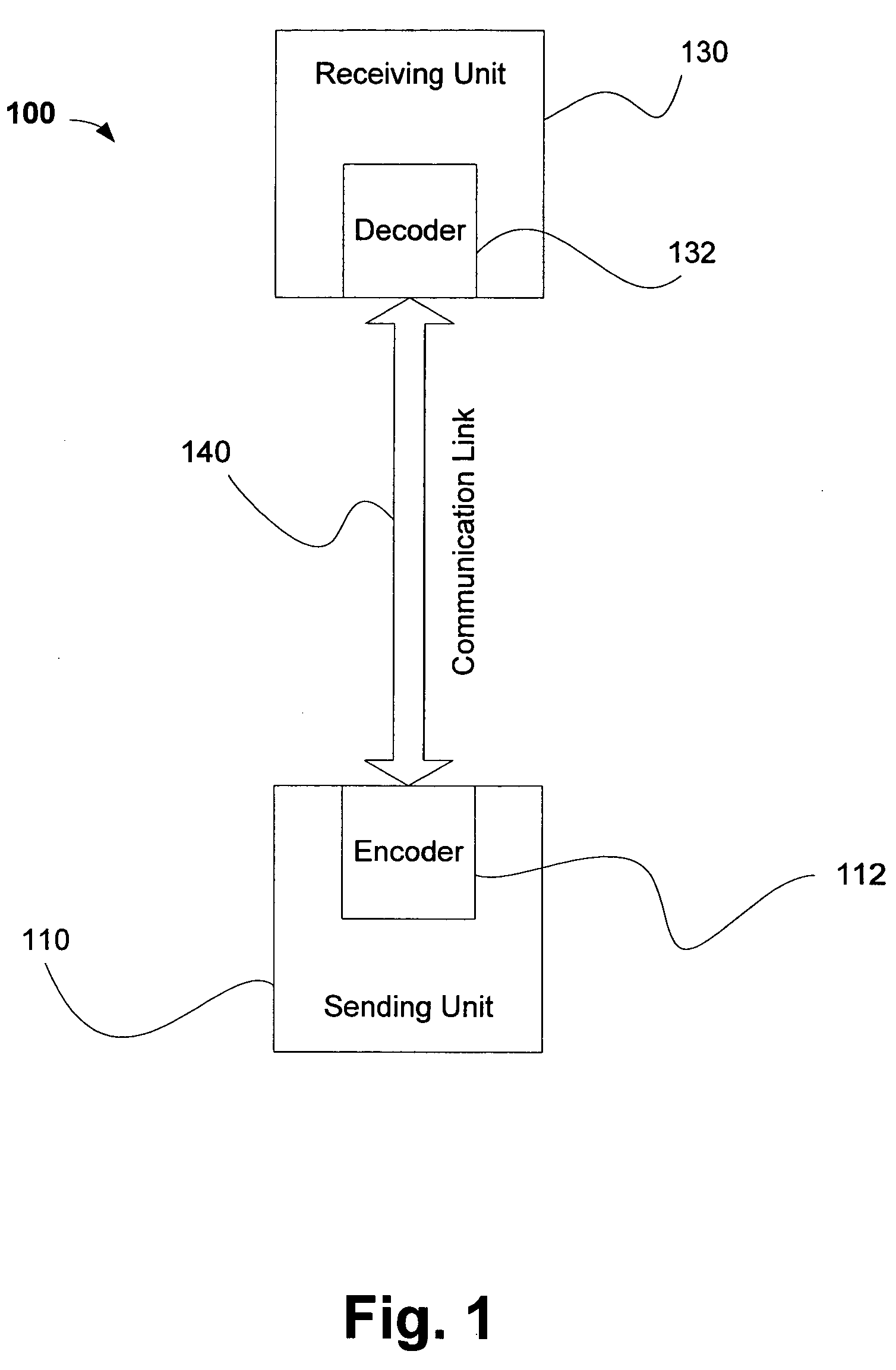

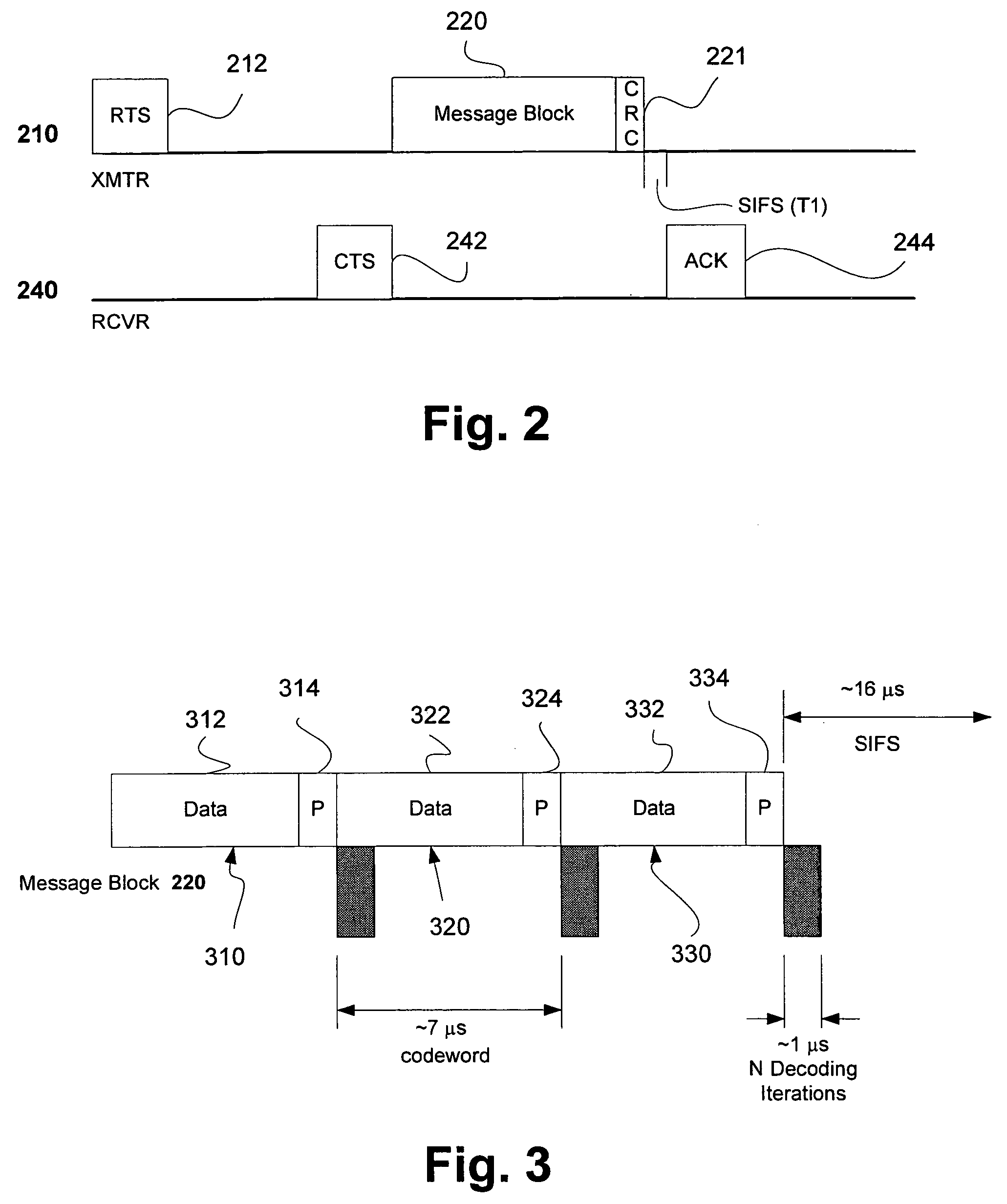

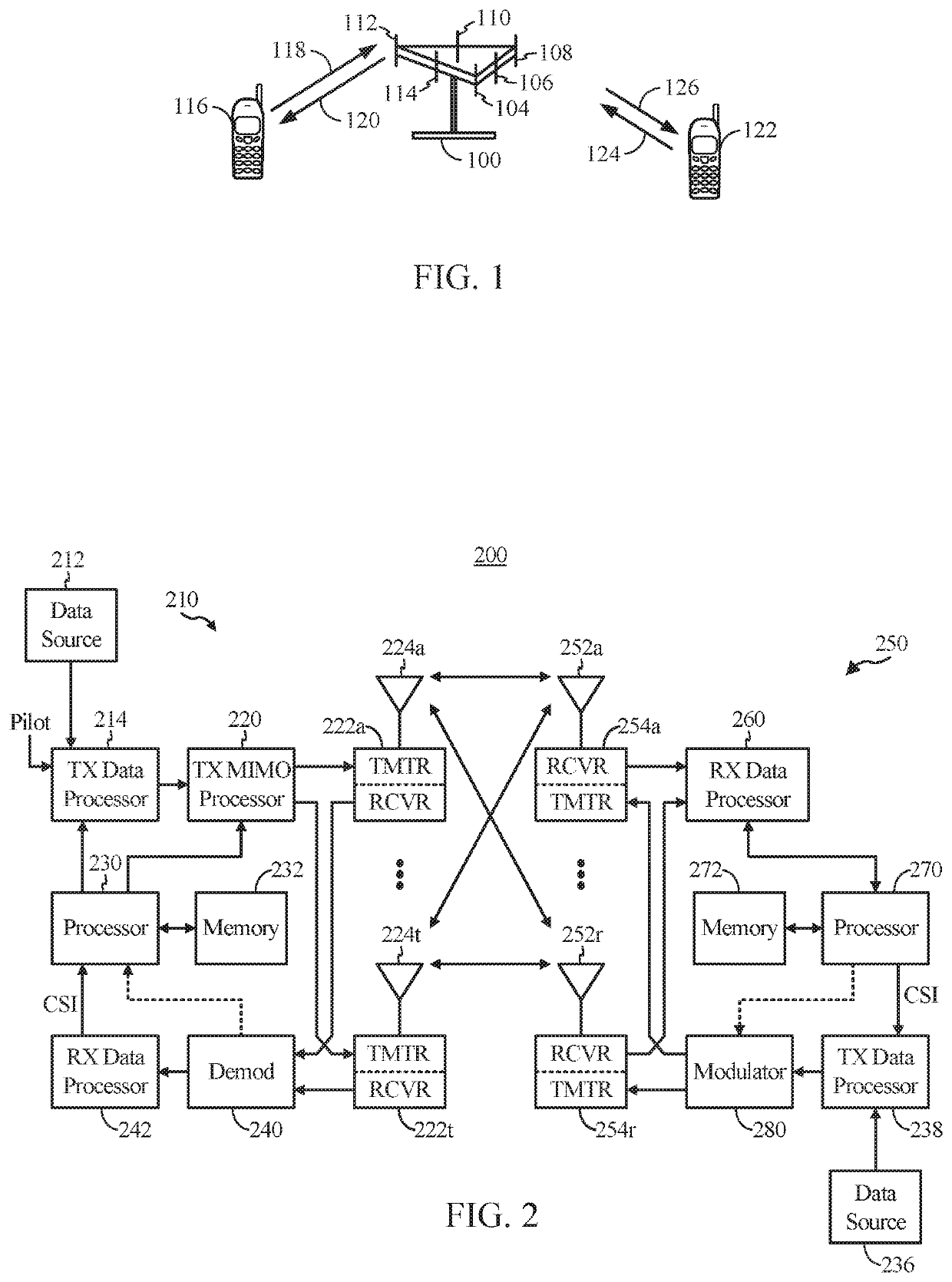

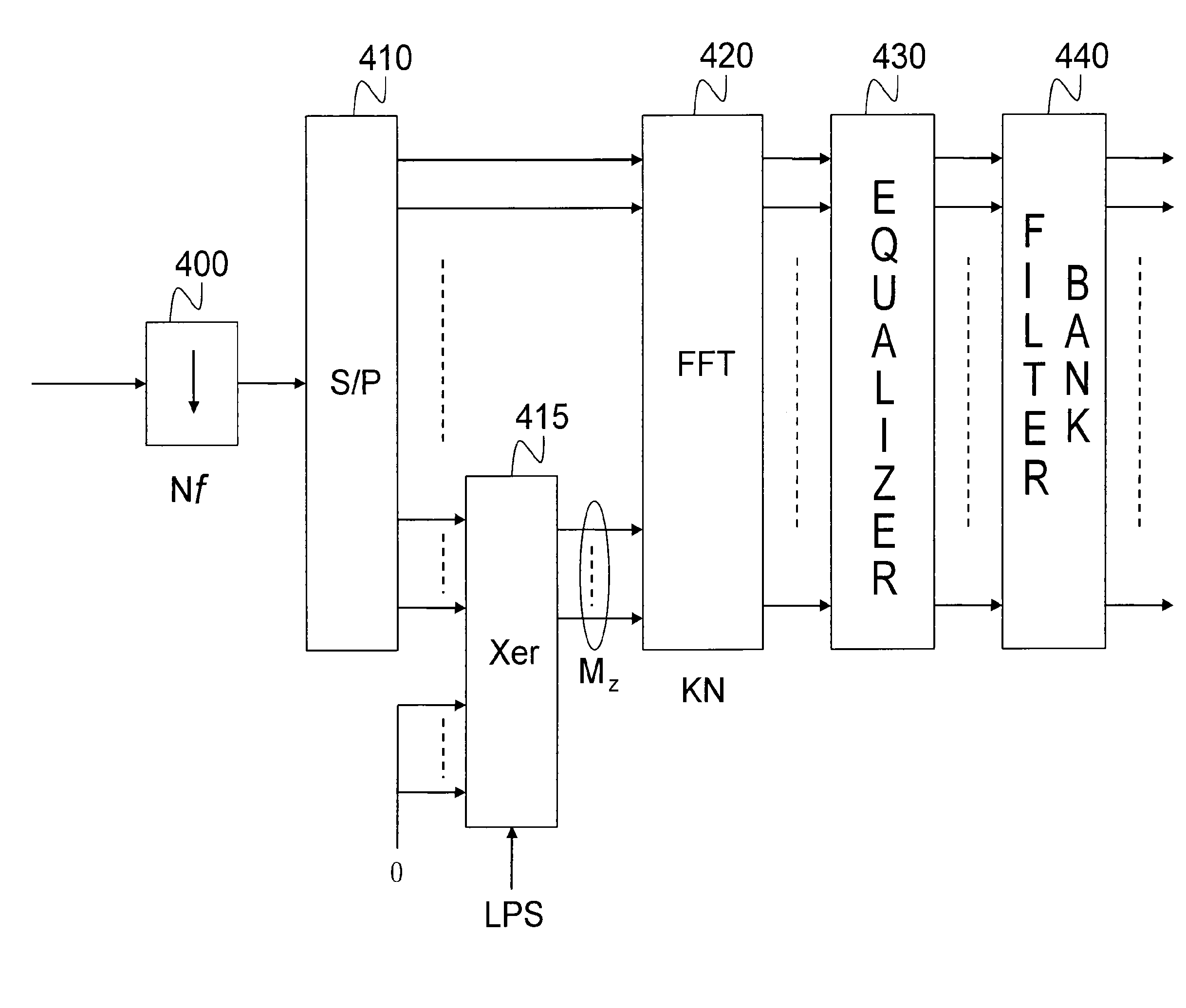

Method and apparatus for encoding blocks of data with a blocks oriented code and for decoding such blocks with a controllable latency decoding, in particular for a wireless communication system of the WLAN or wpan type

ActiveUS20070139229A1Lower latencyImprove communication performanceCode conversionError detection onlyComputer hardwareCommunications system

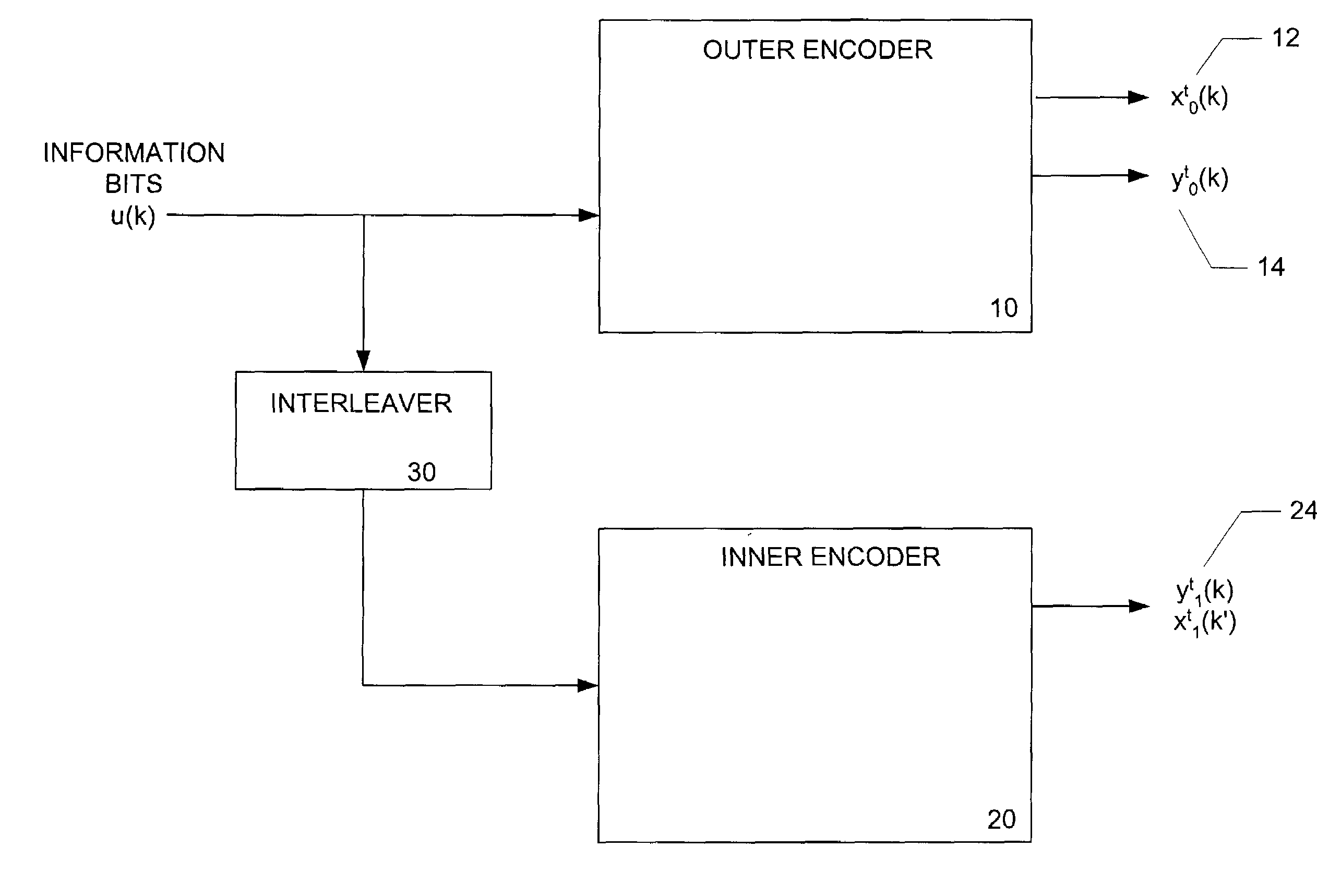

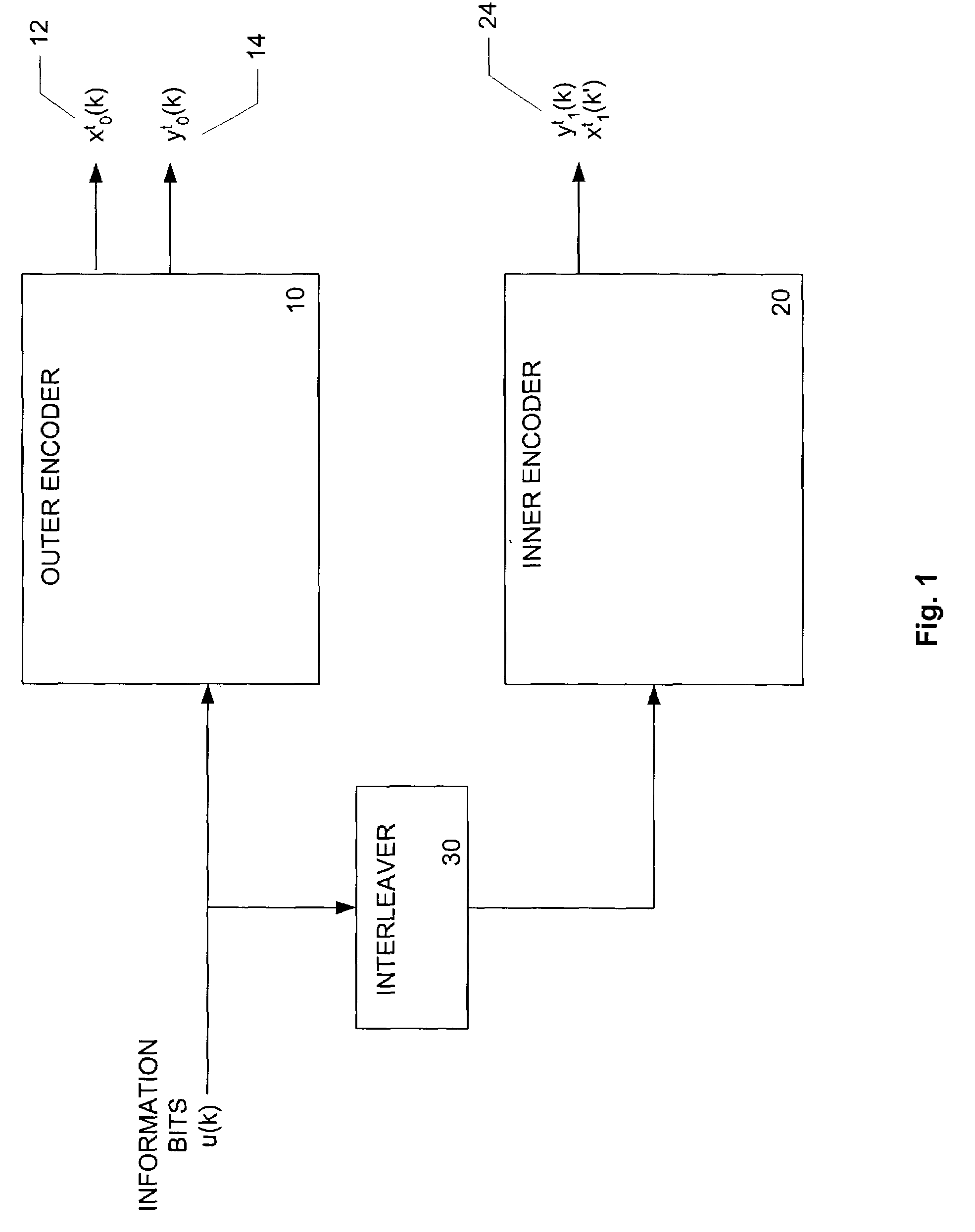

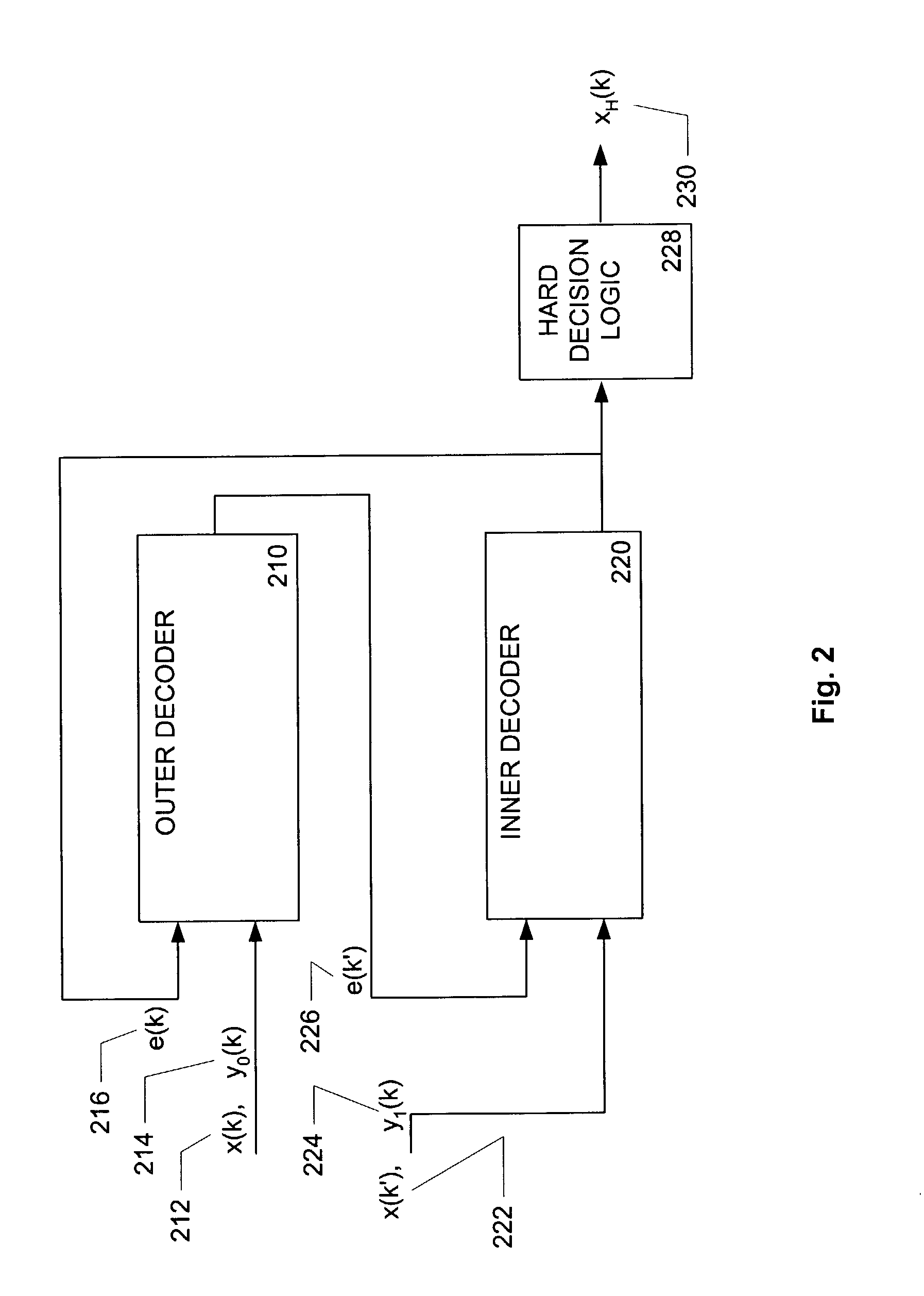

To control a decoding latency, larger blocks are nonequally segmented into smaller ones. The decoding process starts directly after reception of the first small block. The latency is defined by the latency of the last small block decoding. Changing the number of iterations during the turbo-code decoding also permits control of the decoding latency.

Owner:STMICROELECTRONICS INT NV

Memory configuration scheme enabling parallel decoding of turbo codes

InactiveUS6996767B2Accurately indexedData representation error detection/correctionOther decoding techniquesCoding blockParallel computing

Owner:COMBASIS TECH

Frame structure for adaptive data communications over a plastic optical fibre

ActiveUS9094151B2Efficient communication frame structureTime-division optical multiplex systemsTime-division multiplexControl dataPlastic optical fiber

Owner:KNOWLEDGE DEV FOR POF SL

Enhanced polar code constructions by strategic placement of CRC bits

Certain aspects of the present disclosure relate to techniques and apparatus for improving decoding latency and performance of Polar codes. An exemplary method generally includes generating a codeword by encoding information bits, using a multi-dimensional interpretation of a polar code of length N, determining, based on one or more criteria, a plurality of locations within the codeword to insert error correction codes generating the error correction codes based on corresponding portions of the information bits, inserting the error correction codes at the determined plurality of locations, and transmitting the codeword. Other aspects, embodiments, and features are also claimed and described.

Owner:QUALCOMM INC

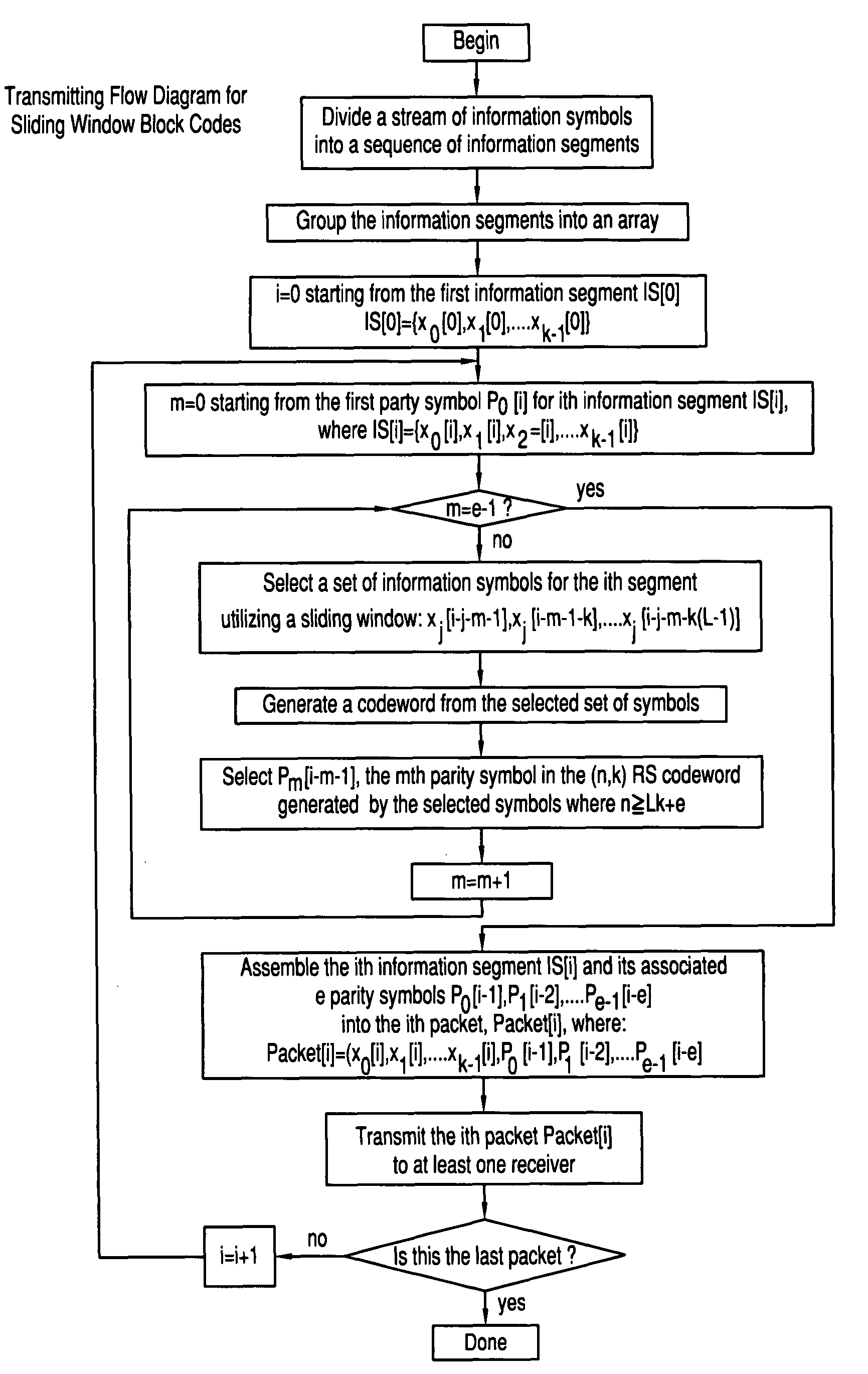

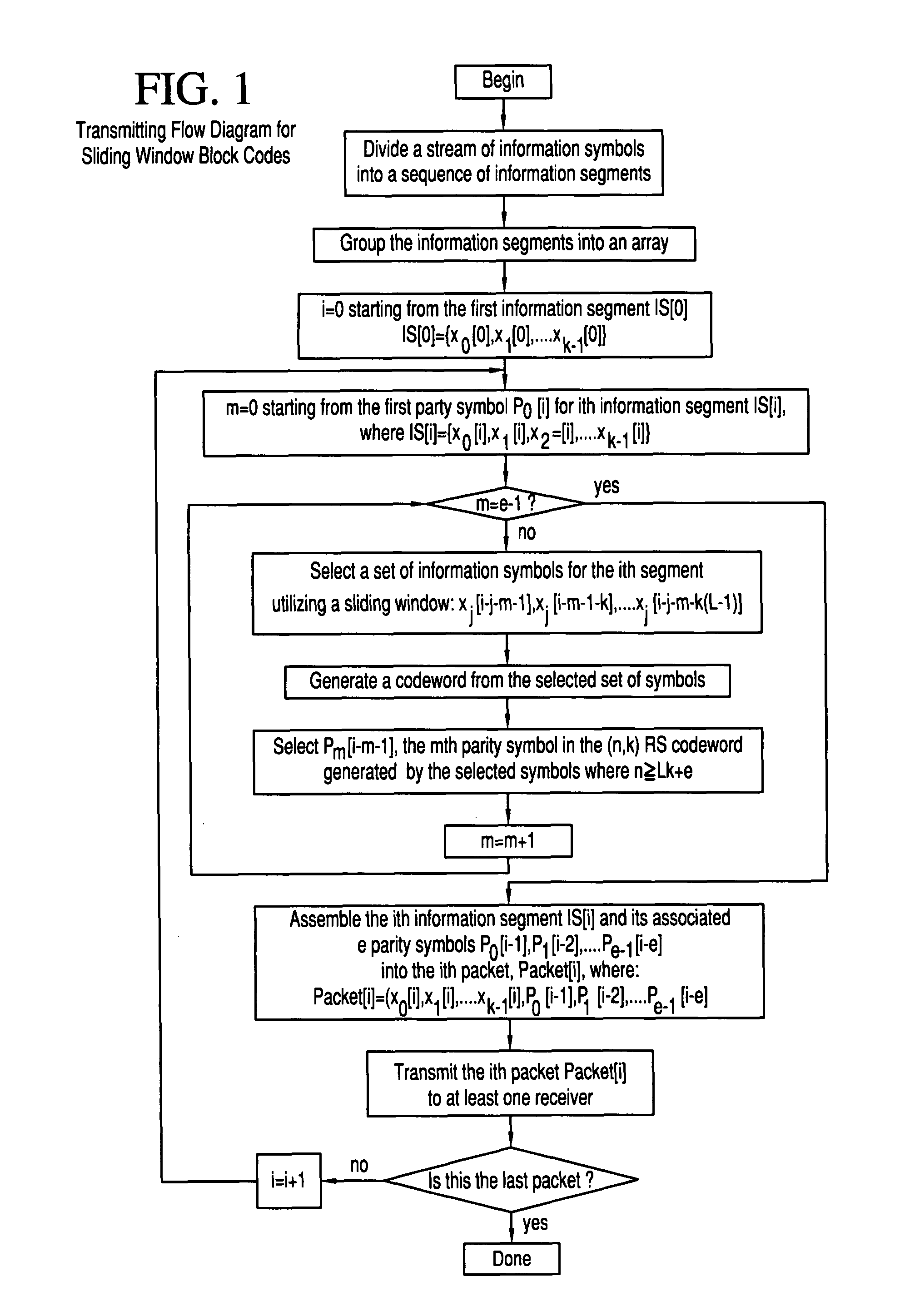

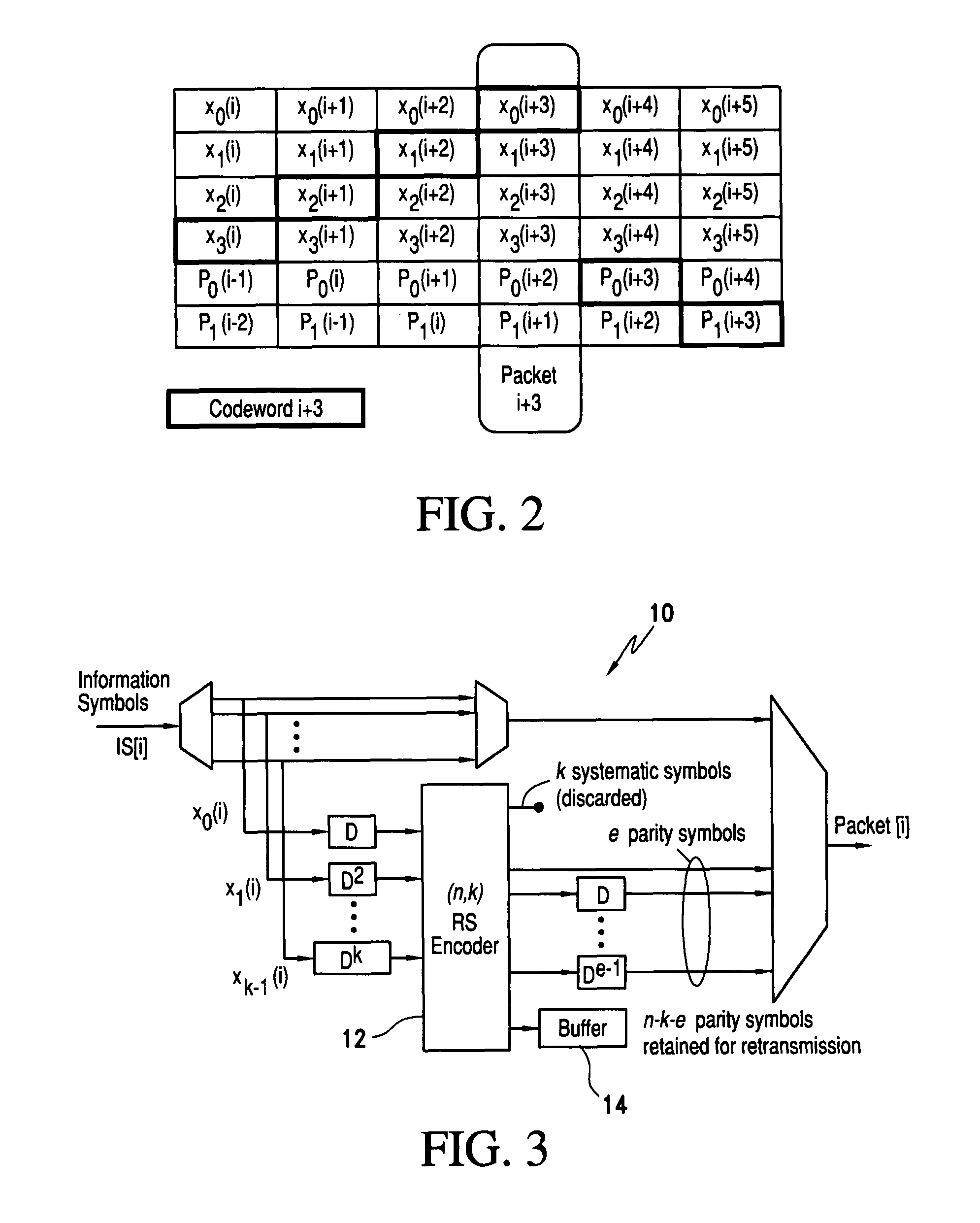

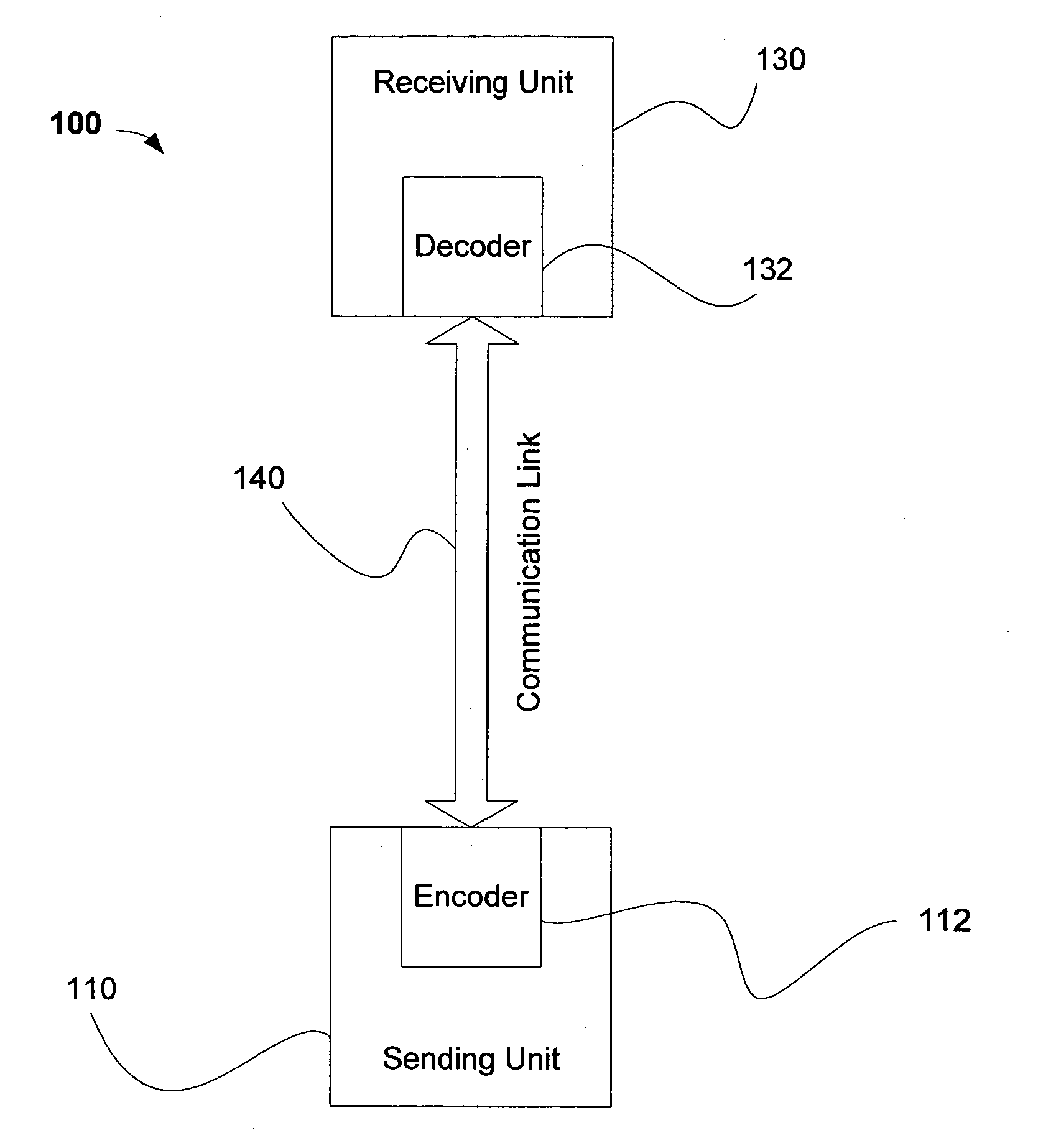

Sliding window block codes for cross-packet coding

ActiveUS7930617B1Reduce transmission overheadLess decoding latencyData representation error detection/correctionError preventionComputer hardwareSlide window

A block-code-based structure that allows cross-packet coding of data using a sliding window. In this structure, each transmitted packet contains both information symbols and parity symbols generated by the information in previous packets. This code structure allows a receiver to recover lost packets without additional transmissions. If enough packets have been lost so that the receiver cannot recover one or more of them, new parity symbols can be generated and transmitted as additional packets. The parity symbols in these additional packets may be used by multiple receivers. Thus, the sliding window block code reduces retransmission overhead, particularly for multicast applications. Furthermore, the sliding window structure does not produce an encoding delay between the arrival of data and its transmission and reduces the decoding delay between the loss of a packet and its recovery.

Owner:ROCKWELL COLLINS INC

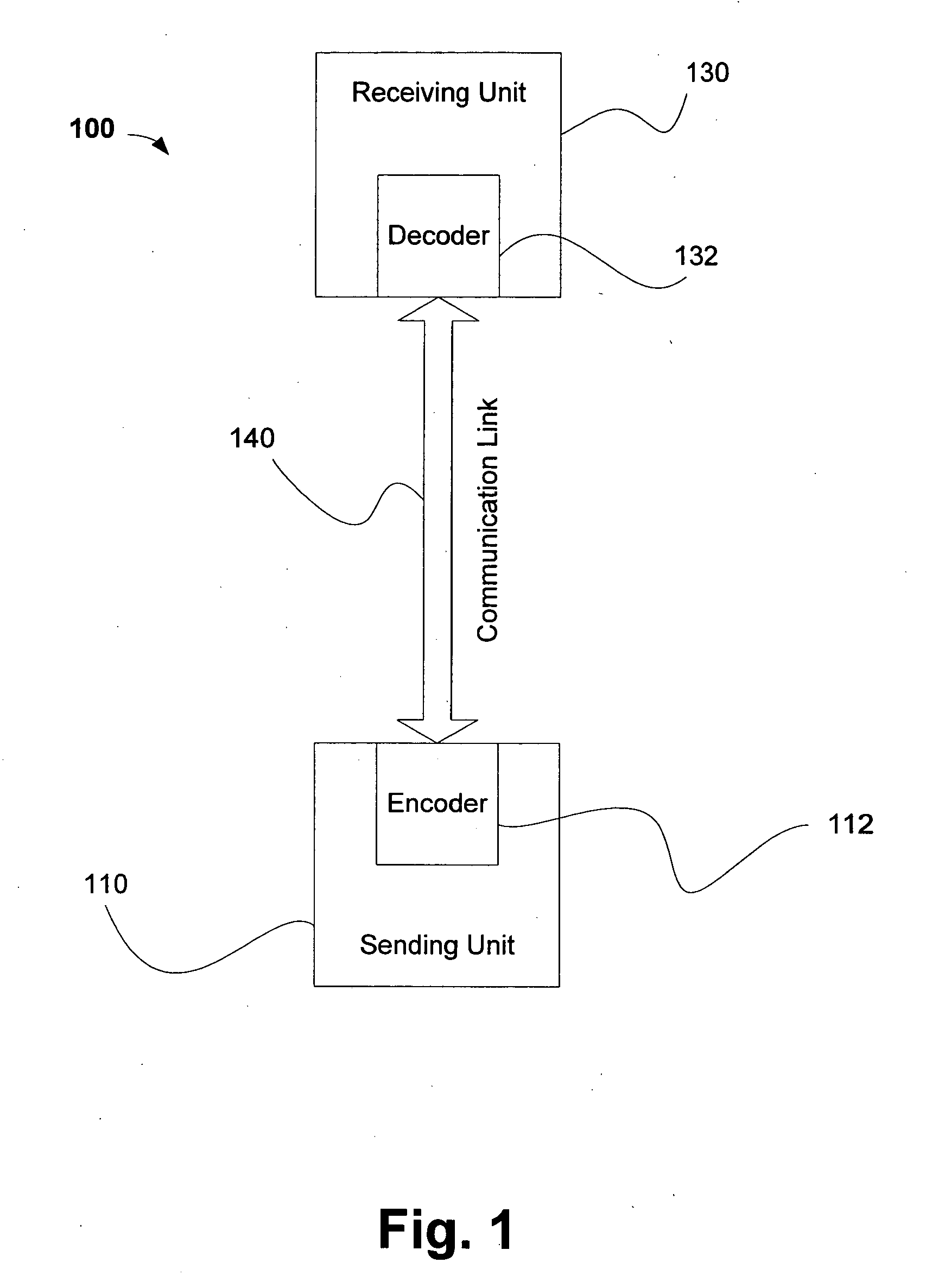

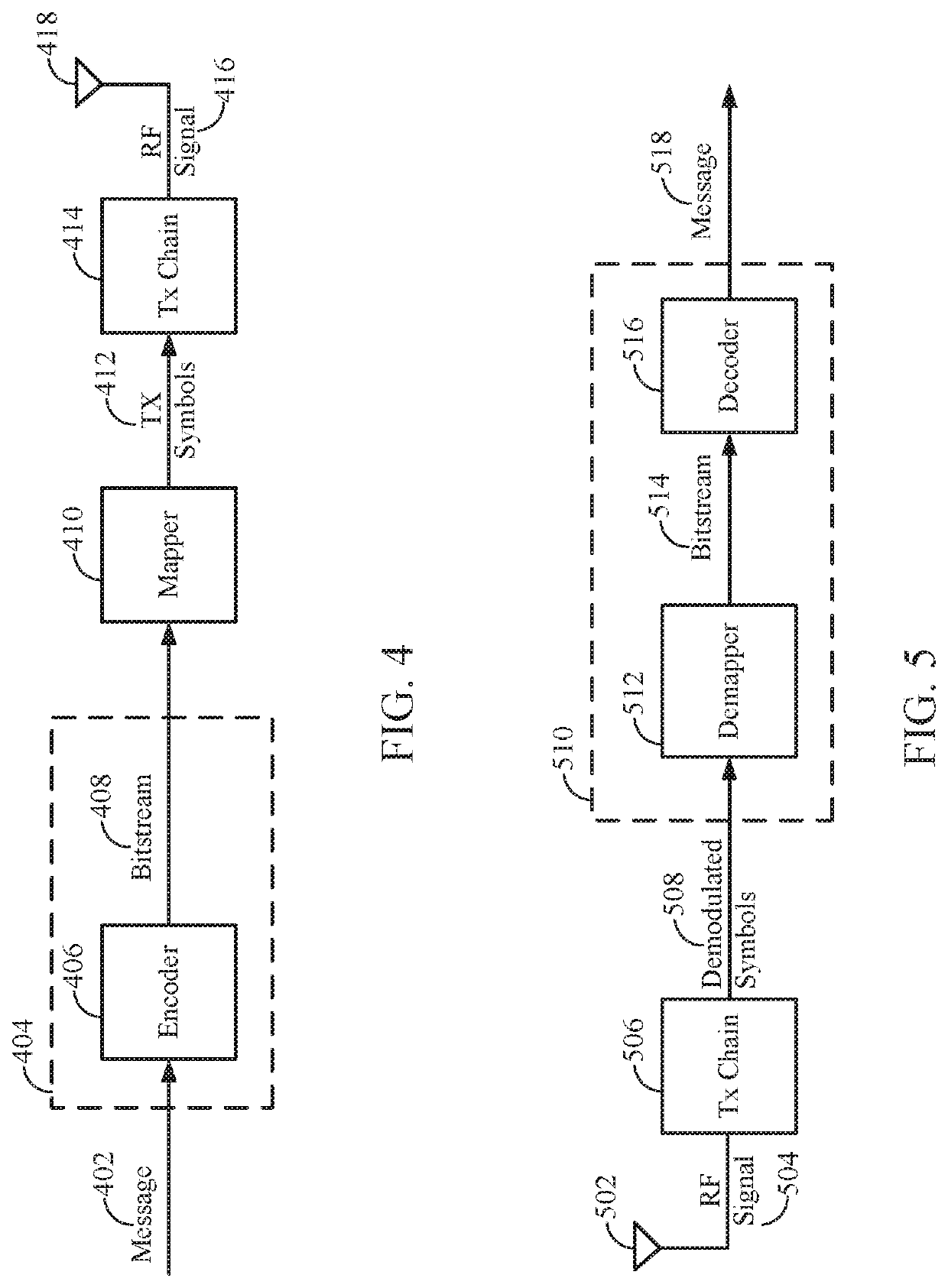

Forward error correction coding in communication networks

InactiveUS20050111345A1Error prevention/detection by using return channelError detection/correctionBlock codeForward error correction

Methods, apparatus and systems are disclosed for block encoding / decoding information wireless networks having narrow decoding latency restrictions. A method includes identifying a length of information to be sent in a block code and encoding the information to be sent in the block code into one or more codewords, where the number of codewords and the amount of information encoded within each codeword is adjusted based on the identified length and to achieve a similar codeword error probability for each codeword considering available decoding time for decoding a last codeword is less than available decoding time for decoding a first codeword. In certain implementations low density parity check (LDPC) encoding may be used in combination with OFDM to provide reliable communications in a high throughput WLAN.

Owner:INTEL CORP

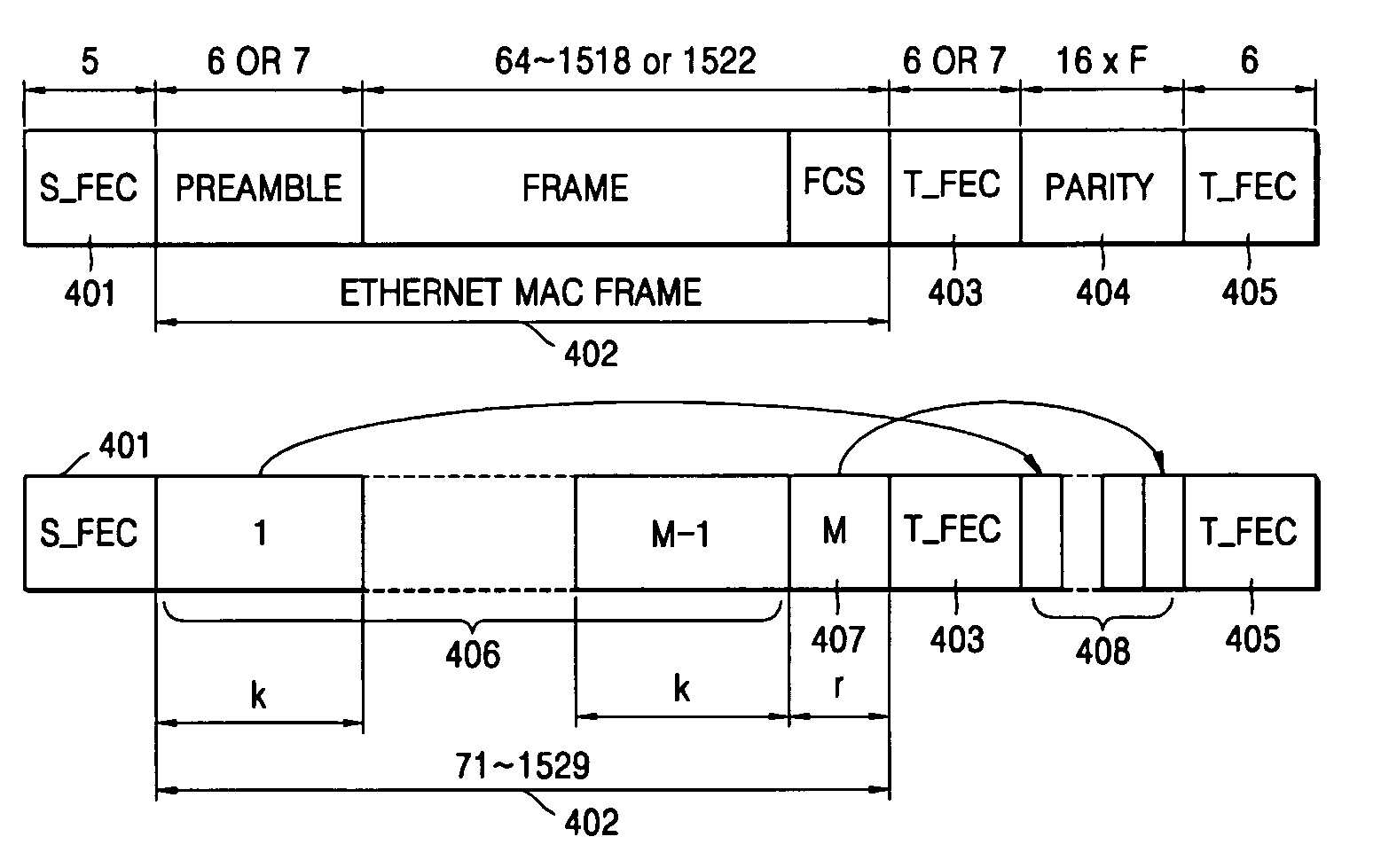

Apparatus for FEC supporting transmission of variable-length frames in TDMA system and method of using the same

InactiveUS20050149821A1Reduce processCorrection errorError preventionError correction/detection using block single space codingDelayed timeVariable length

An apparatus for transmitting a FEC frame is provided. The apparatus includes: a selector determining whether to perform FEC encoding on data to be transmitted; a Reed-Solomon encoding assembler receiving the data on which FEC encoding is to be performed as determined by the selector, and dividing the data into k-byte message blocks (k is a positive integer) for output; a Reed-Solomon encoder receiving the message blocks and performing Reed-Solomon encoding on the message blocks; and an output controller receiving an input parity generated by the Reed-Solomon encoding, and outputting the message block and the parity sequentially or outputting the data on which FEC encoding is not to be performed as determined by the selector. In order to correct an error caused by a transmission medium using FEC in a Reed-Solomon code type, FEC encoding / decoding of a frame is performed. A total transmission delay time is not influenced when FEC is bypassed, a delay caused by a shortened codeword is minimized, and a FEC encoding / decoding delays for frames having different lengths are equalized.

Owner:ELECTRONICS & TELECOMM RES INST

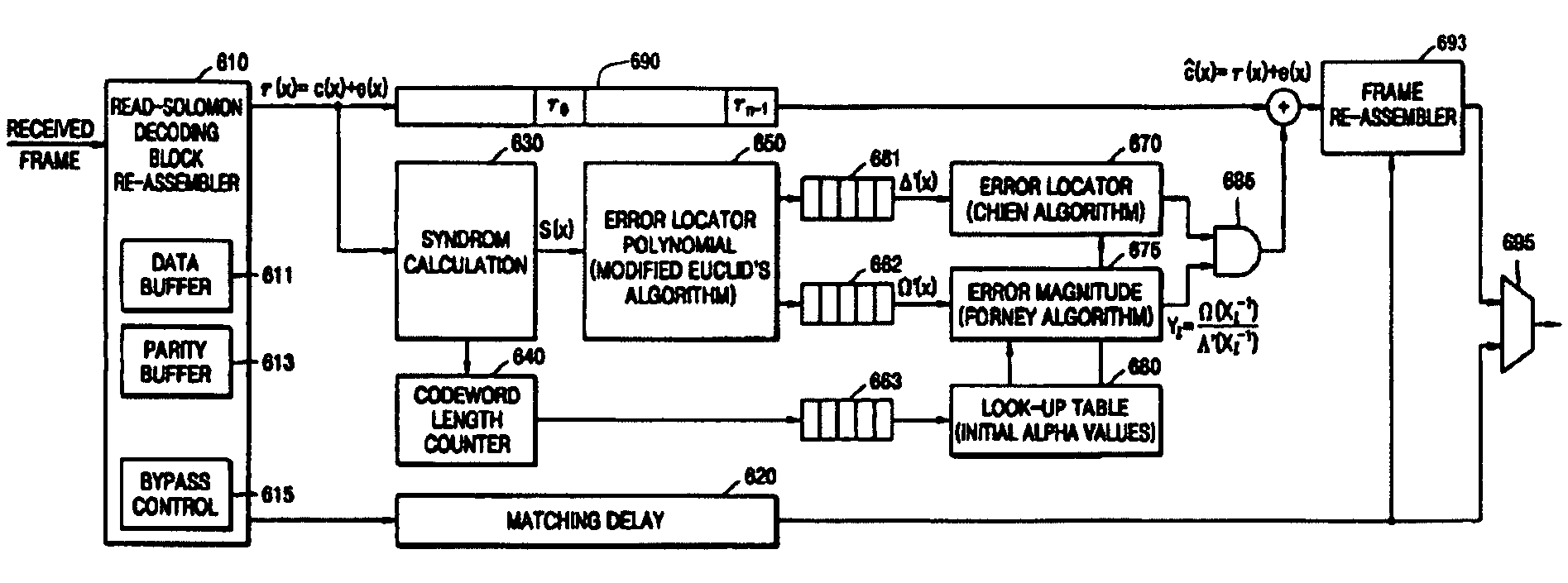

Algebraic decoder and method for correcting an arbitrary mixture of burst and random errors

InactiveUS7131052B2Combine accuratelyError detection/correctionCode conversionAlgebraic decodingByte

An error correction algebraic decoder and an associated method correct a combination of a B-byte burst of errors and t-byte random errors in a failed sector, by iteratively adding and removing an erasure (N−B) times until the entire failed sector has been scanned, provided the following inequality is satisfied: (B+2t)≦(R−1), where N denotes the number of bytes, B denotes the length of the burst of errors, t denotes the total number of random errors, and R denotes the number of check bytes in the failed sector. This results in a corrected sector at a decoding latency that is a generally linear function of the number of the check bytes R, as follows: Decoding Latency=5R(N−B).

Owner:LINKEDIN

Apparatus for FEC supporting transmission of variable-length frames in TDMA system and method of using the same

InactiveUS7581155B2Error preventionError correction/detection using block single space codingDelayed timeVariable length

An apparatus for transmitting a FEC frame is provided. In order to correct an error caused by a transmission medium using FEC in a Reed-Solomon code type, FEC encoding / decoding of a frame is performed. A total transmission delay time is not influenced when FEC is bypassed, a delay caused by a shortened codeword is minimized, and a FEC encoding / decoding delays for frames having different lengths are equalized.

Owner:ELECTRONICS & TELECOMM RES INST

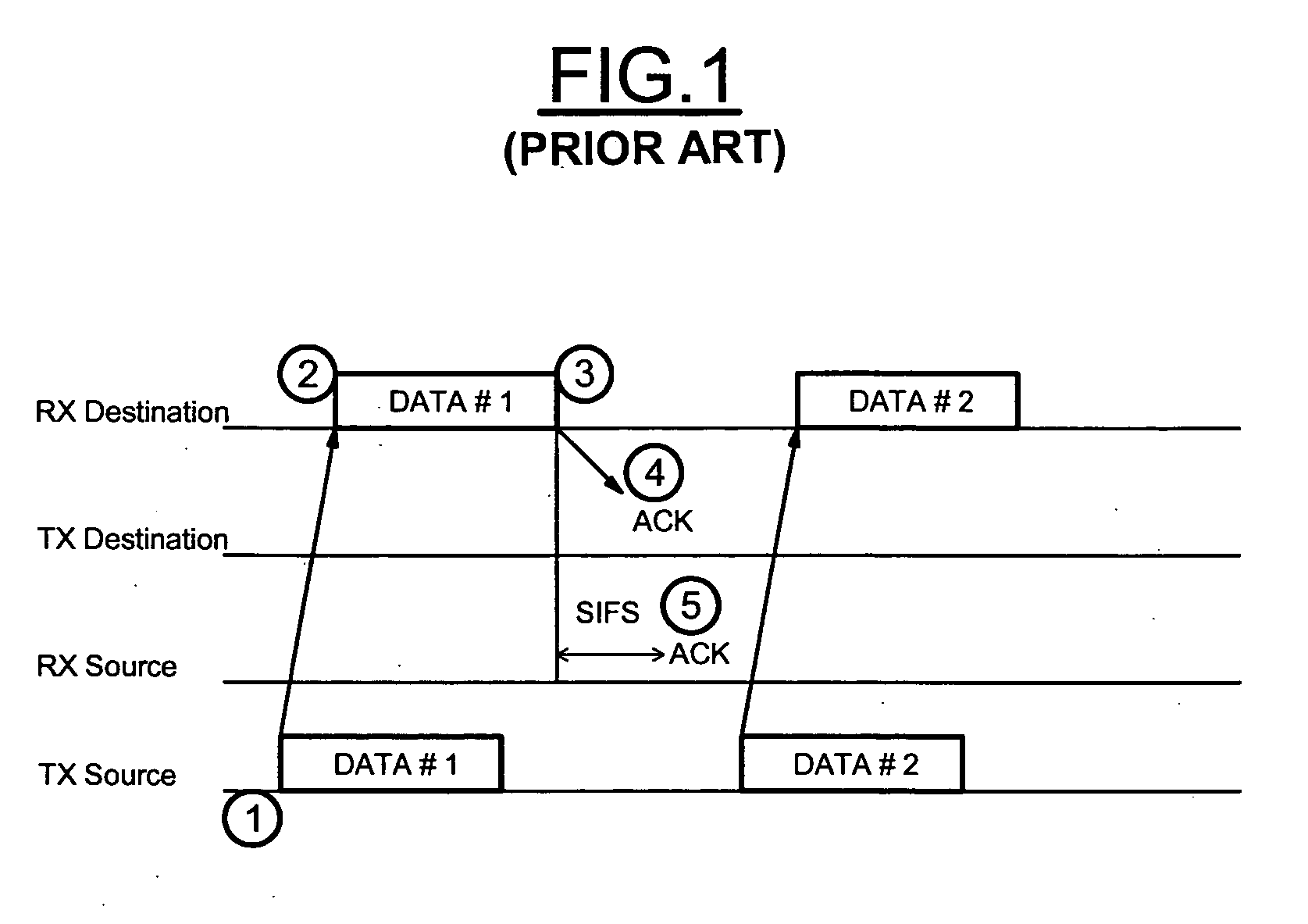

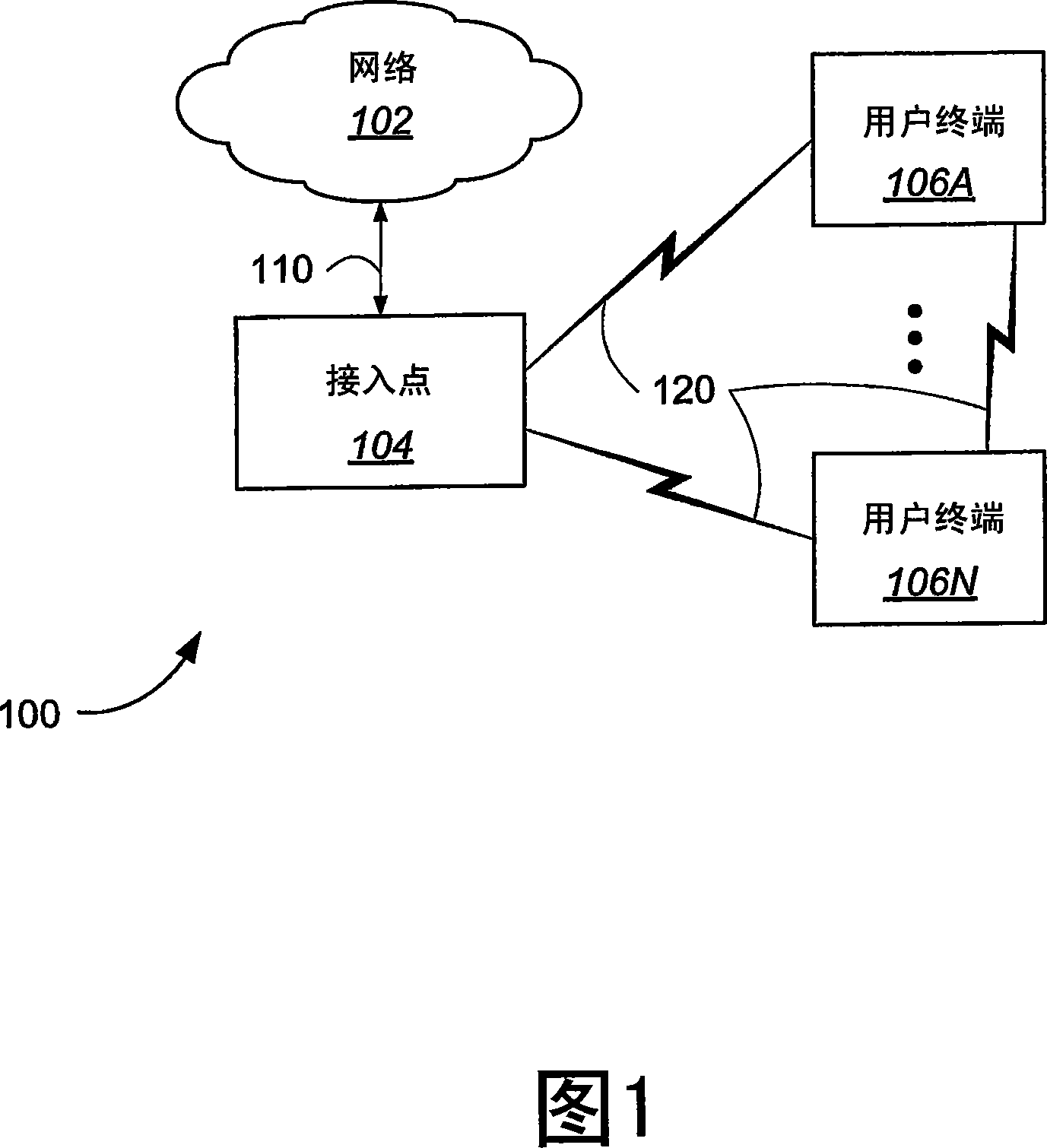

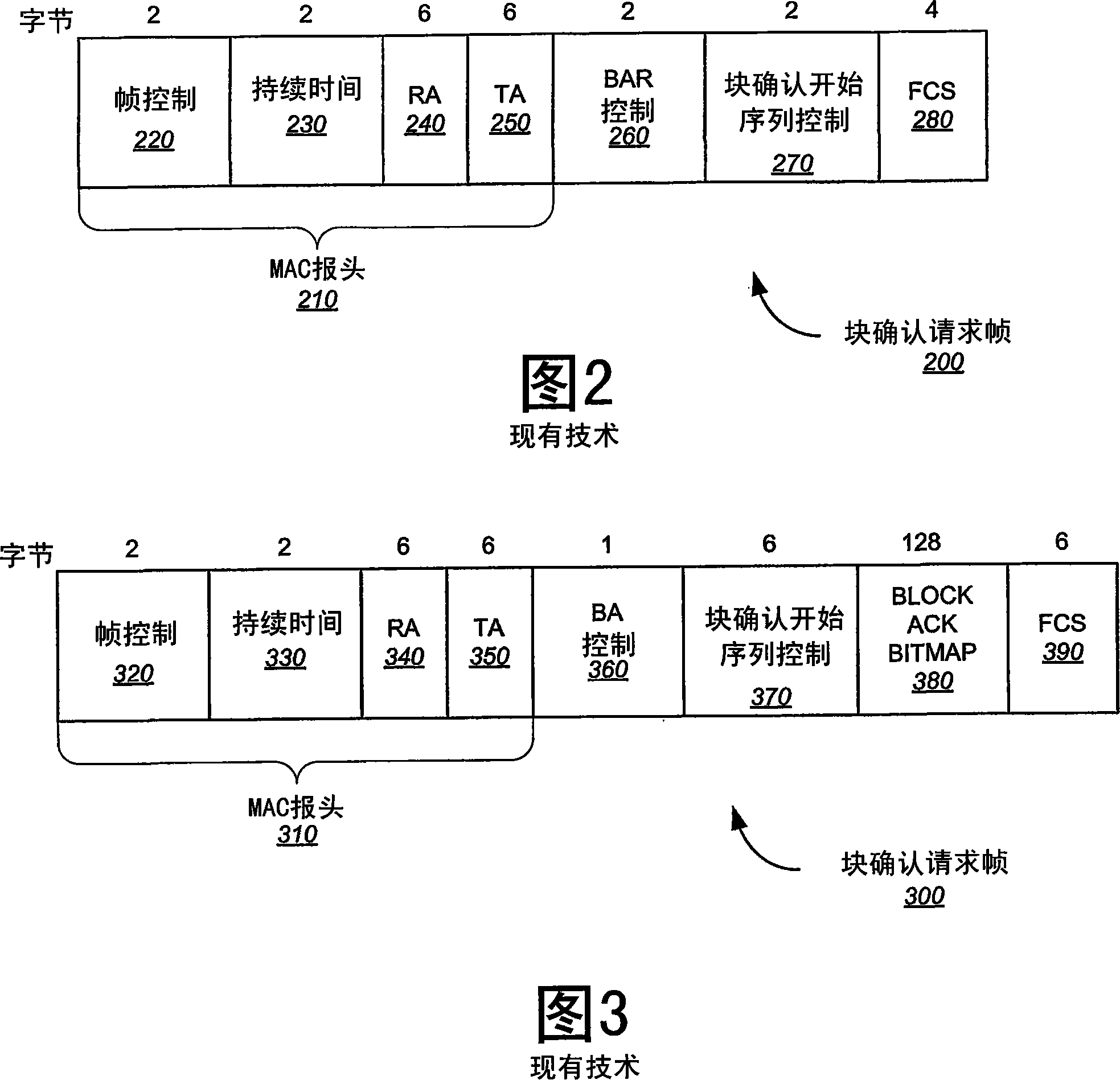

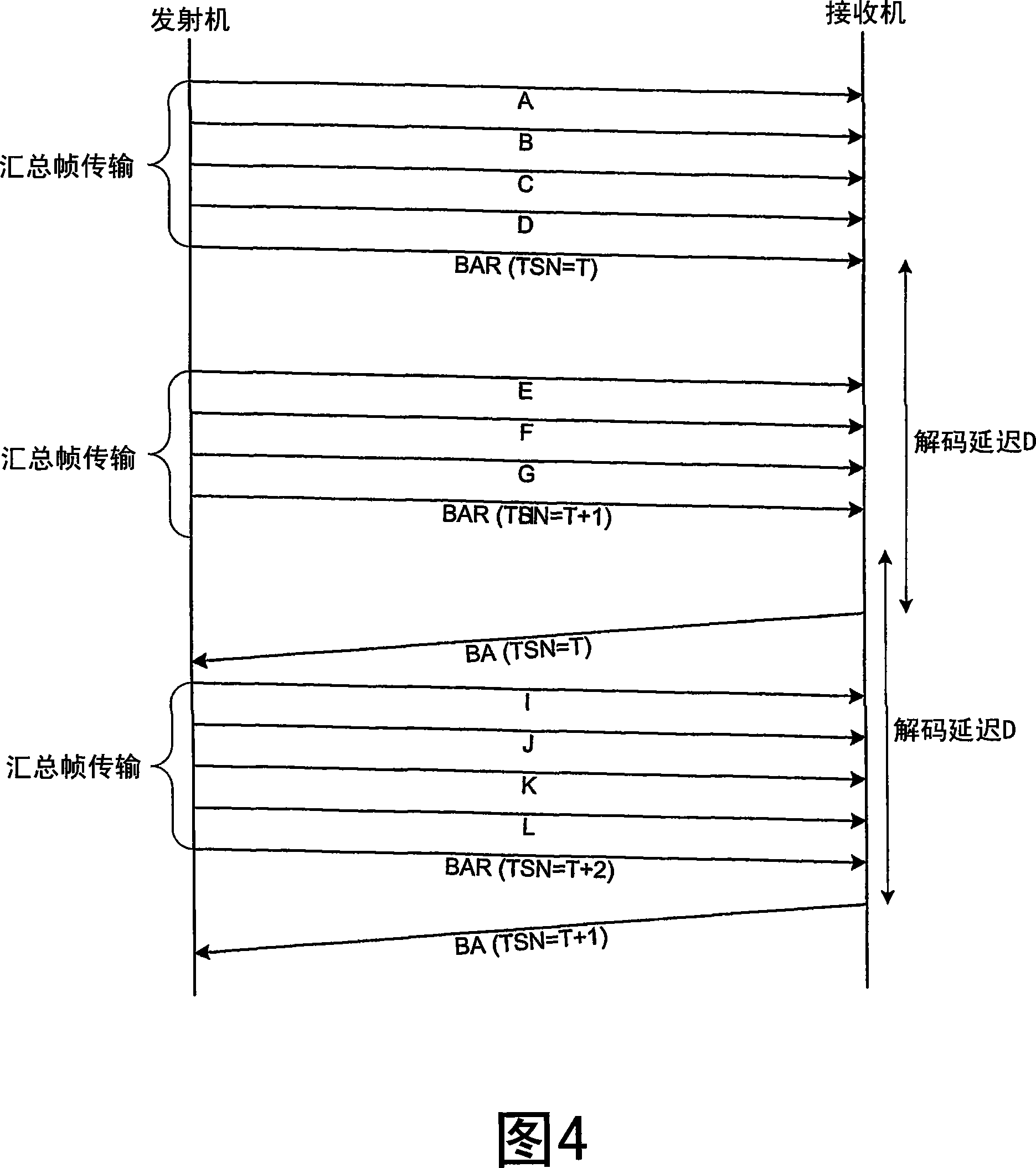

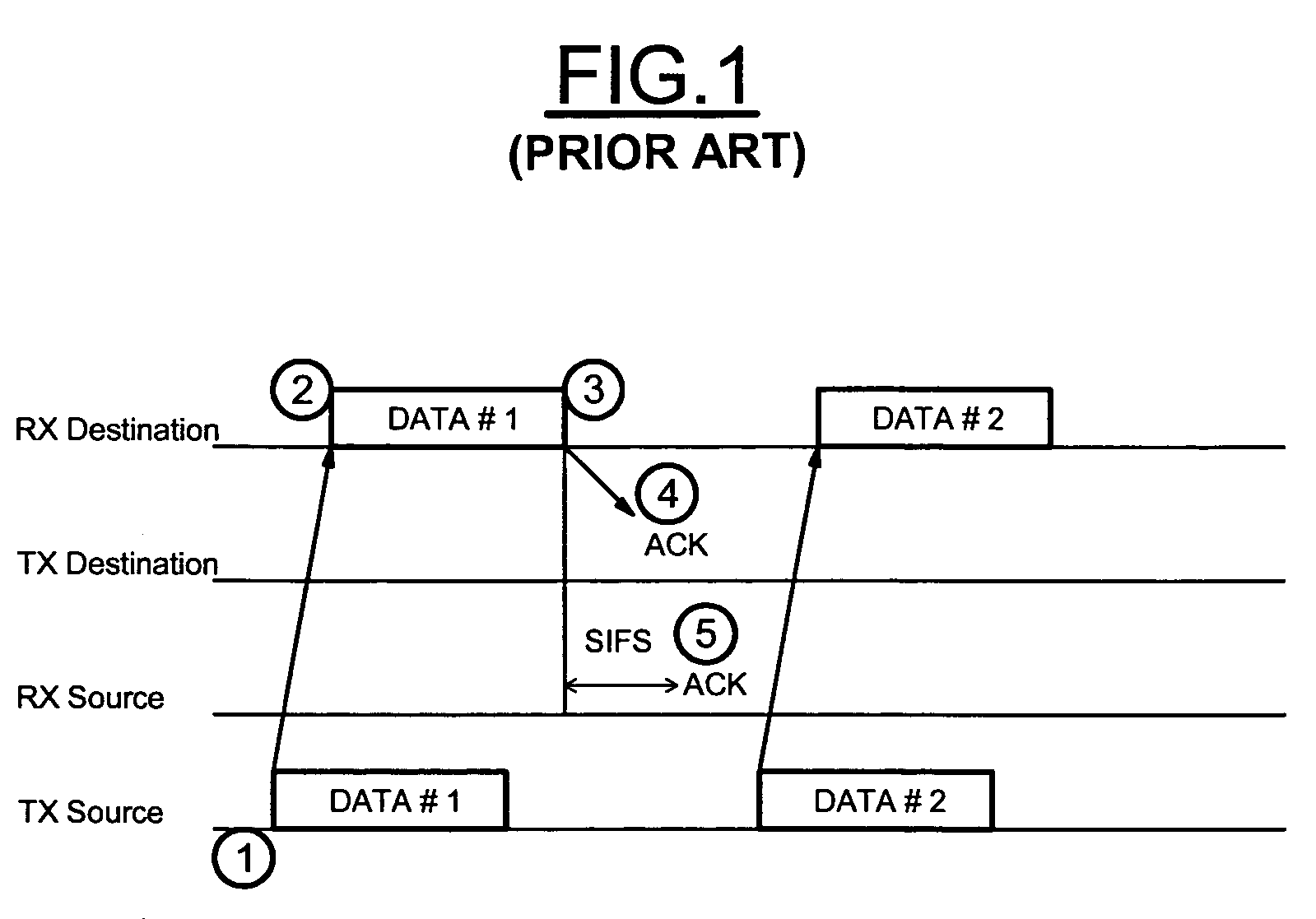

Enhanced block acknowledgement

ActiveCN101073218AError prevention/detection by using return channelTransmission systemsComputer scienceMaximum size

Embodiments disclosed herein address the need in the art for enhanced block acknowledgement. In one embodiment, a receiver indicates a decoding delay for a maximum size aggregate frame in Block Ack negotiation, which may be used by a transmitter to determine to which Block Ack Request a Block Acknowledgement is responsive. In another embodiment, a Transmission Sequence Number (TSN) may be included in a Block Ack Request. The receiver includes the TSN in the corresponding Block Ack response. This allows the transmitter to determine which frames are ''in transit.'' The TSN may be used to identify blocks. In another embodiment, a TSN may be associated with one or more transmitted frames. While, the TSN is not transmitted with the Block Ack Request, the transmitter may determine which TSN corresponds with a Block Ack response in accordance with acknowledgements contained therein. Combinations of these techniques may be deployed. Various other aspects are also presented.

Owner:QUALCOMM INC

Sound data encoding apparatus and sound data decoding apparatus

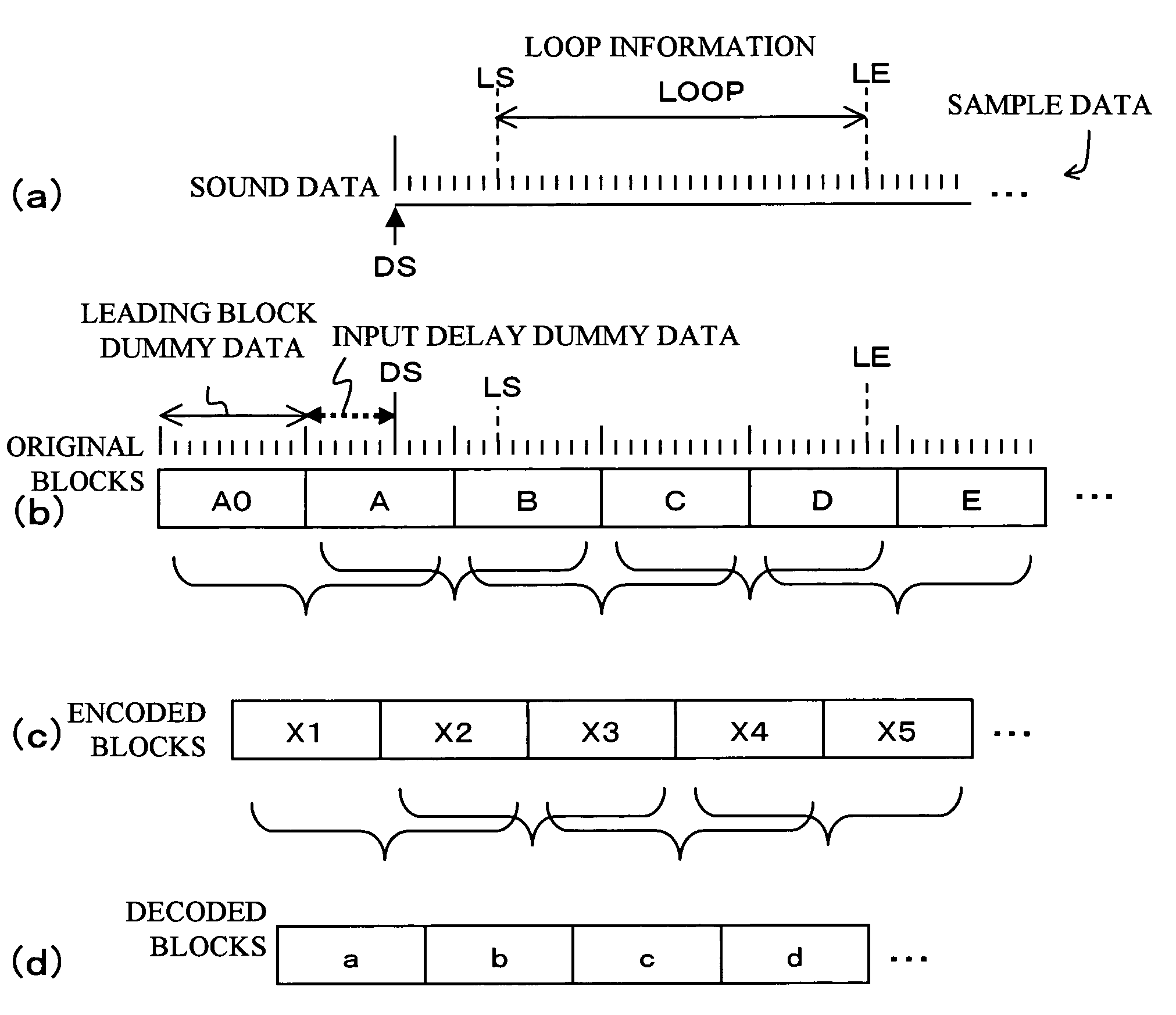

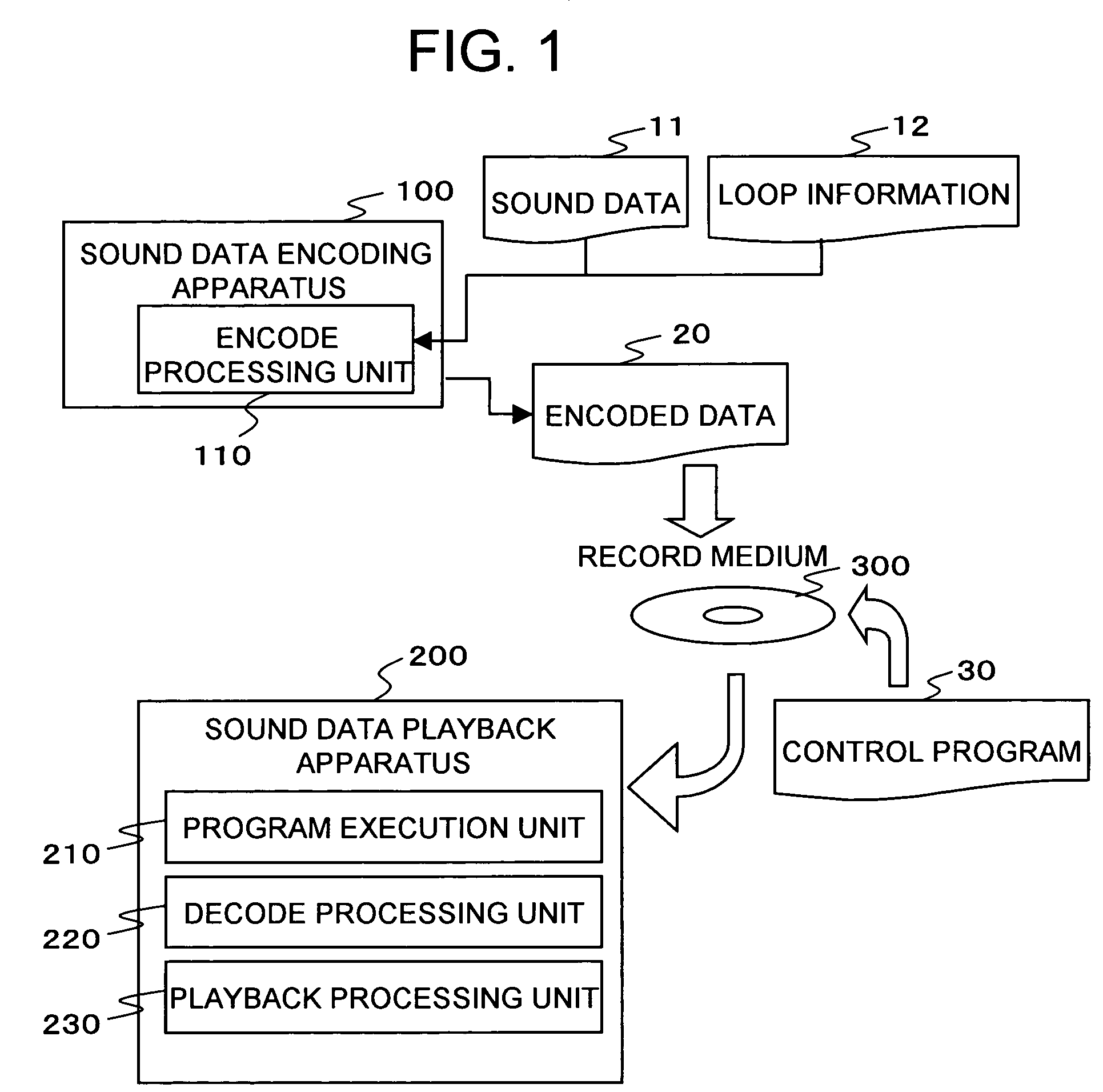

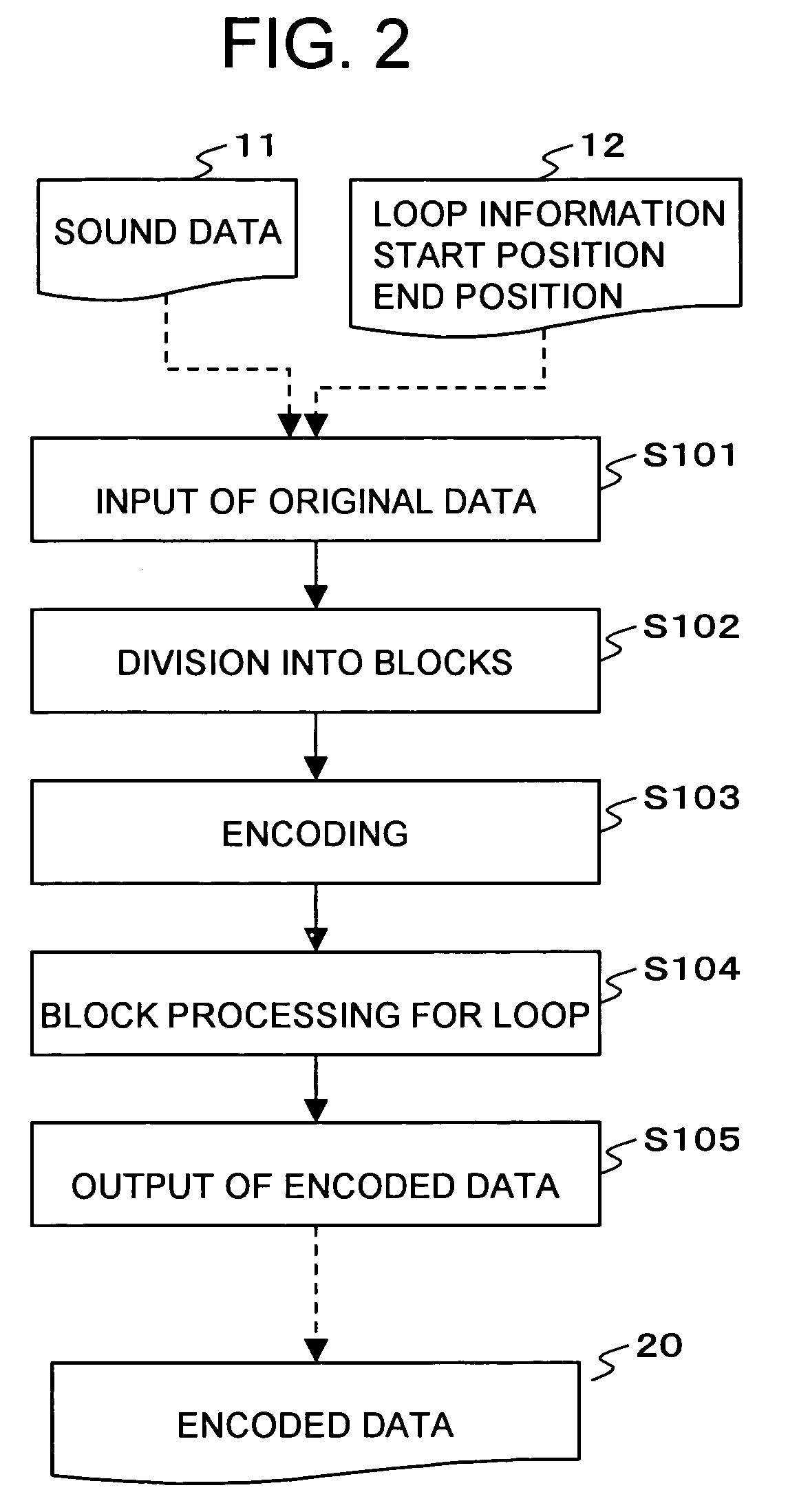

A processing load at the time of playing back sound data having a loop part is reduced.A sound data encoding apparatus comprises a block dividing means that divides the sound data into blocks according to predetermined rules, and an encoding means that encodes the blocks in groups of a plurality of consecutive blocks. The block dividing means divides the sound data such that, when encoded blocks encoded by the encoding means are decoded to output decoded blocks, then the loop end position in a block that includes the loop end position in the decoded blocks is nearer to an end of the block than a predetermined position. In detail, input delay dummy data are added ahead of the sound data before dividing the sound data. At the time of outputting the encoded data, loop information is outputted also. The loop information includes the number of samples of the added input delay dummy data, the number of samples corresponding to the encoding delay, the number of samples corresponding to the decoding delay, the start and end positions of the sound data, and the loop start and end positions.

Owner:SONY COMPUTER ENTERTAINMENT INC

Synchronized audio/video decoding for network devices

InactiveUS8238376B2Time-division multiplexSynchronisation signal speed/phase controlTimestampClock rate

A method of synchronizing decoders within a network to a server includes receiving a set of timestamps and local clock signals upon receiving the beacon interrupt signal, computing differential timestamp and local clock values based on values of timestamp and local clock signals, respectively, within the sets of timestamp and local clock signals, determining whether the differential local clock value has a predetermined relationship with the differential timestamp value, and transmitting a clock rate adjustment command signal to the decoder when differential local clock value does not have the predetermined relationship with the differential timestamp value. The clock rate adjustment command signal adjusts the local system time clock of the decoder such that a subsequent differential clock value will have the predetermined relationship with the differential timestamp value. When this method is performed for each decoder within the network, the decoders are substantially synchronized and the decoding delay can be kept below humanly perceptible levels.

Owner:SONY CORP +1

Forward error correction coding in communication networks

InactiveUS7685500B2Error prevention/detection by using return channelError detection/correctionBlock codeForward error correction

Owner:INTEL CORP

Generalized polar code construction

Certain aspects of the present disclosure relate to techniques and apparatus for improving decoding latency and performance of Polar codes. An exemplary method generally includes generating a codeword by encoding information bits using a first code of length K to obtain bits for transmission via K channels, wherein the first code comprises a polar code, further encoding the bits in each of the K channels using a second code of length M, and transmitting the codeword.

Owner:QUALCOMM INC

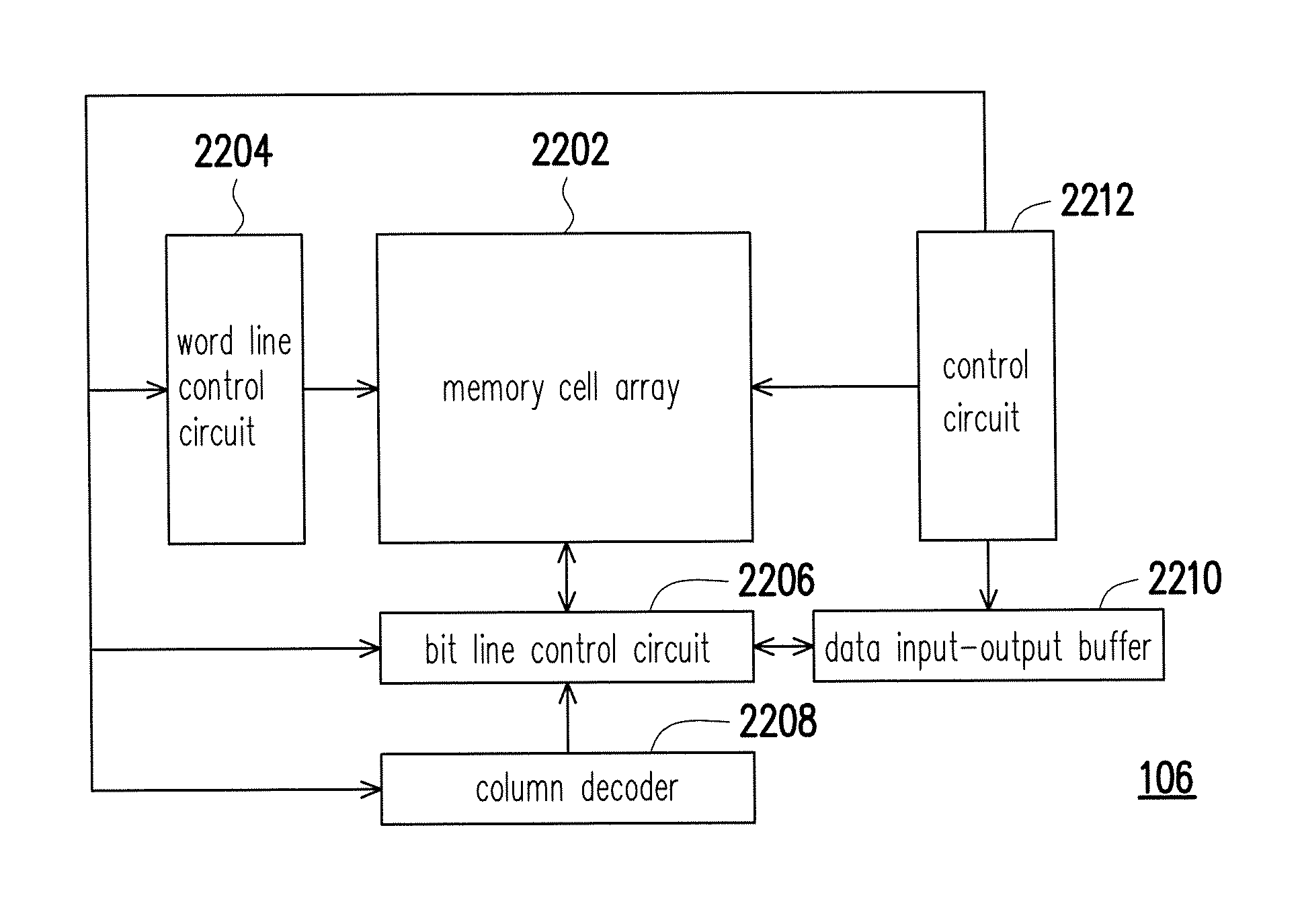

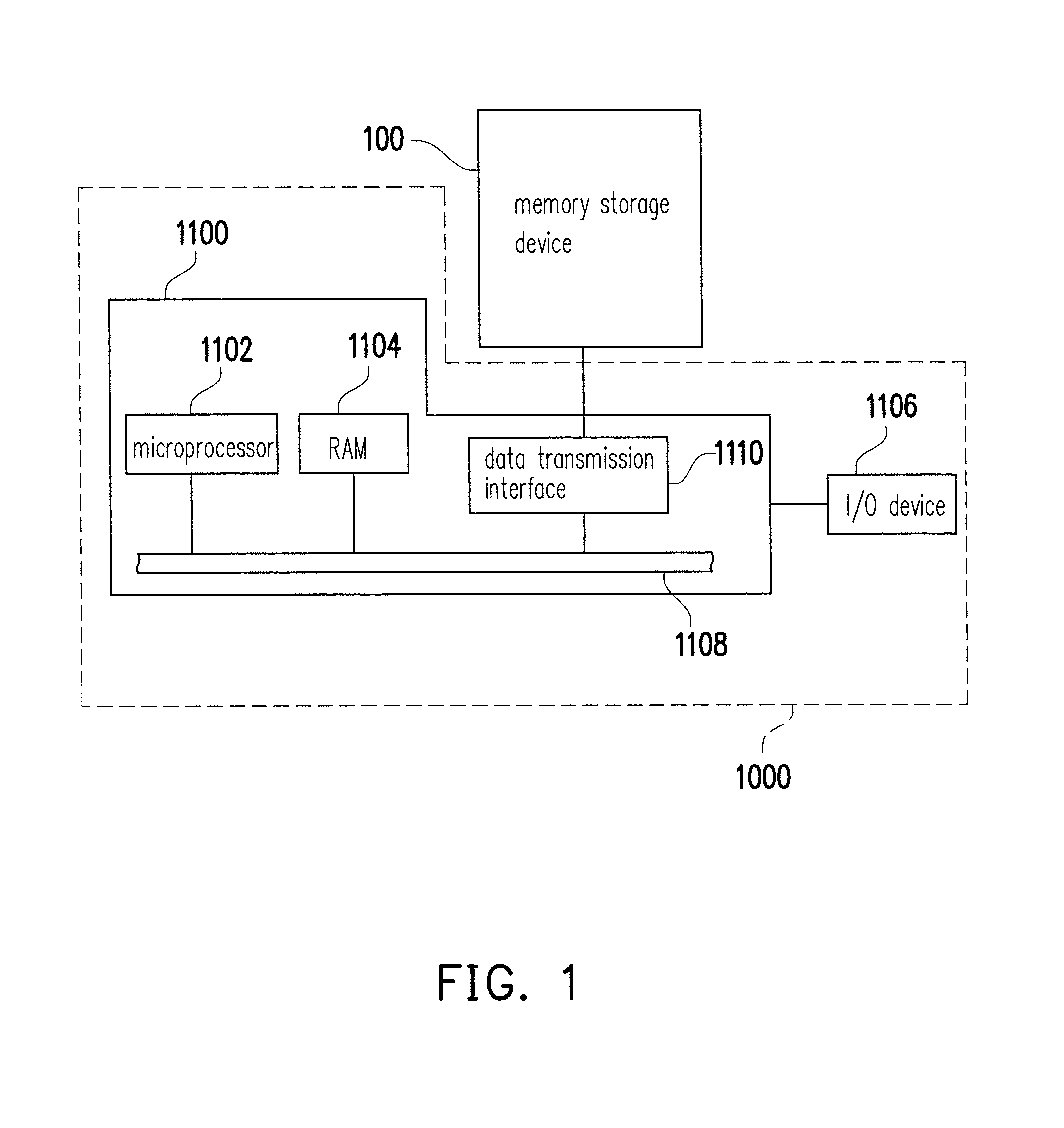

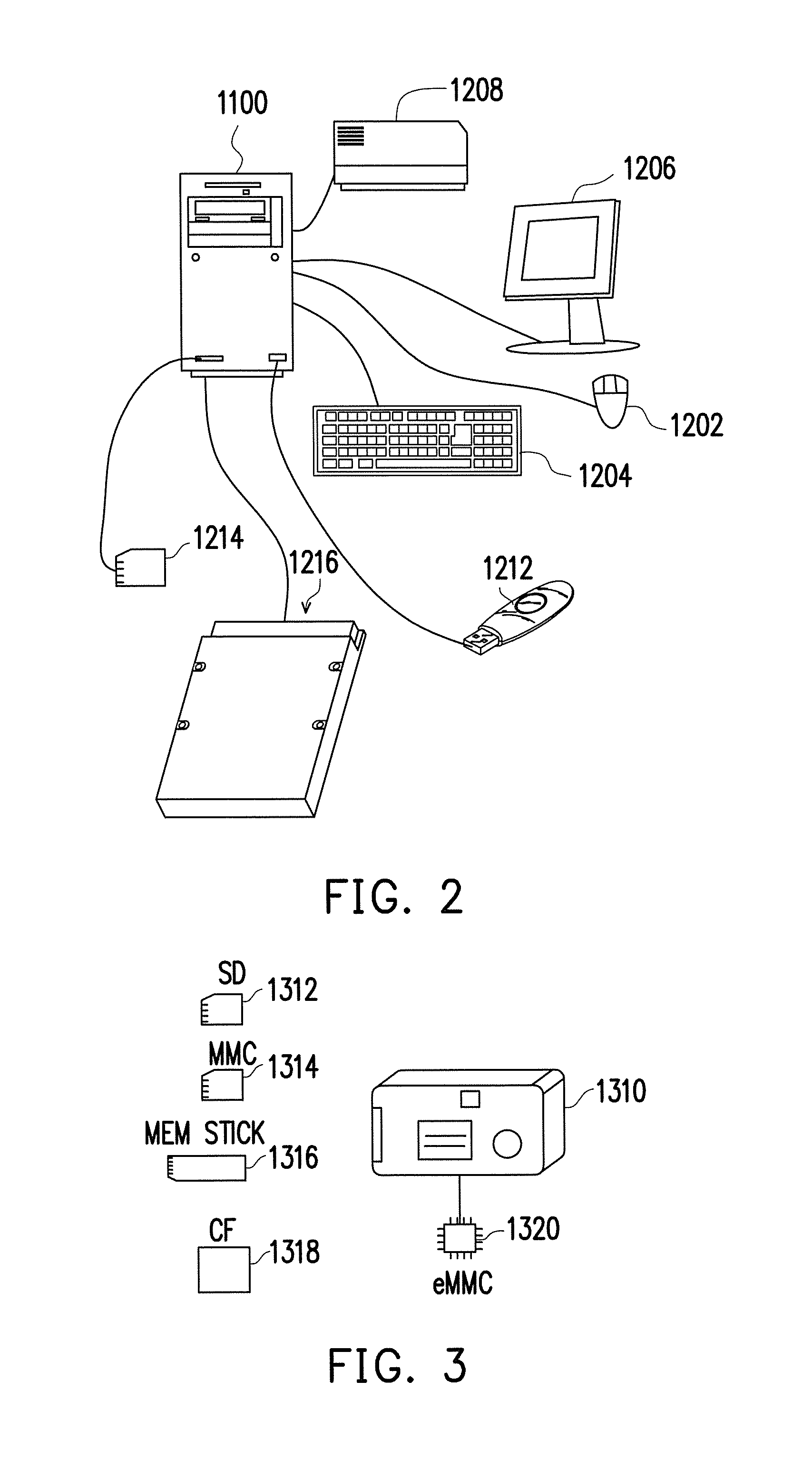

Decoding method, decoding circuit, memory storage device and controlling circuit unit

ActiveUS20150113353A1Lower latencyLow parityError correction/detection using multiple parity bitsCode conversionLow densityControl circuit

A decoding method, a memory storage device, a memory controlling circuit unit and a decoding circuit for low density parity code (LDPC) are provided. The decoding method includes: reading a data bit of each memory cell; performing a parity check procedure on the data bits to generate a plurality of checks; in an iterative decoding of LDPC, obtaining a reliability message of each data bit according to the checks and deciding an index of an error bit from the data bits according to the reliability messages; determining whether the index of the error bit and the checks comply with a parity criteria; and if the index of the error bit and the checks comply with the parity criteria, stopping the iterative decoding and outputting the index of the error bit. Accordingly, a decoding latency is decreased.

Owner:PHISON ELECTRONICS

Method and apparatus for encoding blocks of data with a blocks oriented code and for decoding such blocks with a controllable latency decoding, in particular for a wireless communication system of the WLAN or WPAN type

ActiveUS7836376B2Lower latencyImprove performanceCode conversionStatic storageComputer hardwareCommunications system

To control a decoding latency, larger blocks are nonequally segmented into smaller ones. The decoding process starts directly after reception of the first small block. The latency is defined by the latency of the last small block decoding. Changing the number of iterations during the turbo-code decoding also permits control of the decoding latency.

Owner:STMICROELECTRONICS INT NV

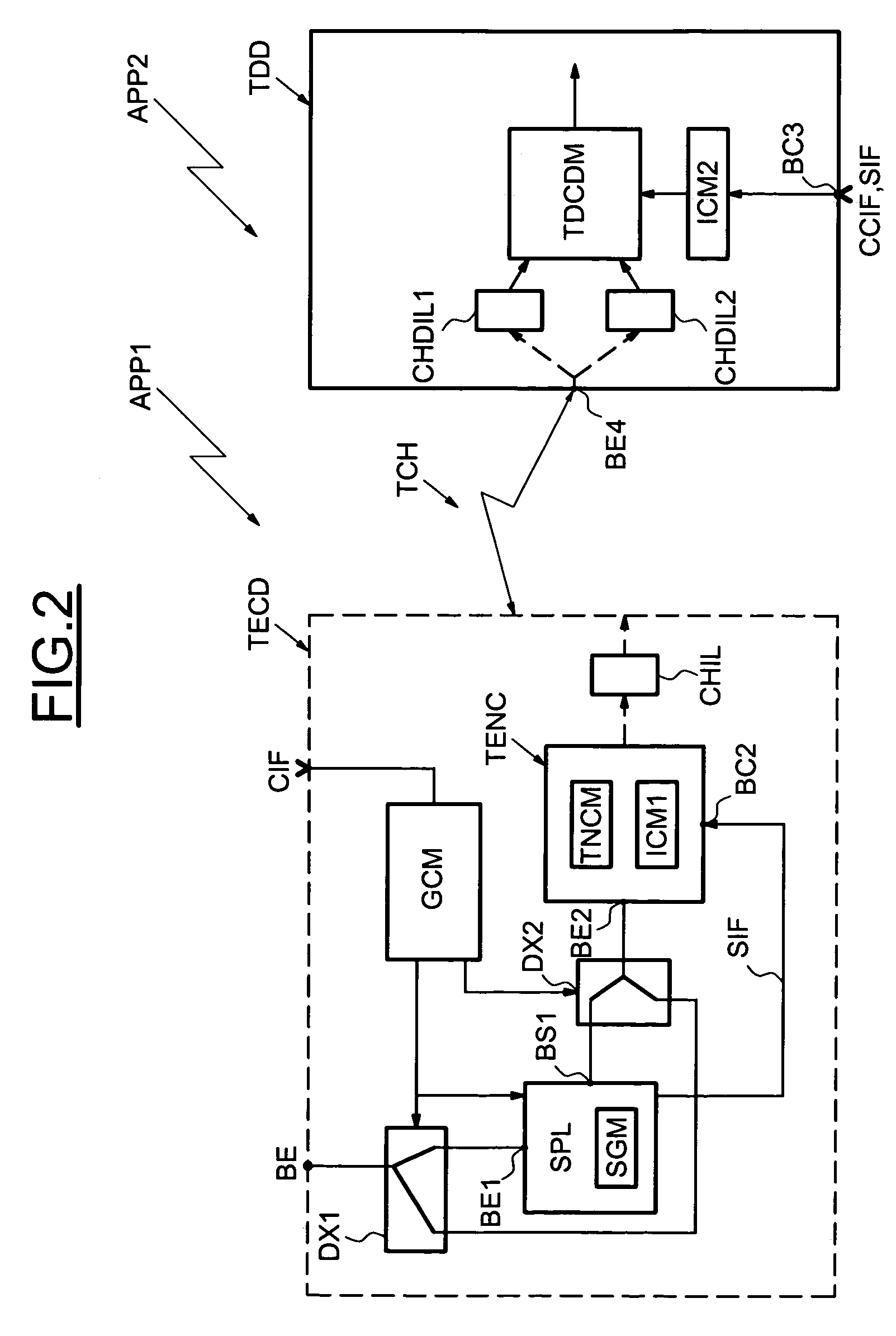

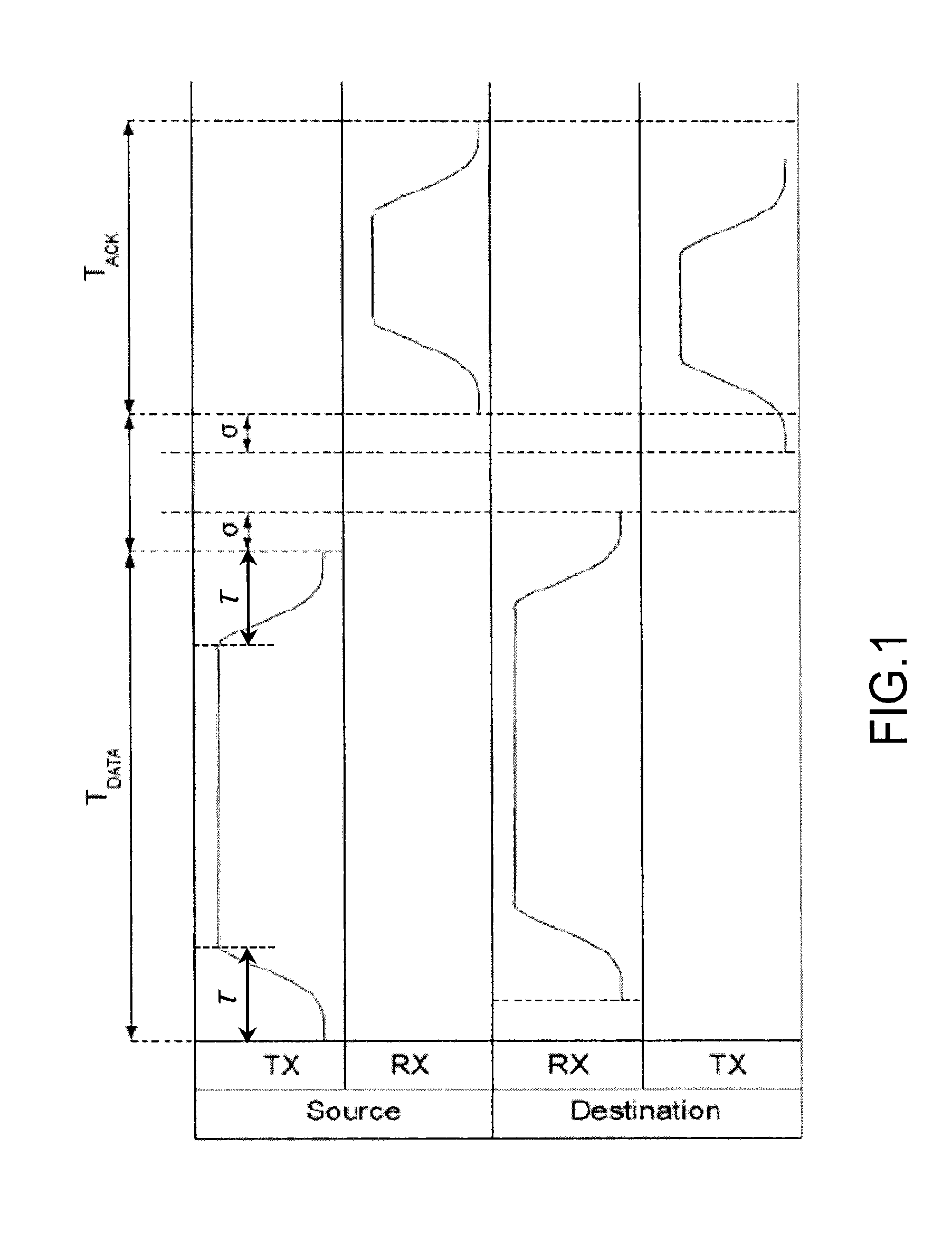

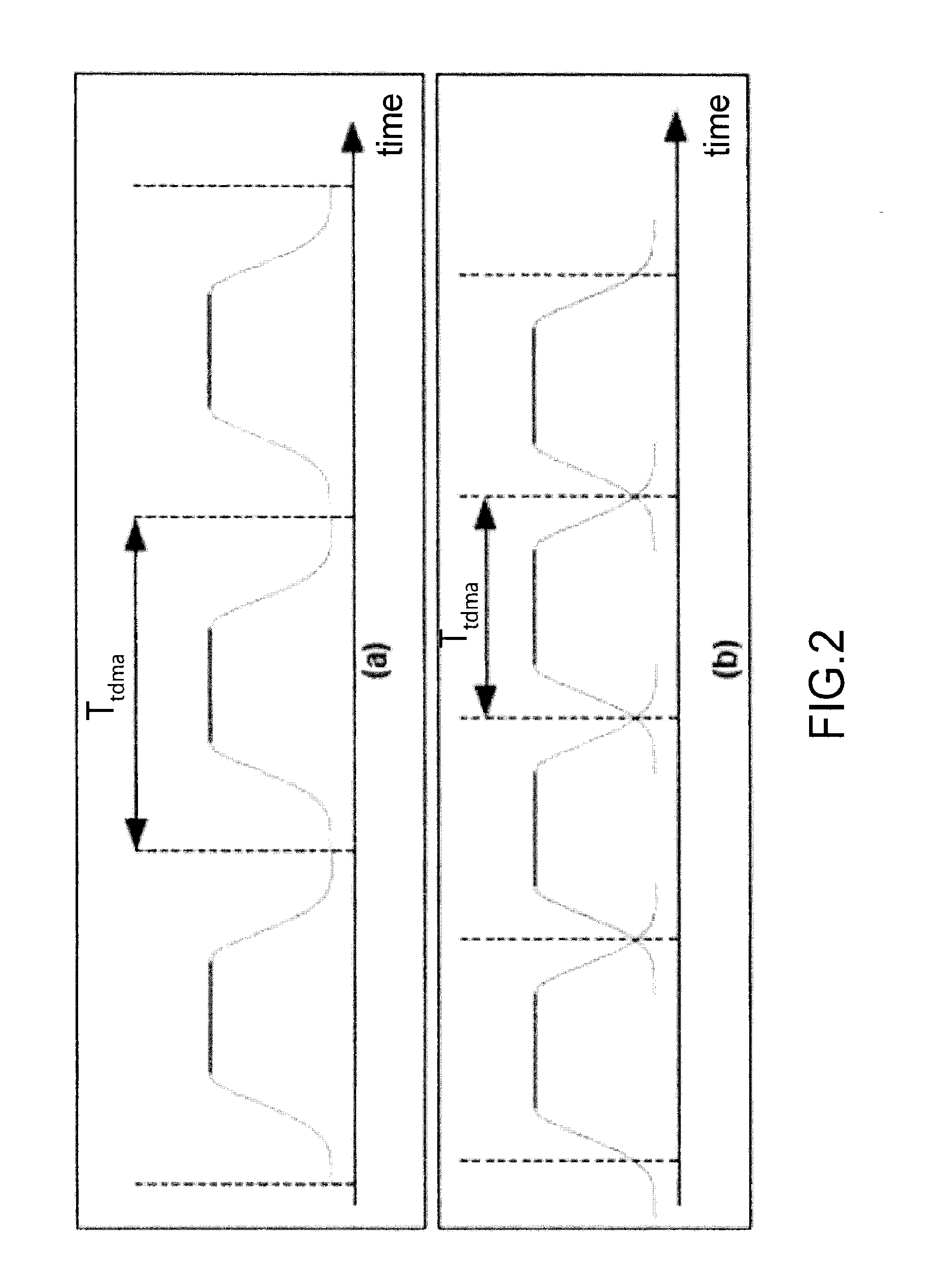

Receiver and fbmc reception method with low decoding latency

The invention relates to a receiver and a FBMC reception method making it possible to reduce the decoding latency time and to increase the data rate in a communication system using a handshake exchange protocol or a TDMA access protocol. The receiver introduces zero padding values in place of the last samples of the last block of samples of a FBMC packet, without waiting for the end of this packet. The decoding of the FBMC packet is thus decoded more rapidly, without significant degradation of the error rate and without reduction of the out-of-band rejection rate of the FBMC signal.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

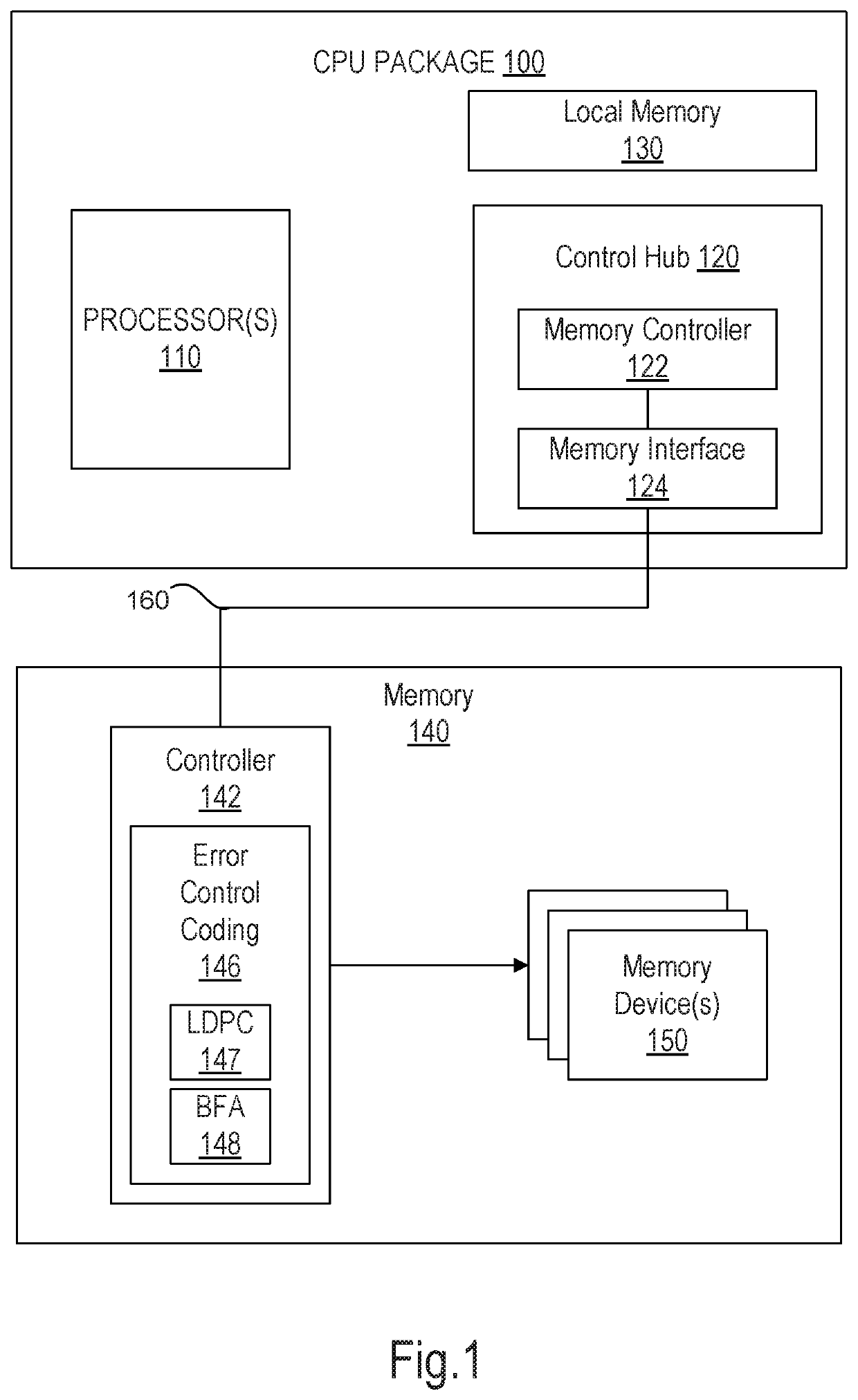

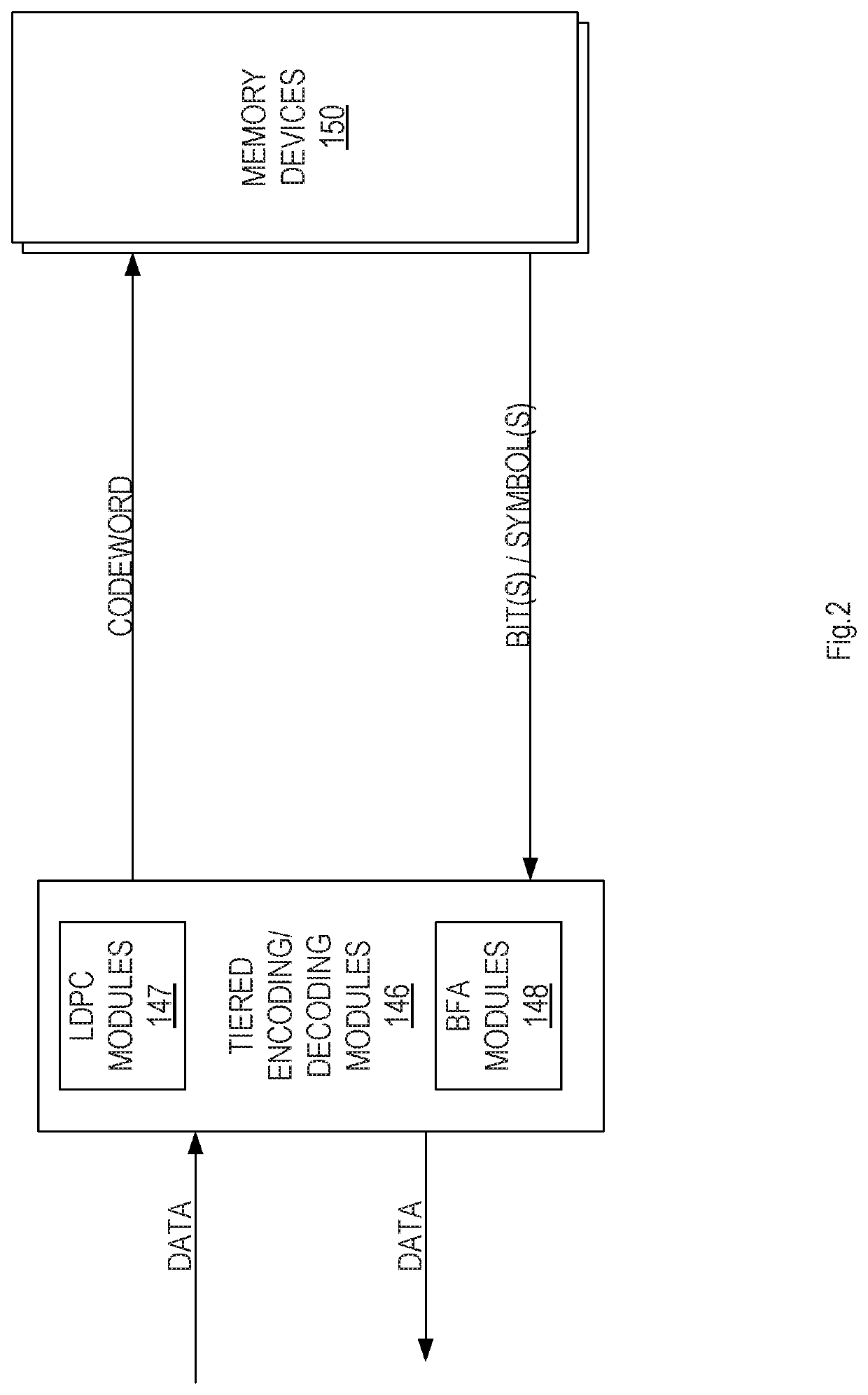

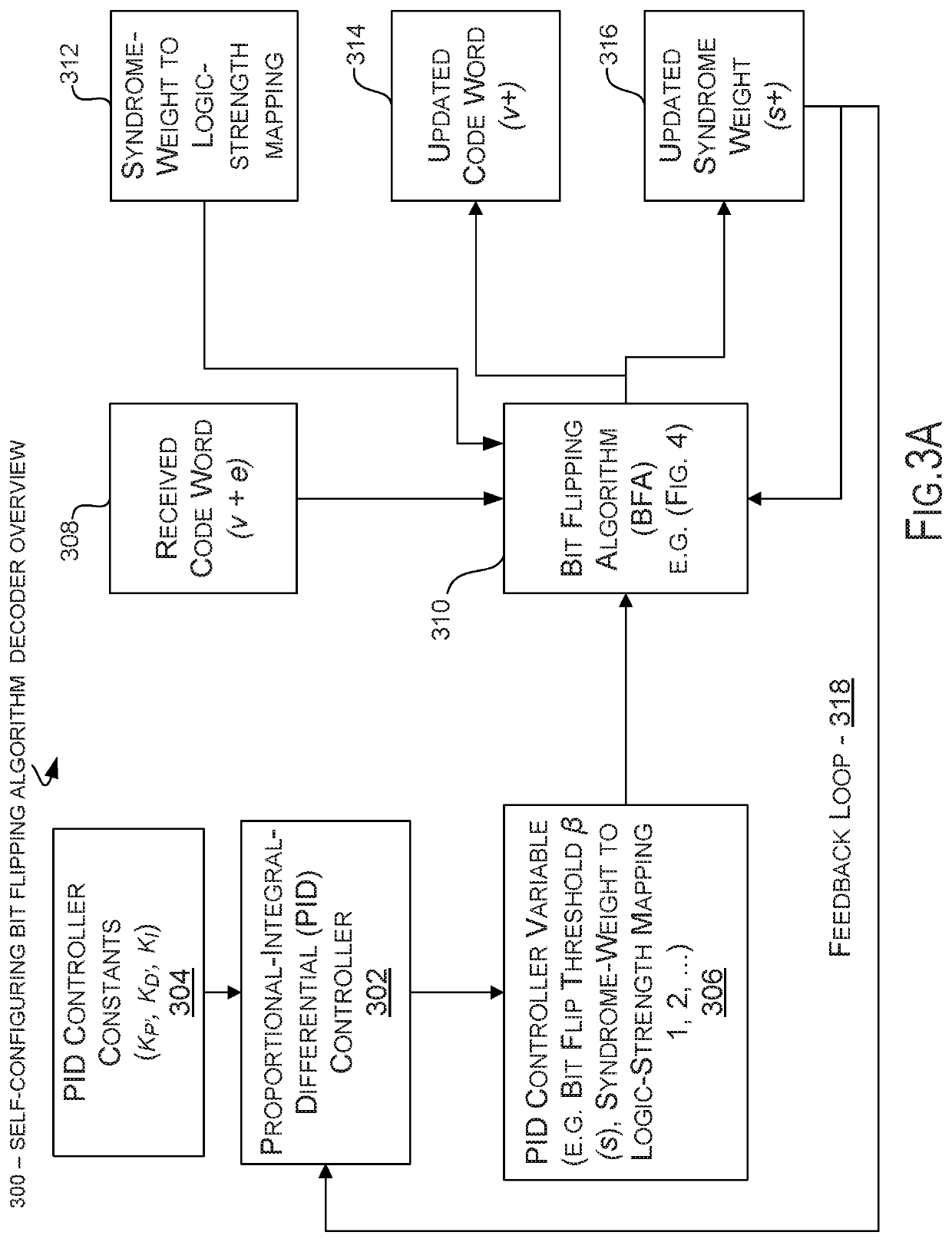

Self-configuring error control coding

ActiveUS10547327B2Error correction/detection using multiple parity bitsCode conversionAlgorithmDecoding latency

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

Video rate control for video coding standards

ActiveUS8401076B2Quality improvementColor television with pulse code modulationColor television with bandwidth reductionVideo rateVideo encoding

A method and device for improving rate controlling in video coding of sequences including a series of Inter frames separated by Intra frames, when a decoding delay is considered, comprise for each Inter frame of the series: computing a target frame size, computing a maximum buffer level related to a position of each Inter frame relative to a previous Intra frame and an upcoming Intra frame, and optimizing a transmission buffer level in response to the computed target frame size and the computed maximum buffer level.

Owner:MASIMO CORP

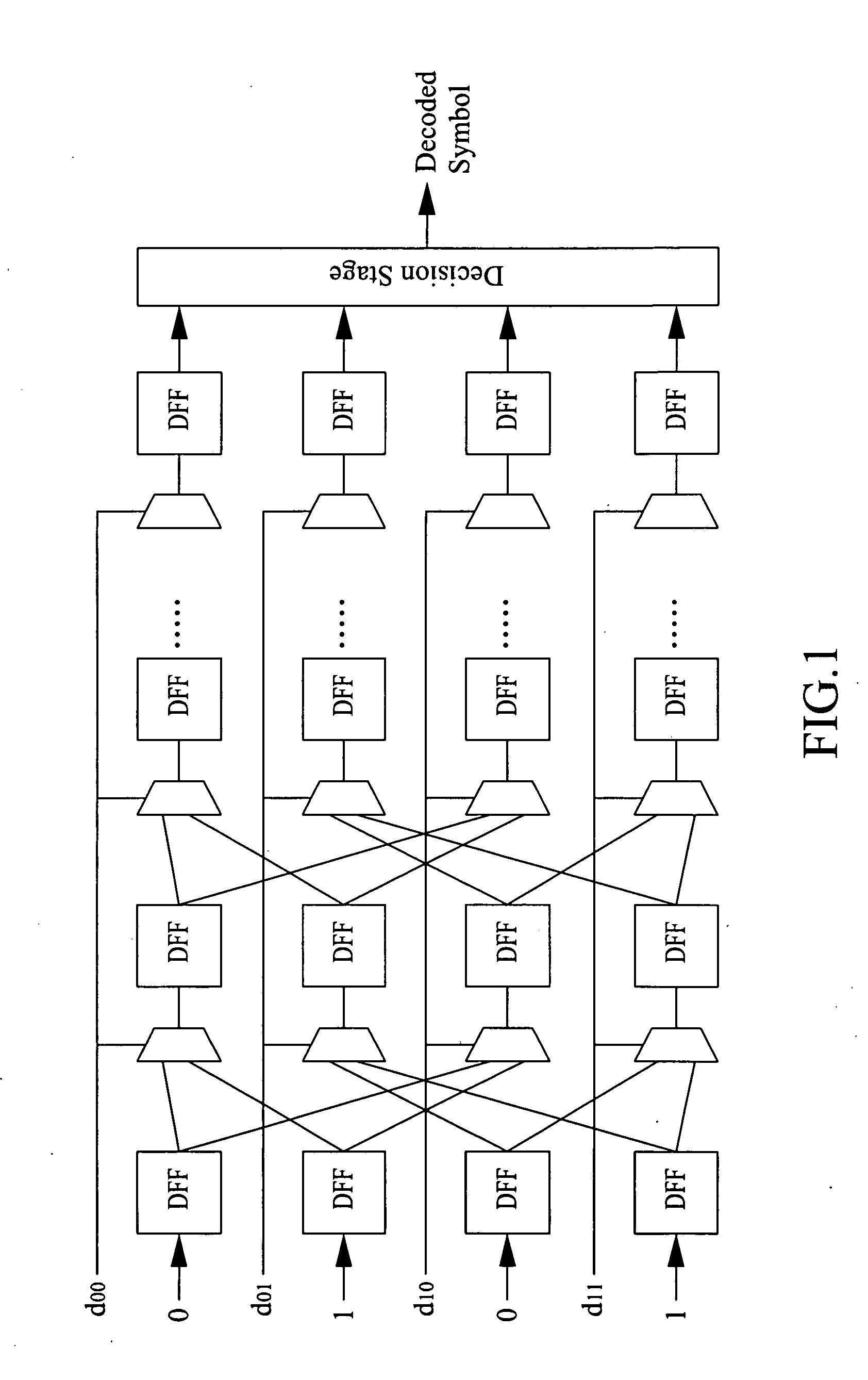

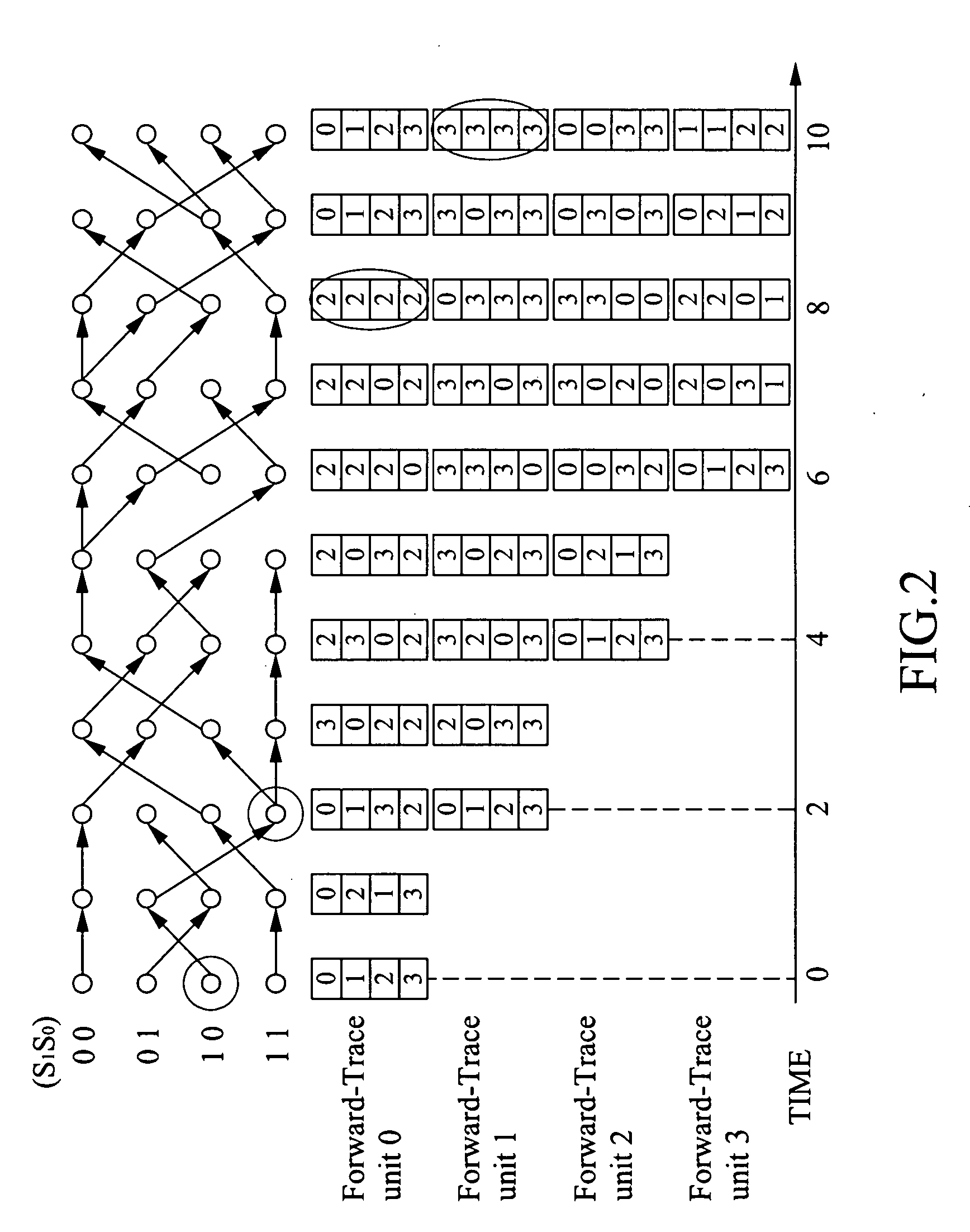

Memory architecture for viterbi decoder and operating method therefor

InactiveUS20090172504A1Reduce power consumptionReduce consumptionEnergy efficient ICTCode conversionViterbi decoderPower efficient

The Viterbi decoder is an essential module in a communication system, in which the power and the decoding latency are restricted. In the present invention, a power efficient low latency survivor memory architecture and an operating method for the Viterbi decoder are disclosed by providing a plurality of trace-forward units, a plurality of first signal selecting units, a plurality of second signal selecting units and a third signal selecting unit to reduce the power consumption by decreasing the exchange times of contents in the trace-forward units. Thus, the present invention is suitable for use in mobile communication devices which require low power consumption.

Owner:IND TECH RES INST