Patents

Literature

52results about "Microinstruction function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

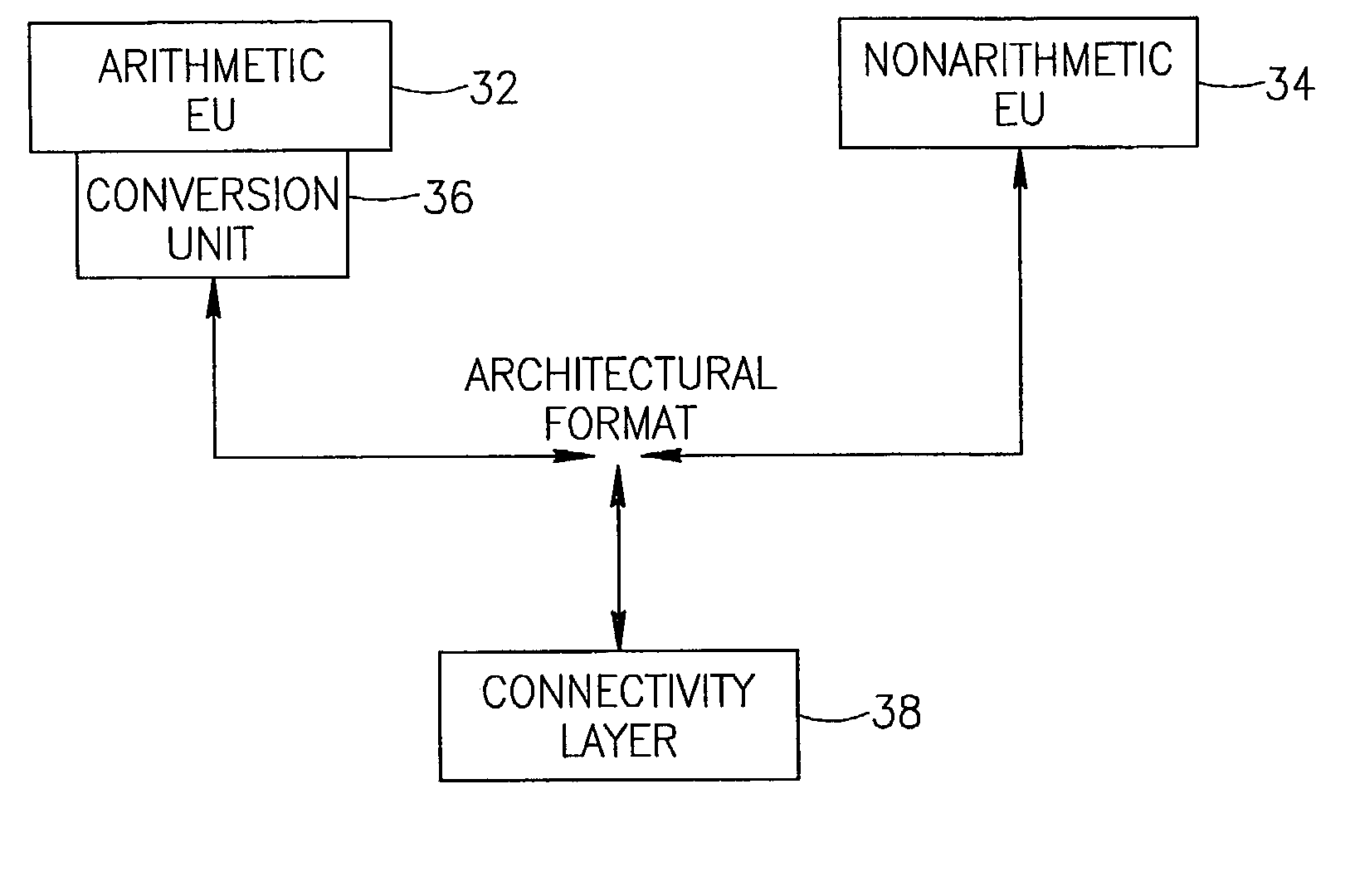

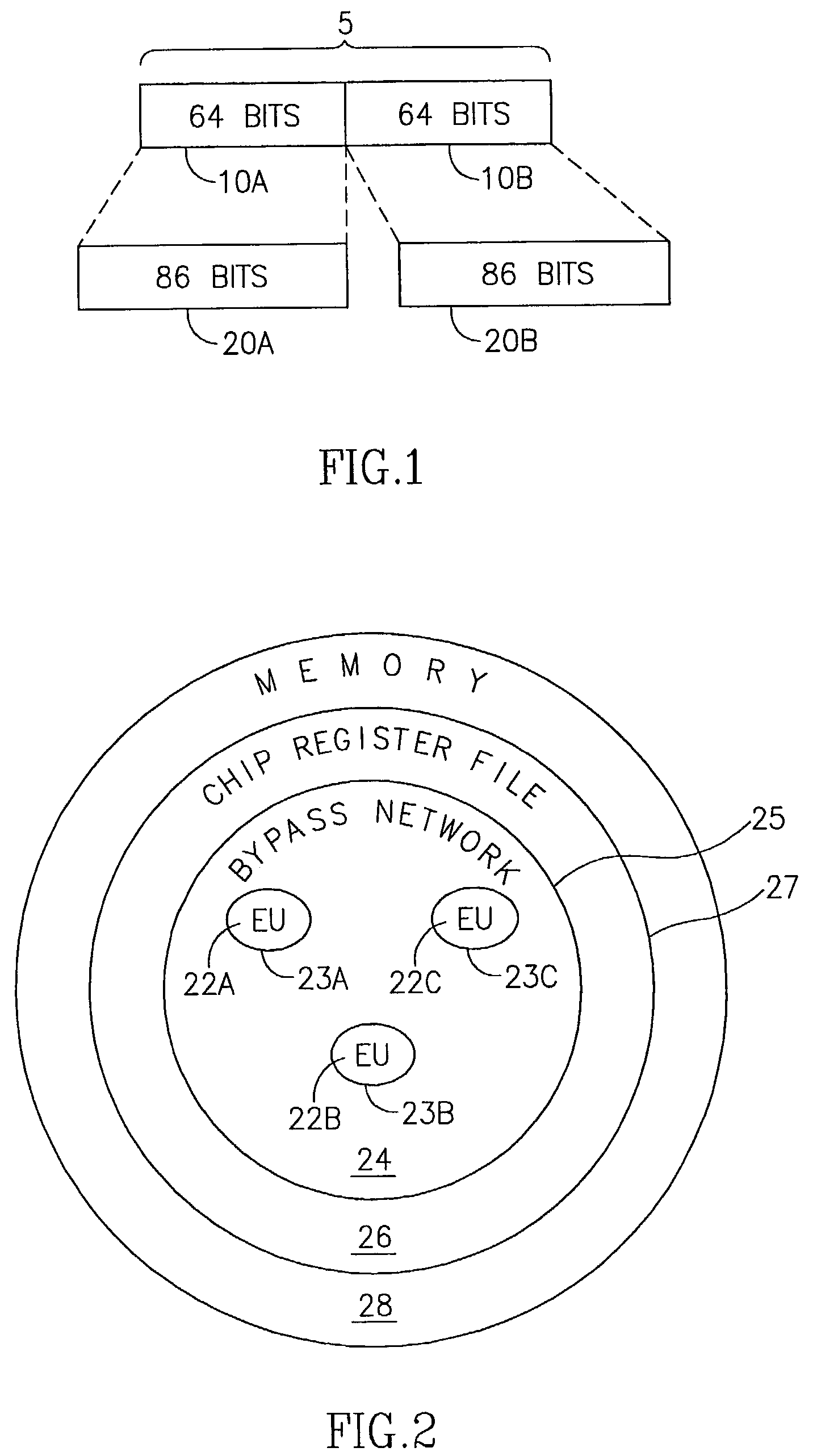

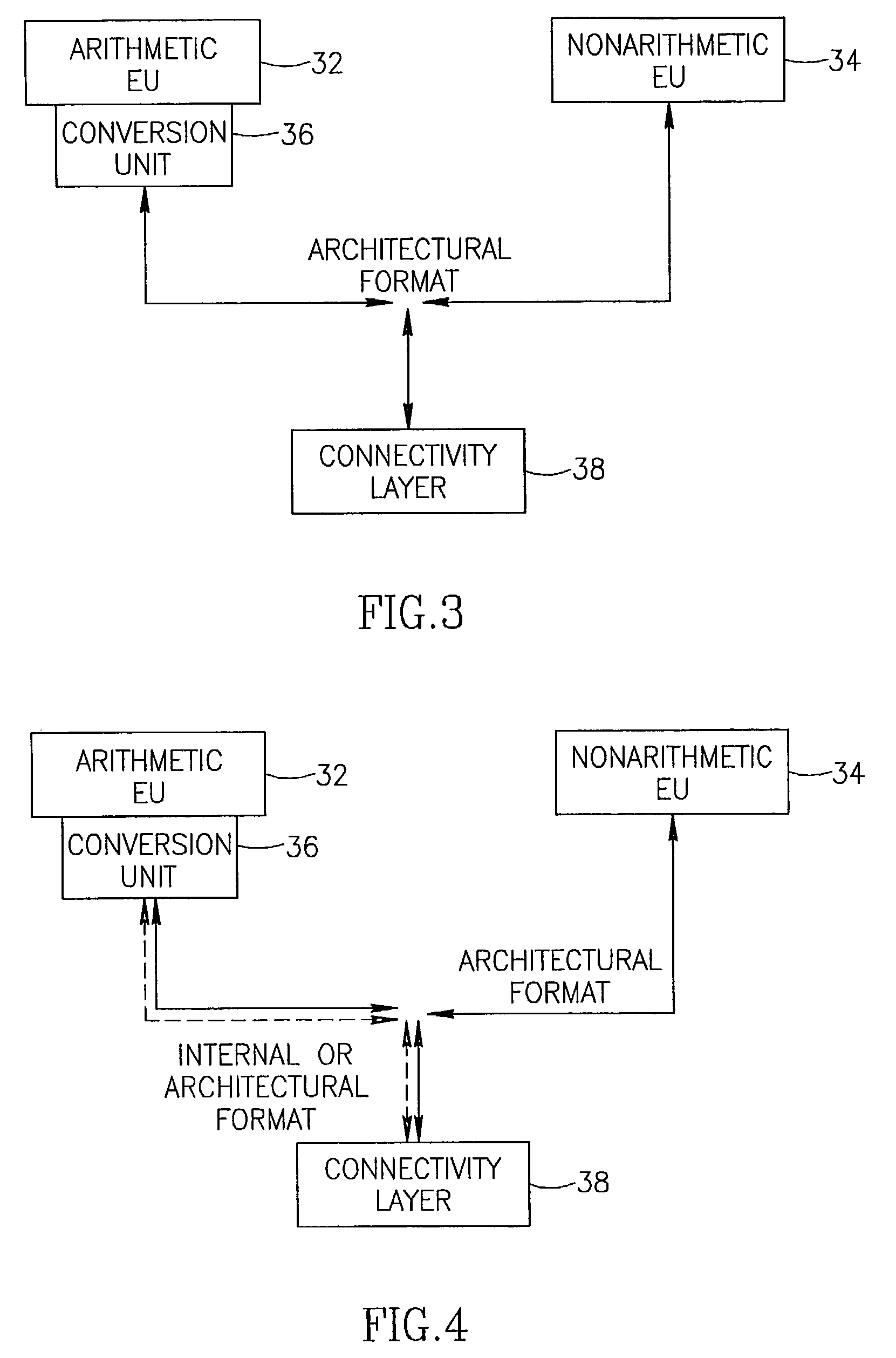

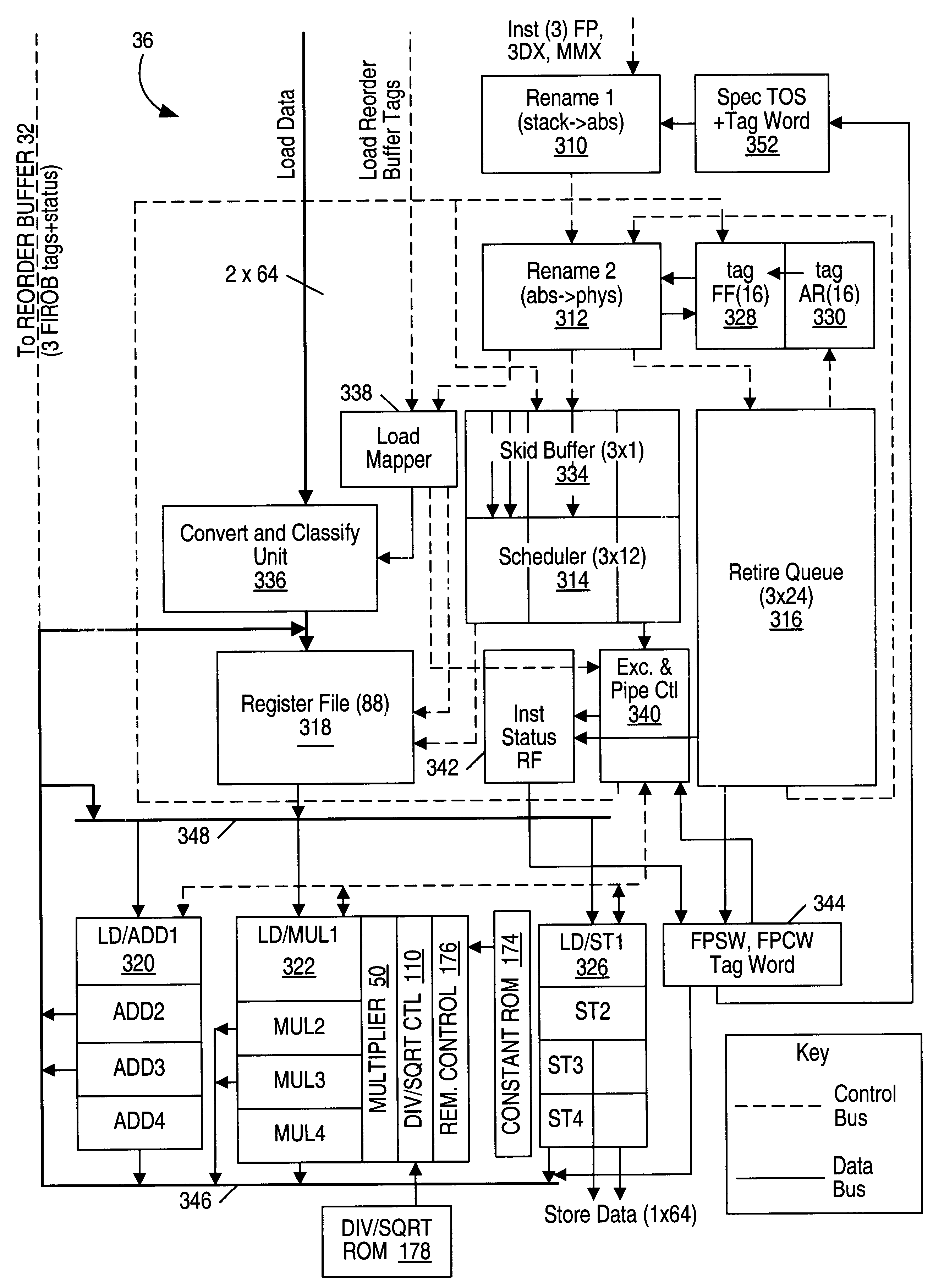

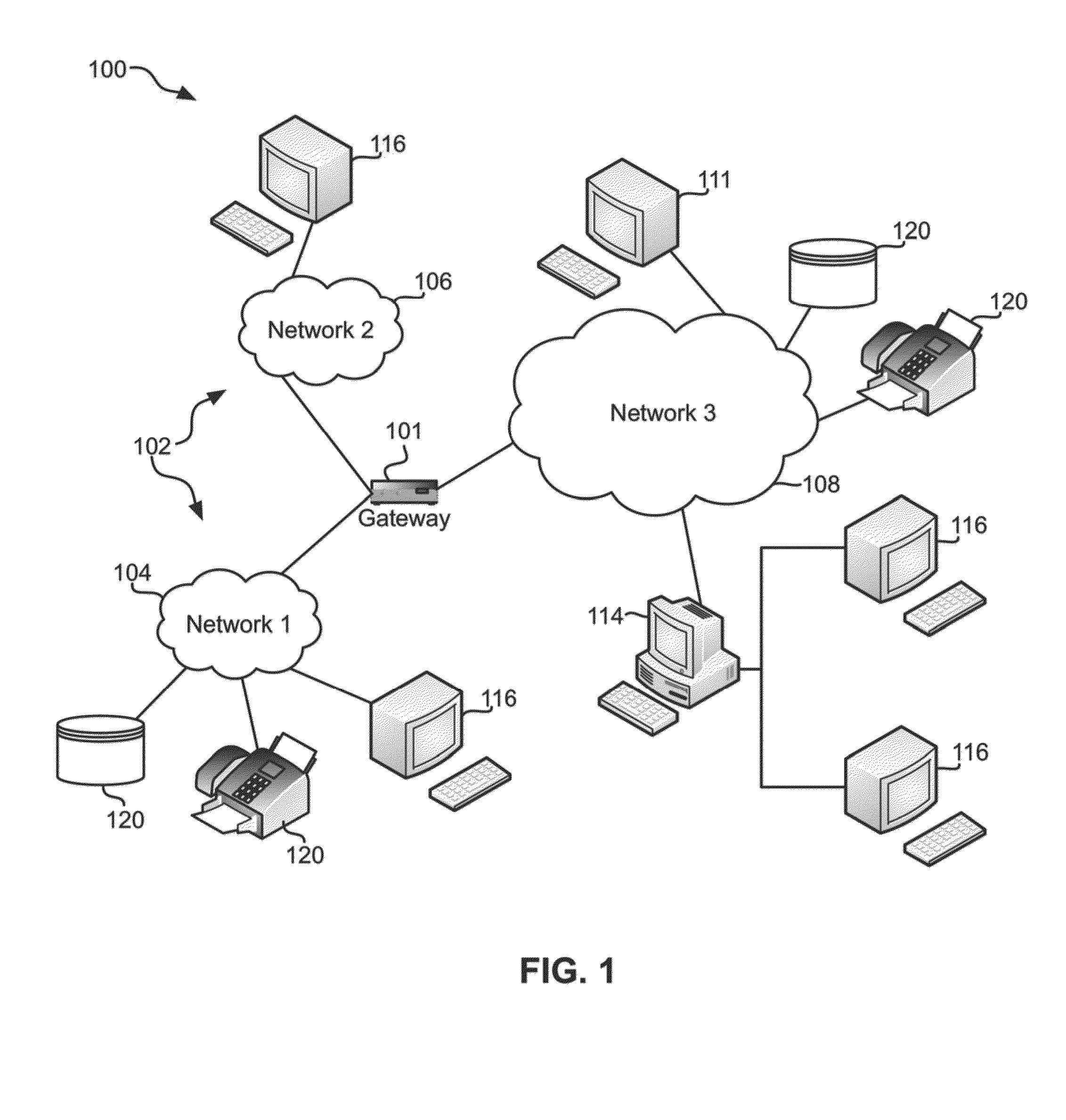

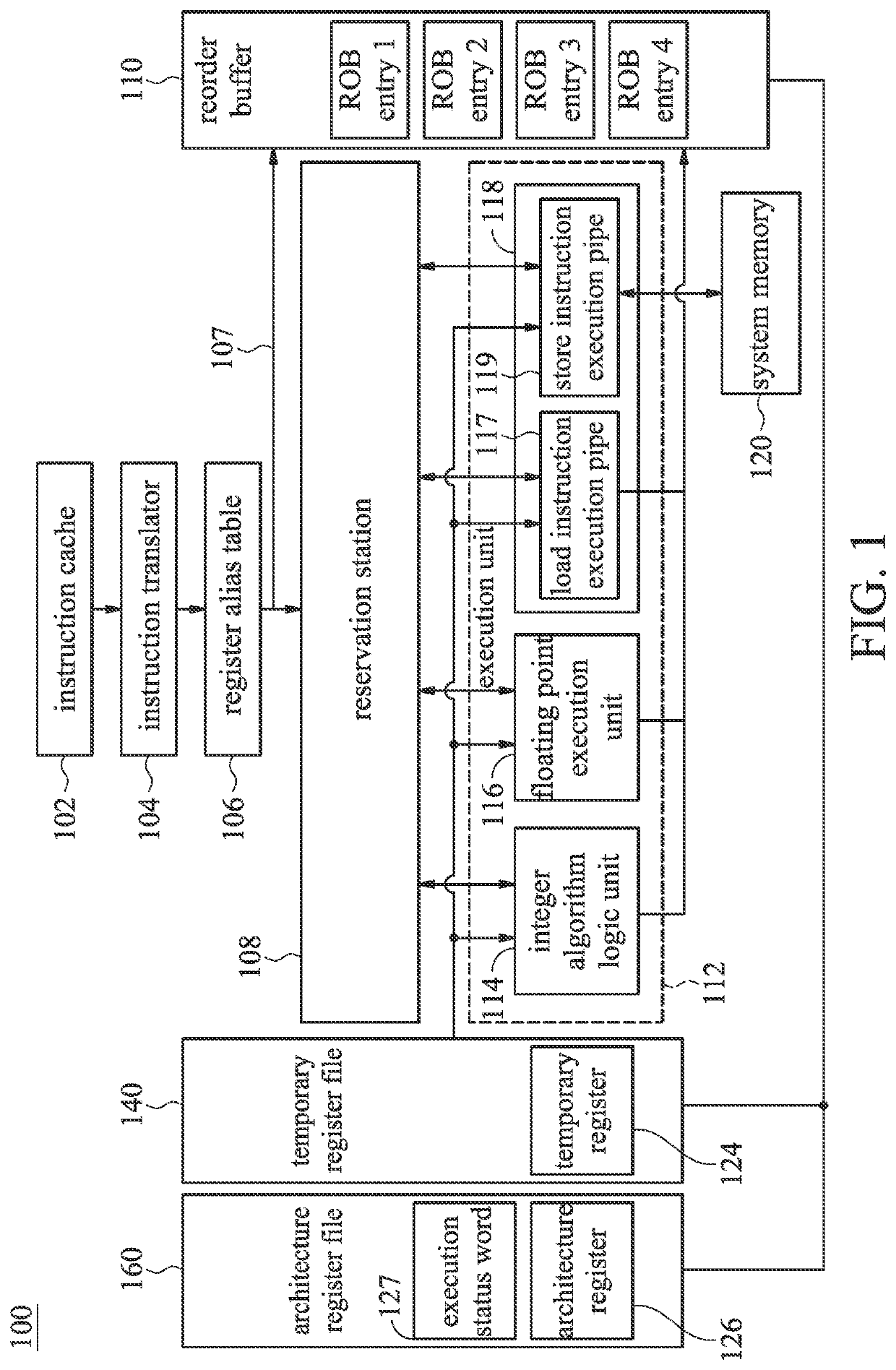

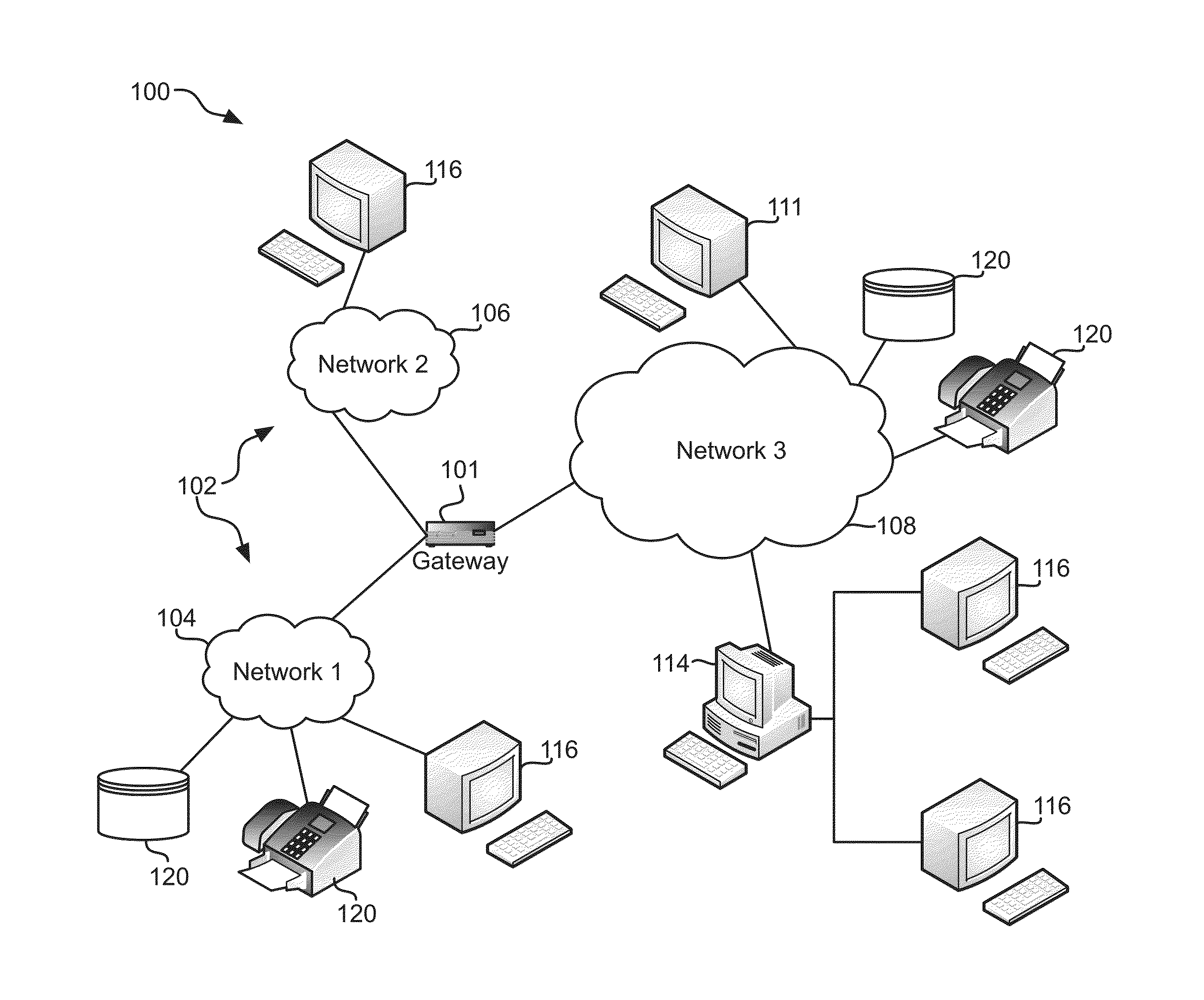

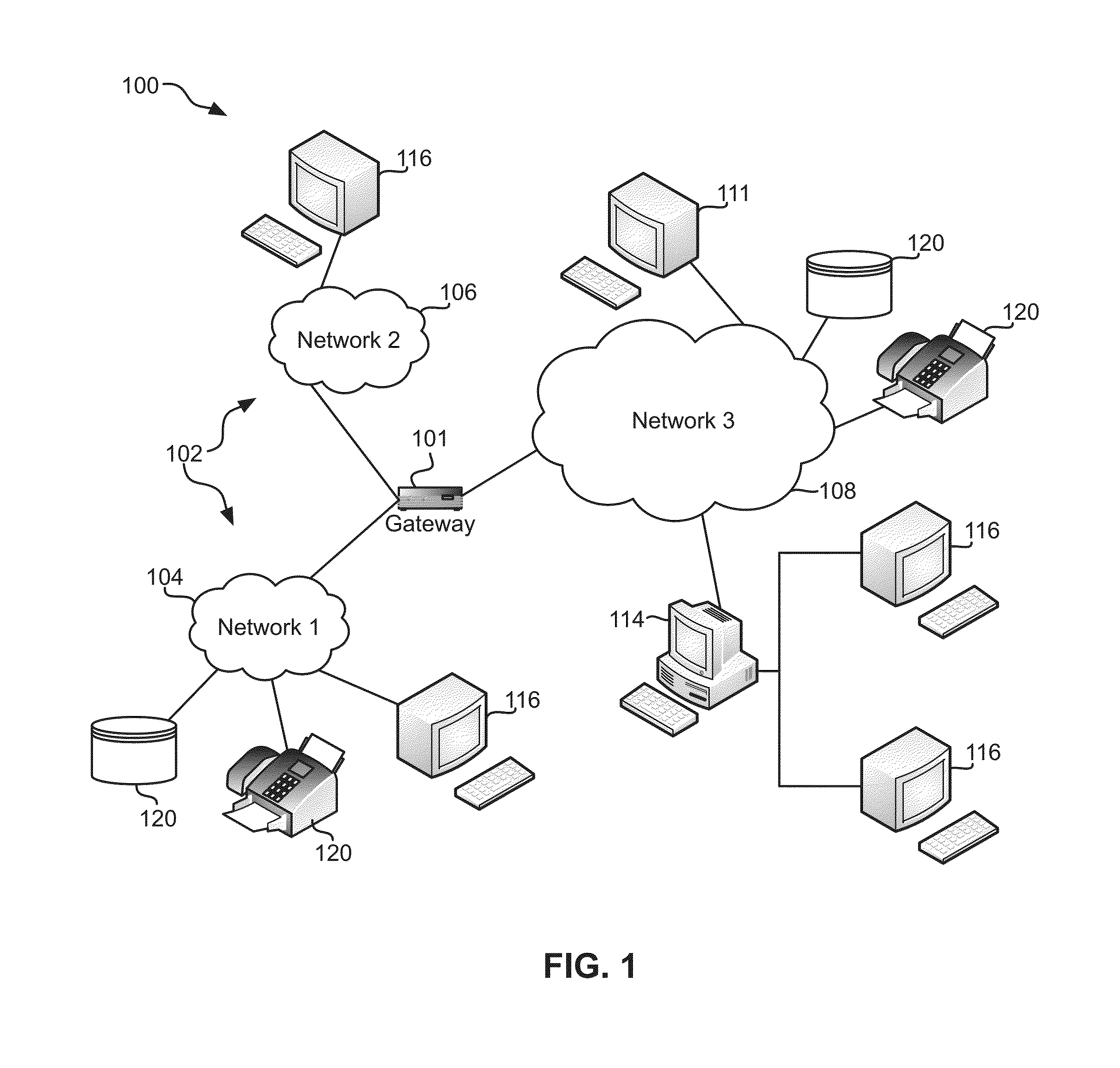

System and method of converting data formats and communicating between execution units

InactiveUS7430656B2Runtime instruction translationDigital computer detailsComputer architectureData transformation

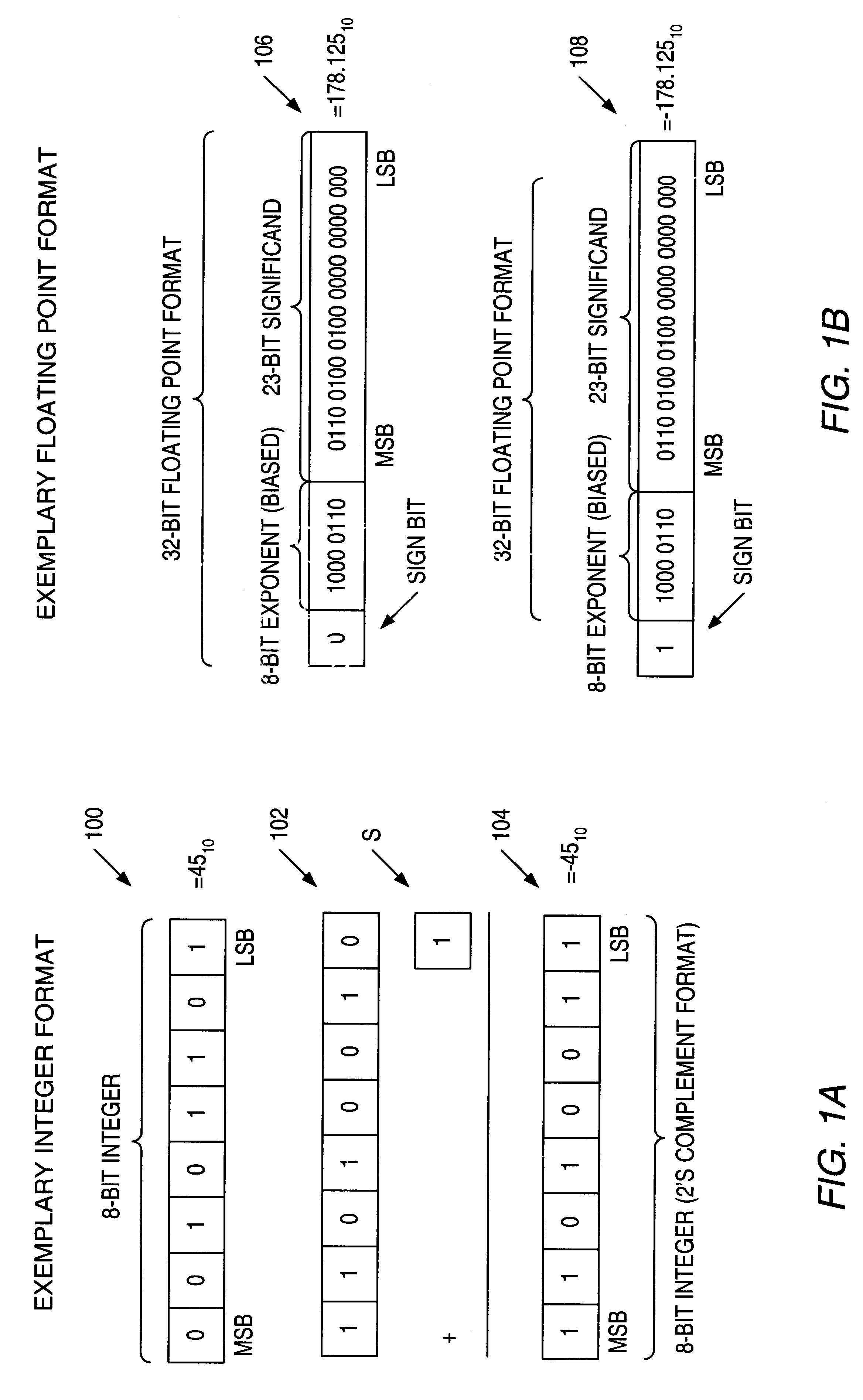

A method and system including transmitting data in an architectural format between execution units in a multi-type instruction set architecture and converting data received in the architectural format to an internal format and data output in the internal format to the architectural format based on an operation code and a data type of a microinstruction.

Owner:INTEL CORP

Apparatus and method for using checking instructions in a floating-point execution unit

InactiveUS6247117B1Digital computer detailsSpecific program execution arrangementsExecution unitOperand

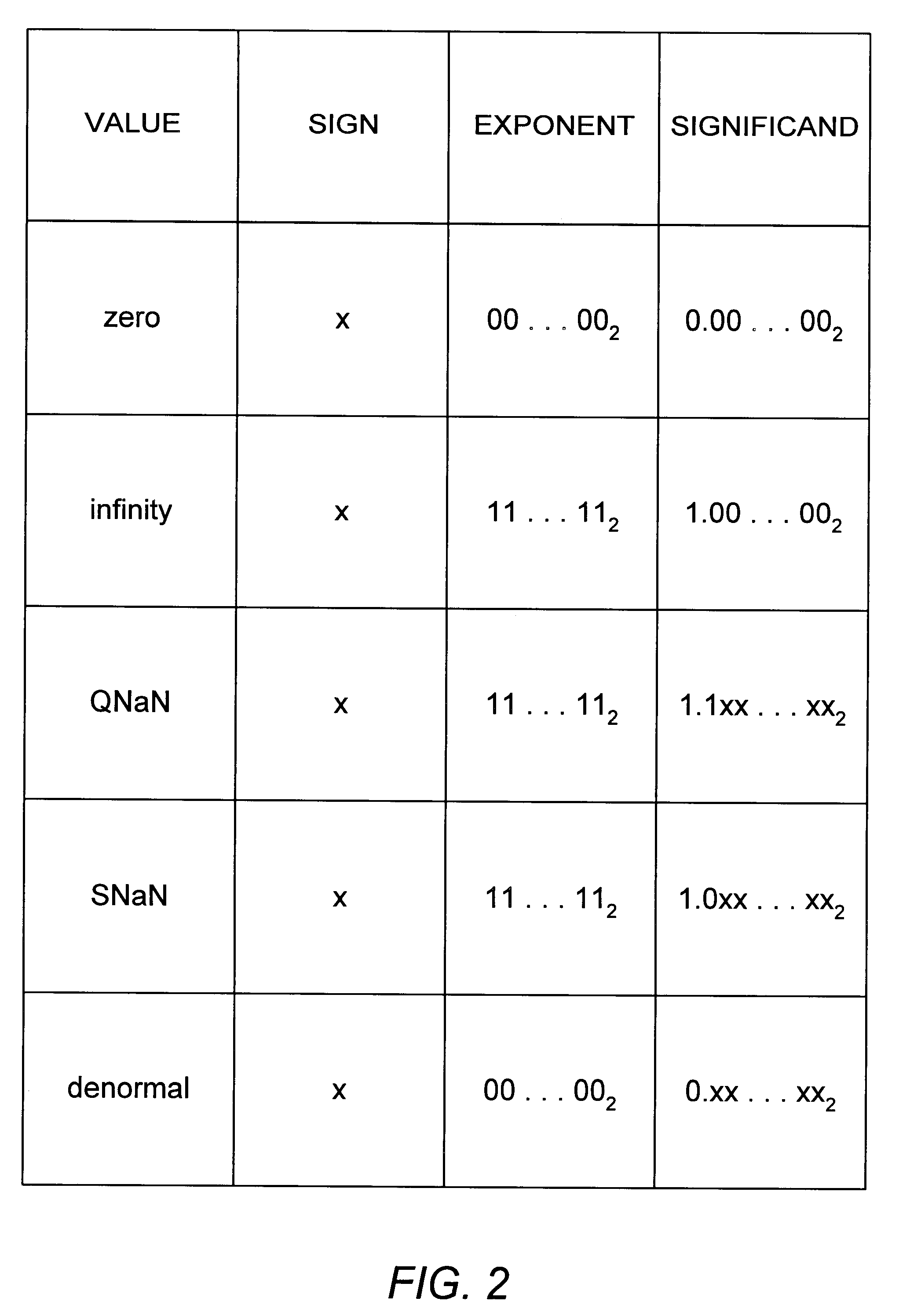

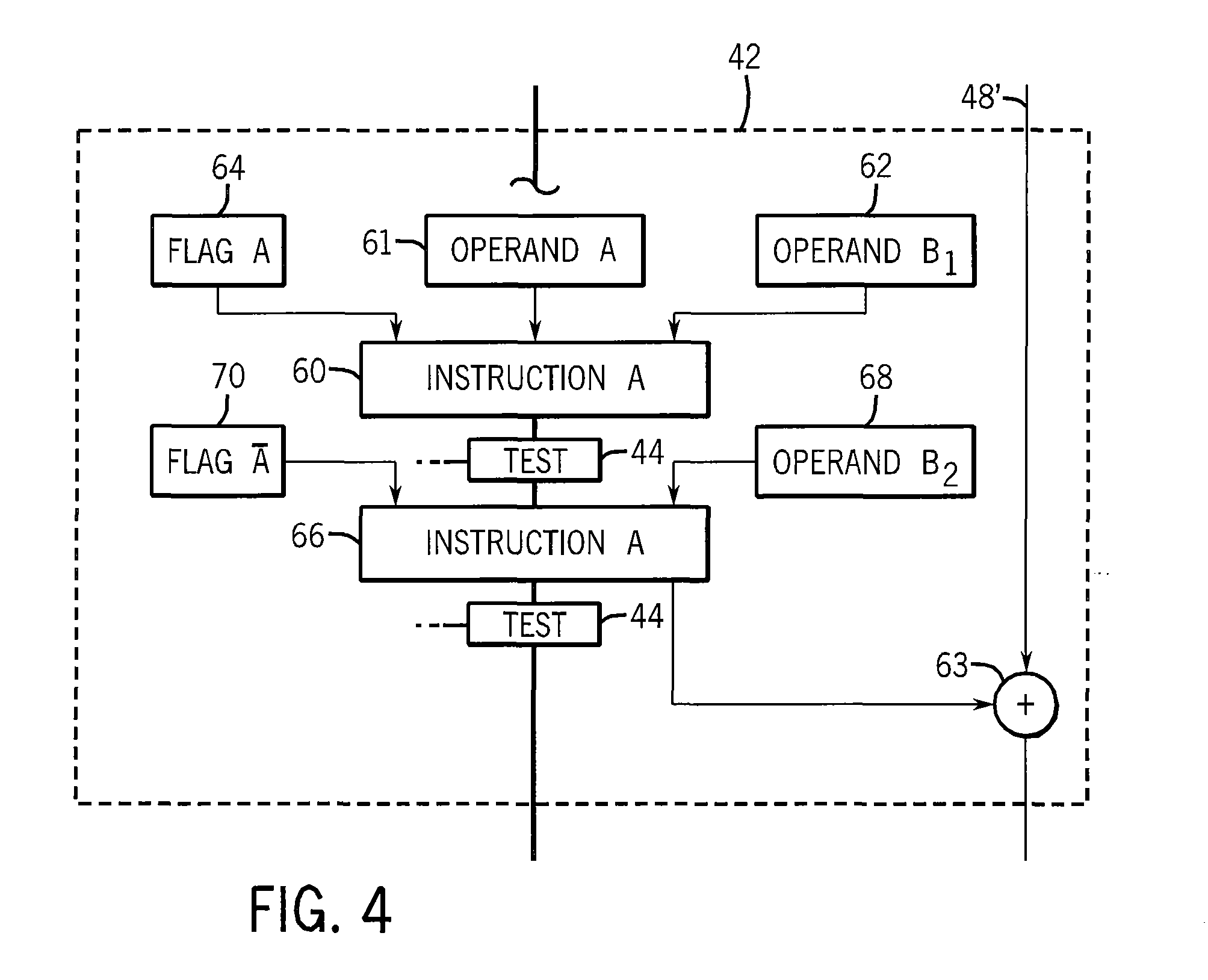

The use of checking instructions to detect special and exceptional cases of a defined data format in a microprocessor is disclosed. Generally speaking, a checking instruction is included with the microcode of floating-point instructions to detect special and exceptional cases of operand values for the floating-point instructions. A checking instruction is configured to set one or more flags in a flags register if it detects a special or exceptional case for an operand value. A checking instruction may also set the result or results of a floating-point instruction to a result value if a special or exceptional case is detected. In addition, a checking instruction may be configured to set one or more bits in status register if a special or exceptional case is detected. After a checking instruction completes execution, a subsequent microcode instruction can be executed to determine if one or more flags were set by the checking instruction. If one or more flags have been set by the checking instruction, the subsequent microcode instruction can branch to a non-sequential microcode instruction to handle the special or exceptional case detected by the checking instruction.

Owner:ADVANCED MICRO DEVICES INC

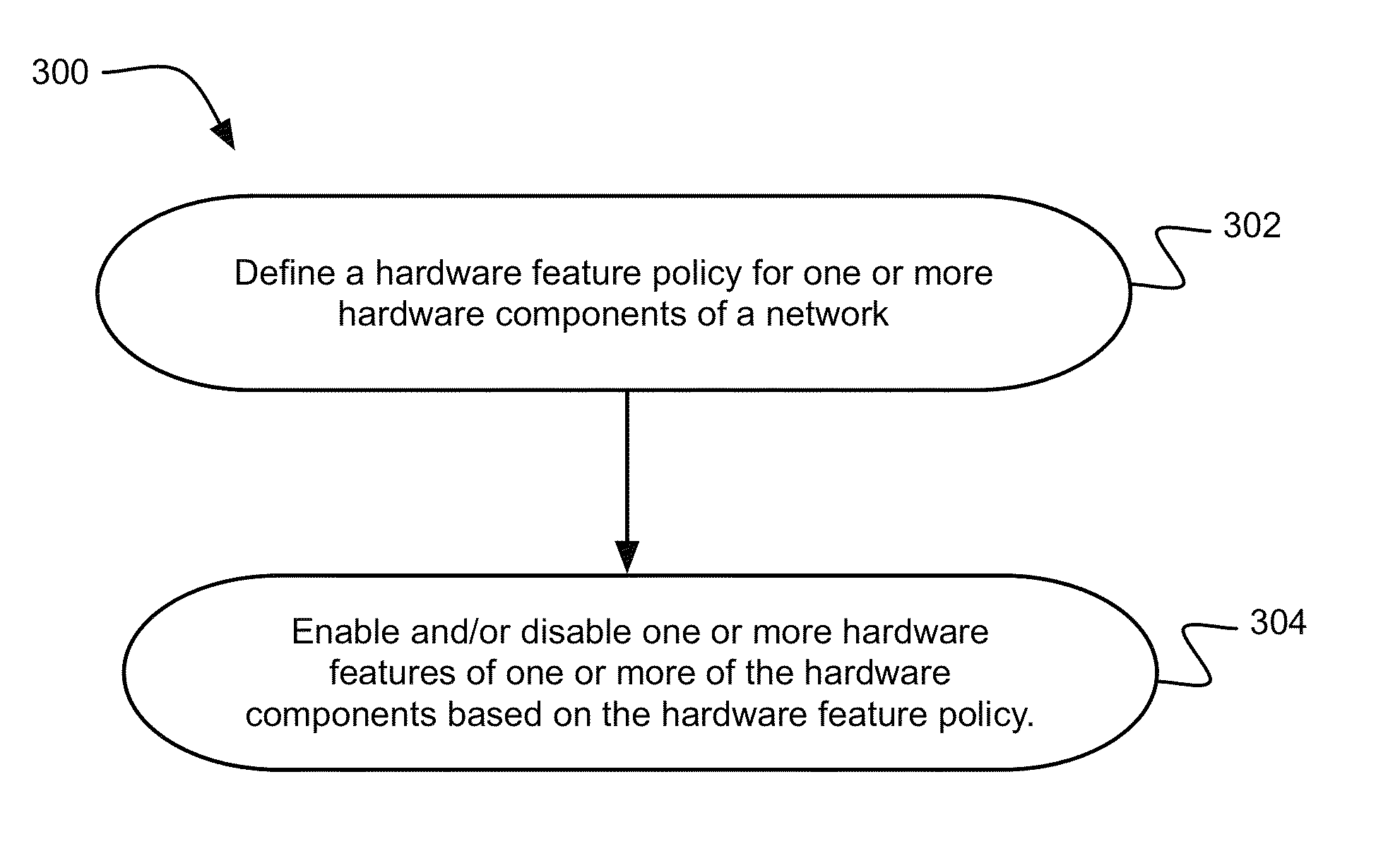

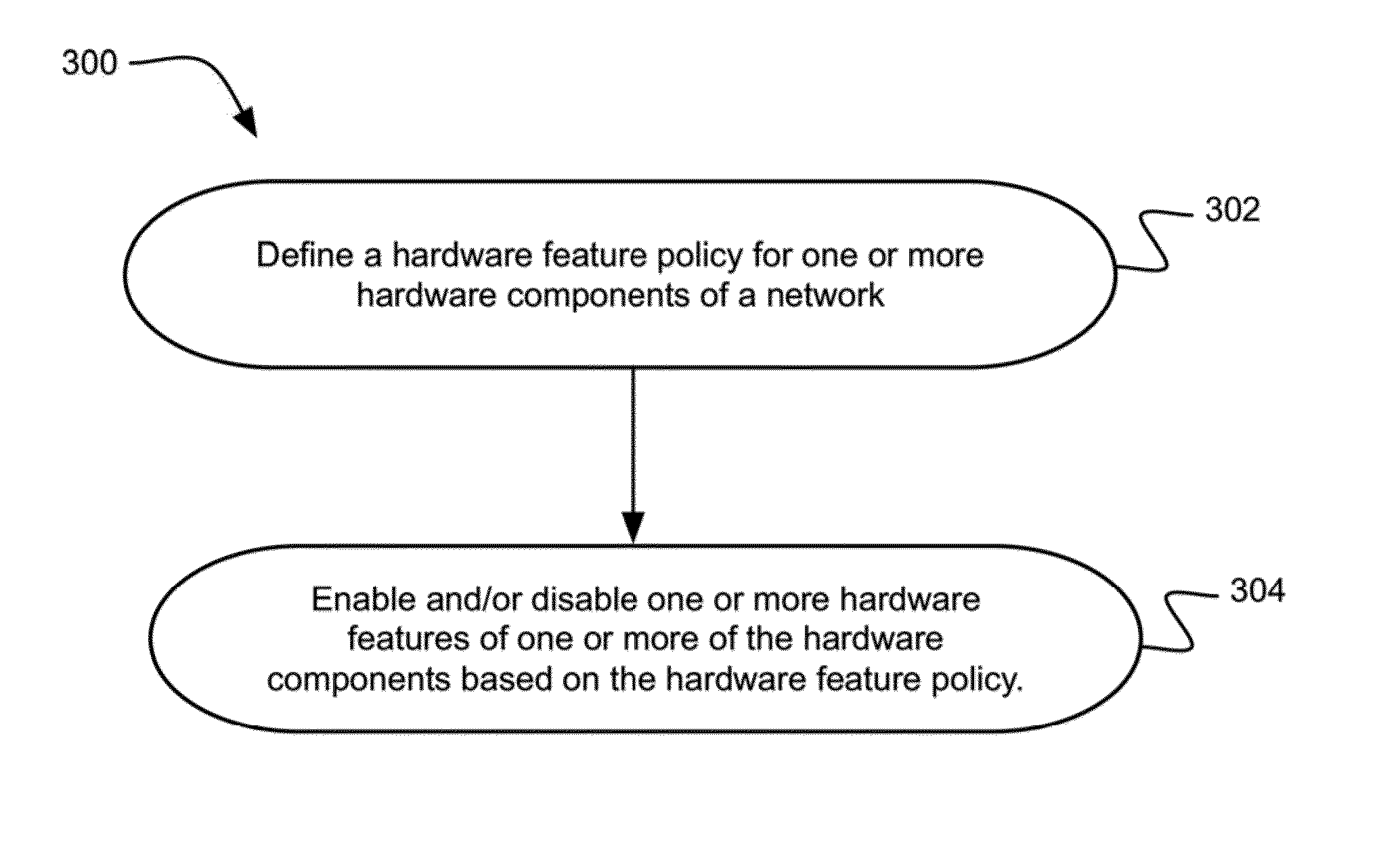

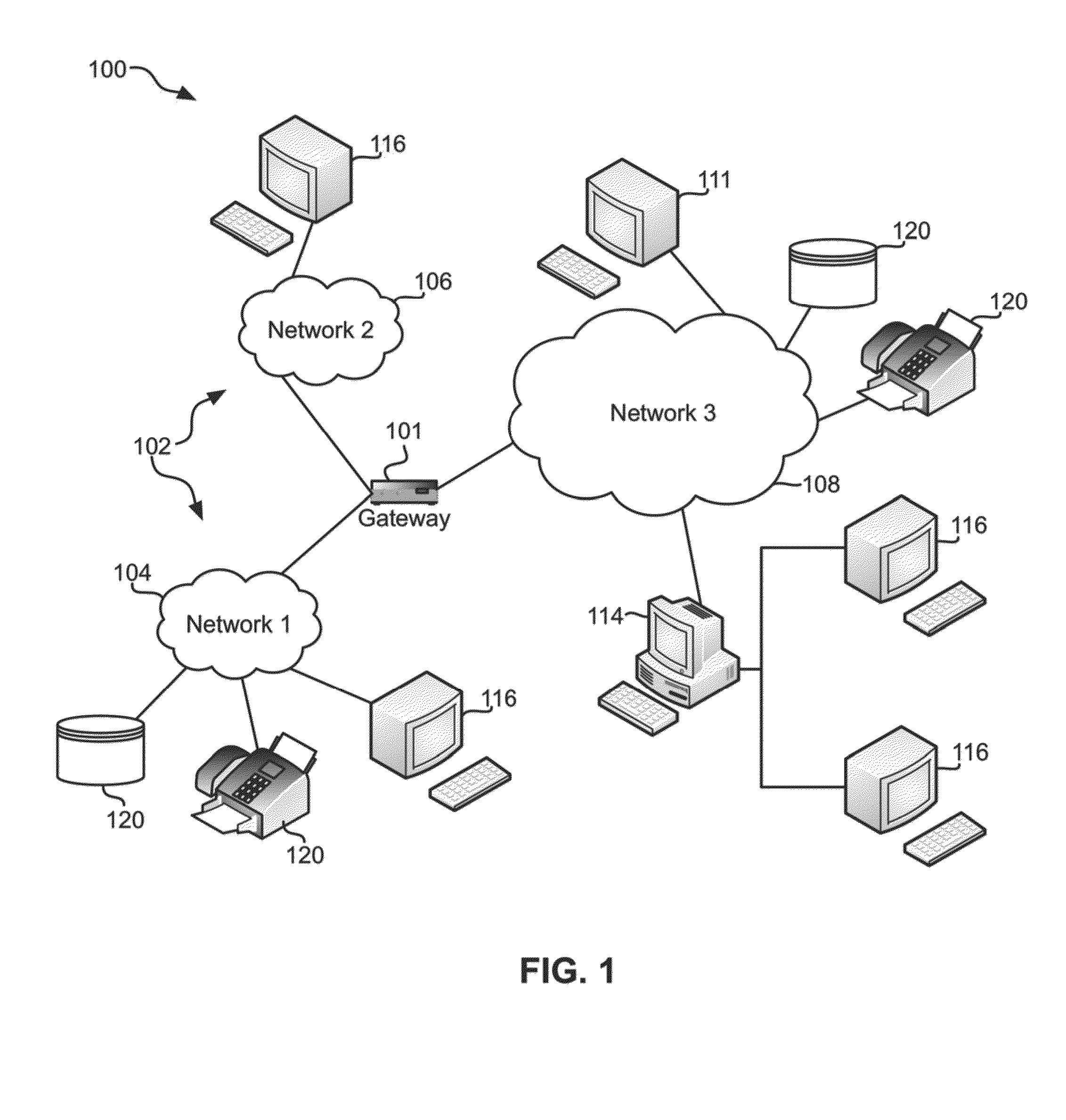

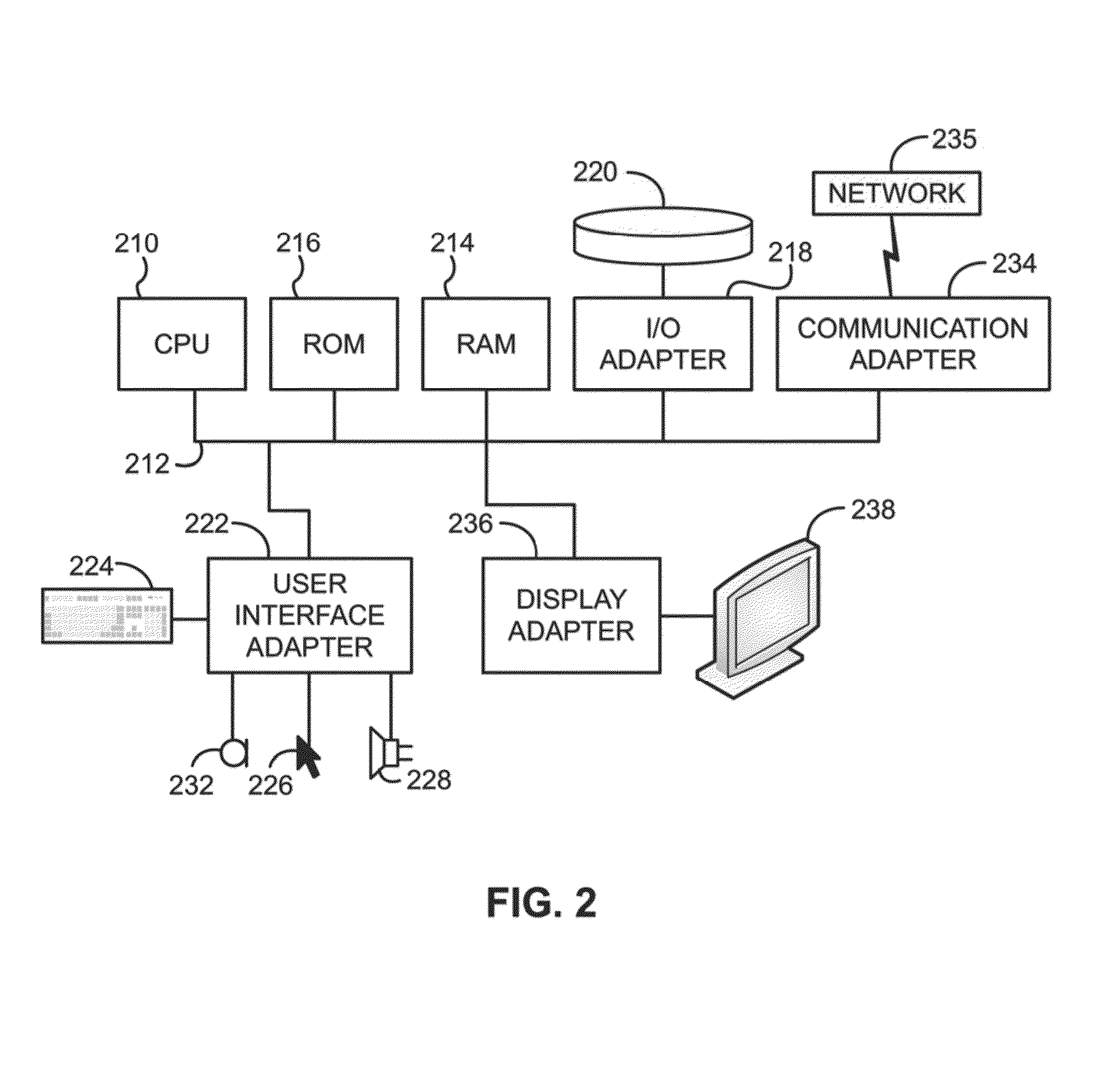

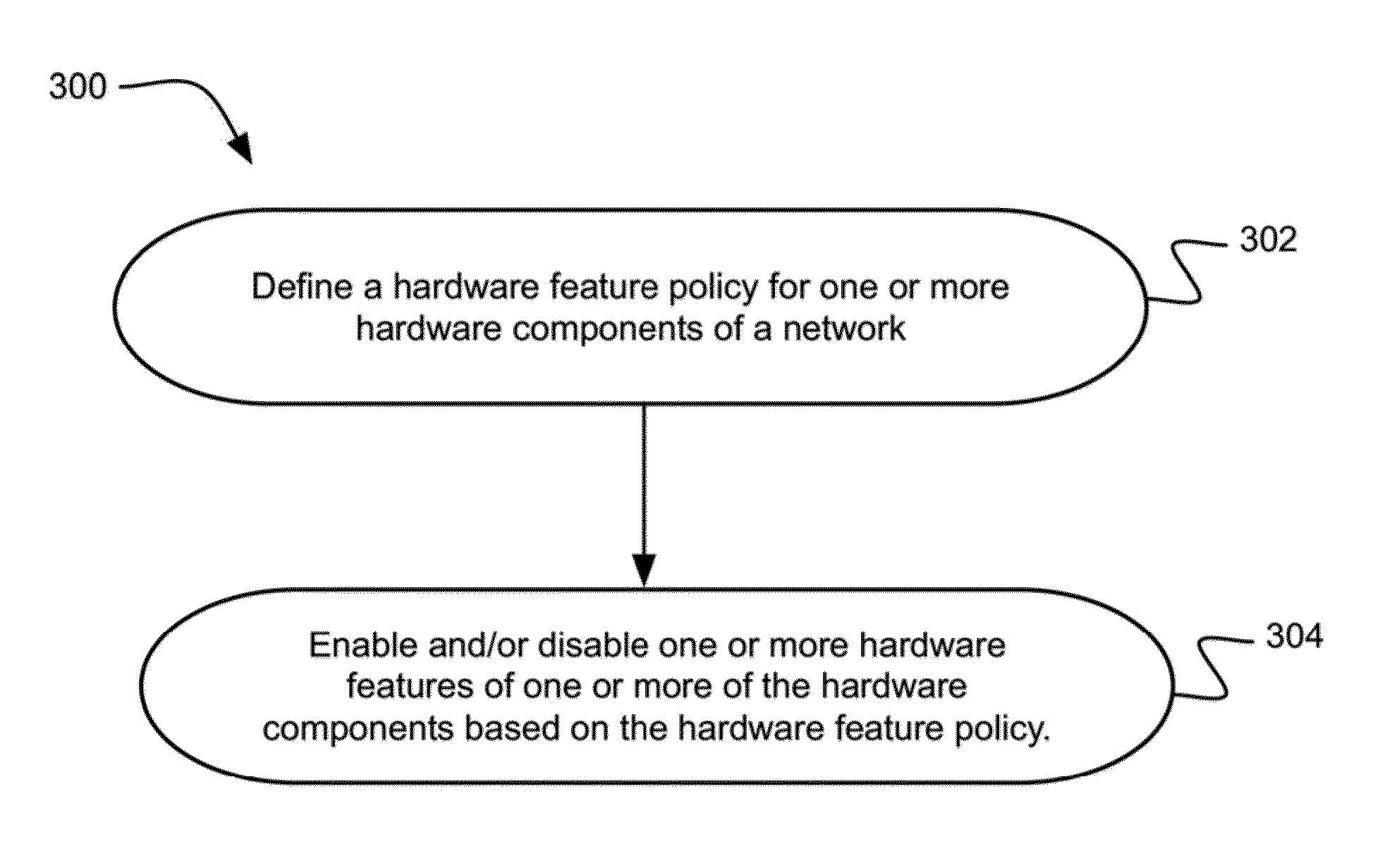

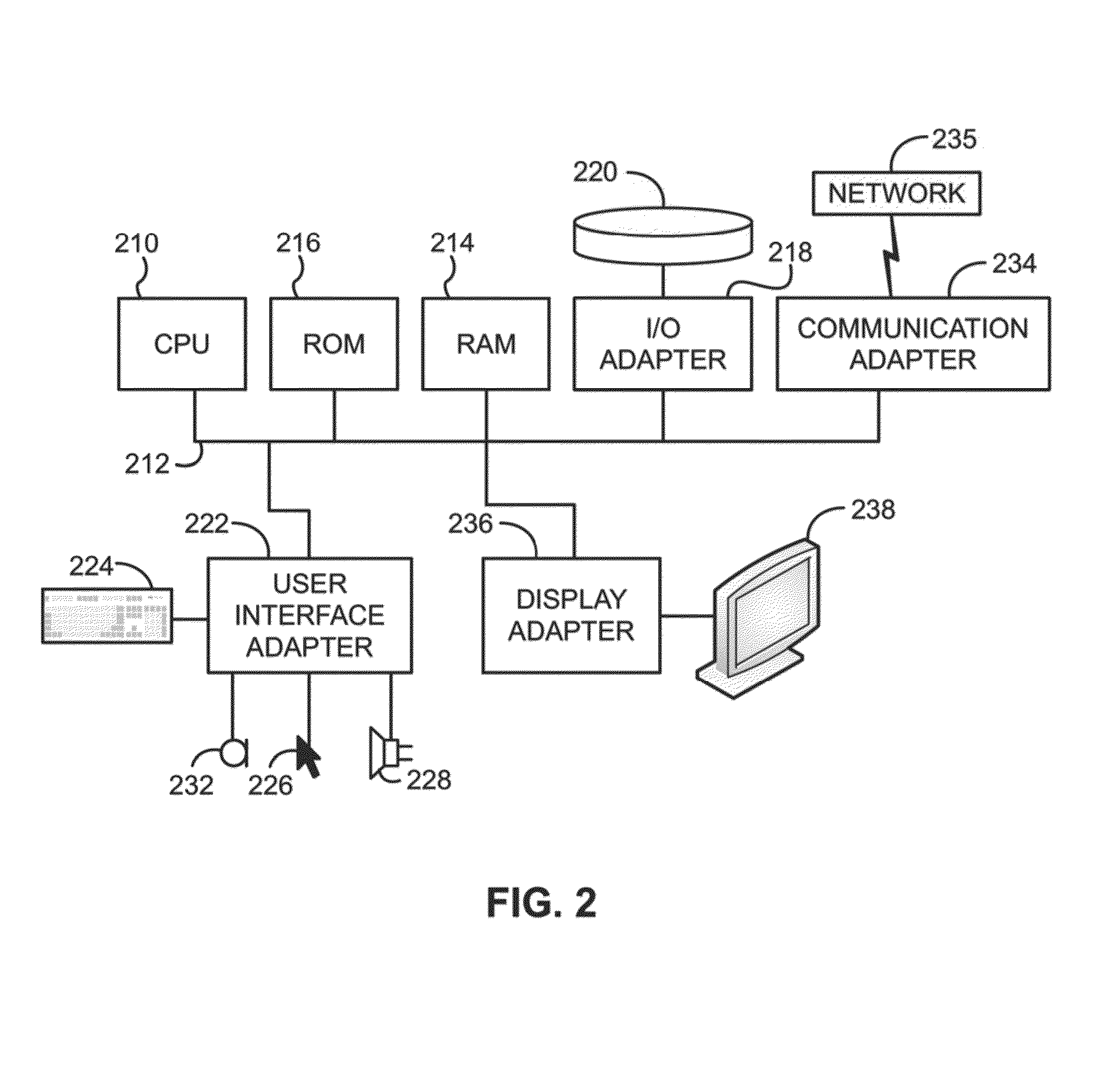

Systems for selectively enabling and disabling hardware features

InactiveUS20140280815A1Specific access rightsError detection/correctionComputer hardwareComputer science

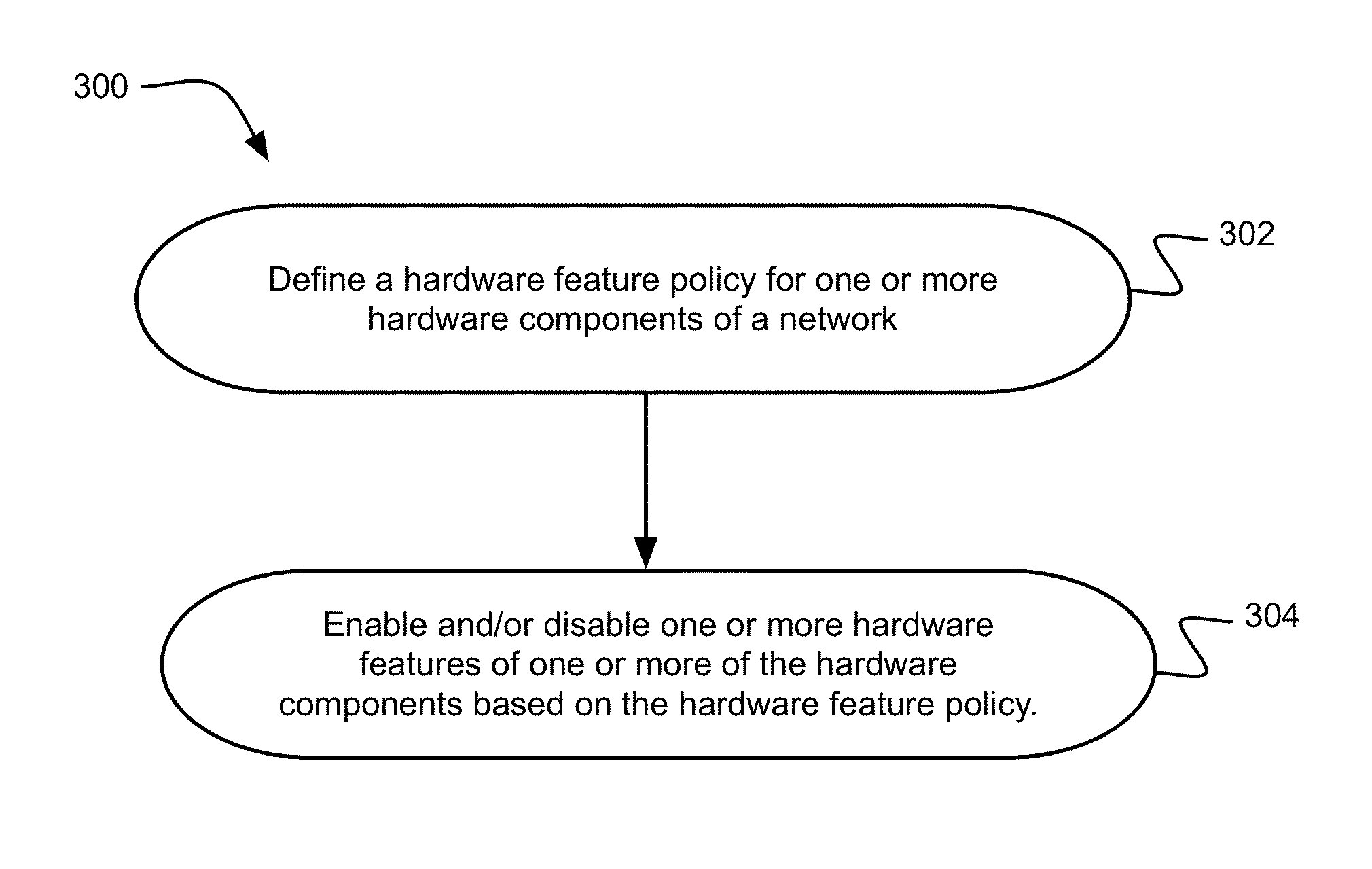

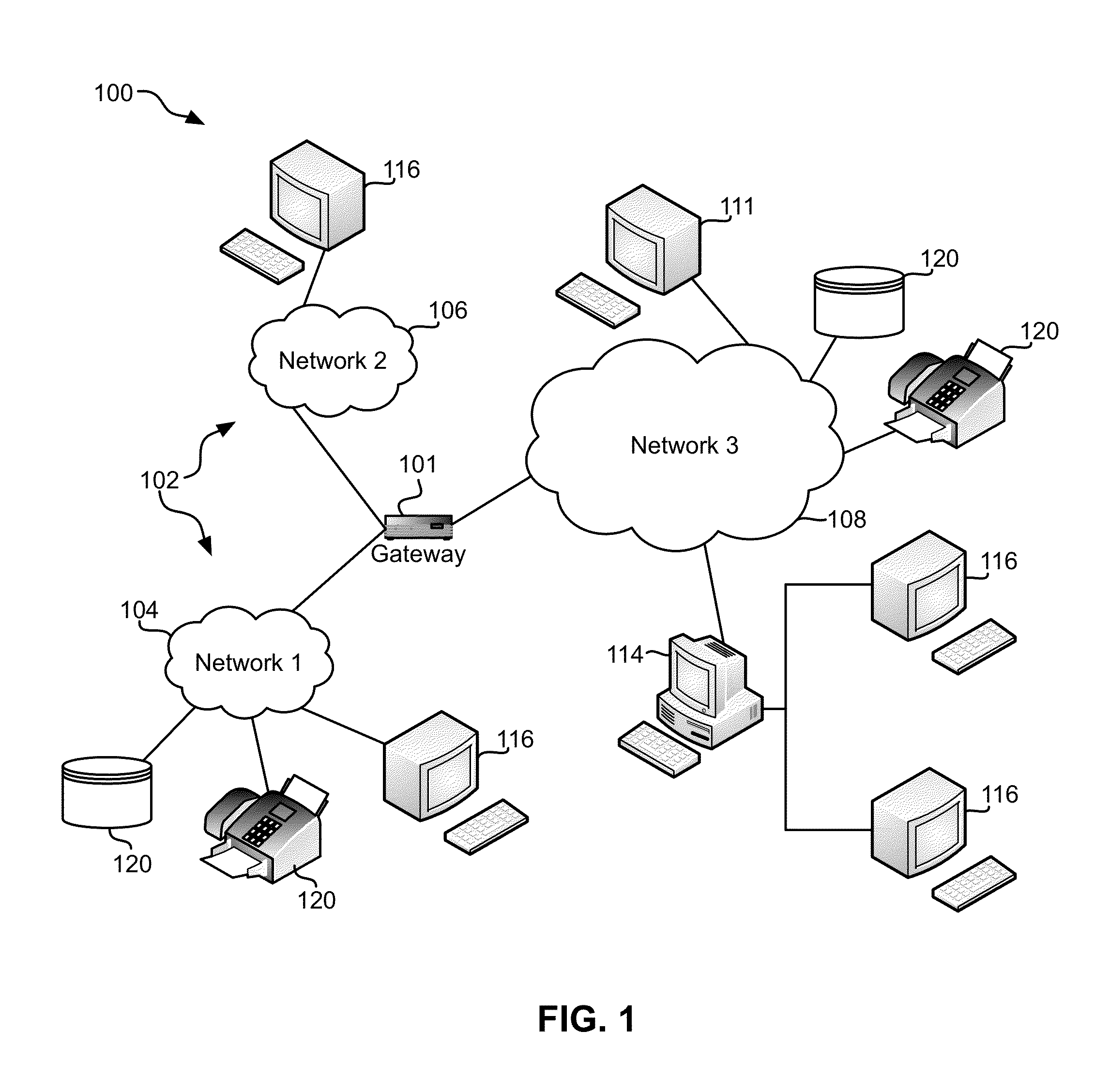

In one embodiment, a system includes a processor and logic integrated with and / or executable by the processor. The logic is adapted to: define a hardware feature policy for one or more hardware components of a system; and enable and / or disable one or more hardware features of one or more of the hardware components based on the hardware feature policy, wherein the hardware feature policy comprises instructions to enable and / or disable access to the one or most hardware features based on one or more criteria selected from a group consisting of: a feature access schedule, a volume feature access group; a job feature access group; and an user feature access group.

Owner:IBM CORP

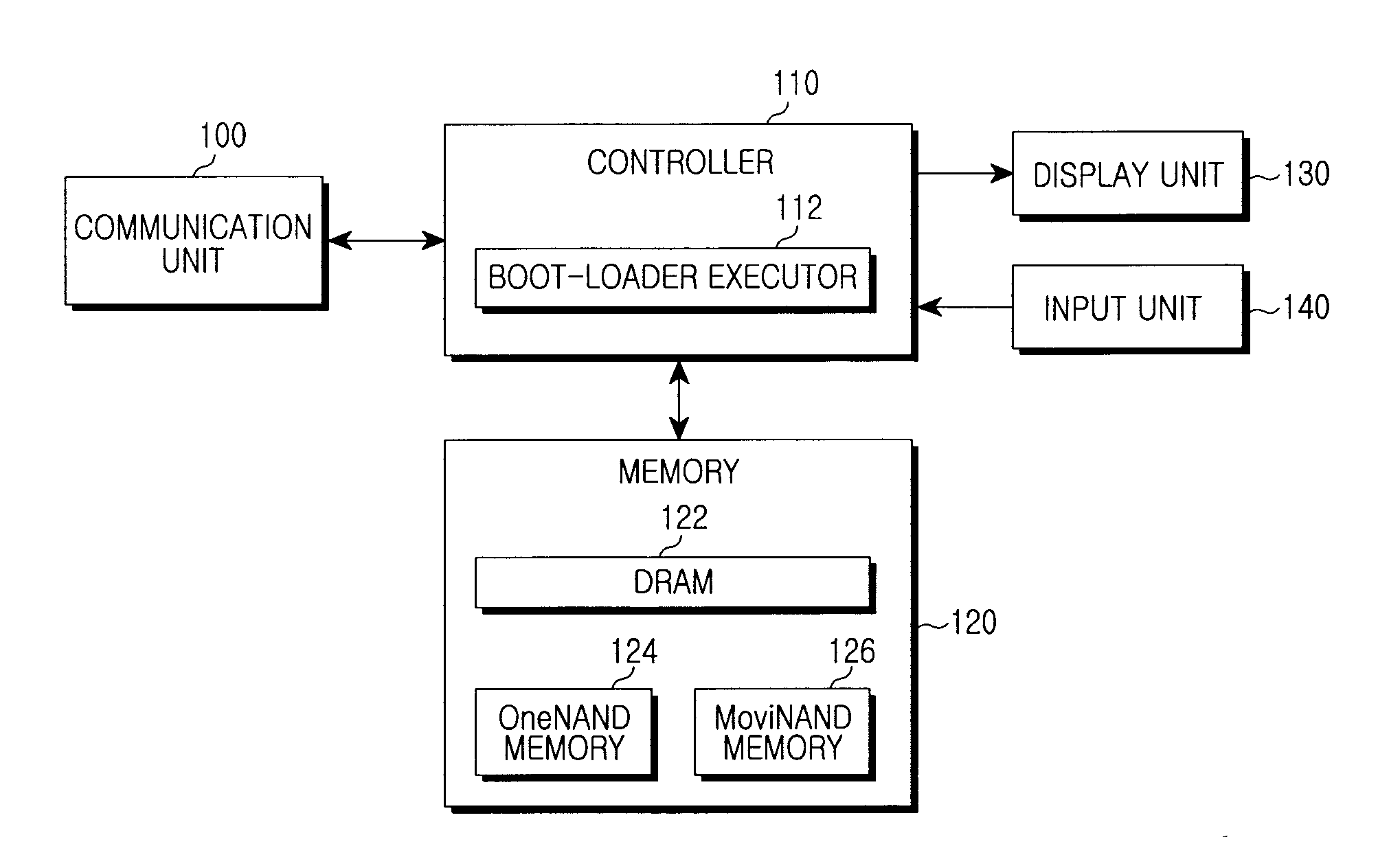

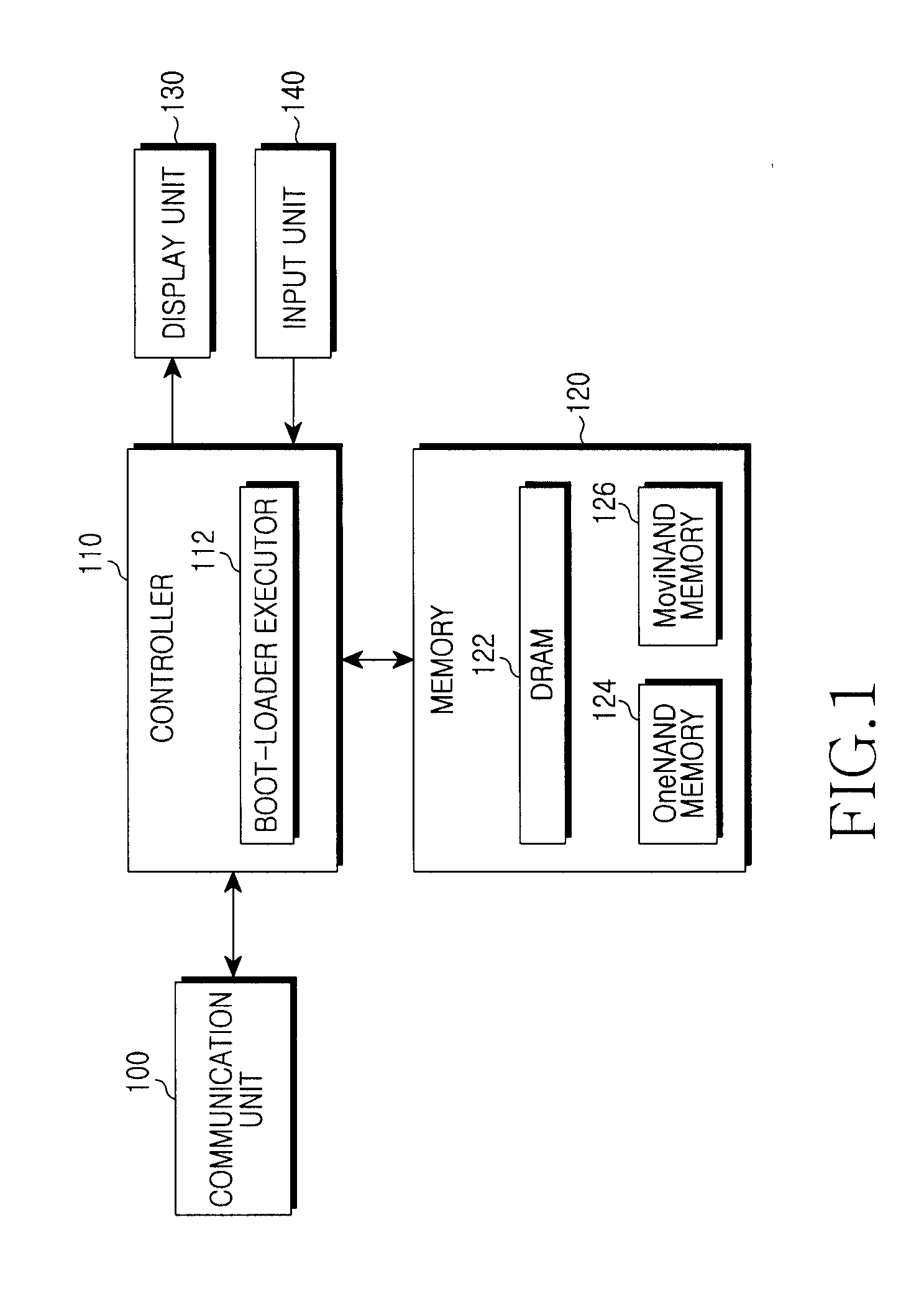

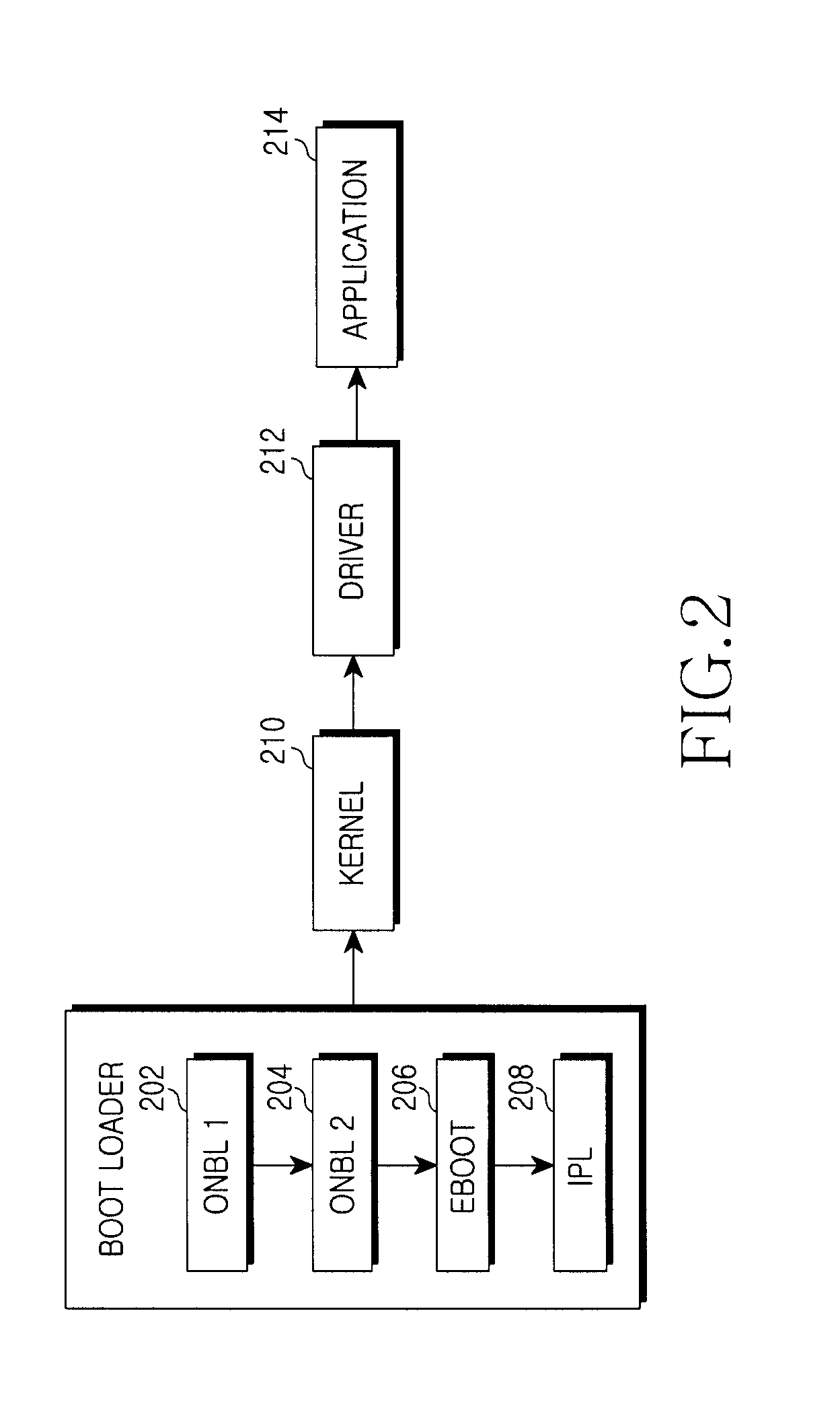

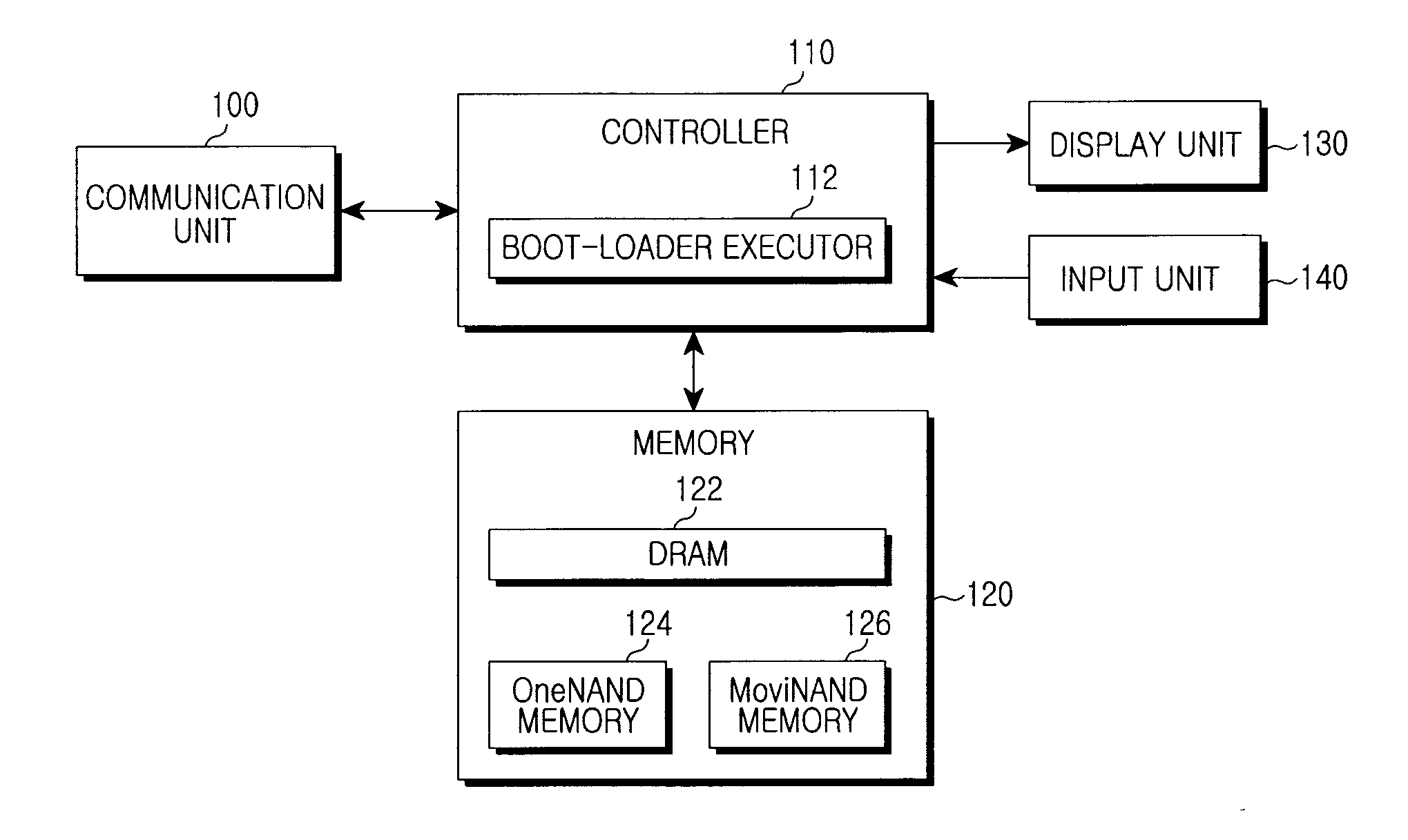

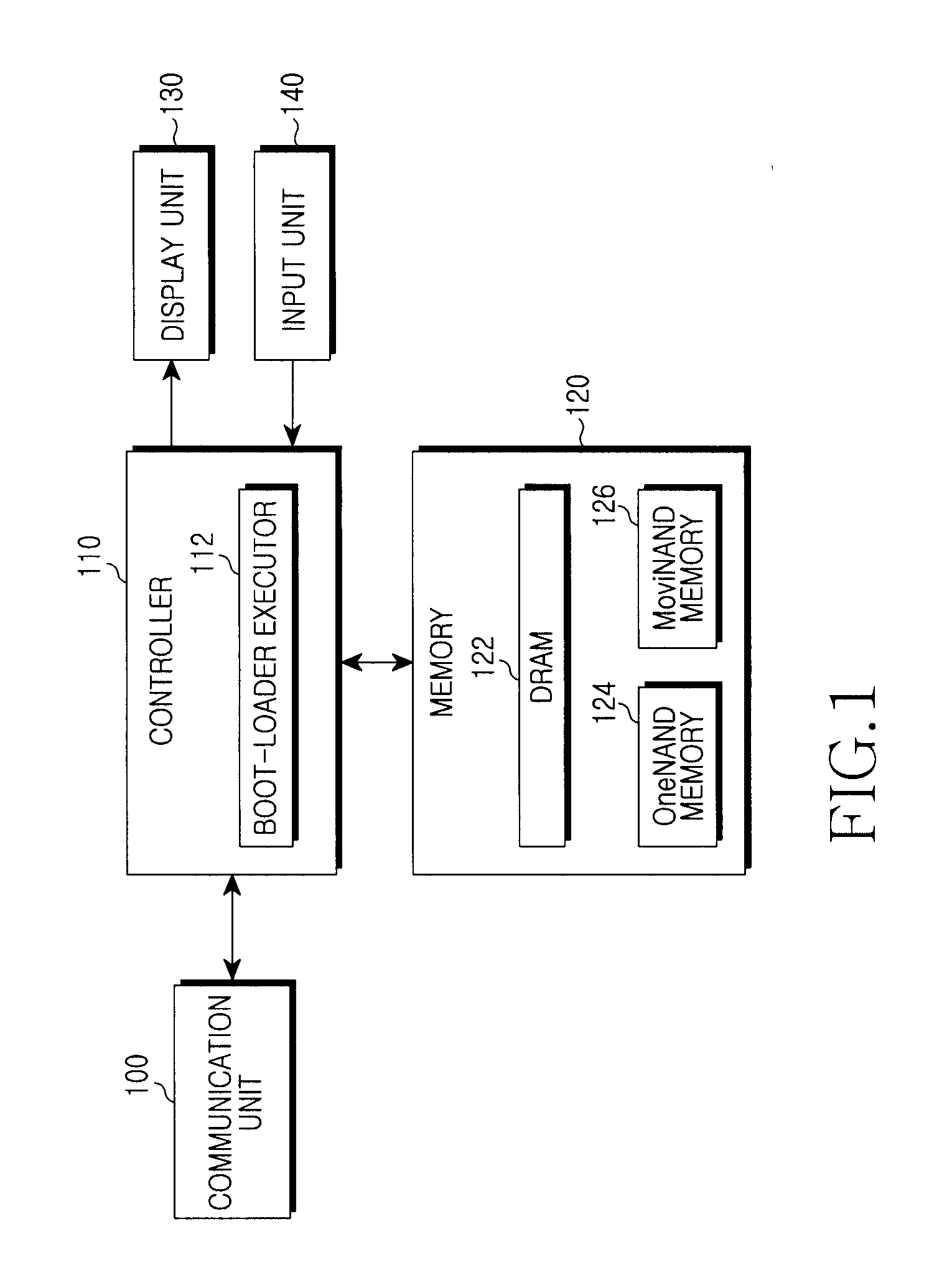

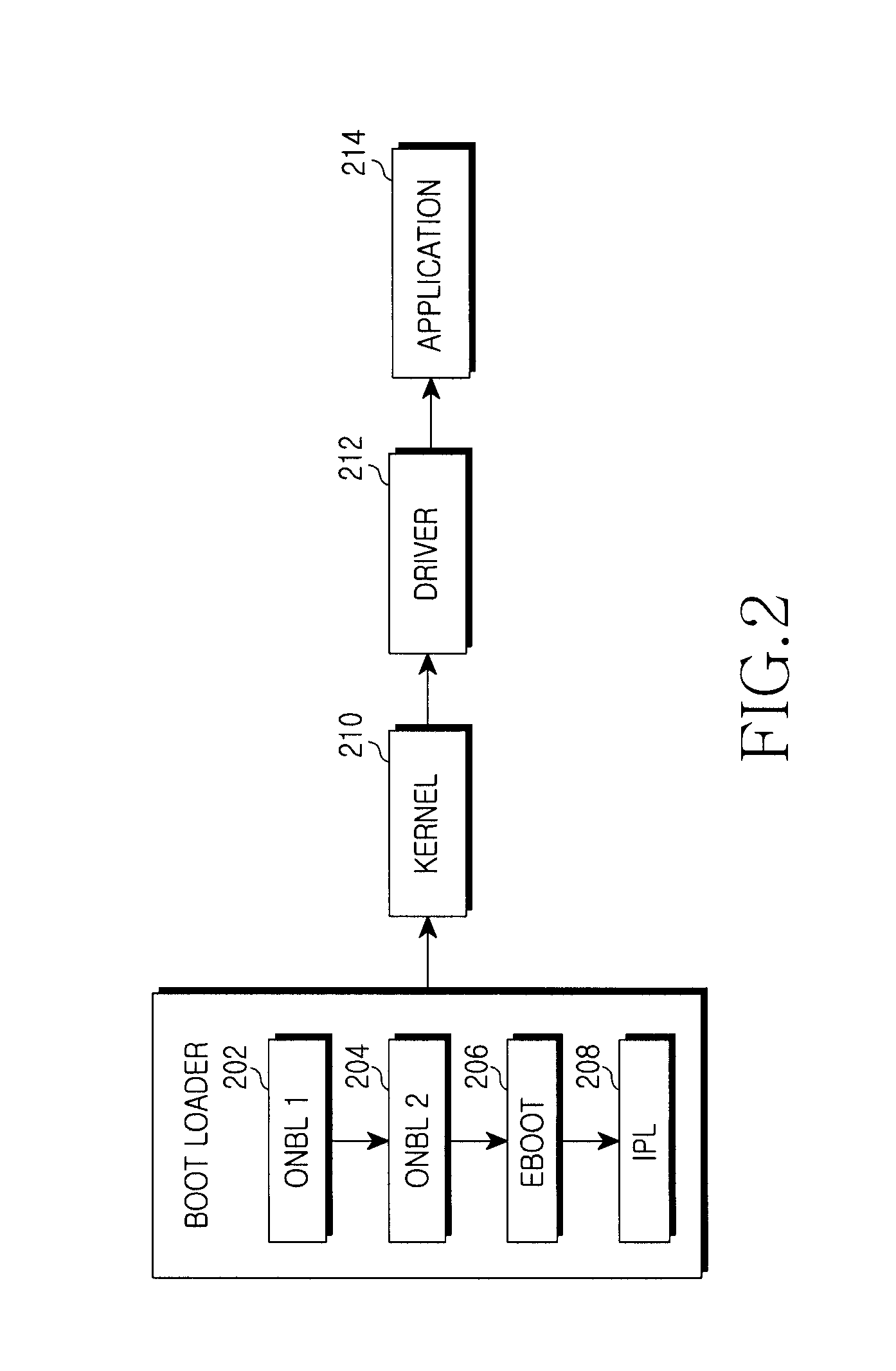

Apparatus and method for downloading contents using an interior mass storage in a portable terminal

ActiveUS20100199081A1Avoid deletionDigital computer detailsData resettingInternal memoryMass storage

A method and apparatus for downloading content to a large-capacity internal memory in a portable terminal are provided. The method includes performing a booting process of the portable terminal at the occurrence of a booting event, examining whether a Universal Serial Bus (USB) port is enabled during the booting process, if the USB port is enabled, receiving data through the USB port before driver loading, and storing the received data into the large-capacity internal memory and performing the booting process.

Owner:SAMSUNG ELECTRONICS CO LTD

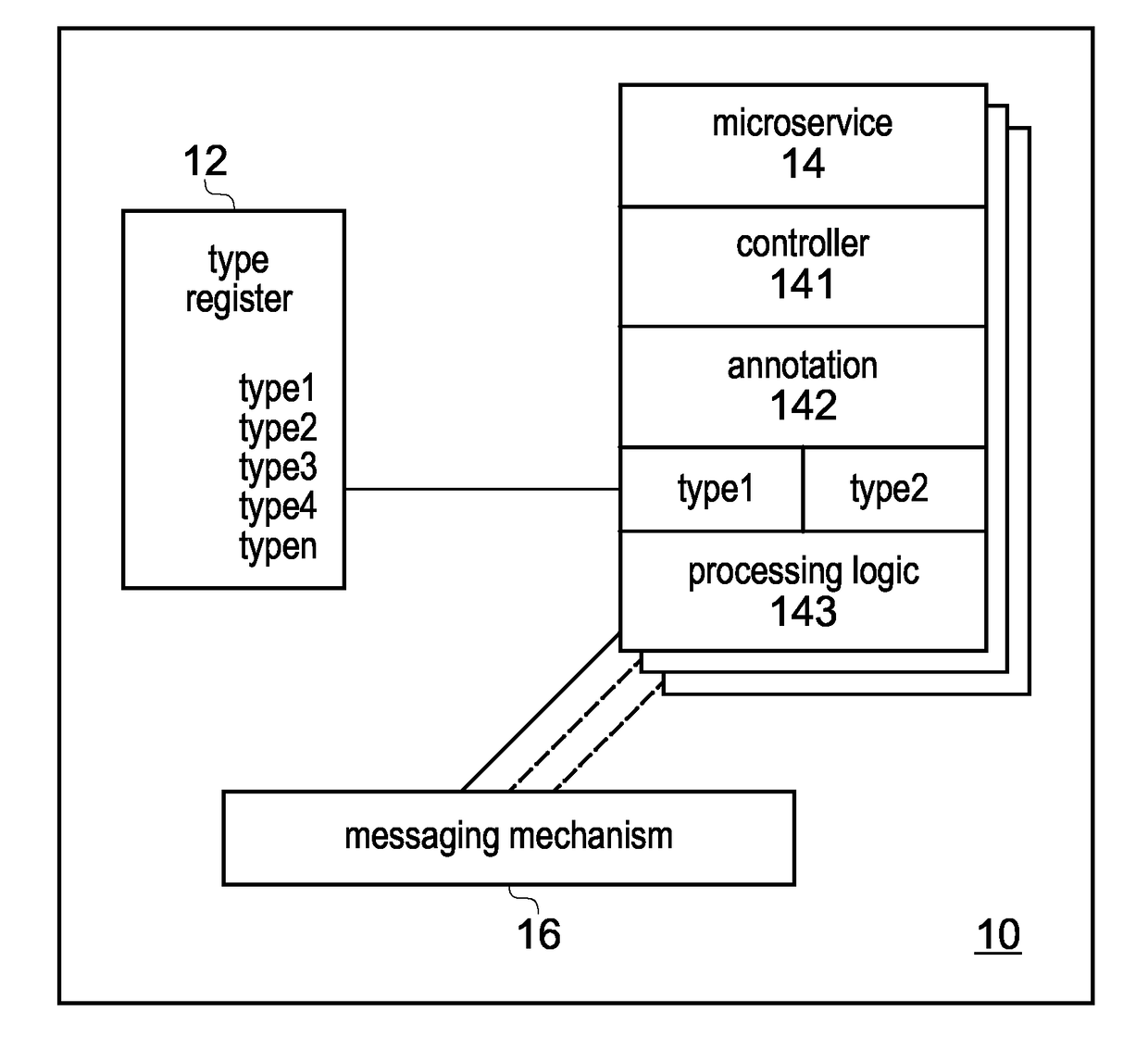

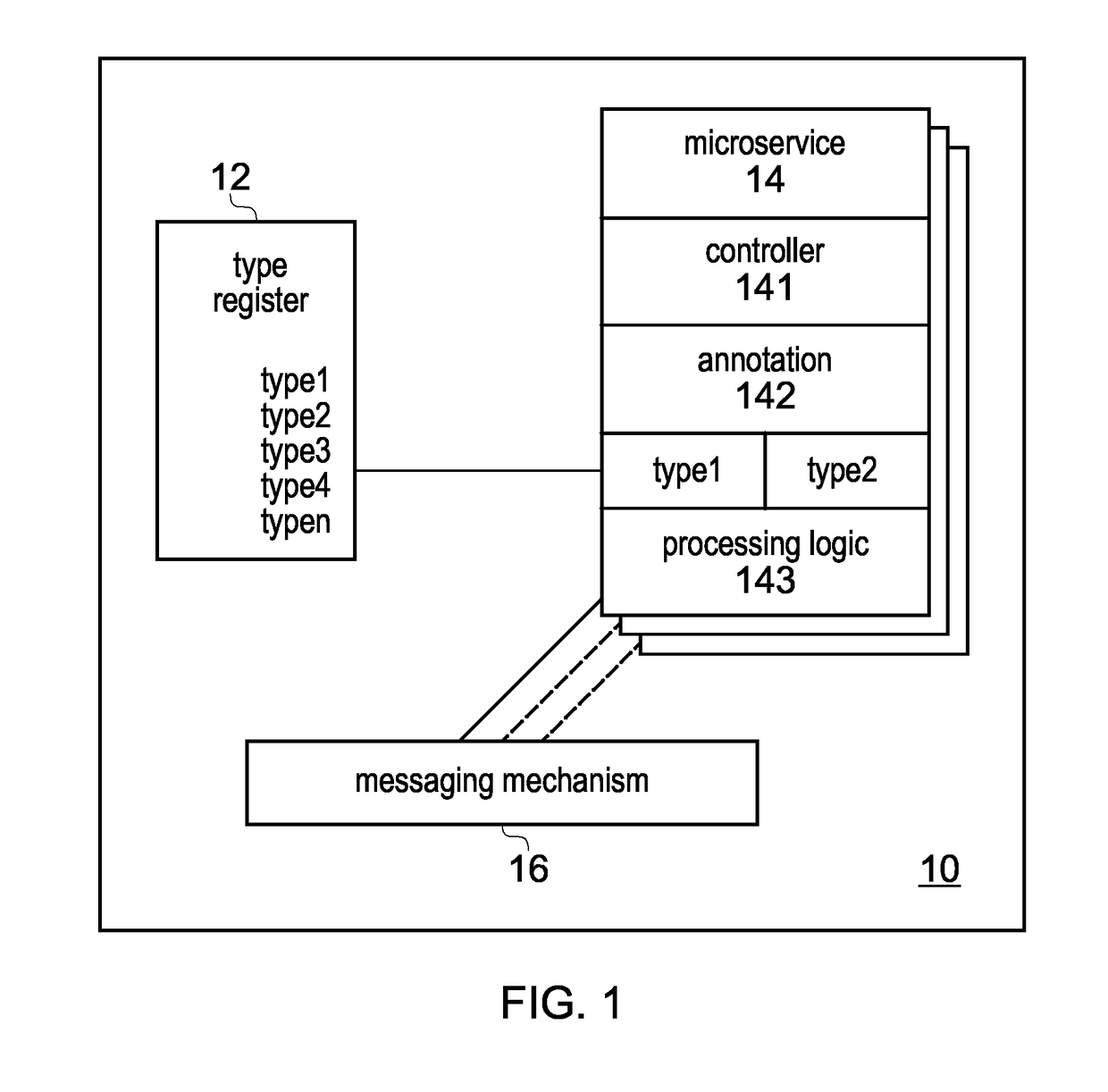

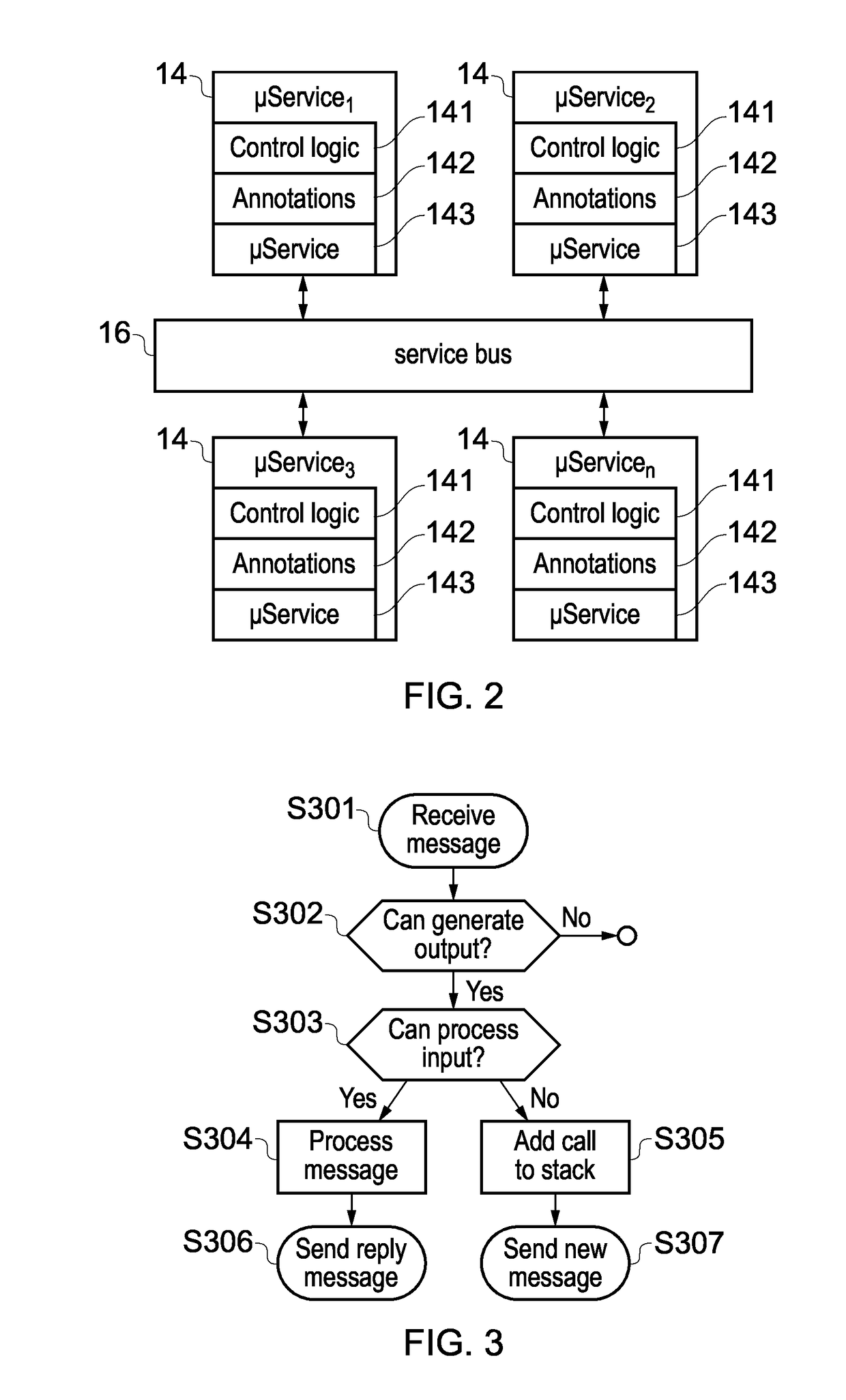

Microservice-based data processing apparatus, method, and program

ActiveUS20180113707A1Accurately interconnectedThe process is simple and fastRegister arrangementsMicroinstruction functionMessage passingAnnotation

A microservice-based data processing apparatus, including: a type register, storing a list of types, a type being a semantic concept expression; and microservices each comprising an annotation of an input type and output types from the list; processing logic transforming input data expressed by the input type into output data expressed by the output types; and a messaging mechanism for inputting data, via a message, to a microservice, the mechanism defining a message format for structuring the messages. The format includes a first field specifying the data being input; and a second field specifying a type, from the list of types, semantically expressing the concept instantiated by the data. Each microservice includes: a controller to receive a message from the mechanism having the format, and to respond by executing the logic when the type specified by the second field matches the input type of the microservice.

Owner:FUJITSU LTD

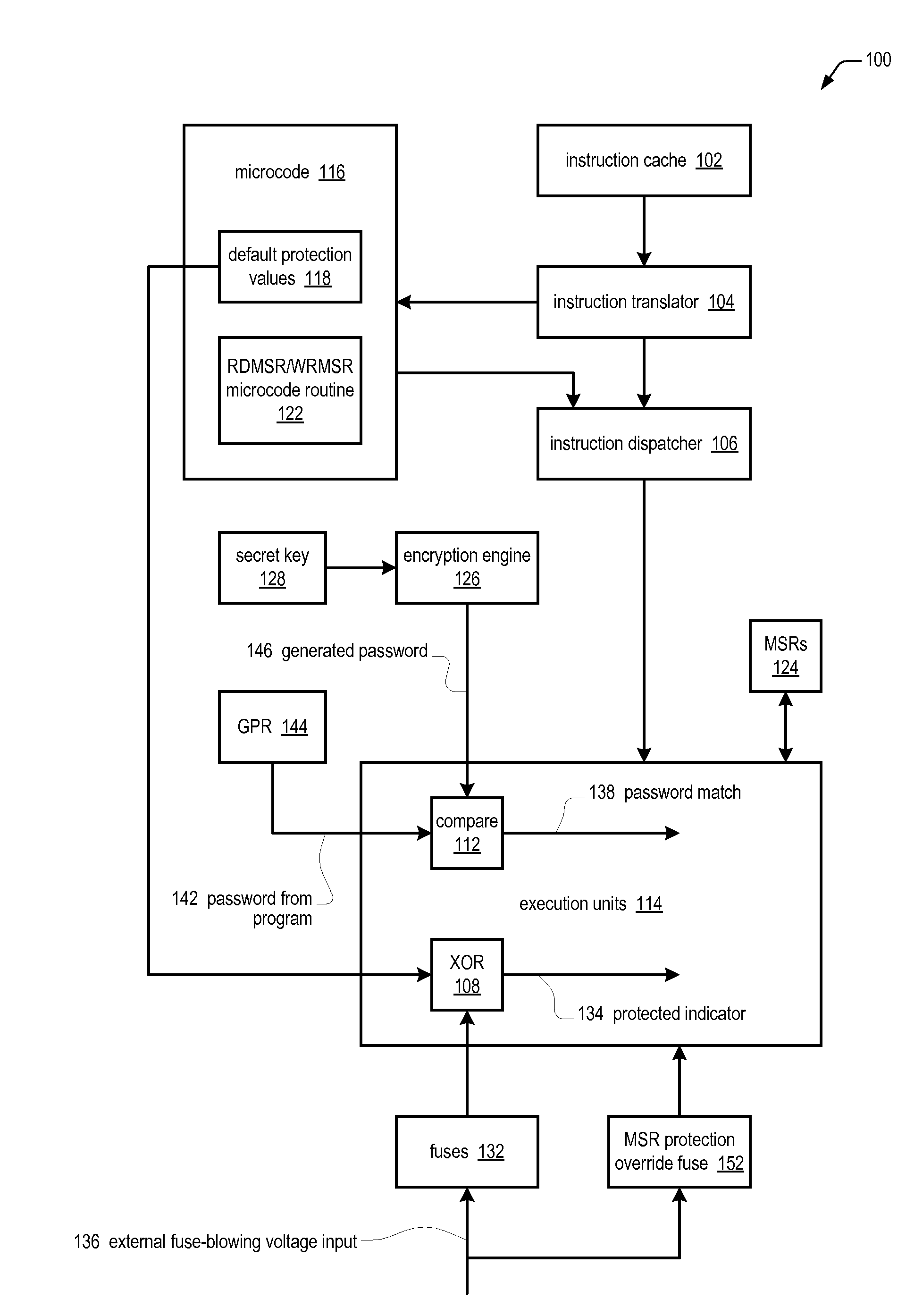

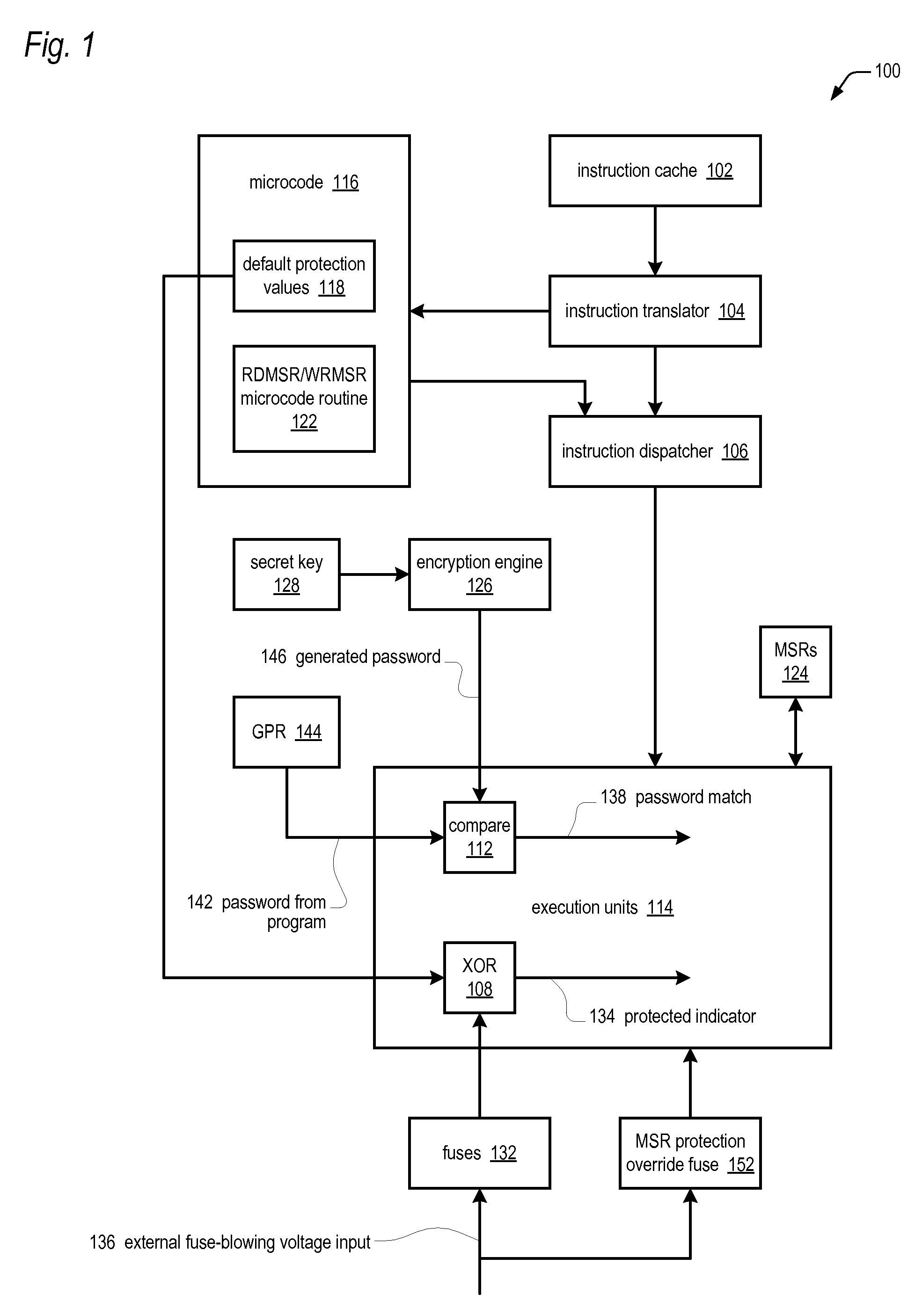

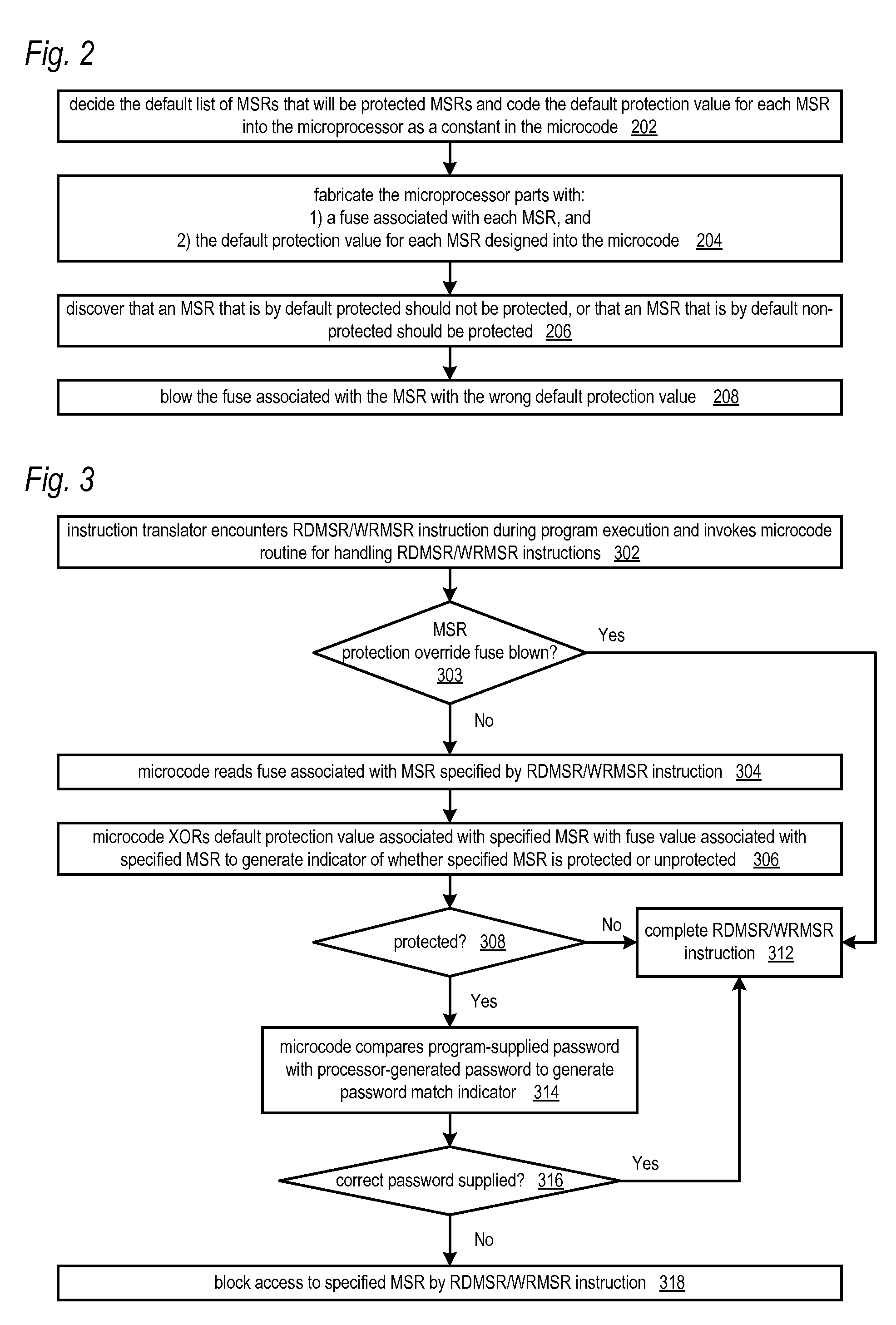

Apparatus and method for updating set of limited access model specific registers in a microprocessor

ActiveUS20100064117A1Save potentially large amount of revenueShorten the timeUser identity/authority verificationUnauthorized memory use protectionLimited accessOperating system

A microprocessor having model specific registers (MSRs) includes, for each of the MSRs, an associated default value that indicates whether the MSR is protected or non-protected and an associated fuse that, if blown, toggles the associated default value from protected to non-protected or non-protected to protected. In one embodiment, microcode that does the following in response to the microprocessor encountering an instruction that accesses a specified MSR: determines whether the fuse associated with the specified MSR is blown or unblown, uses the default value associated with the MSR as an indicator of whether the MSR is protected if the associated fuse is unblown; toggles the associated default value to generate the indicator if the associated fuse is blown; protects access to the MSR if the indicator indicates the MSR is protected; and refrains from protecting access to the MSR if the indicator indicates the MSR is non-protected.

Owner:VIA TECH INC

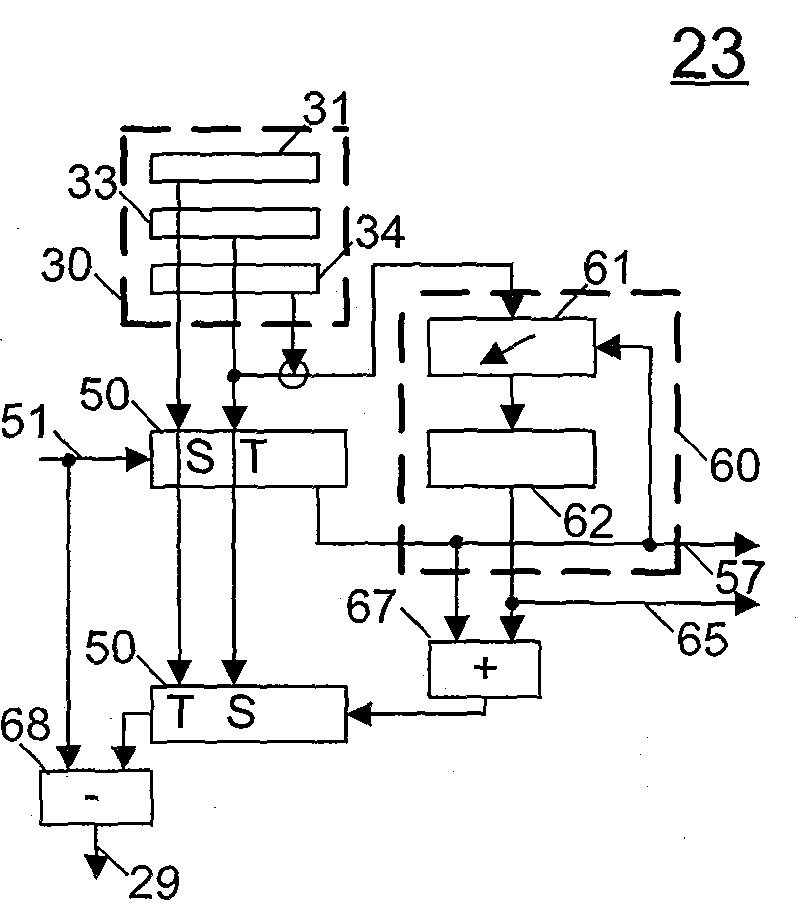

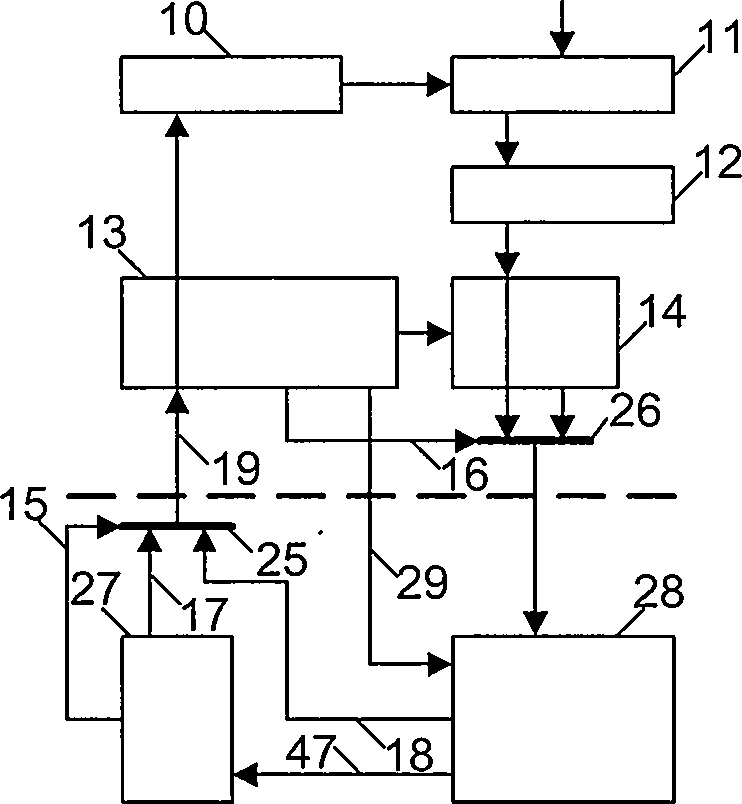

Multi-issue processor system and method

InactiveCN105988774AAvoid or adequately hide cache missesImprove execution efficiencyMemory architecture accessing/allocationInstruction analysisHigh speed memoryParallel computing

The invention provides a multi-issue processor system and method. When the multi-issue processor system and method is applied to the field of processors, before a processor core executes an instruction, the instruction is filled into a high speed memory which can be directly accessed by the processor core to achieve an extremely high cache hit rate. According to the technical scheme of the invention, for the multi-issue processor system which needs to carry out instruction transformation, the repeated transformation of an instruction address can be avoided, and the performance of the multi-issue processor is improved.

Owner:SHANGHAI XINHAO MICROELECTRONICS

Microprocessor with booth multiplication

ActiveUS20190227769A1Register arrangementsDigital data processing detailsProcessor registerAlgorithm

A microprocessor with Booth multiplication, in which several acquisition registers are used. In a first word length, a first acquisition register stores an unsigned ending acquisition of a first multiplier number carried in multiplier number supply data, and a third acquisition register stores a starting acquisition of a second multiplier number carried in the multiplier number supply data. In a second word length that is longer than the first word length, a fourth acquisition register stores a middle acquisition of a third multiplier number carried in the multiplier number supply data. A partial product selection circuit is required for selection of a partial product, to get the partial product from Booth multiplication based on the third acquisition register (corresponding to the first word length) or based on the fourth acquisition register (corresponding to the second word length).

Owner:VIA ALLIANCE SEMICON CO LTD

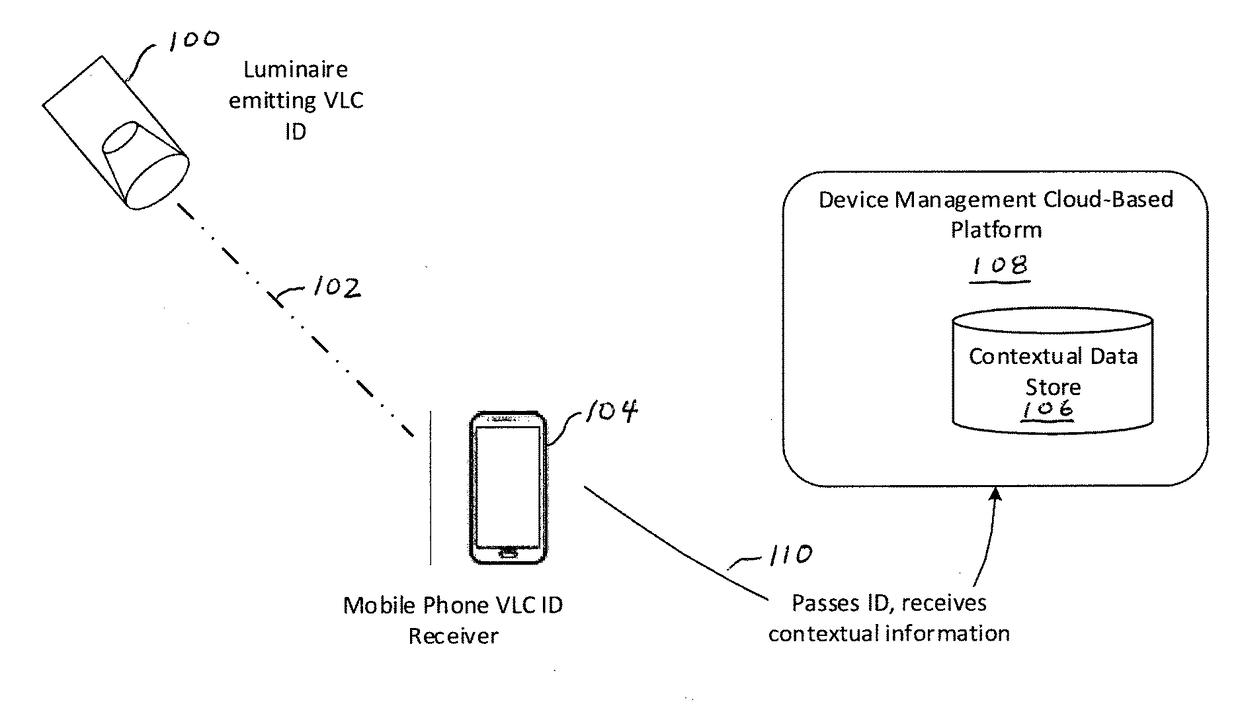

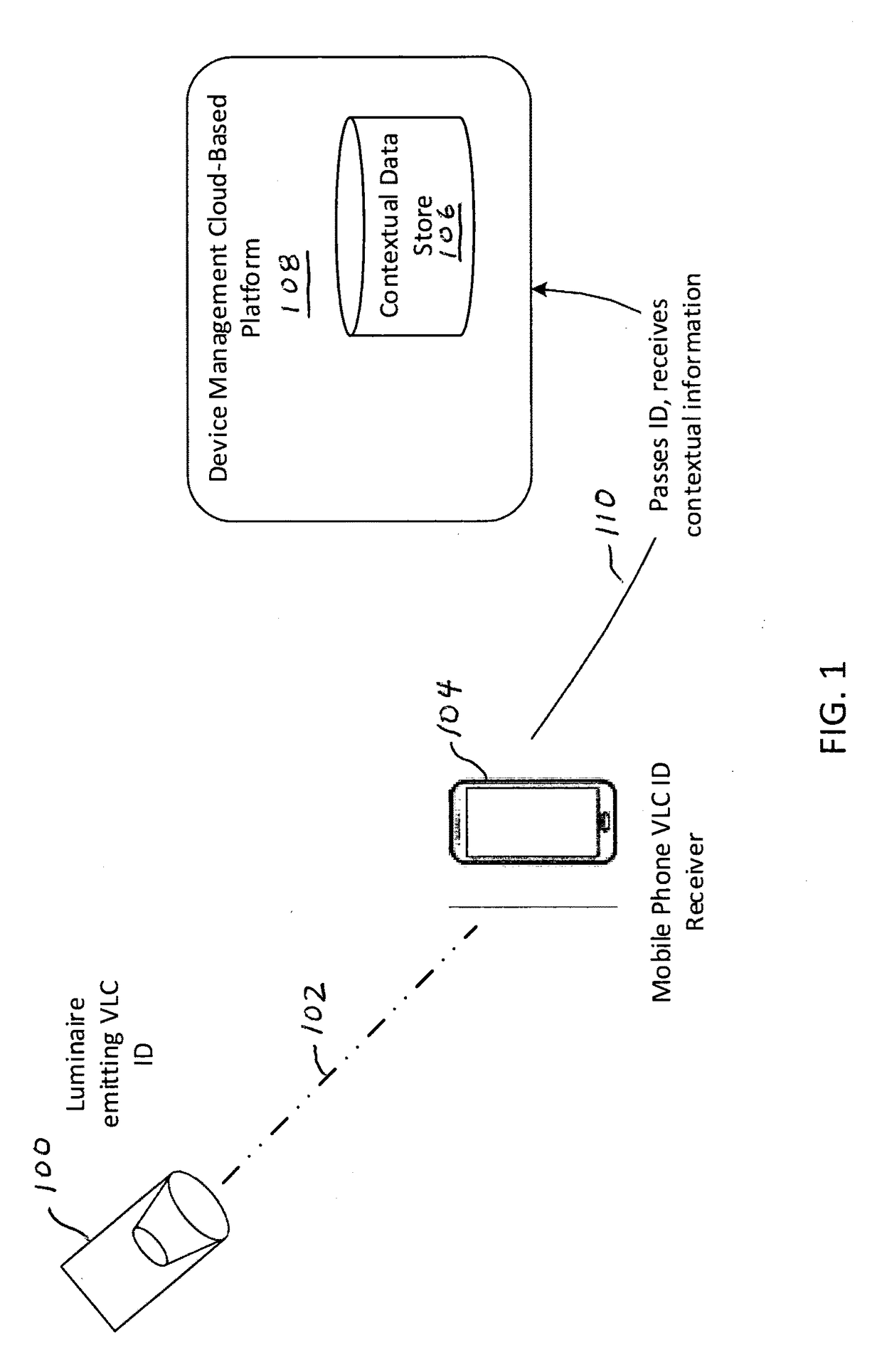

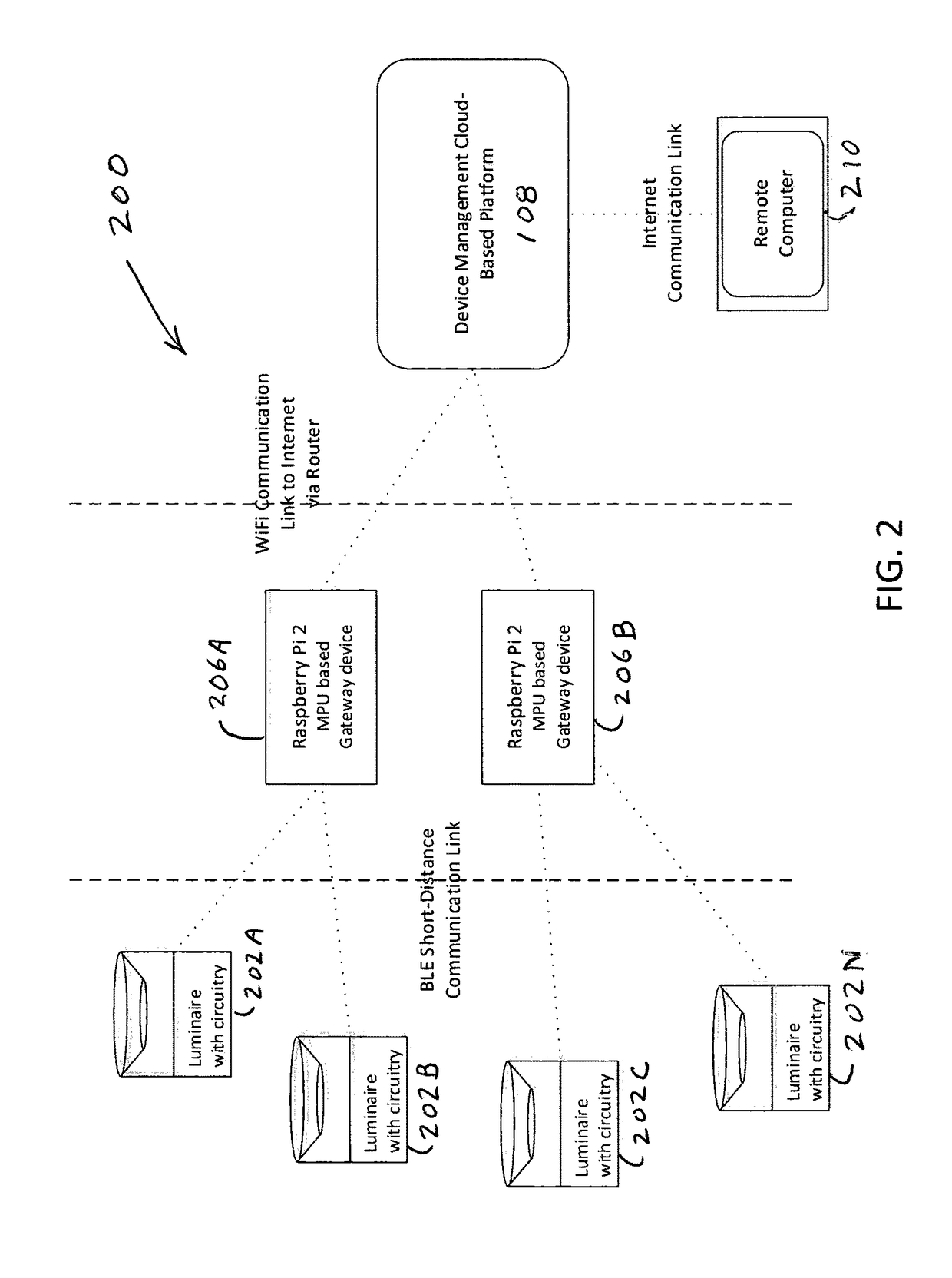

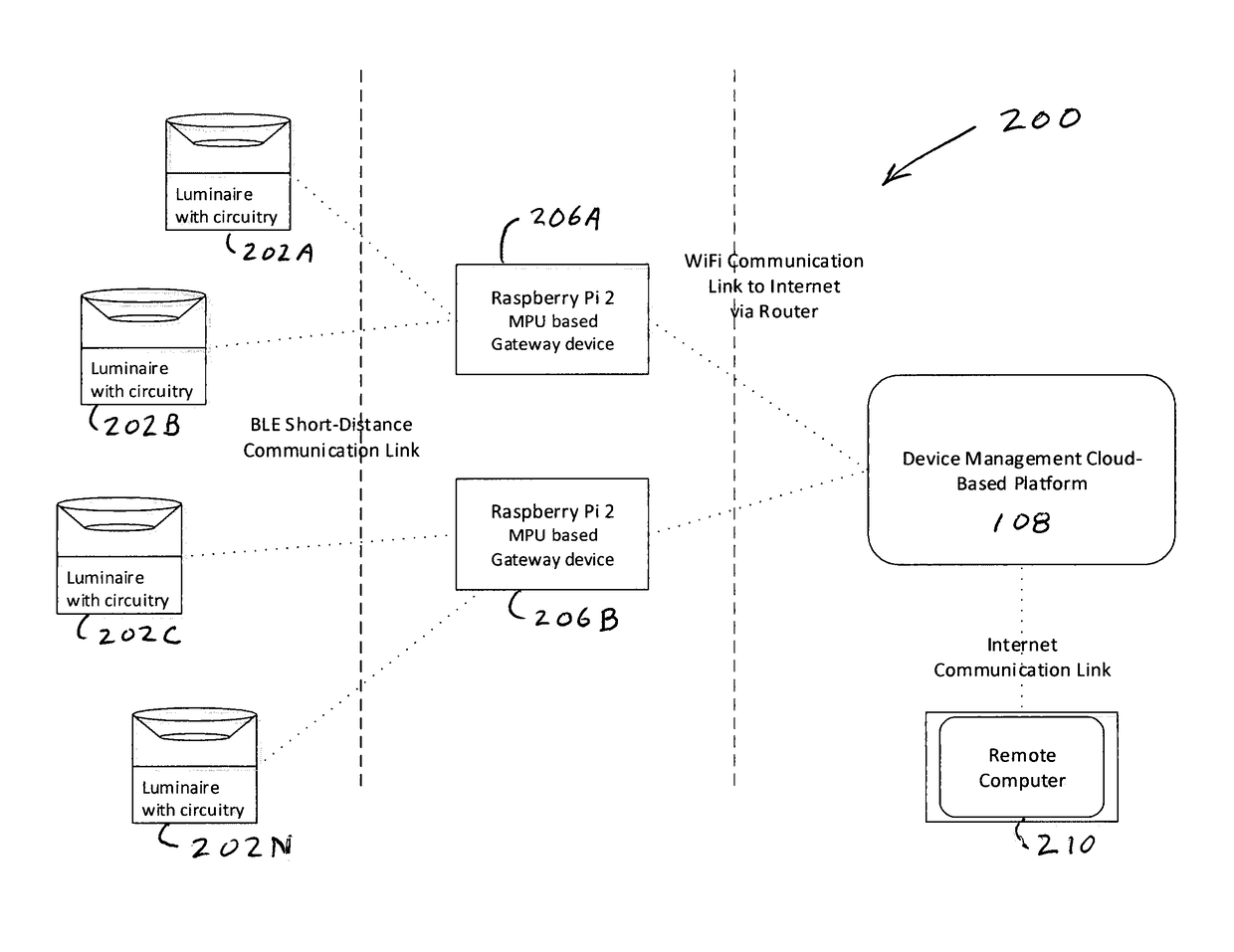

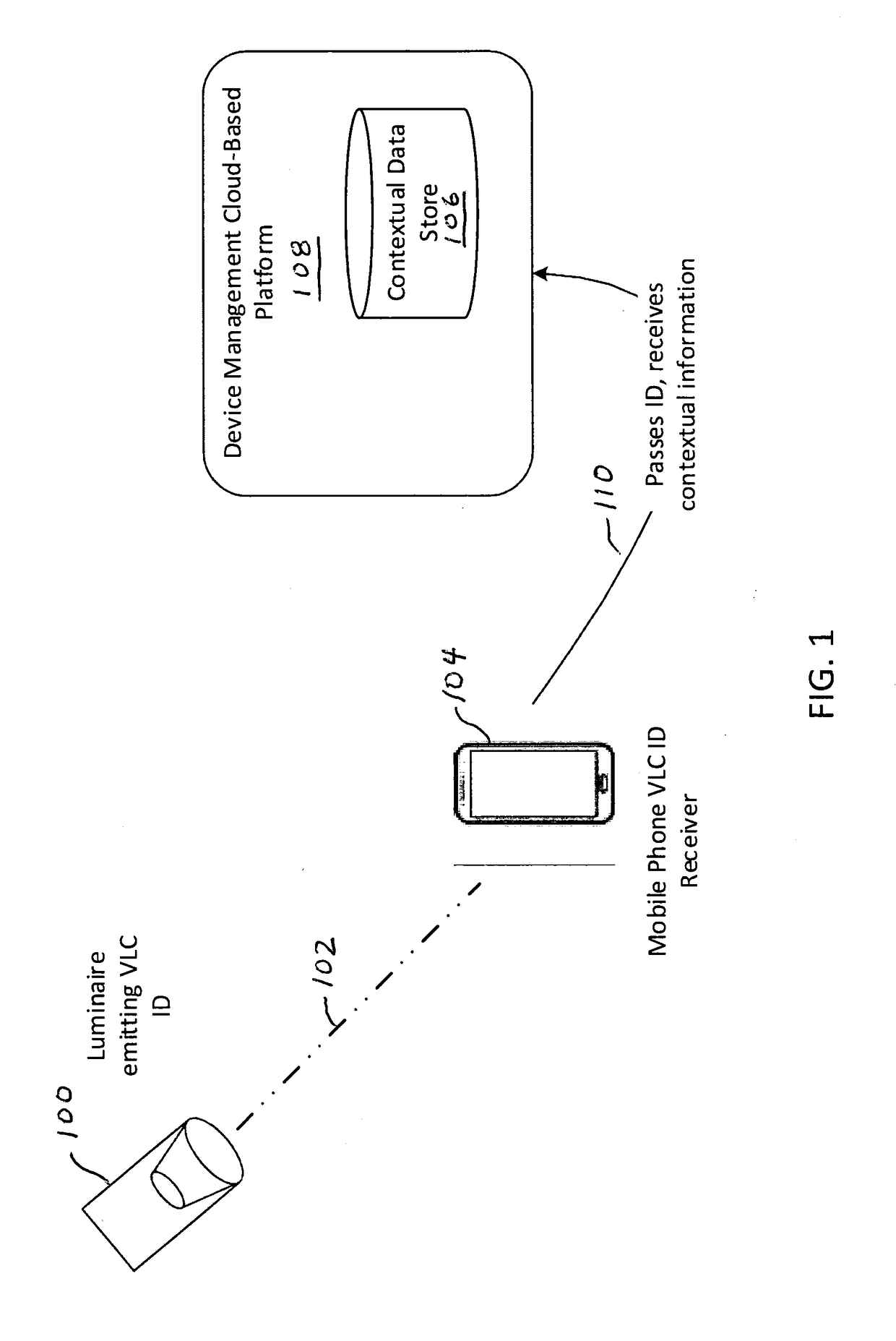

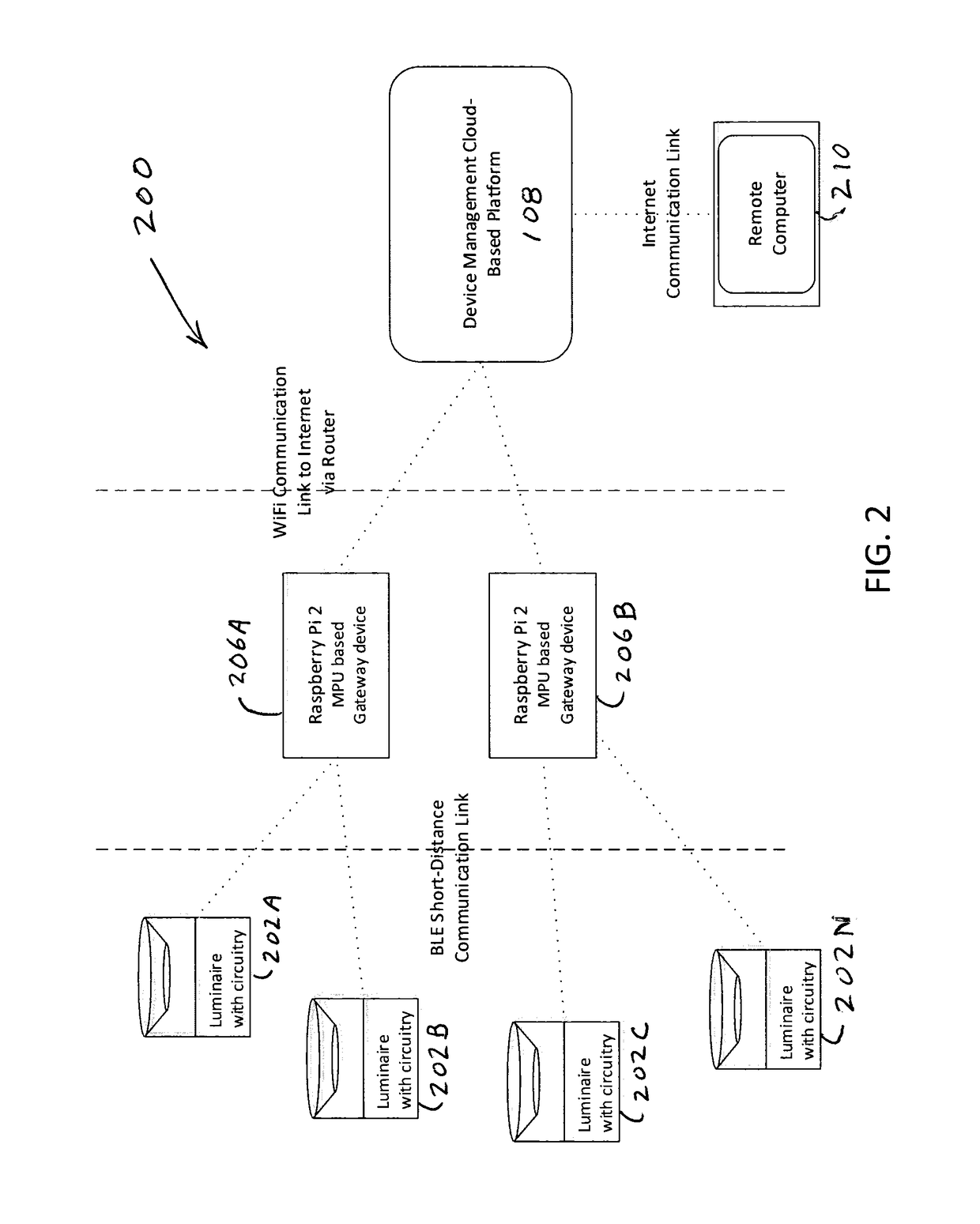

Remote controlled LED based id emitter and deployment, and application of same to multi-factor authentication

InactiveUS20170339561A1Reduced receivable bandwidthReduce software complexityRandom number generatorsTransmission systemsLight equipmentRemote control

An apparatus includes a luminaire; power input for the luminaire; a modulation circuit for modulating the power input so that light output includes an identifier of the luminaire; and a programmable memory for storing at least one of the identifier of the luminaire and a modulation scheme for modulation of the luminaire to place a signal on the light. A method for modulating light includes storing in programmable memory an identifier for the luminaire, the identifier being used to modulate the light, and / or a modulation scheme for modulation of the luminaire; and changing content of programmable memory to change the identifier and / or the modulation scheme. A method of efficiently deploying the luminaires and identifying their locations to a network is disclosed. A method of multi-factor authentication using authentication data transmitted by modulating the light emitted by a luminaire is also disclosed.

Owner:BASIC6

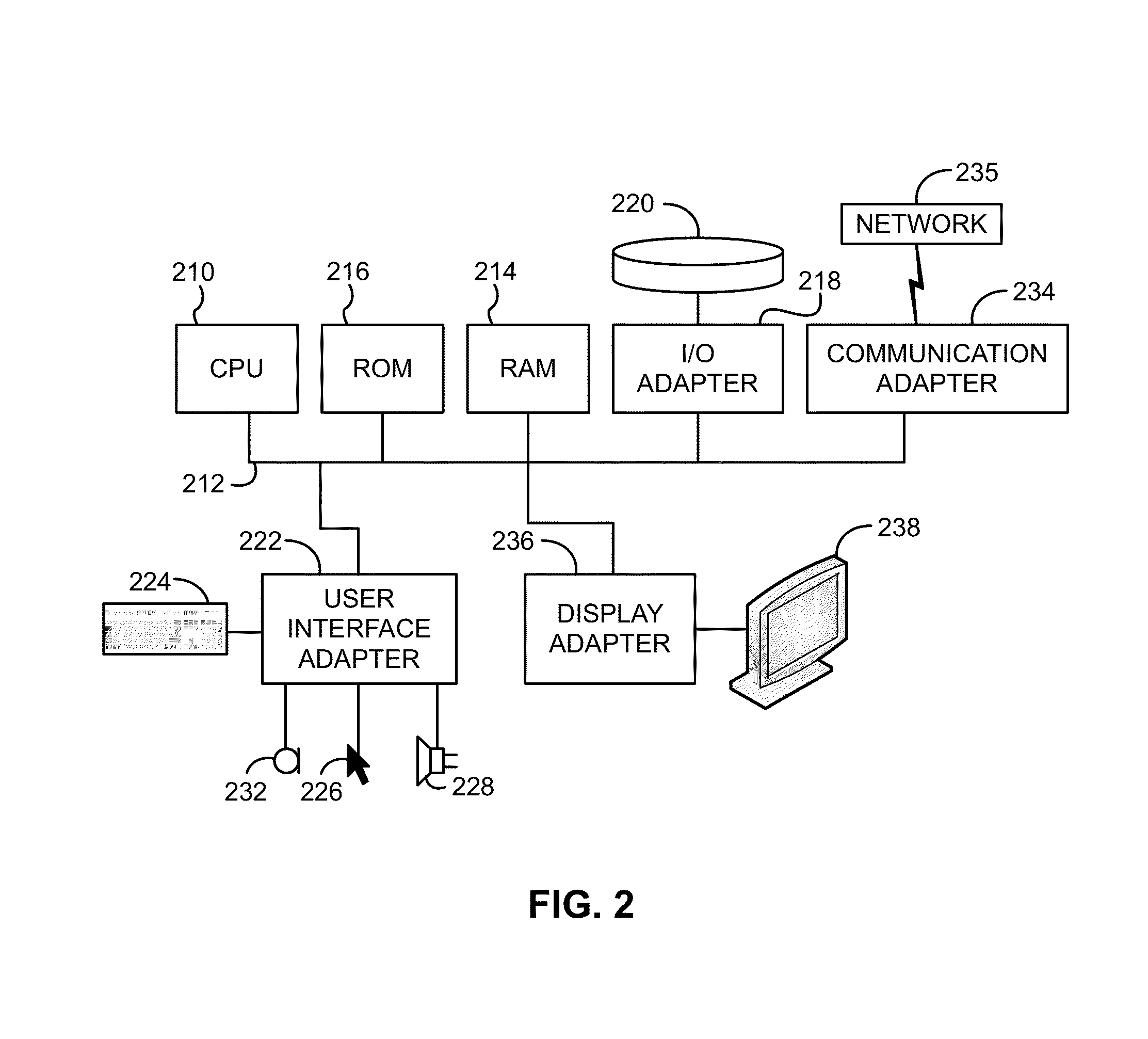

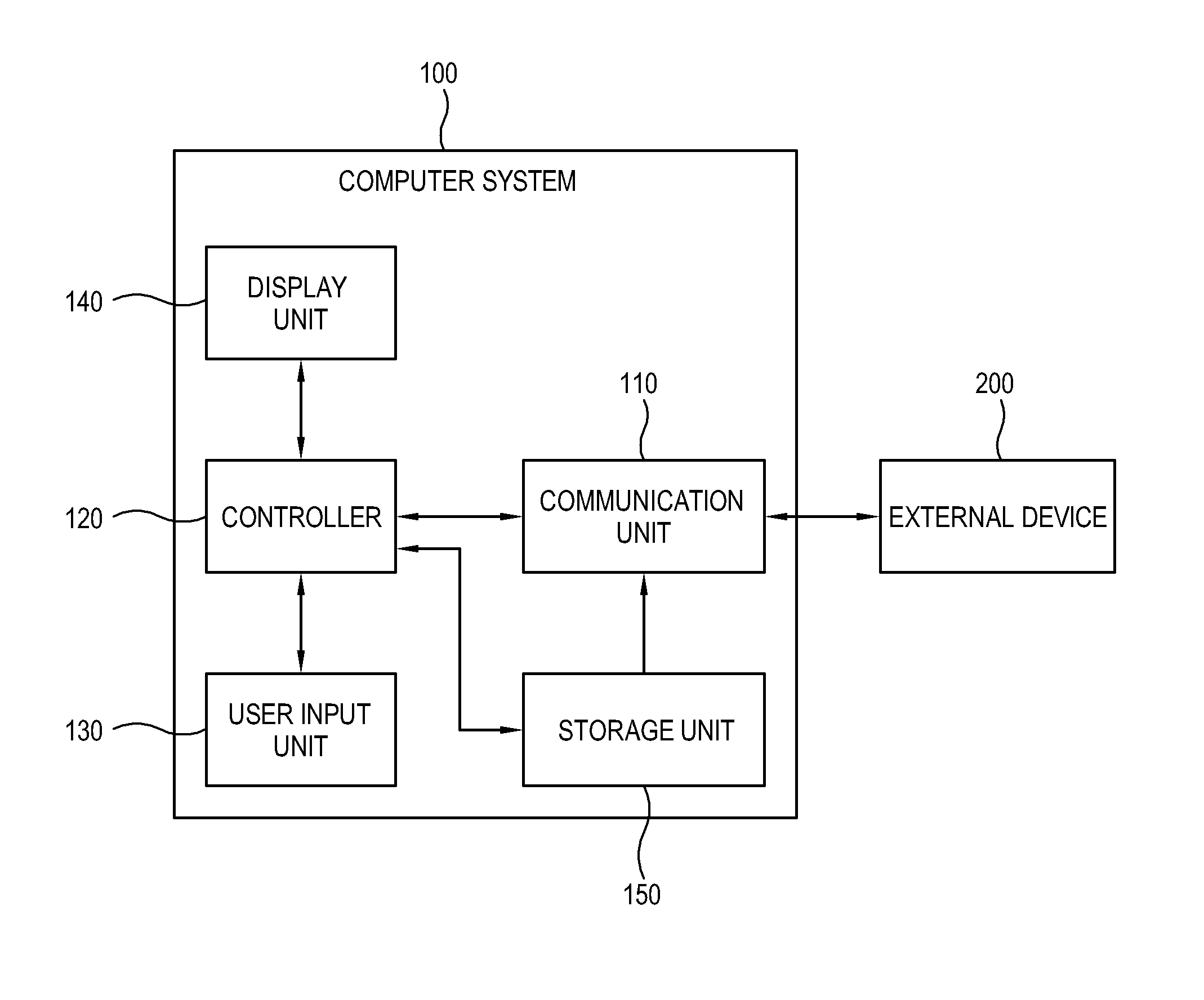

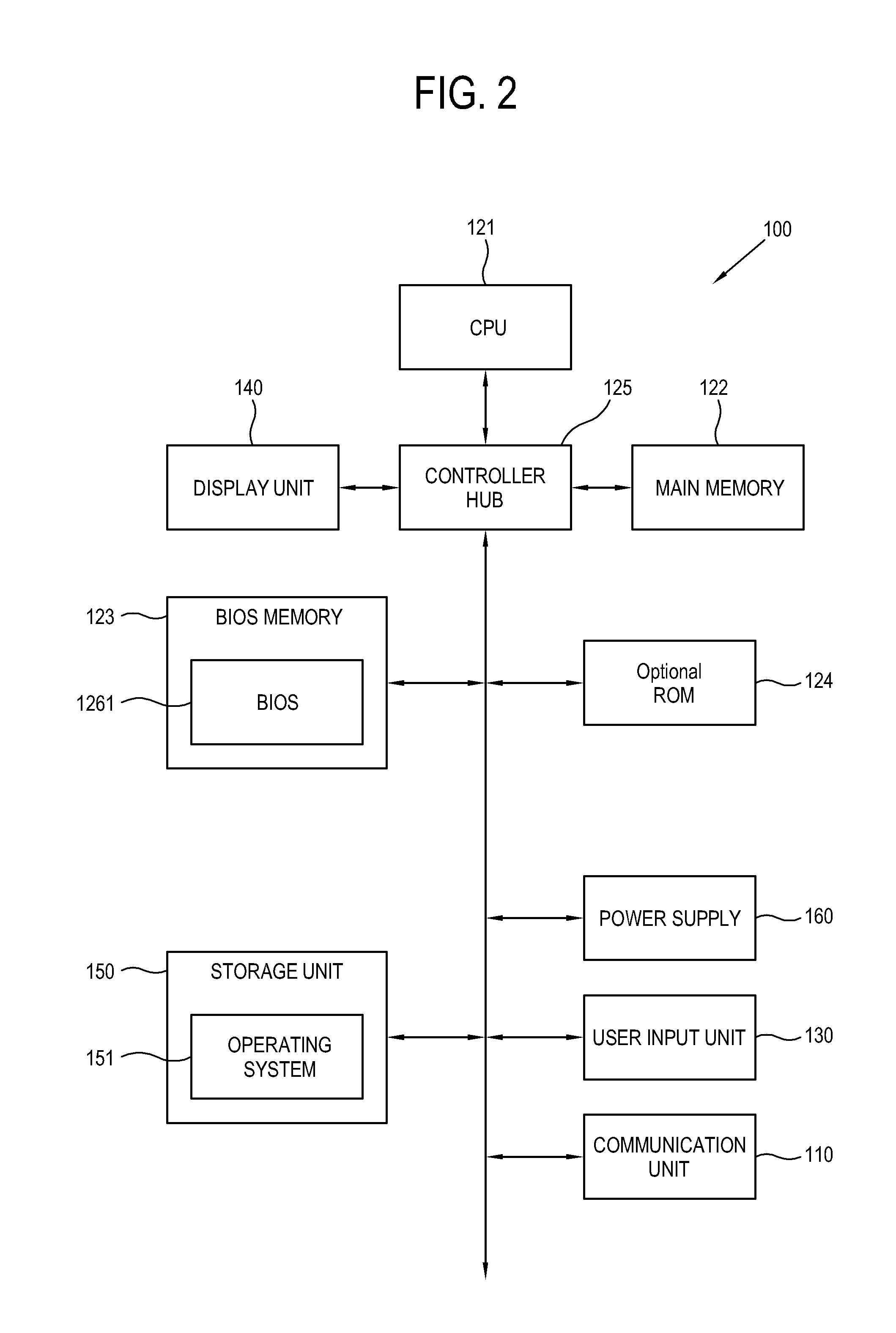

Computer system and method capable of remotely restoring operating system

A computer system and a method for remotely restoring, upgrading, or booting an operating system (O.S). A communication unit communicates with an external device in which a restoring image of the operating system is stored. A user's input request for initialization, causes a controller to perform an initialization according to a power-on input, including checking whether or not a request for restoring the O.S. has been received from a user prior to starting a boot of the operating system. If a request for restoring the operating system is received, the restoring image stored in the external device is accessed through the communication unit to restore the operating system installed in the computer system.

Owner:SAMSUNG ELECTRONICS CO LTD

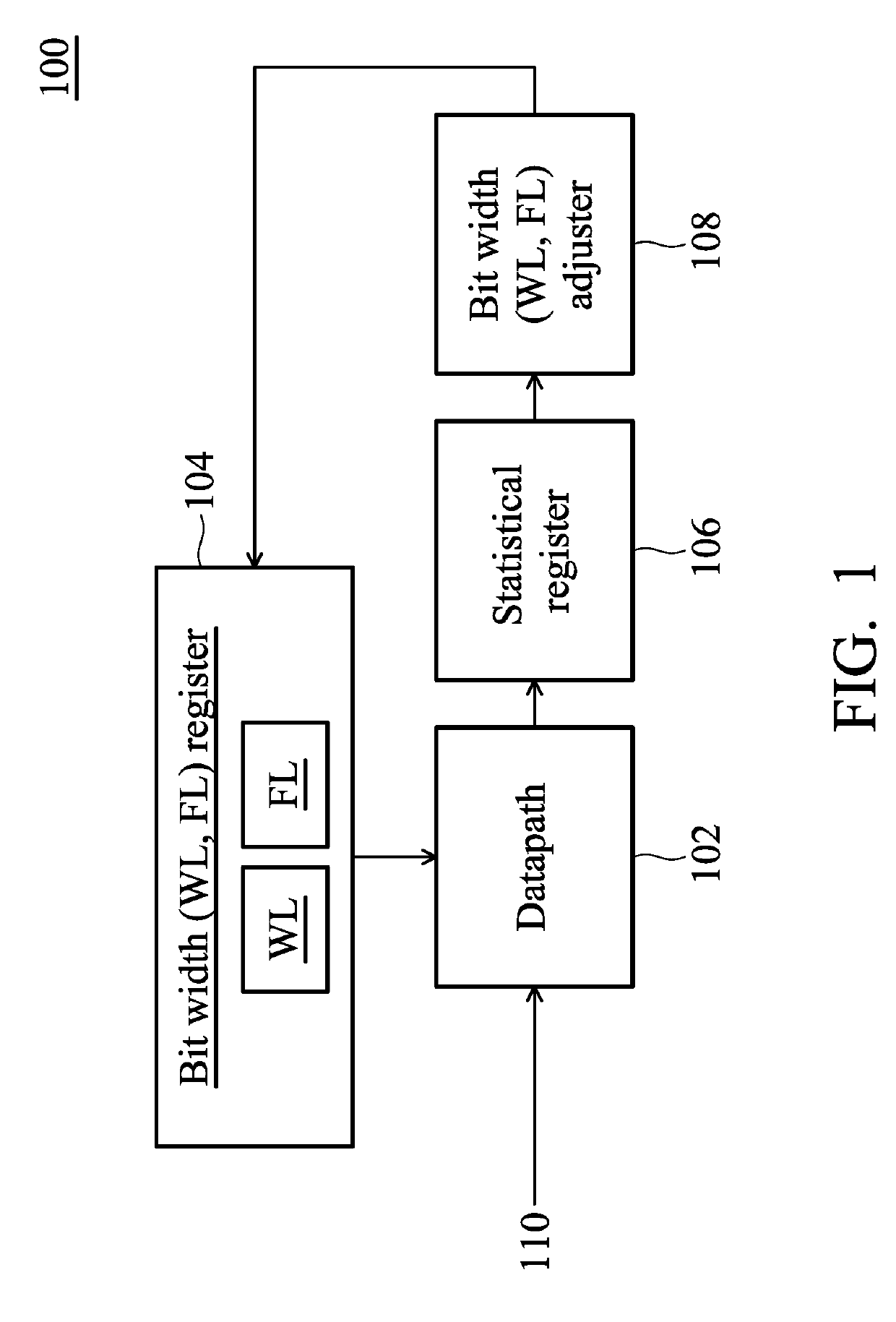

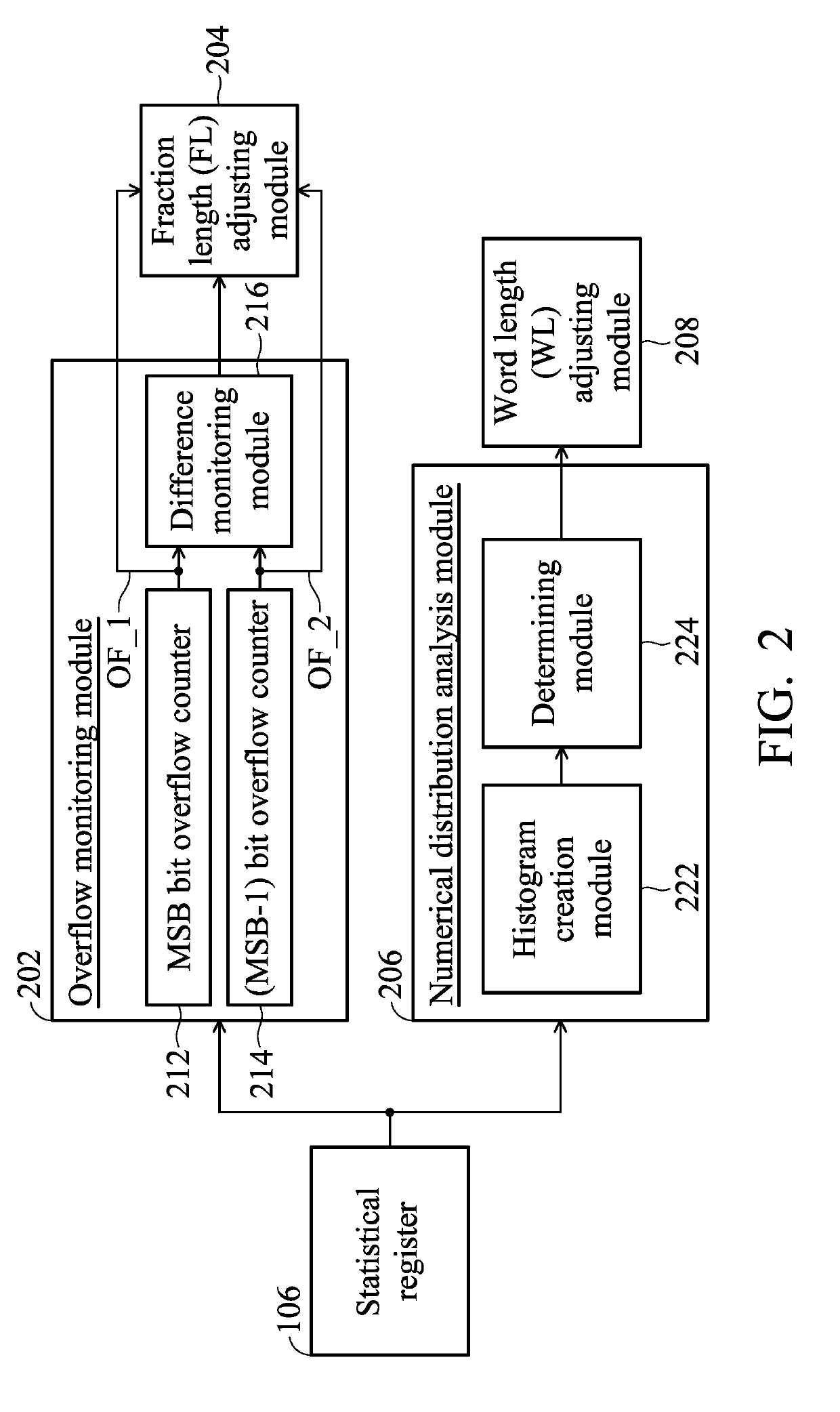

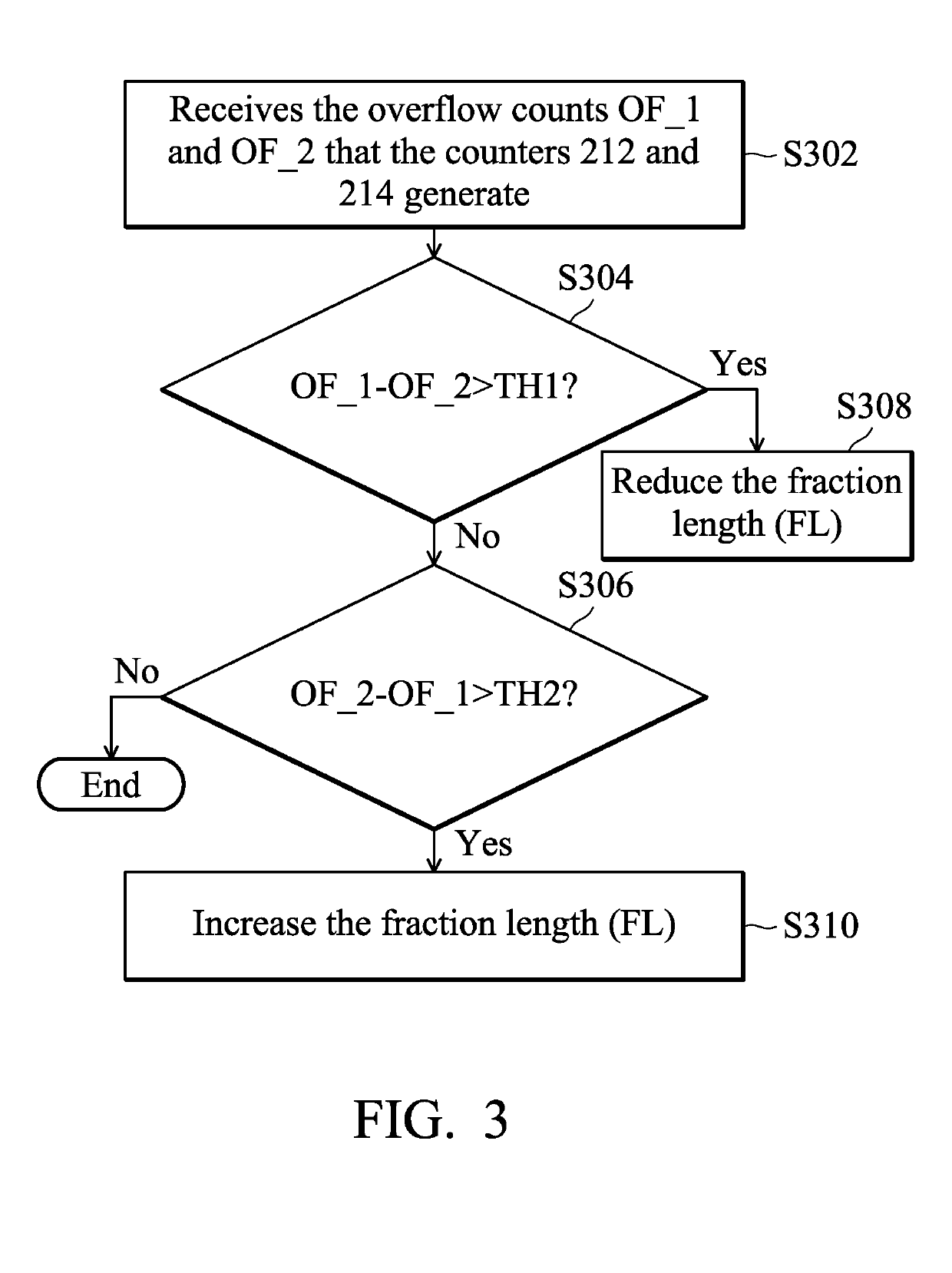

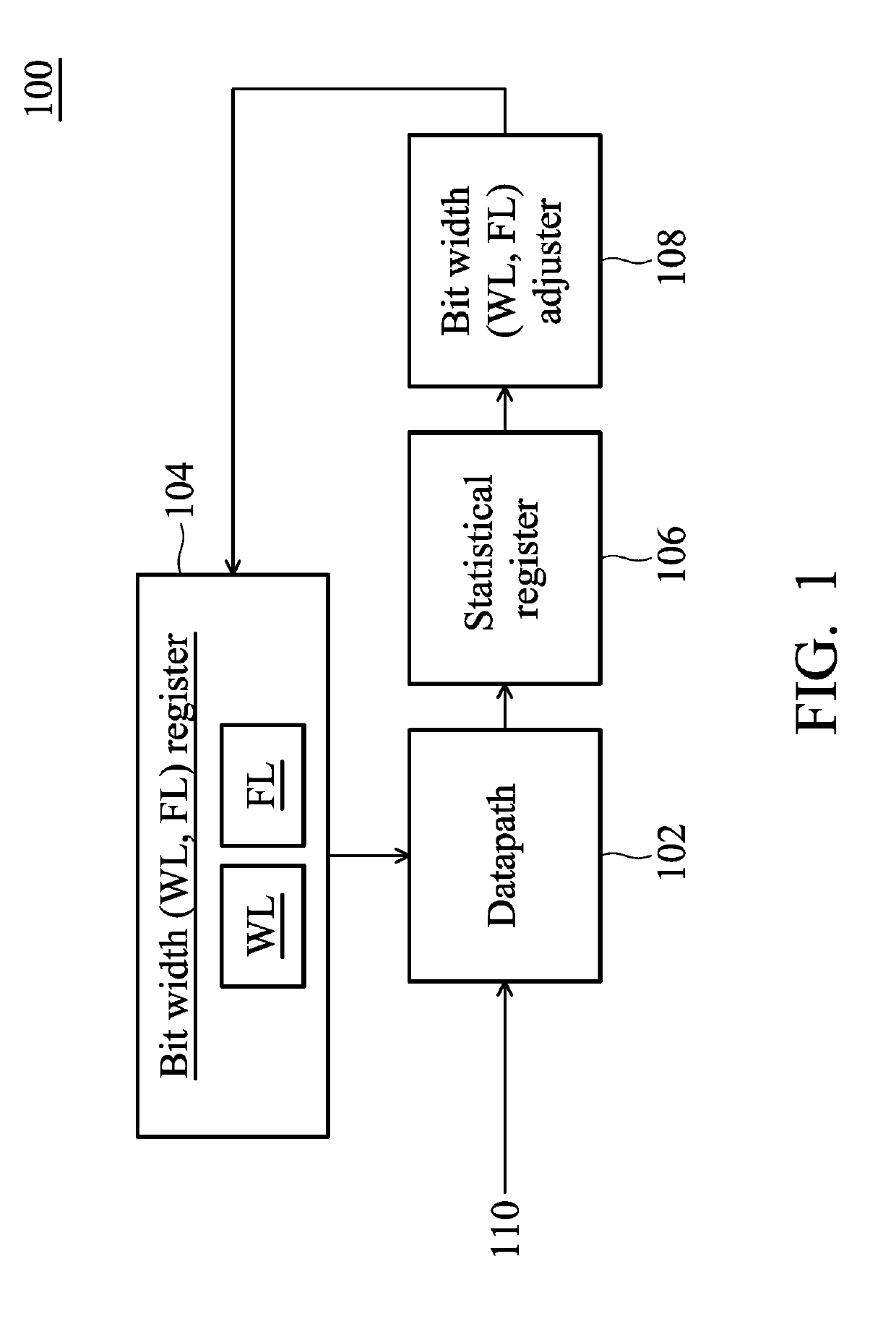

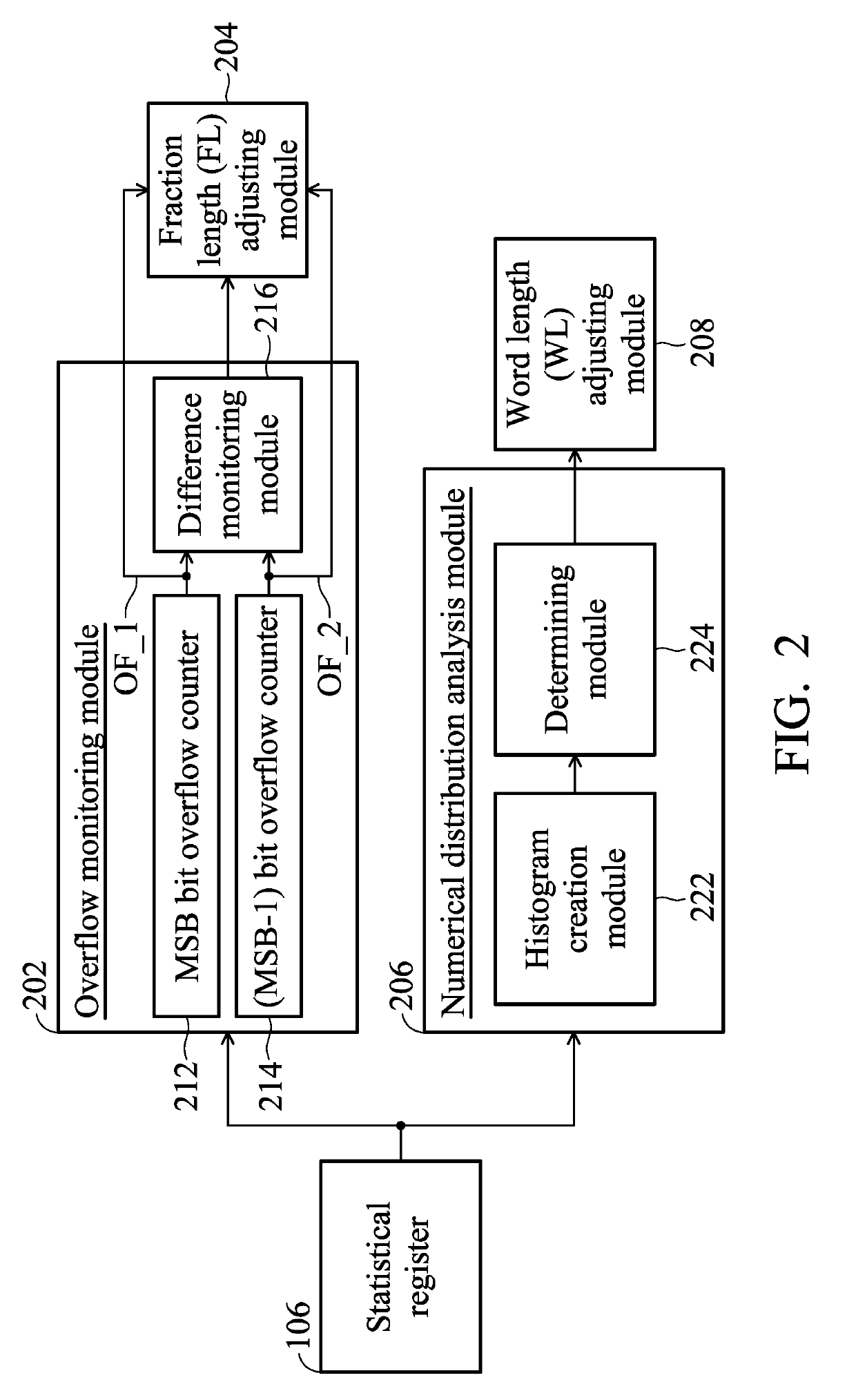

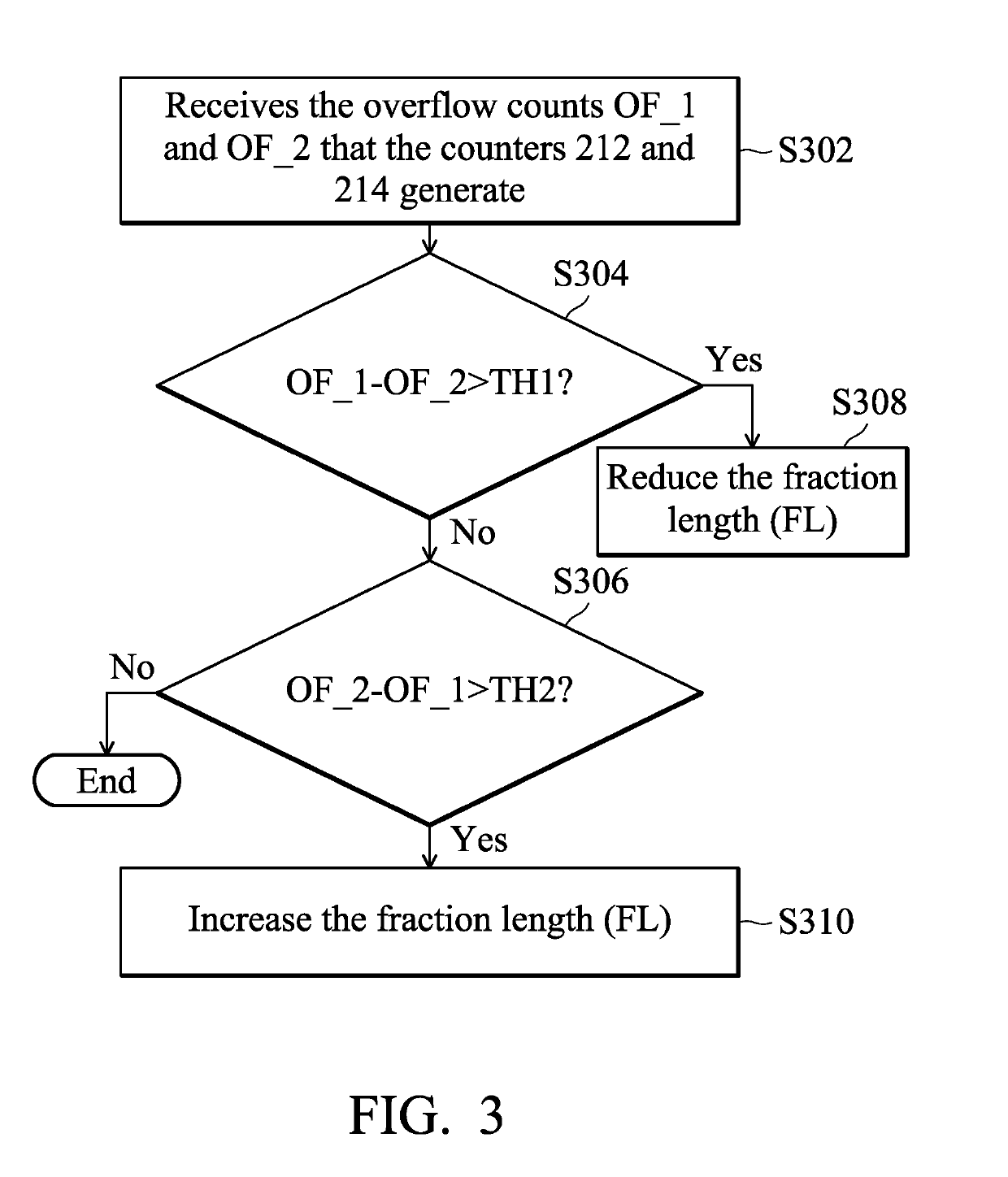

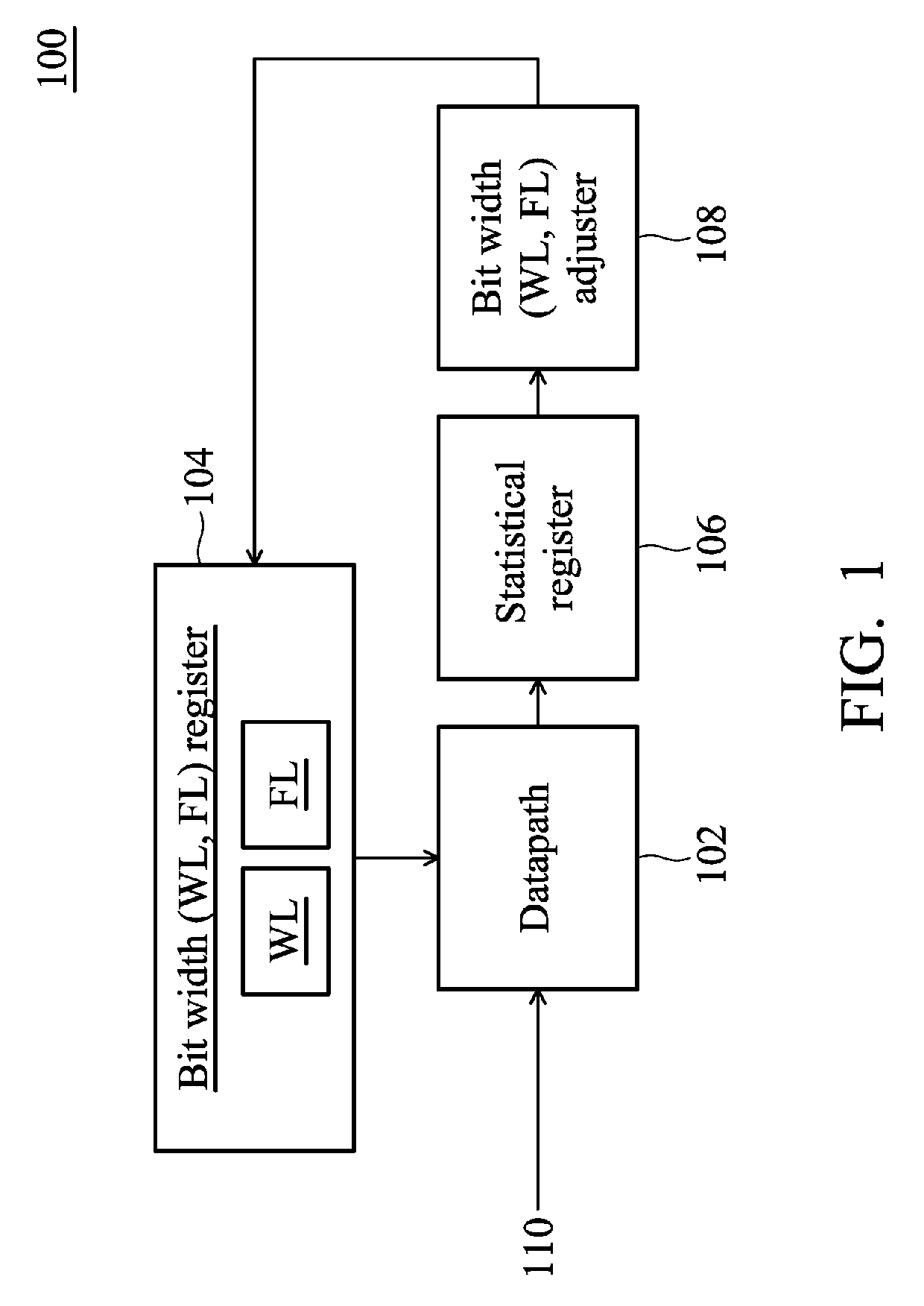

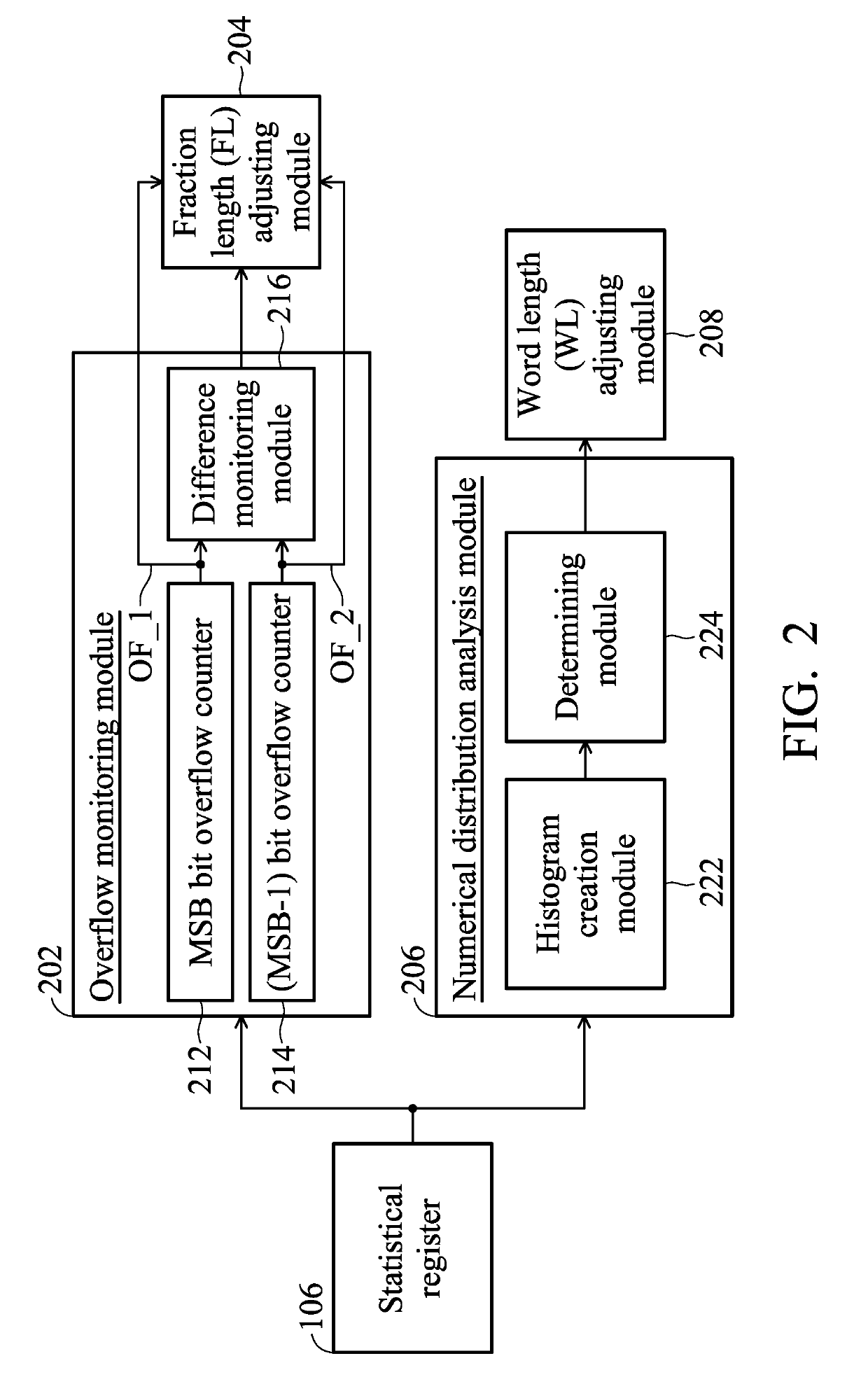

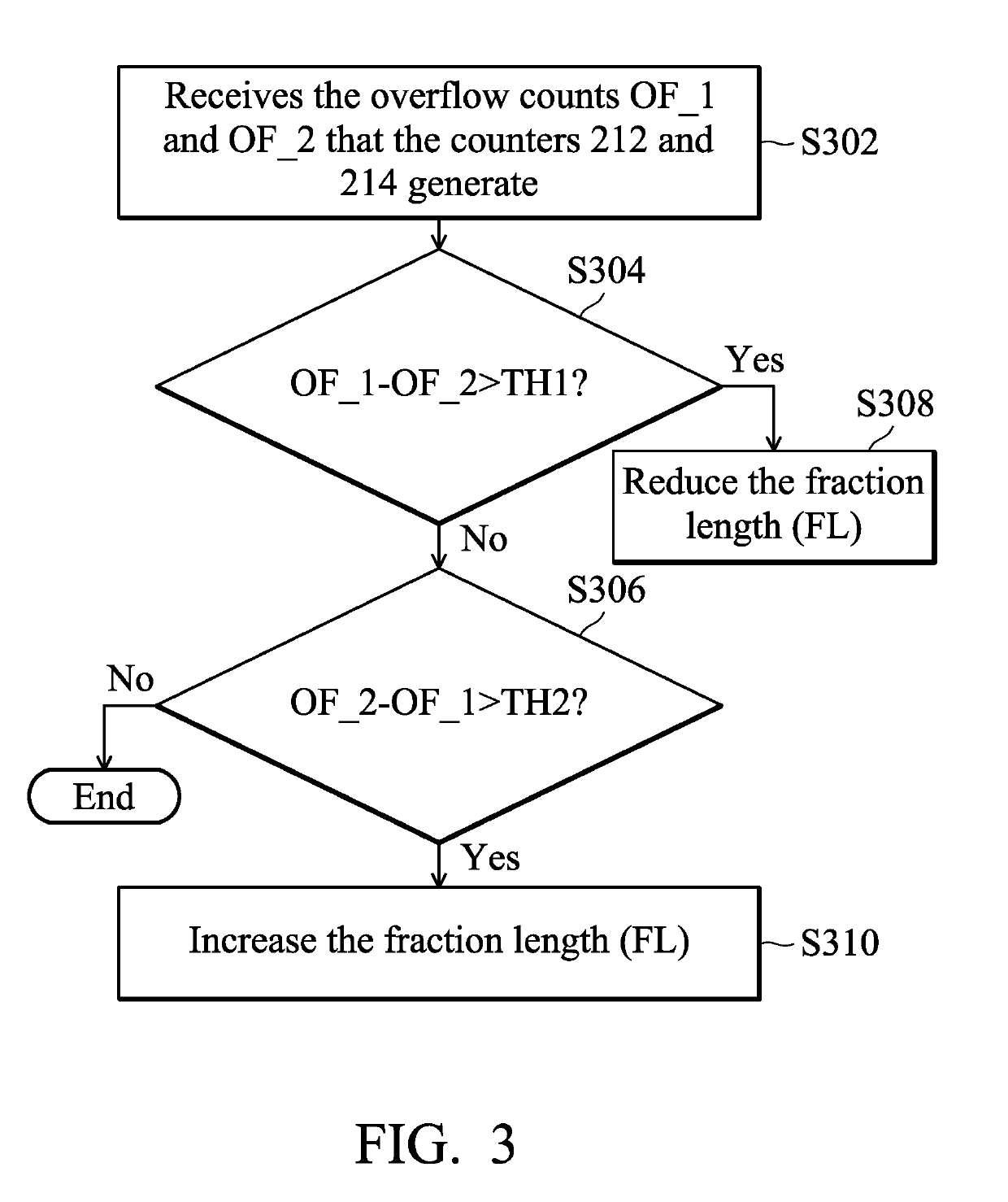

Microprocessor with dynamically adjustable bit width for processing data

ActiveUS20190227799A1Increase heightOptimize networkRegister arrangementsDigital data processing detailsComputer architectureOperand

A microprocessor with dynamically adjustable bit width is provided, which has a bit width register, a datapath, a statistical register, and a bit width adjuster. The bit width register stores at least one bit width. The datapath operates according to the bit width stored in the bit width register to acquire input operands from received data and process input operands. The statistical register collects calculation results of the datapath. The bit width adjuster adjusts the bit width stored in the bit width register based on the calculation results collected in the statistical register.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method for downloading contents using an interior mass storage in a portable terminal

A method and apparatus for downloading content to a large-capacity internal memory in a portable terminal are provided. The method includes performing a booting process of the portable terminal at the occurrence of a booting event, examining whether a Universal Serial Bus (USB) port is enabled during the booting process, if the USB port is enabled, receiving data through the USB port before driver loading, and storing the received data into the large-capacity internal memory and performing the booting process.

Owner:SAMSUNG ELECTRONICS CO LTD

Systems for selectively enabling and disabling hardware features

InactiveUS9400678B2Specific access rightsError detection/correctionComputer hardwareProgram planning

In one embodiment, a system includes a processor and logic integrated with and / or executable by the processor. The logic is adapted to: define a hardware feature policy for one or more hardware components of a system; and enable and / or disable one or more hardware features of one or more of the hardware components based on the hardware feature policy, wherein the hardware feature policy comprises instructions to enable and / or disable access to the one or most hardware features based on one or more criteria selected from a group consisting of: a feature access schedule; a volume feature access group; a job feature access group; and an user feature access group.

Owner:INT BUSINESS MASCH CORP

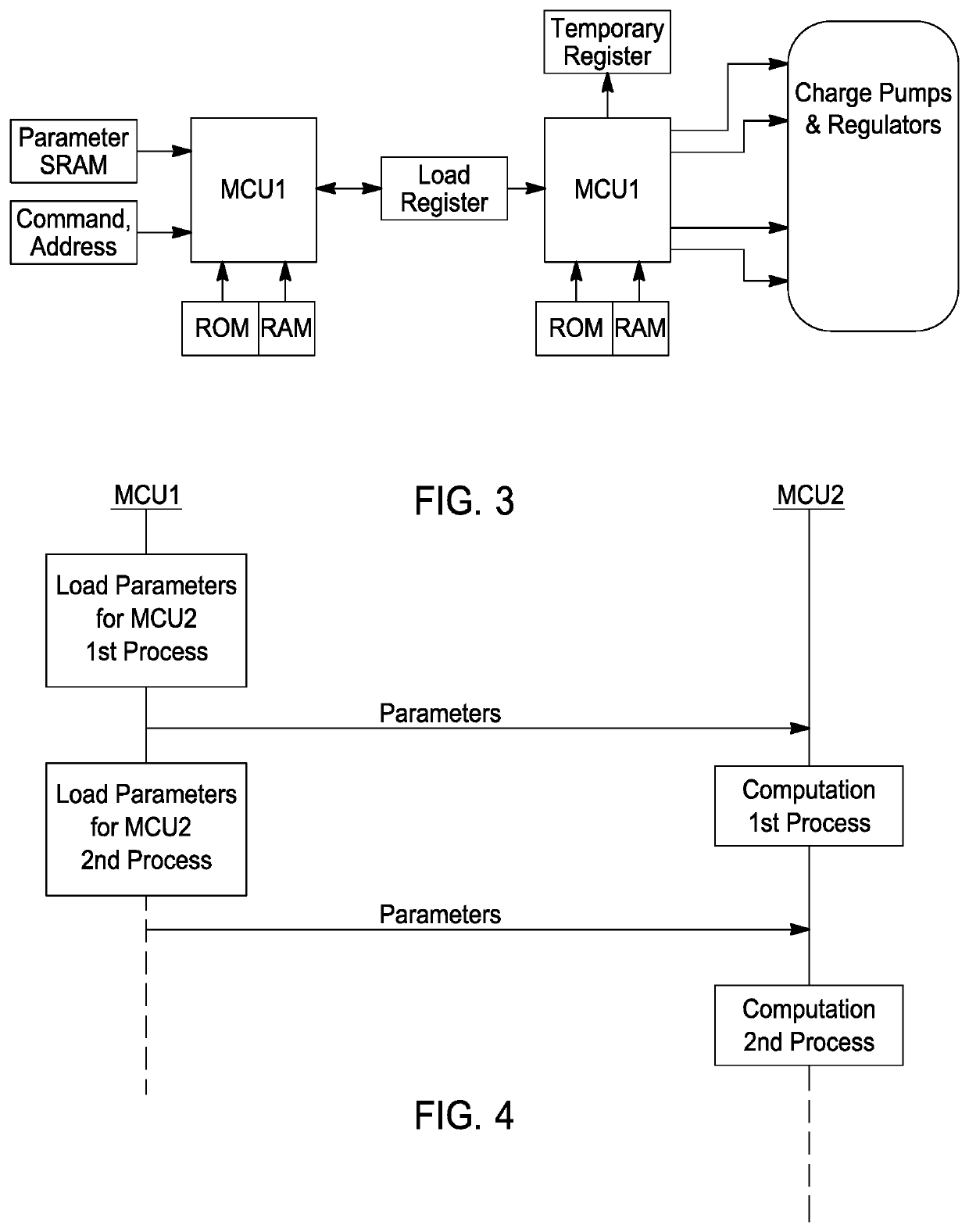

Pipelined micro controller unit

ActiveUS20210182178A1Read-only memoriesSoftware testing/debuggingMicrocontrollerSoftware engineering

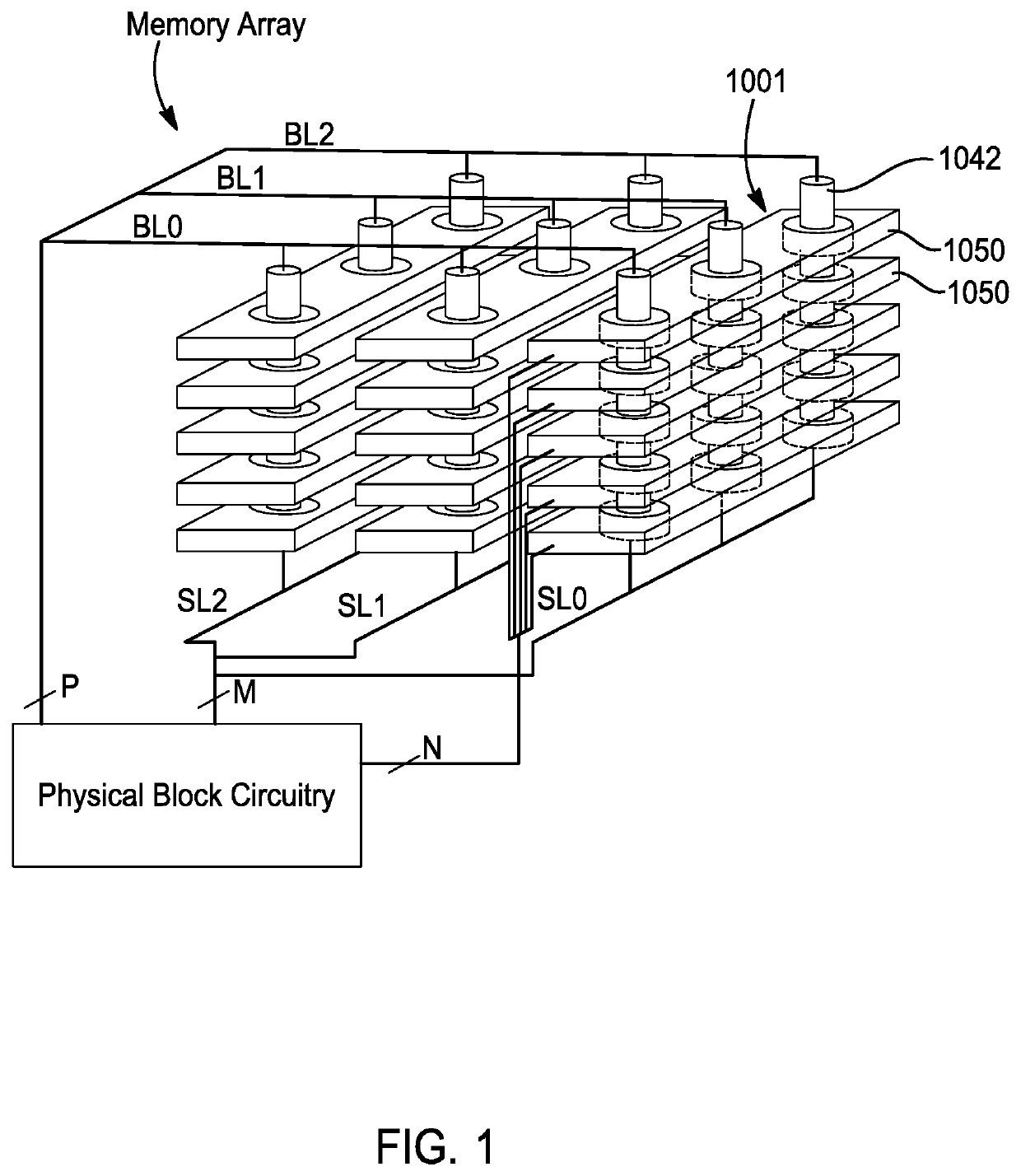

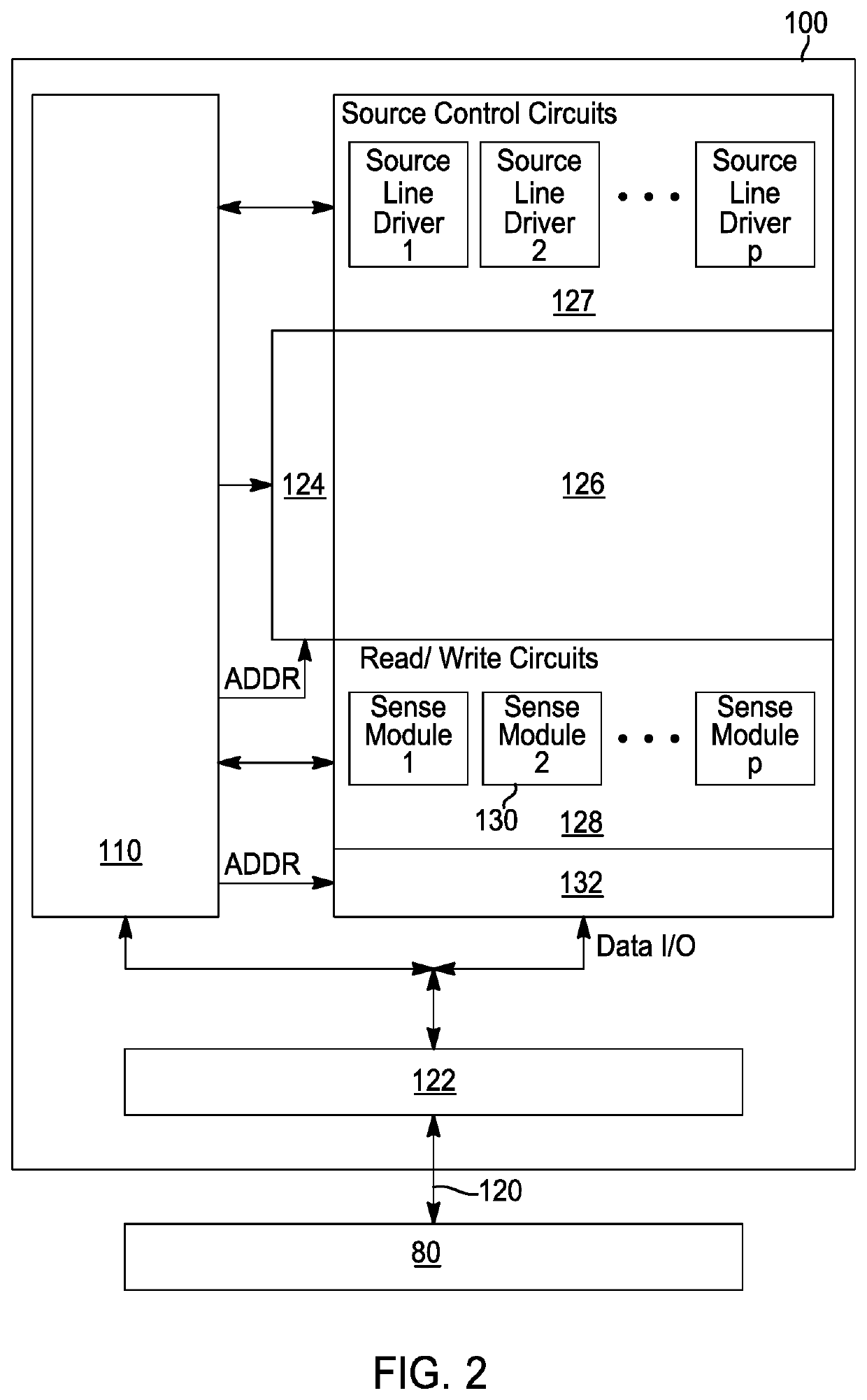

A 3D NAND memory device is provided in which control is performed by two microcontroller units (MCU). During manufacture of the memory device, bug fixes required for the controller may be addressed using a software solution by which an instruction requiring correction in one of the two MCUs is replaced with a corrected instruction stored in a RAM.

Owner:SANDISK TECH LLC

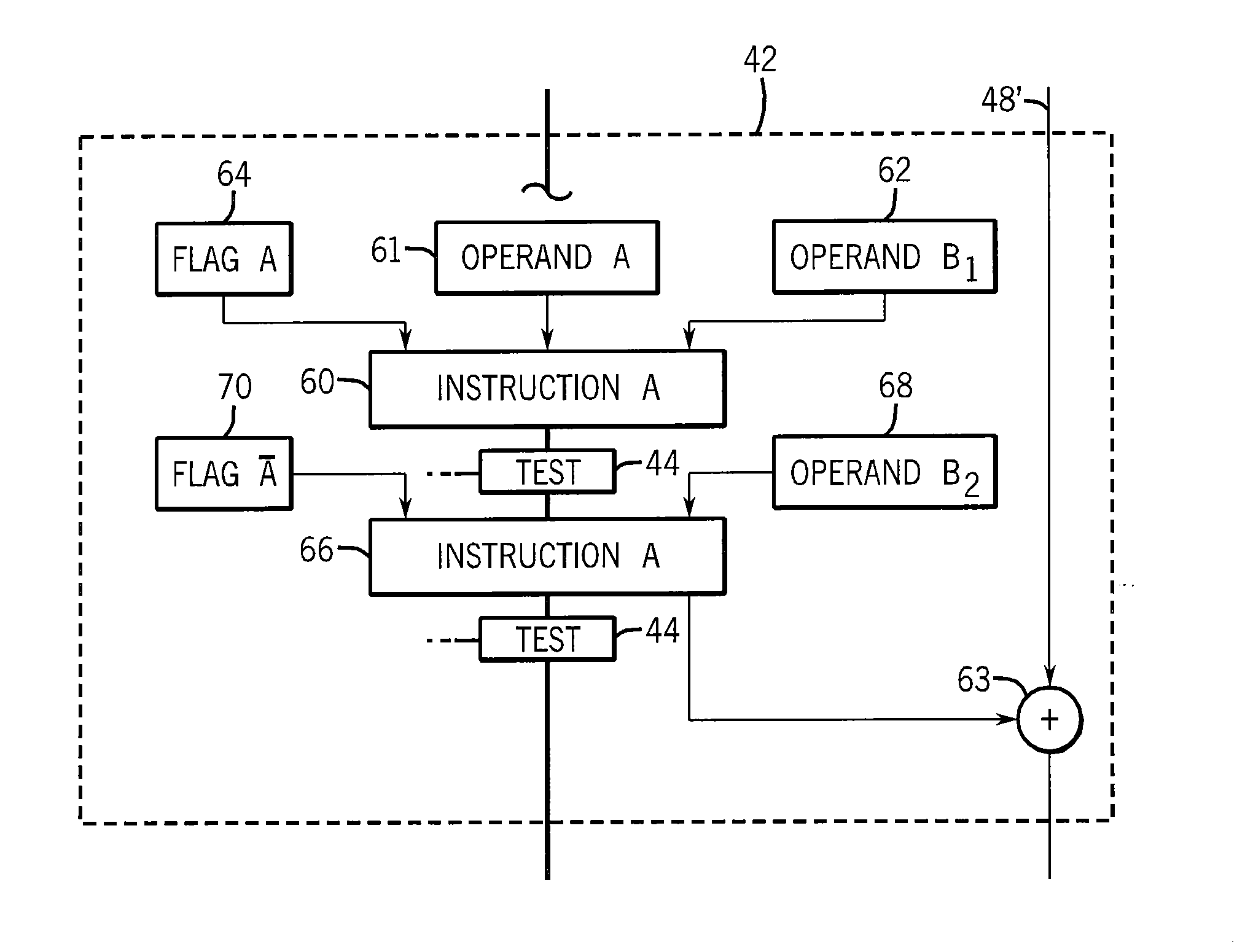

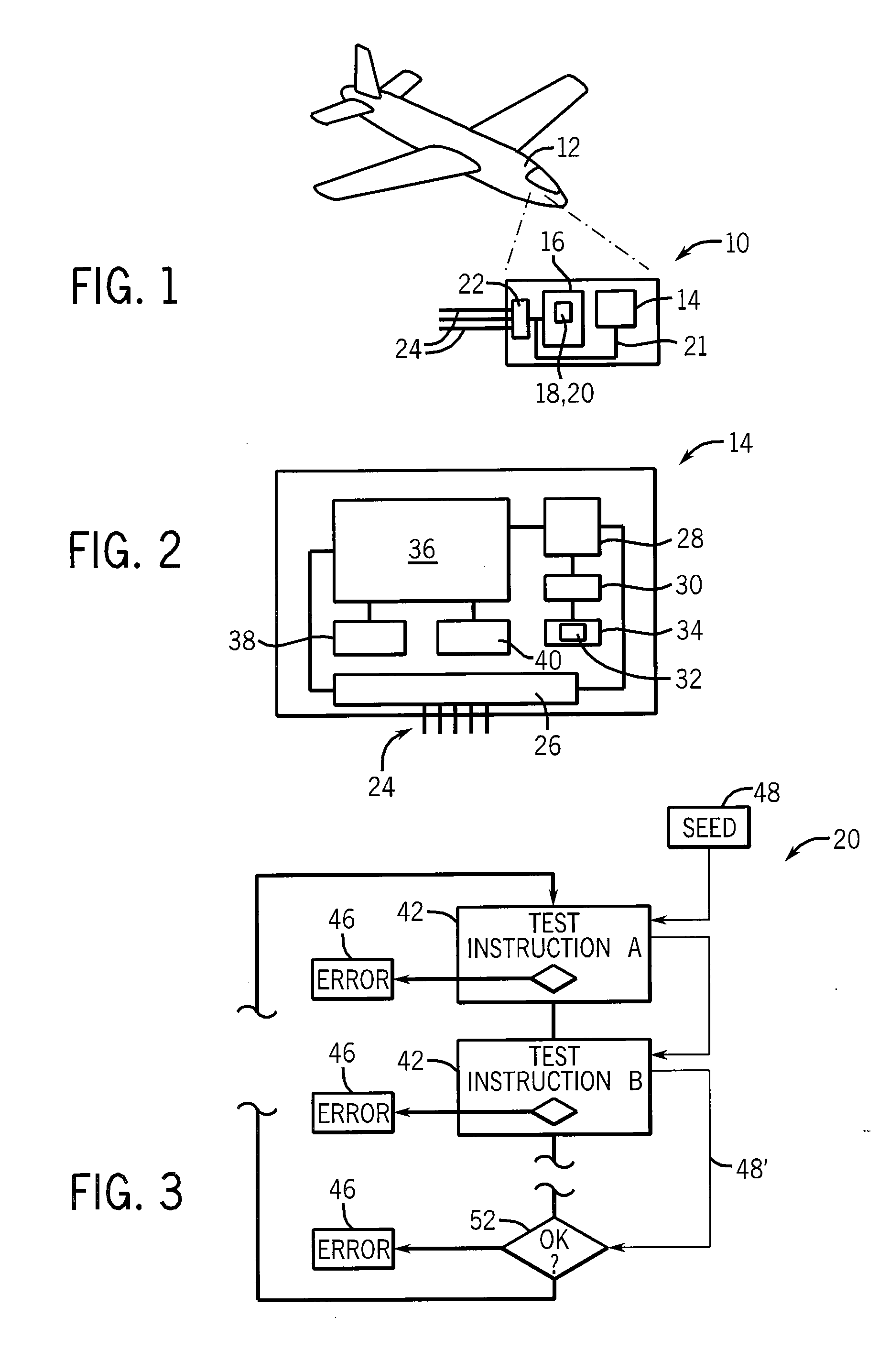

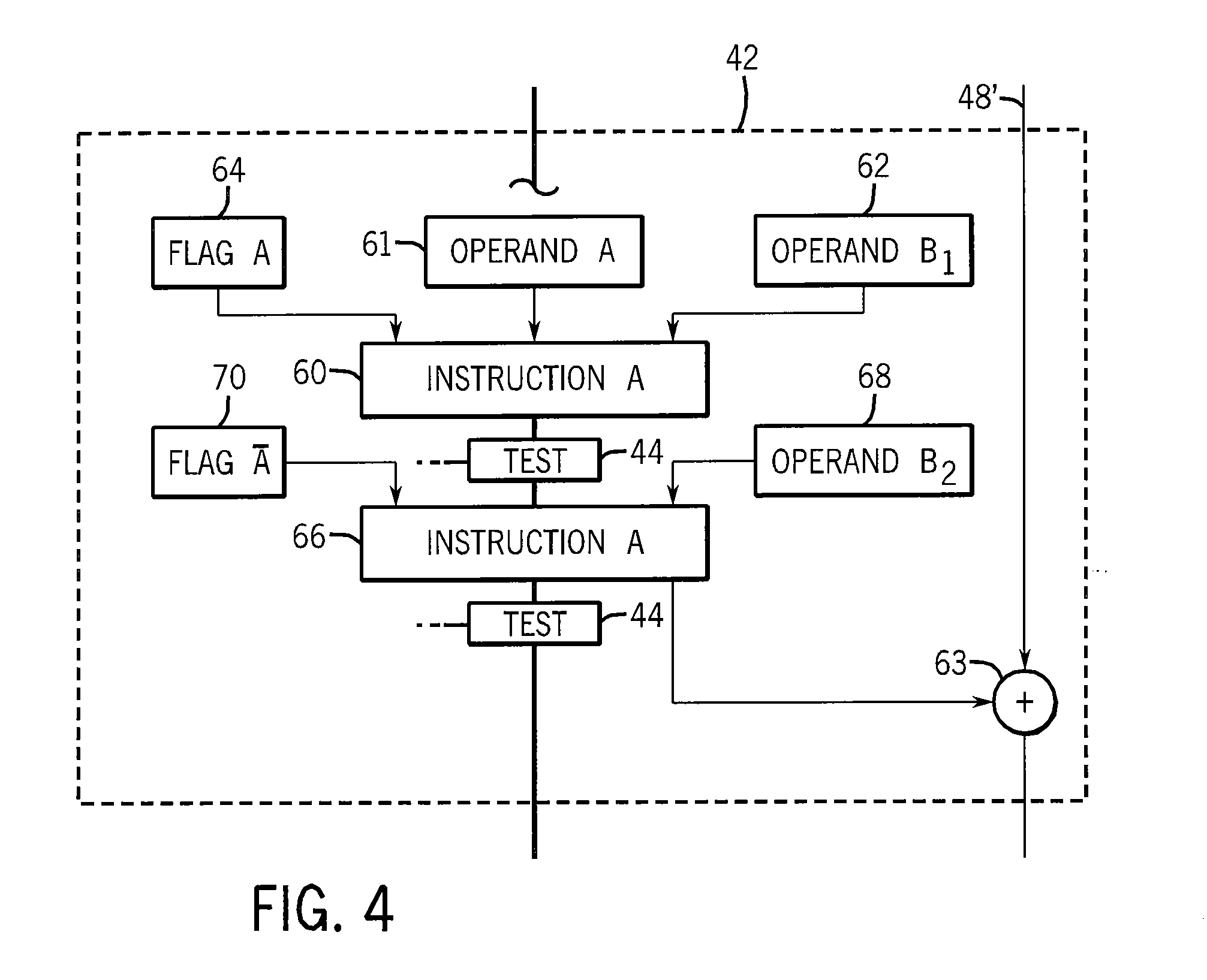

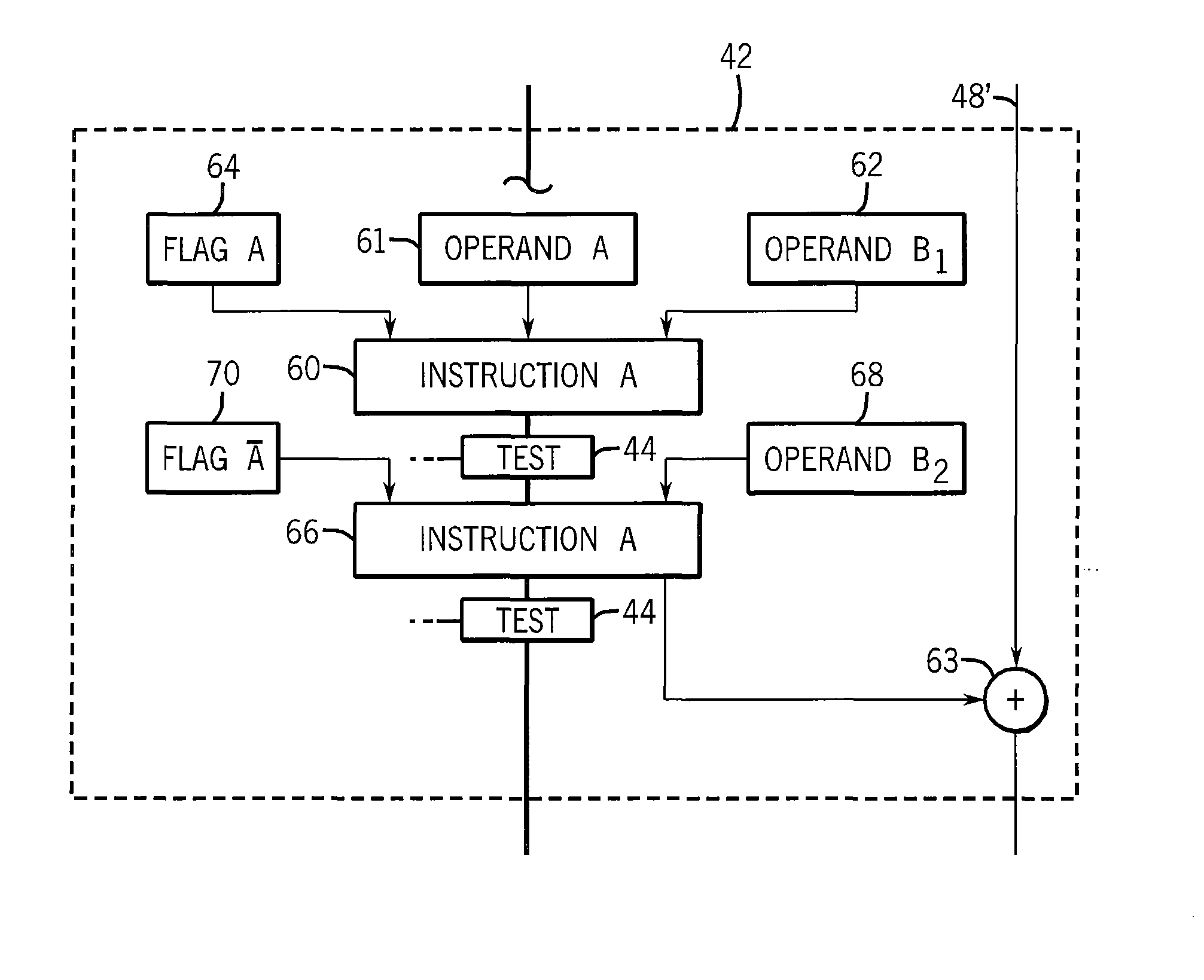

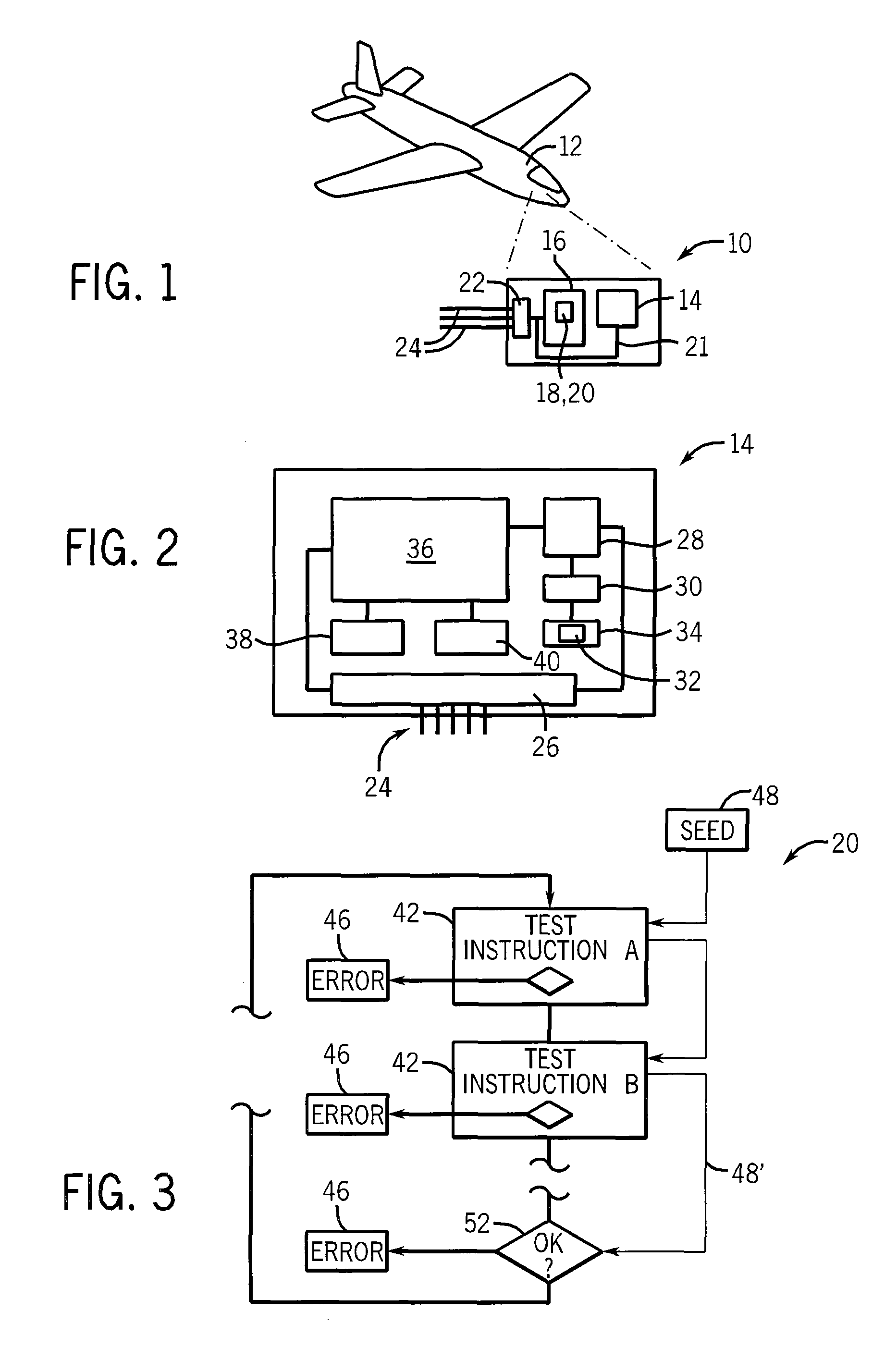

High Reliability Processor System

ActiveUS20120265973A1Raise the possibilityReduce chanceError detection/correctionDigital computer detailsParallel computingDependability

A method of testing the integrity of microprogramming within a computer processor employs a test calculation designed to exercise instructions and to reveal errors in those instructions. The problem of testing instructions using the very instructions which may possibly be corrupt is addressed by developing a signature passed from instruction to instruction providing a low likelihood of a false positive outcome. A time-out system is used in the evaluation of the test calculation to capture a wide variety of other pathological operating conditions.

Owner:ASTRONAUTICS CORPORATION OF AMERICA

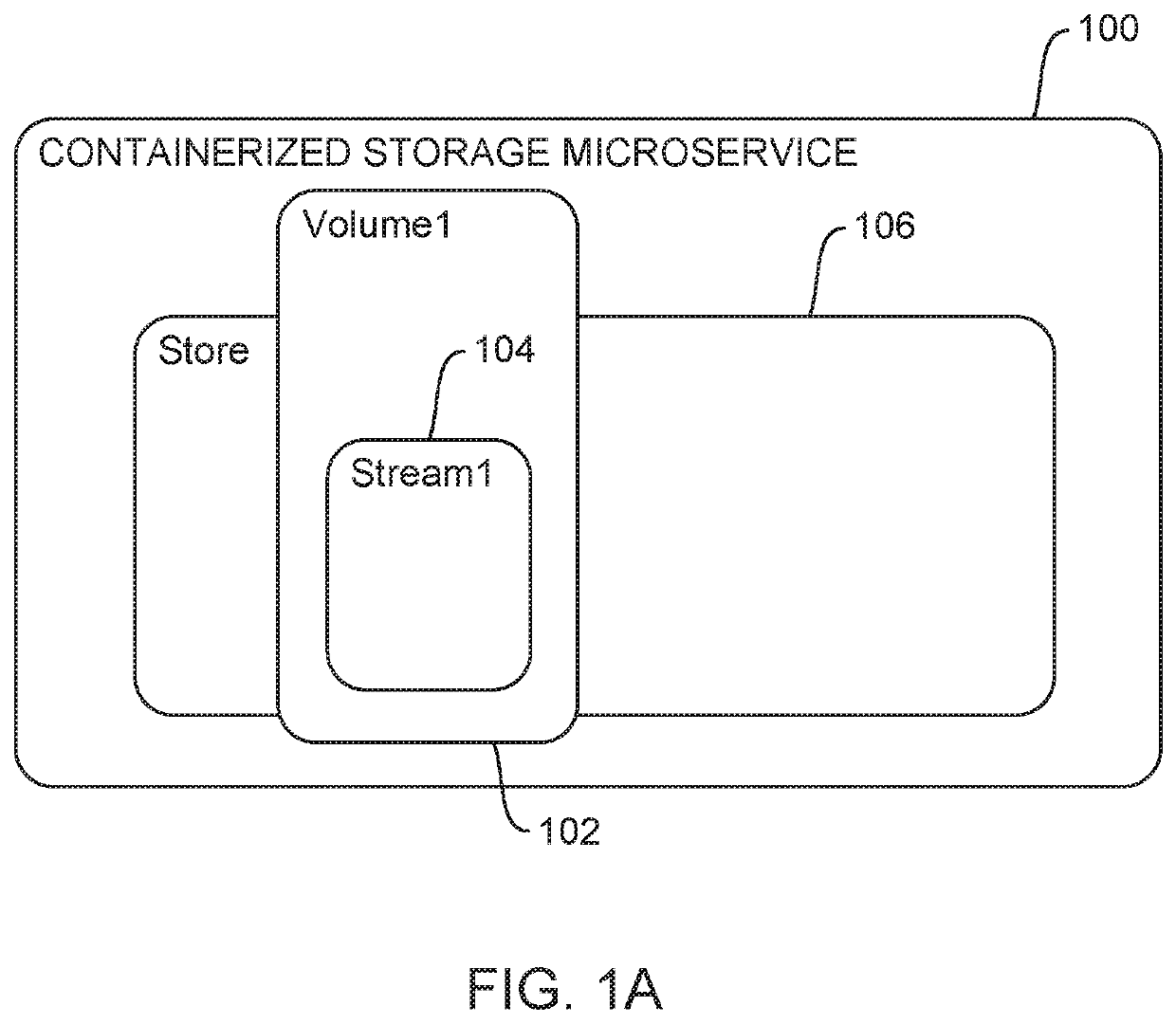

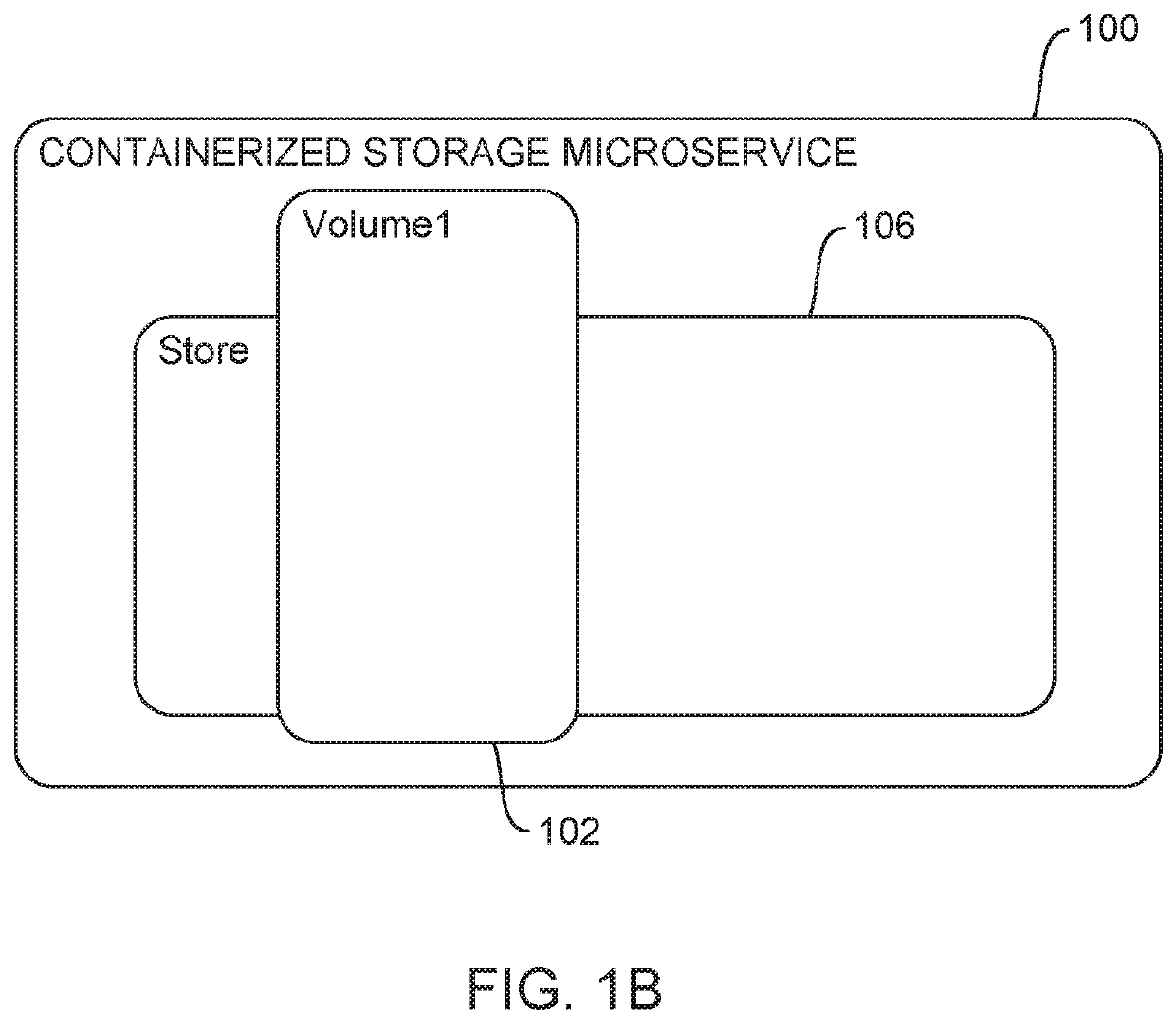

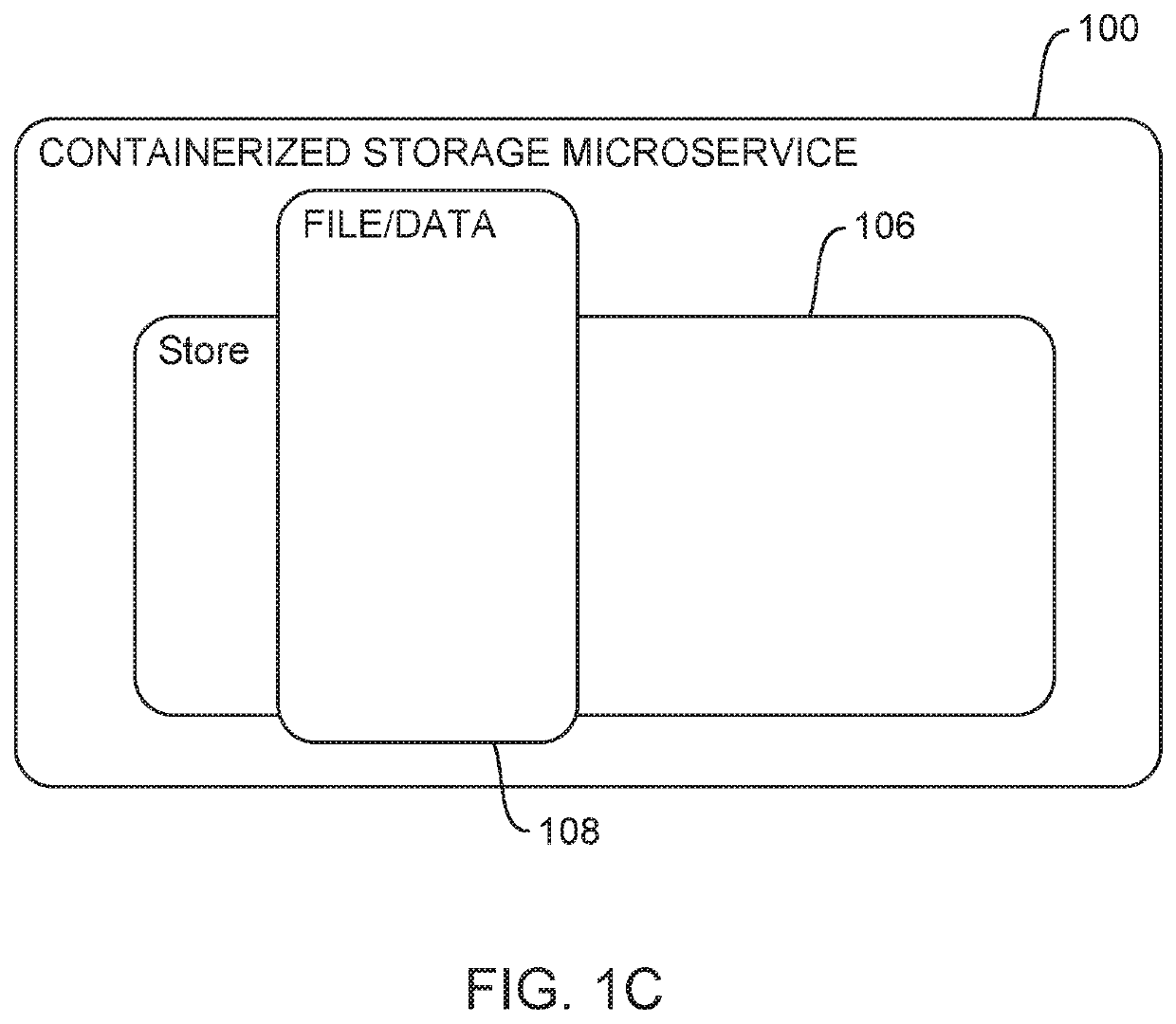

Containerized storage microservice with direct connection to requesting application container

ActiveUS10877750B1Improve securityUser identity/authority verificationDigital data authenticationOperational systemFile system

A containerized storage microservice is described. The containerized storage microservice, and its corresponding architecture, provide an environment wherein an application container accesses containerized storage services through a direct connection. This allows the operating system file system to be effectively bypassed in the provision of storage services. In one example, a library provides a basic file system and is arranged underneath the application container. The library essentially intercepts storage requests and emulates a thin file system. Instead of invoking the kernel of the operating system to process each storage request, the library allows the storage request to bypass the kernel and pass the storage request to the storage microservice. The containerized storage microservices are available in different types, and are configured so that they can be stacked to provide customized sets of storage services to different types of application containers.

Owner:DATACORE SOFTWARE

Remote controlled LED based id emitter

InactiveUS20170339000A1Reduced receivable bandwidthReduce software complexityTransmission systemsDigital data processing detailsLight equipmentSignal on

An apparatus includes a luminaire; power input for the luminaire; a modulation circuit for modulating the power input so that light output includes an identifier of the luminaire; and a programmable memory for storing at least one of the identifier of the luminaire and a modulation scheme for modulation of the luminaire to place a signal on the light. A method for modulating light includes storing in programmable memory an identifier for the luminaire, the identifier being used to modulate the light, and / or a modulation scheme for modulation of the luminaire; and changing content of programmable memory to change the identifier and / or the modulation scheme. A method of efficiently deploying the luminaires and identifying their locations to a network is disclosed. A method of multi-factor authentication using authentication data transmitted by modulating the light emitted by a luminaire is also disclosed.

Owner:BASIC6

Methods for selectively enabling and disabling hardware features

InactiveUS20140280842A1Specific access rightsError detection/correctionComputer hardwareFeature based

In one embodiment, a method includes defining a hardware feature policy for one or more hardware components of a system; and enabling and / or disabling one or more hardware features of one or more of the hardware components based on the hardware feature policy, where the hardware feature policy comprises instructions to enable and / or disable access to the one or more hardware features based on one or more criteria selected from the group consisting of: a feature access schedule; a volume feature access group; a job feature access group; and an user feature access group.

Owner:IBM CORP

Methods for selectively enabling and disabling hardware features

Owner:INT BUSINESS MASCH CORP

Processor device collecting performance information through command-set-based replay

ActiveUS20190213010A1Improve consistencyData augmentationHardware monitoringConcurrent instruction executionCounting NumberParallel computing

Owner:SAMSUNG ELECTRONICS CO LTD

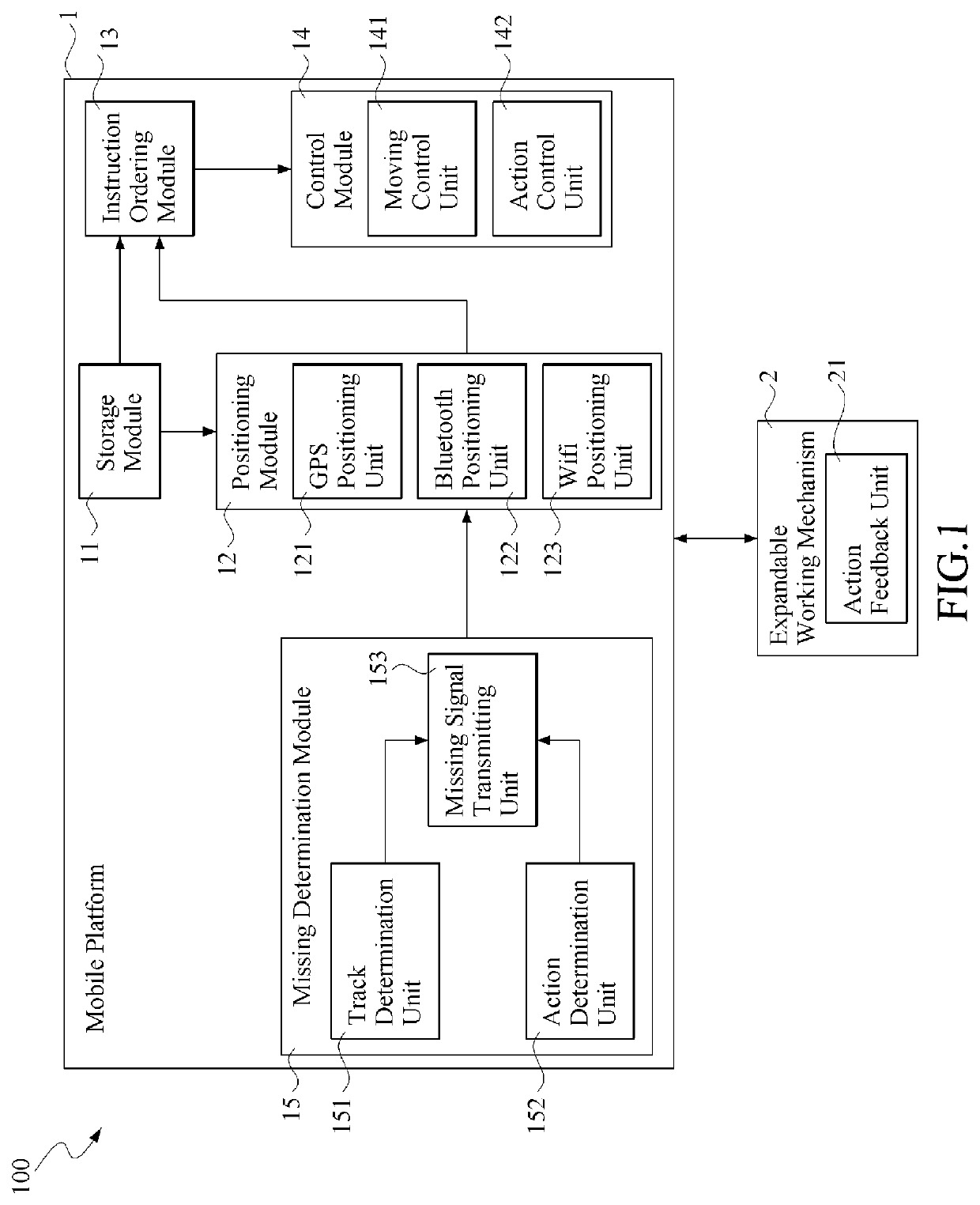

Expandable mobile platform

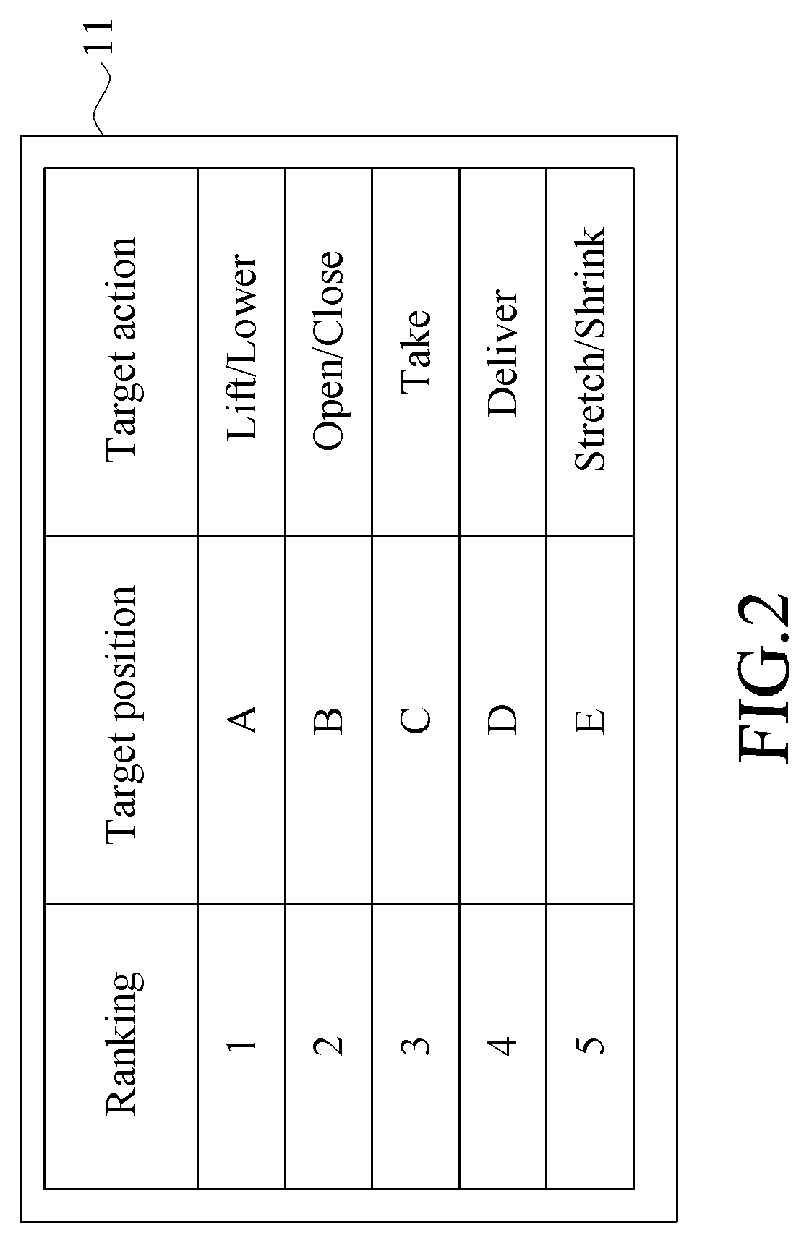

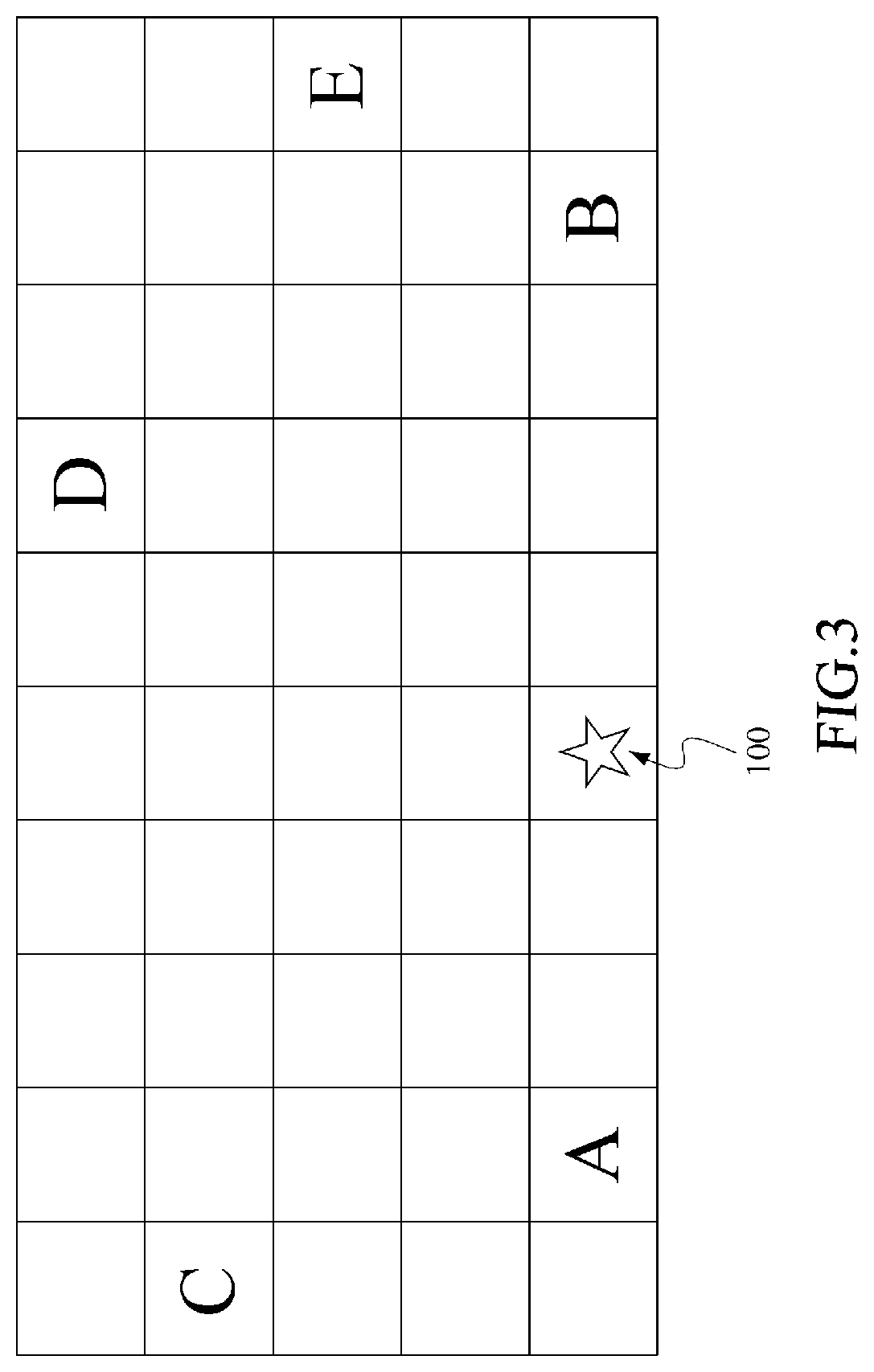

InactiveUS20200110603A1Autonomous decision making processMicroinstruction functionComputer hardwareComputer architecture

An expandable mobile platform is utilized for receiving and executing a plurality of instructions, each instruction has a target position and a target action. The expandable mobile platform includes a mobile platform and an expandable working mechanism. The mobile platform includes a storage module, a positioning module, an instruction ordering module, and a control module. The storage module is utilized for storing a map data and the instructions. The positioning module is utilized for determining a current position of the mobile platform. The instruction ordering module is utilized for analyzing the current position and a plurality of target positions of the instructions, and aligning the target positions as an instruction serial. The control module is utilized for generating moving control signals to control the mobile platform moving to the target positions and action control signals to control the expandable working mechanism executing the target actions according to the instruction serial.

Owner:TECO ELECTRIC AND MACHINERY

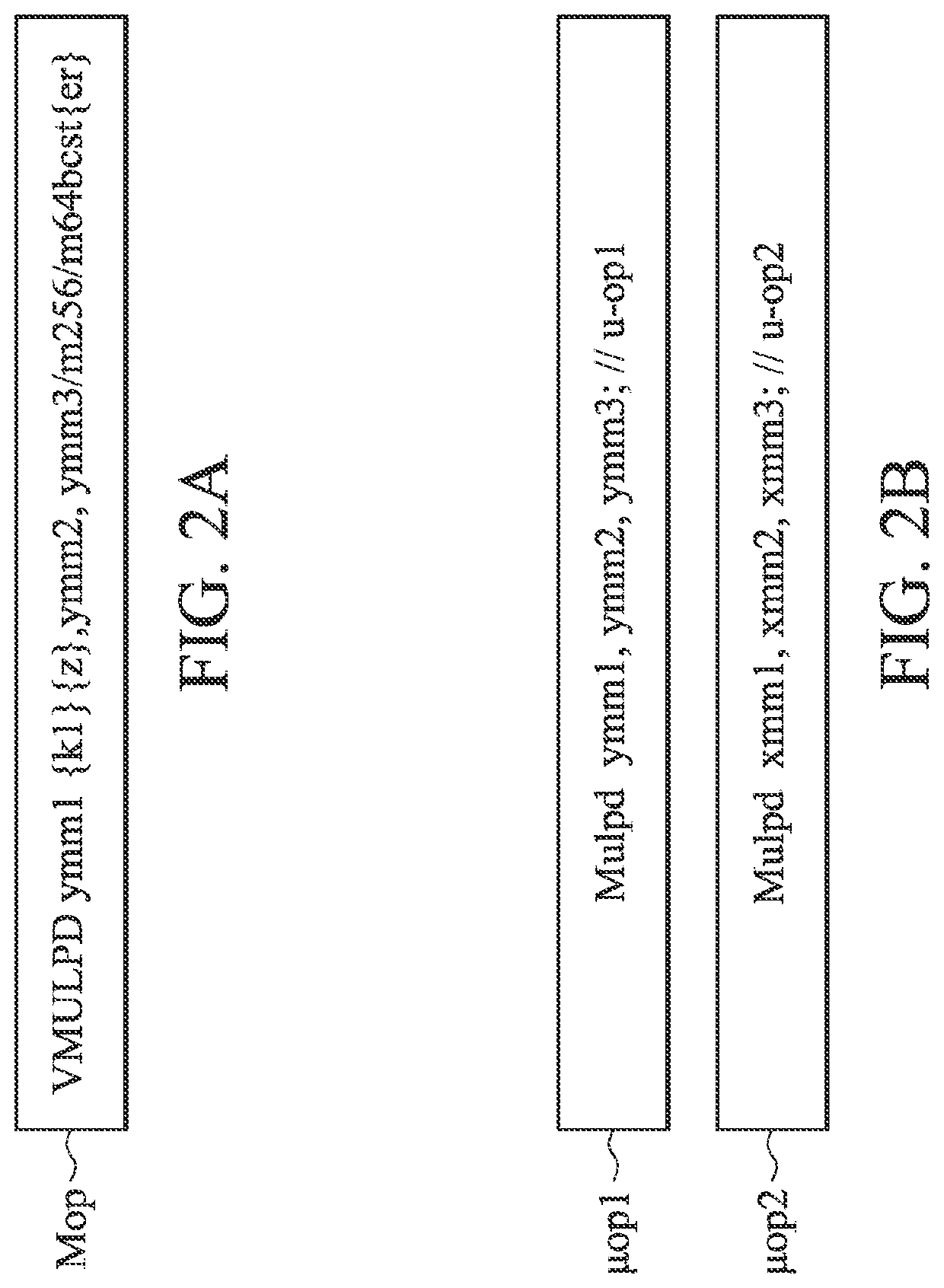

Instruction execution method and instruction execution device

ActiveUS20210208893A1Reduced execution timeReduce power consumptionInstruction analysisConcurrent instruction executionProgramming languageComputer architecture

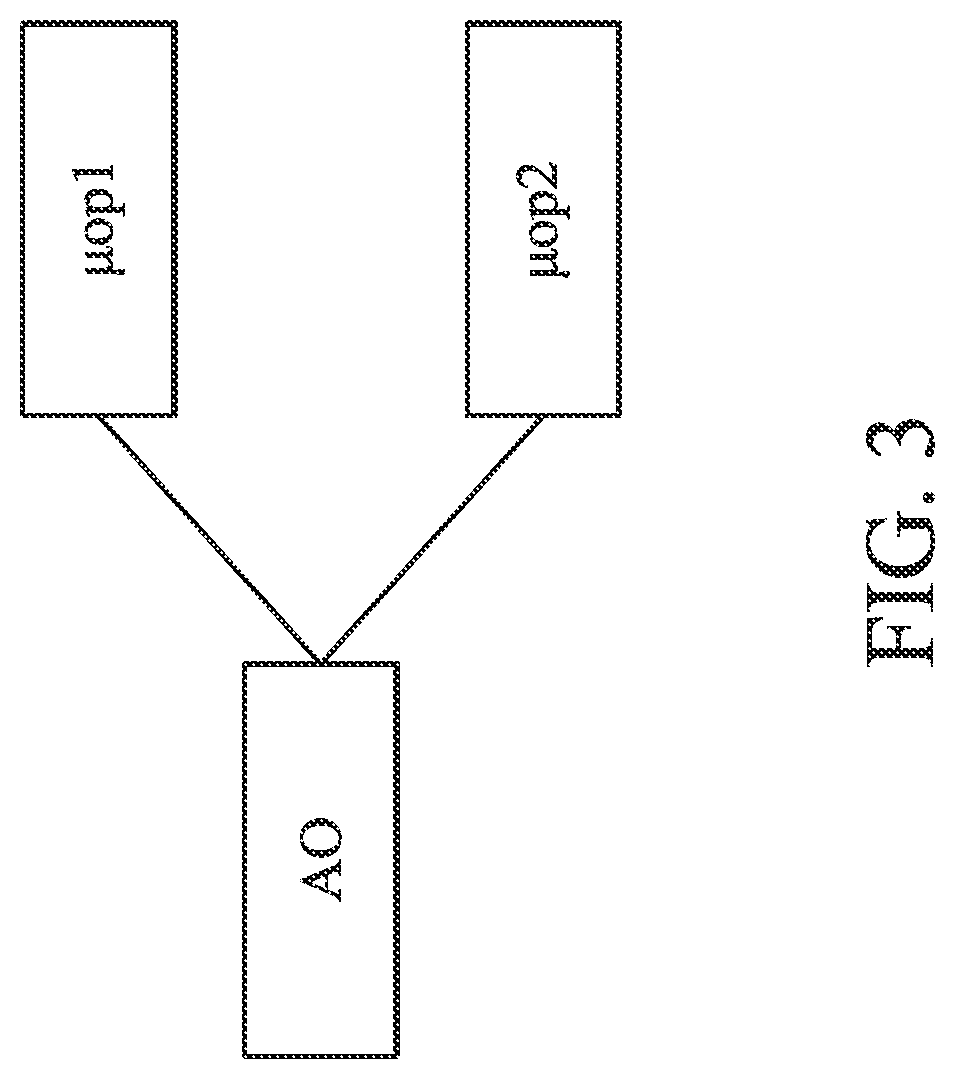

An instruction execution method includes the following steps: translating a macro-instruction into a first micro-instruction and a second micro-instruction, and marking first binding information on the first micro-instruction, and marking second binding information on the second micro-instruction; and simultaneously retiring the first micro-instruction and the second micro-instruction according to the first binding information and the second binding information. The first micro-instruction and the second micro-instruction are adjacent to one another in the micro-instruction storage space.

Owner:VIA ALLIANCE SEMICON CO LTD

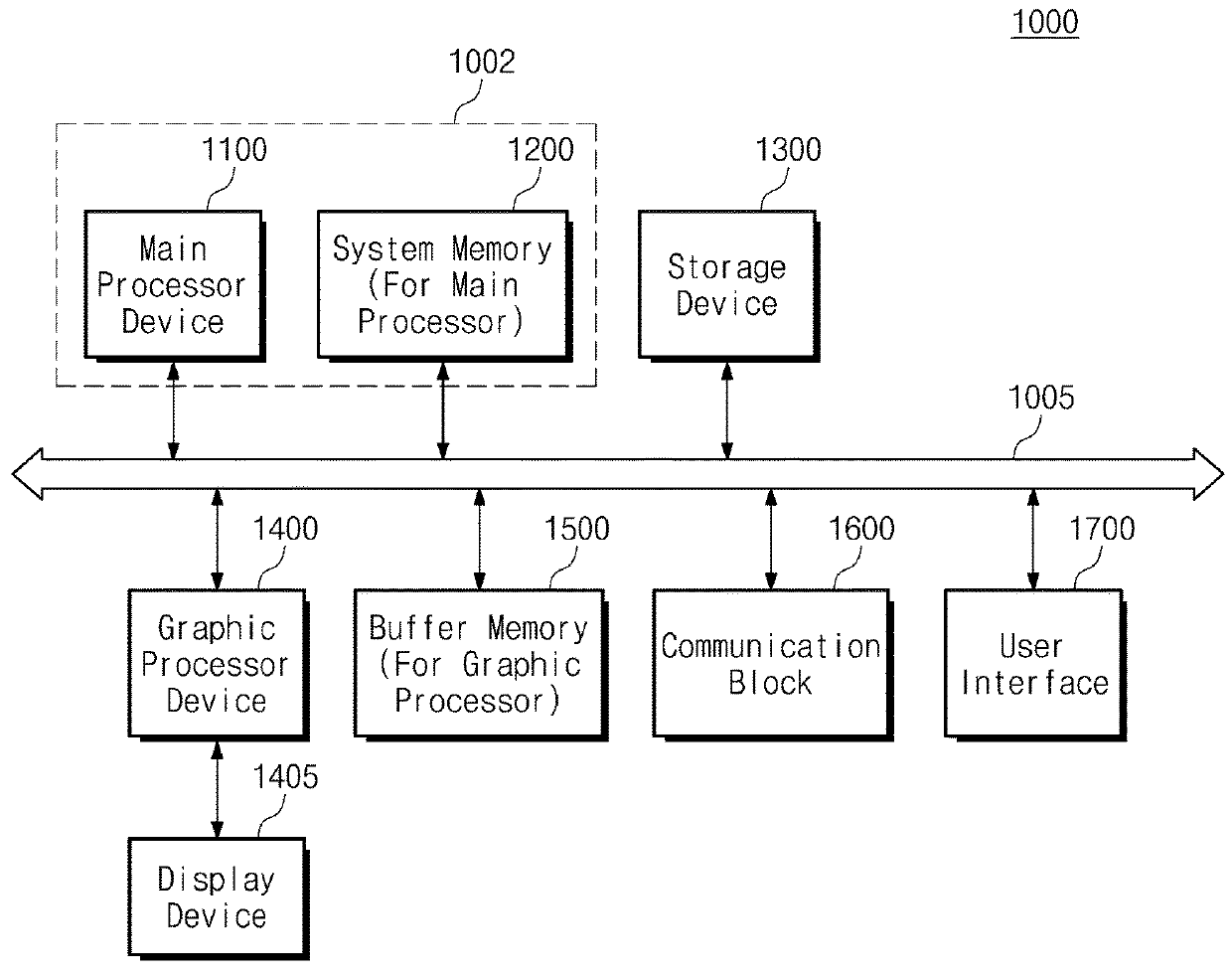

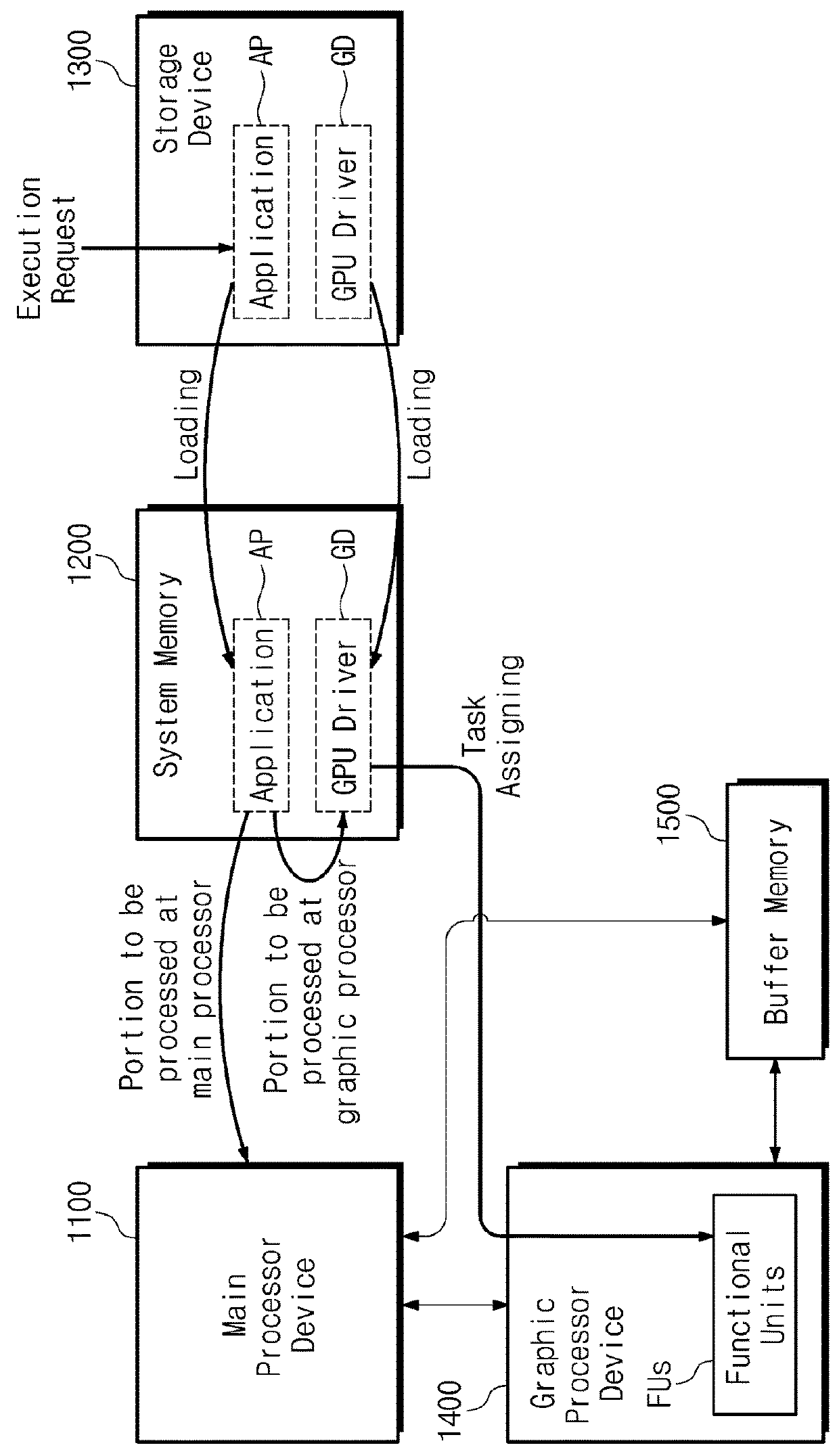

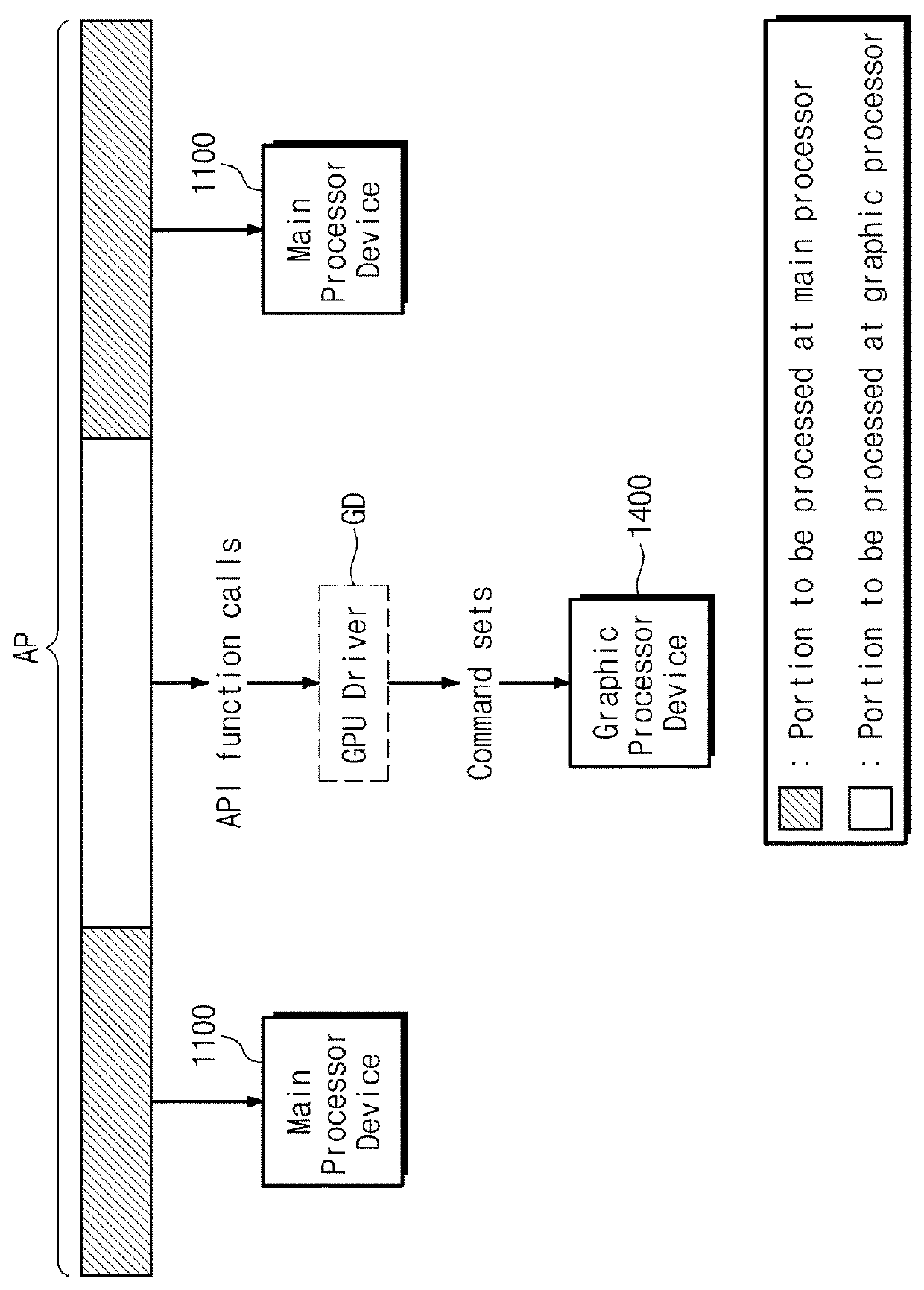

Information processing apparatus and method for accelerating information processing

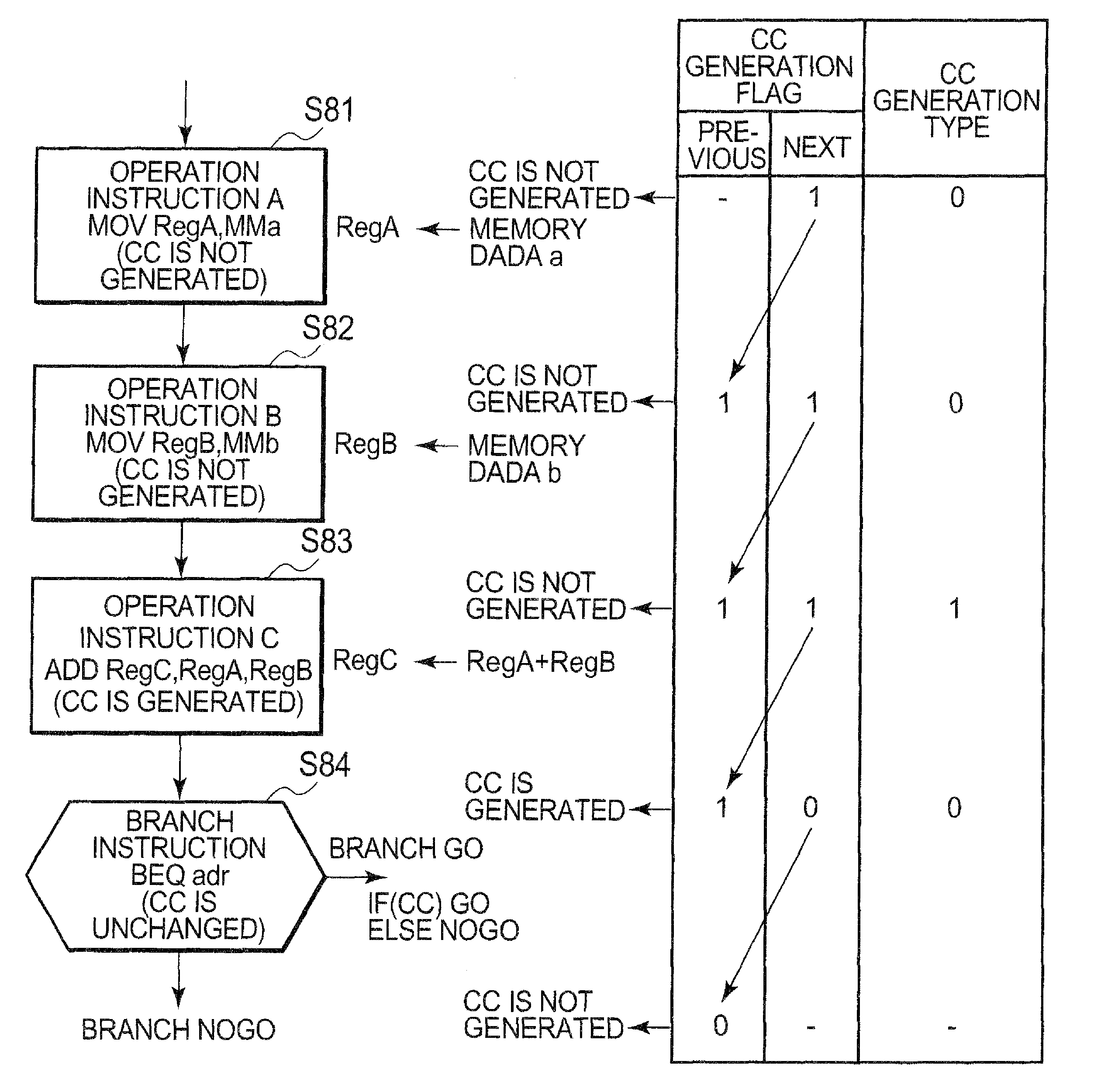

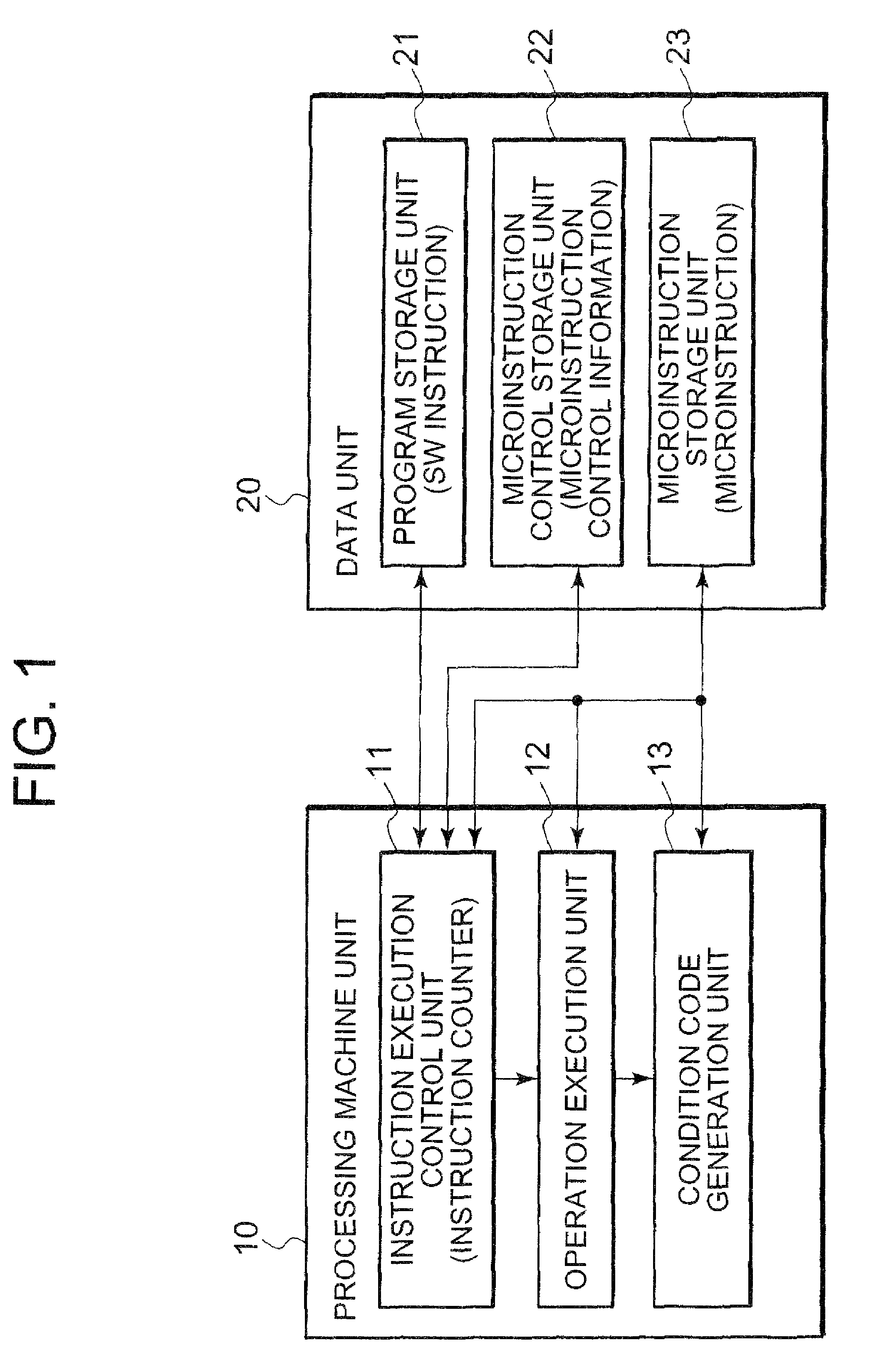

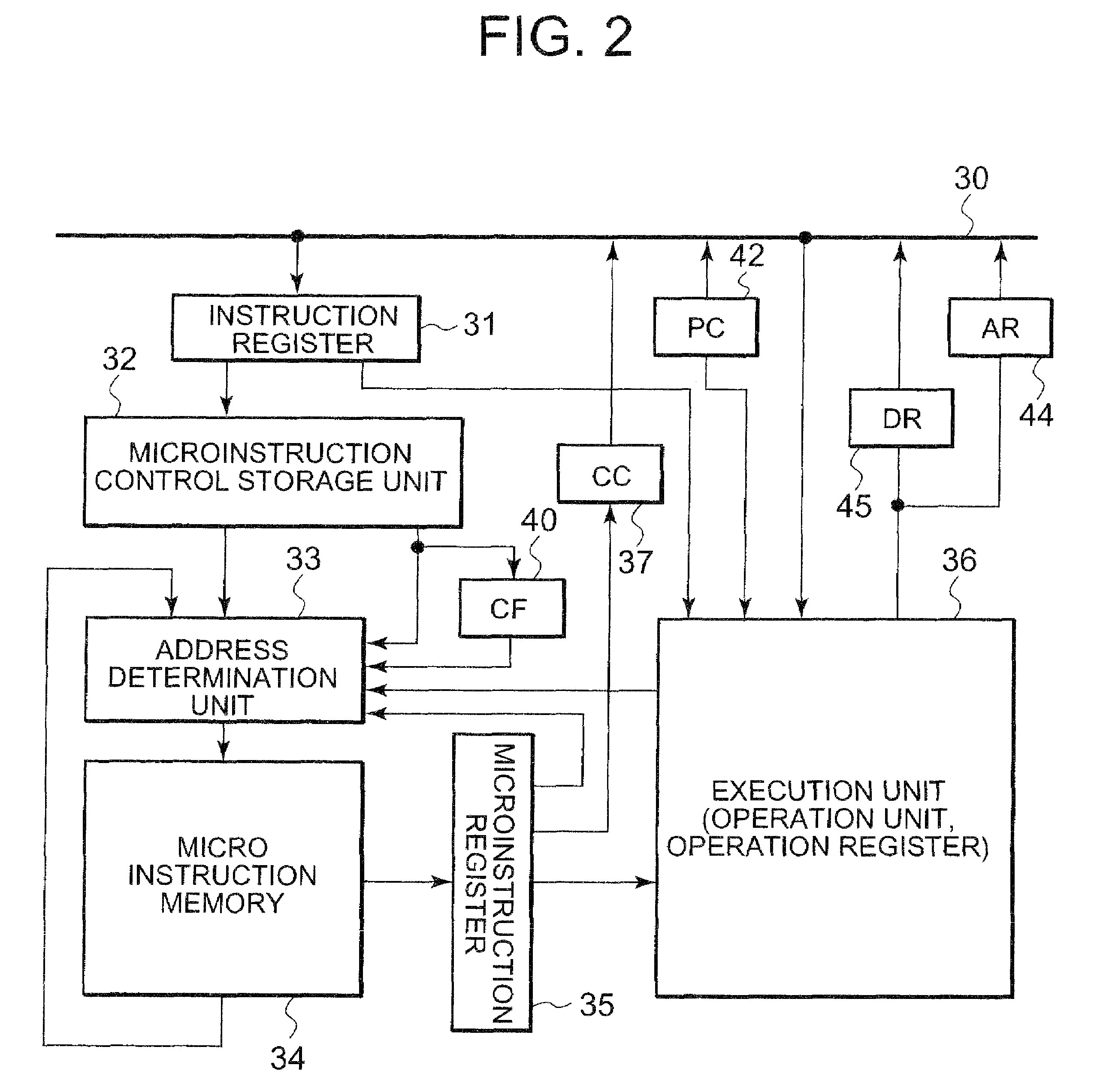

InactiveUS7886133B2Improve processing efficiencySpeed up the processConditional code generationInstruction analysisProgramming languageInformation processing

An apparatus comprises an instruction execution control unit which fetches an instruction executed according to a microinstruction, the instruction is classified into a plurality of types, from a memory, wherein the types include a first type indicative of generating a condition code and a second type indicative of not generating the condition code, the condition code corresponds to a result of execution of the instruction, and a condition code generation unit which generates the condition code of the instruction corresponding to the first type on condition that the instruction corresponding to the second type is executed next to the instruction corresponding to the first type.

Owner:NEC CORP

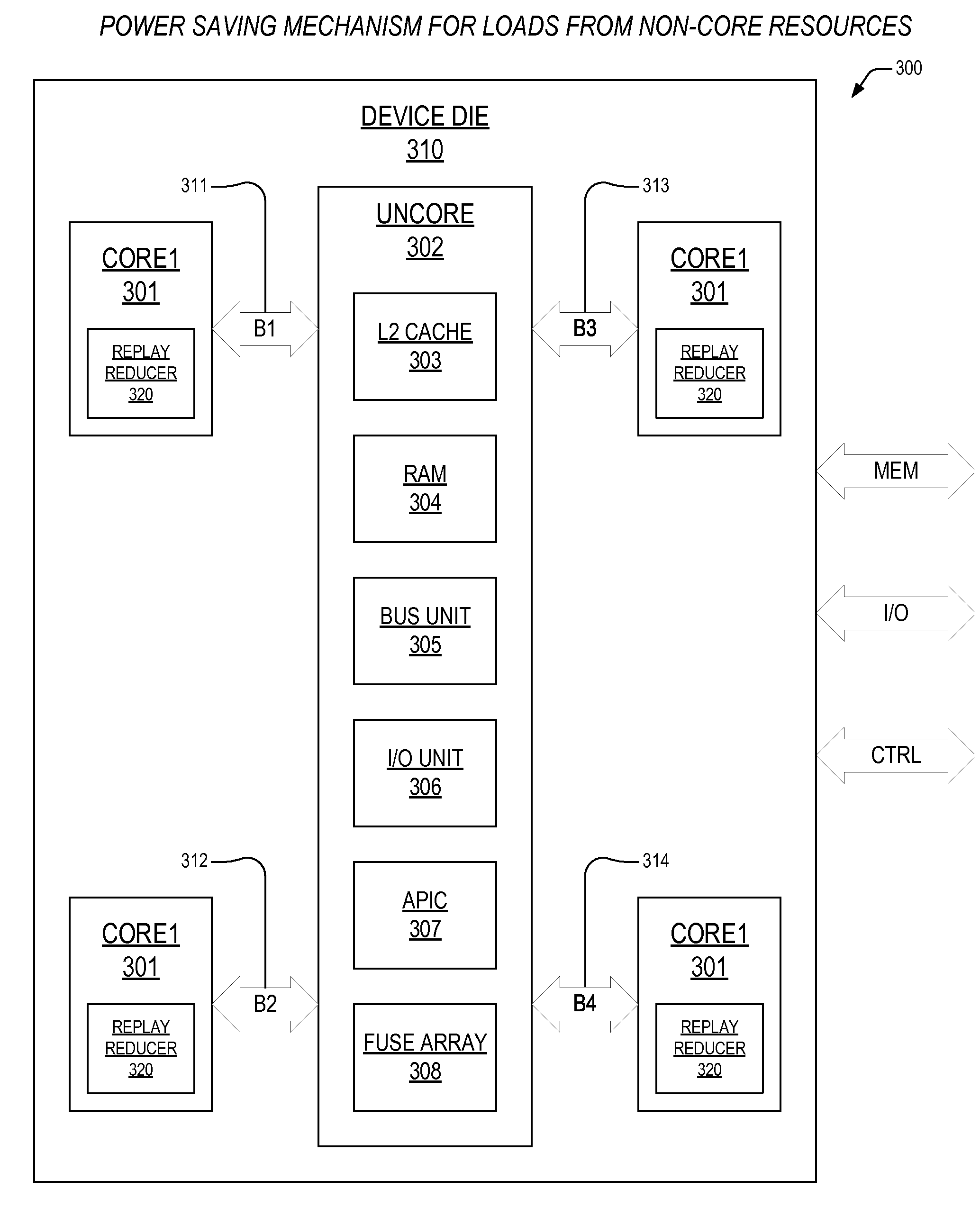

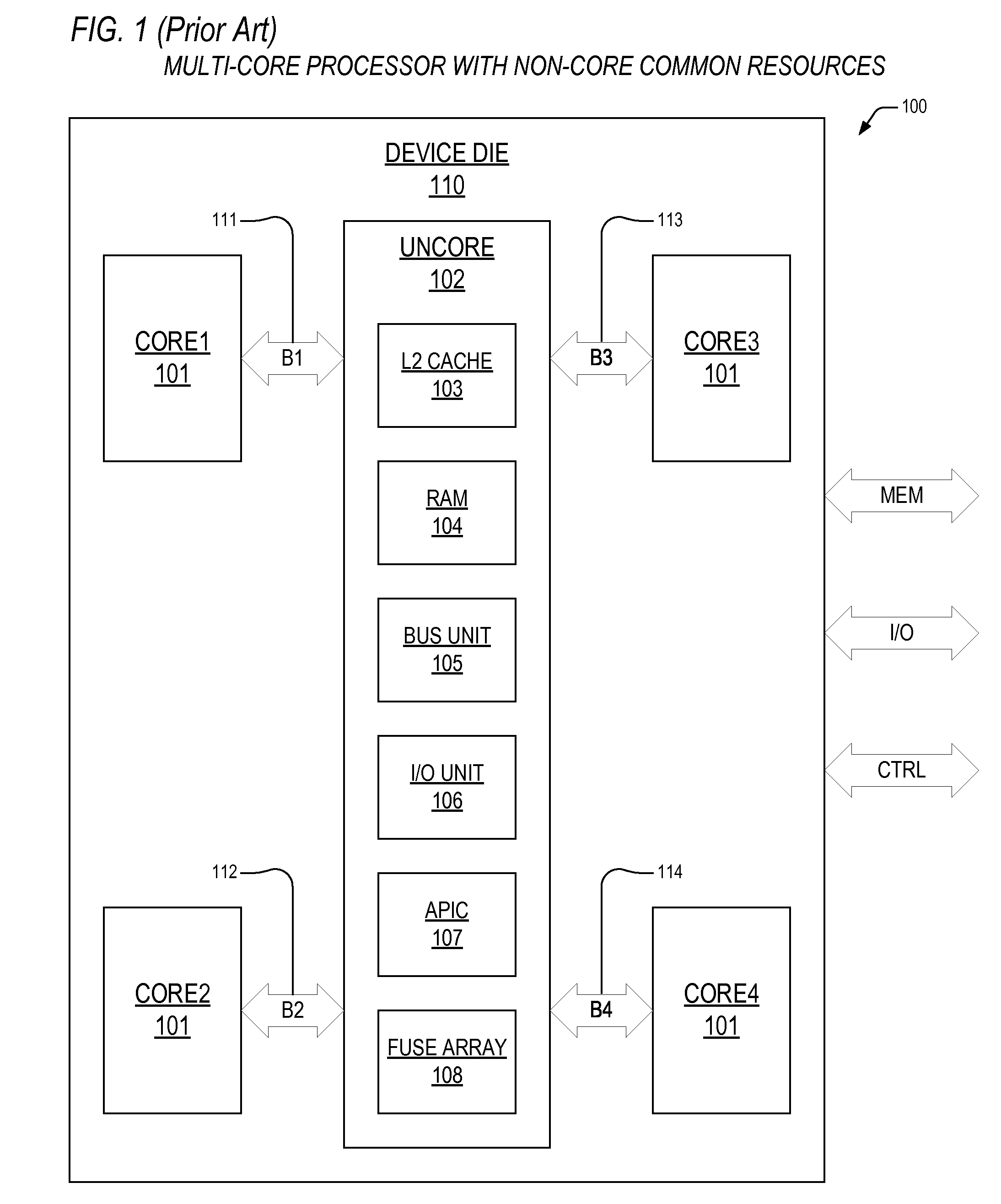

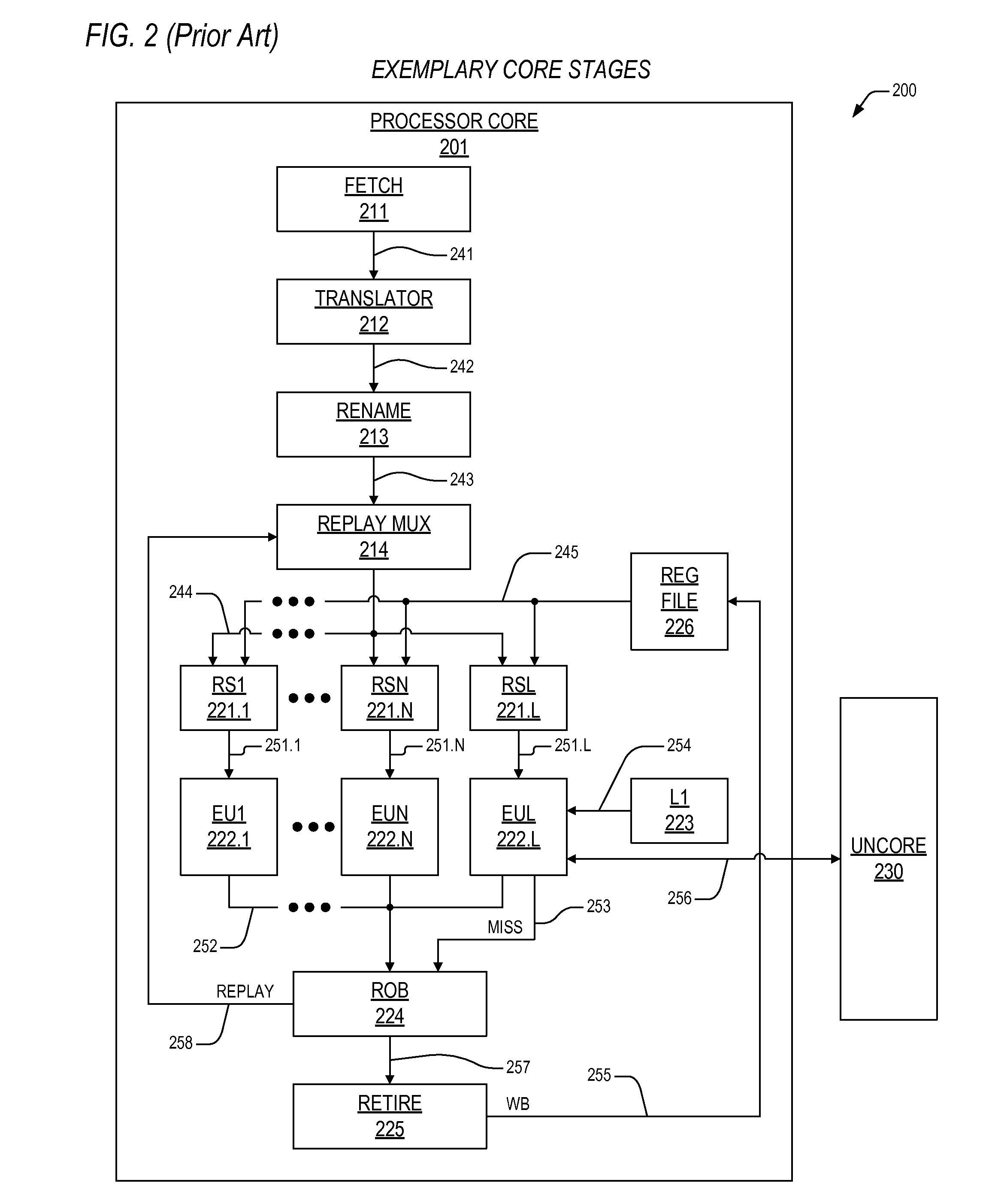

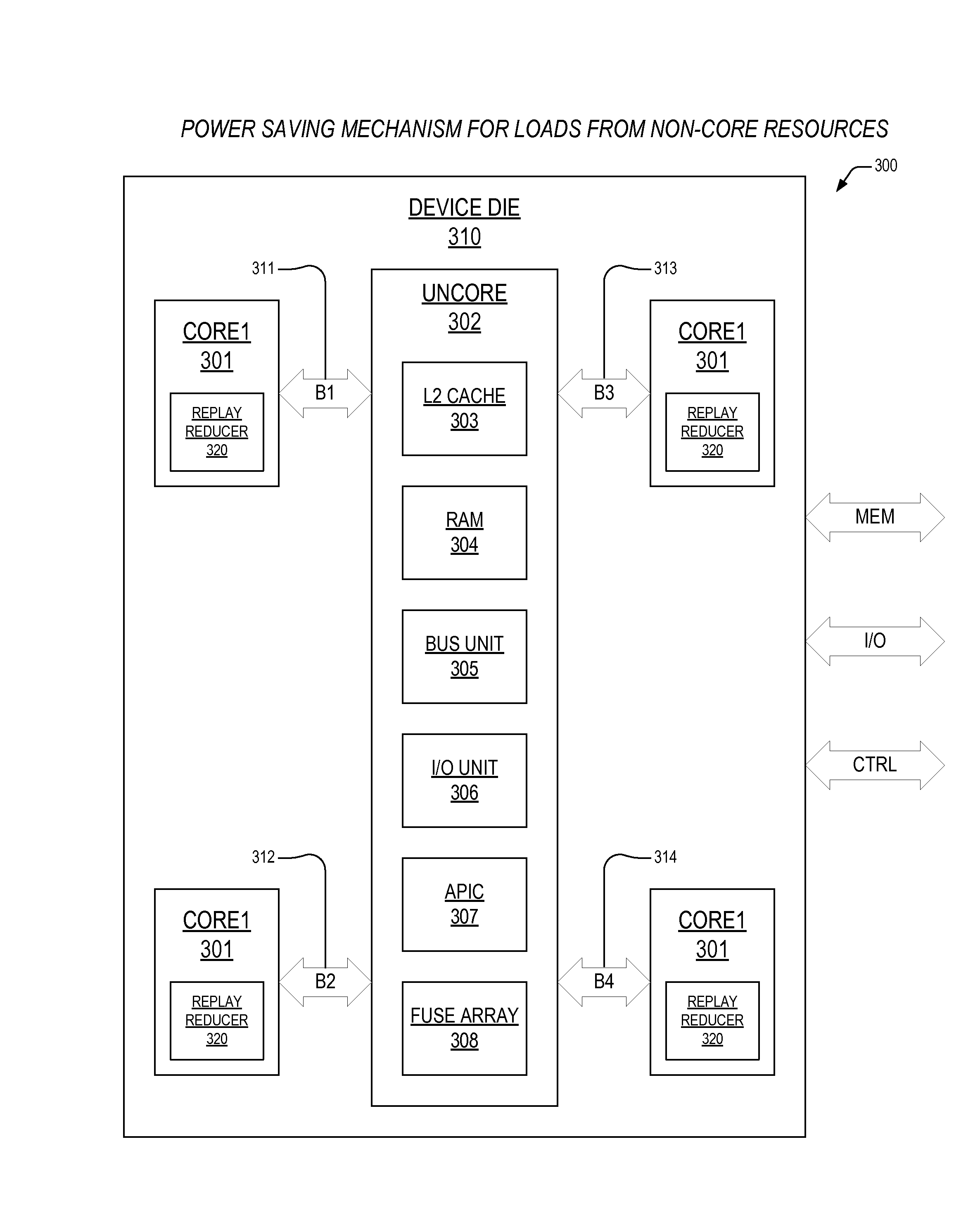

Power saving mechanism to reduce load replays in out-of-order processor

ActiveUS20160170758A1Reducing replayDigital computer detailsPower supply for data processingReservation stationOperand

Owner:VIA ALLIANCE SEMICON CO LTD

Microprocessor for neural network computing and processing method of macroinstruction

ActiveUS20190227795A1High granularity operationEasy networkingRegister arrangementsDigital data processing detailsFinite-state machineDatapath

Owner:VIA ALLIANCE SEMICON CO LTD

High reliability processor system

ActiveUS8615684B2Raise the possibilityReduce chanceError detection/correctionDigital computer detailsParallel computingDependability

A method of testing the integrity of microprogramming within a computer processor employs a test calculation designed to exercise instructions and to reveal errors in those instructions. The problem of testing instructions using the very instructions which may possibly be corrupt is addressed by developing a signature passed from instruction to instruction providing a low likelihood of a false positive outcome. A time-out system is used in the evaluation of the test calculation to capture a wide variety of other pathological operating conditions.

Owner:ASTRONAUTICS CORPORATION OF AMERICA

Aliased Parameter Passing Between Microcode Callers and Microcode Subroutines

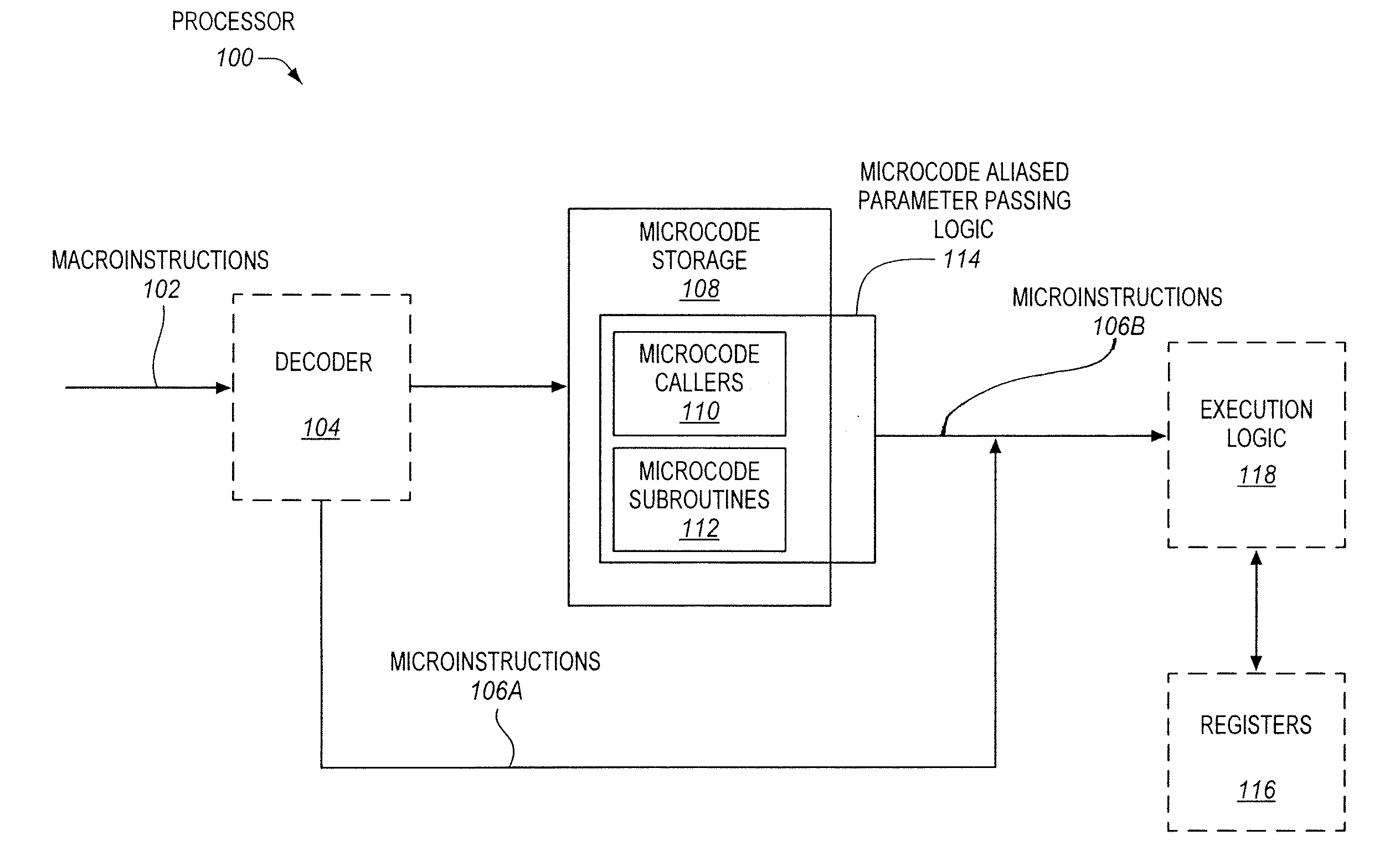

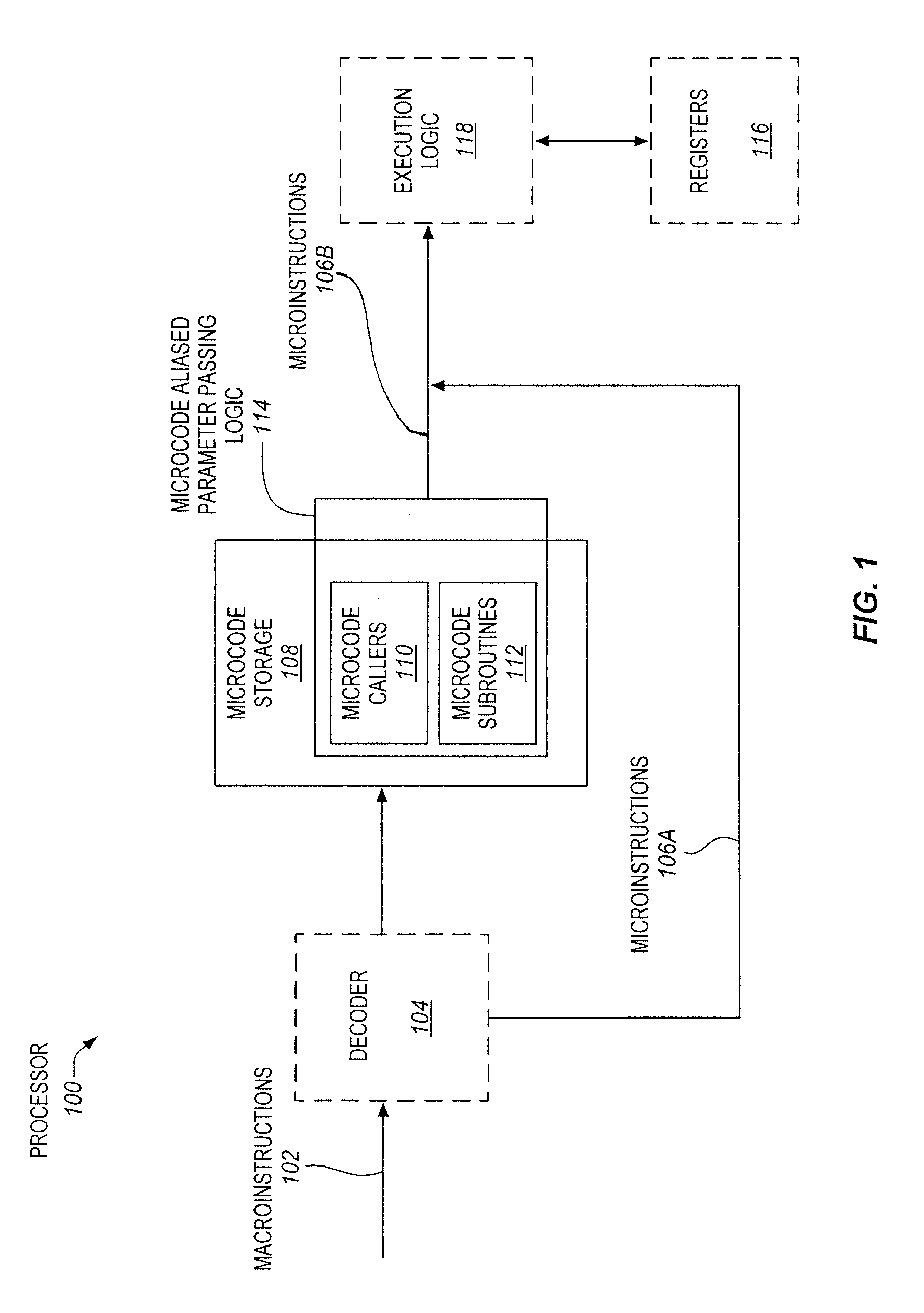

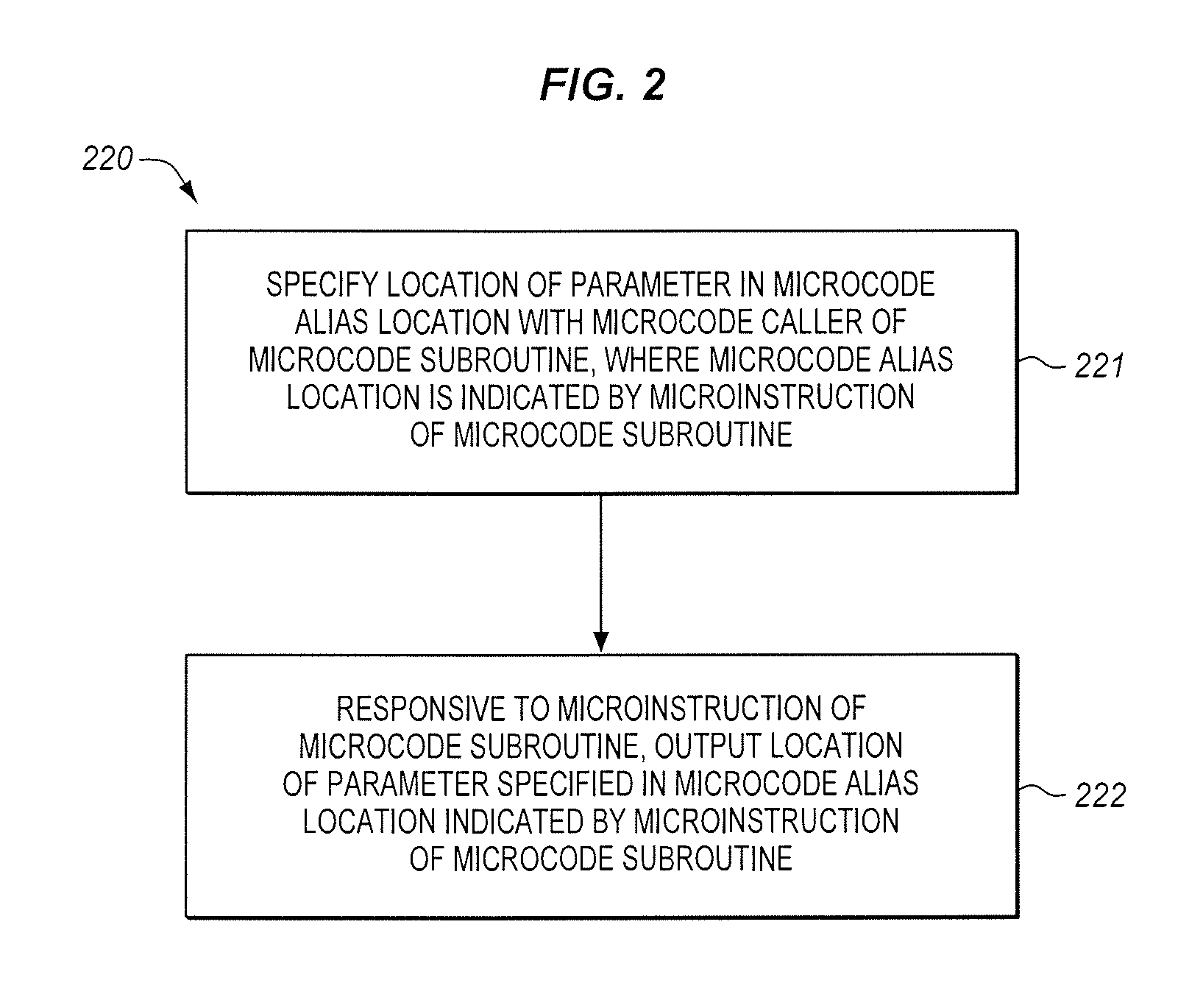

InactiveUS20120079248A1Instruction analysisDigital computer detailsComputer scienceLocation determination

An apparatus of an aspect includes a plurality of microcode alias locations and a microcode storage. A microinstruction of a microcode subroutine is stored in the microcode storage. The microinstruction has an indication of a microcode alias location. A microcode caller of the microcode subroutine is also stored in the microcode storage. The microcode caller is operable to specify a location of a parameter in the microcode alias location that is indicated by the microinstruction of the microcode subroutine. The apparatus also includes parameter location determination logic that is coupled with the microcode alias locations. The parameter location determination logic is operable, responsive to the microinstruction of the microcode subroutine, to receive the indication of the microcode alias location from the microinstruction and determine the location of the parameter specified in the microcode alias location indicated by the microinstruction.

Owner:INTEL CORP

Systems and methods for selectively enabling and disabling hardware features

InactiveUS20160246596A1Specific access rightsError detection/correctionProgram instructionMultiple criteria

In one embodiment, a computer program product includes a computer readable storage medium having stored / encoded thereon: first program instructions executable by a device to cause the device to define a hardware feature policy for one or more hardware components of a system; and second program instructions executable by the device to cause the device to enable and / or disabling one or more hardware features of one or more of the hardware components based on the hardware feature policy, where the hardware feature policy comprises instructions to enable and / or disable access to the one or more hardware features based on one or more criteria.

Owner:INT BUSINESS MASCH CORP

Mechanism to preclude i/o-dependent load replays in an out-of-order processor

ActiveUS20160342414A1Reducing replayMemory architecture accessing/allocationDigital computer detailsReservation stationOperand

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include an input / output (I / O) unit, configured to perform I / O operations via an I / O bus coupling an out-of-order processor to I / O resources.

Owner:VIA ALLIANCE SEMICON CO LTD

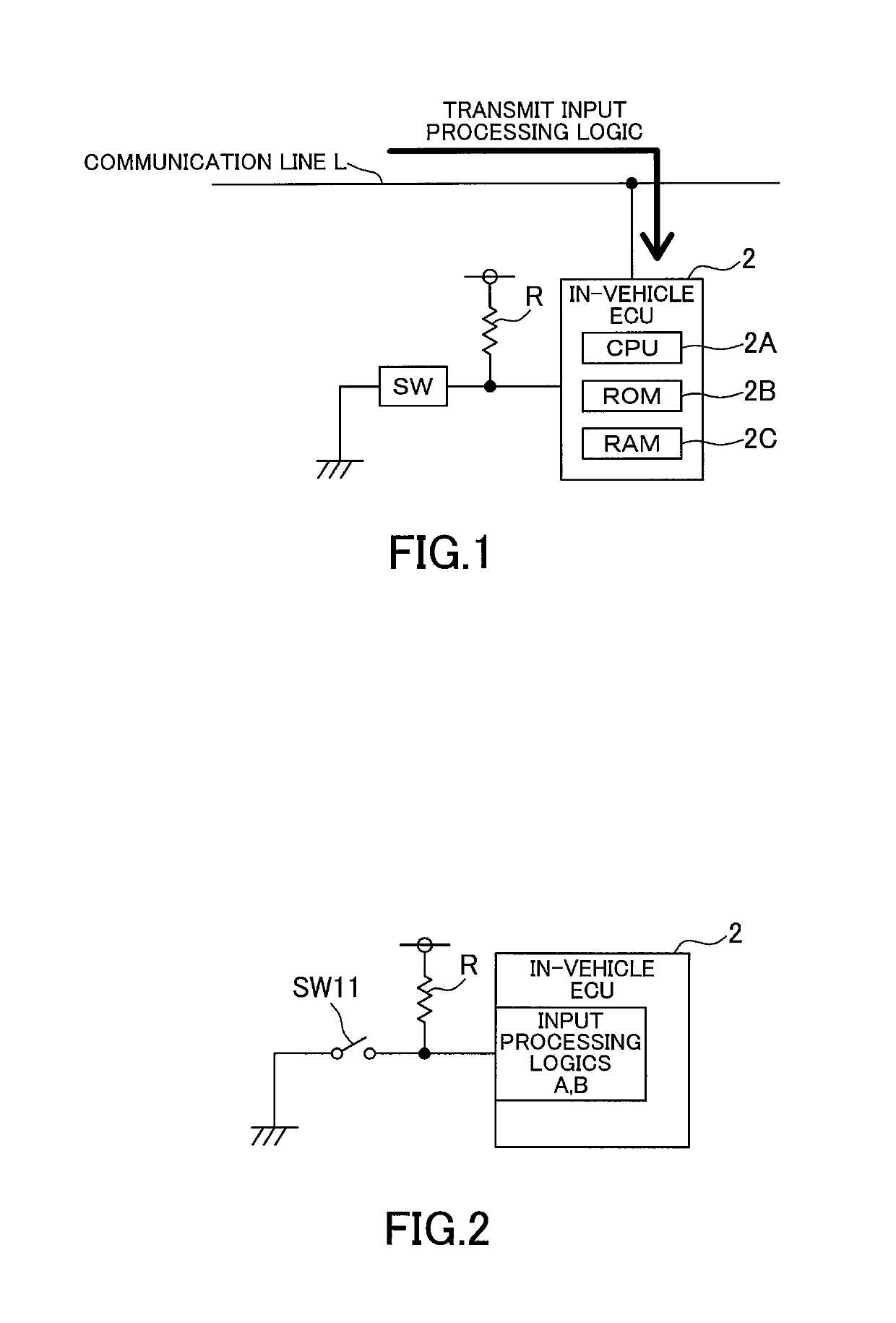

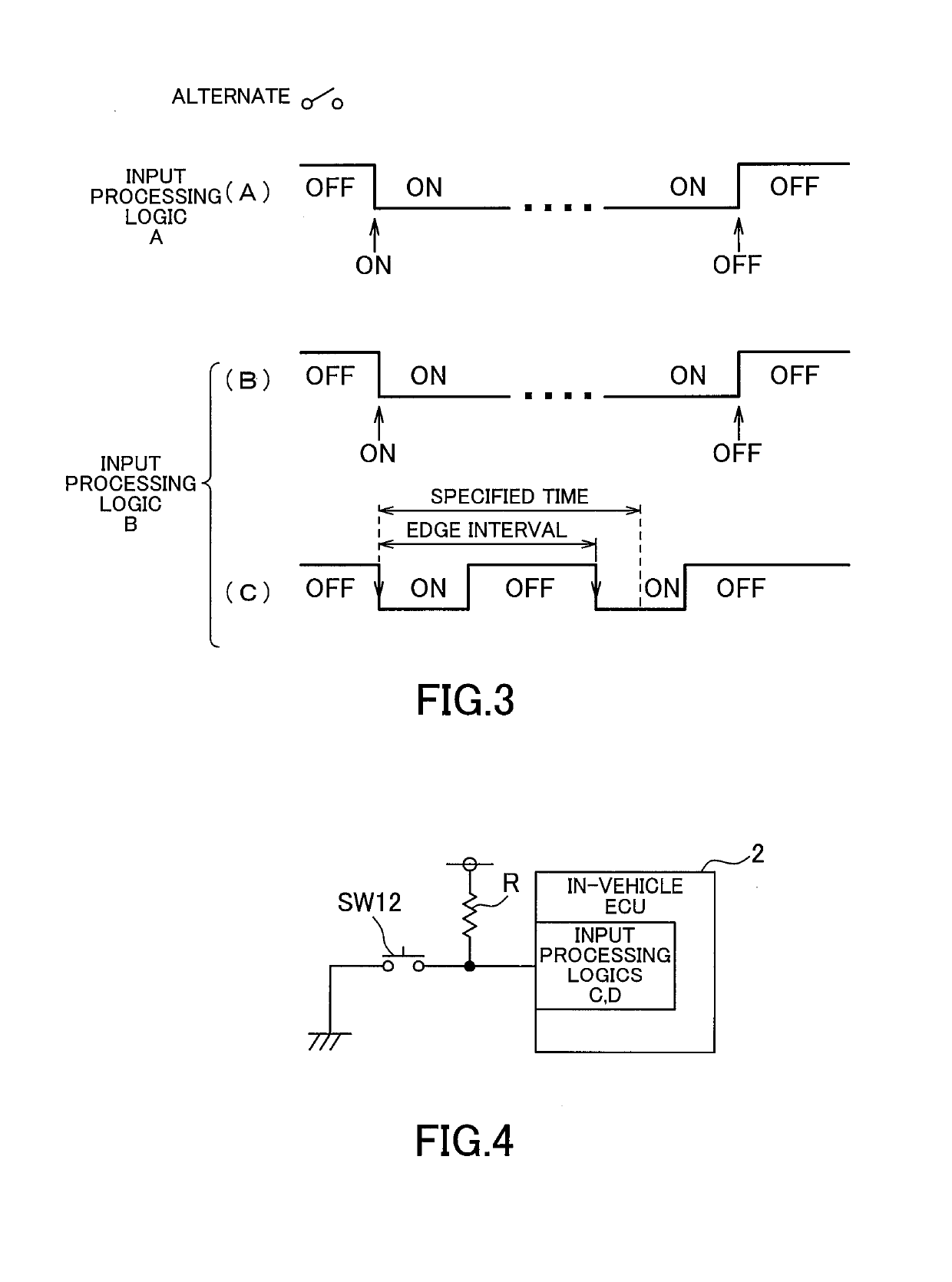

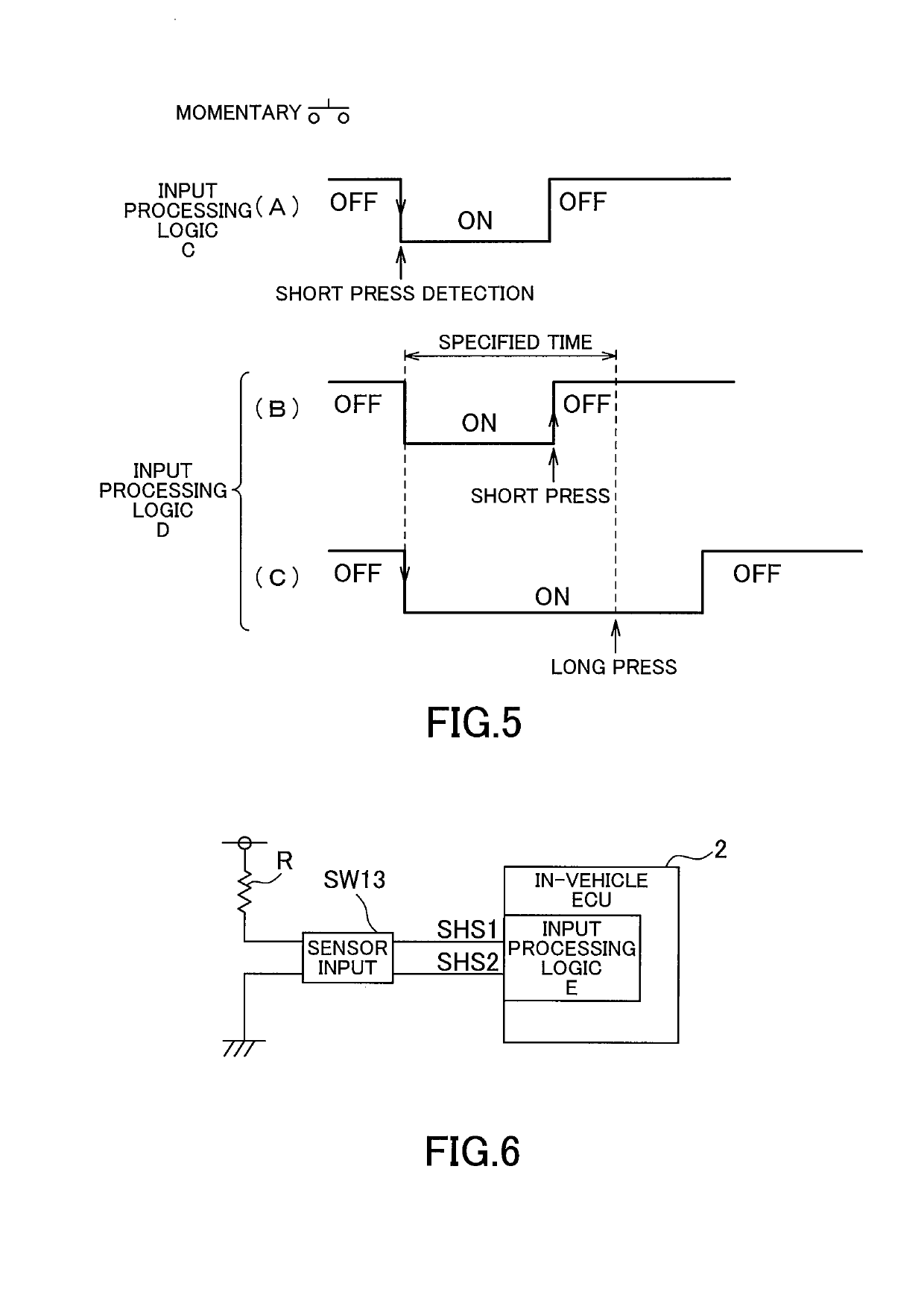

Arithmetic unit

ActiveUS20190171614A1Reduce the number of partsInput/output for user-computer interactionDigital data processing detailsArithmetic logic unit

Provided is an arithmetic processing to reduce a number of parts as it is not necessary to prepare an operation device for each input processing logic. A plurality of types of input processing logics is stored in the ROM, and CPU selects one of the plurality of types of input processing logics and executes input processing according to the selected input processing logic. As a result, there is no need to prepare the ECU for each input processing logic, reducing the number of parts.

Owner:YAZAKI CORP

Popular searches

Memory systems Computation using denominational number representation Data switching networks Software deployment Microprogram loading General purpose stored program computer Internal/peripheral component protection Machine execution arrangements Memory adressing/allocation/relocation Physical realisation