Patents

Literature

33results about How to "Limited support" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

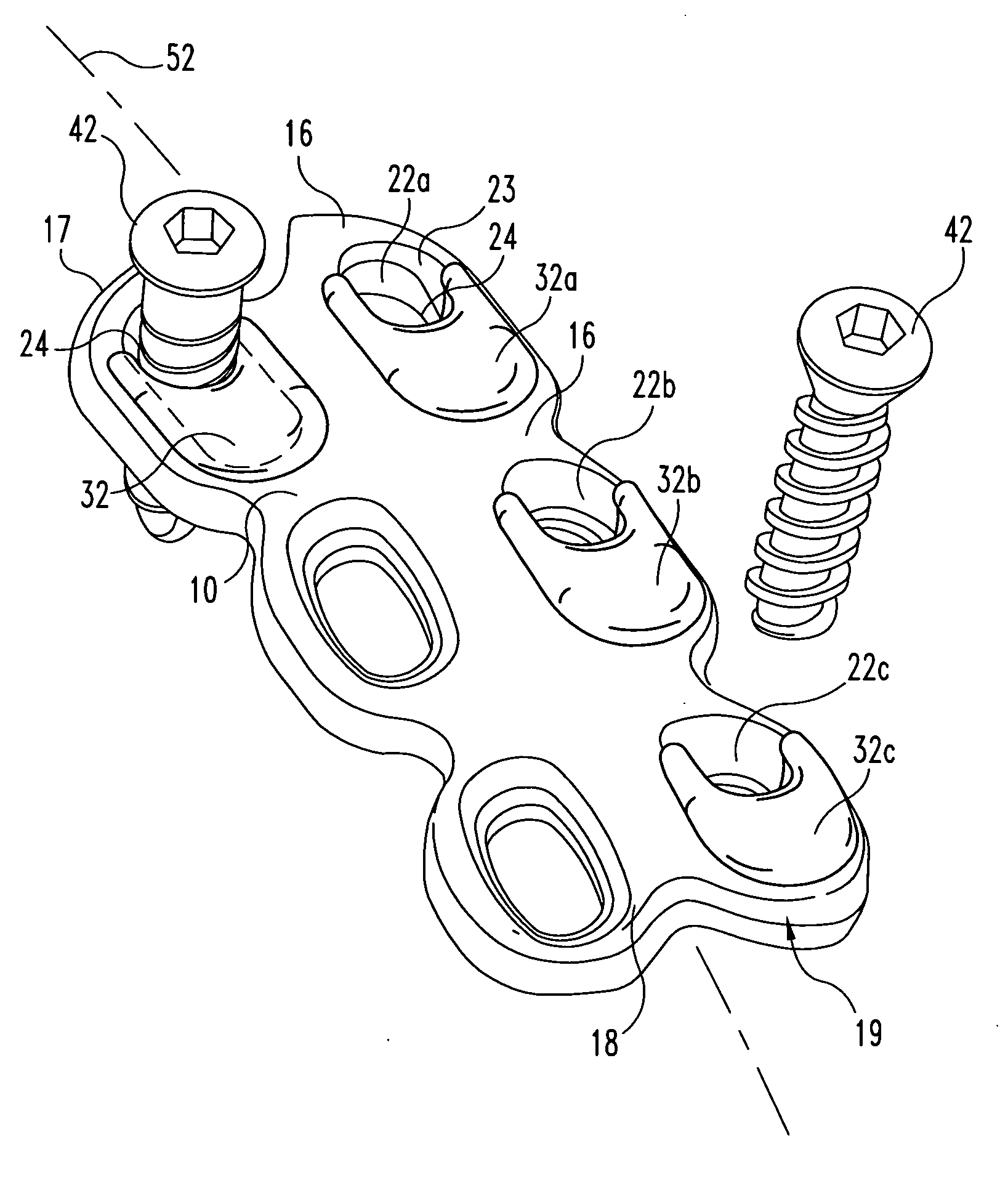

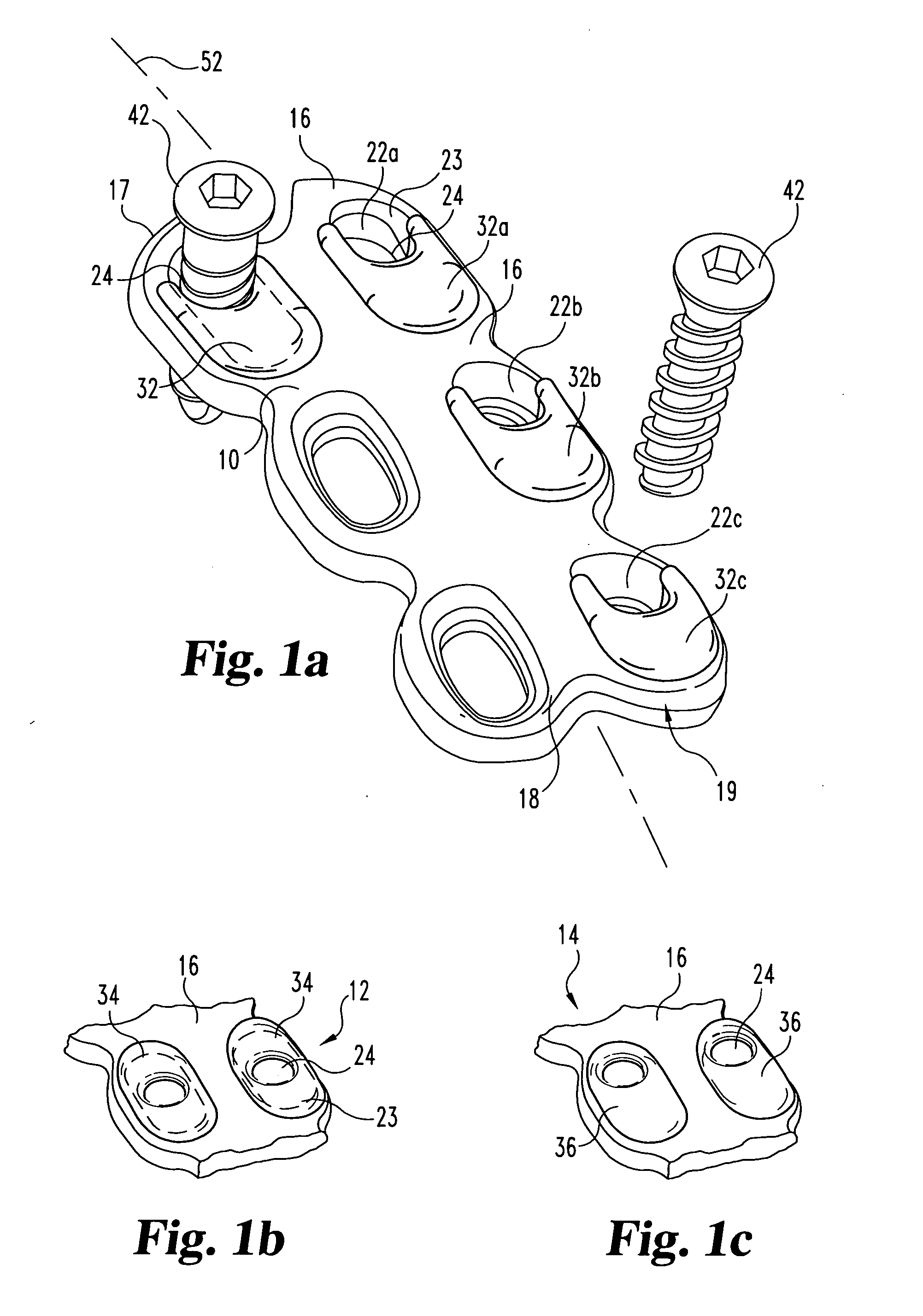

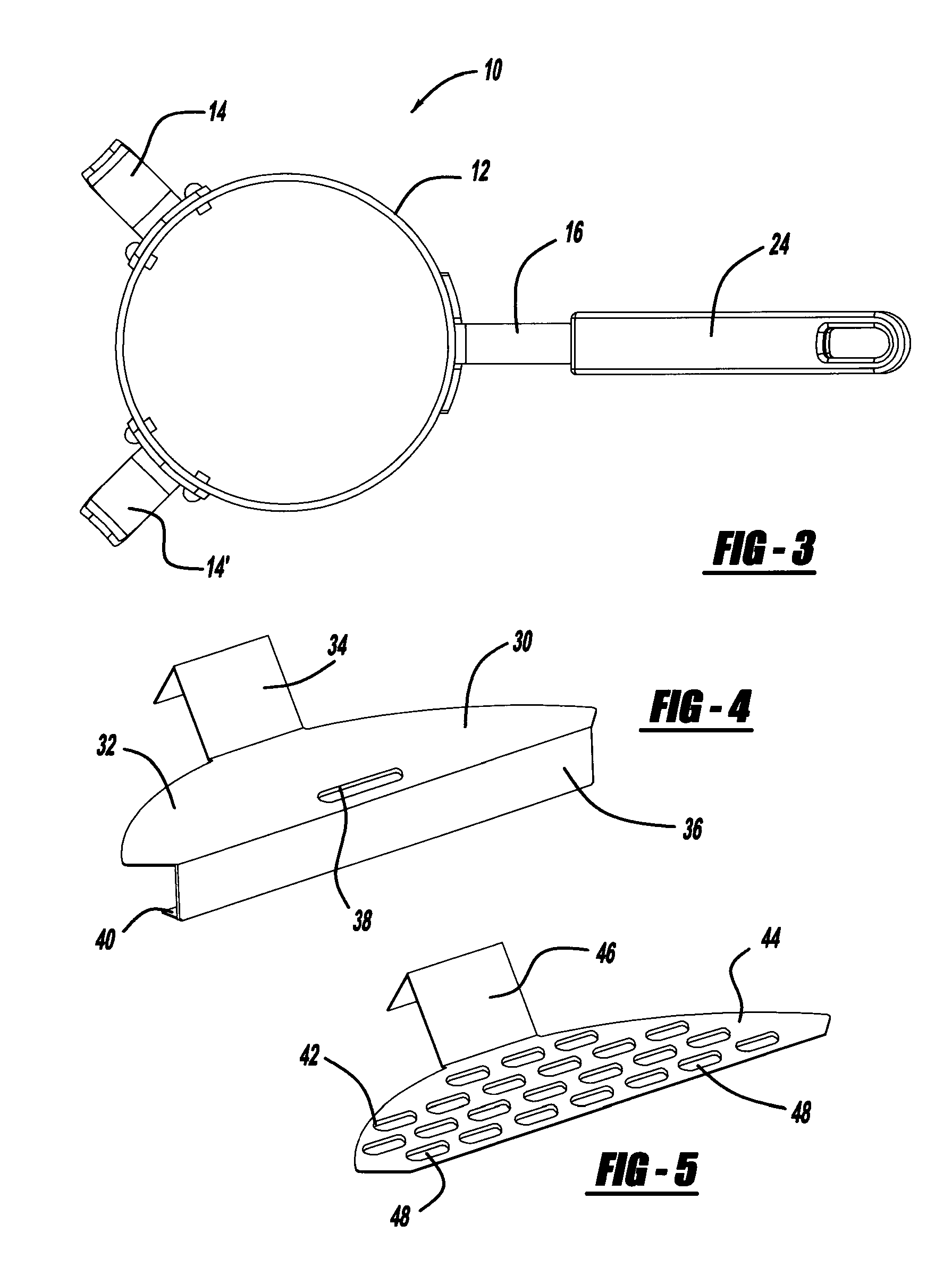

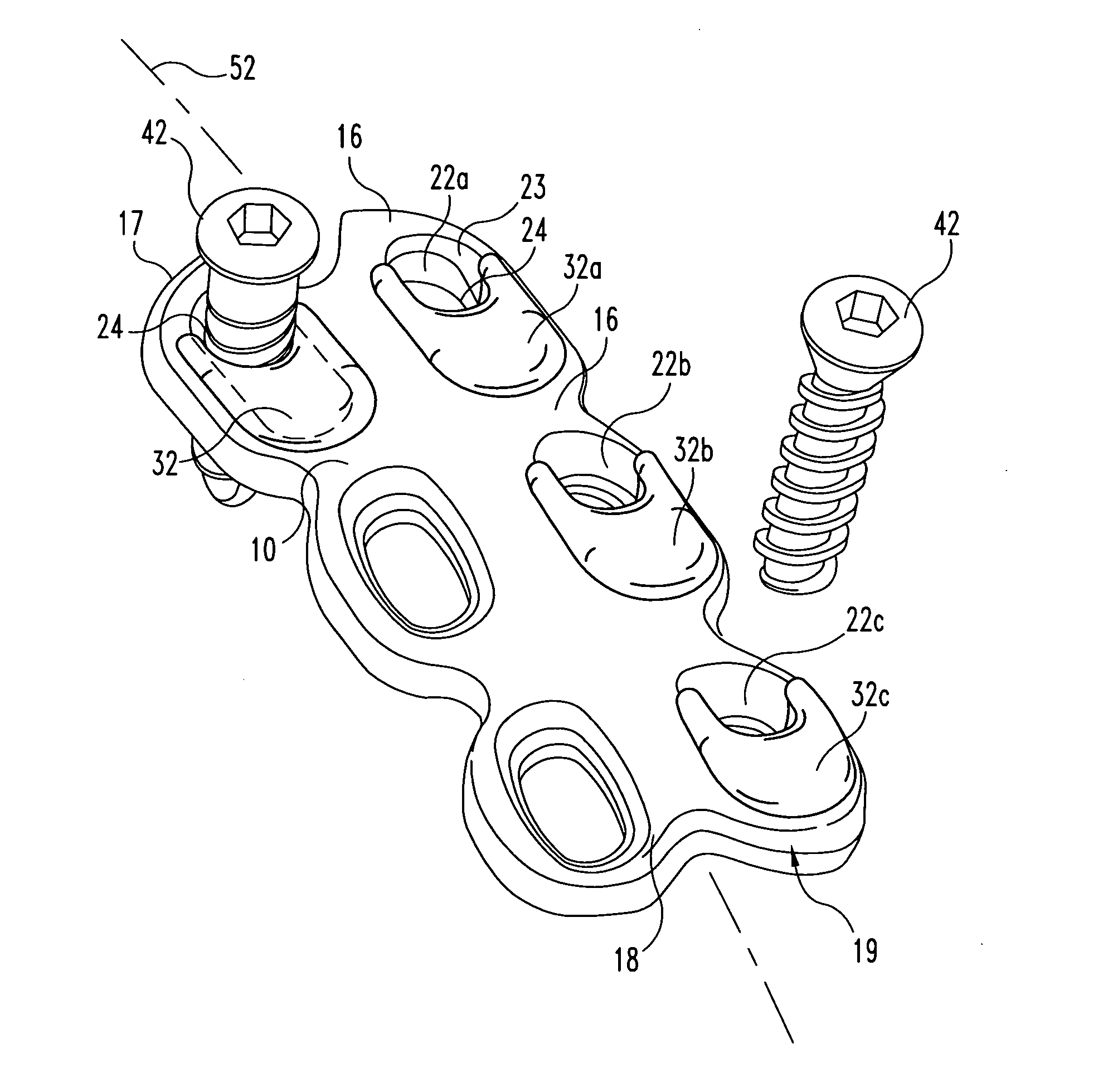

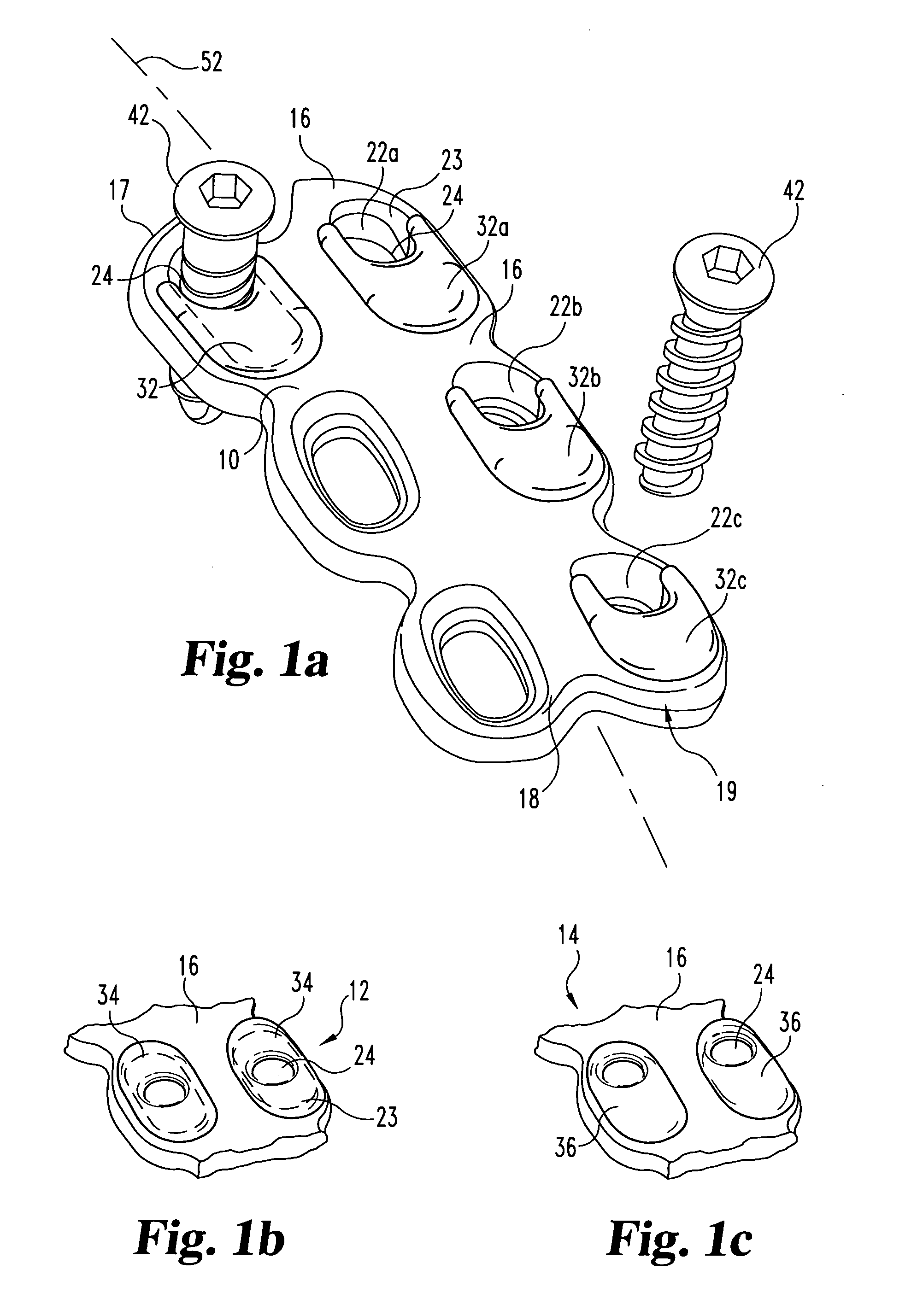

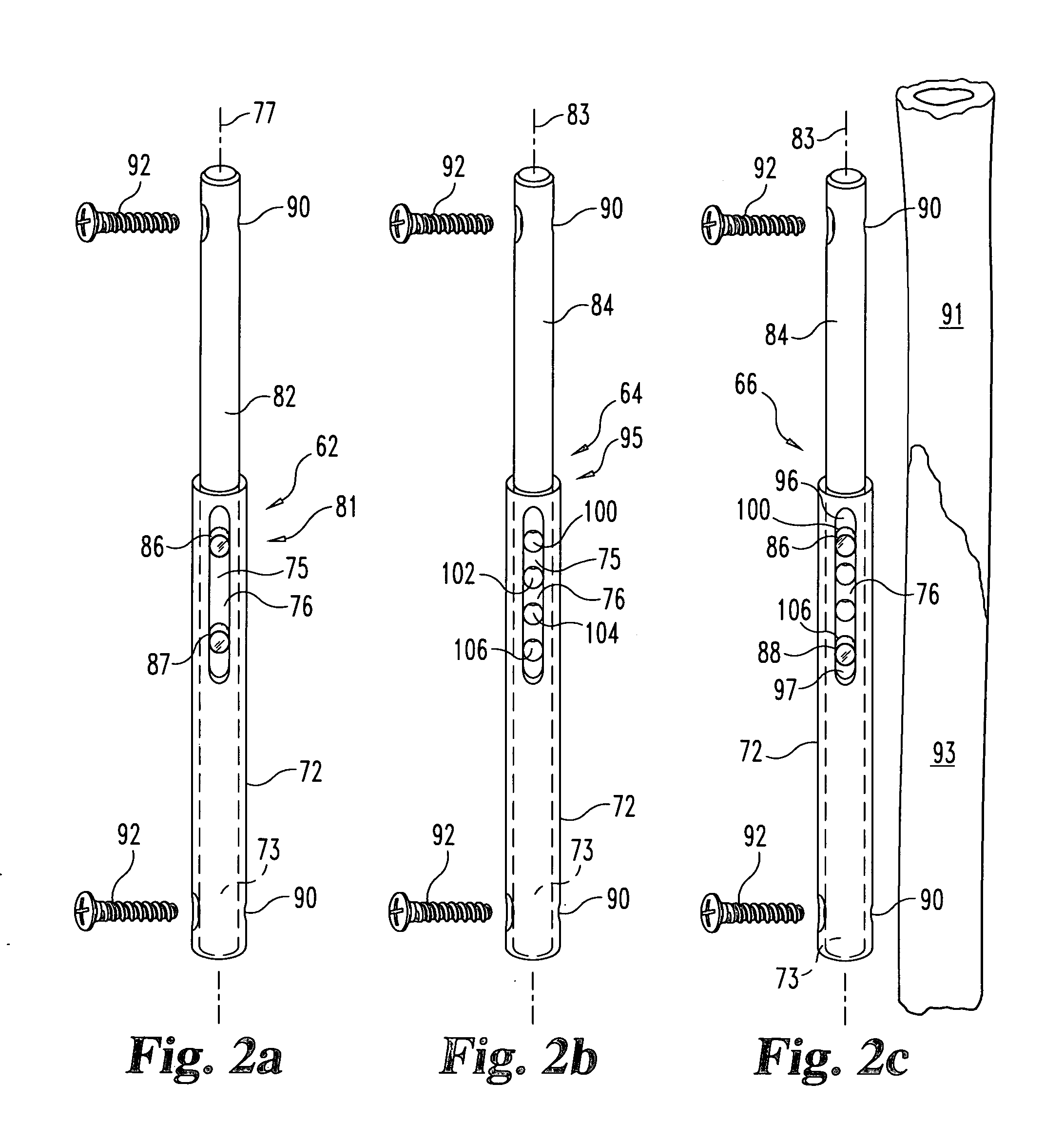

Apparatus and method for providing dynamizable translations to orthopedic implants

InactiveUS20050085812A1Avoid stress shieldingLimited supportSuture equipmentsInternal osteosythesisBone structureJoint arthrodesis

The present invention generally relates to orthopedic devices and methods for treating bone defects. The orthopedic devices can provide sufficient support to the bone defect while allowing bone ingrowth and minimizing the risk to stress shield and / or pseudo-arthrodesis. The bone fixation devices include a biodegradable material or component that further resists relative motion of attached bones and allows the device to gradually transfer at least some load from the device to the growing bone structure in vivo and permitting an increase in the relative motion of bones attached to the device.

Owner:WARSAW ORTHOPEDIC INC

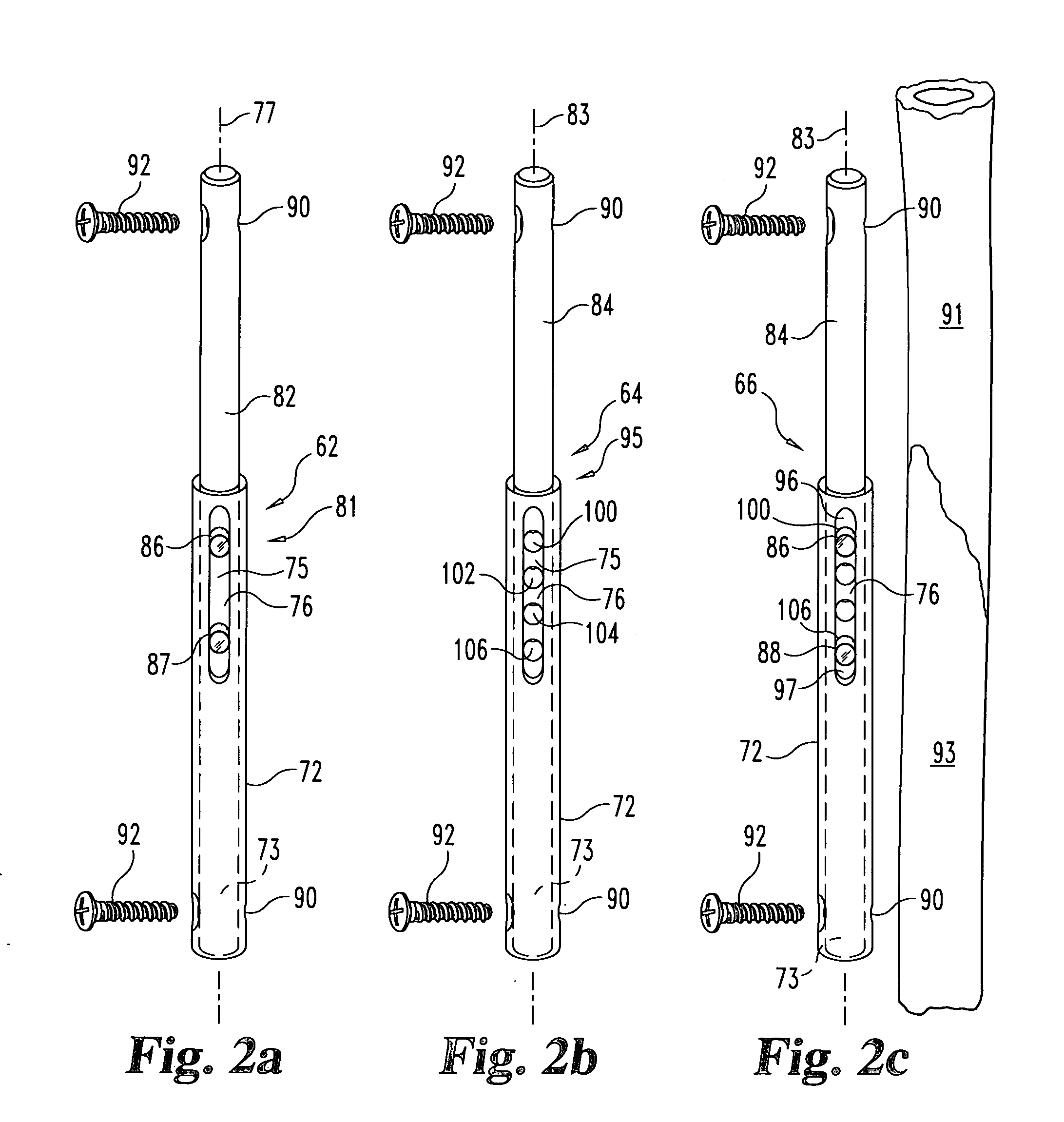

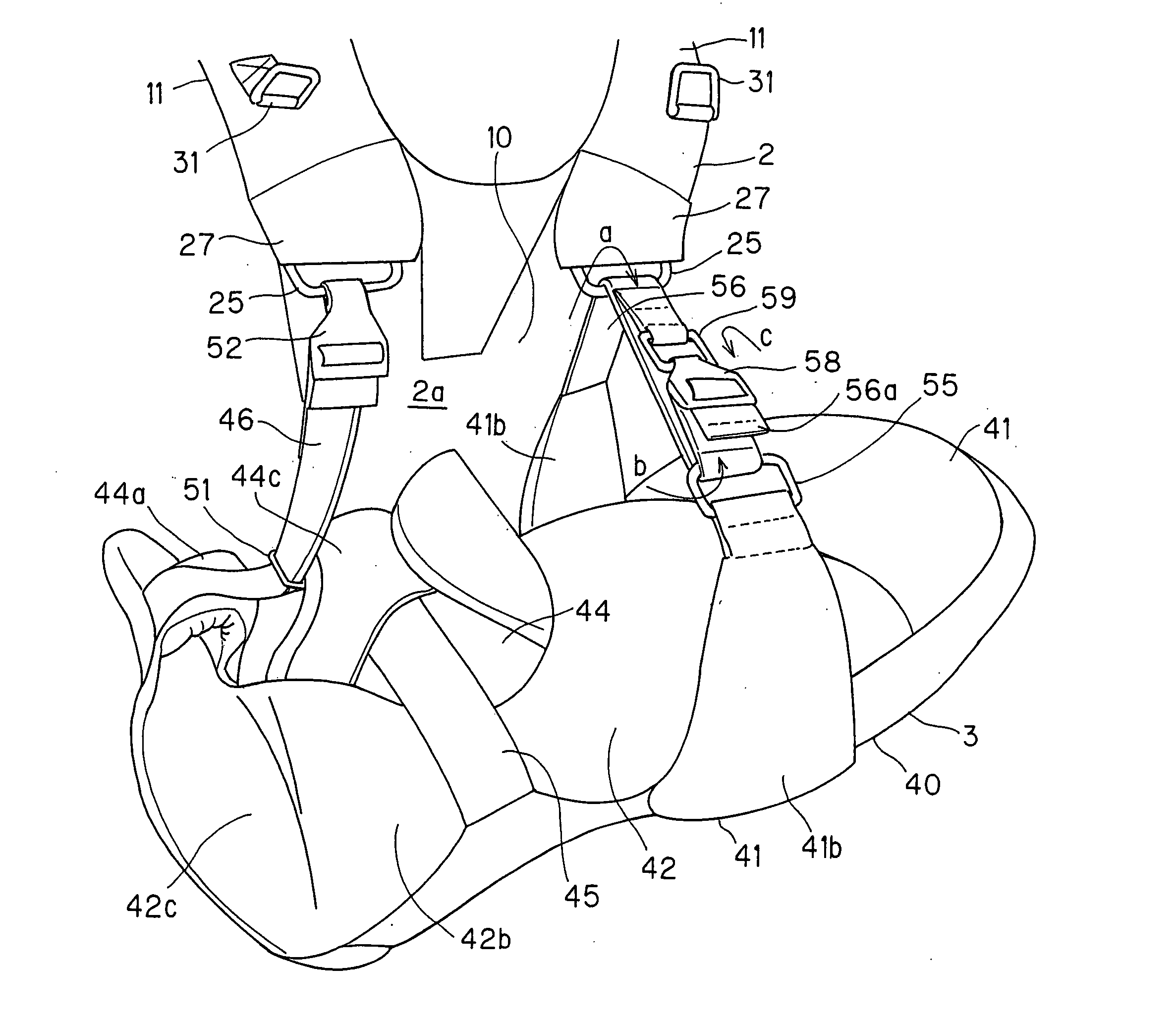

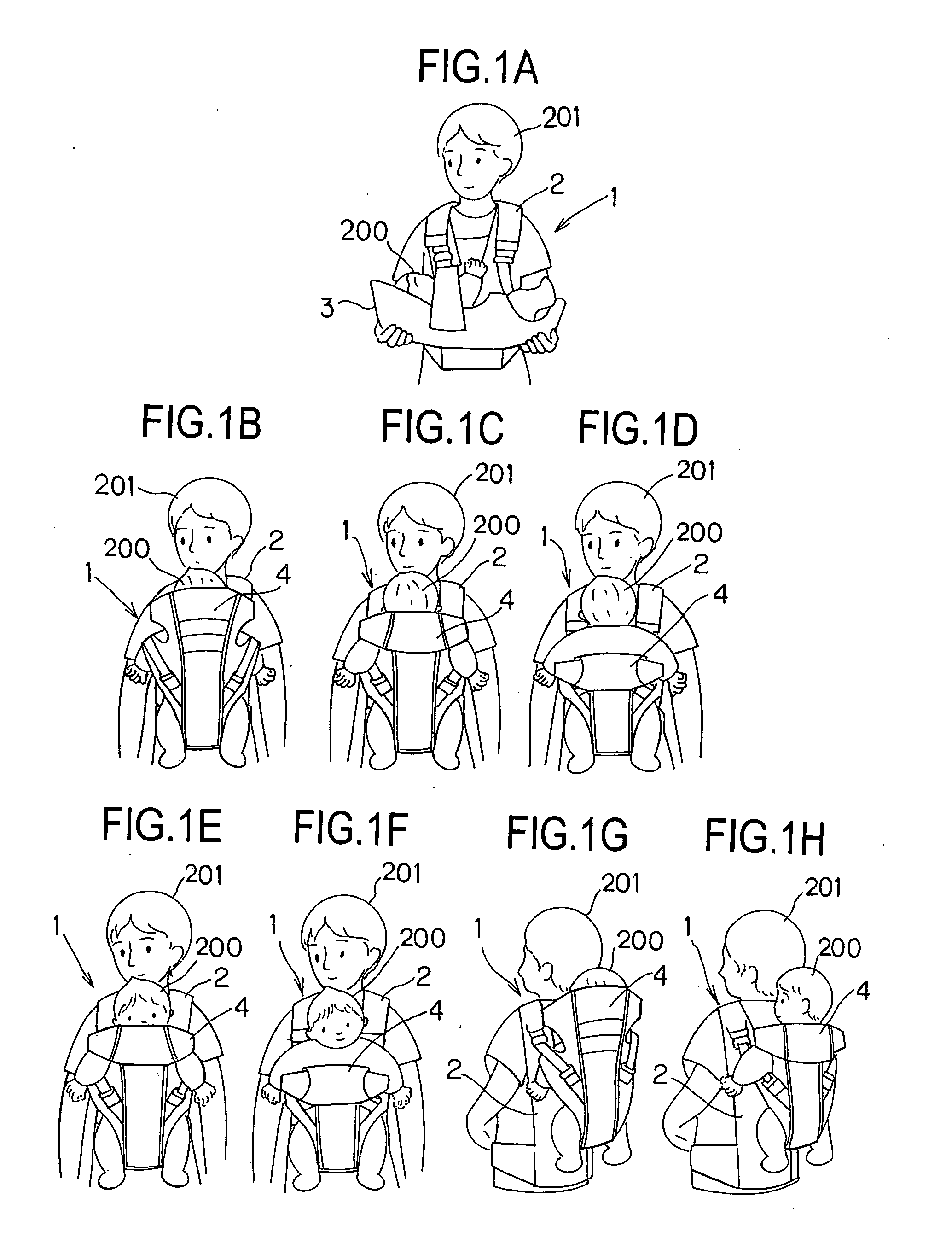

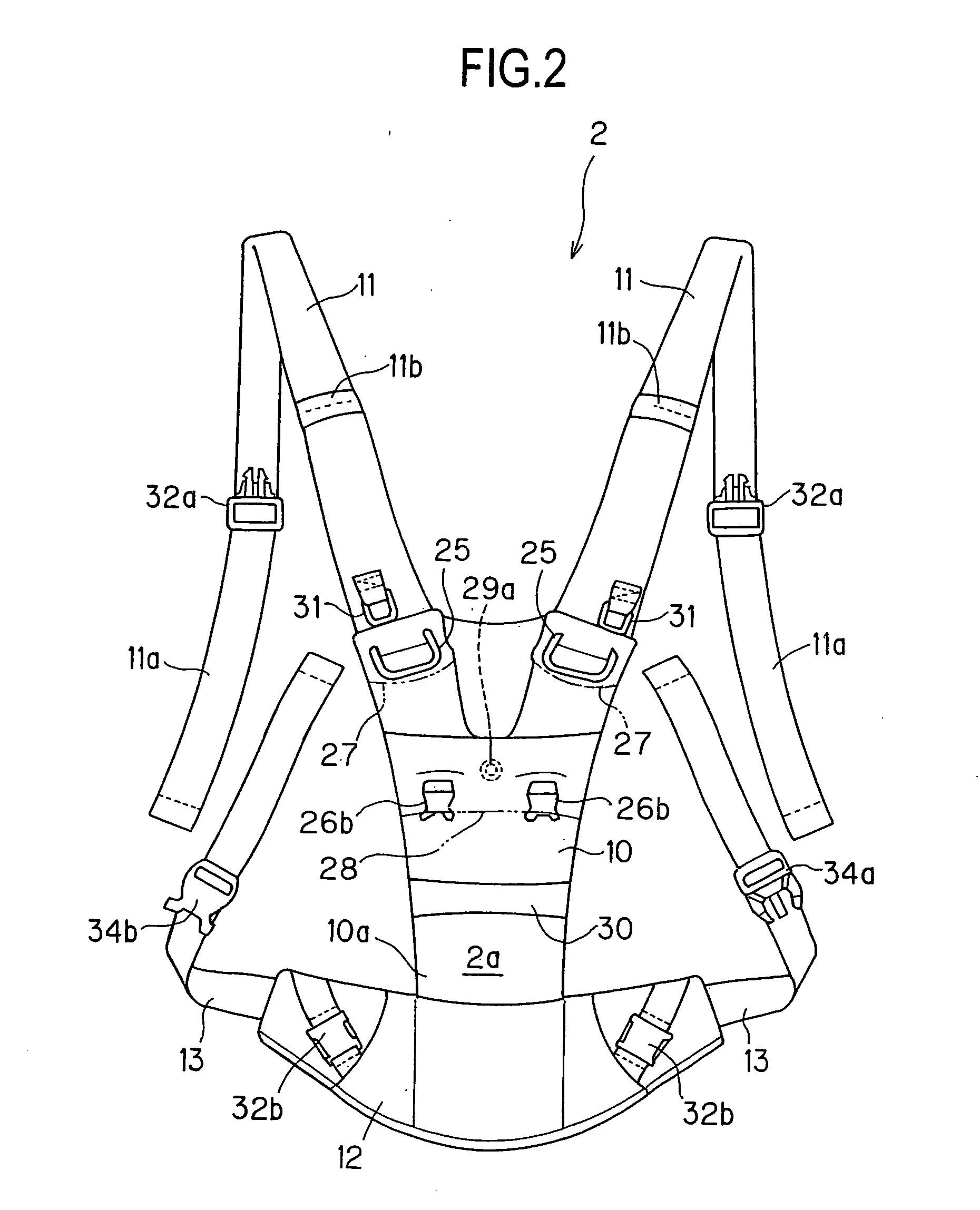

Baby band

InactiveUS20070029356A1Limited supportEasy to distinguishStretcherWheelchairs/patient conveyanceEngineeringFull Term Infant

Owner:COMBI CORP

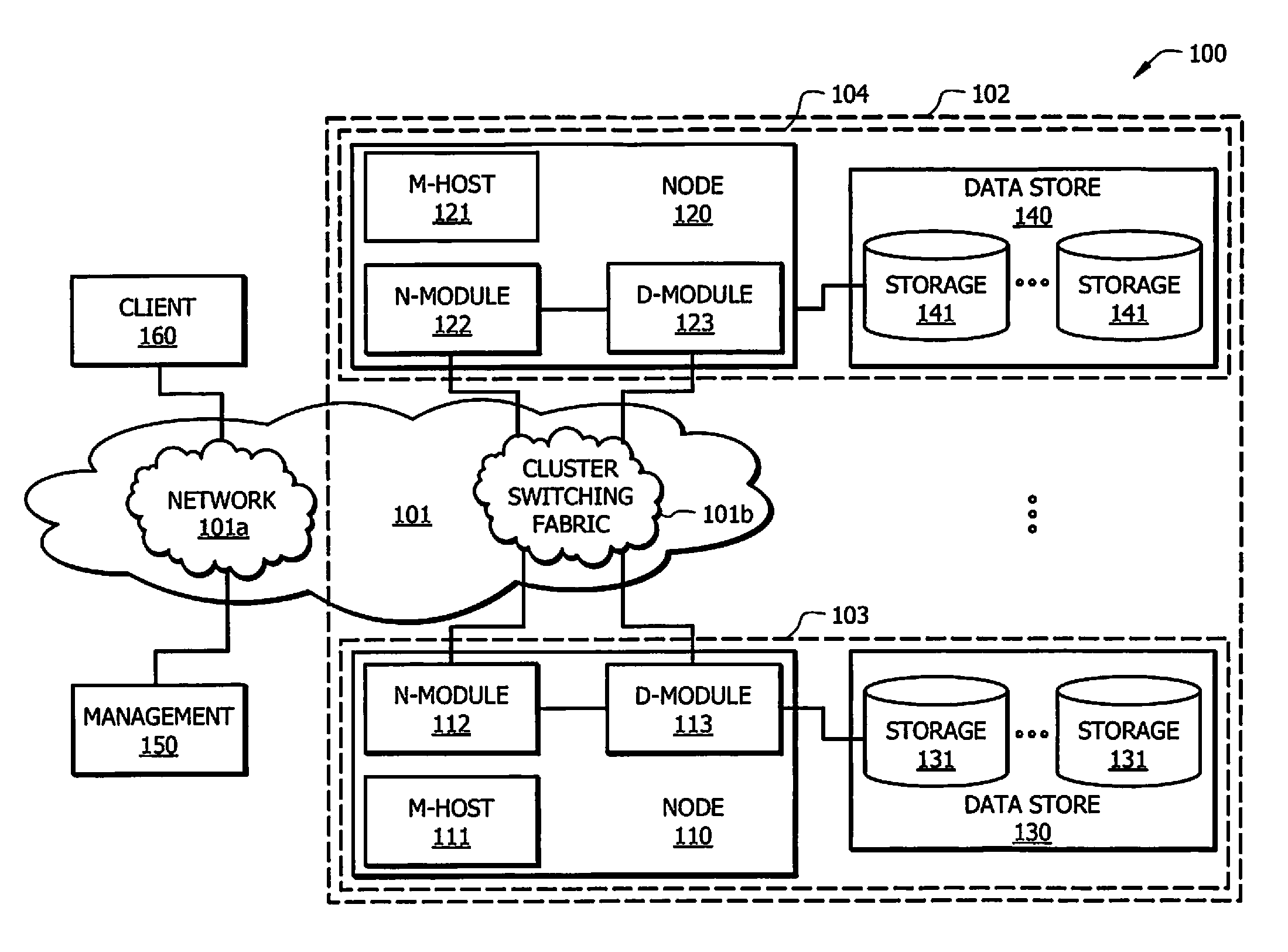

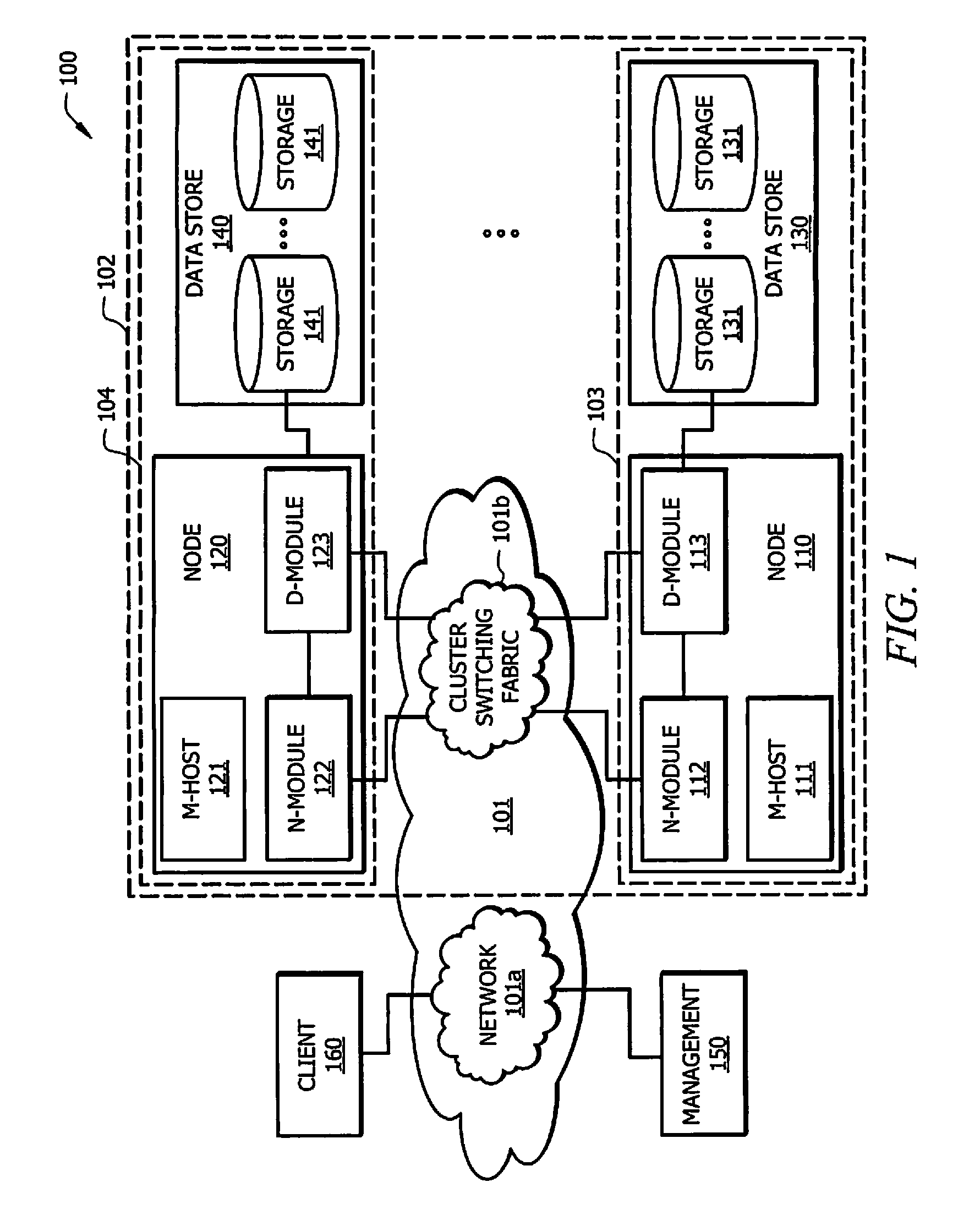

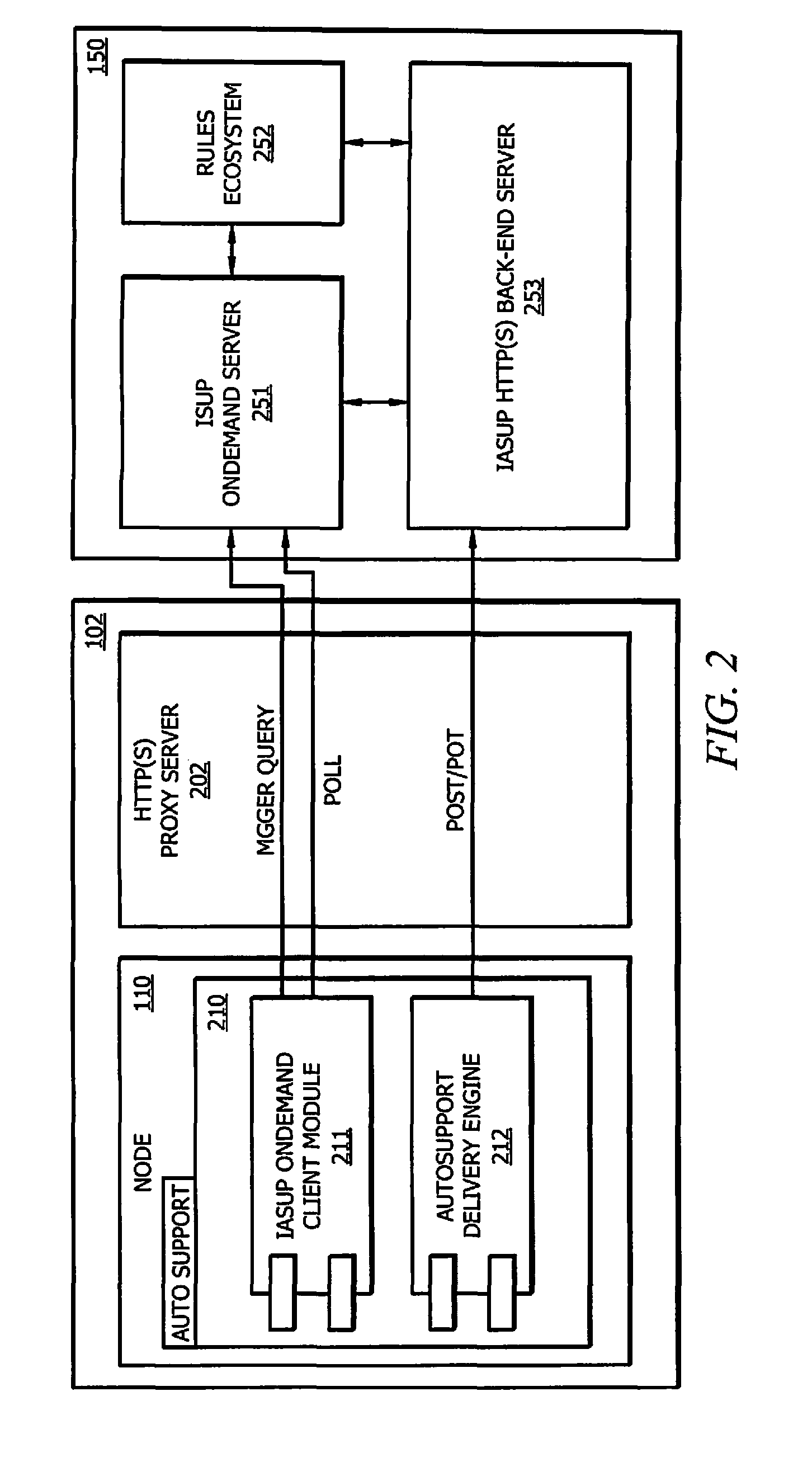

Systems and methods for providing intelligent automated support capable of self rejuvenation with respect to storage systems

ActiveUS8825752B1Facilitate IASUPEasy to collectMemory loss protectionError detection/correctionEnd systemHybrid storage system

Systems and methods which provide an intelligent automated support (IASUP) architecture in which logic is implemented to control support messaging in an automatic, timely, and meaningful fashion to imbibe intelligent automated support functionality are disclosed. Embodiments of an IASUP architecture implement bidirectional communication links between storage systems and IASUP back-end systems providing data collection. The bidirectional communication links supported by IASUP architectures of embodiments facilitate automated storage system rejuvenation functionality whereby an IASUP back-end system provides processing and analysis with respect to storage system data to initiate manipulation or control of one or more components of a storage system.

Owner:NETWORK APPLIANCE INC

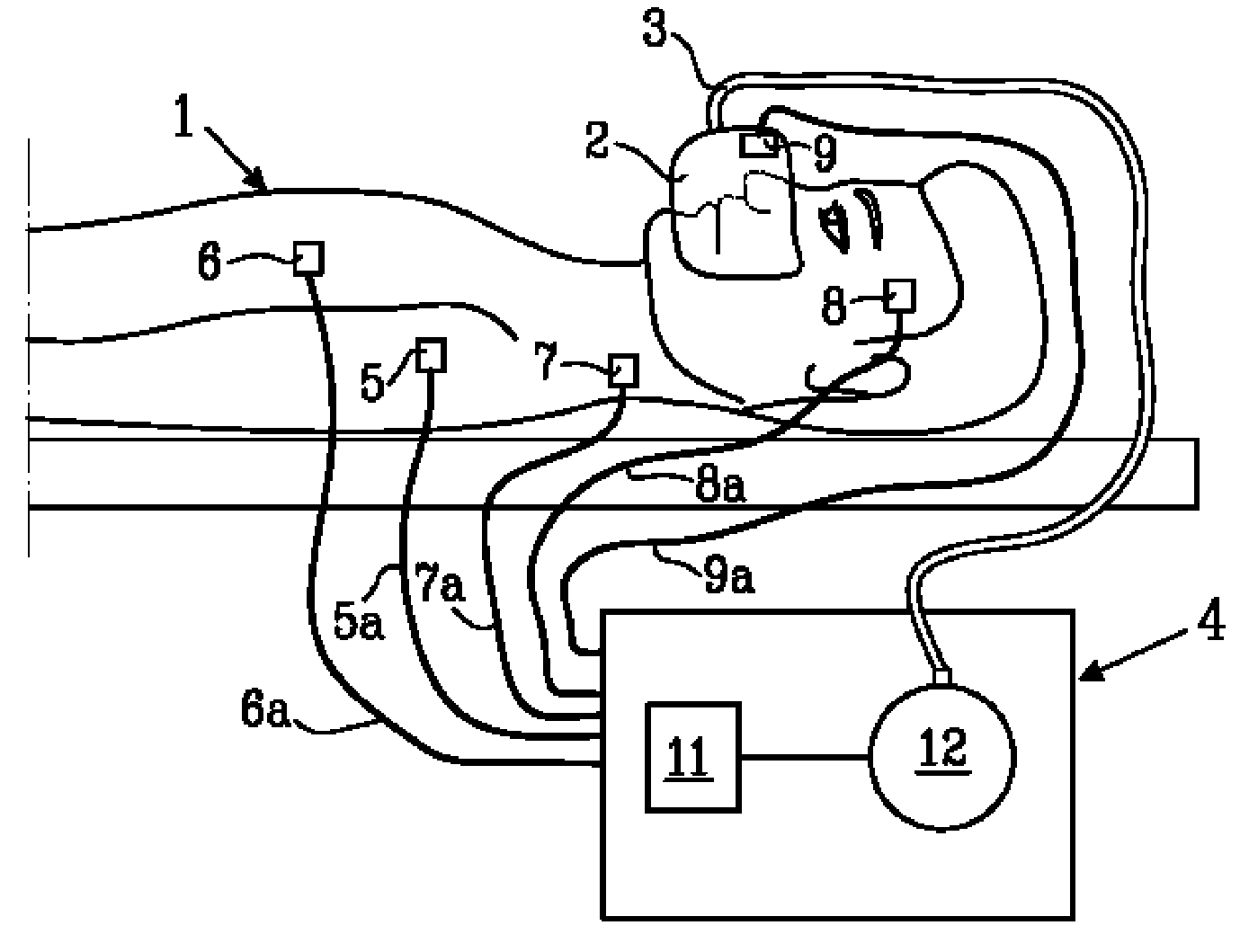

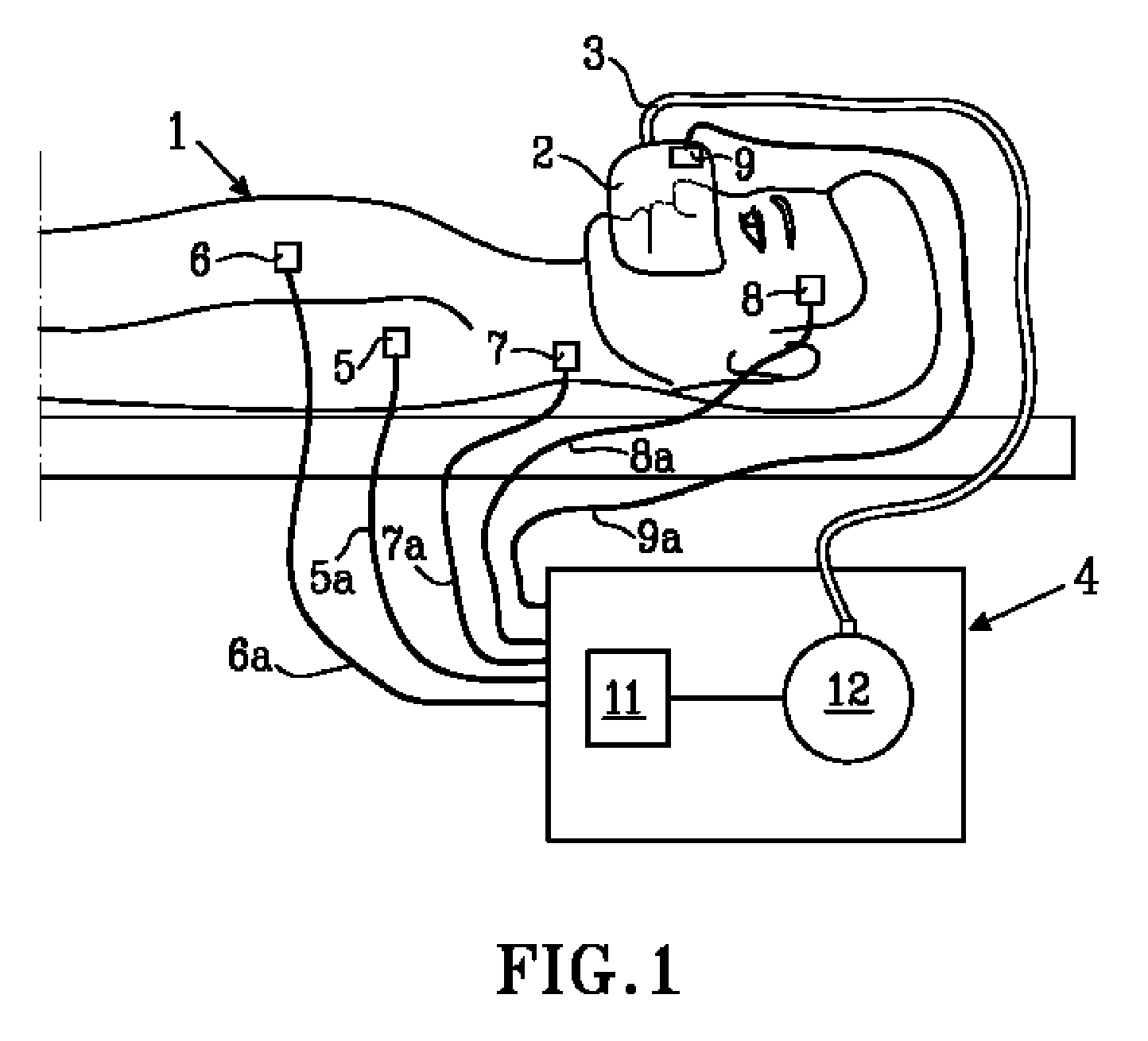

Multilevel Ventilator

InactiveUS20080257349A1Increase effectivenessIncrease therapy comfortBioelectric signal measurementMechanical/radiation/invasive therapiesTraffic volumeBreathing disorders

A method and apparatus for detecting breathing disorders and controlling a breathing ventilator using an artificial neural network working on signals indicative of a patient's physiological status. Preferably the artificial neural network works on a signal indicative of the pressure or flow of supplied breathing gas divided into two or more intervals (401, 402, 403, 404) indicative of patient (1) breathing cycle phases.

Owner:GENERAL ELECTRIC CO

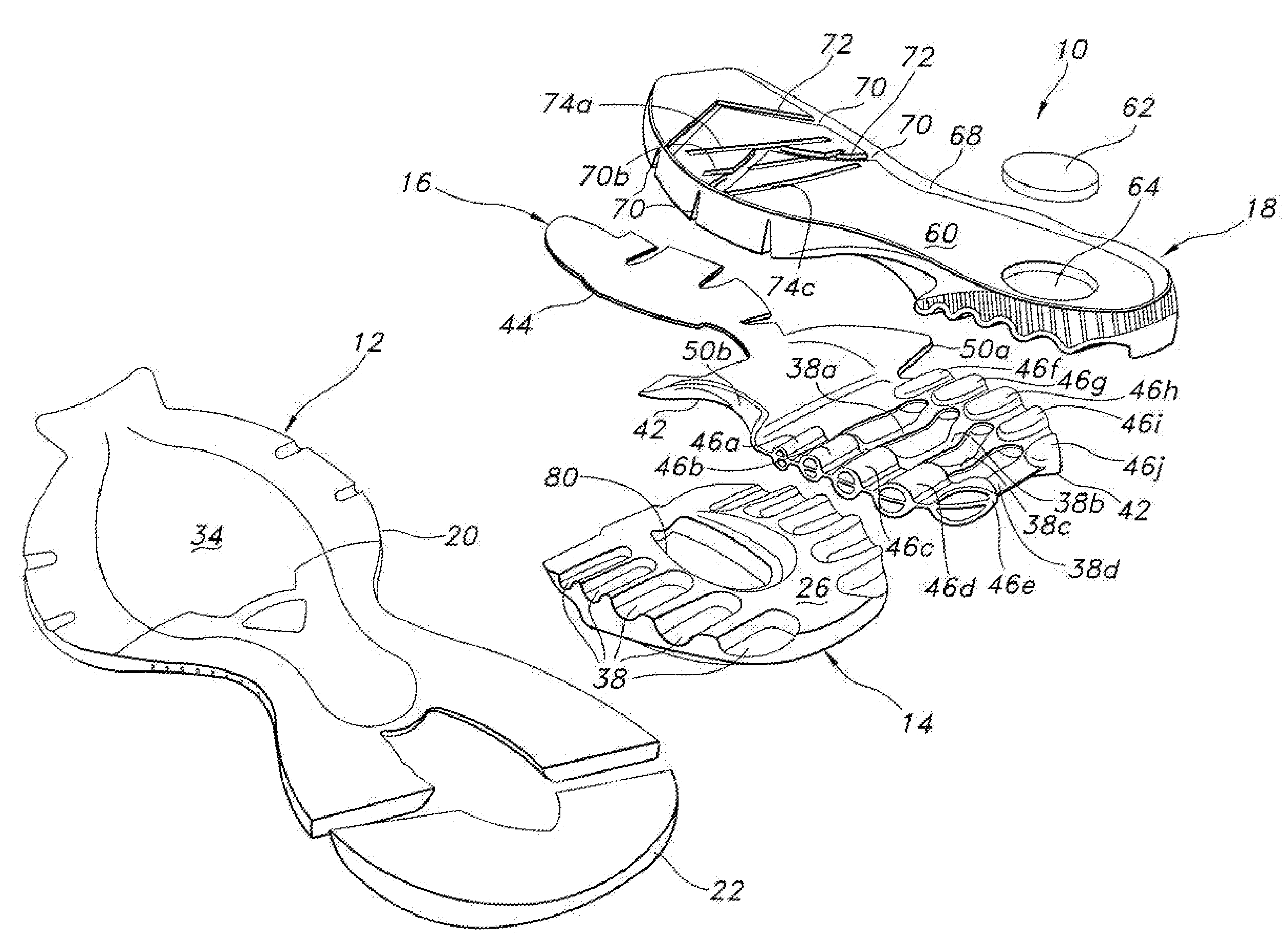

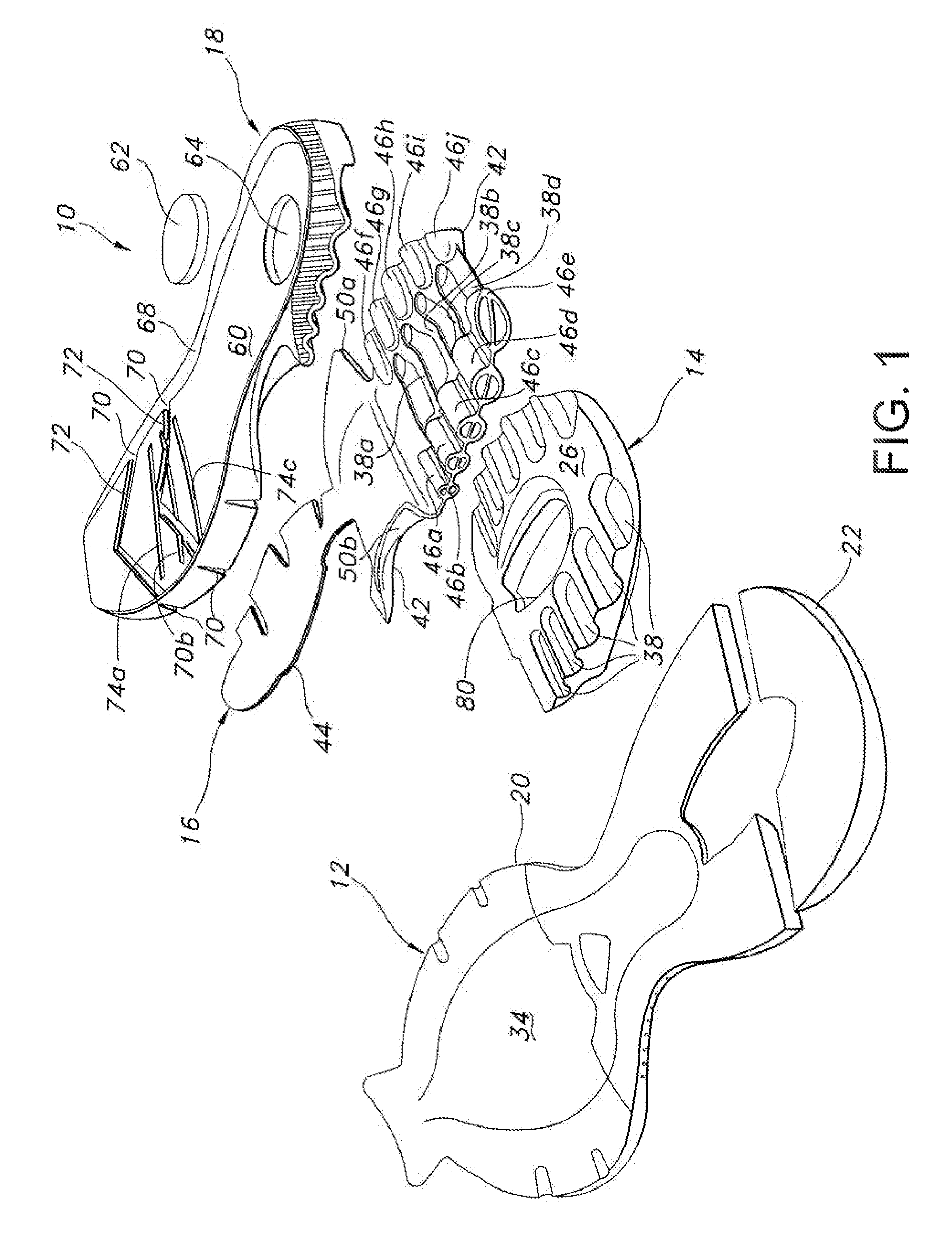

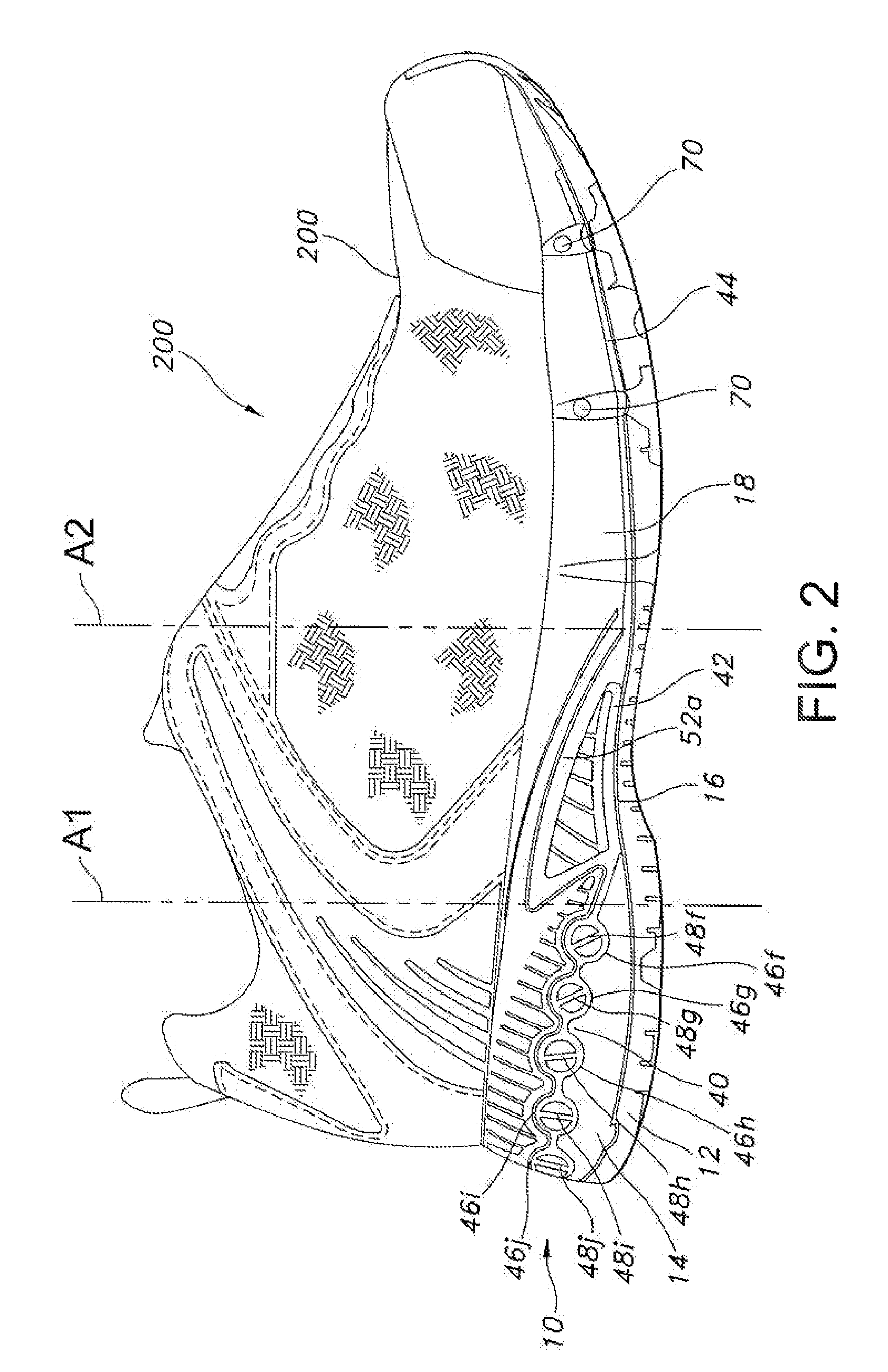

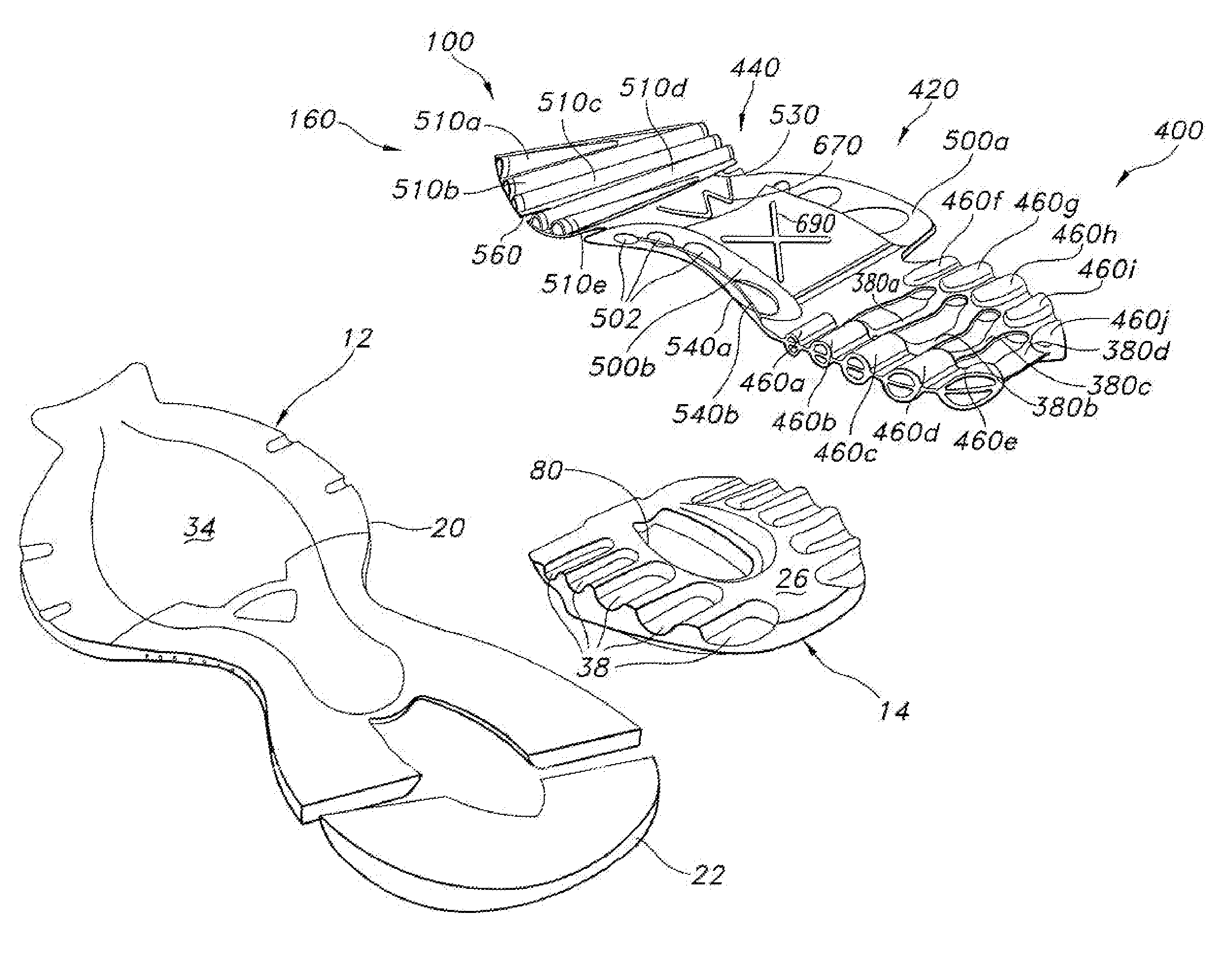

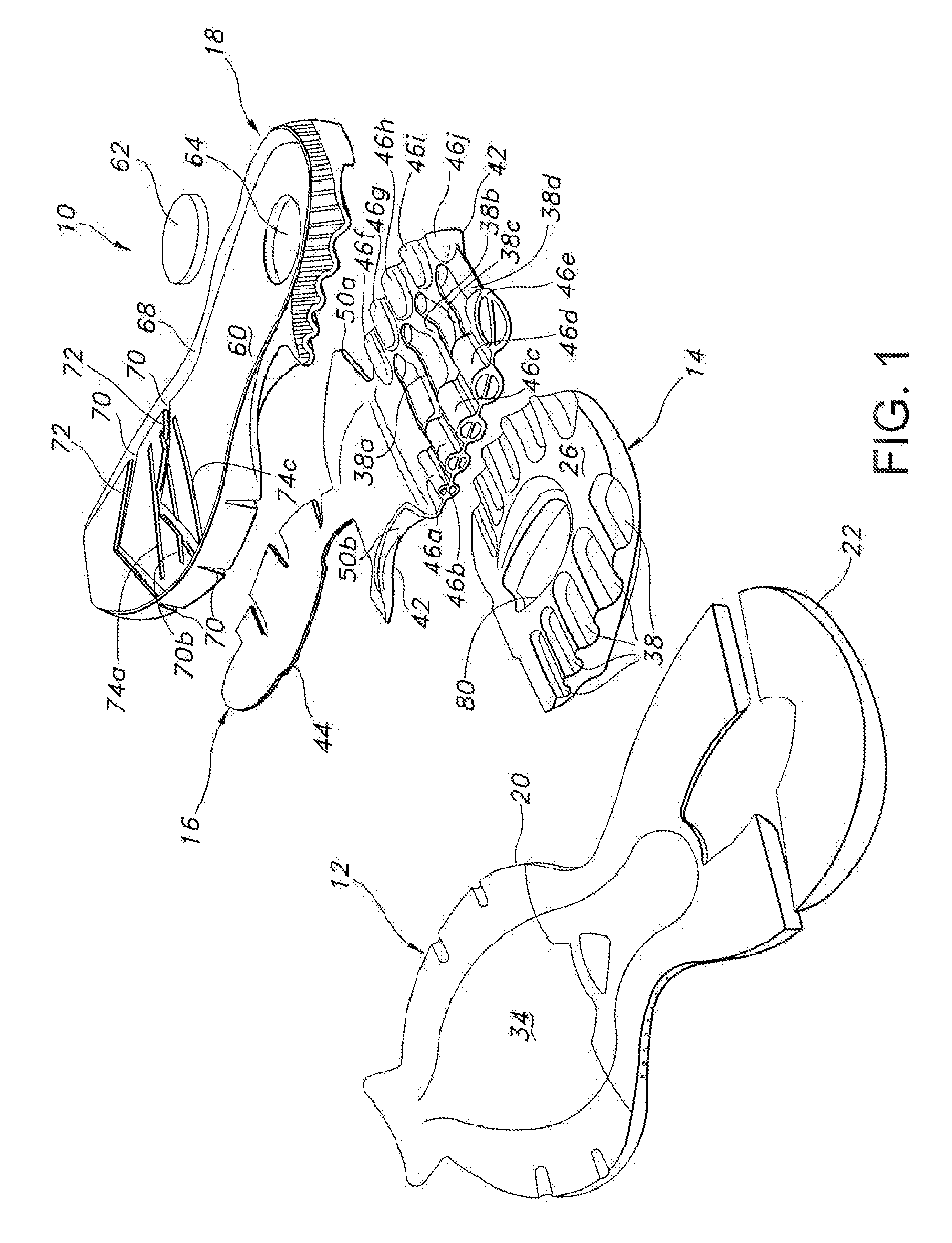

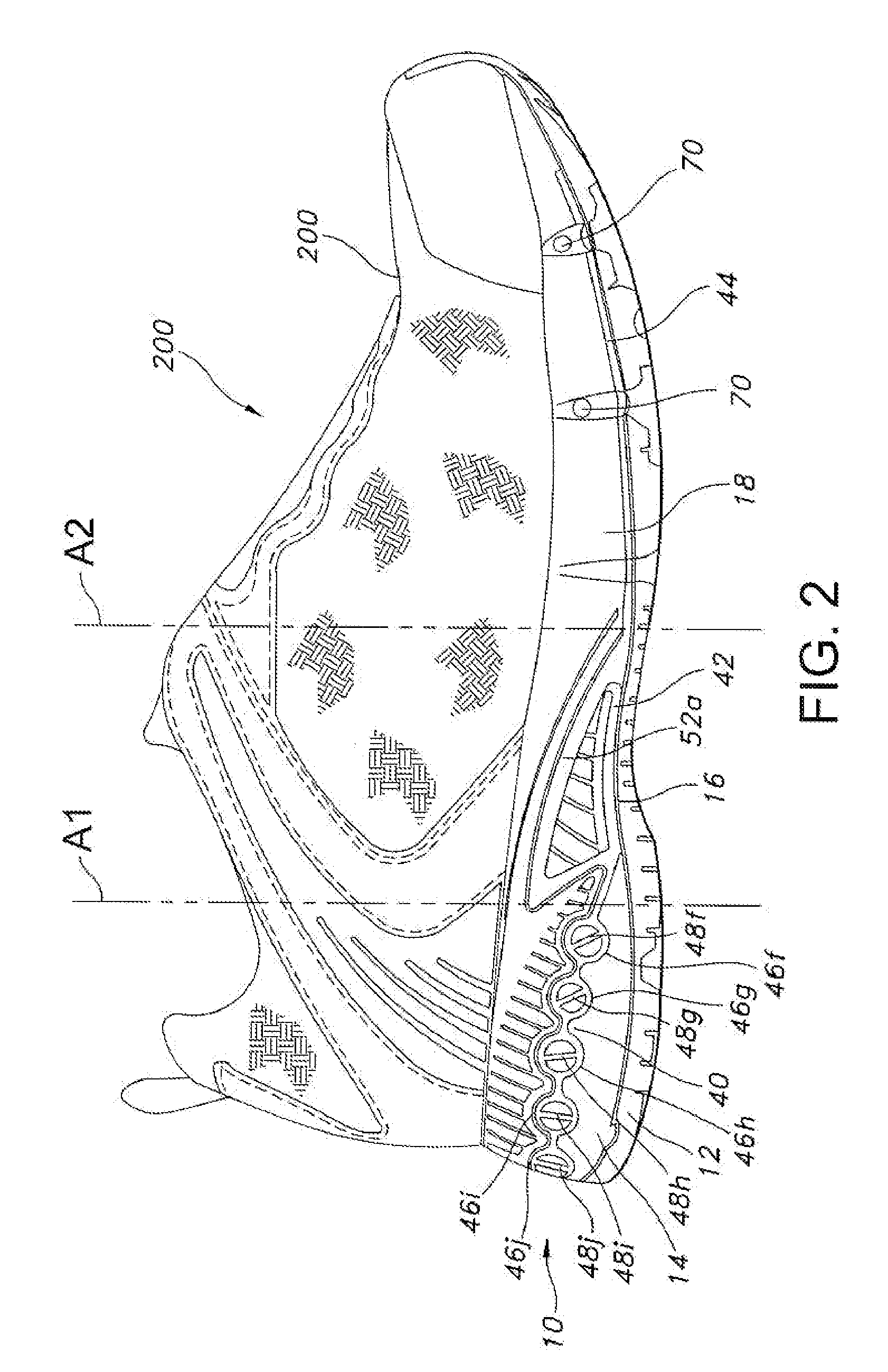

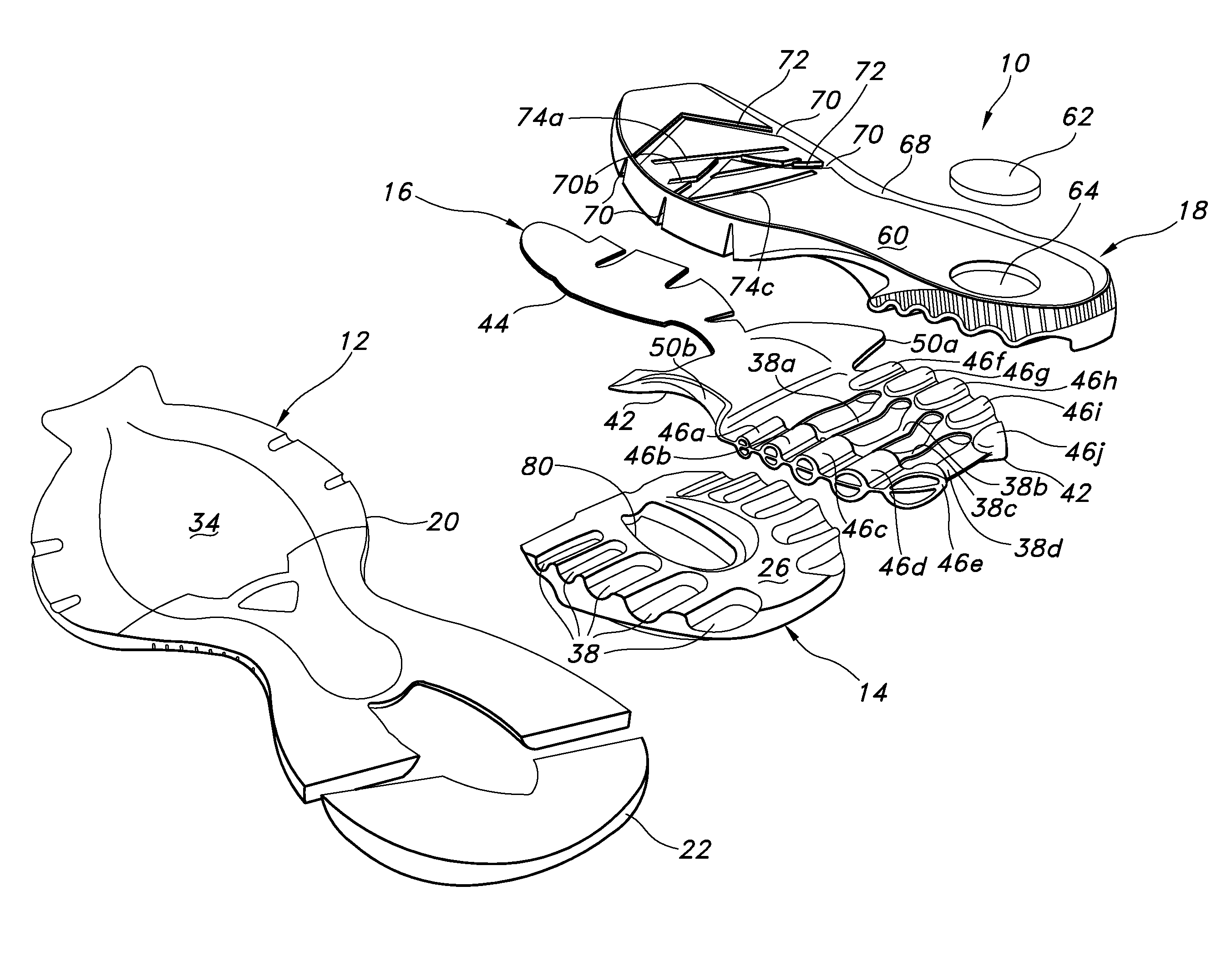

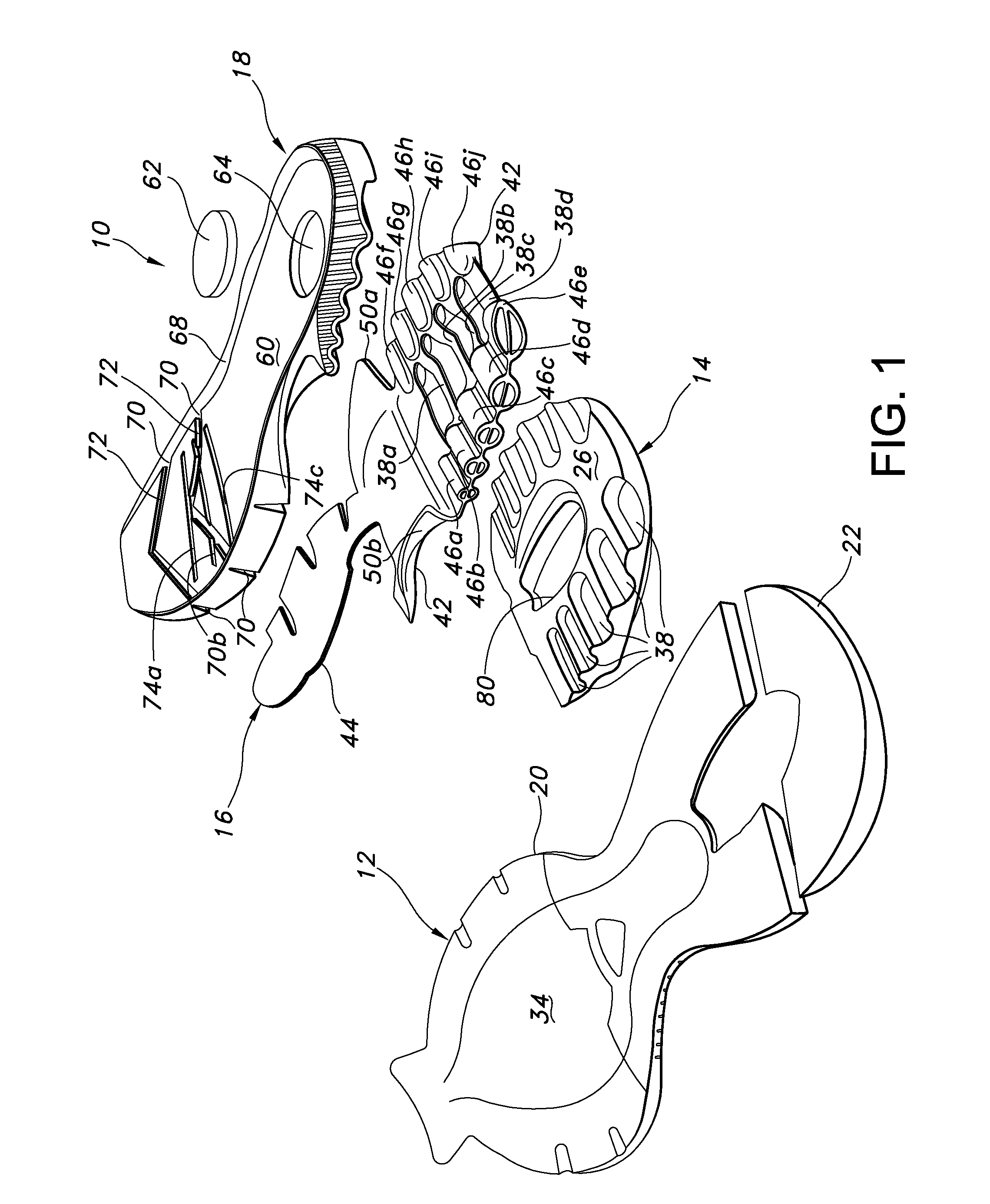

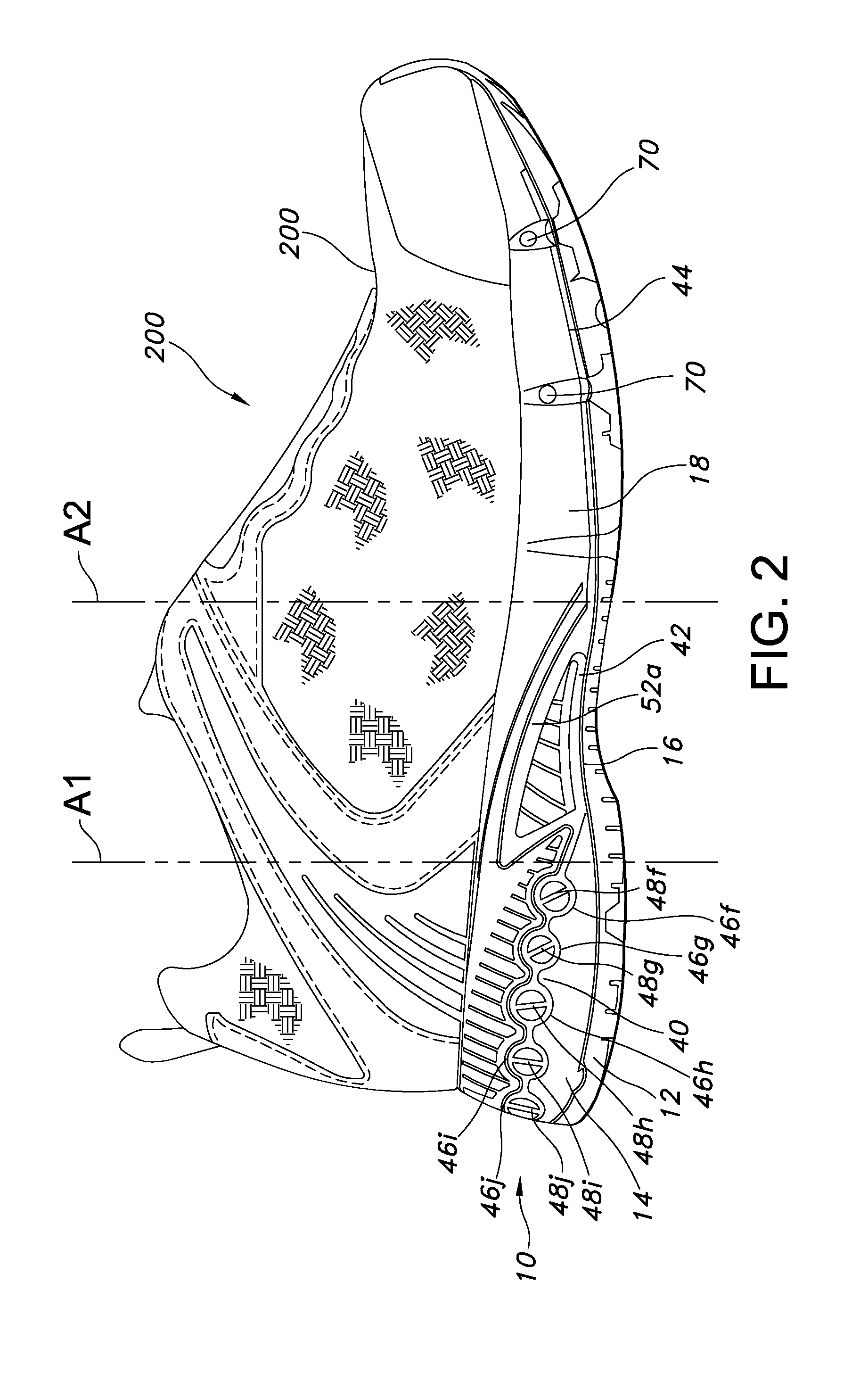

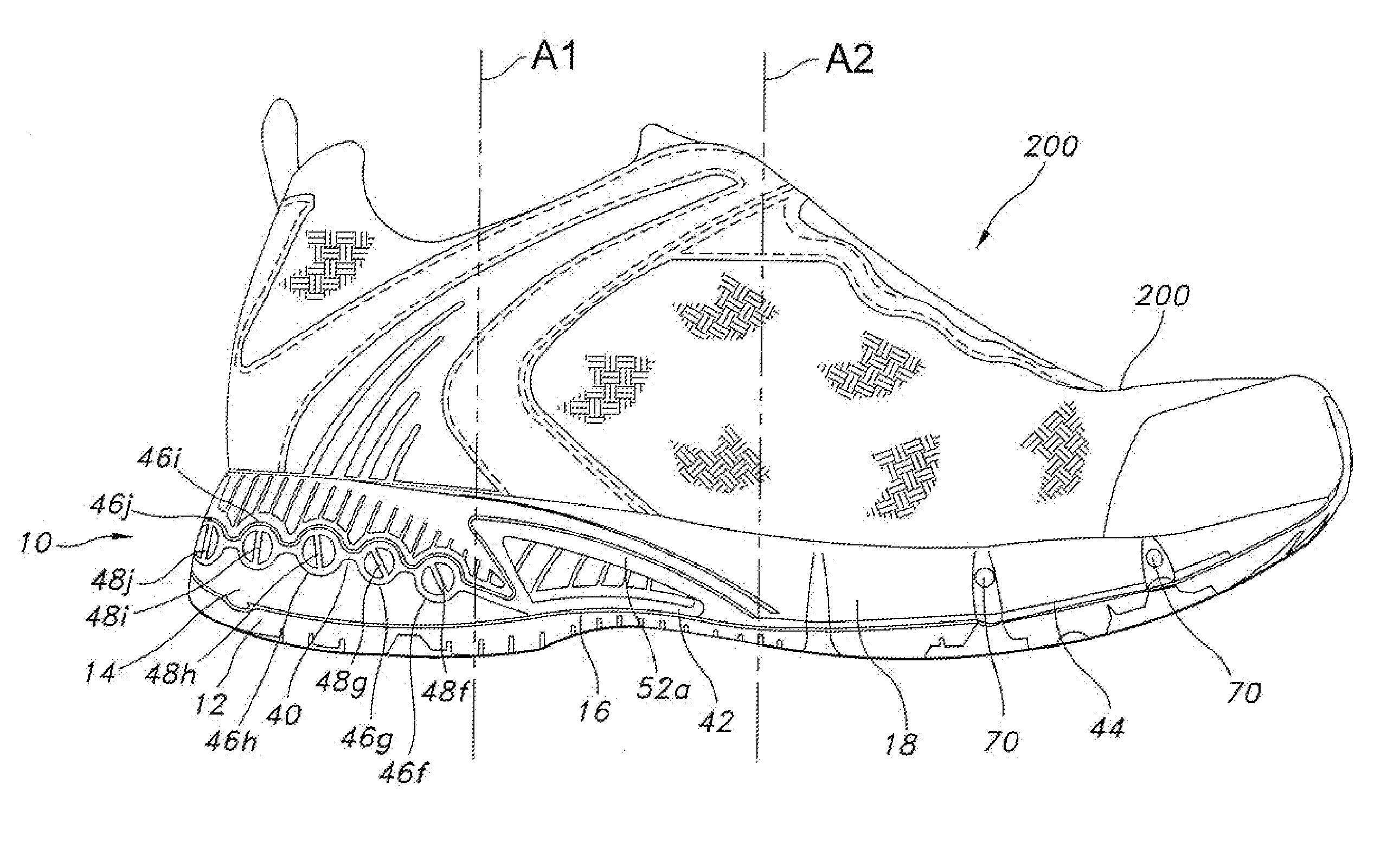

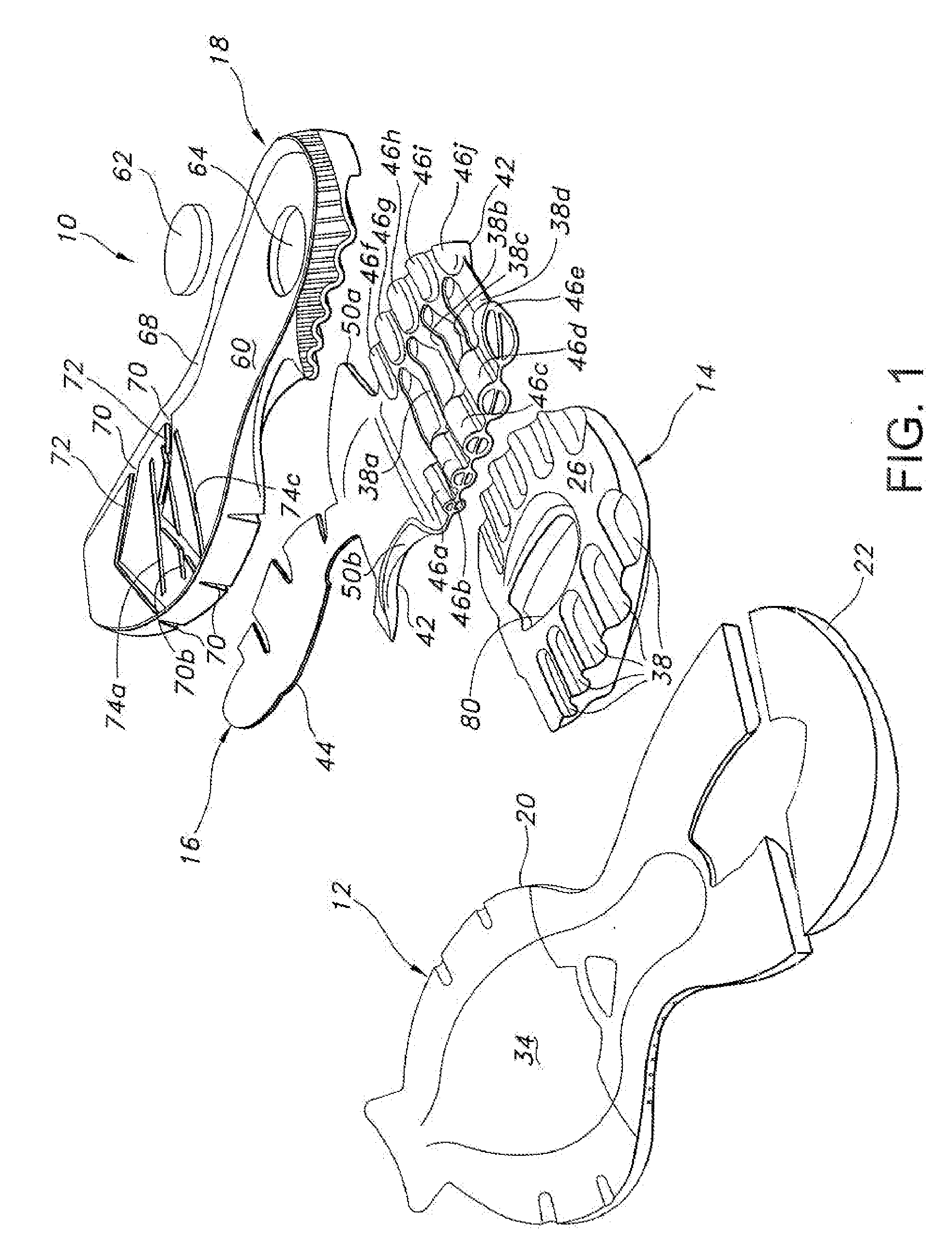

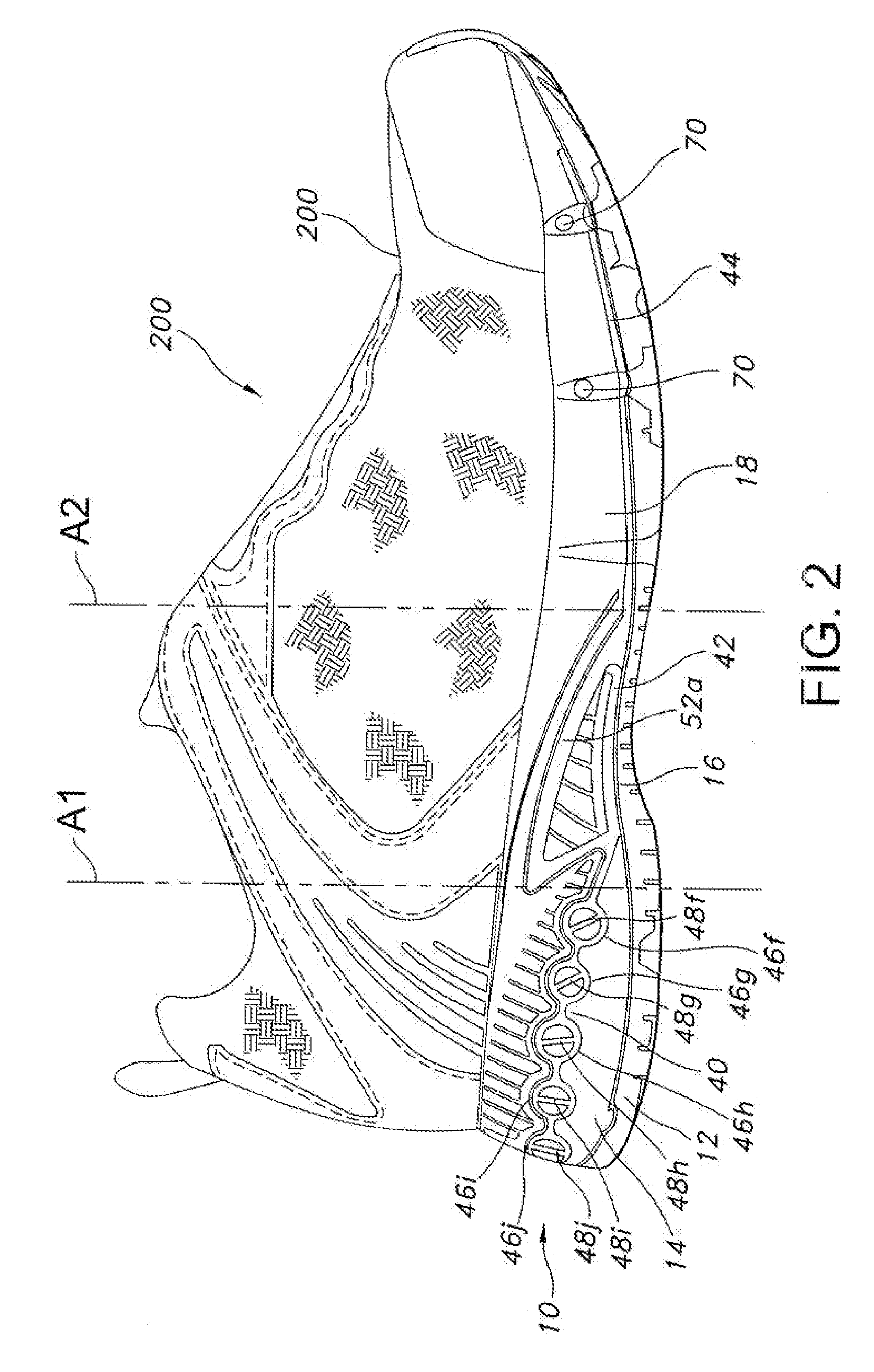

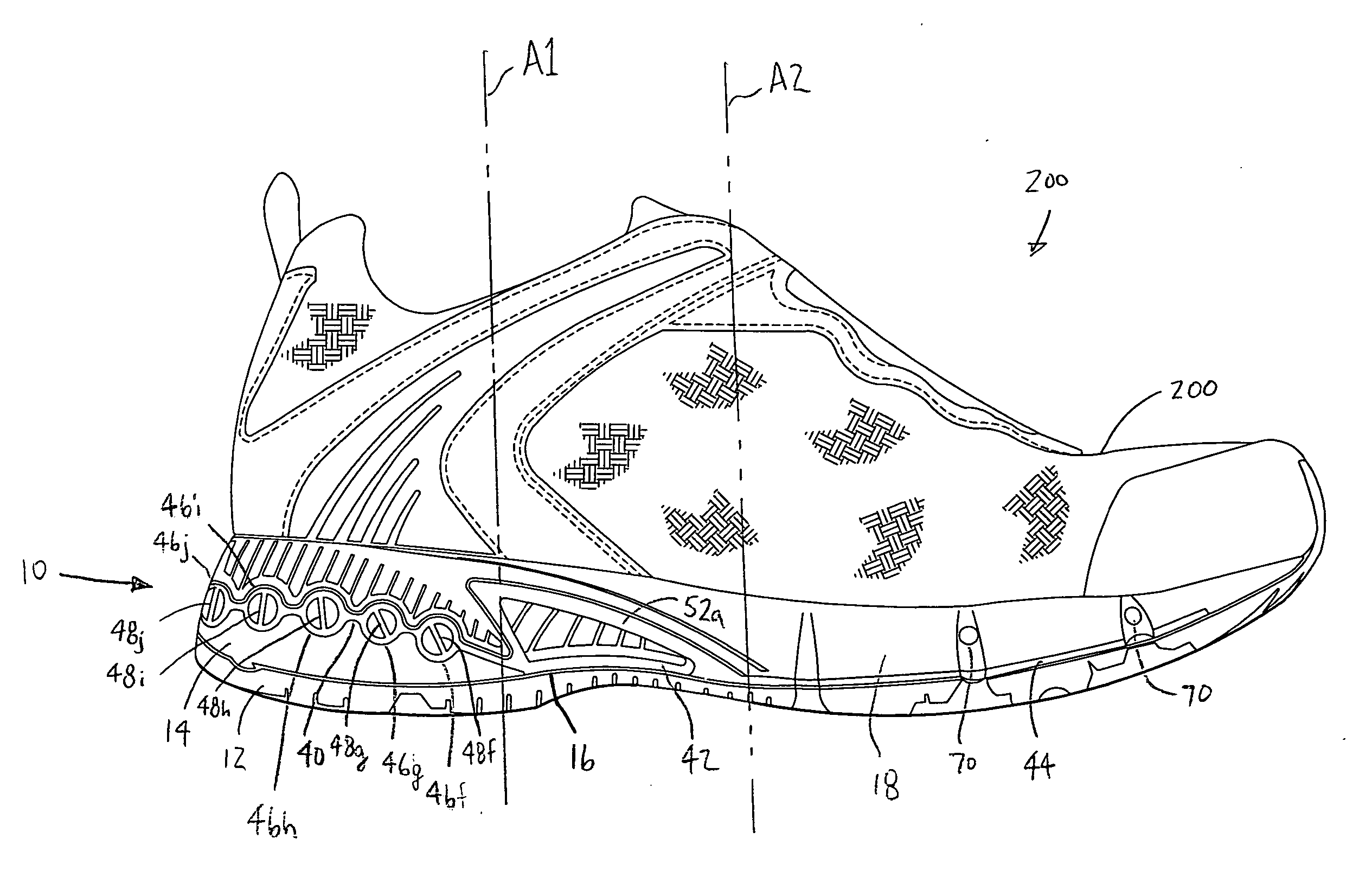

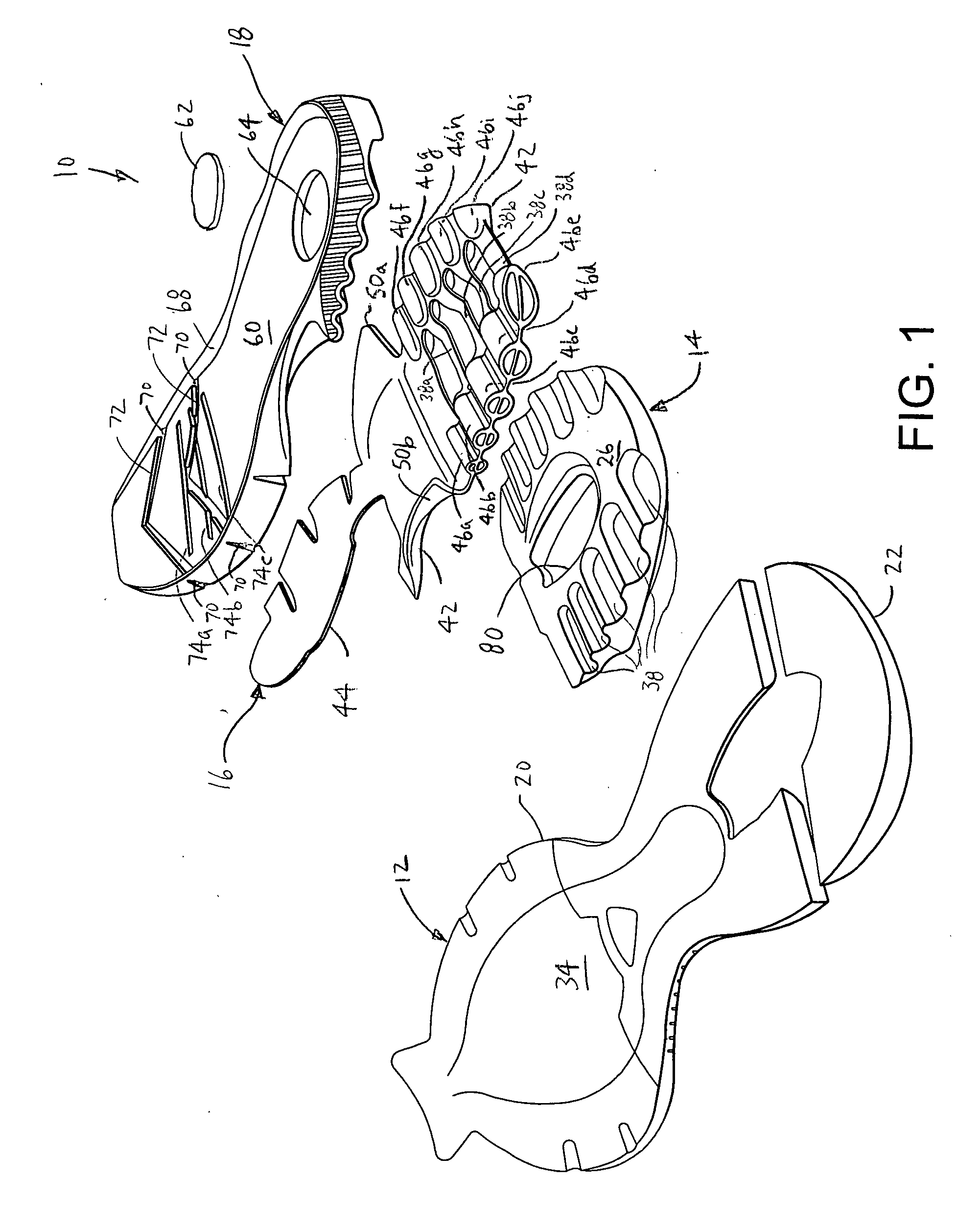

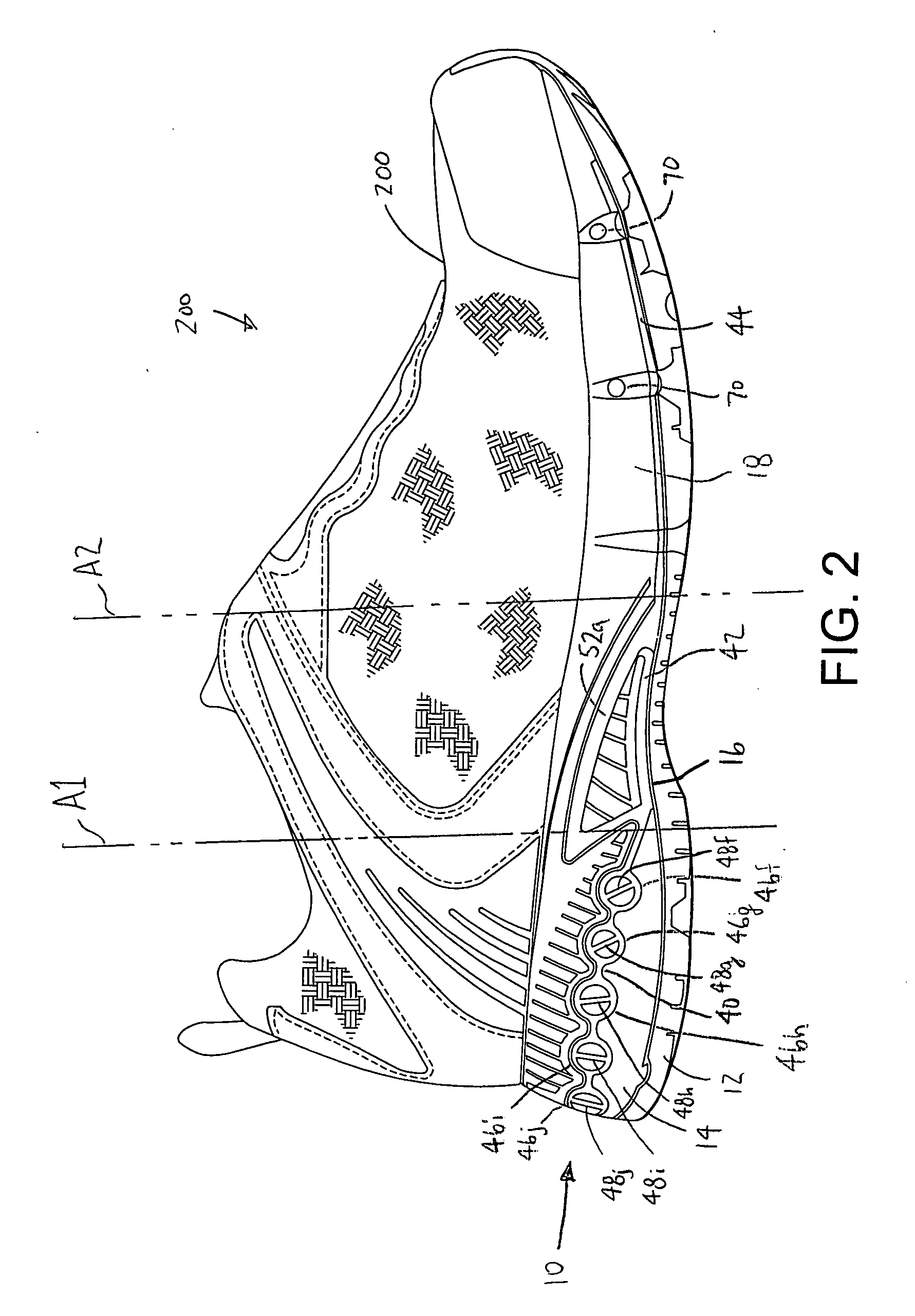

Footwear sole

A sole for an article of footwear having an insert with a plurality of forefoot support tubes are configured to control the support characteristics of the sole in a forefoot region of the sole. In one embodiment, the forefoot support tubes each include a base, and a wall extending from the base. The wall is formed from a material that has a lower durometer value than the base. In another embodiment, the forefoot support tubes air arranged in a radiating pattern, such that at least two of the forefoot support tubes diverge as they extend toward the lateral side of the insert.

Owner:WOLVERINE WORLD WIDE INC

Footwear sole

A sole for an article of footwear having an insert with a plurality of forefoot support tubes are configured to control the support characteristics of the sole in a forefoot region of the sole. In one embodiment, the forefoot support tubes each include a base, and a wall extending from the base. The wall is formed from a material that has a lower durometer value than the base. In another embodiment, the forefoot support tubes air arranged in a radiating pattern, such that at least two of the forefoot support tubes diverge as they extend toward the lateral side of the insert.

Owner:WOLVERINE WORLD WIDE

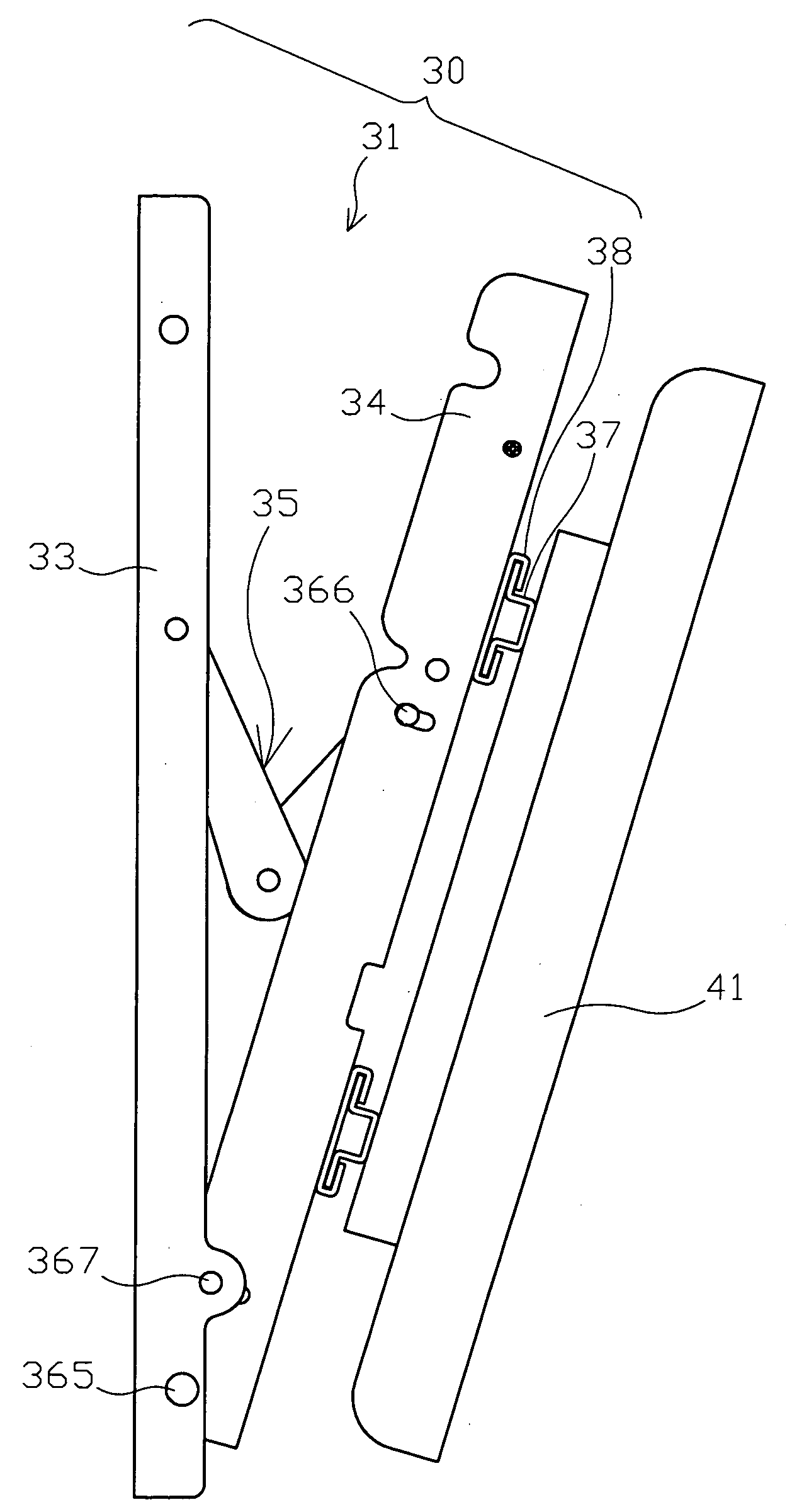

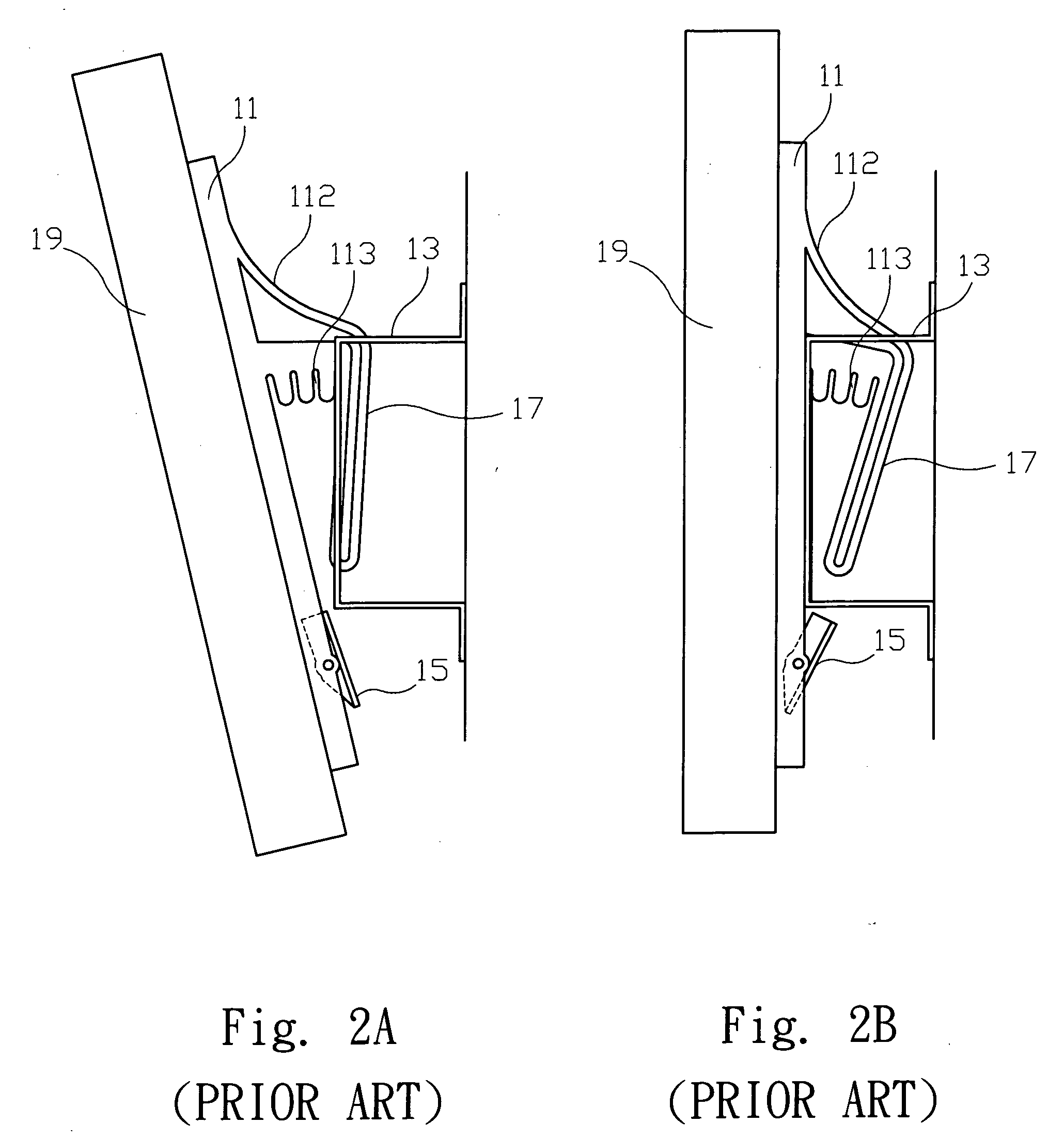

Display panel mount bracket

InactiveUS20070007412A1Improve compatibilityIncrease frictionStands/trestlesKitchen equipmentDisplay deviceEngineering

A display panel mount bracket comprises at least one angle adjustment set, at least one fixed board, and at least one adapting base. Among them, each angle adjustment set comprises a support shaft pivoting with a swing shaft and an activation device for adjusting the sandwiched angle mounted between the swing shaft and the support shaft. A plurality of fixed holes for matching with a display set on the fixed board, and each adapting base is linked with the fixed board and has a hanging button for matching with the first swing holes. Further, each support shaft can be latched on a wall. This way, spaces between each angle adjustment set can be mobile adjusted without limiting by conditions of the wall, as well as the sandwiched angle of the display and the wall can be adjusted by a stepless way to provide users an optimum angle of view.

Owner:SALLAS INDAL

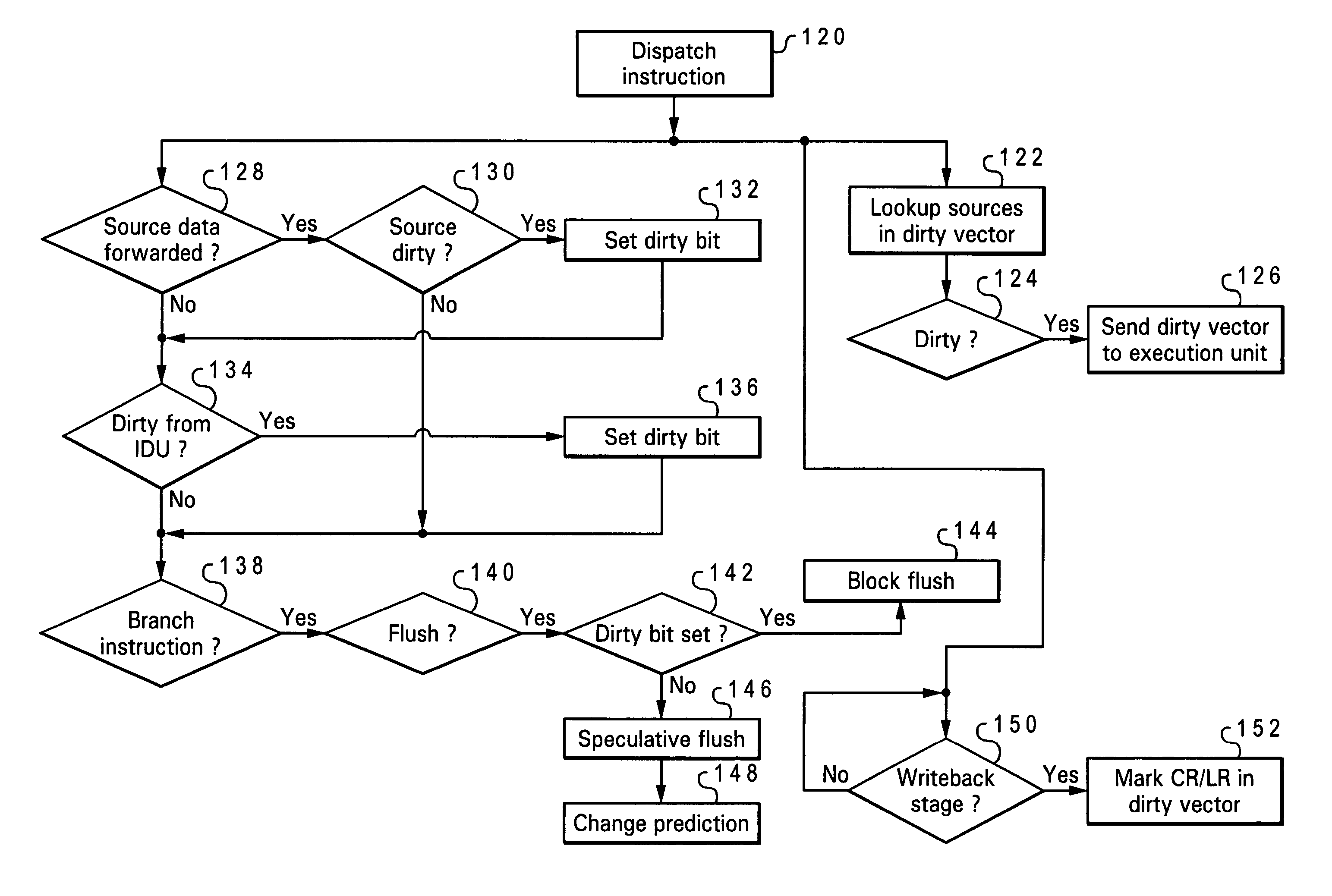

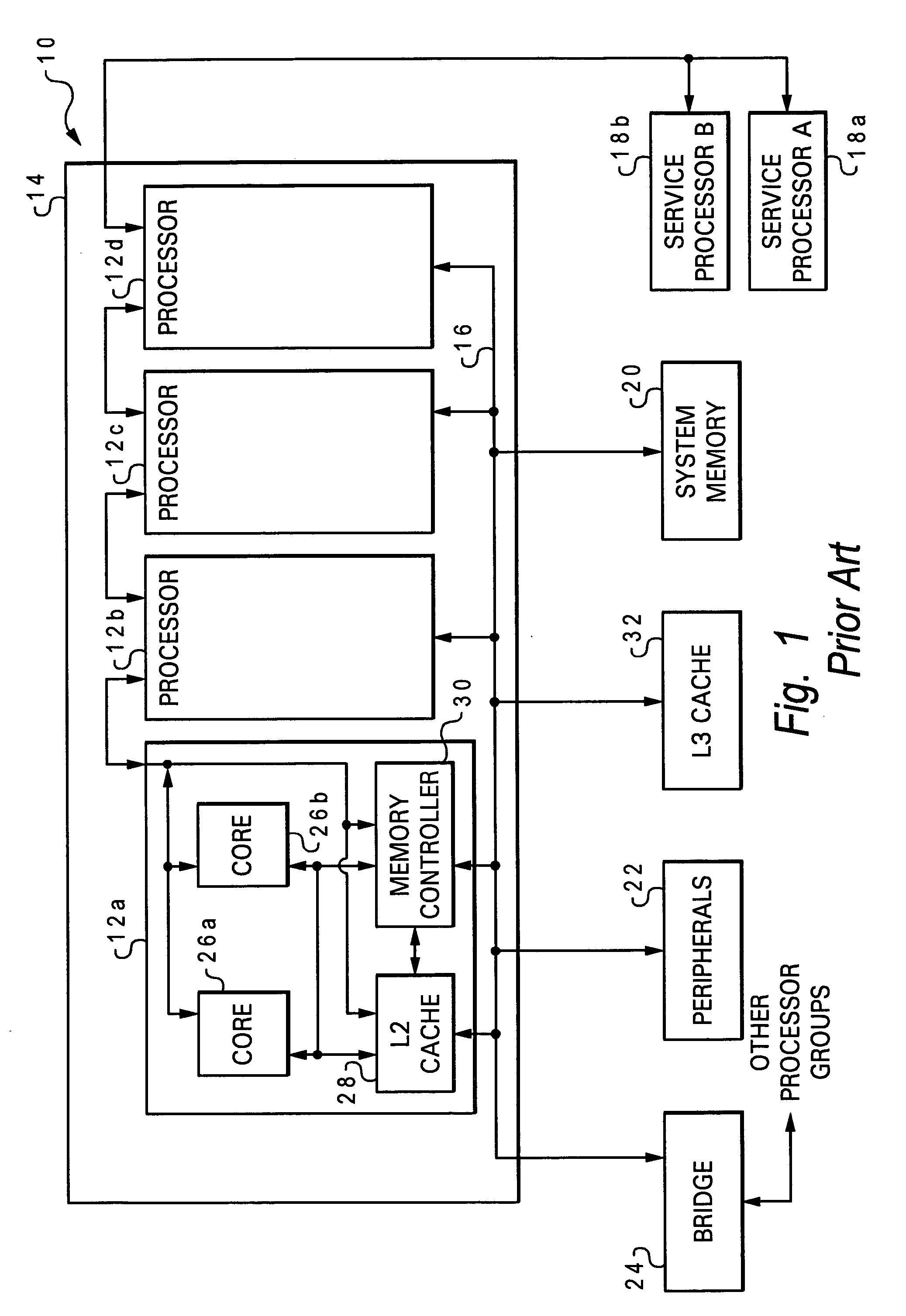

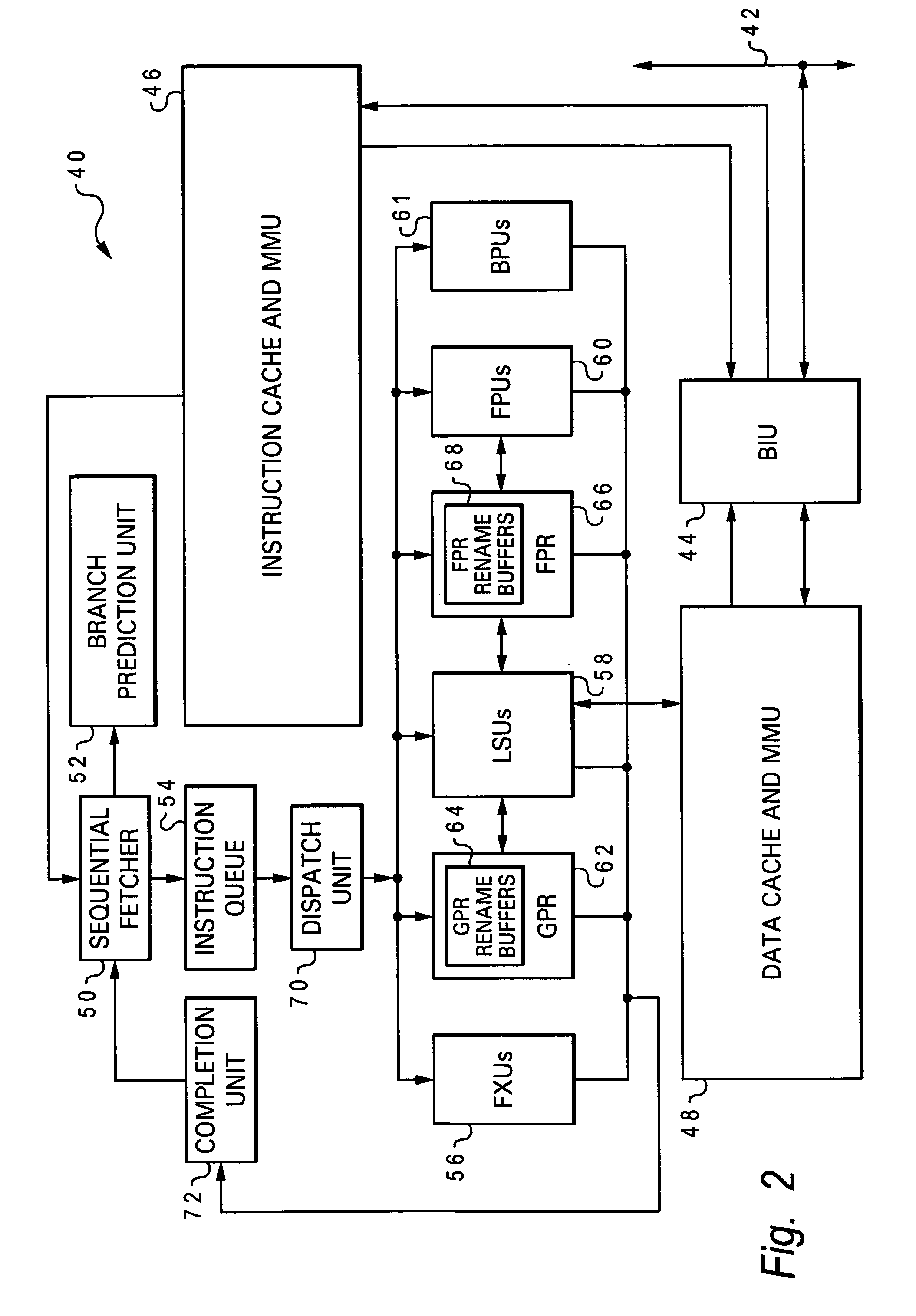

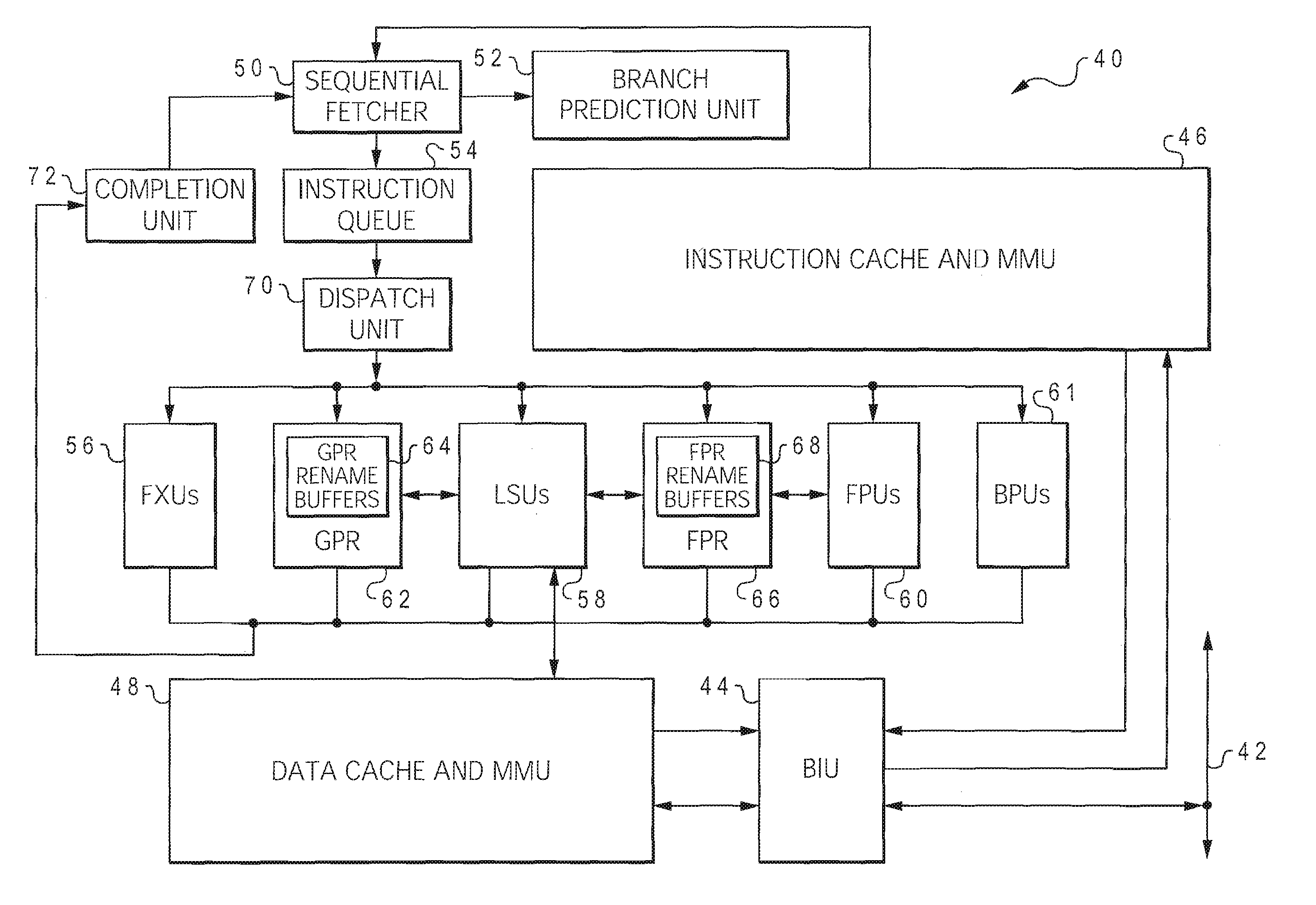

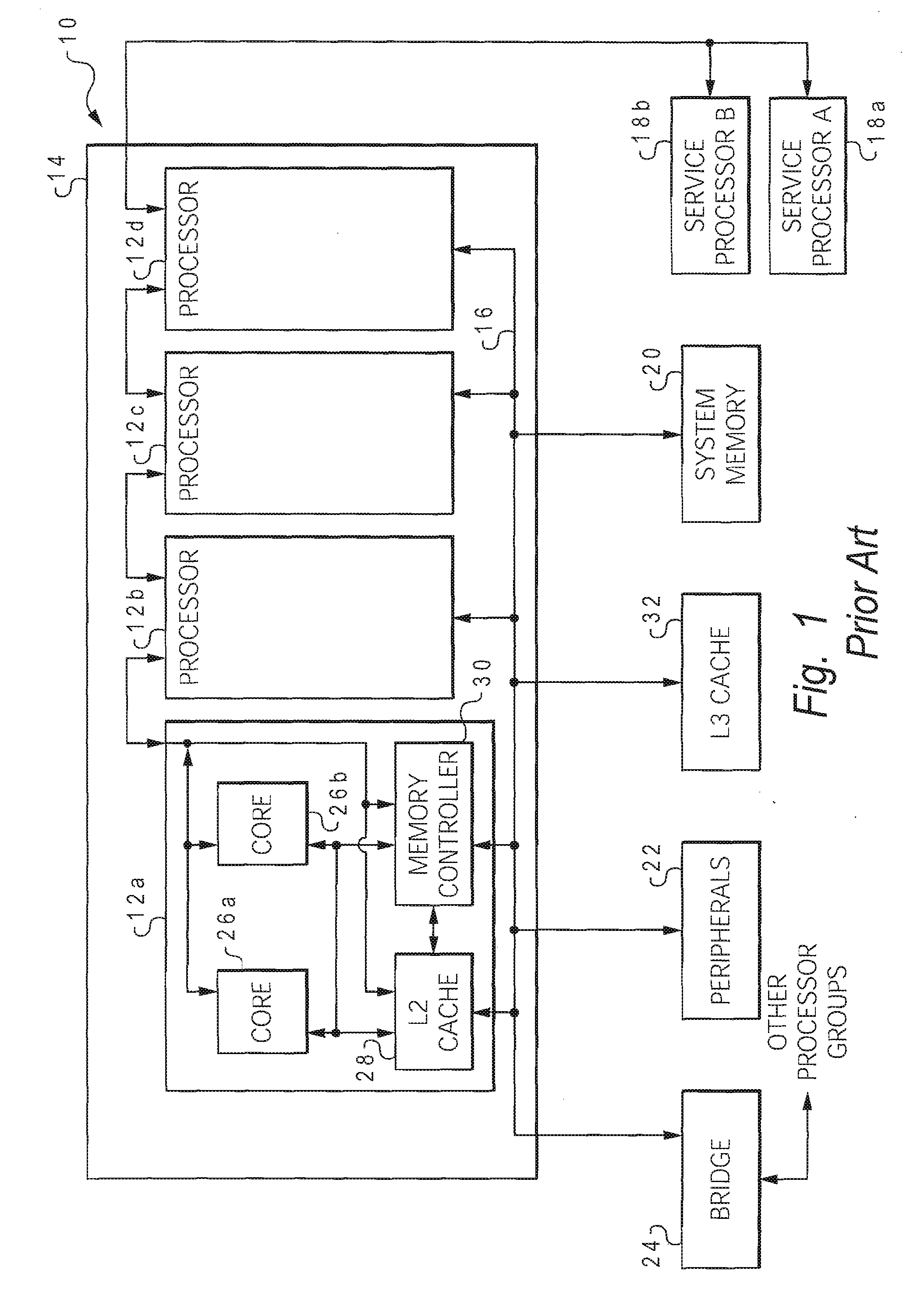

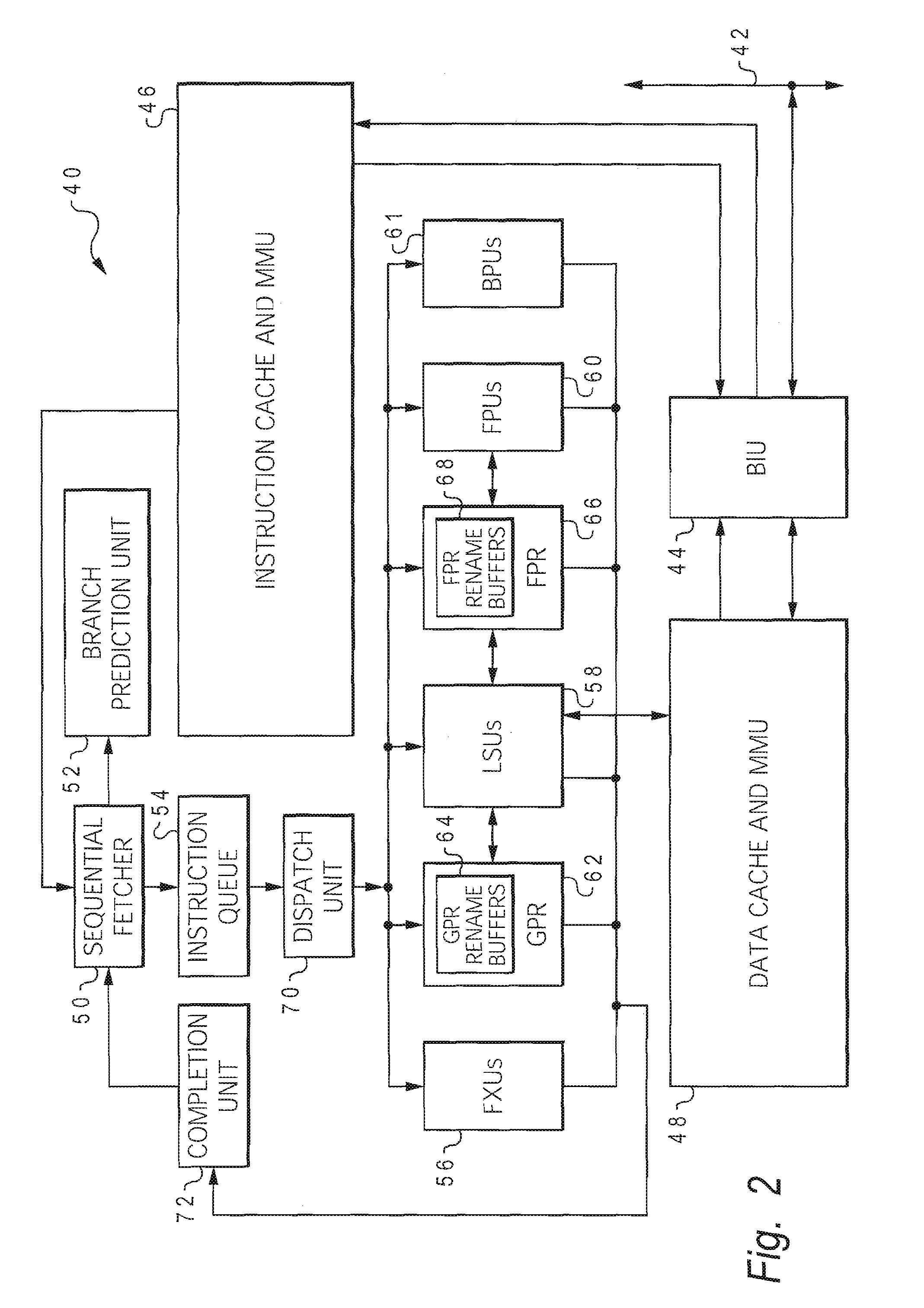

Branch lookahead prefetch for microprocessors

InactiveUS20060149933A1Easy to handleReduce delaysDigital computer detailsSpecific program execution arrangementsSpeculative executionProcessing Instruction

A method of handling program instructions in a microprocessor which reduces delays associated with mispredicted branch instructions, by detecting the occurrence of a stall condition during execution of the program instructions, speculatively executing one or more pending instructions which include at least one branch instruction during the stall condition, and determining the validity of data utilized by the speculative execution. In particular, the method can detect a load instruction miss which results in the stall condition. Dispatch logic determines the validity of the data by marking one or more registers of an instruction dispatch unit to indicate which results of the pending instructions are invalid. The speculative execution of instructions can occur across multiple pipeline stages of the microprocessor, and the validity of the data is tracked during their execution in the multiple pipeline stages while monitoring a dependency of the speculatively executed instructions relative to one another during their execution in the multiple pipeline stages. A branch prediction unit predicts a path of the branch instruction prior to detection of the stall condition, and fetches speculative instructions from the predicted path into an instruction queue. If the speculative execution of the branch instruction indicates it was mispredicted, the speculative instructions are flushed from the pipeline and instruction queue, and the branch prediction information is updated based on results of the speculative execution of the branch instruction. The speculative execution of the instructions occurs without altering any architected facilities of the microprocessor.

Owner:IBM CORP

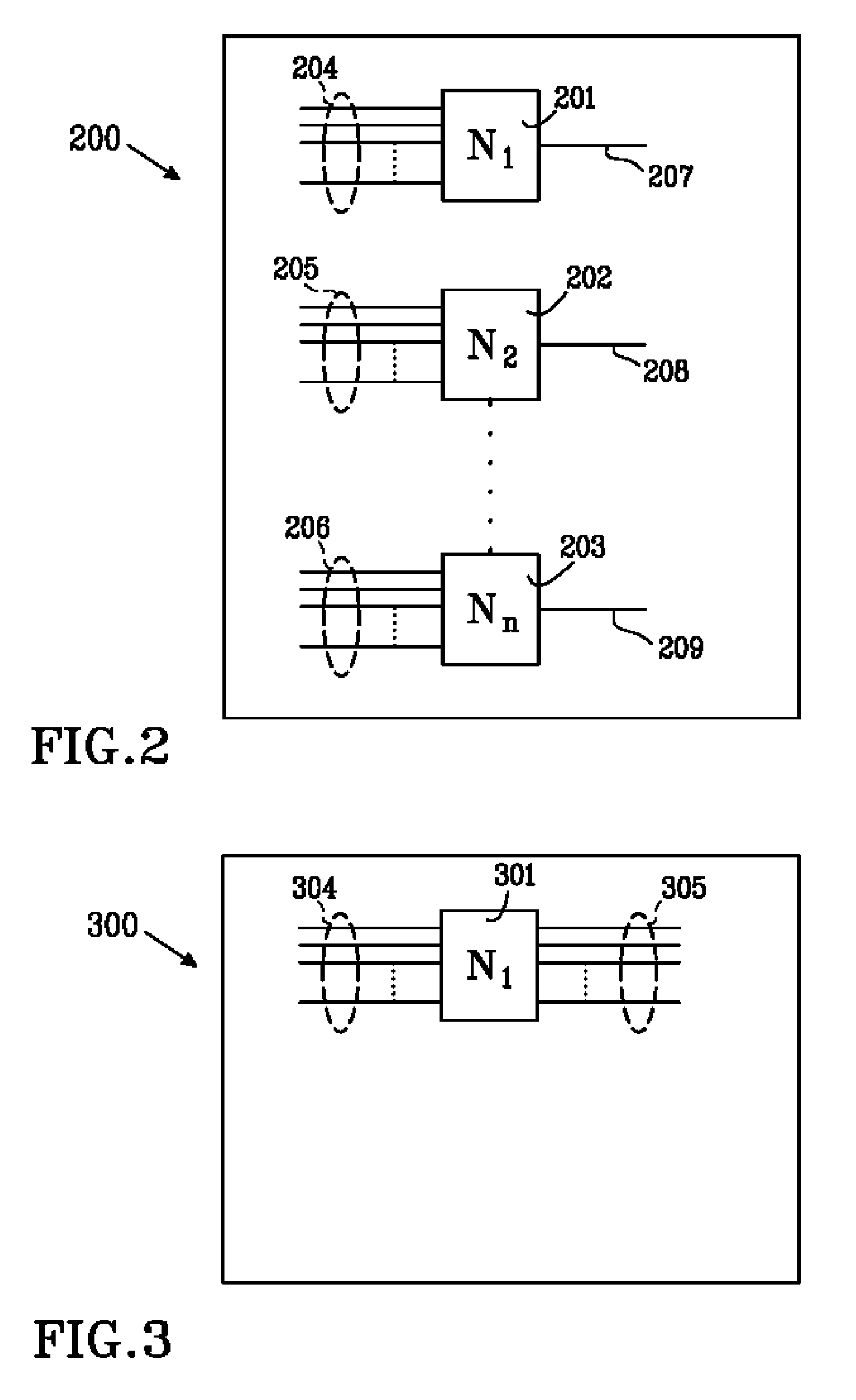

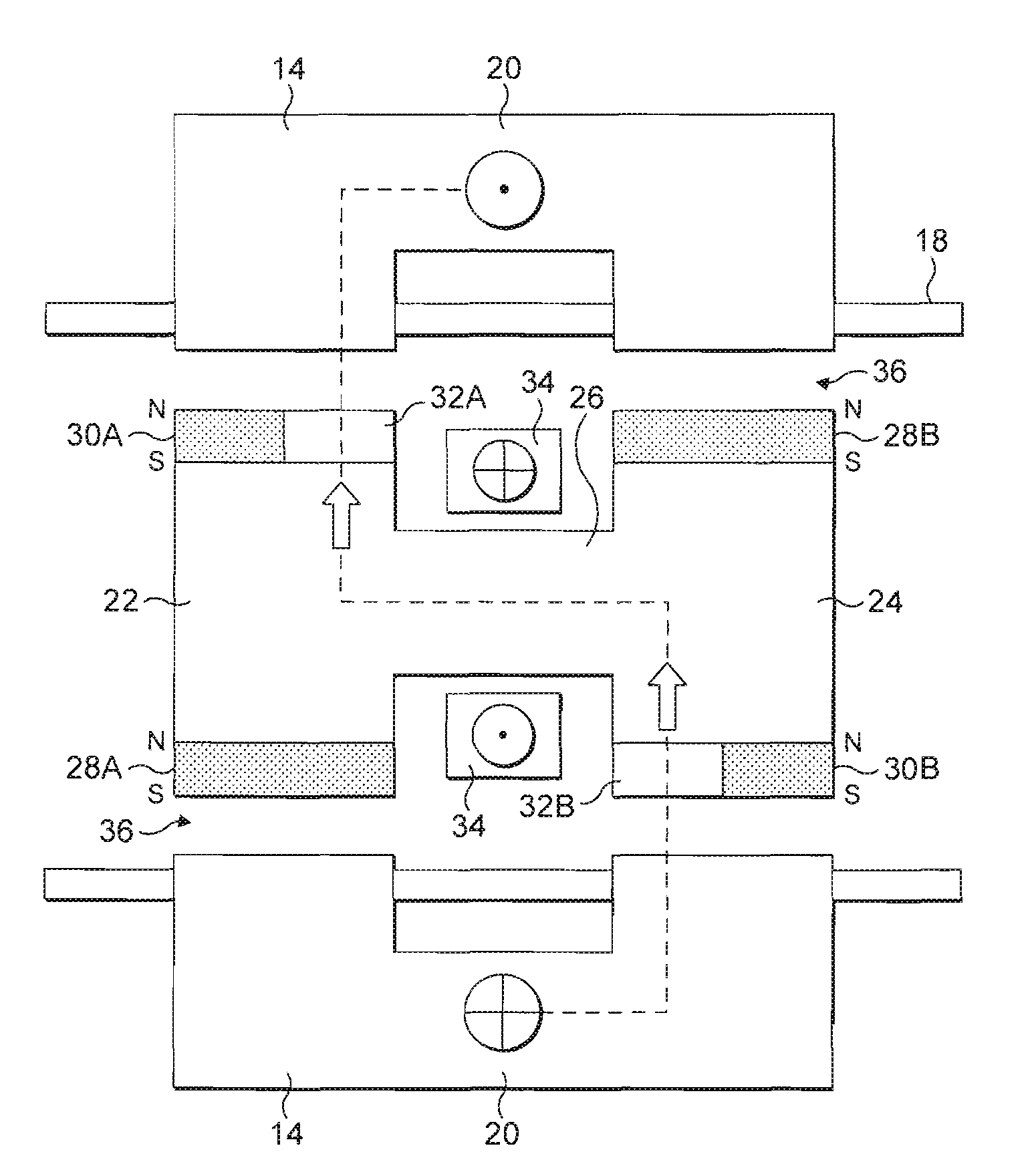

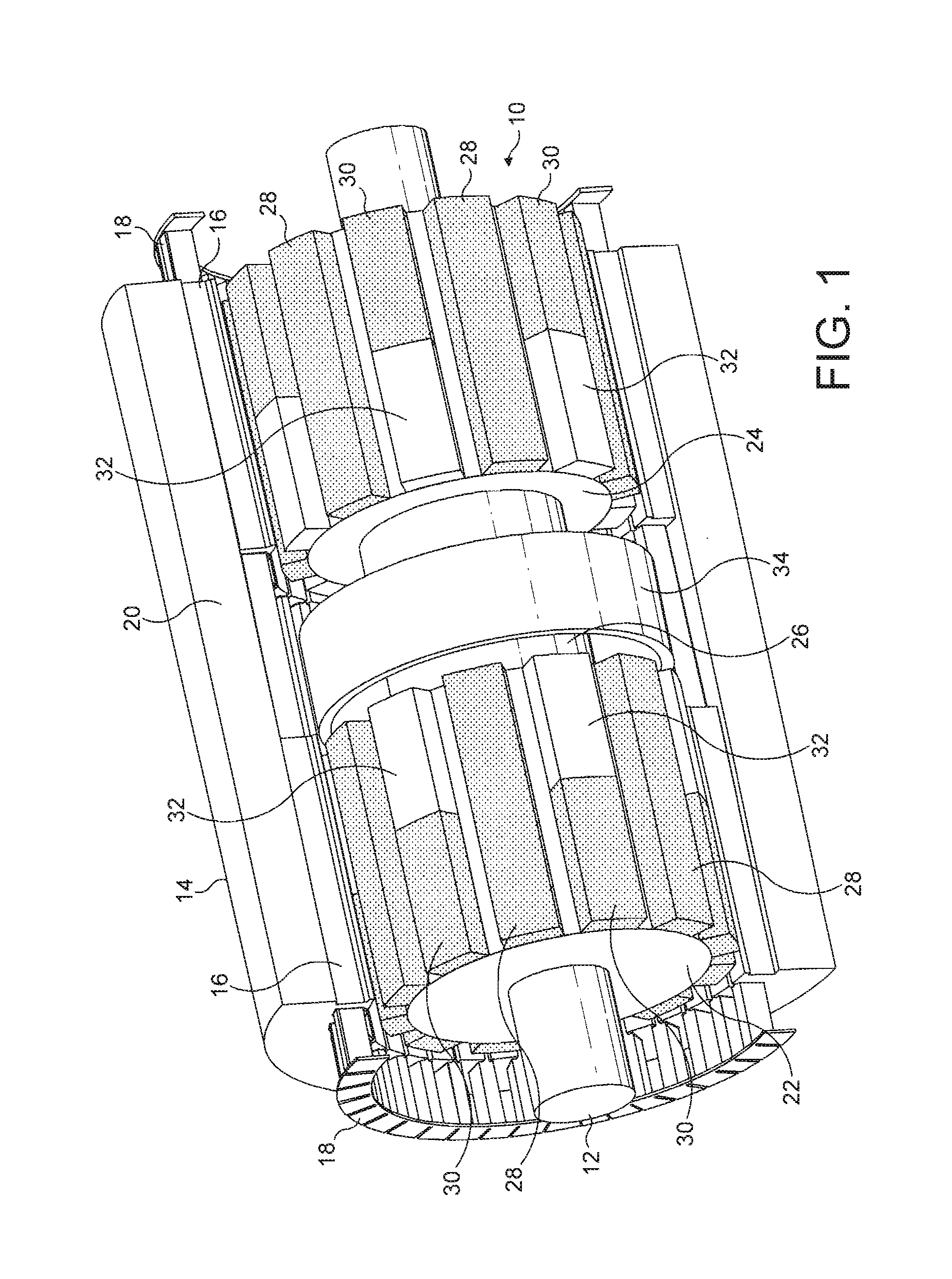

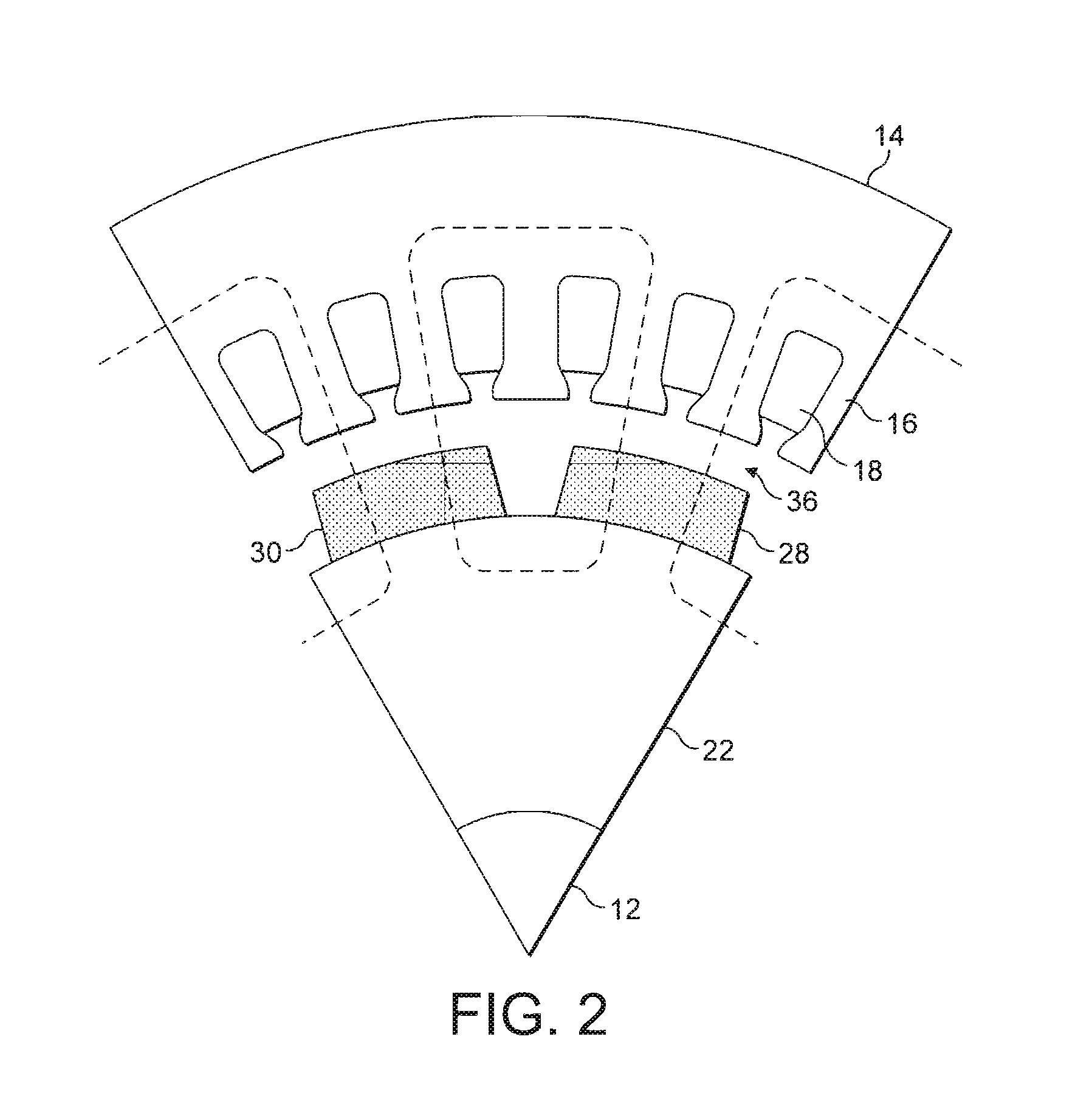

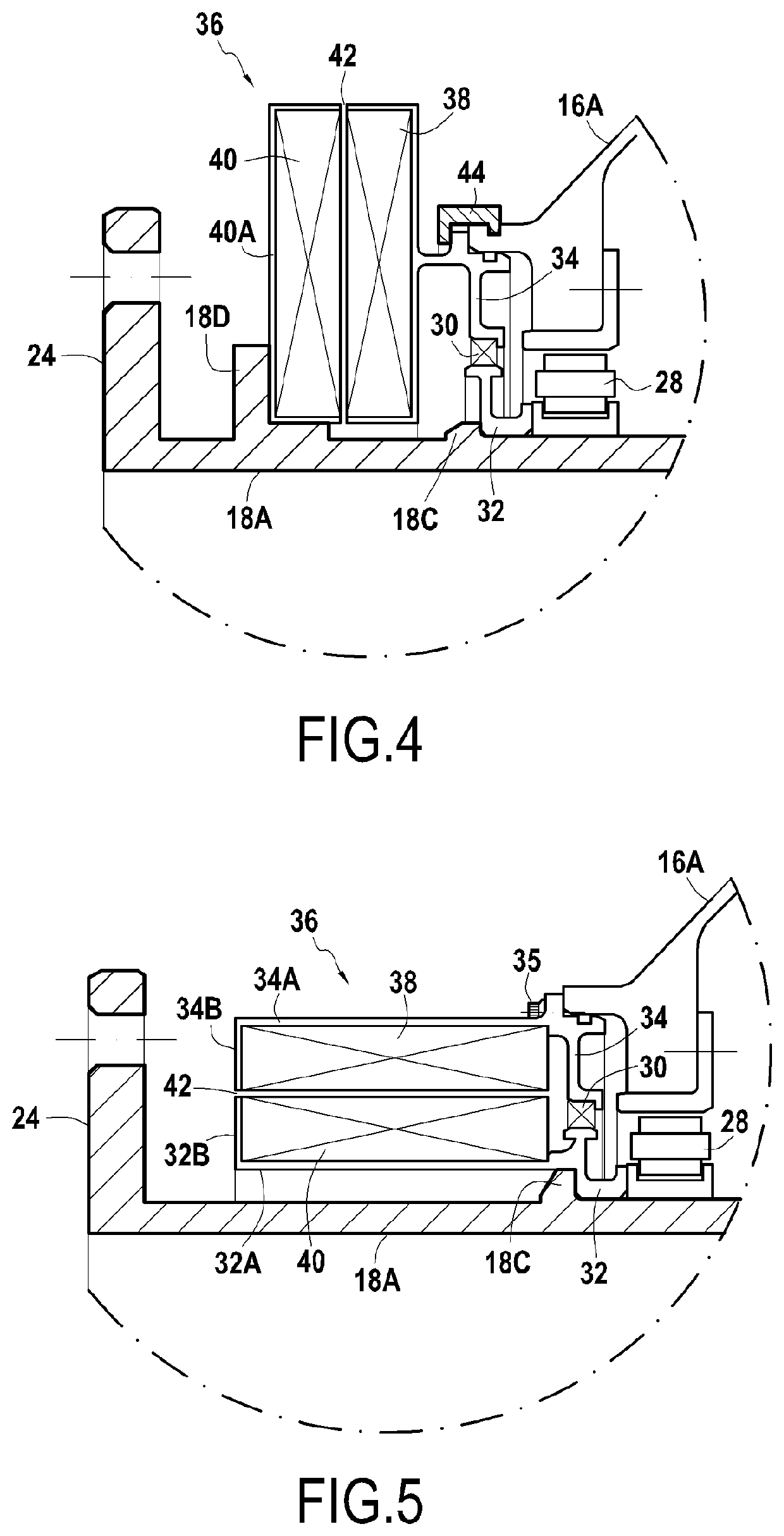

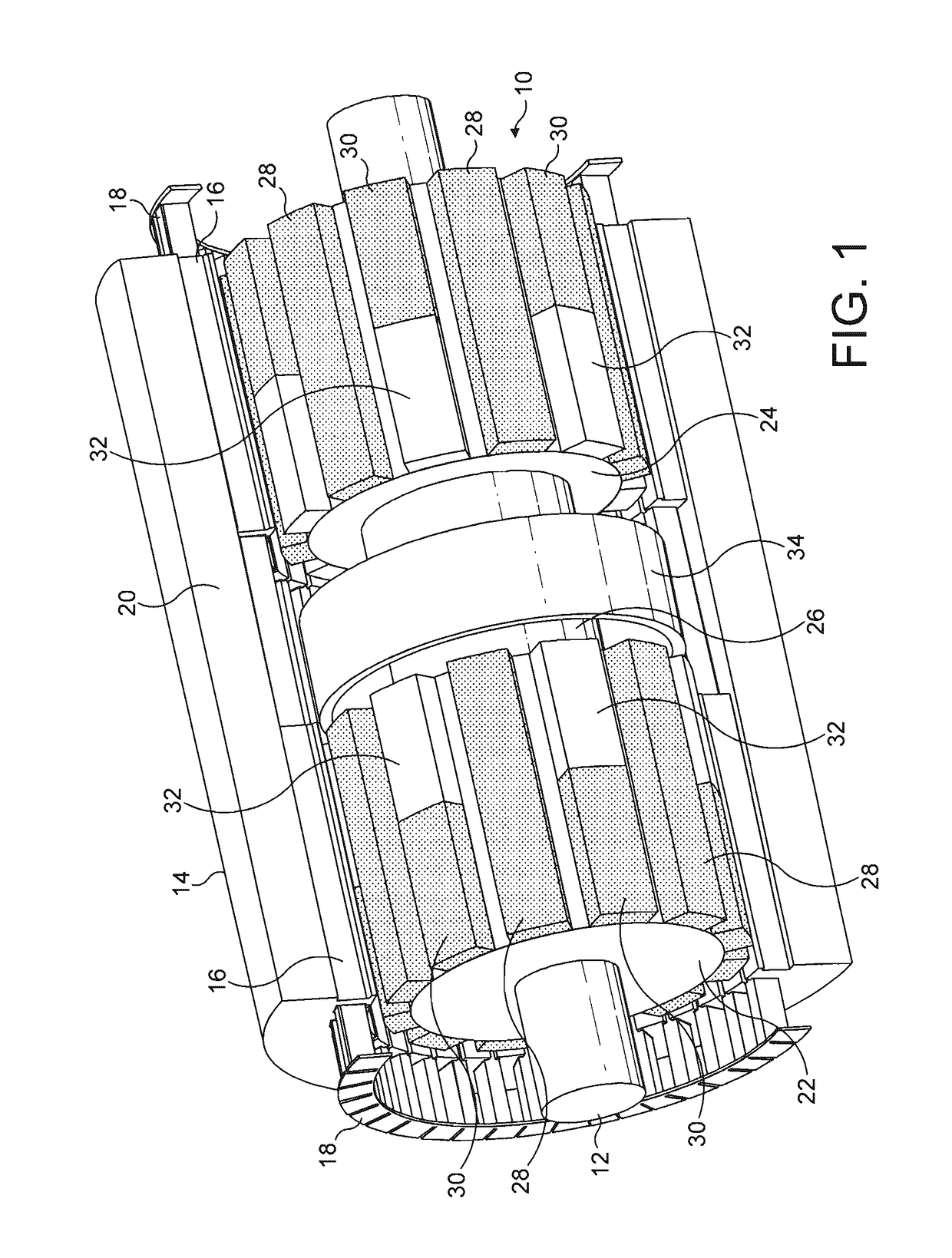

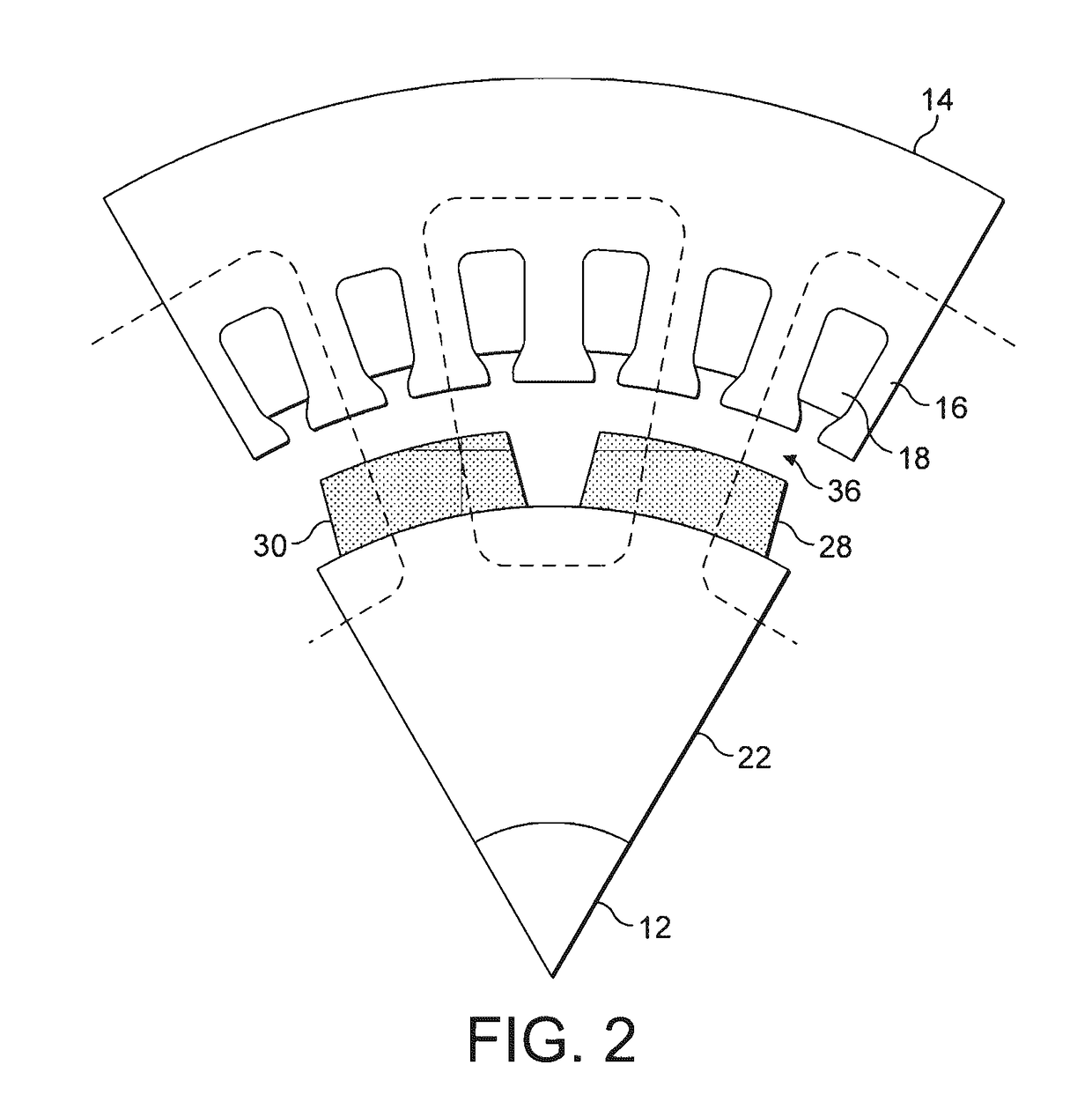

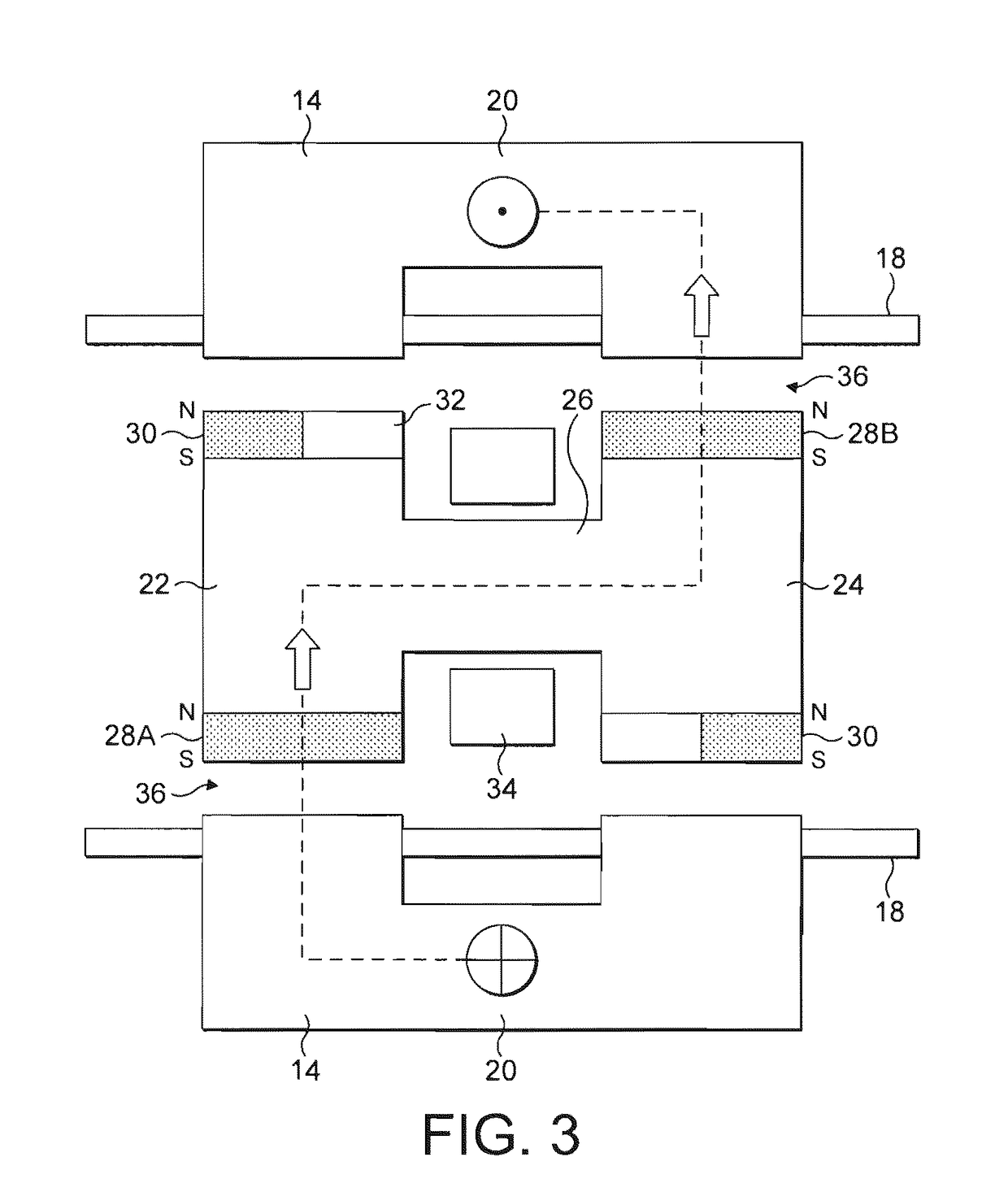

Rotating electrical machine

ActiveUS20100013340A1Change quantitySmall sizeSynchronous generatorsWindingsElectric machineMagnetic flux

A rotating electrical machine is disclosed, the machine comprising a stator 14, 52 and a rotor 10, 50 arranged to rotate inside the stator. The rotor comprises a plurality of permanent magnets 28, 30, 54 arranged to produce a radial magnetic flux in an airgap between the rotor and the stator. The machine also comprises a stationary excitation coil 34, 46, 66. The rotor comprises a plurality of low reluctance elements 32, 58. A current through the stationary excitation coil causes a magnetic flux to be established in a magnetic flux path which passes into the rotor through a first low reluctance element and out of the rotor through a second low reluctance element, which magnetic flux combines with the radial magnetic flux produced by the permanent magnets in the airgap. This arrangement can allow control of the field within a permanent magnet radial flux machine.

Owner:CUMMINS GENERATOR TECH LTD

Footwear sole

A sole for an article of footwear having an insert with a plurality of forefoot support tubes are configured to control the support characteristics of the sole in a forefoot region of the sole. In one embodiment, the forefoot support tubes each include a base, and a wall extending from the base. The wall is formed from a material that has a lower durometer value than the base. In another embodiment, the forefoot support tubes are arranged in a radiating pattern, such that at least two of the forefoot support tubes diverge as they extend toward the lateral side of the insert.

Owner:WOLVERINE WORLD WIDE

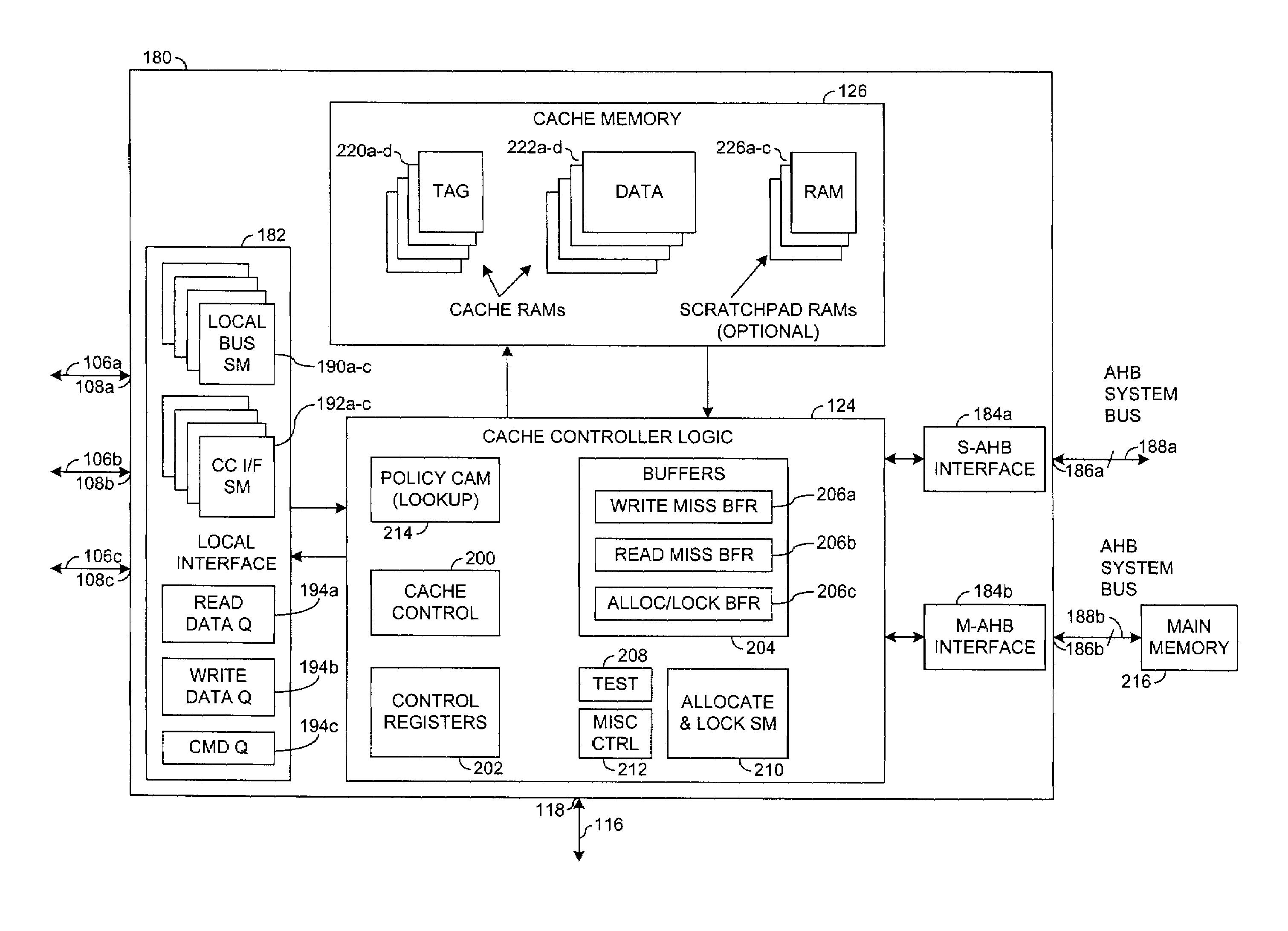

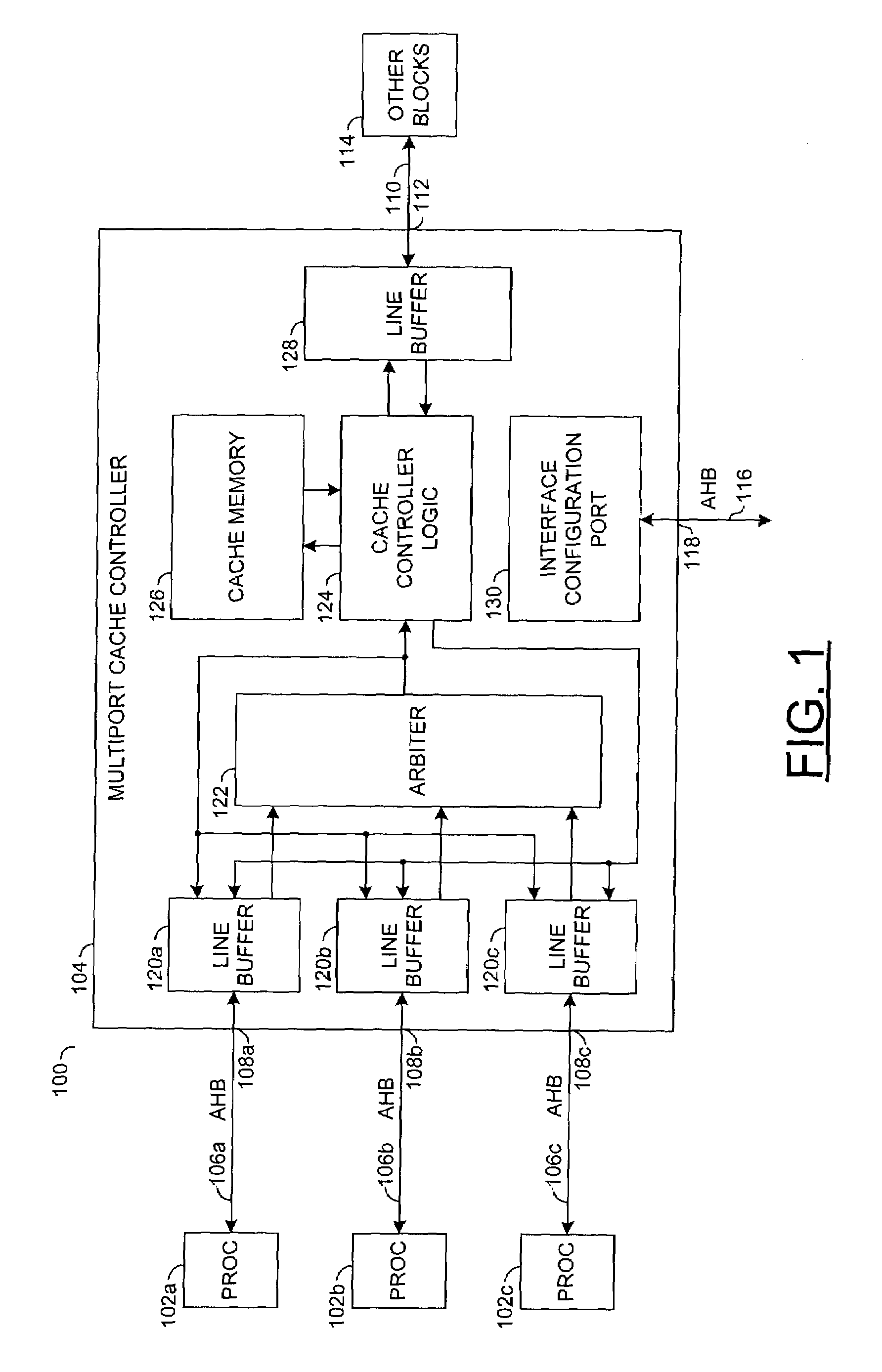

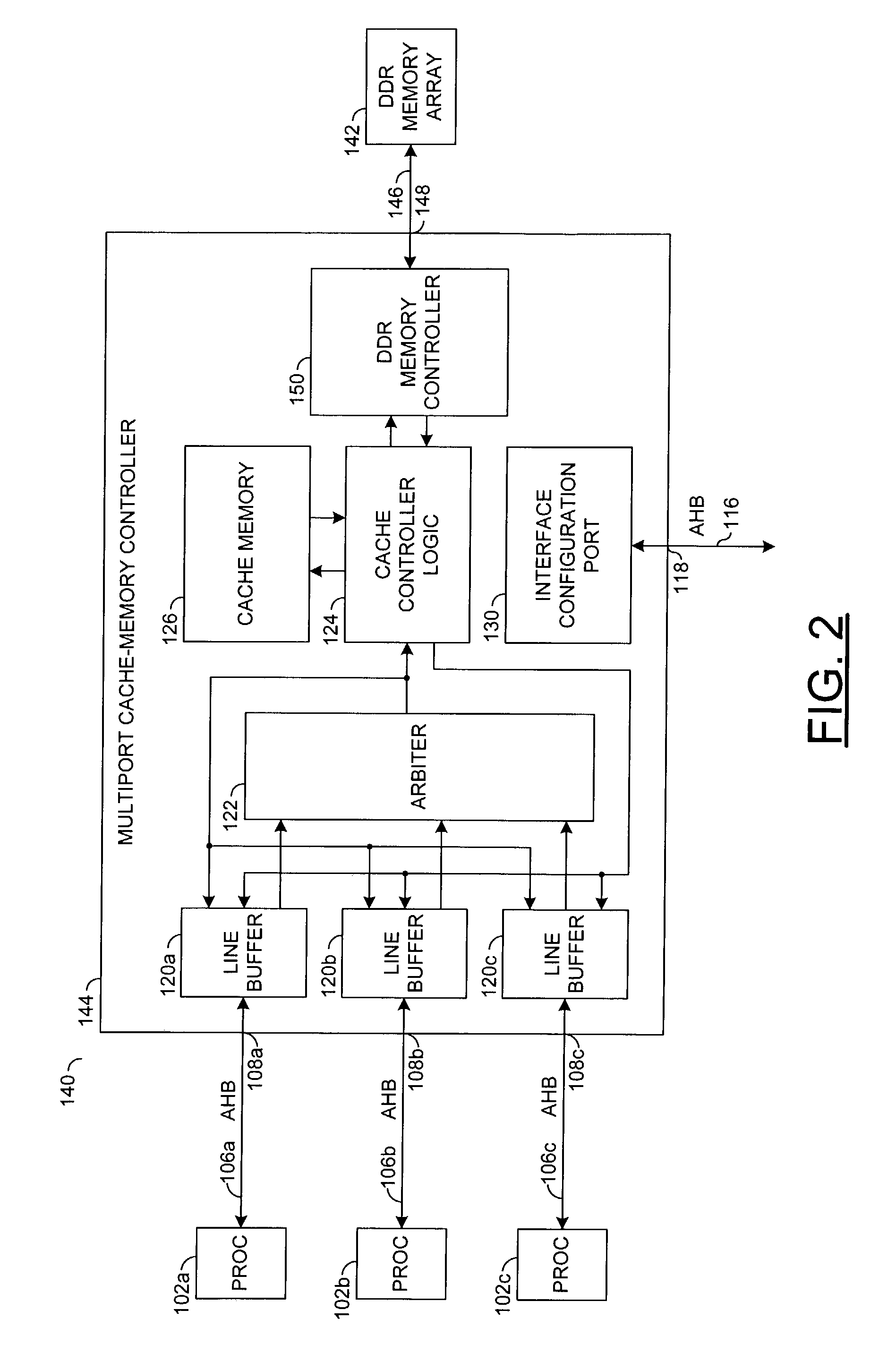

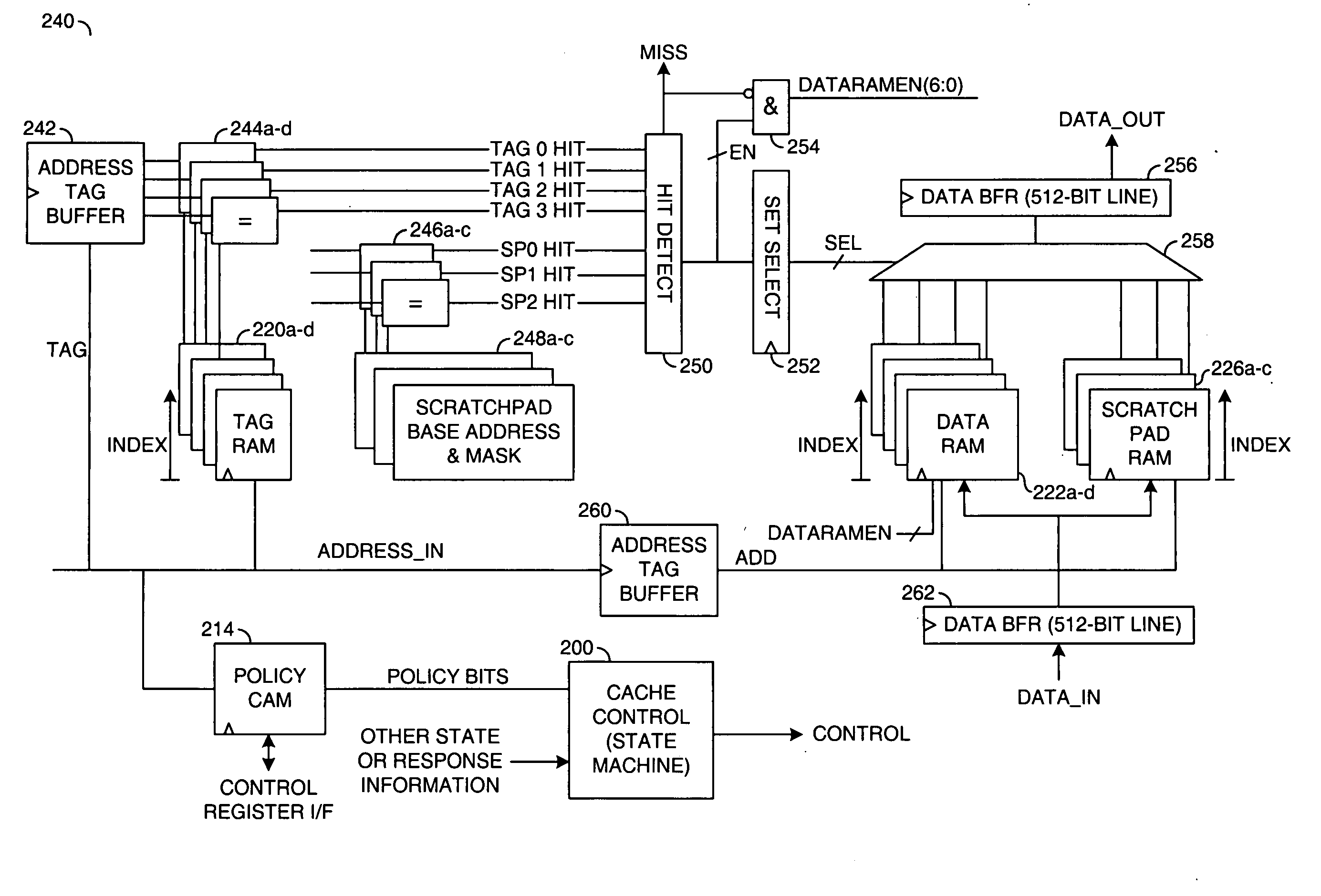

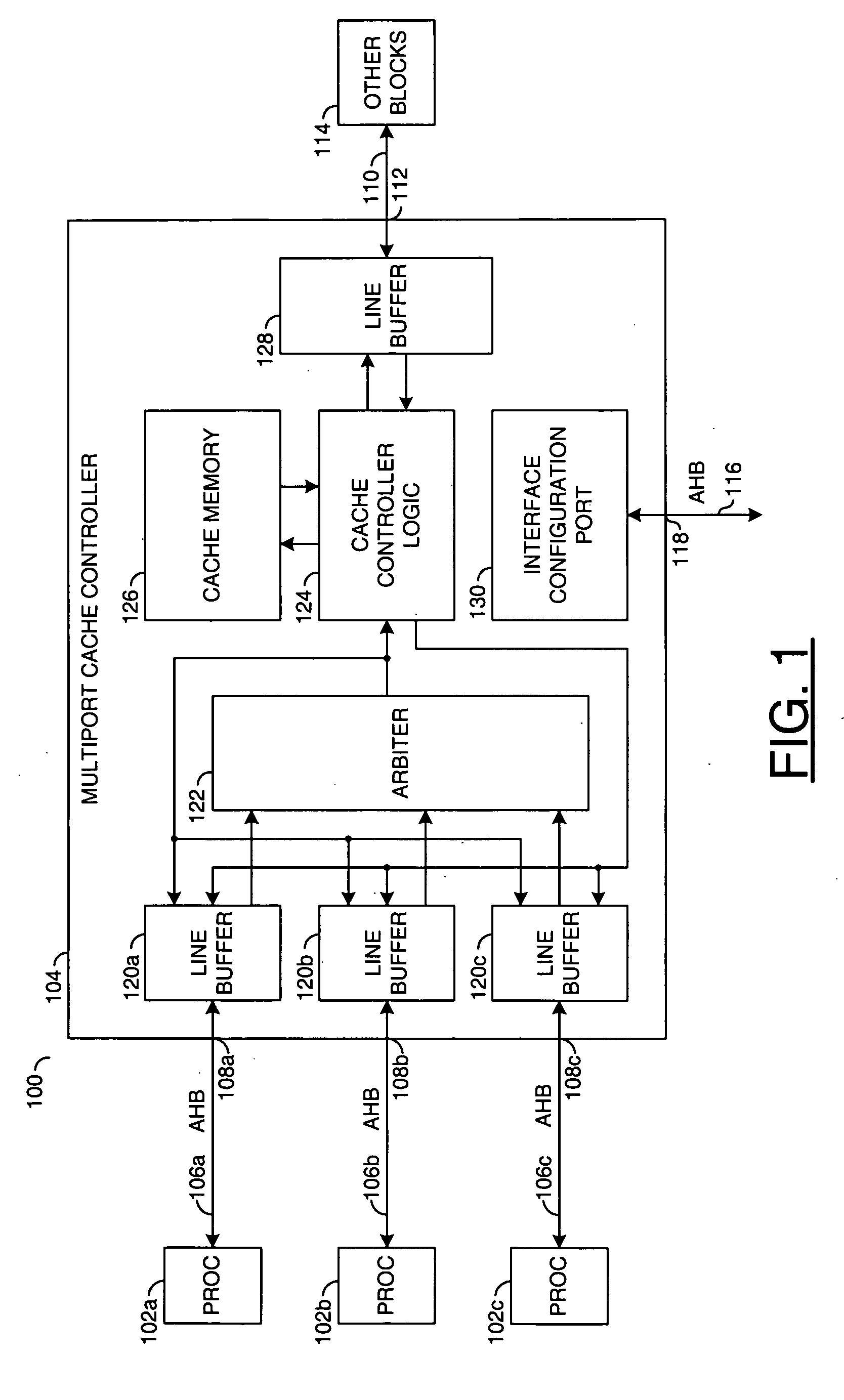

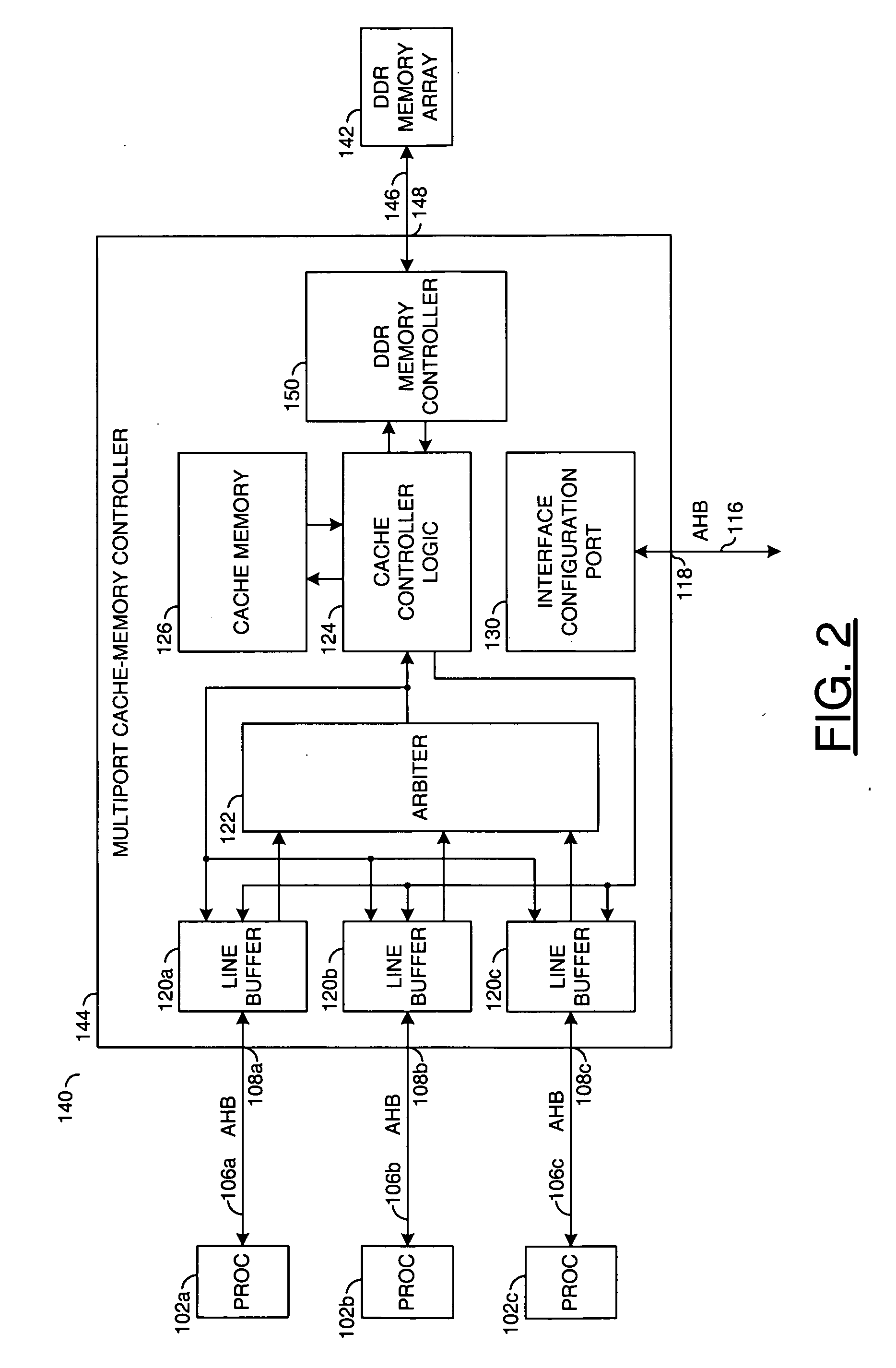

Method for use of ternary CAM to implement software programmable cache policies

InactiveUS7039756B2Variable sizeLimited supportMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingHemt circuits

A method of operating a circuit is disclosed. The method generally comprises the steps of (A) generating a particular policy of a plurality of policies by a lookup operation on a first transaction request received by the circuit, (B) generating a second transaction request for use by a memory external to the circuit based upon the first transaction request and the particular policy in response to a first cache signal of the first transaction request having a non-cacheable state and (C) searching a plurality of address tags for cache data cached within the circuit for a match with the first transaction request in response to the first cache signal having a cacheable state.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

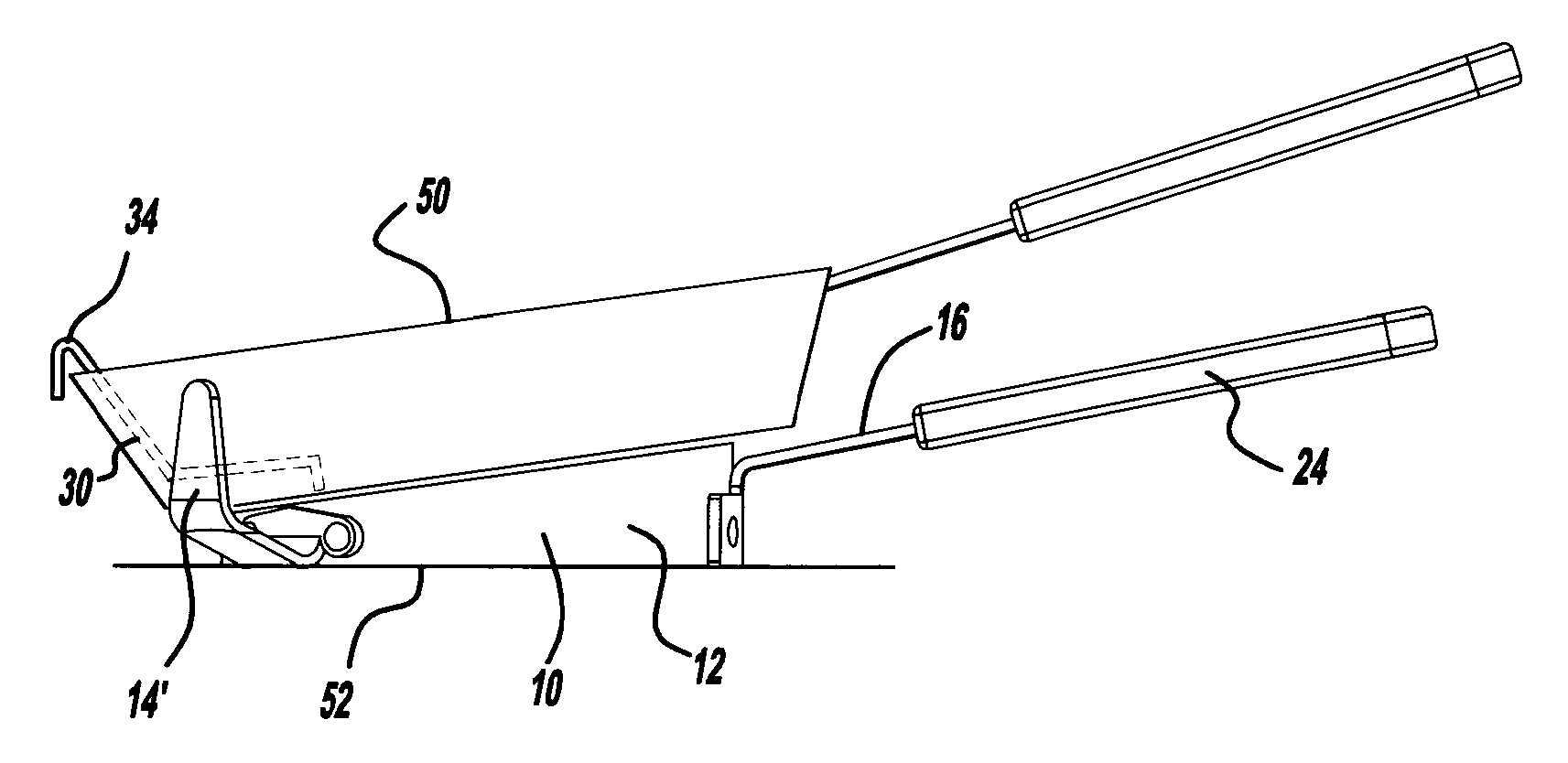

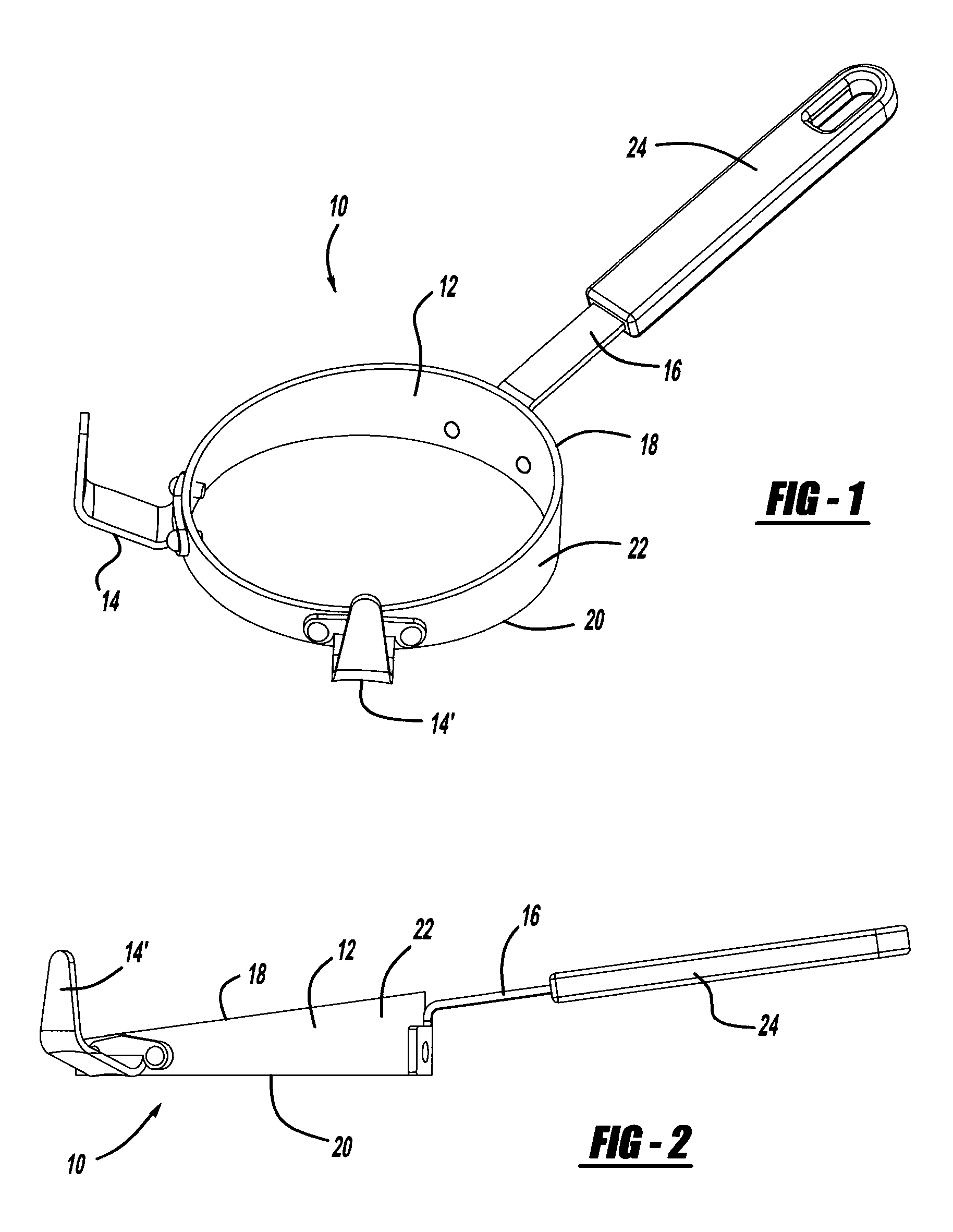

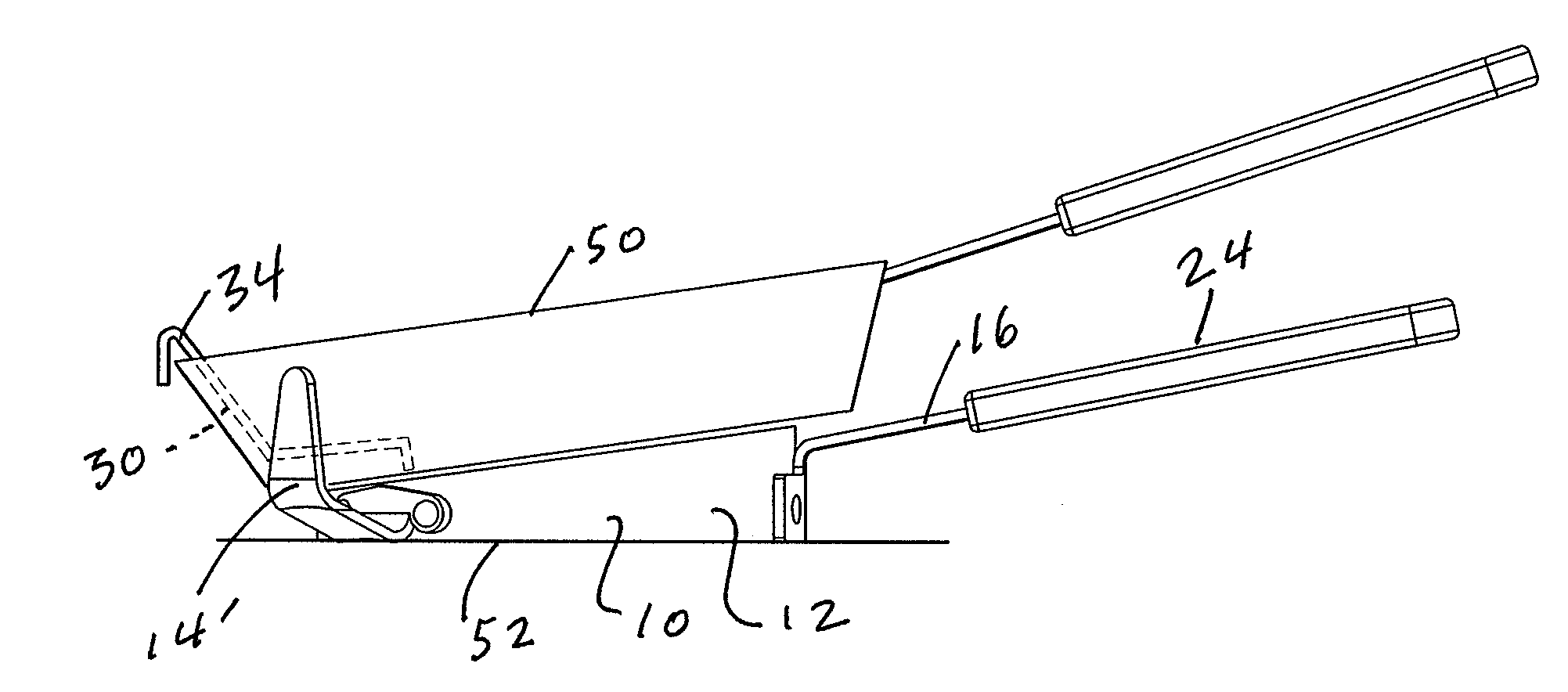

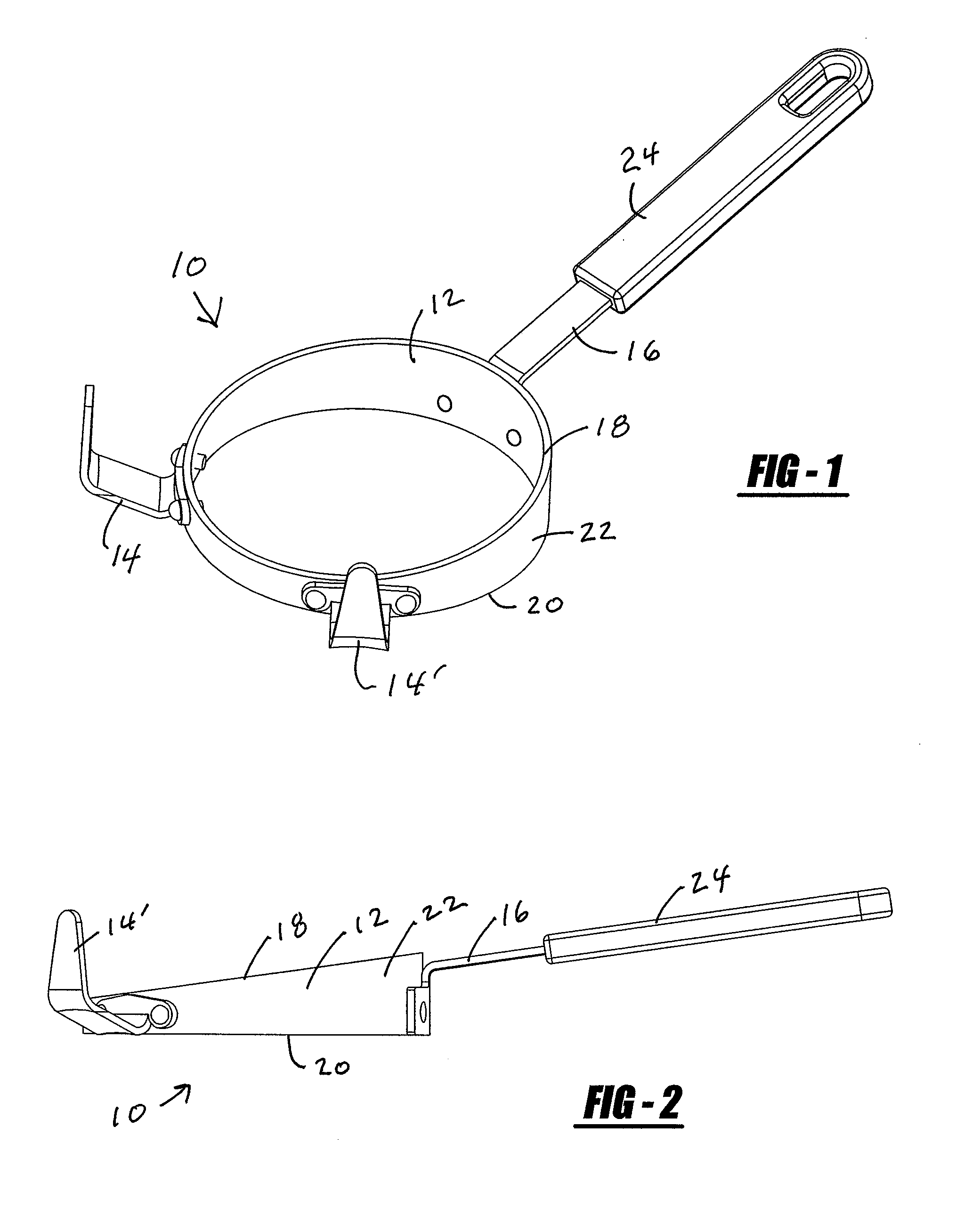

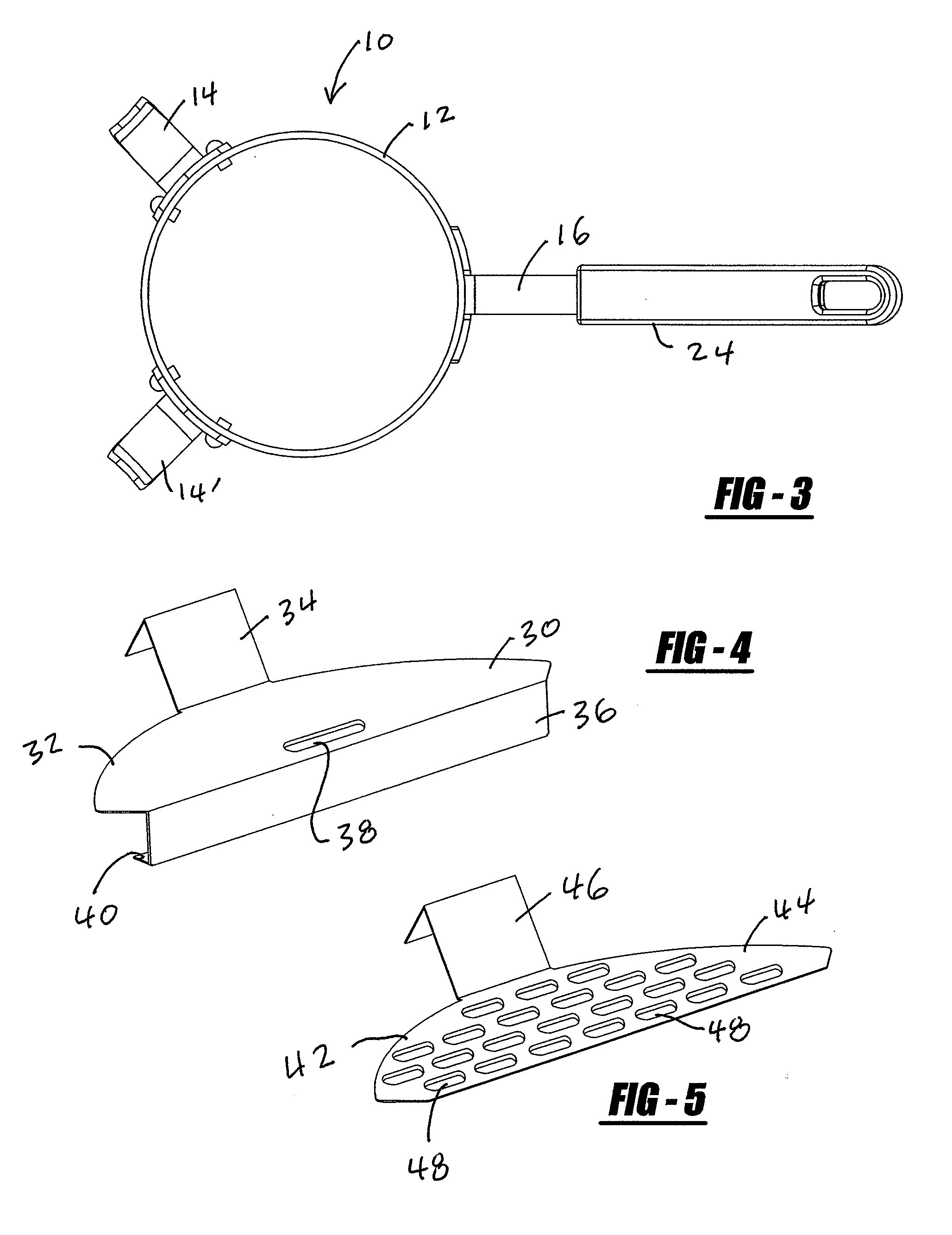

System and method for diverting liquids from foodstuff during preparation in a frying pan

ActiveUS7607387B2Prevents splashing and splatteringEasy to moveMilk preservationJuice extractionEngineeringFrying-pans

A system for directing cooking liquids away from cooking foodstuff in a frying pan is disclosed. The system includes a frying pan supporting structure and a shield. The frying pan supporting structure includes a bottom side for placement on a heating element and a top side upon which said frying pan rests. The bottom side and the top side are angled with respect to each other. The liquid, typically in the form of oil or grease in flowing form, substantially collects under the shield which prevents the splattering and splashing of oil and hot grease on the user.

Owner:STANCZAK EDMUND A

Footwear sole

A sole for an article of footwear having an insert that includes a slot for receiving a gaiter strap. In one embodiment, the insert includes a plurality of support tubes that include internal webs configured to control the support characteristics of each support tube. In one embodiment, a first plurality of support tubes is disposed along the medial side of the sole in the heel region and a second plurality of support tubes is disposed along the lateral side of the sole in the heel region. The insert may include an arch portion that extends through and provides support to the arch region of the sole. The arch portion may define a slot to receive a gaiter strap. The insert may further include a forefoot extension that extends forwardly from the arch along the medial side of the sole. In one embodiment, the sole may include a heel wedge disposed below the insert in the heel region such that the support tubes are supported upon a relatively resilient material. In one embodiment, the insert may include struts that interconnect the medial and lateral support tubes.

Owner:WOLVERINE WORLD WIDE

Apparatus and method for providing dynamizable translations to orthopedic implants

InactiveUS7699879B2Avoid stress shieldingLimited supportSuture equipmentsInternal osteosythesisBone structureJoint arthrodesis

The present invention generally relates to orthopedic devices and methods for treating bone defects. The orthopedic devices can provide sufficient support to the bone defect while allowing bone ingrowth and minimizing the risk to stress shield and / or pseudo-arthrodesis. The bone fixation devices include a biodegradable material or component that further resists relative motion of attached bones and allows the device to gradually transfer at least some load from the device to the growing bone structure in vivo and permitting an increase in the relative motion of bones attached to the device.

Owner:WARSAW ORTHOPEDIC INC

System and method for diverting liquids from foodstuff during preparation in a frying pan

ActiveUS20080017047A1Prevent greasePrevents splashing and splatteringJuice extractionMilk preservationEngineeringHeating element

A system for directing cooking liquids away from cooking foodstuff in a frying pan is disclosed. The system includes a frying pan supporting structure and a shield. The frying pan supporting structure includes a bottom side for placement on a heating element and a top side upon which said frying pan rests. The bottom side and the top side are angled with respect to each other. The liquid, typically in the form of oil or grease in flowing form, substantially collects under the shield which prevents the splattering and splashing of oil and hot grease on the user.

Owner:STANCZAK EDMUND A

Footwear sole

A sole for an article of footwear having an insert with a plurality of support tubes that include internal webs configured to control the support characteristics of each support tube. In one embodiment, a first plurality of support tubes is disposed along the medial side of the sole in the heel region and a second plurality of support tubes is disposed along the lateral side of the sole in the heel region. The insert may include an arch portion that extends through and provides support to the arch region of the sole. The arch portion may define a slot to receive a gaiter strap. The insert may further include a forefoot extension that extends forwardly from the arch along the medial side of the sole. In one embodiment, the sole may include a heel wedge disposed below the insert in the heel region such that the support tubes are supported upon a relatively resilient material. In one embodiment, the insert may include struts that interconnect the medial and lateral support tubes.

Owner:WOLVERINE WORLD WIDE

Branch lookahead prefetch for microprocessors

InactiveUS20080091928A1Easy to handleReduce delaysDigital computer detailsConcurrent instruction executionProcessing InstructionSpeculative execution

A method of handling program instructions in a microprocessor which reduces delays associated with mispredicted branch instructions, by detecting the occurrence of a stall condition during execution of the program instructions, speculatively executing one or more pending instructions which include at least one branch instruction during the stall condition, and determining the validity of data utilized by the speculative execution. Dispatch logic determines the validity of the data by marking one or more registers of an instruction dispatch unit to indicate which results of the pending instructions are invalid. The speculative execution of instructions can occur across multiple pipeline stages of the microprocessor, and the validity of the data is tracked during their execution in the multiple pipeline stages while monitoring a dependency of the speculatively executed instructions relative to one another during their execution in the multiple pipeline stages.

Owner:INT BUSINESS MASCH CORP

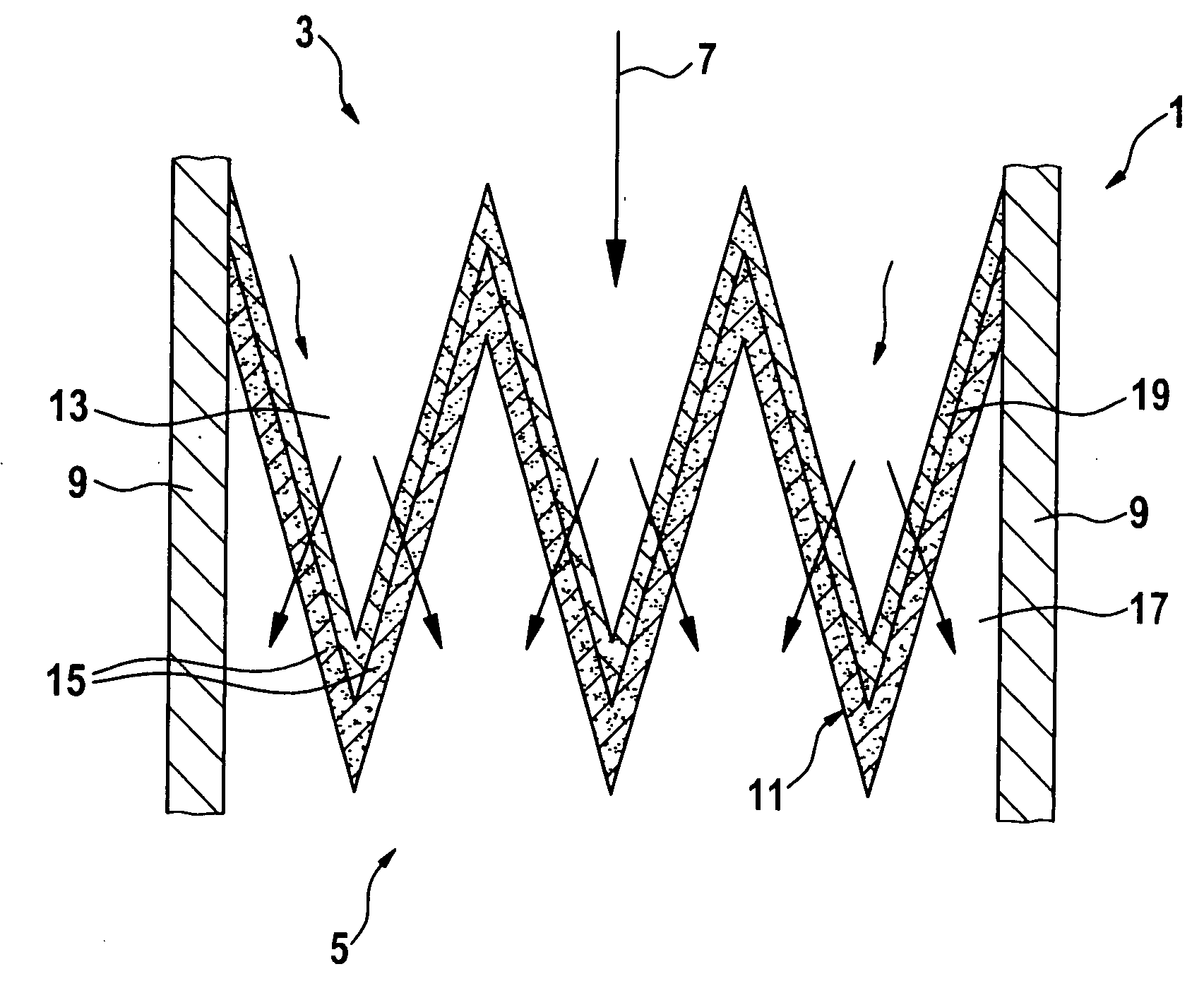

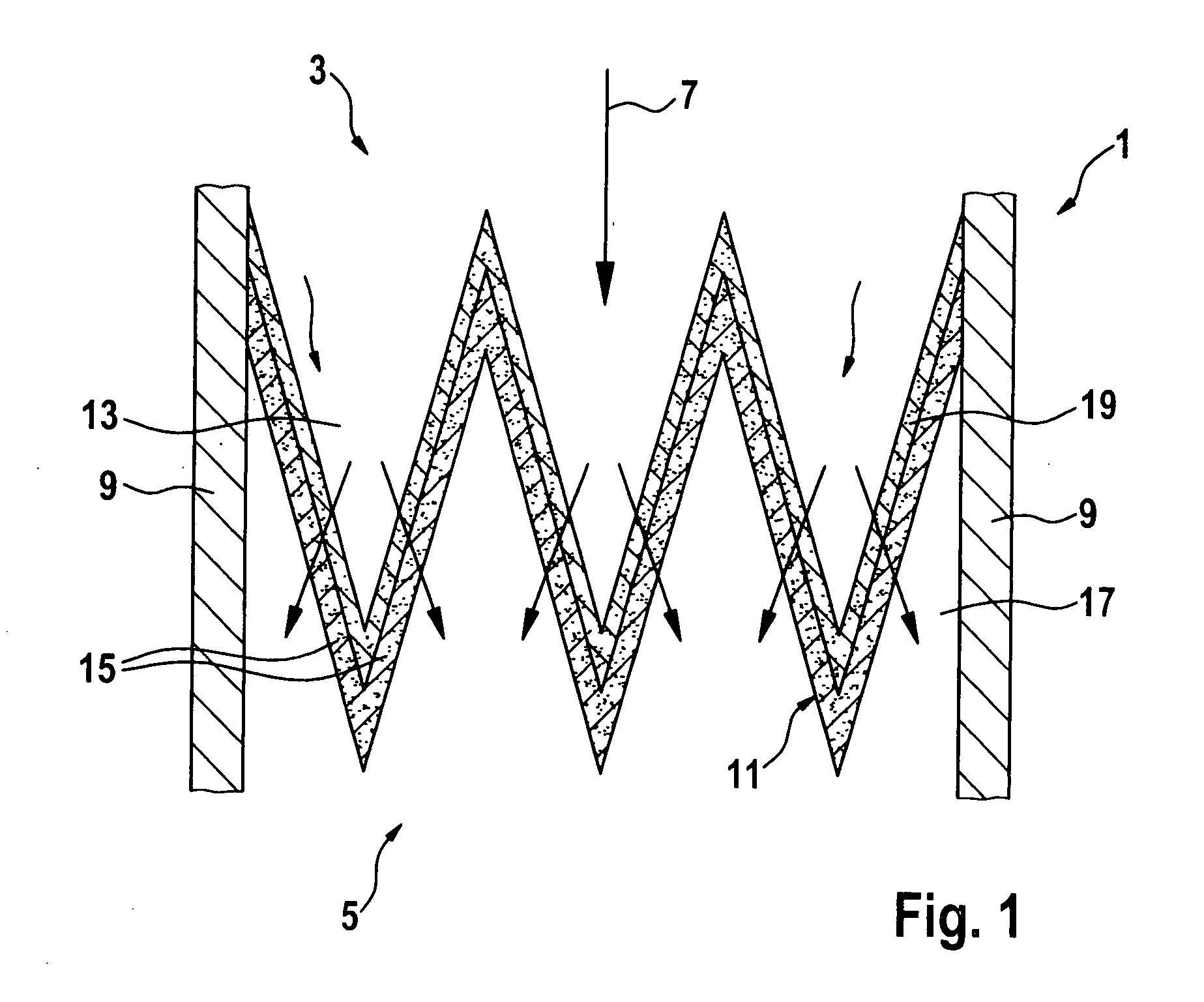

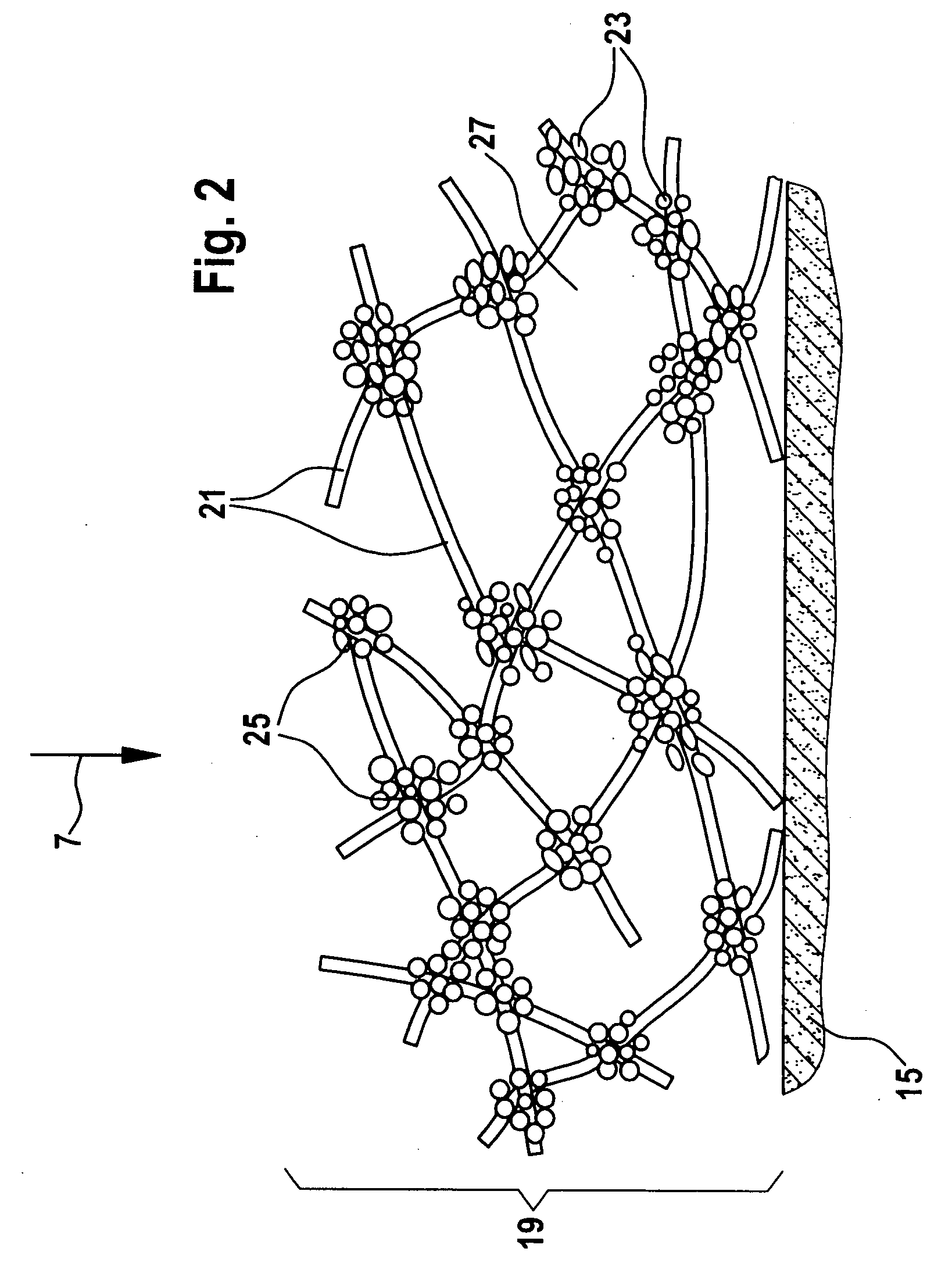

Filter for purifying gas mixtures and method for its manufacture

InactiveUS20070289270A1Increase capacityImprove mutual adhesionCombination devicesGas treatmentFiberParticulates

A filter for purifying gas mixtures containing particulates, in particular exhaust gases of internal combustion engines containing soot. The filter has a porous wall made of a filter base material through which the gas mixture to be purified flows. A surface coating of ceramic fibers is applied to the surface of the wall which is exposed to the flow of the gas mixture to be purified. The ceramic fibers are coated with nanoparticles. Furthermore, a method for manufacturing such a filter.

Owner:ROBERT BOSCH GMBH

Ternary cam with software programmable cache policies

InactiveUS20060117143A1Variable sizeLimited supportMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingSoftware

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

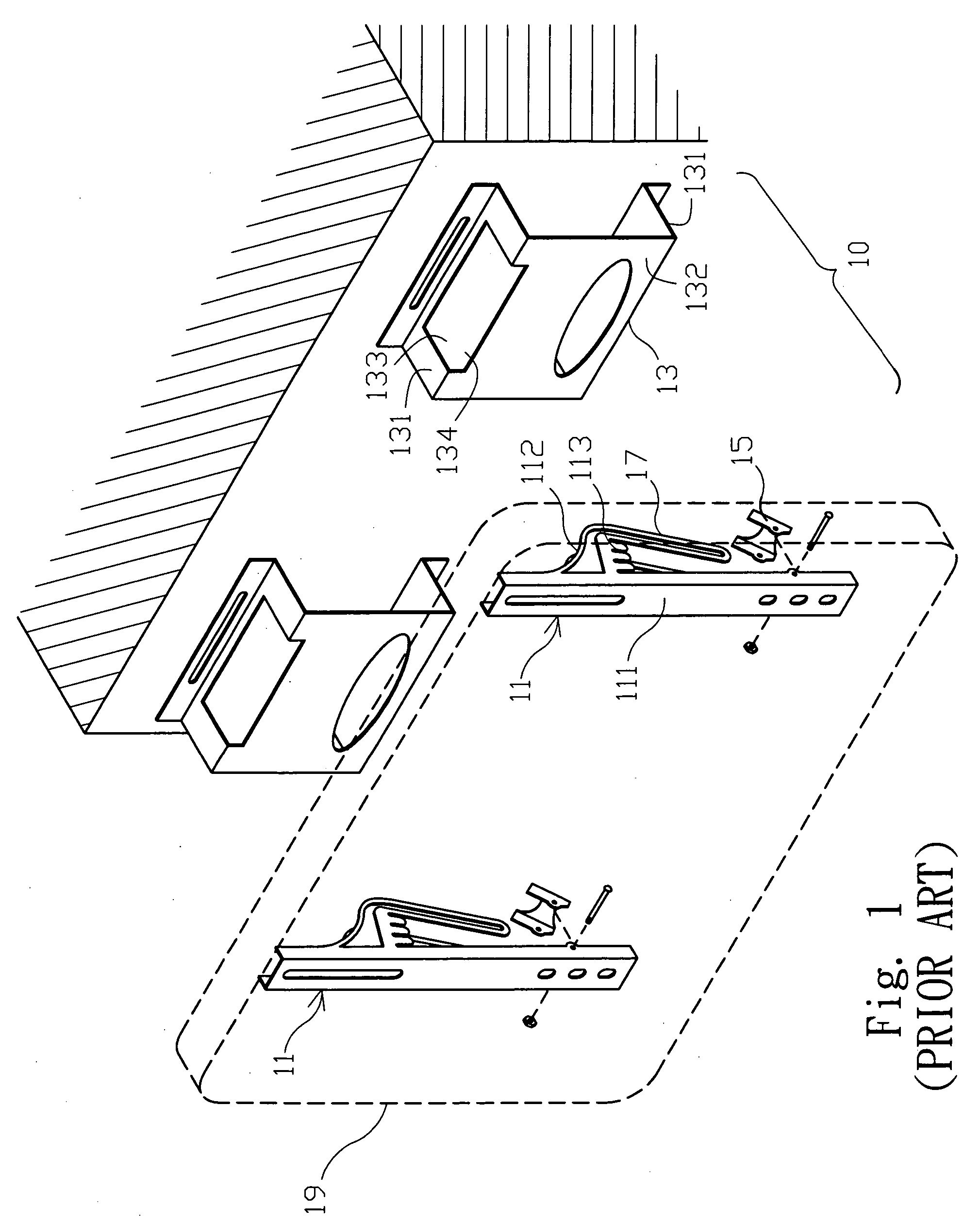

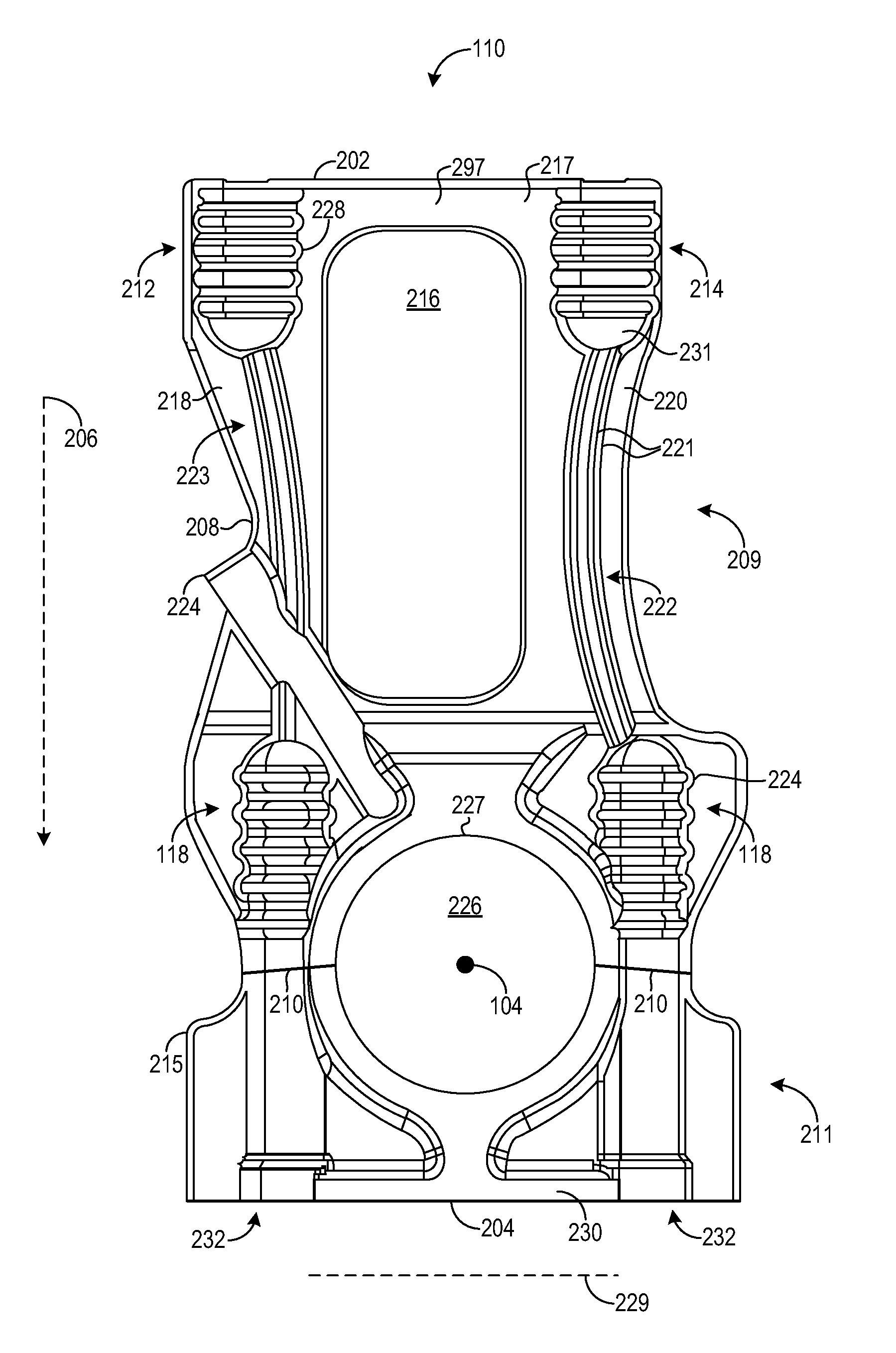

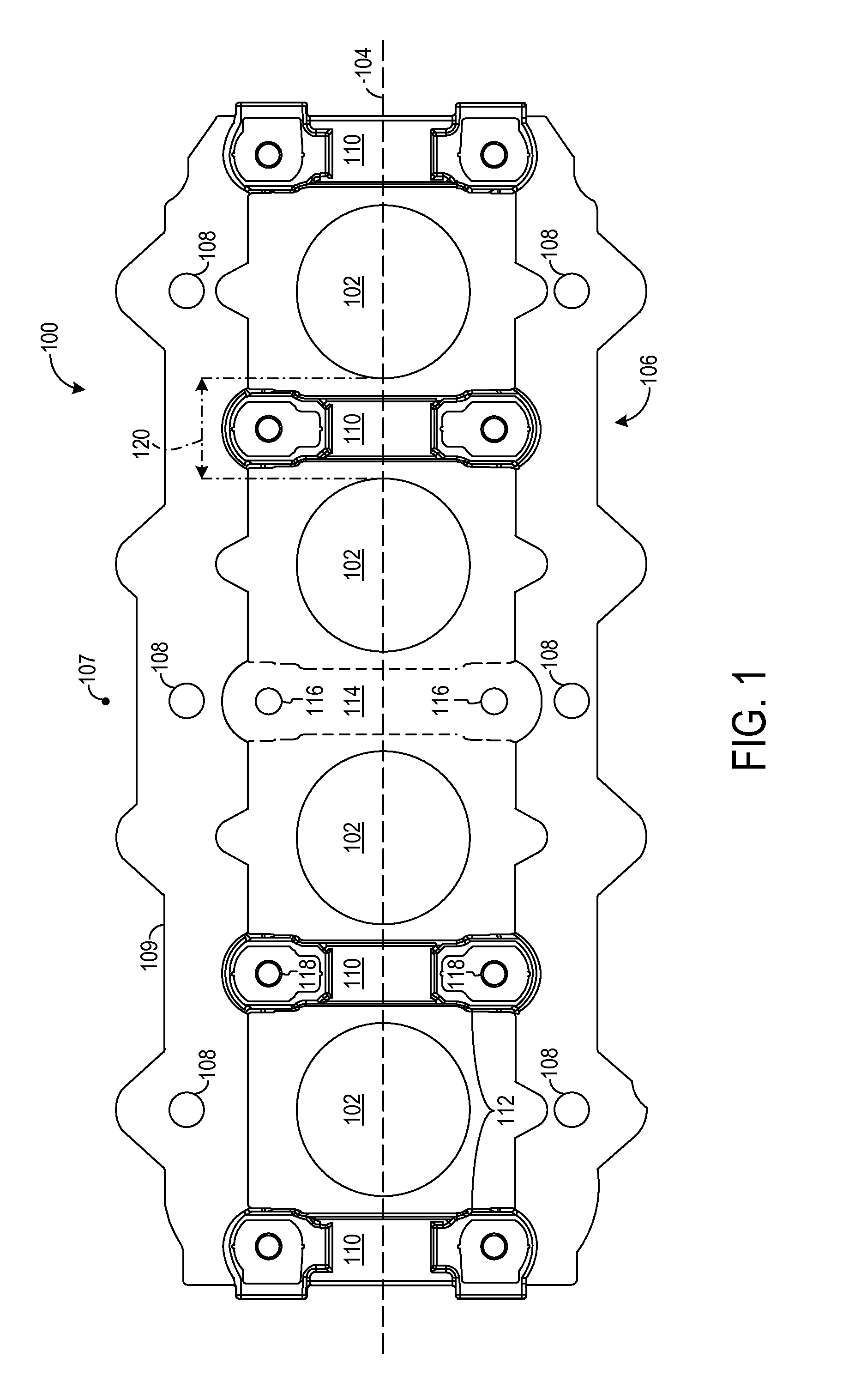

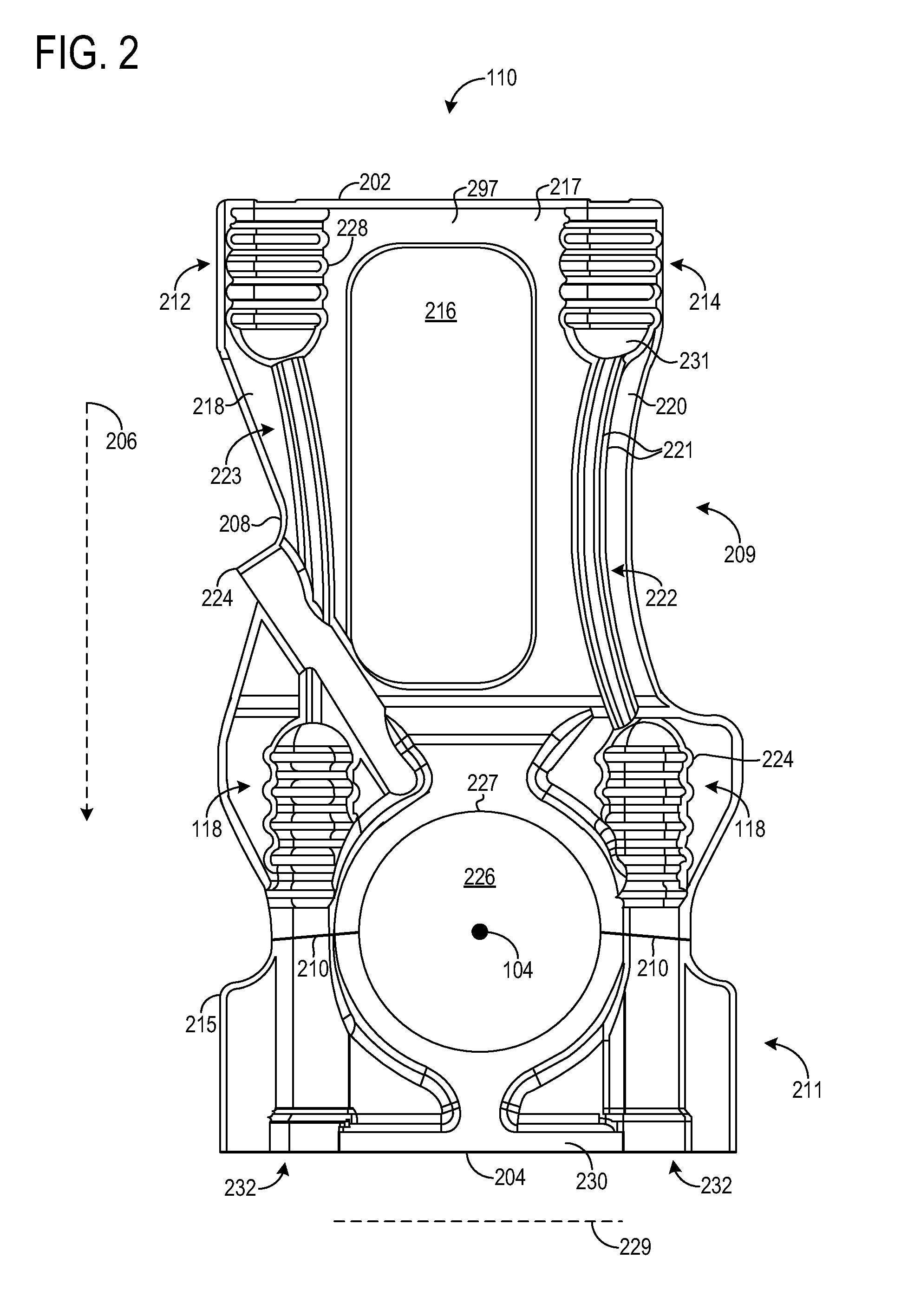

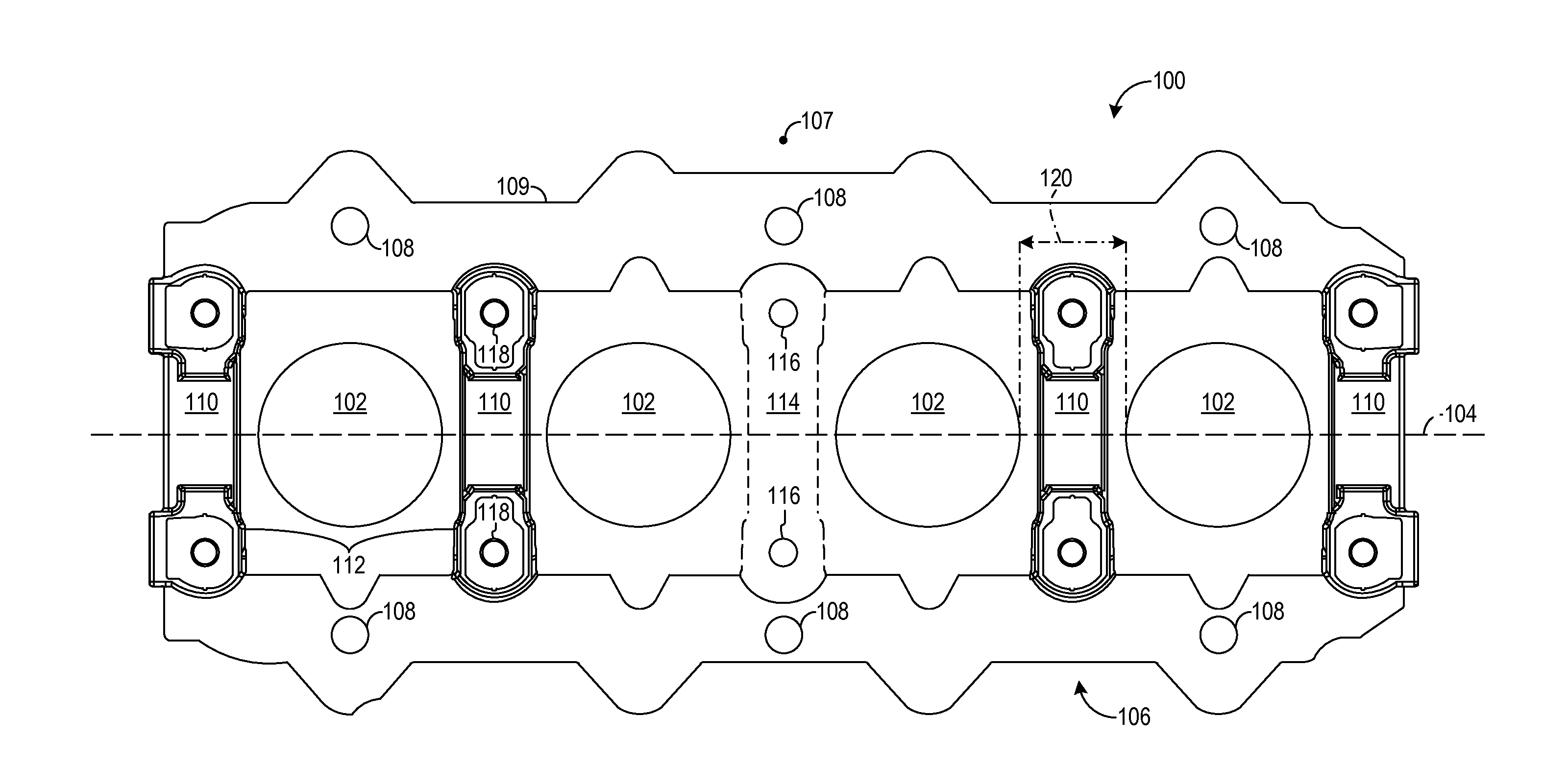

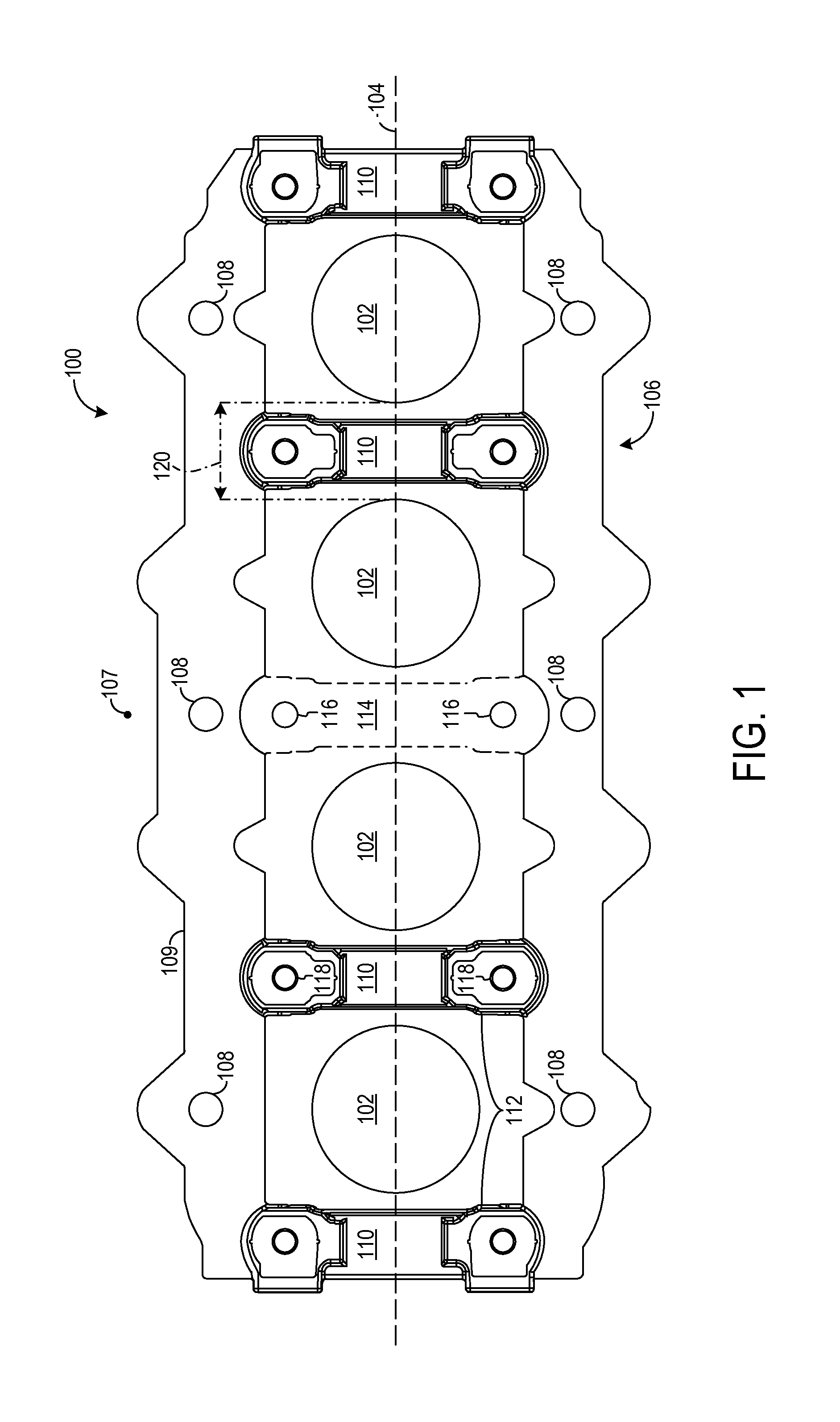

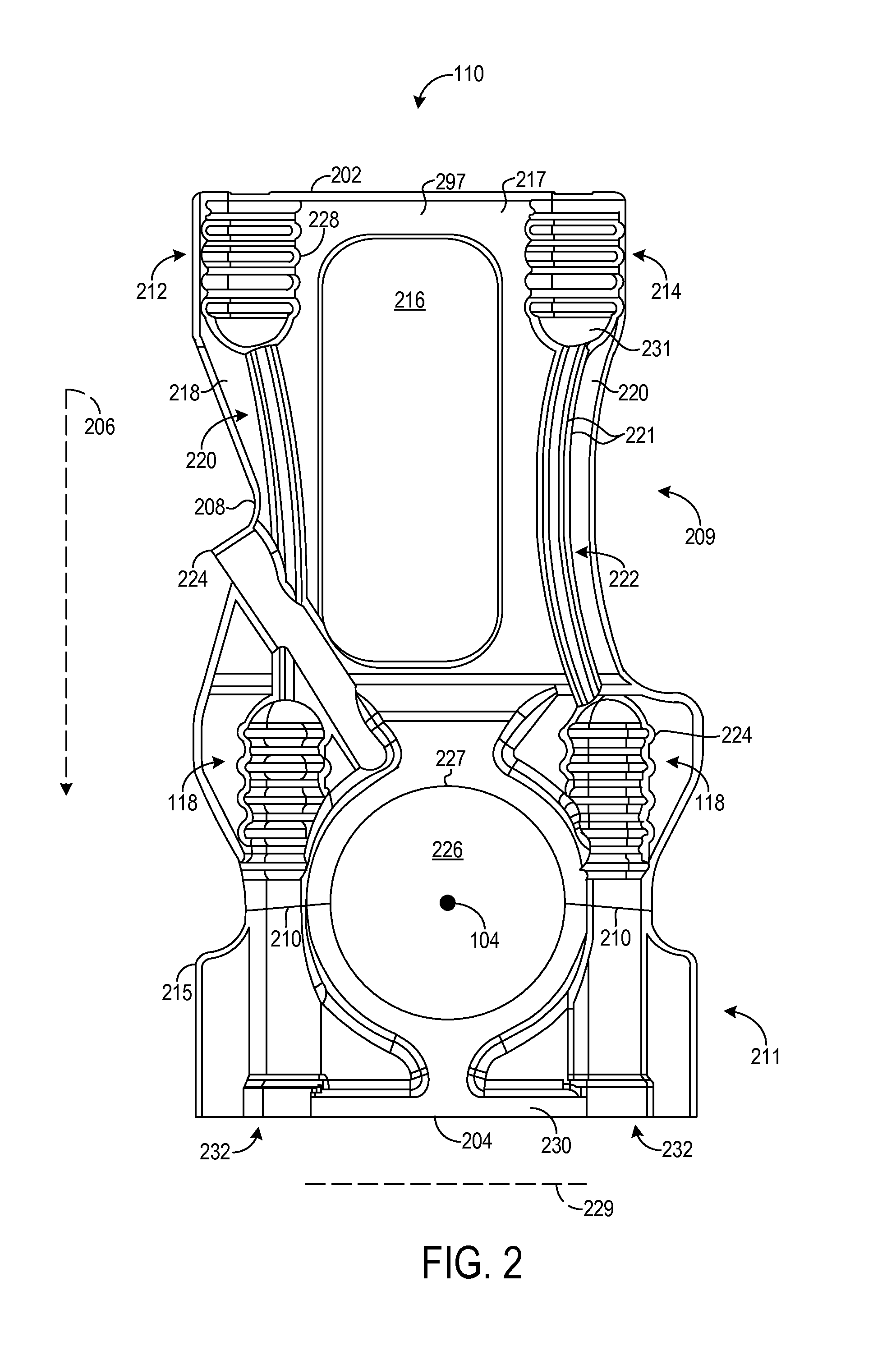

Cracked cap bulkhead insert

ActiveUS9086031B2Increases stiffness and structural integrityIncreases volume and massCasingsMachines/enginesEngineeringCrankcase

Owner:FORD GLOBAL TECH LLC

Cracked cap bulkhead insert

ActiveUS20140261285A1Increase stiffnessImproves Structural IntegrityCasingsCylinder headsCrankcaseCylinder block

Various bulkhead inserts having a cracked cap are provided. In one example, a cylinder block includes a plurality of cylinder bores, a crankcase disposed below the cylinder block in a vertical direction, and a plurality of inserts, where each adjacent pair of inserts of the plurality of inserts partitions each cylinder bore of the plurality of cylinder bores. Each insert of the plurality of inserts has an upper portion and a cap disposed below the upper portion, the cap cracked from the upper portion and rejoined to the upper portion by one or more fastening devices, the upper having one or more upper bosses, each upper boss having a surface with extruded, circumferentially-extending serrations.

Owner:FORD GLOBAL TECH LLC

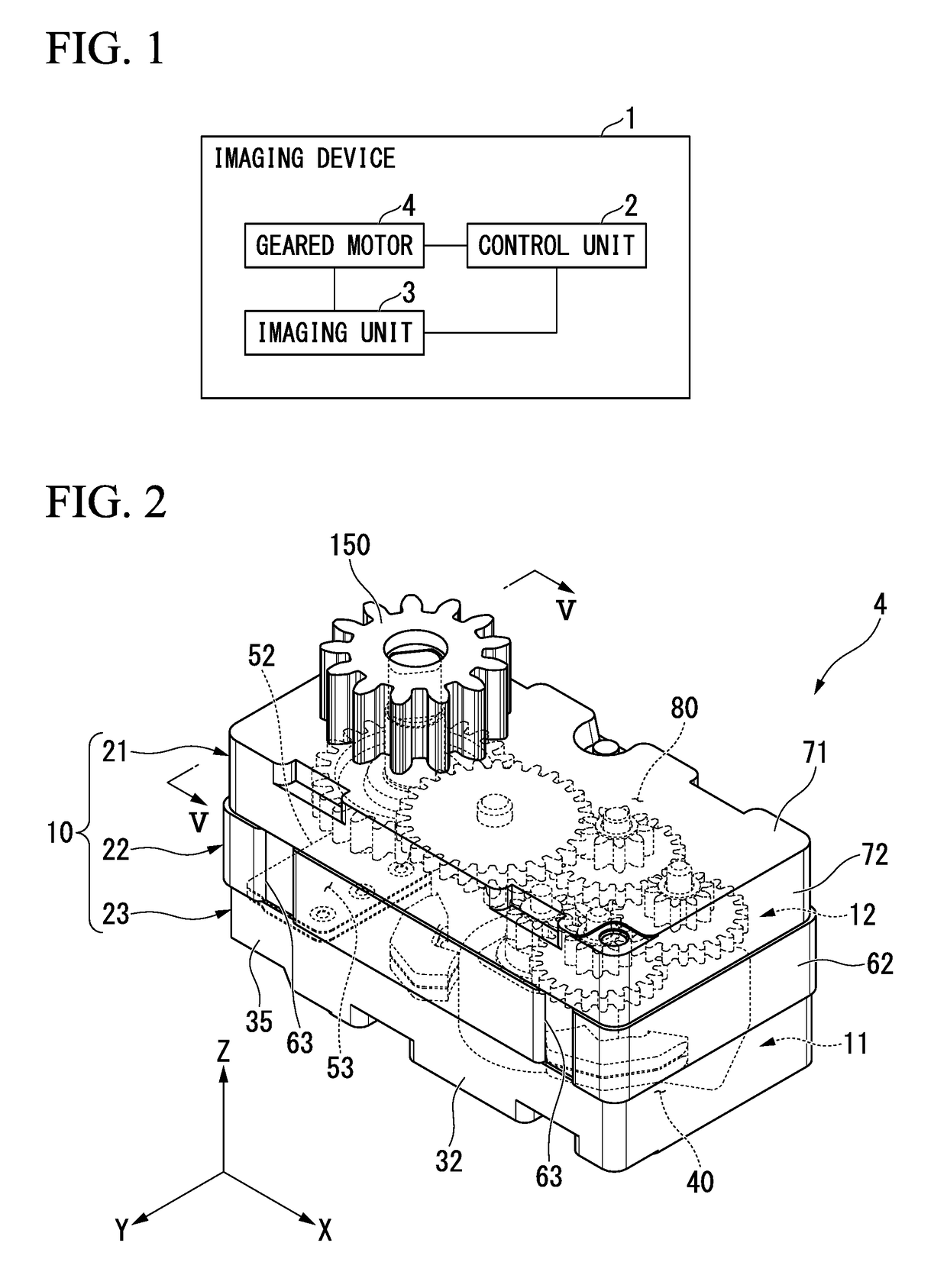

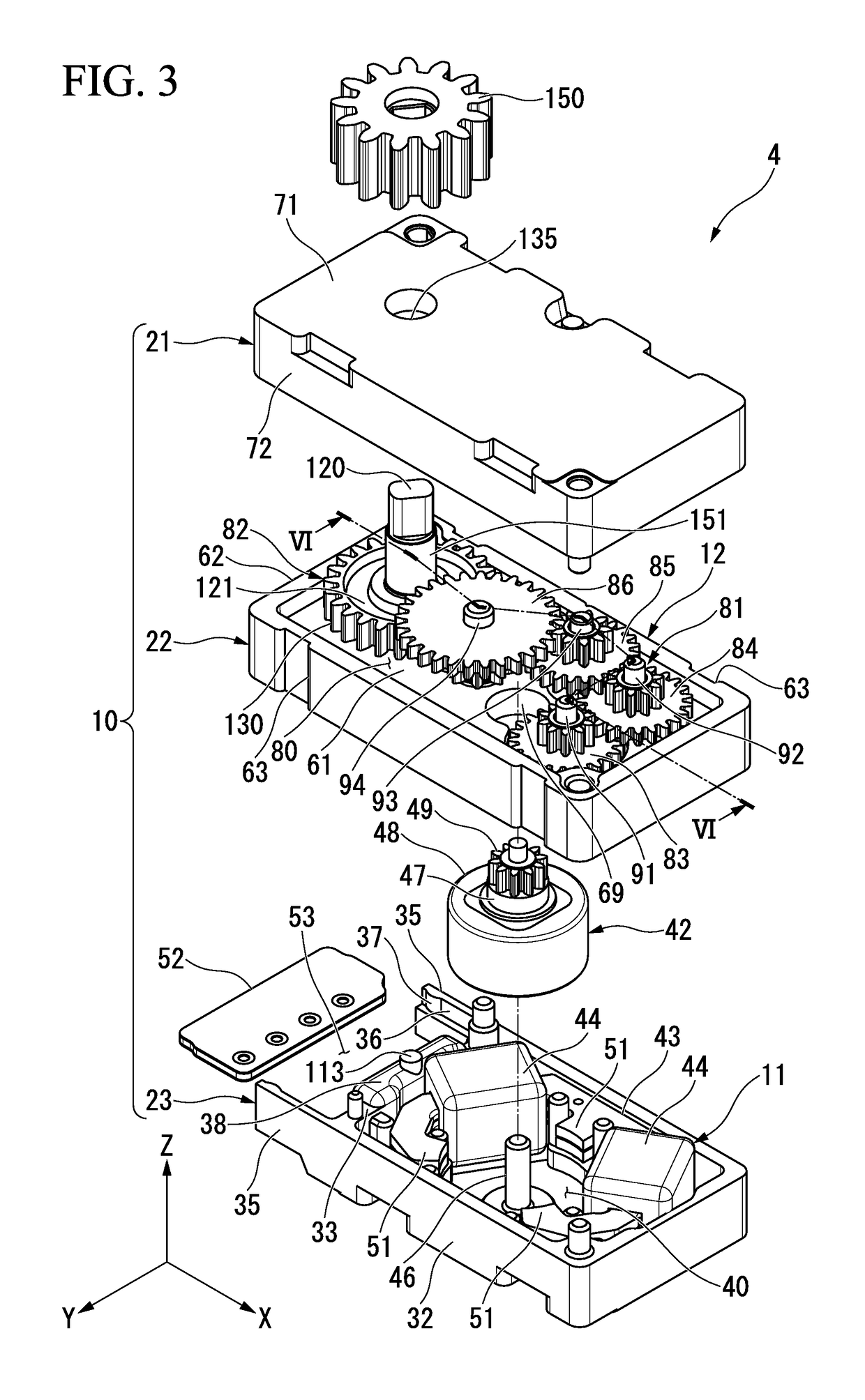

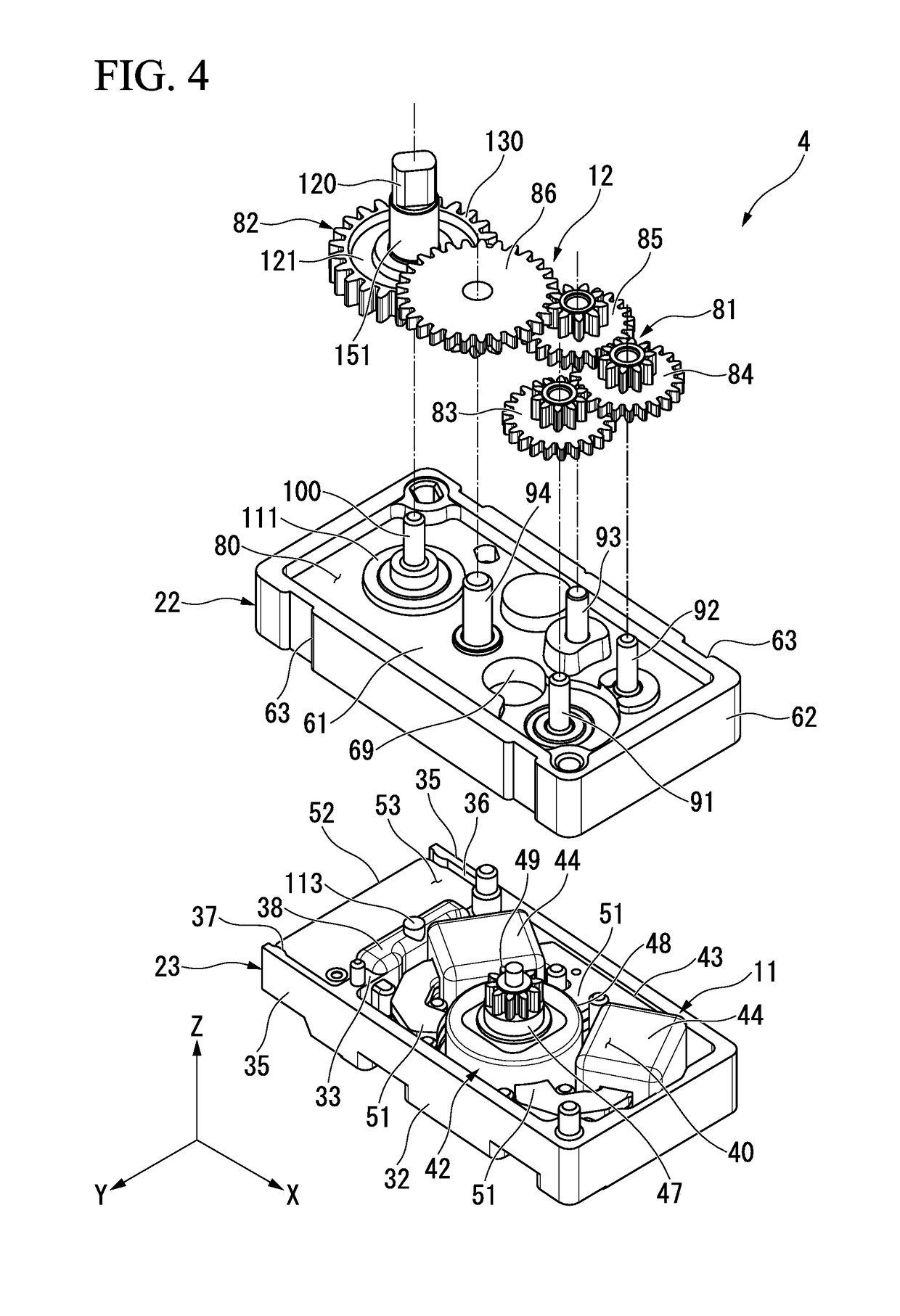

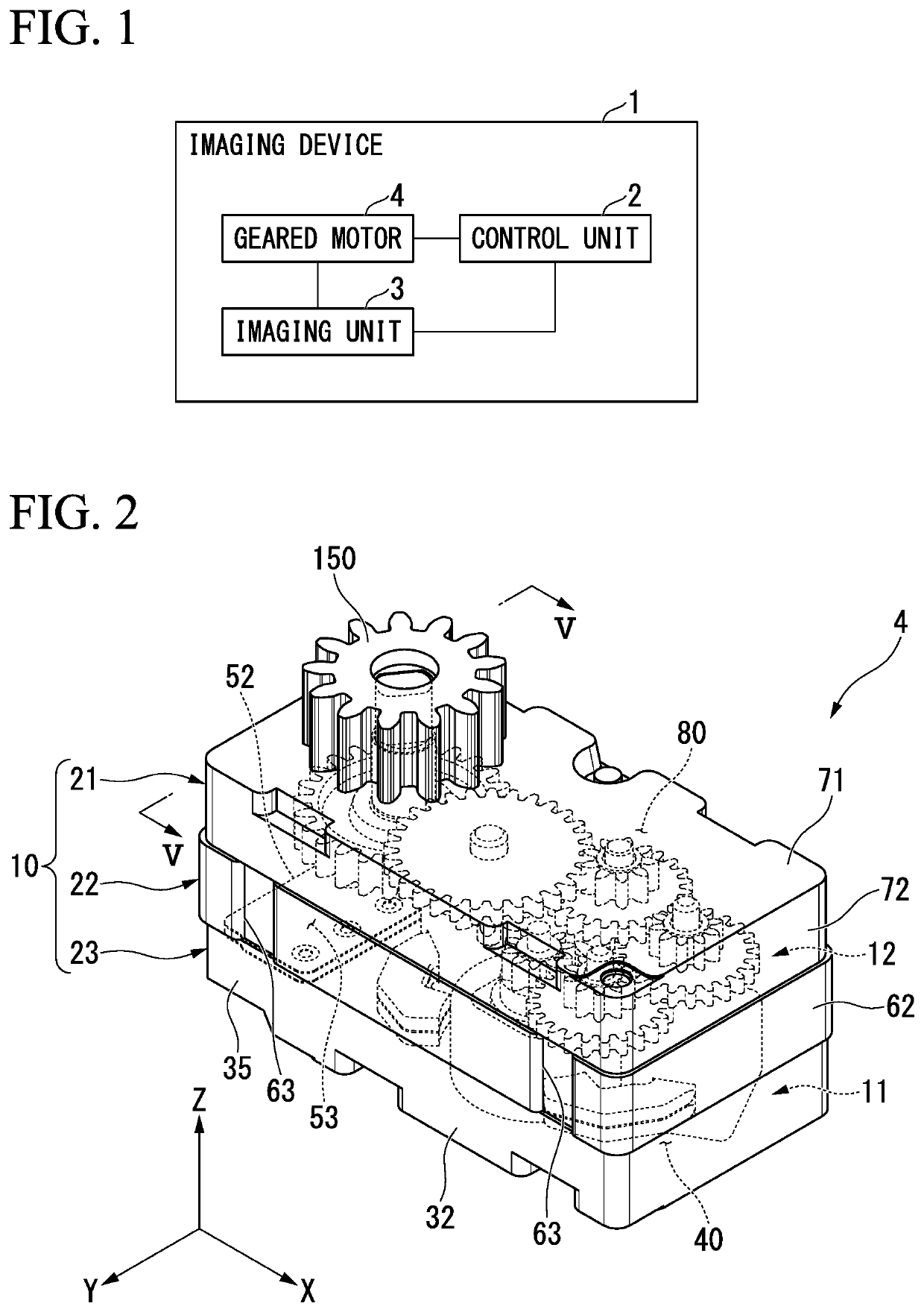

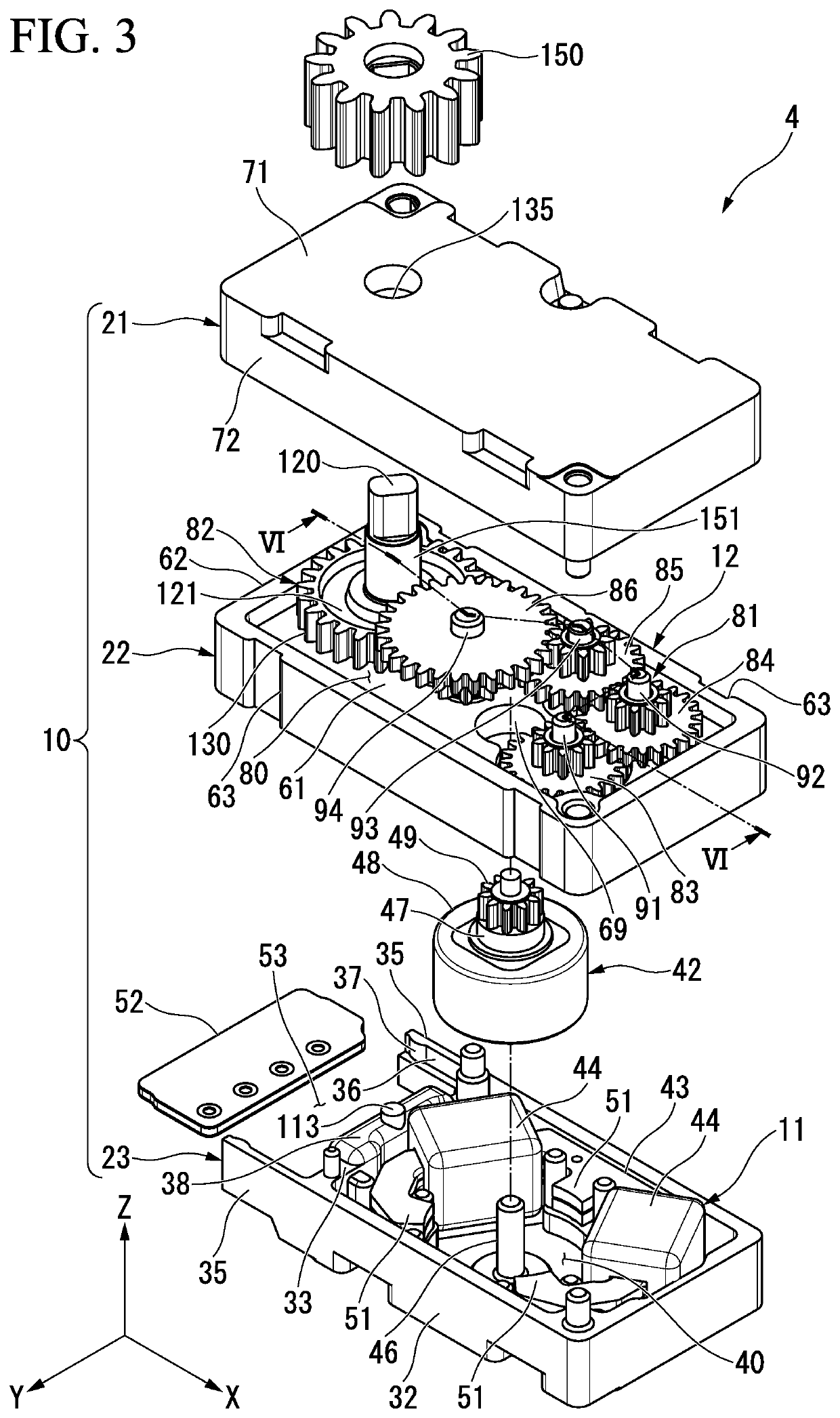

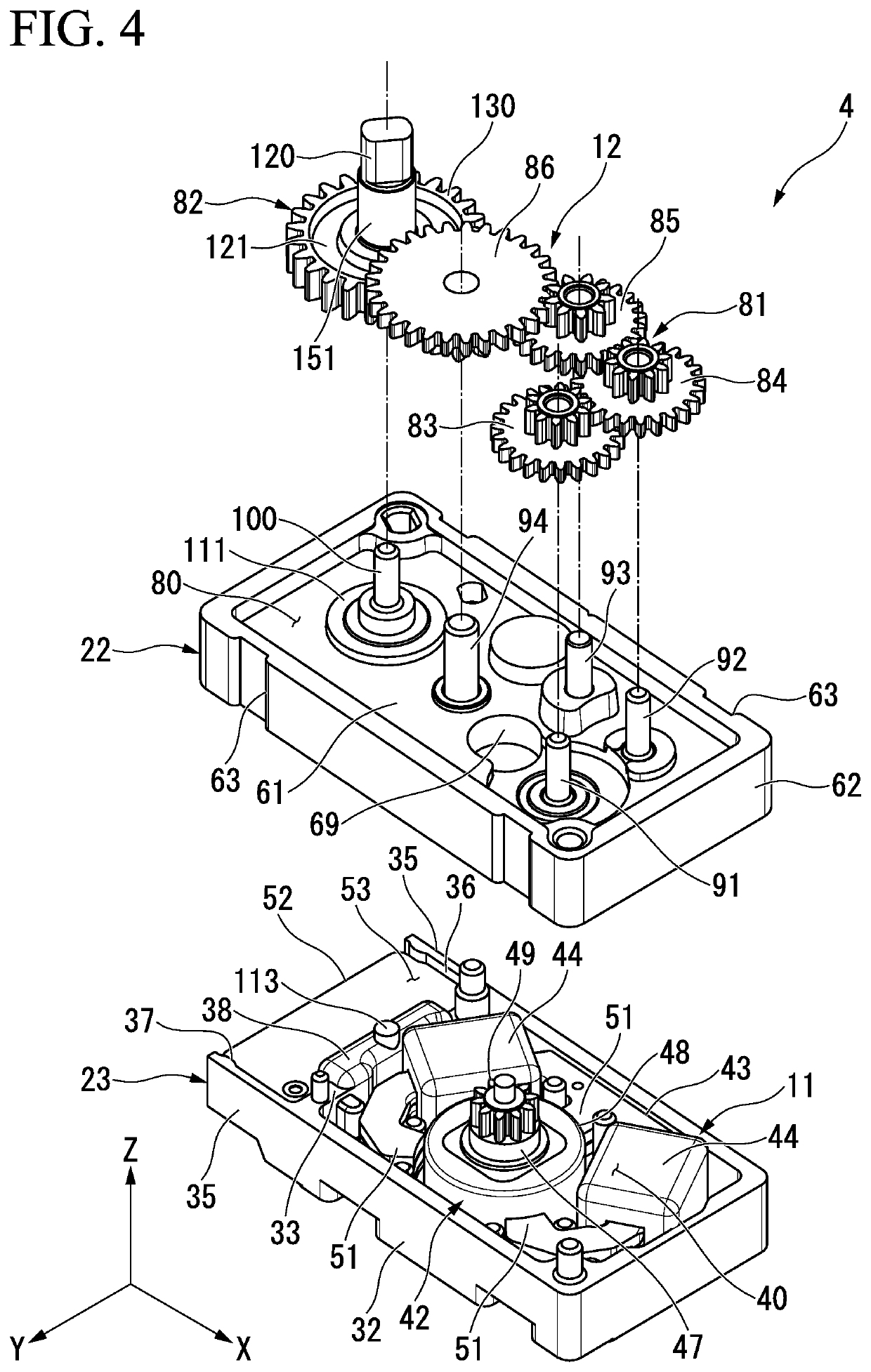

Gear box, driving device, and electronic apparatus

ActiveUS20180347682A1Drive stabilitySuppress lead to damageToothed gearingsMechanical energy handlingEngineeringPinion

A gear box includes a casing having a partition portion, a supporting shaft fixed to the partition portion, and an output shaft supported so as to be rotatable around the supporting shaft and to which a pinion gear is fixed. The casing has a division wall that is positioned in the −Z direction with respect to the partition portion and is capable of abutting against the supporting shaft. The division wall constitutes a portion of a motor accommodation portion for accommodating a motor.

Owner:SEIKO INSTR INC

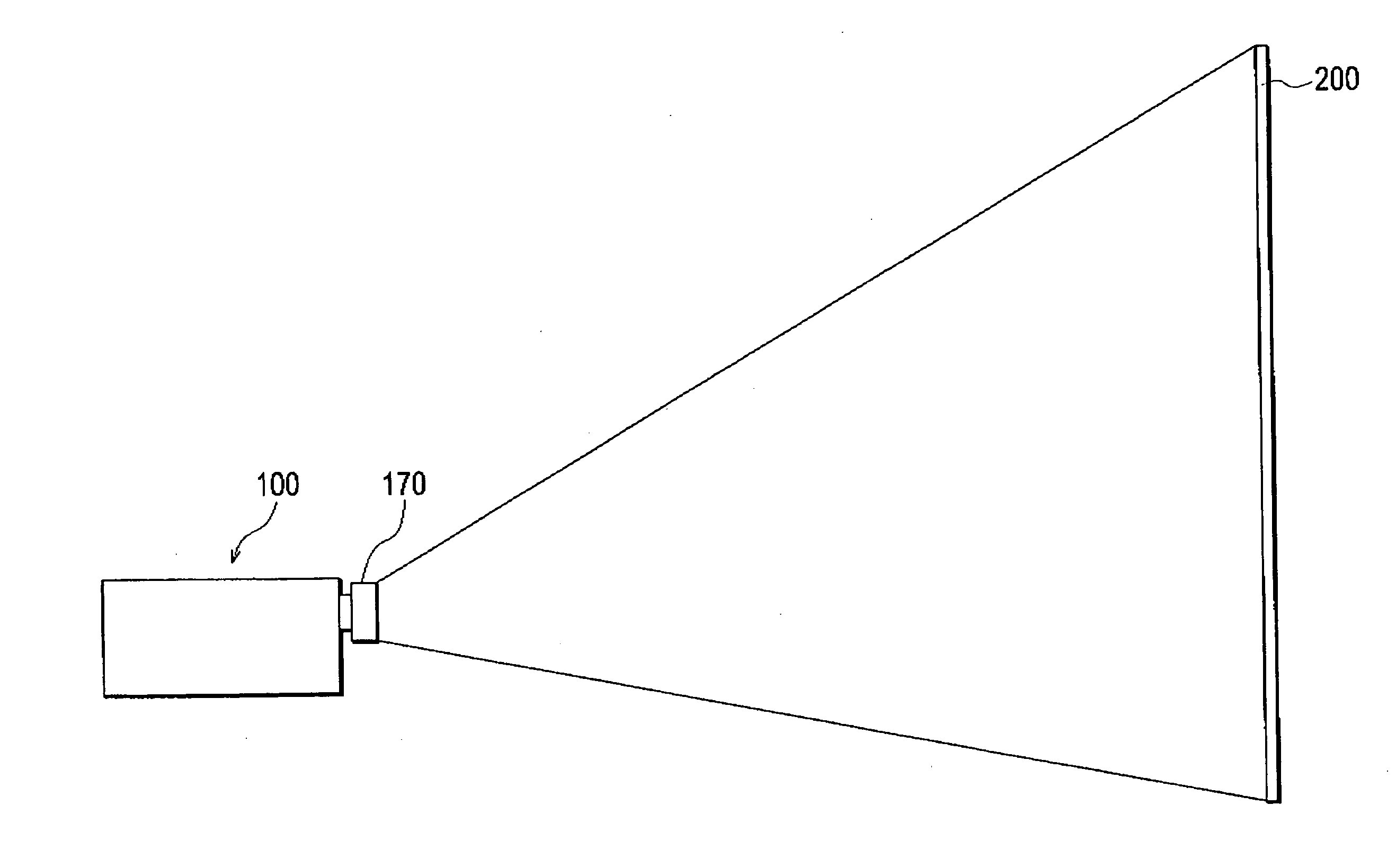

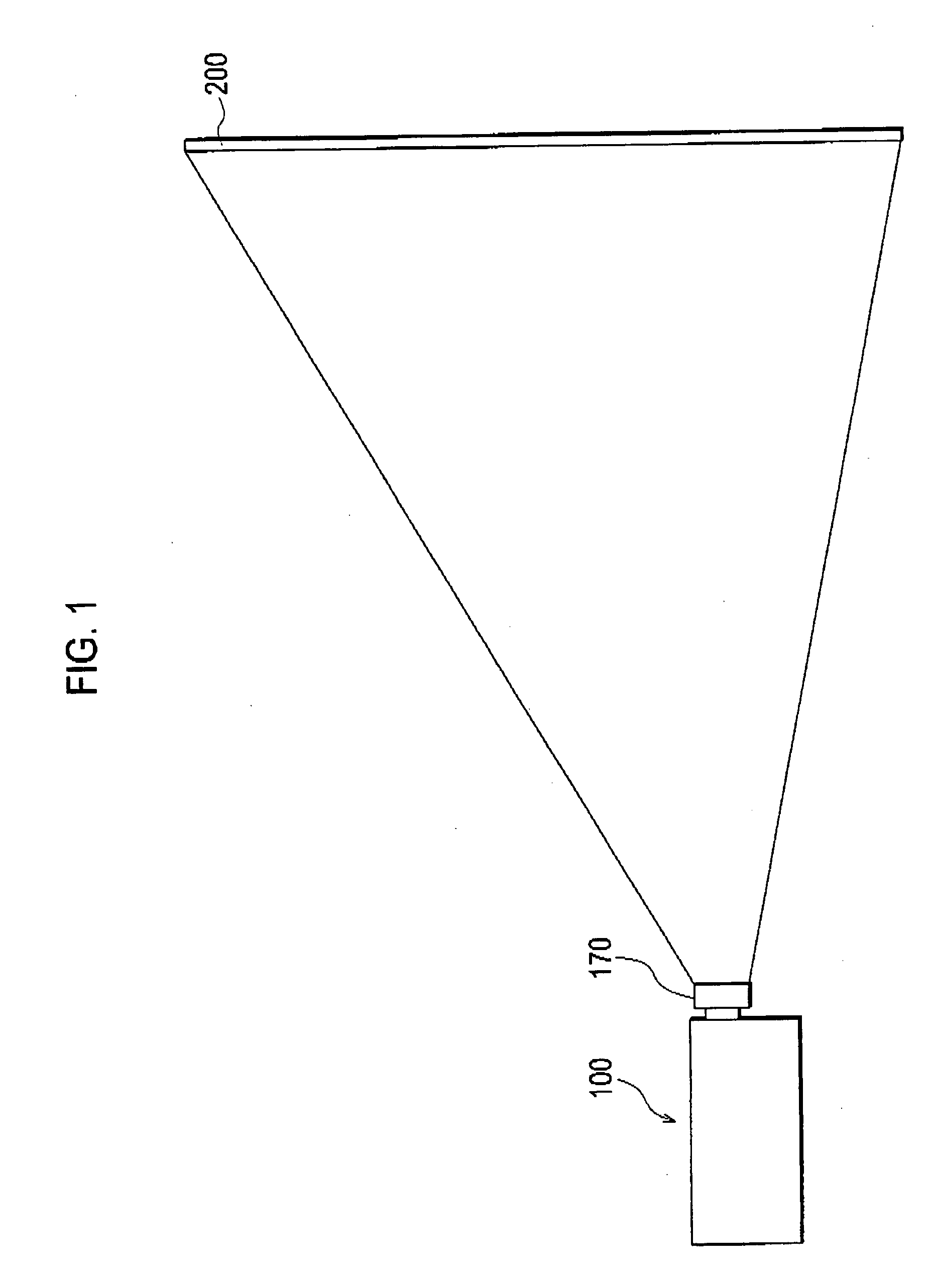

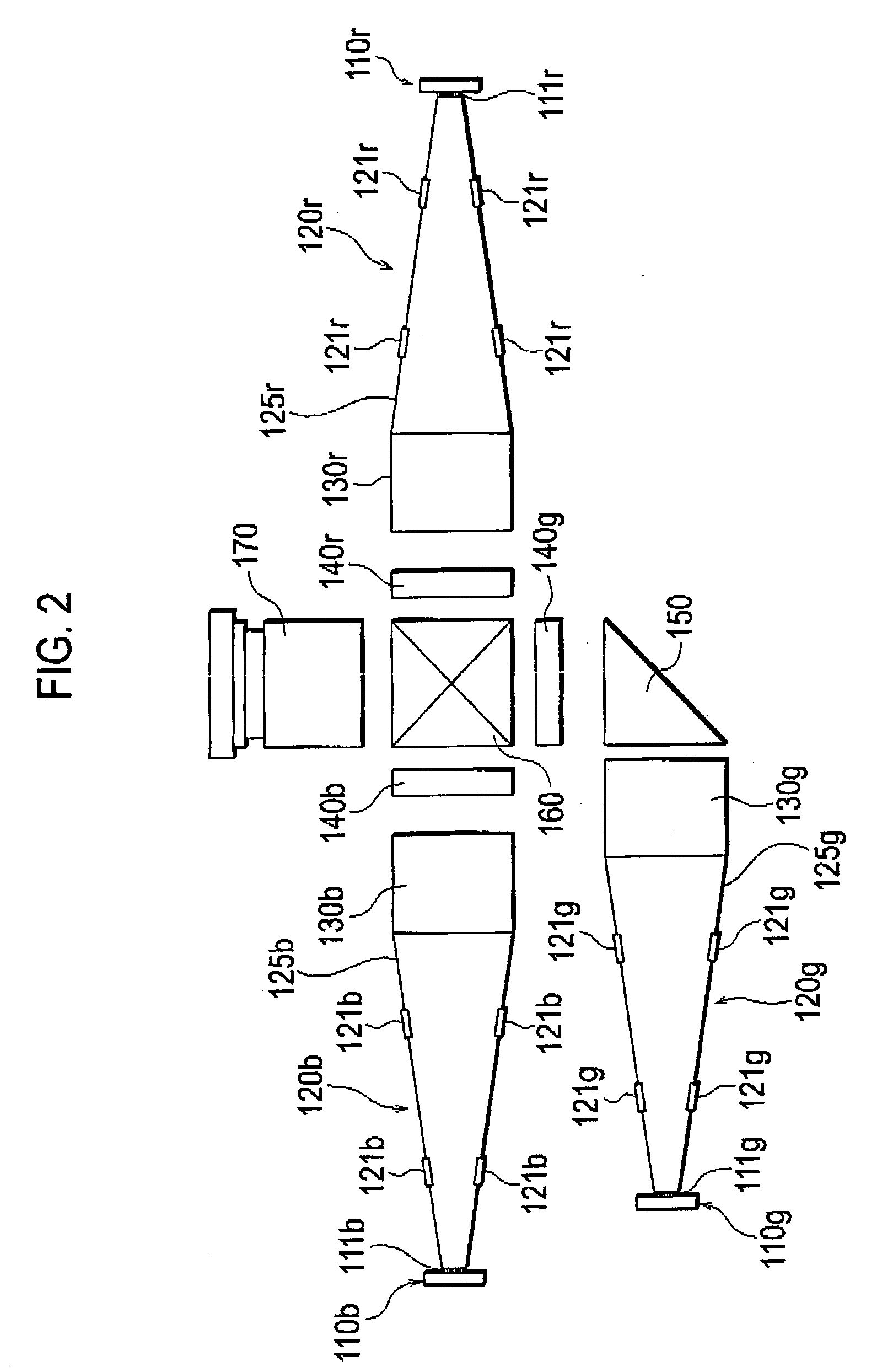

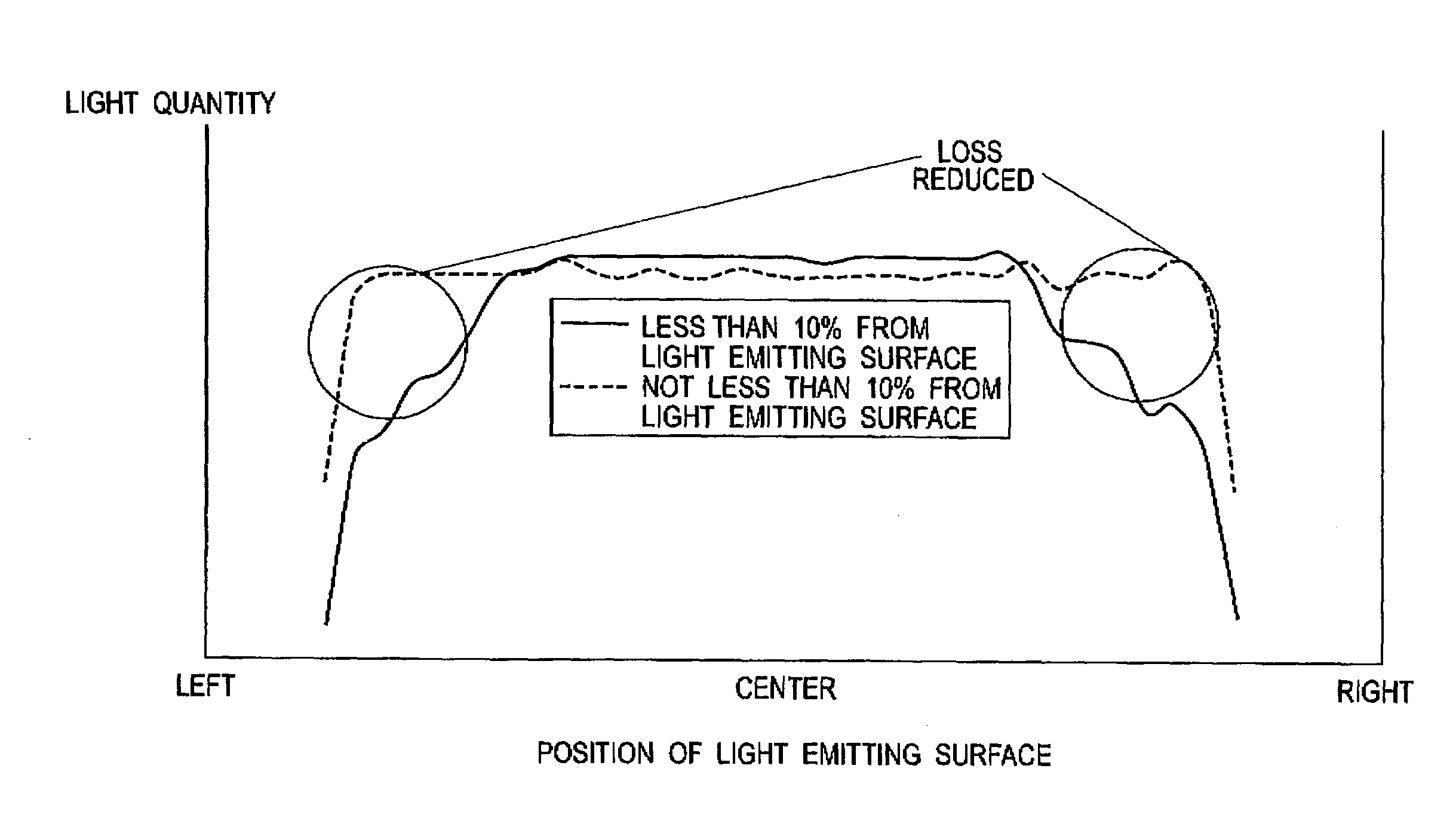

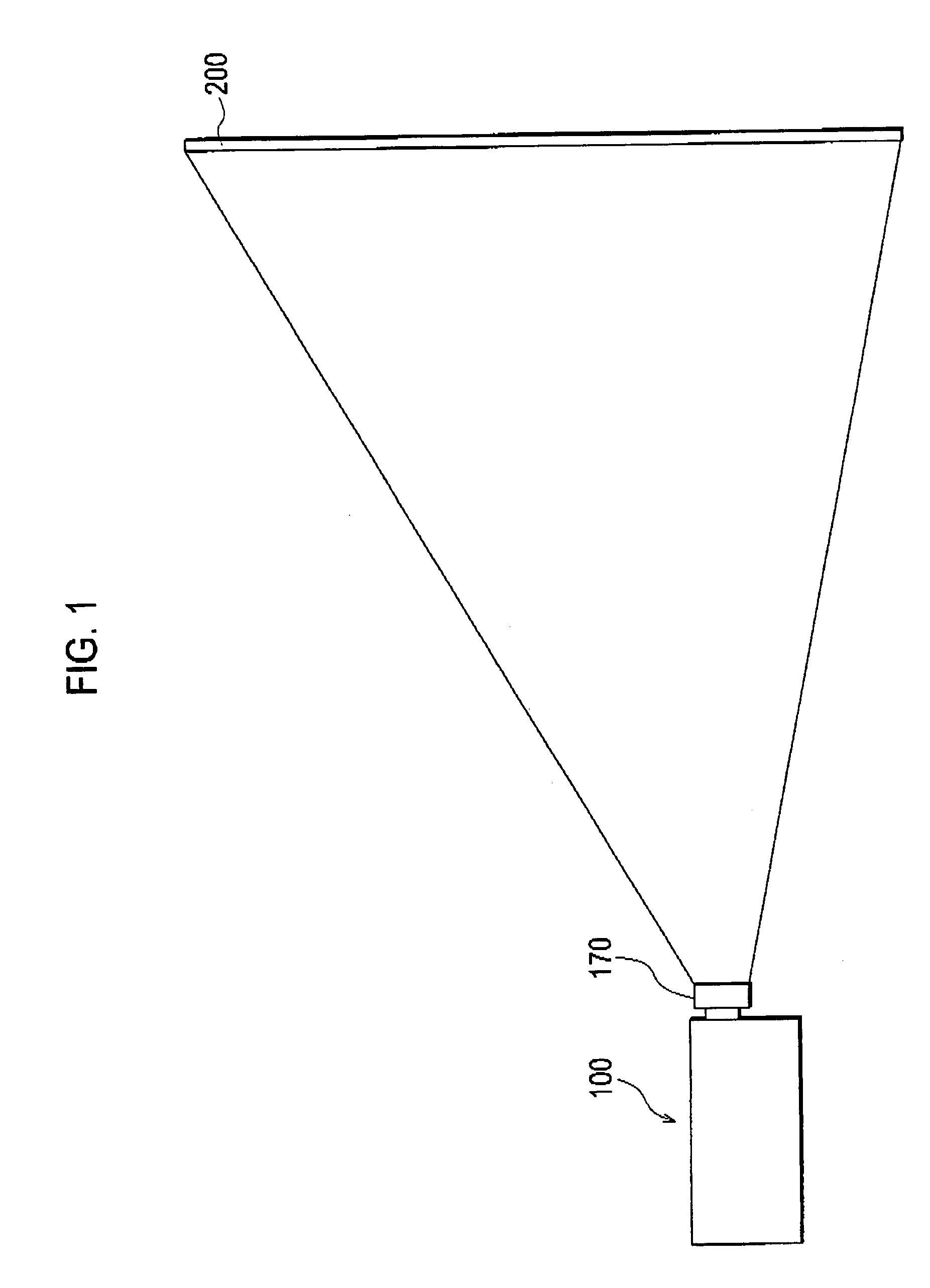

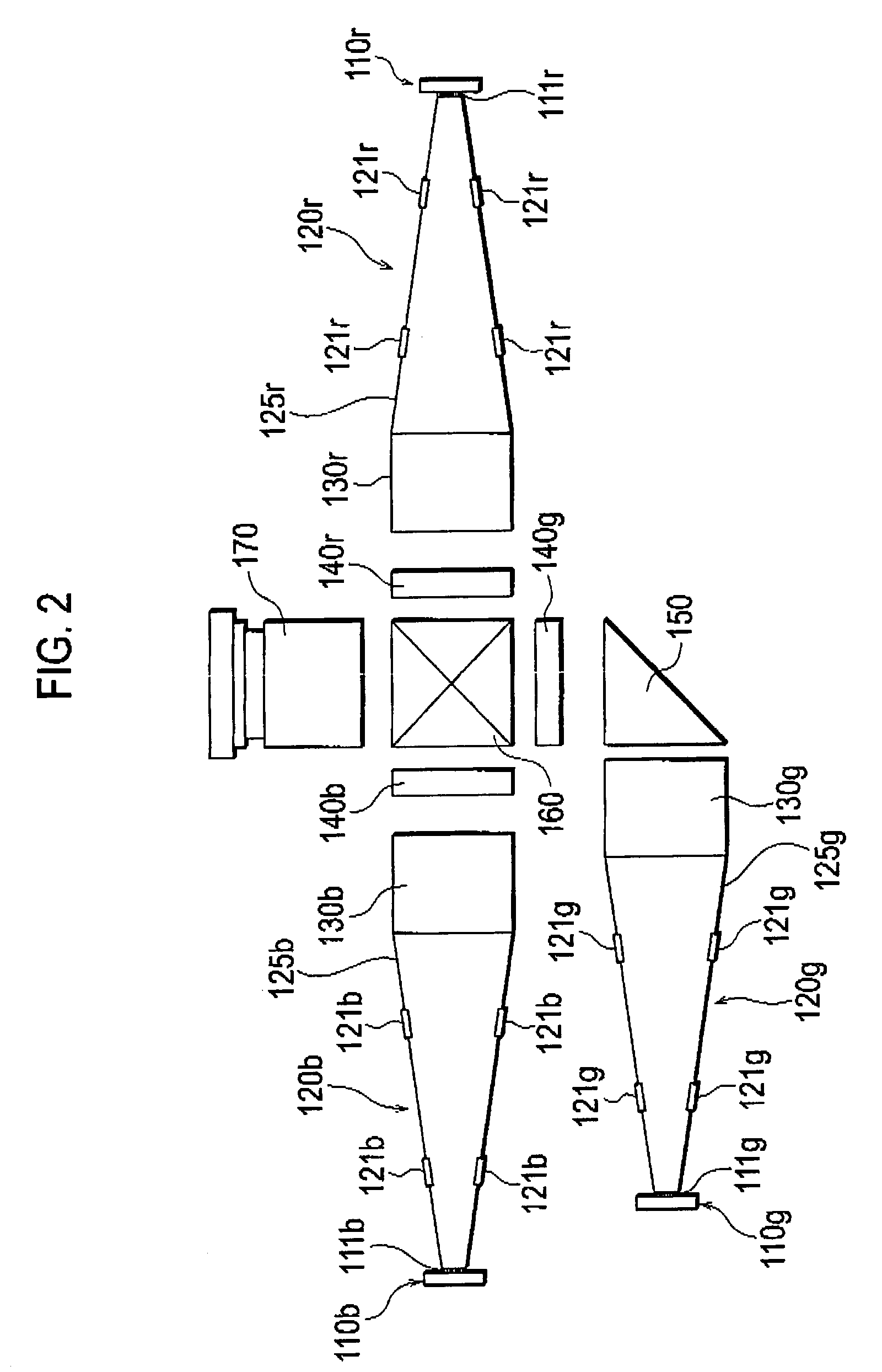

Optical device and projection-type image display apparatus

InactiveUS20070258058A1Low costReduction in light-use efficiency can be suppressedShow cabinetsAircraft componentsLight reflexOptoelectronics

Owner:SANYO ELECTRIC CO LTD +1

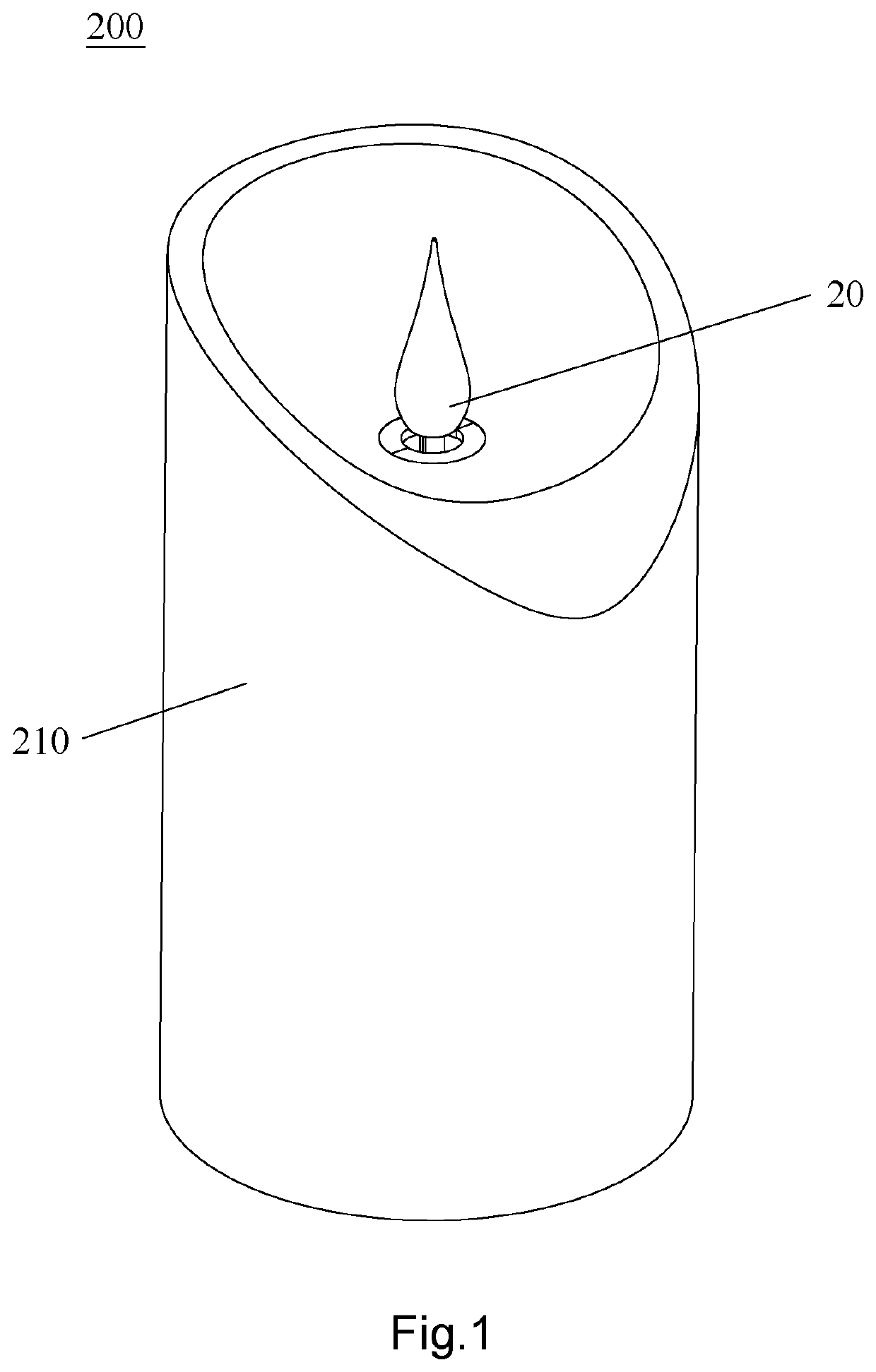

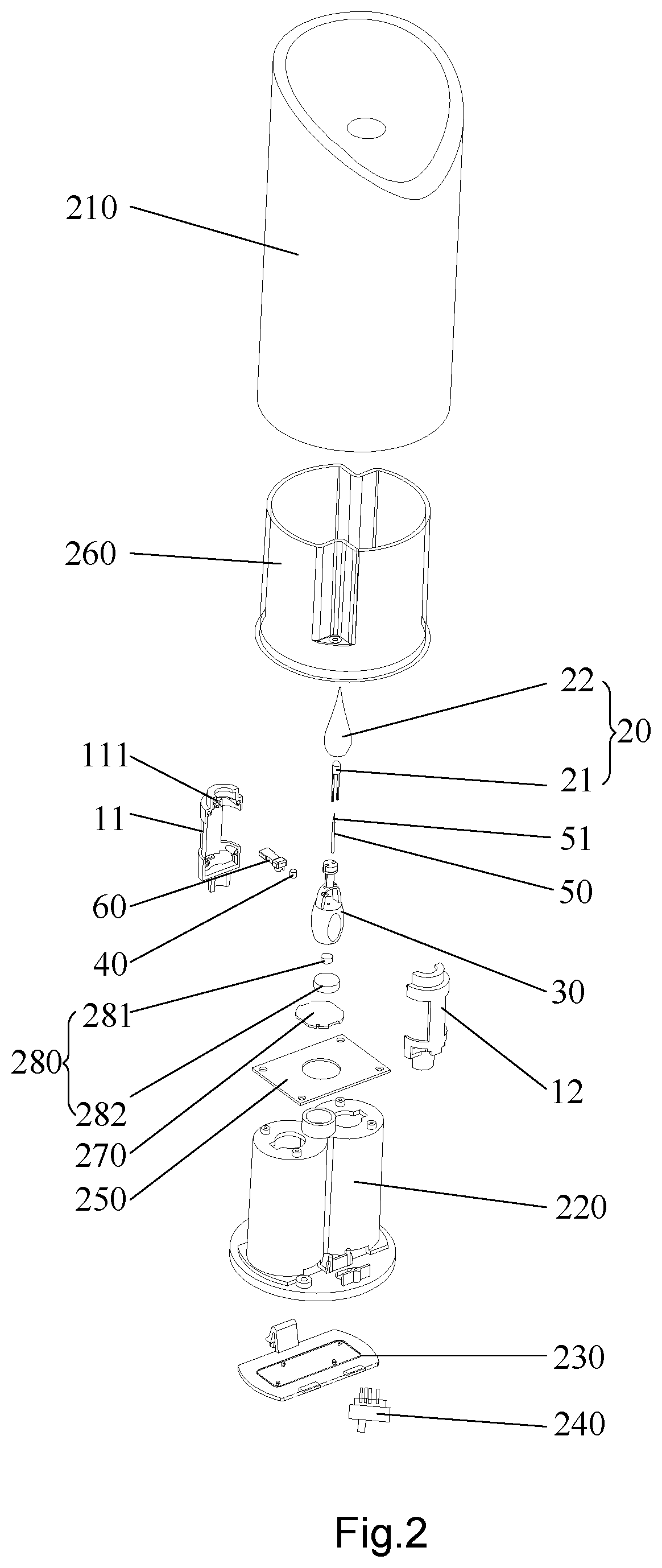

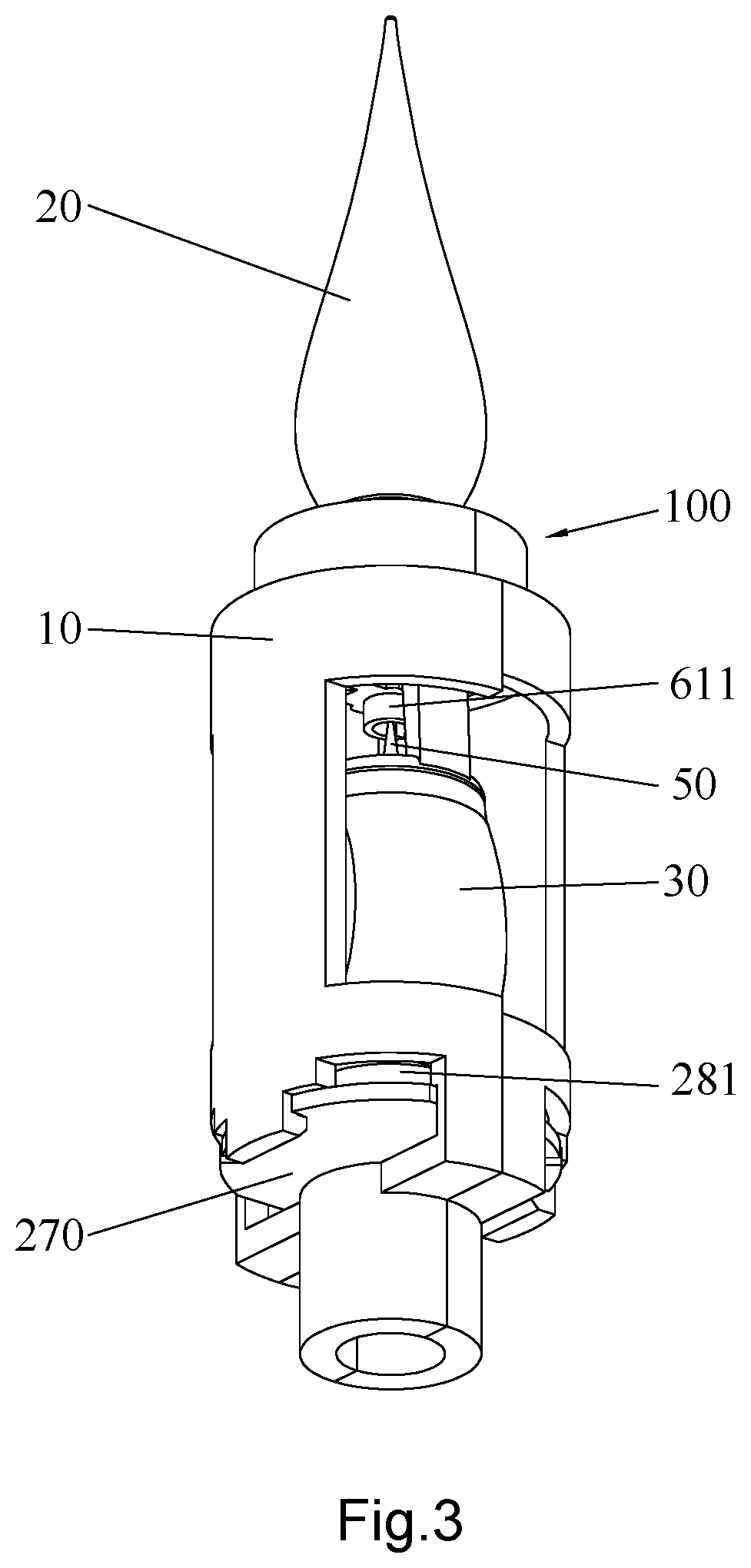

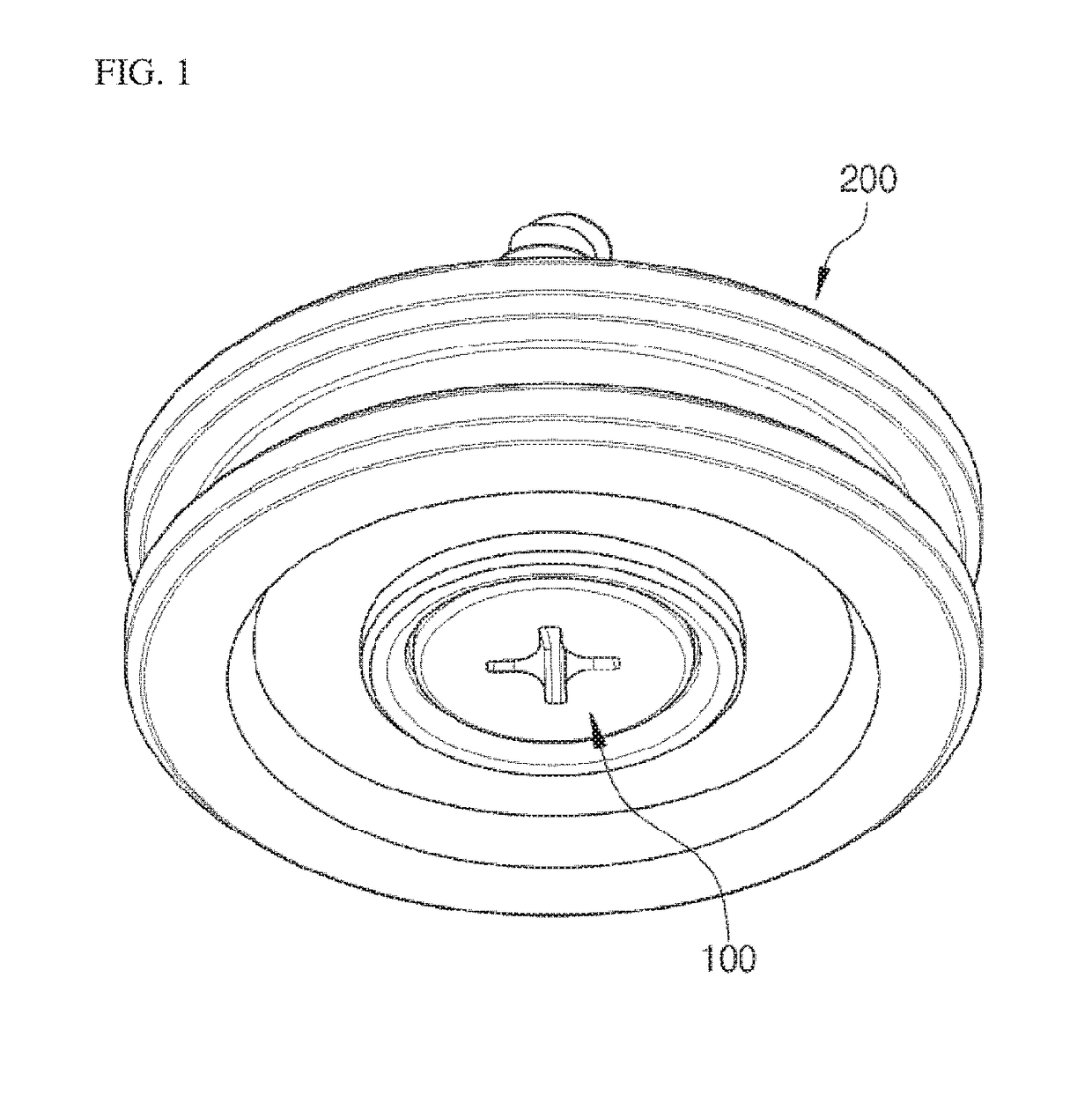

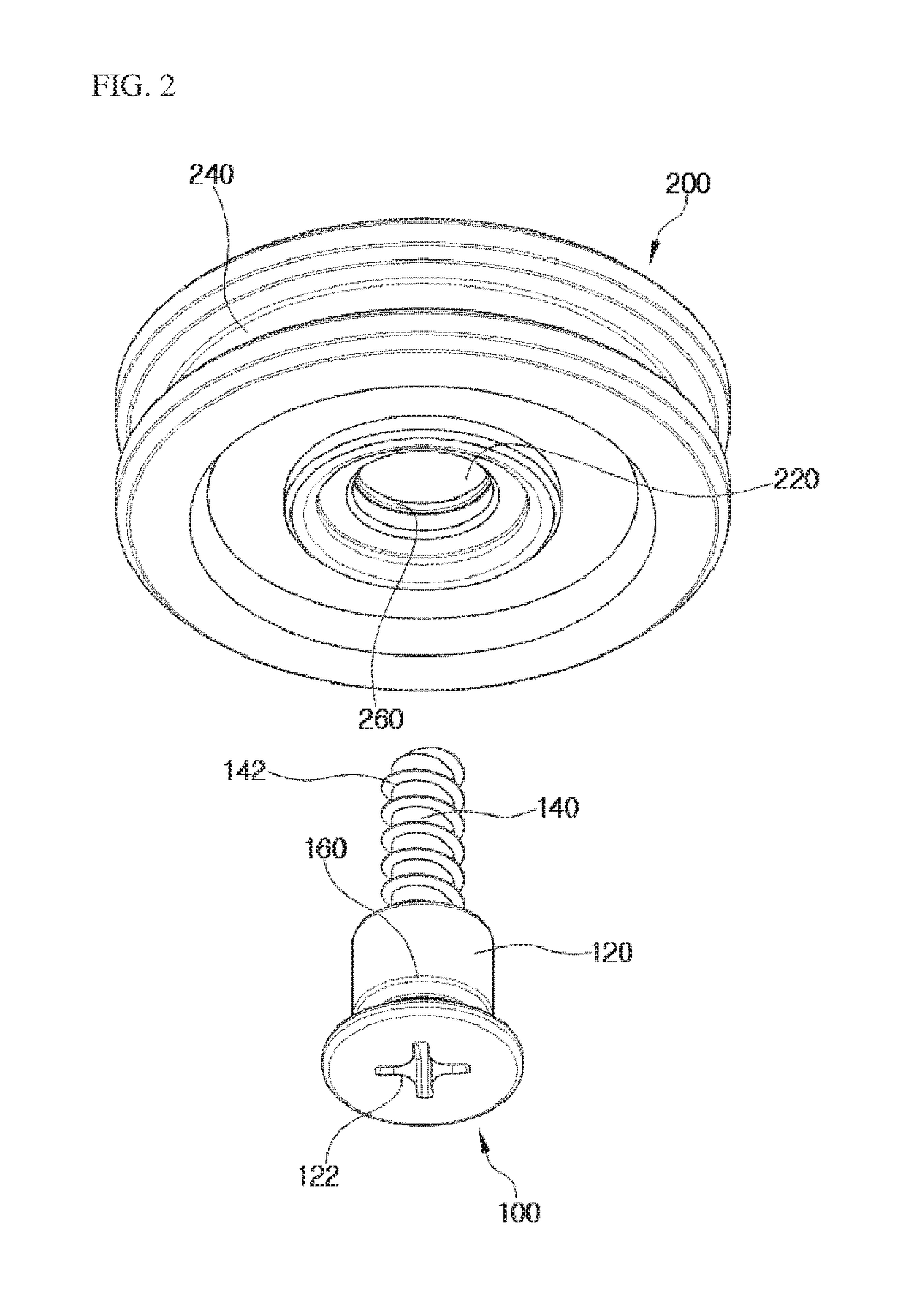

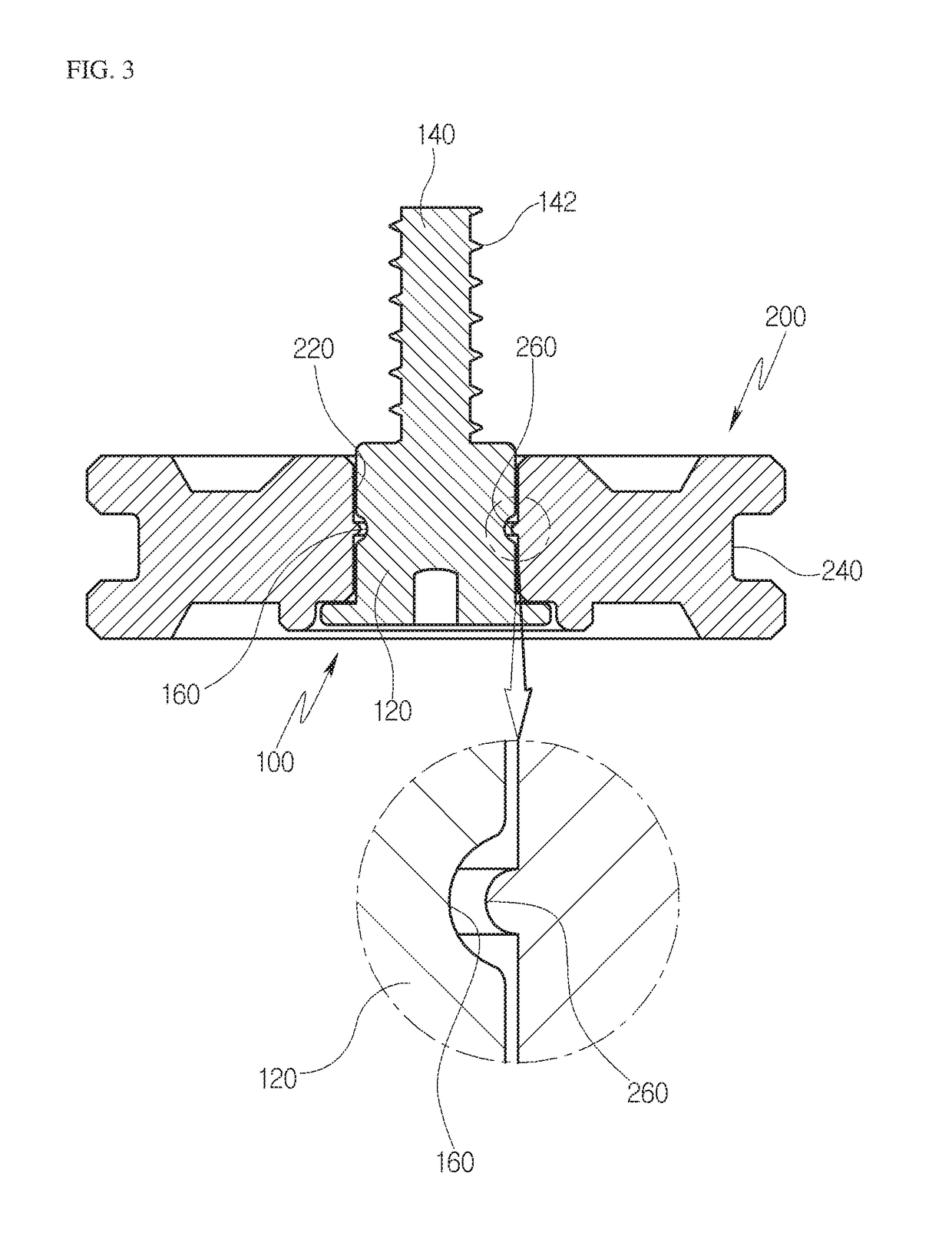

Imitation flame device and imitation flame lamp having the same

ActiveUS10520150B2Good imitation effectSave energyElectric circuit arrangementsLight effect designsSoftware engineeringPoint contact

An imitation flame device includes a base, a flame component, a swing support, a first magnet, and a ferromagnetic element. The swing support is configured in the base, the flame component is fixed on the swing support and protruded out of the base, one of the first magnet and the ferromagnetic element is installed in the base, another of the first magnet and the ferromagnetic element is fixed on the swing support, the first magnet and the ferromagnetic element are attracted each other to cause the swing support to suspend within the base, and the first magnet and the ferromagnetic element are in point contact. The device shows flaming effect of faux flame to achieve an excellent imitation effect and saves energy.

Owner:SHENZHEN HAOJING IND CO LTD

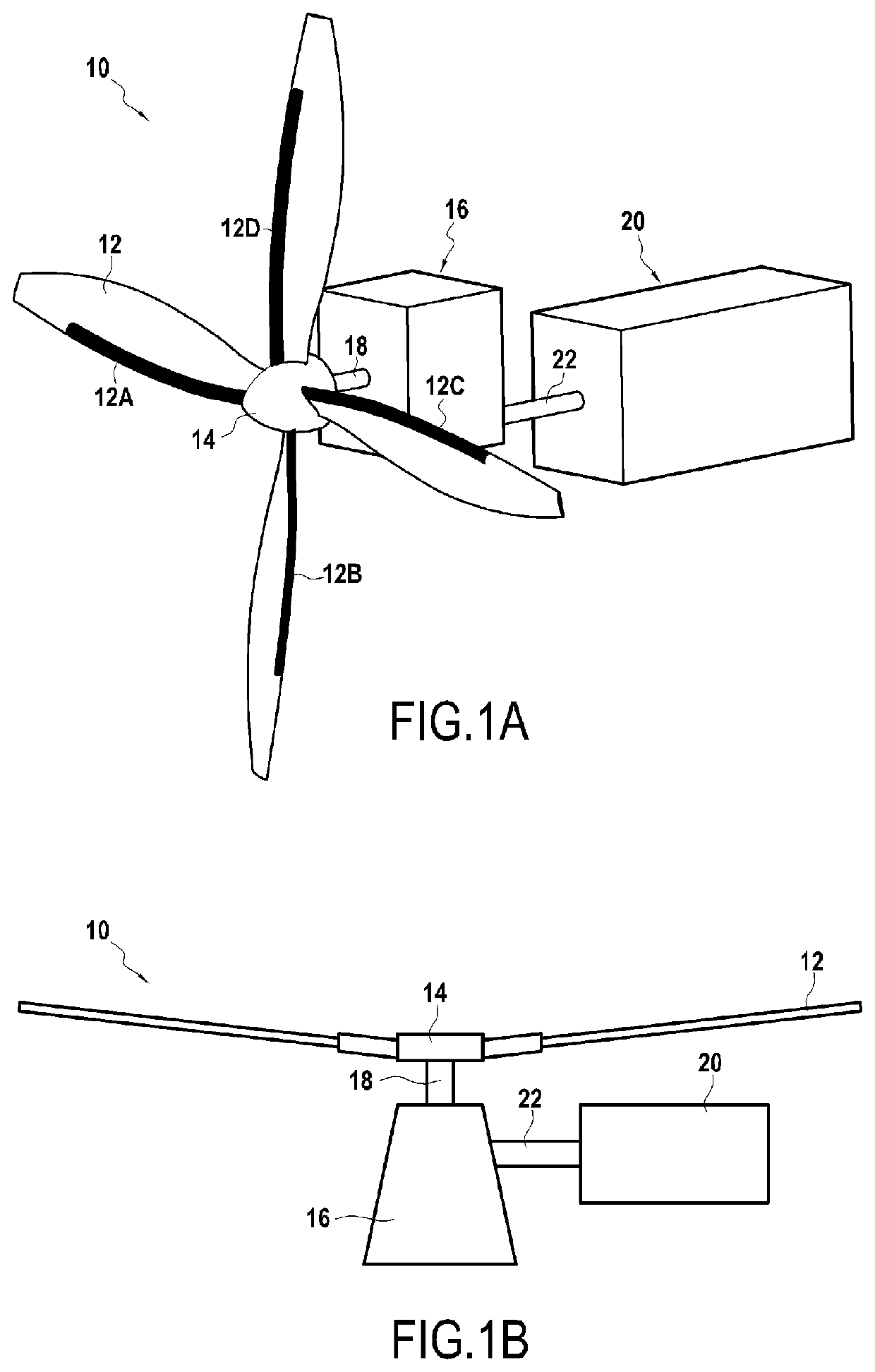

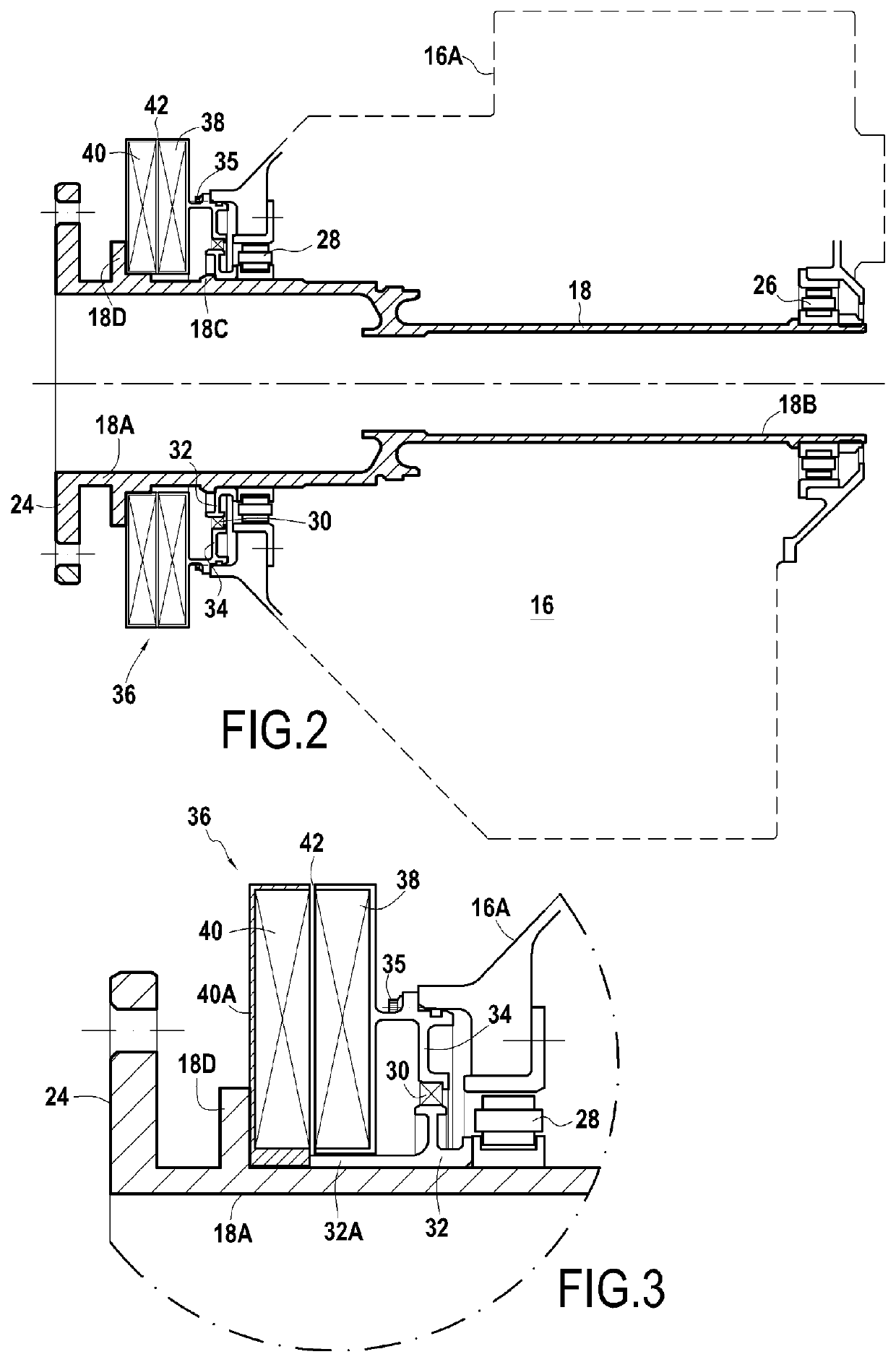

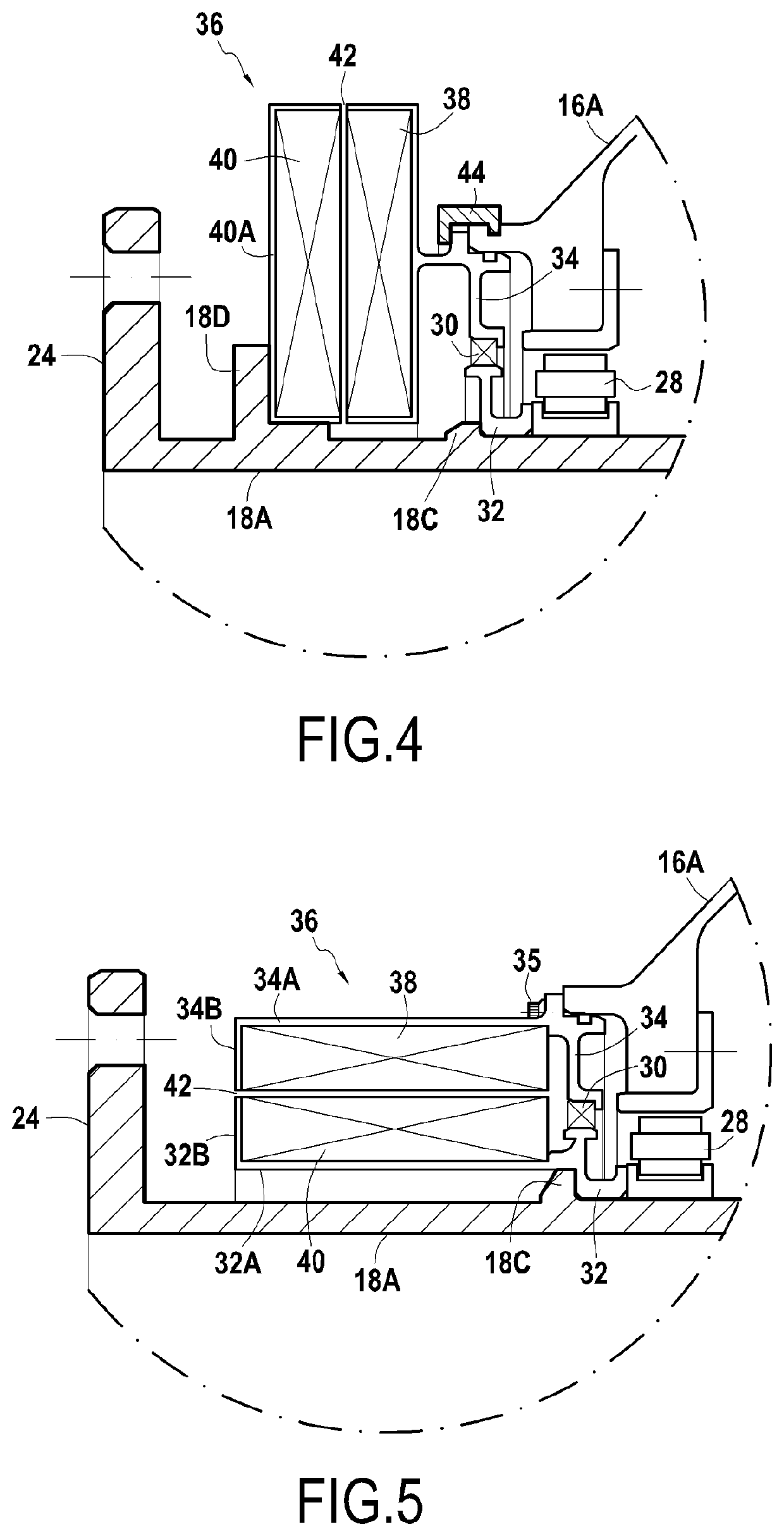

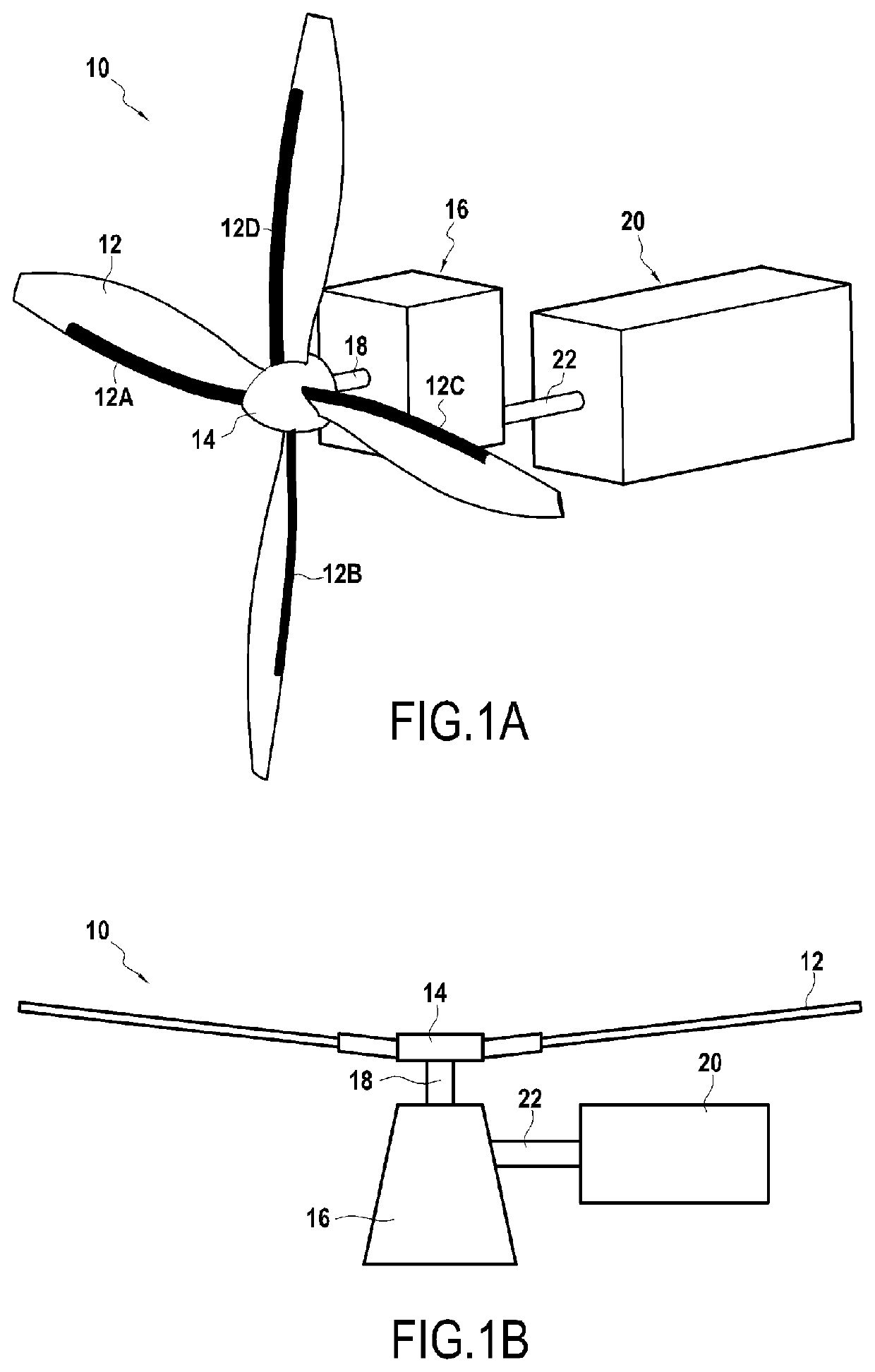

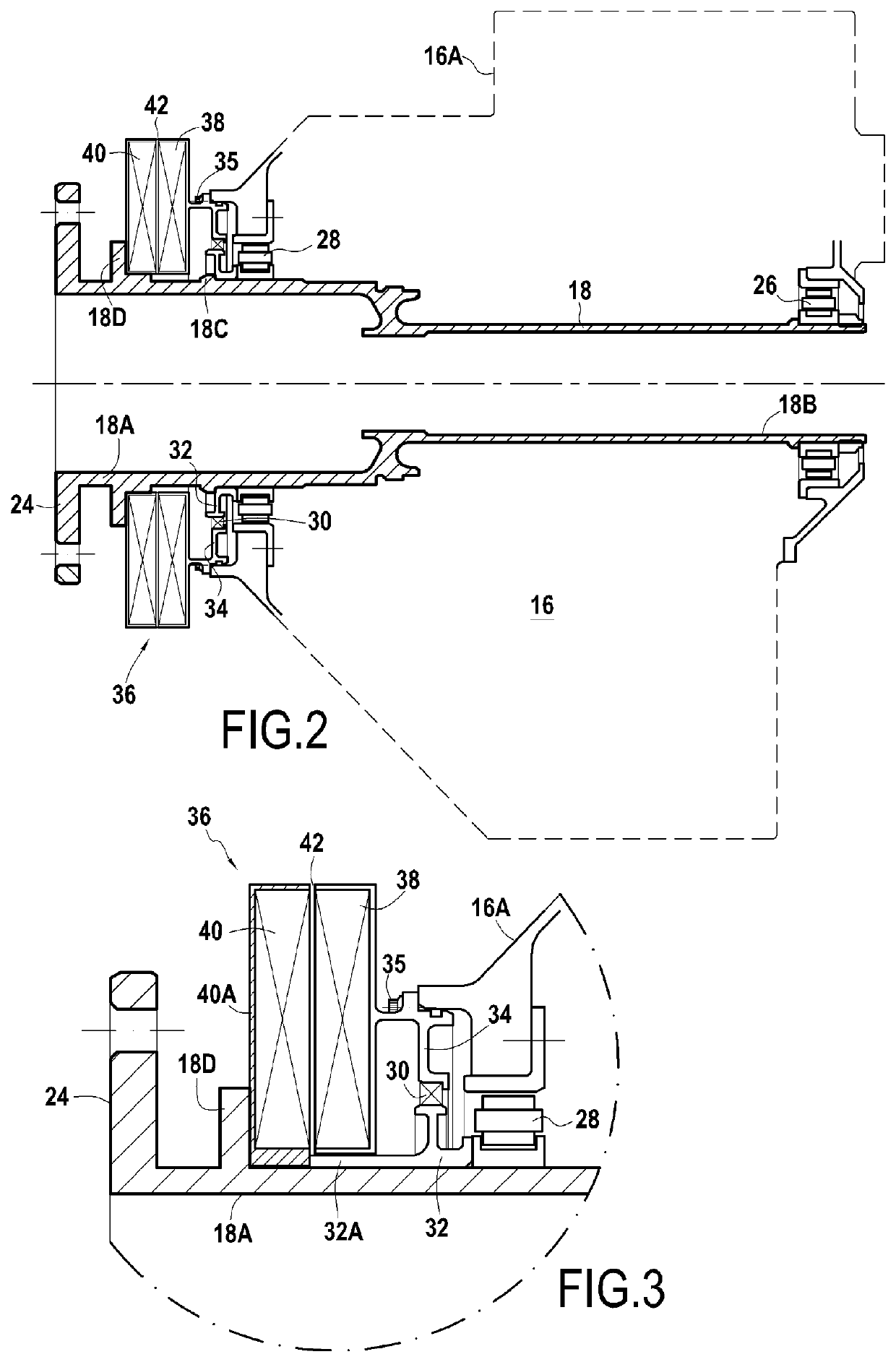

Aircraft propulsion assembly provided with a rotary transformer for supplying the blades with electrical energy

ActiveUS11370551B2Reduce air gapLimited supportElectric power distributionPropellersDrive shaftPropeller

A propulsion unit for an aircraft, including an engine and a propeller shaft and further a propeller with airfoils which is coupled to the propeller shaft and having electrical members consuming electrical power, sealing between a case and the propeller shaft being ensured by a dynamic seal housed between a rotating dynamic seal support secured to the propeller shaft and a dynamic seal support flange secured to an end portion of the case, the rotating dynamic seal support being secured to the propeller shaft and abutted against a bearing for supporting this propeller shaft, it is provided that the propulsion unit, in order to deliver electrical power to the electrical members, having a rotating transformer rotated by the propeller shaft and including a stator, a casing of which is secured to the dynamic seal support flange and a rotor, a casing of which is secured to this propeller shaft.

Owner:SN DETUDE & DE CONSTR DE MOTEURS DAVIATION S N E C M A +2

Optical device and projection-type image display apparatus

InactiveUS8511831B2Low costLight-reflecting side surface will be scratched can be loweredAircraft componentsShow cabinetsOptoelectronicsImage display

Owner:SANYO ELECTRIC CO LTD +1

Aircraft propulsion assembly provided with a rotary transformer for supplying the blades with electrical energy

ActiveUS20210061479A1Small modificationReduce air gapPropellersElectric power distributionPropellerAutomotive engineering

A propulsion unit for an aircraft, including an engine and a propeller and further a propeller with airfoils which is coupled to the propeller shaft and having electrical members consuming electrical power, sealing between a case and the propeller shaft being ensured by a dynamic seal housed between a rotating dynamic seal support secured to the propeller shaft and a dynamic seal support flange secured to an end portion of the case, the rotating dynamic seal support being secured to the propeller shaft and abutted against a bearing for supporting this propeller shaft, it is provided that the propulsion unit, in order to deliver electrical power to the electrical members, having a rotating transformer rotated by the propeller shaft and including a stator, a casing of which is secured to the dynamic seal support flange and a rotor, a casing of which is secured to this propeller shaft.

Owner:SN DETUDE & DE CONSTR DE MOTEURS DAVIATION S N E C M A +2

Roller unit for drawer

ActiveUS10143305B2Reduce in quantityImprove AssemblabilityLinear bearingsCastorsEngineeringMechanical engineering

Owner:SEGOS

Gear box, driving device, and electronic apparatus

ActiveUS10670134B2Suppress lead to damageLimited supportGearboxesToothed gearingsStructural engineeringPinion

A gear box includes a casing having a partition portion, a supporting shaft fixed to the partition portion, and an output shaft supported so as to be rotatable around the supporting shaft and to which a pinion gear is fixed. The casing has a division wall that is positioned in the −Z direction with respect to the partition portion and is capable of abutting against the supporting shaft. The division wall constitutes a portion of a motor accommodation portion for accommodating a motor.

Owner:SEIKO INSTR INC

Rotating electrical machine

A rotating electrical machine includes a stator and a rotor arranged to rotate inside the stator. The rotor includes a plurality of permanent magnets arranged to produce a radial magnetic flux in an airgap between the rotor and the stator. The machine also includes a stationary excitation coil. The rotor also includes a plurality of low reluctance elements. A current through the stationary excitation coil causes a magnetic flux to be established in a magnetic flux path which passes into the rotor through a first low reluctance element and out of the rotor through a second low reluctance element, which magnetic flux combines with the radial magnetic flux produced by the permanent magnets in the airgap. This arrangement can allow control of the field within a permanent magnet radial flux machine.

Owner:CUMMINS GENERATOR TECH LTD